1

∑ Fabricated with RICMOS

TM

IV Bulk CMOS

0.8

µ

m Process (L

eff

= 0.65

µ

m)

∑ CMOS Compatible I/O

∑ Single 5V + 10% Power Supply

FEATURES

DUAL RATE 1773 FIBER OPTIC TRANSCEIVER

HC1773

The HC1773 chip is intended to be used in a hybrid package

with a photo diode, a transimpedance amplifier, a crystal

and an LED or laser diode. Interfacing is intended to be via

a protocol chip. Information is transmitted over the fiber

optic cable in either 1Mbps or 20Mbps 1773 format. The

transceiver chip recovers clock and data from the transim-

pedance amplifier's output for 20Mbps data, but only recov-

ers the data in the 1Mbps mode. The transceiver chip does

not decode the Manchester data, but instead treats the

1Mbps Manchester data as 2Mbps NRZ data, and the

20Mbps Manchester data as 40Mbps NRZ data. An LED or

laser diode is also driven with data received from the

protocol chip.

GENERAL DESCRIPTION

∑

1Mbps or 20Mbps 1773 format

∑

Total Dose Hardness of

3x10

5

rad(SiO

2

)

∑

No Latchup

Advance Information

Military & Space Products

FUNCTIONAL DIAGRAM

Data Rate Detector

Transmitter Switch

2:1 MUX

Oscillator/PLL

40 MHz Crystal

Clock

Rate Out

Rate Select

Receive Data

Receive Clock

Transmit Data

Protocol

Chip

Pull Up

Pull Down

1 Mbps Detector

20 Mbps Detector

-

+

The fiber optic transceiver chip consists of five main circuits

as shown in the functional diagram.

∑ Receive post-amplifiers

∑ 1Mbps decision circuit

∑ 20Mbps decision circuit

∑ Data rate detect circuit

∑ Crystal oscillator and frequency multiplier

∑ Transmit switch

A detailed functional description of each circuit is available.

2

HC1773

Helping You Control Your World

Honeywell reserves the right to make changes to any products or technology herein to improve reliability, function or design. Honeywell does not assume any liability

arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.

900176

4/96

To learn more about Honeywell Solid State Electronics Center, visit our web site at

http://www.ssec.honeywell.com

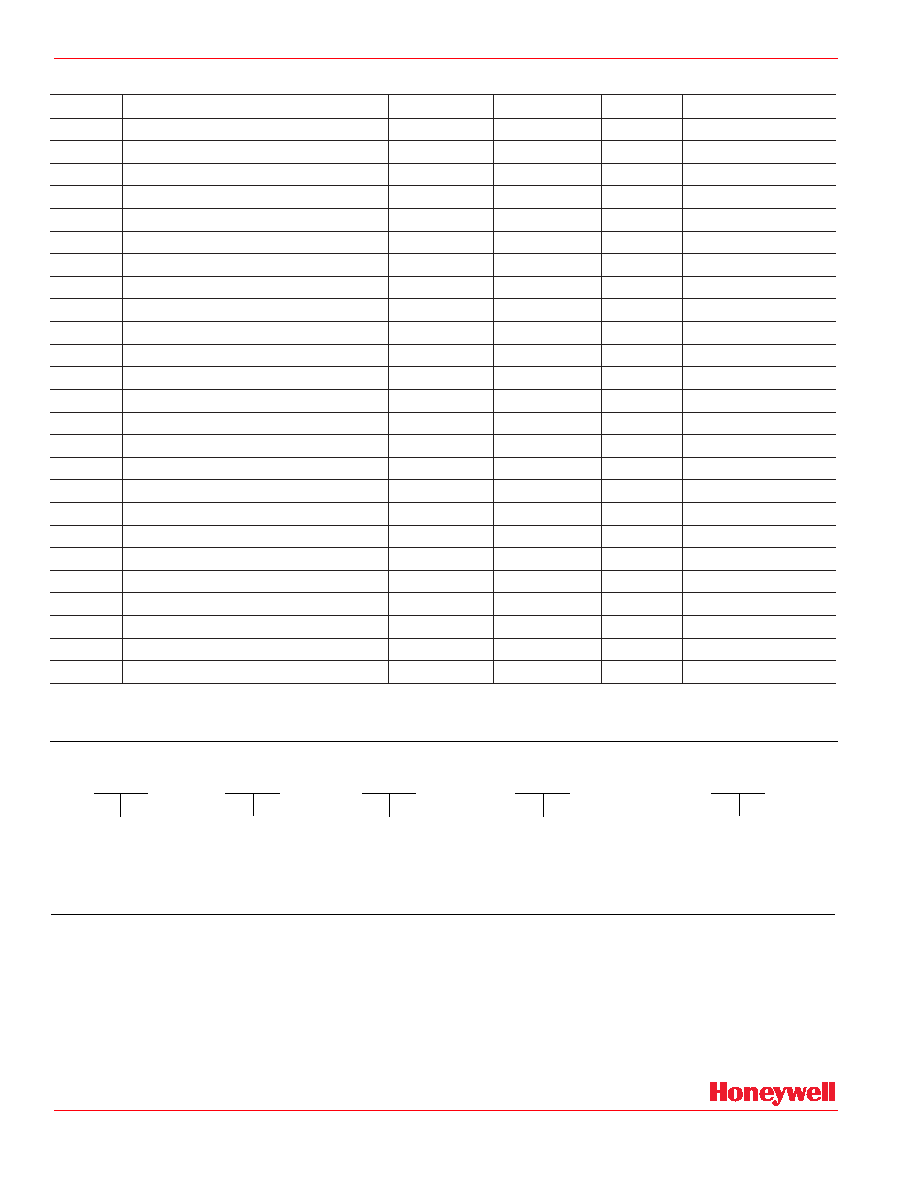

ELECTRICAL CHARACTERISTICS

(1) Worst case operating conditions: VDD=4.5 V to 5.5 V, Die Temp = -55

∞

C, post total dose at 25

∞

C.

(2) Cjo is the zero bias junction capacitance of the LED or laser diode.

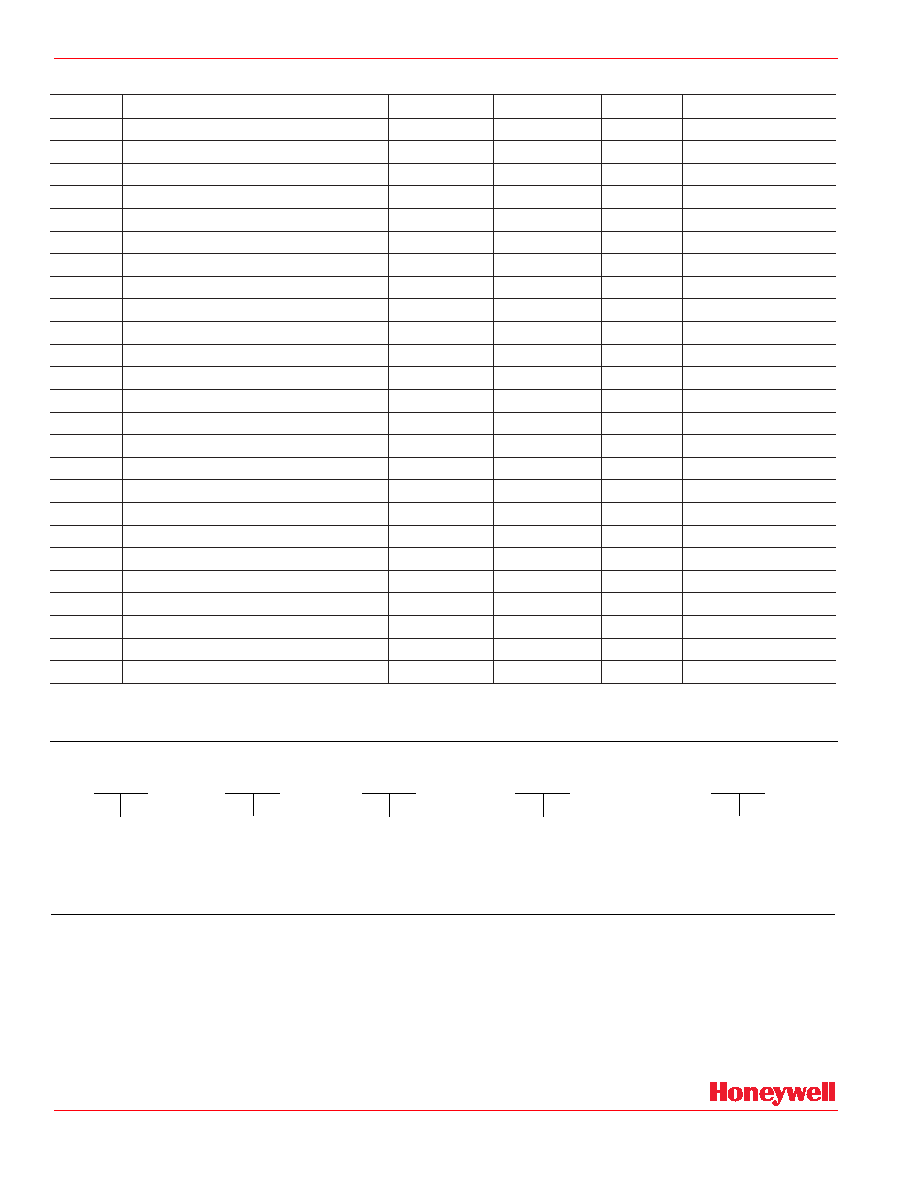

ORDERING INFORMATION (1)

PART NUMBER

1773

C

H

PROCESS

C=Bulk CMOS

(1) Orders may be faxed to 612-954-2051. Please contact our Customer Logistics Department at 612-954-2888 for further information.

(2) Parts are delivered in die form.

(3) Engineering Device description: Parameters are tested from -55 to 125

∞

C, 24 hr burn-in, no radiation guaranteed.

Contact Factory with other needs.

R

TOTAL DOSE

HARDNESS

R=1x10

5

rad(SiO

2

)

F=3x10

5

rad(SiO

2

)

N=No Level Guaranteed

S

SCREEN LEVEL (2)

S=Class S Visual

B=Class B Visual

E=Engr Device (3)

SOURCE

H=HONEYWELL

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

n

i

M

x

a

M

s

t

i

n

U

s

n

o

i

t

i

d

n

o

C

L

I

V

e

g

a

t

l

o

v

t

u

p

n

I

l

e

v

e

L

-

w

o

L

S

S

V

D

D

V

x

3

.

0

V

H

I

V

e

g

a

t

l

o

V

t

u

p

n

I

l

e

v

e

L

-

h

g

i

H

D

D

V

x

7

.

0

D

D

V

V

L

O

V

e

g

a

t

l

o

v

t

u

p

t

u

O

l

e

v

e

l

-

w

o

L

S

S

V

D

D

V

x

1

.

0

V

A

µ

0

0

5

<

L

O

I

H

O

V

e

g

a

t

l

o

V

t

u

p

t

u

O

l

e

v

e

L

-

h

g

i

H

D

D

V

x

9

.

0

D

D

V

V

A

µ

0

0

5

<

H

O

I

R

H

I

V

e

g

a

t

l

o

V

h

g

i

H

t

u

p

n

I

L

T

T

0

.

2

D

D

V

V

n

i

P

t

e

s

e

R

R

L

I

V

e

g

a

t

l

o

V

w

o

L

t

u

p

n

I

L

T

T

S

S

V

8

.

0

V

n

i

P

t

e

s

e

R

L

I

I

e

g

a

k

a

e

L

t

u

p

n

I

0

.

1

-

0

.

1

+

A

µ

r

T

e

m

i

T

e

s

i

R

t

u

p

t

u

O

0

.

4

s

n

F

p

0

5

<

d

a

o

l

C

f

T

e

m

i

T

l

l

a

F

t

u

p

t

u

O

0

.

4

s

n

F

p

0

5

<

d

a

o

l

C

W

B

B

d

3

p

m

A

-

t

s

o

P

s

p

b

M

0

2

0

5

z

H

M

F

p

0

2

<

d

a

o

l

C

W

B

B

d

3

p

m

A

-

t

s

o

P

s

p

b

M

1

0

5

5

z

H

M

n

i

a

G

p

m

A

-

t

s

o

P

s

p

B

M

0

2

9

3

1

4

B

d

k

1

<

d

a

o

l

R

n

i

a

G

p

m

A

-

t

s

o

P

s

p

b

M

1

9

3

1

4

B

d

k

0

0

1

<

d

a

o

l

R

R

t

u

p

n

I

m

A

-

t

s

o

P

s

p

b

M

0

2

0

0

9

0

0

1

1

n

o

i

t

r

o

t

s

i

D

h

t

d

i

W

e

s

l

u

P

0

2

-

0

2

%

p

a

C

t

u

p

n

I

p

n

I

1

P

0

5

F

n

d

l

o

h

s

e

r

h

T

d

e

x

i

F

s

p

b

M

1

3

.

0

4

.

0

V

k

c

a

t

t

A

t

c

e

t

e

D

k

a

e

P

0

5

s

n

F

p

0

5

1

<

p

a

C

D

P

t

n

e

r

r

u

C

r

e

t

t

i

m

s

n

a

r

T

0

5

1

A

m

V

5

.

0

t

u

o

V

e

m

i

T

e

s

i

R

r

e

t

t

i

m

s

n

a

r

T

2

s

n

)

2

(

F

p

0

5

<

o

j

C

k

l

C

R

d

o

i

r

e

P

0

2

s

n

)

2

(

F

p

0

5

<

o

j

C

e

o

L

h

t

d

i

W

e

s

l

u

P

k

l

C

R

5

s

n

h

g

i

H

h

t

d

i

W

e

s

l

u

P

k

l

C

R

5

s

n

n

o

i

t

p

m

u

s

n

o

C

r

e

w

o

P

0

0

2

W

m

f

f

O

r

e

t

t

i

m

s

n

a

r

T

e

m

i

T

p

U

r

e

w

o

P

1

.

0

c

e

s

m