Microsoft PowerPoint - COVER.PPT

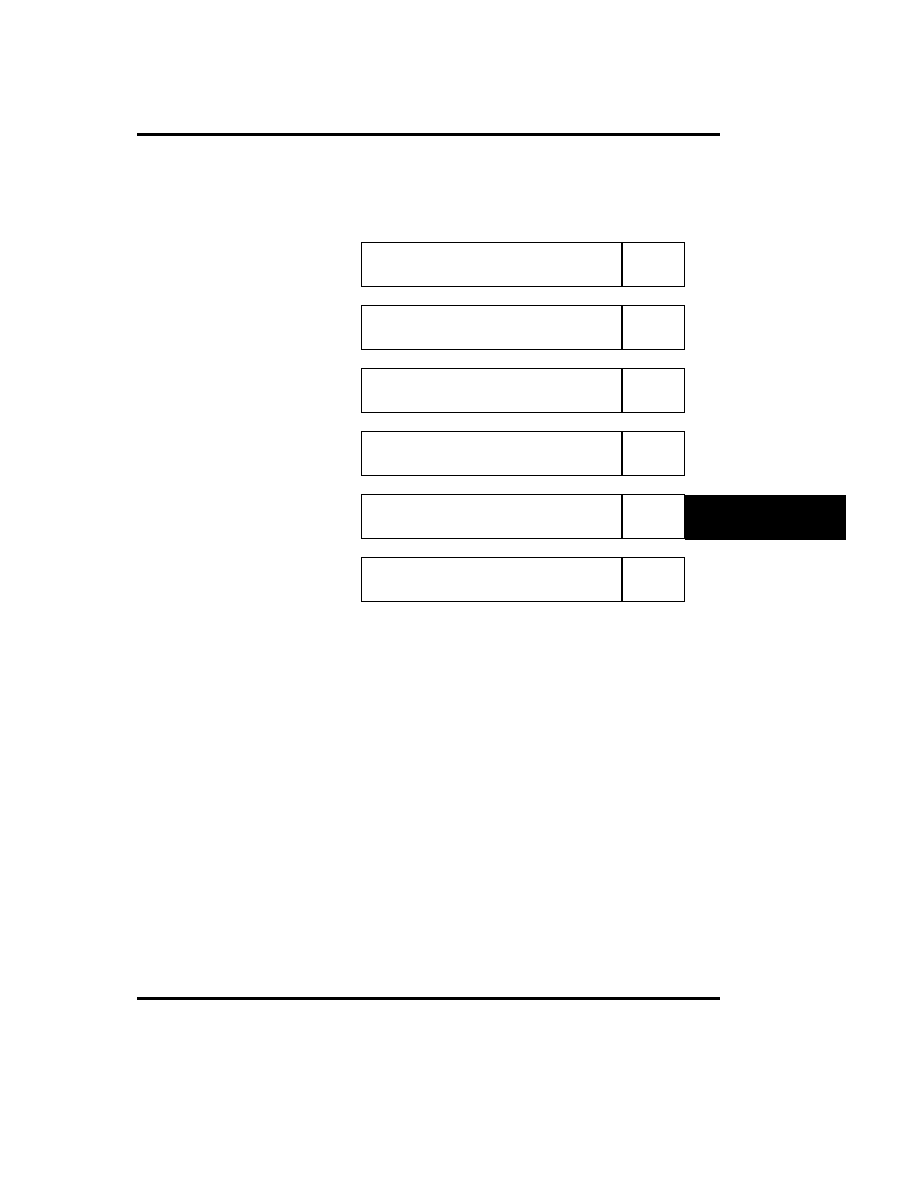

4-BIT SINGLE CHIP MICROCOMPUTERS

GMS300 SERIES

USER`S MANUAL

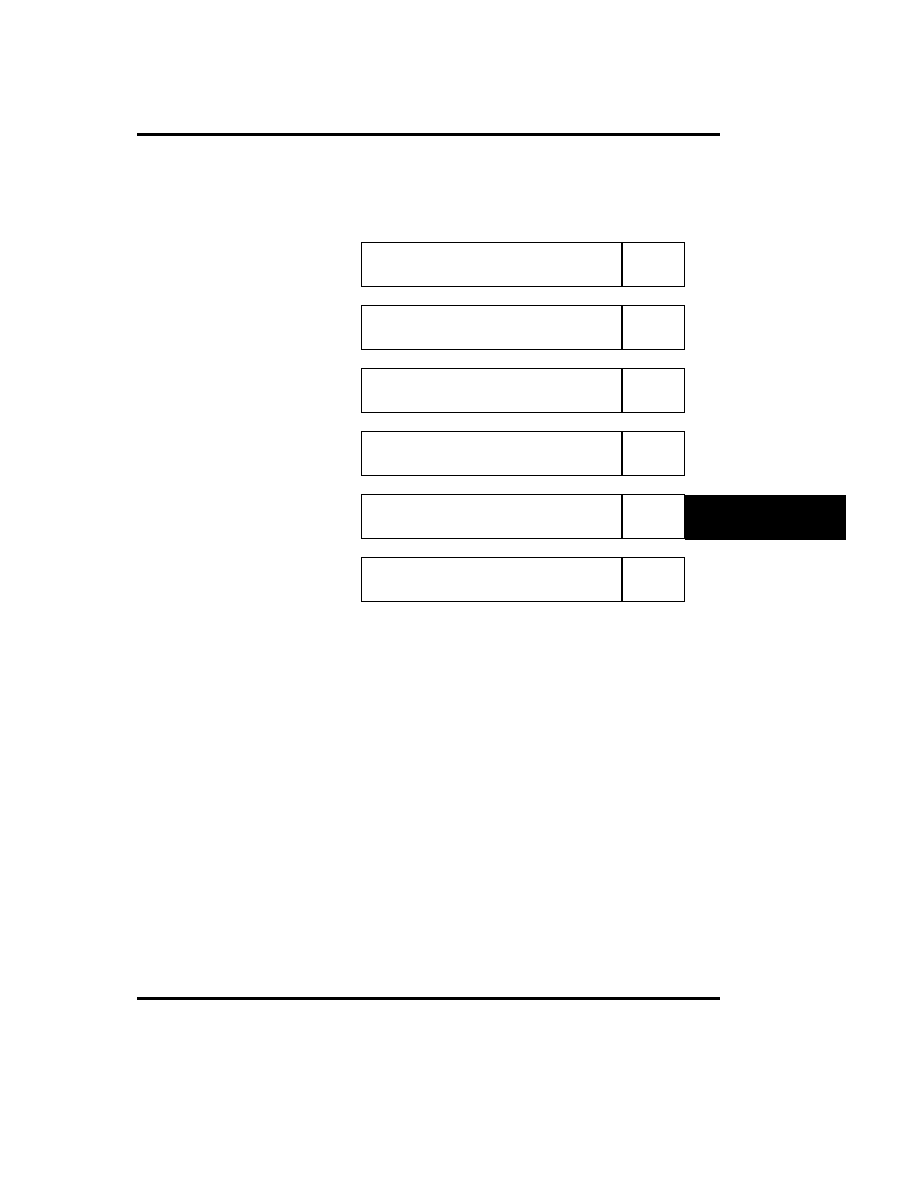

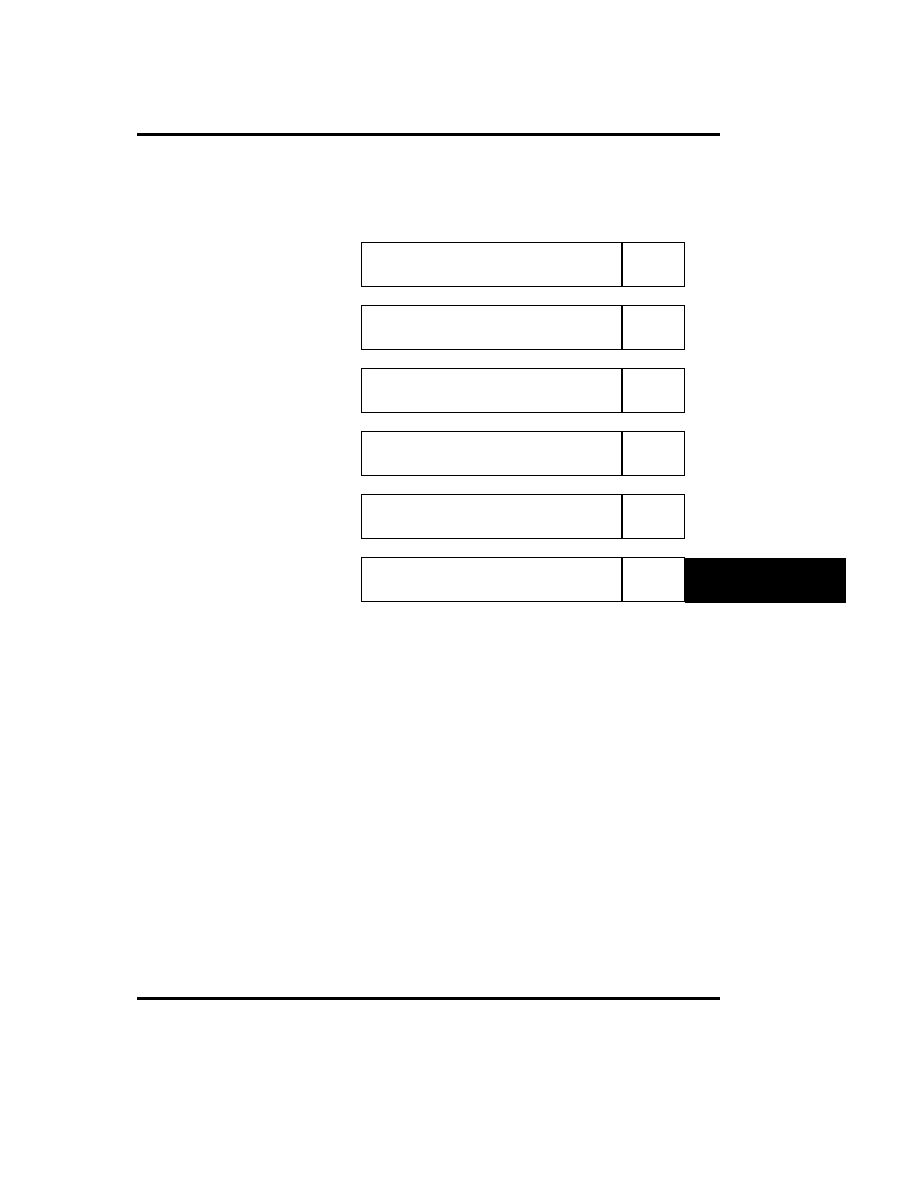

· GMS30004

· GMS30012

· GMS30112

· GMS30120

· GMS30140

· GMS30000 EVA

JUNE. 2001

Rev. 3.2

INTRODUCTION

We hereby introduce the manual for CMOS 4-bit

microcomputer GMS300 Series.

This manual is prepared for the users who should

understand fully the functions and features of

GMS300 Series so that you can utilize this

product to its fullest capacity. A detailed explana-

tions of the specifications and applications regard-

ing the hardware is hereby provided.

The contents of this user`s manual are subject to

change for the reasons of later improvement of

the features.

The information, diagrams, and other data in this

user`s manual are correct and reliable; however,

HYNIX Semiconductor, Inc. is in no way responsible

for any violations of patents or other rights of the

third party generated by the use of this manual

GMS300 SERIES

Revision History: 1997. APR.

Previous Release: 1994.NOV., 1994.JUN., 1994.JAN., 1995.JAN,

1995.AUG., 1996.APR., 1996.JUL.

Page

Subject(Change since last revision)

Appendix

Modification(Magic IIa Removal)

Table of Contents

Table of Contents

Chapter 1

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-1

Outline of Characteristics . . . . . . . . . . . . . . . . . . . . .

1-1

Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-1

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-2

Pin Assignment and Dimension . . . . . . . . . . . . . . . . . . . .

1-3

Electrical Characteristics of GMS300 Series . . . . . . . . . .

1-8

I/O circuit types and options . . . . . . . . . . . . . . . . . . . . . . .

1-10

Masked options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-13

STOP Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-13

Chapter 2

Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-1

Block Description . . . . . . . . . . . . . . . . . . . . . . . . . . .. . .. . .

2-1

Program Memory (ROM). . . . . . . . . . . . . . . . . . . . . . . . .

2-1

ROM Address Register . . . . . . . . . . . . . . . . . . . . . . . . .

2-2

Data Memory (RAM) . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-3

X-Register (X) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-3

Y-Register (Y) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-4

Accumulator (Acc) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-4

Arithmetic and Logic Unit (ALU) . . . . . . . . . . . . . . . . . . .

2-4

I/O circuit . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-4

State Counter (SC) . . . . . . . . . . . .. . . . . . . . . . . . . . . . .

2-5

Clock Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-6

Carrier Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-6

Initial Reset Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-7

Watch Dog Timer (WDT) . . . . . . . . . . . . . . . . . . . . . . . .

2-7

Chapter 3

Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-1

Instruction format . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-1

Instruction Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-2

Details of Instruction System . . . . . . . . . . . . . . . . . . . .

3-5

Detailed Description . . . . . . . . . . . . . . . . . . . . . . .

3-6

Table of Contents

Chapter 4

Evaluation Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-1

Outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-1

Product Specification . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-1

Connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-2

Optional Setting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-3

Caution of Operation . . . . . . . . . . . . . . . . . . . . . .. . . . .

4-6

Chapter 5

Software . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-1

Configuration of Assembler . . . . . . . . . . . . . . . . . . . . . .

5-1

Booting up Assembler . . . . . . . . . . . . . . . . . . . . . . . . .

5-1

Configuration of Simulator . . . . . . . . . . . . . . . . . . . . . . .

5-2

Booting up Simulator . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-2

Simulator commands . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-15

Description of commands . . . . . . . . . . . . . . . . . . . . . . . .

5-18

File types used in the simulator . . . . . . . . . . . . . . . . . . .

5-48

Error message and troubleshooting . . . . . . . . . . . . . . . .

5-49

Appendix

Magic-

é

. . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A-1

Magic- Ia . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B-1

Magic-

ê

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C-1

Magic-

ê

b

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

D-1

Magic-

ë

a .. . . . . . . . . . . . . . . . . . .. . . . . . . . . . .

E-1

Magic-

ë

b . . . . . . . . . . . . . . .. . .. . . . . . . . . . . . ..

F-1

Magic-

ë

c . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

G-1

INTRODUCTION

1

ARCHITECTURE

2

INSTRUCTION

3

EVALUATION BOARD

4

SOFTWARE

5

APPENDIX

6

1 - 1

CHAPTER 1. Introduction

OUTLINE OF CHARACTERISTICS

The GMS300 series is a family of 4-bit, single chip CMOS microcomputer.

Since it can form a system by one chip, it contributes to cost reduction and higher

efficiency in system.

Characteristics

$

Program memory : 512 bytes for GMS30004/012

1024 bytes for GMS30112/120/140

$

Data memory : 32

Ø

4 bits

$

43 types of instruction set

$

3 levels of subroutine nesting

$

1 bit output port for a large current (REMOUT signal)

$

Operating frequency : 300KHz to 1MHz

$

Instruction cycle :

12.5usec @480KHz

$

CMOS process (Single 3.0V power supply)

$

Stop mode (Through internal instruction)

$

Released stop mode by key input (Masked option)

$

Built in capacitor for ceramic oscillation circuit (Masked option)

$

Built in a watch dog timer (WDT)

$

Low operating voltage : (2.0~4.0V)

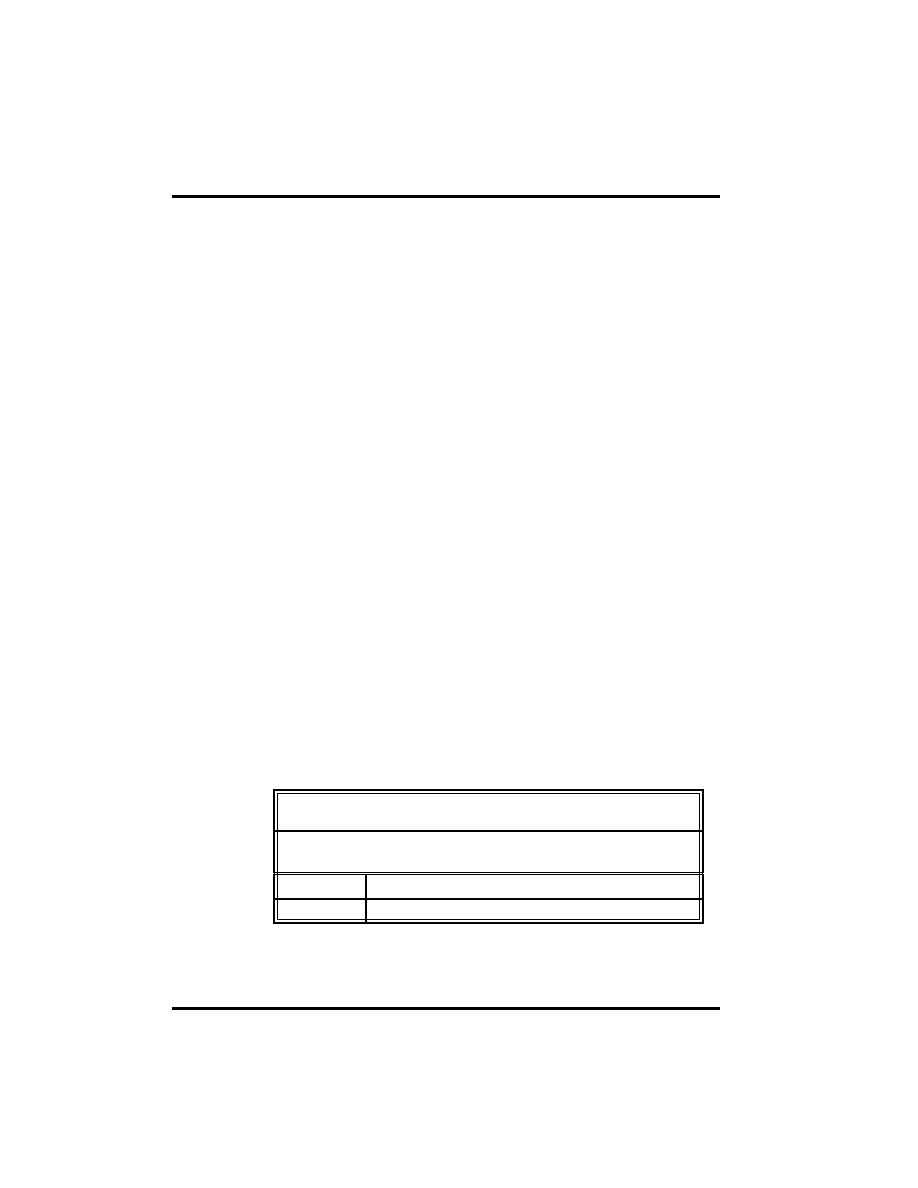

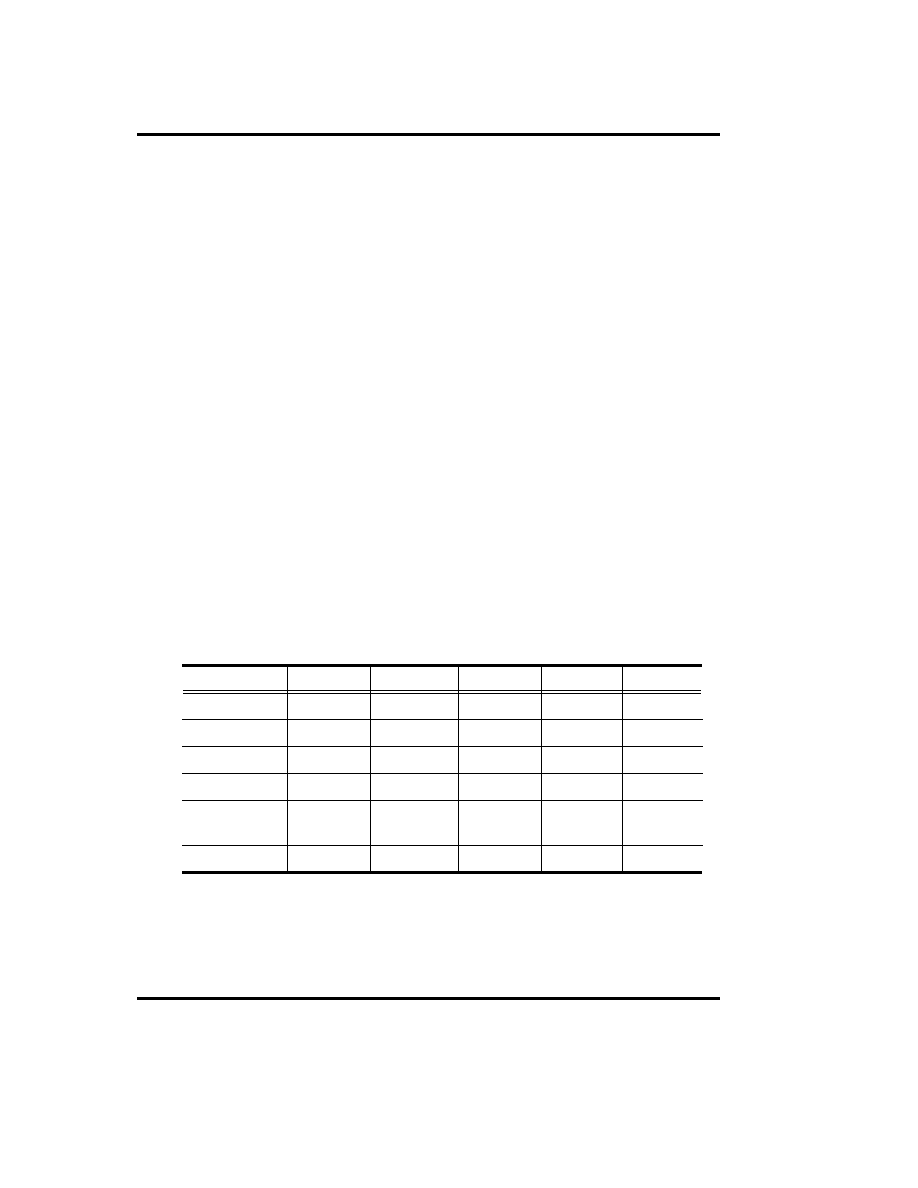

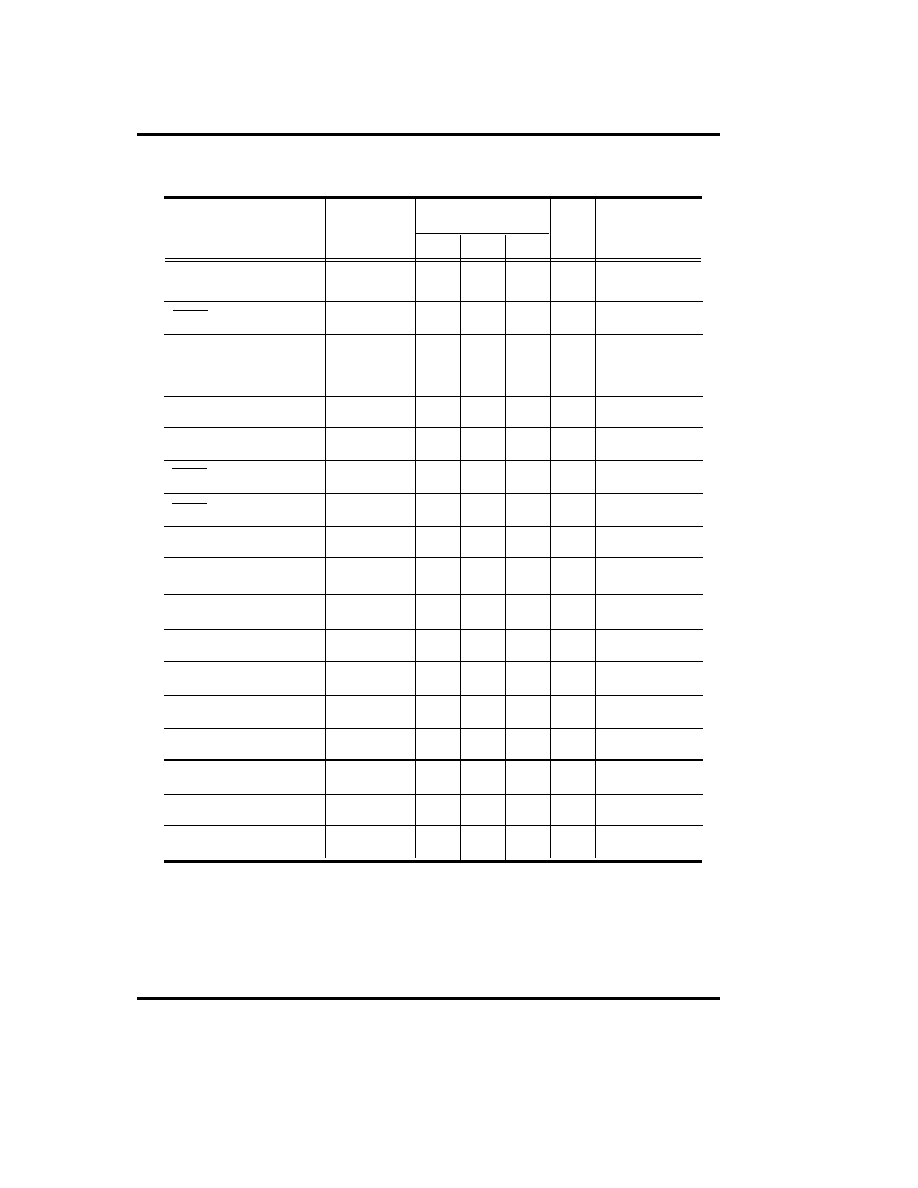

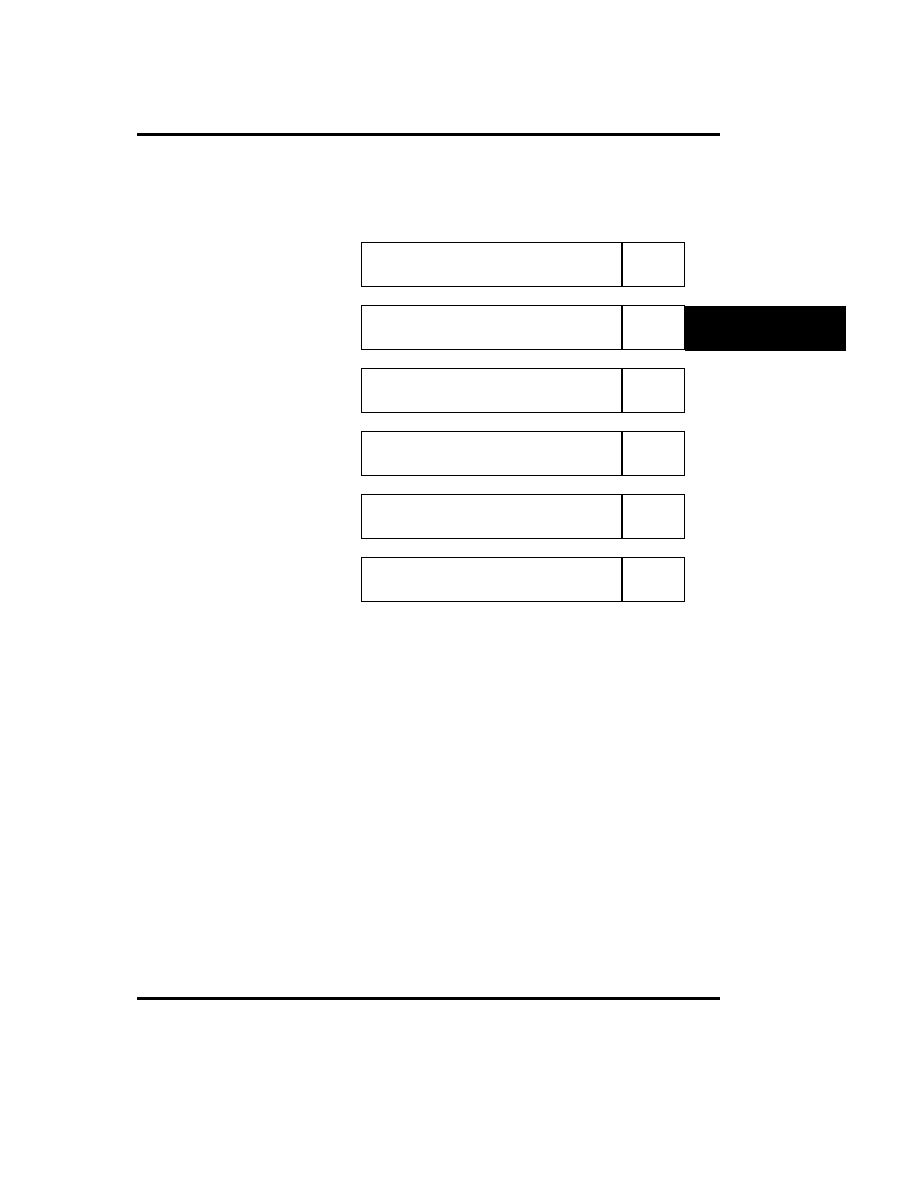

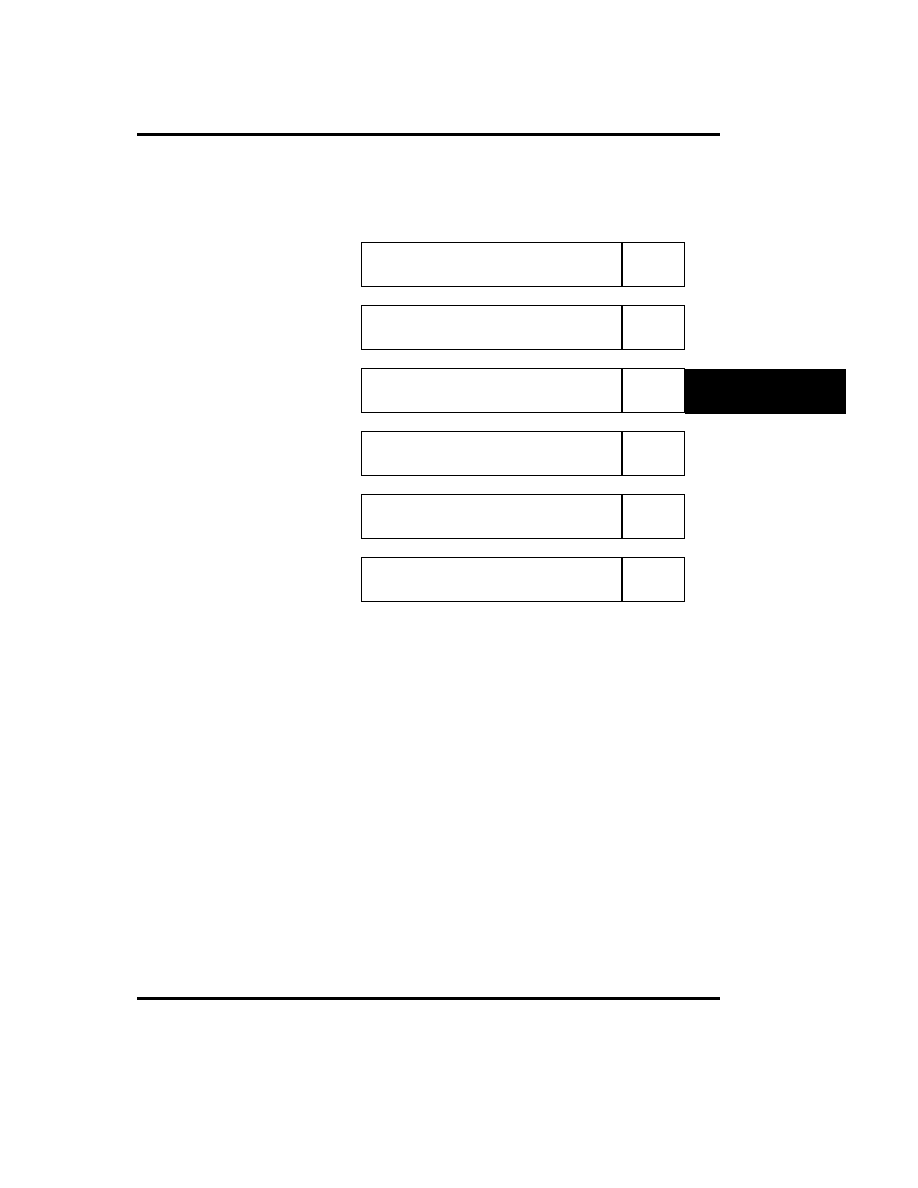

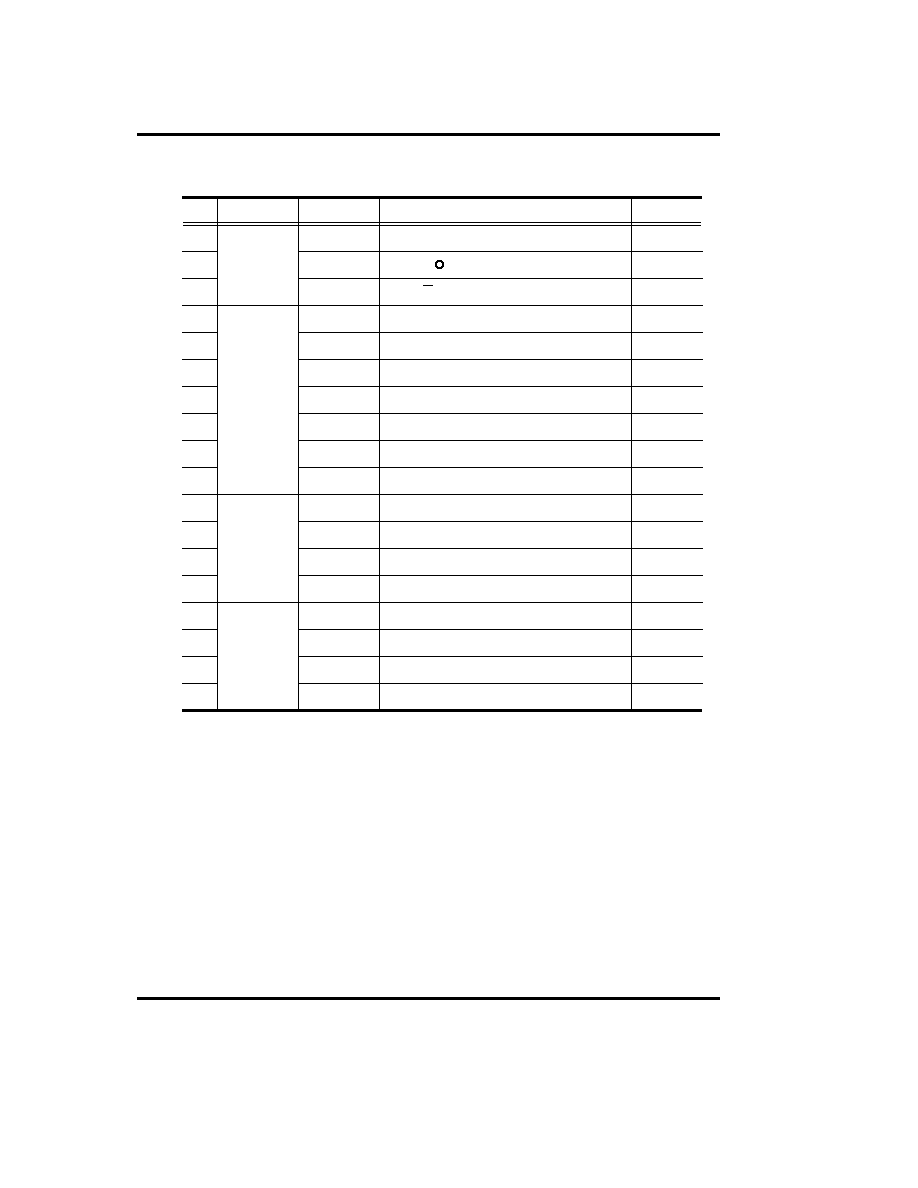

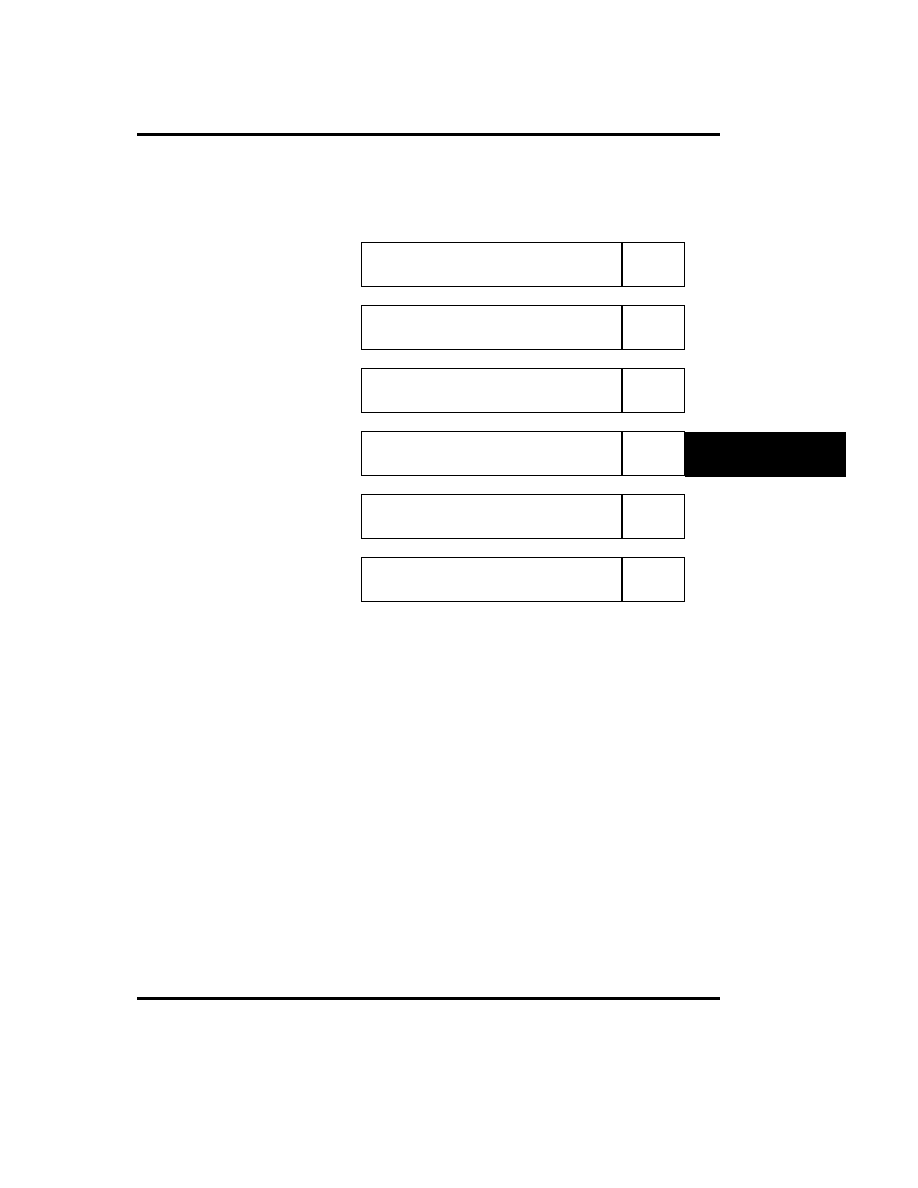

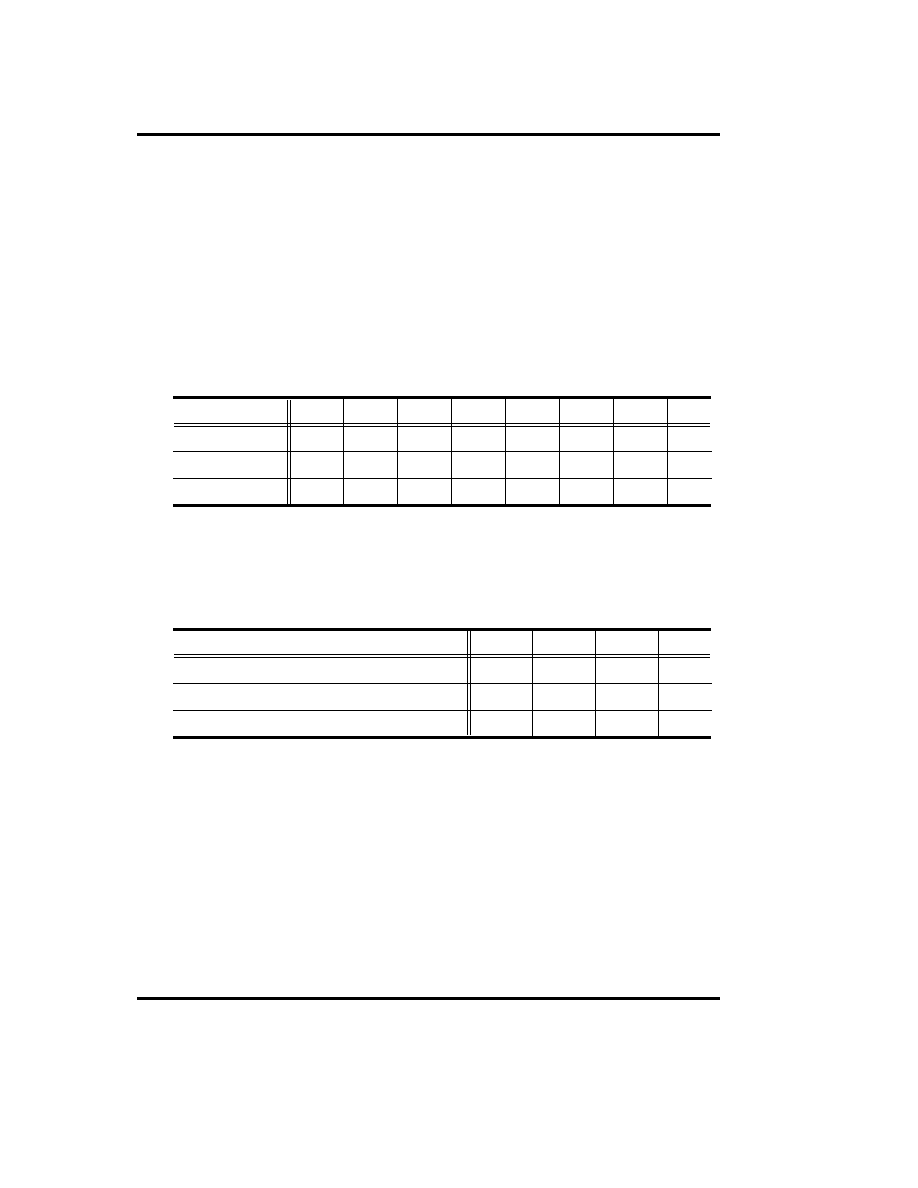

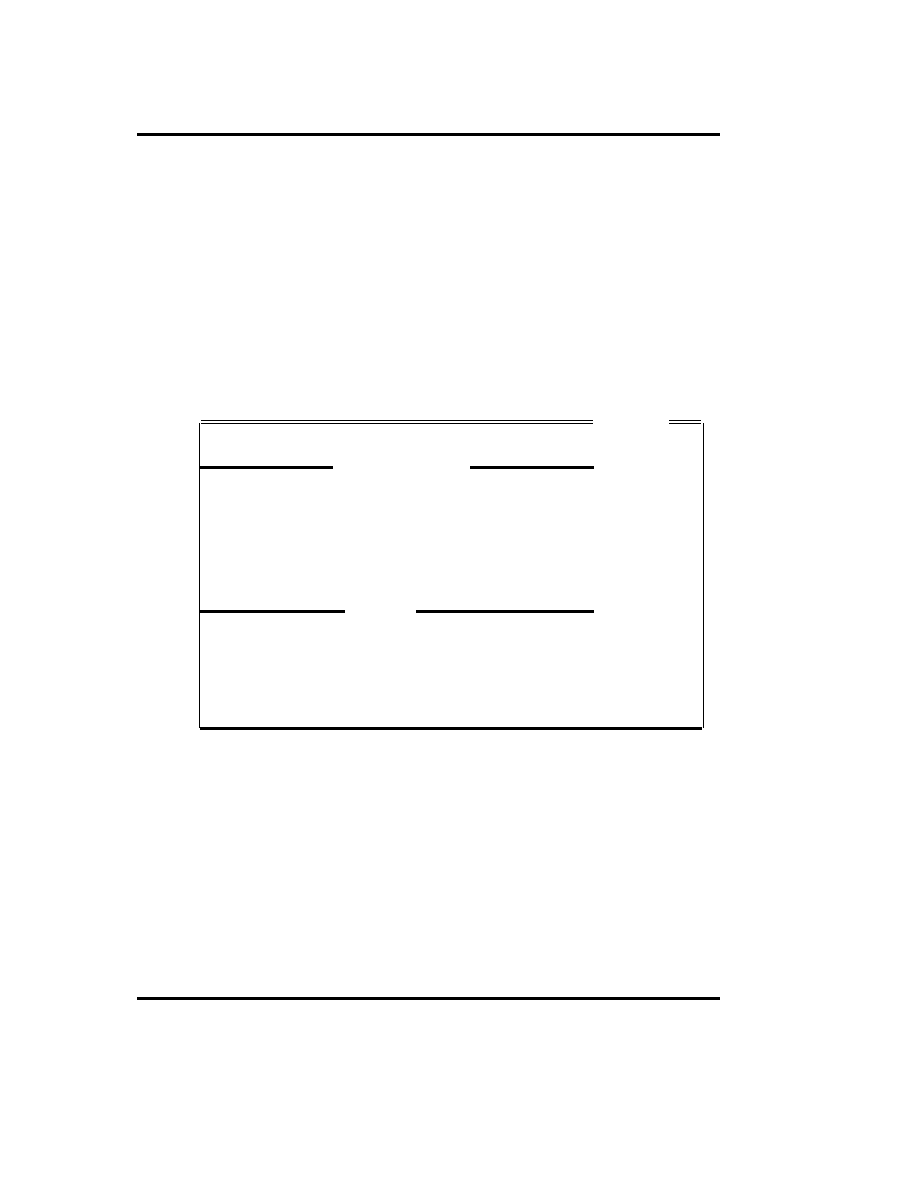

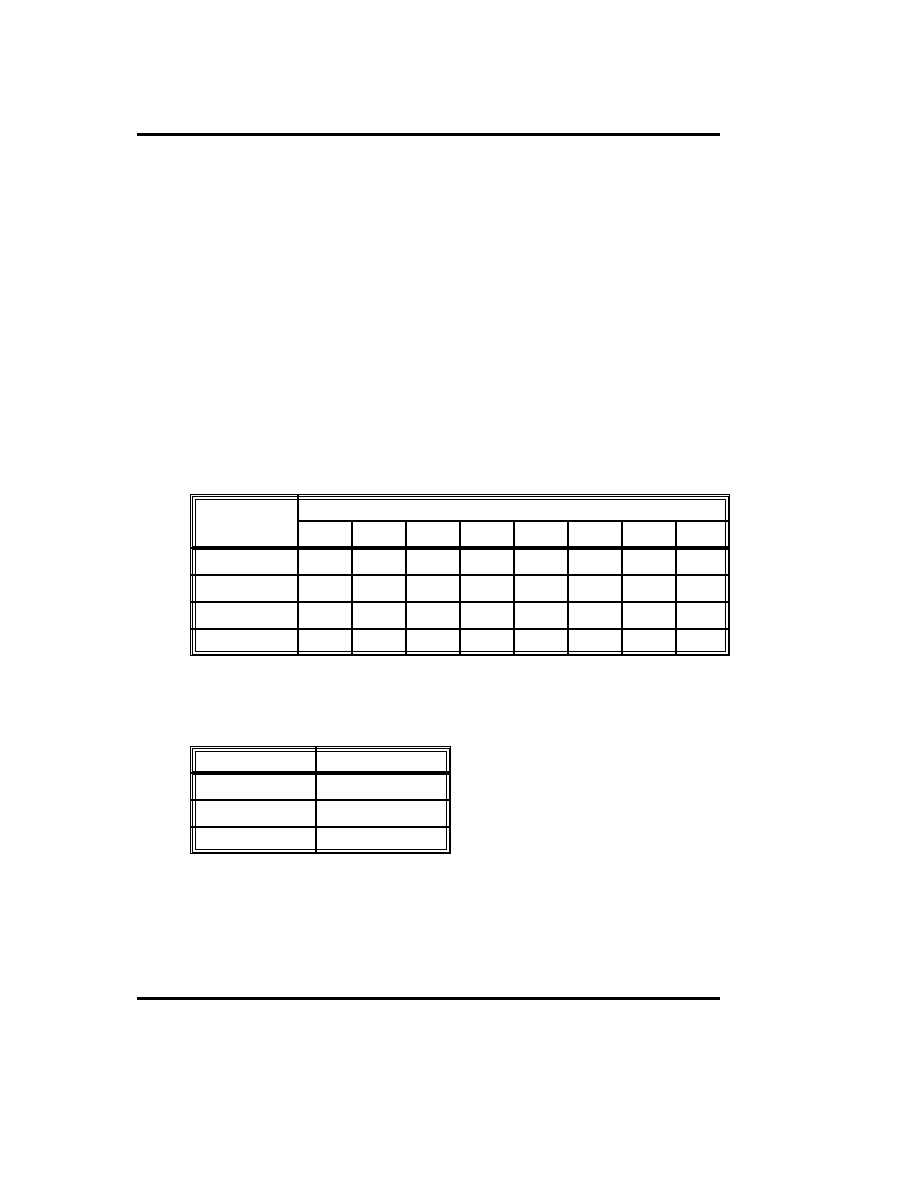

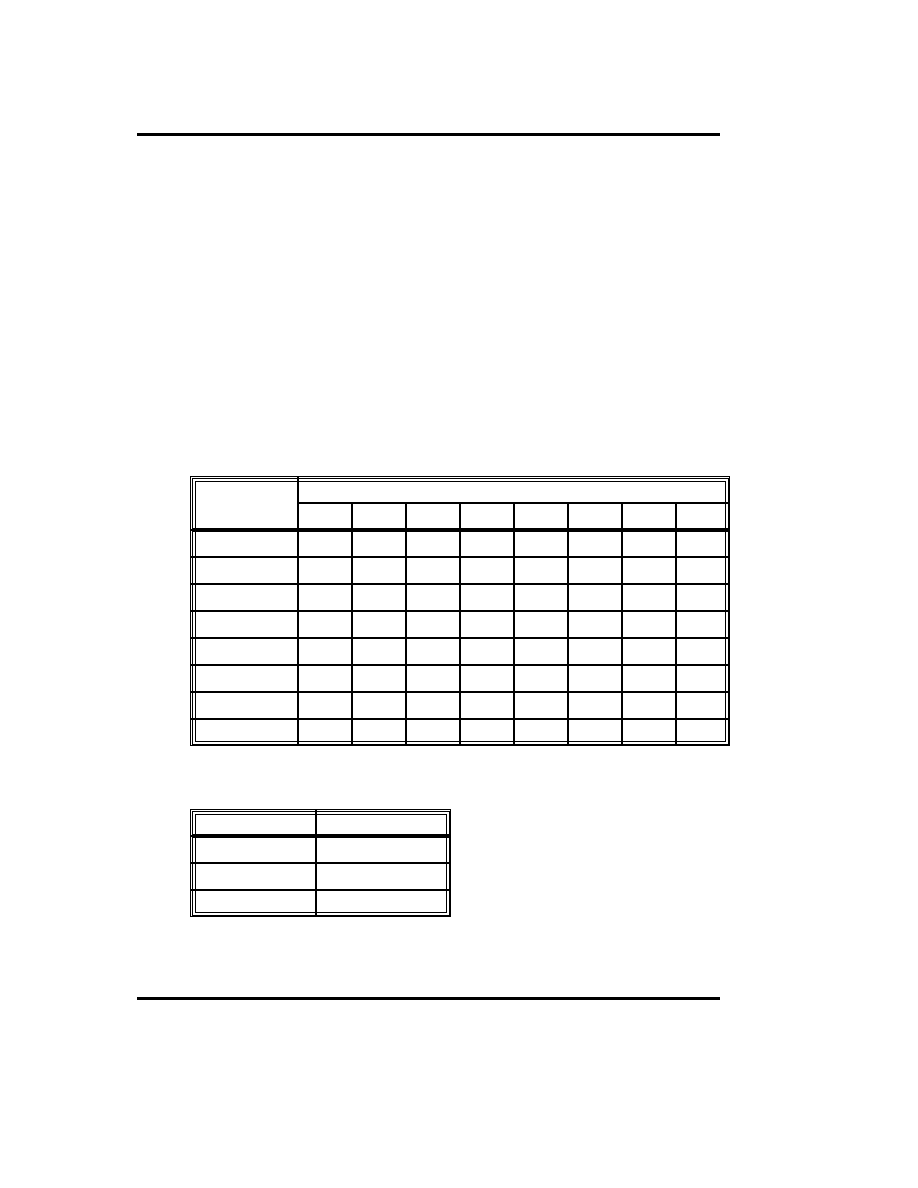

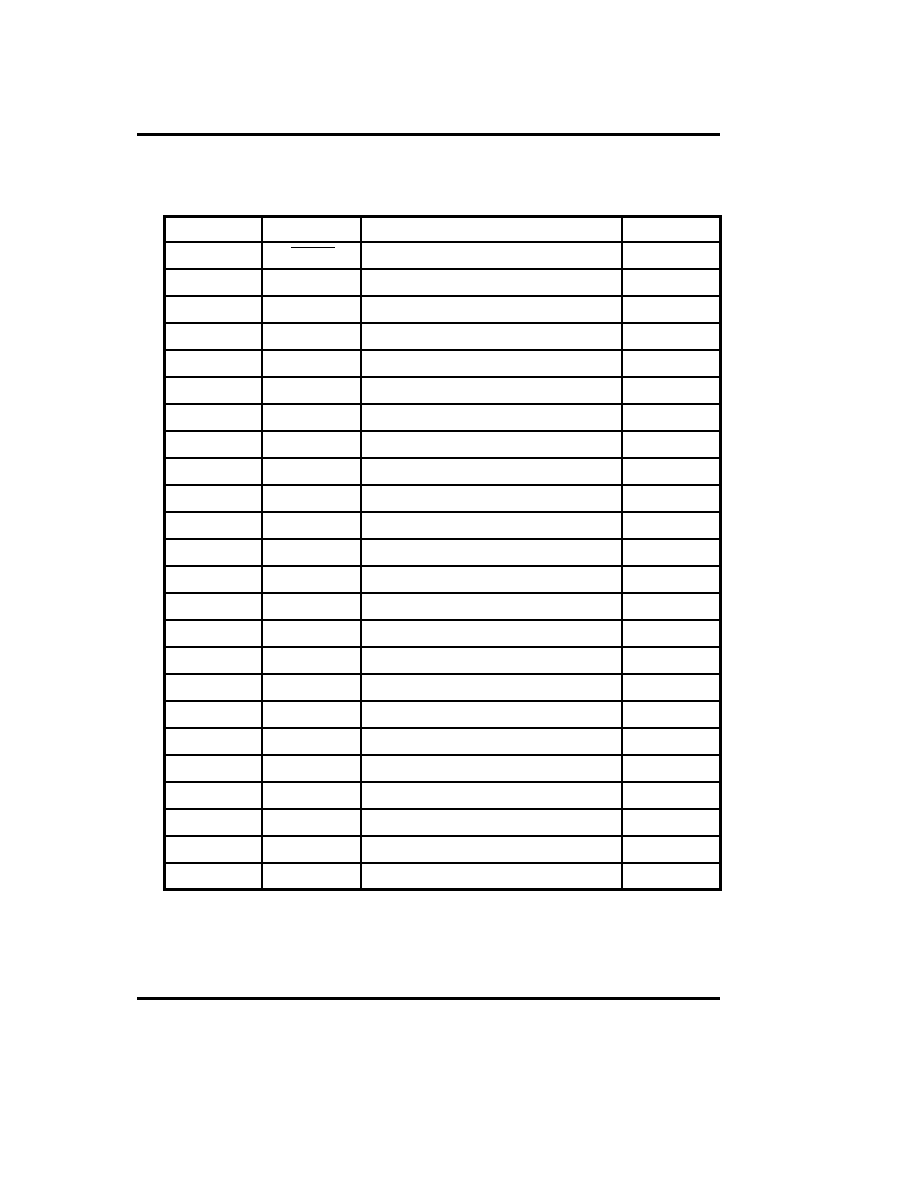

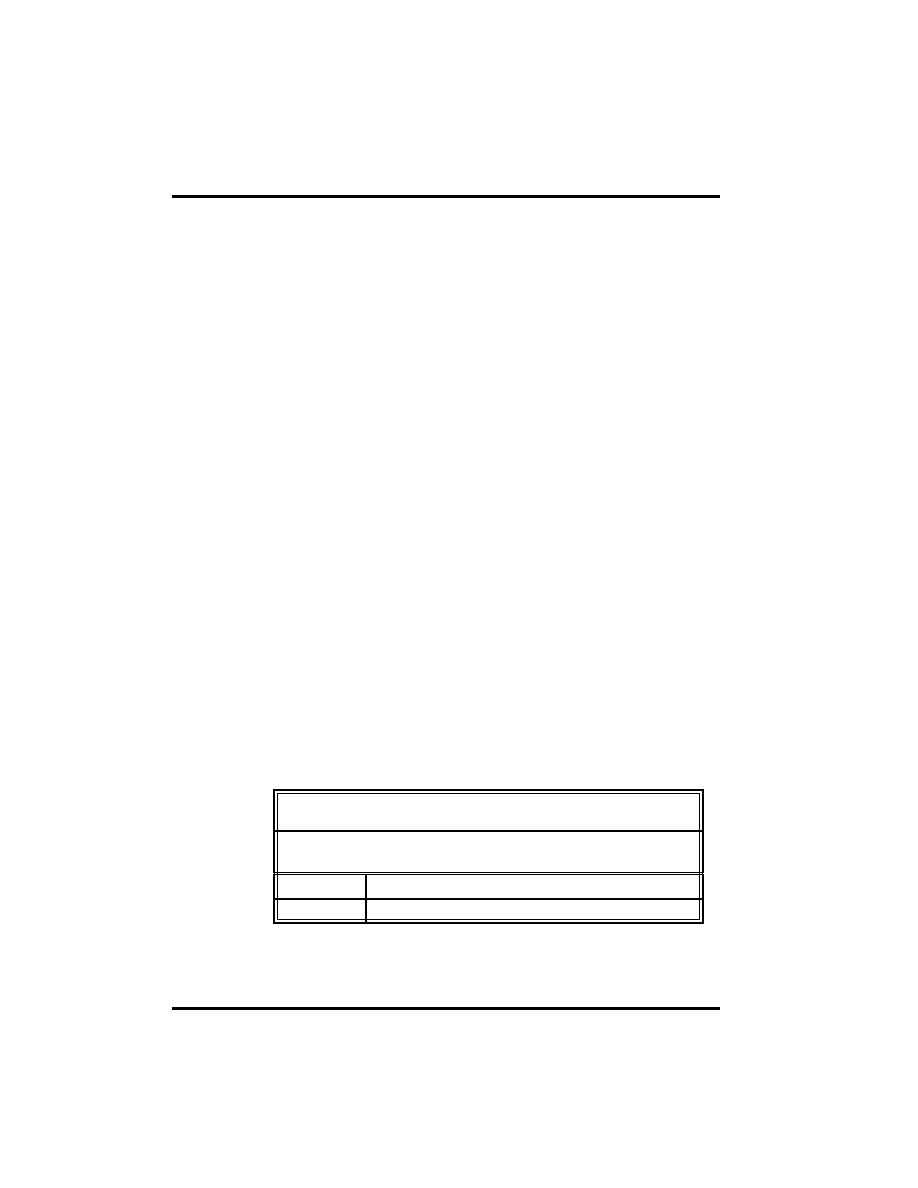

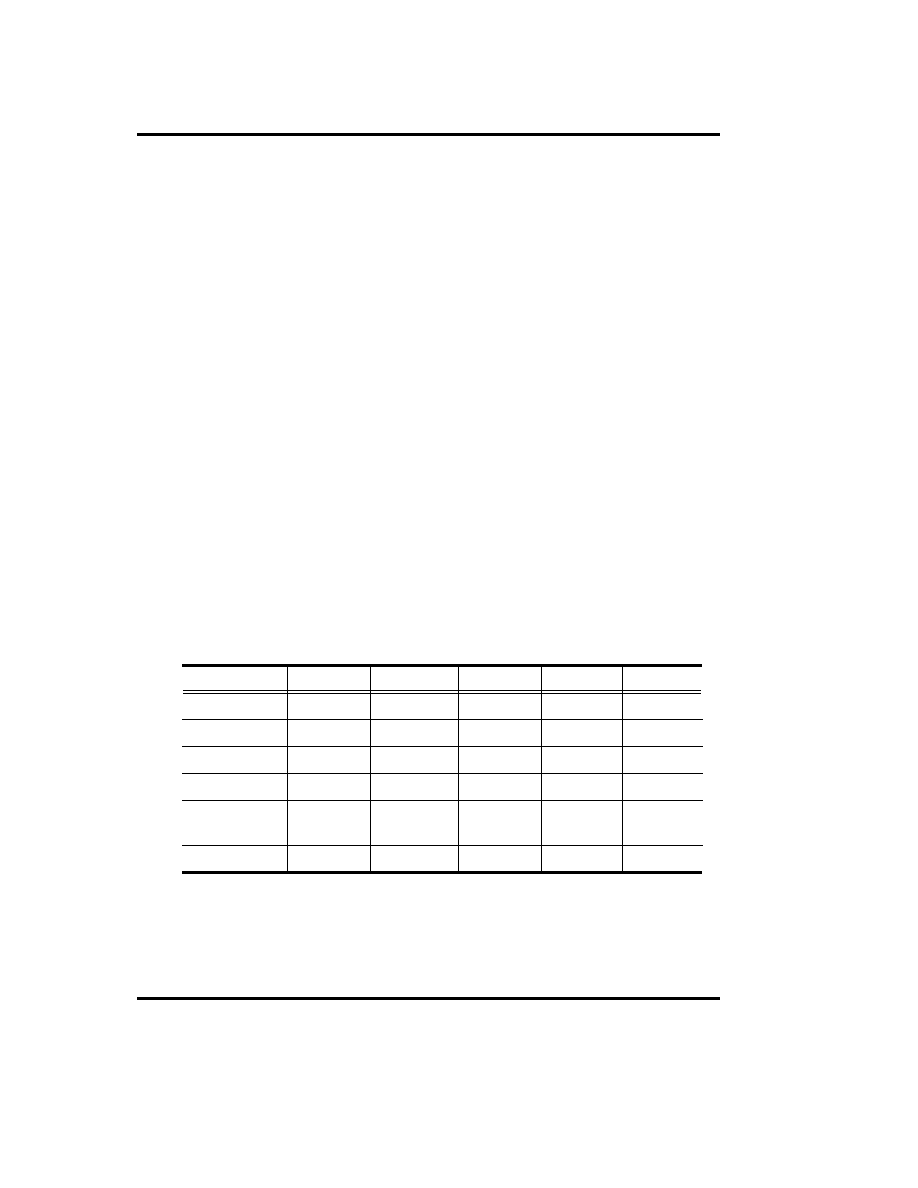

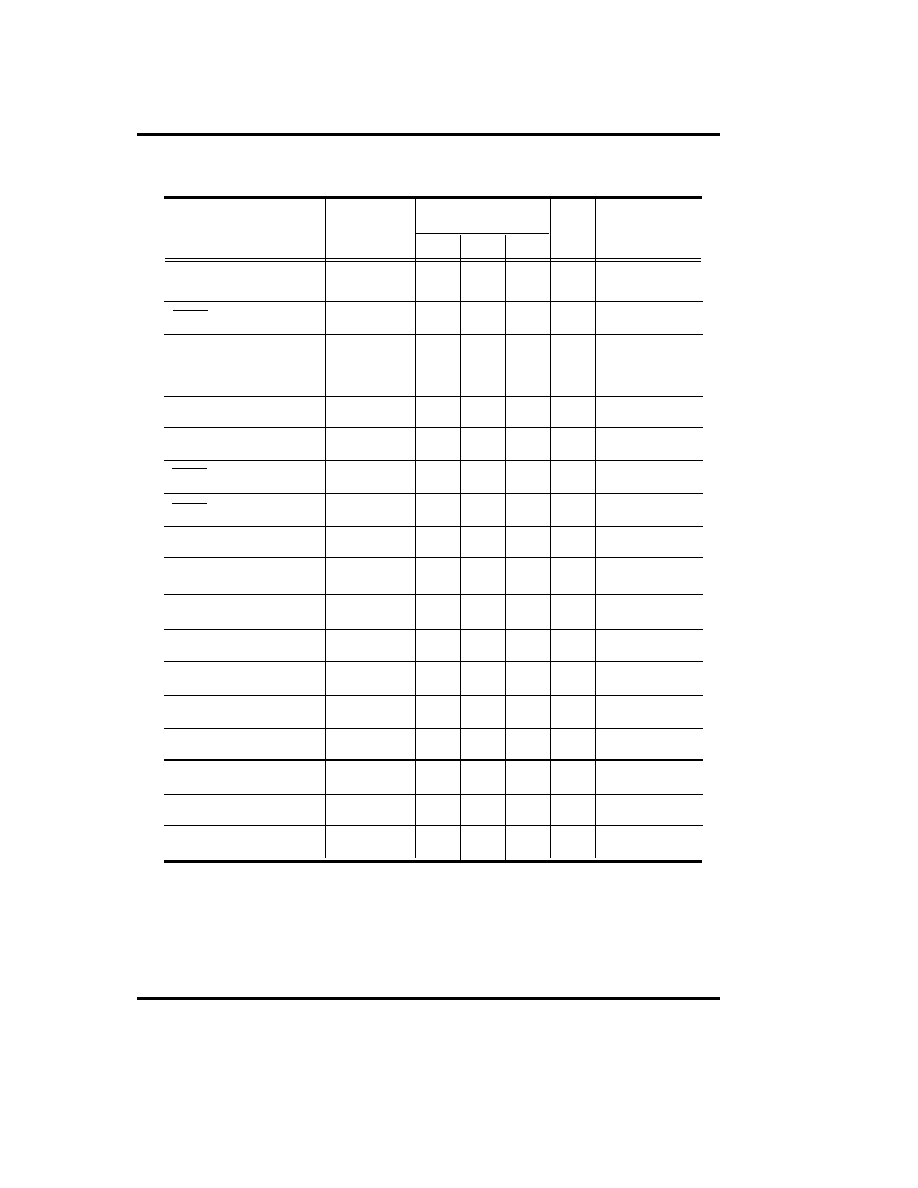

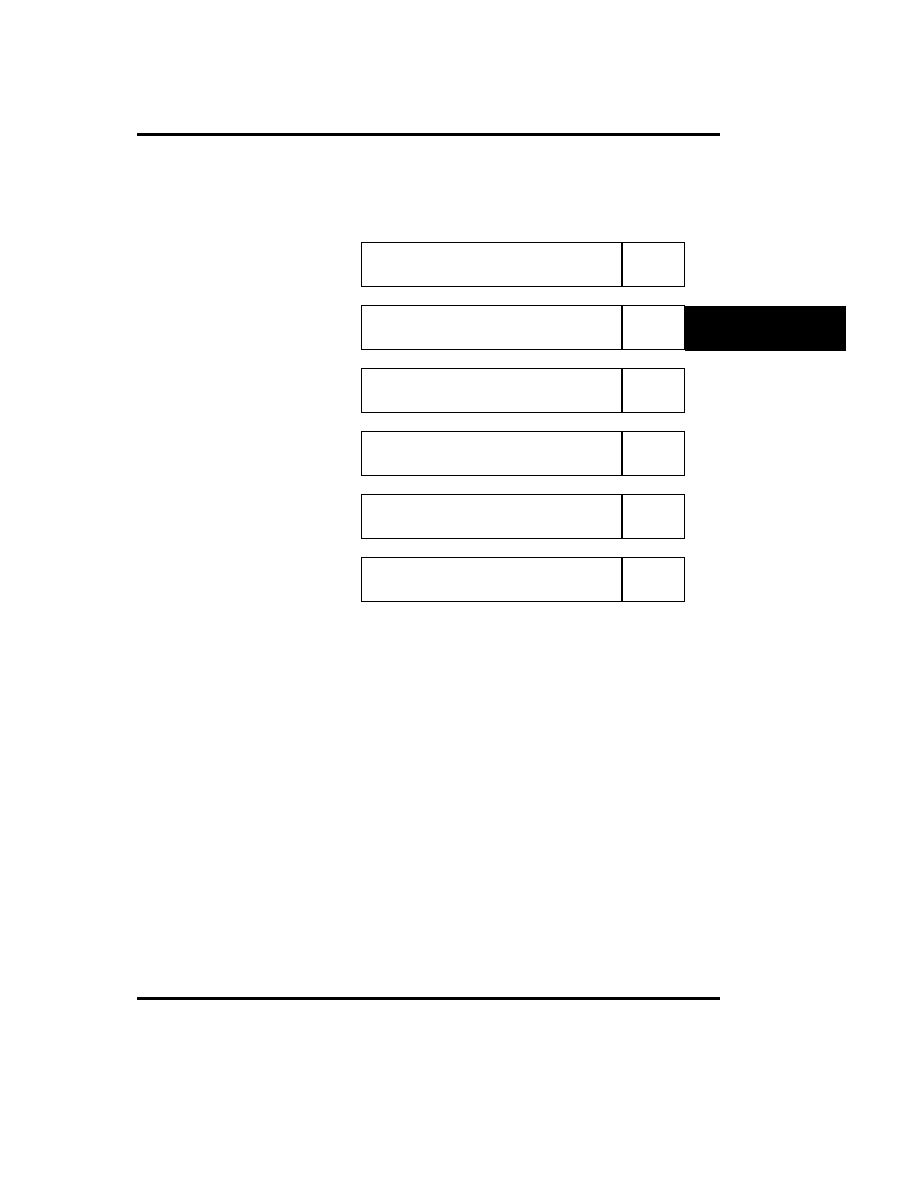

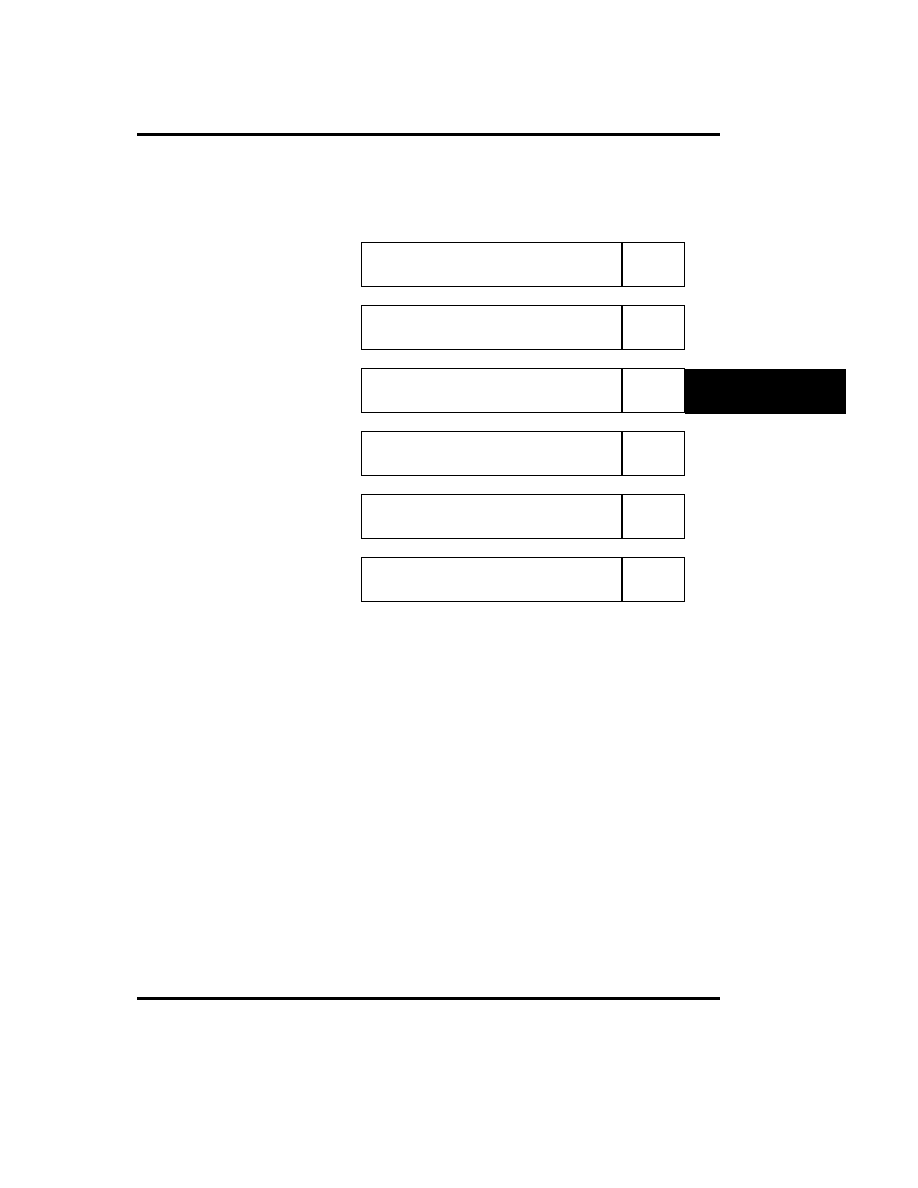

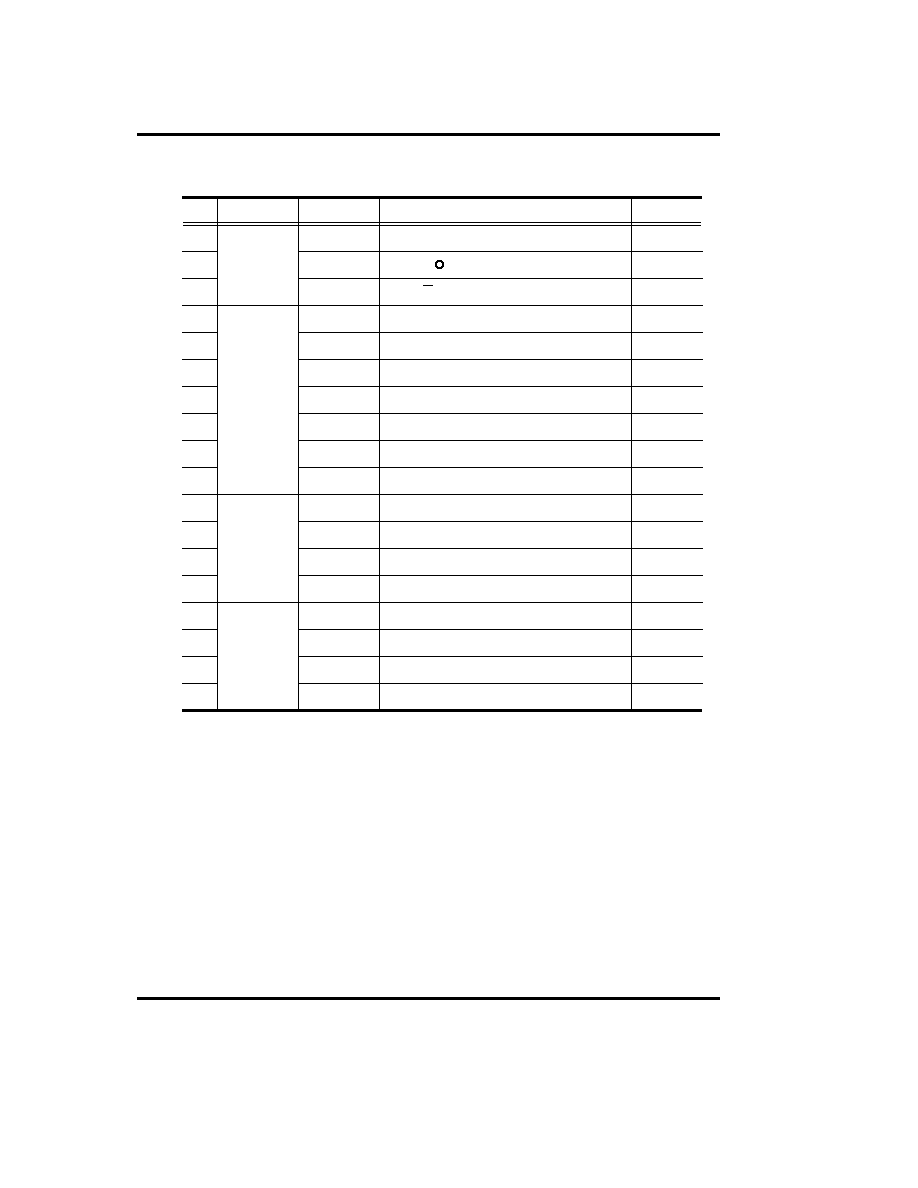

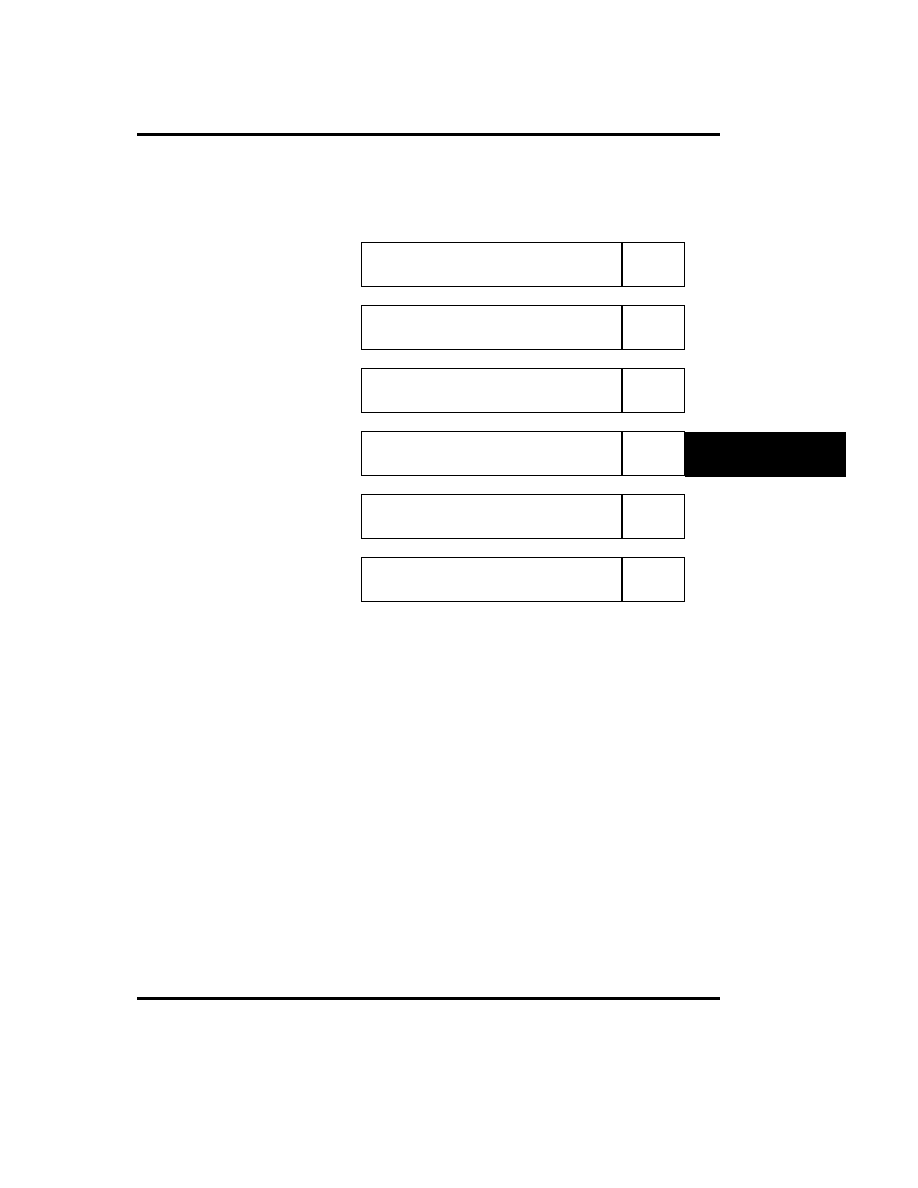

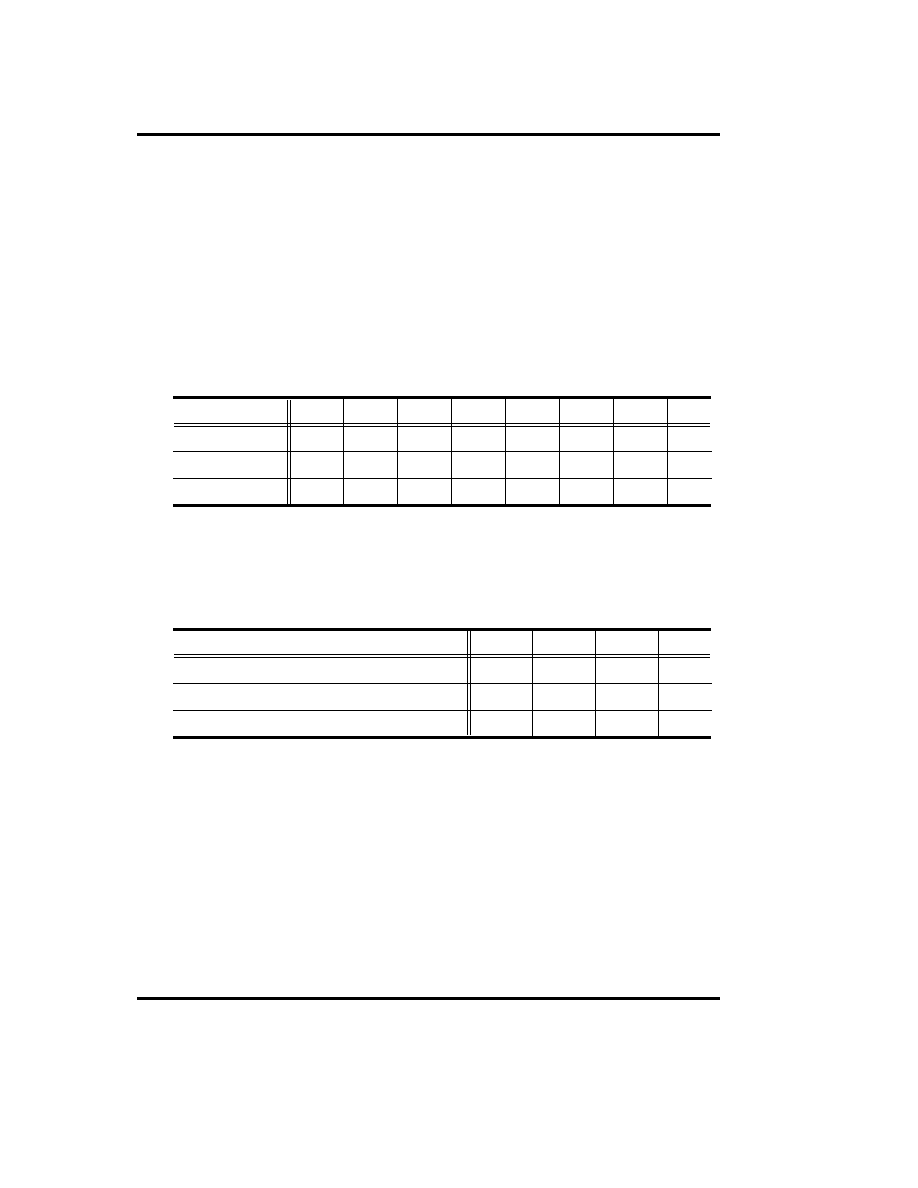

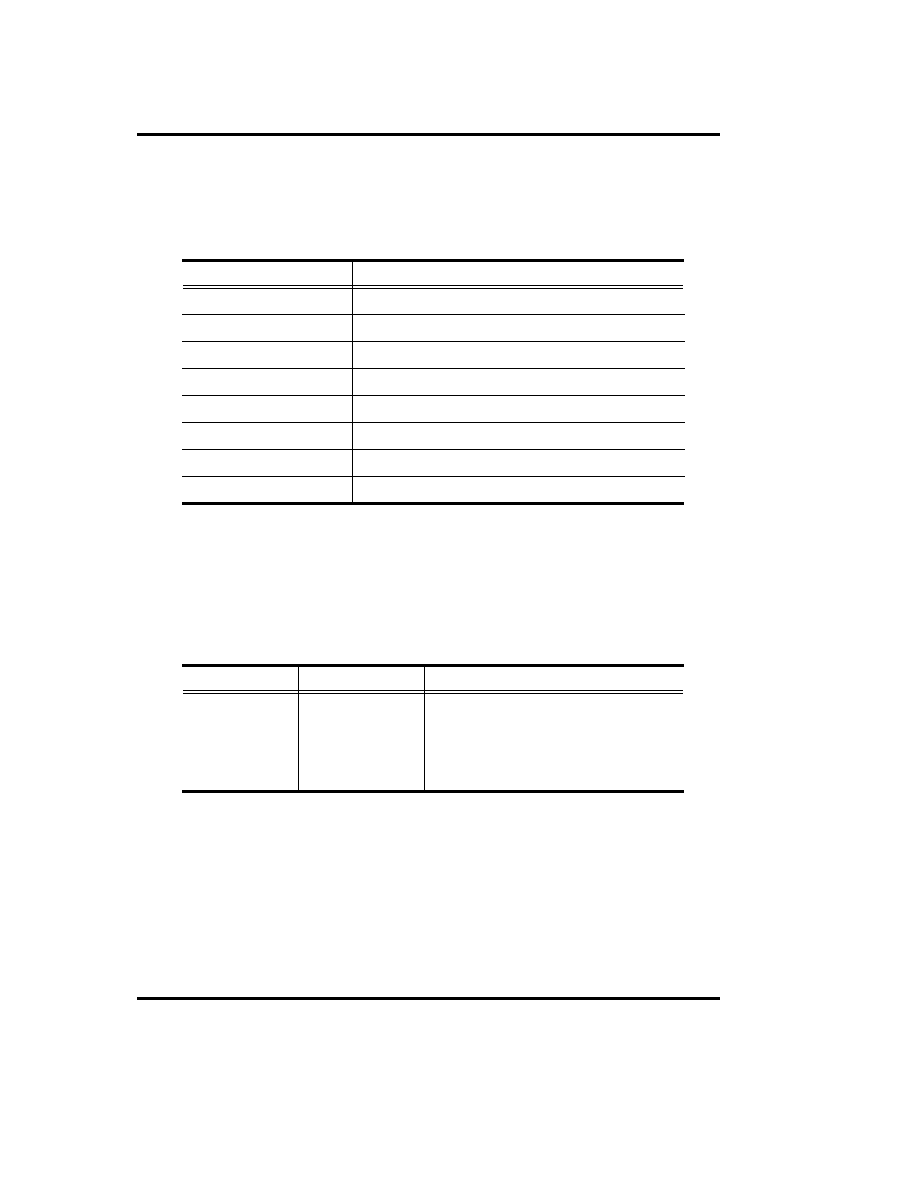

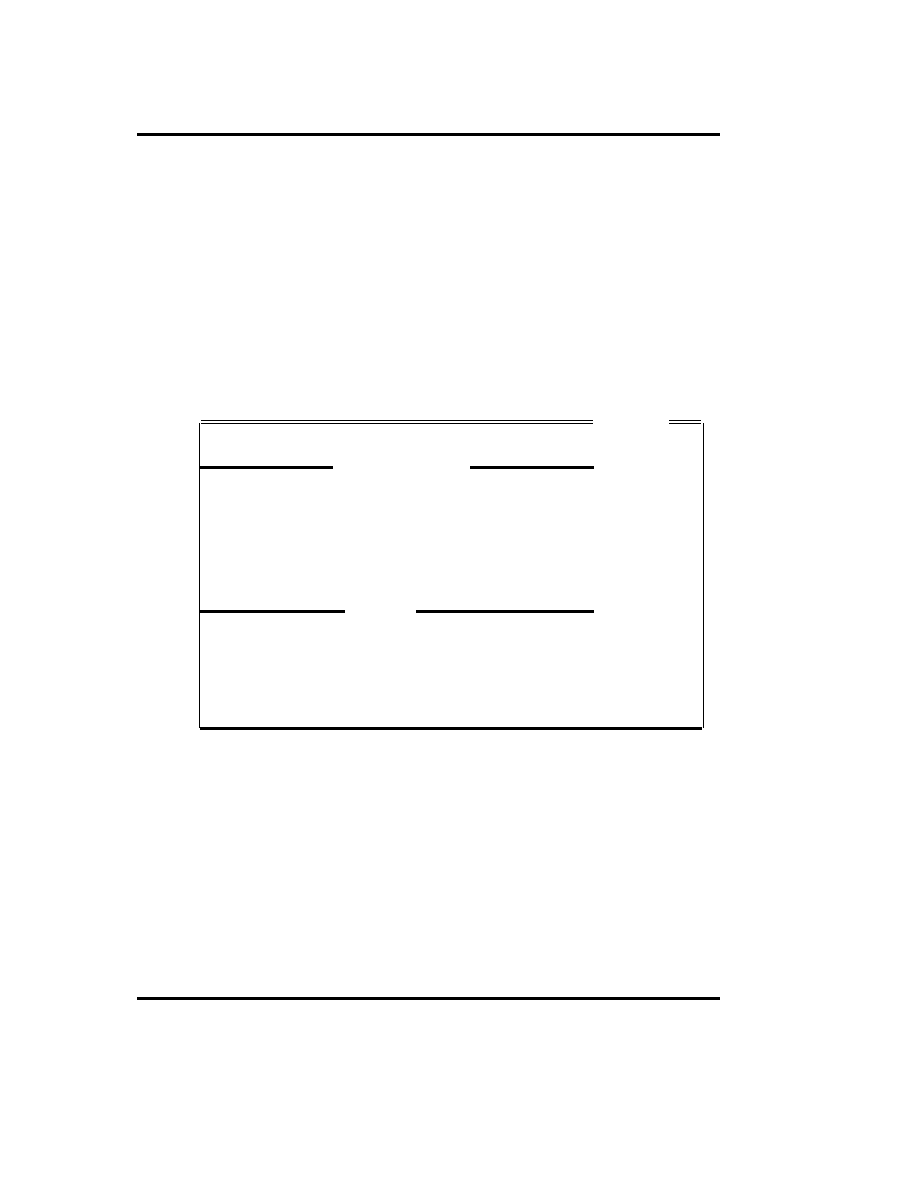

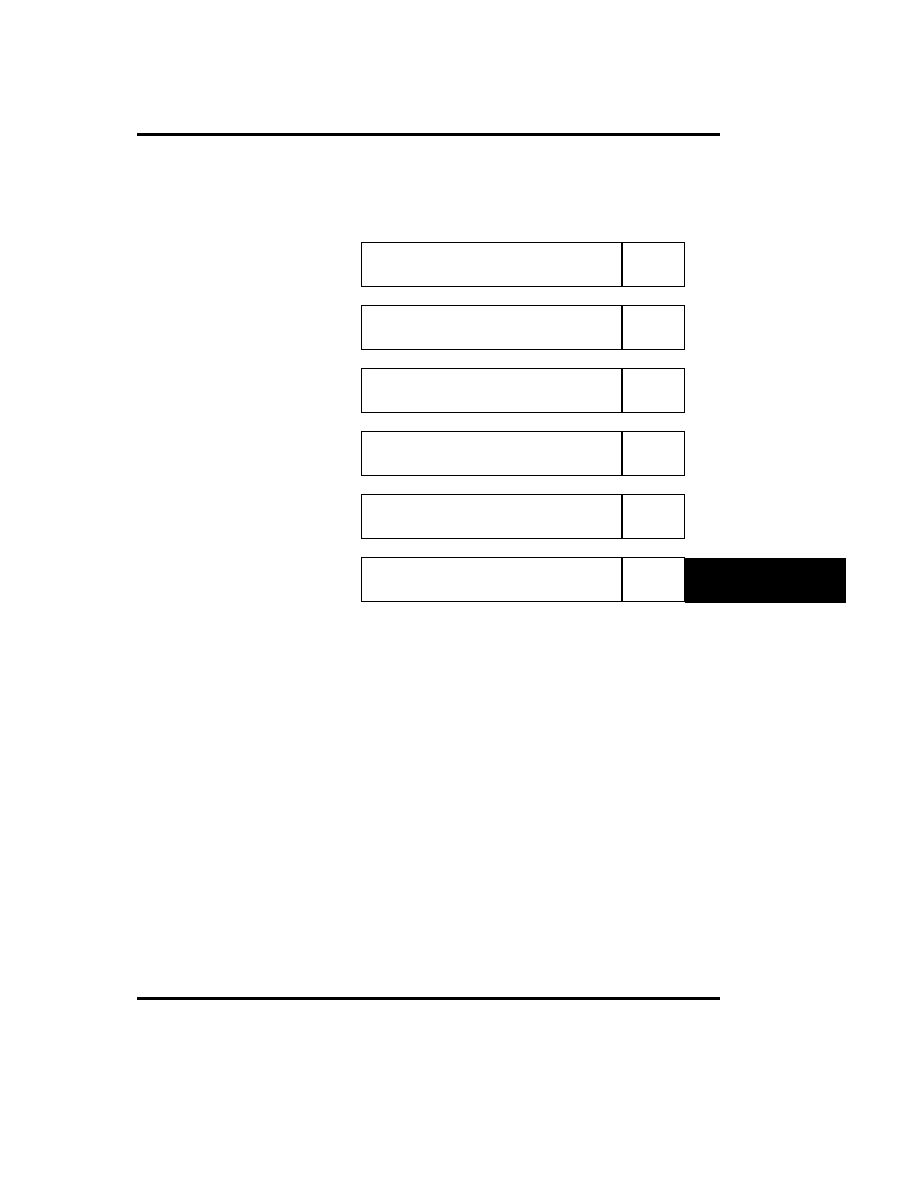

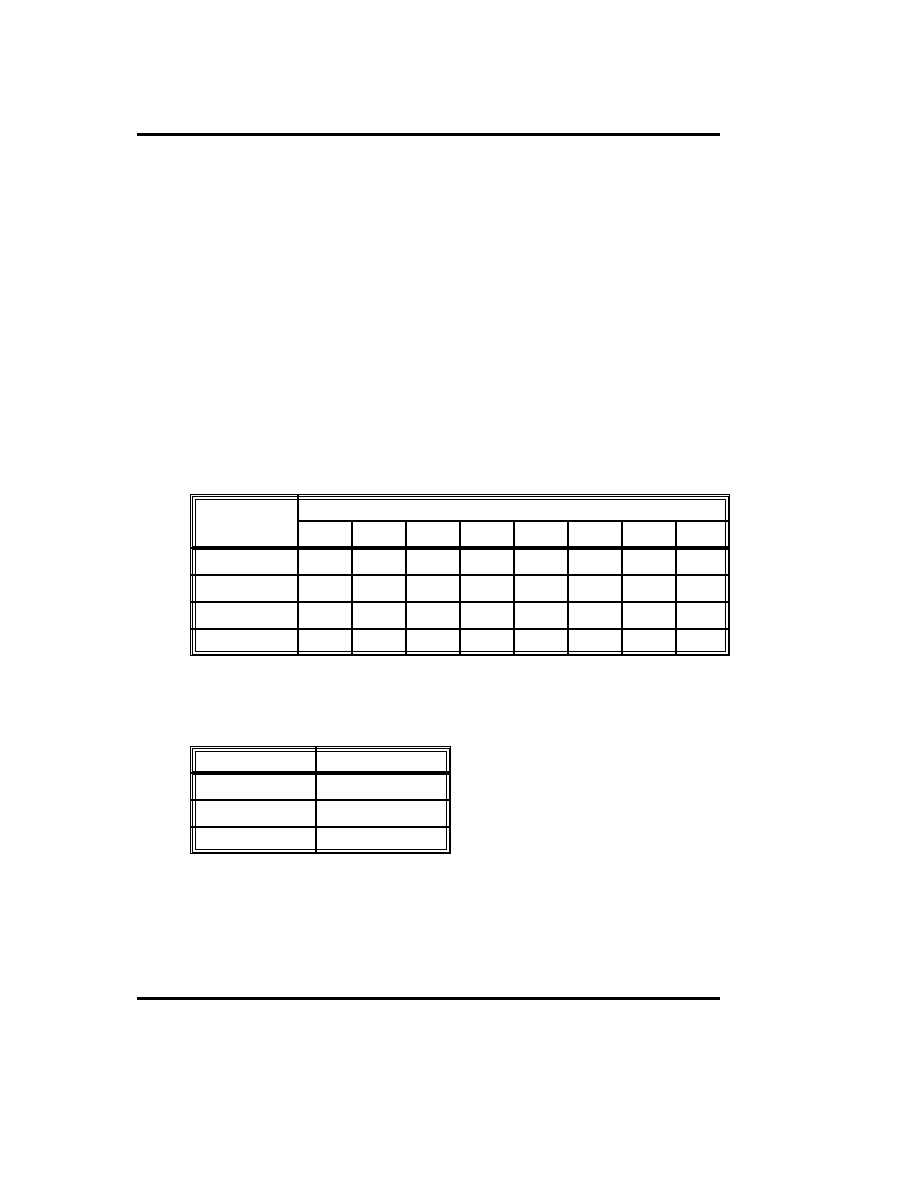

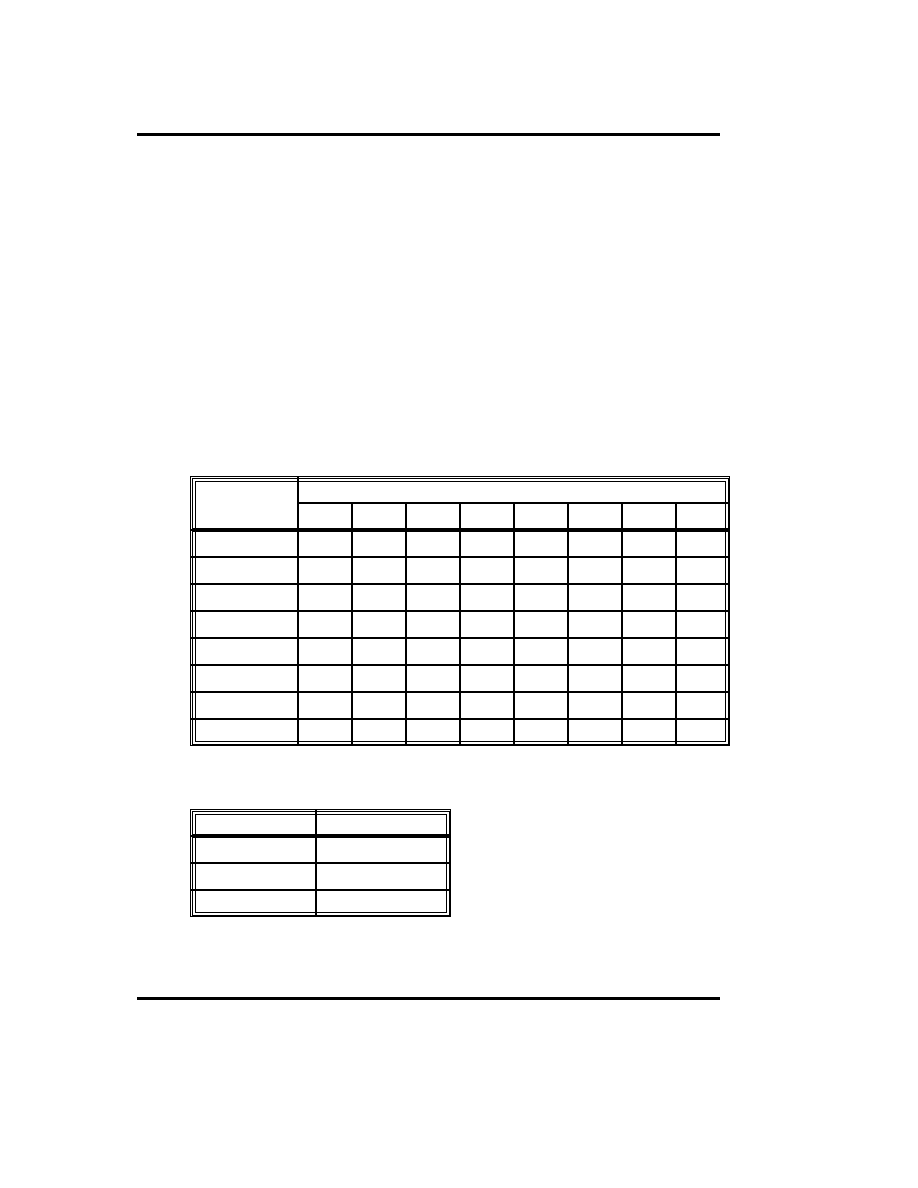

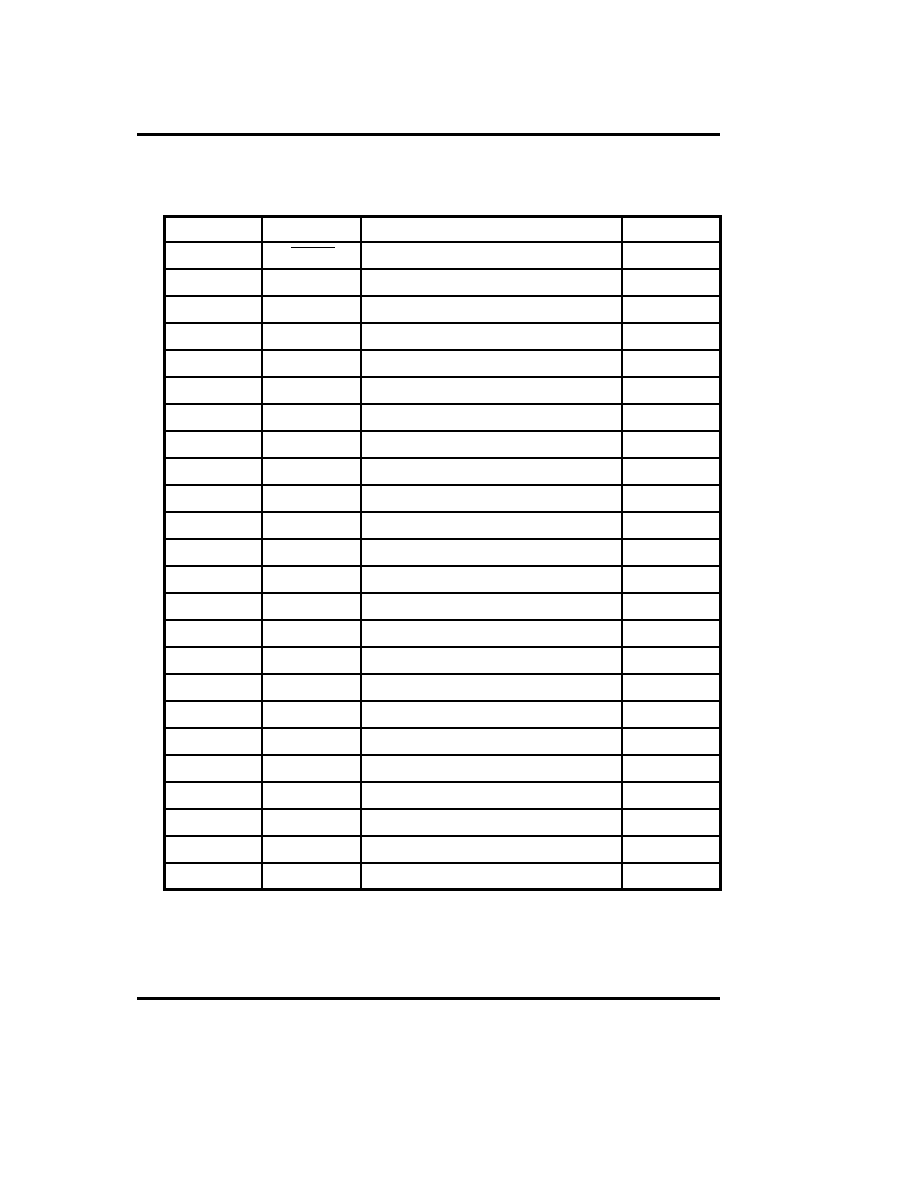

Table 1-1 GMS300 series members

Chapter 1. Introduction

Series

Program memory

Data memory

I/O ports

Input ports

Output ports

Package

GMS30004

512

32

Ø

4

-

4

6

D0 ~ D5

16DIP/SOP

GMS30012

à

à

4

à

6

D0 ~ D5

20DIP/SOP

GMS30112

1024

à

à

à

6

D0 ~ D5

à

GMS30120

à

à

à

à

8

D0 ~ D7

24DIP/SOP

GMS30140

à

à

à

à

10

D0 ~ D9

à

1 - 2

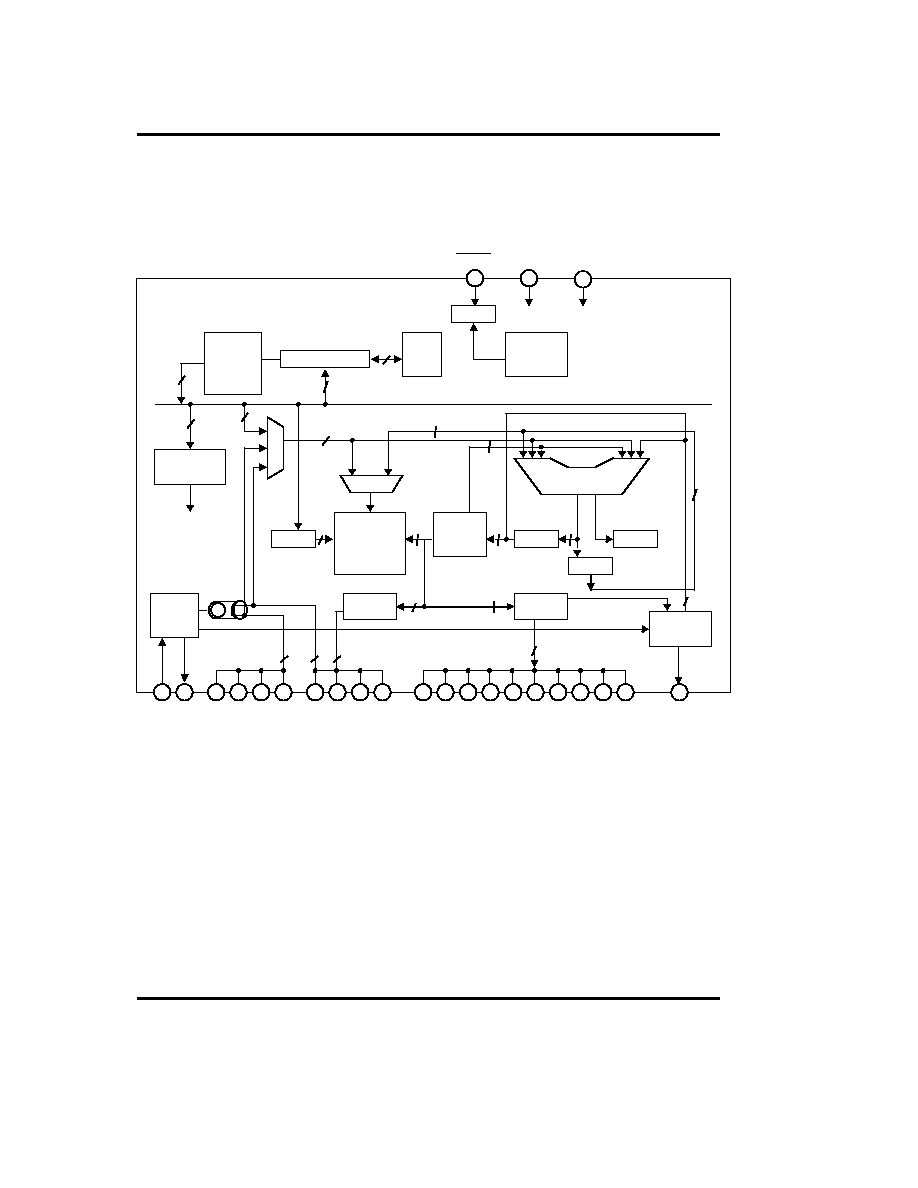

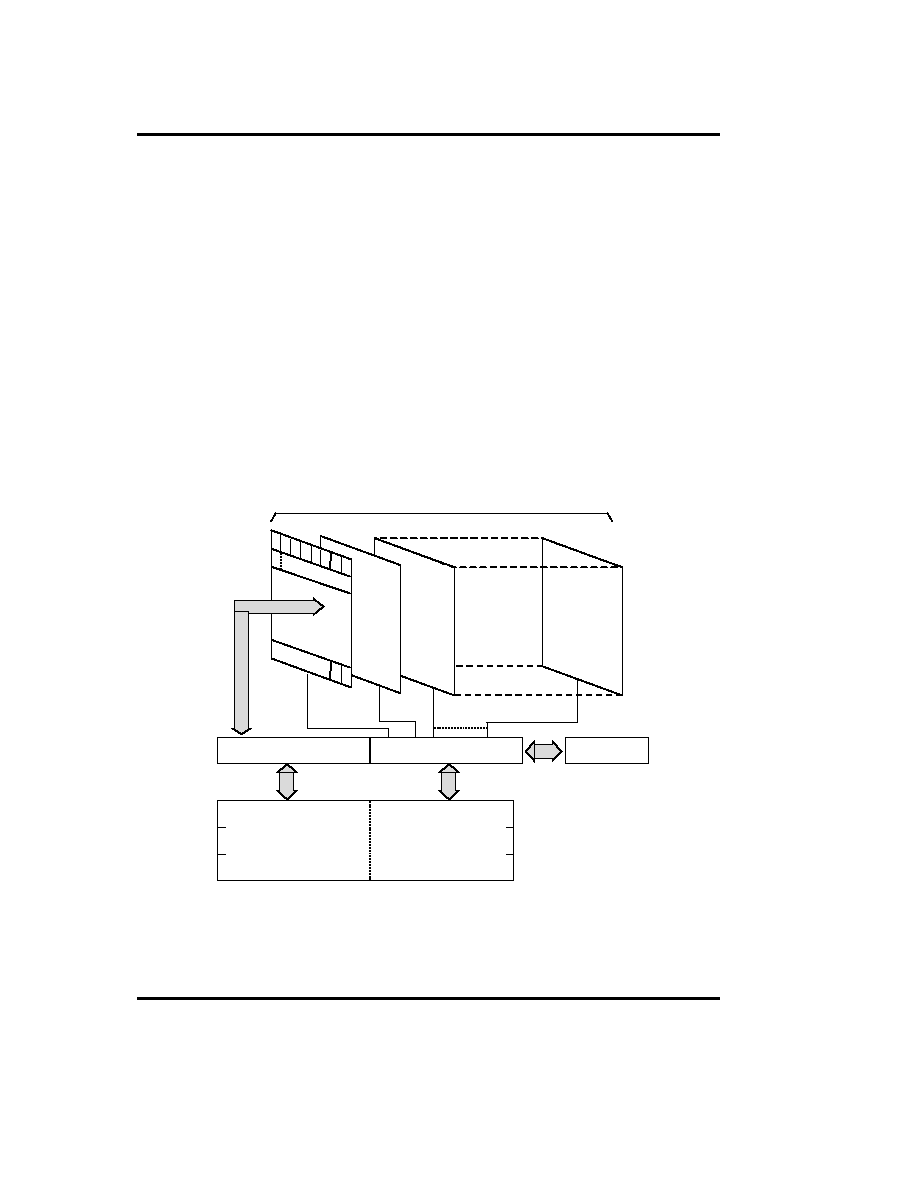

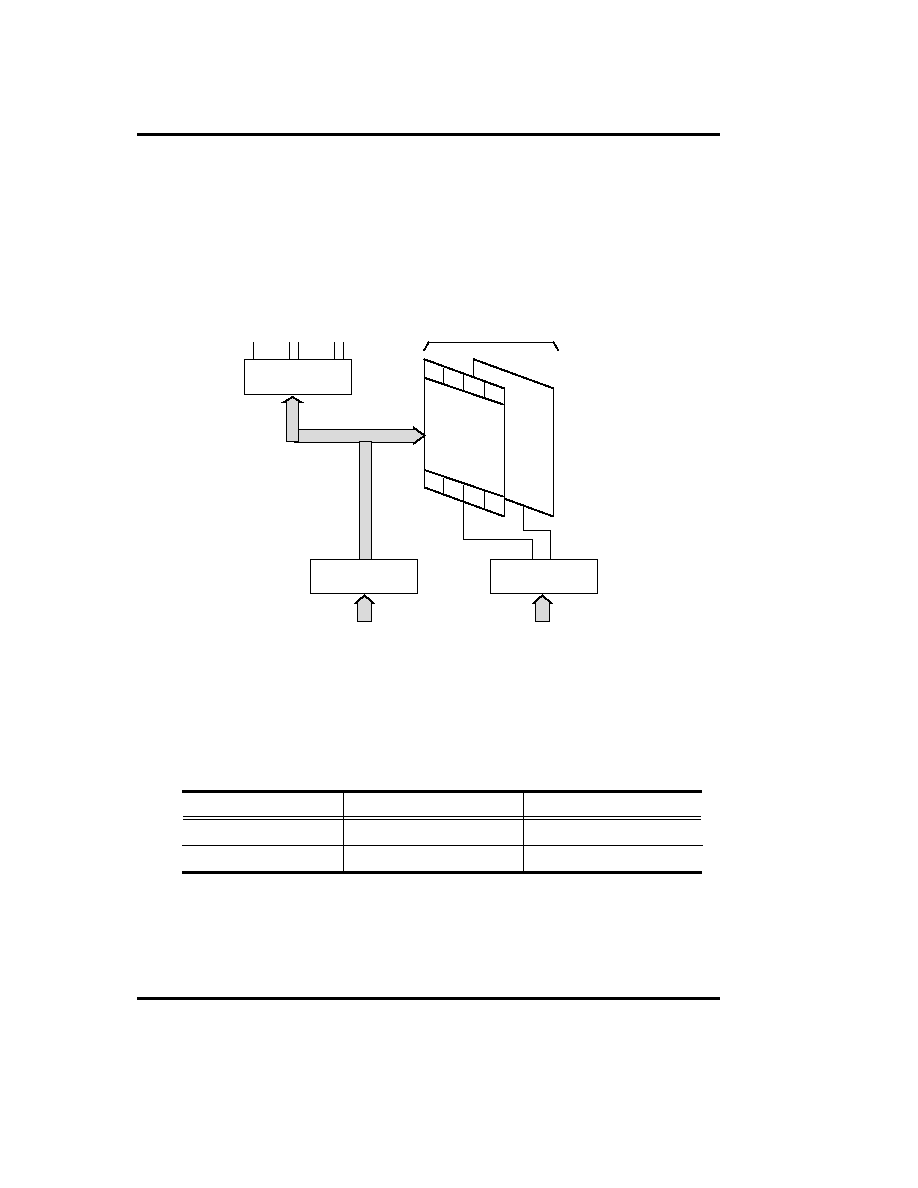

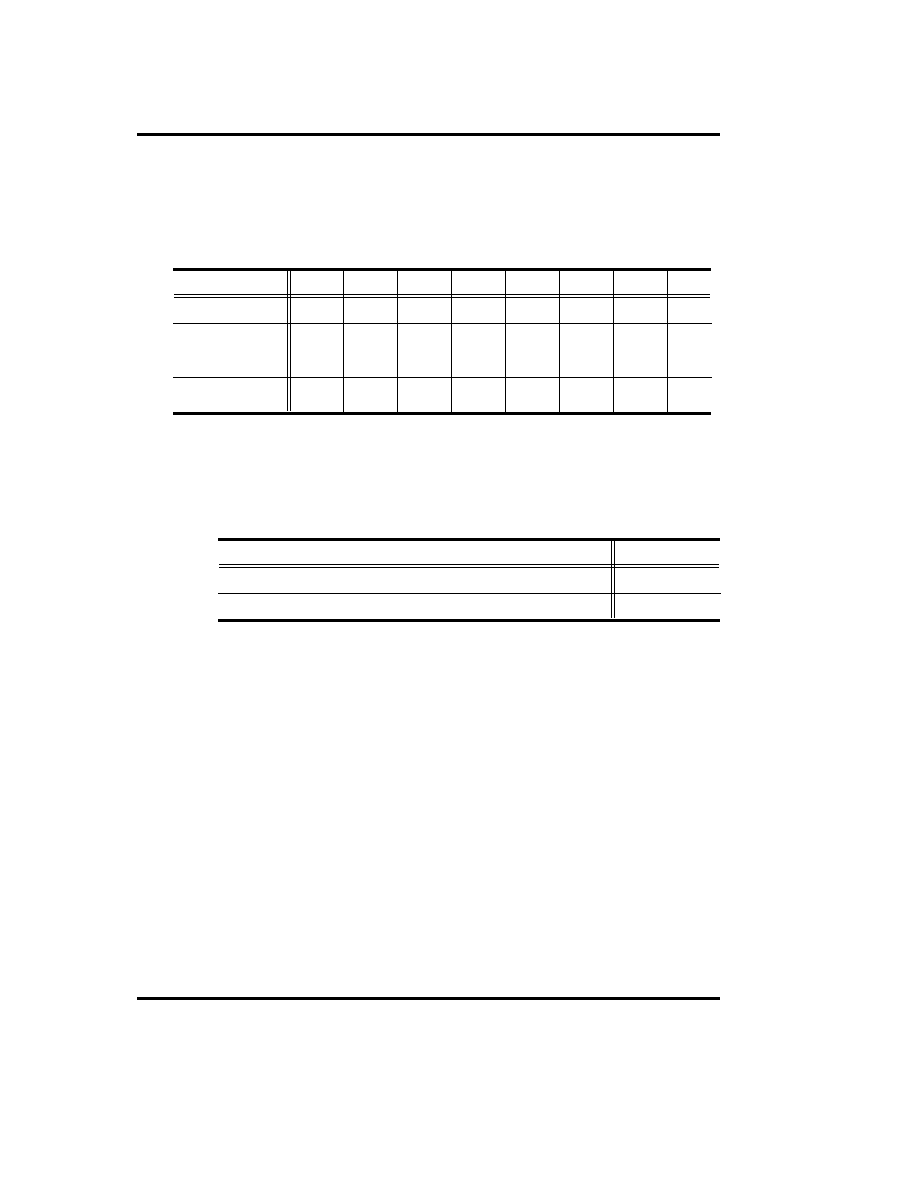

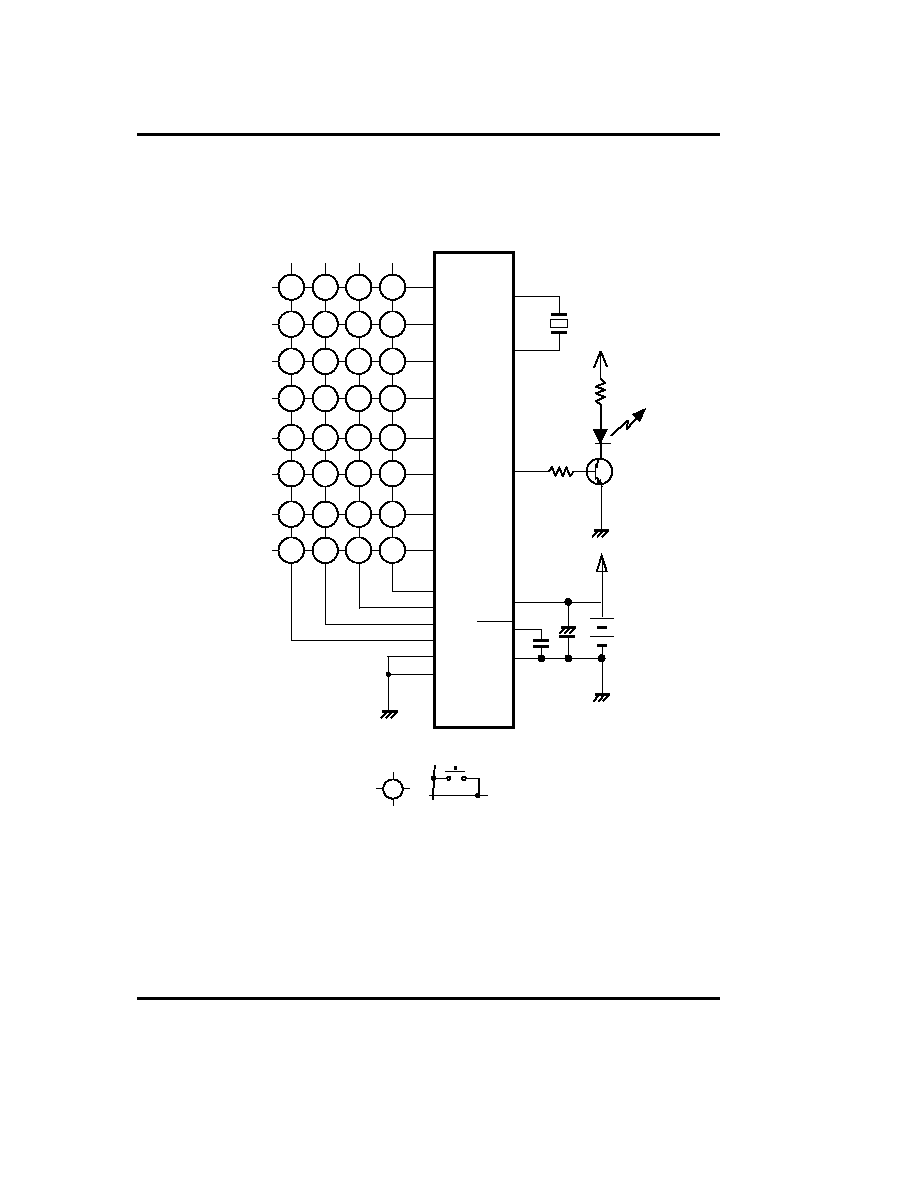

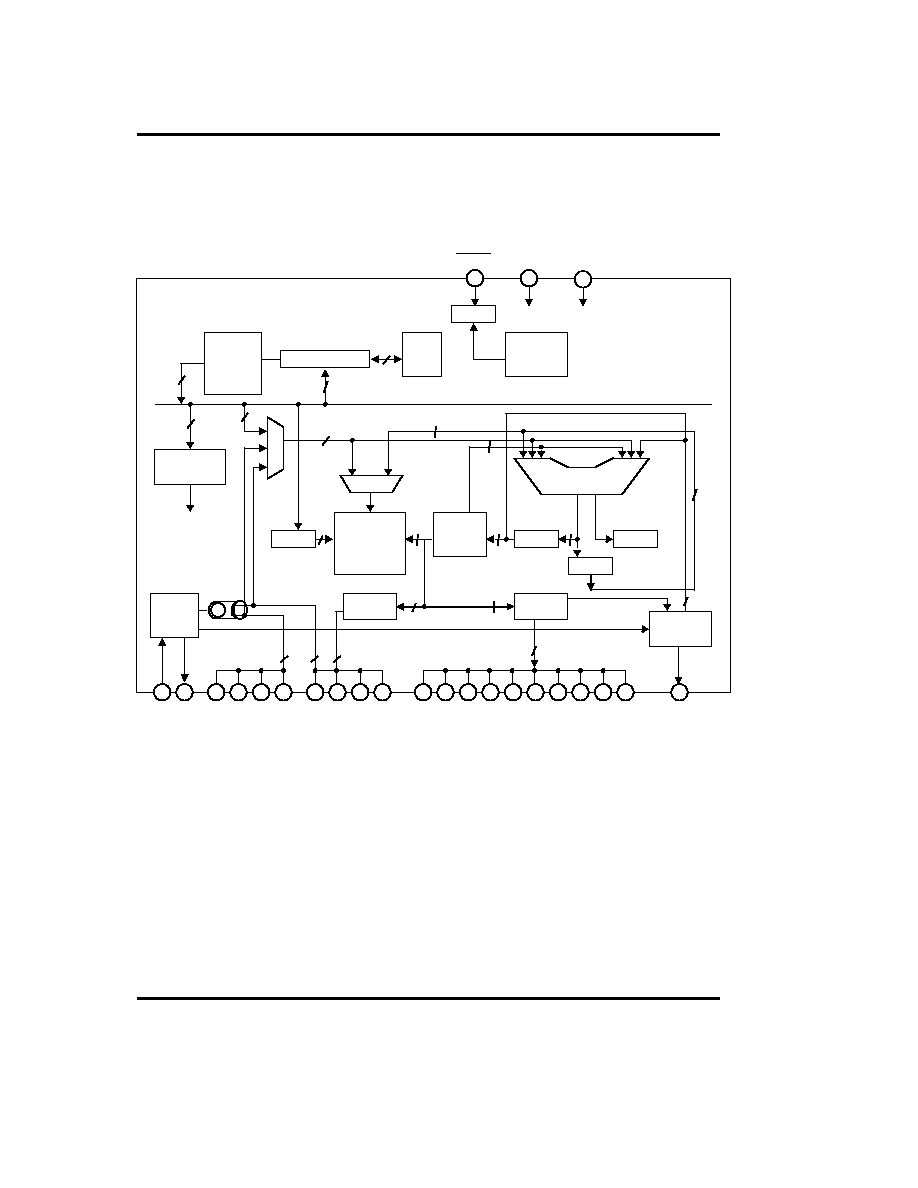

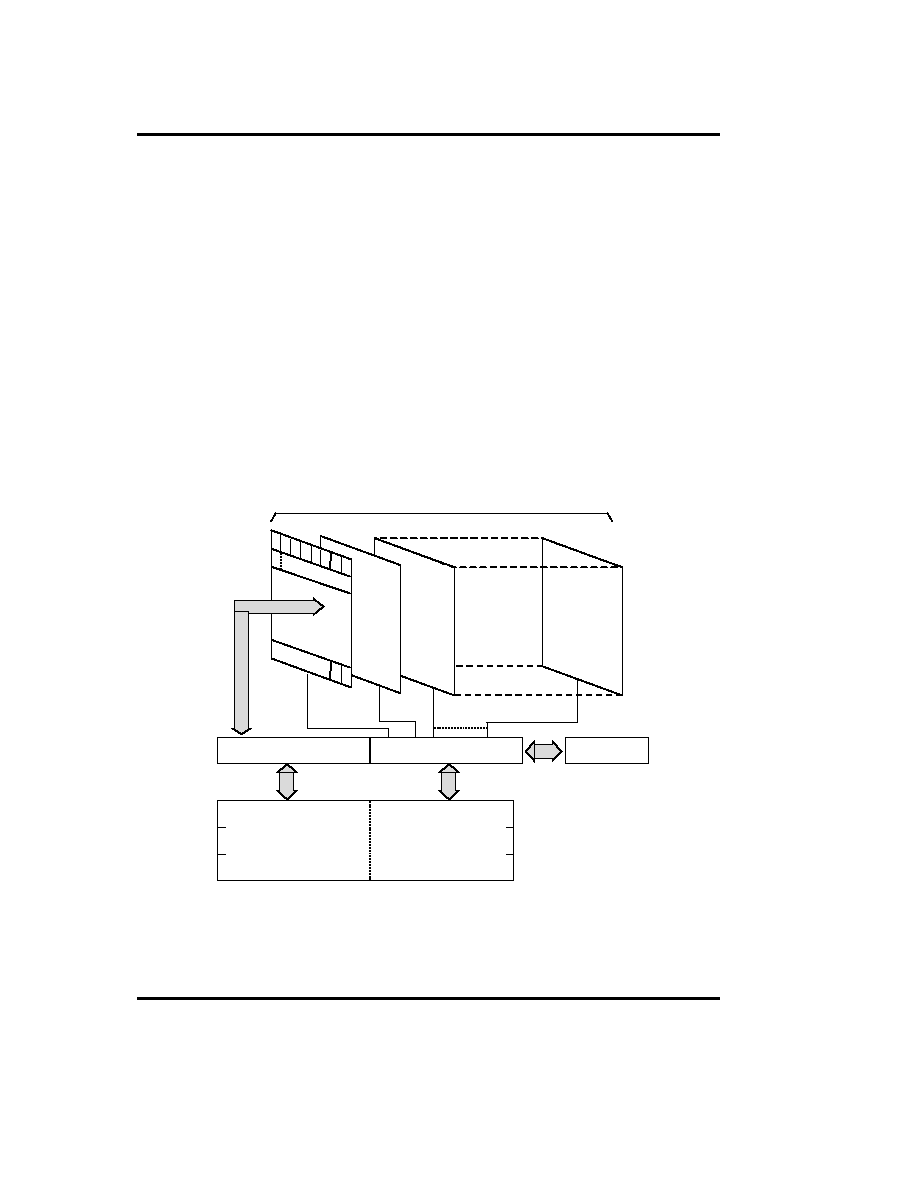

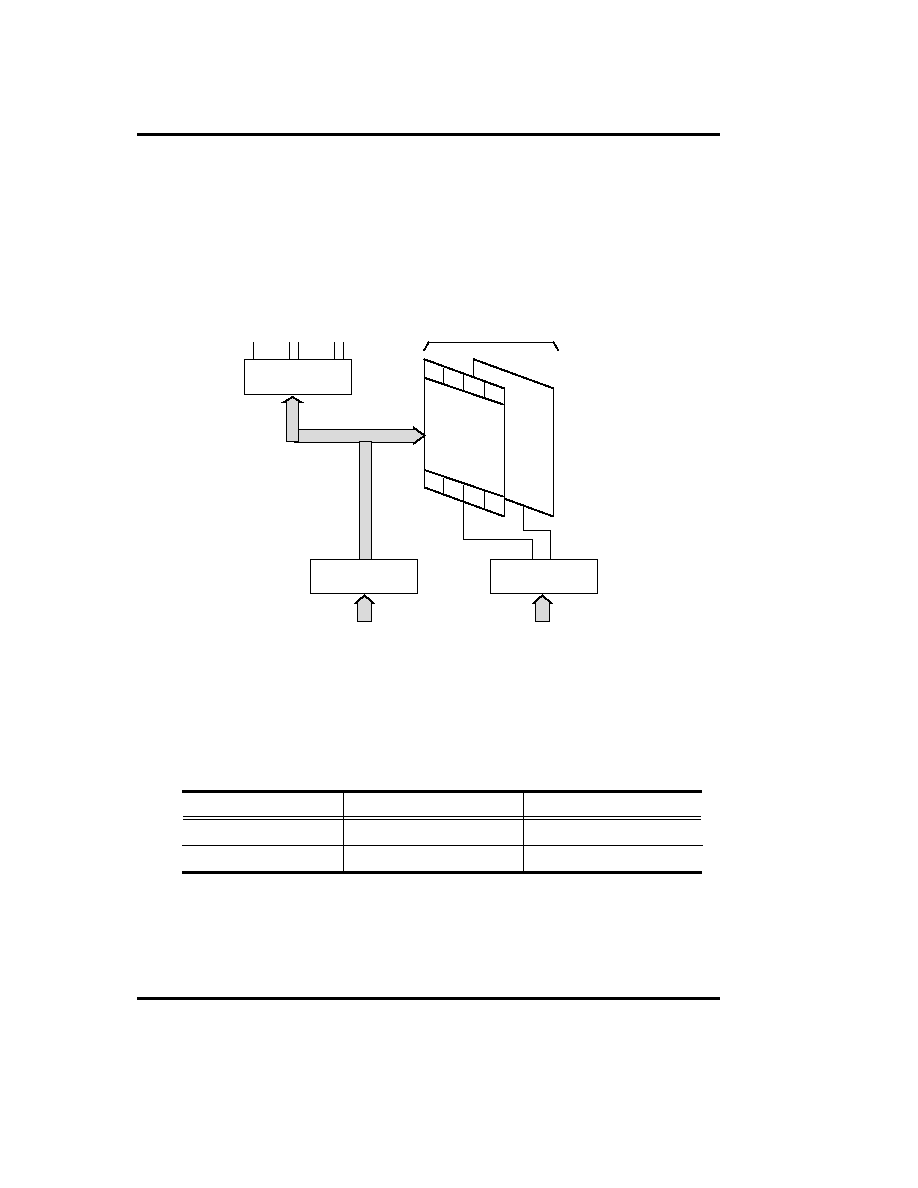

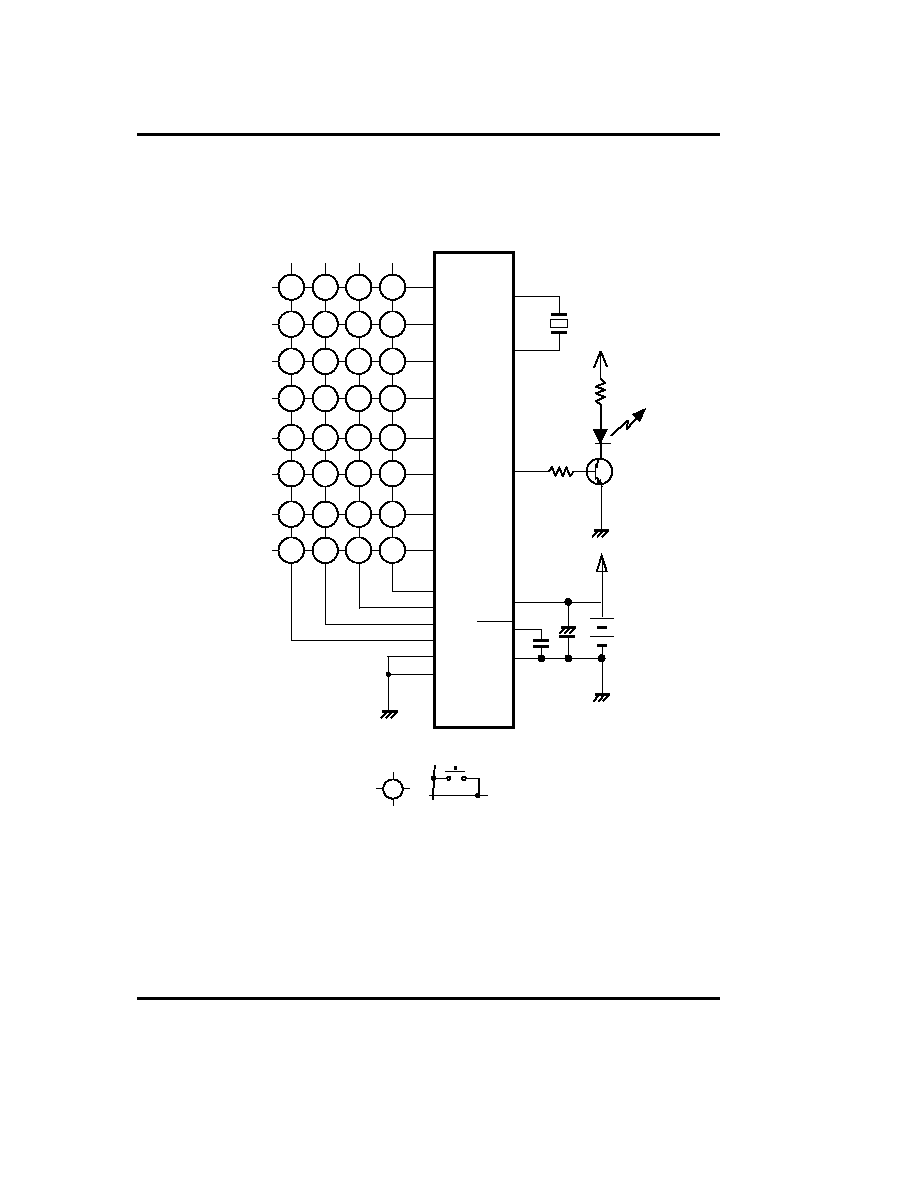

Block Diagram

The GMS300 series is composed as shown below. These blocks are detailed in

CHAPTER2.

RAM

16word x

2page x 4bit

RAM

Word

Selector

Y-Reg

ACC

ST

R-Latch

D-Latch

Pluse

Generator

X-Reg

MUX

08

;

ALU

23

22

7

8

9

4

21

10

3

5

6

11

12

13

14

15

16

17

18

19

20

Instruction

Decoder

Program counter

Stack

Reset

Watchdog

timer

1

24

2

10

10

8

ROM

64word

Ø

16page

Ø

8bit

8

4

4

2

4

10

4

10

4

4

4

16

4

4

4

4

4

OSC1 OSC2

K0 ~ K3

R0 ~ R3

D0 ~ D9

REMOUT

RESET

VDD

GND

OSC

Fig 1-1 Block Diagram (for GMS30140)

Chapter 1. Introduction

Control Signal

1 - 3

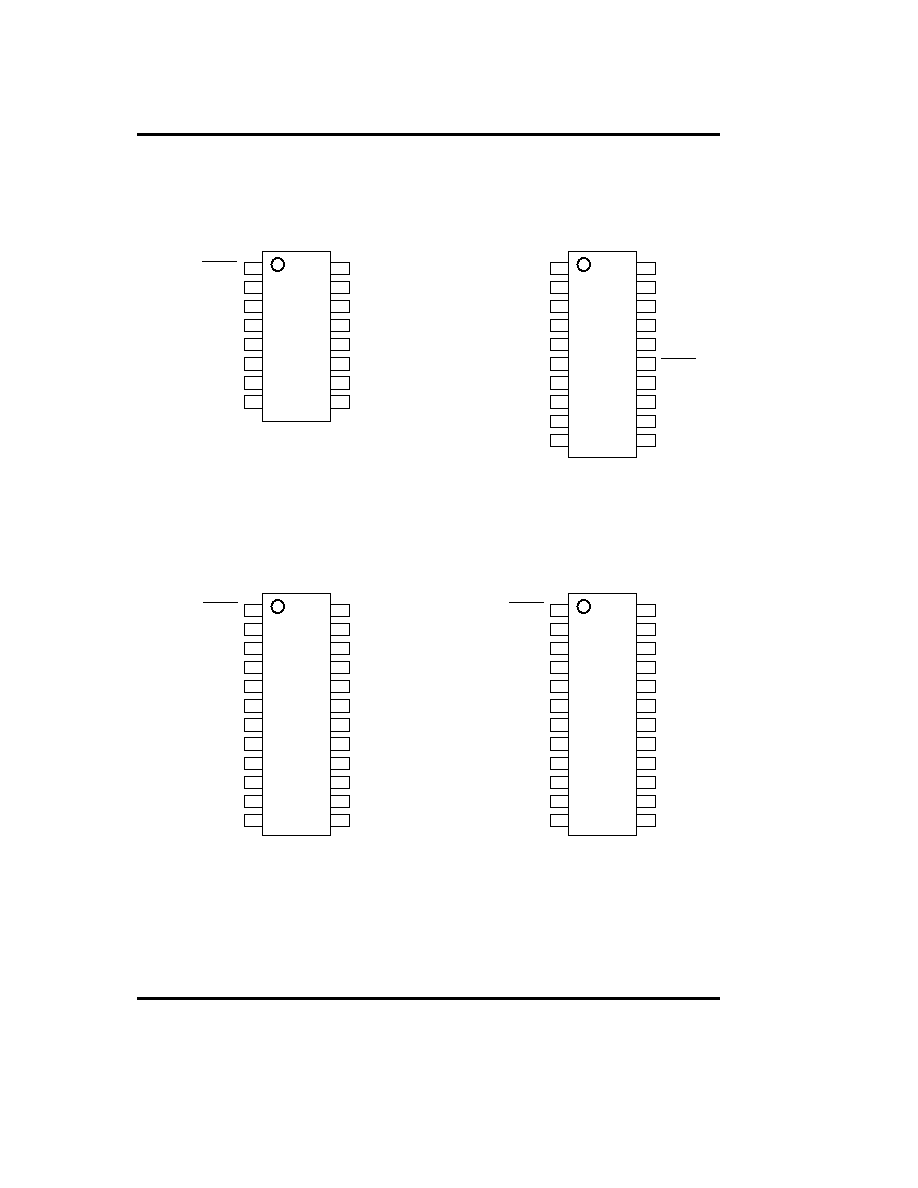

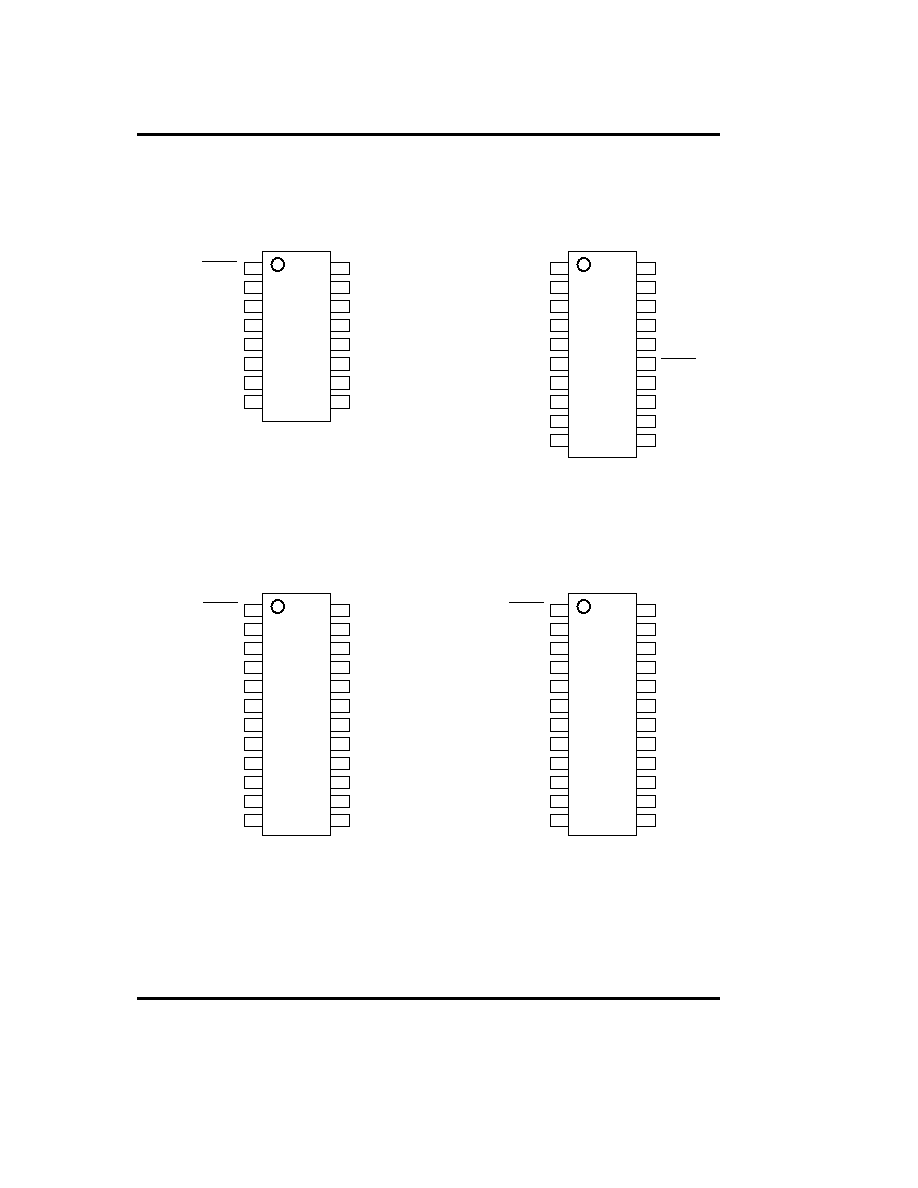

Pin Assignment and terminals

Pin Assignment

2

23

3

22

4

21

5

20

6

19

7

18

8

17

9

16

10

15

11

14

12

13

1

24 VDD

OSC1

OSC2

REMOUT

D7

D6

D5

D4

D3

D2

D1

NC

RESET

GND

R0

R1

R2

R3

K0

K1

K2

K3

D0

NC

Fig 1-2 GMS30004 Pin Assignment

Fig 1-3 GMS30012/112 Pin Assignment

Fig 1-4 GMS30120 Pin Assignment

Chapter 1. Introduction

2

15

3

14

4

13

5

12

6

11

7

10

8

9

1

16 VDD

OSC1

OSC2

REMOUT

D5

D4

D3

D2

RESET

GND

K0

K1

K2

K3

D0

D1

2

19

3

18

4

17

5

16

6

15

7

14

8

13

9

12

10

11

1

20 R3

R2

R1

R0

GND

RESET

VDD

OSC1

OSC2

REMOUT

K0

K1

K2

K3

D0

D1

D2

D3

D4

D5

2

23

3

22

4

21

5

20

6

19

7

18

8

17

9

16

10

15

11

14

12

13

1

24 VDD

OSC1

OSC2

REMOUT

D7

D6

D5

D4

D3

D2

D1

D9

RESET

GND

R0

R1

R2

R3

K0

K1

K2

K3

D0

D8

Fig 1-5 GMS30140 Pin Assignment

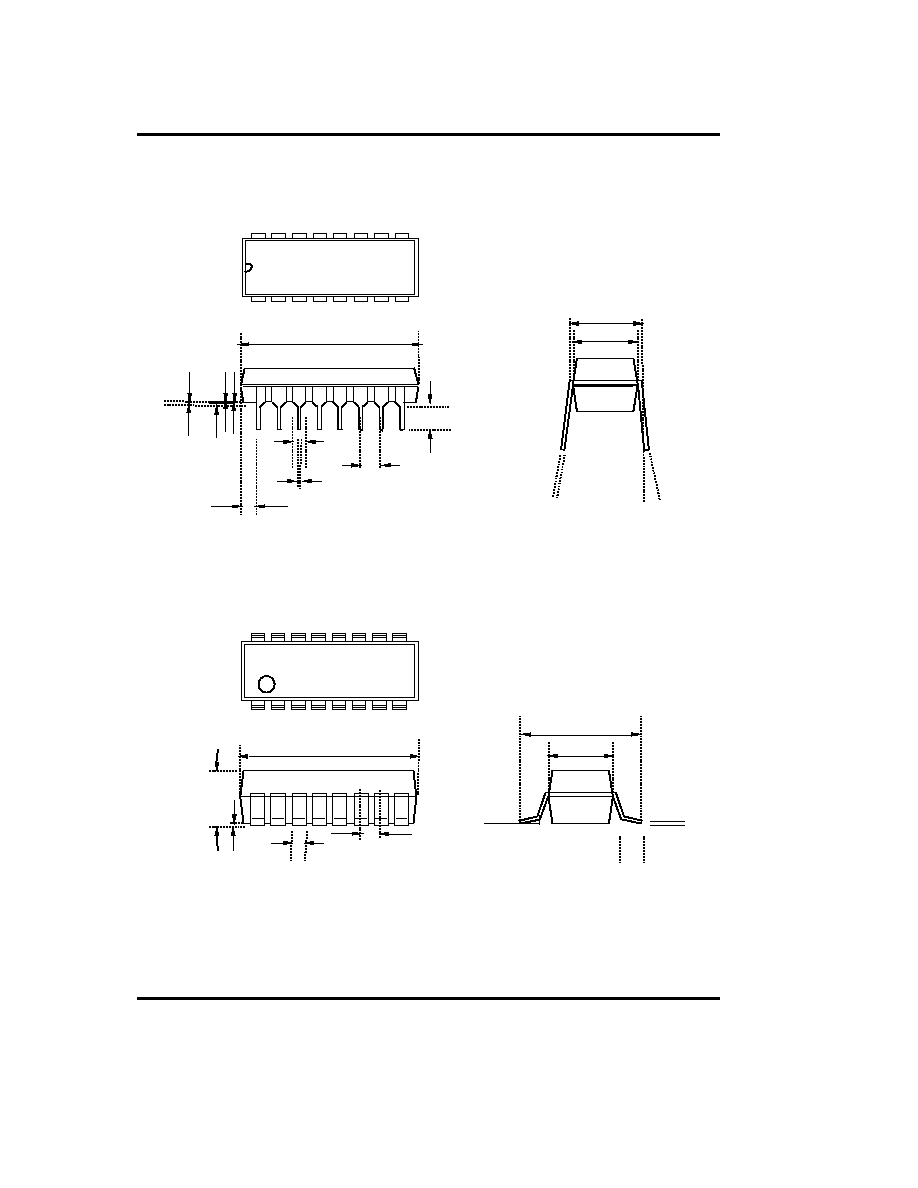

1 - 4

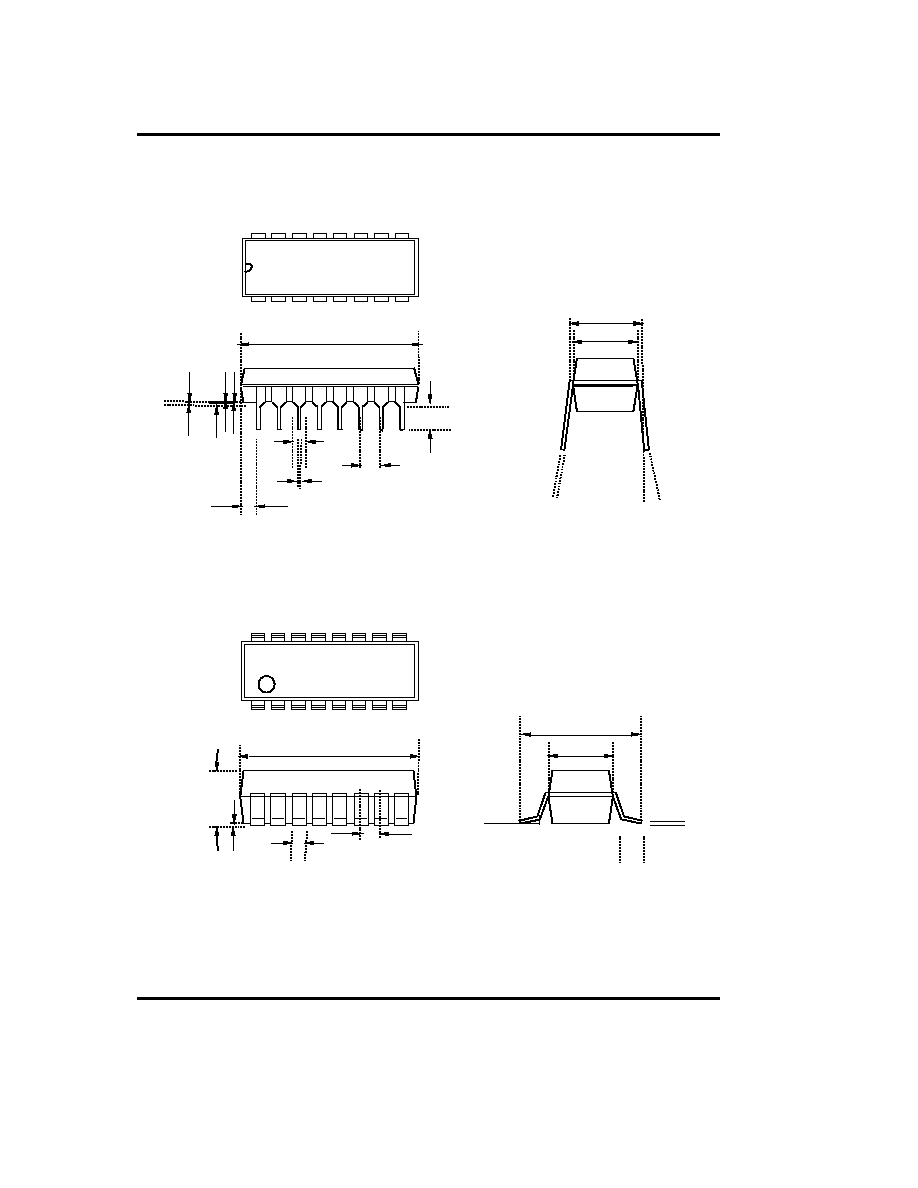

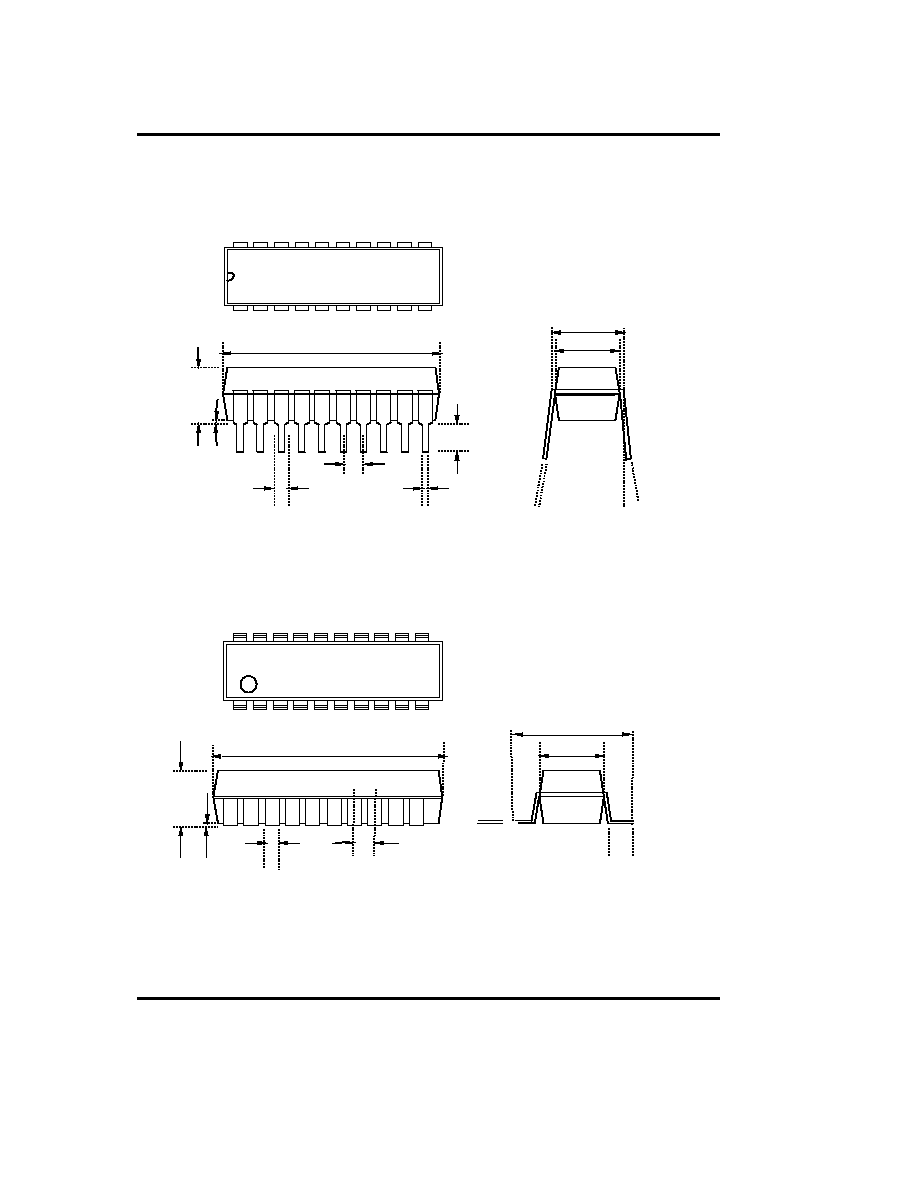

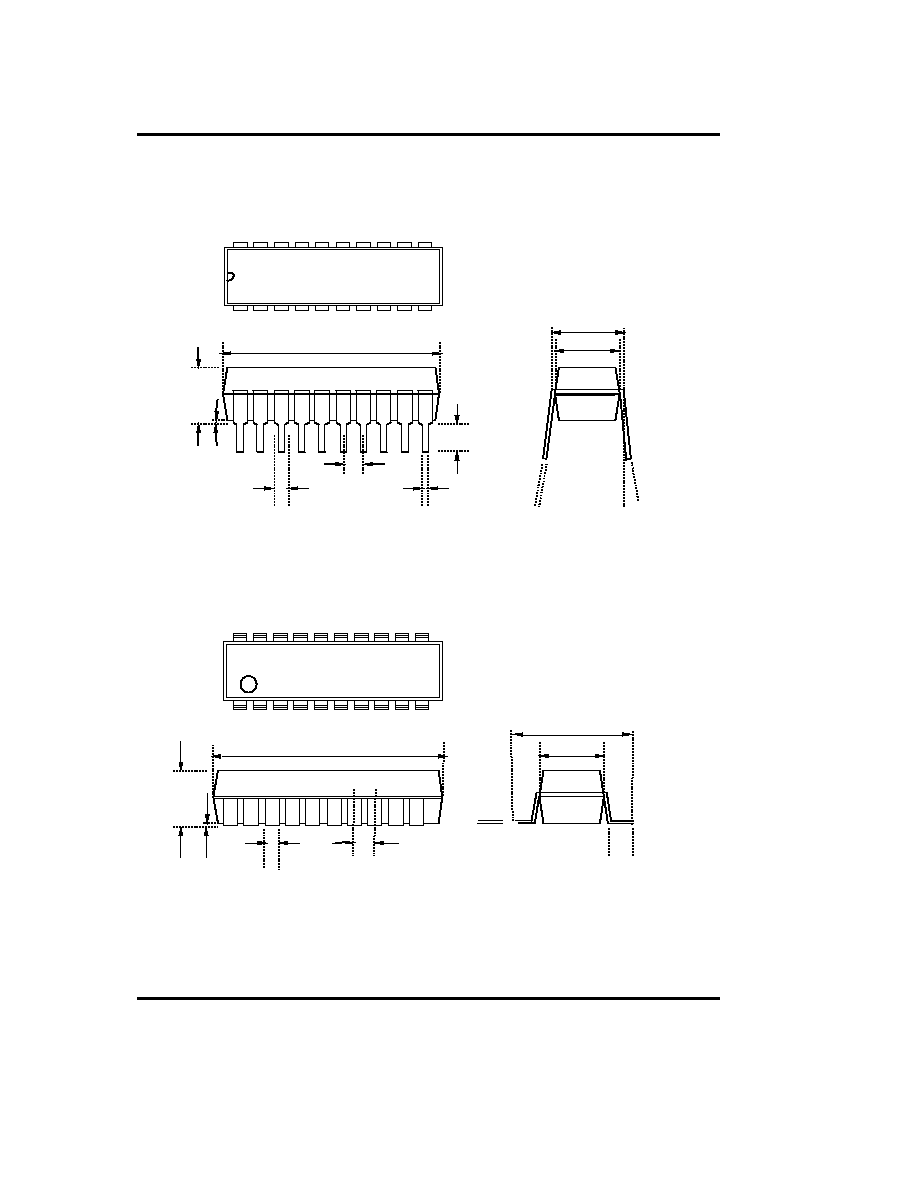

Pin Dimension

Chapter 1. Introduction

1

2

3

4

5

6

7

8

16

15

14 13

12

11

10

9

0.785MAX

0.745MIN

0.040MAX

0.020MIN

0.065MAX

0,

1

0$;

0,

1

â à

â

à

0~15

Ë

0.280MAX

0.240MIN

0.300BSC

0.014MAX

0.008MIN

Outline (Unit:Inch)

0.050MIN

0.022MAX

0.015MIN

0.100BSC

Fig 1-6 16PDIP Pin Dimension

0,

1

0$;

0$;

Outline (Unit : Inch)

0.392MAX

0.386MIN

0.050BSC

0.0200MAX

0.0138MIN

0$; 0,

1

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

0$;

0,

1

â

à

â

à

0.157MAX

0.150MIN

0.244MAX

0.035MAX

0.016MIN

0.230MIN

a

Ë

â

à

0$; 0,

1

Fig 1-7 16SOP Pin Dimension (150Mil)

Base Plane

Seating Plane

1 - 5

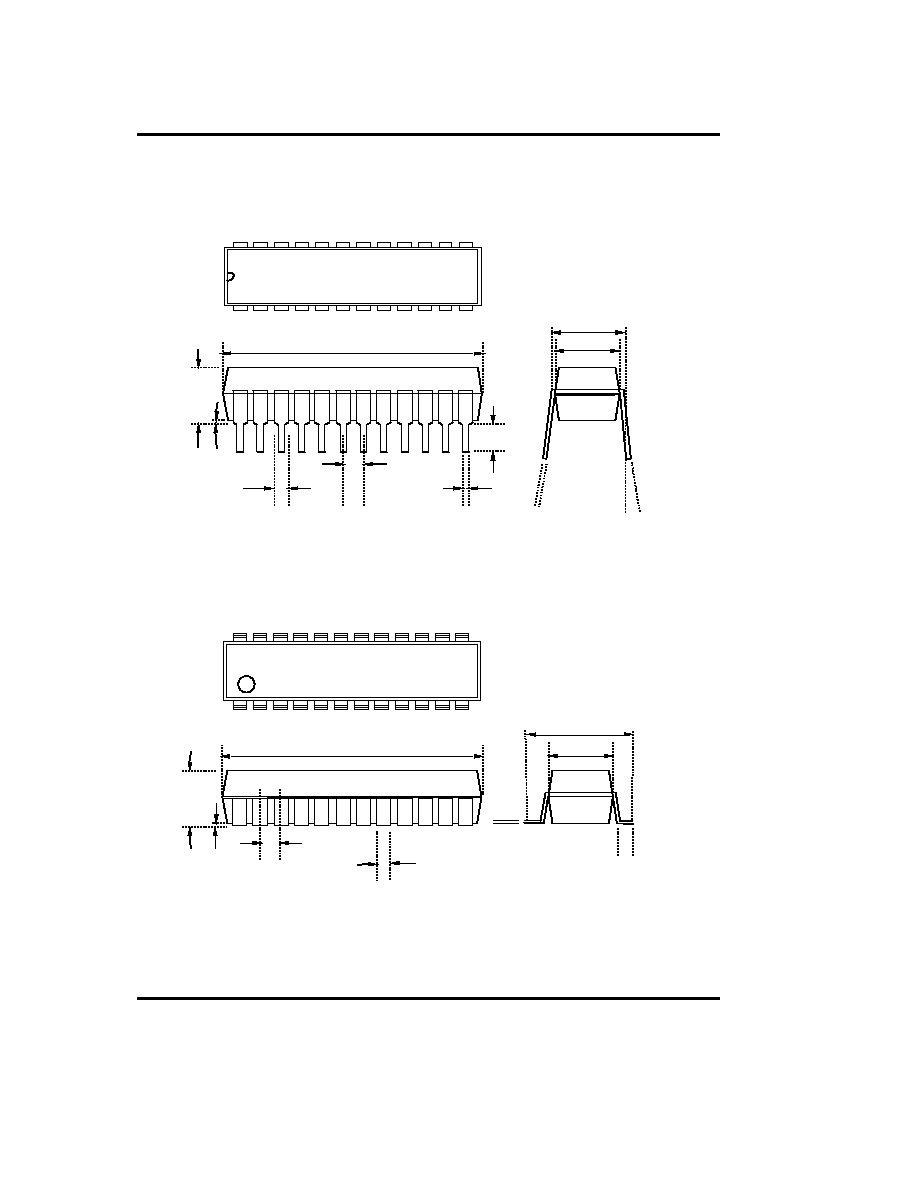

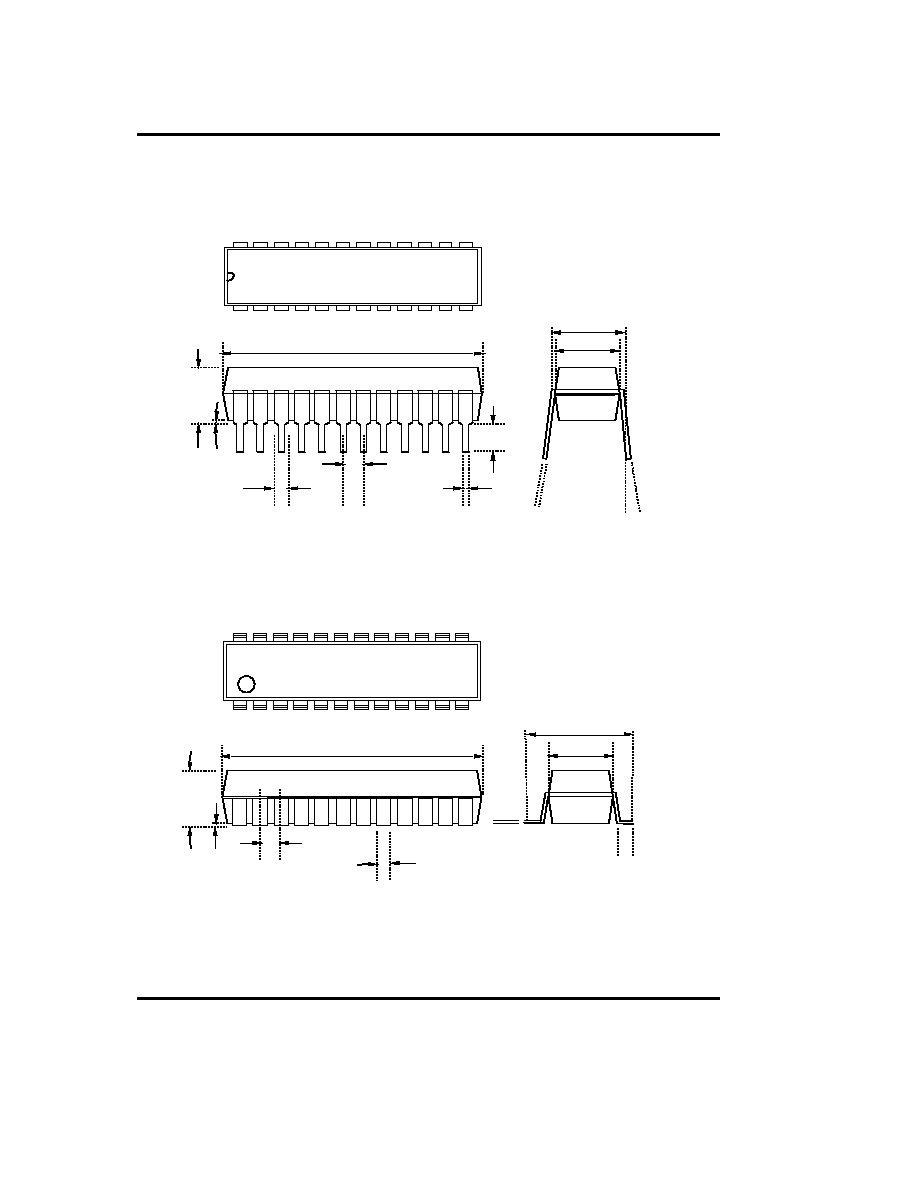

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

0.984MAX

0.968MIN

0.065MAX

0.055MIN

0.022MAX

0.015MIN

0.1TYP

0$;

0,

1

0$;

0,

1

â à

â

à

0~15

Ë

0.270MAX

0.250MIN

0.3TYP

0.012MAX

0.008MIN

Outline (Unit : Inch)

Fig 1-8 20PDIP Pin Dimension

0.5118MAX

0.4961MIN

0.020MAX

0.014MIN

0.05TYP

0$; 0,

1

1

2

3

4

5

6

7

8

9

10

20

19

1 8 17

16

15

14

13

12

11

â

à

â

à

0.299MAX

0.292MIN

0.419MAX

0.125MAX

0.0091MIN

0$;

0,

1

0.042MAX

0.016MIN

Outline (Unit : Inch)

0.398MIN

Fig 1-9 20SOP Pin Dimension

Chapter 1. Introduction

1 - 6

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

1.255MAX

1.245MIN

0.065MAX

0.055MIN

0.022MAX

0.015MIN

0.1TYP

0$;

0,

1

0$;

0,

1

â à

â à

0~15

Ë

0.270MAX

0.250MIN

0.3TYP

0.012MAX

0.008MIN

Outline (Unit : Inch)

Fig 1-10 24PDIP Pin Dimension

0.618MAX

0.595MIN

0.020MAX

0.014MIN

0.05TYP

0.018MAX

0.004MIN

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

â

à

â

à

0.299MAX

0.292MIN

0.419MAX

0.125MAX

0.0091MIN

0$;

0,

1

0.042MAX

0.016MIN

Outline (Unit : Inch)

0.396MIN

Fig 1-11 24SOP Pin Dimension

Chapter 1. Introduction

1 - 7

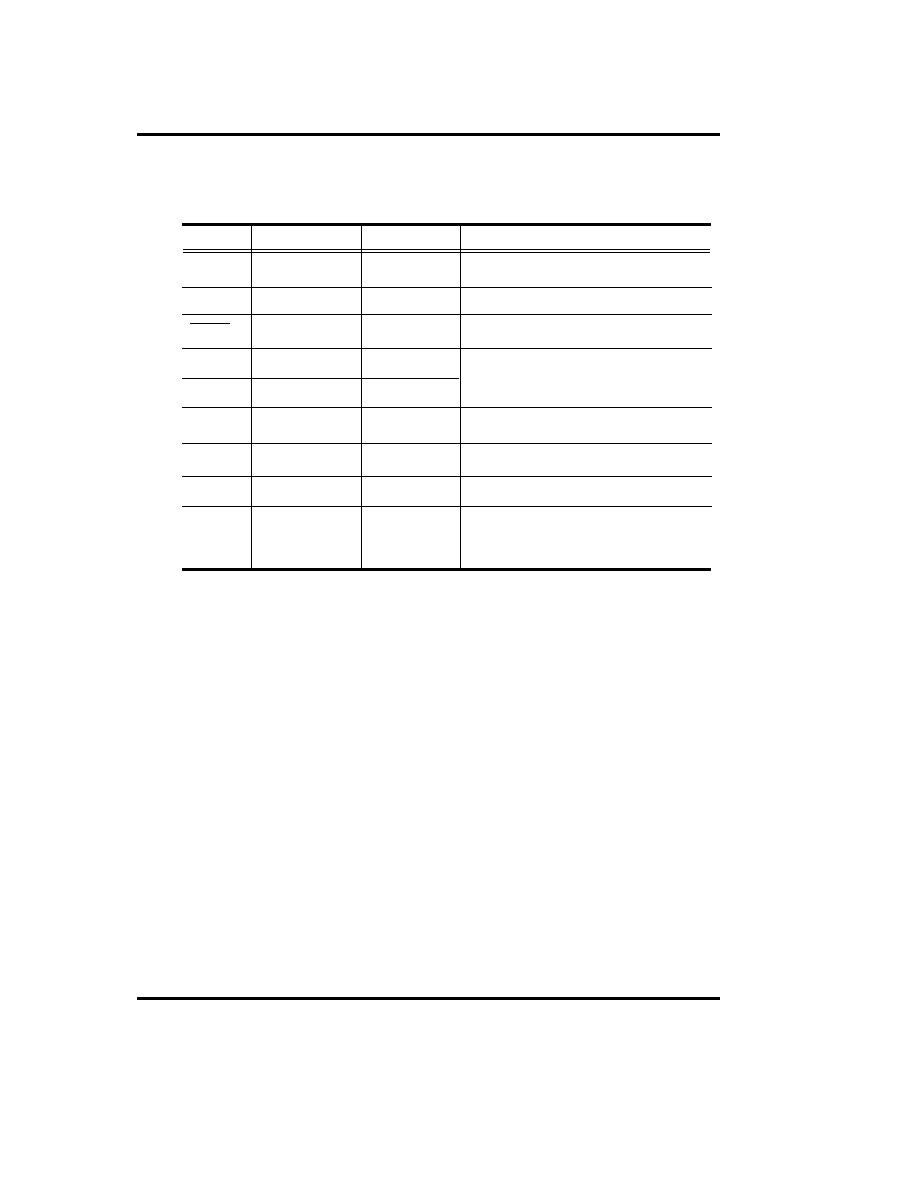

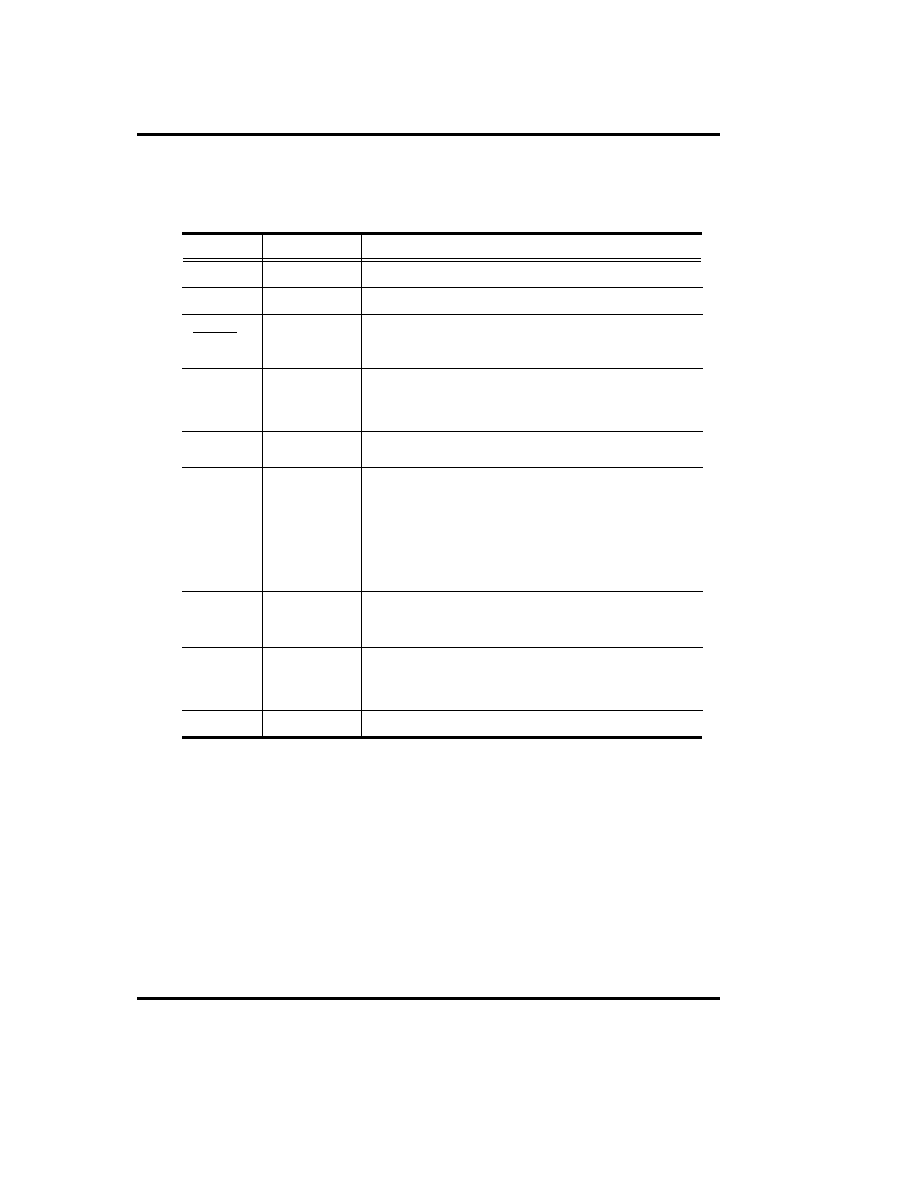

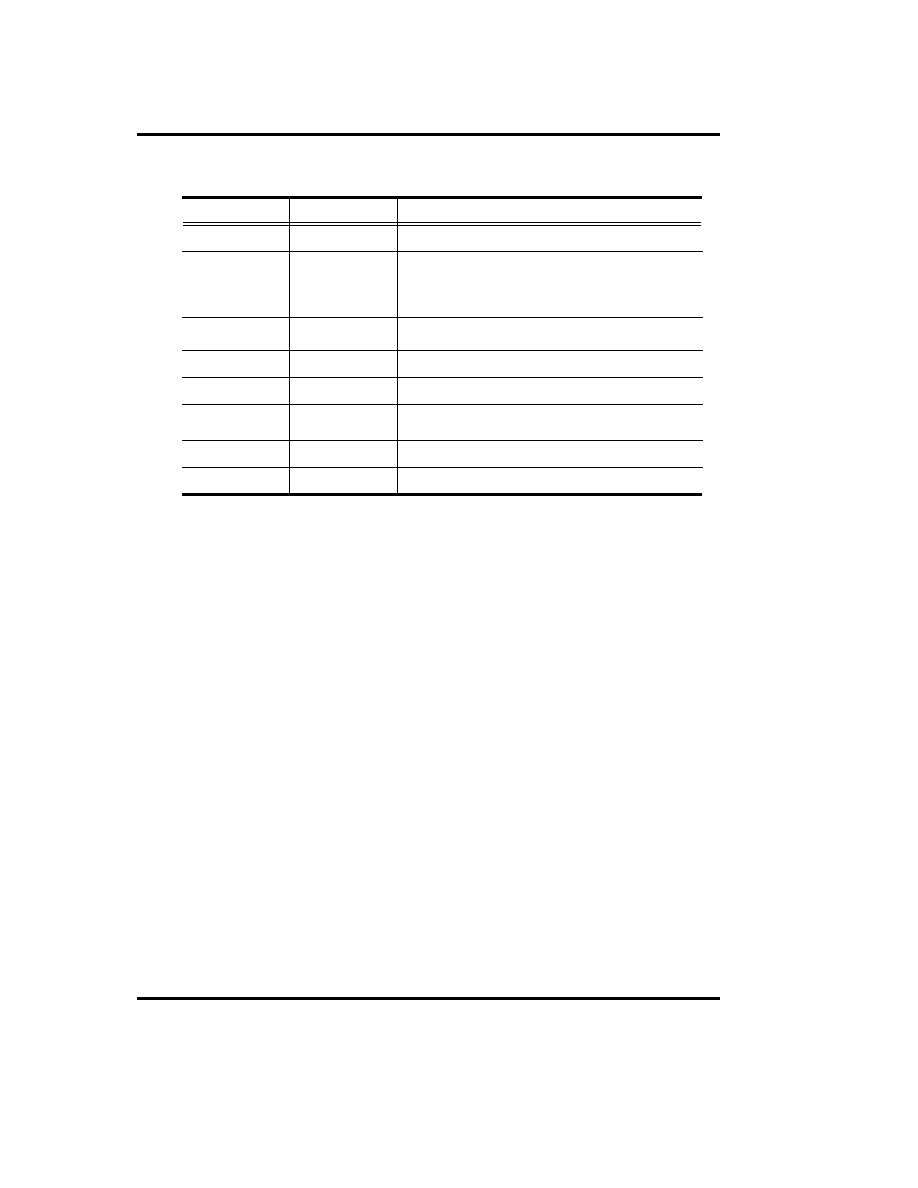

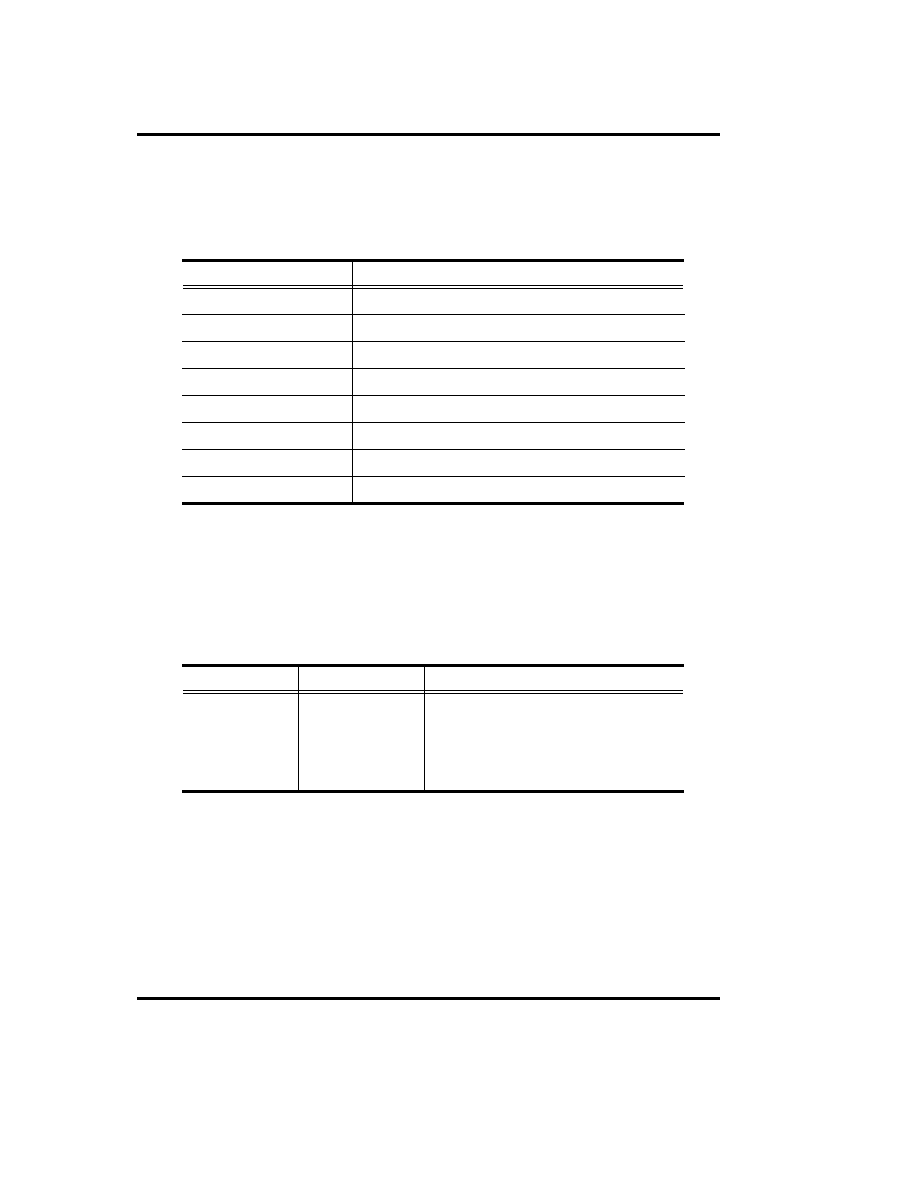

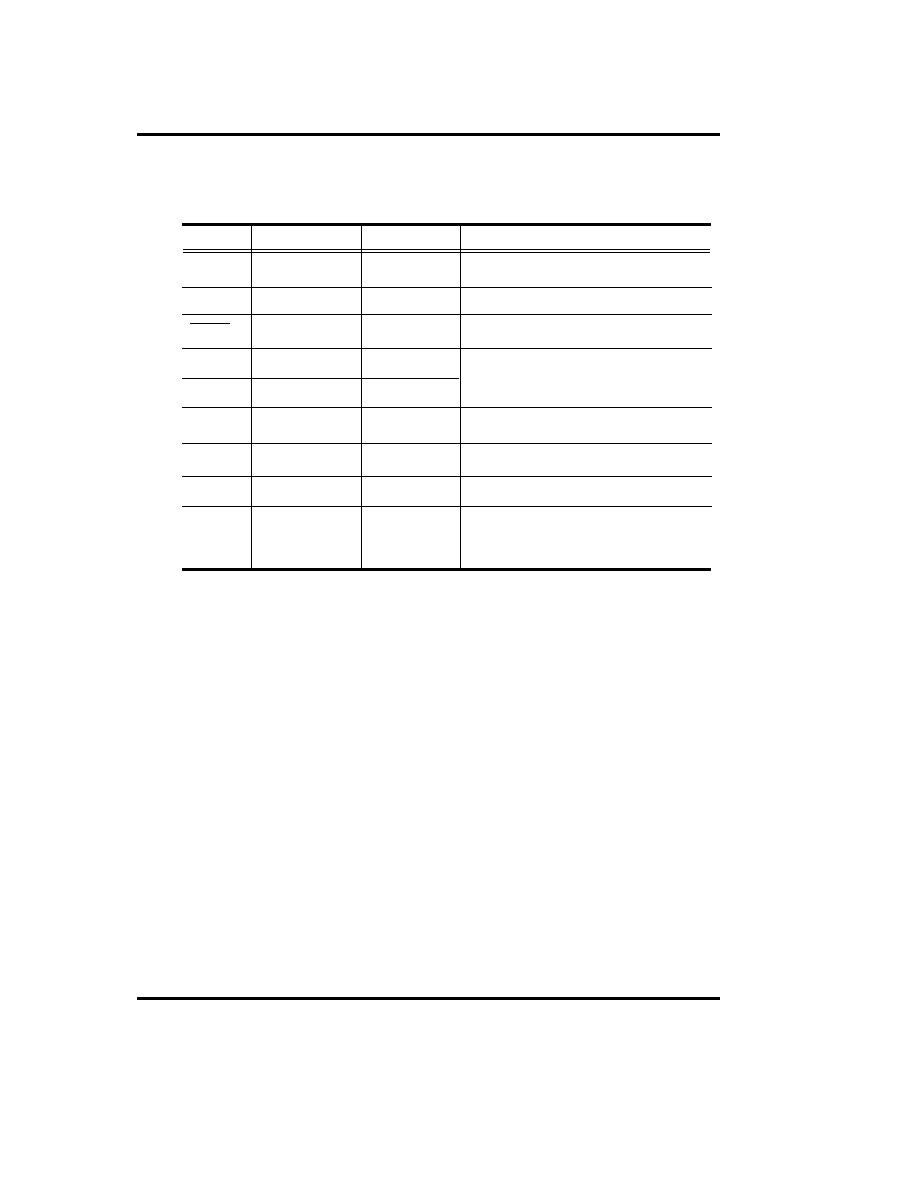

Pin Description

Chapter 1. Introduction

Pin

VDD

GND

RESET

OSC1

OSC2

REMOUT

R0 ~ R3

K0 ~ K3

D0 ~ D9

Name

Ground

Reset input

Oscillator input

Oscillator output

R-Port

K-Port

D-Port

Input/Output

I

I

O

O

I/O

I

O

Function

Connected to 2.0~4.0V power supply

Connected to 0V power supply.

Reset signal input which is a low active.

I/O pins of internal clock oscillating circuit.

Built in feedback resistor. Connect a ceramic

resonator to these pins.

Remocon signal output port which has high

current driving capability.

4bit programmable I/O port.

4bit input port with built in pull-up resistor.

10bit output port which can be set or reset pin

by pin independently.

The output structure is N-channel open drain.

1 - 8

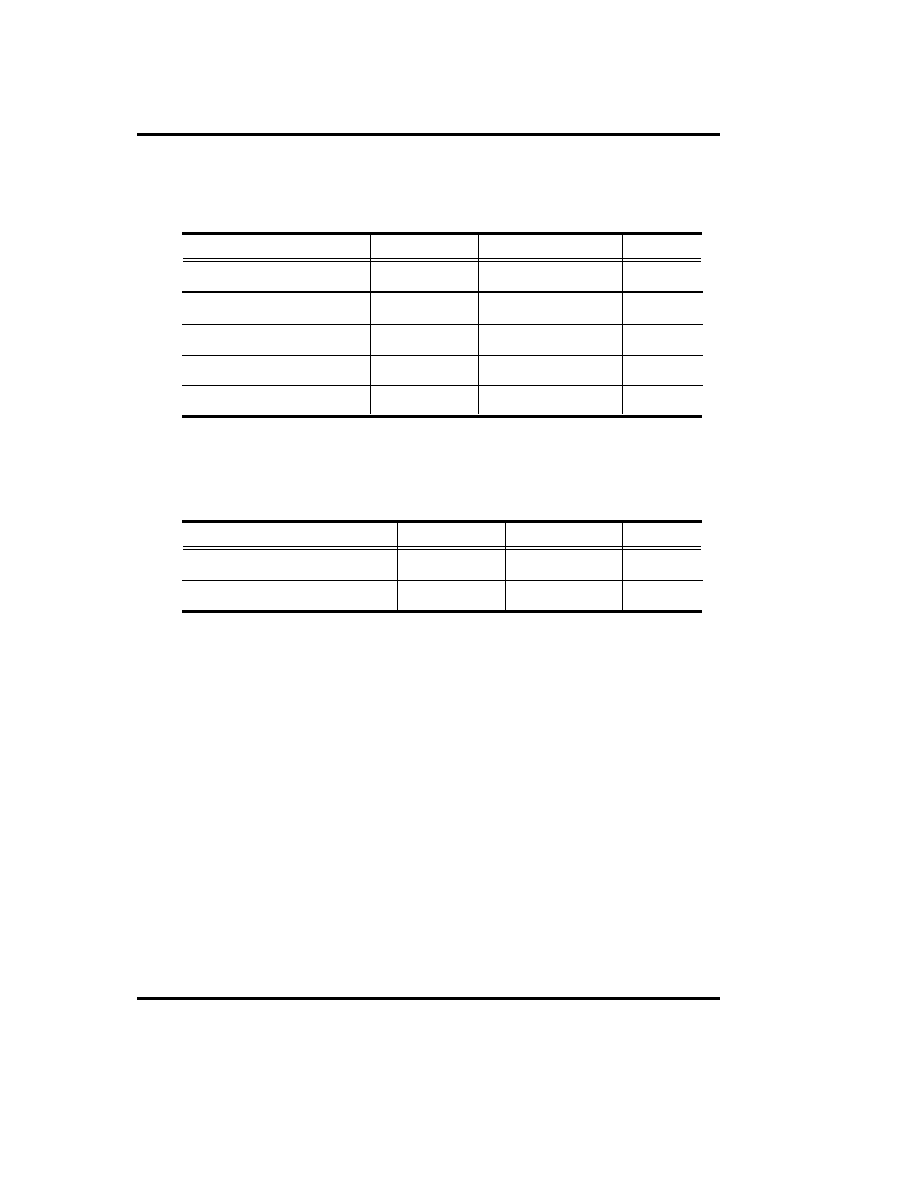

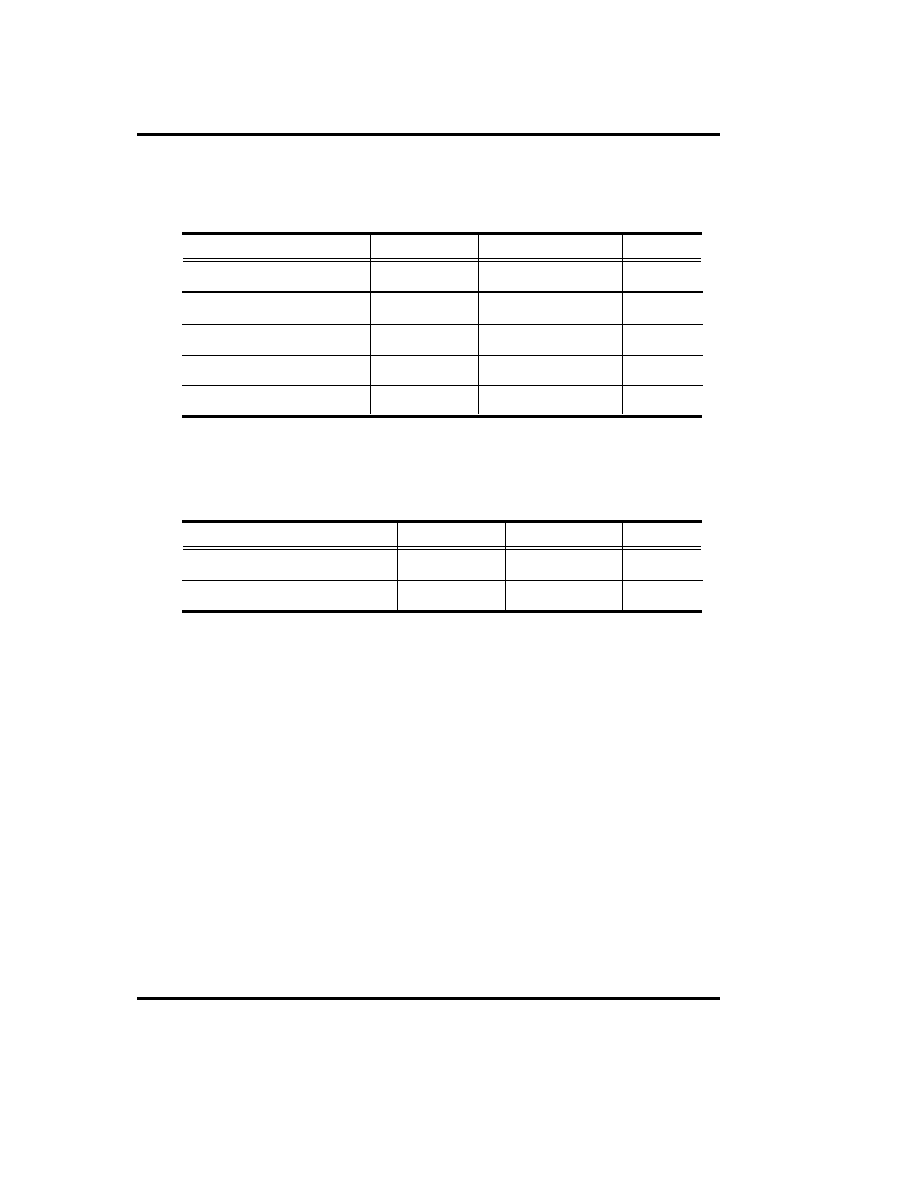

Parameter

Supply Voltage

Power dissipation

Storage temperature range

Input voltage

Output voltage

Unit

V

mW

Î

V

V

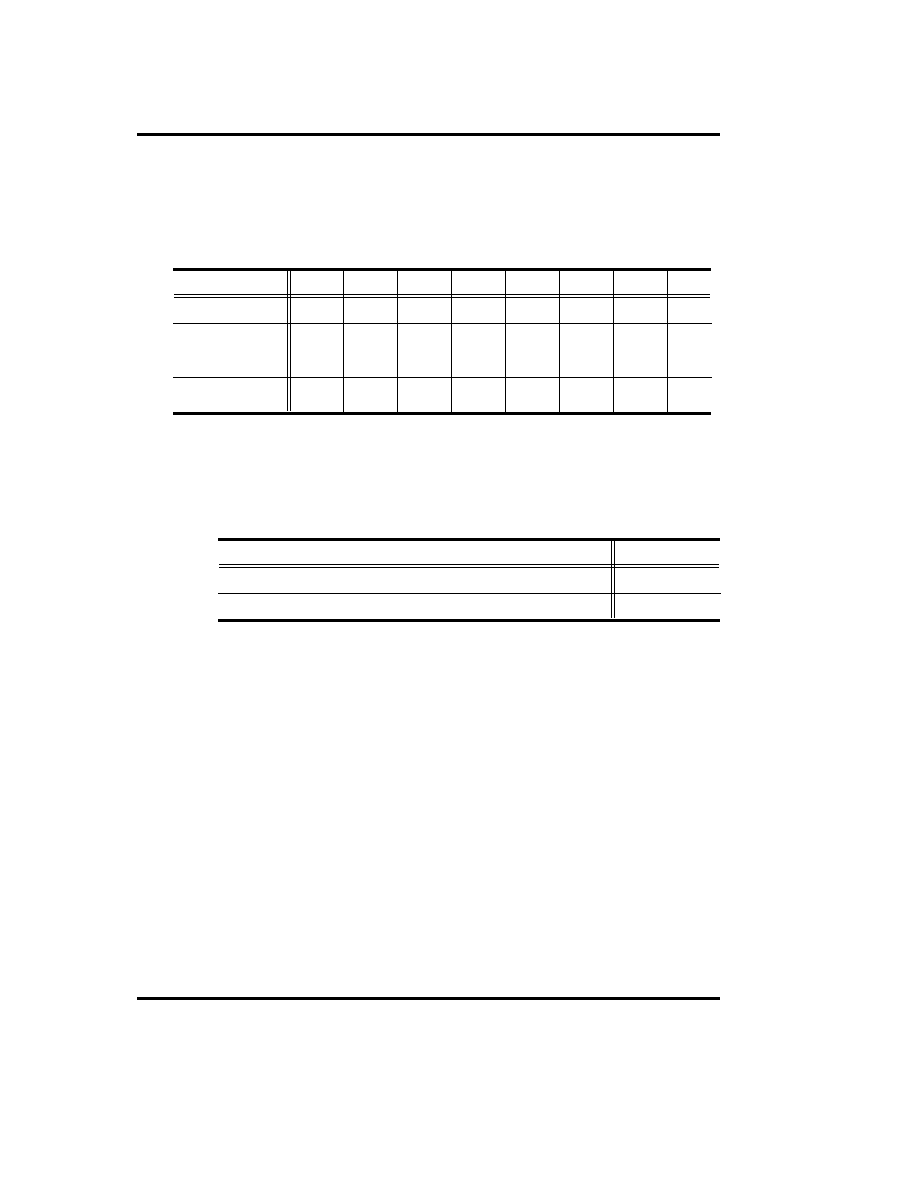

Electrical Characteristics for GMS300 series

Absolute maximum ratings (Ta = 25

Î

)

Symbol

V

DD

P

D

Tstg

V

IN

V

OUT

Max. rating

-0.3 ~ 5.0

700*

-55 ~ 125

-0.3 ~ V

DD

+0.3

-0.3 ~ V

DD

+0.3

* Thermal derating above 25

Î

: 6mW per degree

Î

rise in temperature.

Parameter

Supply Voltage

Operating temperature

Unit

V

Î

Recommended operation condition

Rating

2.2 ~ 4.0

-20 ~ +70

Chapter 1. Introduction

Symbol

V

DD

Topr

* In case of using 455KHz resonator.

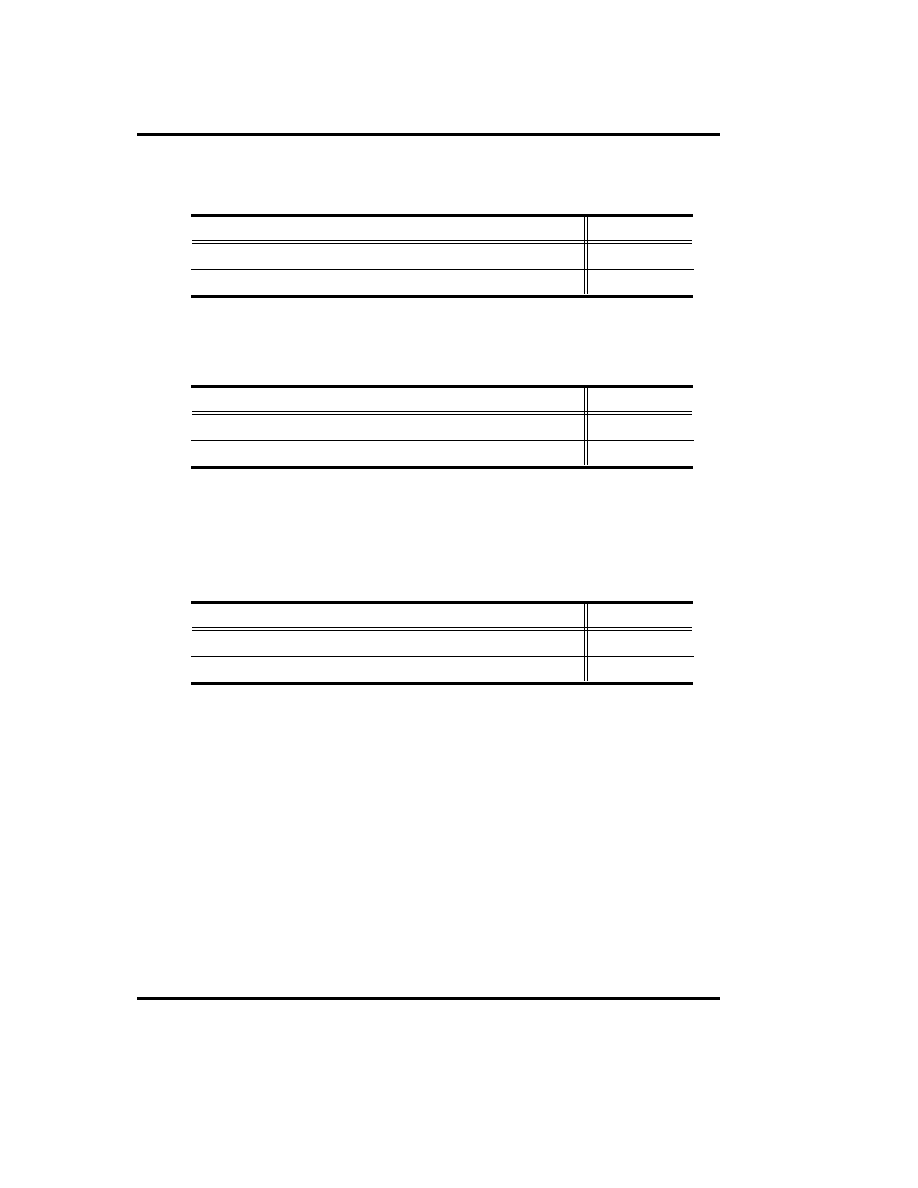

1 - 9

Parameter

Input H current

RESET input L current

K, R input L current

K, R input H voltage

K, R input L voltage

RESET input H voltage

RESET input L voltage

D. R output L voltage

REMOUT output L voltage

REMOUT output H voltage

OSC2 output L voltage

OSC2 output H voltage

D, R output leakage current

Current on STOP mode

Operating supply current 1

Operating supply current 2

Operating frequency

Electrical characteristics (Ta=25

Î

, V

DD

=3V)

Symbol

I

IH

I

IL2

I

IL1

V

IH1

V

IL1

V

IH2

V

IL2

V

OL2

V

OL1

V

OH1

V

OL3

V

OH3

I

OL

I

STOP

I

DD1

I

DD2

f

OSC

Limits

Unit

uA

uA

uA

V

V

V

V

V

V

V

V

V

uA

uA

mA

mA

MHz

Min.

-

-3

-9

2.1

-

2.25

-

-

-

2.1

-

2.1

-

-

-

-

0.3

Typ.

-

-7.5

-25

-

-

-

-

0.15

0.15

2.5

0.4

2.5

-

-

0.3

0.2 5

-

Max.

1

-16

-50

-

0.9

-

0.75

0.4

0.4

-

0.9

-

1

1

1.0

-

1

Condition

V

I

=V

DD

V

I

=GND

V

I

=GND, Output off,

Pull-up resistor

provided.

-

-

-

-

I

OL

=1mA

I

OL

=100uA

I

OH

=-8mA

I

OL

=70uA

I

OH

=70uA

V

0

=V

DD

, Output off

At STOP mode

f

OSC

= 455KHz

f

OSC

= 1MHz

-

Chapter 1. Introduction

1 - 10

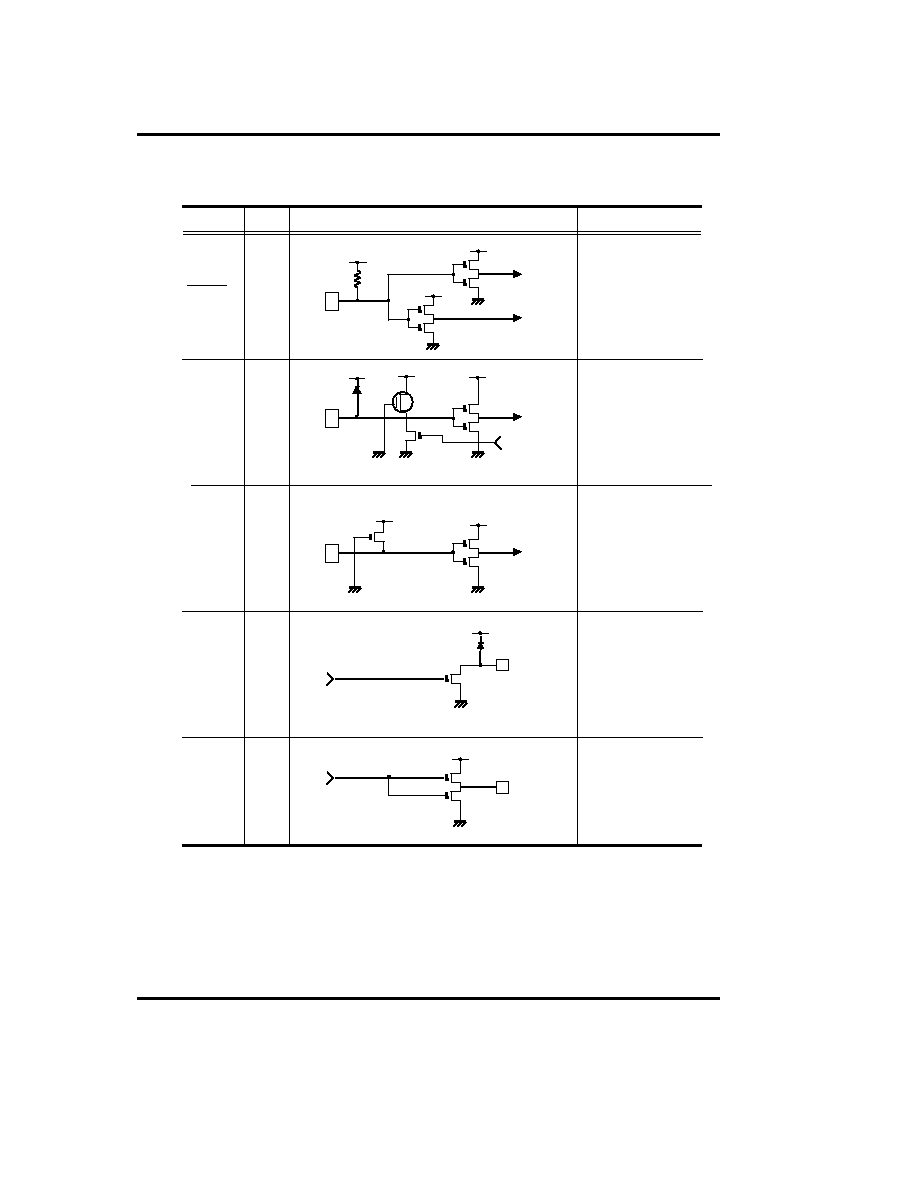

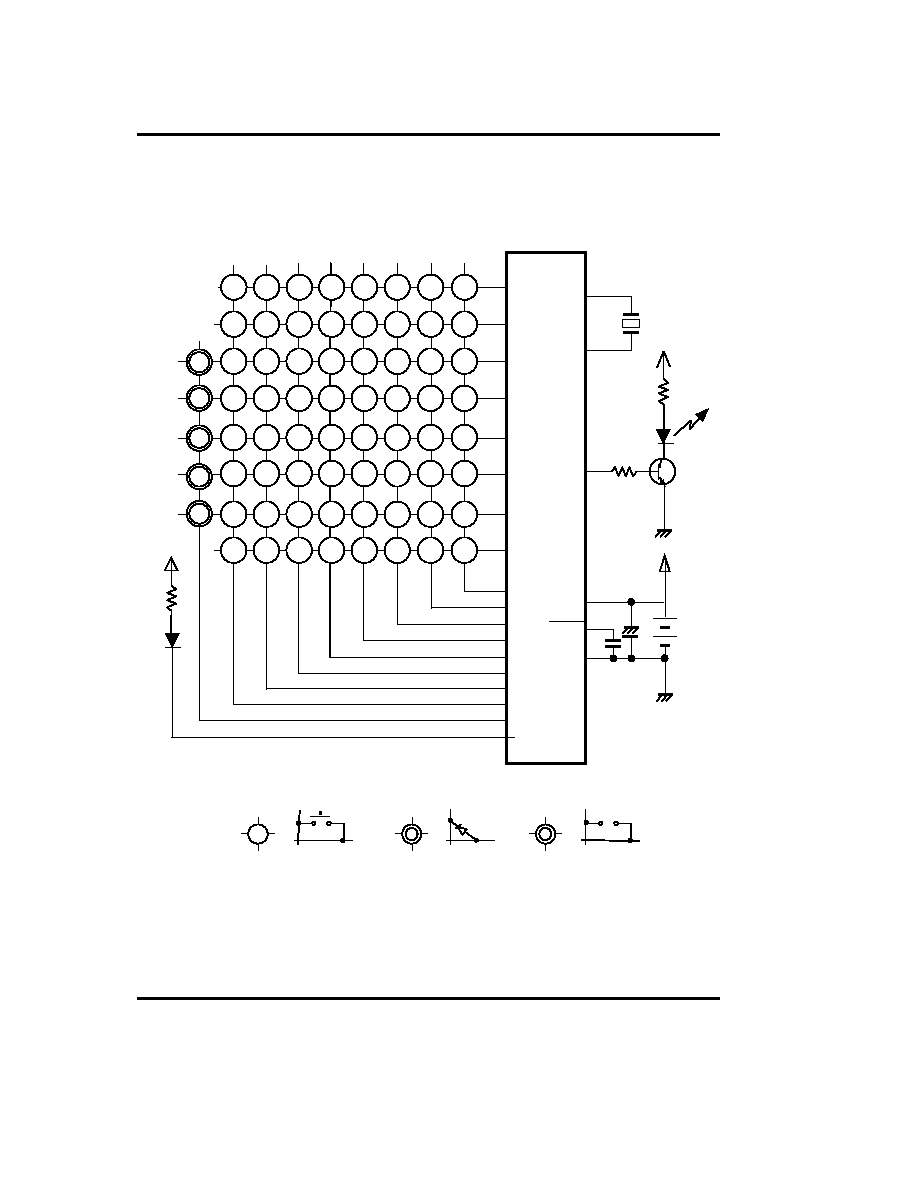

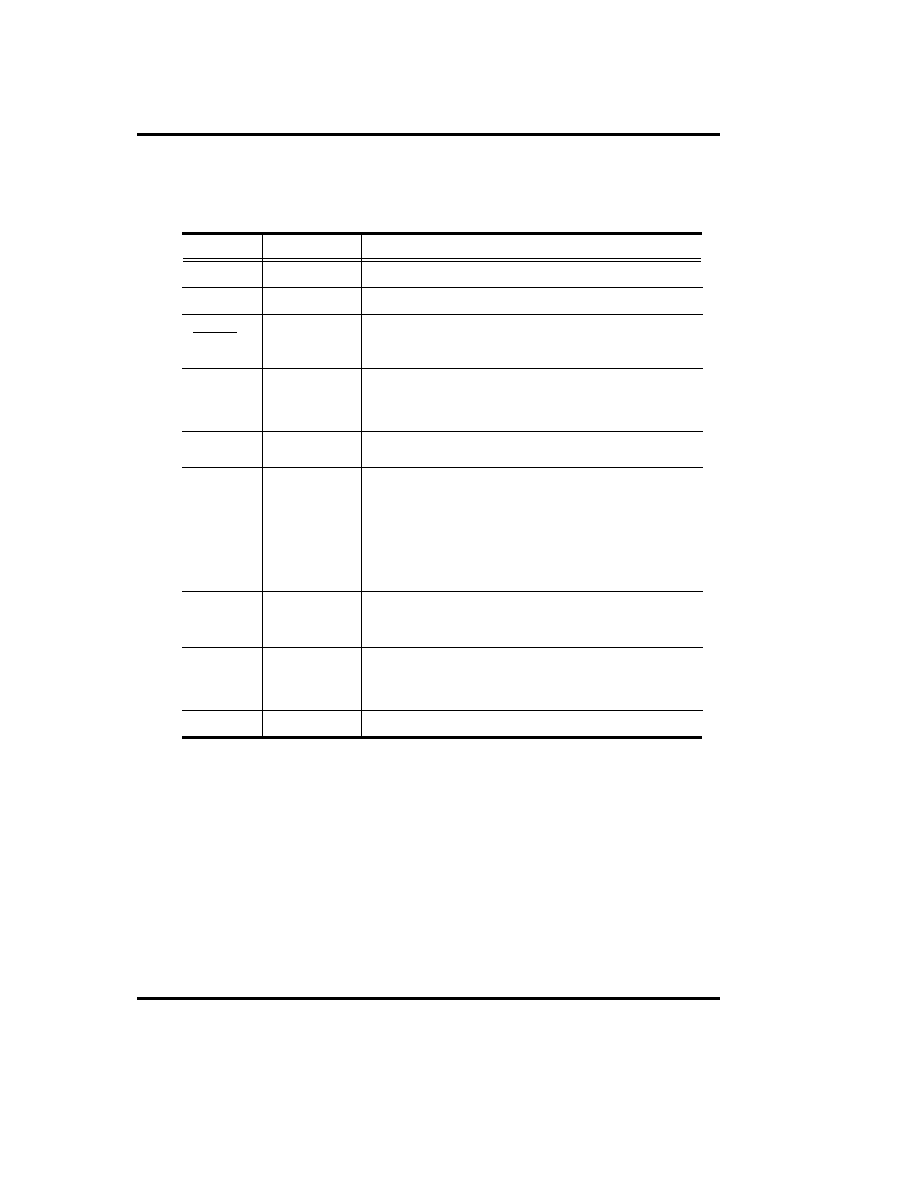

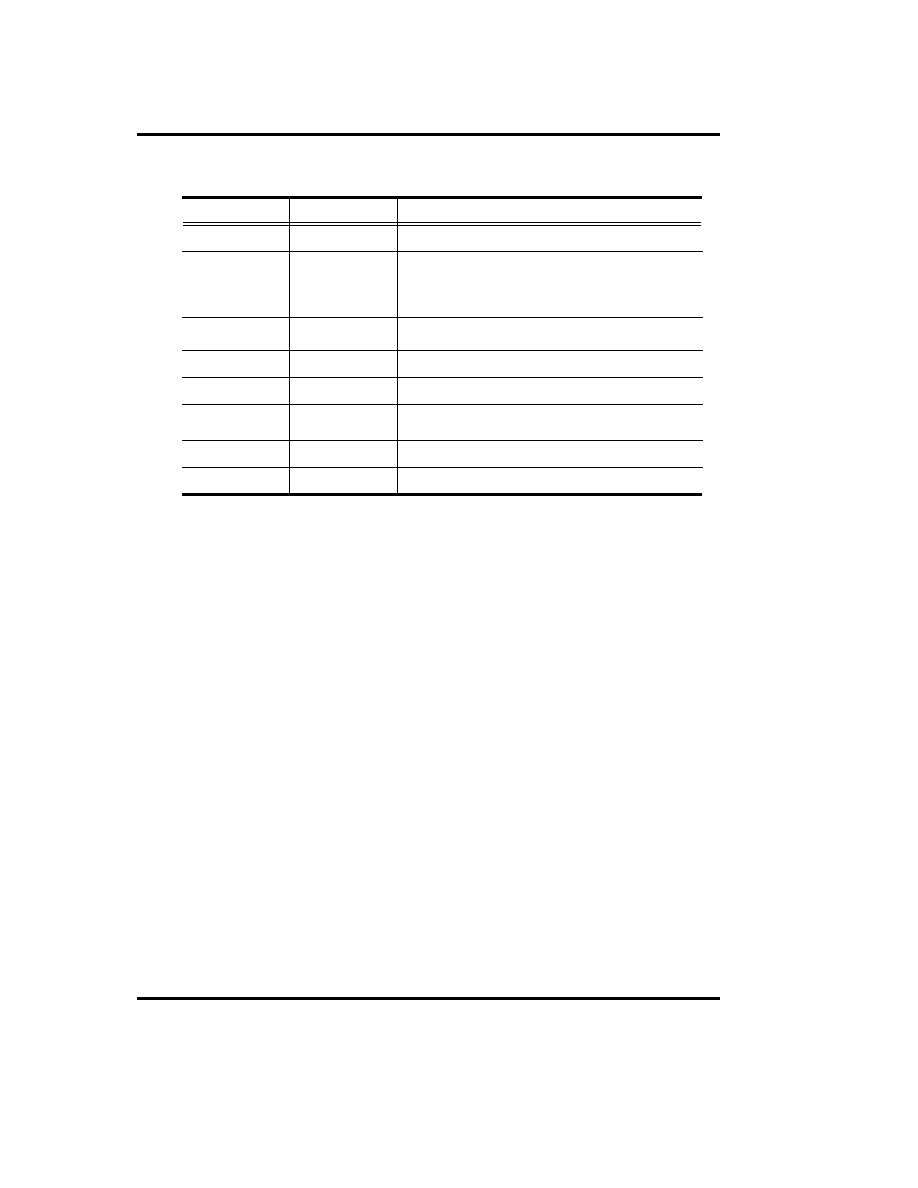

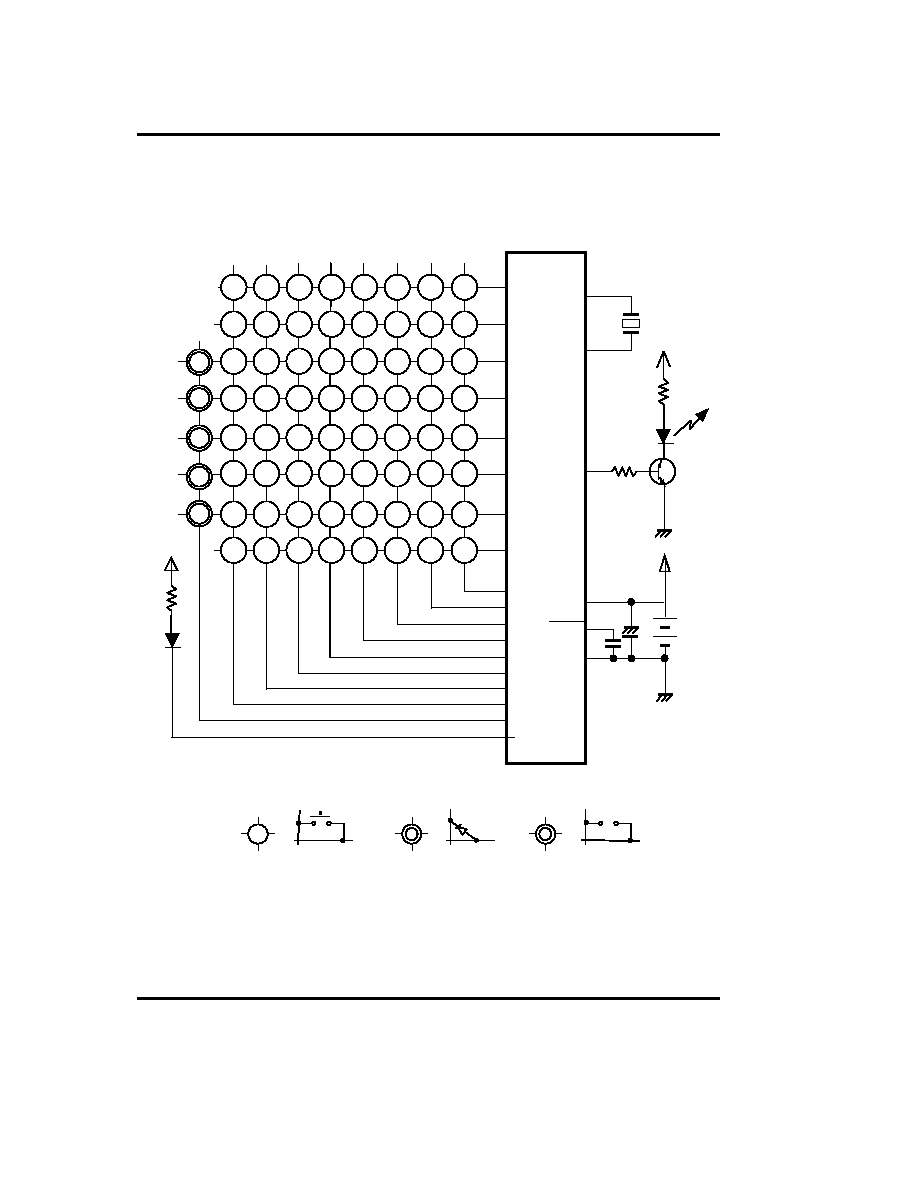

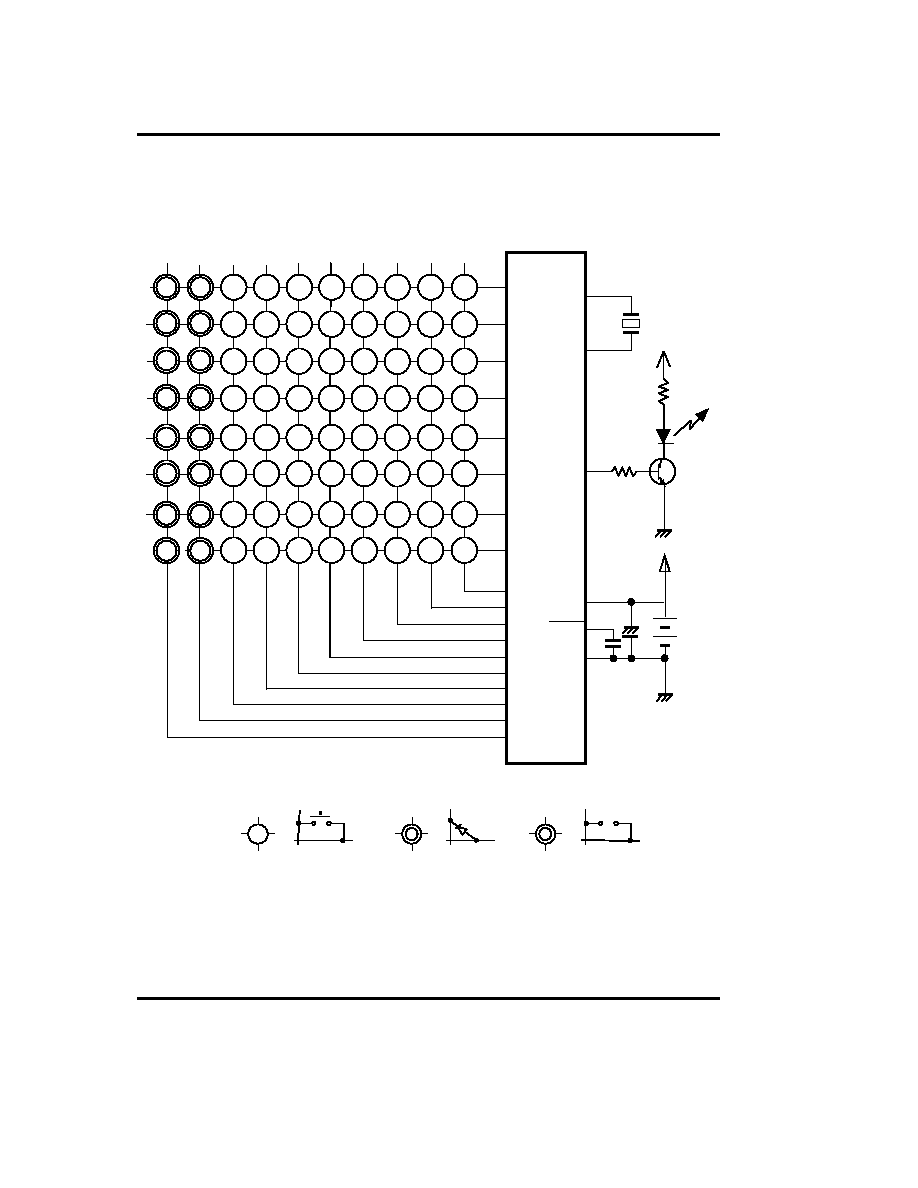

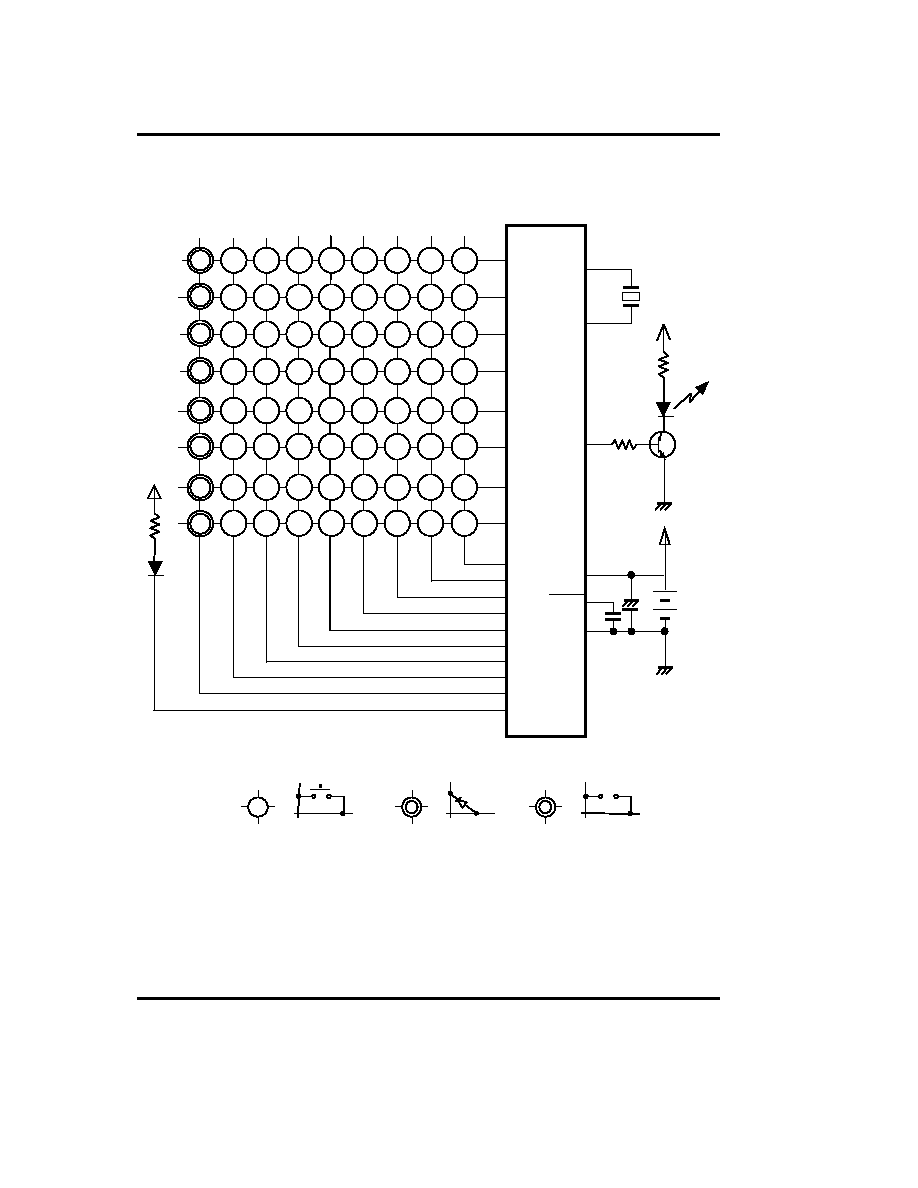

I/O circuit types and options

GMS300 series I/O port types

Chapter 1. Introduction

Pin

Function

I/O

Connected to 2.0~4.0V power supply.

Connected to 0V power supply.

Used to input a manual reset. When the pin goes

Ì

L

Ì

, the

D-output ports and REMOUT-output port are initialized to

Ì

L

Ì

, and ROM address is set to address 0 on page 0.

4-bit input port.

Released STOP mode built in pull-up resistor by each pin

as masked option.

(It is released by

Ì

L

Ì

input at STOP)

Each can be set and reset independently. The output is in

the form of N-channel-open-drain.

4-bit I/O port. (Input mode is set only when each of them

output

Ì

H

Ì

.)

In outputting, each can be set and reset independently(or at

once.)

The output is in the form of N-channel-open-drain.

Pull-up resistor and STOP release mode can be respectively

selected as masked option for each bit. (It is released by

Ì

L

Ì

input at STOP.)

High current output port.

The output is in the form of C-MOS.

The state of large current on is

Ì

H

Ì

.

Oscillator input. Input to the oscillator circuit and connection

point for ceramic resonator.

Internal capacitors available as masked option.

A feedback resistor is connected between this pin and OSC2

Connect a ceramic resonator between this pin and OSC1.

V

DD

GND

RESET

K0~K3

D0~D9

R0~R3

REMOUT

OSC1

OSC2

Input

Input

Output

I/O

Output

Input

Output

-

-

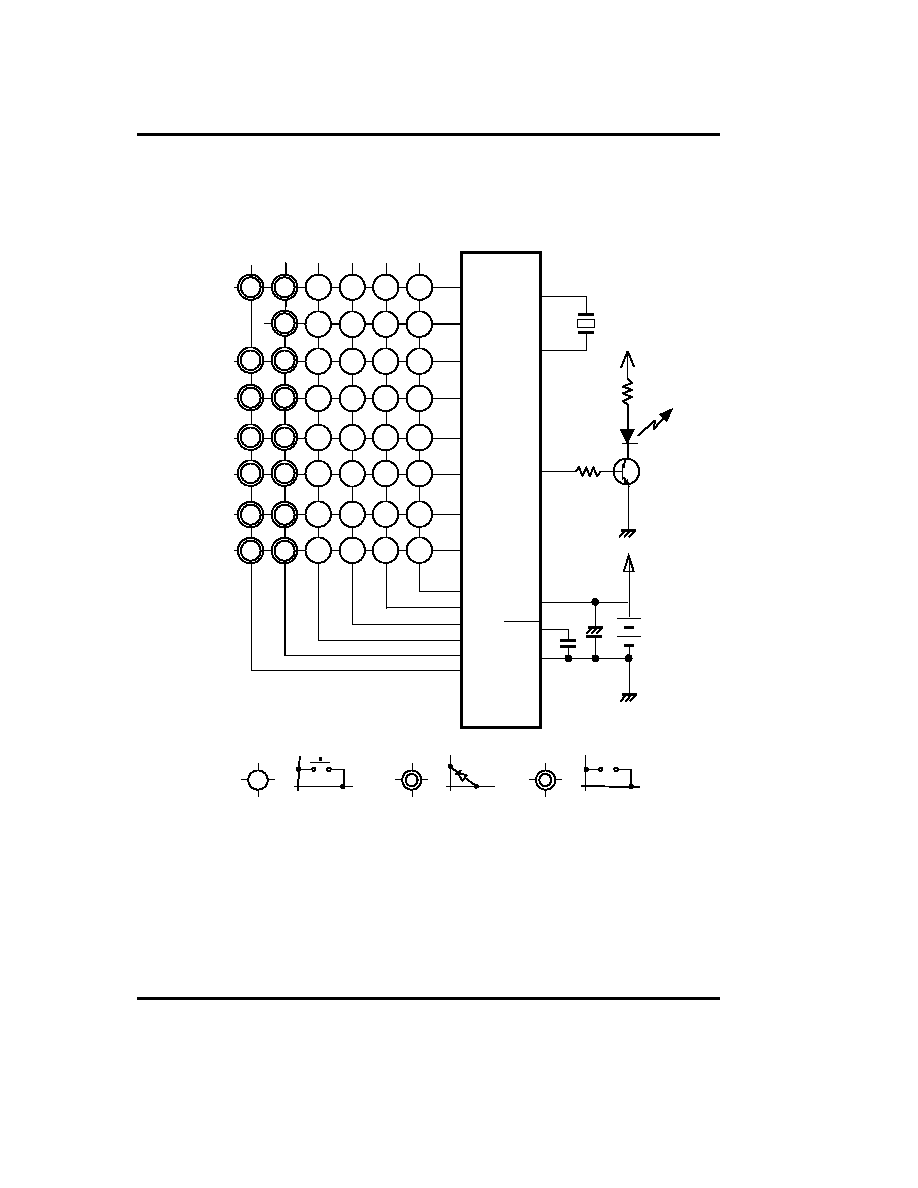

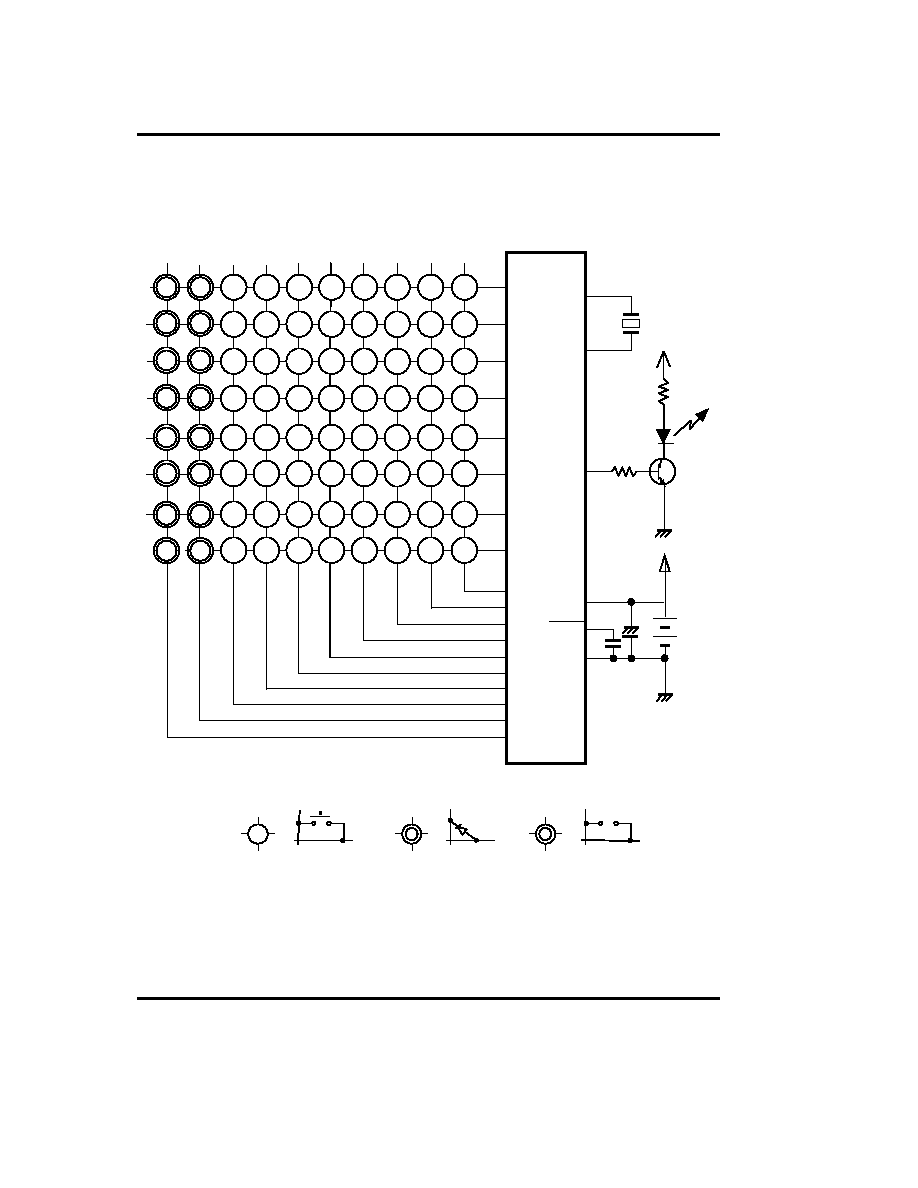

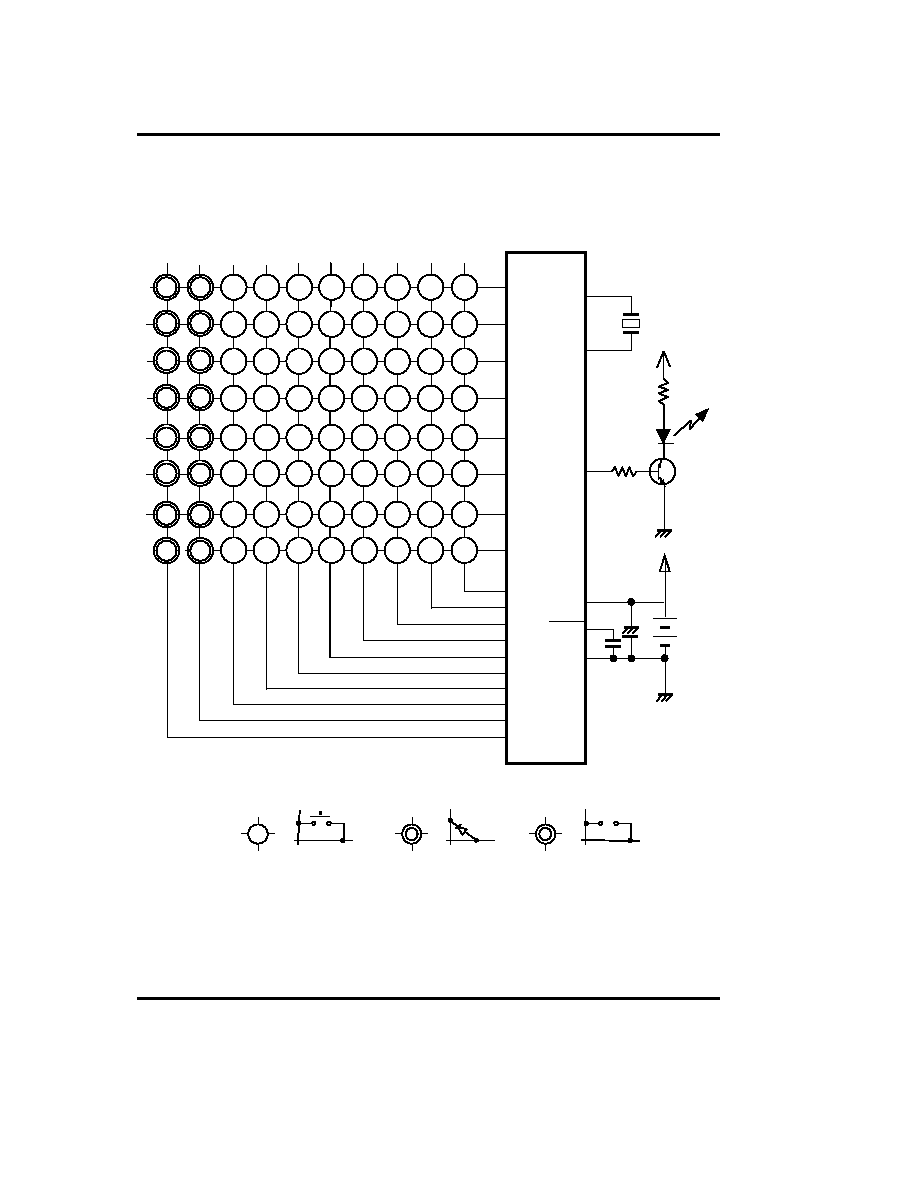

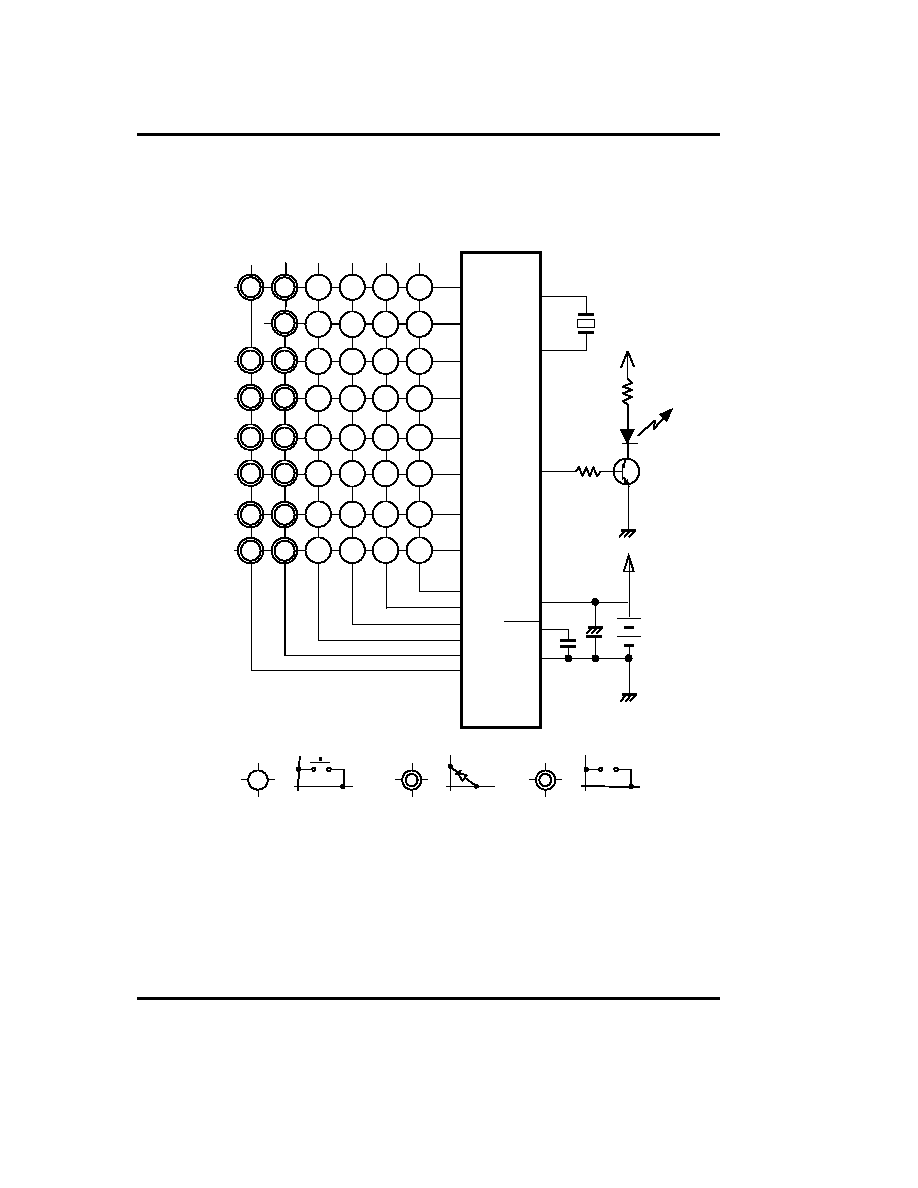

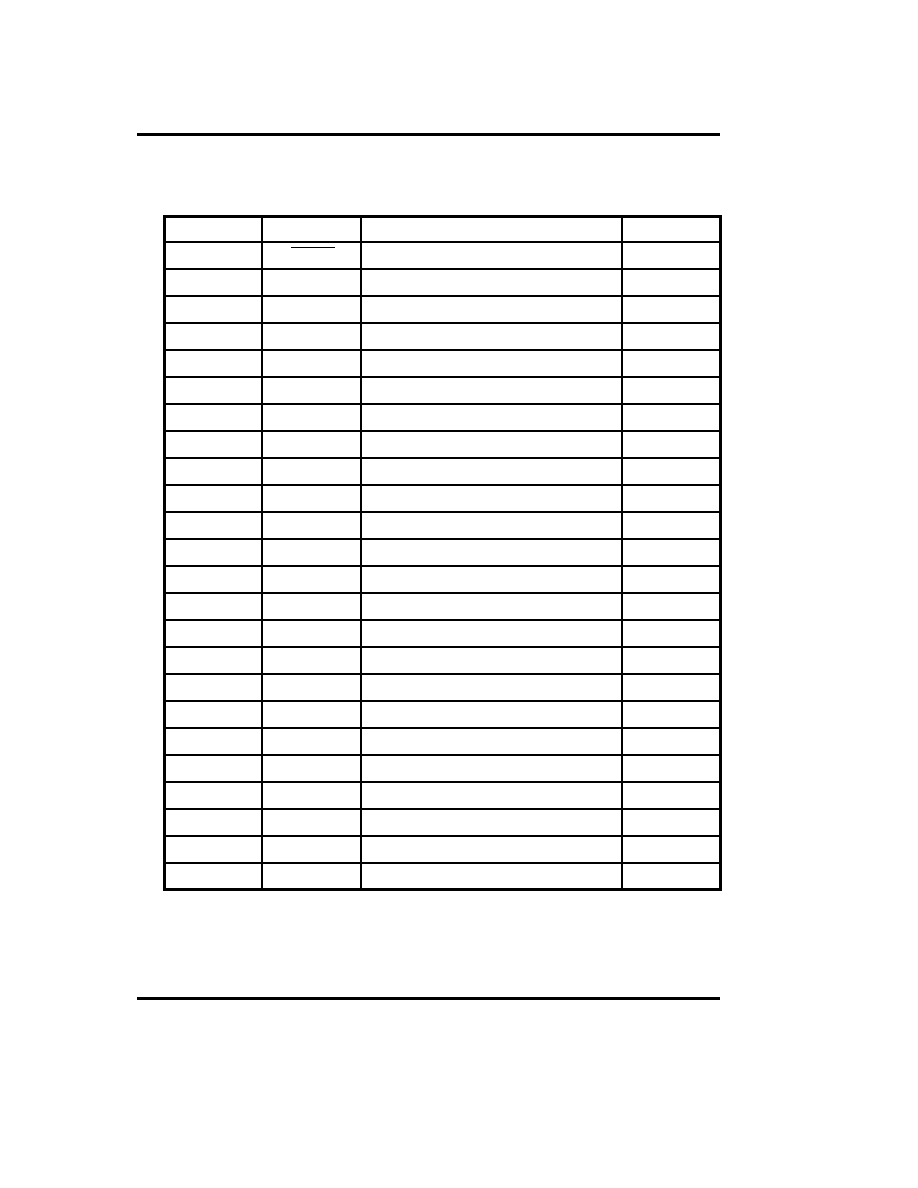

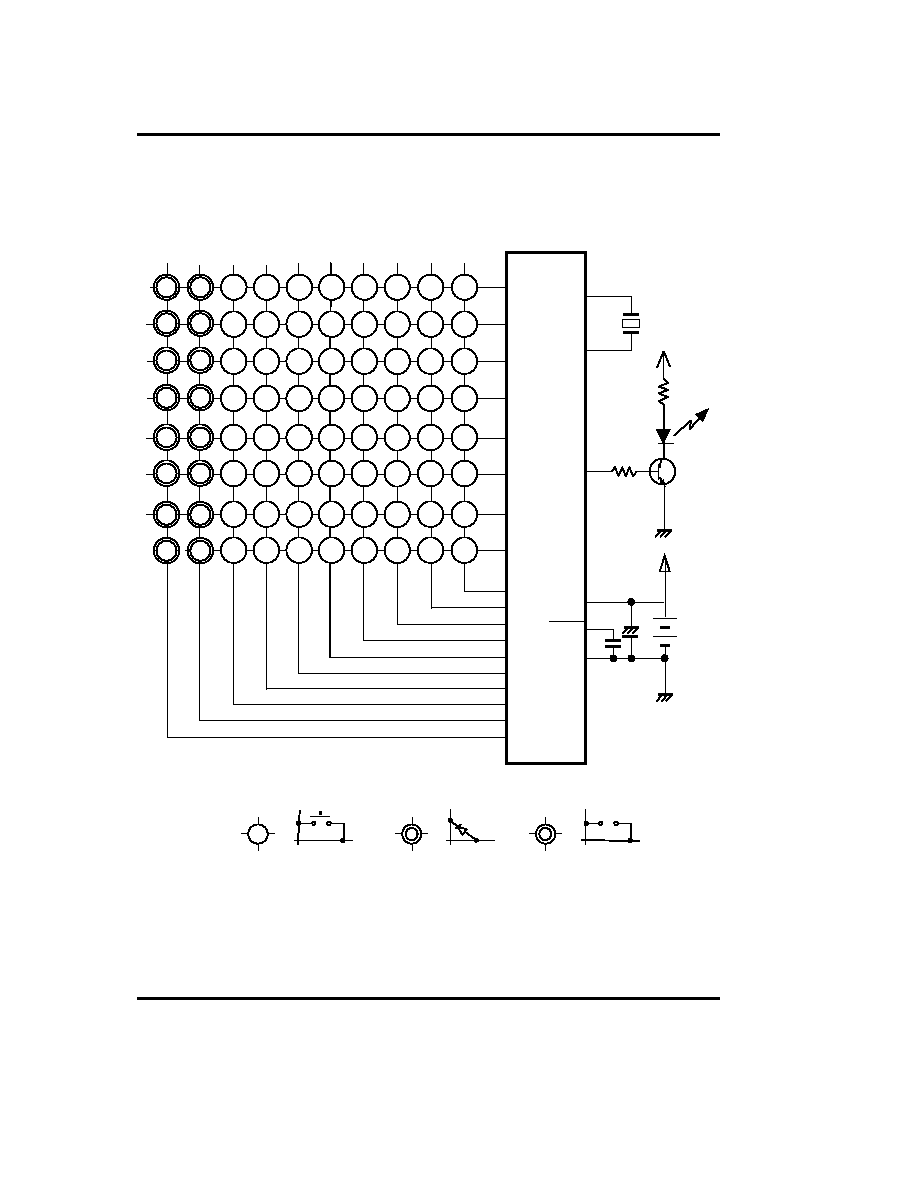

1 - 11

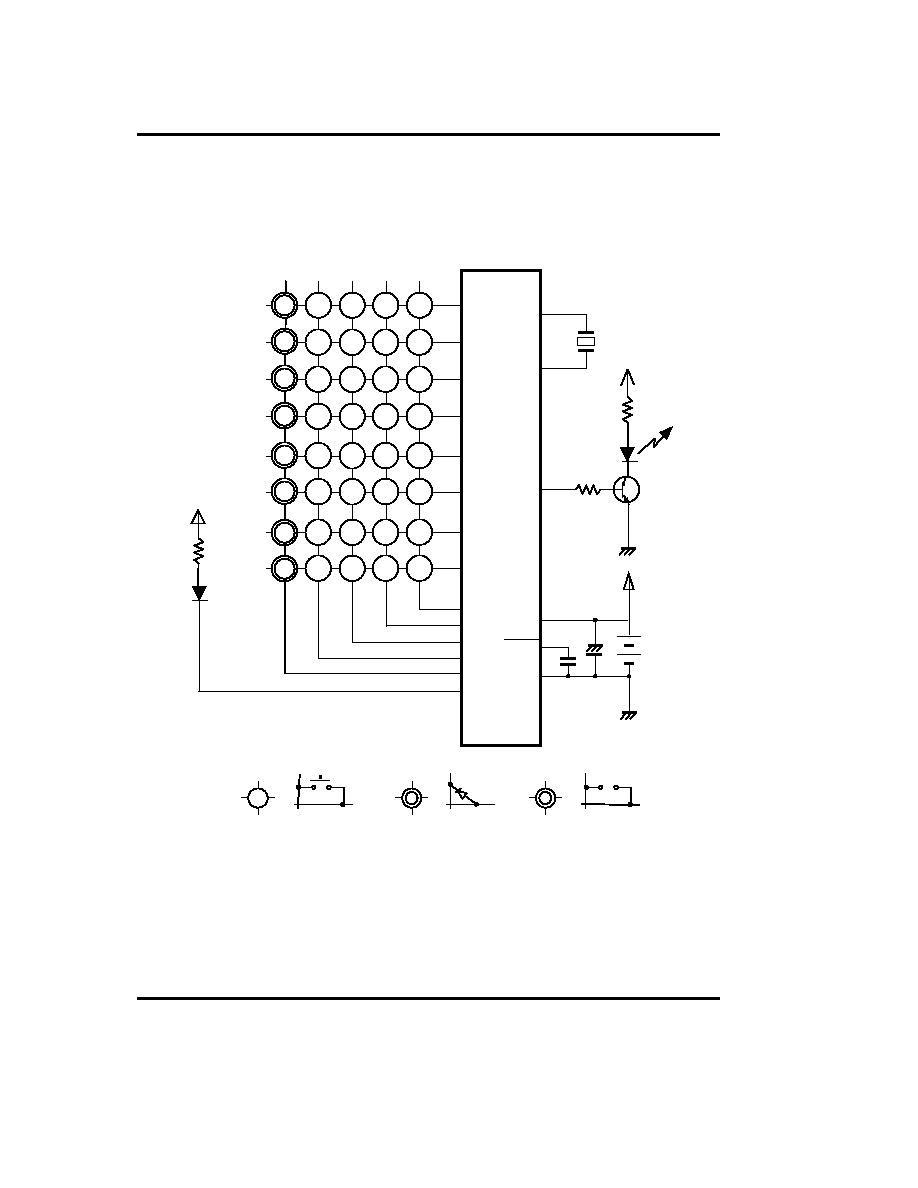

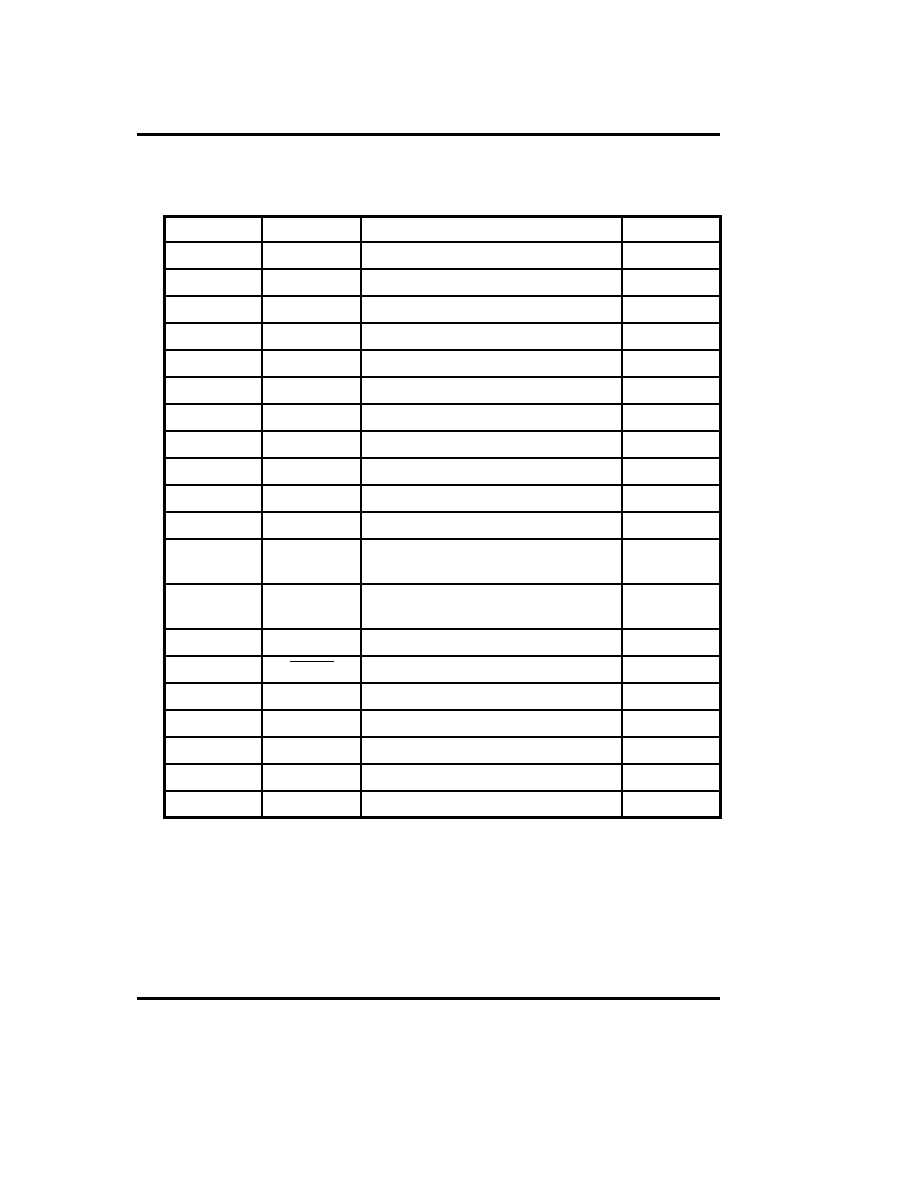

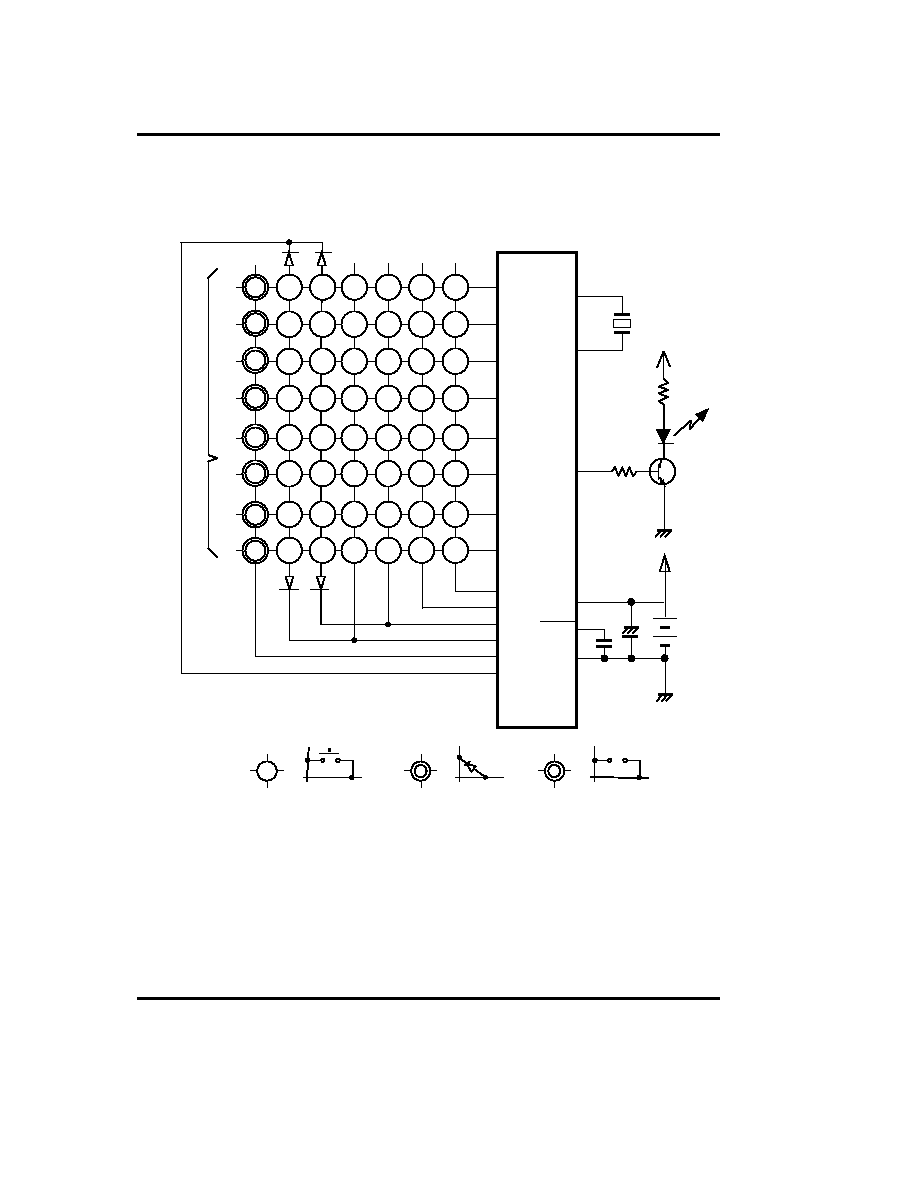

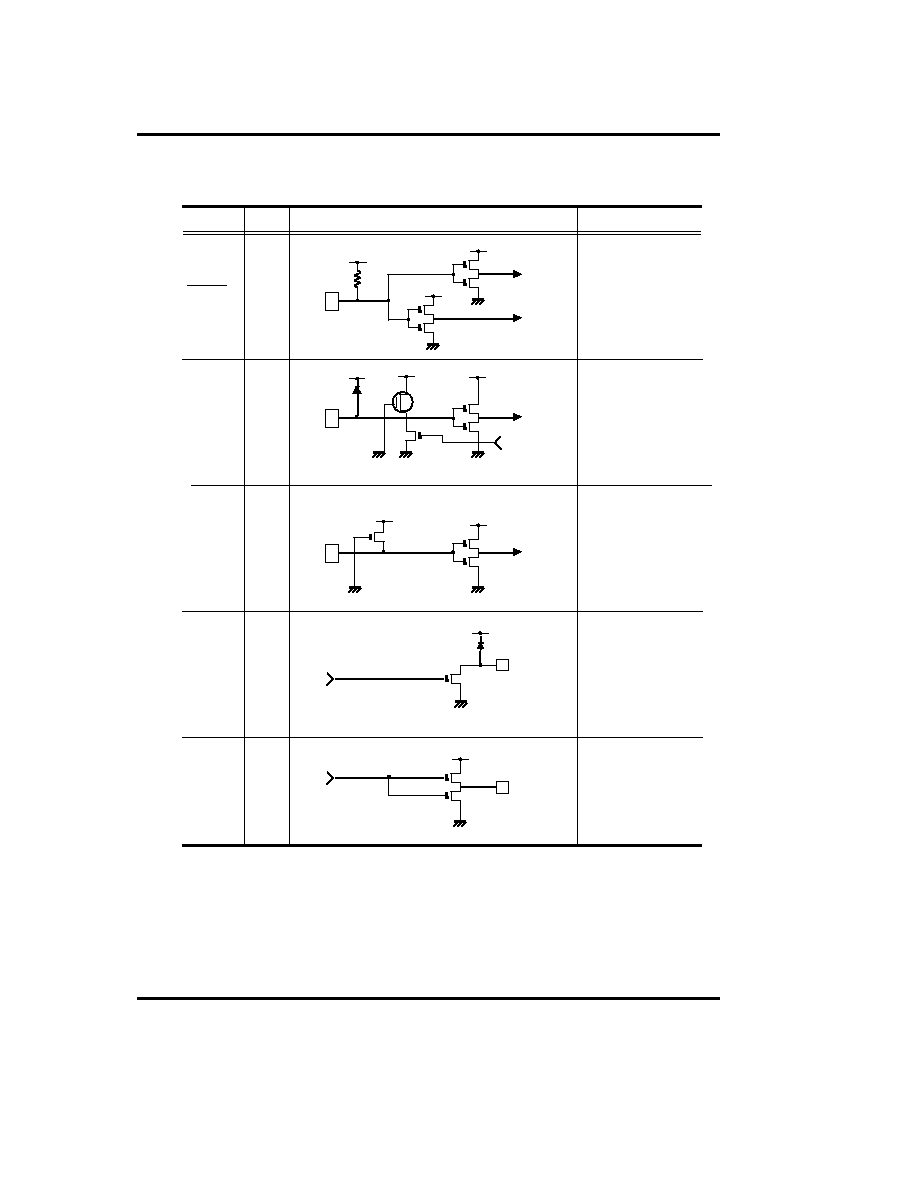

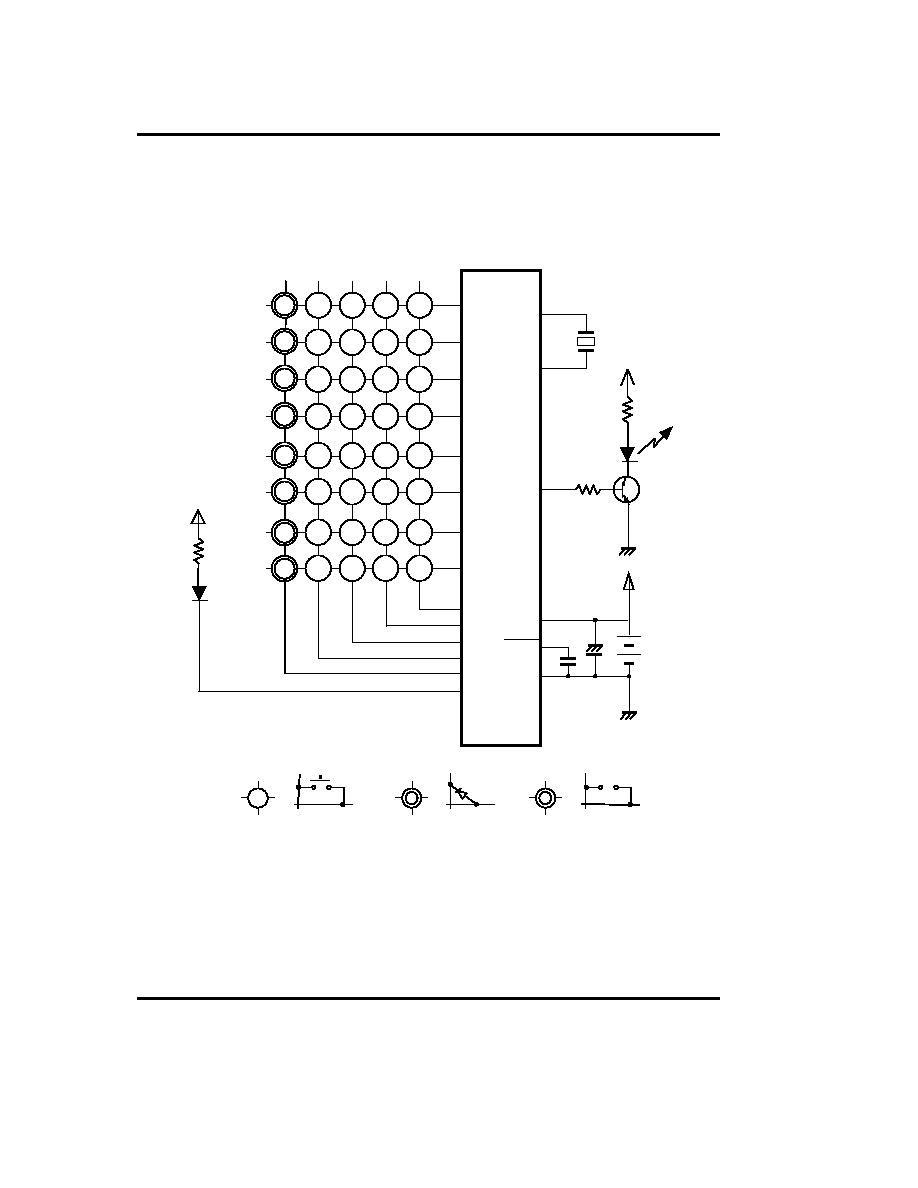

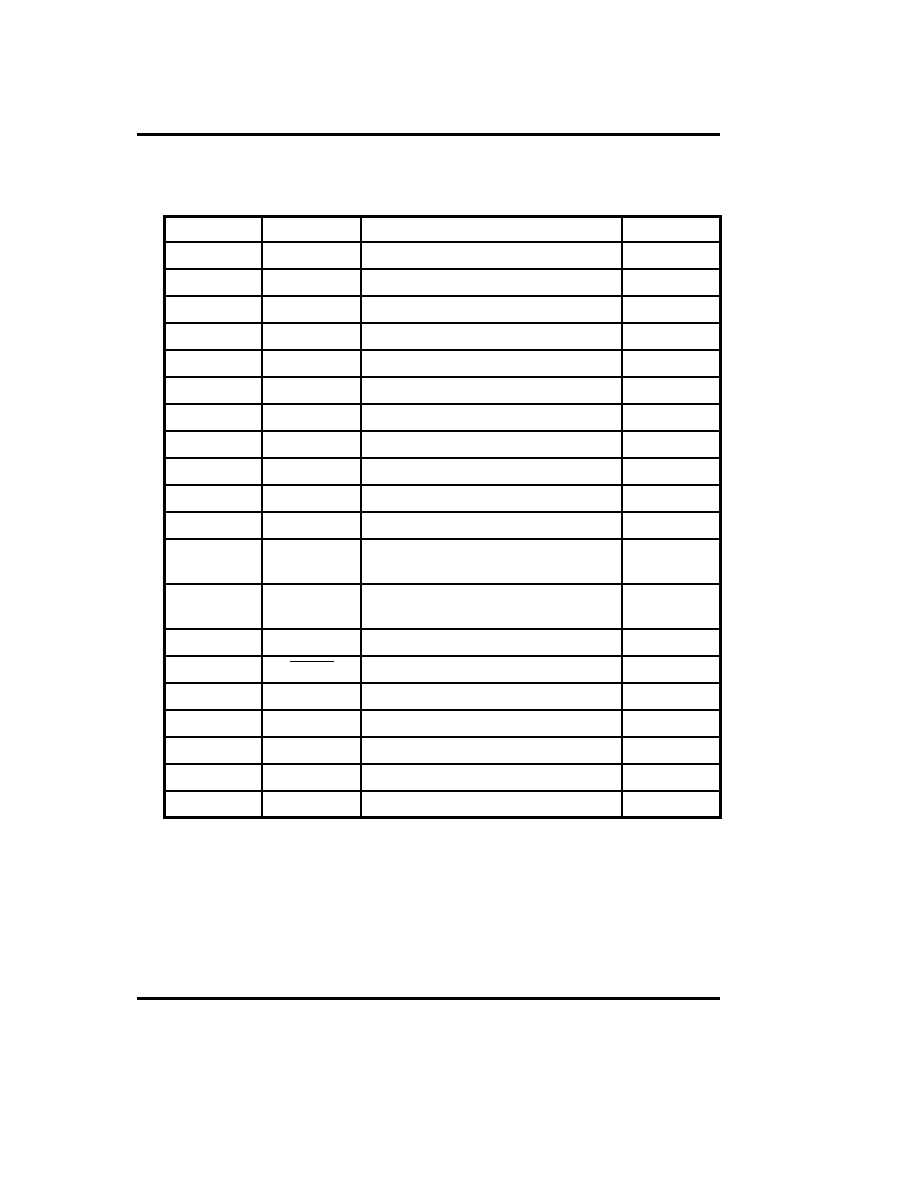

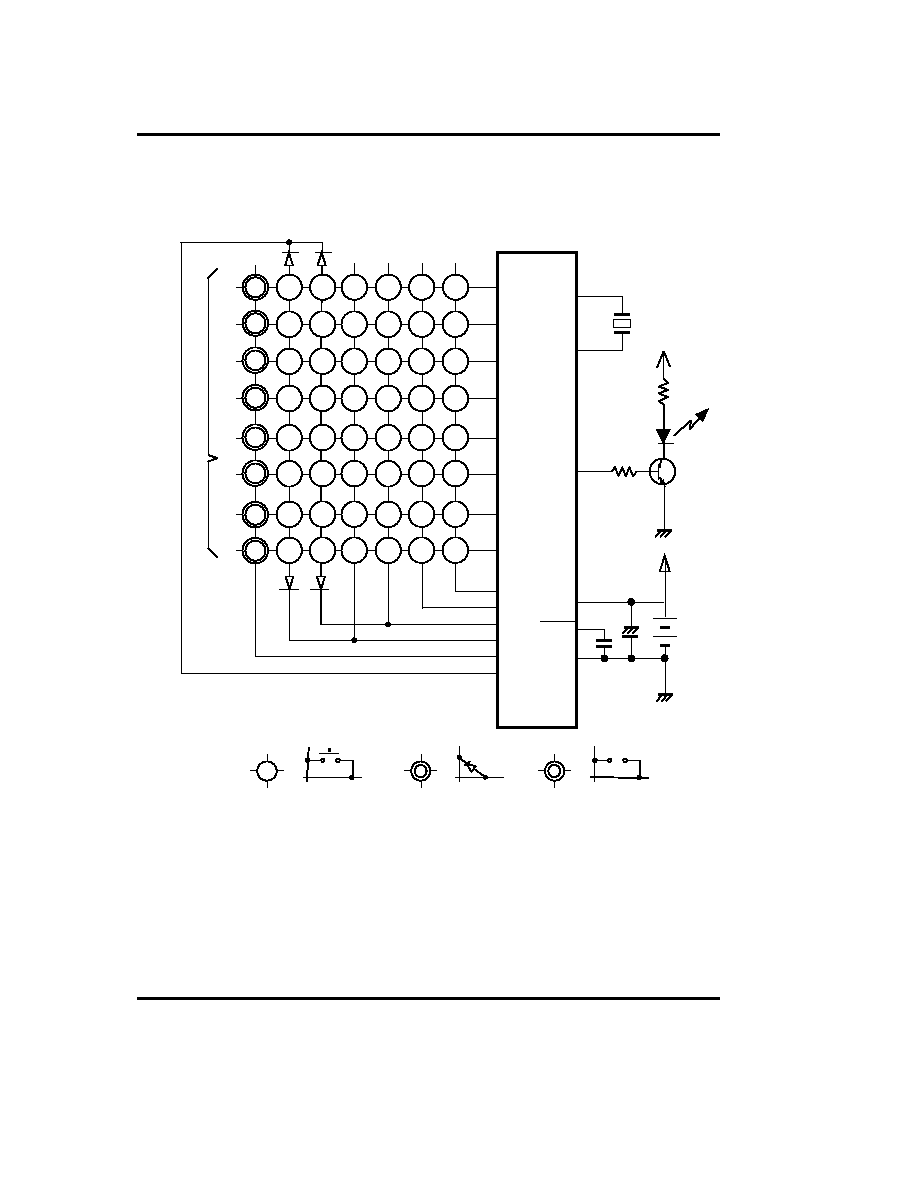

I/O circuit types and options

Hysteresis Input Type

Built in pull-up-

resistor About 400

Ï

RESET

I

Pin

I/O

Note

â

â

à

à

â

â

à

à

Open drain output

Ì

H

Ì

output at reset

(Option)

Built in MOS Tr for

pull-up About 120

Ï

R0~R3

I/O

â

â

à

à

â

â

Built in MOS Tr for

pull-up About 120

Ï

K0~K3

I

Open drain output

Ì

L

Ì

output at reset

D0~D9

O

à

à

â

â

à

à

CMOS output

Ì

L

Ì

output at reset

High current source

output

REMOUT

O

I/O circuit

Chapter 1. Introduction

â

â

â

â

à

à

à

à

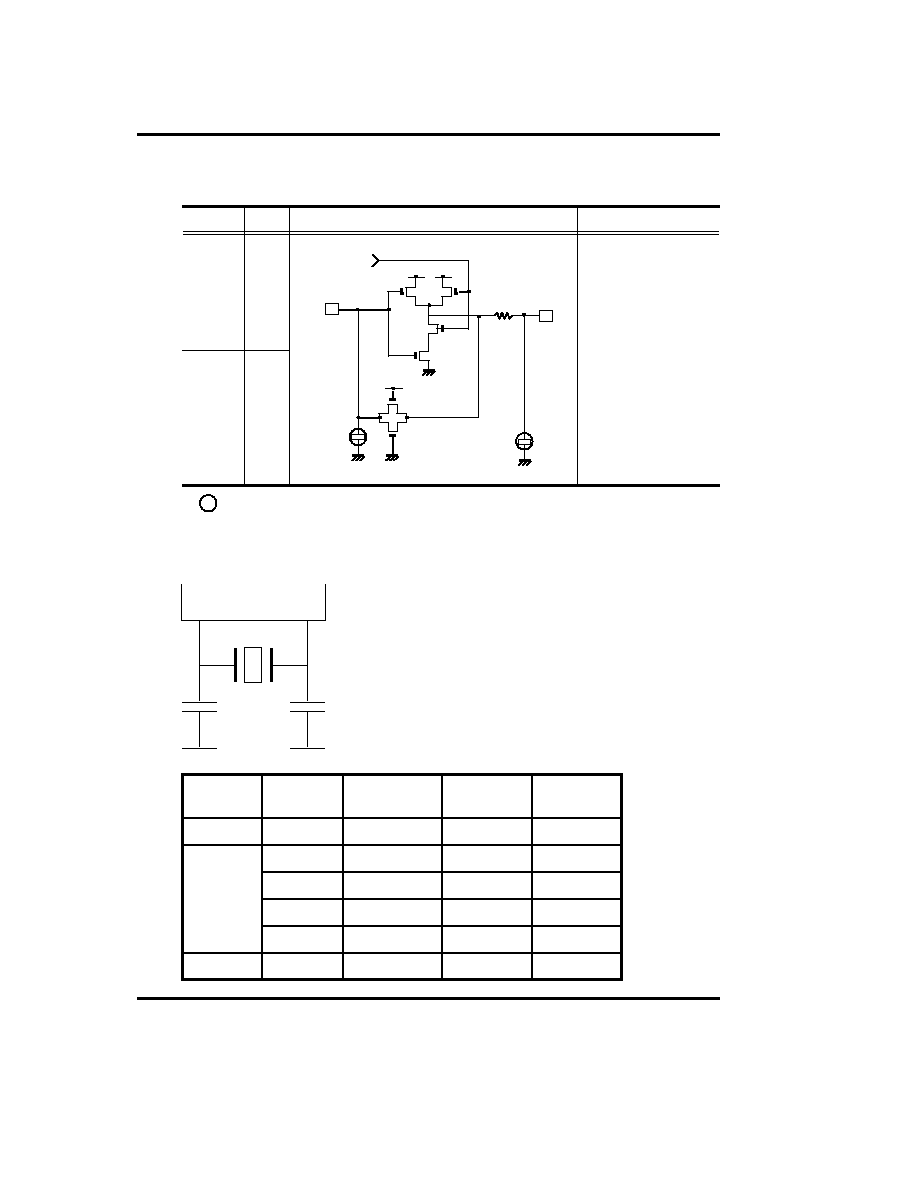

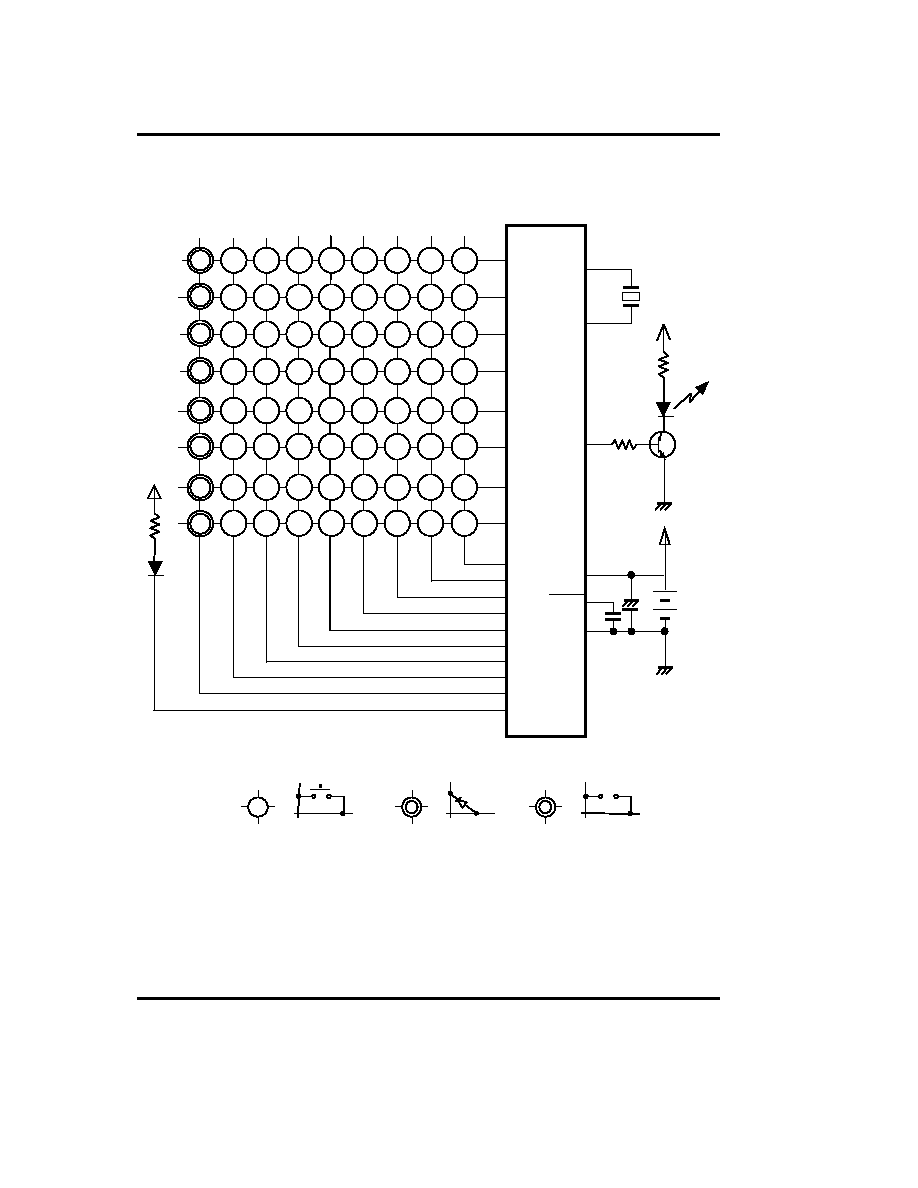

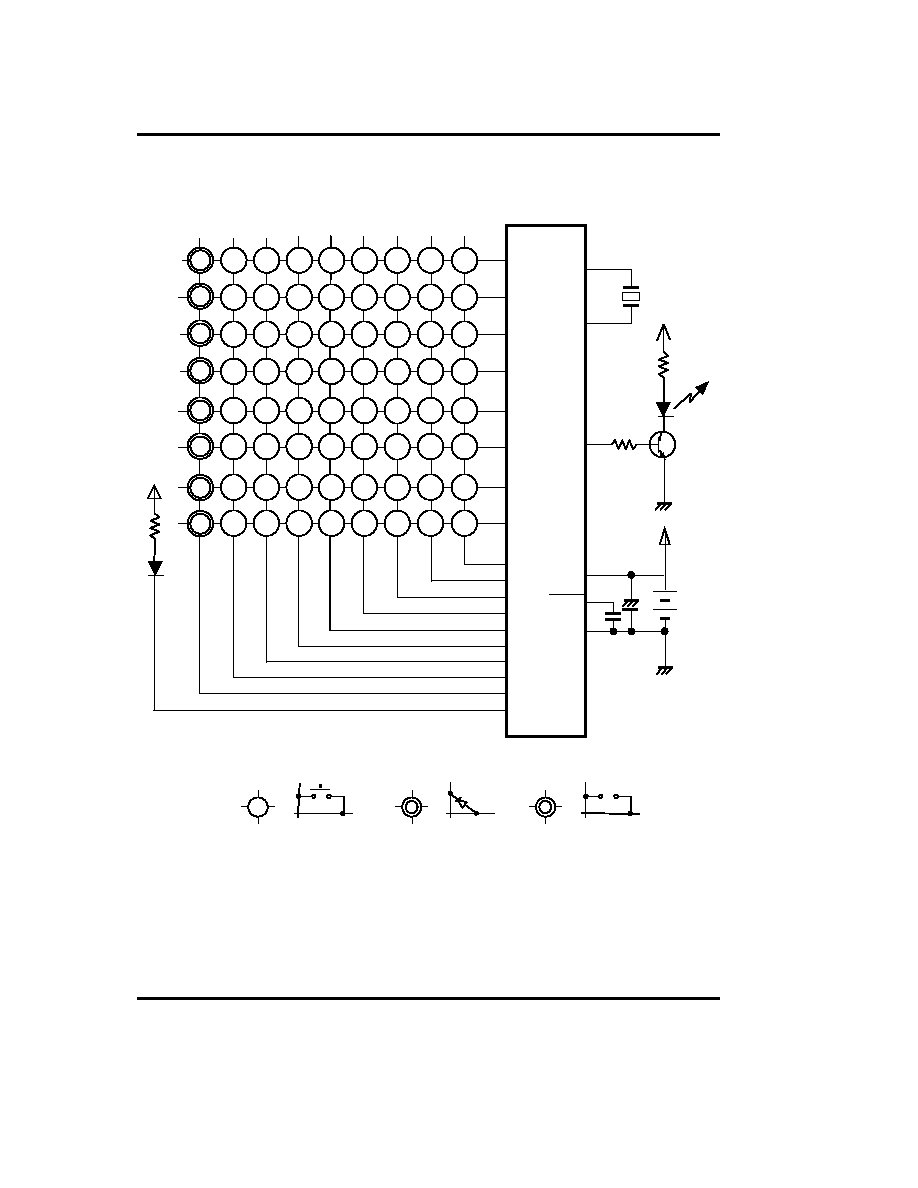

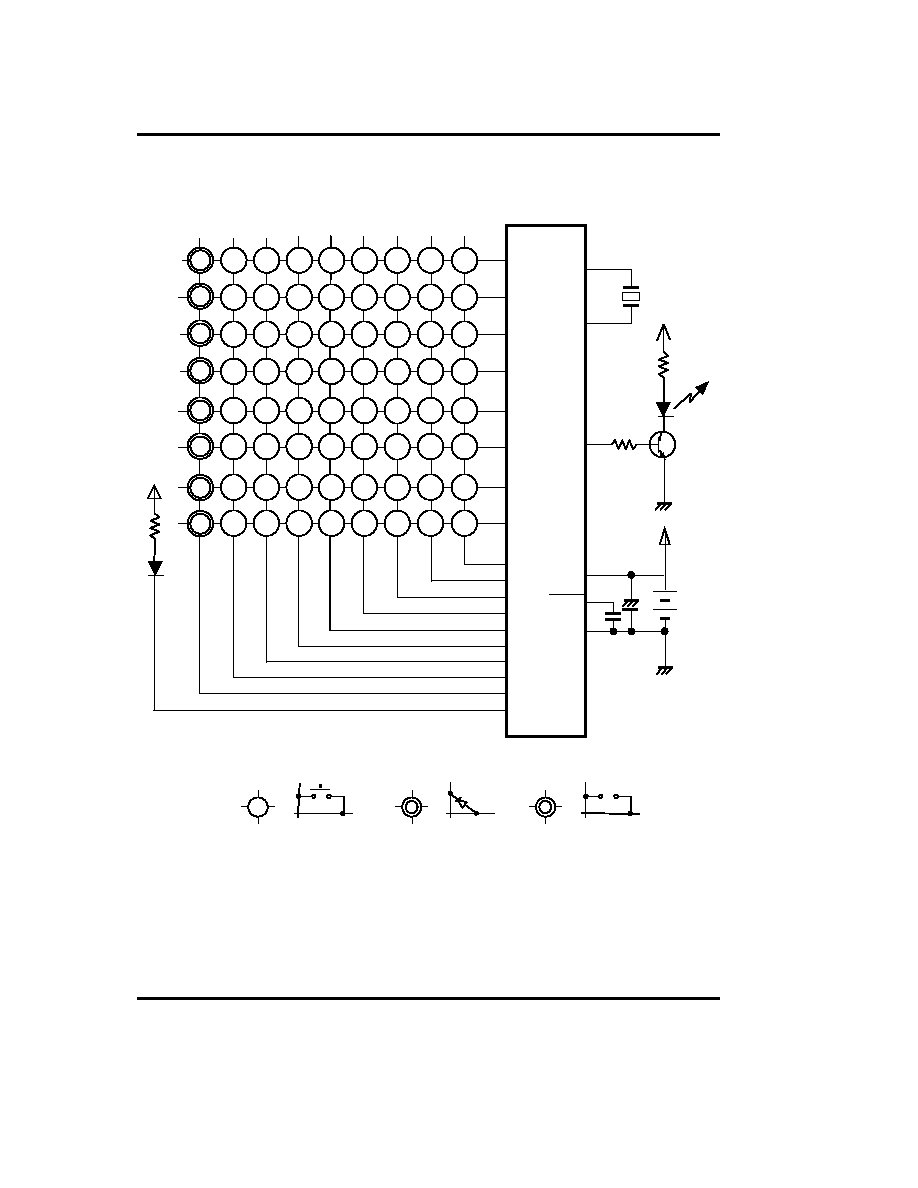

1 - 12

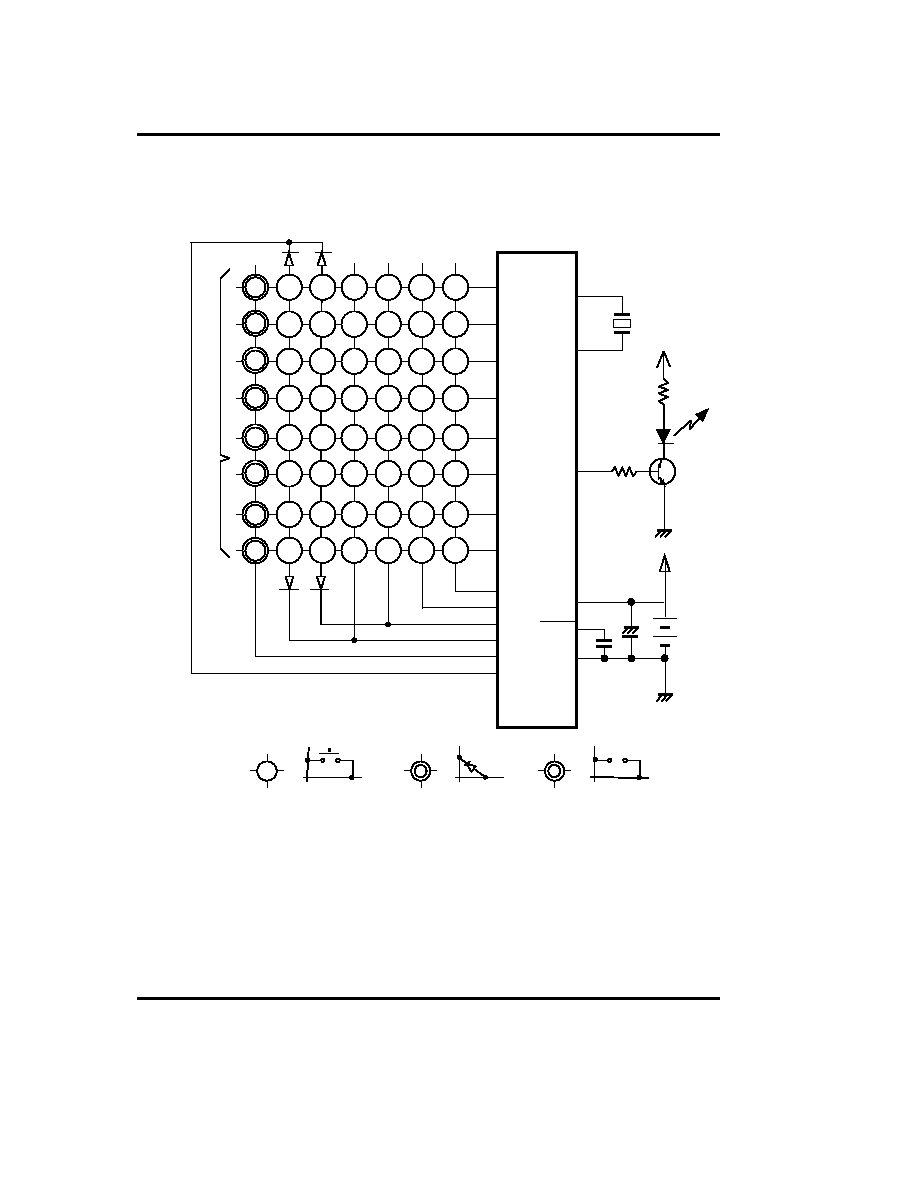

Built in feedback-Resister

About 1

Ð

OSC2

O

Pin

I/O

Note

(Option)

Built in resonance

Capacitor

C1/C2 = 100pF

²

n%

or C1/C2 = 10 ~

100pF

OSC1

I

I/O circuit

â

â

à

à

â

â

à

à

á

á

á

á

OSC2

Rd

C2

Rf

C1

OSC1

OSCSTB

Built in dumping-Resister

Rd : About 6

Ï

: Masked option

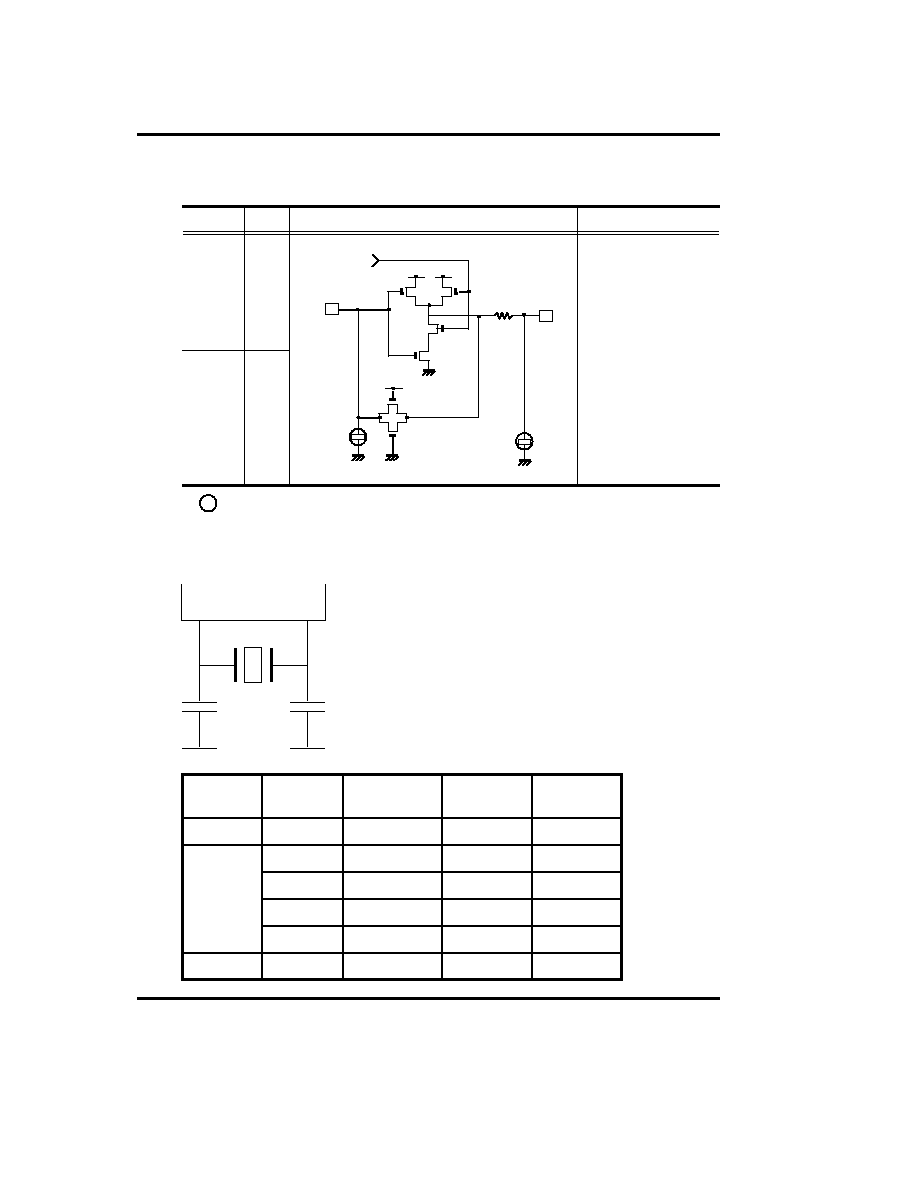

*. Recommendable circuit

OSC1

OSC2

C1

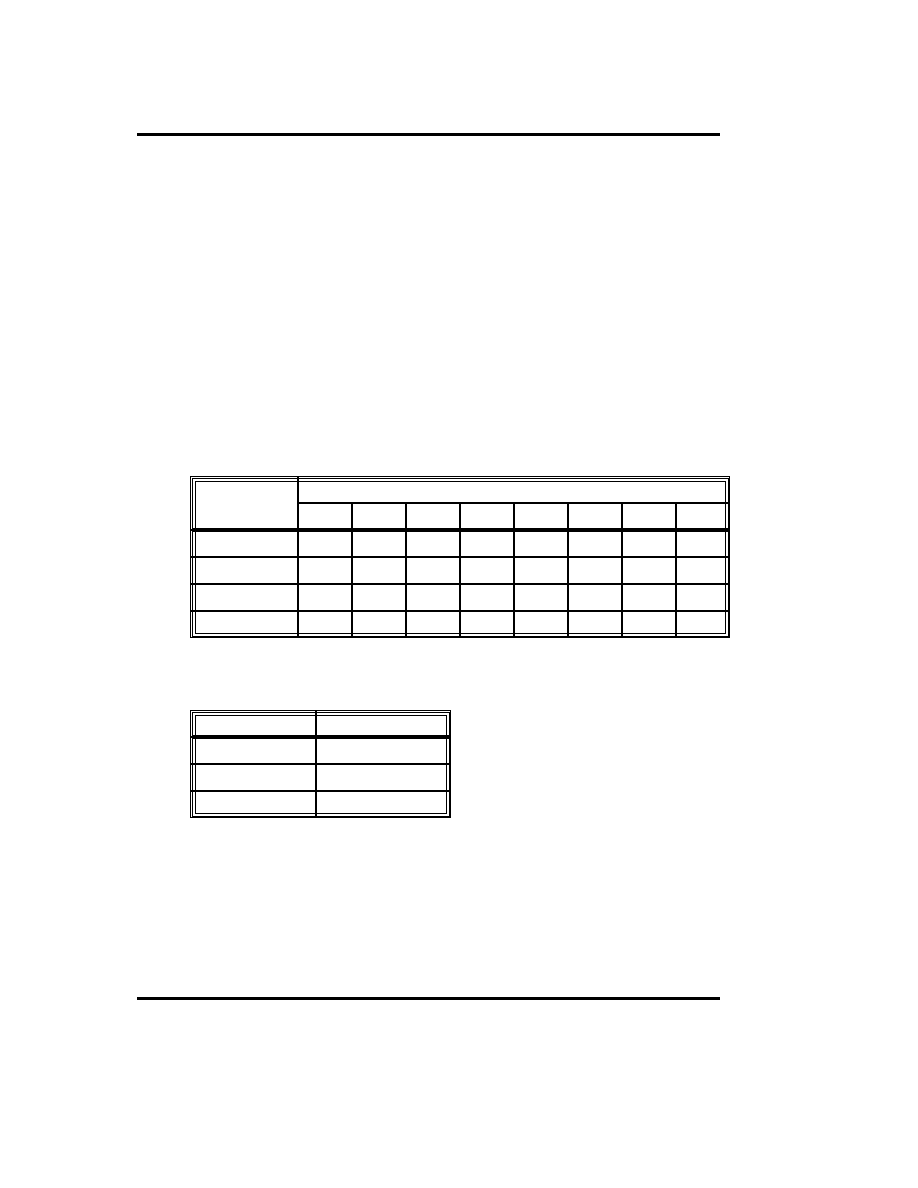

C2

Frequency

(KHz)

Resonator

Maker

Part Name

Load

Capacitor

Operating

Voltage

320

Murata

CSB320D

C1=C2=220pF

2.0 ~ 4.0V

455

Murata

CSB455E35

C1=C2=Open

2.0 ~ 4.0V

Kyocera

KBR-455BKTL70

C1=C2=Open

2.0 ~ 4.0V

Chapter 1. Introduction

Chequers

ZTB-455ET4C

C1=C2=Open

2.0 ~ 4.0V

TDK

FCR455K3

C1=C2=Open

2.0 ~ 4.0V

Murata

CSB480E35

C1=C2=Open

2.0 ~ 4.0V

480

1 - 13

Masked options

The GMS300 series offer the following optional features.

These options are masked.

1. Watch dog timer reset by REMOUT output signal.

2. Input terminals having STOP release mode : K0~K3, R0~R3.

3. I/O terminals having pull-up resistor : R0~R3

4. Ceramic oscillation circuit contained (or not contained).

5. Output form at stop mode

D0~D7 :

Ì

L

Ì

or keep before stop mode

STOP Function

Stop mode can be achieved by STOP instructions.

In stop mode :

1. Oscillator is stopped, the operating current is low.

2. Watch dog timer is reset, D8~D9 output and REMOUT output are

Ì

L

Ì

.

3. Part other than WDT, D8~D9 output and REMOUT output have a value before

come into stop mode.

Ì

But, the state of D0~D7 output in stop mode is able to choose as masked

option.

Ì

L

Ì

output or same level before come into stop mode.

The function to release stop mode is able to choose each bit of K or R input.

Stop mode is released when one of K or R input is going to

Ì

L

Ì

.

1. State of D0~D7 output and REMOUT output is return to state of before stop mode

is achieved.

2. After 1024

Ø

8 enable clocks for stable oscillating. First instruction start to operate.

3. In return to normal operation, WDT is counted from zero again.

But, at executing stop instruction, if one of K or R input is chosen to

Ì

L

Ì

, stop

instruction is same to NOP instruction.

Chapter 1. Introduction

INTRODUCTION

1

ARCHITECTURE

2

INSTRUCTION

3

EVALUATION BOARD

4

SOFTWARE

5

APPENDIX

6

2 - 1

CHAPTER 2. Architecture

BLOCK DESCRIPTION

Characteristics

The GMS300 series can incorporate maximum 1024 words (64 words

Ø

16

pages

Ø

8bits) for program memory. Program counter PC (A

0

~A

5

) and page

address register (A

6

~A

9

) are used to address the whole area of program memory

having an instruction (8bits) to be next executed.

The program memory consists of 64 words on each page, and thus each page

can hold up to 64 steps of instructions.

The program memory is composed as shown below.

0 1

2 3

4 5

6 7

8

63

Program counter (PC)

Page address register (PA)

Page buffer (PB)

6

4

(Level

Ì

1

Ì

)

(Level

Ì

2

Ì

)

(Level

Ì

3

Ì

)

(PRS)

(SR)

Stack register

Page 0

Page 1

Page 2

Page 15

A0~A5

0

1

2

15

A6~A9

Program capacity (pages)

Fig 2-1 Configuration of Program Memory

Chapter 2. Architecture

2 - 2

ROM Address Register

The following registers are used to address the ROM.

· Page address register (PA) :

Holds ROM`s page number (0~Fh) to be addressed.

· Page buffer register (PB) :

Value of PB is loaded by an LPBI command when newly addressing a page.

Then it is shifted into the PA when rightly executing a branch instruction (BR)

and a subroutine call (CAL).

· Program counter (PC) :

Available for addressing word on each page.

· Stack register (SR) :

Stores returned-word address in the subroutine call mode.

(1) Page address register and page buffer register :

Address one of pages #0 to #15 in the ROM by the 4-bit binary counter.

Unlike the program counter, the page address register is usually unchanged

so that the program will repeat on the same page unless a page changing

command is issued. To change the page address, take two steps such as

(1) writing in the page buffer what page to jump to (execution of LPBI) and

(2) execution of BR or CAL, because and instruction code is of eight bits so

that page and word cannot be specified at the same time.

In case a return instruction (RTN) is executed within the subroutine that has

been called in the other page, the page address will be changed at the same

time.

(2) Program counter :

This 6-bit binary counter increments for each fetch to address a word in the

currently addressed page having an instruction to be next executed.

For easier programming, at turning on the power, the program counter is

reset to the zero location. The PA is also set to

Ì

0

Ì

. Then the program

counter specifies the next ROM address in random sequence.

When BR, CAL or RTN instructions are decoded, the switches on each step

are turned off not to update the address. Then, for BR or CAL, address data

are taken in from the instruction operands (a

0

to a

5

), or for RTN, and

address is fetched from stack register No. 1.

(3) Stack register :

This stack register provides two stages each for the program counter (6 bits)

and the page address register (4bits) so that subroutine nesting can be

mode on two levels.

Chapter 2. Architecture

2 - 3

Data memory (RAM)

Up to 32 nibbles (16 words

Ø

2pages

Ø

4bits) is incorporated for storing data.

The whole data memory area is indirectly specified by a data pointer (X,Y). Page

number is specified by zero bit of X register, and words in the page by 4 bits in

Y-register. Data memory is composed in 16 nibbles/page. Figure 2.2 shows the

configuration.

0

1

2

3

15

Output port

Y-register (Y)

X-register (X)

D0

D9 R0

R3 REMOUT

Page 0

Page 1

0

1

4

A0~A3

Data memory page (0~1)

X-register (X)

X-register is consist of 2bit, X0 is a data pointer of page in the RAM, X1 is only

used for selecting of D8~D9 with value of Y-register

Fig 2-2 Composition of Data Memory

Table 2-1 Mapping table between X and Y register

Chapter 2. Architecture

X1=1

X1=0

D8

D9

Y=0

Y=1

D1

D0

4

2

2 - 4

Y-register (Y)

Y-register has 4 bits. It operates as a data pointer or a general-purpose register.

Y-register specifies and address (a

0

~a

3

) in a page of data memory, as well as it

is used to specify an output port. Further it is used to specify a mode of carrier

signal outputted from the REMOUT port. It can also be treated as a general-

purpose register on a program.

Accumulator (A

CC

)

The 4-bit register for holding data and calculation results.

Arithmetic and Logic Unit (ALU)

In this unit, 4bits of adder/comparator are connected in parallel as it`s main

components and they are combined with status latch and status logic (flag.)

(1) Operation circuit (ALU) :

The adder/comparator serves fundamentally for full addition and data

comparison. It executes subtraction by making a complement by processing

an inversed output of A

CC

(A

CC

+1)

(2) Status logic :

This is to bring an ST, or flag to control the flow of a program. It occurs when

a specified instruction is executed in two cases such as overflow in operation

and two inputs unequal.

I/O circuit

Ports K0~K3 are 4-bit input ports were pulled up by MOS Tr resistor internally.

Ports D0~D9 are output ports, each of which can be independently set and

reset. The output is in the form of Nch-open-drain circuit. The input is in the

form of a MOS transistor input (MOS Tr resistor pull-up. Masked option).

Further, the REMOUT port is a large current driven output port. This port is

designed for source current to drive a high current device.

Chapter 2. Architecture

2 - 5

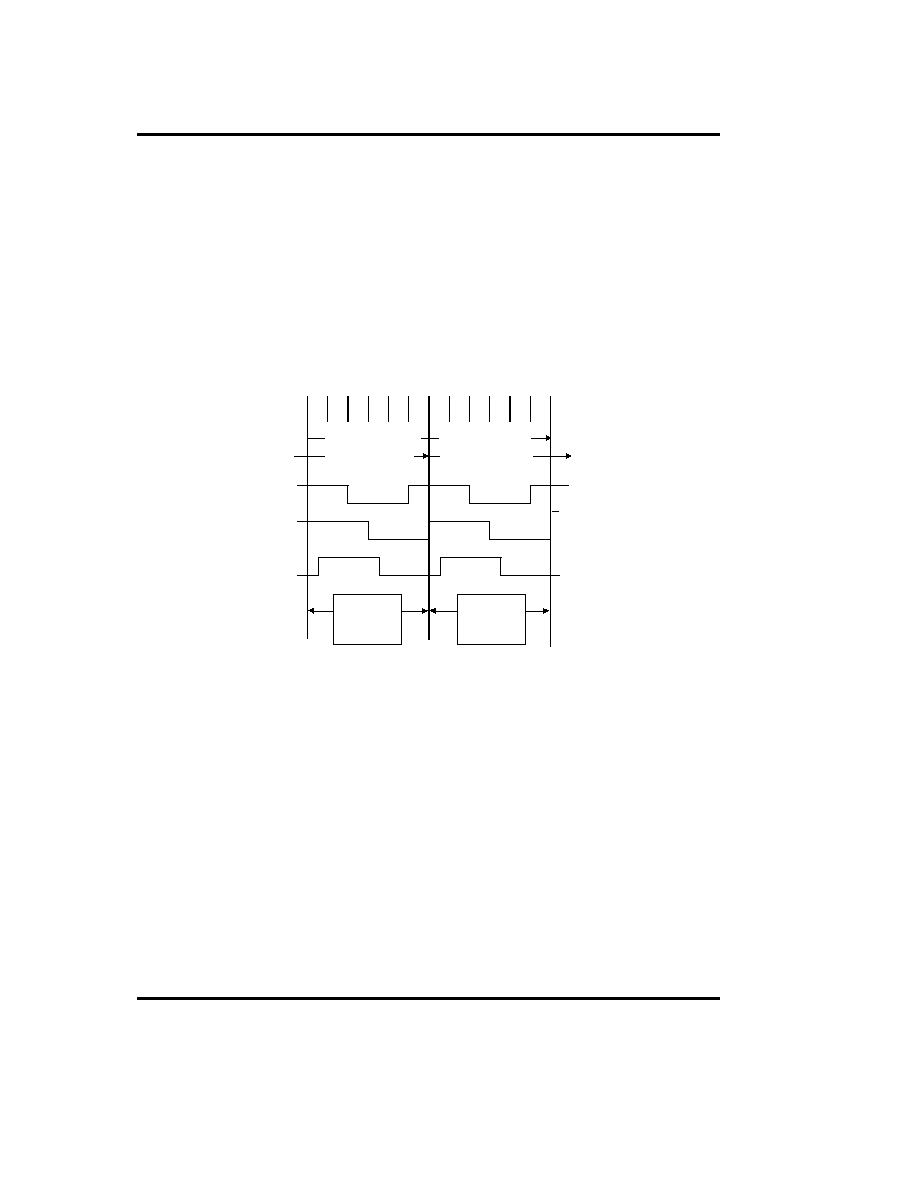

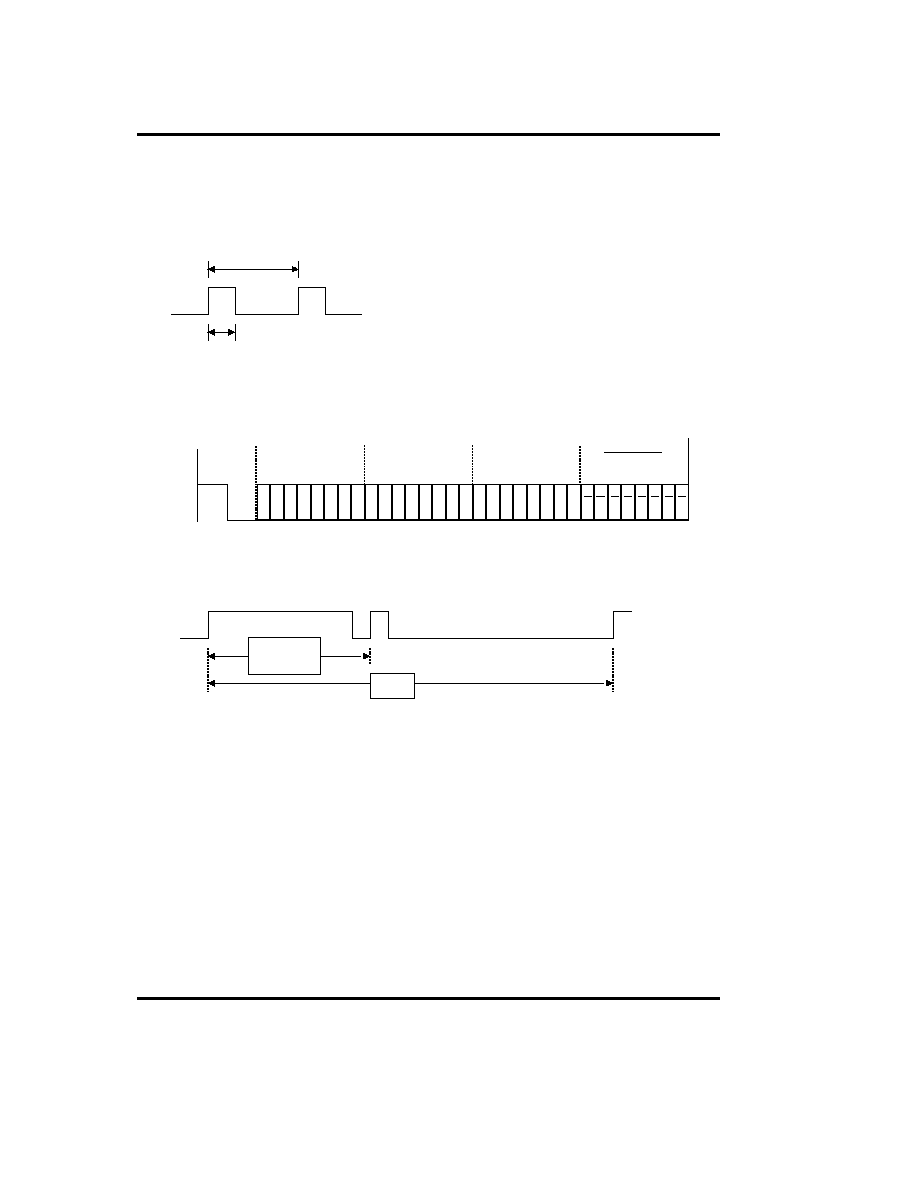

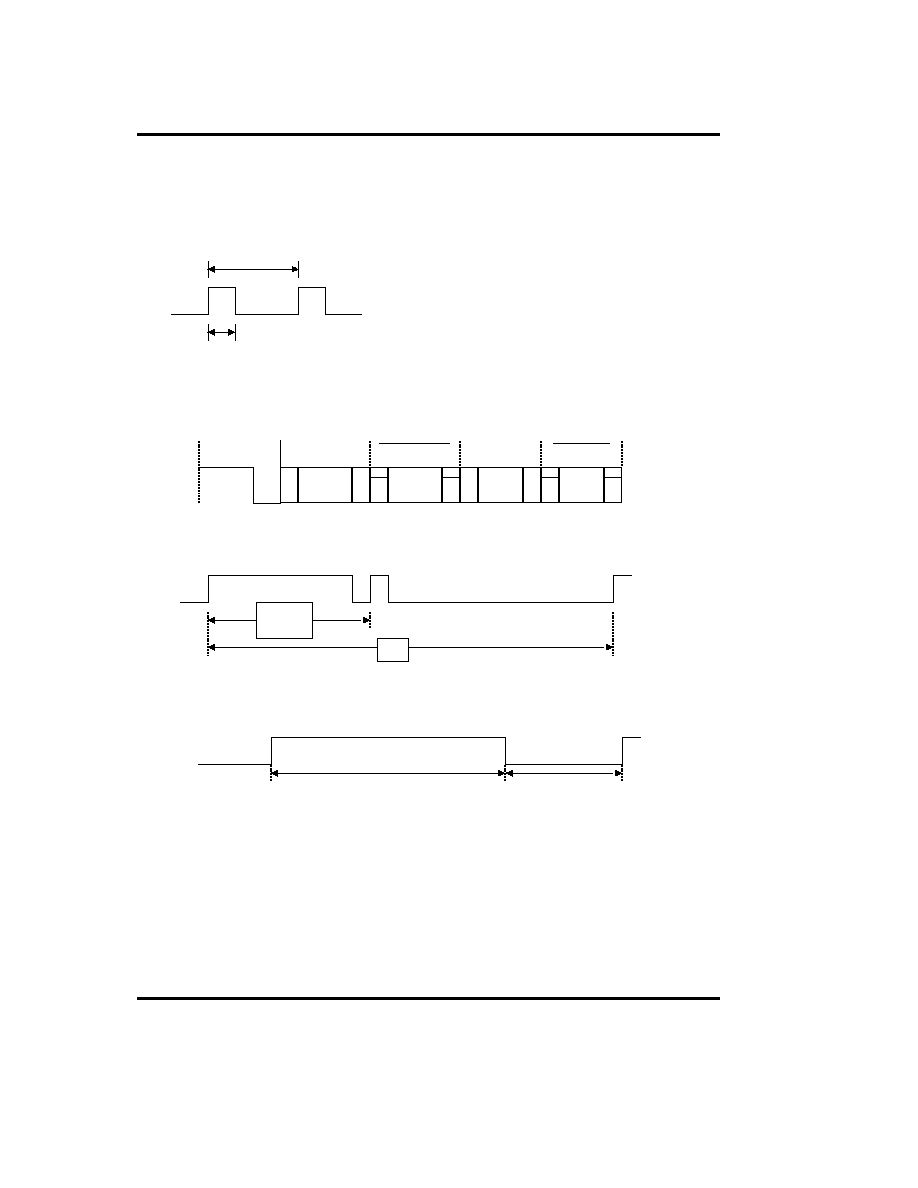

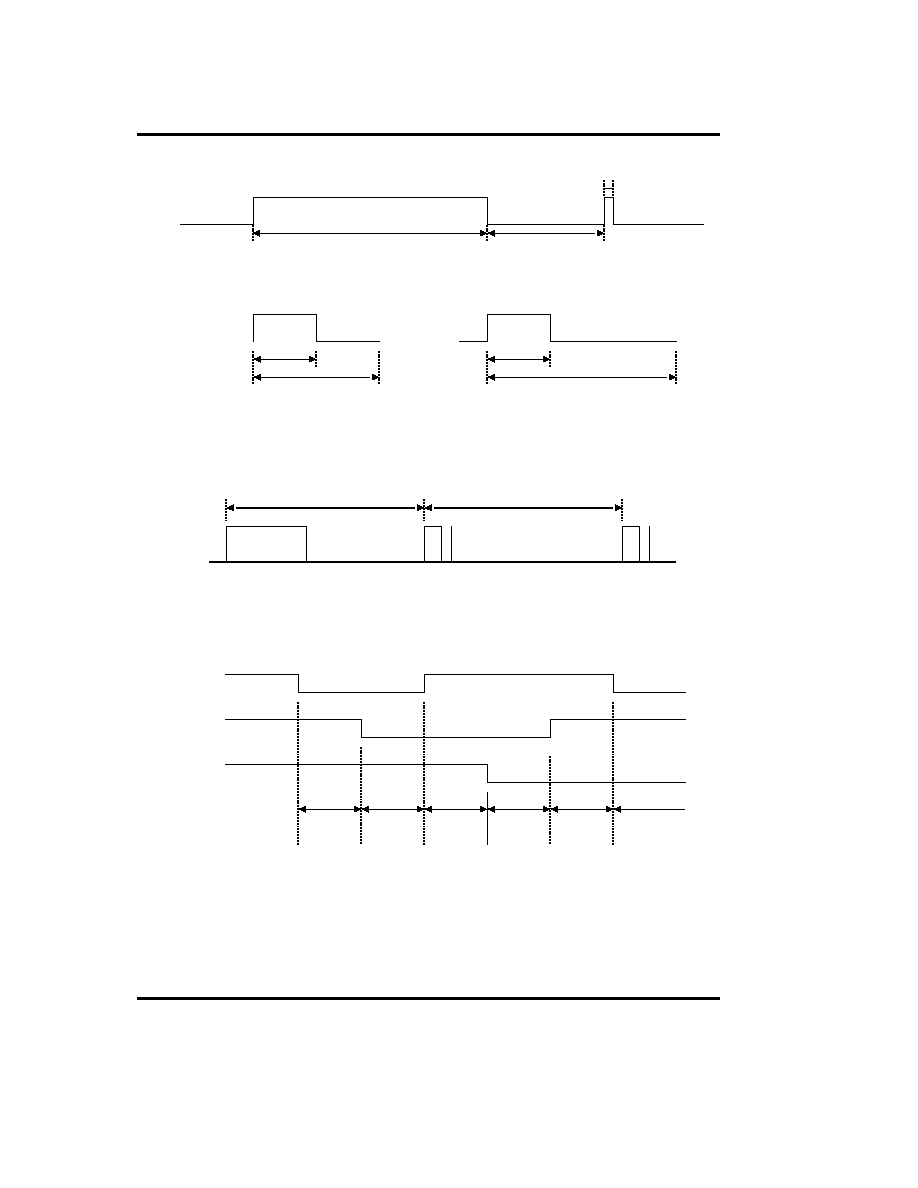

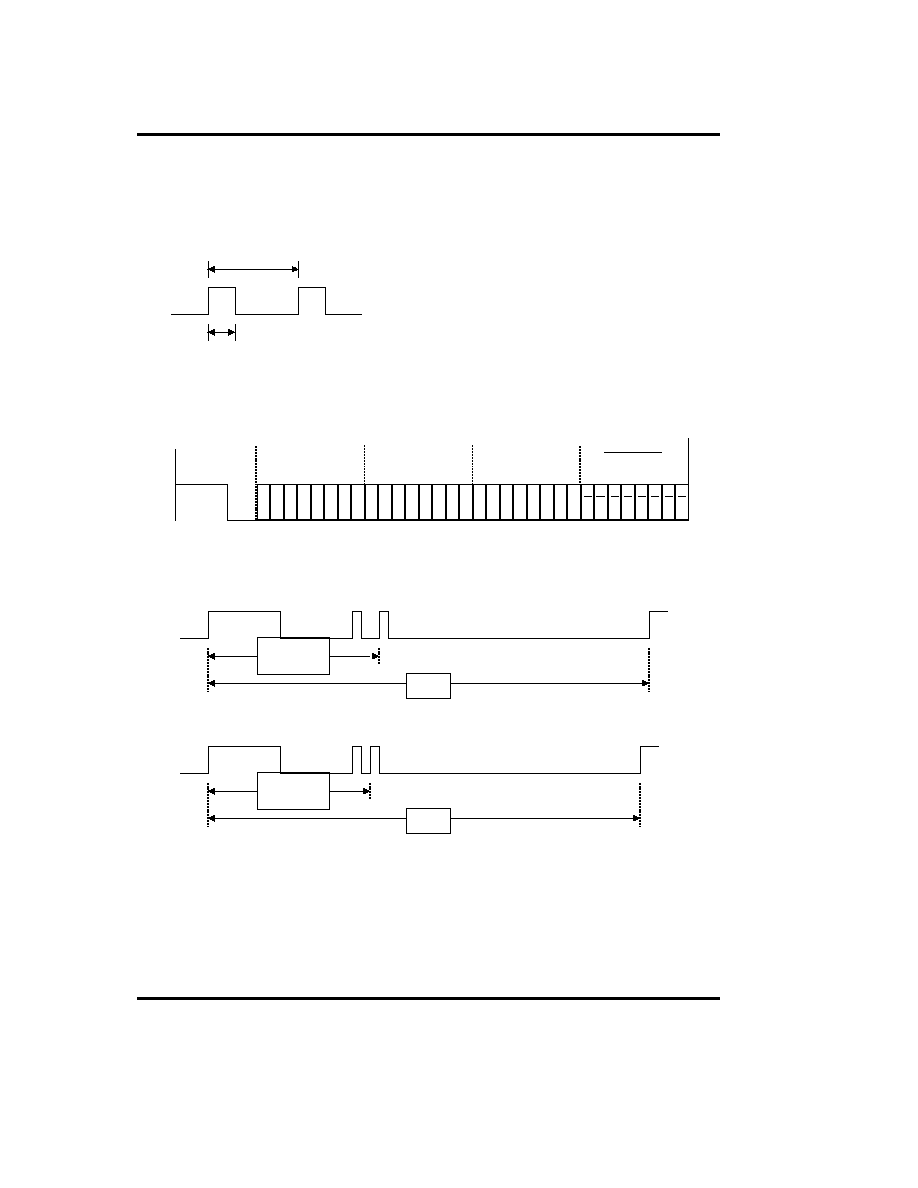

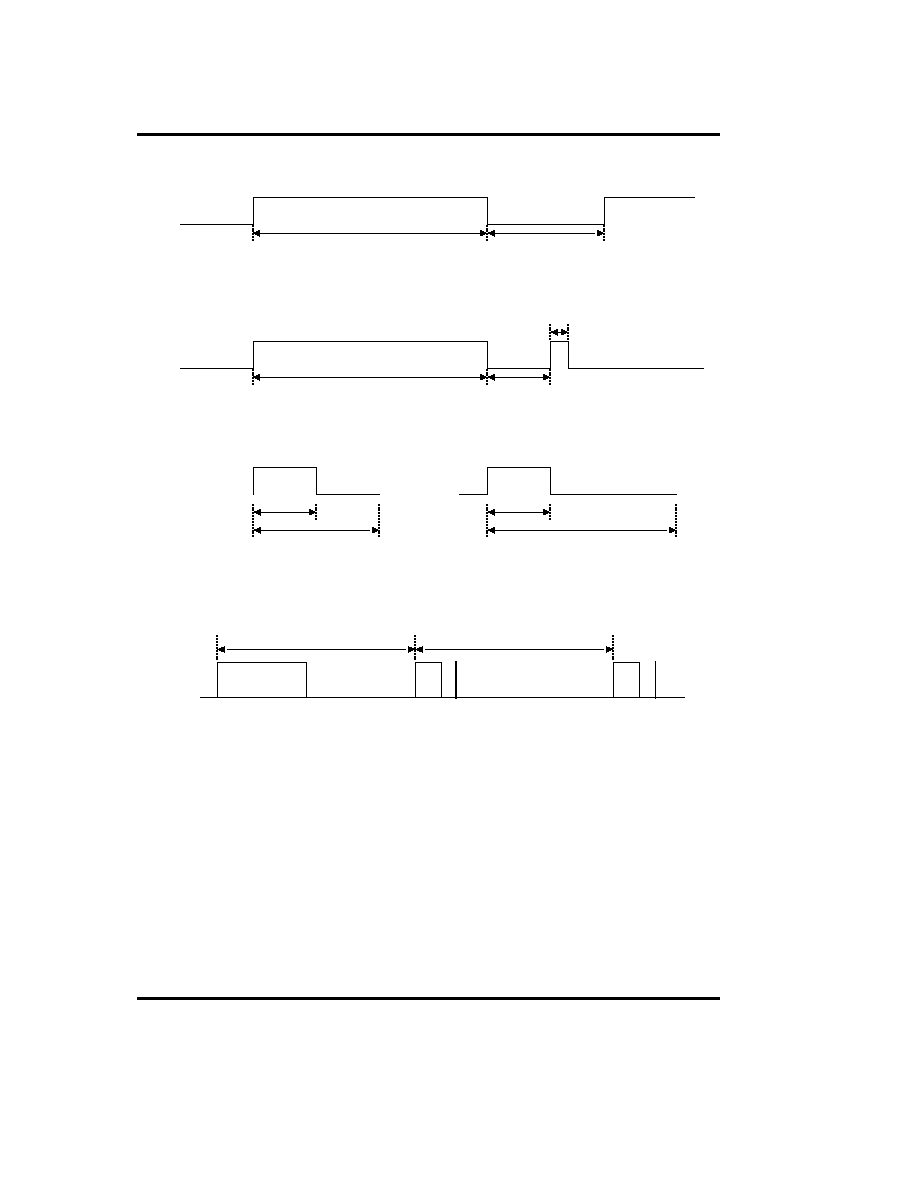

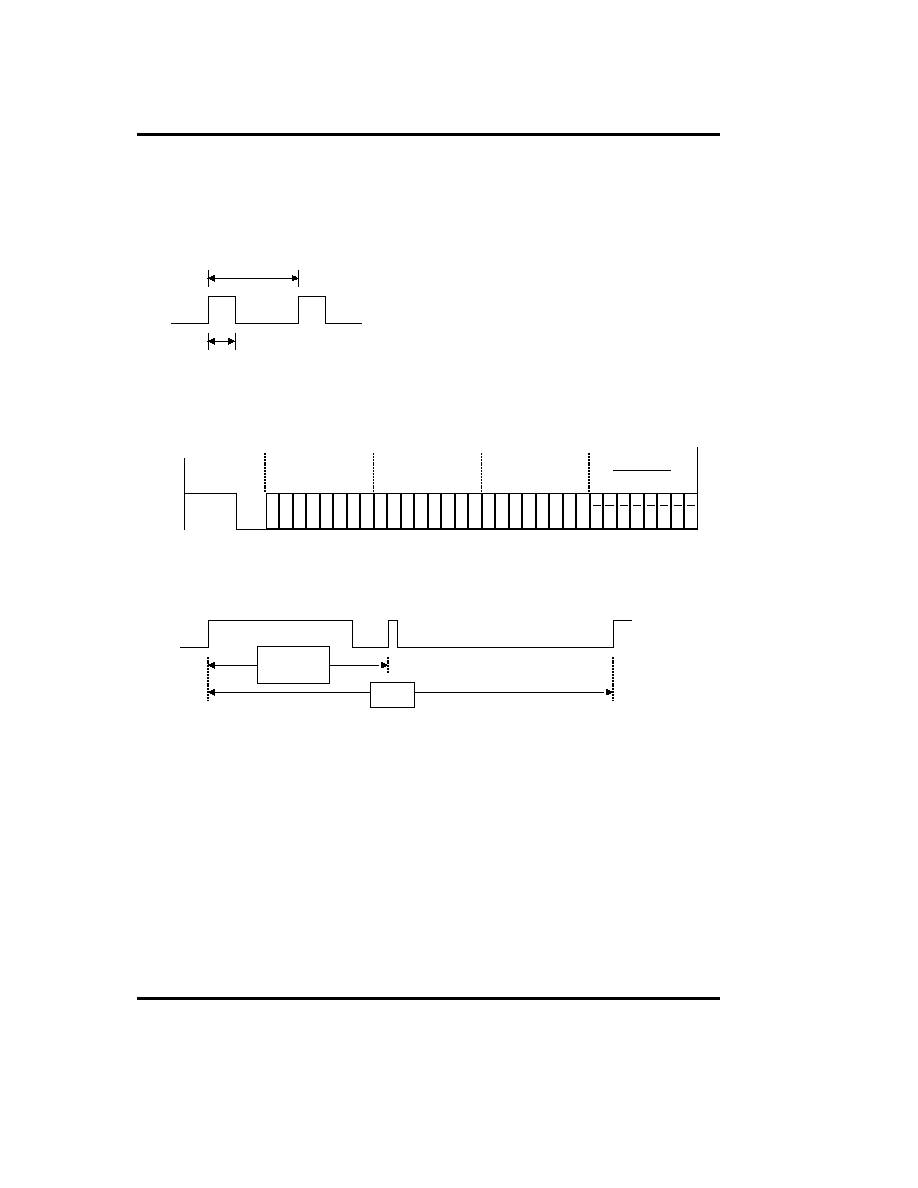

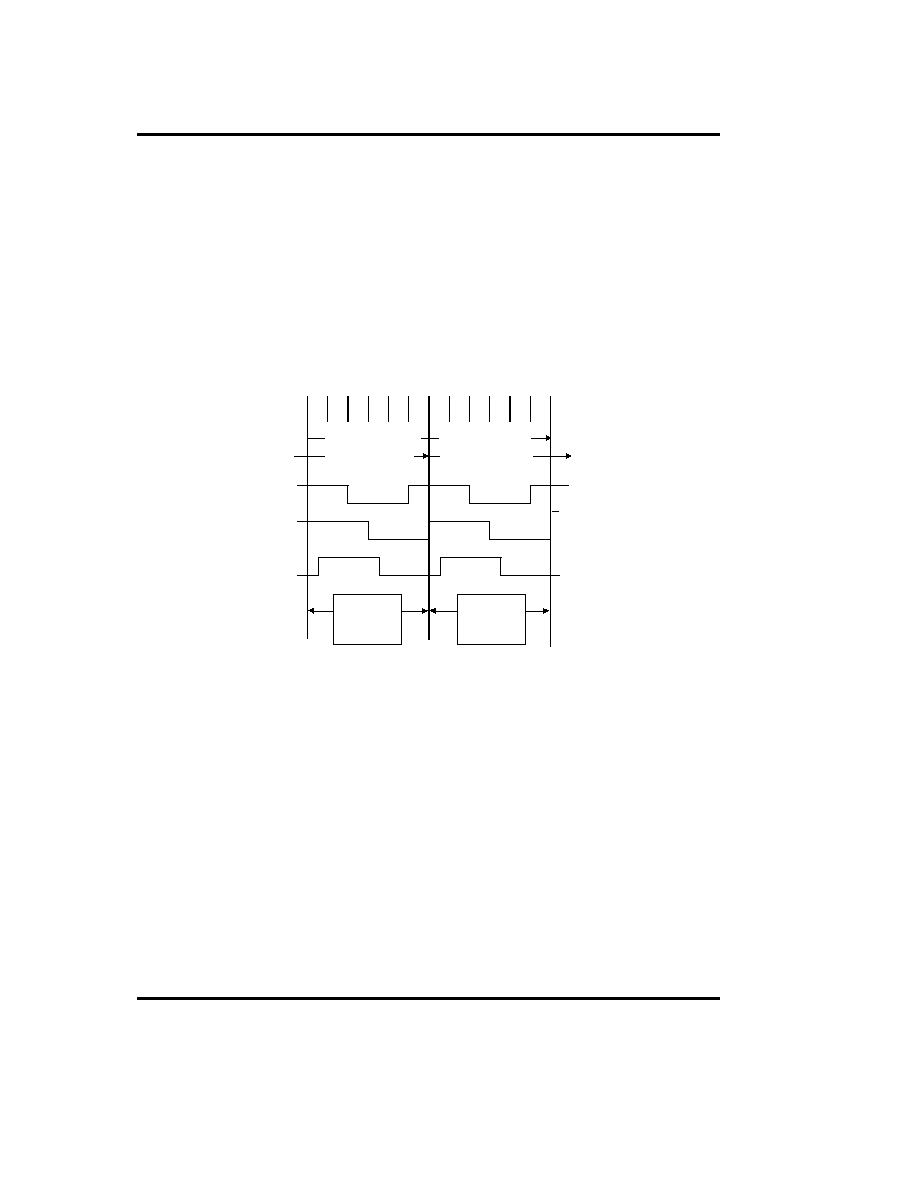

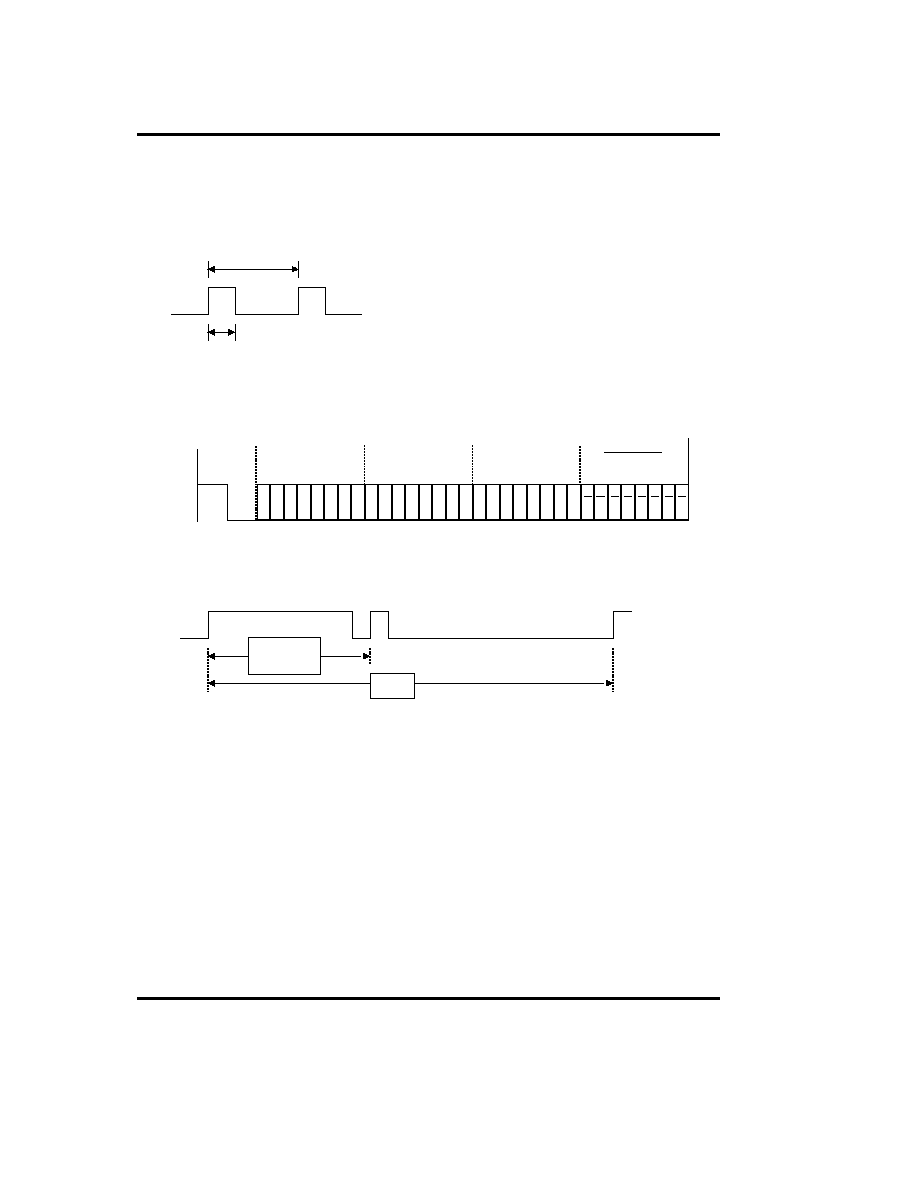

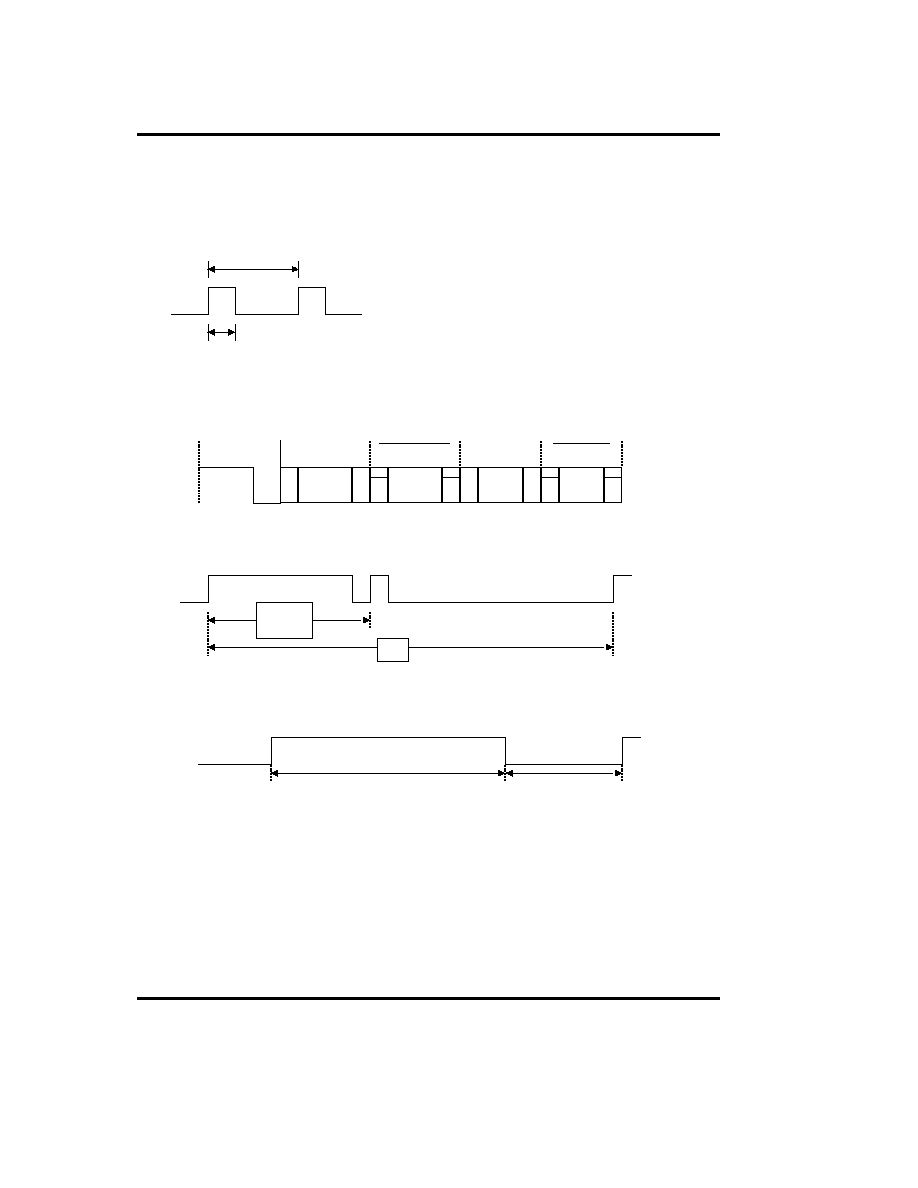

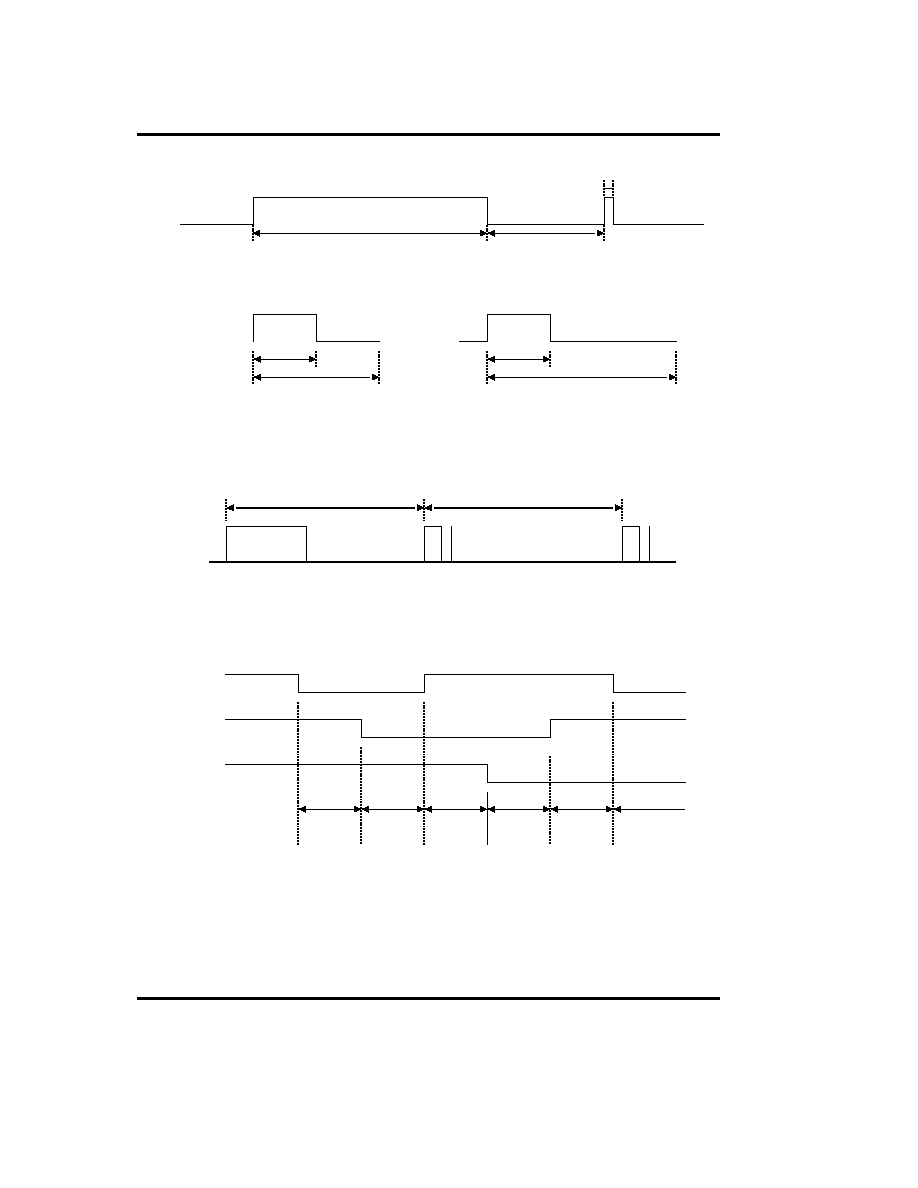

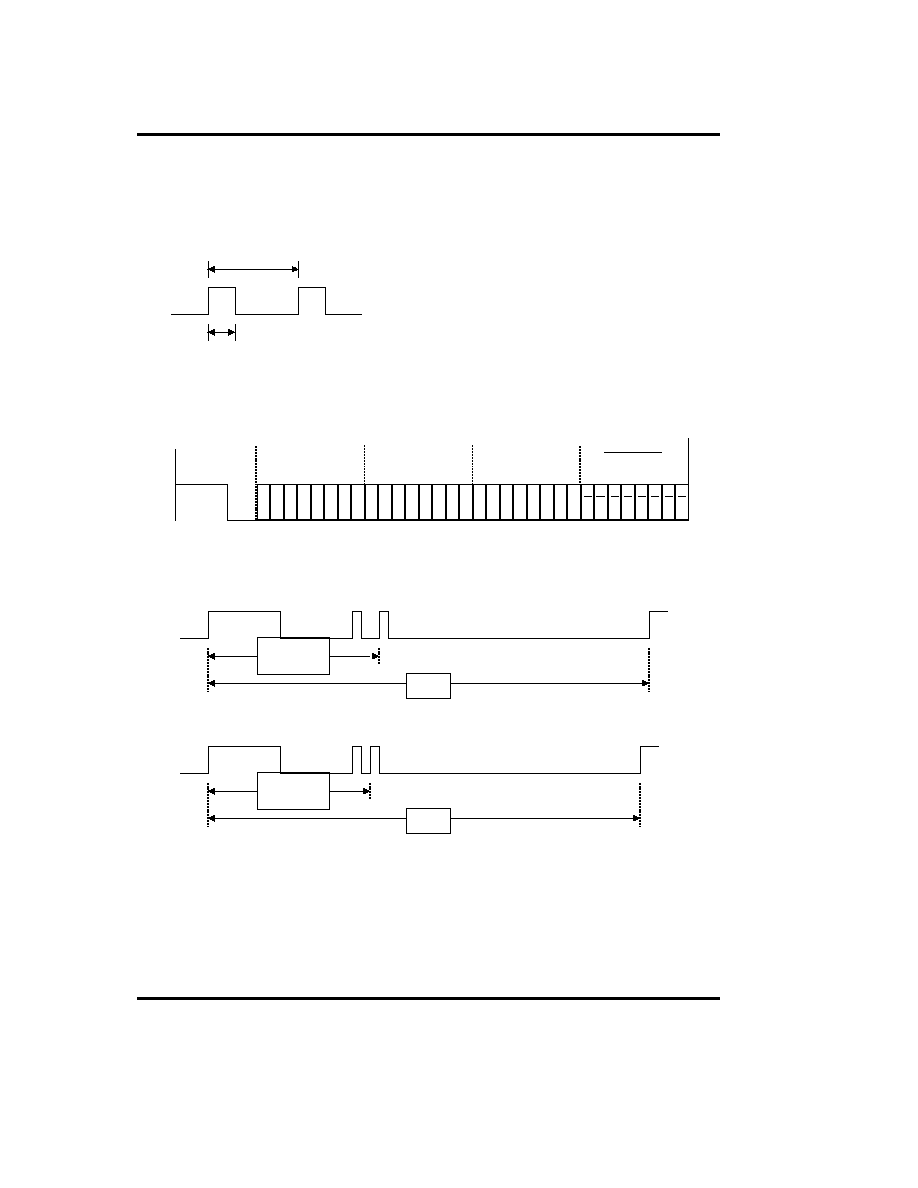

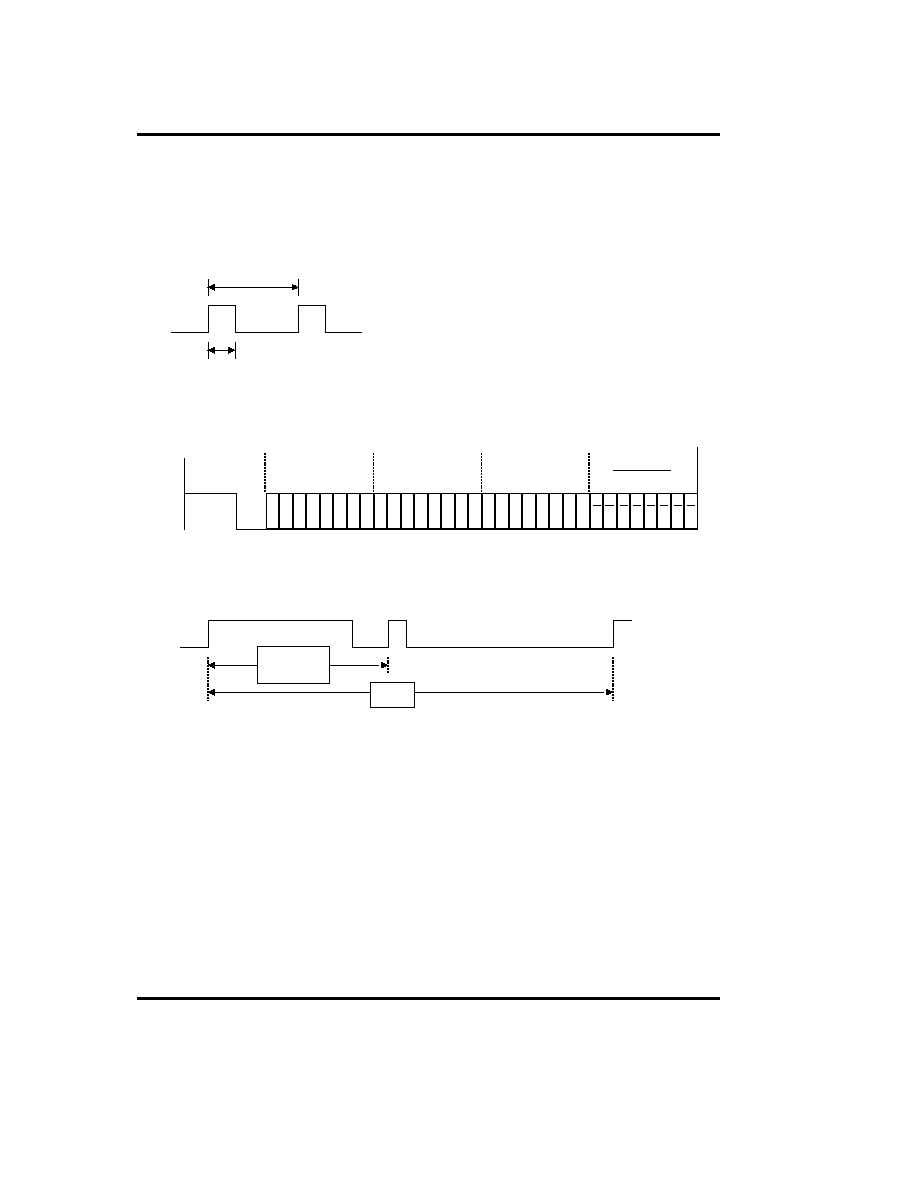

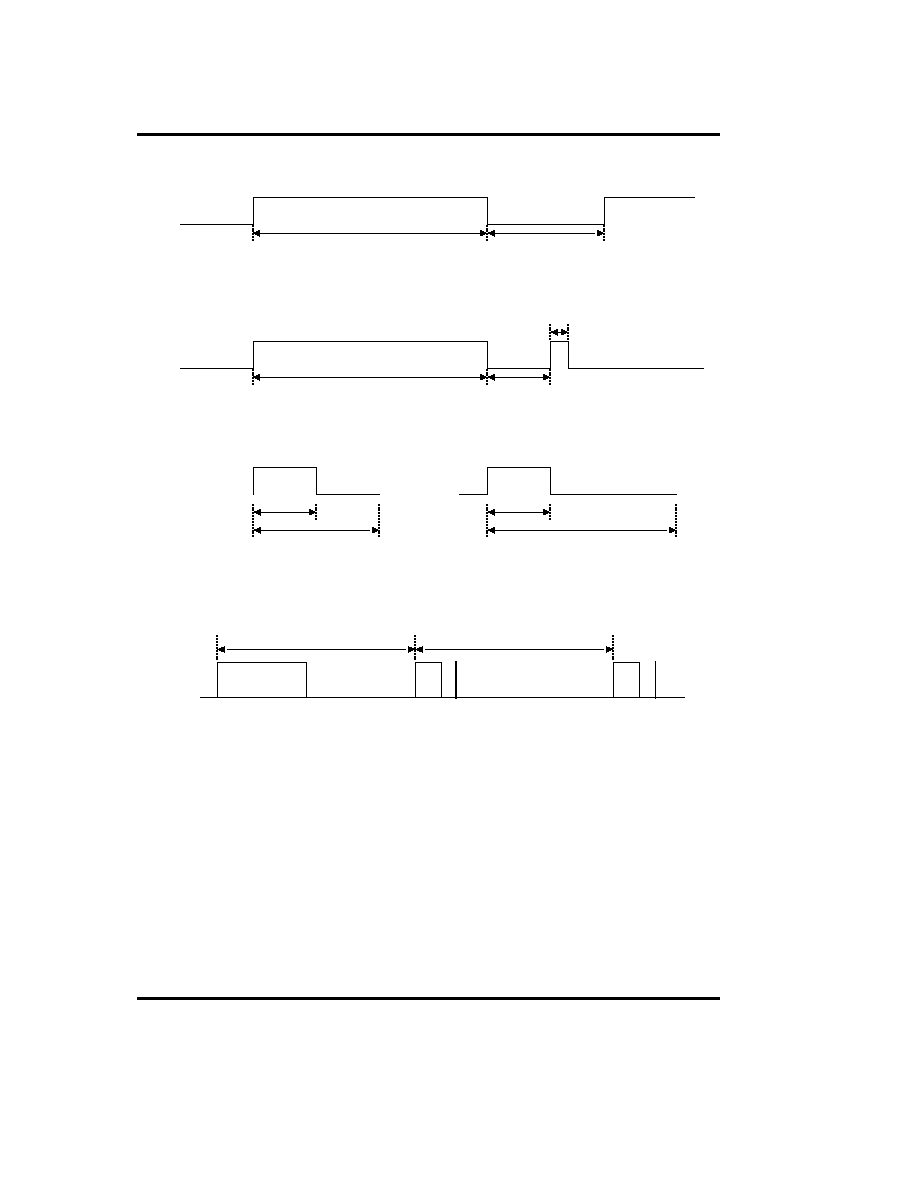

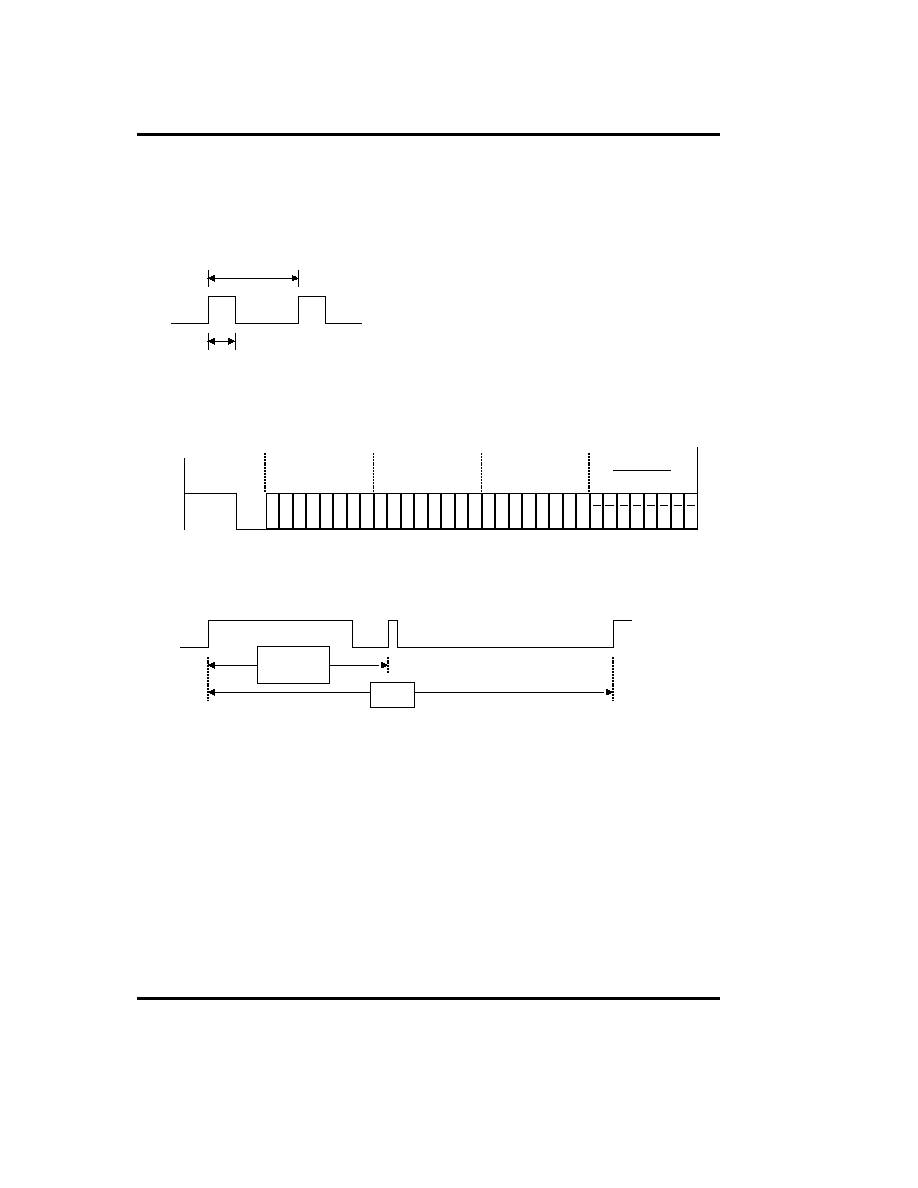

State Counter (SC)

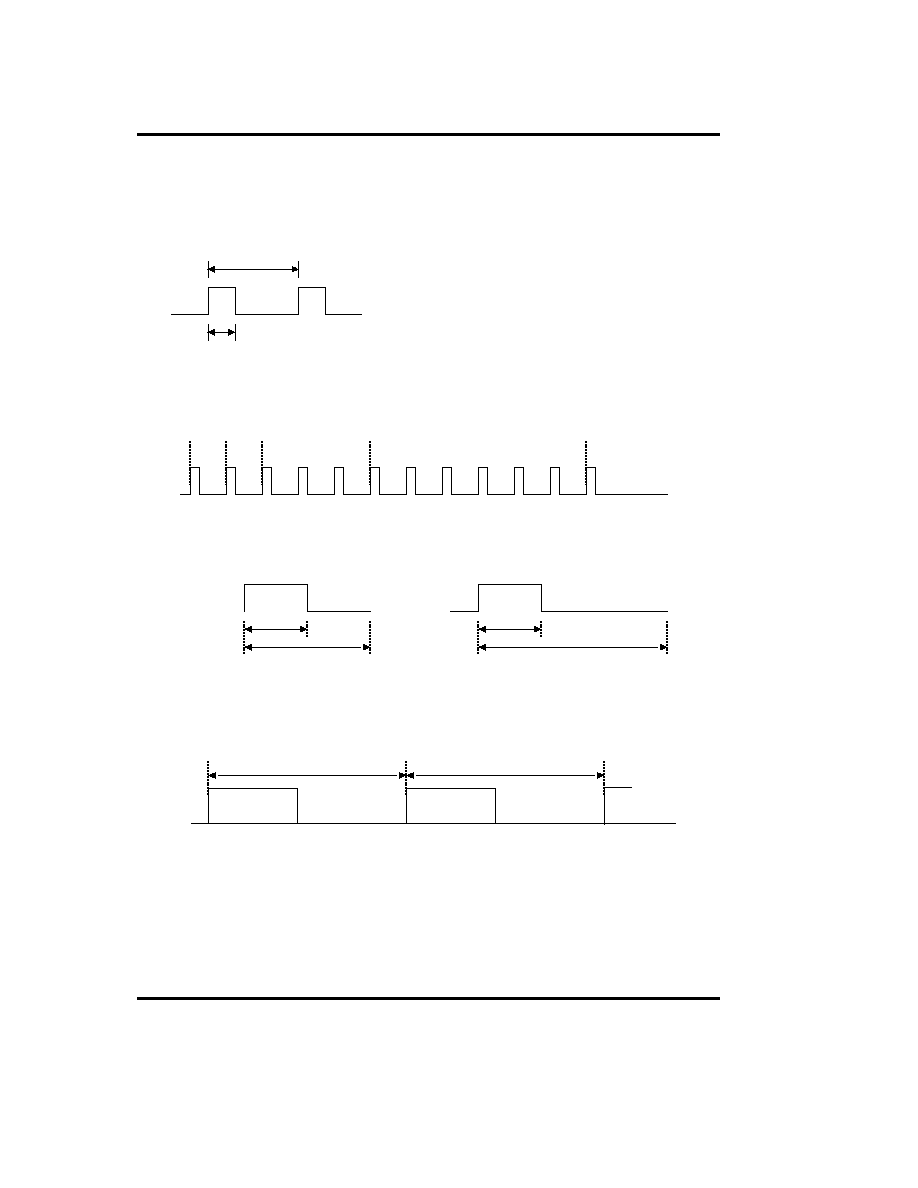

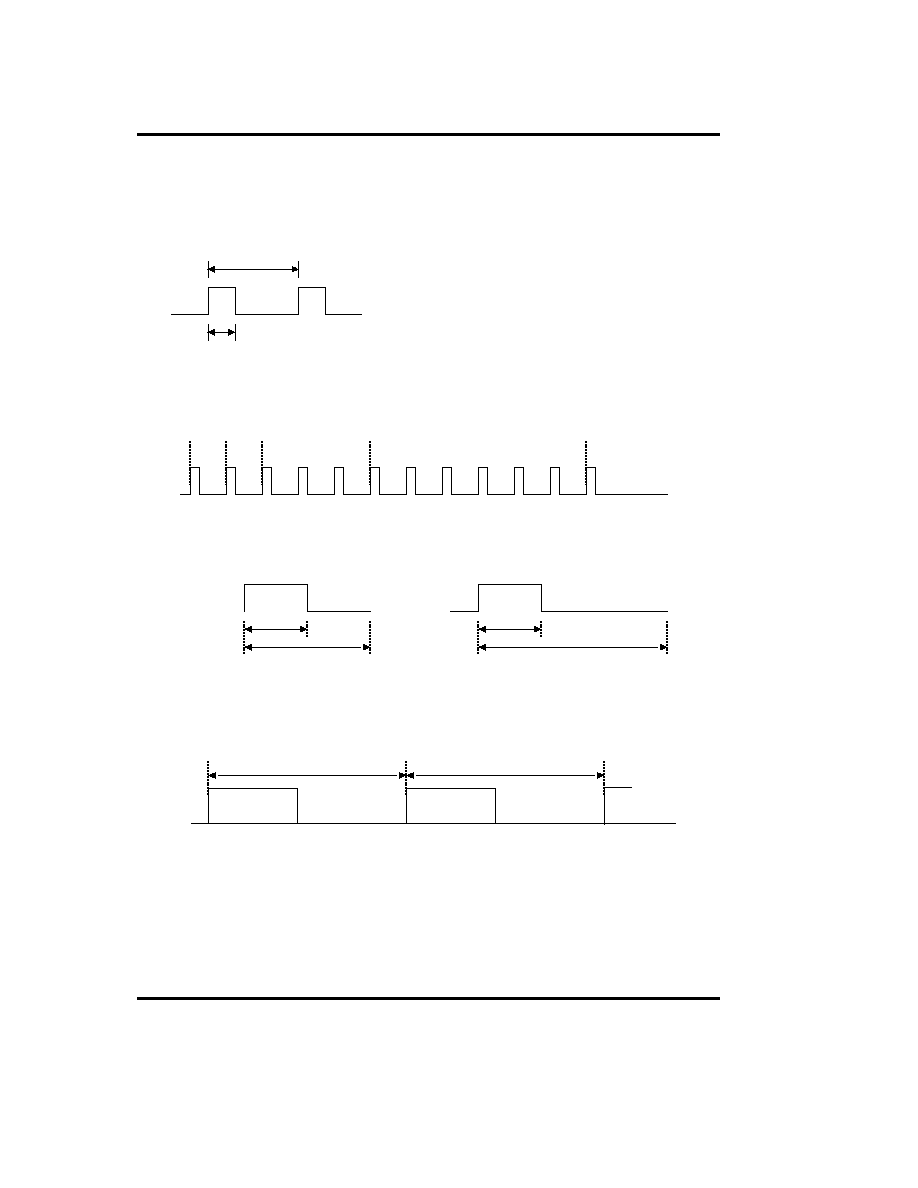

A fundamental machine cycle timing chart is shown below. Every instruction is

one byte length. Its execution time is the same. Execution of one instruction

takes 6 clocks for fetch cycle and 6 clocks for execute cycle (12 clocks in total).

Virtually these two cycles proceed simultaneously, and thus it is apparently

completed in 6 clocks (one machine cycle). Exceptionally BR, CAL and RTN

instructions is normal execution time since they change an addressing

sequencially. Therefore, the next instruction is prefetched so that its execution

is completed within the fetch cycle.

T1 T2 T3 T4 T5 T6 T1 T2 T3 T4 T5 T6

Fetch cycle N

Execute cycle N-1

Execute cycle N

Fetch cycle N-1

Machine

Cycle

Machine

Cycle

Phase

é

Phase

ê

Phase

ë

Fig. 2-3 Fundamental timing chart

Chapter 2. Architecture

2 - 6

Clock Generator

The GMS300 series has an internal clock oscillator. The oscillator circuit is

designed to operate with an external ceramic resonator. Internal capacitors are

available as a masked option. Oscillator circuit is able to organize by connecting

ceramic resonator to outside. (In order to built in capacitor for oscillation as

masked option.)

* It is necessary to connect capacitor to outside in order to change ceramic

resonator, You must examine refer to a manufacturer`s

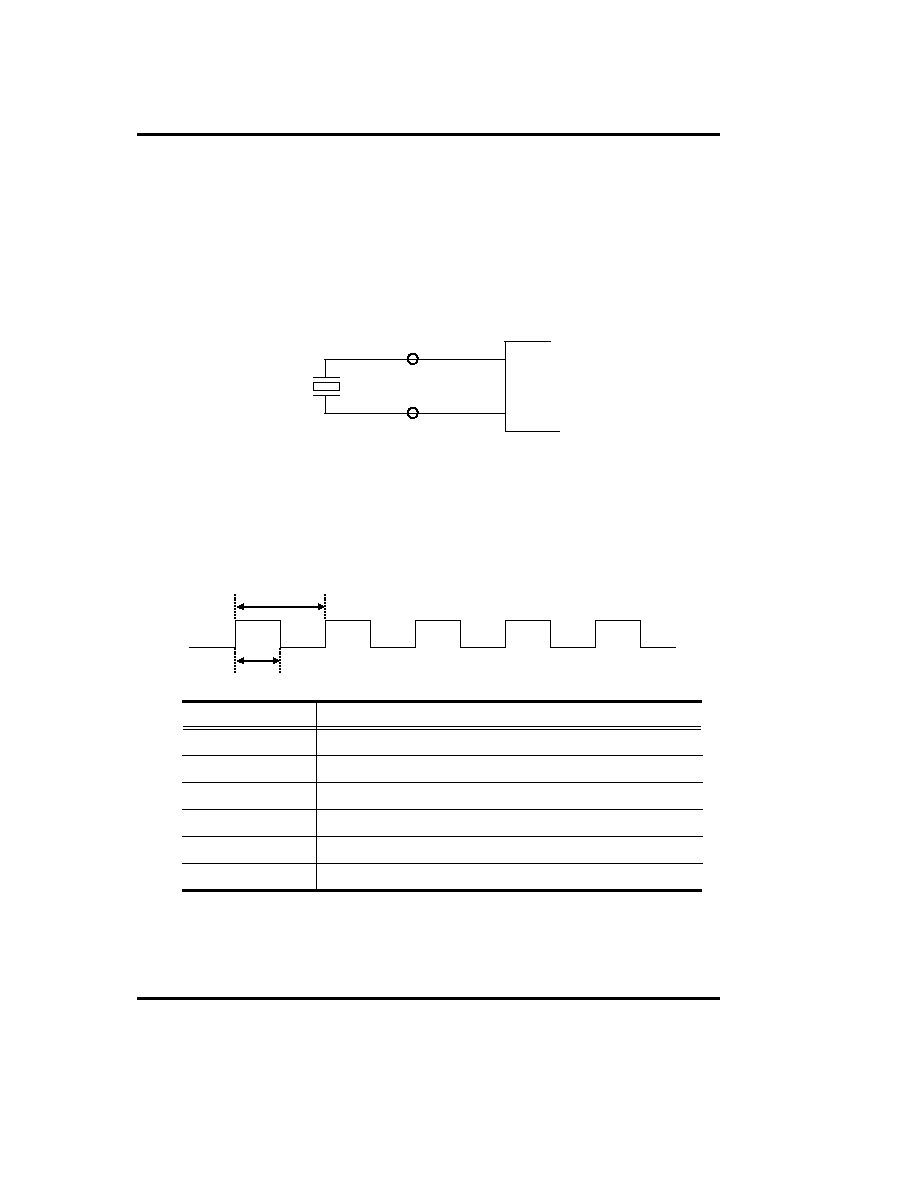

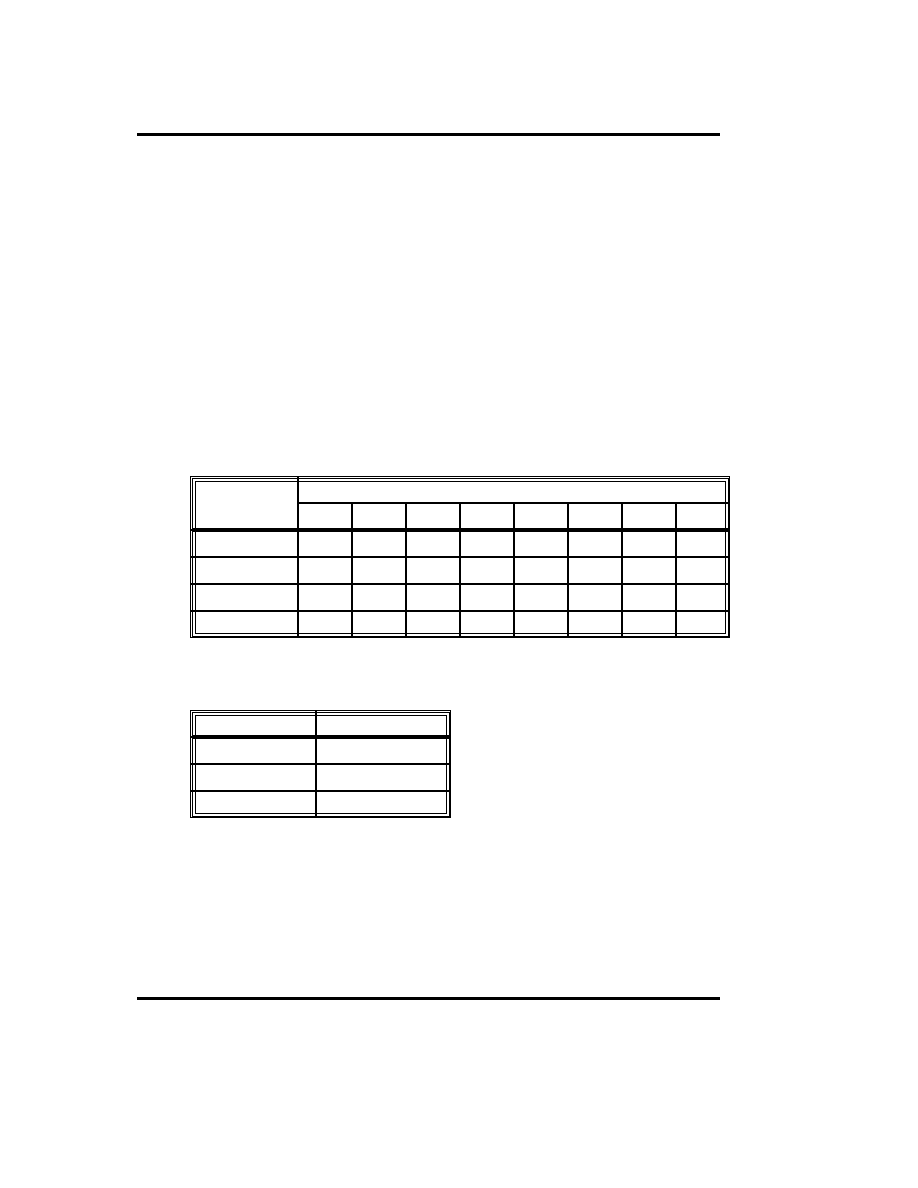

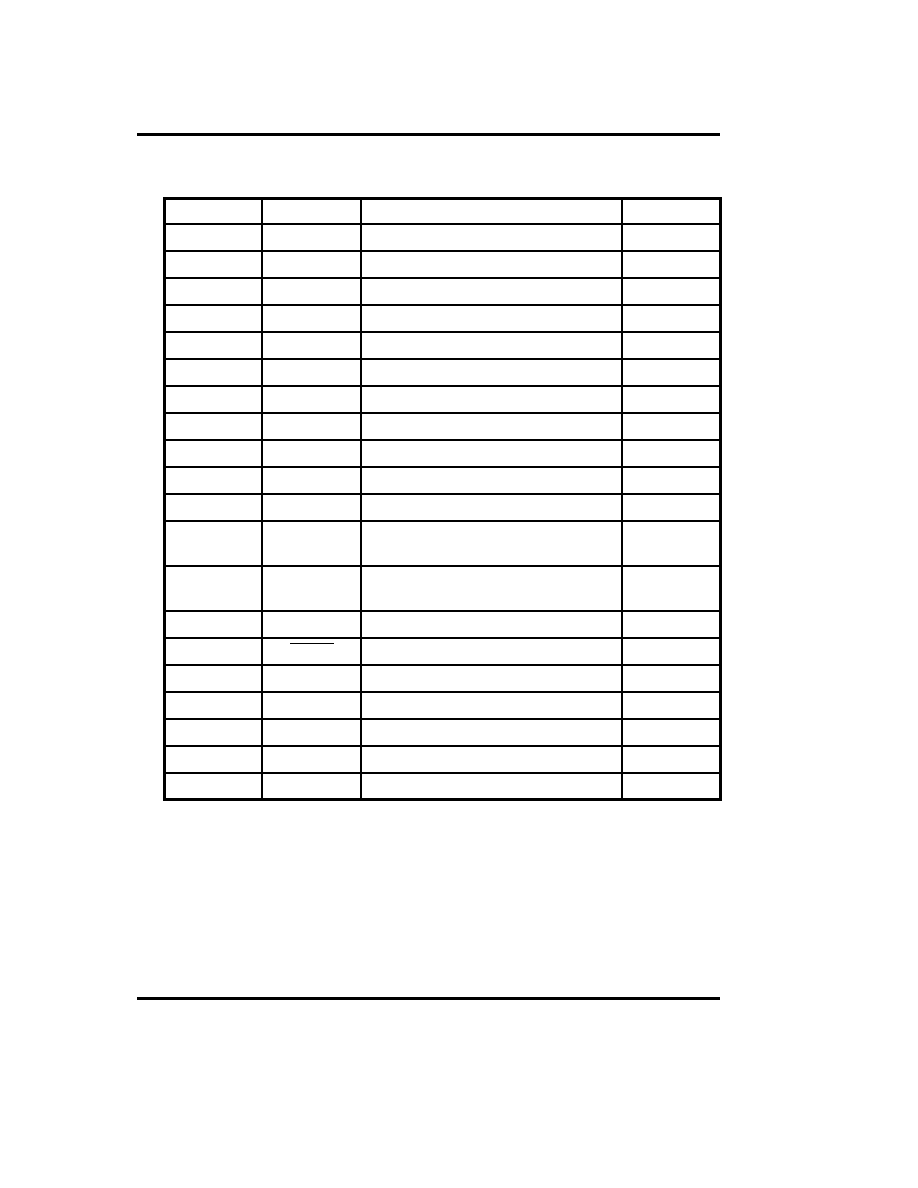

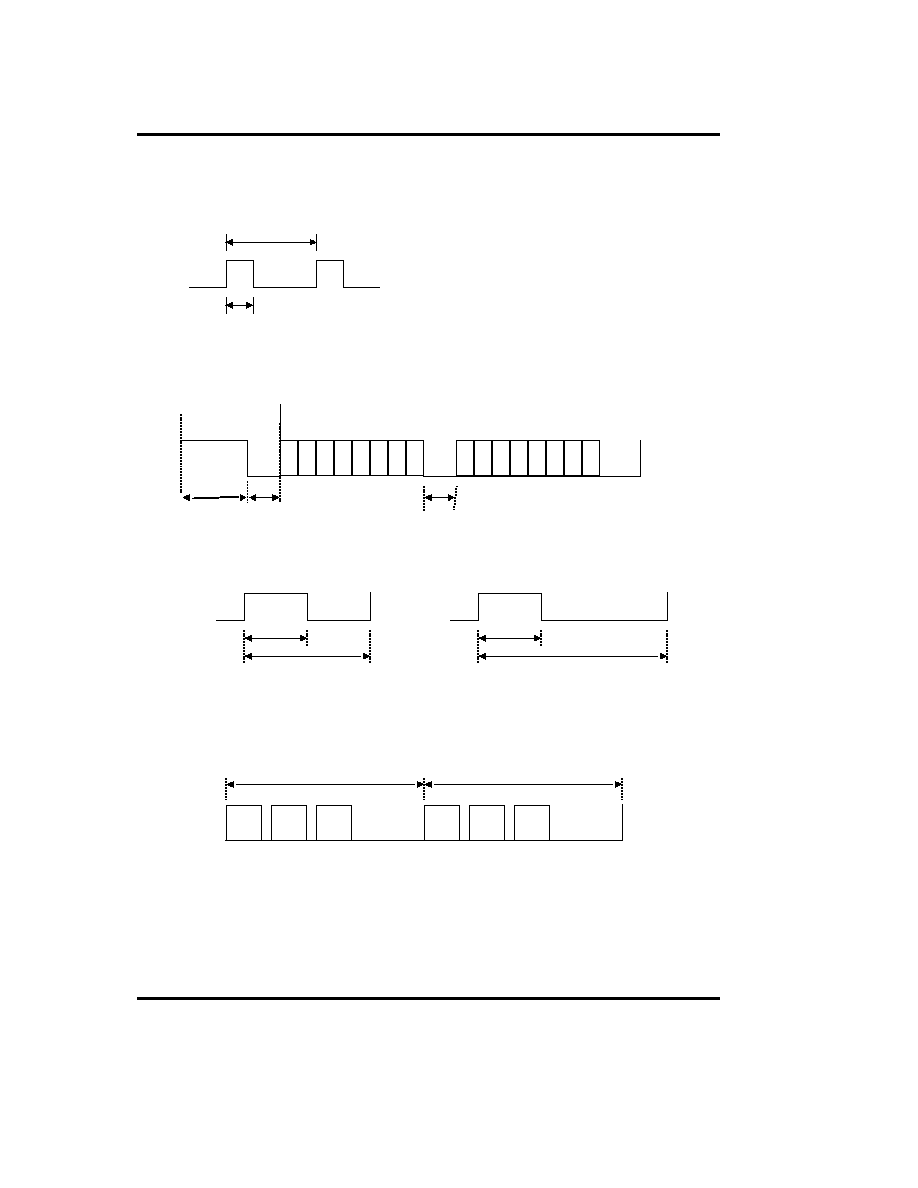

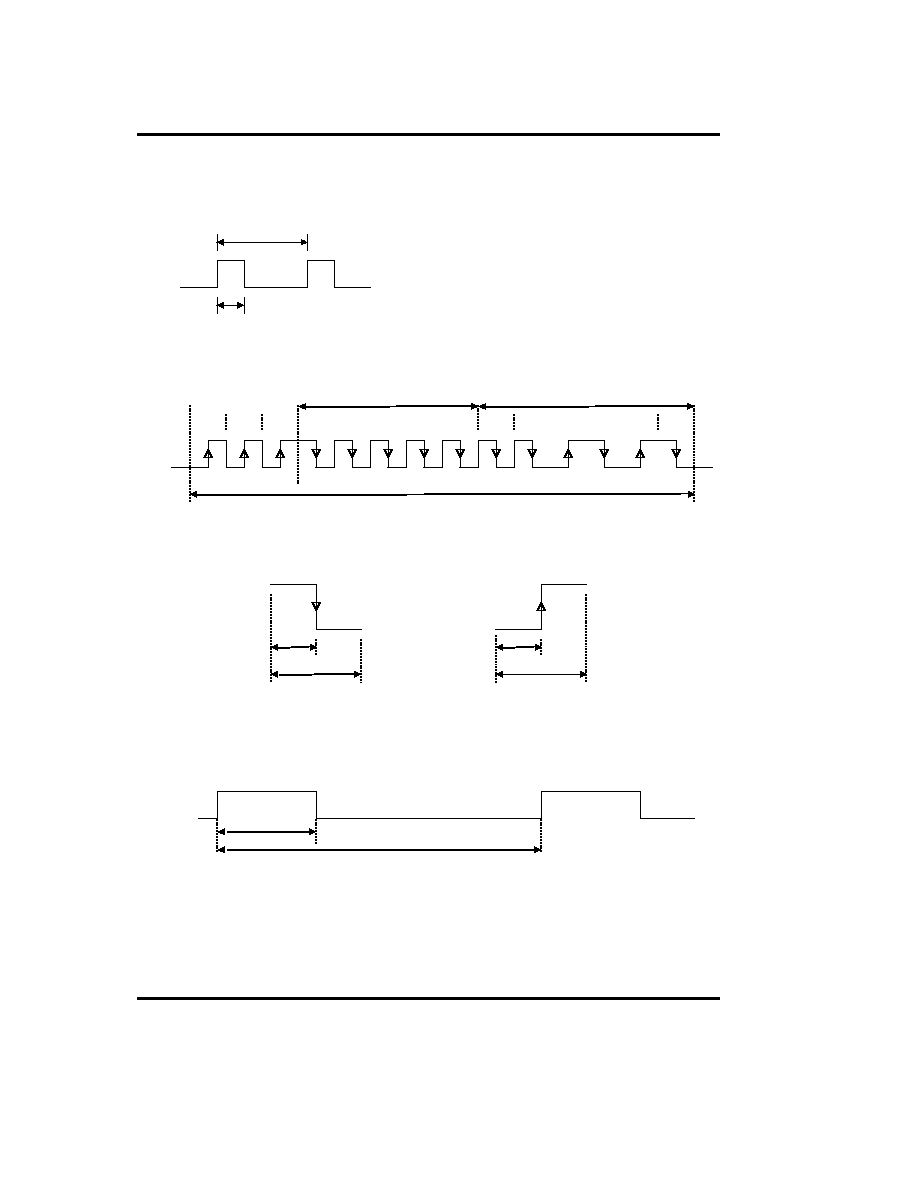

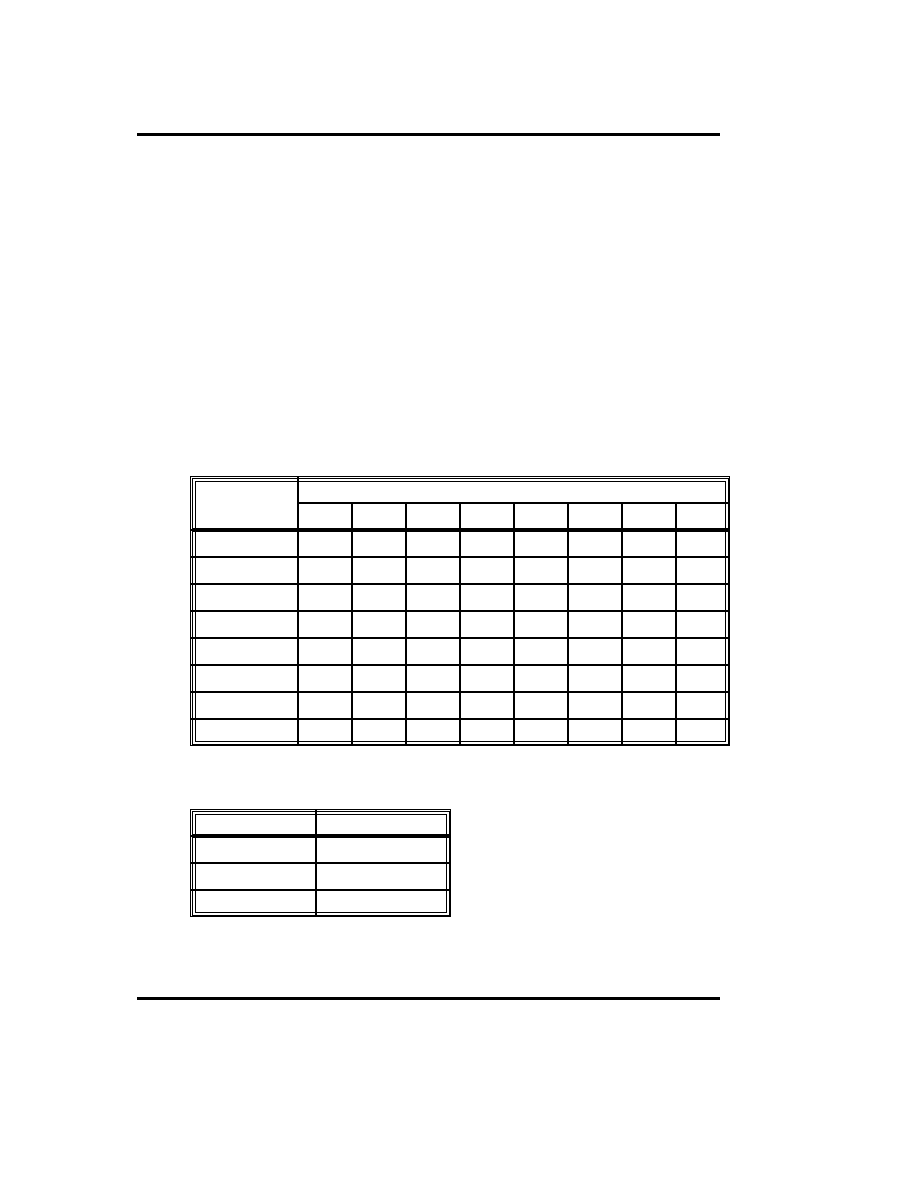

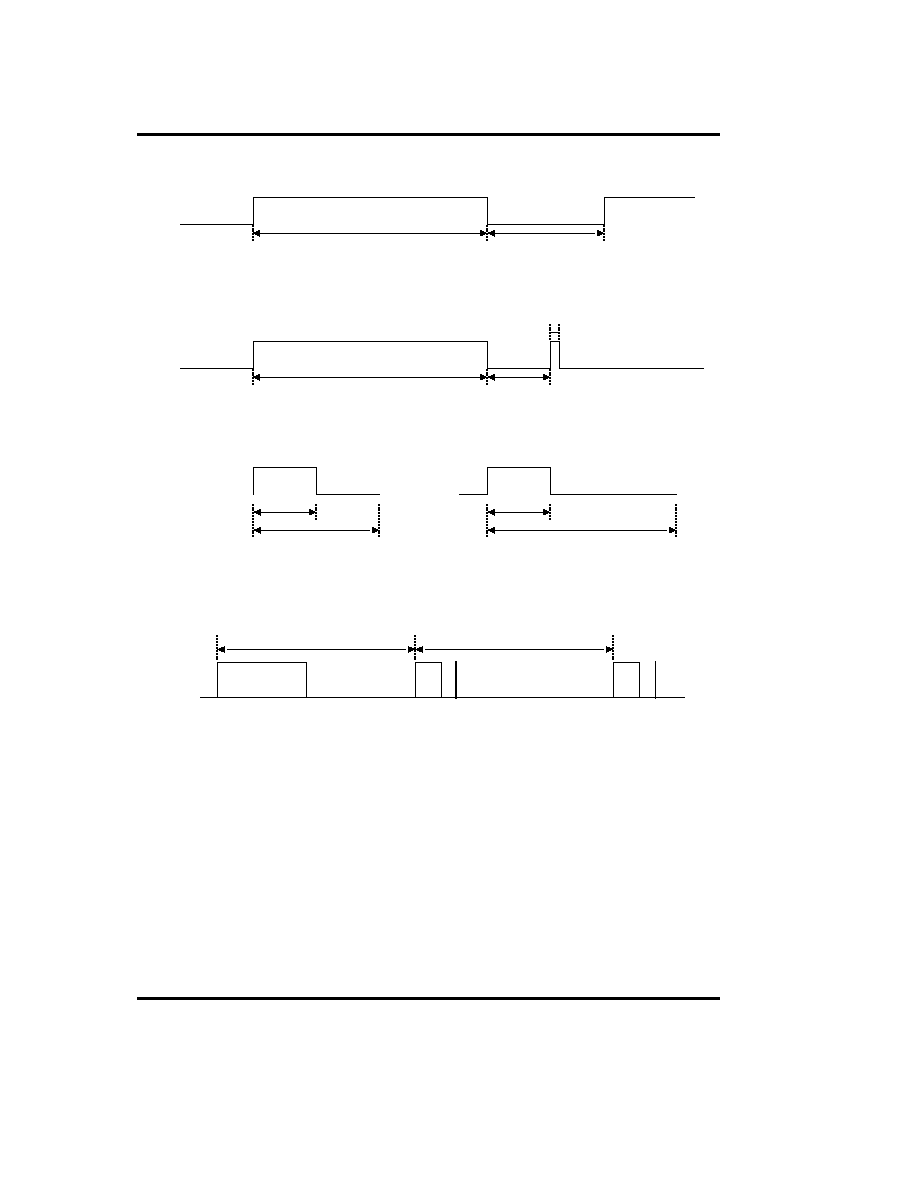

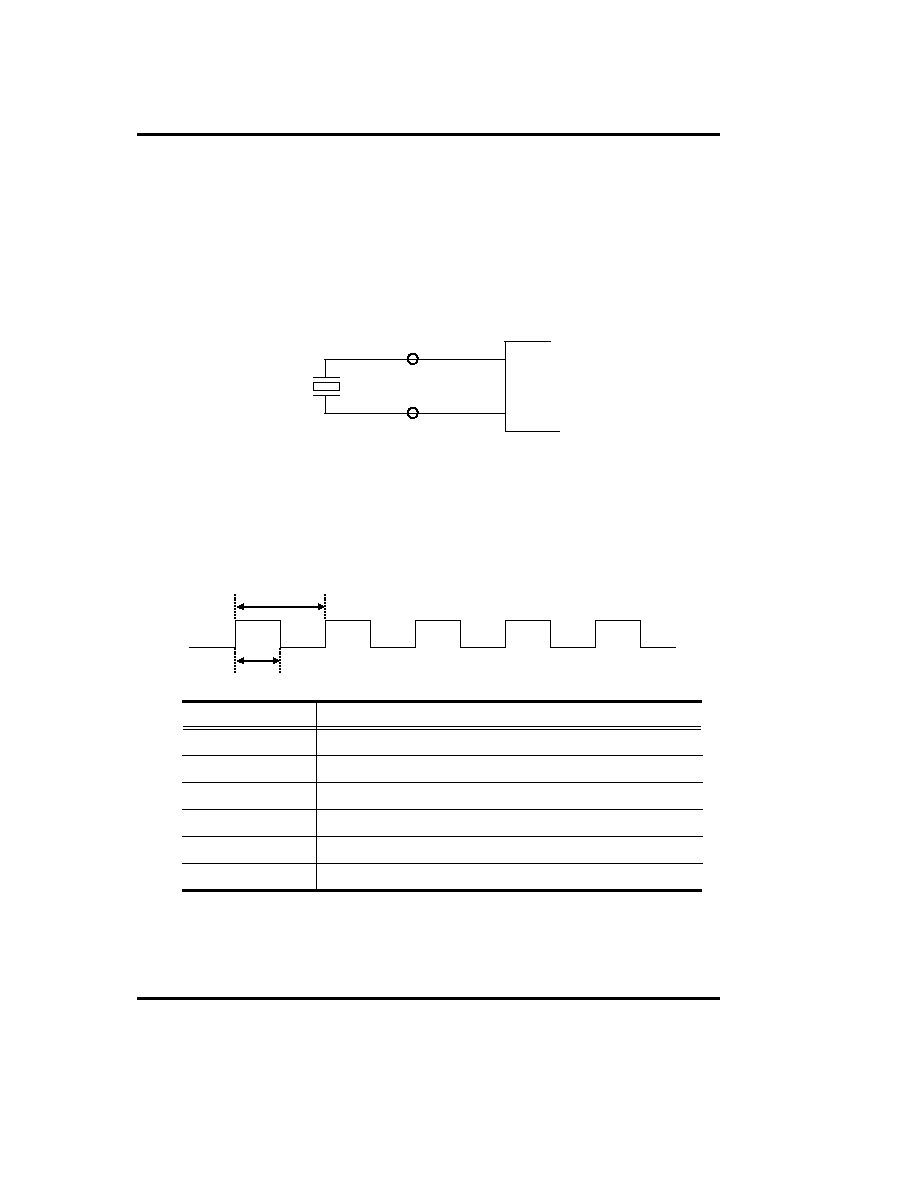

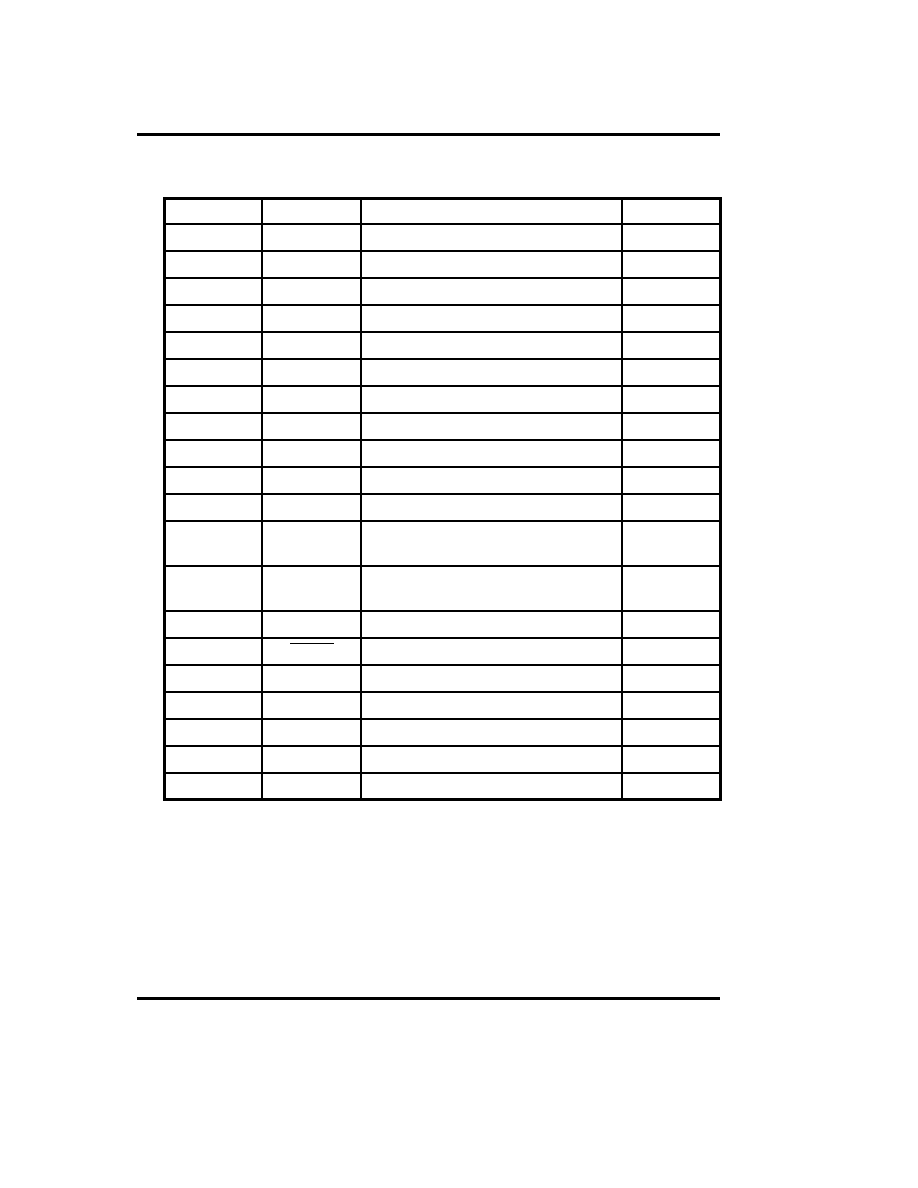

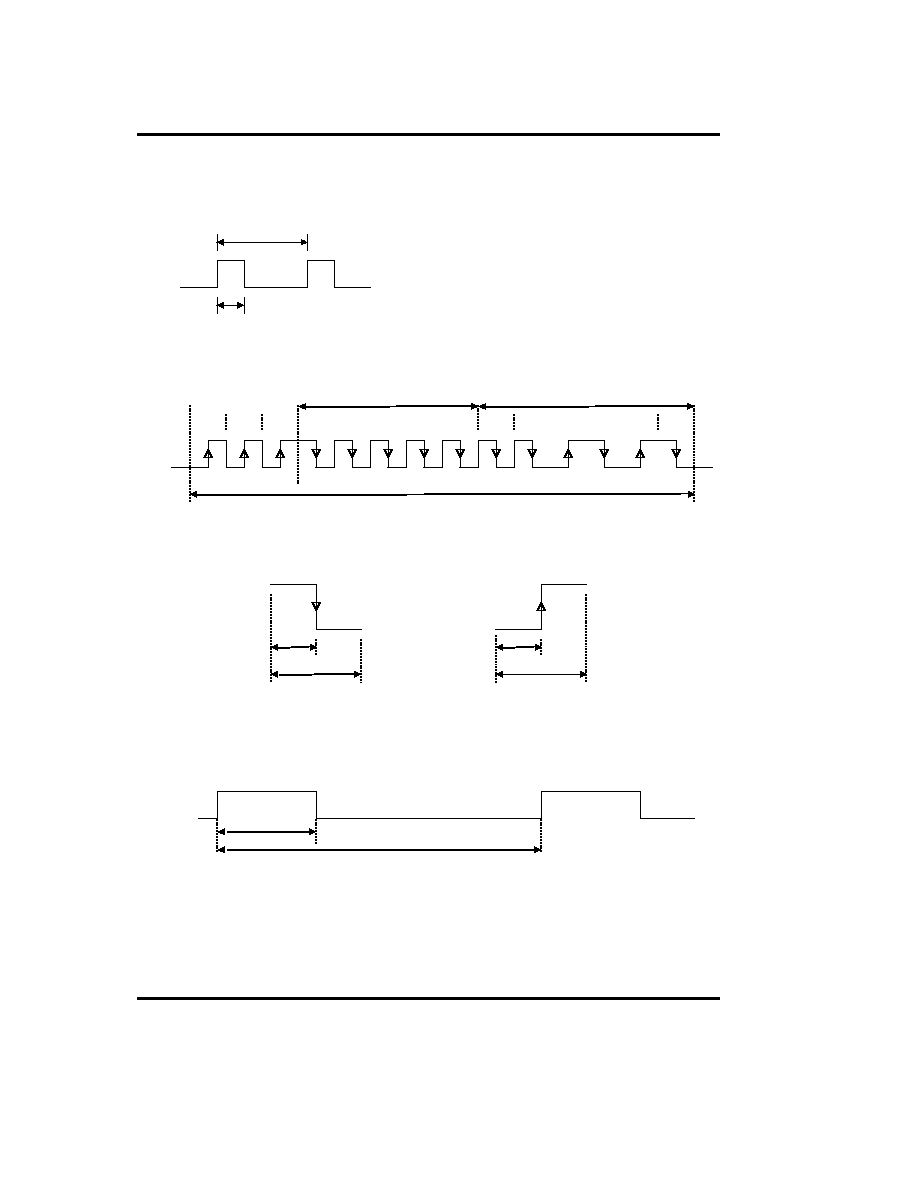

Pulse generator

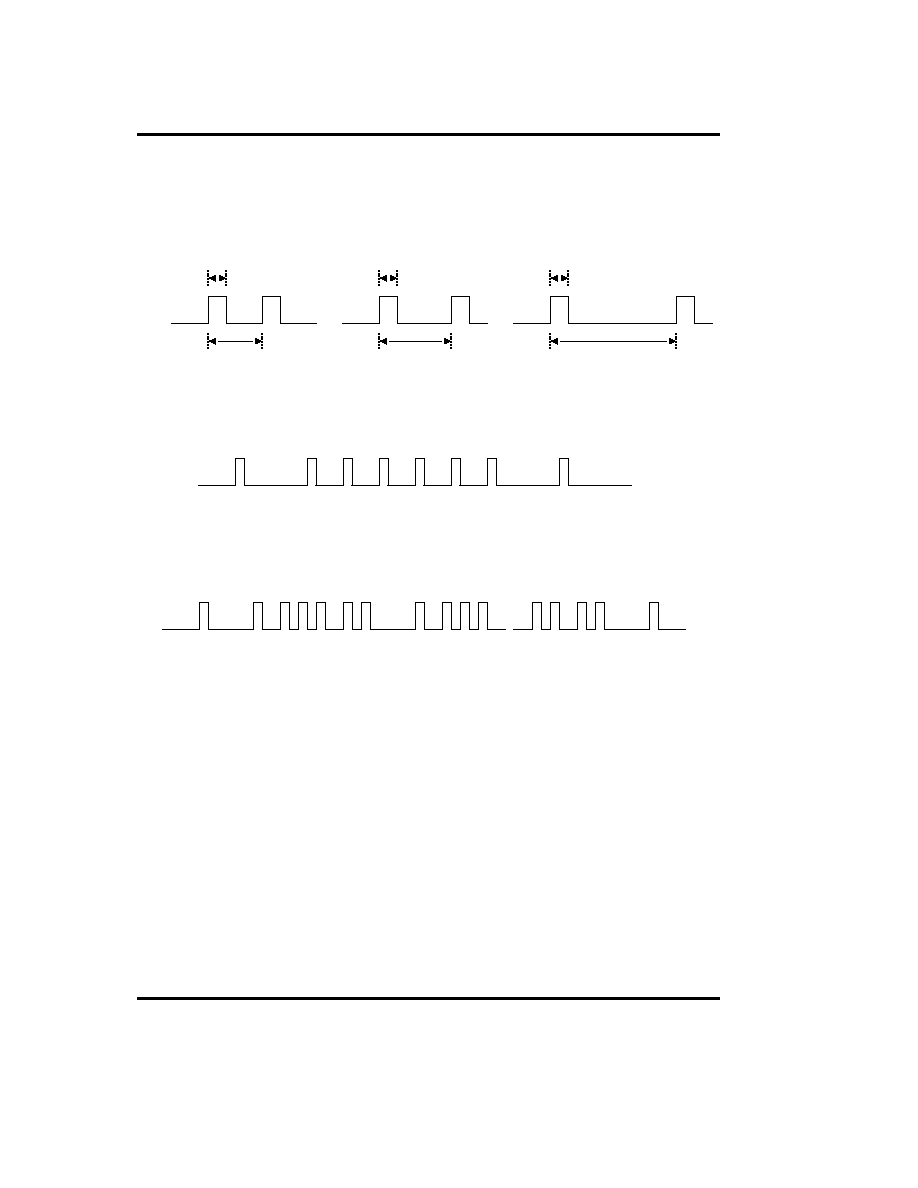

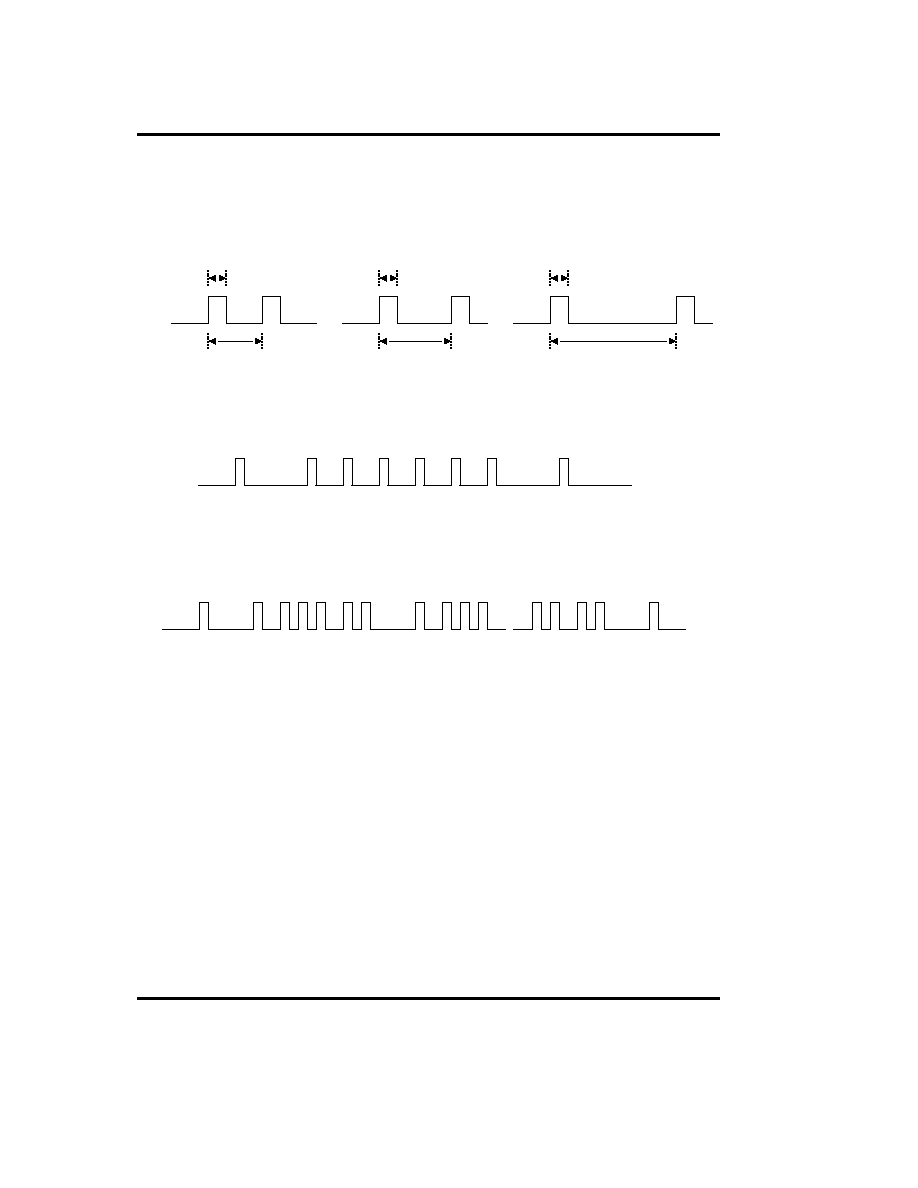

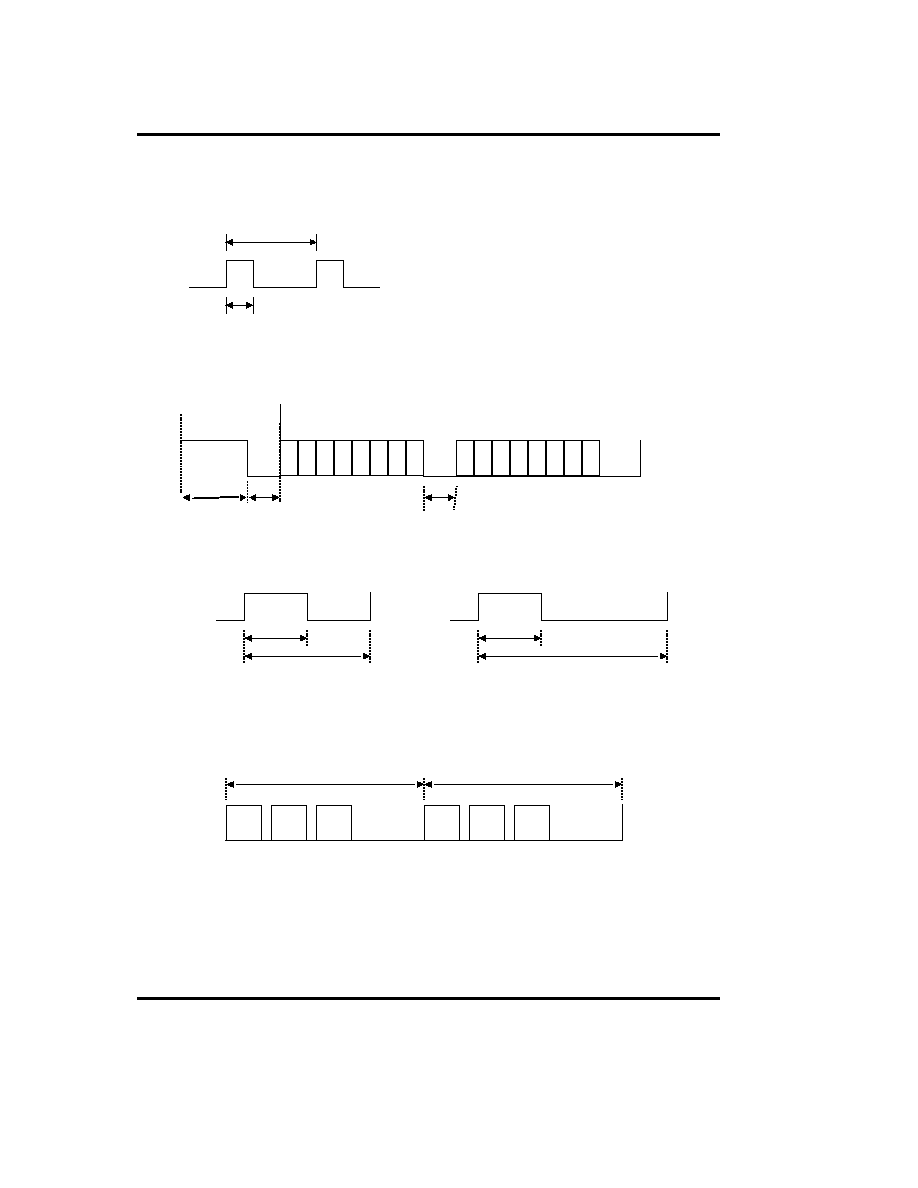

The following frequency and duty ratio are selected for carrier signal outputted

from the REMOUT port depending on a PMR (Pulse Mode Register) value set in

a program.

T

T1

REMOUT signal

T=1/f

PUL

= 12/f

OSC

,

T1/T = 1/2

0

1

PMR

2

3

4

5

T=1/f

PUL

= 12/f

OSC

,

T1/T = 1/3

T=1/f

PUL

= 8/f

OSC

,

T1/T = 1/2

T=1/f

PUL

= 8/f

OSC

,

T1/T = 1/4

T=1/f

PUL

= 11/f

OSC

,

T1/T = 4/11

No Pulse (same to D0~D9)

* Default value is

Ì

0

Ì

Table 2-2 PMR selection table

Chapter 2. Architecture

22

23

OSC2

OSC1

2 - 7

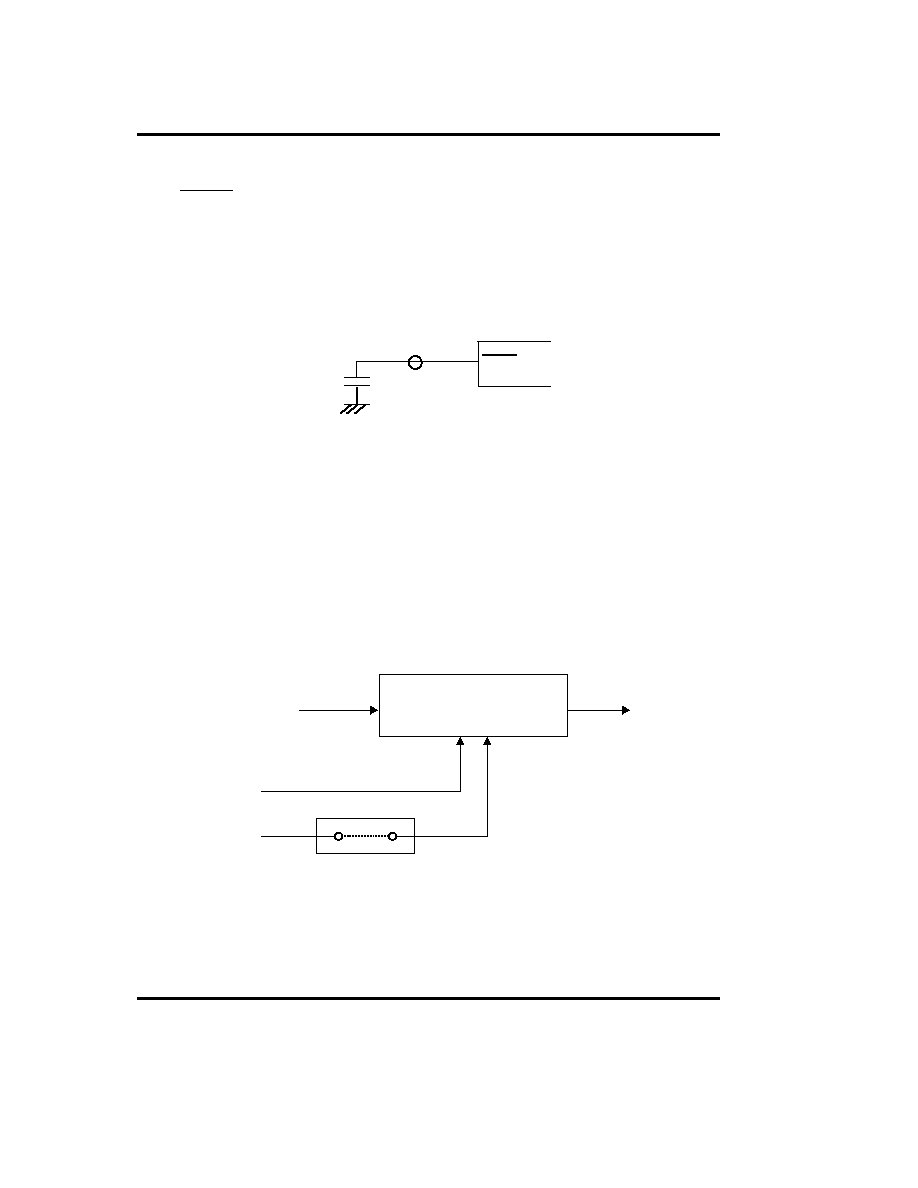

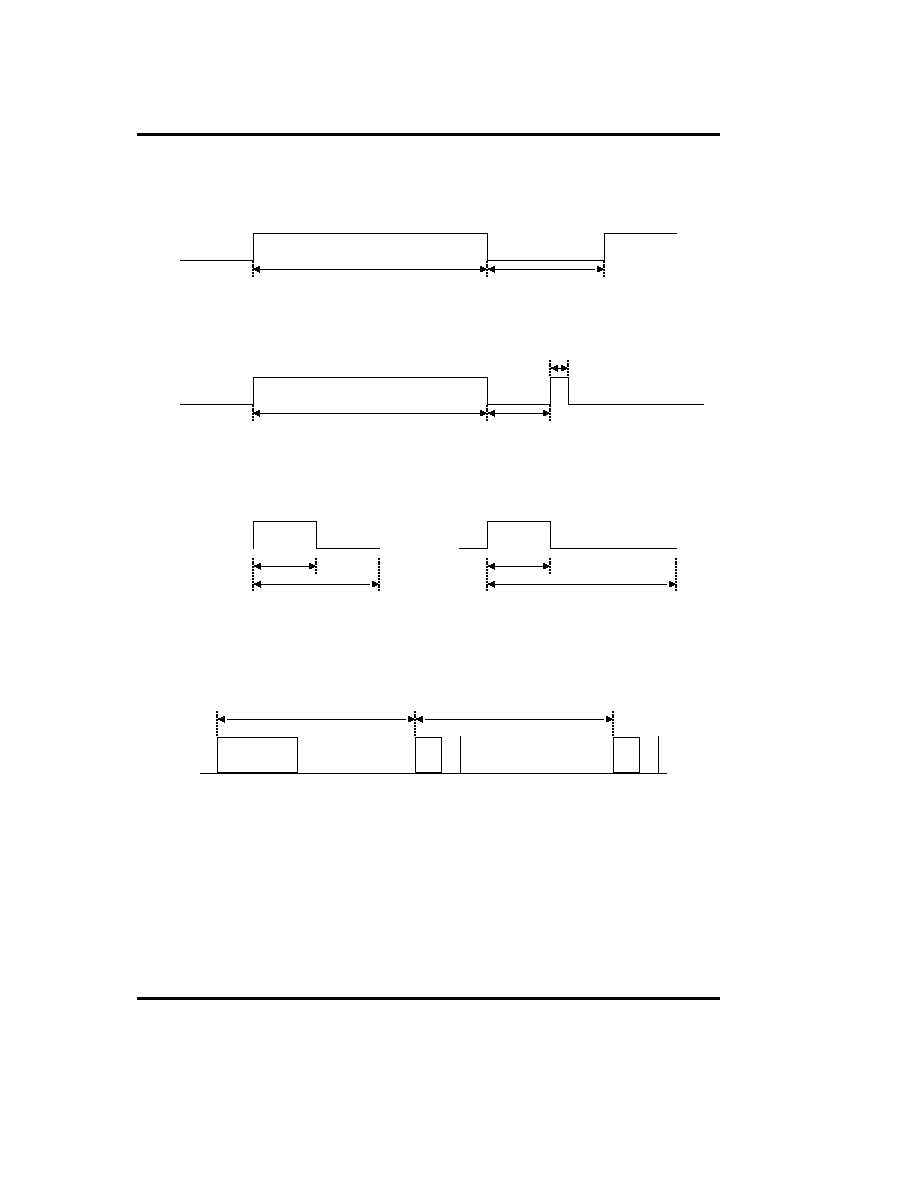

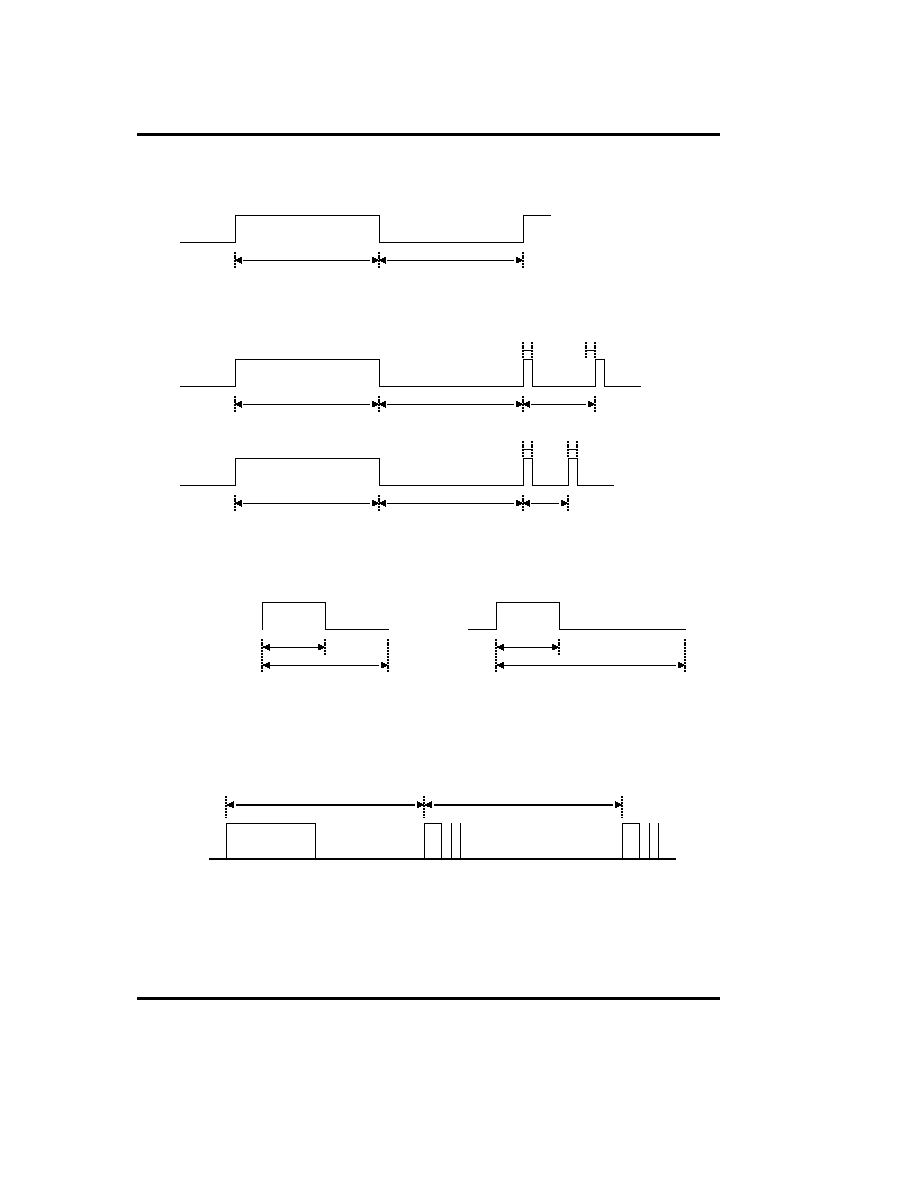

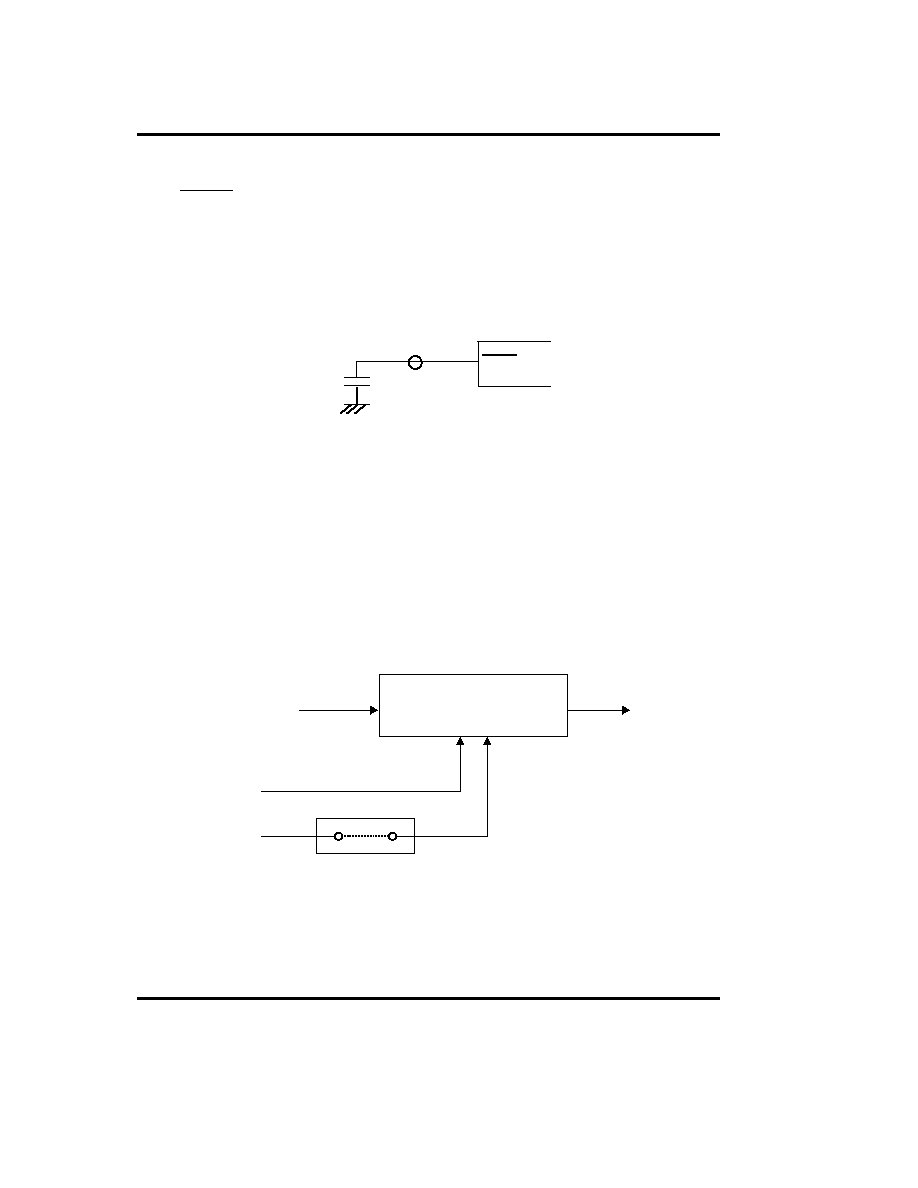

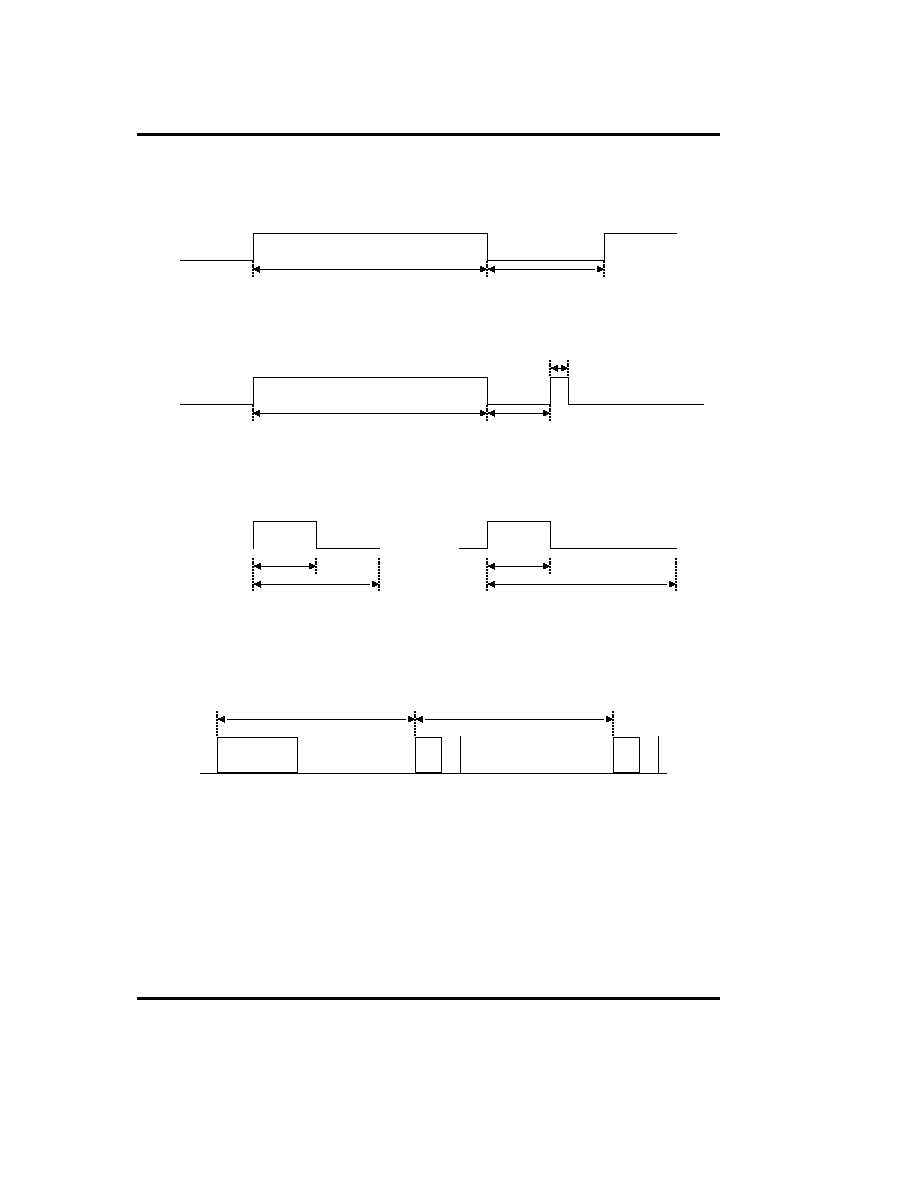

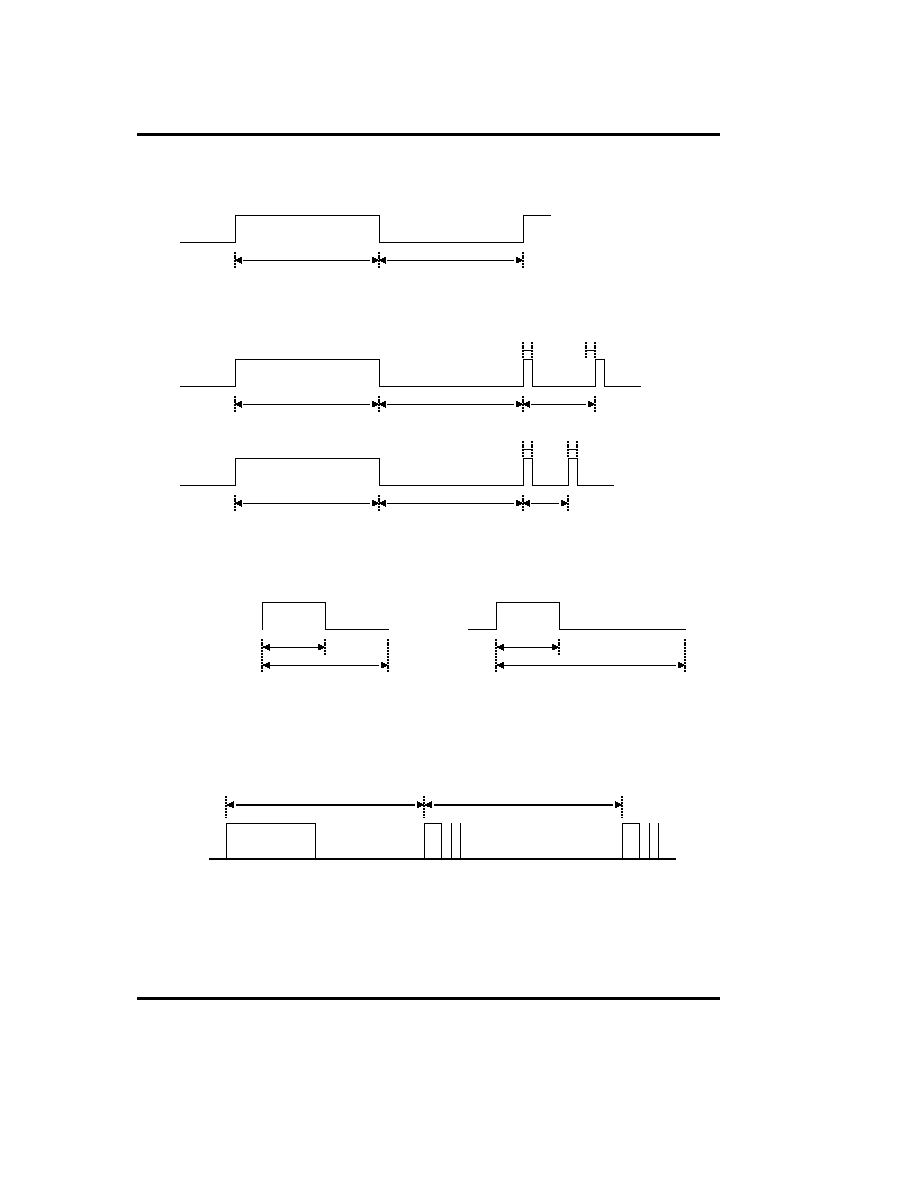

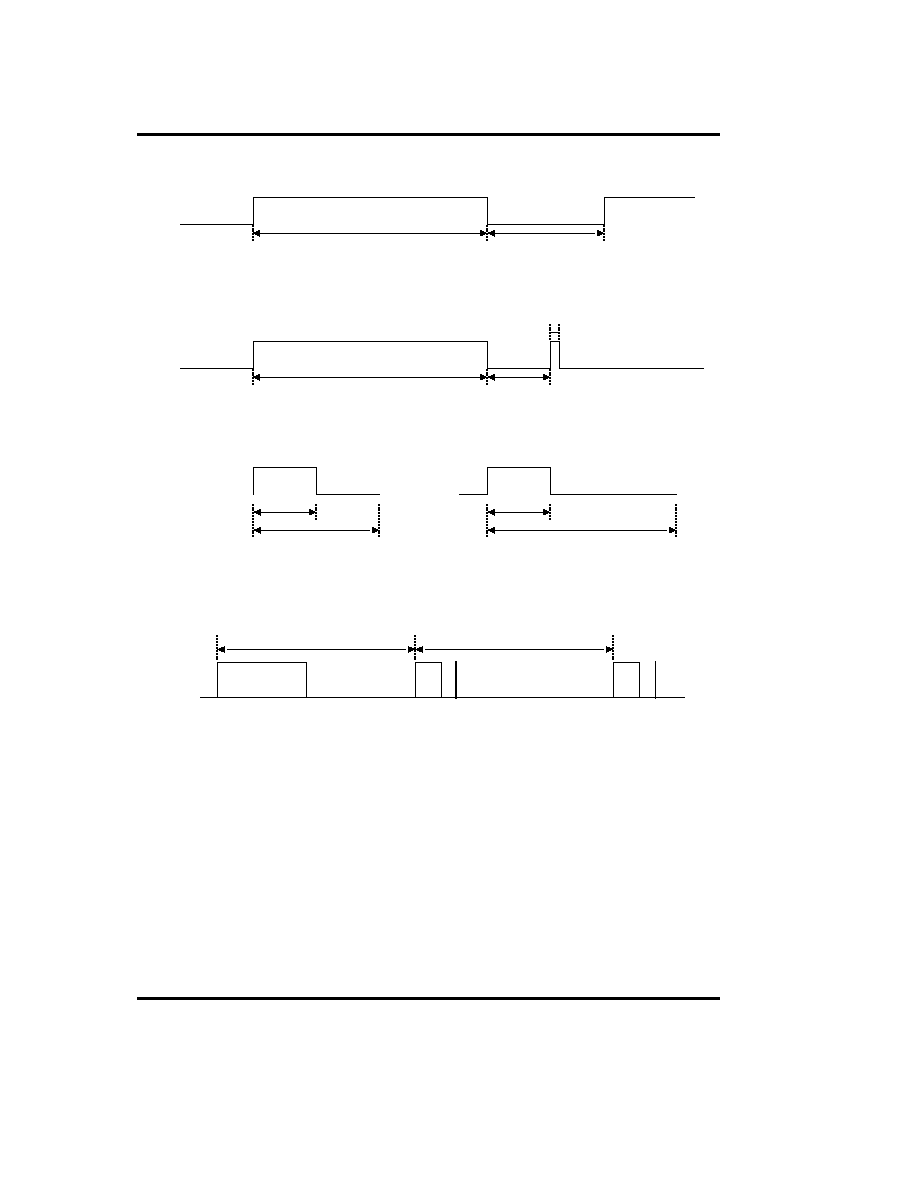

Initial Reset Circuit

RESET pin must be down to

Ì

L

Ì

more than 4 machine cycle by outside

capacitor or other for power on reset.

The mean of 1 machine cycle is below. 1 machine cycle is 6/f

OSC

, however,

operating voltage must be in recommended operating conditions, and clock

oscillating stability.

* It is required to adjust C value depending on rising time of power supply.

(Example shows the case of rising time shorter than 10ms.)

Watch Dog Timer (WDT)

Watch dog timer is organized binary counter of 14 steps. The selected of

f

OSC

/6 cycle come in the first step of WDT. If this counter was overflowed, come

out reset signal automatically, internal circuit is initialized.

The overflow time is 6

Ø

2

13

/f

OSC

(108.026ms at f

OSC

= 455KHz).

Normally, the binary counter must be reset before the overflow by using reset

instruction (WDTR) or / and REMOUT port (Y-reg=8, SO instruction execution) at

masked option.

* It is constantly reset in STOP mode. When STOP is released, counting is

restarted. (Refer to 1-13 STOP function>)

1

RESET

0.1uF

Chapter 2. Architecture

Binary counter

(14 steps)

RESET (edge-trigger)

f

OSC

/6

CPU reset

Reset

by instruction

REMOUT

output

Mask Option

INTRODUCTION

1

ARCHITECTURE

2

INSTRUCTION

3

EVALUATION BOARD

4

SOFTWARE

5

APPENDIX

6

3 - 1

Chapter 3. Instruction

CHAPTER 3. Instruction

INSTRUCTION FORMAT

All of the 43 instruction in GMS300 series is format in two fields of OP code and

operand which consist of eight bits. The following formats are available with

different types of operands.

Format

é

All eight bits are for OP code without operand.

Format

ê

Two bits are for operand and six bits for OP code.

Two bits of operand are used for specifying bits of RAM and X-register (bit 1 and

bit 7 are fixed at

Ì

0

Ì

)

Format

ë

Four bits are for operand and the others are OP code.

Four bits of operand are used for specifying a constant loaded in RAM or Y-

register, a comparison value of compare command, or page addressing in ROM.

Format

ì

Six bits are for operand and the others are OP code.

Six bits of operand are used for word addressing in the ROM.

3 - 2

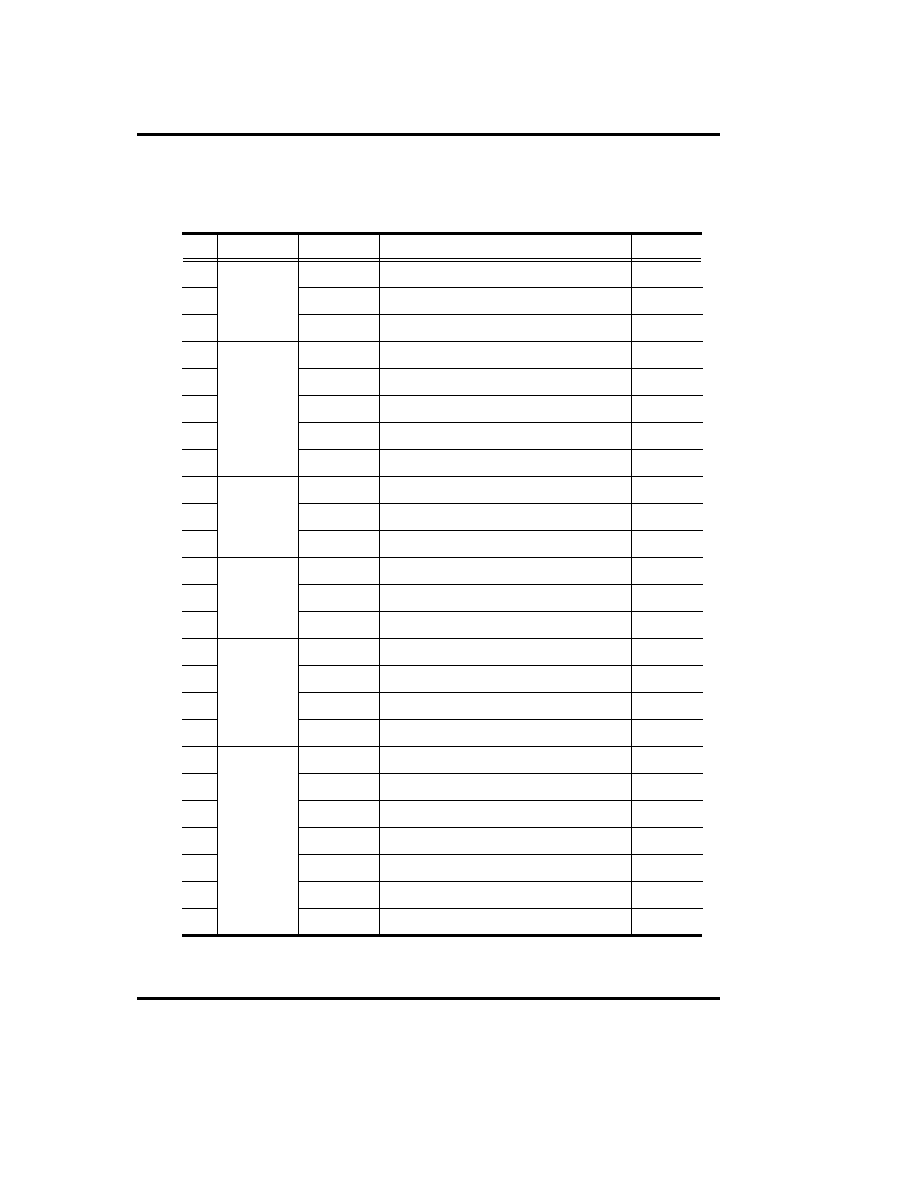

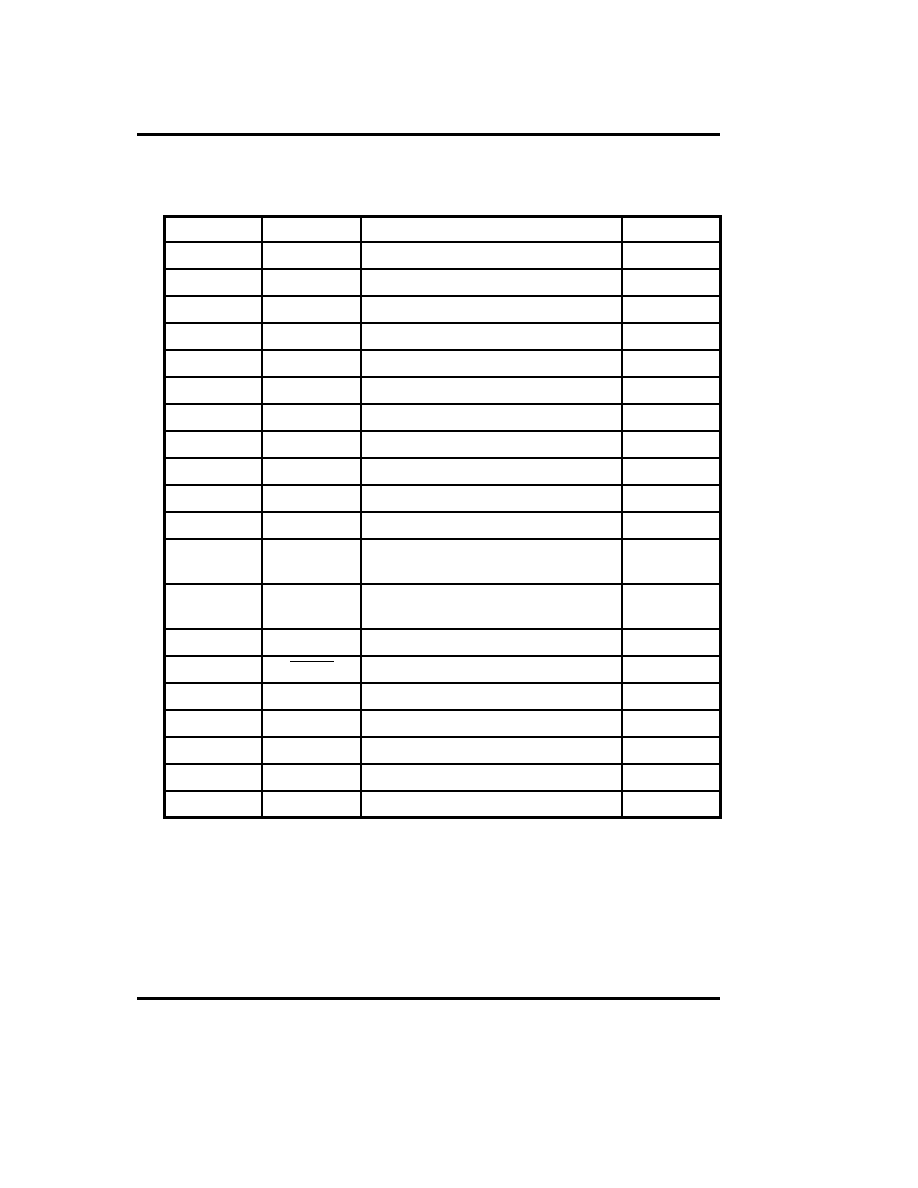

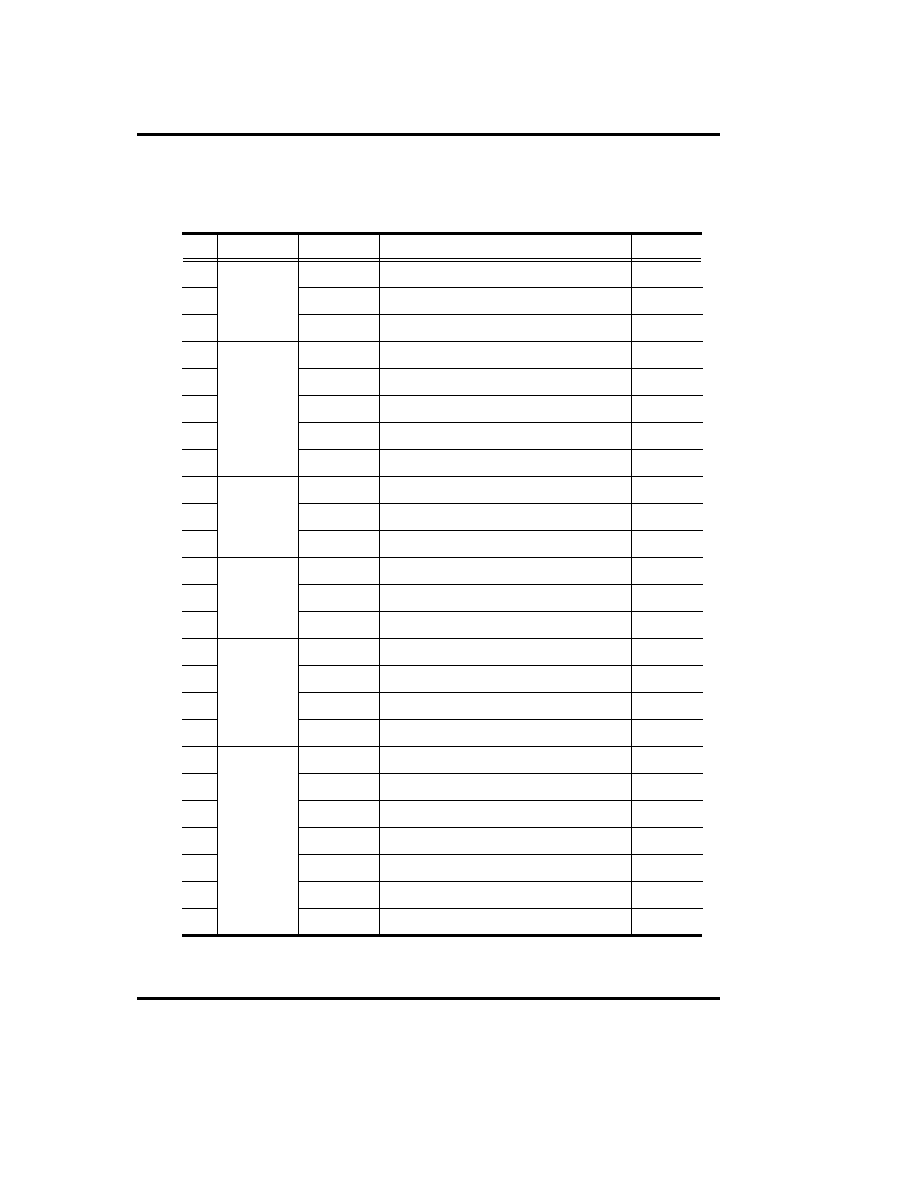

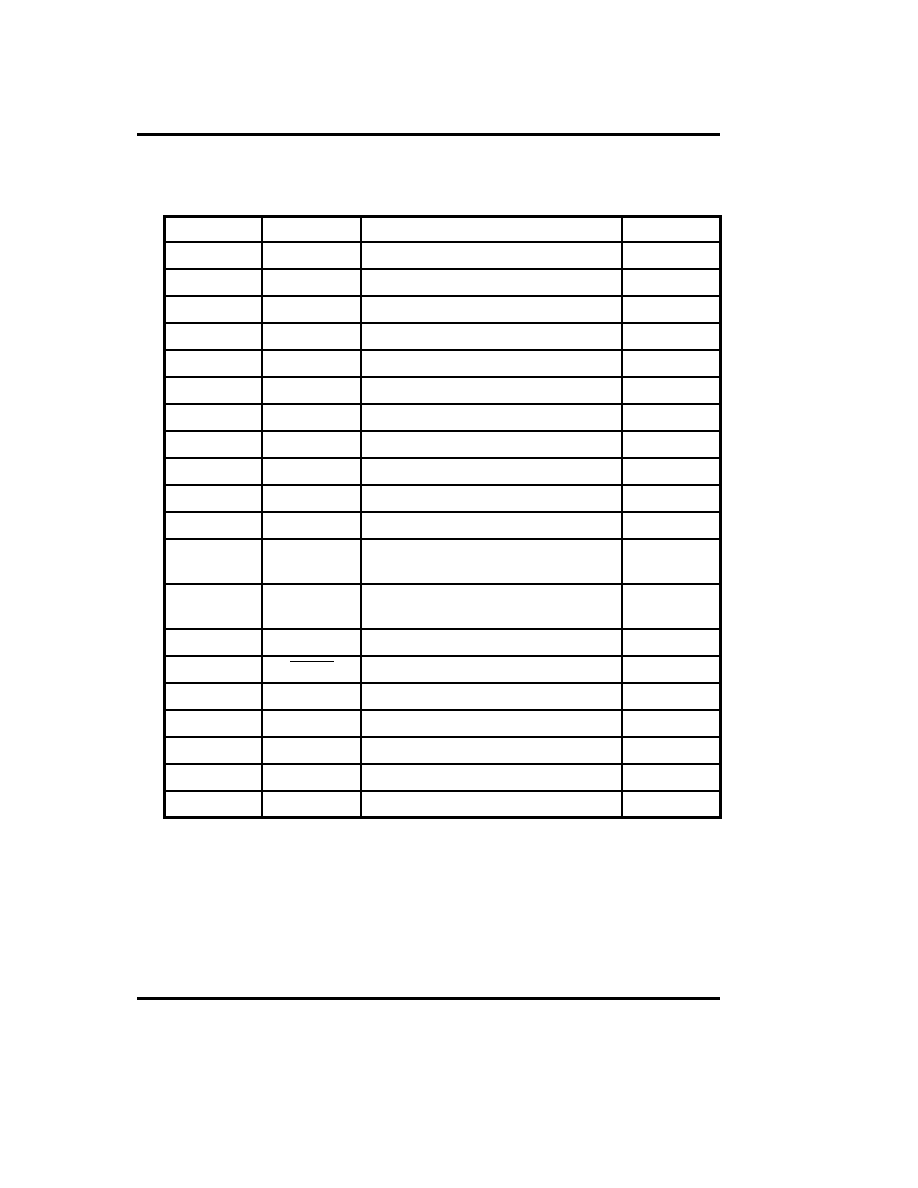

INSTRUCTION TABLE

The GMS300 series provides the following 43 basic instructions.

Category

1

2

3

Register to

Register

LAY

LYA

LAZ

Mnemonic

A

à

Y

Function

Y

à

A

A

à

0

S

S

S

ST

*1

4

5

6

RAM to

Register

LMA

LMAIY

LYM

M(X,Y)

à

A

M(X,Y)

à

A, Y

à

Y+1

Y

à

M(X,Y)

S

S

S

7

8

LAM

XMA

A

à

M(X,Y)

A

ä

M(X,Y)

S

S

9

10

11

Immediate

LYI i

LMIIY i

LXI n

Y

à

i

M(X,Y)

à

i, Y

à

Y+1

X

à

n

S

S

S

12

13

14

RAM Bit

Manipulatio

n

SEM n

REM n

TM n

M(n)

à

1

M(n)

à

0

TEST M(n) = 1

S

S

E

15

16

17

ROM

Address

BR a

CAL a

RTN

if ST = 1 then Branch

if ST = 1 then Subroutine call

Return from Subroutine

S

S

S

18

LPBI i

PB

à

i

S

19

20

21

Arithmetic

AM

SM

IM

A

à

A + M(X,Y)

A

à

M(X,Y) - A

A

à

M(X,Y) + 1

C

B

C

22

23

DM

IA

A

à

M(X,Y) - 1

A

à

A + 1

B

S

24

25

IY

DA

Y

à

Y + 1

A

à

A - 1

C

B

Chapter 3. Instruction

3 - 3

Category

26

27

28

Arithmetic

DY

EORM

NEGA

Mnemonic

Y

à

Y - 1

Function

A

à

A + M (X,Y)

A

à

A + 1

B

S

Z

ST

*1

29

30

Comparison

ALEM

ALEI i

TEST A

õ

M(X,Y)

TEST A

õ

i

E

E

31

32

MNEZ

YNEA

TEST M(X,Y)

ó

0

TEST Y

ó

A

N

N

33

34

YNEI i

KNEZ

TEST Y

ó

i

TEST K

ó

0

N

N

35

RNEZ

TEST R

ó

0

N

36

37

Input /

Output

LAK

LAR

A

à

K

A

à

R

S

S

38

39

SO

RO

Output(Y)

à

1

*2

Output(Y)

à

0

*2

S

S

40

41

Control

WDTR

STOP

Watch Dog Timer Reset

Stop operation

S

S

42

43

LPY

NOP

PMR

à

Y

No operation

S

S

Note) i = 0~f, n = 0~3, a = 6bit PC Address

*1 Column ST indicates conditions for changing status. Symbols have the following

meanings

S : On executing an instruction, status is unconditionally set.

C : Status is only set when carry or borrow has occurred in operation.

B : Status is only set when borrow has not occurred in operation.

E : Status is only set when equality is found in comparison.

N : Status is only set when equality is not found in comparison.

Z : Status is only set when the result is zero.

Chapter 3. Instruction

3 - 4

Value of X-reg

0 or 1

SO : D(Y)

à

1, RO : D(Y)

à

0

Operation

REMOUT port repeats

Ì

H

Ì

and

Ì

L

Ì

in pulse

frequency. (when PMR = 5, it is fixed at

Ì

H

Ì

)

SO : REMOUT (PMR)

à

1

RO : REMOUT (PMR)

à

0

Value of Y-reg

0~7

0 or 1

8

0 or 1

SO : D0 ~ D9

à

1 (High-Z)

R0 : D0 ~ D9

à

0

9

0 or 1

SO : R(Y-Ah)

à

1, RO : R(Y-Ah)

à

0

A ~ D

0 or 1

SO : R0 ~ R3

à

1, RO : R0~R3

à

0

E

0 or 1

SO : D0 ~ D9

à

1 (High-Z) R0~R3

à

1

R0 : D0 ~ D9

à

0

R0~R3

à

0

F

2 or 3

SO : D(8)

à

1, RO : D(8)

à

0

0

2 or 3

SO : D(9)

à

1, RO : D(9)

à

0

1

*2 Operation is settled by a value of Y-register.

Chapter 3. Instruction

3 - 5

DETAILS OF INSTRUCTION SYSTEM

All 43 basic instructions of the GMS300 Series are one by one described in detail

below.

Description Form

Each instruction is headlined with its mnemonic symbol according to the

instructions table given earlier.

Then, for quick reference, it is described with basic items as shown below. After

that, detailed comment follows.

· Items :

- Naming :

Full spelling of mnemonic symbol

- Status :

Check of status function

- Format :

Categorized into

é

to

ì

- Operand :

Omitted for Format

é

- Function

Chapter 3. Instruction

3 - 6

Detailed Description

(1) LAY

Naming :

Load Accumulator from Y-Register

Status :

Set

Format :

I

Function :

A

à

Y

<Comment>

Data of four bits in the Y-register is unconditionally transferred

to the accumulator. Data in the Y-register is left unchanged.

(2) LYA

Naming :

Load Y-register from Accumulator

Status :

Set

Format :

I

Function :

Y

à

A

<Comment>

Load Y-register from Accumulator

(3) LAZ

Naming :

Clear Accumulator

Status :

Set

Format :

I

Function :

A

à

0

<Comment>

Data in the accumulator is unconditionally reset to zero.

(4) LMA

Naming :

Load Memory from Accumulator

Status :

Set

Format :

I

Function :

M(X,Y)

à

A

<Comment>

Data of four bits from the accumulator is stored in the RAM

location addressed by the X-register and Y-register. Such data

is left unchanged.

(5) LMAIY

Naming :

Load Memory from Accumulator and Increment Y-Register

Status :

Set

Format :

I

Function :

M(X,Y)

à

A, Y

à

Y+1

<Comment>

Data of four bits from the accumulator is stored in the RAM

location addressed by the X-register and Y-register. Such data

is left unchanged.

Chapter 3. Instruction

3 - 7

(6) LYM

Naming :

Load Y-Register form Memory

Status :

Set

Format :

I

Function :

Y

à

M(X,Y)

<Comment>

Data from the RAM location addressed by the X-register and

Y-register is loaded into the Y-register. Data in the memory is

left unchanged.

(7) LAM

Naming :

Load Accumulator from Memory

Status :

Set

Format :

I

Function :

A

à

M(X,Y)

<Comment>

Data from the RAM location addressed by the X-register and

Y-register is loaded into the Y-register. Data in the memory is

left unchanged.

(8) XMA

Naming :

Exchanged Memory and Accumulator

Status :

Set

Format :

I

Function :

M(X,Y)

ä

A

<Comment>

Data from the memory addressed by X-register and Y-register

is exchanged with data from the accumulator. For example,

this instruction is useful to fetch a memory word into the

accumulator for operation and store current data from the

accumulator into the RAM. The accumulator can be restored

by another XMA instruction.

(9) LYI i

Naming :

Load Y-Register from Immediate

Status :

Set

Format :

ë

Operand :

Constant 0

õ

i

õ

15

Function :

Y

à

i

<Purpose>

To load a constant in Y-register. It is typically used to specify

Y-register in a particular RAM word address, to specify the

address of a selected output line, to set Y-register for

specifying a carrier signal outputted from OUT port, and to

initialize Y-register for loop control. The accumulator can be

restored by another XMA instruction.

<Comment>

Data of four bits from operand of instruction is transferred to

the Y-register.

Chapter 3. Instruction

3 - 8

(10) LMIIY i

Naming :

Load Memory from Immediate and Increment Y-Register

Status :

Set

Format :

ë

Operand :

Constant 0

õ

i

õ

15

Function :

M(X,Y)

à

i, Y

à

Y + 1

<Comment>

Data of four bits from operand of instruction is stored into the

RAM location addressed by the X-register and Y-register.

Then data in the Y-register is incremented by one.

(11) LXI n

Naming :

Load X-Register from Immediate

Status :

Set

Format :

ê

Operand :

X file address 0

õ

n

õ

3

Function :

X

à

n

<Comment>

A constant is loaded in X-register. It is used to set X-register in

an index of desired RAM page. Operand of 1 bit of command

is loaded in X-register.

(12) SEM n

Naming :

Set Memory Bit

Status :

Set

Format :

ê

Operand :

Bit address 0

õ

n

õ

3

Function :

M(X,Y,n)

à

1

<Comment>

Depending on the selection in operand of operand, one of four

bits is set as logic 1 in the RAM memory addressed in

accordance with the data of the X-register and Y-register.

(13) REM n

Naming :

Reset Memory Bit

Status :

Set

Format :

ê

Operand :

Bit address 0

õ

n

õ

3

Function :

M(X,Y,n)

à

0

<Comment>

Depending on the selection in operand of operand, one of four

bits is set as logic 0 in the RAM memory addressed in

accordance with the data of the X-register and Y-register.

Chapter 3. Instruction

3 - 9

(14) TM n

Naming :

Test Memory Bit

Status :

Comparison results to status

Format :

ê

Operand :

Bit address 0

õ

n

õ

3

Function :

M(X,Y,n)

à

1?

ST

à

1 when M(X,Y,n)=1, ST

à

0 when M(X,Y,n)=0

<Purpose>

A test is made to find if the selected memory bit is logic. 1

Status is set depending on the result.

(15) BR a

Naming :

Branch on status 1

Status :

Conditional depending on the status

Format :

ì

Operand :

Branch address a (Addr)

Function :

When ST =1 , PA

à

PB, PC

à

a(Addr)

When ST = 0, PC

à

PC + 1, ST

à

1

Note : PC indicates the next address in a fixed sequence that

is actually pseudo-random count.

<Purpose>

For some programs, normal sequential program execution can

be change.

A branch is conditionally implemented depending on the status

of results obtained by executing the previous instruction.

<Comment>

· Branch instruction is always conditional depending on the

status.

a. If the status is reset (logic 0), a branch instruction is not

rightly executed but the next instruction of the sequence is

executed.

b. If the status is set (logic 1), a branch instruction is executed

as follows.

· Branch is available in two types - short and long. The former

is for addressing in the current page and the latter for

addressing in the other page. Which type of branch to exeute

is decided according to the PB register. To execute a long

branch, data of the PB register should in advance be modified

to a desired page address through the LPBI instruction.

Chapter 3. Instruction

3 - 10

(16) CAL a

Naming :

Subroutine Call on status 1

Status :

Conditional depending on the status

Format :

ì

Operand :

Subroutine code address a(Addr)

Function :

When ST =1 , PC

à

a(Addr)

PA

à

PB

SR1

à

PC + 1,

PSR1

à

PA

SR2

à

SR1

PSR2

à

PSR1

SR3

à

SR2

PSR3

à

PSR2

When ST = 0 PC

à

PC + 1

PB

à

PS ST

à

1

Note : PC actually has pseudo-random count against the next

instruction.

<Comment>

· In a program, control is allowed to be transferred to a mutual

subroutine. Since a call instruction preserves the return

address, it is possible to call the subroutine from different

locations in a program, and the subroutine can return control

accurately to the address that is preserved by the use of the

call return instruction (RTN).

Such calling is always conditional depending on the status.

a. If the status is reset, call is not executed.

b. If the status is set, call is rightly executed.

The subroutine stack (SR) of three levels enables a subroutine to

be manipulated on three levels. Besides, a long call (to call

another page) can be executed on any level.

· For a long call, an LPBI instruction should be executed before

the CAL. When LPBI is omitted (and when PA=PB), a short

call (calling in the same page) is executed.

Chapter 3. Instruction

3 - 11

(17) RTN

Naming :

Return from Subroutine

Status :

Set

Format :

é

Function :

PC

à

SR1

PA, PB

à

PSR1

SR1

à

SR2

PSR1

à

PSR2

SR2

à

SR3

PSR2

à

PSR3

SR3

à

SR3

PSR3

à

PSR2

ST

à

1

<Purpose>

Control is returned from the called subroutine to the calling

program.

<Comment>

Control is returned to its home routine by transferring to the PC

the data of the return address that has been saved in the stack

register (SR1).

At the same time, data of the page stack register (PSR1) is

transferred to the PA and PB.

(18) LPBI i

Naming :

Load Page Buffer Register from Immediate

Status :

Set

Format :

ë

Operand :

ROM page address 0

õ

i

õ

15

Function :

PB

à

i

<Purpose>

A new ROM page address is loaded into the page buffer

register (PB).

This loading is necessary for a long branch or call instruction.

<Comment>

The PB register is loaded together with three bits from 4 bit

operand.

(19) AM

Naming :

Add Accumulator to Memory and Status 1 on Carry

Status :

Carry to status

Format :

é

Function :

A

à

M(X,Y)+A, ST

à

1(when total>15),

ST

à

0 (when total

õ

15)

<Comment>

Data in the memory location addressed by the X and Y-register

is added to data of the accumulator. Results are stored in the

accumulator. Carry data as results is transferred to status.

When the total is more than 15, a carry is caused to put

Ì

1

Ì

in the status. Data in the memory is not changed.

Chapter 3. Instruction

3 - 12

(20) SM

Naming :

Subtract Accumulator to Memory and Status 1 Not Borrow

Status :

Carry to status

Format :

é

Function :

A

à

M(X,Y) - A

ST

à

1(when A

õ

M(X,Y))

ST

à

0(when A > M(X,Y))

<Comment>

Data of the accumulator is, through a 2`s complemental

addition, subtracted from the memory word addressed by the

Y-register. Results are stored in the accumulator. If data of

the accumulator is less than or equal to the memory word, the

status is set to indicate that a borrow is not caused.

If more than the memory word, a borrow occurs to reset the

status to

Ì

0

Ì

.

(21) IM

Naming :

Increment Memory and Status 1 on Carry

Status :

Carry to status

Format :

é

Function :

A

à

M(X,Y) + 1

ST

à

1(when M(X,Y)

ö

15)

ST

à

0(when M(X,Y) < 15)

<Comment>

Data of the memory addressed by the X and Y-register is

fetched. Adding 1 to this word, results are stored in the

accumulator. Carry data as results is transferred to the status.

When the total is more than 15, the status is set. The memory

is left unchanged.

(22) DM

Naming :

Decrement Memory and Status 1 on Not Borrow

Status :

Carry to status

Format :

é

Function :

A

à

M(X,Y) - 1

ST

à

1(when M(X,Y)

ö

1)

ST

à

0 (when M(X,Y) = 0)

<Comment>

Data of the memory addressed by the X and Y-register is

fetched, and one is subtracted from this word (addition of Fh)>

Results are stored in the accumulator. Carry data as results is

transferred to the status. If the data is more than or equal to

one, the status is set to indicate that no borrow is caused. The

memory is left unchanged.

Chapter 3. Instruction

3 - 13

(23) IA

Naming :

Increment Accumulator

Status :

Set

Format :

é

Function :

A

à

A+1

<Comment>

Data of the accumulator is incremented by one. Results are

returned to the accumulator.

A carry is not allowed to have effect upon the status.

(24) IY

Naming :

Increment Y-Register and Status 1 on Carry

Status :

Carry to status

Format :

é

Function :

Y

à

Y + 1

ST

à

1 (when Y = 15)

ST

à

0 (when Y < 15)

<Comment>

Data of the Y-register is incremented by one and results are

returned to the Y-register.

Carry data as results is transferred to the status. When the

total is more than 15, the status is set.

(25) DA

Naming :

Decrement Accumulator and Status 1 on Borrow

Status :

Carry to status

Format :

é

Function :

A

à

A - 1

ST

à

1(when A

ö

1)

ST

à

0 (when A = 0)

<Comment>

Data of the accumulator is decremented by one. As a result

(by addition of Fh), if a borrow is caused, the status is reset to

Ì

0

Ì

by logic. If the data is more than one, no borrow occurs

and thus the status is set to

Ì

1

Ì

.

Chapter 3. Instruction

3 - 14

(26) DY

Naming :

Decrement Y-Register and Status 1 on Not Borrow

Status :

Carry to status

Format :

é

Function :

Y

à

Y -1

ST

à

1 (when Y

ö

1)

ST

à

0 (when Y = 0)

<Purpose>

Data of the Y-register is decremented by one.

<Comment>

Data of the Y-register is decremented by one by addition of

minus 1 (Fh).

Carry data as results is transferred to the status. When the

results is equal to 15, the status is set to indicate that no

borrow has not occurred.

(27) EORM

Naming :

Exclusive or Memory and Accumulator

Status :

Set

Format :

é

Function :

A

à

M(X,Y) + A

<Comment>

Data of the accumulator is, through a Exclusive OR,

subtracted from the memory word addressed by X and Y-

register. Results are stored into the accumulator.

(28) NEGA

Naming :

Negate Accumulator and Status 1 on Zero

Status :

Carry to status

Format :

é

Function :

A

à

A + 1

ST

à

1(when A = 0)

ST

à

0 (when A != 0)

<Purpose>

The 2`s complement of a word in the accumulator is obtained.

<Comment>

The 2`s complement in the accumulator is calculated by adding

one to the 1`s complement in the accumulator. Results are

stored into the accumulator. Carry data is transferred to the

status. When data of the accumulator is zero, a carry is

caused to set the status to

Ì

1

Ì

.

Chapter 3. Instruction

3 - 15

(29) ALEM

Naming :

Accumulator Less Equal Memory

Status :

Carry to status

Format :

é

Function :

A

õ

M(X,Y)

ST

à

1 (when A

õ

M(X,Y))

ST

à

0 (when A > M(X,Y))

<Comment>

Data of the accumulator is, through a complemental addition,

subtracted from data in the memory location addressed by the

X and Y-register. Carry data obtained is transferred to the

status. When the status is

Ì

1

Ì

, it indicates that the data of

the accumulator is less than or equal to the data of the

memory word. Neither of those data is not changed.

(30) ALEI

Naming :

Accumulator Less Equal Immediate

Status :

Carry to status

Format :

ë

Function :

A

õ

i

ST

à

1 (when A

õ

i)

ST

à

0 (when A > i)

<Purpose>

Data of the accumulator and the constant are arithmetically

compared.

<Comment>

Data of the accumulator is, through a complemental addition,

subtracted from the constant that exists in 4bit operand. Carry

data obtained is transferred to the status. The status is set

when the accumulator value is less than or equal to the

constant. Data of the accumulator is left unchanged.

(31) MNEZ

Naming :

Memory Not Equal Zero

Status :

Comparison results to status

Format :

é

Function :

M(X,Y)

ó

0

ST

à

1(when M(X,Y)

ó

0)

ST

à

0 (when M(X,Y) = 0)

<Purpose>

A memory word is compared with zero.

<Comment>

Data in the memory addressed by the X and Y-register is

logically compared with zero. Comparison data is thransferred

to the status. Unless it is zero, the status is set.

Chapter 3. Instruction

3 - 16

(32) YNEA

Naming :

Y-Register Not Equal Accumulator

Status :

Comparison results to status

Format :

é

Function :

Y

ó

A

ST

à

1 (when Y

ó

A)

ST

à

0 (when Y = A)

<Purpose>

Data of Y-register and accumulator are compared to check if

they are not equal.

<Comment>

Data of the Y-register and accumulator are logically compared.

Results are transferred to the status. Unless they are equal,

the status is set.

(33) YNEI

Naming :

Y-Register Not Equal Immediate

Status :

Comparison results to status

Format :

ë

Operand :

Constant 0

õ

i

õ

15

Function :

Y

ó

i

ST

à

1 (when Y

ó

i)

ST

à

0 (when Y = i)

<Comment>

The constant of the Y-register is logically compared with 4bit

operand. Results are transferred to the status. Unless the

operand is equal to the constant, the status is set.

(34) KNEZ

Naming :

K Not Equal Zero

Status :

The status is set only when not equal

Format :

é

Function :

When K

ó

0, ST

à

1

<Purpose>

A test is made to check if K is not zero.

<Comment>

Data on K are compared with zero. Results are transferred to

the status. For input data not equal to zero, the status is set.

(35) RNEZ

Naming :

R Not Equal Zero

Status :

The status is set only when not equal

Format :

é

Function :

When R

ó

0, ST

à

1

<Purpose>

A test is made to check if R is not zero.

<Comment>

Data on R are compared with zero. Results are transferred to

the status. For input data not equal to zero, the status is set.

Chapter 3. Instruction

3 - 17

(36) LAK

Naming :

Load Accumulator from K

Status :

Set

Format :

é

Function :

A

à

K

<Comment>

Data on K are transferred to the accumulator

(37) LAR

Naming :

Load Accumulator from R

Status :

Set

Format :

é

Function :

A

à

R

<Comment>

Data on R are transferred to the accumulator

(38) SO

Naming :

Set Output Register Latch

Status :

Set

Format :

é

Function :

D(Y)

à

1

0

õ

Y

õ

7

REMOUT

à

1(PMR=5)

Y = 8

D0~D9

à

1 (High-Z)

Y = 9

R(Y)

à

1

Ah

õ

Y

õ

Dh

R

à

1

Y = Eh

D0~D9, R

à

1

Y = Fh

<Purpose>

A single D output line is set to logic 1, if data of Y-register is

between 0 to 7.

Carrier frequency come out from REMOUT port, if data of

Y-register is 8.

All D output line is set to logic 1, if data of Y-register is 9.

It is no operation, if data of Y-register between 10 to 15.

When Y is between Ah and Dh, one of R output lines is set at

logic 1.

When Y is Eh, the output of R is set at logic 1.

When Y is Fh, the output D0~D9 and R are set at logic 1.

<Comment>

Data of Y-register is between 0 to 7, selects appropriate D

output.

Data of Y-register is 8, selects REMOUT port.

Data of Y-register is 9, selects all D port.

Data in Y-register, when between Ah and Dh, selects an

appropriate R output (R0~R3).

Data in Y-register, when it is Eh, selects all of R0~R3.

Data in Y-register, when it is Fh, selects all of D0~D9 and

R0~R3.

Chapter 3. Instruction

3 - 18

(39) RO

Naming :

Reset Output Register Latch

Status :

Set

Format :

é

Function :

D(Y)

à

0

0

õ

Y

õ

7

REMOUT

à

0

Y = 8

D0~D9

à

0

Y = 9

R(Y)

à

0

Ah

õ

Y

õ

Dh

R

à

0

Y = Eh

D0~D9, R

à

0

Y = Fh

<Purpose>

A single D output line is set to logic 0, if data of Y-register is

between 0 to 9.

REMOUT port is set to logic 0, if data of Y-register is 9.

All D output line is set to logic 0, if data of Y-register is 9.

When Y is between Ah and Dh, one of R output lines is set at

logic 0.

When Y is Eh, the output of R is set at logic 0

When Y is Fh, the output D0~D9 and R are set at logic 1.

<Comment>

Data of Y-register is between 0 to 7, selects appropriate D

output.

Data of Y-register is 8, selects REMOUT port.

Data of Y-register is 9, selects D port.

Data in Y-register, when between Ah and Dh, selects an

appropriate R output (R0~R3).

Data in Y-register, when it is Eh, selects all of R0~R3.

Data in Y-register, when it is Fh, selects all of D0~D9 and

R0~R3.

(40) WDTR

Naming :

Watch Dog Timer Reset

Status :

Set

Format :

é

Function :

Reset Watch Dog Timer (WDT)

<Purpose>

Normally, you should reset this counter before overflowed

counter for dc watch dog timer. this instruction controls this

reset signal.

Chapter 3. Instruction

3 - 19

(41) STOP

Naming :

STOP

Status :

Set

Format :

é

Function :

Operate the stop function

<Purpose>

Stopped oscillator, and little current.

(See 1-12 page, STOP function.)

(42) LPY

Naming :

Pulse Mode Set

Status :

Set

Format :

é

Function :

PMR

à

Y

<Comment>

Selects a pulse signal outputted from REMOUT port.

(43) NOP

Naming :

No Operation

Status :

Set

Format :

é

Function :

No operation

Chapter 3. Instruction

INTRODUCTION

1

ARCHITECTURE

2

INSTRUCTION

3

EVALUATION BOARD

4

SOFTWARE

5

APPENDIX

6

4 - 1

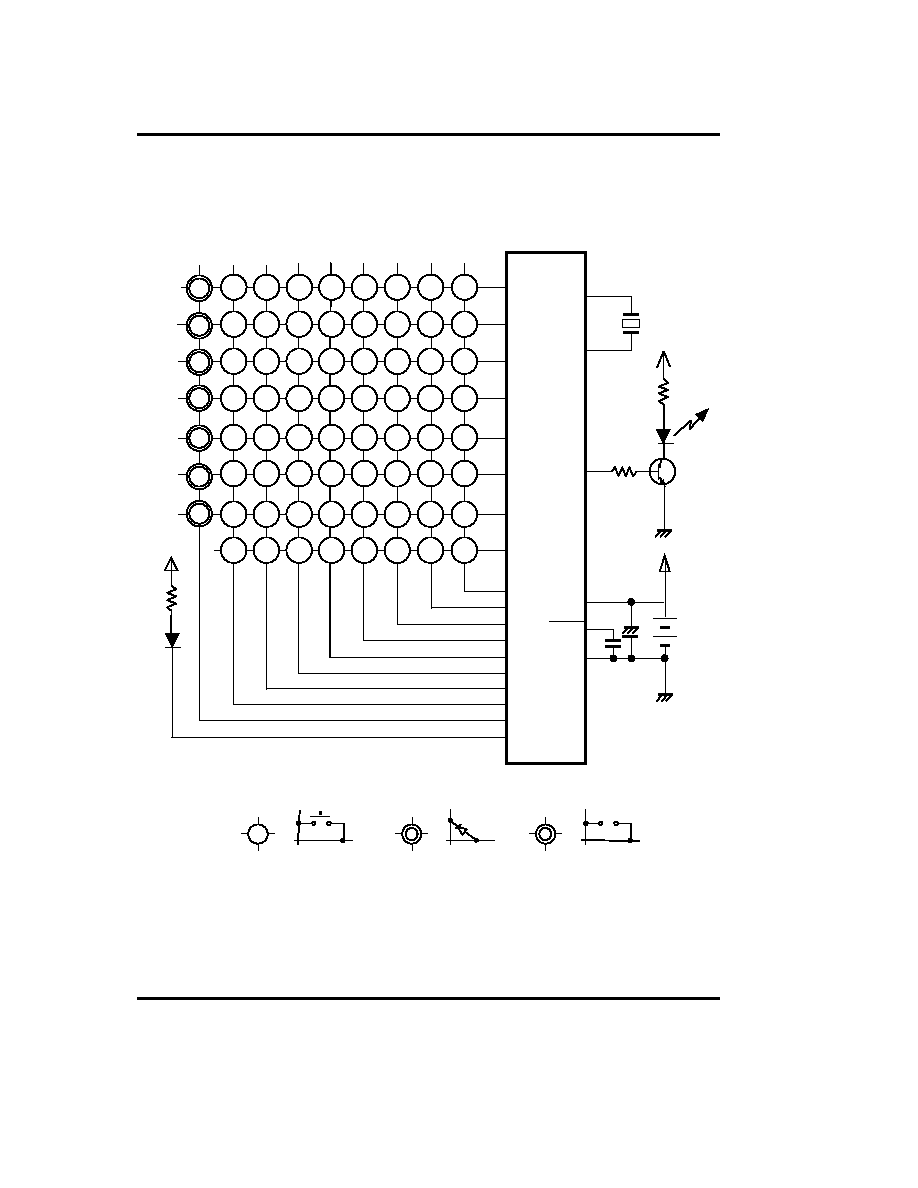

Chapter 4. Evaluation Board

CHAPTER 4. Evaluation Board

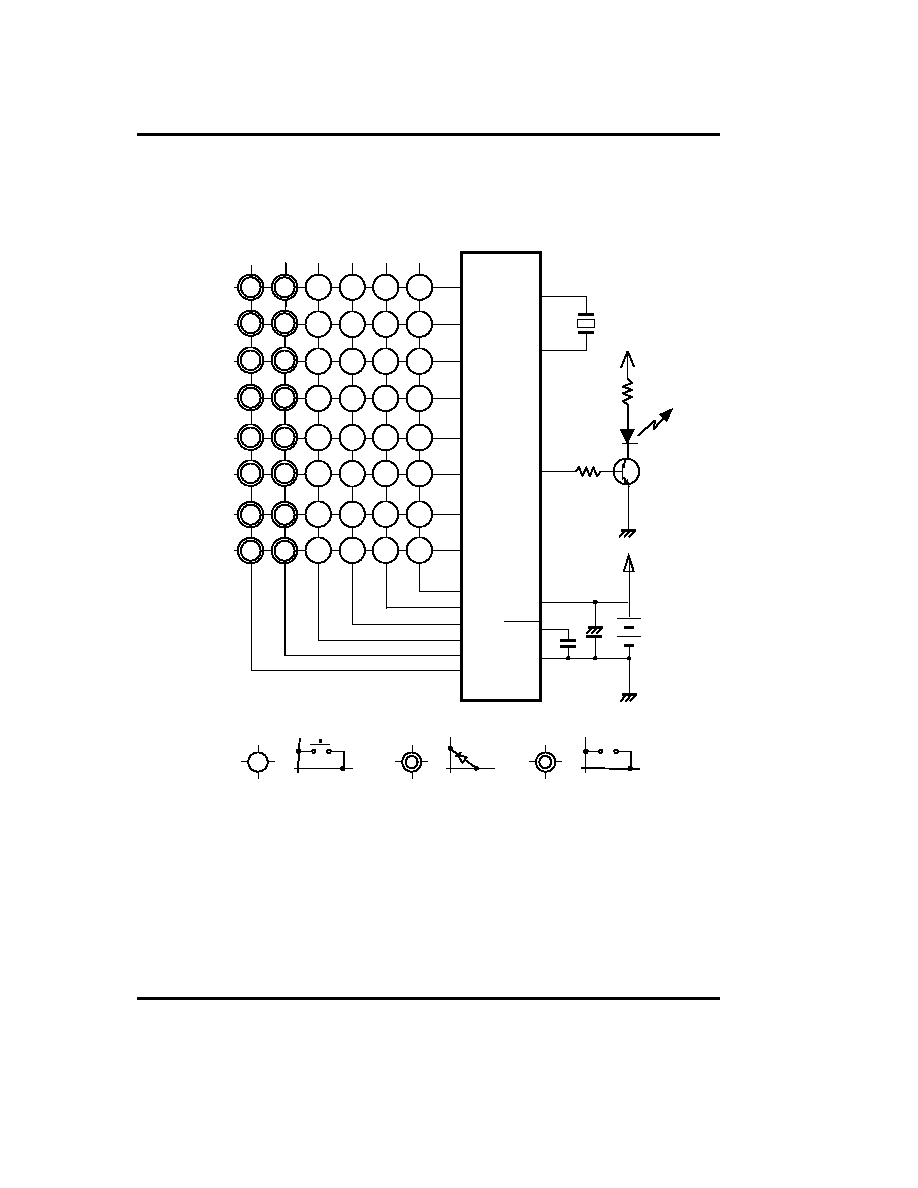

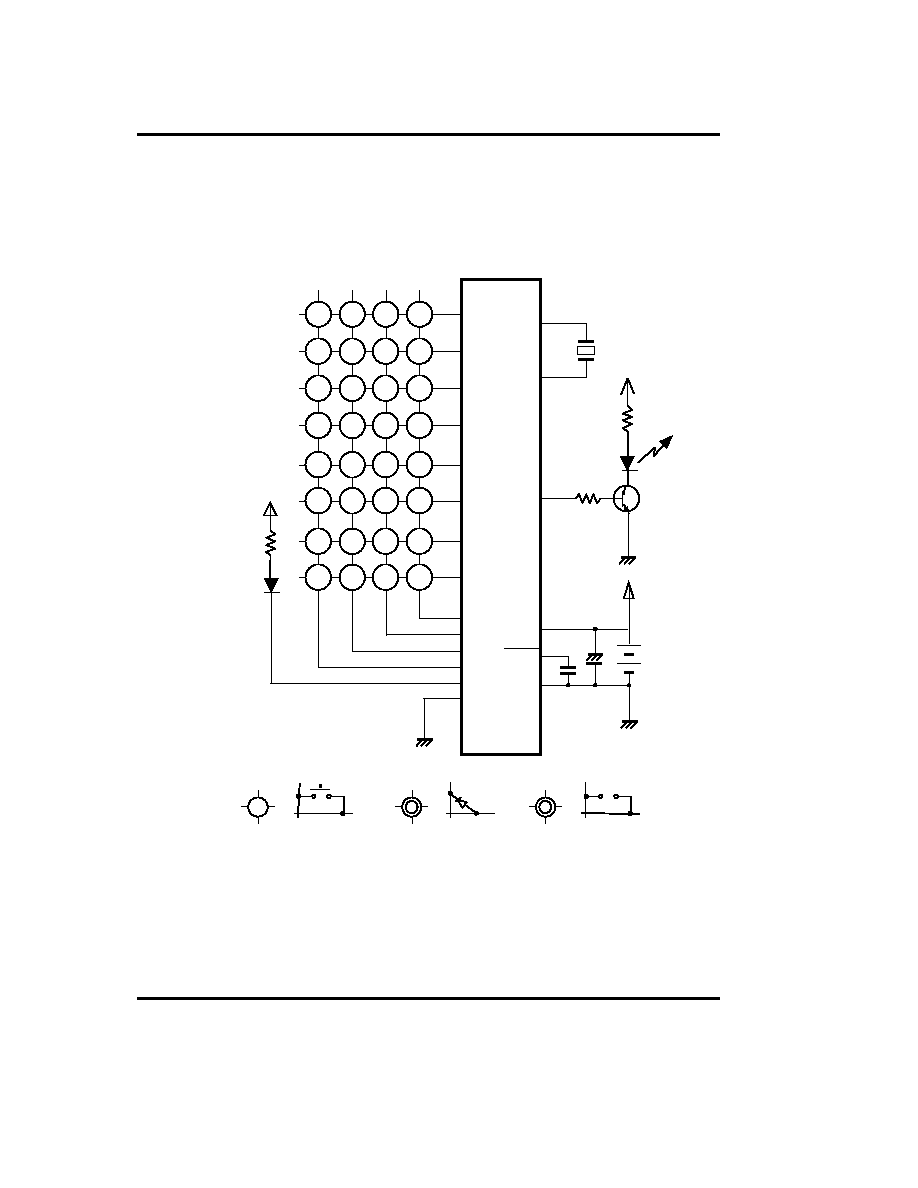

OUTLINE

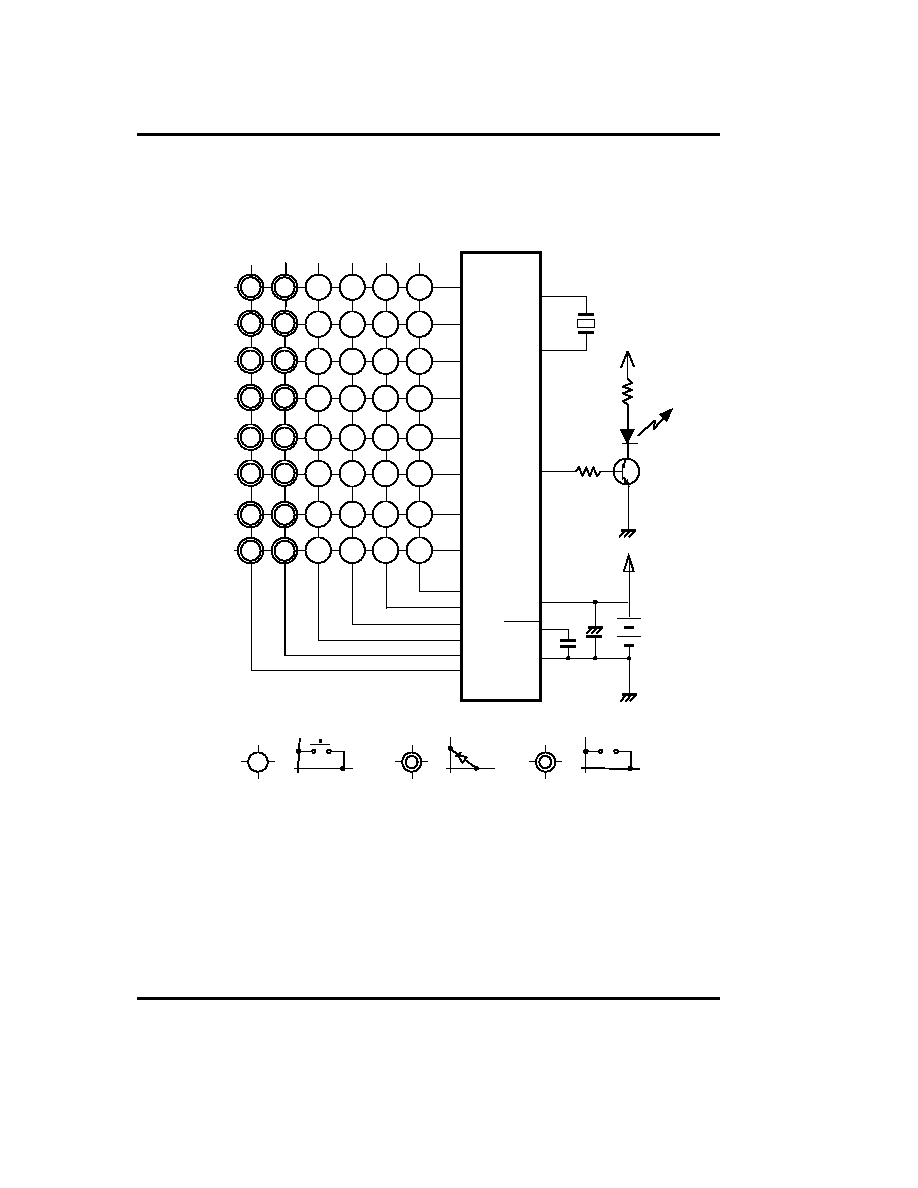

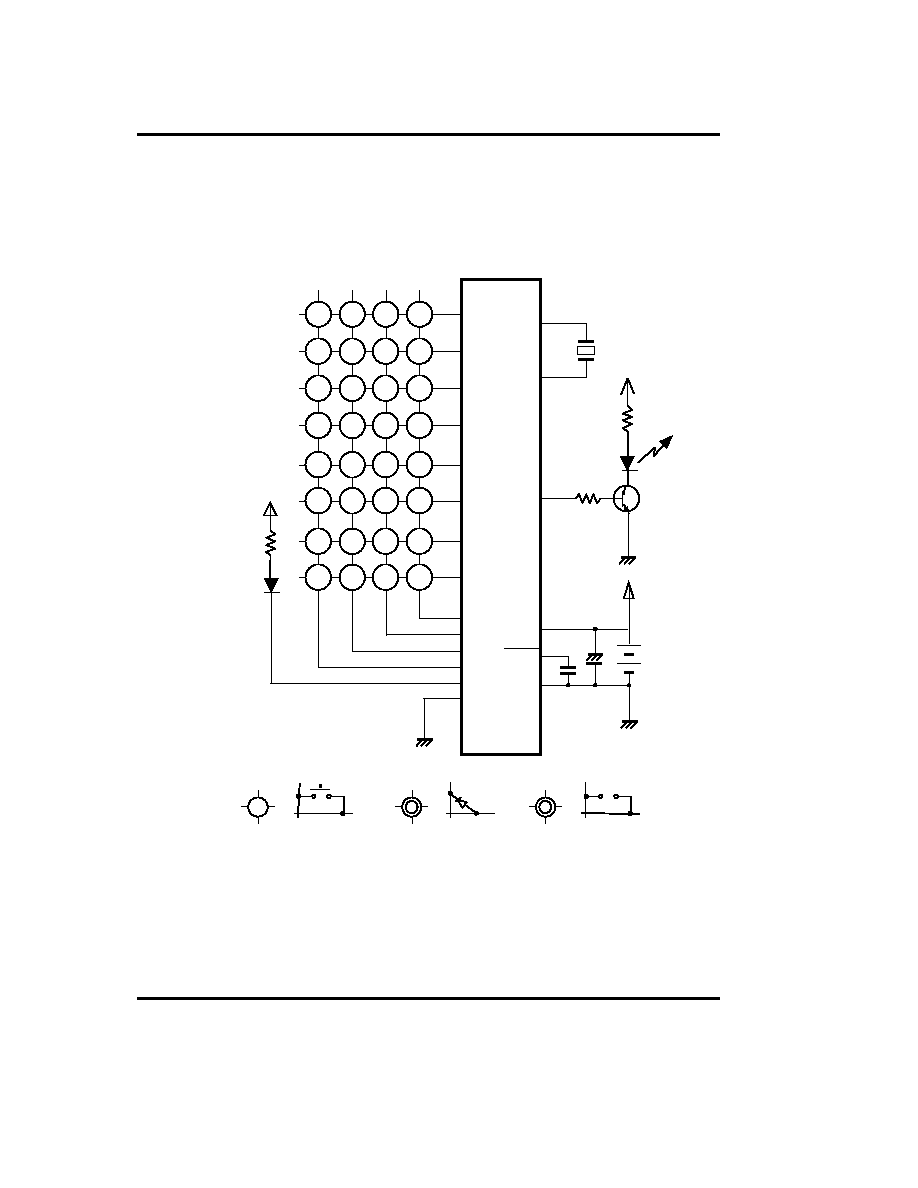

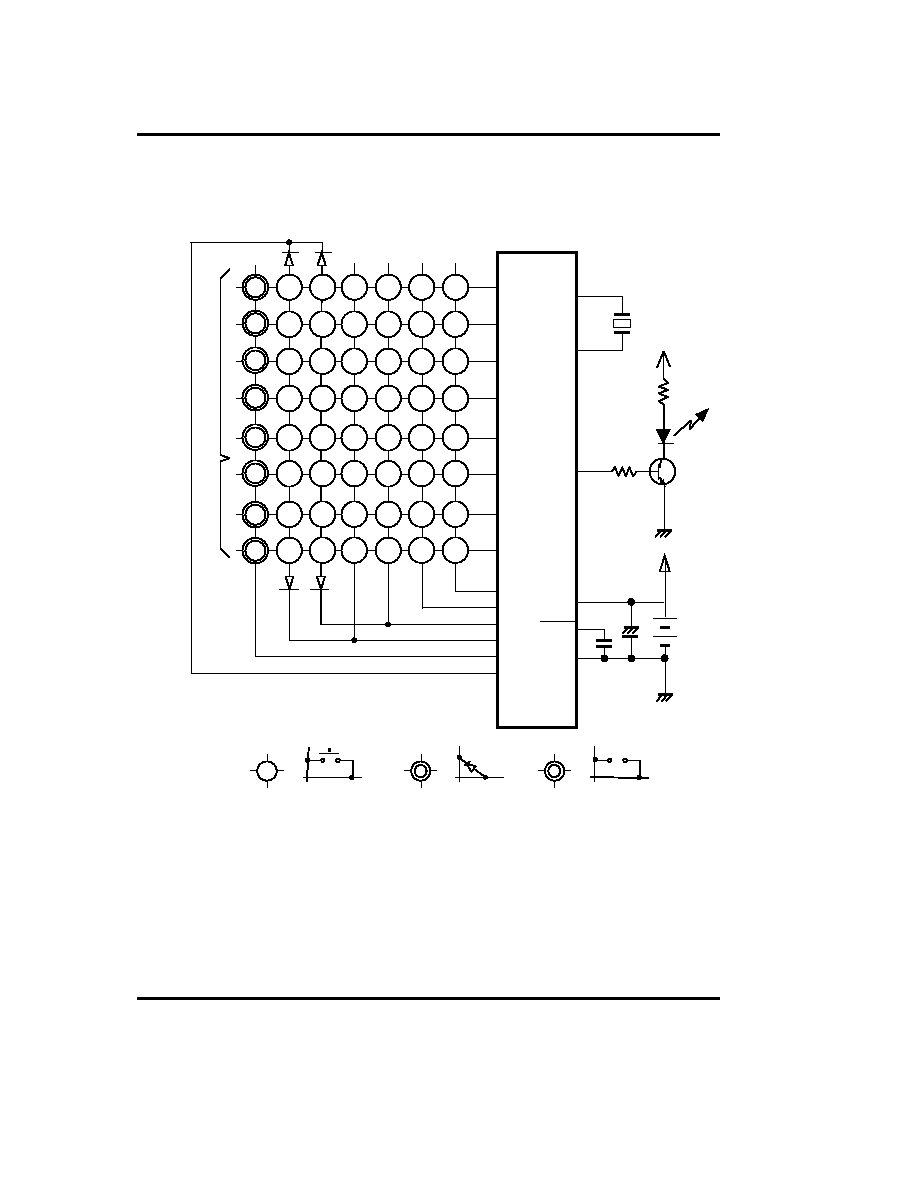

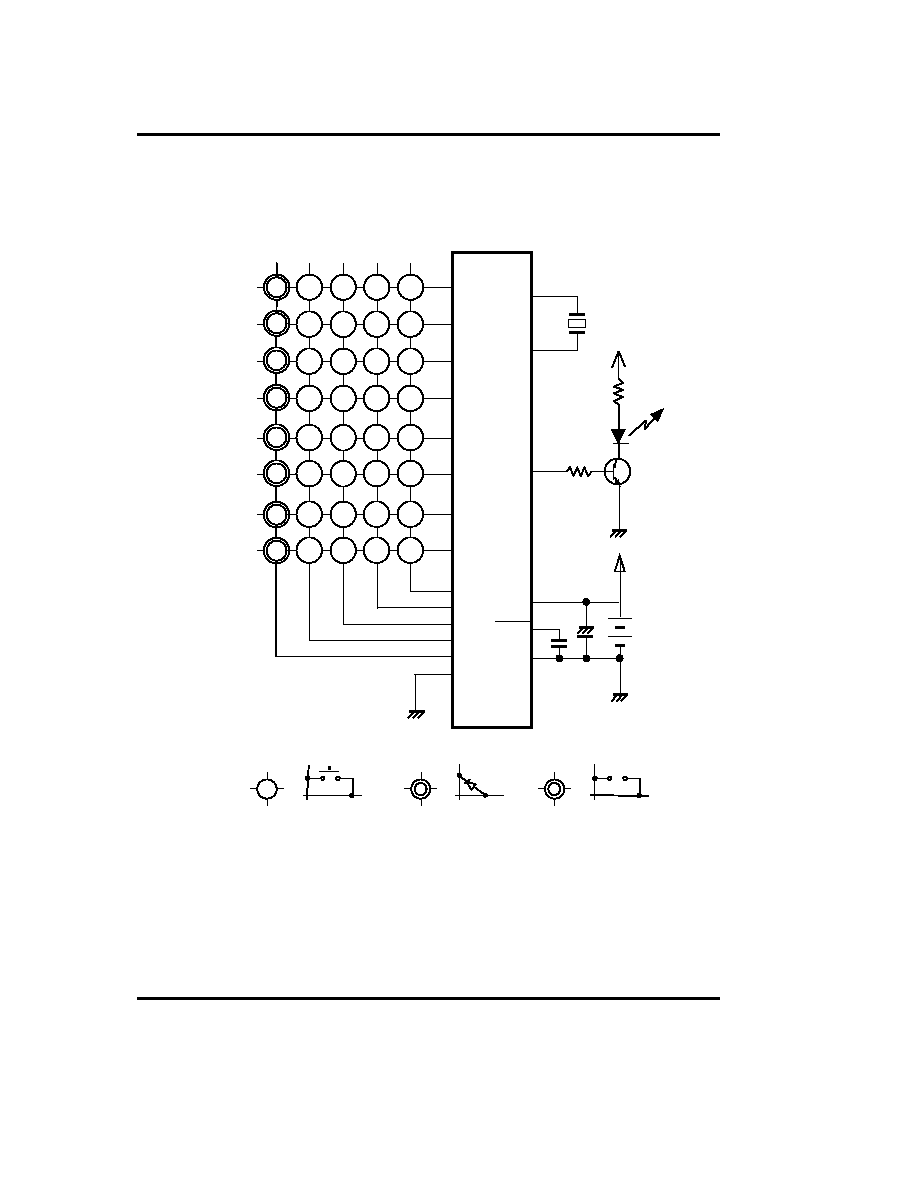

The GMS 30000 EVA is an evaluation board for GMS300 series, 4-bit, 1-chip

microcomputer. It is designed to evaluate and confirm the operations of the

application system in the nearest possible form of final products while it is under

development.

The major features are as follows :

· The GMS 30000 EVA is used for the evaluation chip.

· The board is connected to the application system through an connection

cable (DIP24).

· EPROM of 2764, 27128, and 27256 are used for the program memory.

· The instruction system and I/O specifications are basically the same as

those of the GMS300 series.

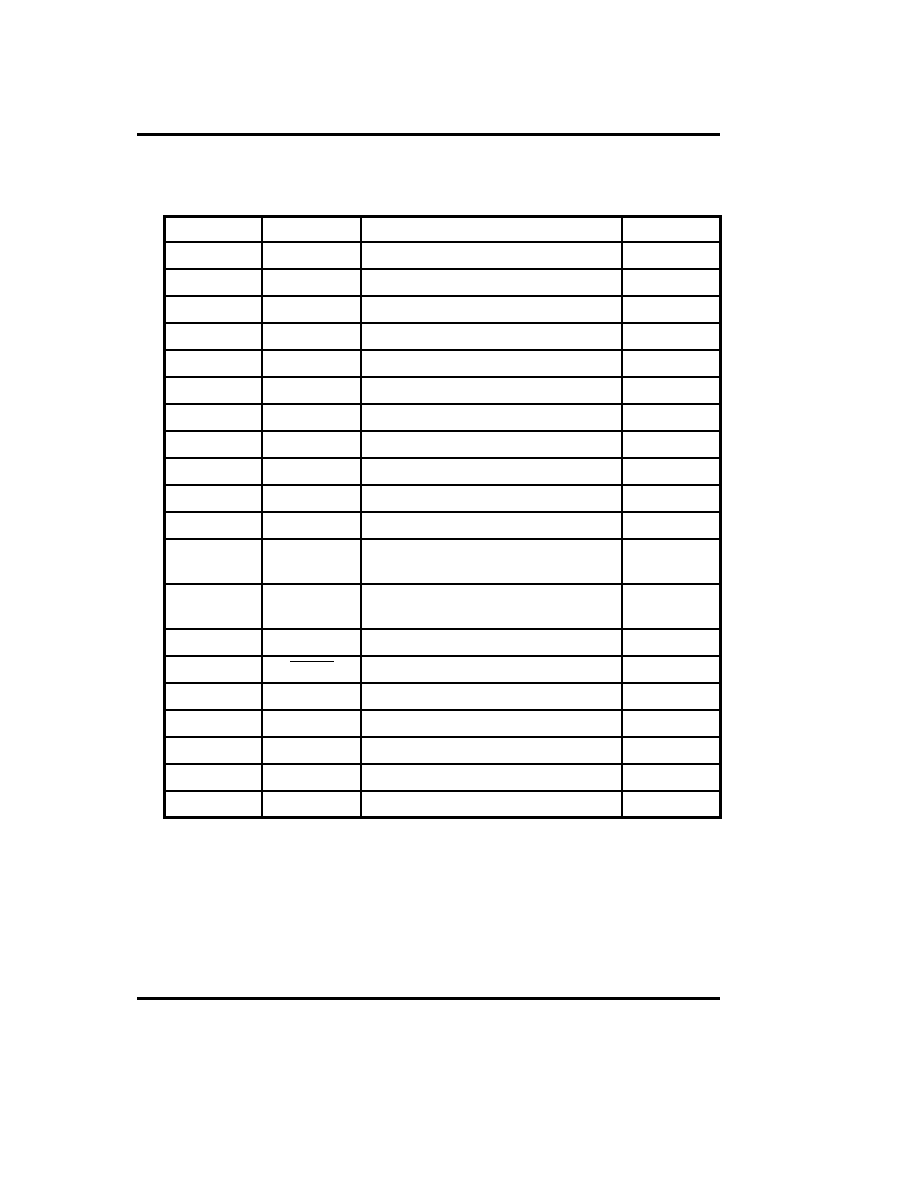

Product Specifications

· GMS 30000 EVA board module

Dimensions

64

Ø

82 (mm)

Supply Voltage

2.5 ~ 5.5 (V)

Operating temperature 0~50 (

Î

)

· Connection cable

DIP 24 cable

4 - 2

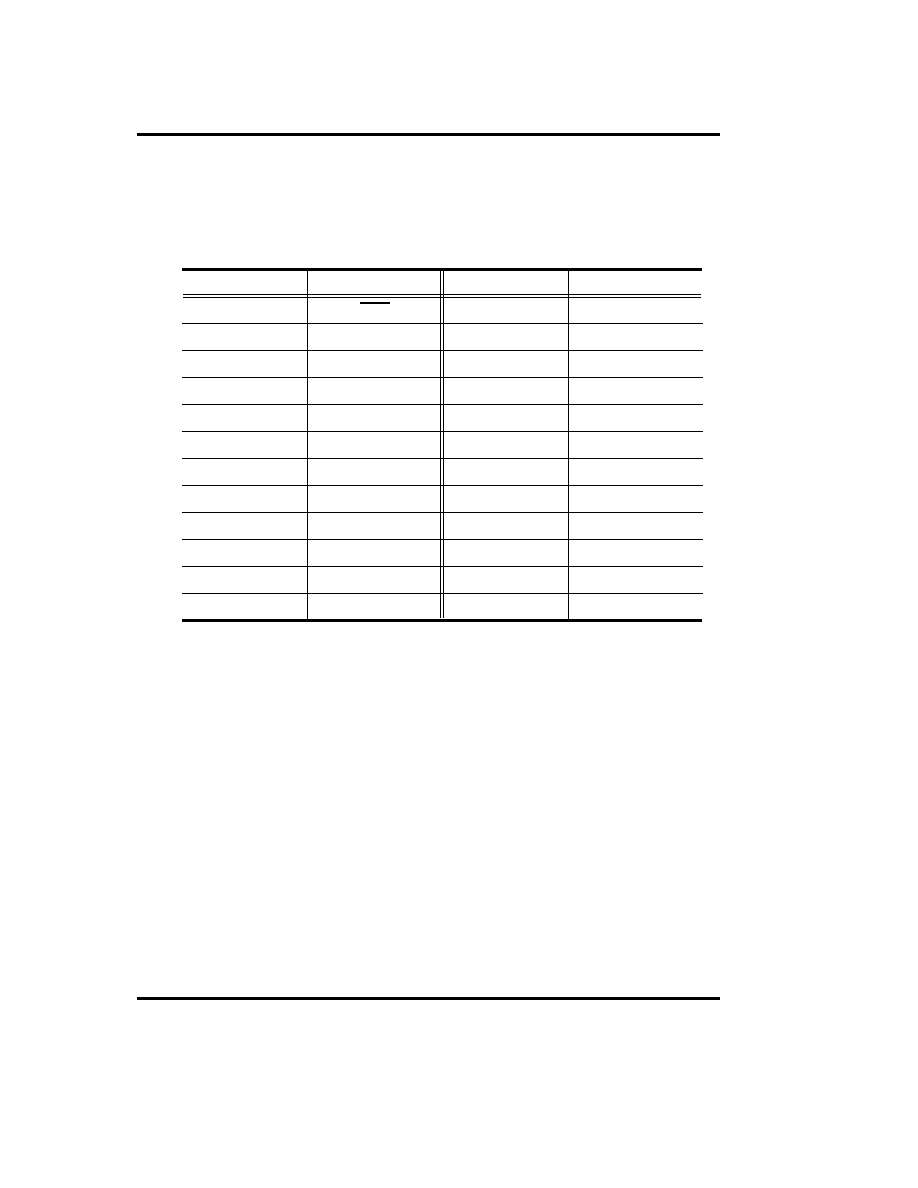

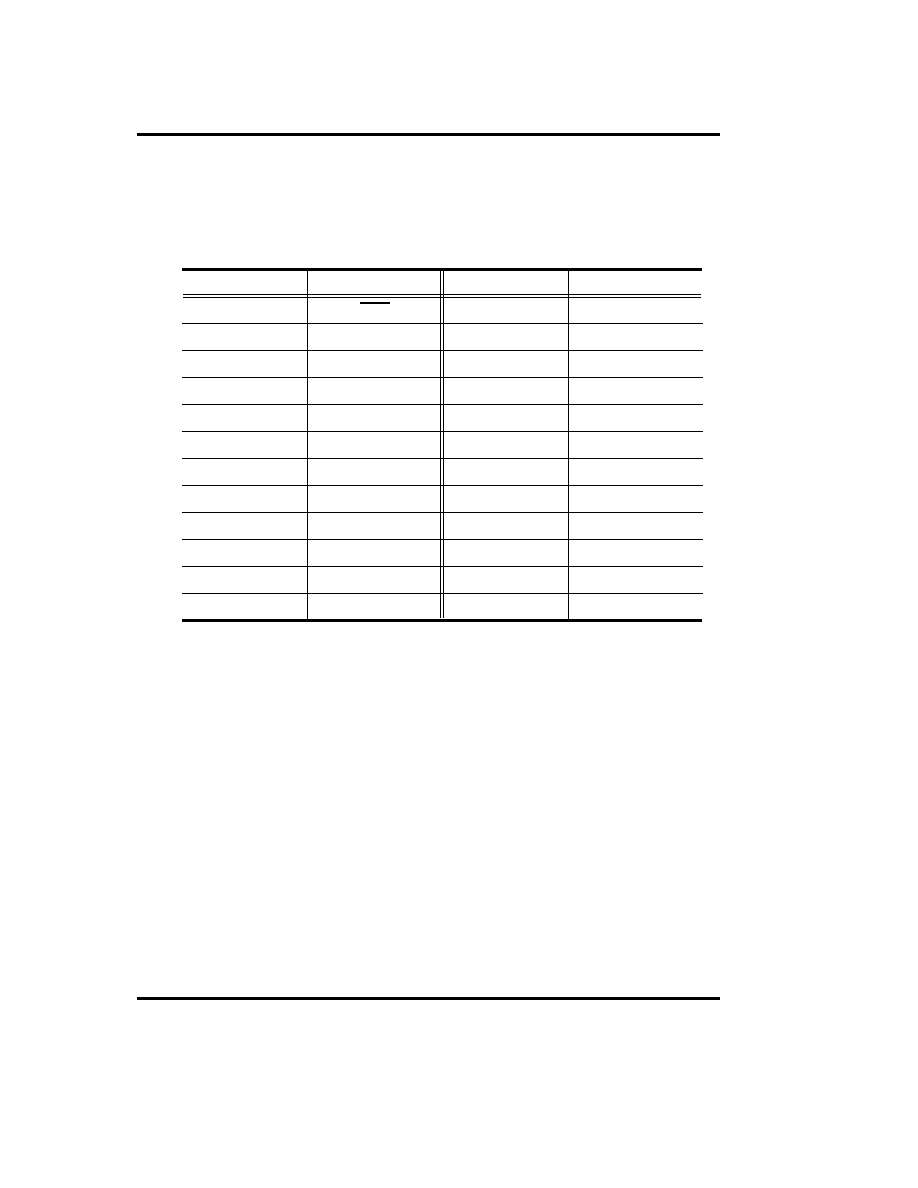

Connection

Perform emulation with the following connectors.

[User] Connection socket

The cable for the target system is connected.

Pin No.

1

Signal

Reset

Pin No.

13

Signal

D9

2

GND

14

D1

3

R0

15

D2

4

R1

16

D3

5

R2

17

D4

6

R3

18

D5

7

K0

19

D6

8

K1

20

D7

9

K2

21

Remout

10

K3

22

OSC2

11

D0

23

OSC1

12

D8

24

VDD

[M1] Monitor pin

Operations inside the GMS 30000 EVA can be monitored. Signals that can be

monitored are as follows.

AC0~AC3, X0, X1, Y0~Y3, REMDATA, CK2, CK5, WDTR, GND

[M2] Oscillation monitoring pin

The oscillation output signal can be monitored.

[T1] D8 output monitoring pin

The D8 output signal can be monitored.

[T2] D9 output monitoring pin

The D9 output signal can be monitored.

Chapter 4. Evaluation Board

4 - 3

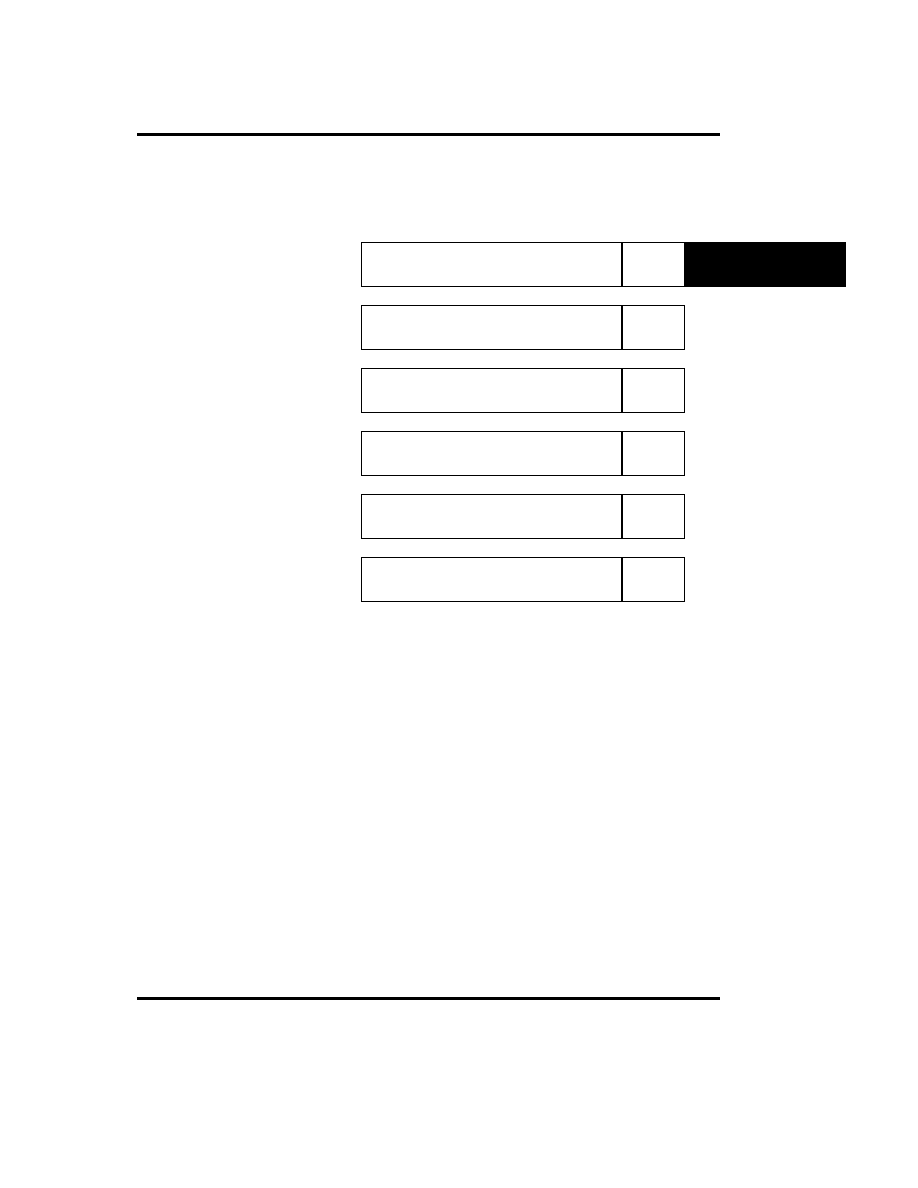

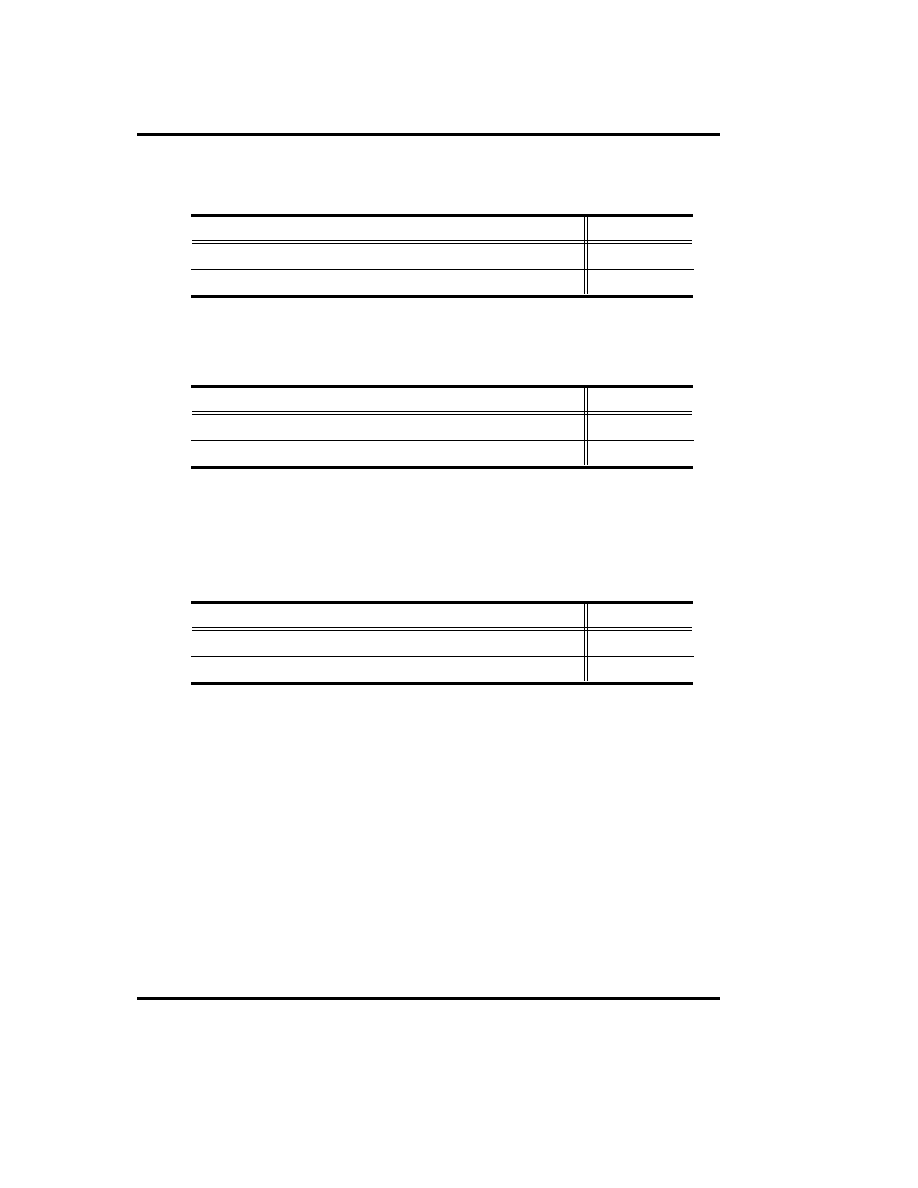

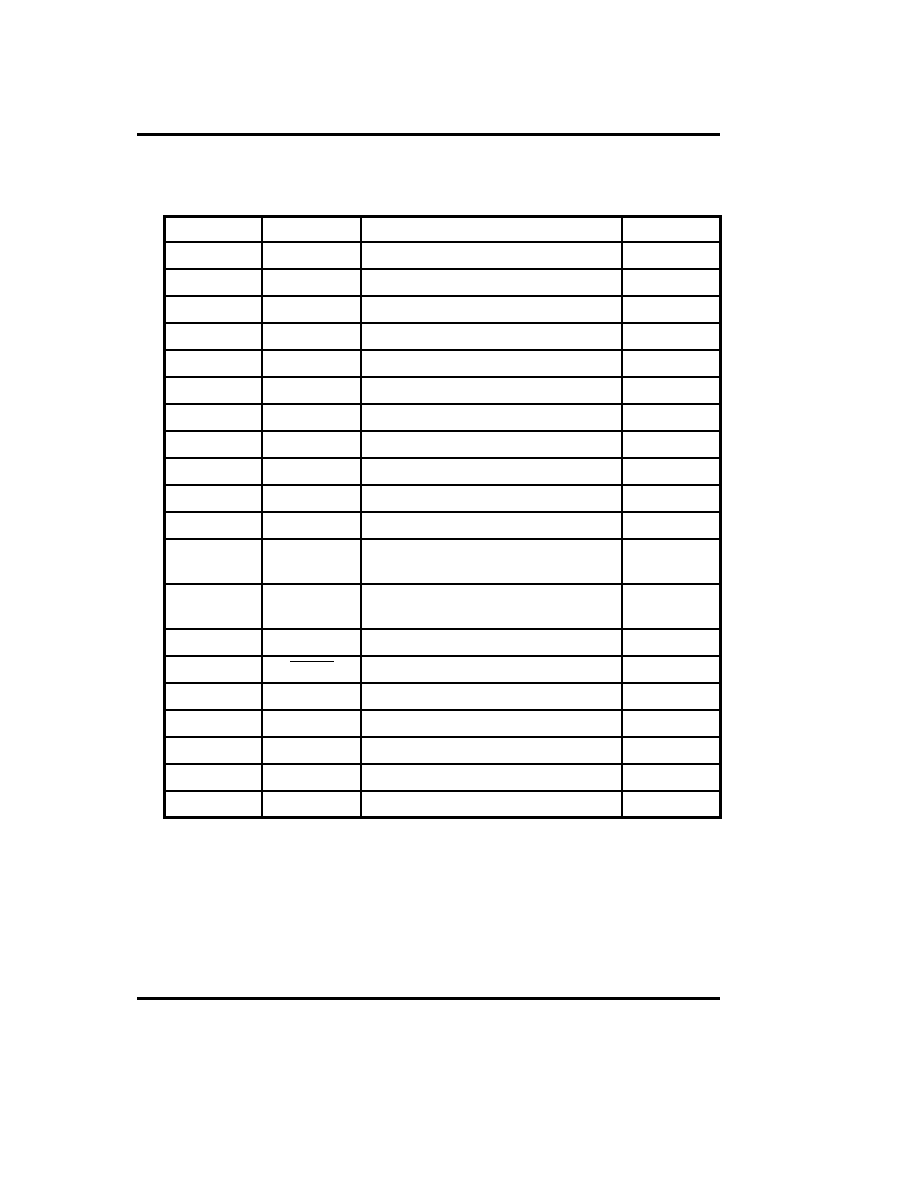

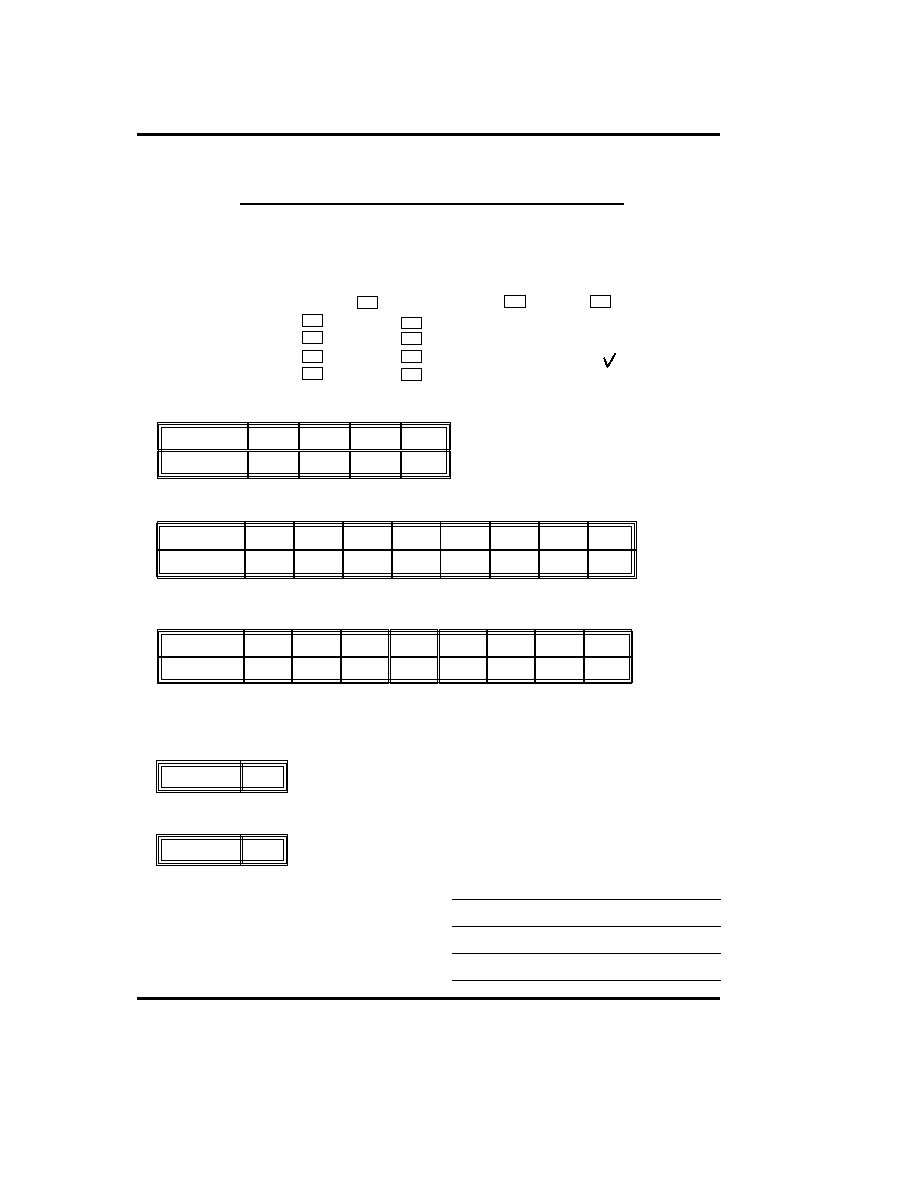

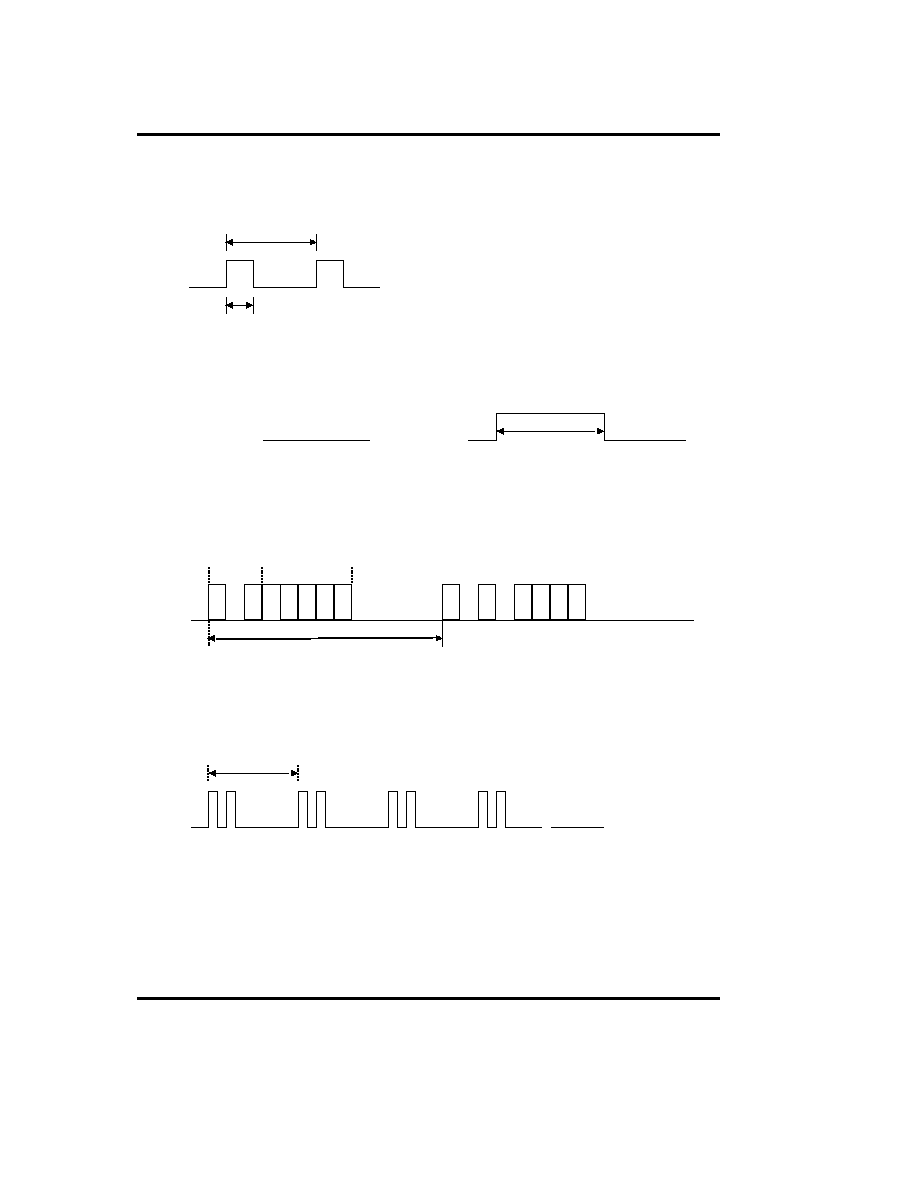

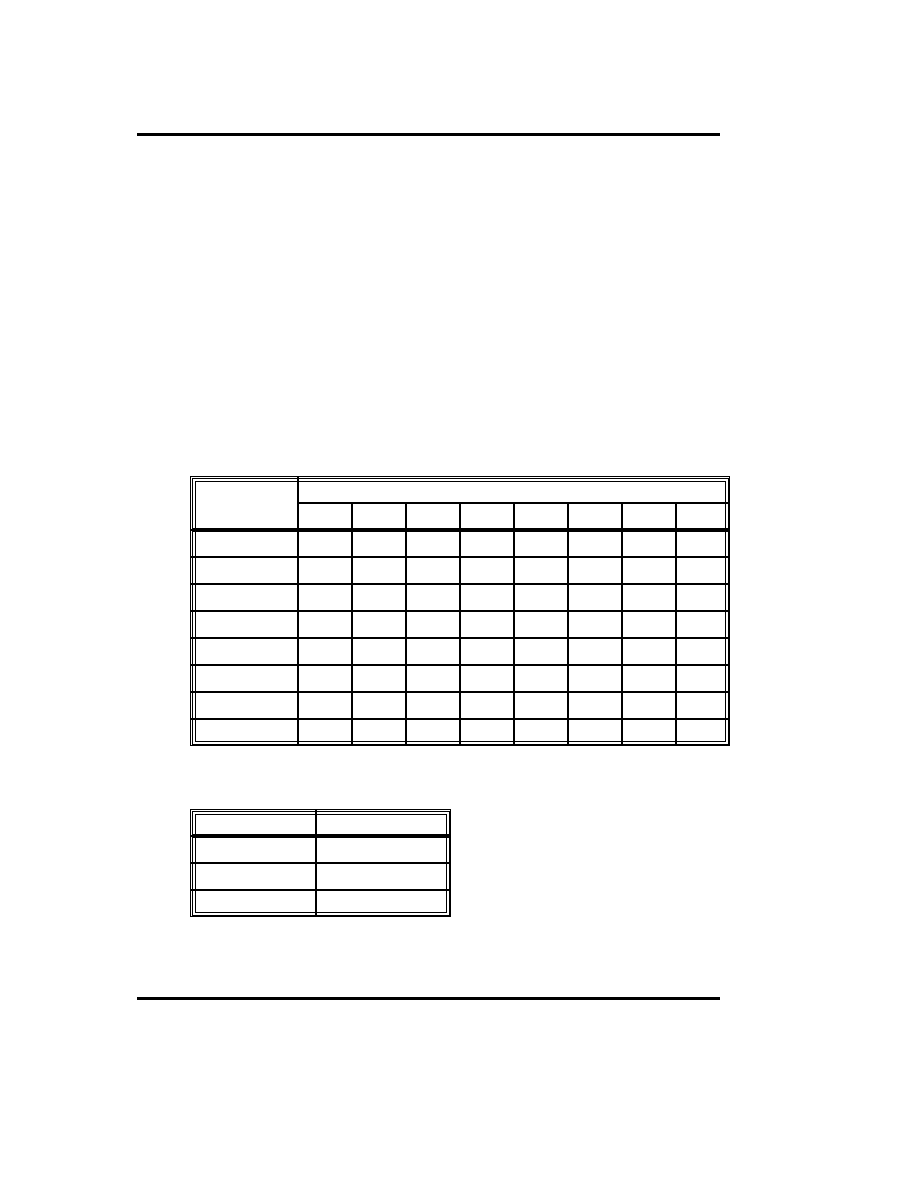

Optional setting

The following optional setting in accordance with the application system

specifications is required :

[S1] Optional mask setting

Optional masks available with GMS300 series units can be set by selecting

short posts.

1. Setting of K-input and R-Port for STOP release

Shorting the KSR0 ~ KSR3 and RSR0 ~ RSR3 with the side of H can set the

STOP releasing function by the corresponding KSR0 ~ KSR3 and RSR0 ~

RSR3. If no STOP releasing function is desired, short them with the side of L.

Setting pin

Short post

K0

KSR0

Setting of STOP

No setting of STOP

H

L

K1

KSR1

H

L

K2

KSR2

H

L

K3

KSR3

H

L

R0

RSR0

H

L

R1

RSR1

H

L

R2

RSR2

H

L

R3

RSR3

H

L

2. Setting of pull-up resistor built-in R-Port pull-up resistor can be built in the

R-Port by shorting the corresponding RPU0 ~ RPU3 with the side of H.

If installation of built-in pull-up resistor is not desired, short them with the

side of L.

Setting pin

Short post

Built-in pull-up resistor installation

No built-in pull-up resistor installation

R0

RPU0

H

L

R1

RPU1

H

L

R2

RPU2

H

L

R3

RPU3

H

L

Chapter 4. Evaluation Board

4 - 4

3. Setting of output condition of D0~D7 in STOP

Shorting the DSC0~DSC7 with the side of H can set the output condition of

corresponding D-output in STOP at

Ì

L

Ì

forcibly.

To set the condition of usual output (the condition before STOP started is

maintained), short them with the side of L.

Setting pin

Short post

D0

DSC0

Forced setting at

Ì

L

Ì

in STOP

release

Usual output in

STOP released

H

L

D1

DSC1

H

L

D2

DSC2

H

L

D3

DSC3

H

L

D4

DSC4

H

L

D5

DSC5

H

L

D6

DSC6

H

L

D7

DSC7

H

L

4. Setting of watch dog timer release with REMOUT output

The watch dog timer can be reset with REMOUT output signals by shorting

the WDTM with the side of L.

If the WDT resetting with REMOUT output signals is not desired, short it

with the side of H.

Short post

Reset timer

WDTM

L

H

Do not reset timer

[S2] External STOP setting

STOP can be set from the outside by shorting the S2 toward the side of H.

Usually, short it toward the side of L.

[S3] Power supply connection

This selection should be strapped to V

DD

.

Chapter 4. Evaluation Board

4 - 5

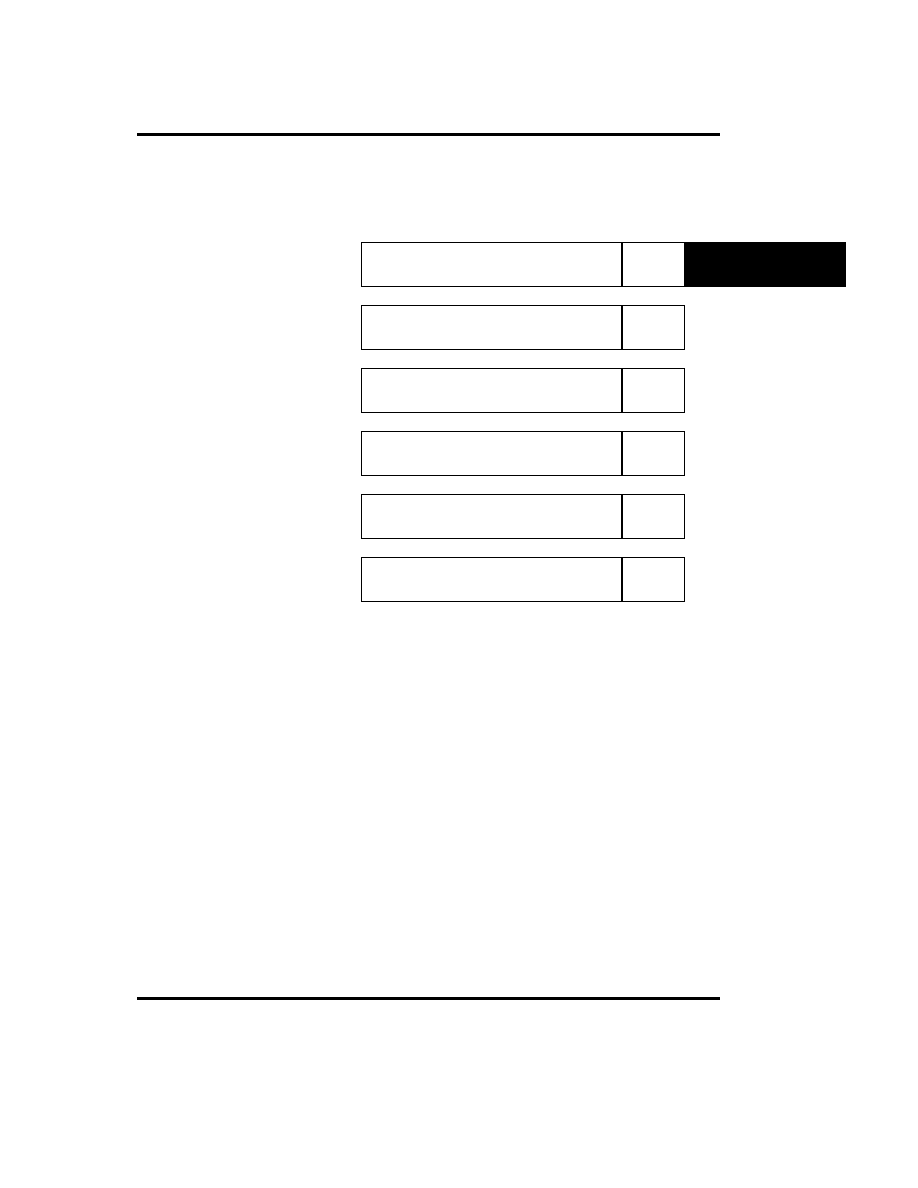

Short post

2764/128

S4

H

L

27256

[S4] EPROM 2764/128, and 27256 can be installed by switching over the S4. For

EPROM, however, right-justify ROM chip pin 1 from socket pin 3.

Short post

External clock input

S5 & S6

U

X

Internal self-induced oscillation

[S5, S6] Clock input selection

Self-induced oscillation with the external clock input and oscillator can be set by

switching over the S5 & S6

For internal clock input, install an oscillator on the PCB. Since the oscillation

circuit constant varies depending on the oscillator, adjust the constant by

referring to the oscillator manufacture`s recommendable values.

Chapter 4. Evaluation Board

Short post

MHz oscillation

S7 & S8 & JP

M

K

KHz oscillation

[S7, S8, JP] Clock input selection

MHz and KHz oscillation can be selected by switching over the S7, S8 and JP.

4 - 6

Caution on Operation

· It is required to install a 24DIP IC socket in the application system. The

connection cable is connected to the socket.

· There is a possibility that the ceramic oscillator on the application system cannot

oscillate properly due to the influence of connection cable wiring capacitor or other

reasons. In such a case, install the oscillator on the evaluation board.

· Since the GMS 30000 EVA is designed to evaluate the program operations, there

is a case where the AC and DC characteristics differ from those of the mass-

produced chips

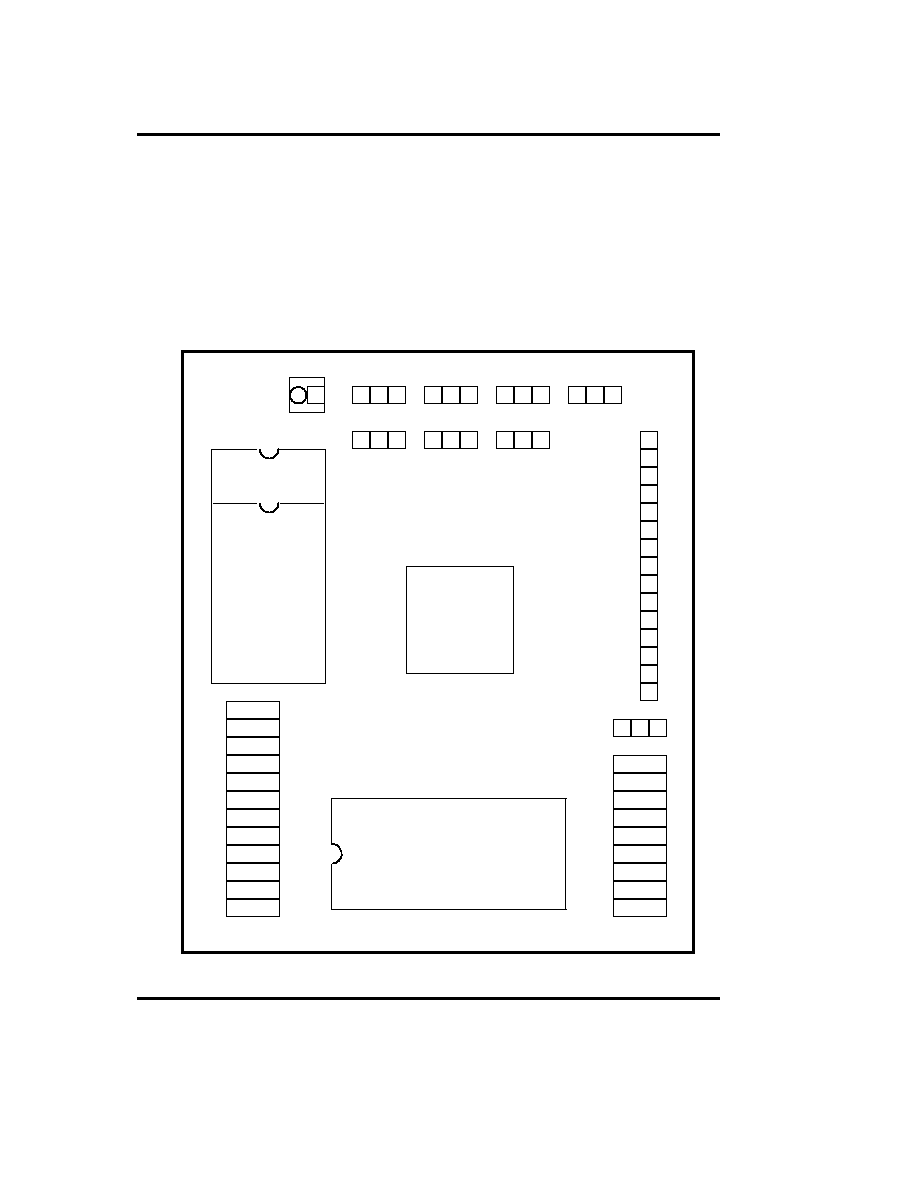

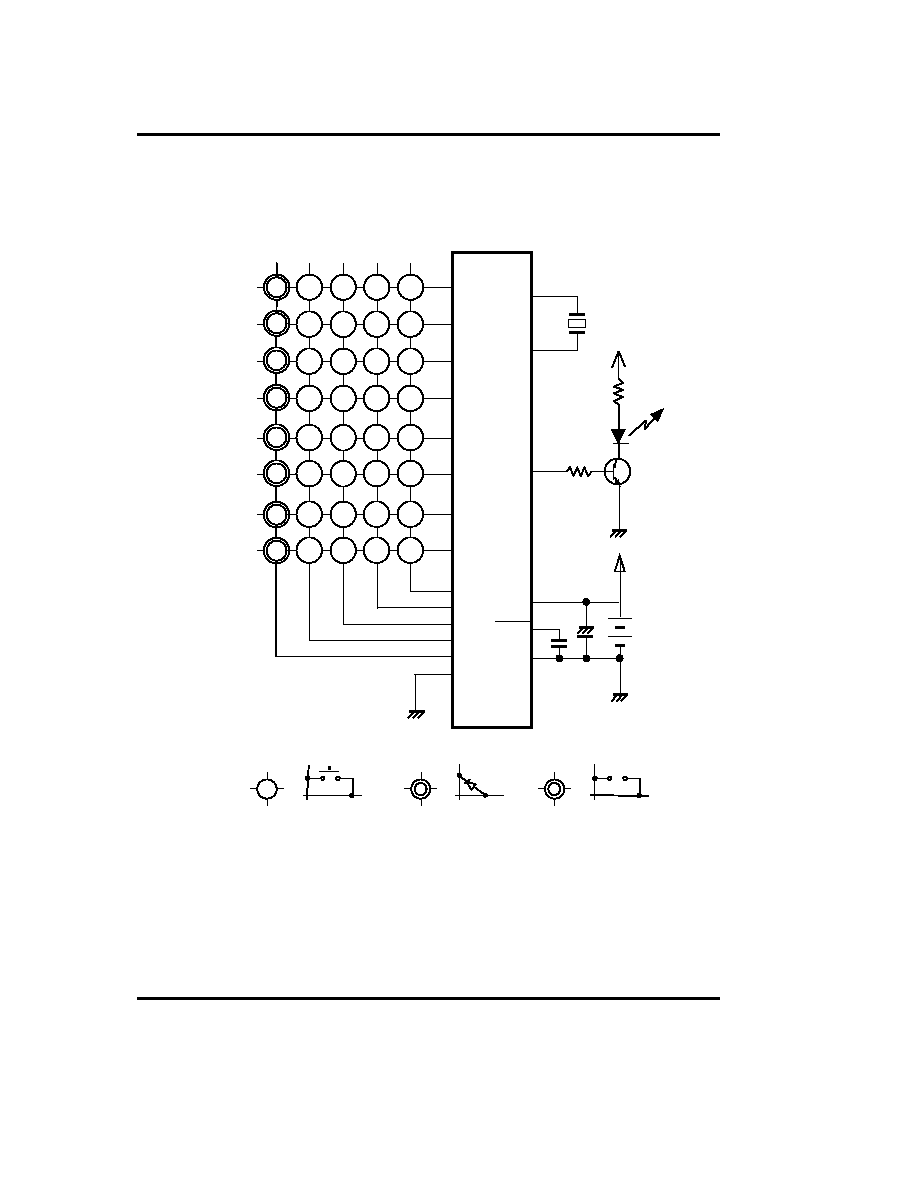

Chapter 4. Evaluation Board

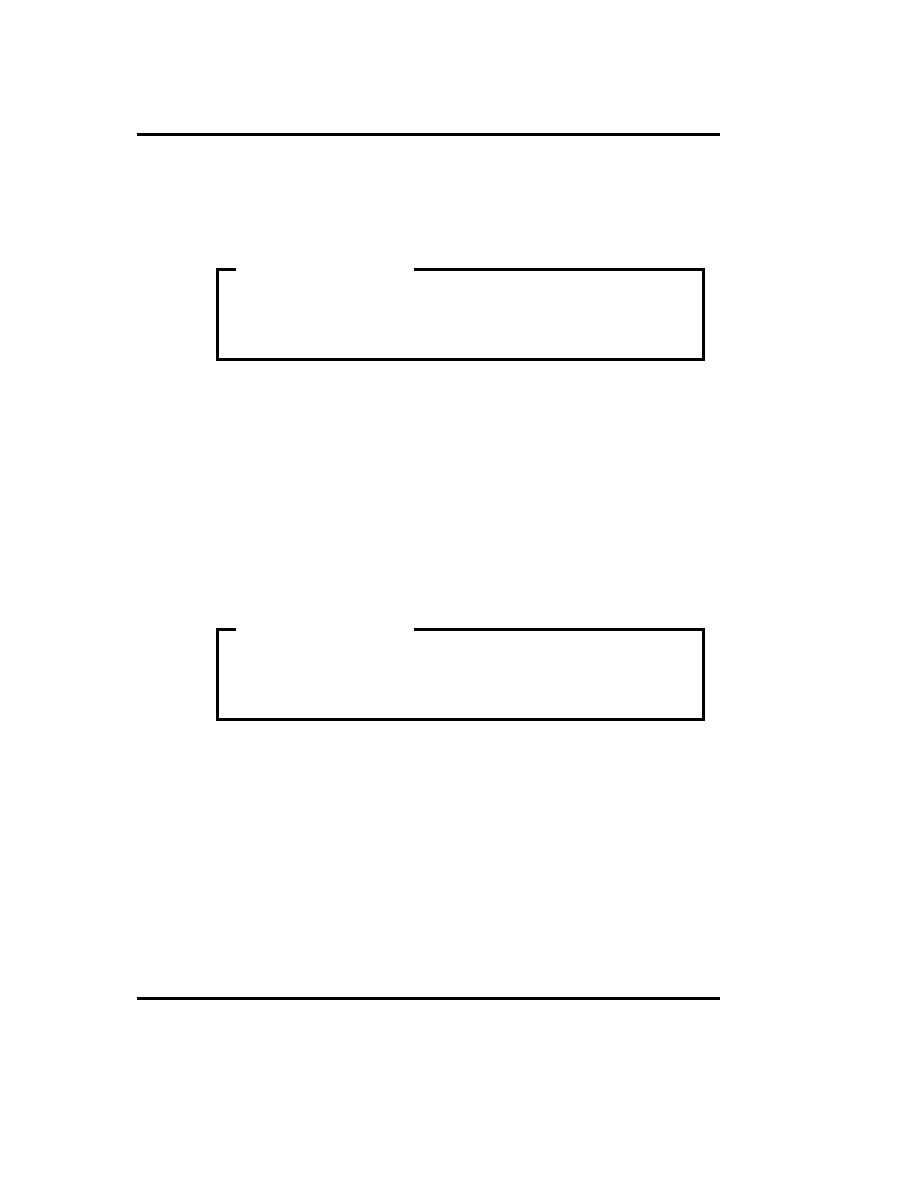

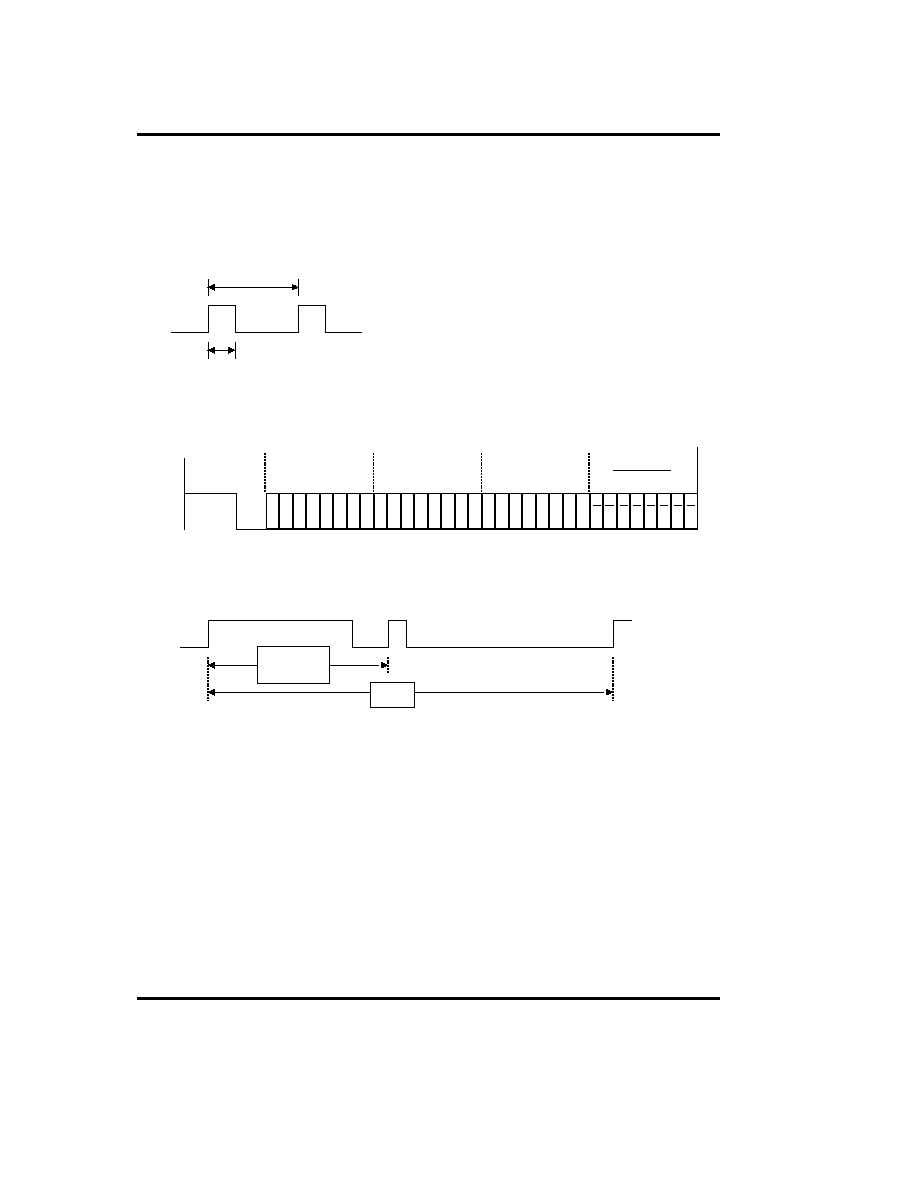

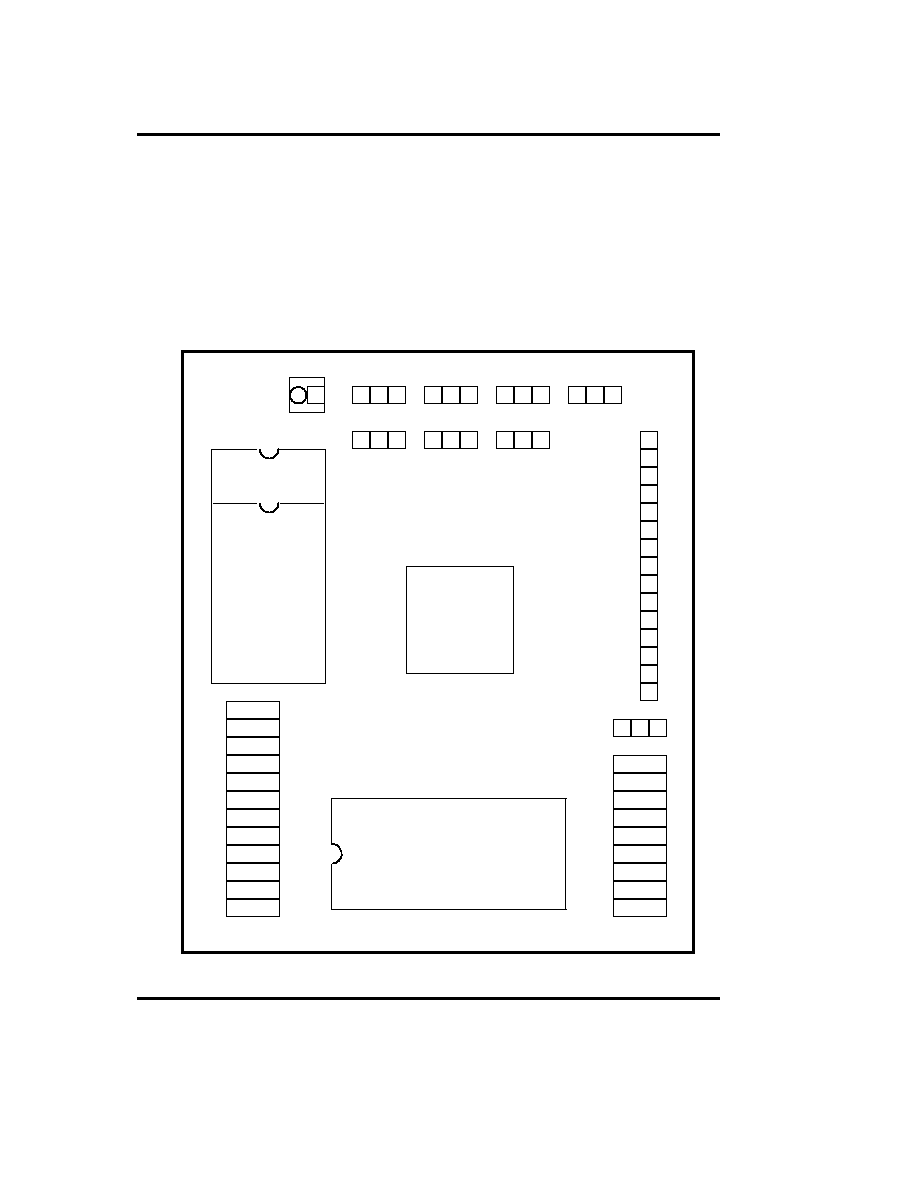

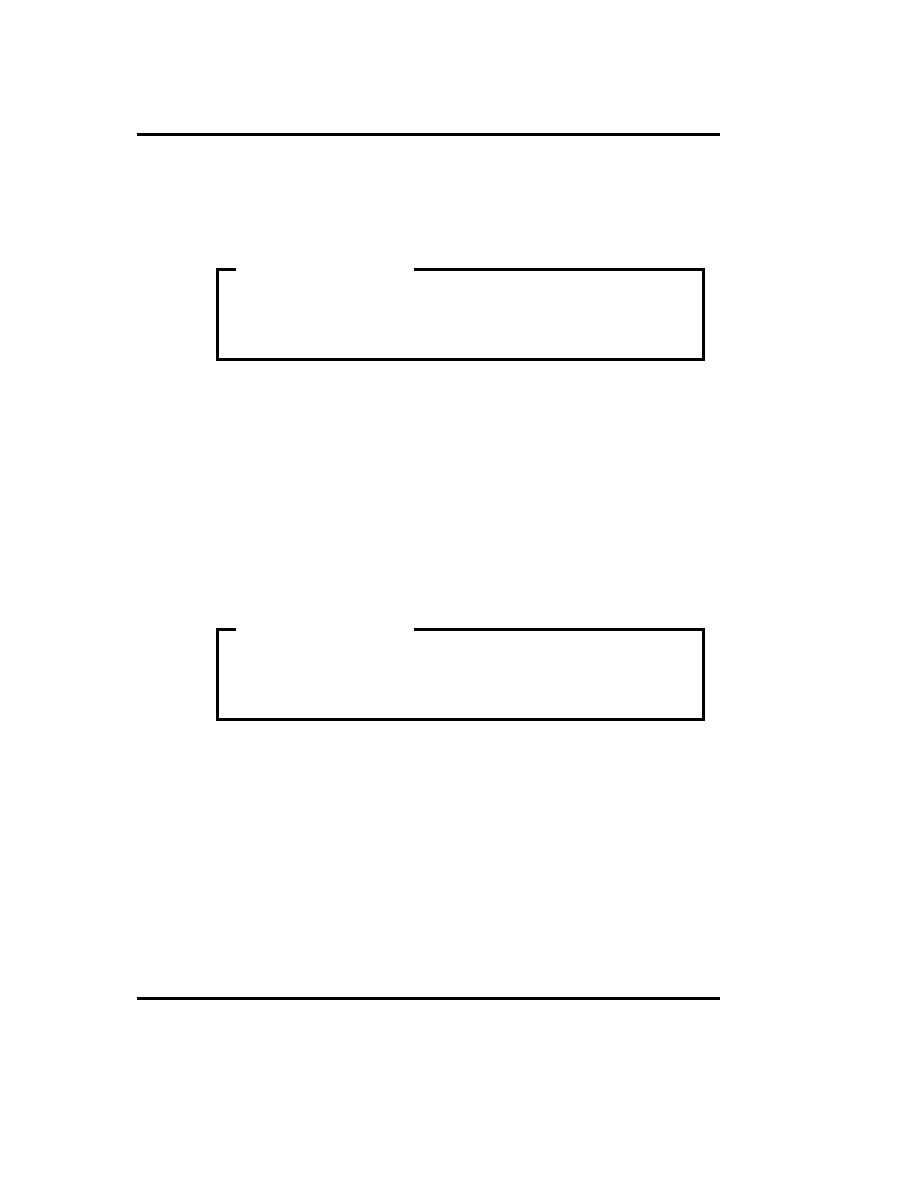

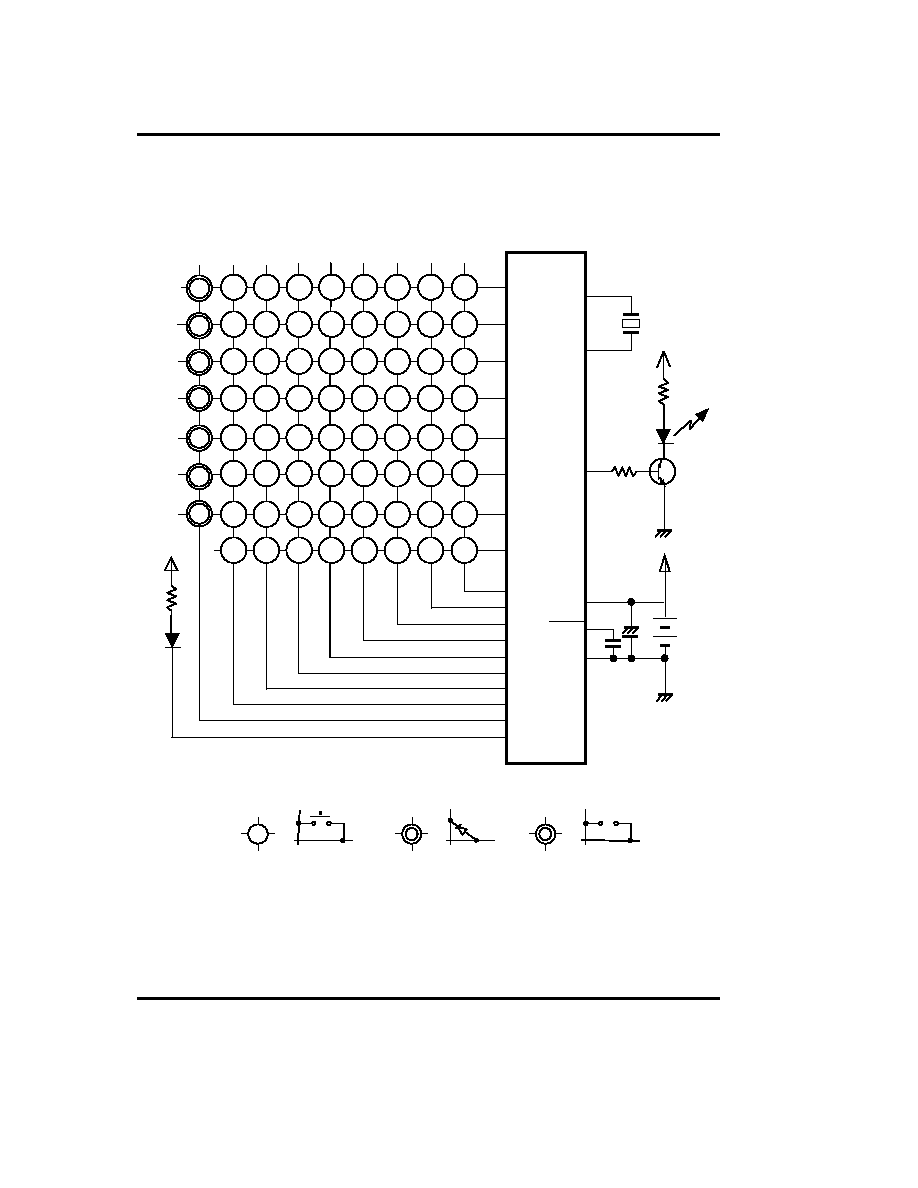

!

S3

S5

S6

H

L

U

X

U

X

M

K

1

28

Connector

!#

1

80

E V A

M1

GND

CX3

CX2

X1

X0

AC3

AC2

AC1

AC0

Y3

Y2

Y1

Y0

WDTR

REM DATA

S2

H

L

S1

BKPOINT

WDTM

DSC7

DSC6

DSC5

DSC4

DSC3

DSC2

DSC1

DSC0

H

L

RSR0

RSR1

RSR2

RSR3

RPU0

RPU1

RPU2

RPU3

KSR0

KSR1

KSR2

KSR3

(80QFP)

Connector

(24Pin Socket)

GSEN

EVA30000

USER

S1

H

L

T1

T2

GND

JP

S4

S7

S8

H

L

M

K

M

K

Fig 4-1 Layout Diagram

INTRODUCTION

1

ARCHITECTURE

2

INSTRUCTION

3

EVALUATION BOARD

4

SOFTWARE

5

APPENDIX

6

5 - 1

Chapter 5. Software

CHAPTER 5. Software

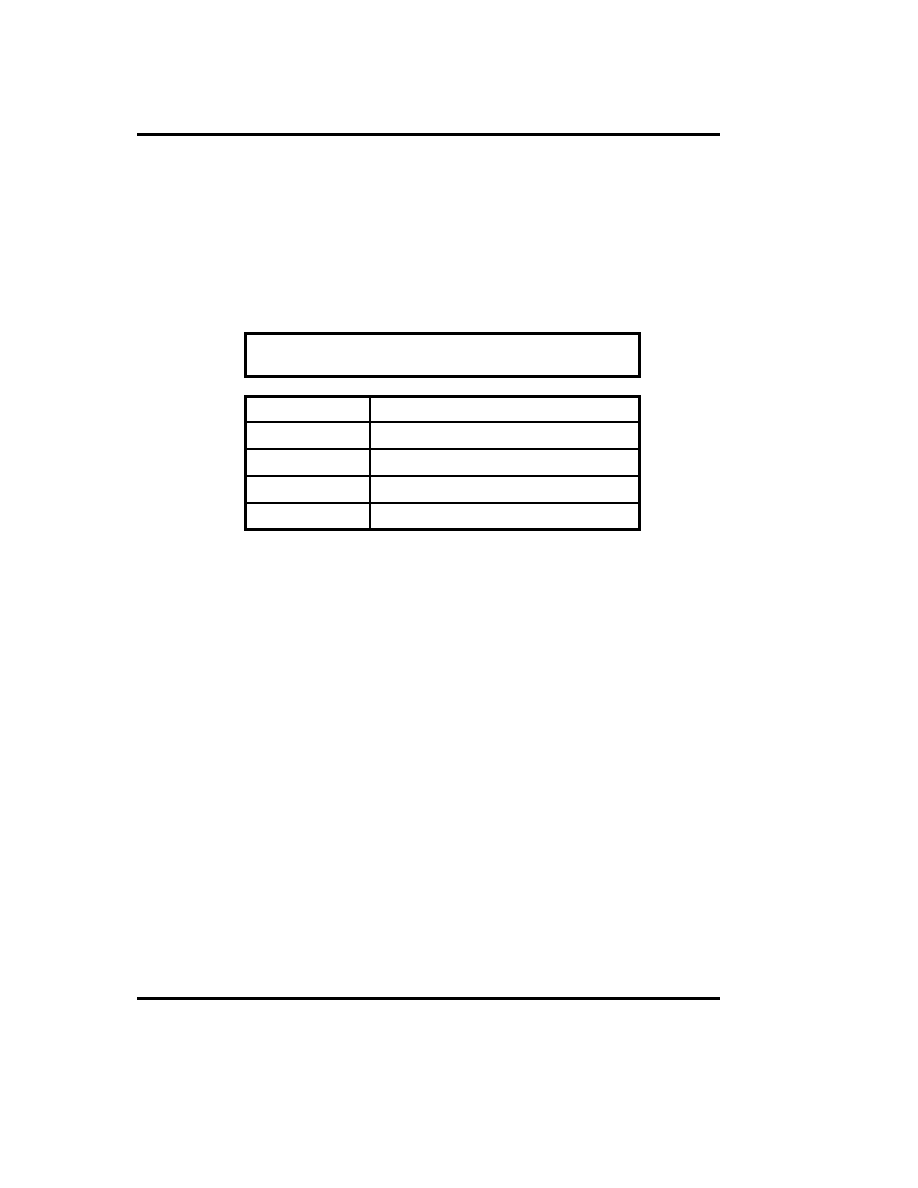

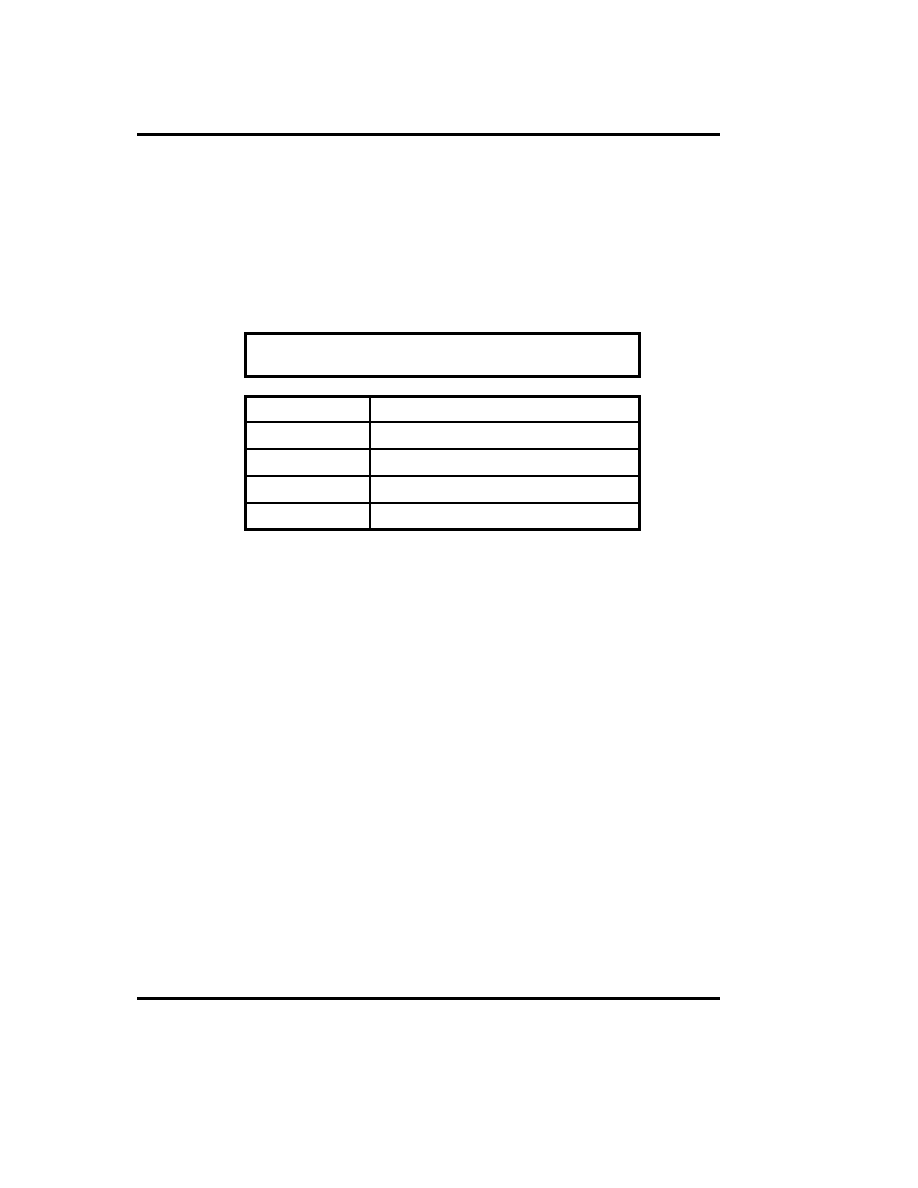

Configuration of Assembler

Execute File

GA80.EXE

Description

Assembler

Create assembler list file

GMSLST.EXE

GMSHEX.EXE

Create HEX.file

Create cross reference file

GMSCRF.EXE

GMSTST.EXE

Create instruction check file

Create ROM dump file

GMSROM.EXE

GS.BAT

Batch processing of the above

Instruction library file

GMS30K.LIB

Boothing up Assembler

Creating your own source file with the extension name of SRC and execute

batch

file (GS.BAT). This batch file converts the source code written in mnemonic into

machine language and generate a kind of useful file.

C> GS Source file (.SRC)

Input File

EX.SRC

Content

List file

Hexa file (for EPROM, simulator)

Cross reference file

Instruction check file

ROM dump file (for masking data)

Symbol file

Output File

EX.LST

EX.RHX

EX.CRF

EX.TST

EX.DMP

EX.SYM

* HEX and PRN file is intermediate file

5 - 2

Configuration of Simulator

1. Overview

The simulator is a program for GMS300 Series 4-bit one-chip microcomputer.

The environment is organized based upon Hexa file of *.RHX and Cross Reference

file of *.CRF generated by assembling the source program coded by programmer.

Execution Environment

System : IBM-PC/AT or higher (MS-DOS or PC-DOS)

Video : Hercules, EGA or VGA color

Organizing files

GSSIM.EXE

: Simulator execution file

GMS30K.GSP

: Store the simulator environment. It is

generated automatically when executing

the program initially (Selected CPU.

Store the file names previously loaded.).

GMS30K.HLP

:

Help file of simulator commands.

GMS30K.LOG

:

Record the working history of users. Generated

by LOG ON and LOG OFF commands.

*.BAT

:

List a set of simulator command. Generated by

user.

PORTIN.DAT

:

Provide the port input-value when executing

the simulator. Generated by user.

Supporting CPU

GMS30004, GMS30012, GMS30112, GMS30120, GMS30140

Chapter 5. Software

5 - 3

2. Characteristics of Simulator

- User-friendly pop-up window menu. Select the necessary command and display

the screen in windows format so that users can know the execution results.

- Display always the register window in the right side so that programmer can check

easily the change of data memory value as program proceeds.

- Maintain the previous simulator environment if user does not make the extra

changes when re-executing after logging out completely from the simulator

previously executed by loading the source program. In other words, the previously-

executed file is automatically loaded when the simulator is executed (GMS30K.GSP

file).

- When trace command ([F8] or > T command) is executed, the changed values are

noticed easily by displaying the highlighted changed values in register and memory

windows, if the contents of each register or data memory is changed as command

line is processed.

- When trace command ([F8] or > T command) is executed, the current execution

line is highlighted.

- Out of the simulator commands, load or save commands is executable in pop-up

windows. In-line command is executable as prompt command in the command

window.

Chapter 5. Software

5 - 4

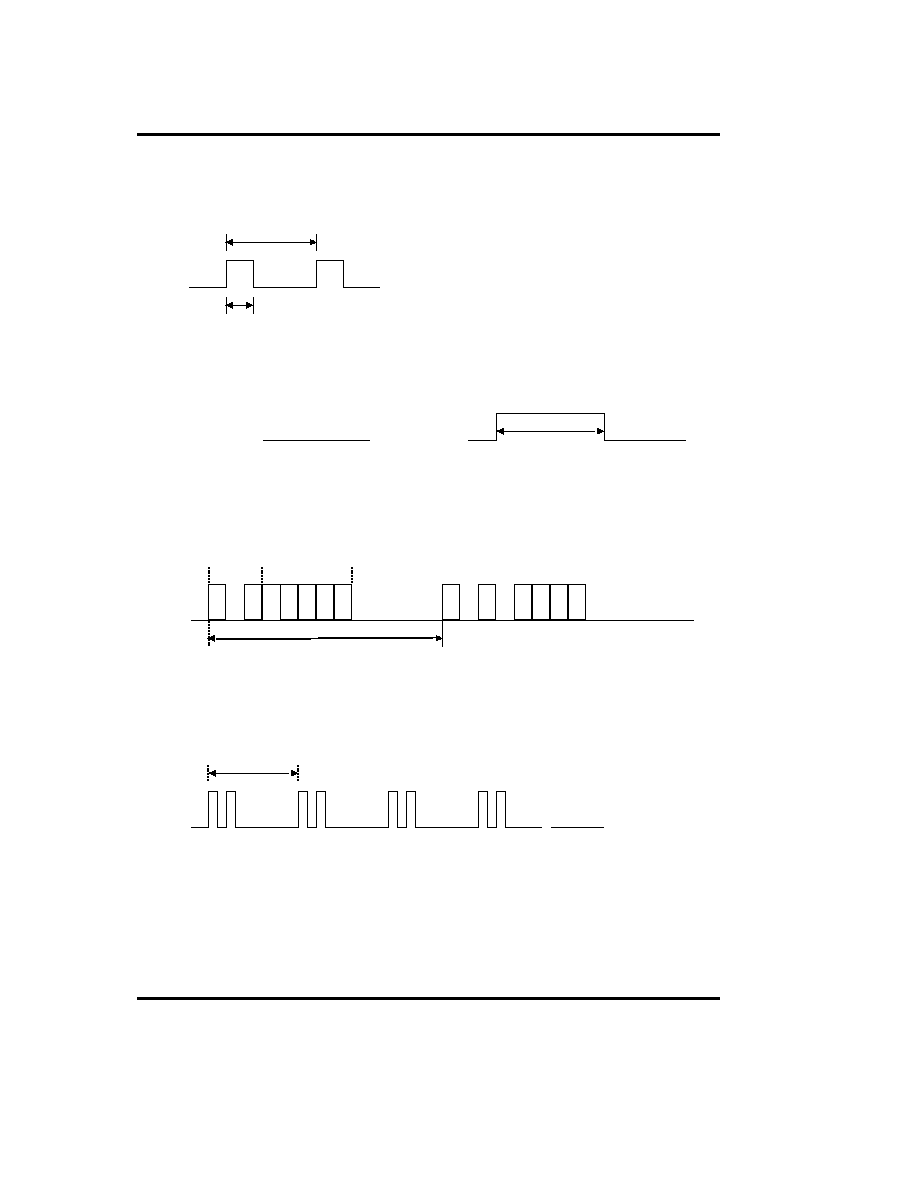

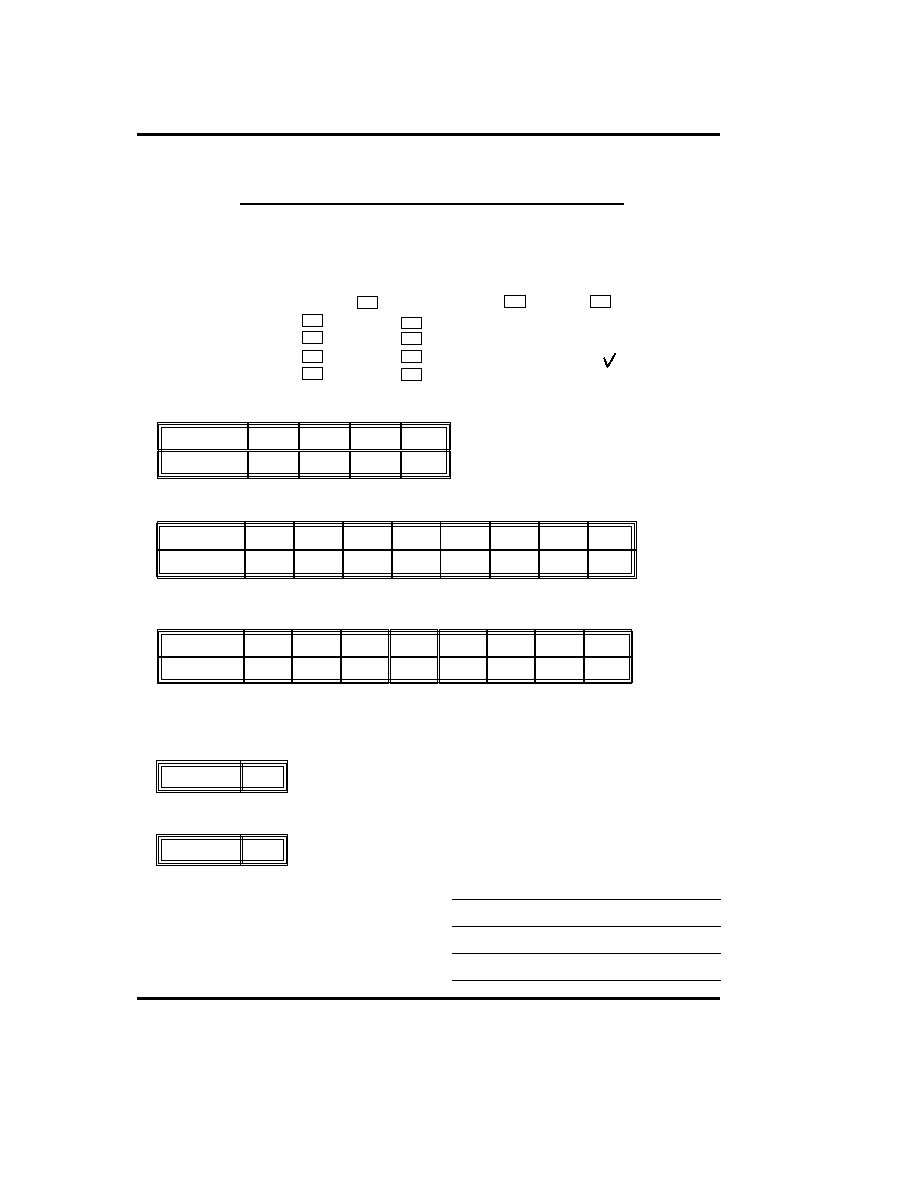

3. Screen Organization of Simulator

Screen is basically organized with four windows; Memory, Source, Command and

Register. Source and Command windows can be enlarged up to the full screen

size (CTRL-[F10]). Movement between windows is made by [F6].

3.1 Memory

Window

Data memory contents of the currently selected micom is displayed. 32 nibble

data values of 00~1F(h) addresses are displayed.

3.2 Source

Window

The contents of *.RHX file called by load command is displayed in the state of

being disassembled. Addresses are displayed randomly in the state of

polynomial together with instruction code and mnemonic. If *.CRF file is

called, label is displayed at the corresponding position. Display position of

source program is adjustable with Up/Down arrow keys and Page Up/Down

keys.

3.3 Command