/home/web/htmldatasheet/RUSSIAN/html/hynix/213015

8-BIT SINGLE-CHIP MICROCONTROLLERS

GMS87C4060

GMS81C4040

User's Manual

MicroElectronics

Semiconductor Group of Hyundai Electronics Industrial Co., Ltd.

Additional information of this manual may be served by HYUNDAI Micro Electronics offices in Korea or Dis-

tributors and Representatives listed at address directory.

HYUNDAI Micro Electronics reserves the right to make changes to any information here in at any time without

notice.

The information, diagrams and other data in this manual are correct and reliable; however, HYUNDAI Micro

Electronics is in no way responsible for any violations of patents or other rights of the third party generated by

the use of this manual.

Version 1.00

Published by

MCU Application Team bjlim@hmec.co.kr conner@hmec.co.kr

2000 HYUNDAI Micro Electronics All right reserved.

HYUNDAI

GMS81C4040/87C4060

May. 2000 Ver 1.0

1

Table of Contents

OVERVIEW.......................................... 1

Description ...................................................1

Features .......................................................1

Development Tools..................................... 2

BLOCK DIAGRAM .............................. 3

PIN ASSIGNMENT .............................. 4

PACKAGE DIAGRAM ......................... 5

PIN FUNCTION .................................... 6

PORT STRUCTURES .......................... 9

RESET ................................................................ 9

TEST ................................................................... 9

XIN, XOUT ........................................................ 9

OSC1, OSC2 ..................................................... 9

R00~07, R53 ...................................................... 9

R10~15 (AN0~5) ................................................ 9

R16, 17, 20, 24, 25, 26, 27, 52, 67 ................... 10

R21/Sclk, R22/Sout .......................................... 10

R23/Sin ............................................................ 10

R40~43 (PWM0~3) .......................................... 10

R44, 45, 46, 47 (SCL, SDA, PWM) .................. 10

R50/BUZZ, R51/PWM8 .................................... 11

R54/YM, R55/YS, R56/I ................................... 11

R, G, B ............................................................. 11

ELECTRICAL CHARACTERISTICS . 12

Absolute Maximum Ratings .....................12

Recommended Operating Conditions ....12

DC Electrical Characteristics - GMS81C4040

.....................................................................12

A/D Comparator Characteristics .............14

AC Characteristics ....................................14

Typical Characteristics ............................16

MEMORY ORGANIZATION .............. 17

Registers ...................................................17

Program Memory ......................................20

PCALL

rel ..................................................... 21

TCALL

n ....................................................... 21

Data Memory .............................................23

User Memory .................................................... 23

Control Registers ............................................. 23

Stack Area ........................................................ 23

Addressing Mode ......................................25

(1) Register Addressing ................................... 25

(2) Immediate Addressing

#imm .................. 25

(3) Direct Page Addressing

dp ..................... 25

(4) Absolute Addressing

!abs ....................... 25

(5) Indexed Addressing .................................... 26

X indexed direct page (no offset)

{X} ........... 26

X indexed direct page, auto increment

{X}+ . 26

X indexed direct page (8 bit offset)

dp+X ..... 26

Y indexed direct page (8 bit offset)

dp+Y ..... 27

Y indexed absolute

!abs+Y .......................... 27

Direct page indirect

[dp] ............................... 27

X indexed indirect

[dp+X] ............................. 27

Y indexed indirect

[dp]+Y ............................. 28

Absolute indirect

[!abs] ................................ 28

I/O PORTS ......................................... 29

Registers for Port ..................................... 29

Port Data Registers .......................................... 29

I/O Ports Configuration ............................ 30

R0 Ports ........................................................... 30

R1 Ports ........................................................... 30

R2 Port ............................................................. 31

R4 Port ............................................................. 31

R5 Port ............................................................. 32

R6 Port ............................................................. 32

CLOCK GENERATOR ...................... 33

TIMER ................................................ 34

Basic Interval Timer ................................. 34

Timer 0, 1 ................................................... 35

Timer / Event Counter 2, 3 ....................... 37

Timer Mode ...................................................... 39

Event counter Mode ......................................... 39

A/D Converter ................................... 42

Control .............................................................. 42

Serial I/O ........................................... 44

Control .............................................................. 44

Pulse Width Modulation (PWM) ...... 46

8bit PWM Control ............................................. 47

14bit PWM Control ........................................... 47

Interrupt interval measurement circuit

........................................................... 49

Control .............................................................. 49

Buzzer driver .................................... 51

Control .............................................................. 51

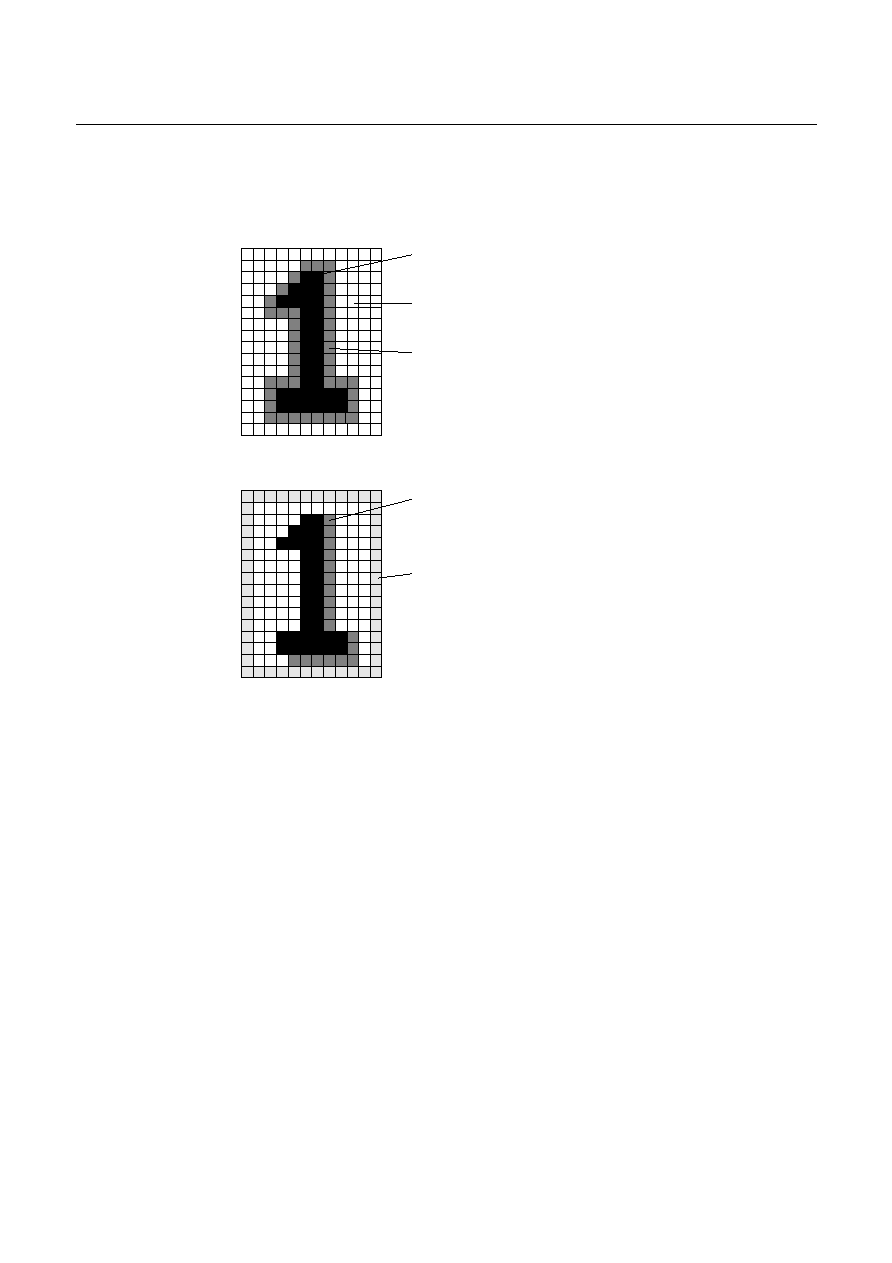

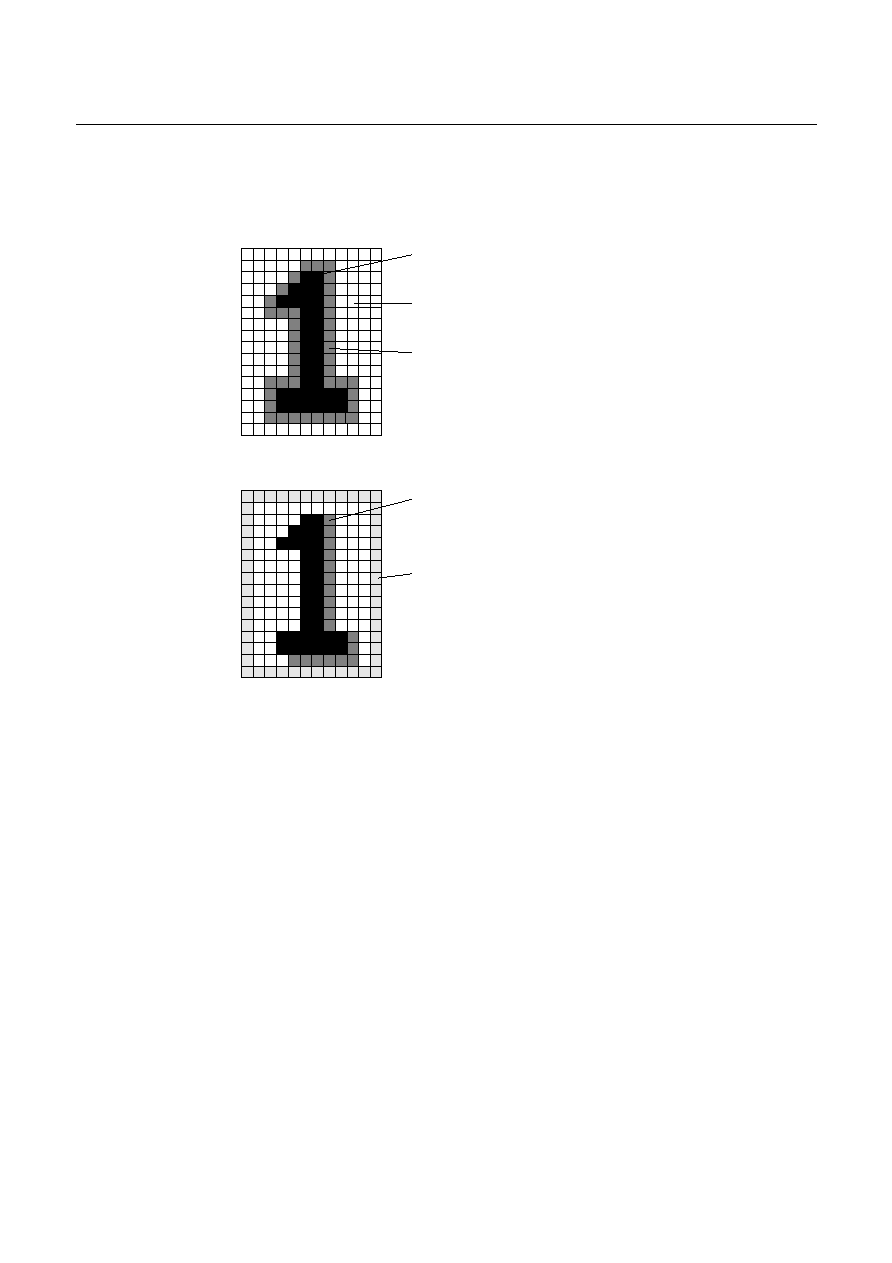

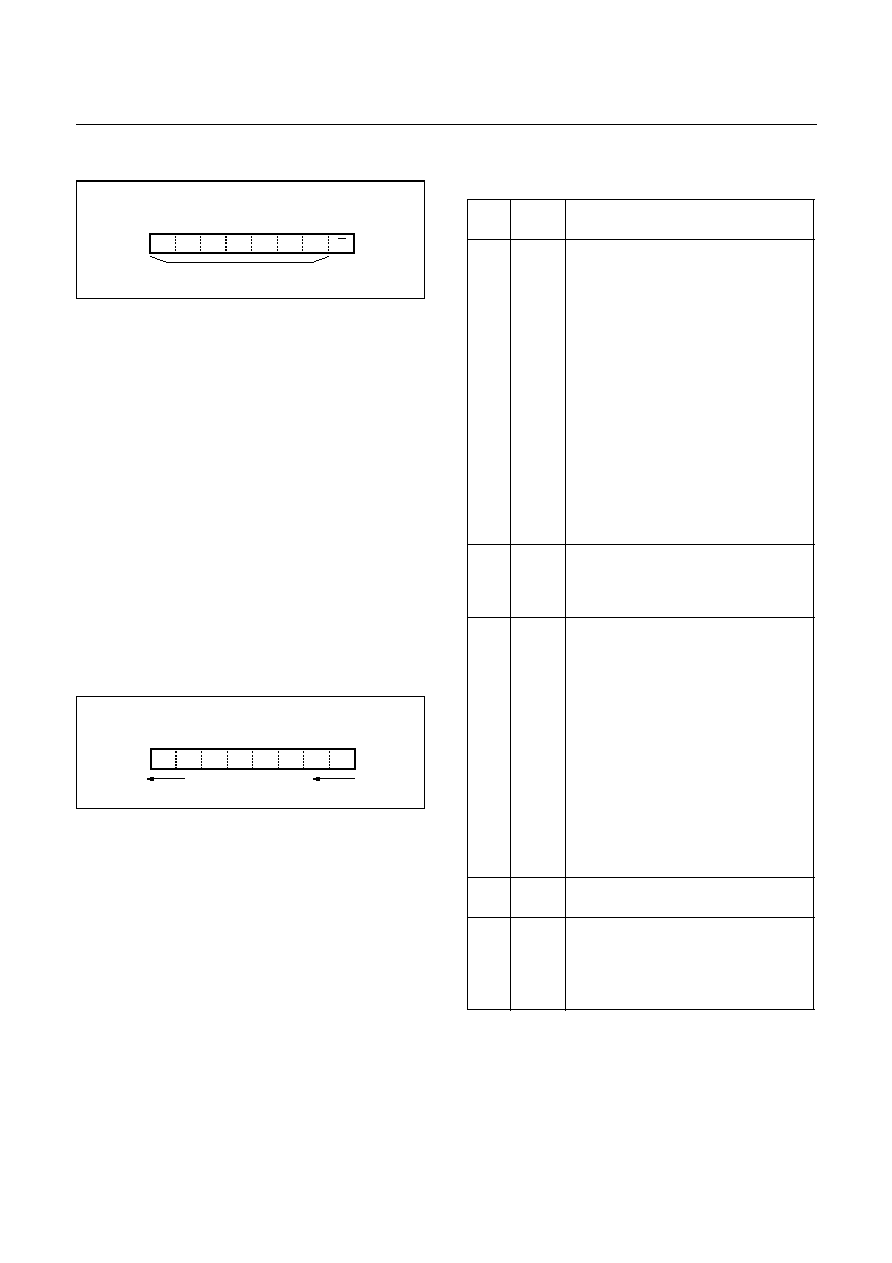

On Screen Display (OSD) ................ 53

OSDCON1 ....................................................... 55

OSDCON2 ....................................................... 55

OSDPOL .......................................................... 56

FDWSET .......................................................... 56

L1ATTR ............................................................ 57

L1VPOS ........................................................... 58

L2ATTR ............................................................ 58

L2VPOS ........................................................... 58

COLMOD ......................................................... 58

MESHCON ....................................................... 58

VRAM ............................................................... 58

Font ROM ......................................................... 60

GMS81C4040/87C4060

HYUNDAI

2

May. 2000 Ver 1.0

Sprite RAM ....................................................... 60

Test Font .......................................................... 61

I2C Bus Interface .............................. 62

Control .............................................................. 62

I2C address register ......................................... 62

I2C data shift register [ICDR] ........................... 63

I2C status register ............................................ 63

I2C control register 1 ........................................ 64

I2C control register 2 ........................................ 64

START condition generation ............................ 65

RESTART condition generation ....................... 65

STOP condition generation .............................. 65

START / STOP condition detect ...................... 66

Address data communication ........................... 67

INTERRUPTS .................................... 68

Interrupt Mode Register ................................... 68

Interrupt Sequence ...................................72

Interrupt acceptance ........................................ 72

Saving/Restoring General-purpose Register ... 73

Multi Interrupt ............................................74

External Interrupt ..................................... 75

Response Time ................................................ 75

WATCHDOG TIMER ......................... 76

Watchdog Timer Control .................................. 76

Enable and Disable Watchdog ......................... 77

Watchdog Timer Interrupt ................................ 77

Minimizing Current Consumption ..................... 78

OSCILLATOR CIRCUIT .................... 80

RESET ............................................... 81

External Reset Input ................................. 81

Watchdog Timer Reset ............................ 82

OTP Programming ........................... 83

GMS87C4060 OTP Programming ............ 83

.Device configuration data ...................... 84

Timing Chart ............................................. 87

Assemble mnemonics ..................... 89

Instruction Map ......................................... 89

Alphabetic order table of instruction ..... 90

Instruction Table by Function ................. 94

HYUNDAI

GMS81C4040/87C4060

May. 2000 Ver 1.0

1

GMS81C4040/GMS87C4060

CMOS SINGLE-CHIP 8-BIT MICROCONTROLLER

FOR TELEVISION

1. OVERVIEW

1.1 Description

The GMS81C4040/GMS87C4060 is an advanced CMOS 8-bit microcontroller with 40K(60K) bytes of ROM. The device is

one of GMS800 family. The HYUNDAI's GMS81C4040/GMS87C4060 is a powerful microcontroller which provides a

highly flexible and cost effective solution to many TV applications. The GMS81C4040/GMS87C4060 provides the follow-

ing standard features: 40K(60K) bytes of ROM, 1,536 bytes of RAM, 8-bit timer/counter .

1.2 Features

� 40K(60K) Bytes On-chip Program Memory

� 1,536 Bytes of On-chip Data RAM

(Included 256 bytes stack memory)

� Instruction Cycle Time (ex:NOP)

- 0.5us at 8MHz

� 40 Programmable I/O pins

- 33 I/O and 7 Output pins

� Serial I/O : 8bit x 1ch

� I

2

C Bus interface

- Multimaster (2 Pairs interface pins)

� A/D Converter : 8bit x 6ch (TBD LSB)

� Pulse Width Modulation

- 14bit x 1ch

- 8bit x 6ch

� Timer

- Timer/Counter : 8bit x 4ch (16bit x 2ch)

- Basic interval timer : 8bit x 1ch

- Watch Dog Timer

� Number of Interrupt sources : 18

� On Screen Display

- Number of characters : 512 (6 characters are

reserved for IC test)

- Character size : 12 dots(X) x 16 dots(Y)

- Character display size : Large, Medium, Small

- DIsplay capability : 24Characters x 16 Line

(Two line VRAM buffer)

- Character, Back ground color : 16kinds

- Special functions : Rounding, Outline, Sprite,

Shadow,...

� Buzzer Driving port

- 500Hz ~ 250kHz @8MHz (Duty 50%)

� Operating Range : 4.5V to 5.5V

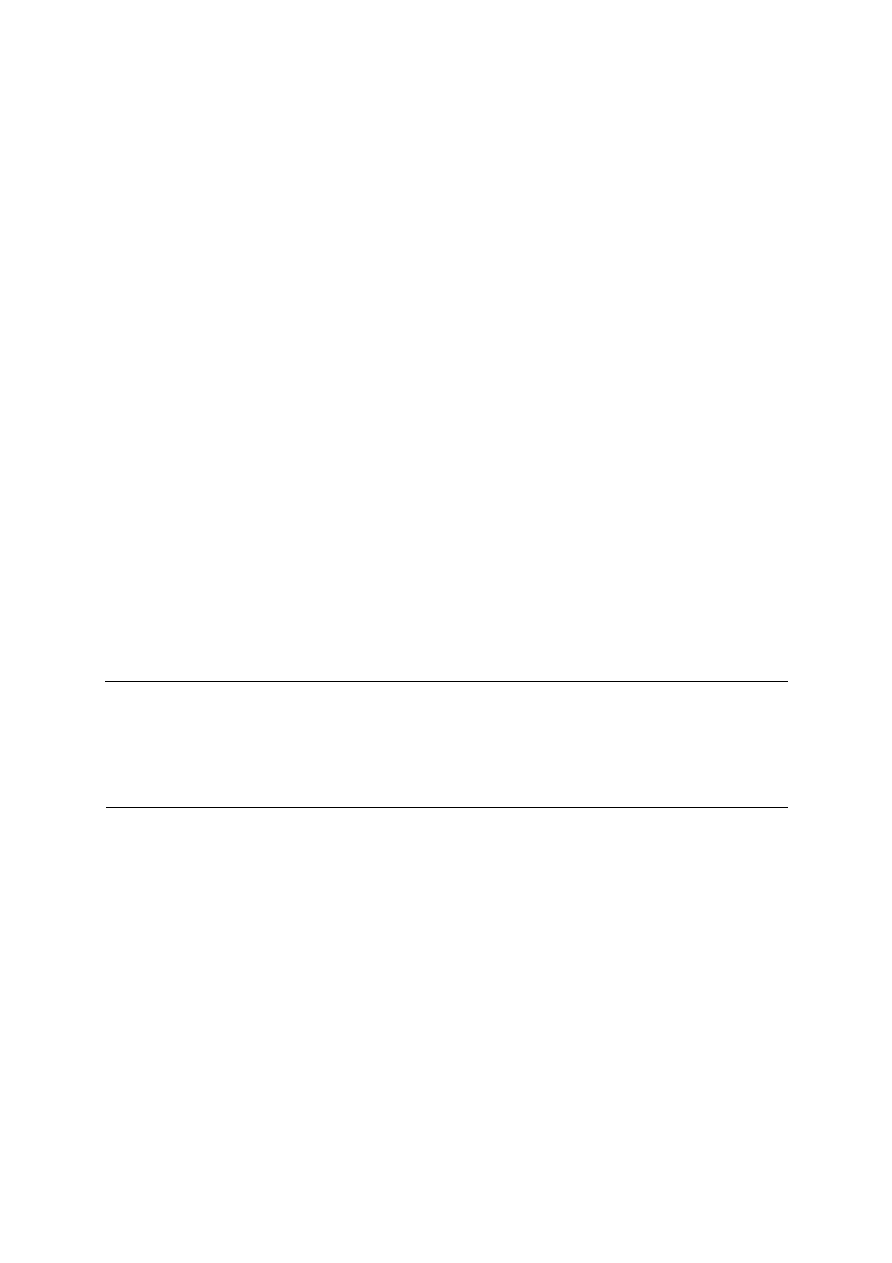

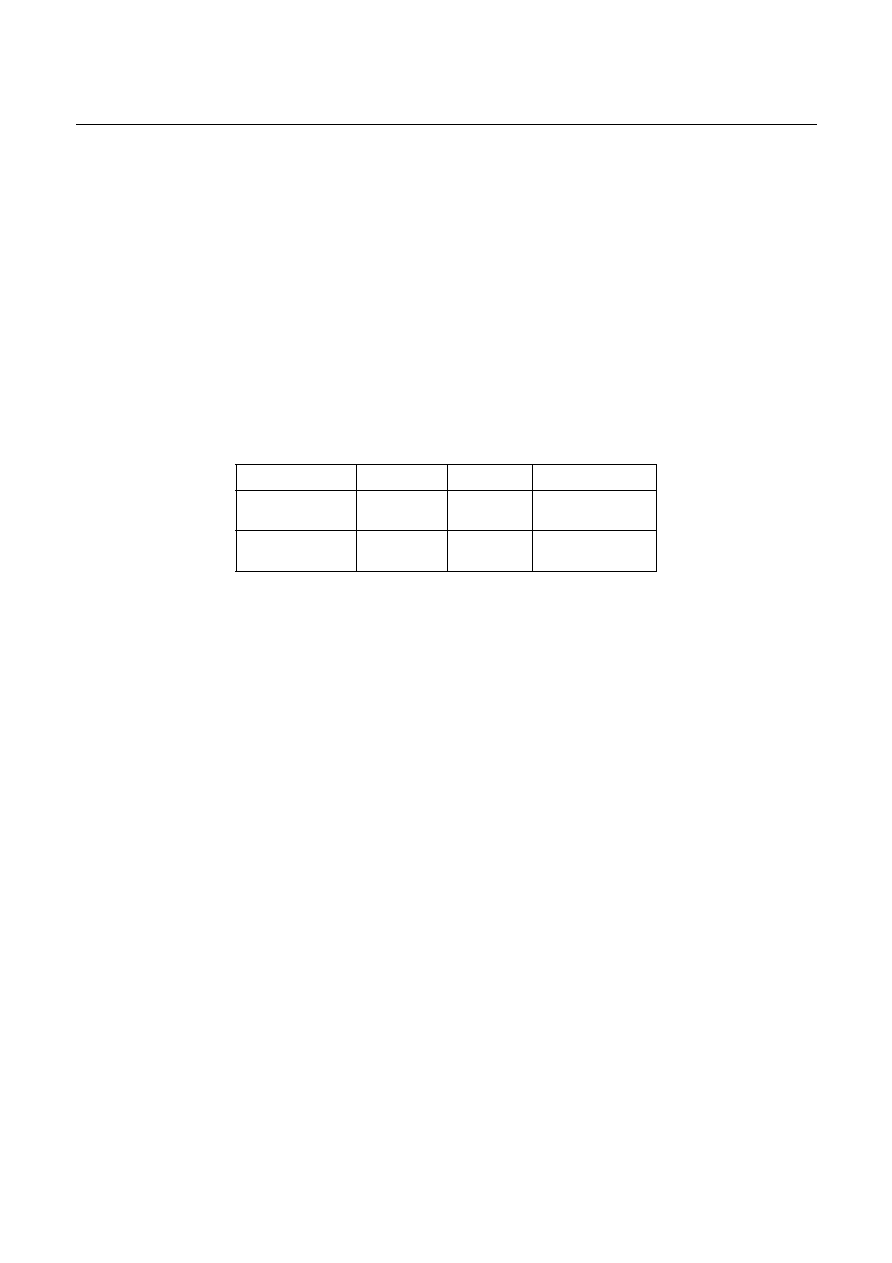

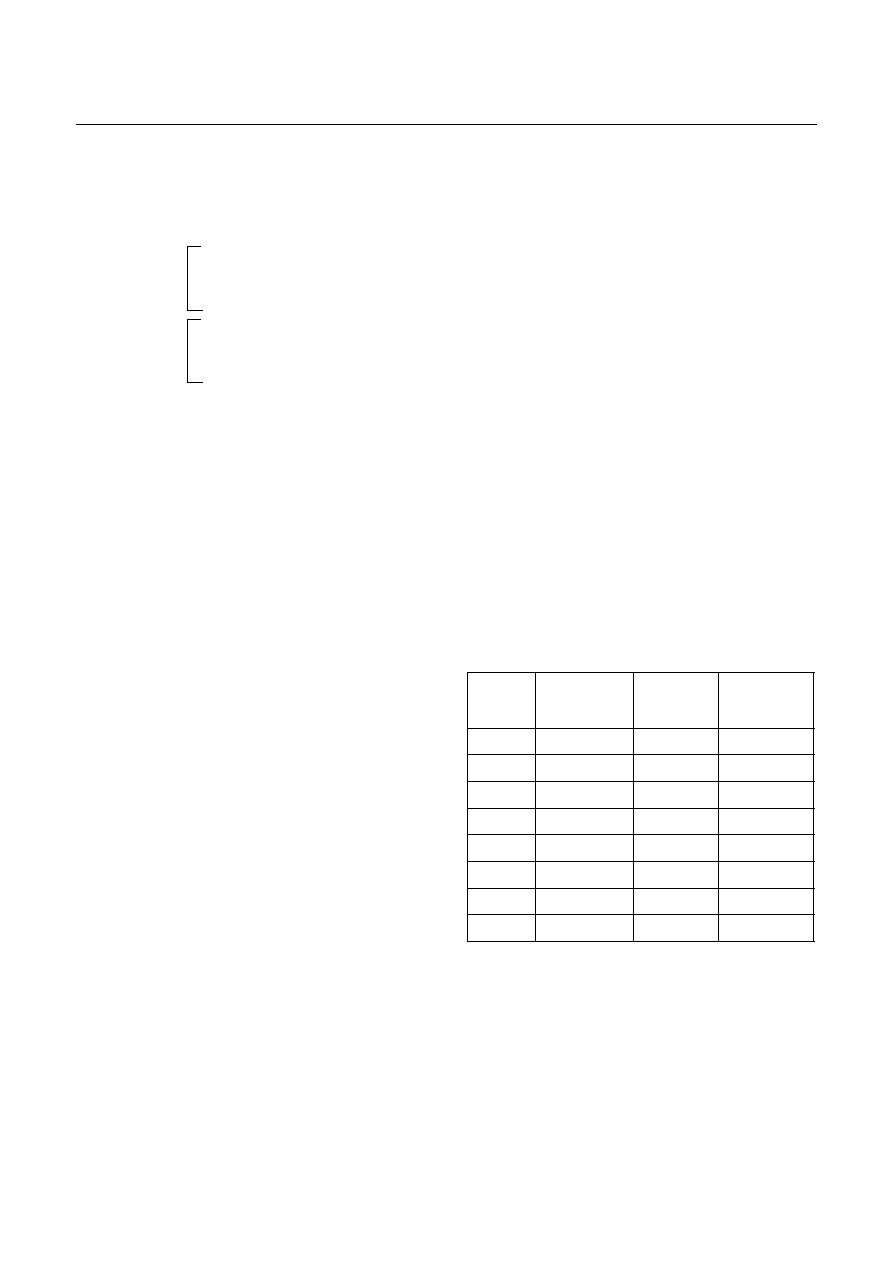

Device name

ROM Size

RAM Size

Package

GMS81C4040

40K bytes

Mask ROM

1,536 bytes

52SDIP

GMS87C4060

60K bytes

EPROM

1,536 bytes

52SDIP

GMS81C4040/87C4060

HYUNDAI

2

May. 2000 Ver 1.0

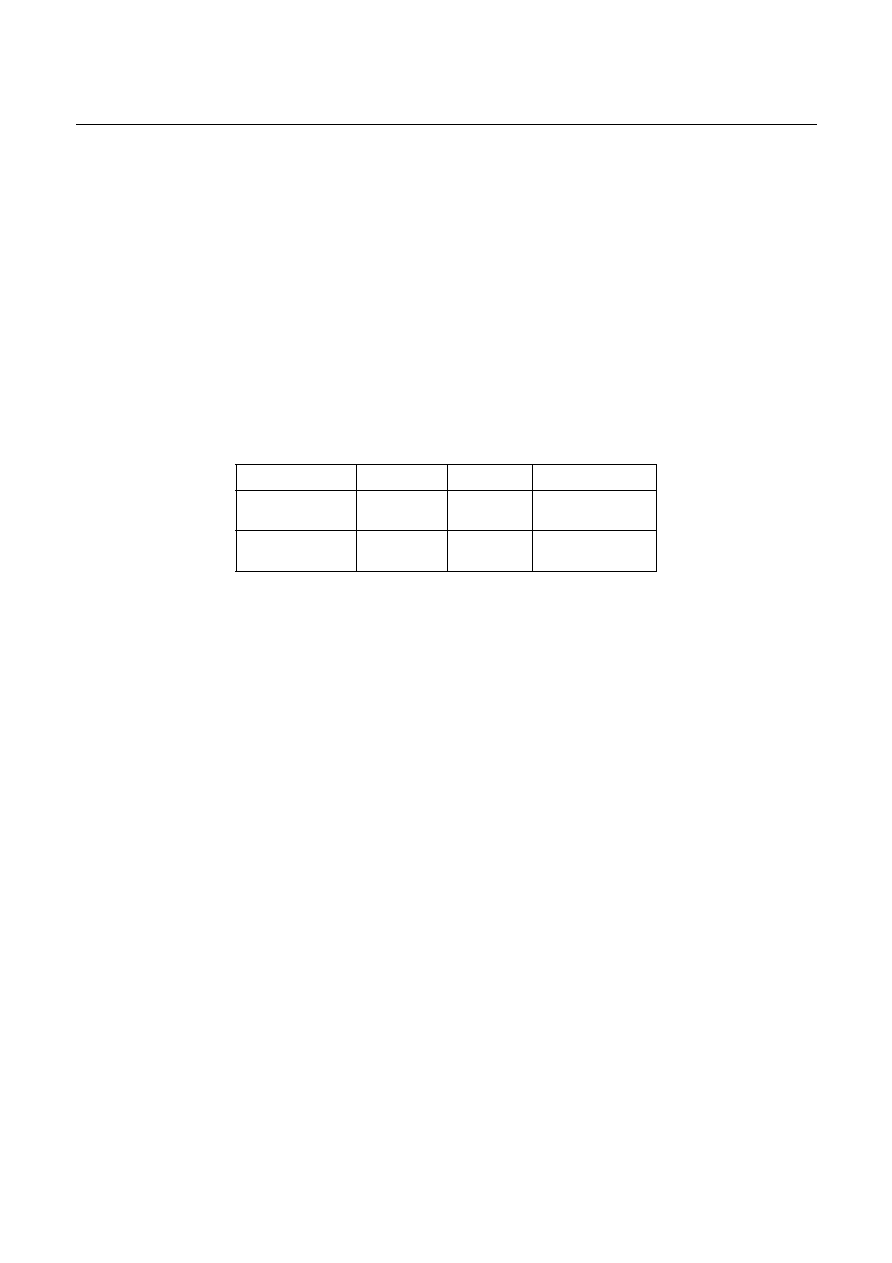

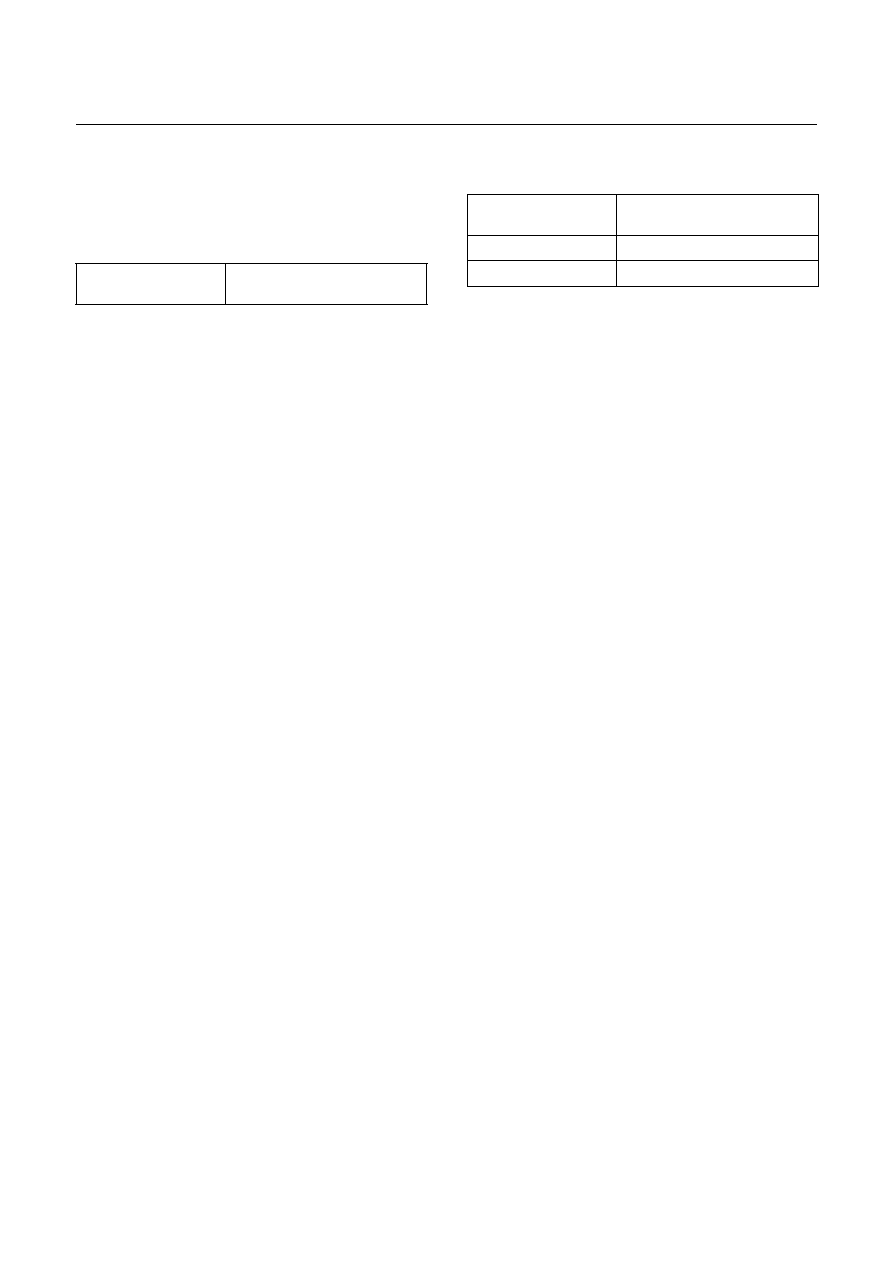

1.3 Development Tools

The GMS81C4040/GMS87C4060 is supported by a full-

featured macro assembler / linker , OSD font editor, an in-

circuit emulator CHOICE-Dr

TM

.

In Circuit Emulators

CHOICE-Dr.

(with EVA81C4xxx board)

Assembler / Linker

HYUNDAI's Macro Assembler /

Linker

Font Editor

MS-Windows GUI version

Debugger

MS-Windows GUI version

HYUNDAI

GMS81C4040/87C4060

May. 2000 Ver 1.0

3

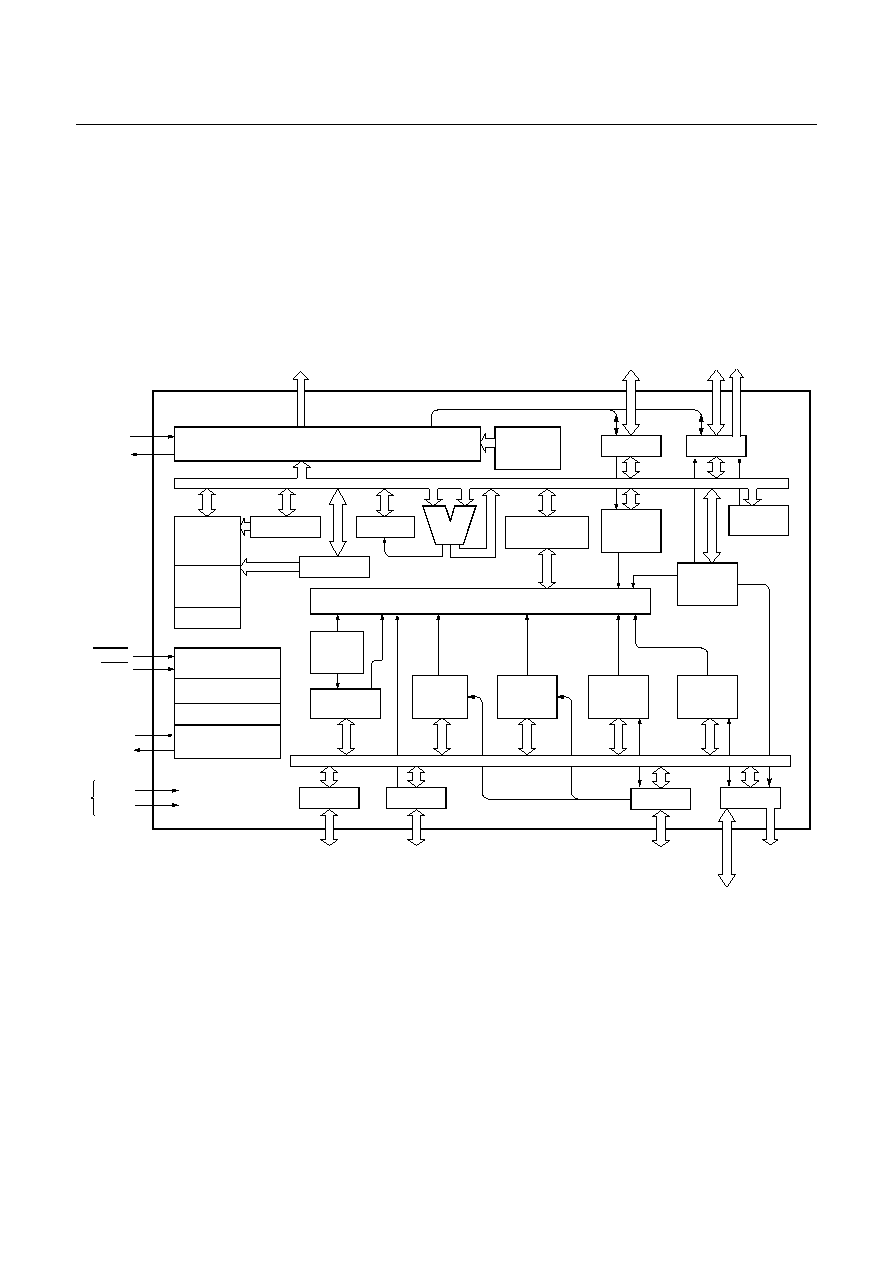

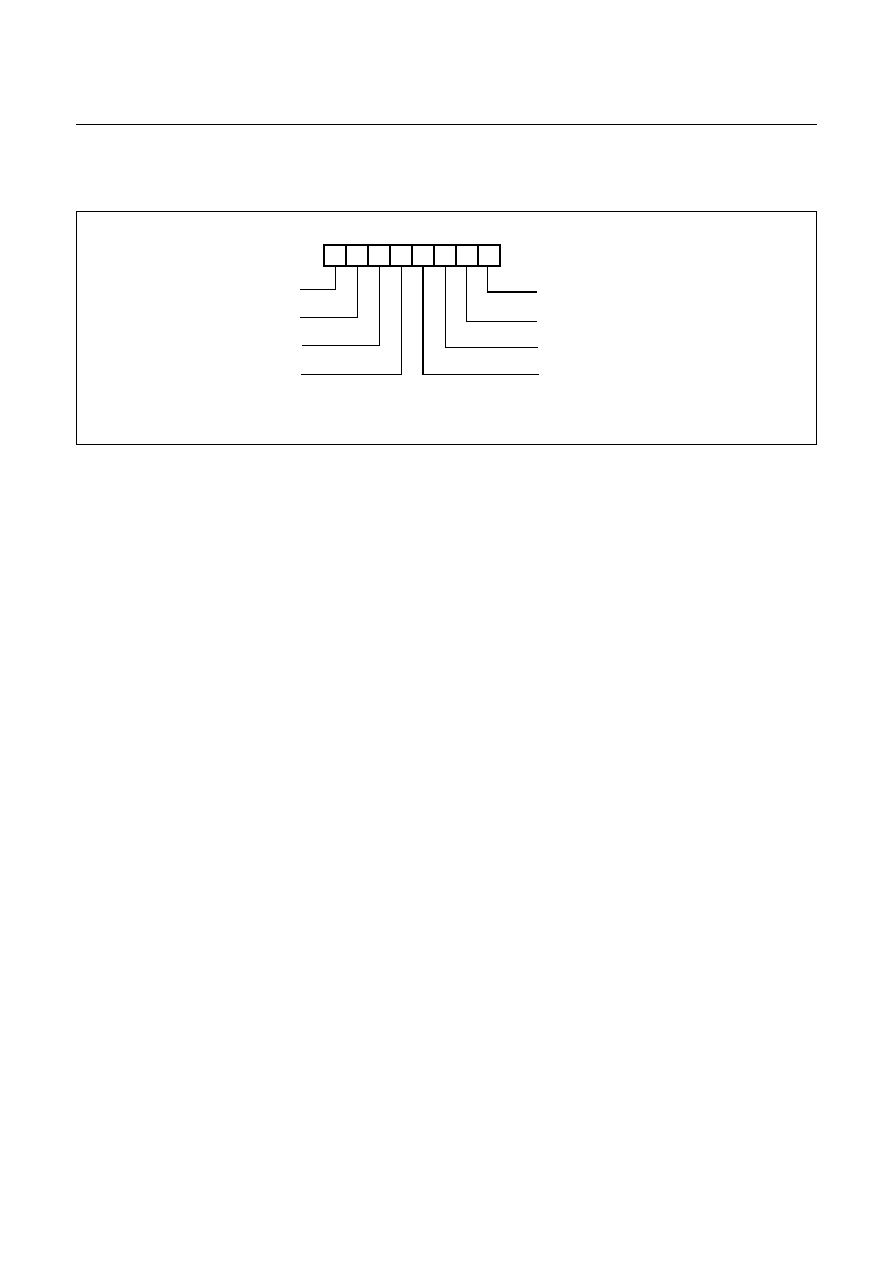

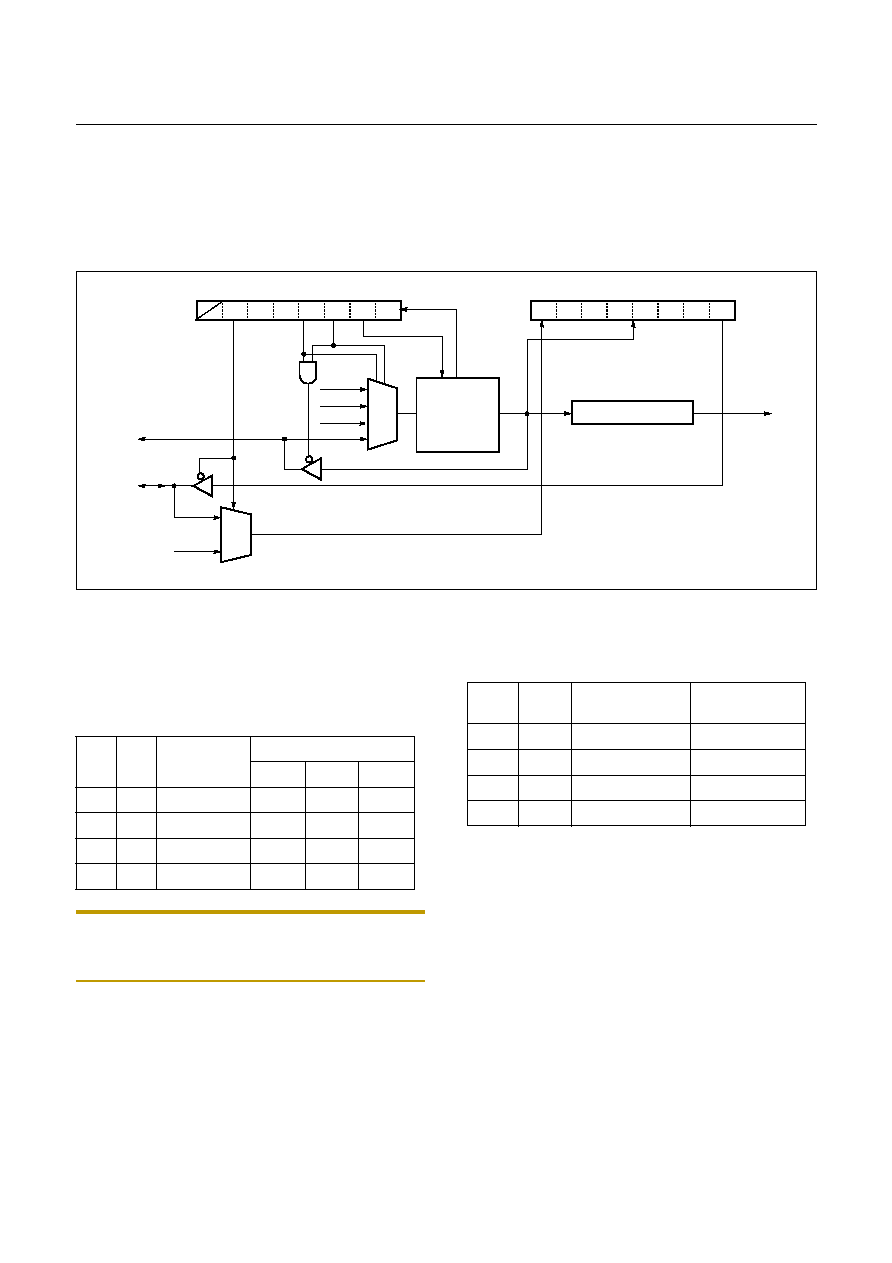

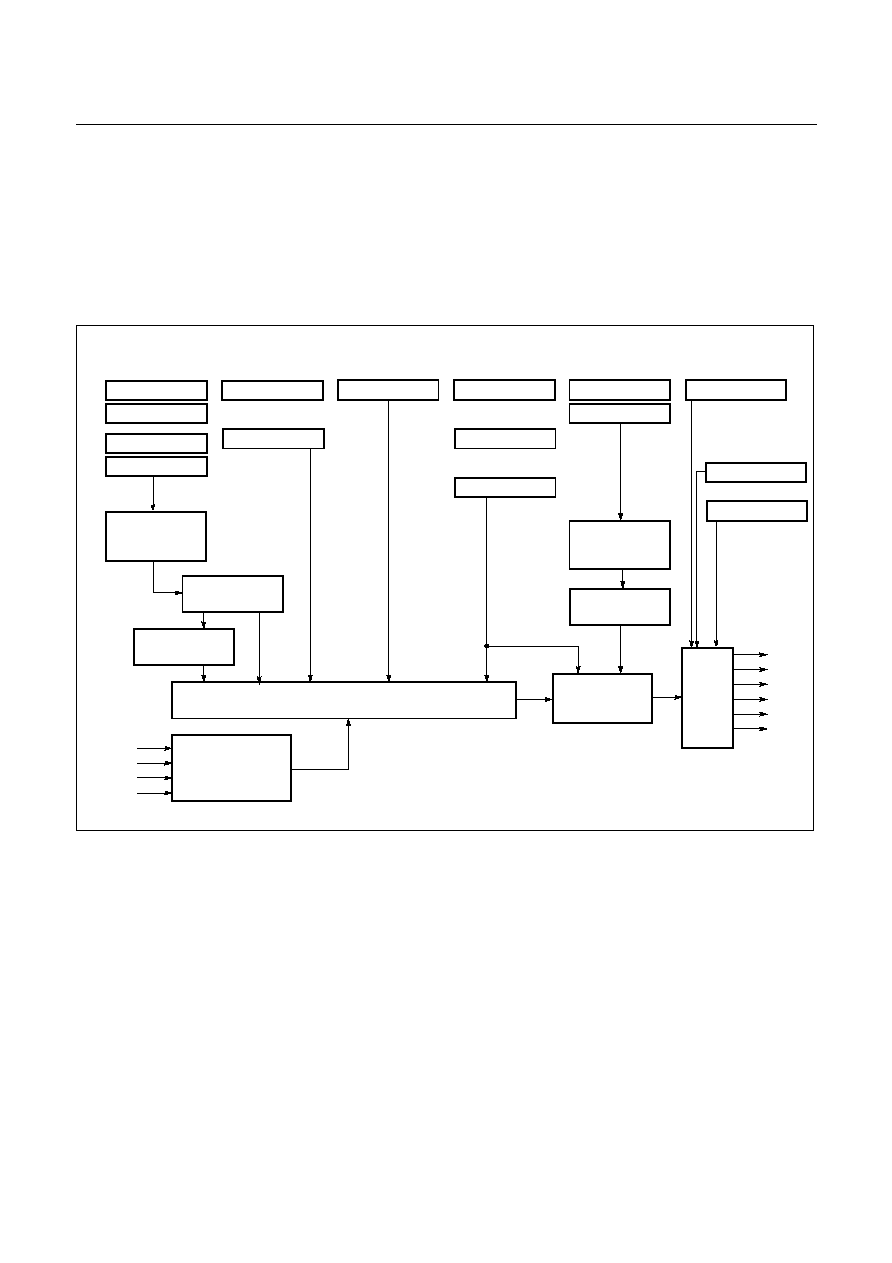

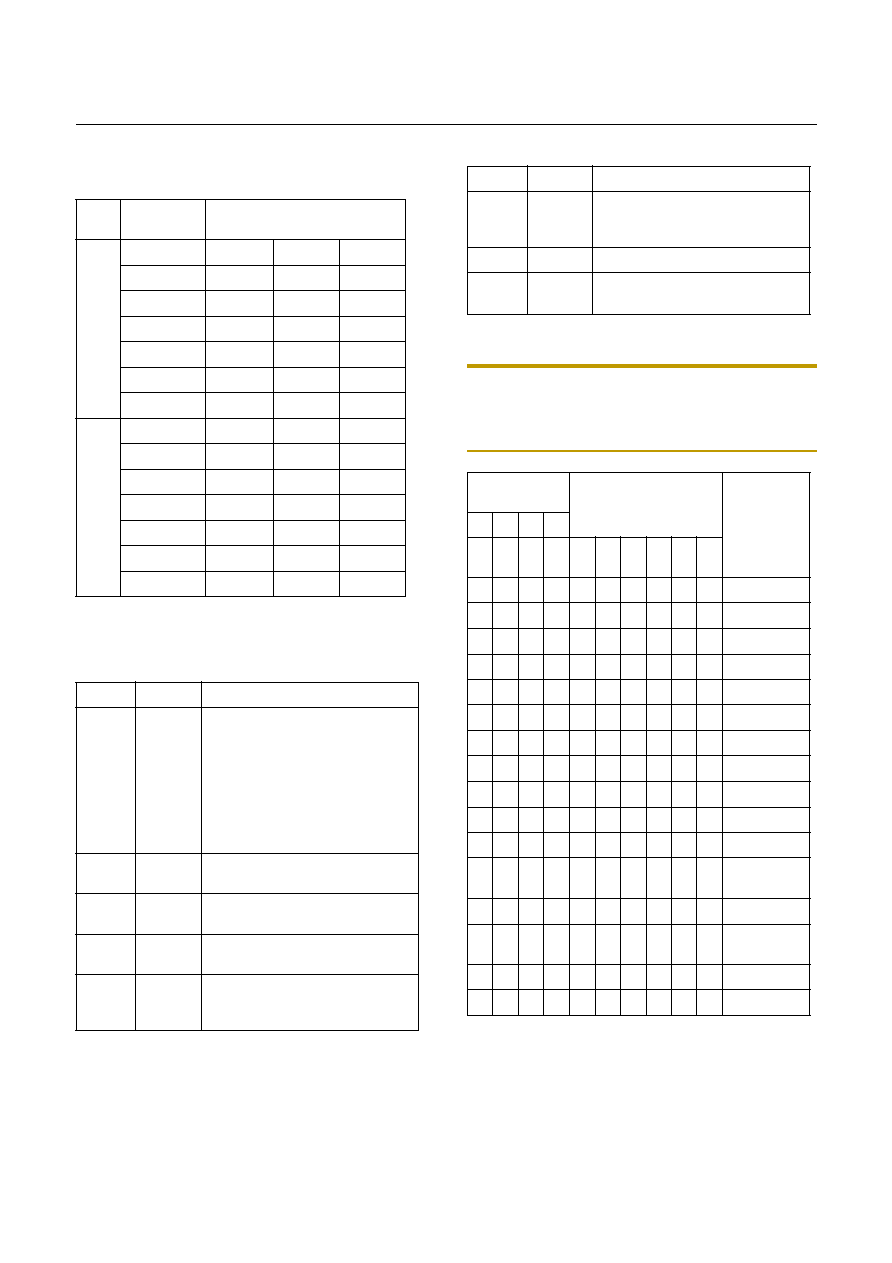

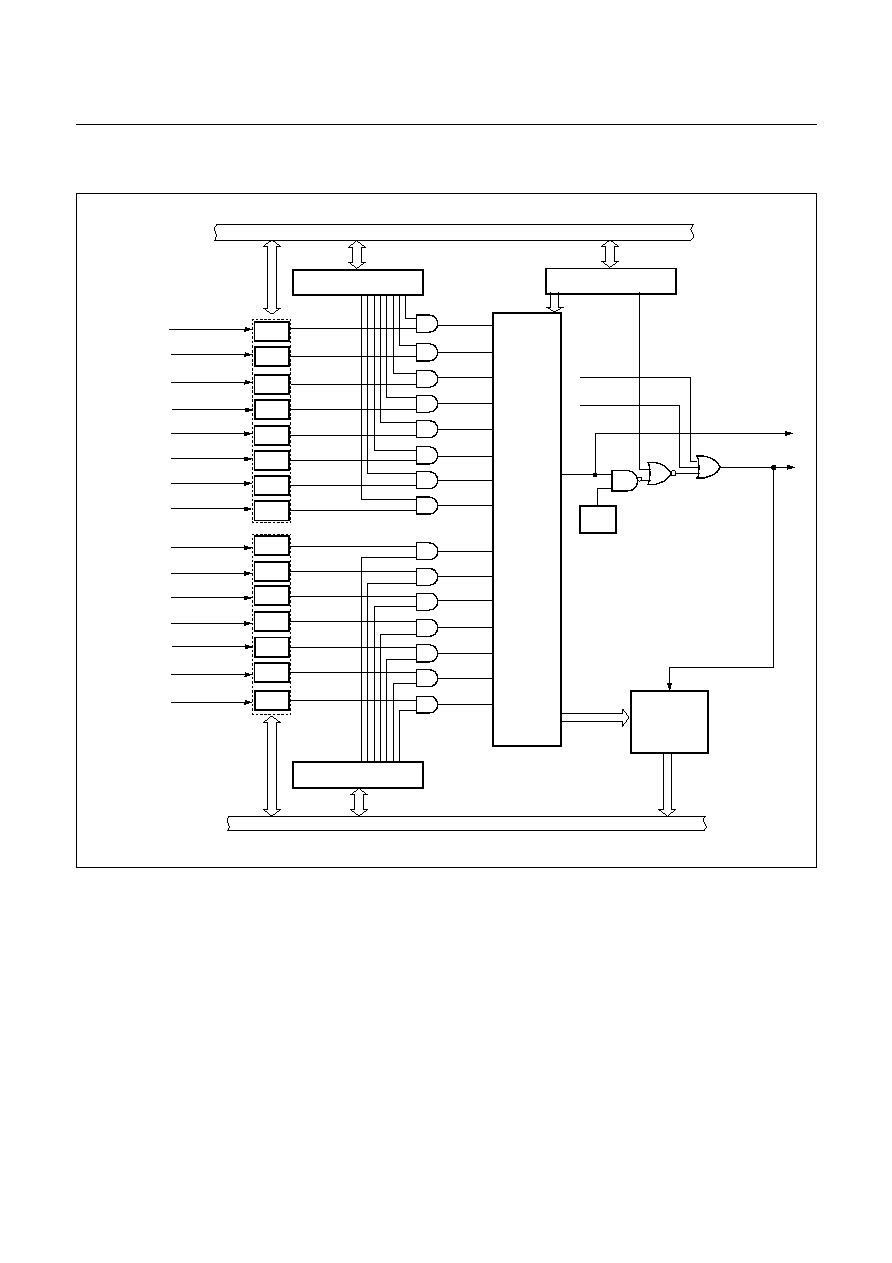

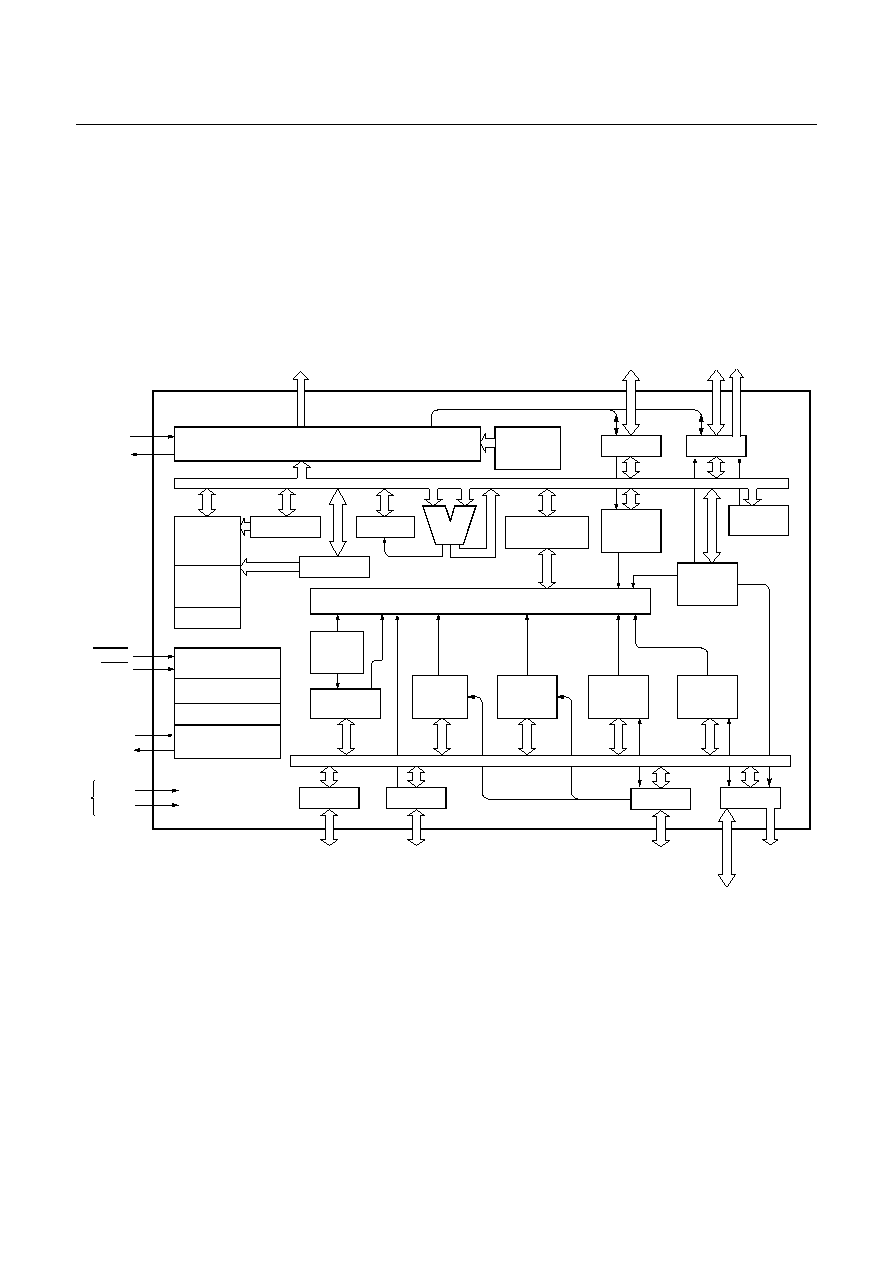

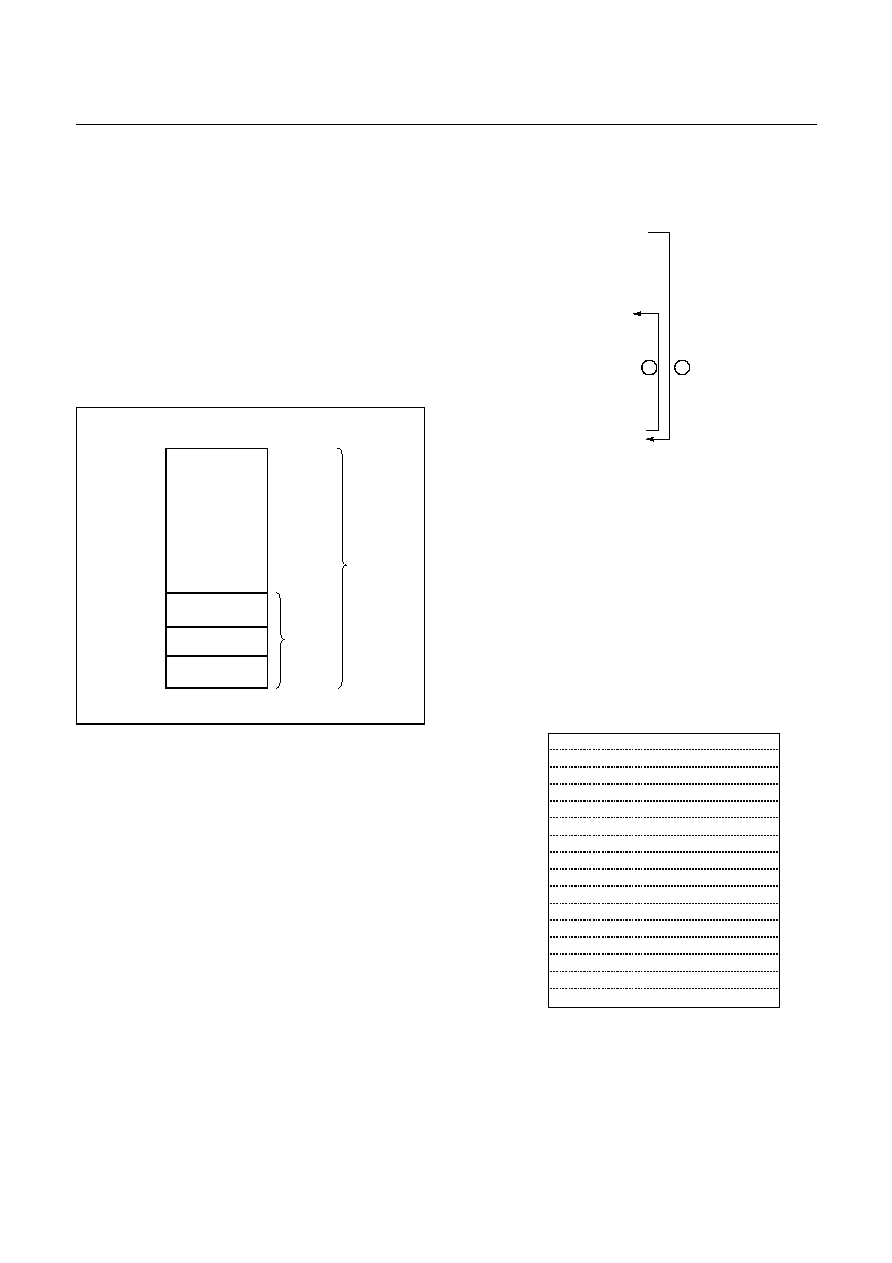

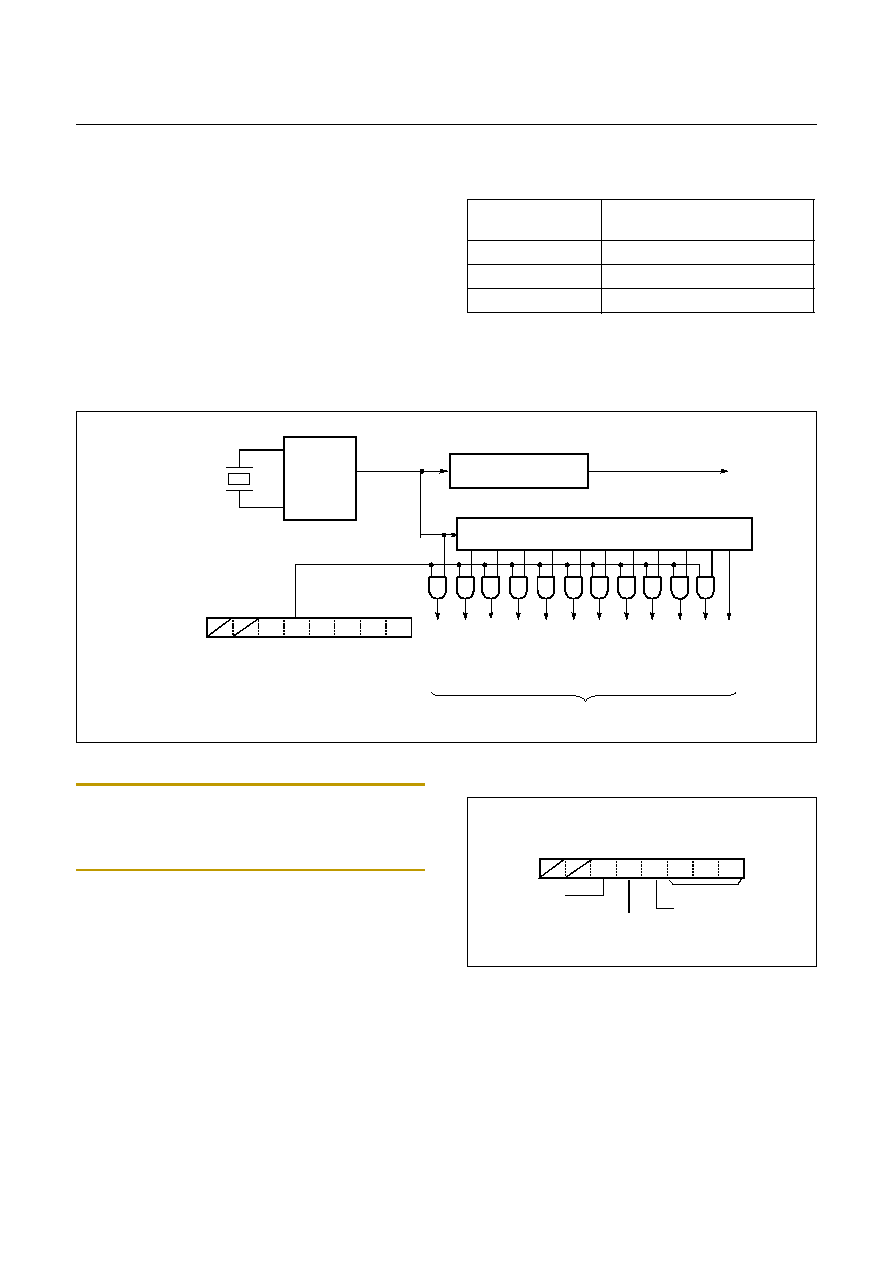

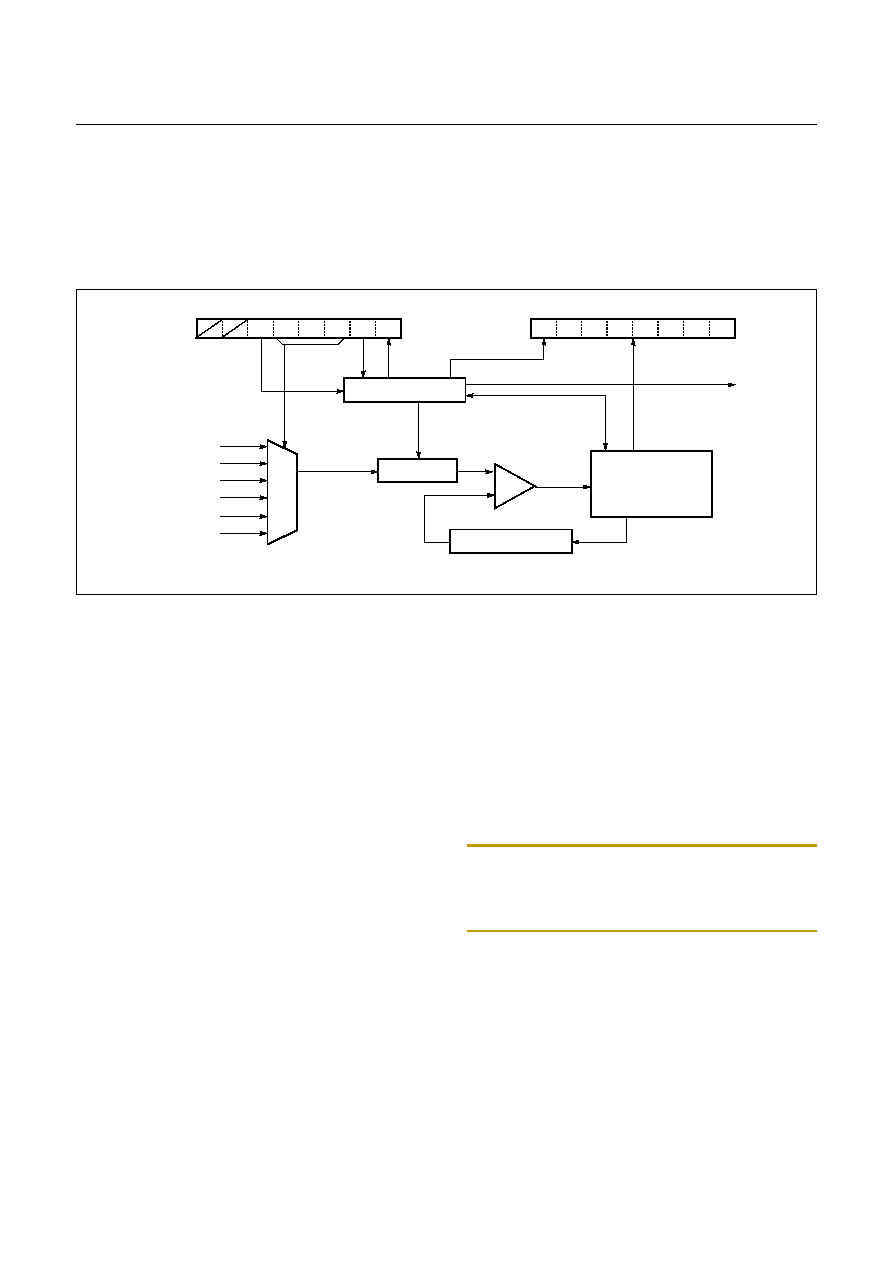

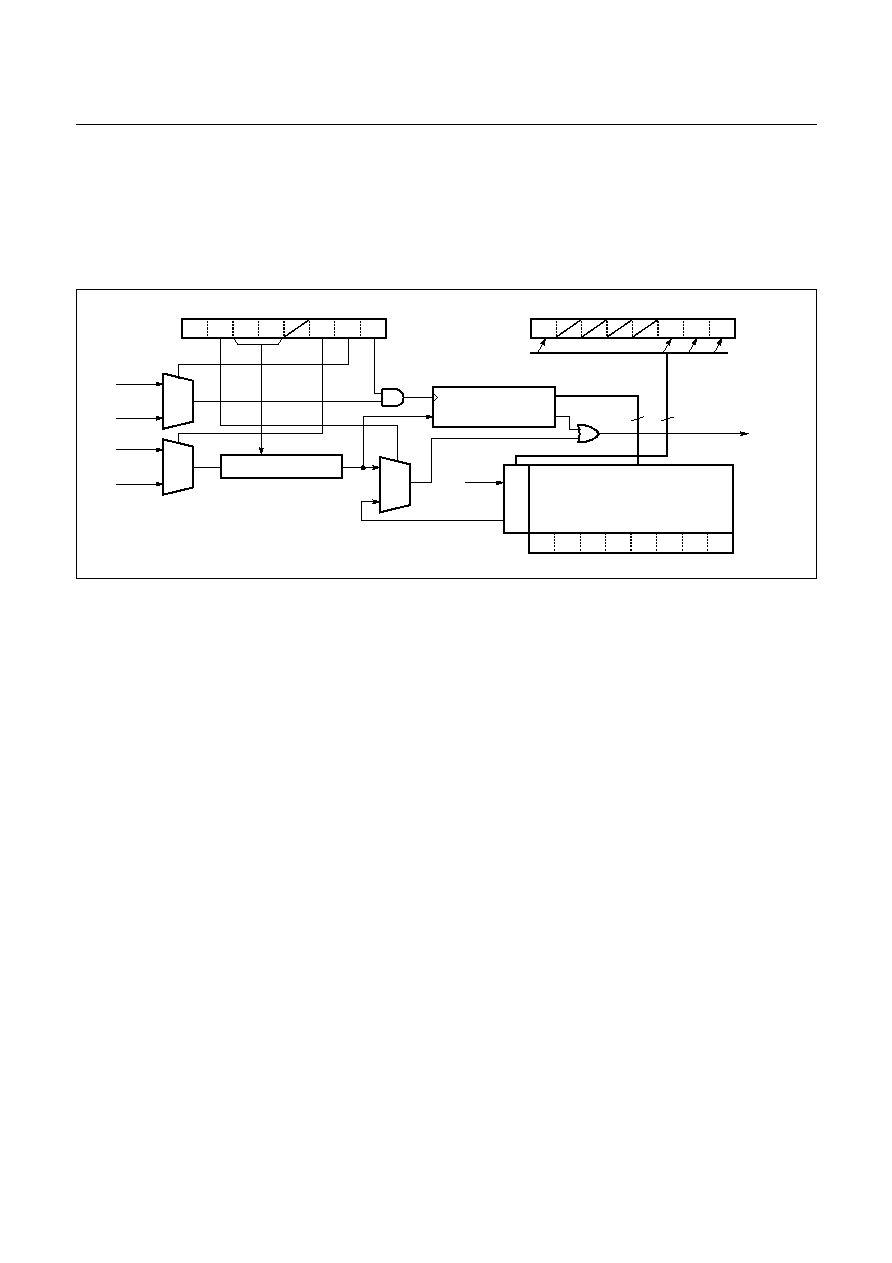

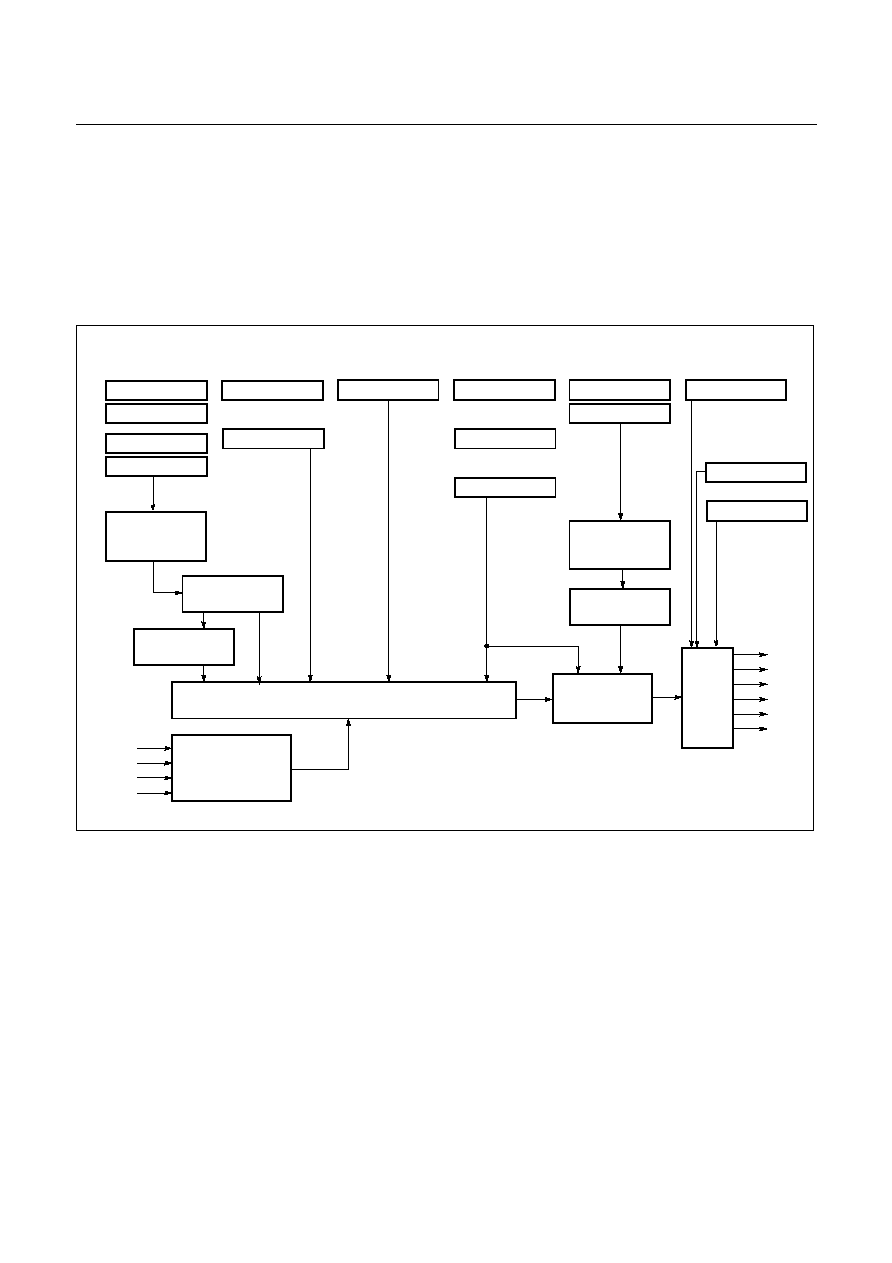

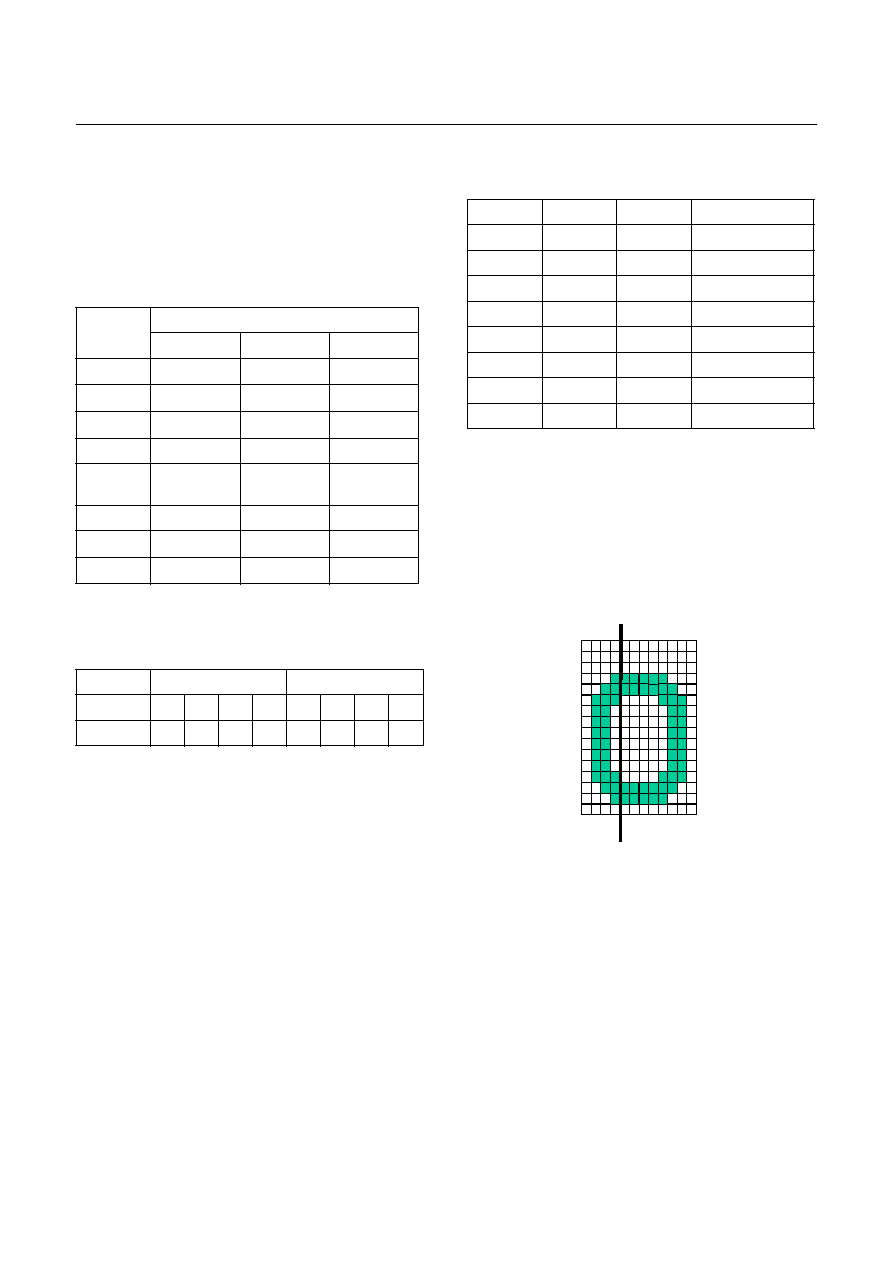

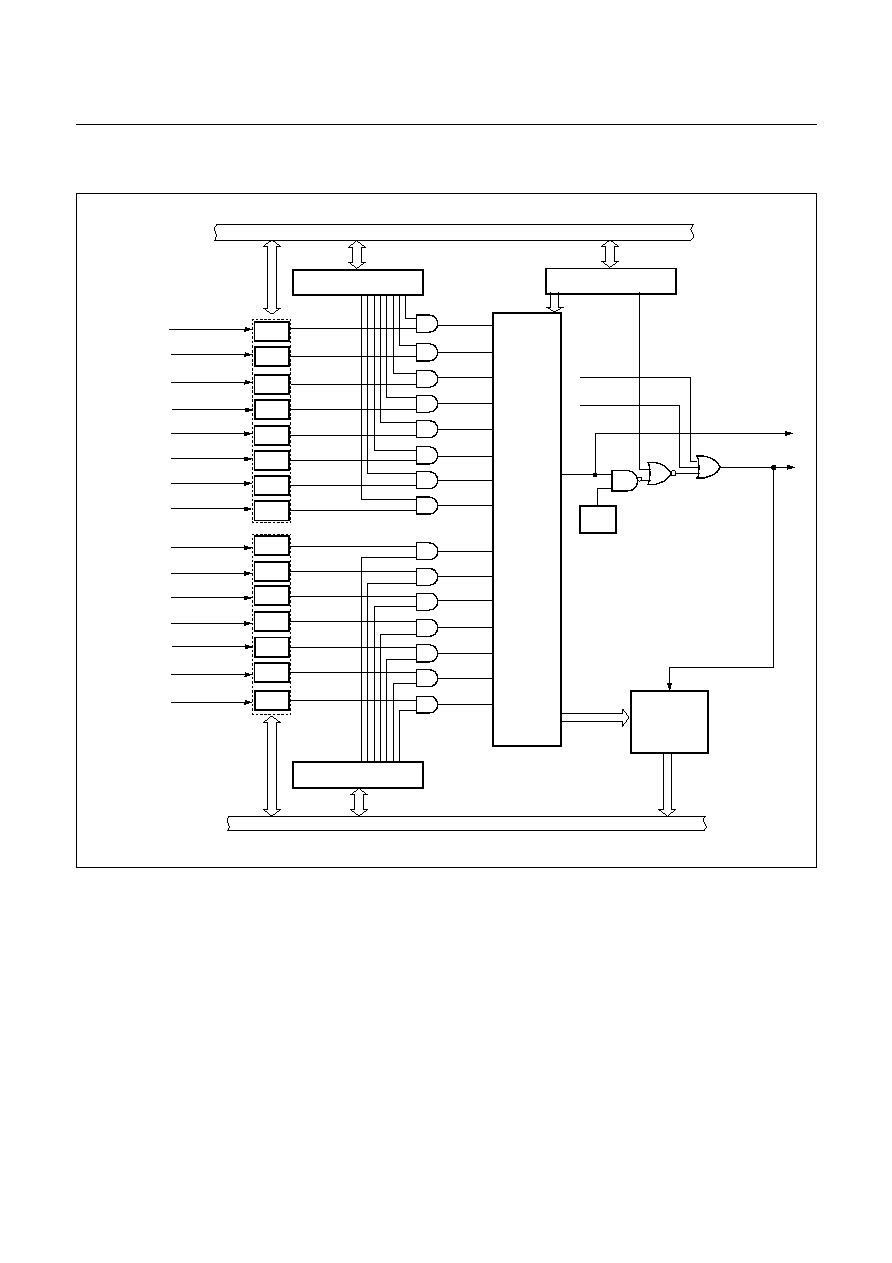

2. BLOCK DIAGRAM

ALU

OSD (On Screen Display) Controller

Accumulator

Interrupt Controller

Data

Memory

OSD

Memory

Display

8-bit x 4

Counter

Timer/

Program

Memory

Vector Table

8-bit Basic

Tim er

Interval

Watchdog

Timer

PSW

System controller

Timing generator

System

Clock Controller

RESET

TEST

XIN

XOUT

OSC1

OSC2

R,G,B

VDD

VSS

Power

Supply

R 1

Clock generator

& Index X,Y

8bit A/D

C on verto r

Buzzer

R 5

PWM

14 bit x 1

8b it x 6

D a t a b u s

I

2

C

In te rface

R 4

D a t a b u s

Serial I/O

In terfa ce

Interrupt

In te rva l

M ea sure

R 2

R 0

R 6

Stack pointer

PC

R00

R01

R02

R03

R04

R05

R06

R07

R67 / INT1

R20 / INT2

R21 / Sclk

R22 / Sout

R23 / Sin

R24 / INT3

R25 / EC2

R26 / INT4

R27 / EC3

R40 / PWM0

R41 / PWM1

R42 / PWM2

R43 / PWM3

R44 / SCL0

R45 / SCL1 / PWM4

R46 / SDA0

R47 / SDA1 / PWM5

R10 / AN0

R11 / AN1

R12 / AN2

R13 / AN3

R14 / AN4

R15 / AN5

R16 / VD

R17 / HD

R50 / BUZZ

R51 / PWM8

R52 / INT0

R53

R54 / YM

R55 / YS

R56 / I

GMS81C4040/87C4060

HYUNDAI

4

May. 2000 Ver 1.0

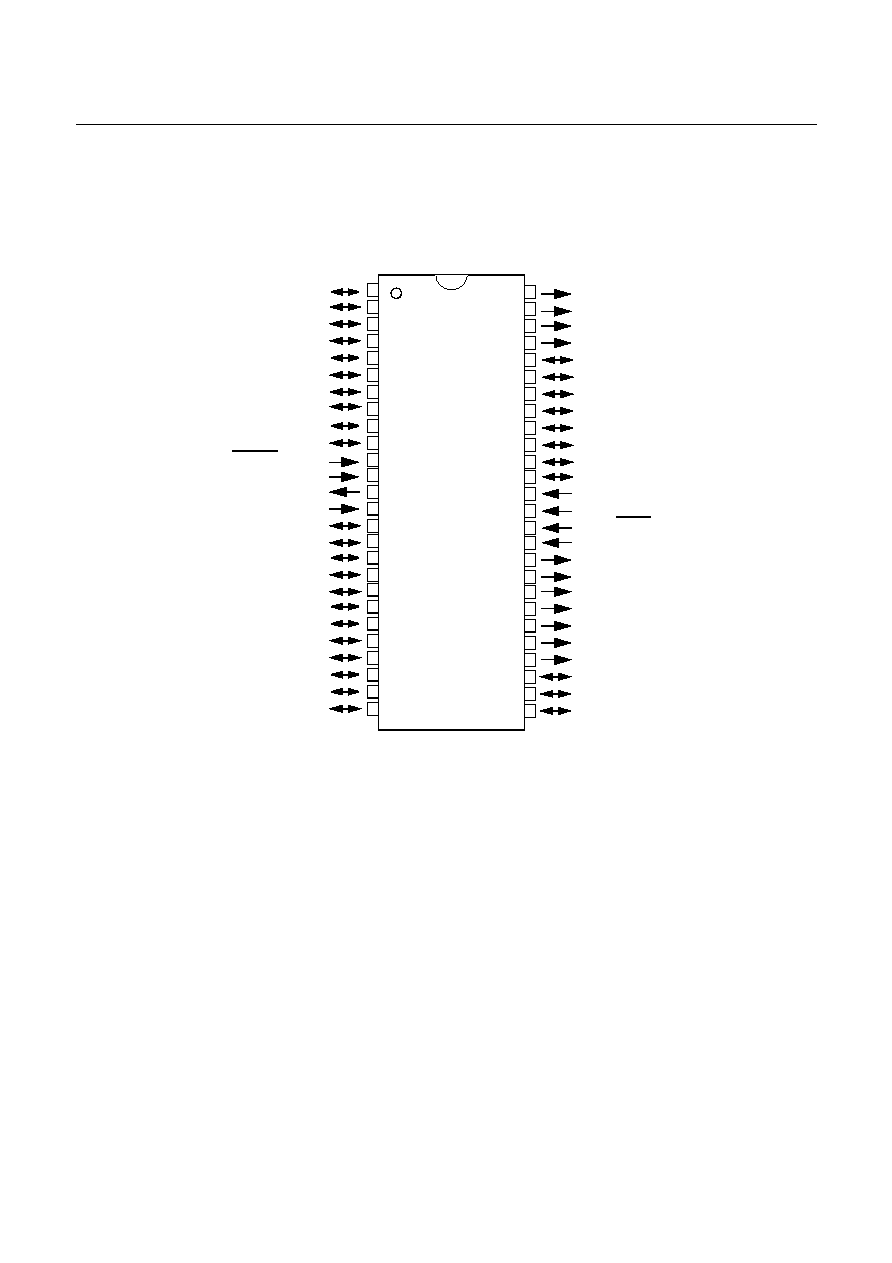

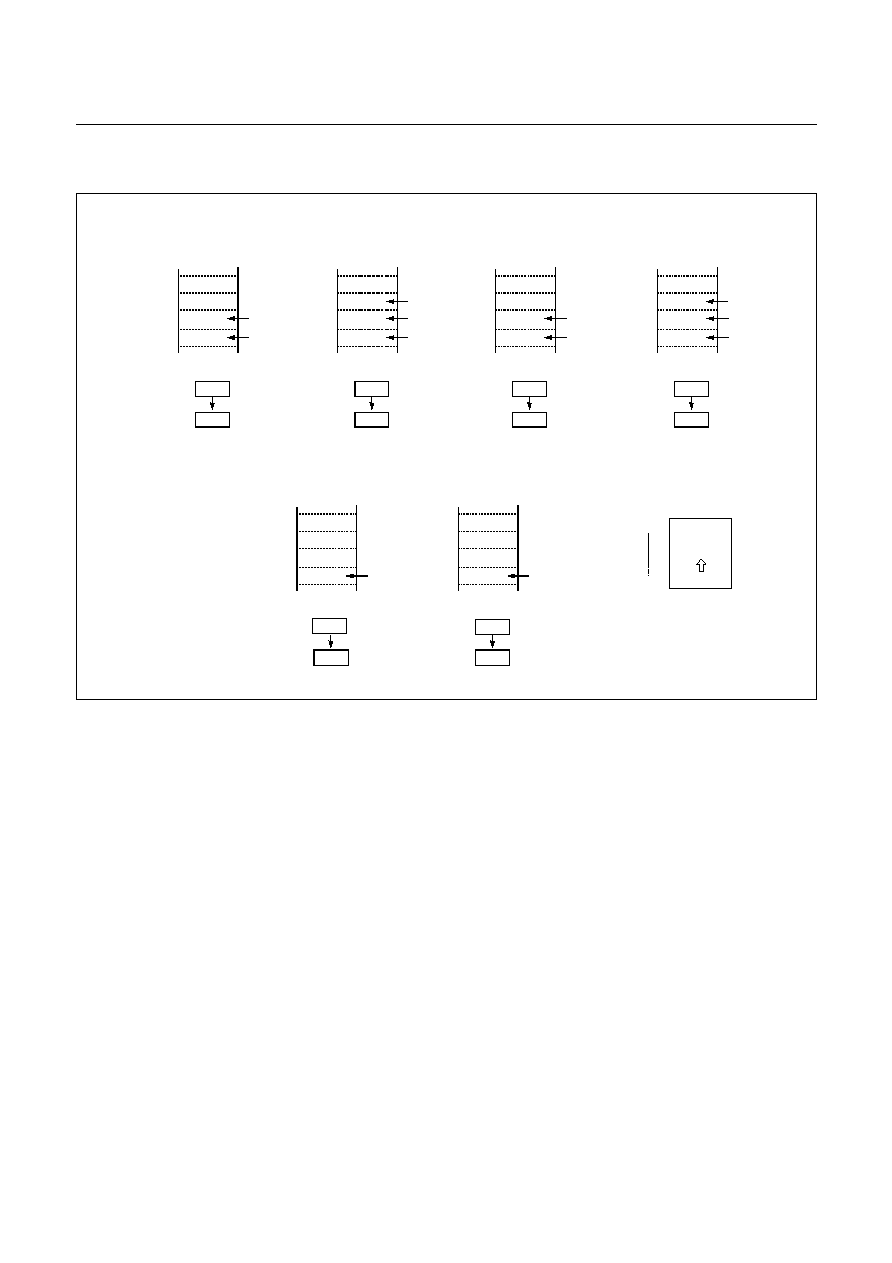

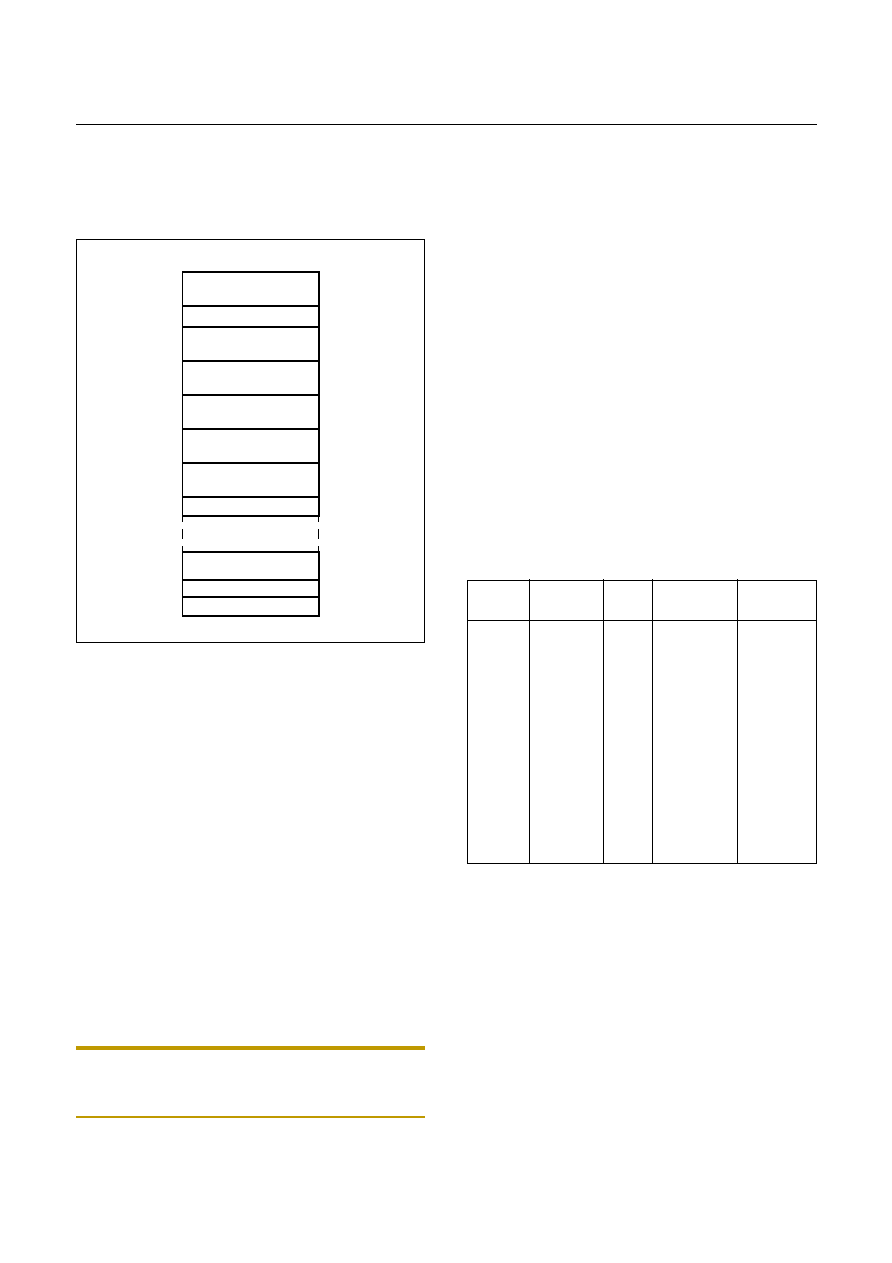

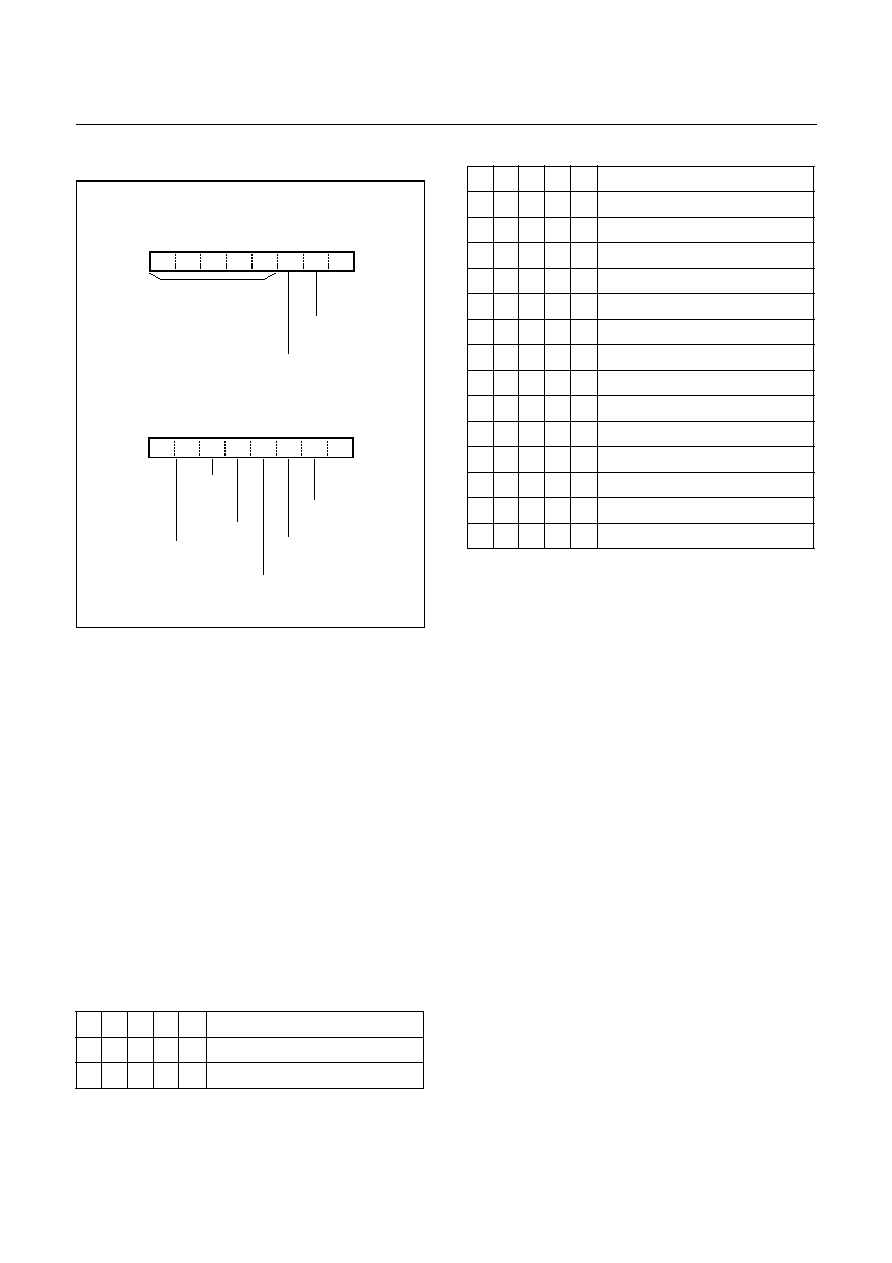

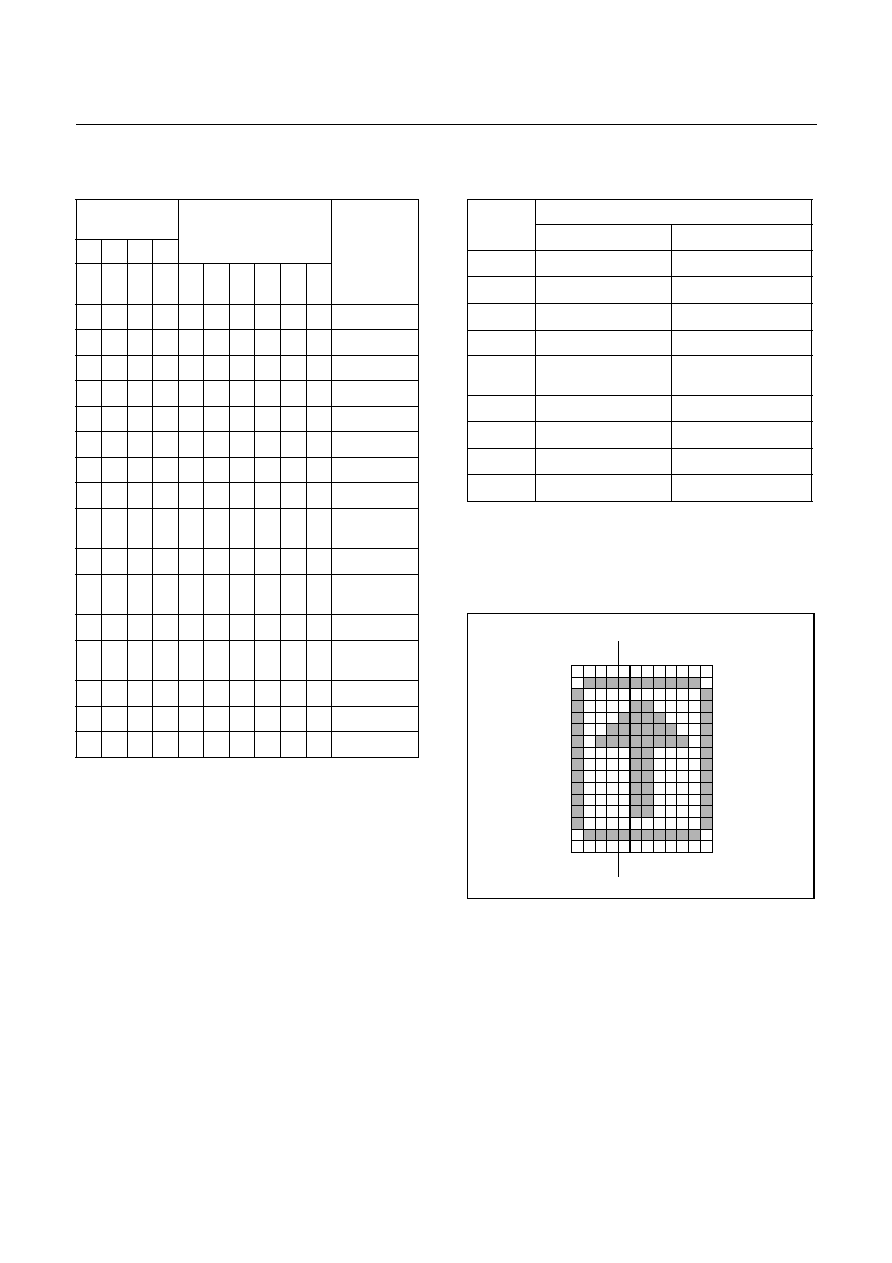

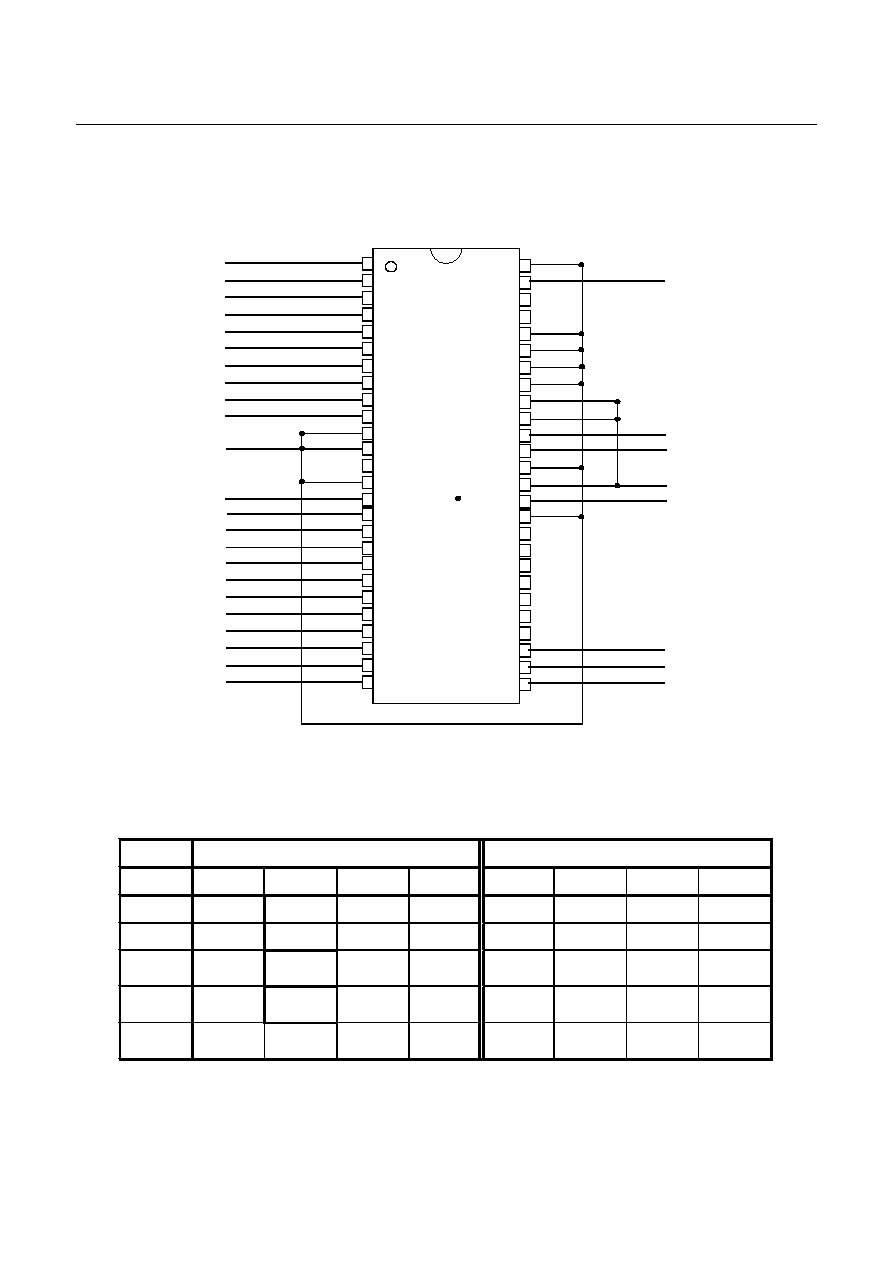

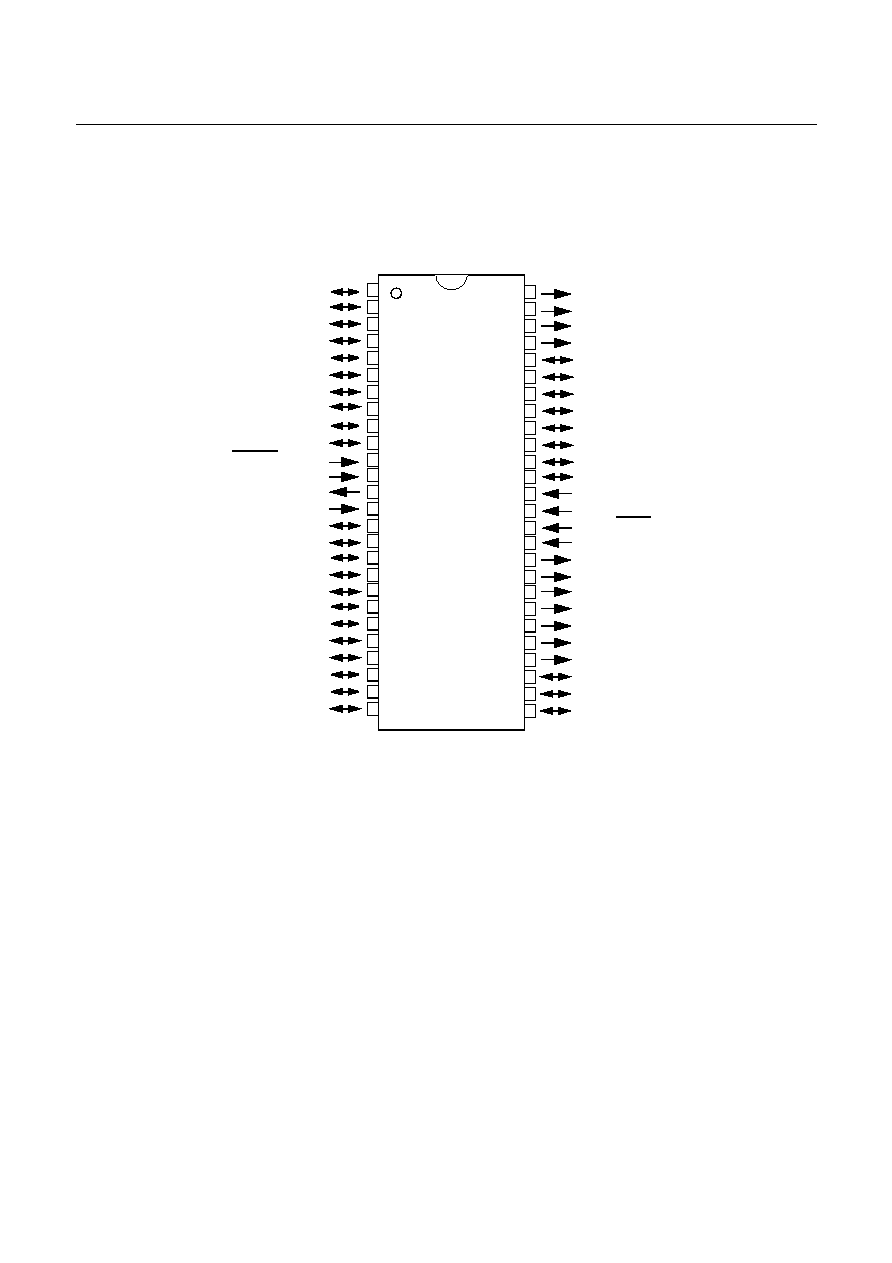

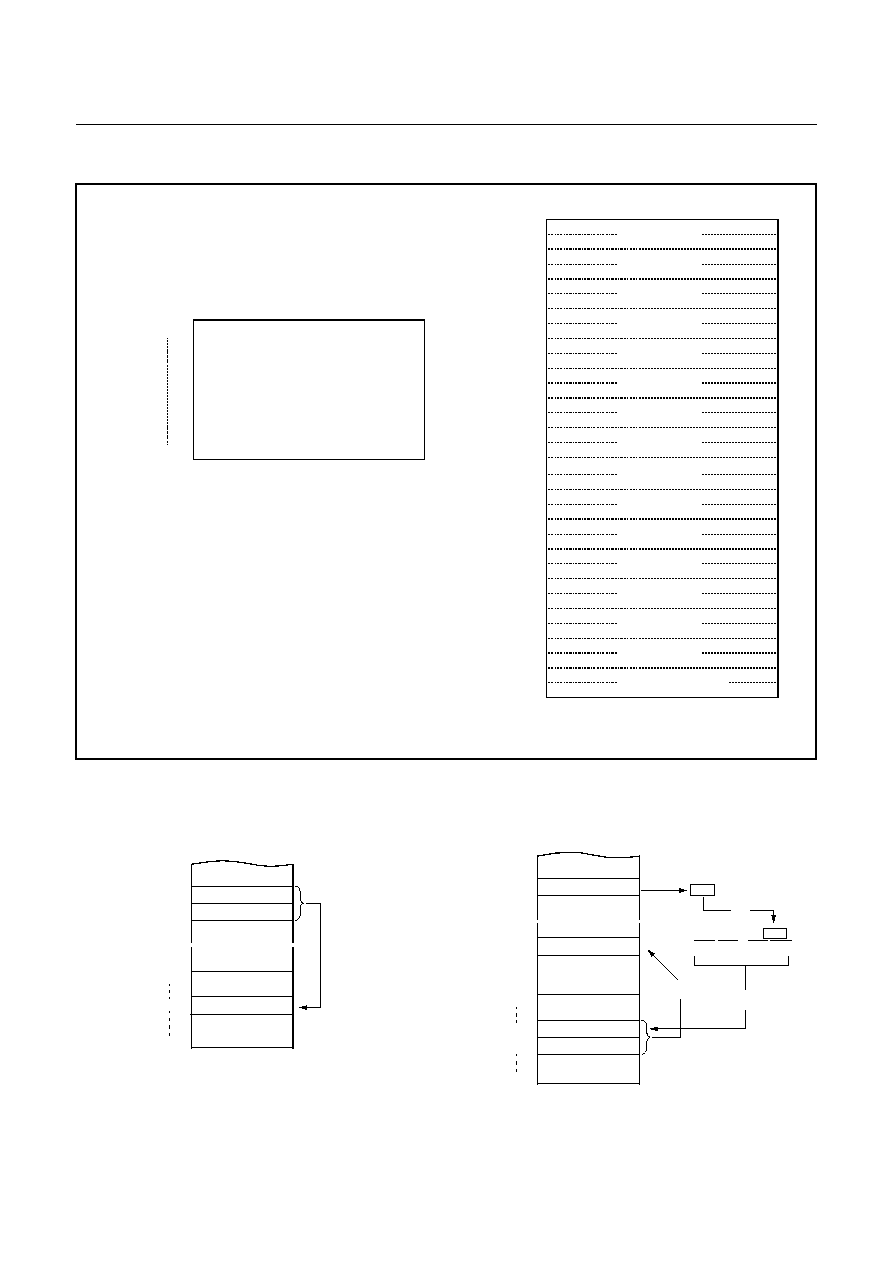

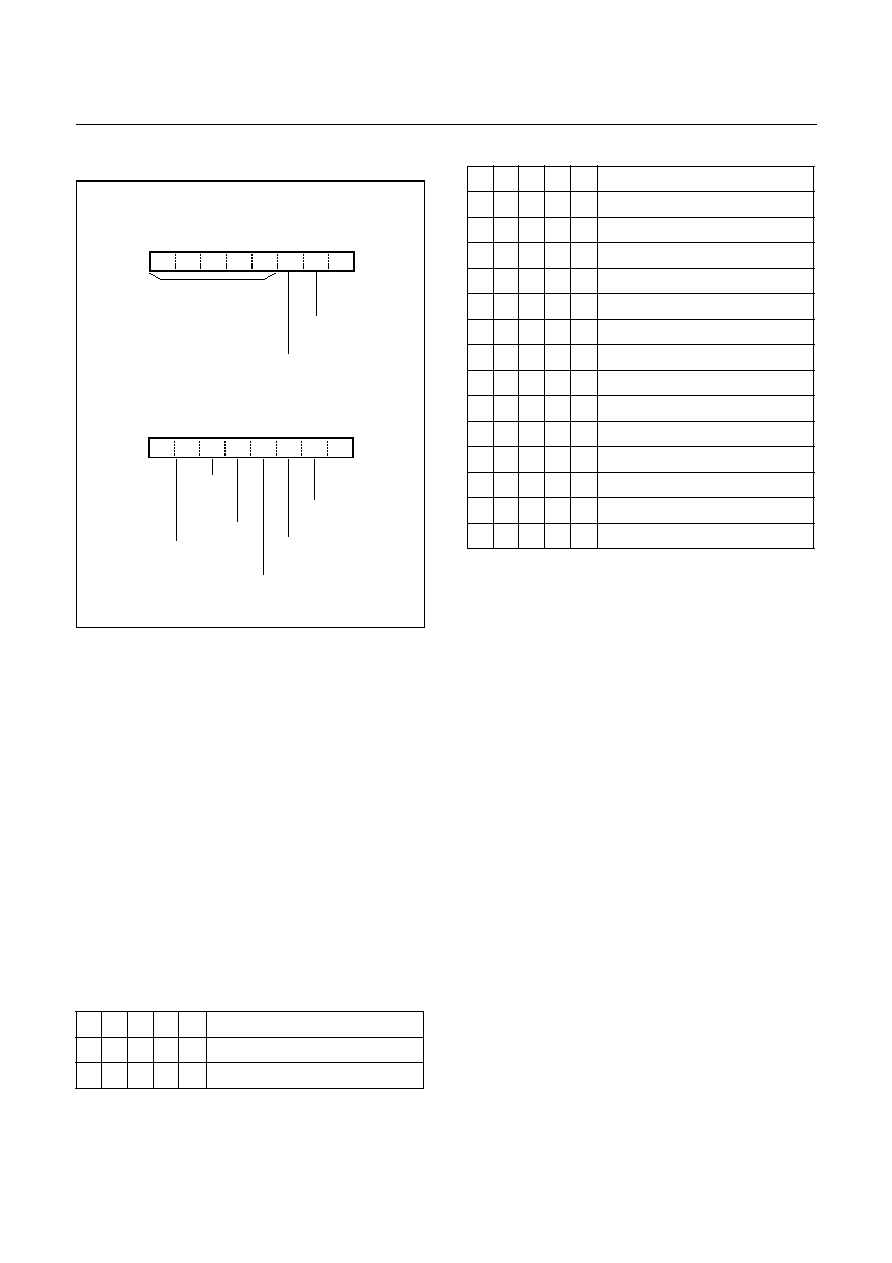

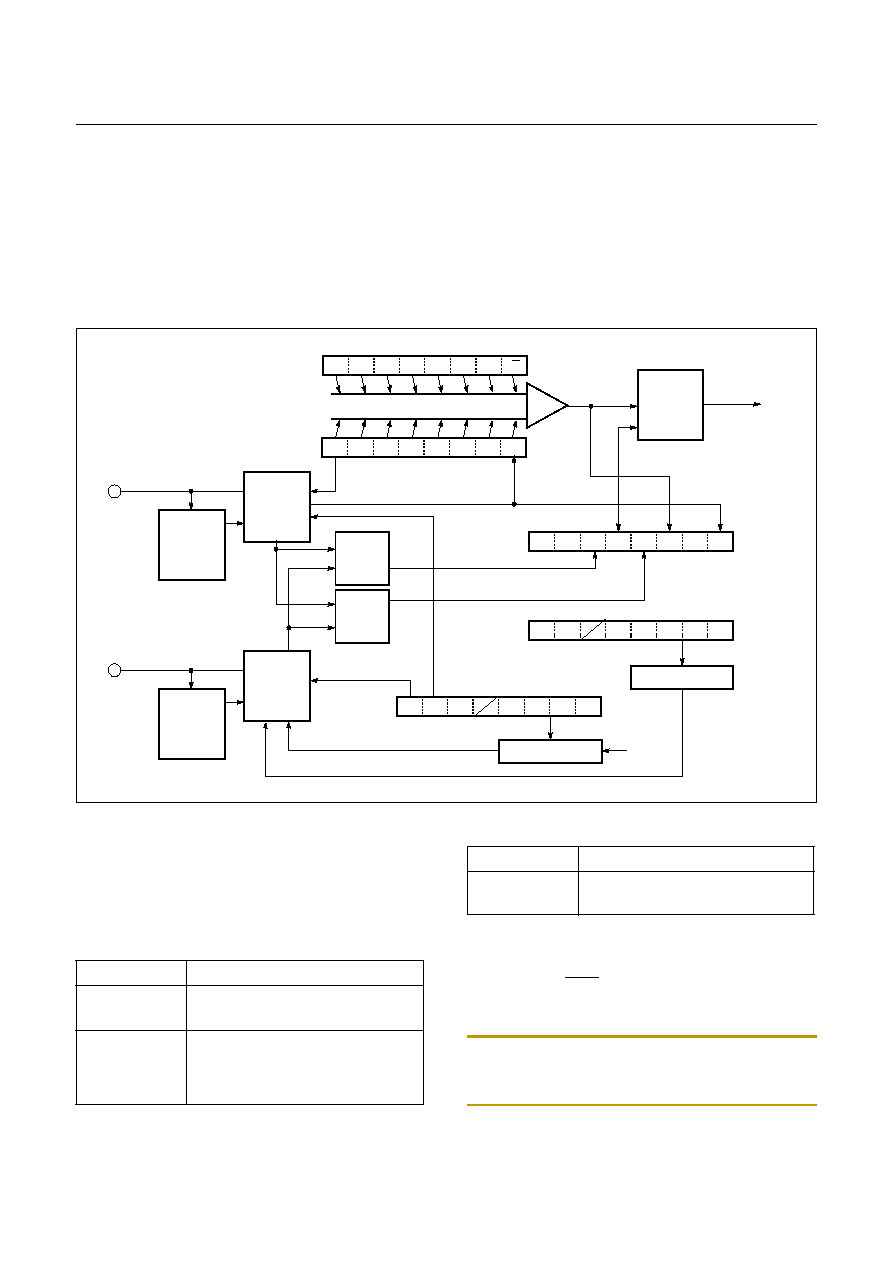

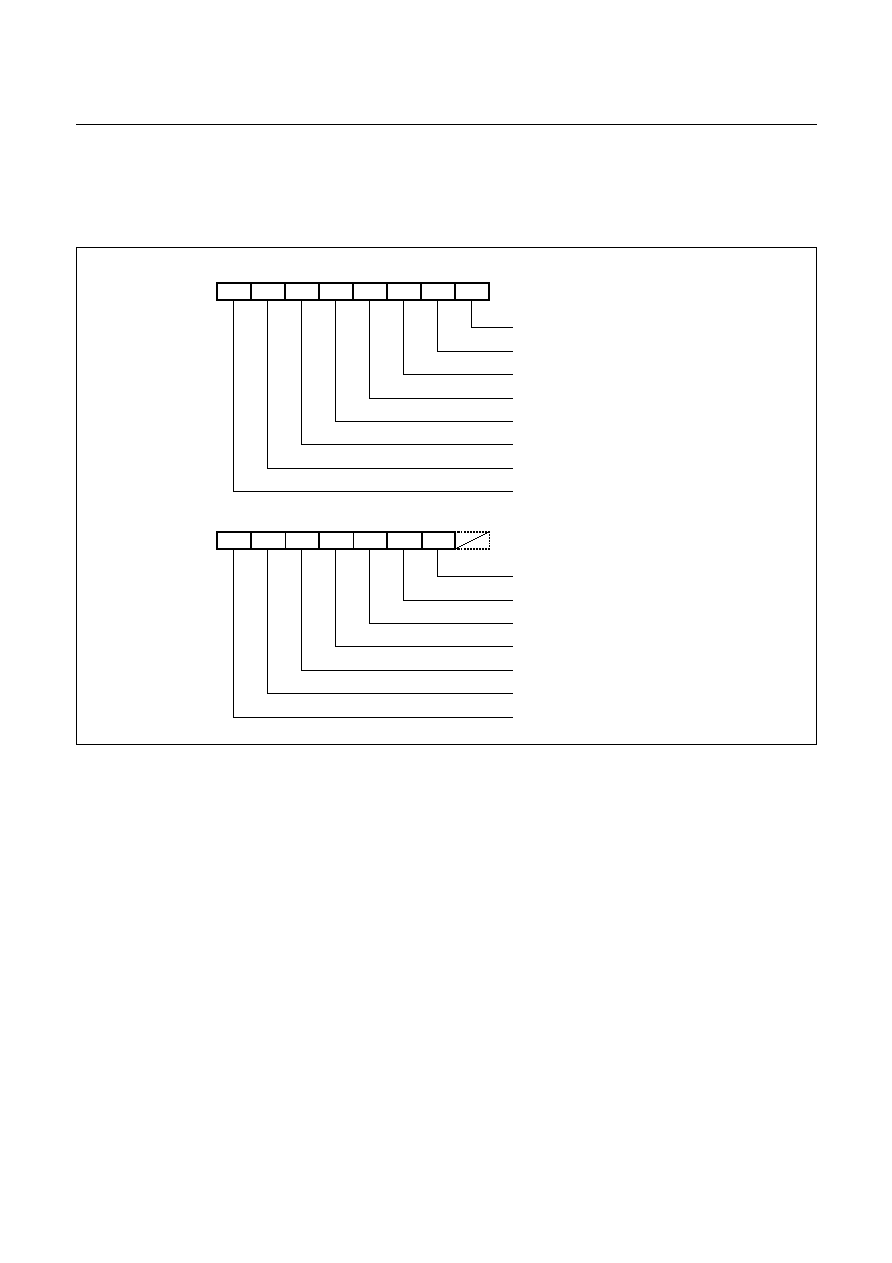

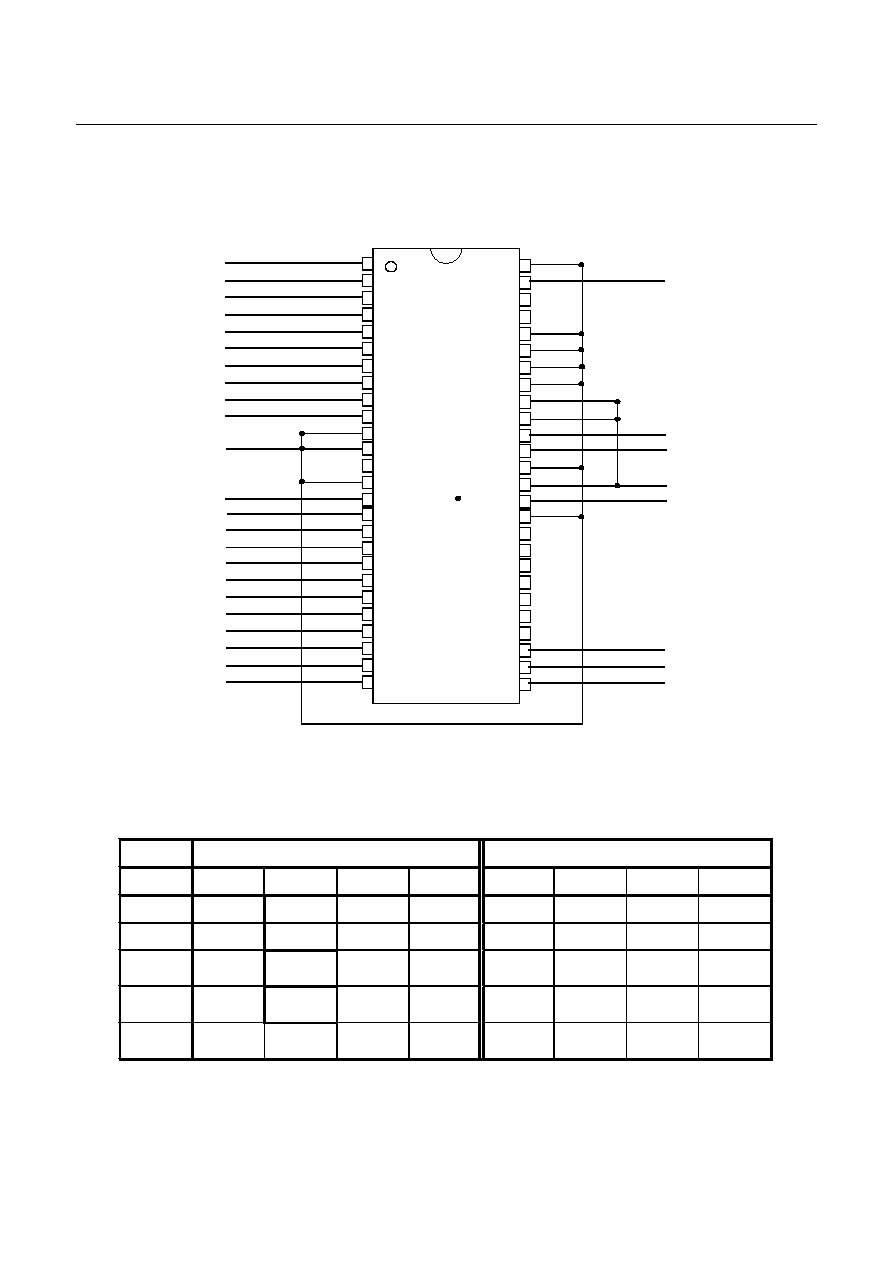

3. PIN ASSIGNMENT

R40/PWM0

R41/PWM1

R42/PWM2

R43/PWM3

R44/SCL0

R45/SCL1/PWM4

R46/SDA0

R47/SDA1/PWM5

R50/BUZZ

R51/PWM8

R52/INT0

R53

Vss

Vdd

TEST

OSC1

OSC2

R54/YM

R55/YS

R56/I

B

G

R

R00

R01

R02

R27/EC3

R26/INT4

R25/EC2

R24/INT3

R23/Sin

R22/Sout

R21/Sclk

R20/INT2

R17/HD

R16/VD

RESET

Vss

Xout

Xin

R15/AN5

R14/AN4

R13/AN3

R12/AN2

R11/AN1

R10/AN0

R07

R06

R05

R04

R03

R67/INT1

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

HY

UNDAI

GMS8

1C40

XX

HYUNDAI

GMS81C4040/87C4060

May. 2000 Ver 1.0

5

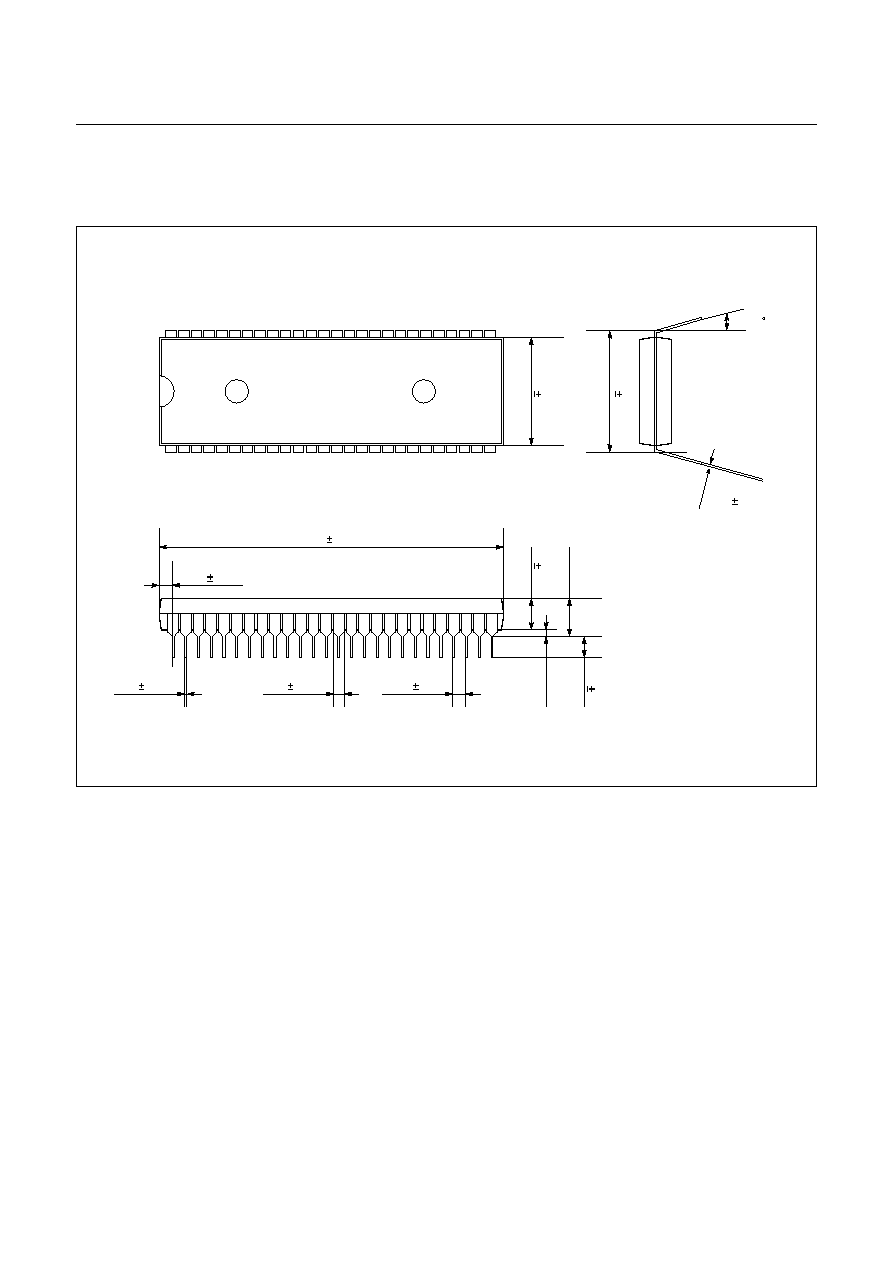

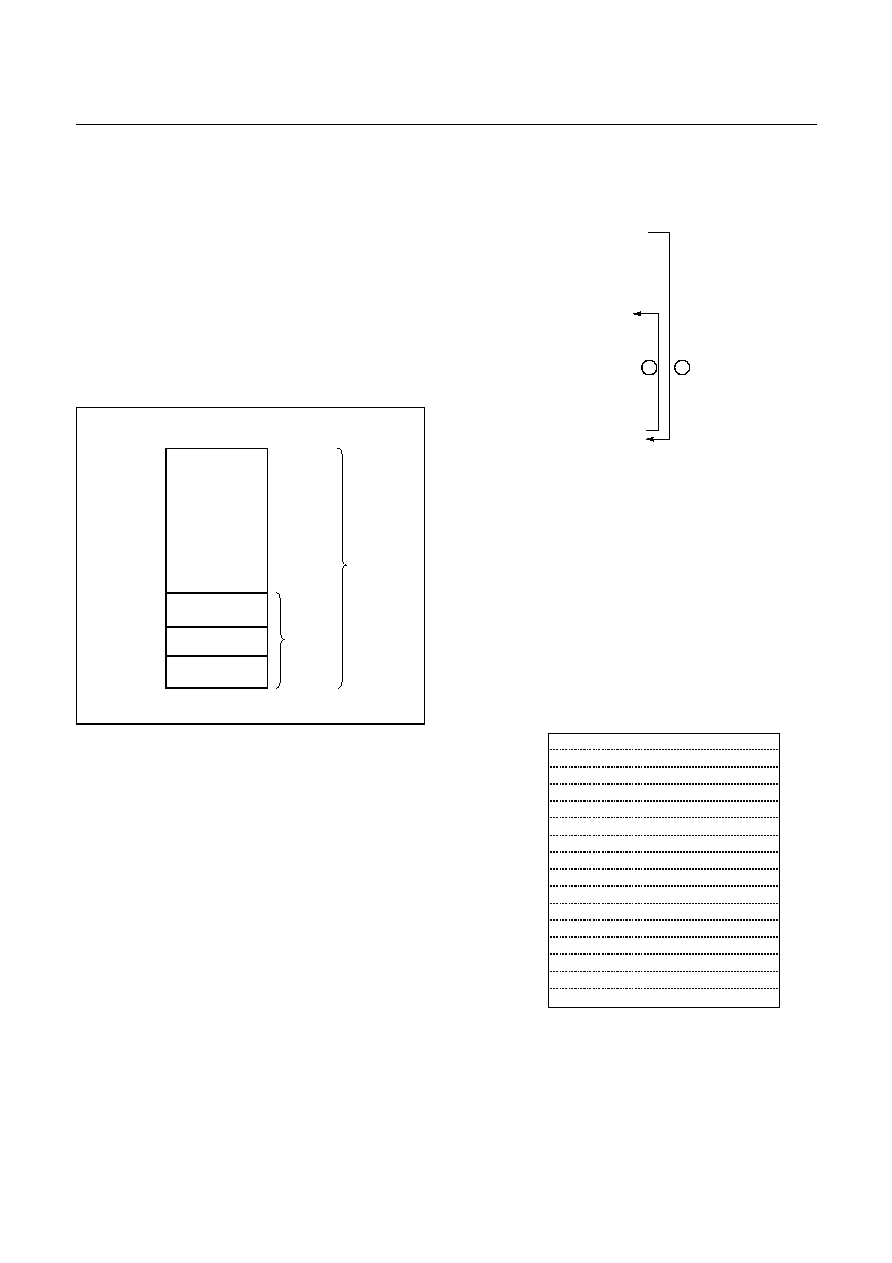

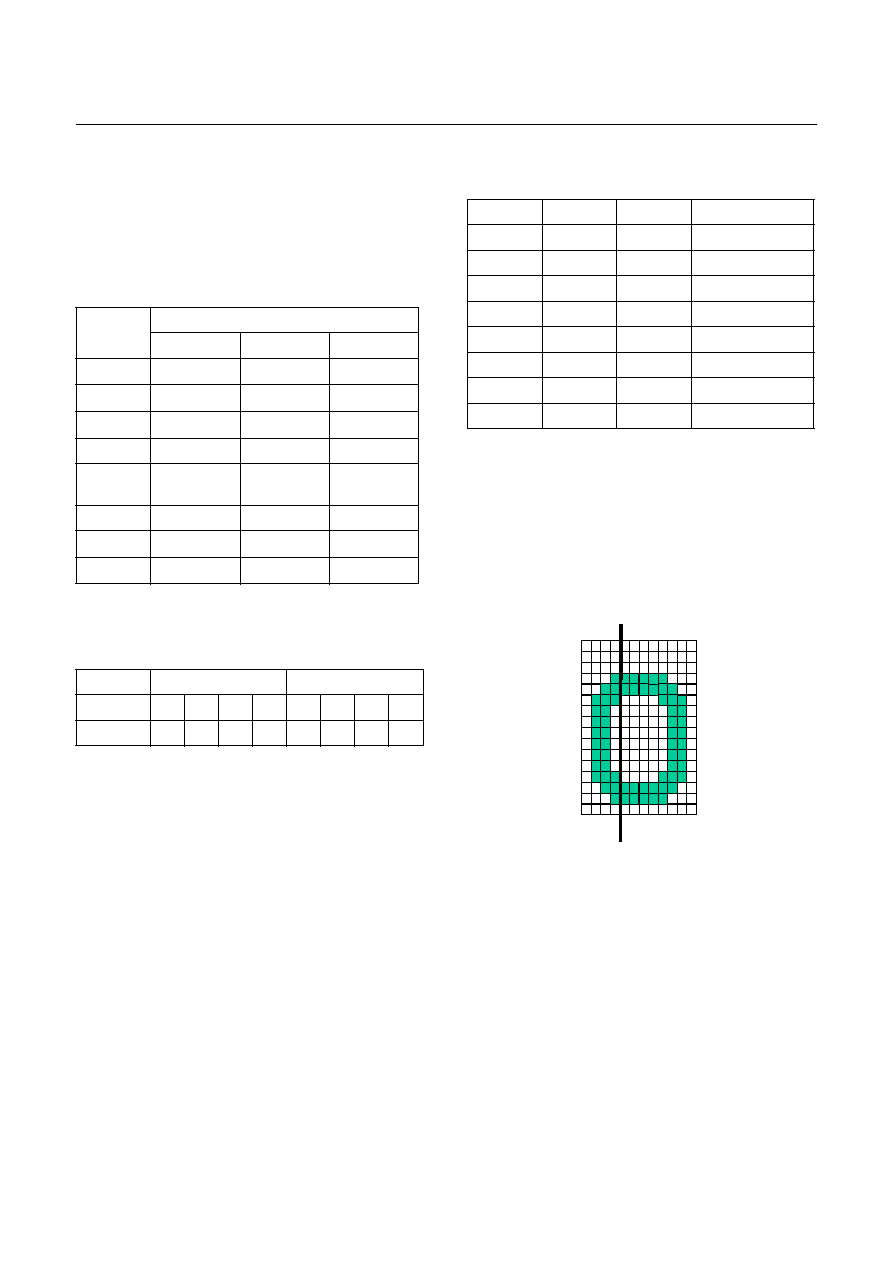

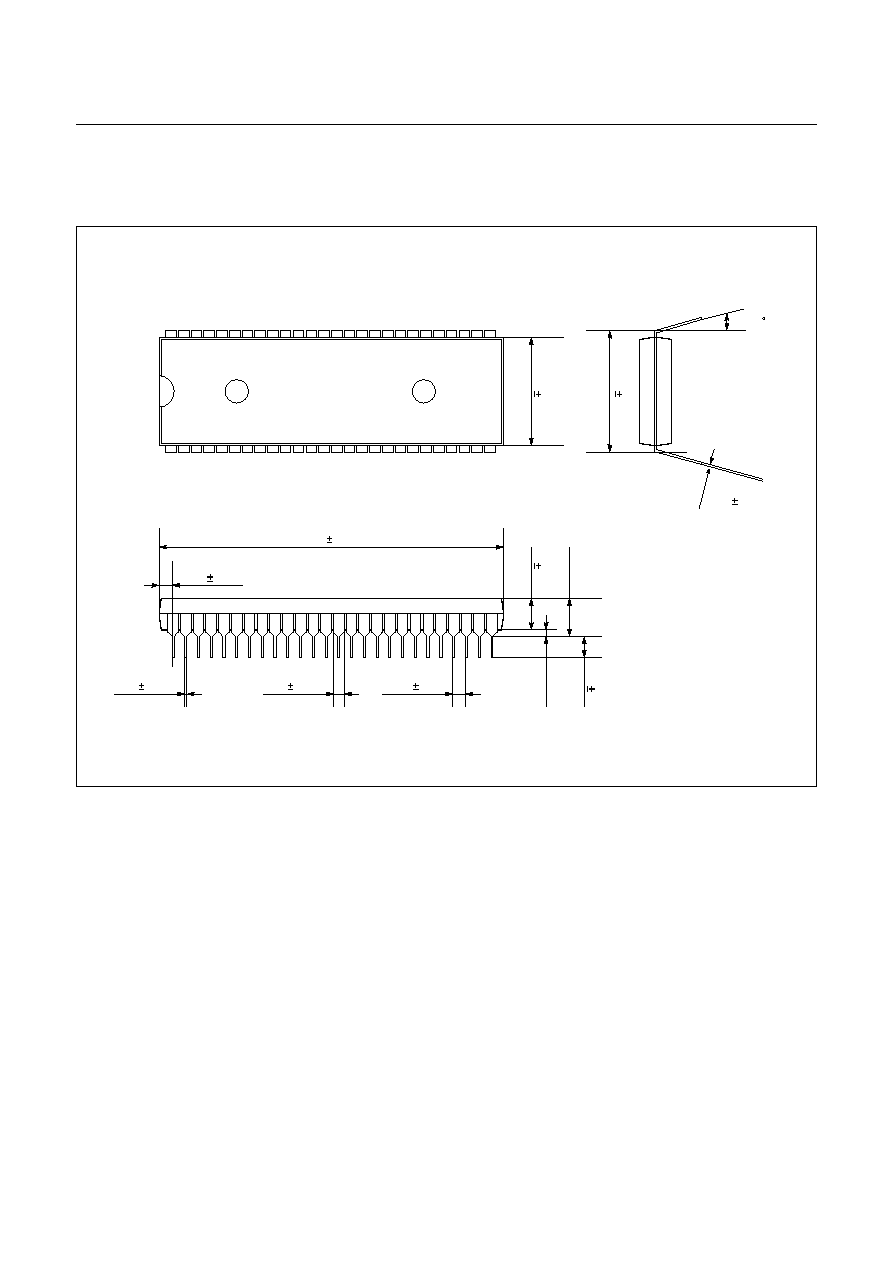

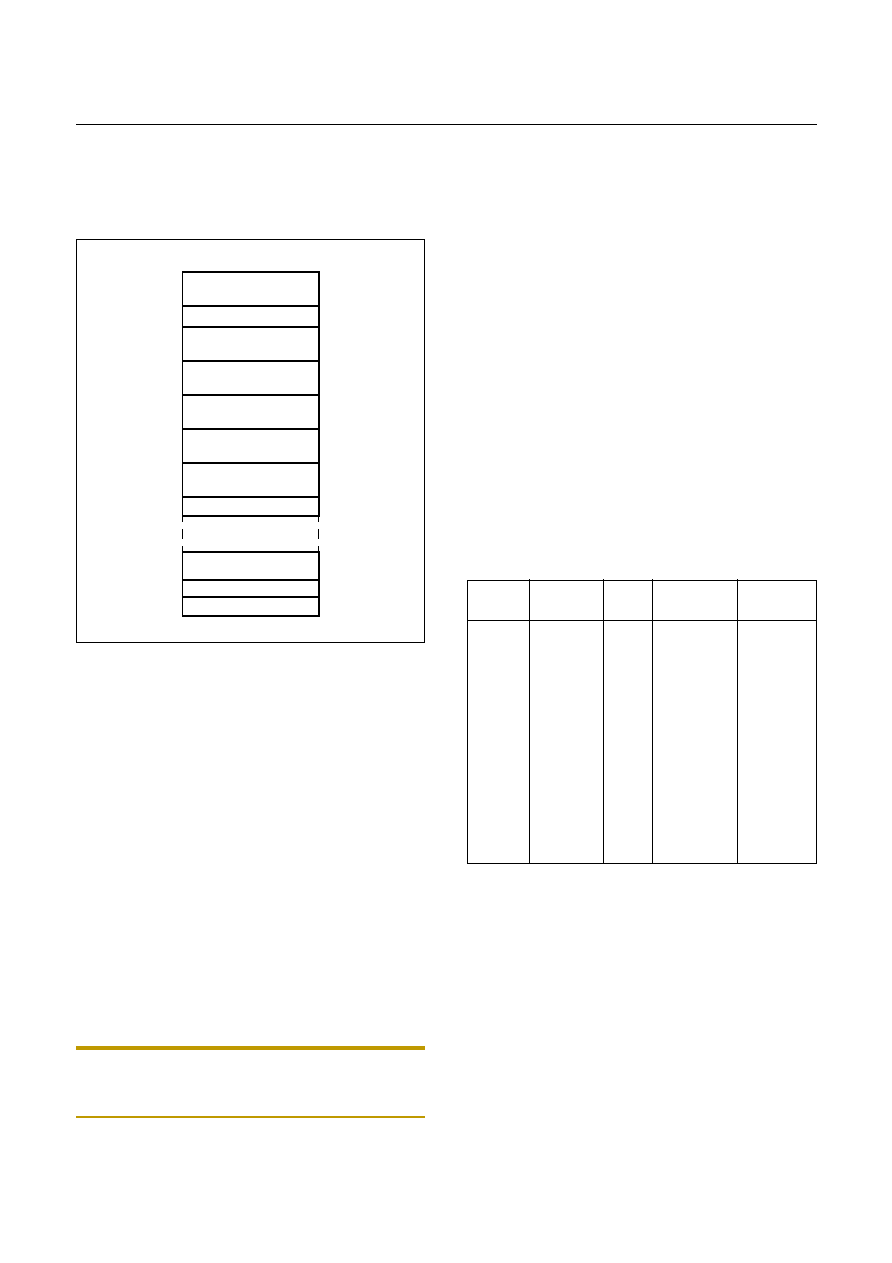

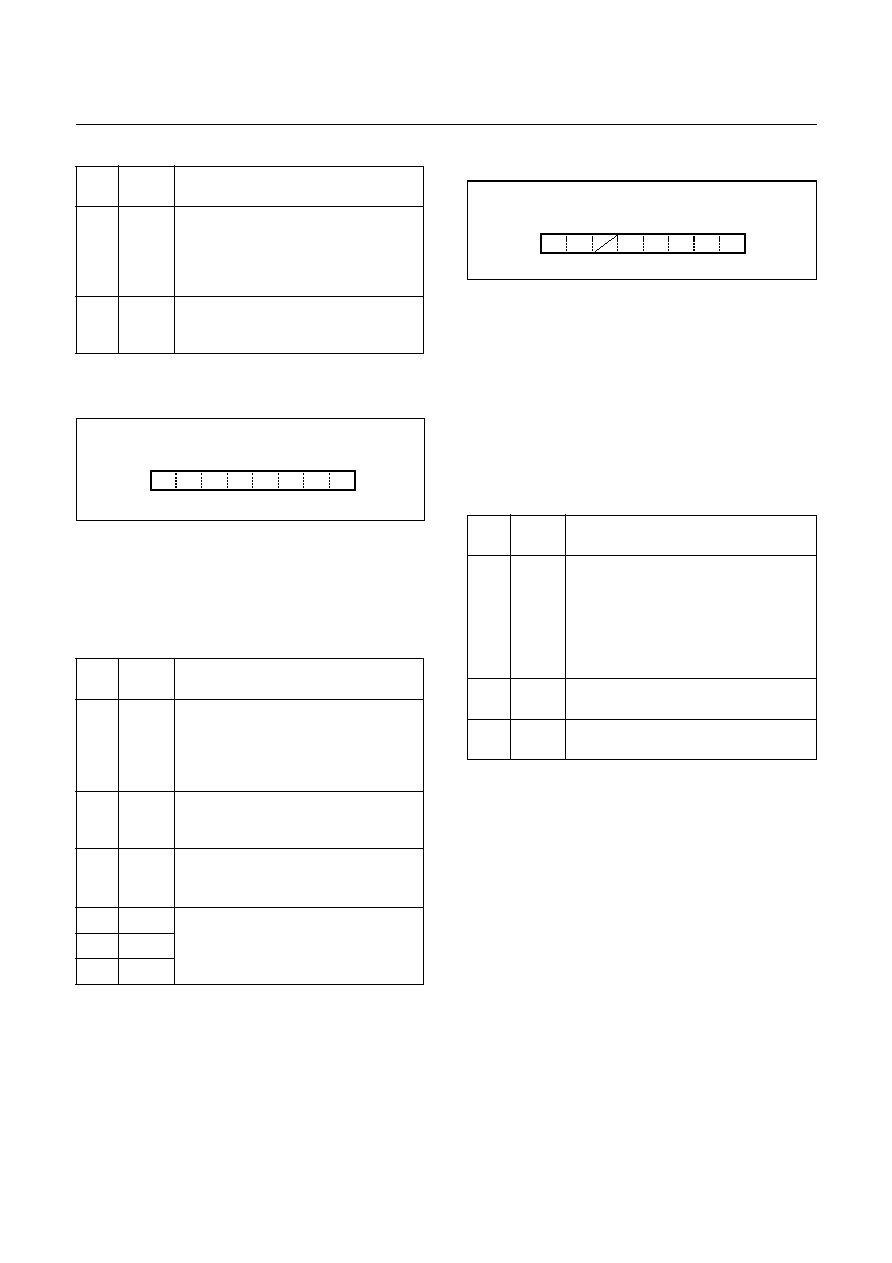

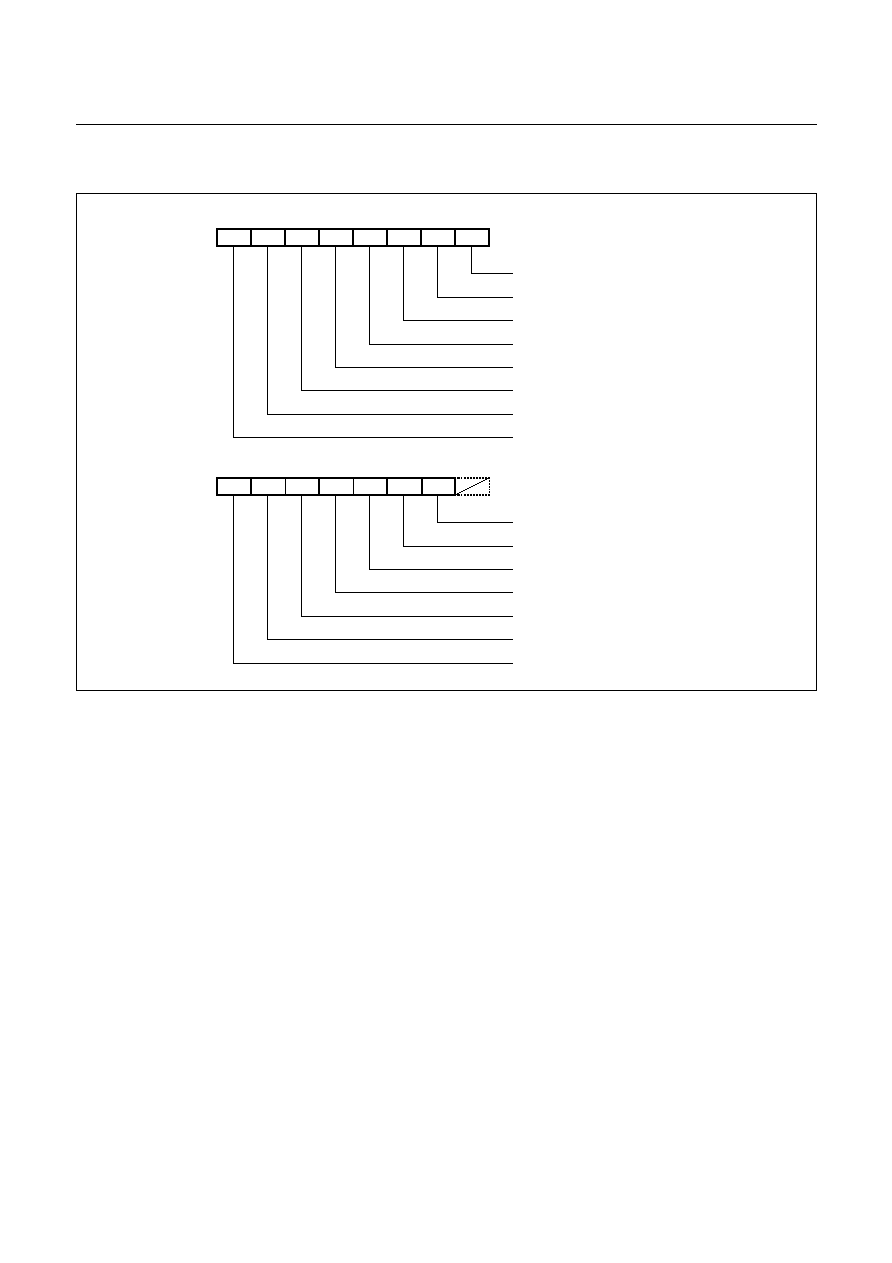

4. PACKAGE DIAGRAM

Figure 4-1 52pin Shrink DIP Package Diagram

UNIT: mm

HYUNDAI

GMS81C40XX

1

26

27

52

45.97

0.13

0.76

0.13

1.778

0.25

4.38

Max

.

13

.

9

7

0.

2

5

15

.

2

4

0.

2

5

0.47

0.13

1.02

0.25

3.81

0.

1

3

3.

2

4

0.20

0.50

Mi

n

.

0.25

0.05

0 ~ 15

GMS81C4040/87C4060

HYUNDAI

6

May. 2000 Ver 1.0

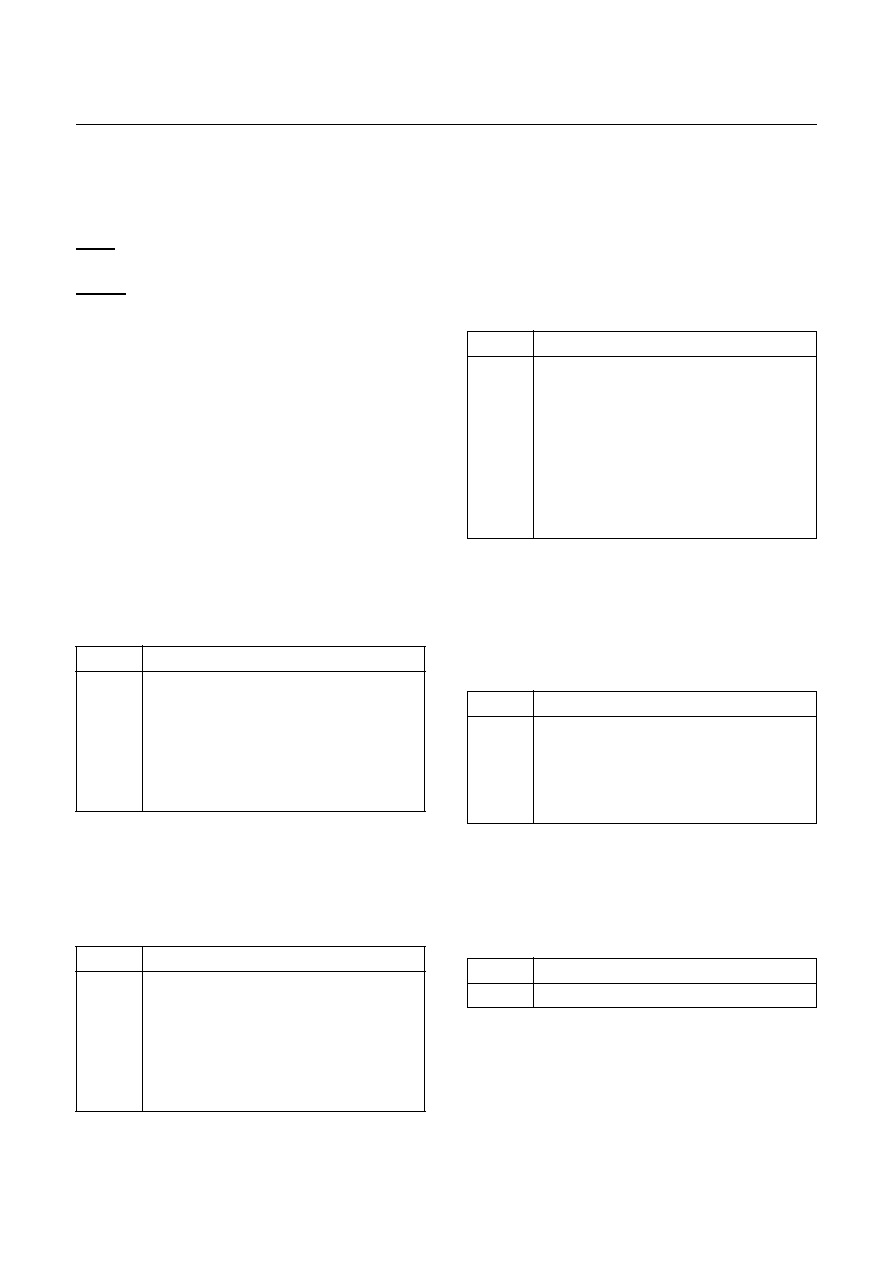

5. PIN FUNCTION

V

DD

: Supply voltage.

V

SS

: Circuit ground.

TEST: Used for shipping inspection of the IC. For normal

operation, it should not be connected .

RESET: Reset the MCU.

X

IN

: Input to the inverting oscillator amplifier and input to

the internal main clock operating circuit.

X

OUT

: Output from the inverting oscillator amplifier.

OSC1: Input to the internal On Screen Display operating

circuit.

OSC2: Output from the inverting OSC1 amplifier.

R00~R07: R0 is an 8-bit CMOS bidirectional I/O port. R0

pins 1 or 0 written to the Port Direction Register can be

used as outputs or inputs.

R10~R17: R1 is an 8-bit CMOS bidirectional I/O port. R1

pins 1 or 0 written to the Port Direction Register can be

used as outputs or inputs.

In addition, R1 serves the functions of the various follow-

ing special features.

R20~R27: R2 is a 8-bit CMOS bidirectional I/O port. Each

pins 1 or 0 written to the their Port Direction Register can

be used as outputs or inputs.

In addition, R2 serves the functions of the various follow-

ing special features.

R40~R47: R40~R43 are 8-bit NMOS open drain output

and R45~R47 are bidirectional CMOS Input / NMOS open

drain output port. R4 pins 1 or 0 written to the Port Direc-

tion Register can be used as outputs or inputs.

In addition, R4 serves the functions of the various follow-

ing special features.

R50~R56: R50~R53 are 4-bit CMOS bidirectional I/O and

R54~R56 are CMOS output port. R5 pins 1 or 0 written to

the Port Direction Register can be used as outputs or in-

puts.

In addition, R5 serves the functions of the various follow-

ing special features.

R67: R67 is an 1-bit CMOS bidirectional I/O port. R67

pins 1 or 0 written to the Port Direction Register can be

used as outputs or inputs.

In addition, R67 serves the functions of the various follow-

ing special features.

R,G,B: R,G,B CMOS output port. Each pins controls Red,

Green,. Blue color control.

Port pin

Alternate function

R10

R11

R12

R13

R14

R15

R16

R17

AN0 (A/D converter input 0)

AN1 (A/D converter input 1)

AN2 (A/D converter input 2)

AN3 (A/D converter input 3)

AN4 (A/D converter input 4)

AN5 (A/D converter input 5)

VD (Vertical Sync. input)

HD (Horisontal Sync. input)

Port pin

Alternate function

R20

R21

R22

R23

R24

R25

R26

R27

INT2 (External interrupt input 2)

Sclk (Serial communication clock)

Sout (Serial communication data out)

Sin (Serial communication data in)

INT3 (External interrupt input 3)

EC2 (Event counter input 2)

INT4 (External interrupt input 4)

EC3 (Event counter input 3)

Port pin

Alternate function

R40

R41

R42

R43

R44

R45

R46

R47

PWM0 (Pulse Width Modulation output 0)

PWM1 (Pulse Width Modulation output 1)

PWM2 (Pulse Width Modulation output 2)

PWM3 (Pulse Width Modulation output 3)

SCL0 (I

2

C Clock 0)

SCL1 (I

2

C Clock 1)

PWM4 (Pulse Width Modulation output 4)

SDA0 (I

2

C Data 0)

SDA1 (I

2

C Data 1)

PWM5 (Pulse Width Modulation output 5)

Port pin

Alternate function

R50

R51

R52

R54

R55

R56

BUZZ (Buzzer output)

PWM8 (Pulse Width Modulation output 8)

INT0 (External interrupt input 0)

YM (Back ground)

YS (Edge)

I (Intencity)

Port pin

Alternate function

R67

INT1 (External interrupt input 1)

HYUNDAI

GMS81C4040/87C4060

May. 2000 Ver 1.0

7

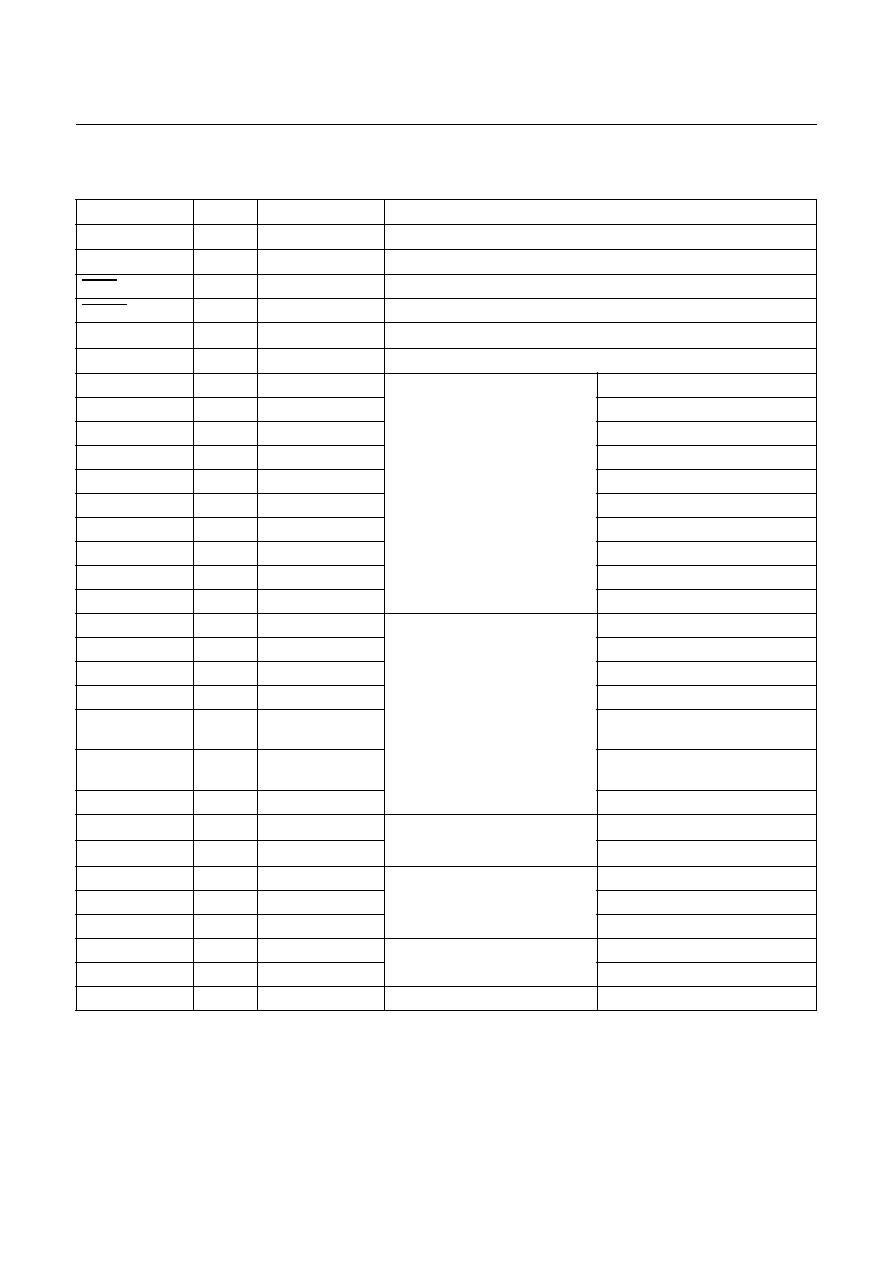

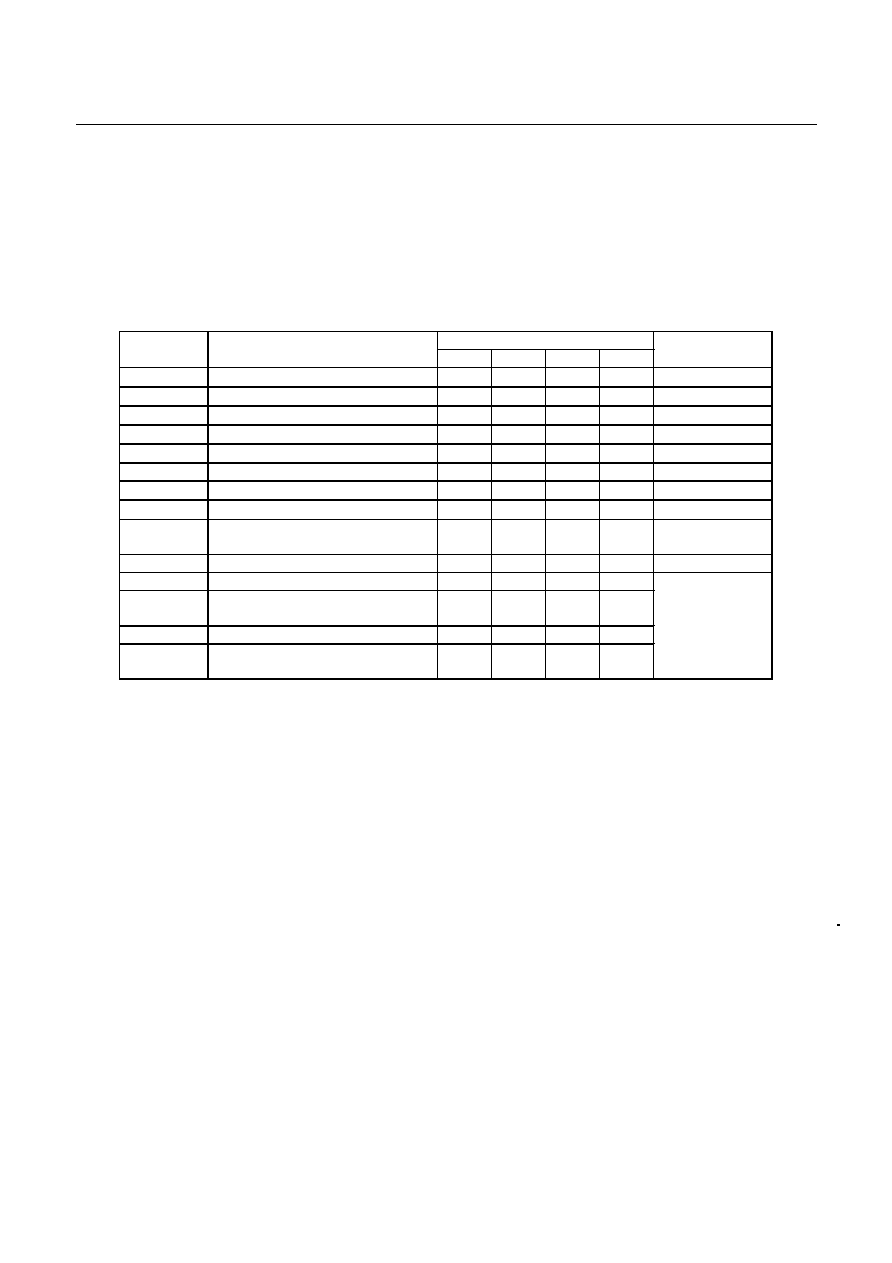

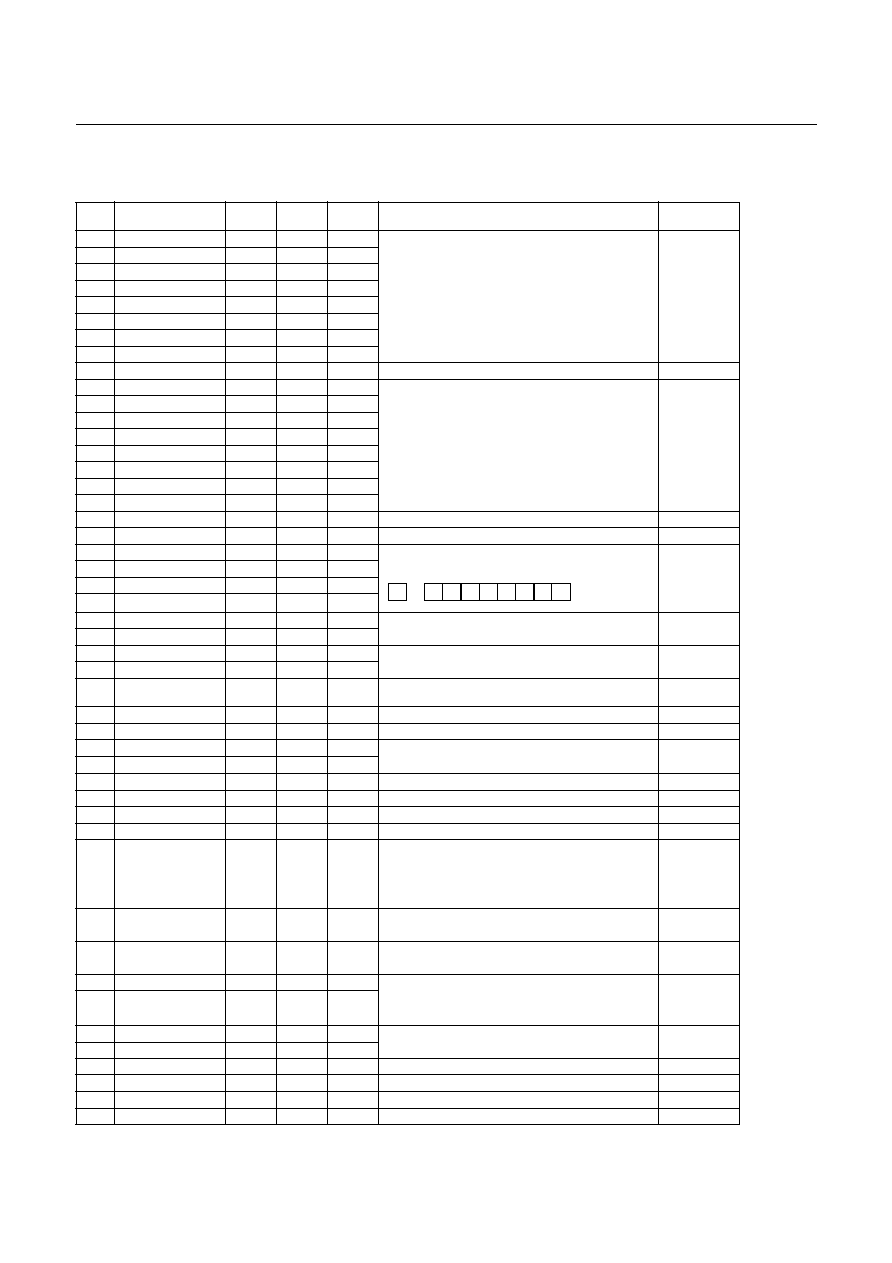

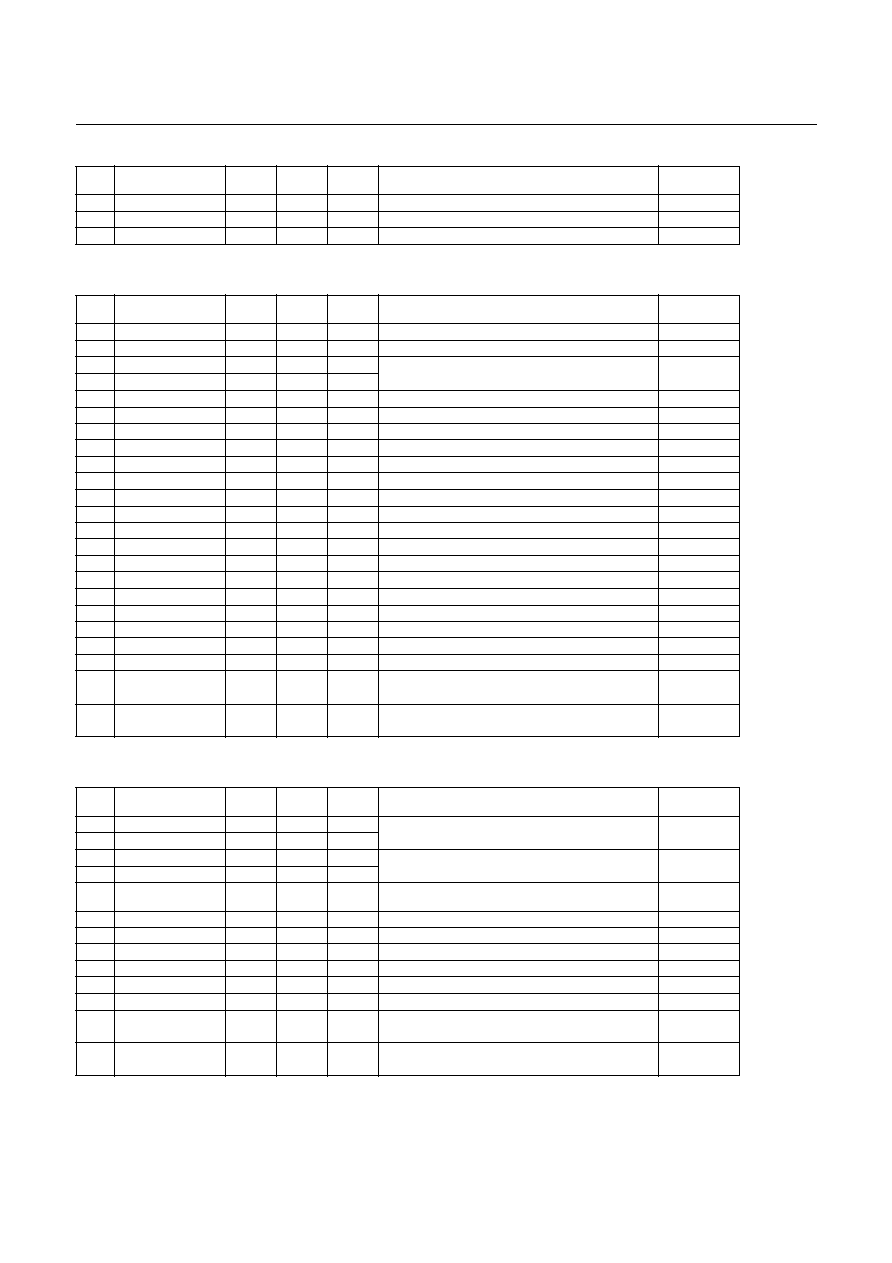

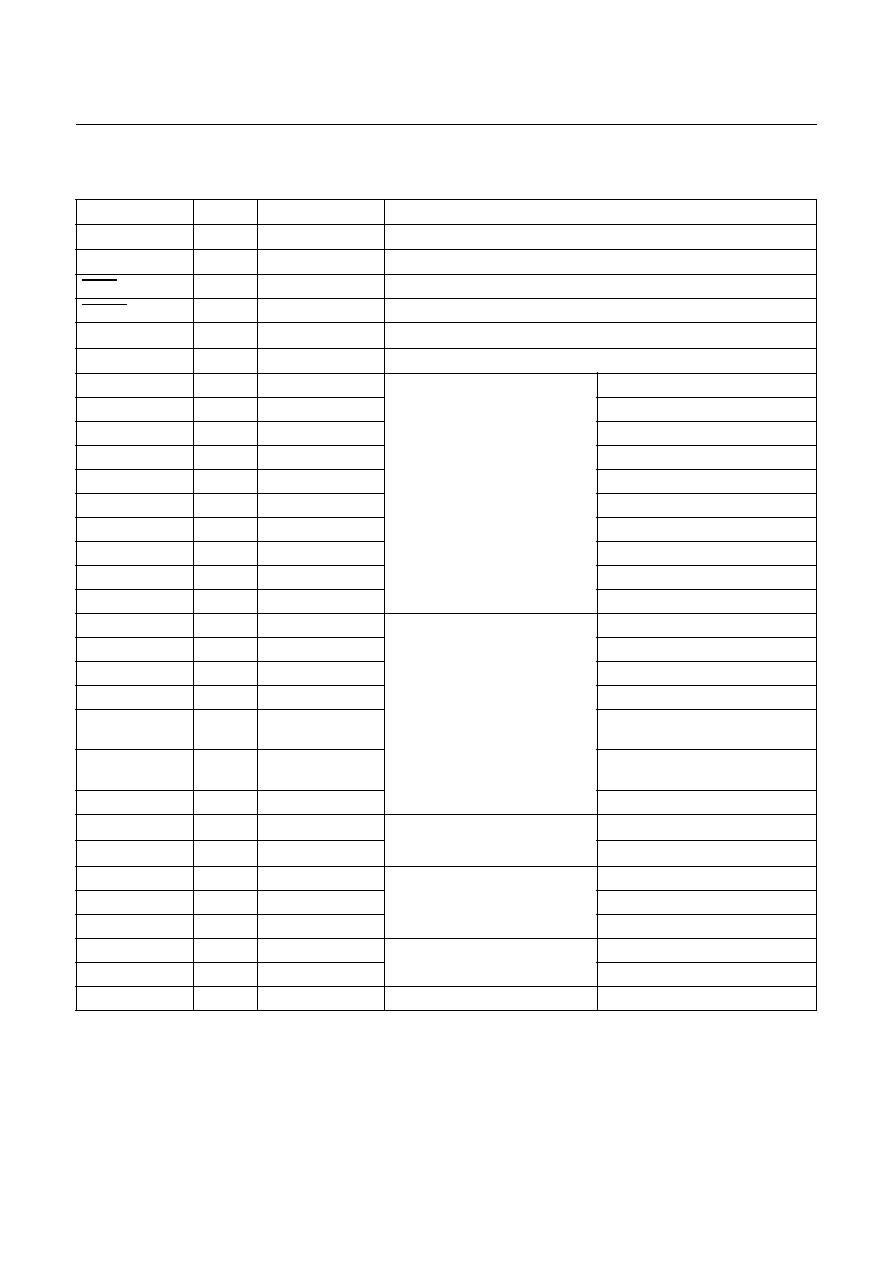

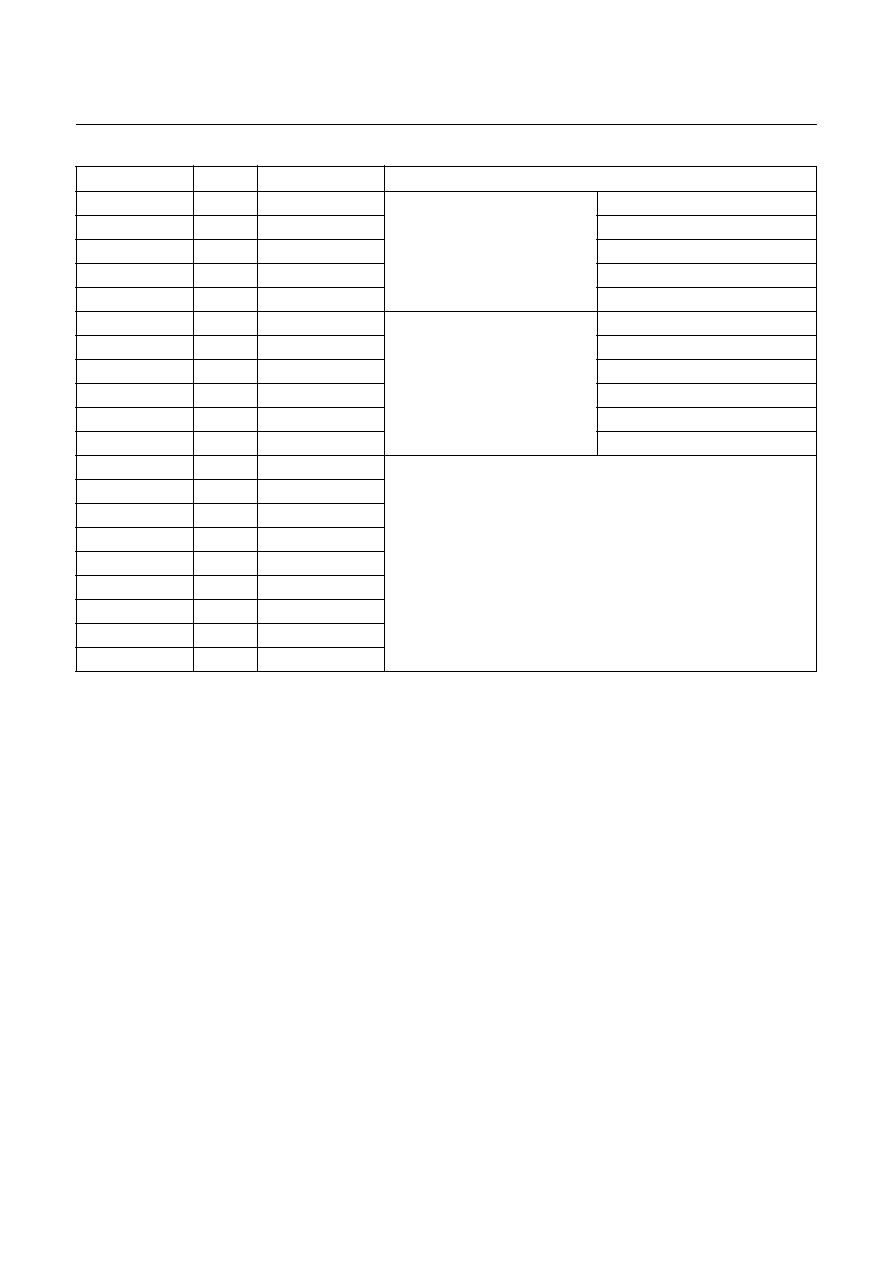

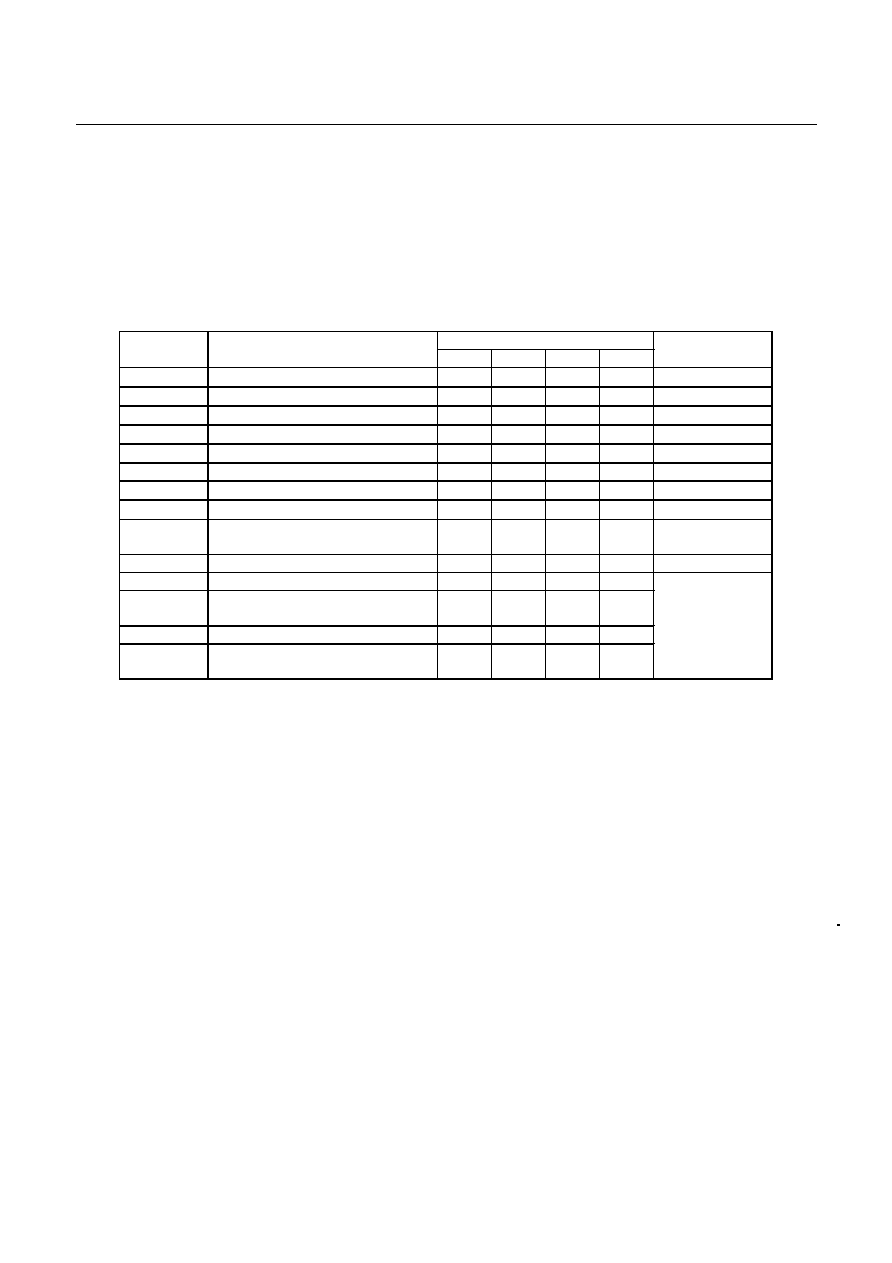

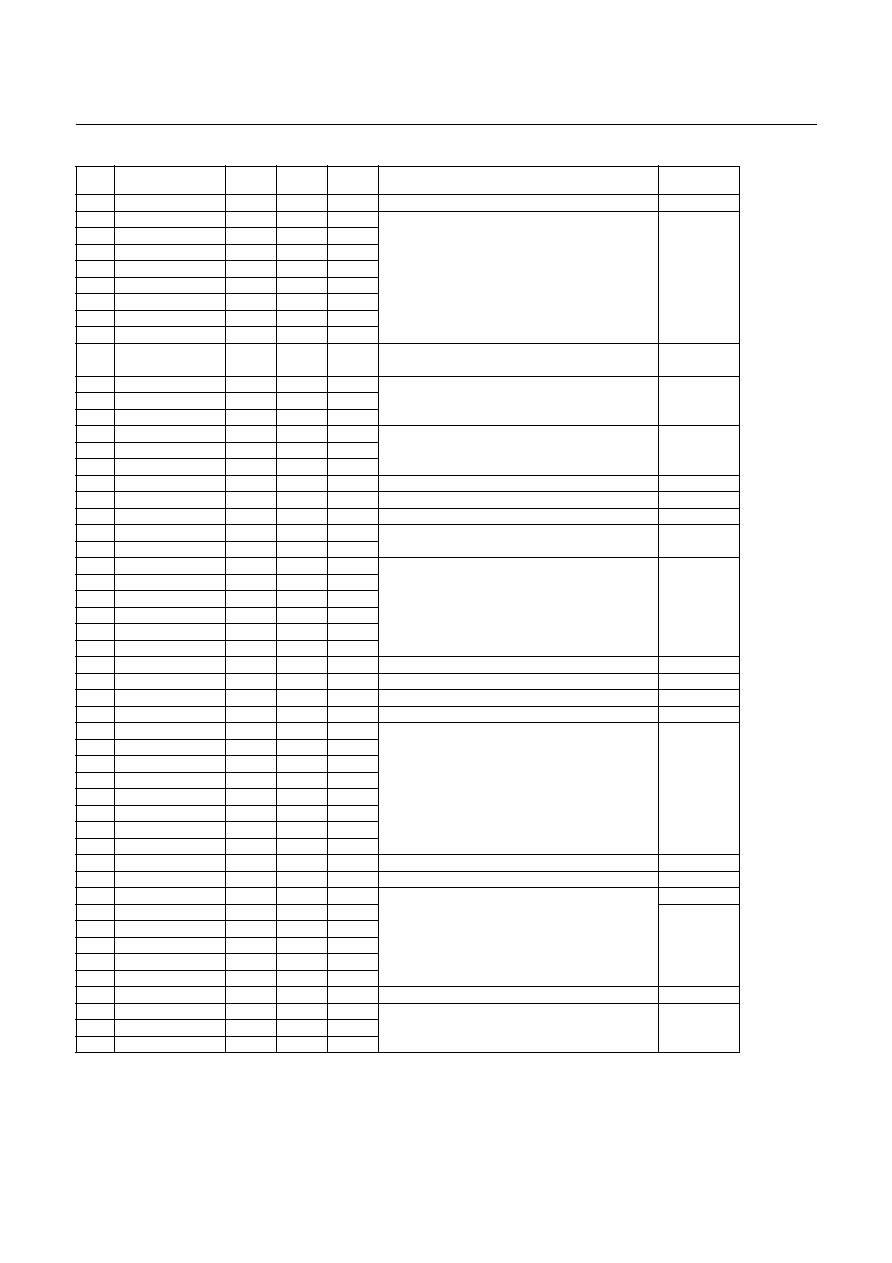

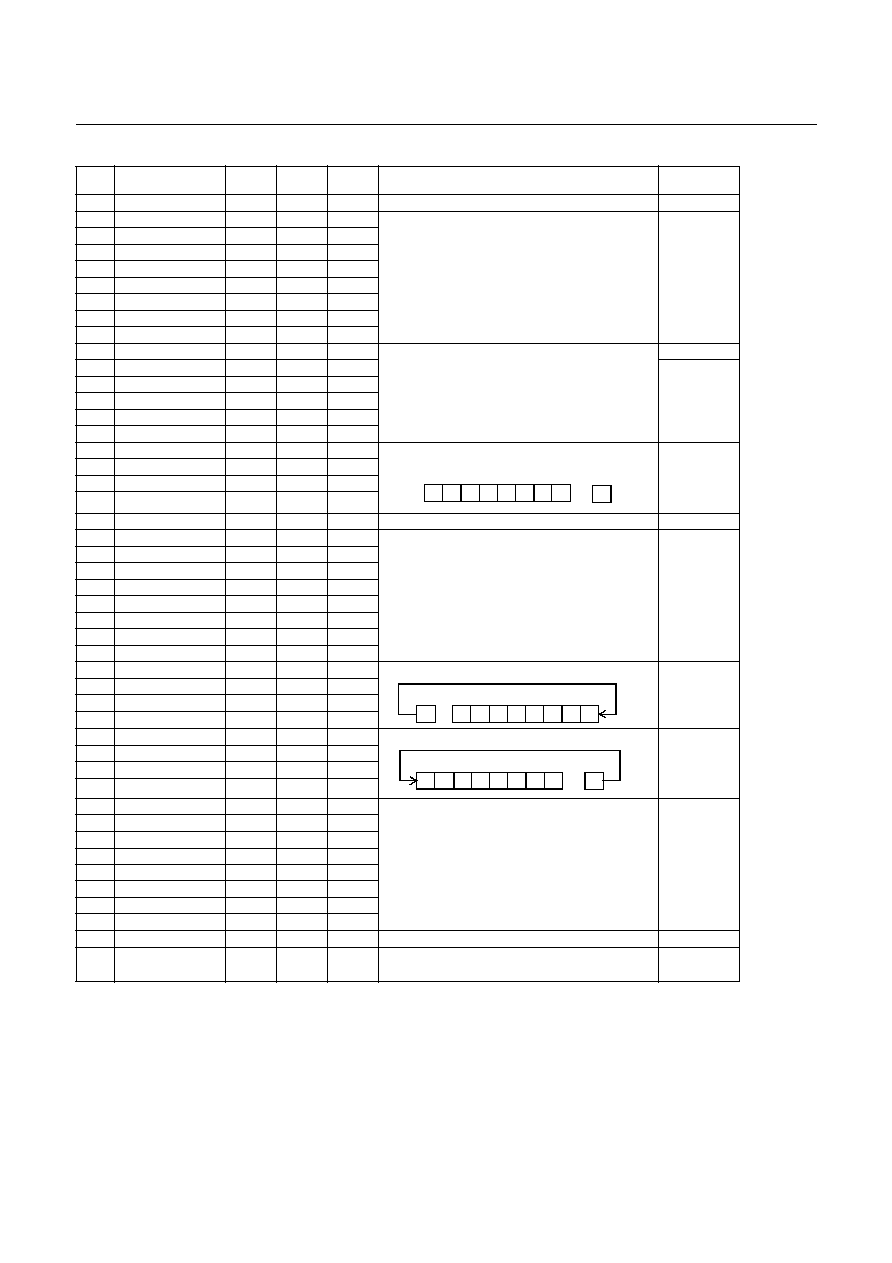

PIN NAME

Pin No.

In/Out

Function

V

DD

39

-

Supply voltage

V

SS

12, 40

-

Circuit ground

TEST

38

I

For test purposes. Should not be connected. (N.C.)

RESET

11

I

Reset signal input

X

IN

14

I

Main oscillation input

X

OUT

13

O

Main oscillation output

OSC1

37

I

On screen display functions

On screen display oscillation input

OSC2

36

O

On screen display osc. output

R17/HD

9

I/O

Horisontal Sync. input

R16/VD

10

I/O

Vertical Sync. input

R

30

O

Red signal output

G

31

O

Green signal output

B

32

O

Blue signal output

R56/I

33

O

Intencity signal output

R55/YS

34

O

Edge signal output

R54/YM

35

O

Background signal output

R40/PWM0

52

O

PWM functions

8bit PWM

R41/PWM1

51

O

8bit PWM

R42/PWM2

50

O

8bit PWM

R43/PWM3

49

O

8bit PWM

R45/SCL1/

PWM4

47

I/O

Include I

2

C Serial clock 1 (SCL1)

R47/SDA1/

PWM5

45

I/O

Include I

2

C Serial data 1 (SDA1)

R51/PWM8

43

I/O

14bit PWM

R44/SCL0

48

I/O

I

2

C functions

I

2

C Serial clock 0

R46/SDA0

46

I/O

I

2

C Serial data 0

R23/Sin

5

I/O

SCI functions

Serial data input

R22/Sout

6

I/O

Serial data output

R21/Sclk

7

I/O

Serial communication clock

R27/EC3

1

I/O

Timer event functions

Event counter input 3

R25/EC2

3

I/O

Event counter input 2

R50/Buzzer

44

I/O

Buzzer function

500Hz ~ 250KHz @8MHz

Table 5-1 Port Function Description

GMS81C4040/87C4060

HYUNDAI

8

May. 2000 Ver 1.0

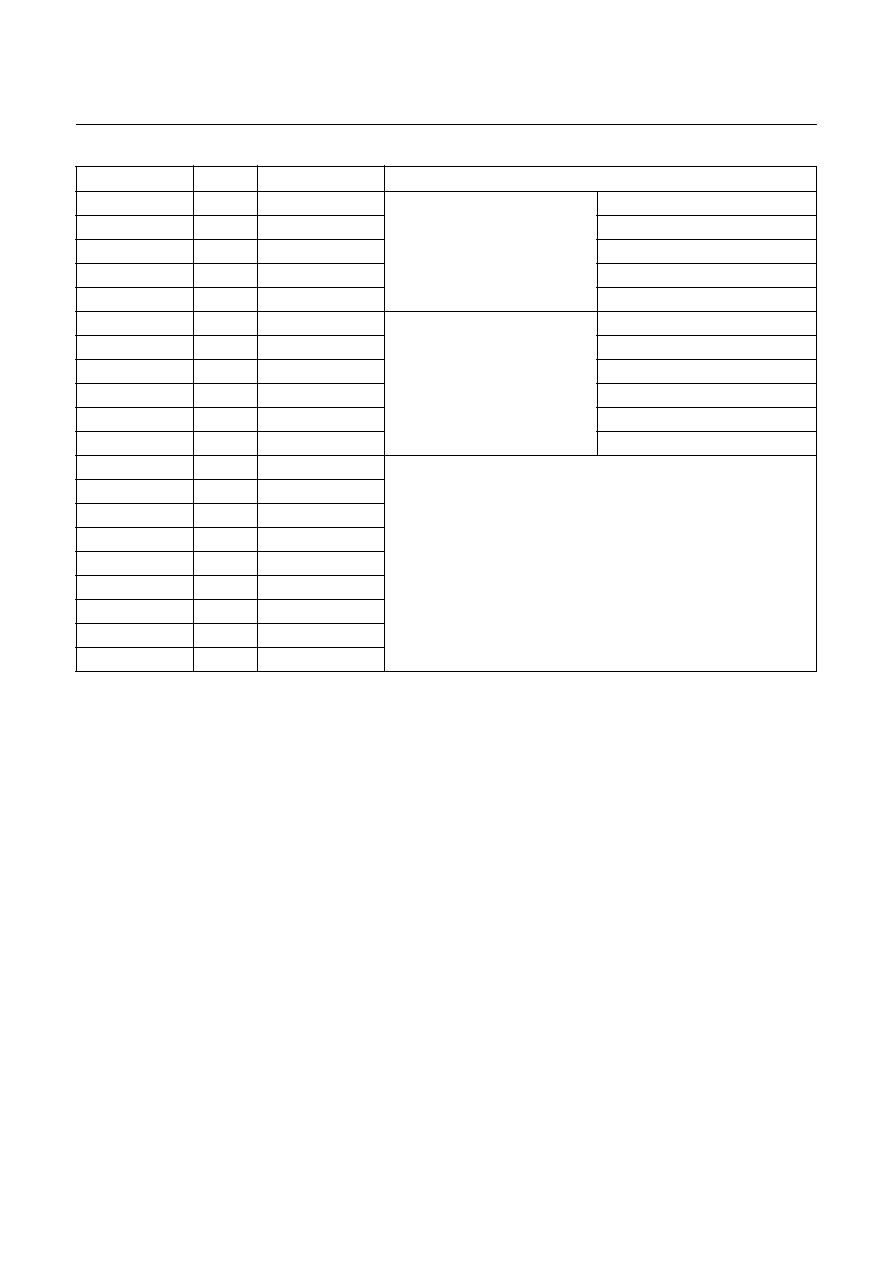

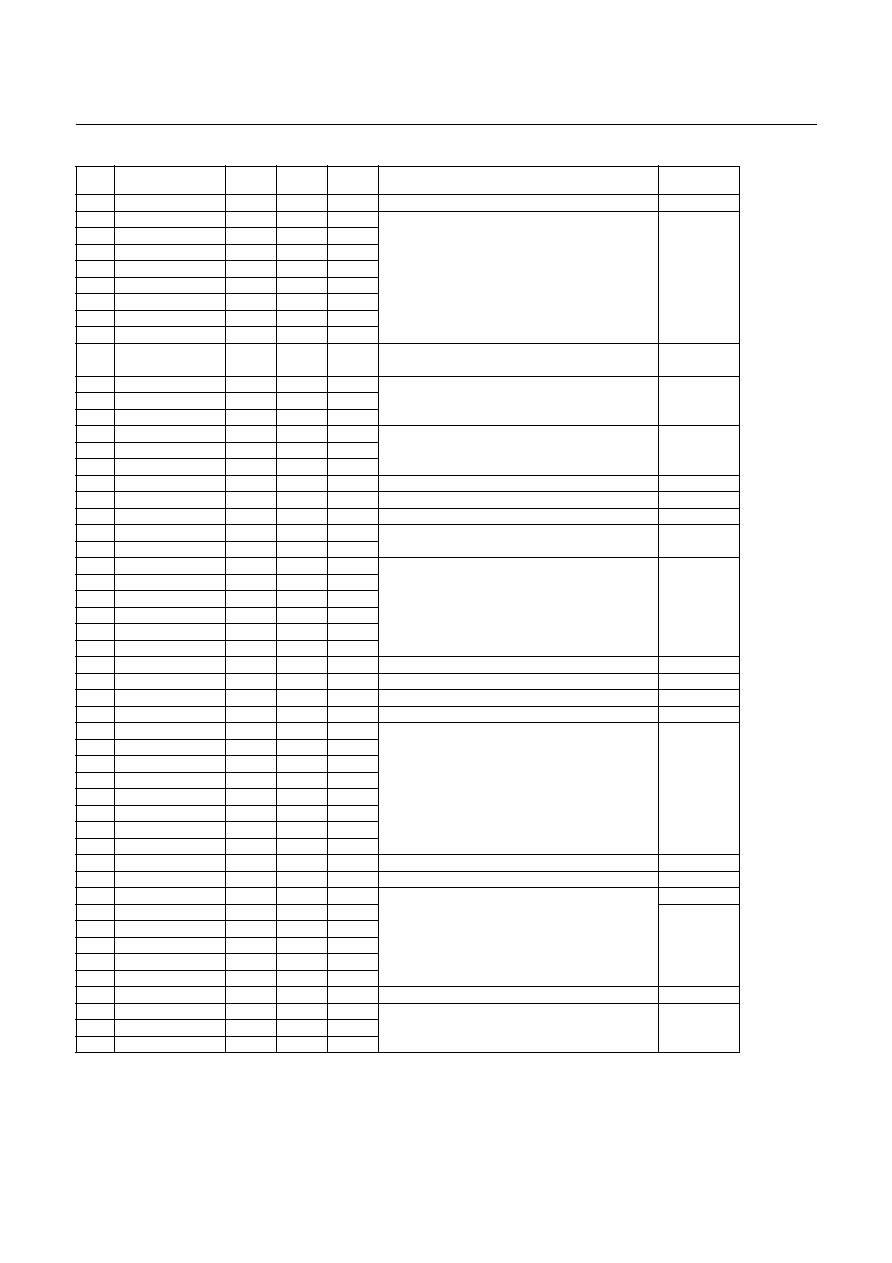

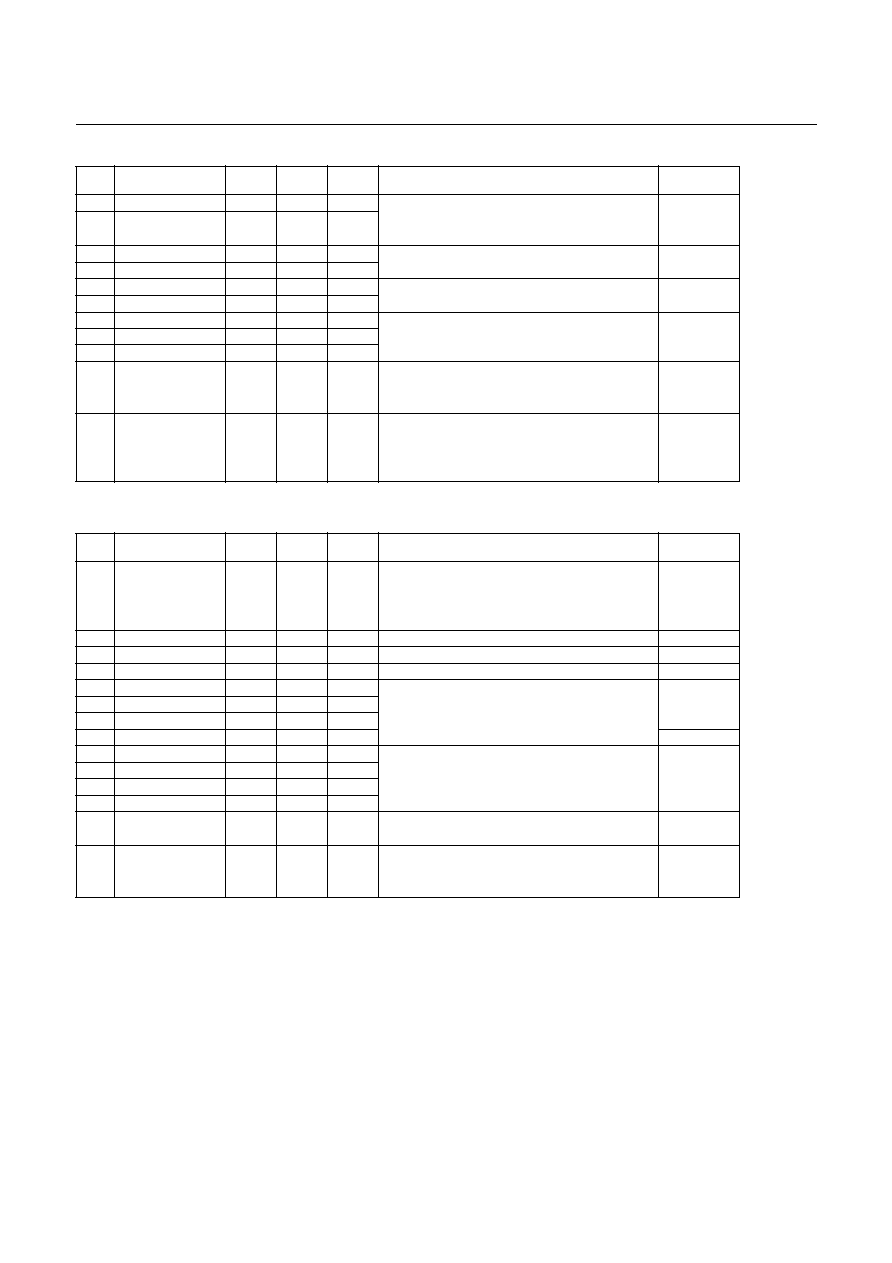

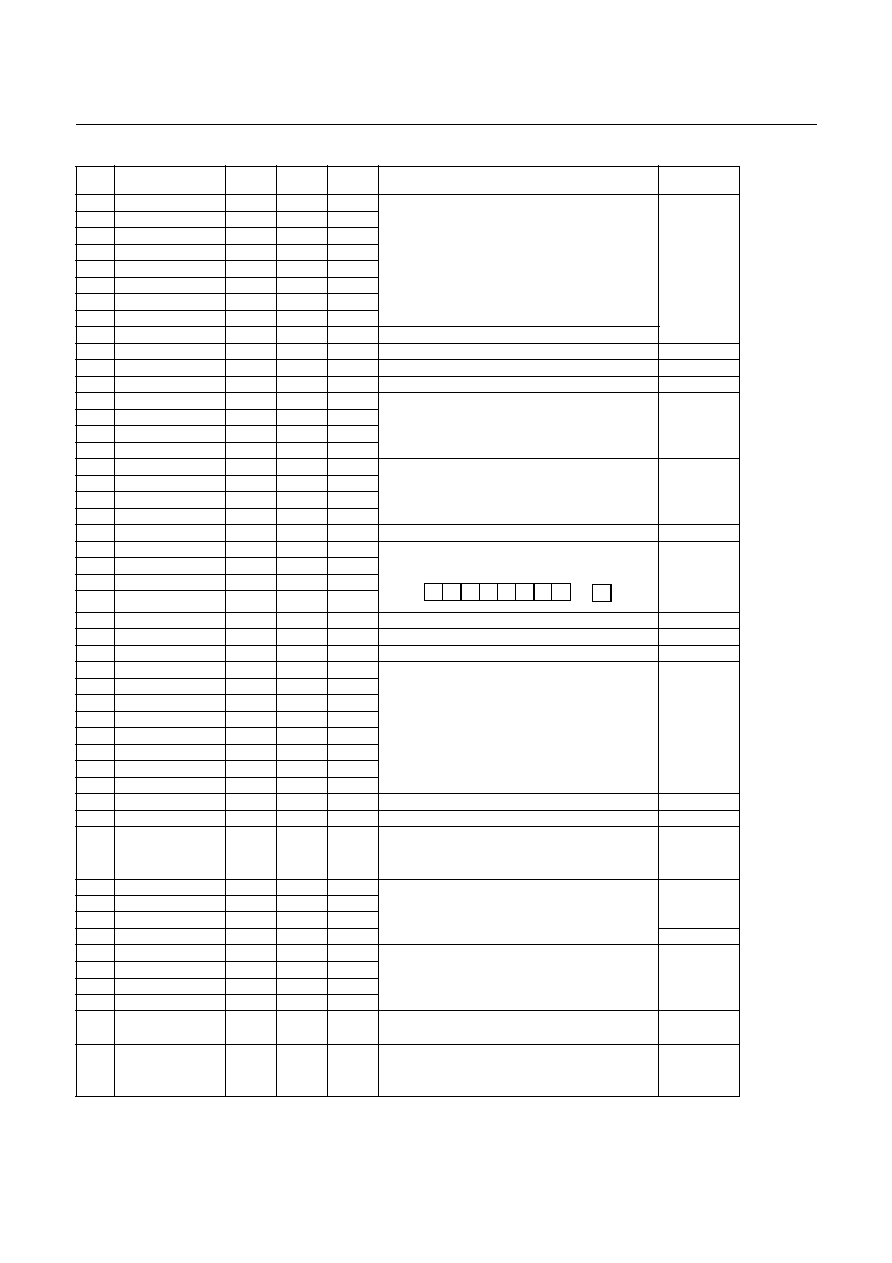

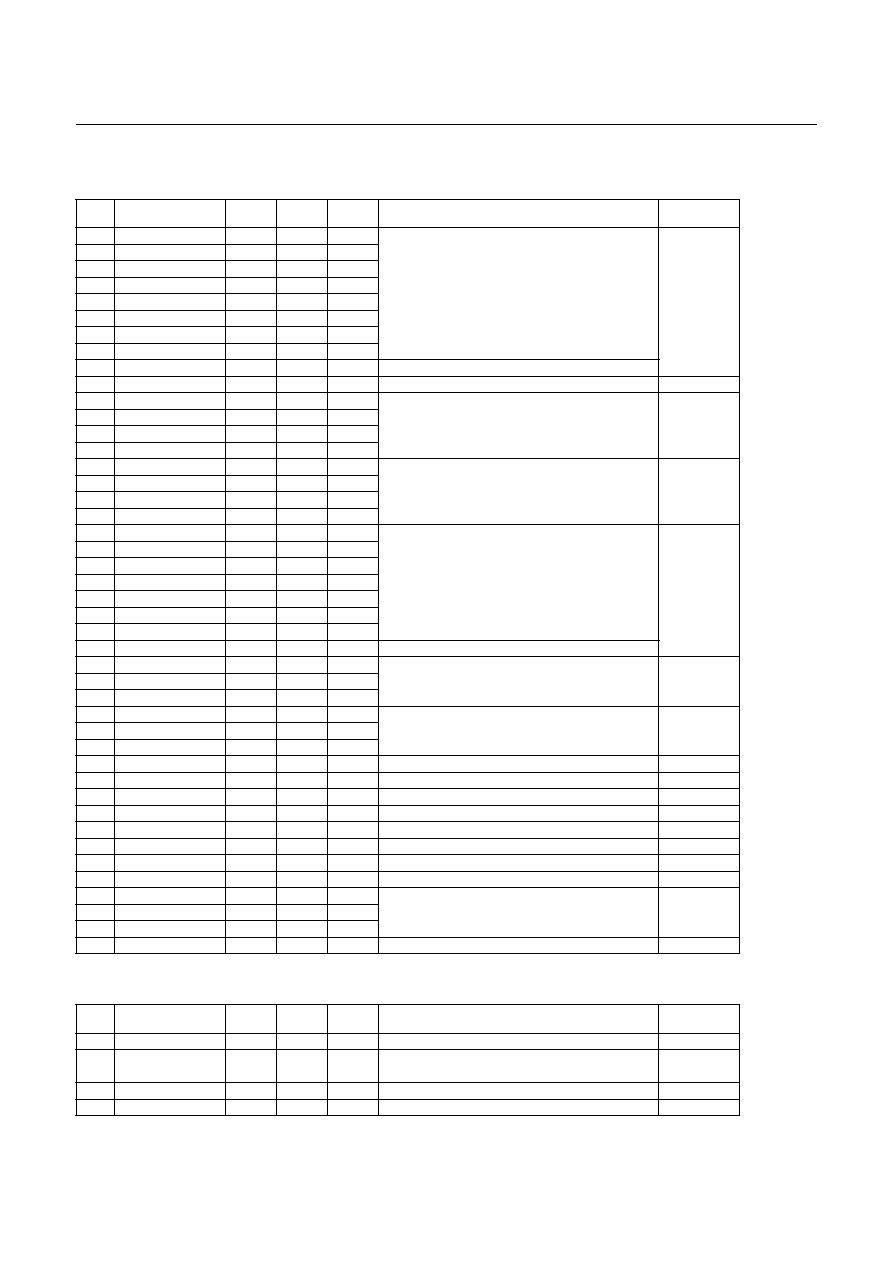

R52/INT0

42

I/O

External interrupt functions

External interrupt input 0

R67/INT1

26

I/O

External interrupt input 1

R20/INT2

8

I/O

External interrupt input 2

R24/INT3

4

I/O

External interrupt input 3

R26/INT4

2

I/O

External interrupt input 4

R10/AN0

20

I/O

A/D conversion functions

Analog input 0

R11/AN1

19

I/O

Analog input 1

R12/AN2

18

I/O

Analog input 2

R13/AN3

17

I/O

Analog input 3

R14/AN4

16

I/O

Analog input 4

R15/AN5

15

I/O

Analog input 5

R00

29

I/O

Digital I/O functions

R01

28

I/O

R02

27

I/O

R03

25

I/O

R04

24

I/O

R05

23

I/O

R06

22

I/O

R07

21

I/O

R53

41

I/O

PIN NAME

Pin No.

In/Out

Function

Table 5-1 Port Function Description

HYUNDAI

GMS81C4040/87C4060

May. 2000 Ver 1.0

9

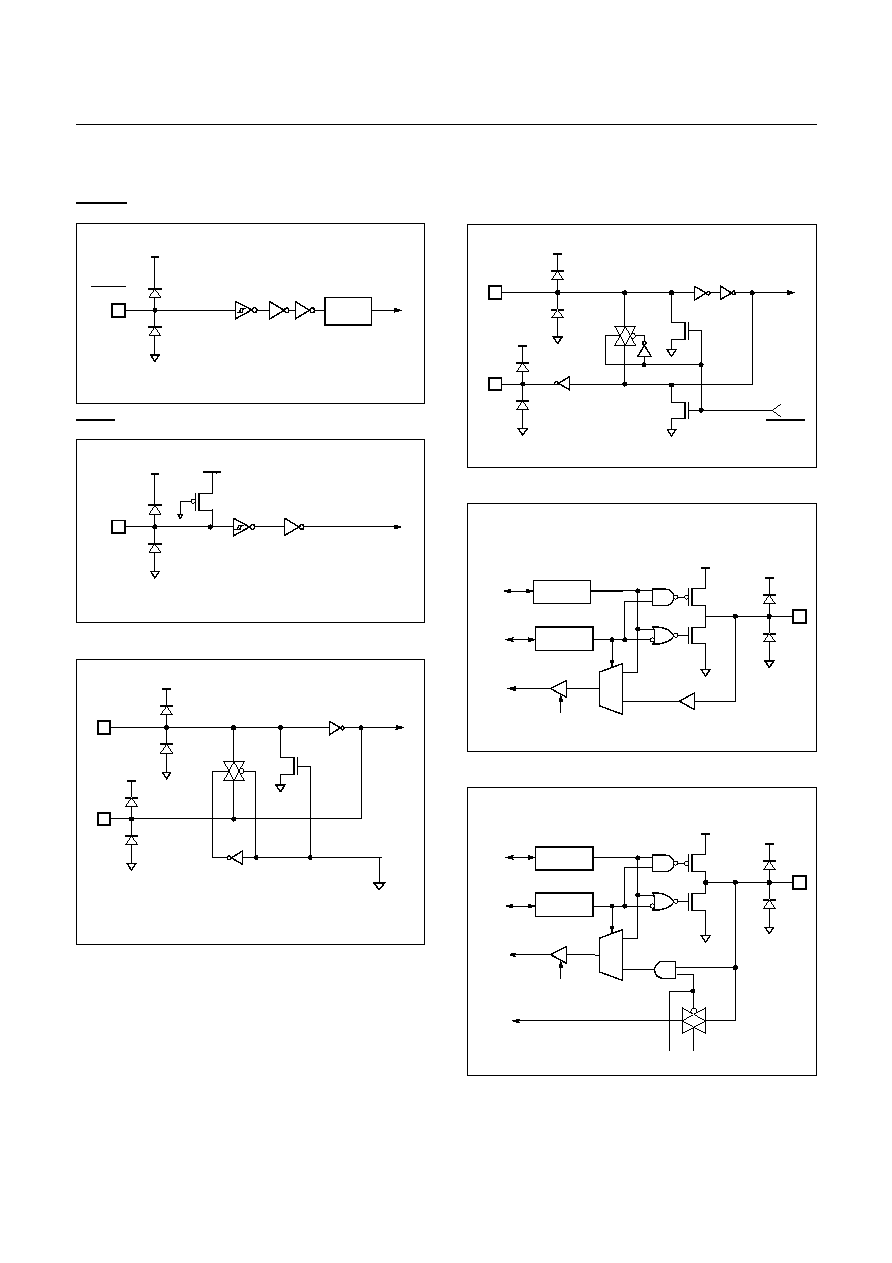

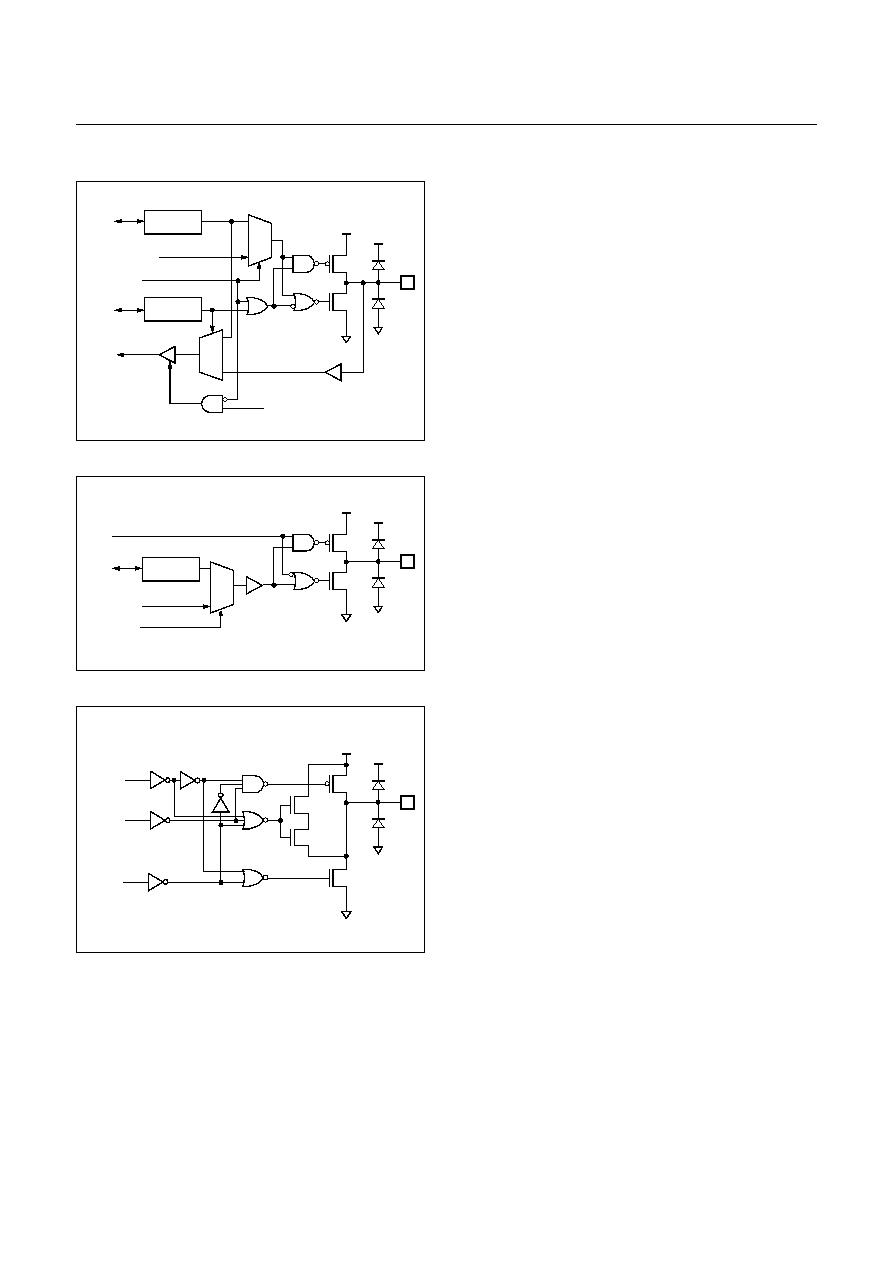

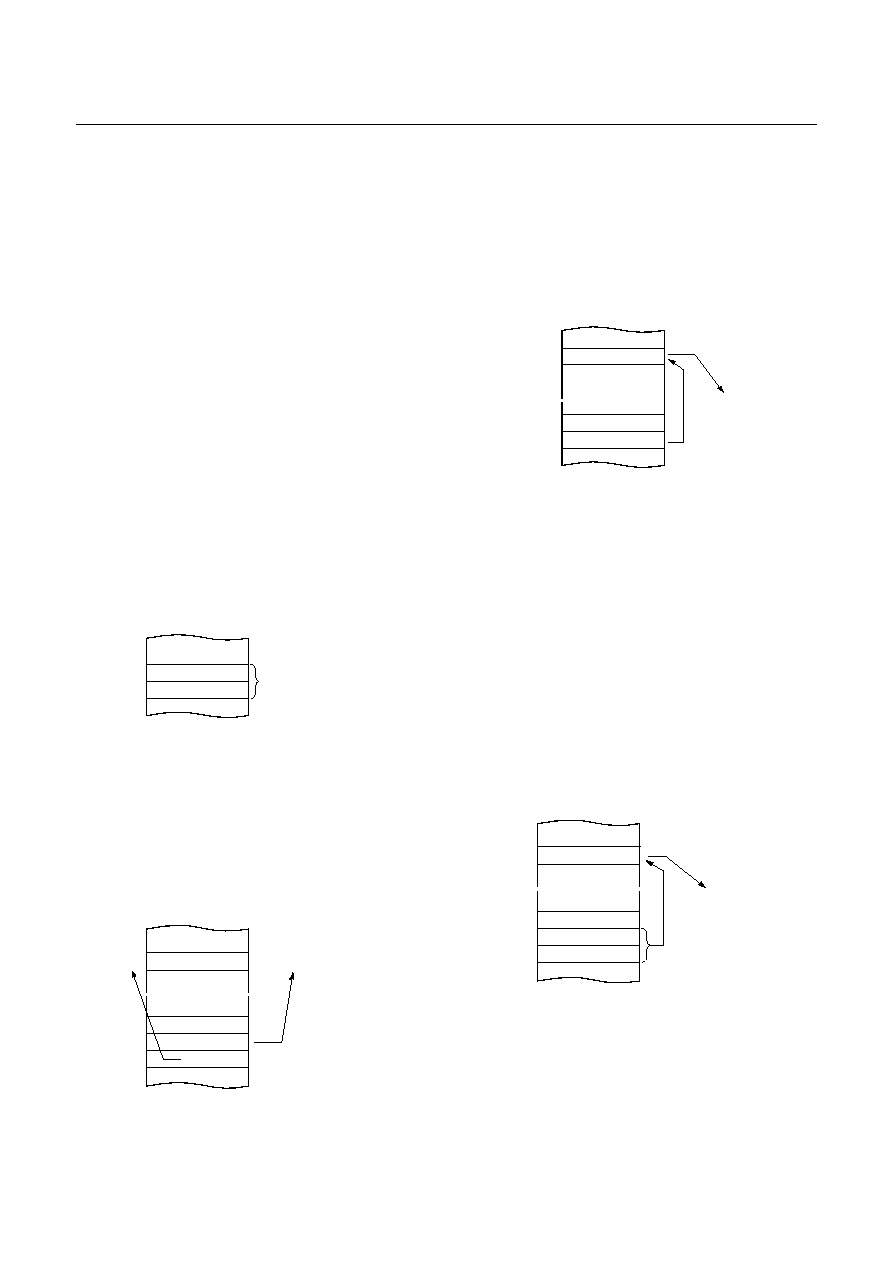

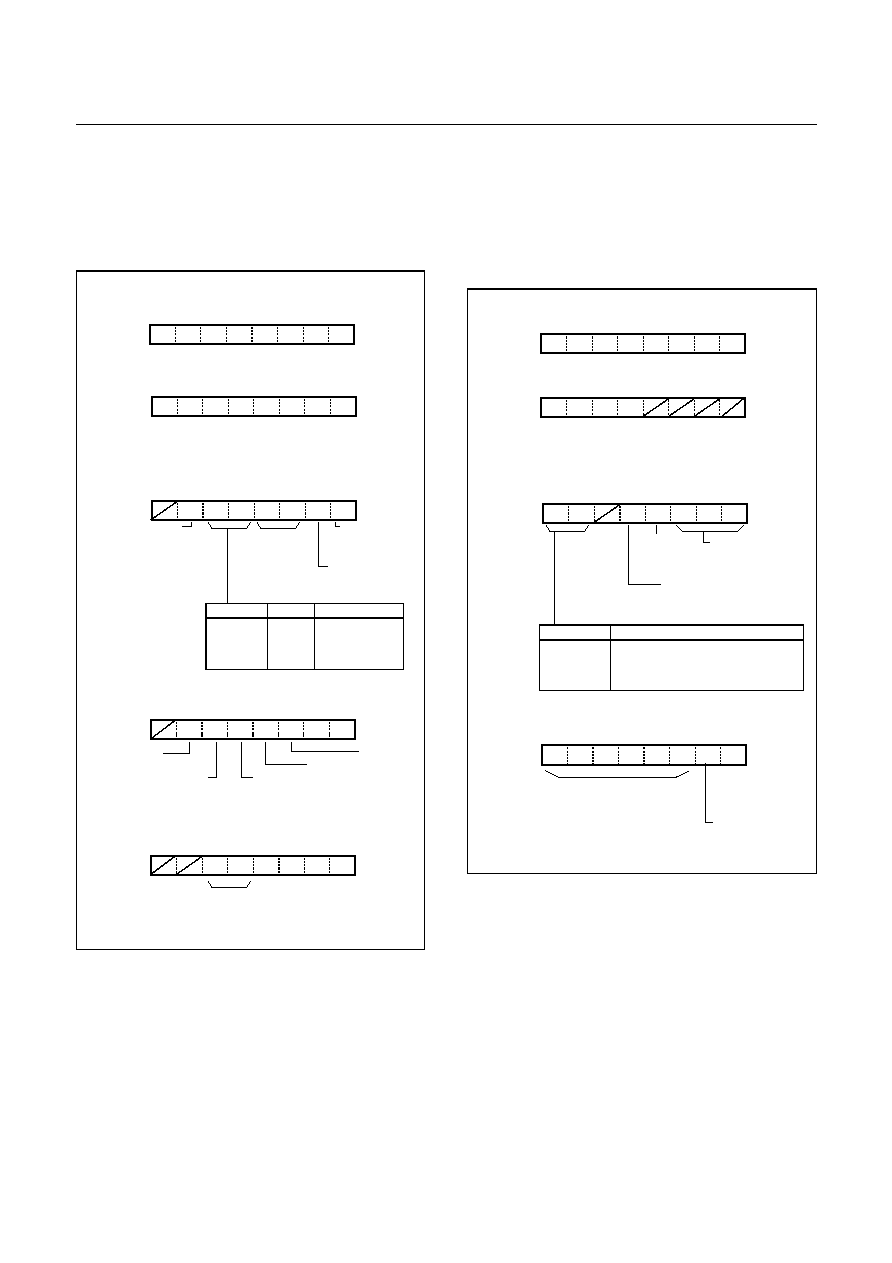

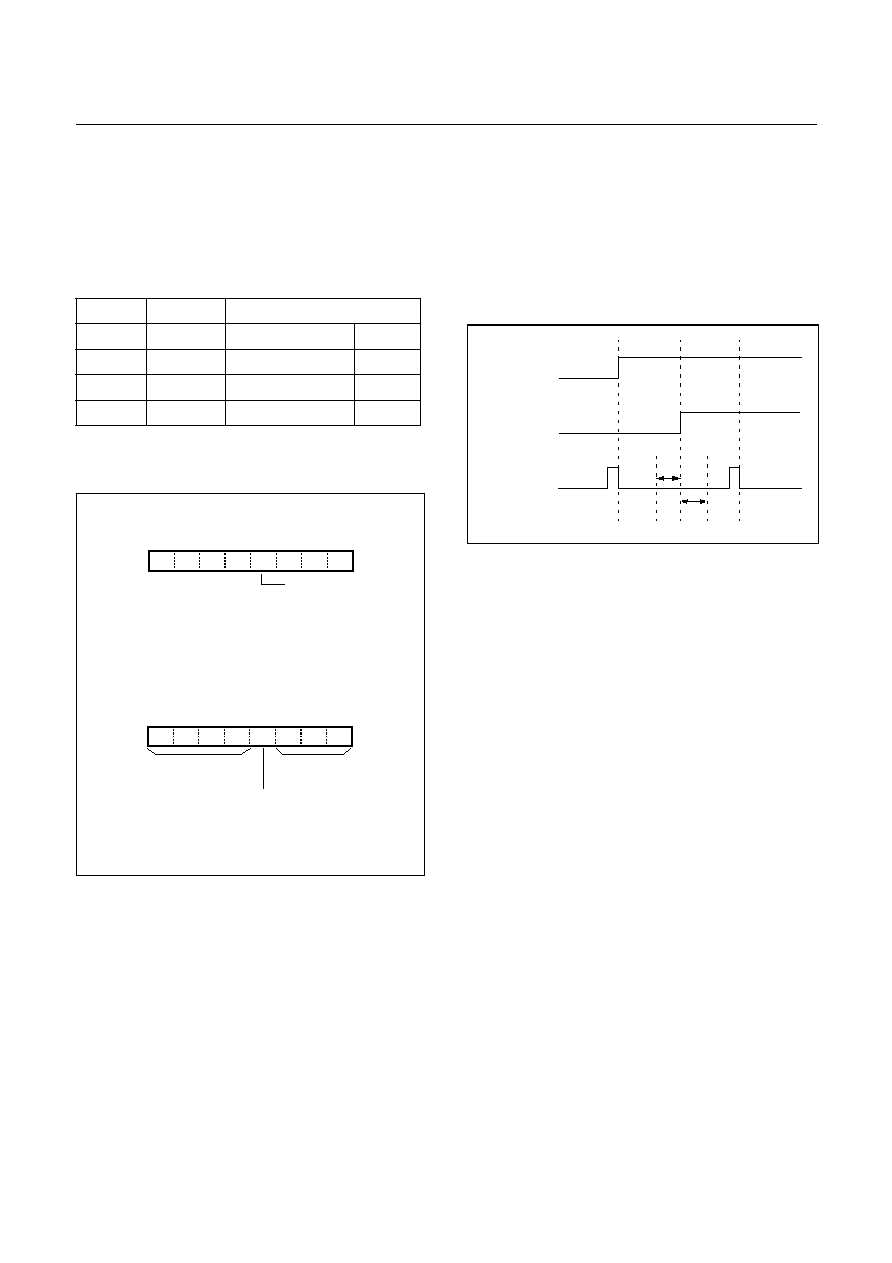

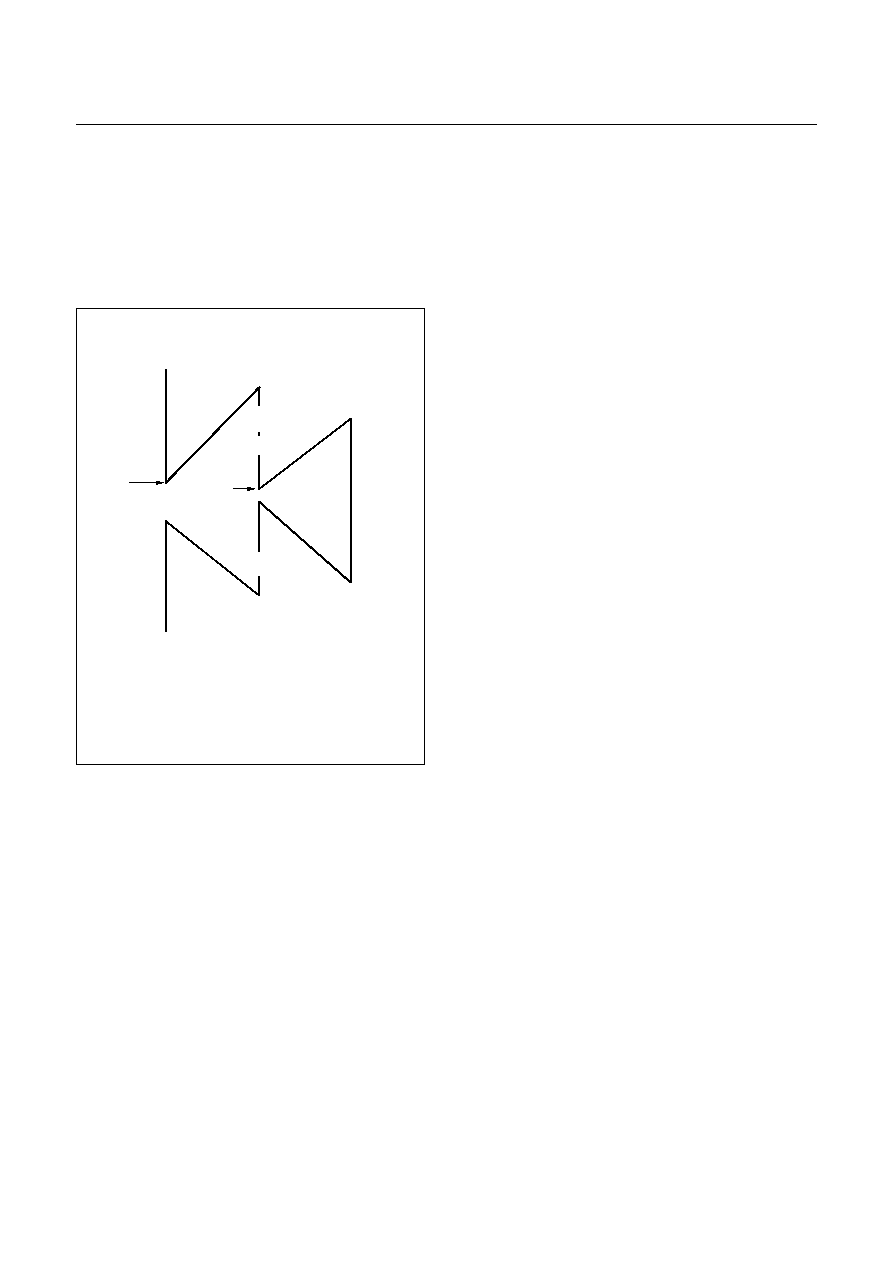

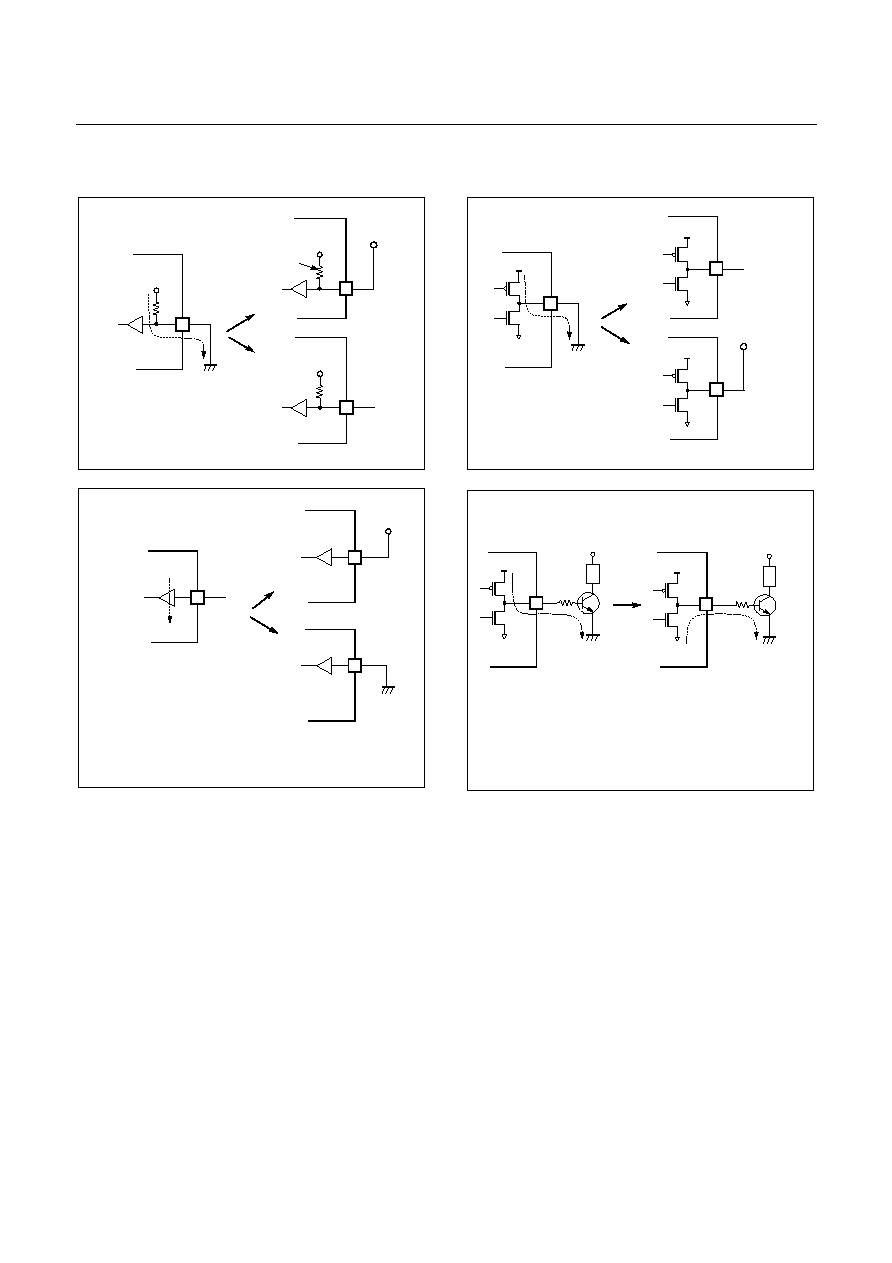

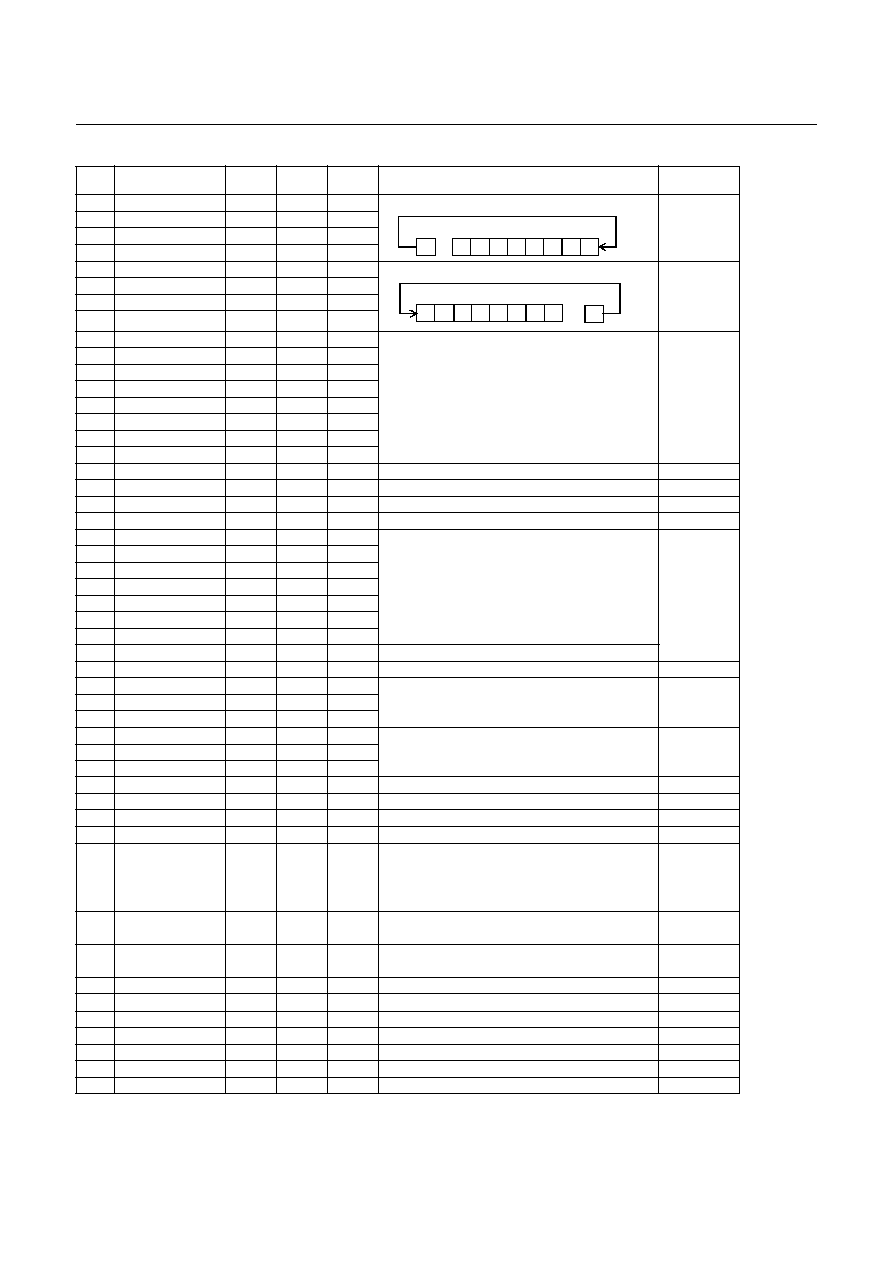

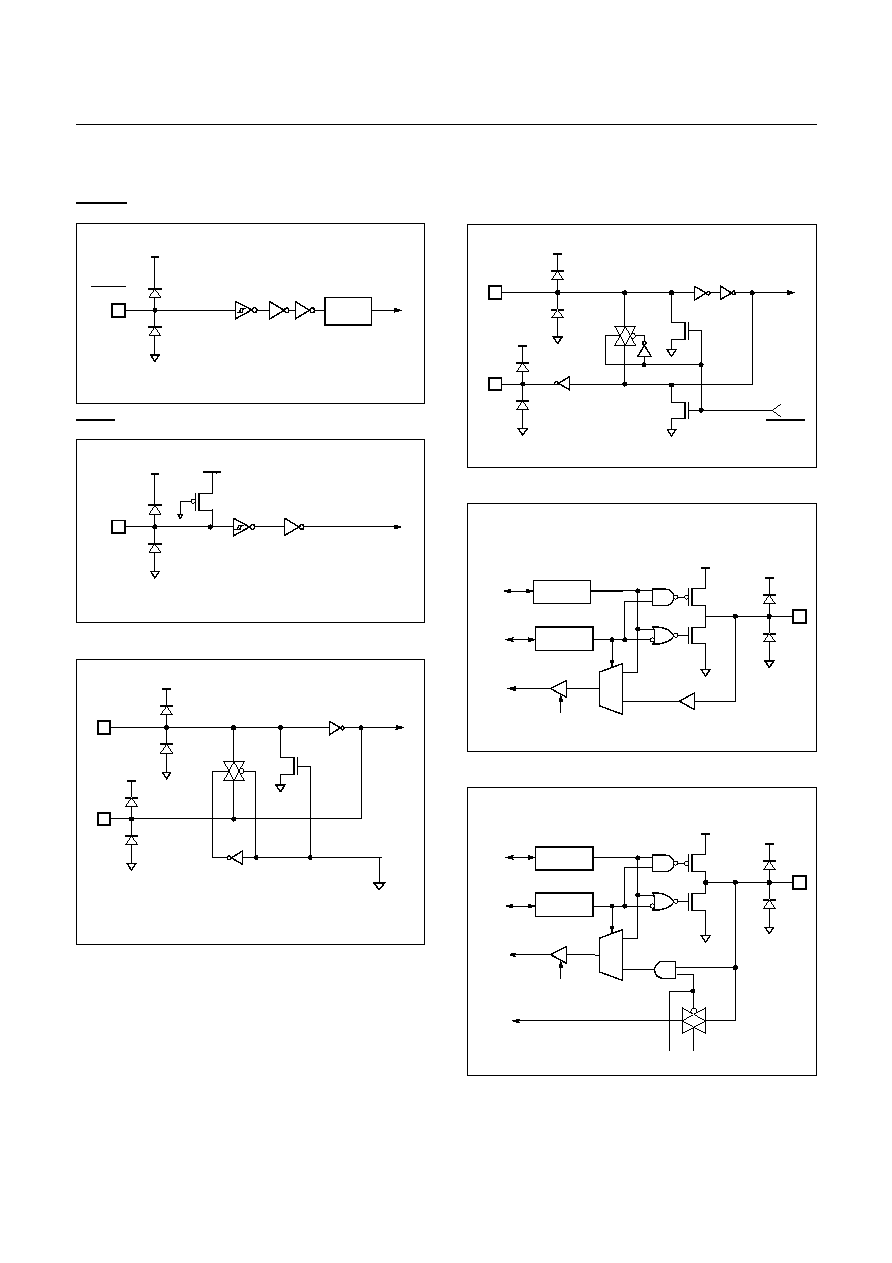

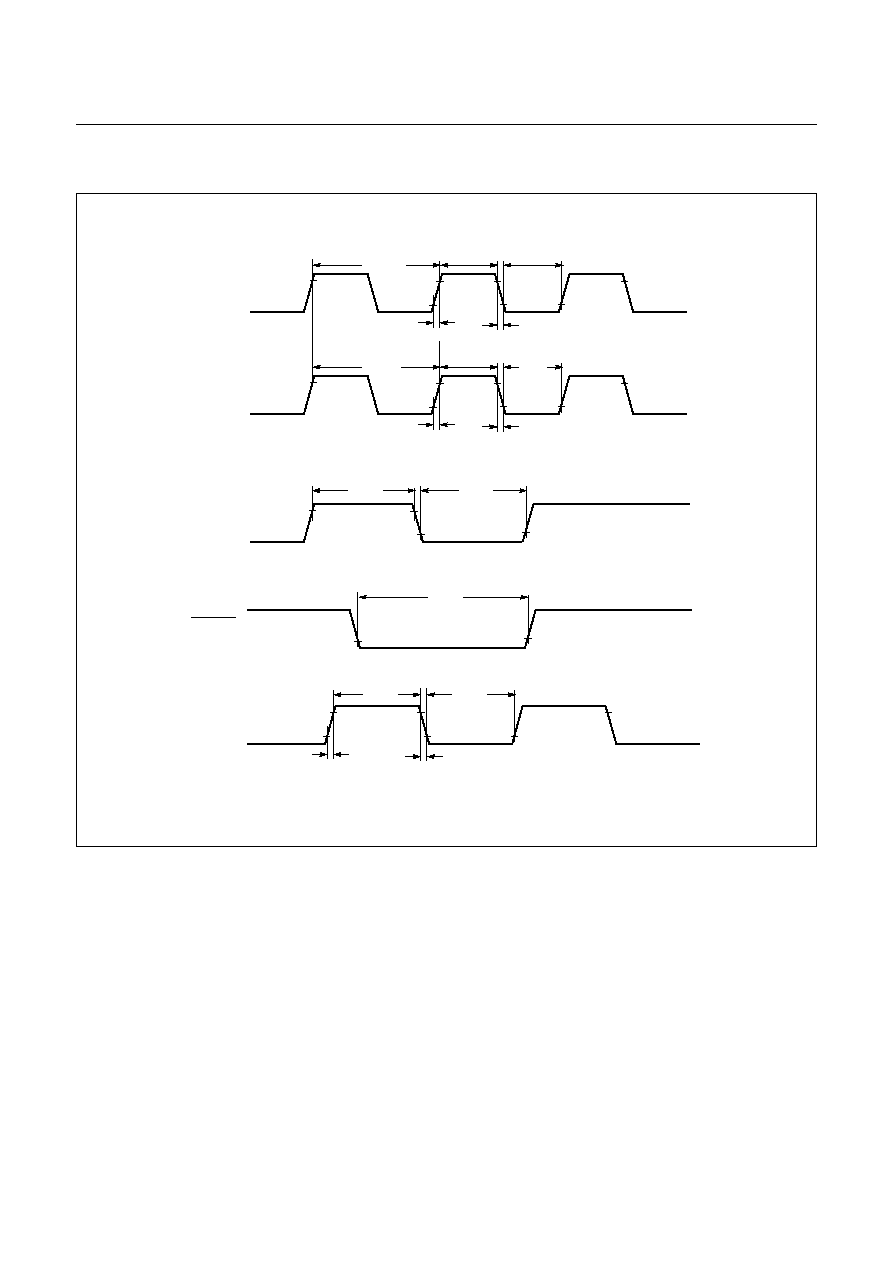

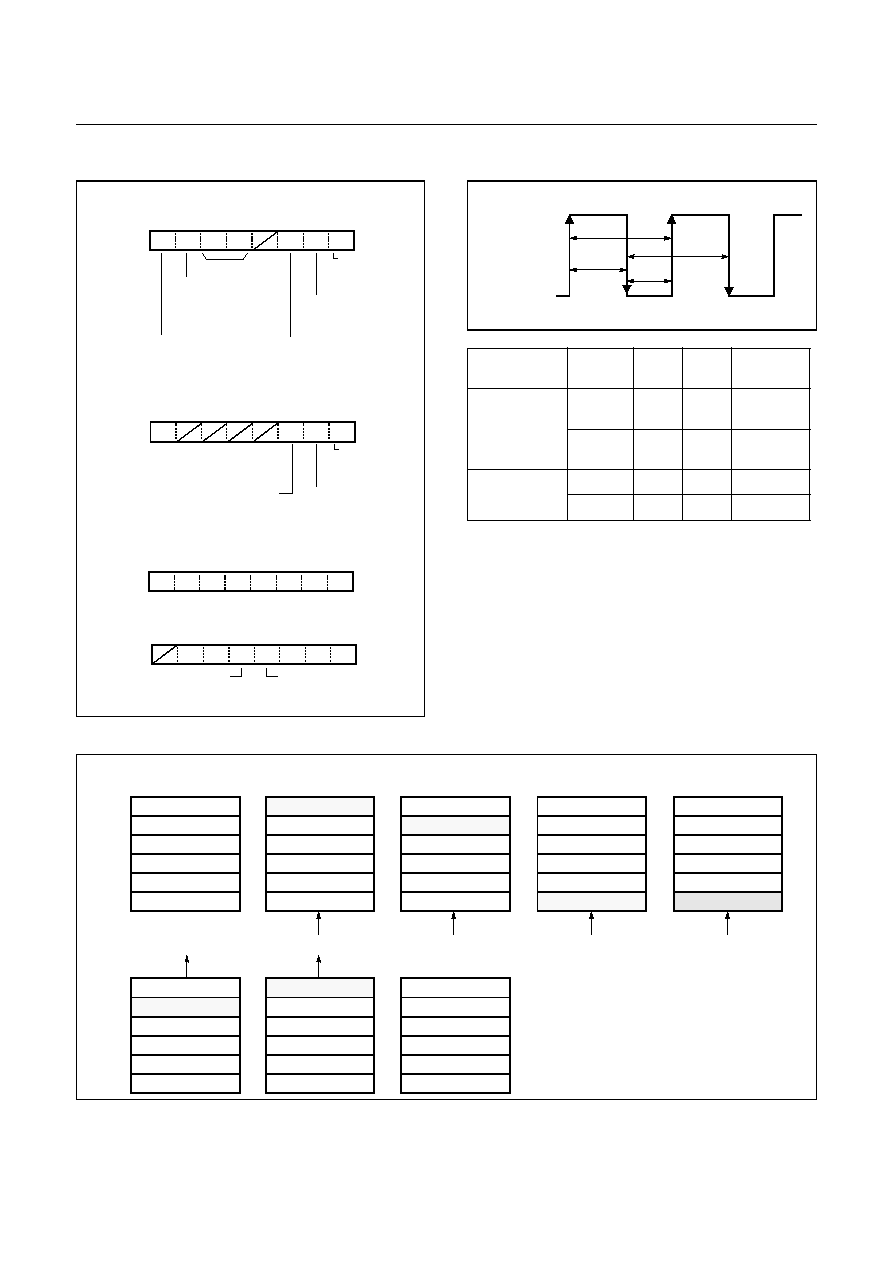

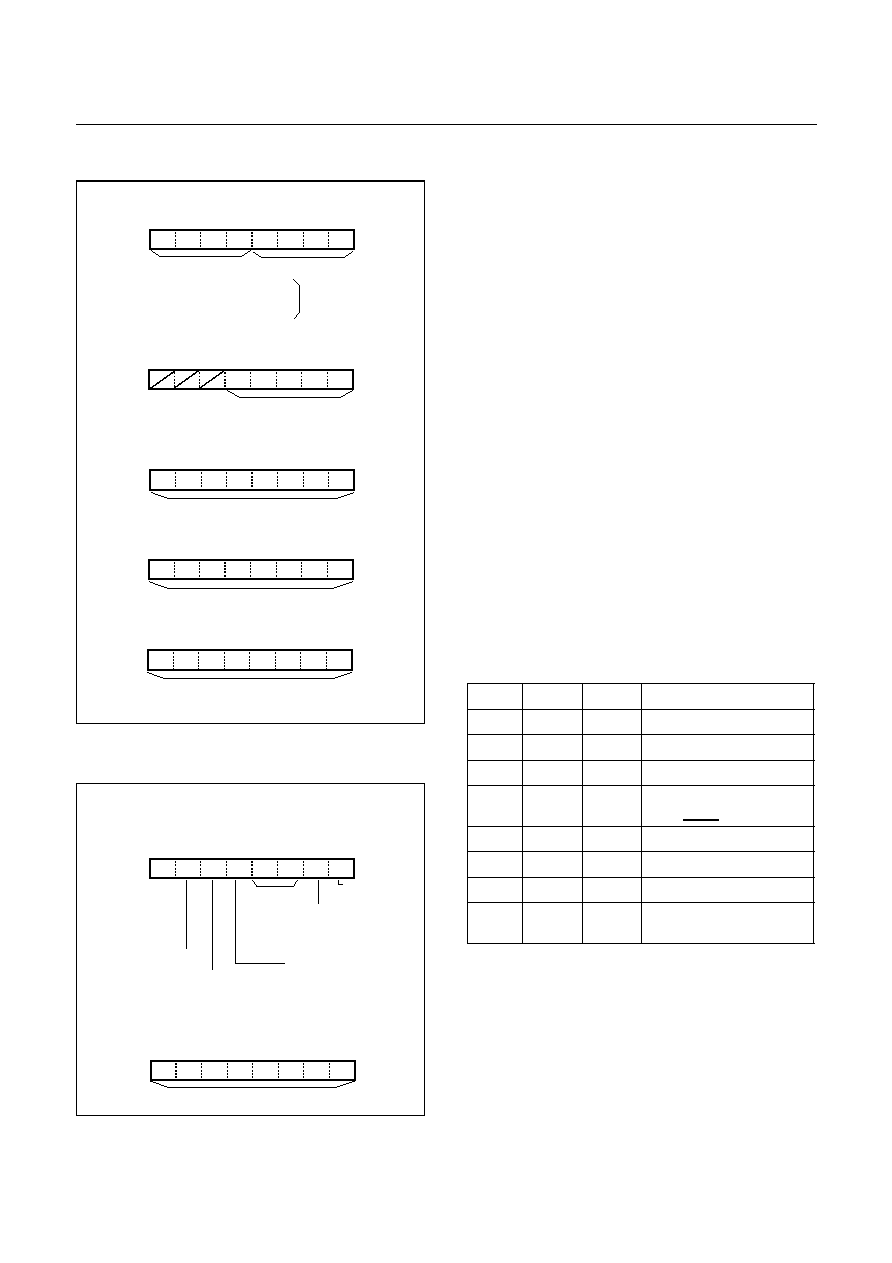

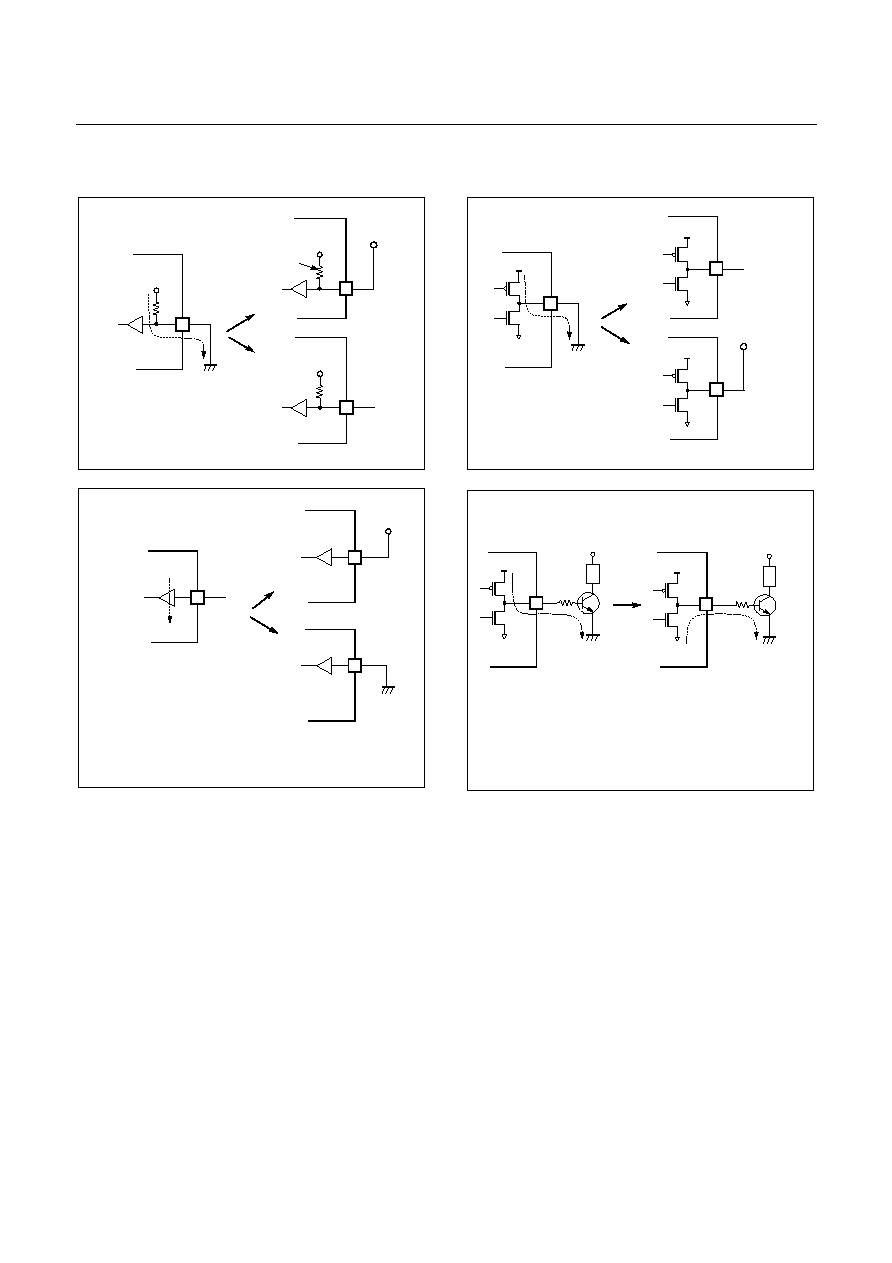

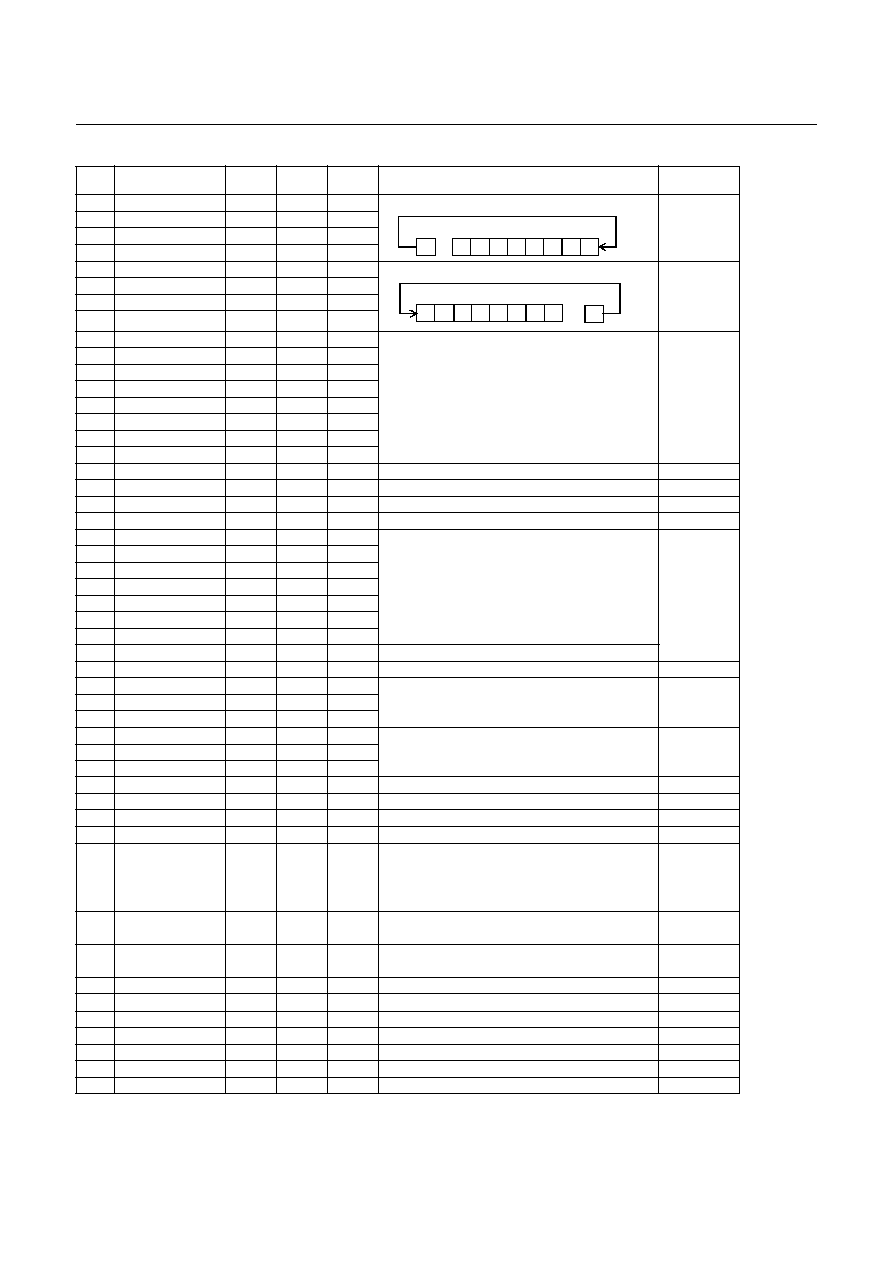

6. PORT STRUCTURES

RESET

TEST

X

IN

, X

OUT

OSC1, OSC2

R00~07, R53

R10~15 (AN0~5)

RESET

V

DD

V

SS

Noise

Canceler

V

DD

V

SS

X

IN

X

OUT

V

SS

V

DD

V

SS

V

DD

Main frequency

clock

V

S S

OSDON

OSC1

OSC2

V

SS

V

DD

V

SS

V

DD

Main frequency

clock

Pin

Data Reg.

Dir. Reg.

DB

DB

DB

MU X

RD

V

DD

V

SS

Pin

Data Reg.

Dir. Reg.

DB

DB

DB

MU X

RD

V

DD

V

SS

AN0~5

GMS81C4040/87C4060

HYUNDAI

10

May. 2000 Ver 1.0

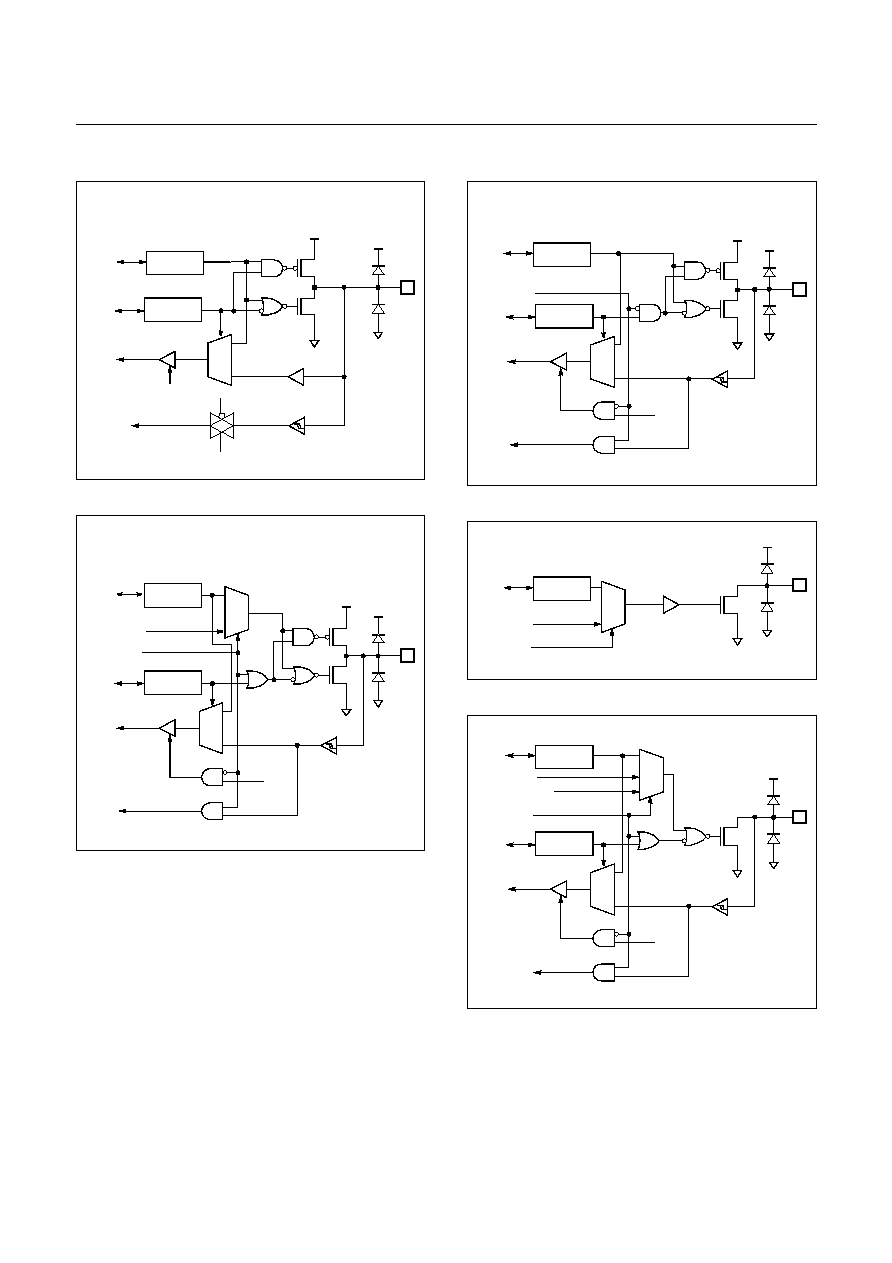

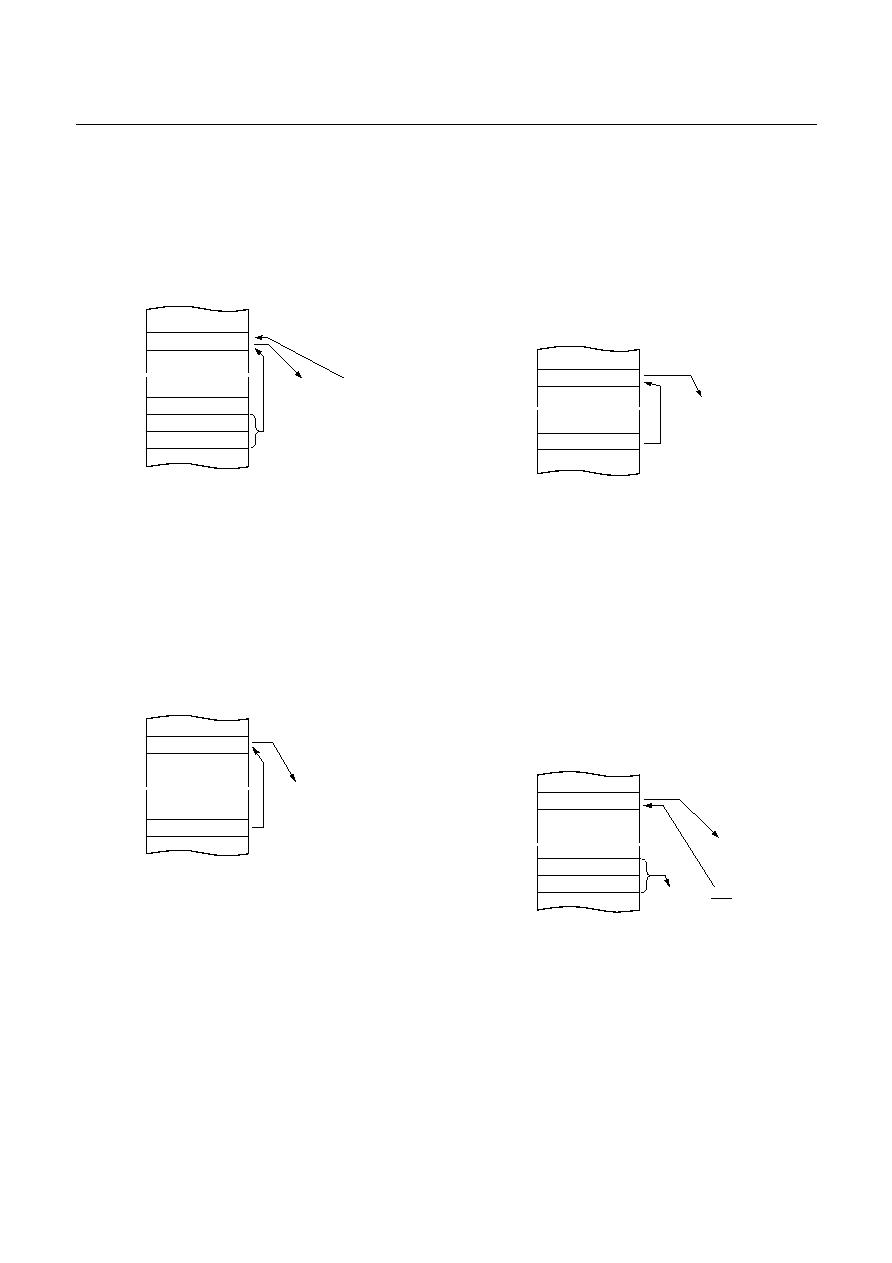

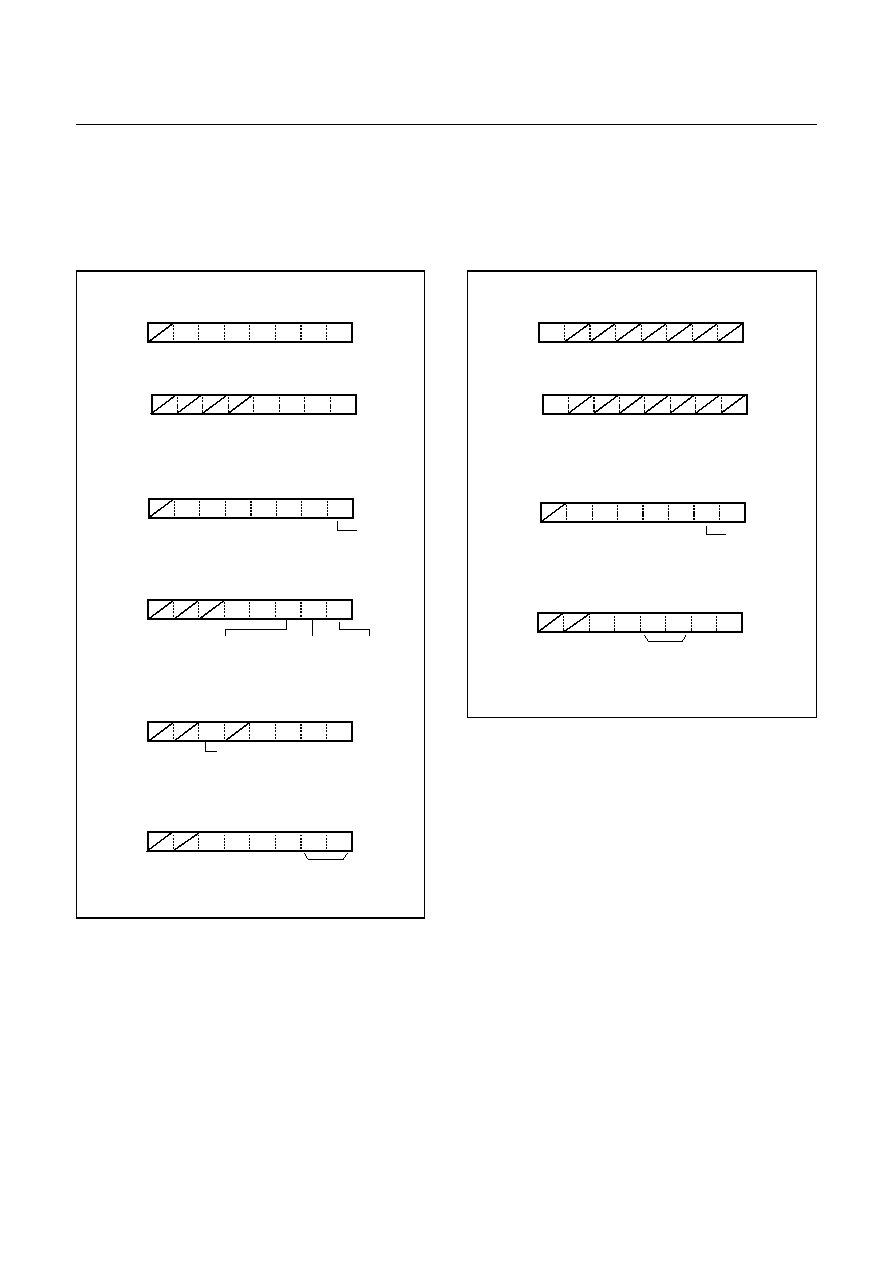

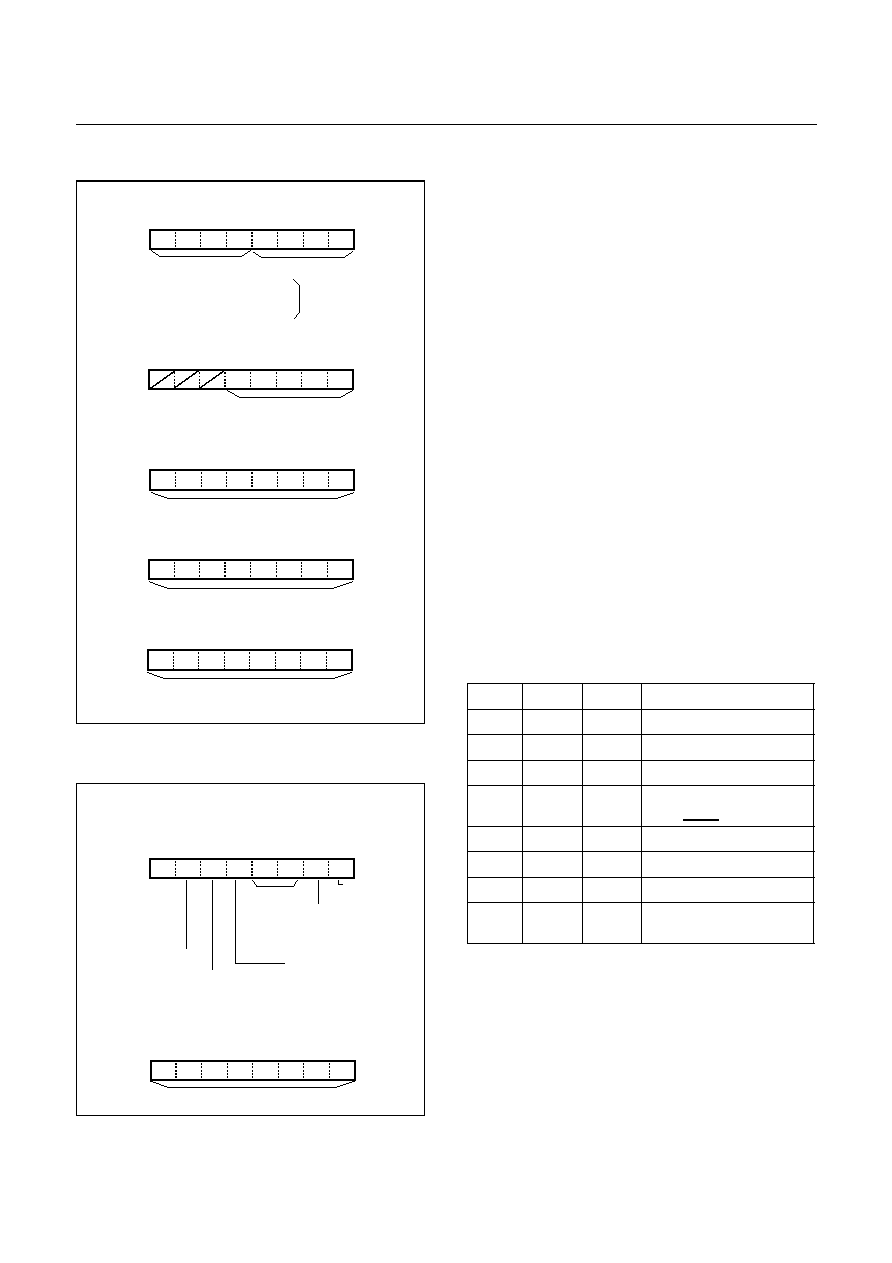

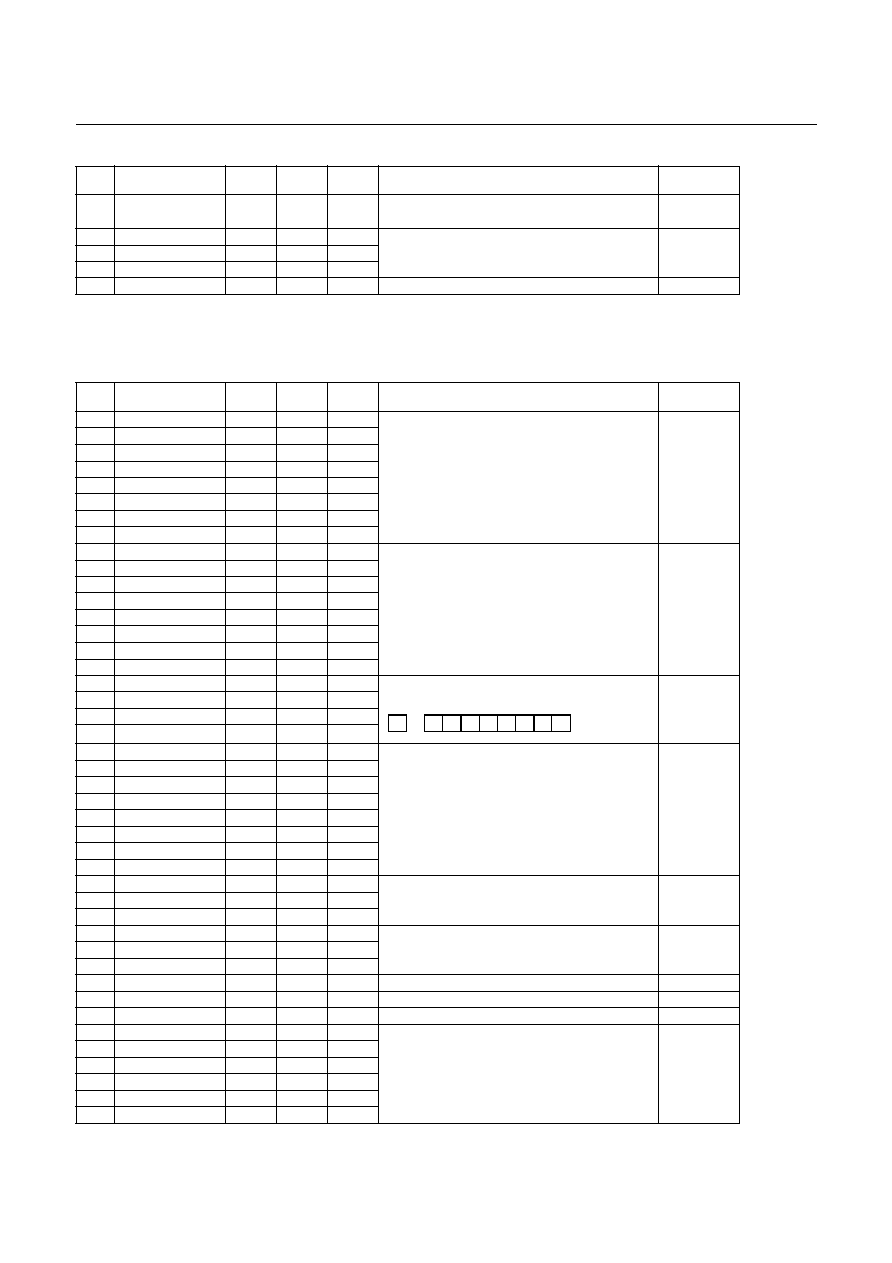

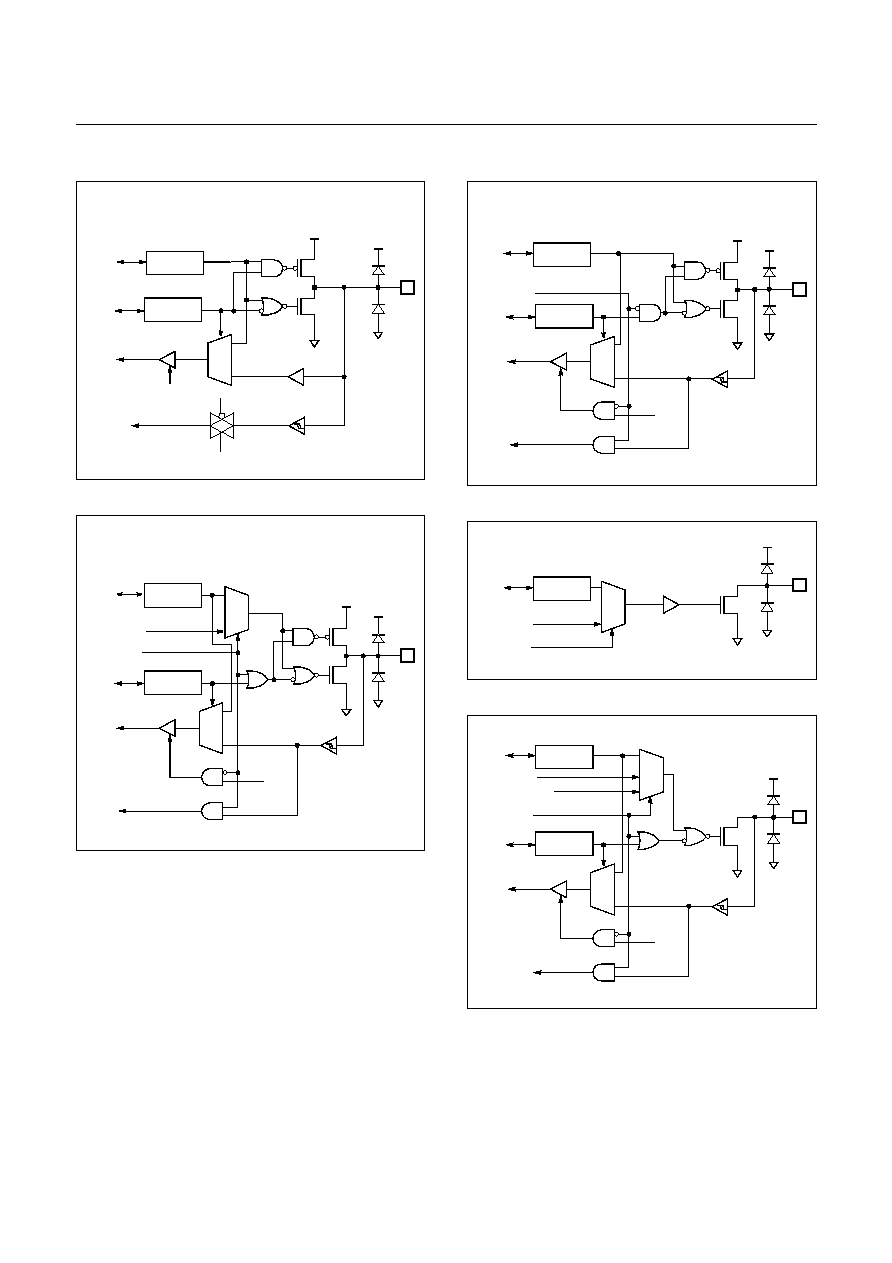

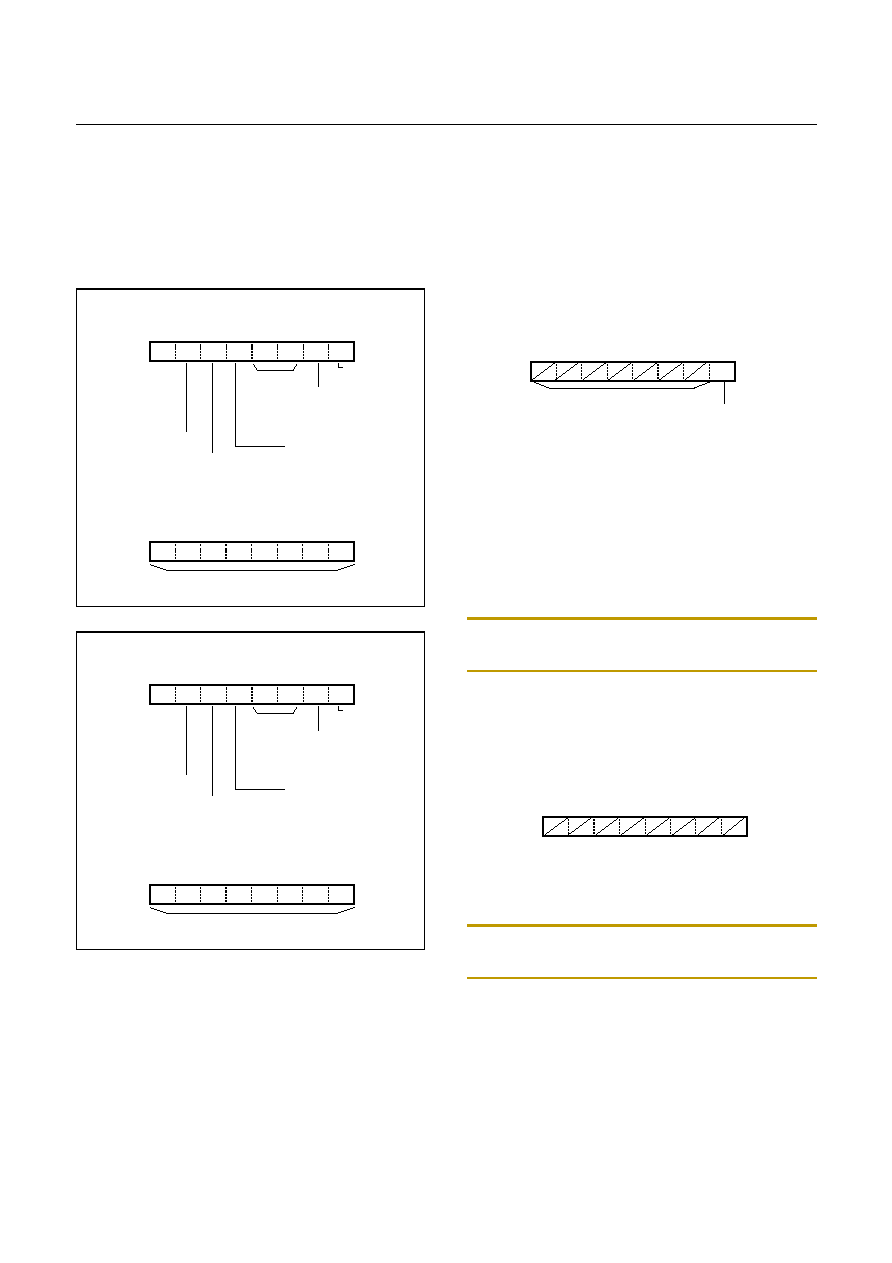

R16, 17, 20, 24, 25, 26, 27, 52, 67

R21/Sclk, R22/Sout

R23/Sin

R40~43 (PWM0~3)

R44, 45, 46, 47 (SCL, SDA, PWM)

Pin

Data Reg.

Dir. Reg.

DB

DB

DB

MU X

RD

V

DD

V

SS

HD,VD,

EC2~3

INT0~INT4

Pin

Data Reg.

Dir. Reg.

DB

DB

DB

M U X

RD

V

DD

V

SS

Sclk

M U X

Sout, Sclk

Selection

Pin

Data Reg.

Dir. Reg.

DB

DB

DB

M U X

RD

V

DD

V

SS

Sin

Selection

Pin

Data Reg.

DB

V

SS

M UX

PWM0~3

Selection

Pin

Data Reg.

Dir. Reg.

DB

DB

DB

M U X

RD

V

SS

SCL, SDA

M U X

PWM4,PWM5

Selection

SCL,SDA

HYUNDAI

GMS81C4040/87C4060

May. 2000 Ver 1.0

11

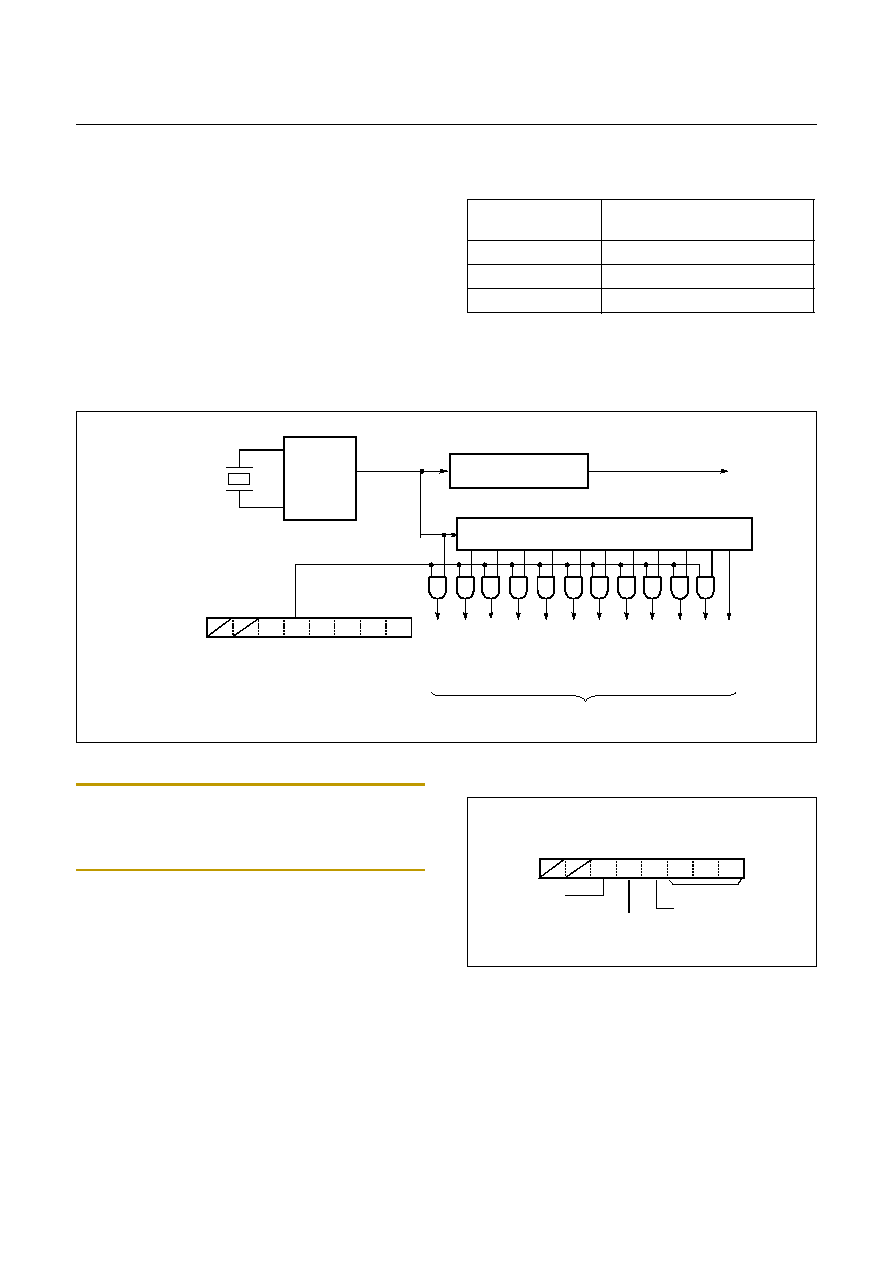

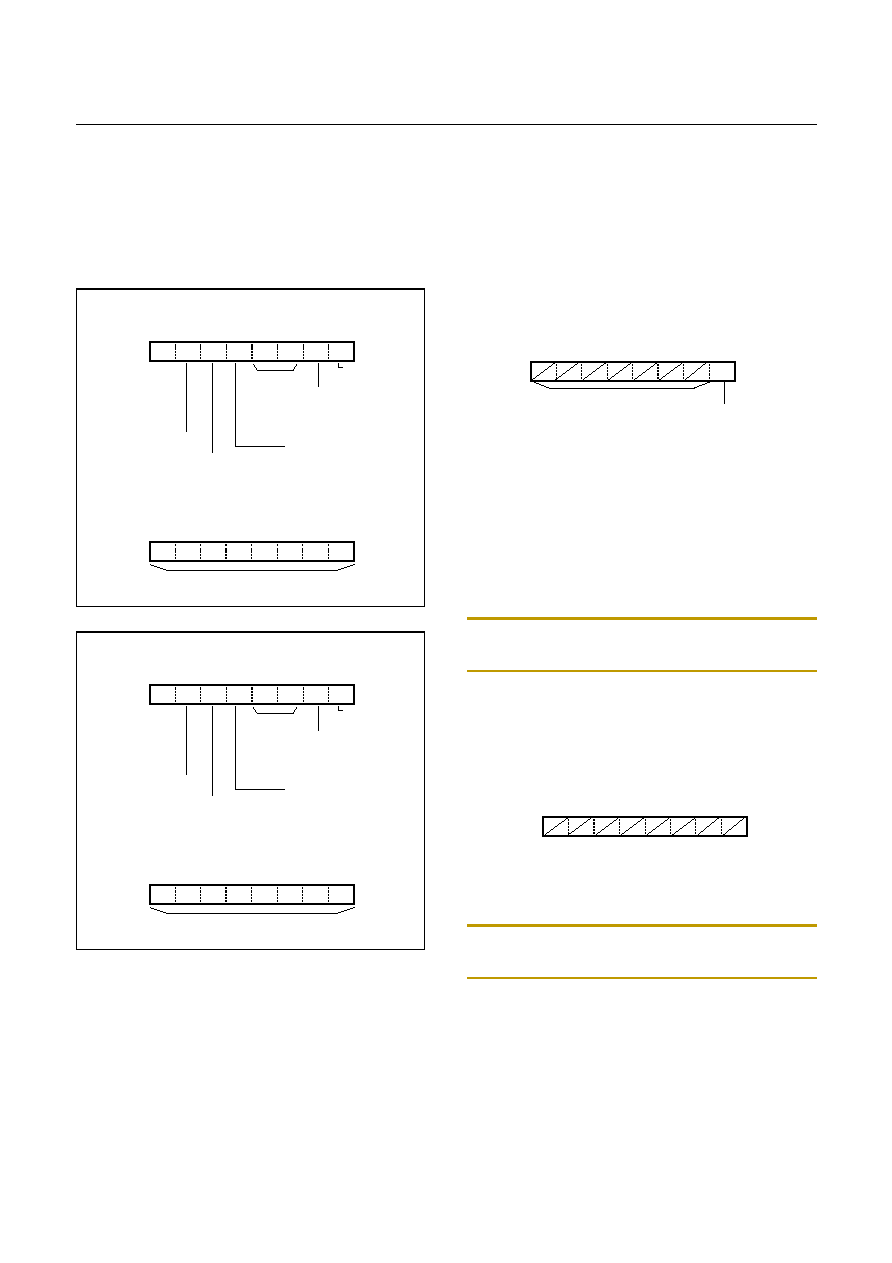

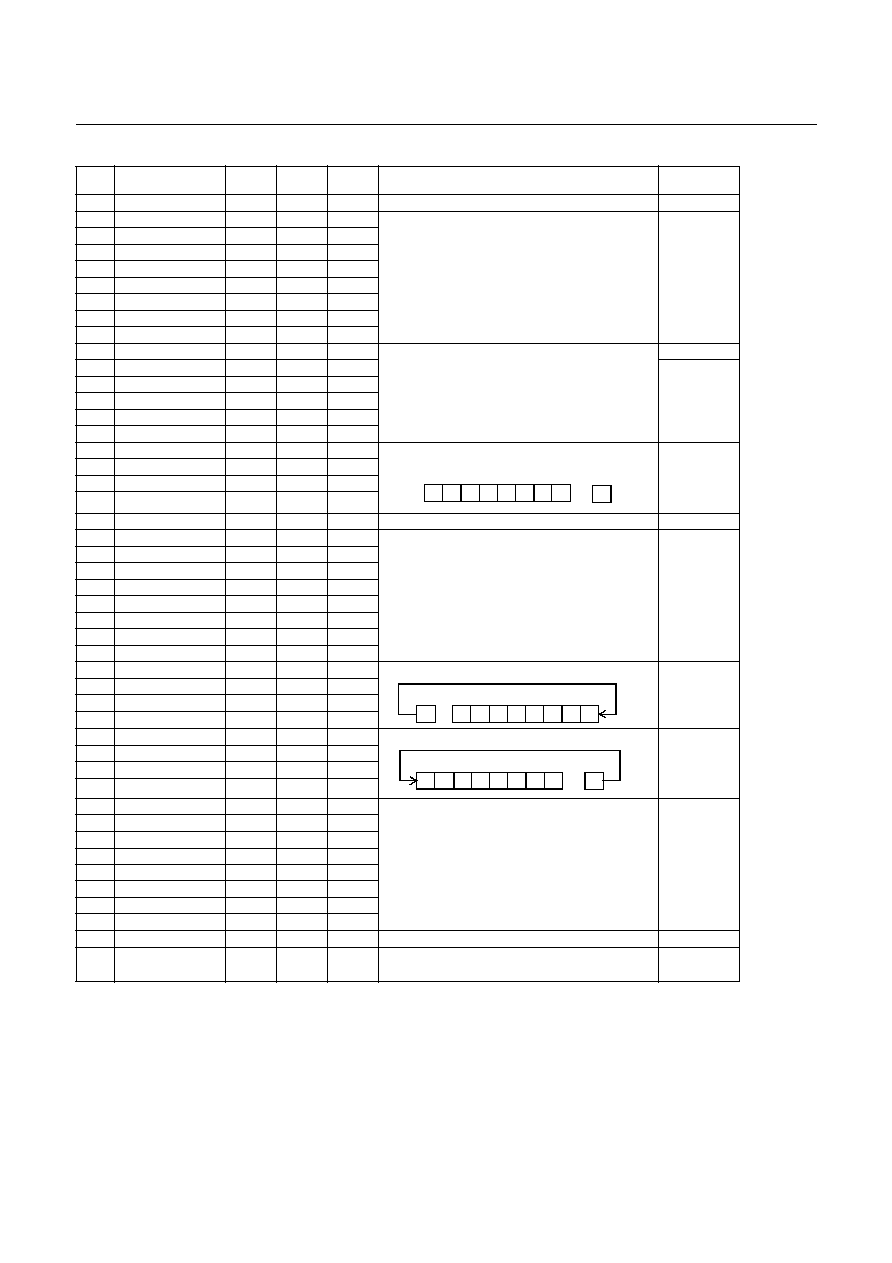

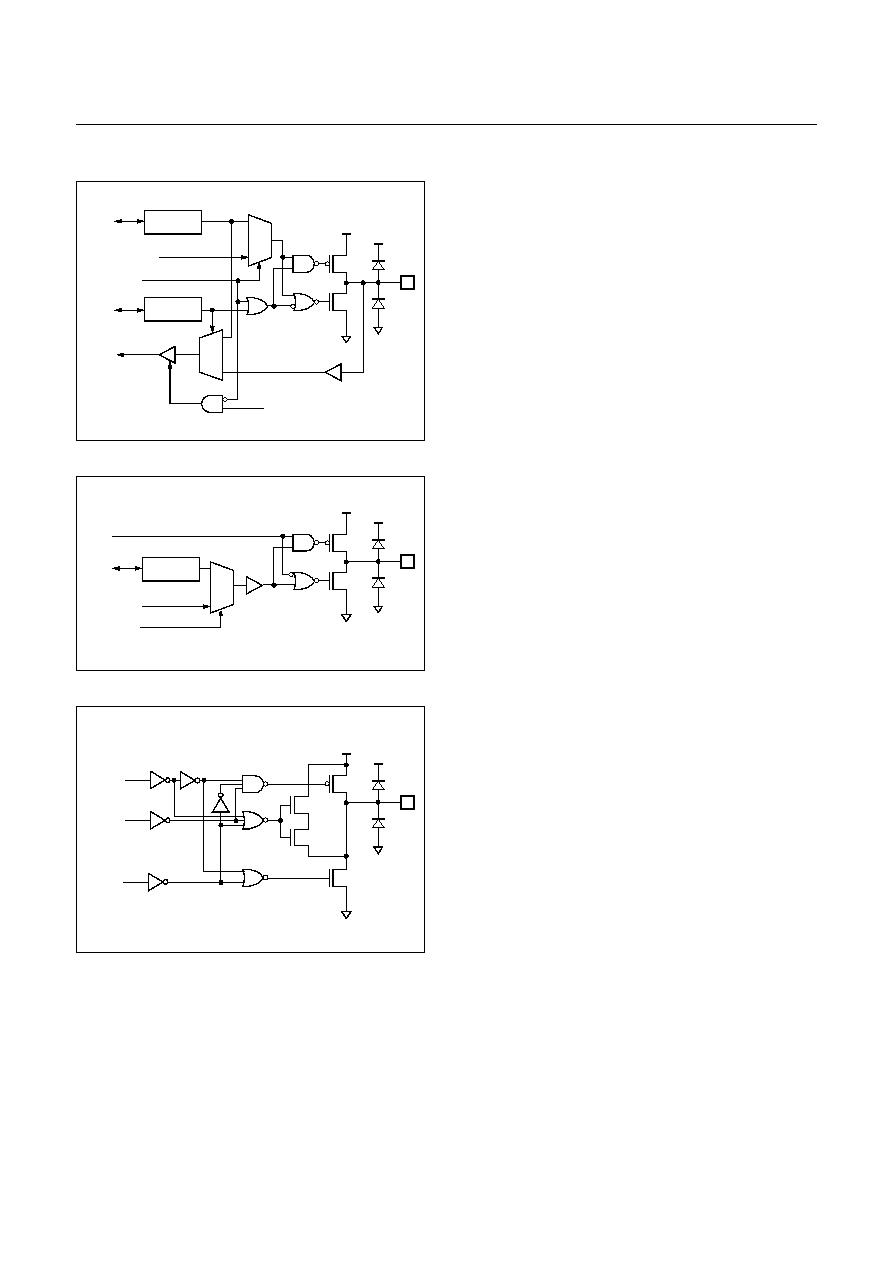

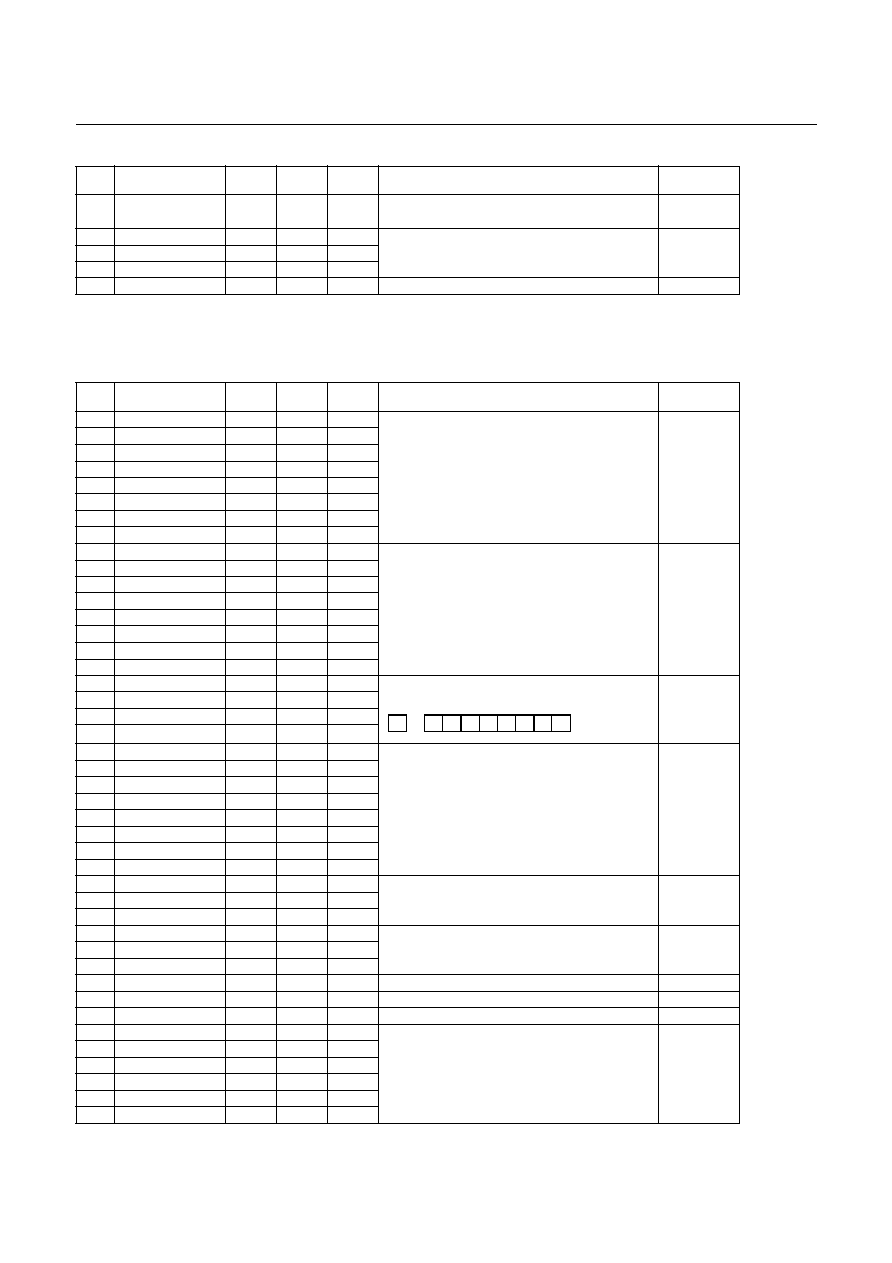

R50/BUZZ, R51/PWM8

R54/YM, R55/YS, R56/I

R, G, B

Pin

Data Reg.

Dir. Reg.

DB

DB

DB

M U X

RD

V

DD

V

SS

M U X

Buzz, PWM8

Selection

Pin

Data Reg.

DB

V

DD

V

SS

M UX

YM, YS, I

Selection

OSD ON or Data Reg Write.

Pin

R, G, B

V

DD

V

SS

i

OSD_ON

GMS81C4040/87C4060

HYUNDAI

12

May. 2000 Ver 1.0

7. ELECTRICAL CHARACTERISTICS

7.1 Absolute Maximum Ratings

Supply voltage ........................................... -0.3 to +6.0 V

Storage Temperature ................................-40 to +125

�

C

Voltage on any pin with respect to Ground (V

SS

)

............................................................... -0.3 to V

DD

+0.3

Maximum current out of V

SS

pin ........................100 mA

Maximum current into V

DD

pin ............................80 mA

Maximum current sunk by (I

OL

per I/O Pin) ........20 mA

Maximum output current sourced by (I

OH

per I/O Pin)

.................................................................................8 mA

Maximum current (

I

OL

) ...................................... 80 mA

Maximum current (

I

OH

)...................................... 50 mA

Note: Stresses above those listed under "Absolute Maxi-

mum Ratings" may cause permanent damage to the de-

vice. This is a stress rating only and functional operation of

the device at any other conditions above those indicated in

the operational sections of this specification is not implied.

Exposure to absolute maximum rating conditions for ex-

tended periods may affect device reliability.

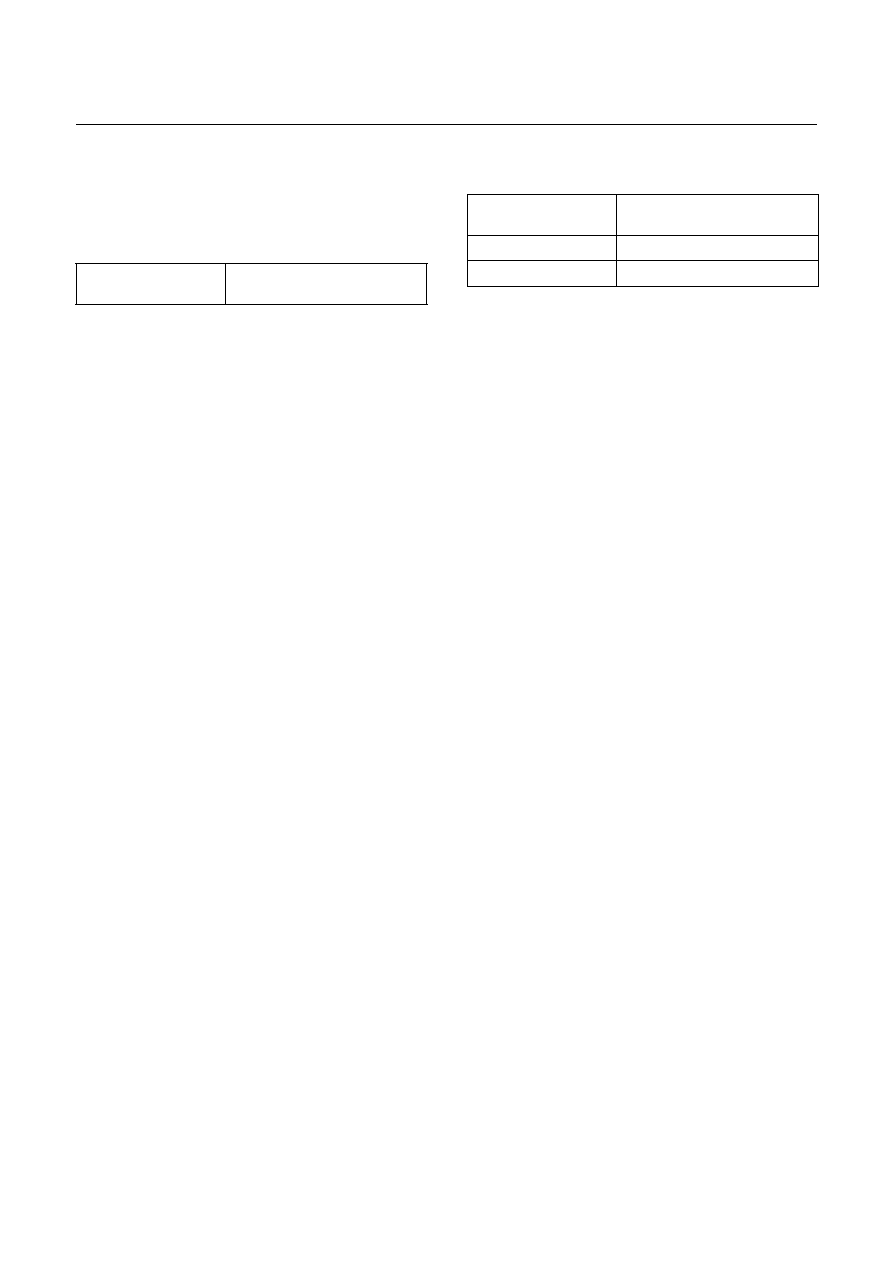

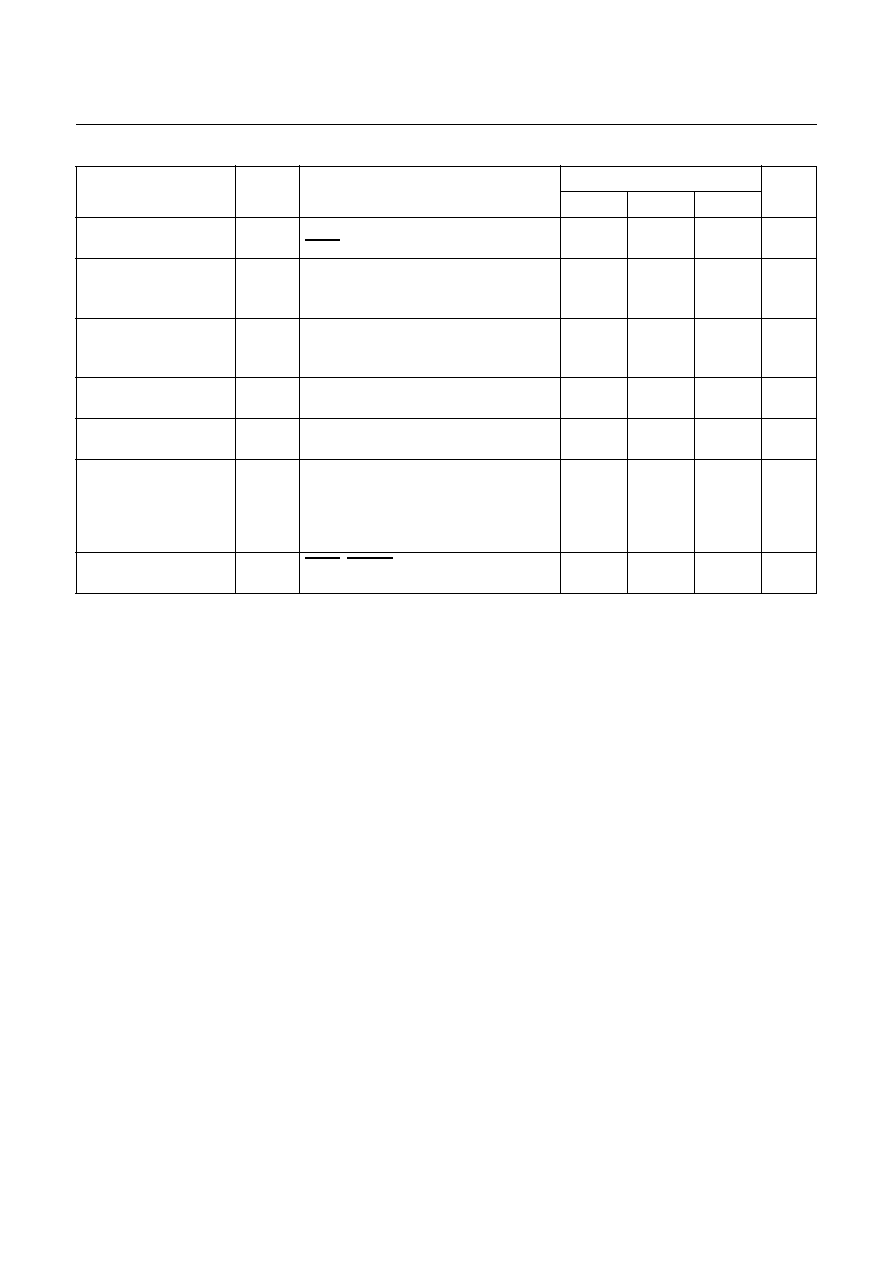

7.2 Recommended Operating Conditions

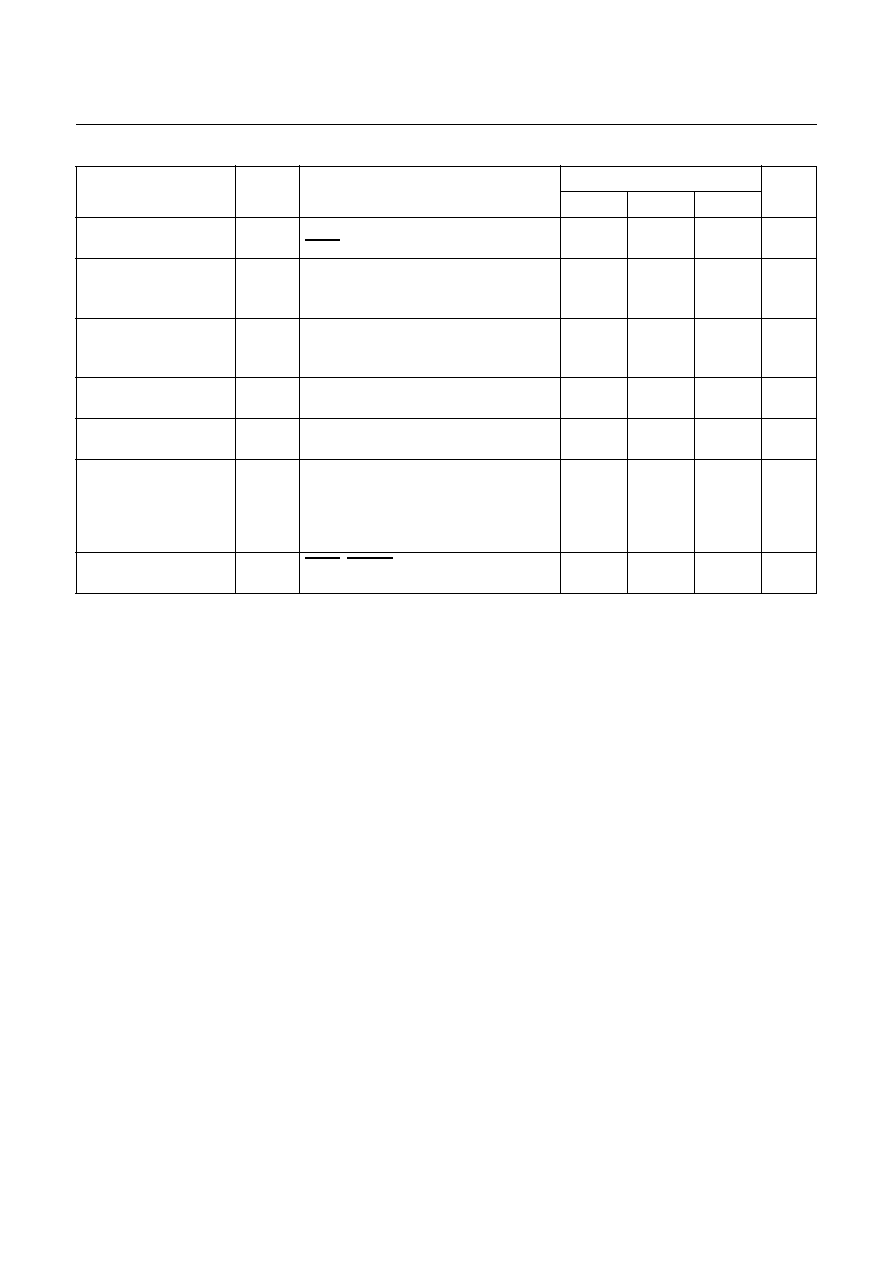

7.3 DC Electrical Characteristics - GMS81C4040

(T

A

=-10~70

�

C, V

DD

=4.5~5.5V)

,

Parameter

Symbol

Condition

Specifications

Unit

Min.

Max.

Supply Voltage

V

DD

f

XIN

=8MHz

f

OSC

=16MHz

4.5

5.5

V

Operating Frequency

f

XIN

V

DD

=4.5~5.5V

4

8

MHz

On Screen Display Oper-

ating Frequency

f

OSC

V

DD

=4.5~5.5V

8

16

MHz

Operating Temperature

T

OPR

-10

70

�

C

Parameter

Symbol

Condition

Specifications

Unit

Min.

Typ.

Max.

High level input voltage

V

IH1

TEST, RESET, Xin, OSC1, R17~16,

R27~20, R47~44, R52, R67

0.8 V

DD

-

V

DD

V

V

IH2

R0, R15~10, R53~50

0.7 V

DD

-

V

DD

V

Low level input voltage

V

IL1

TEST, RESET, Xin, OSC1, R17~16,

R27~20, R47~44, R52, R67

0

-

0.12 V

DD

V

V

IL2

R0, R15~10, R53~50

0

-

0.3 V

DD

V

High level output voltage

V

OH

I

OH

= -5mA

R0, R1, R2, R5, R67

V

DD

- 1

-

-

V

I

OH

= -1.2mA

R,G,B

V

DD

- 1

-

-

V

Low level output voltage

V

OL

I

OL

= 5mA

R0, R1, R2, R4, R5, R67, R, G, B

-

-

1.0

V

Supply current in

ACTIVE mode

I

DD

V

DD

-

-

30

mA

HYUNDAI

GMS81C4040/87C4060

May. 2000 Ver 1.0

13

pull-up lekage current

I

RUP

V

DD

= 5.5v, V

PIN

= 0.4V

TEST

-1.5

-400

�

A

High input leakage

current

I

IZH

V

DD

= 5.5V

,

V

PIN

= V

DD

All input, I/O pins except X

IN

, OSC1,

R47~40

-5

-

5

�

A

Low input leakage

current

I

IZL

V

DD

= 5.5V

,

V

PIN

= 0V

All input, I/O pins except X

IN

, OSC1,

R47~44

-5

-

5

�

A

Open drain leakage

current

I

LOZ

V

DD

= 5.5V

,

V

OH

= V

DD

, N-ch Tr. off

R47~40

-

-

10

�

A

RAM data retention

voltage

V

RAM

V

DD

1.2

-

-

V

I

2

C port impedance

(I/O Transistor off)

R

BS

V

DD

= 4.5V

,

V

SCL0

= V

SCL1

= 2.25V

V

SDA0

= V

SDA1

= 2.25V

SCL0:SCl1 (R44:R45)

SDA0:SDA1 (R46:R47)

-

-

120

Hysterisis

Vt+ ~

Vt-

TEST, RESET, Xin, OSC1, R17~16,

R27~20, R47~44, R52, R67

1.0

-

-

V

Parameter

Symbol

Condition

Specifications

Unit

Min.

Typ.

Max.

GMS81C4040/87C4060

HYUNDAI

14

May. 2000 Ver 1.0

7.4 A/D Comparator Characteristics

(T

A

=-10~70

�

C, V

DD

=5.0V)

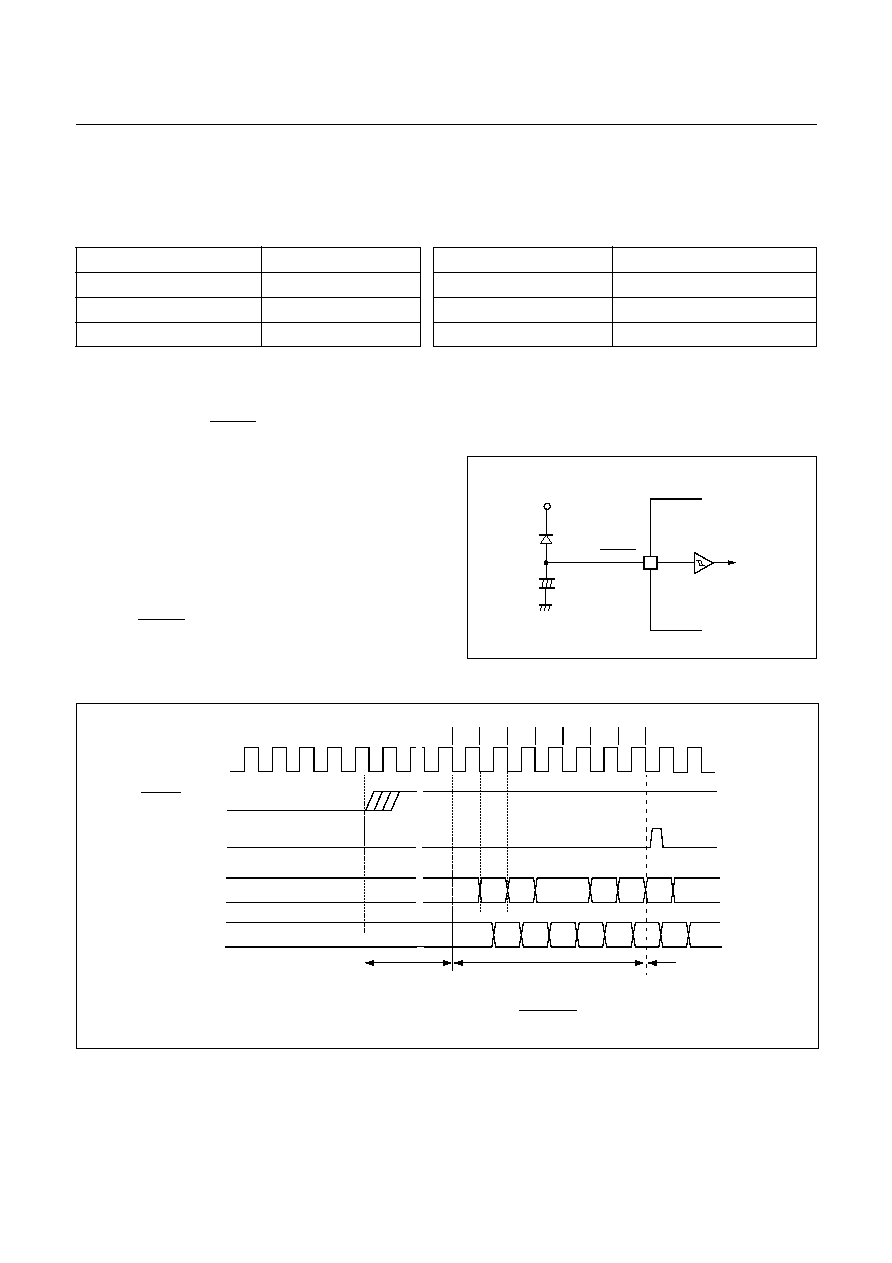

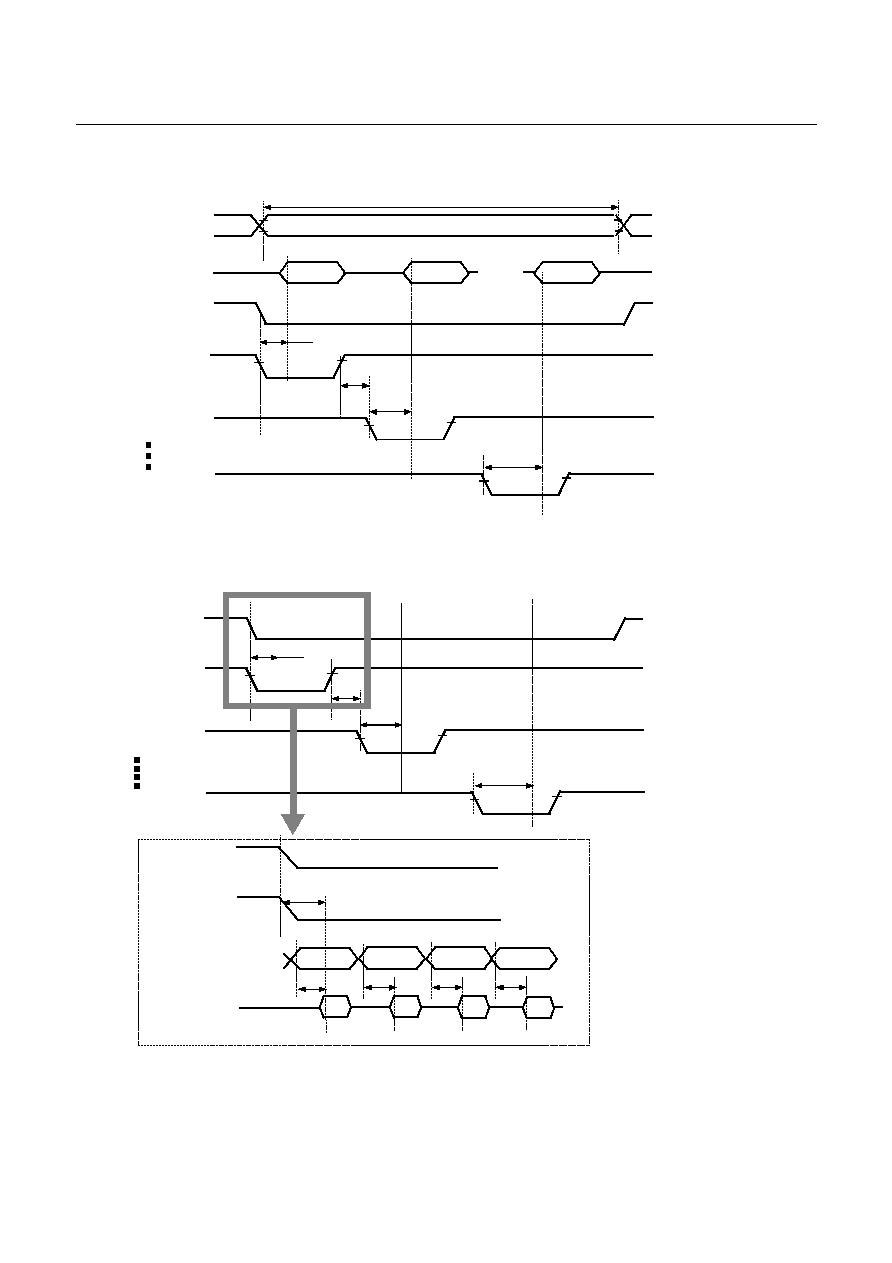

7.5 AC Characteristics

(T

A

=-10~70

�

C, V

DD

=5V

�

10%

,

V

SS

=0V)

Parameter

Symbol

Pins

Specifications

Unit

Min.

Typ.

Max.

Analog Input Voltage Range

V

AIN

AN0~AN5

V

SS

-

V

DD

V

Accuracy

N

FS

-

-

-

LSB

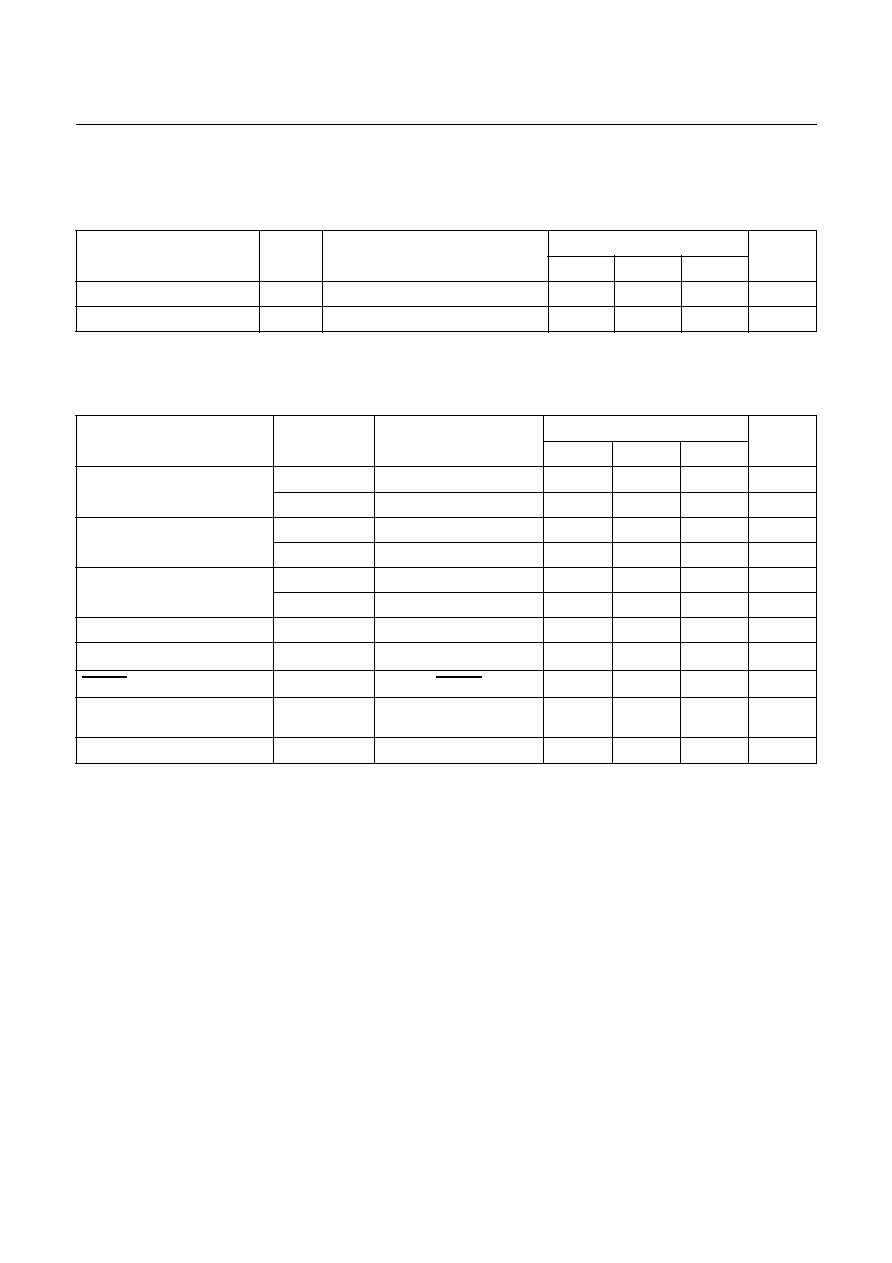

Parameter

Symbol

Pins

Specifications

Unit

Min.

Typ.

Max.

Operating Frequency

f

XIN

X

IN

4

-

8

MHz

f

OSC

OSC

8

-

16

MHz

External Clock Pulse Width

t

MCPW

X

IN

62.5

-

125

nS

t

SCPW

S

CLK

0.5

-

�

S

External Clock Transition Time

t

MRCP,

t

MFCP

X

IN

-

-

20

nS

t

SRCP,

t

SFCP

S

CLK

-

-

20

nS

Oscillation Stabilizing Time

t

ST

X

IN

, X

OUT

-

-

20

mS

Interrupt Pulse Width

t

IW

INT0~4

2

-

-

t

SYS

1

RESET Input Width

t

RST

RESET

8

-

-

t

SYS

1

Event Counter Input Pulse

Width

t

ECW

EC2, EC3

2

-

-

t

SYS

1

Event Counter Transition Time

t

REC,

t

FEC

EC2, EC3

-

-

20

nS

1. t

SYS

is one of 2/f

XIN

main clock operation mode,

HYUNDAI

GMS81C4040/87C4060

May. 2000 Ver 1.0

15

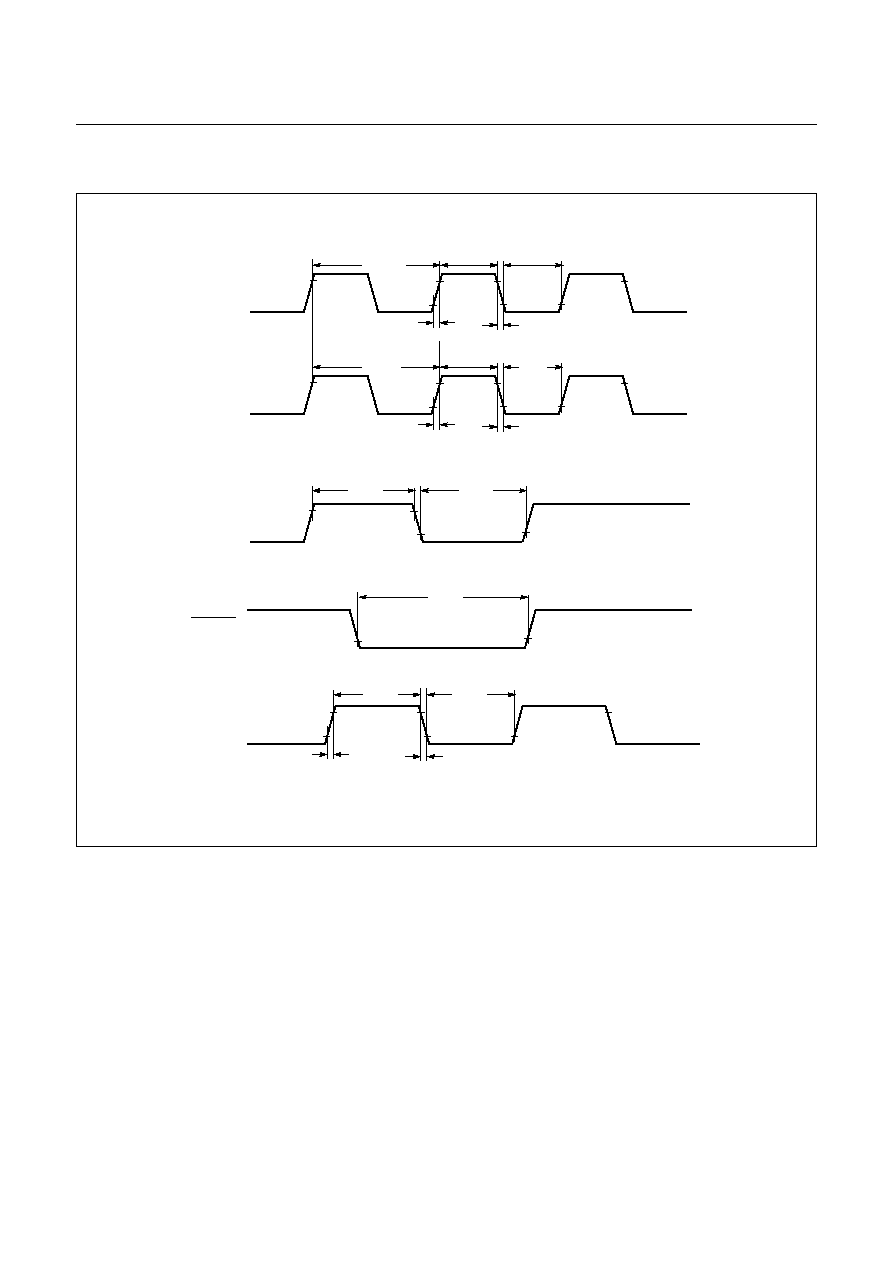

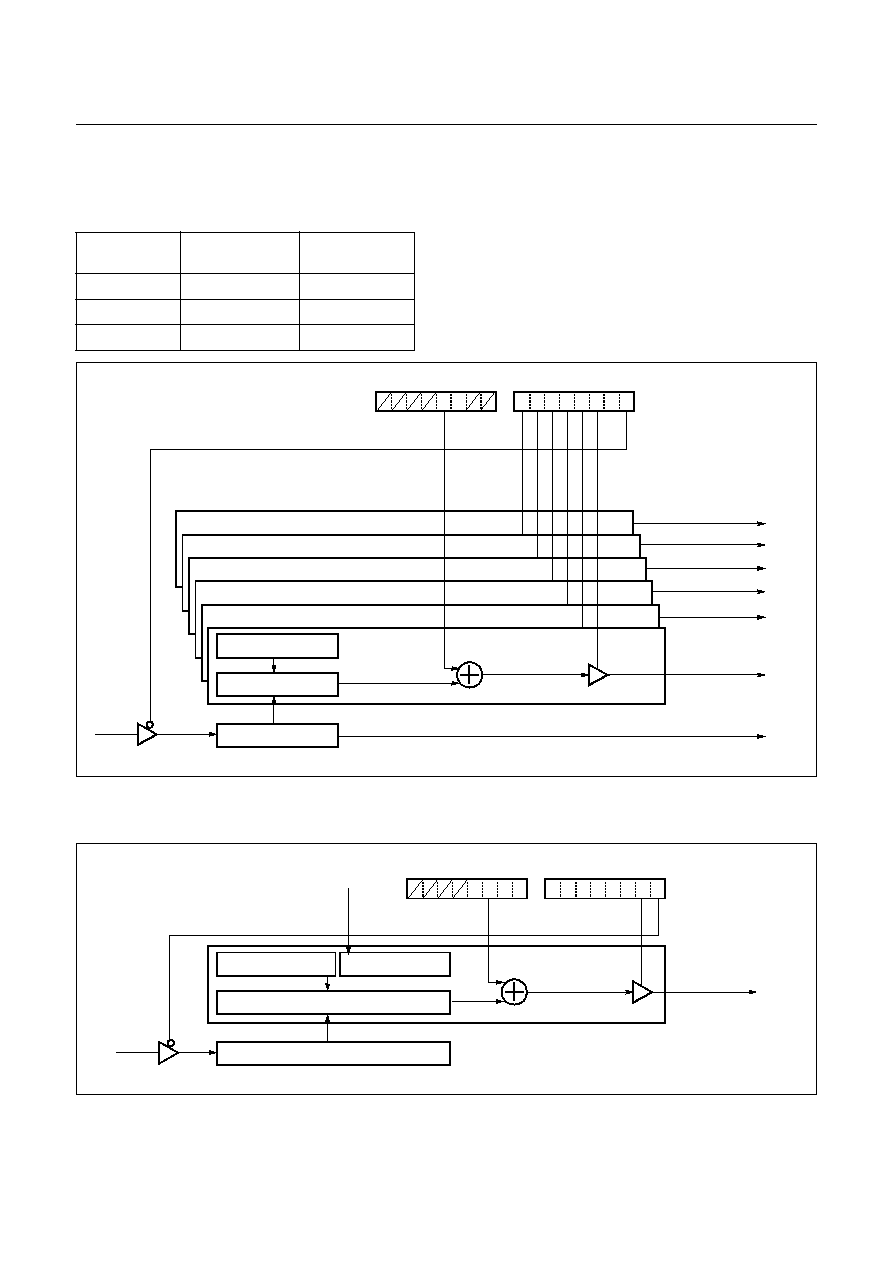

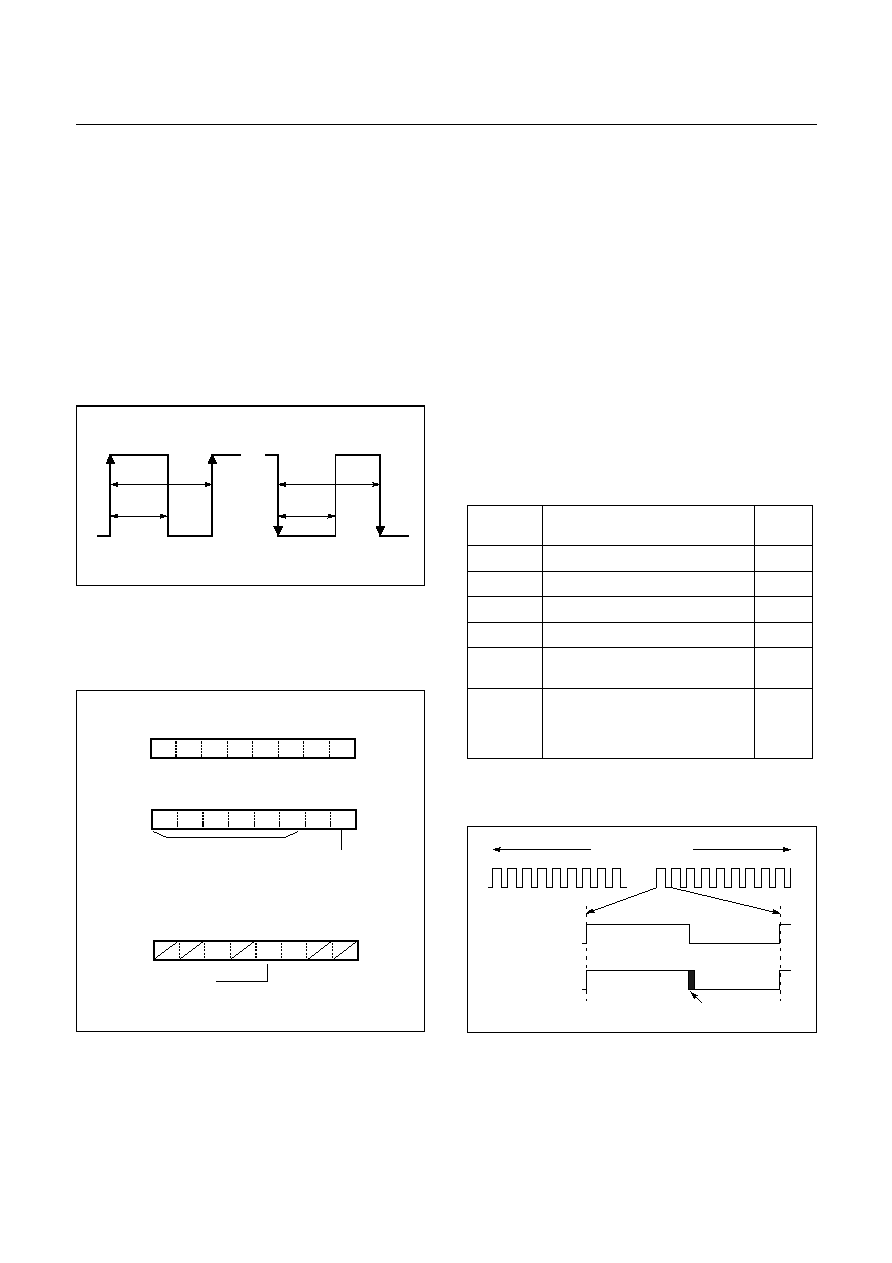

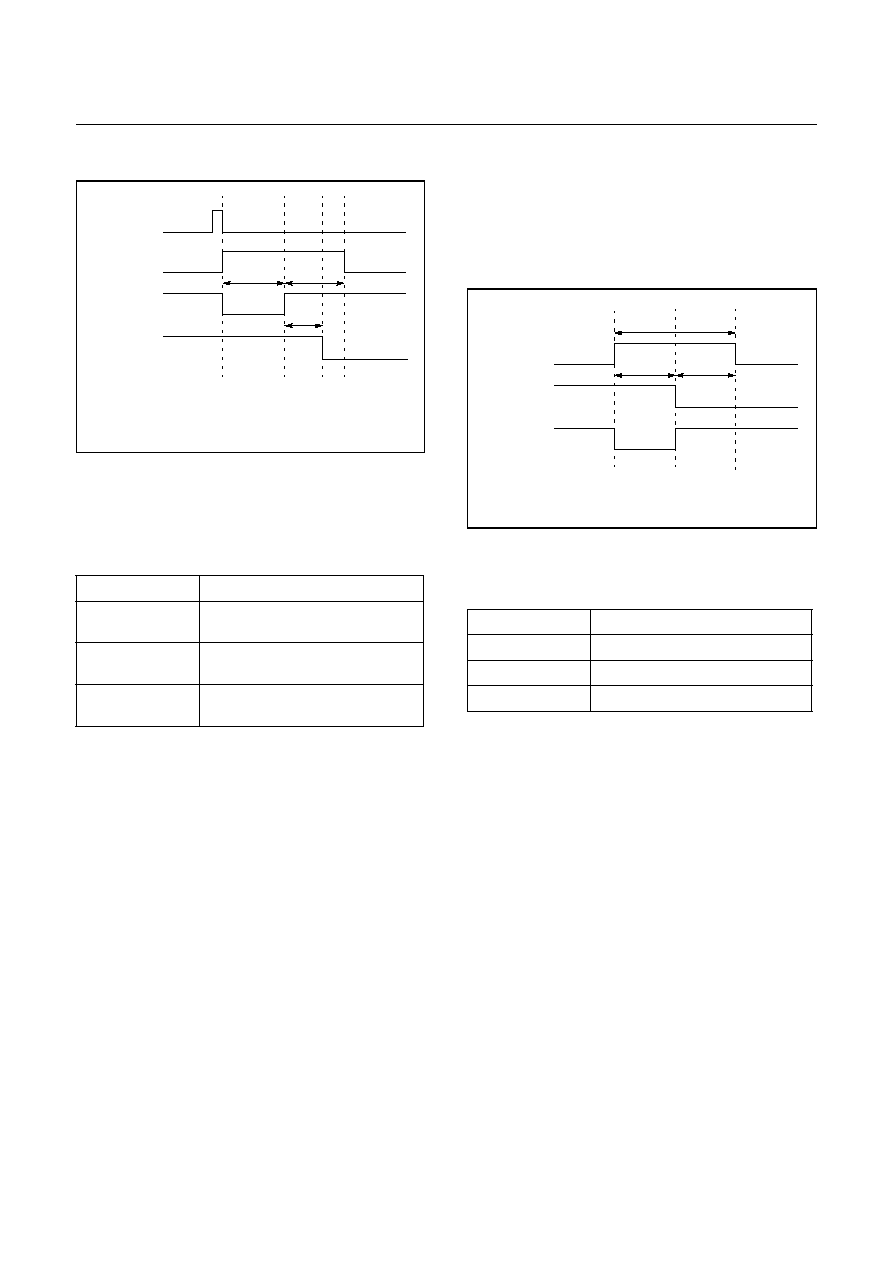

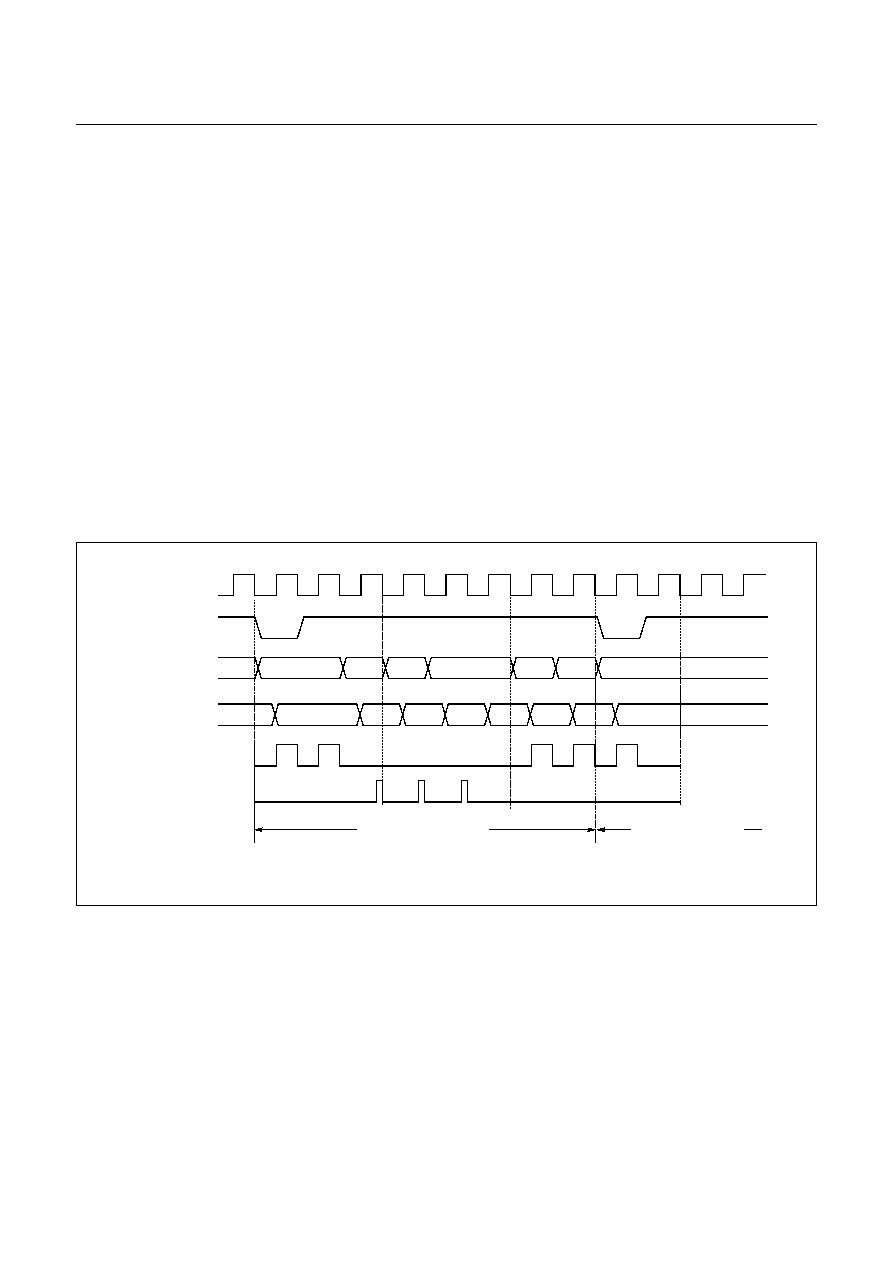

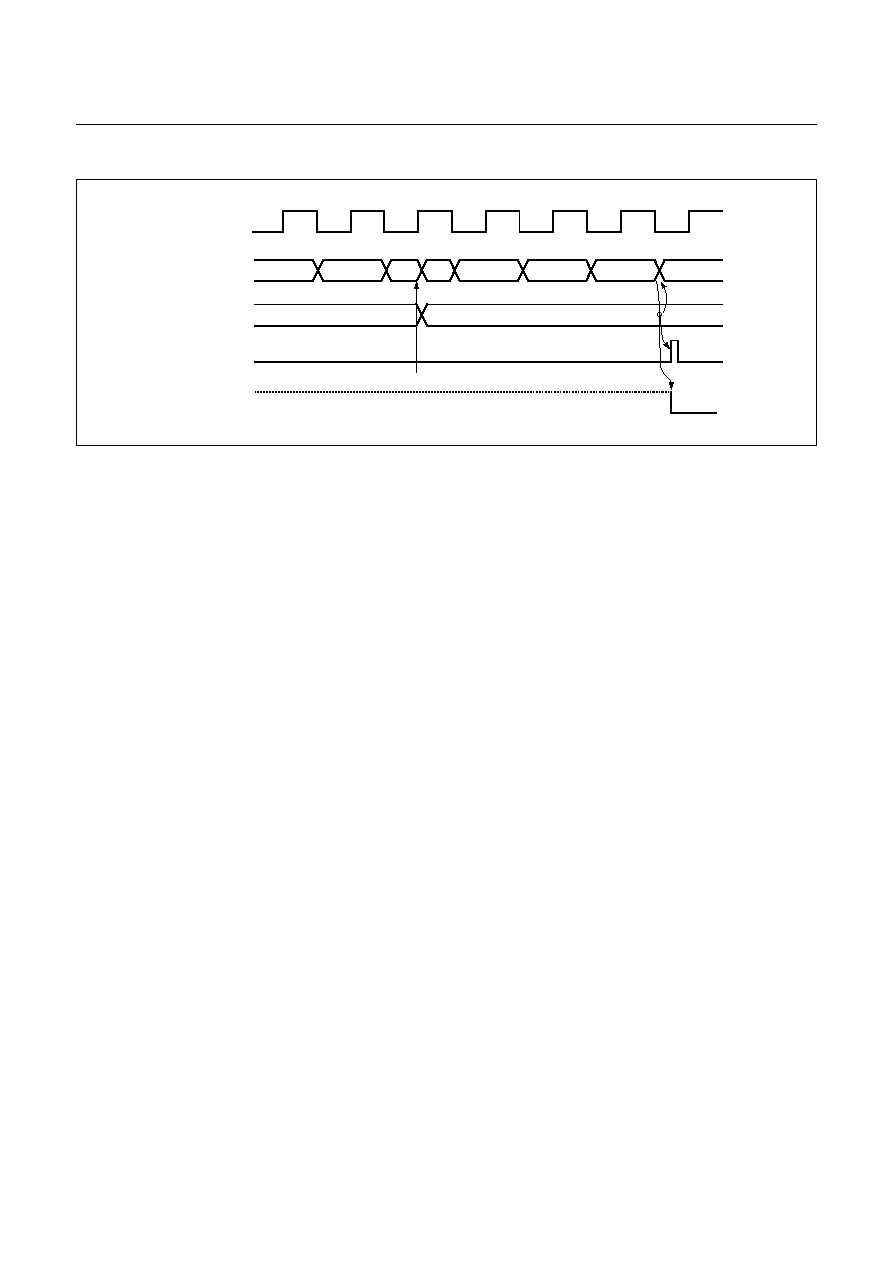

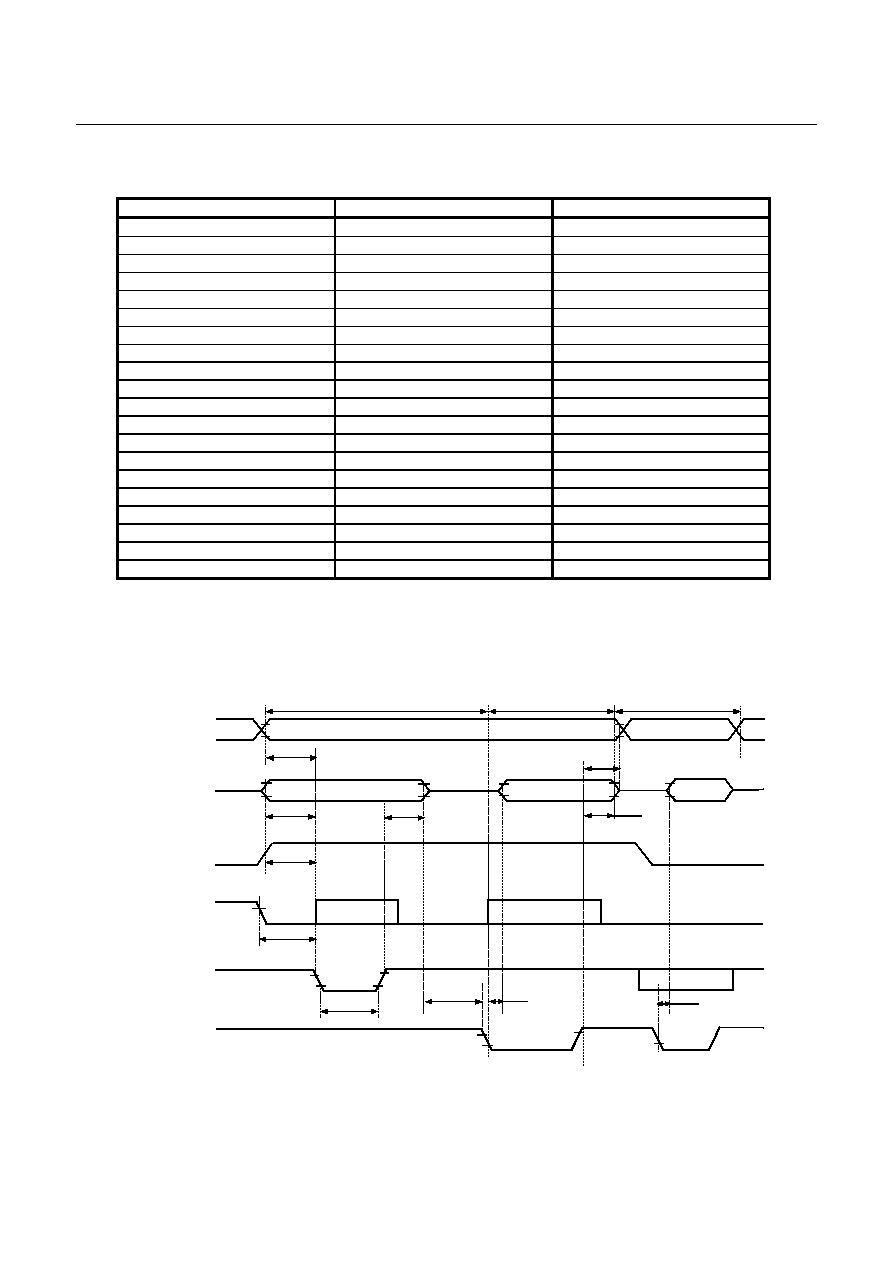

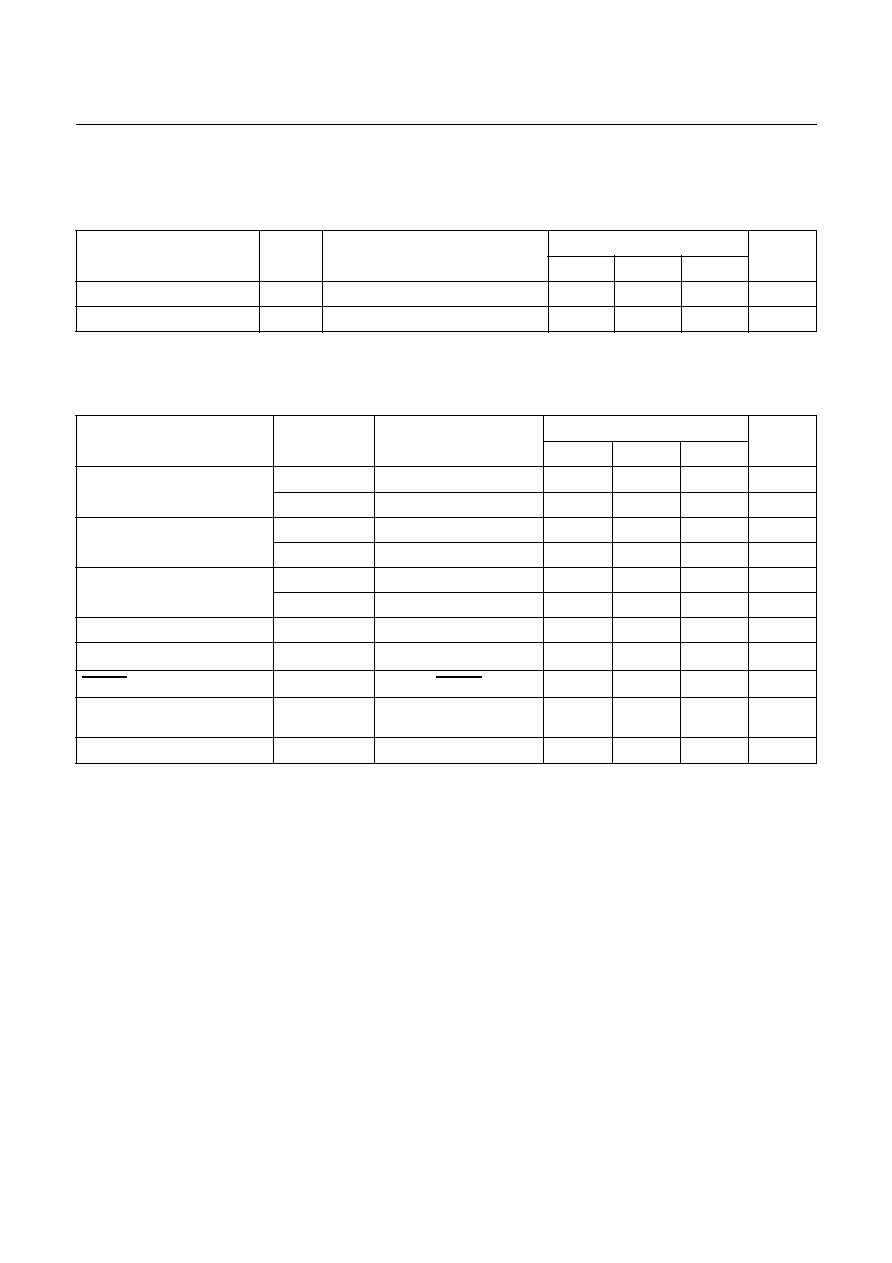

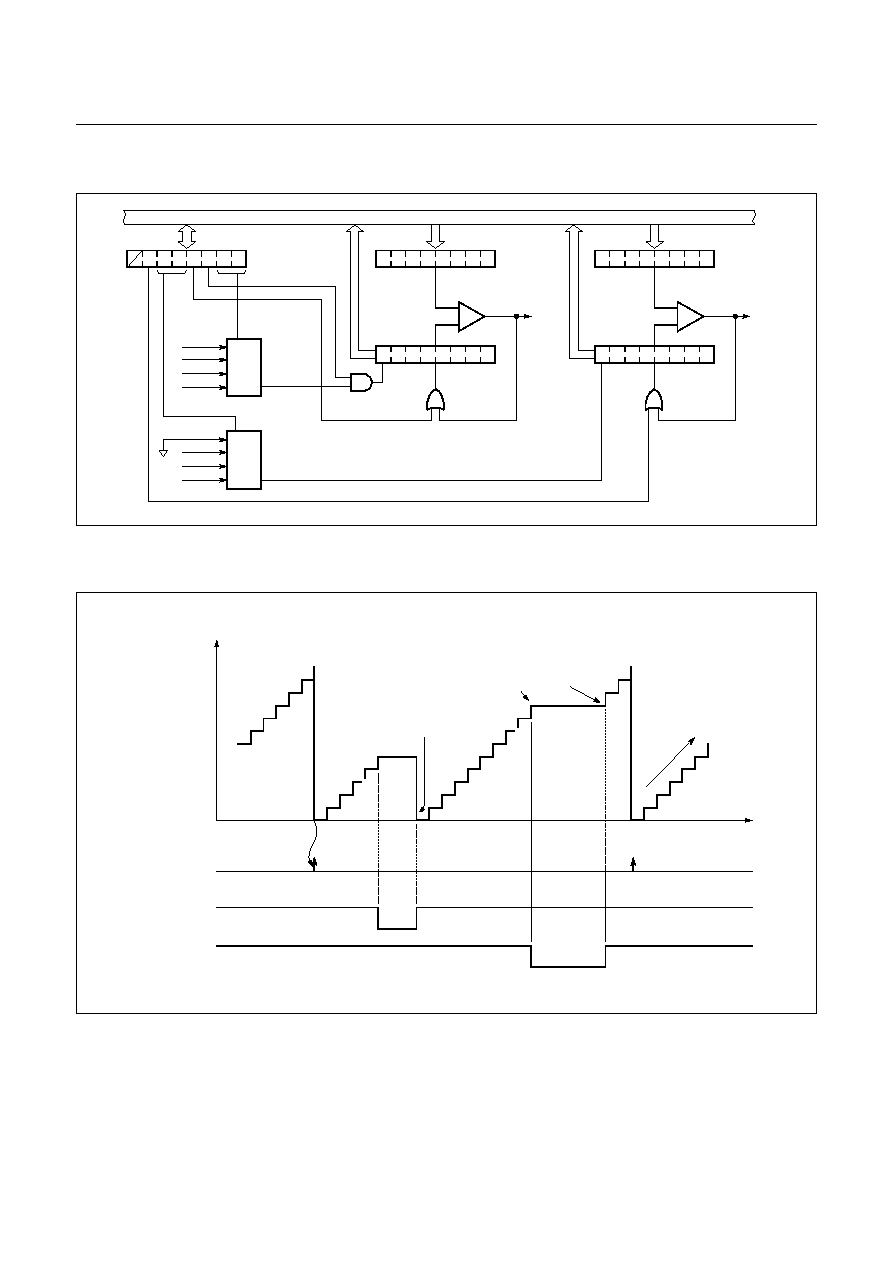

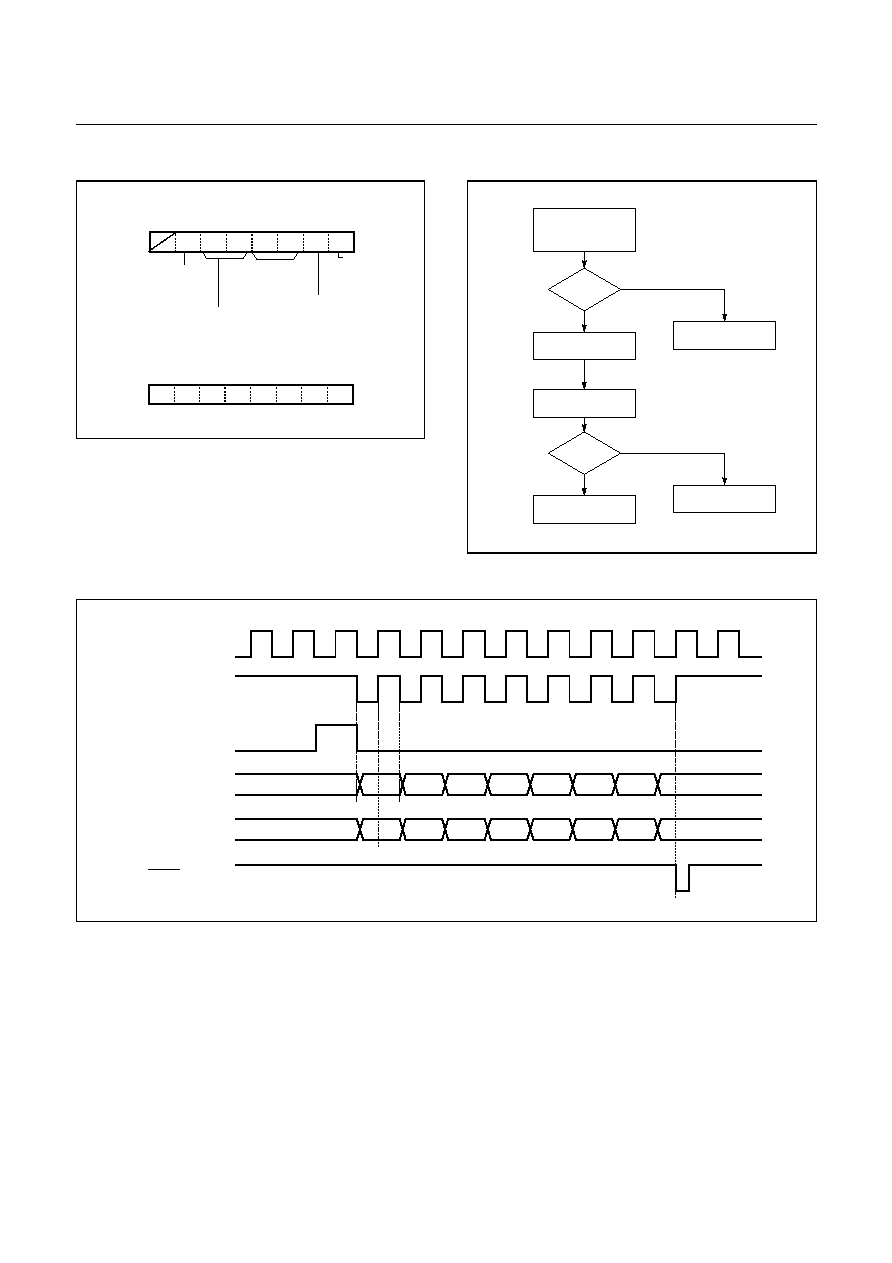

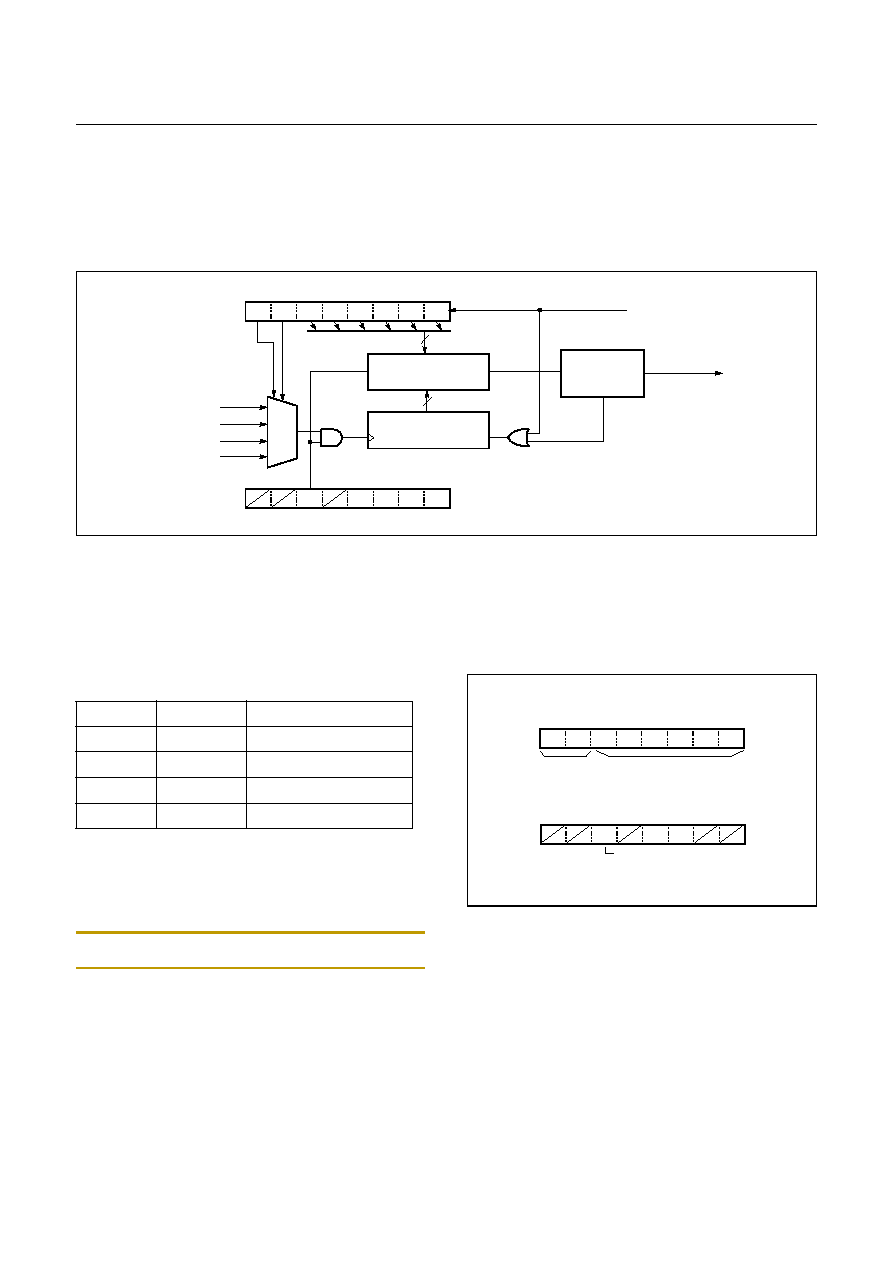

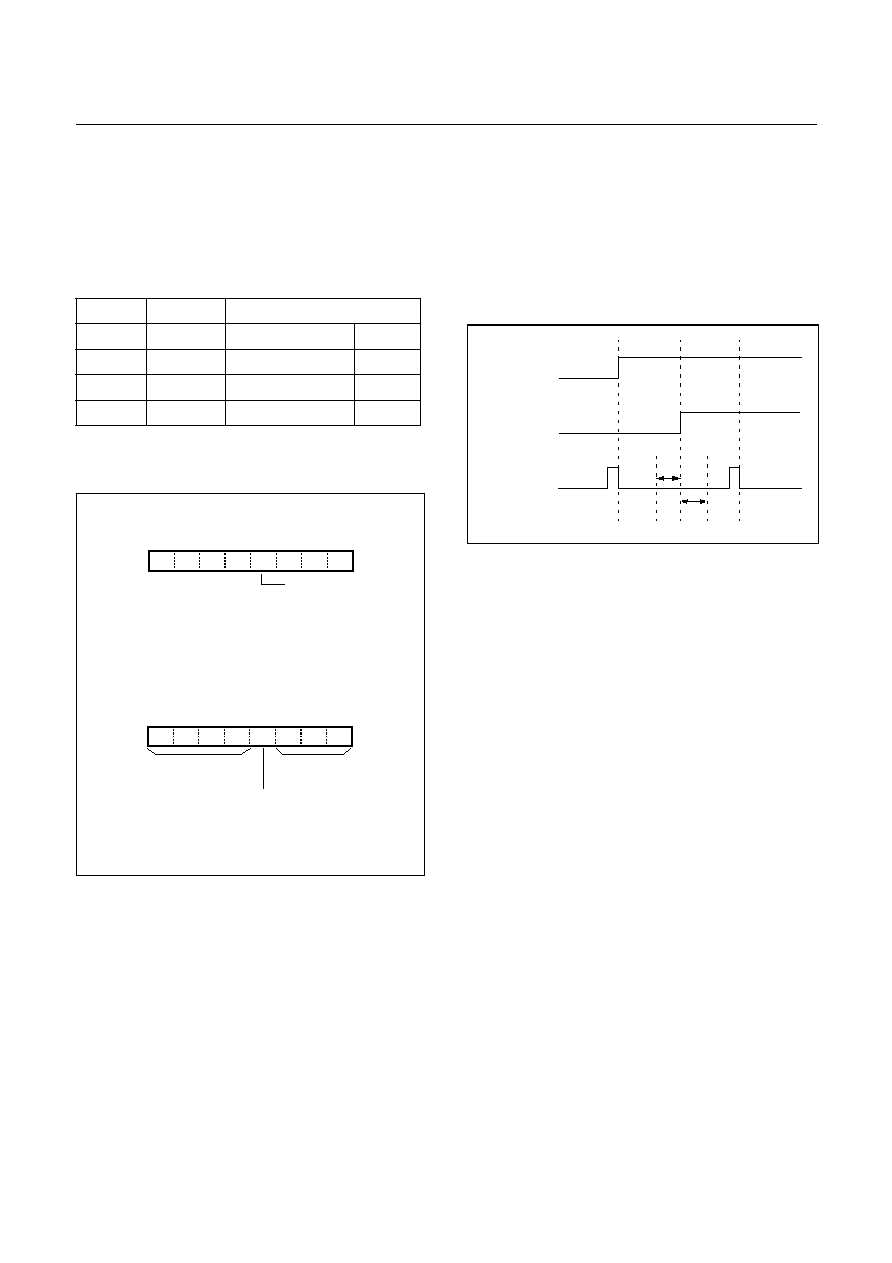

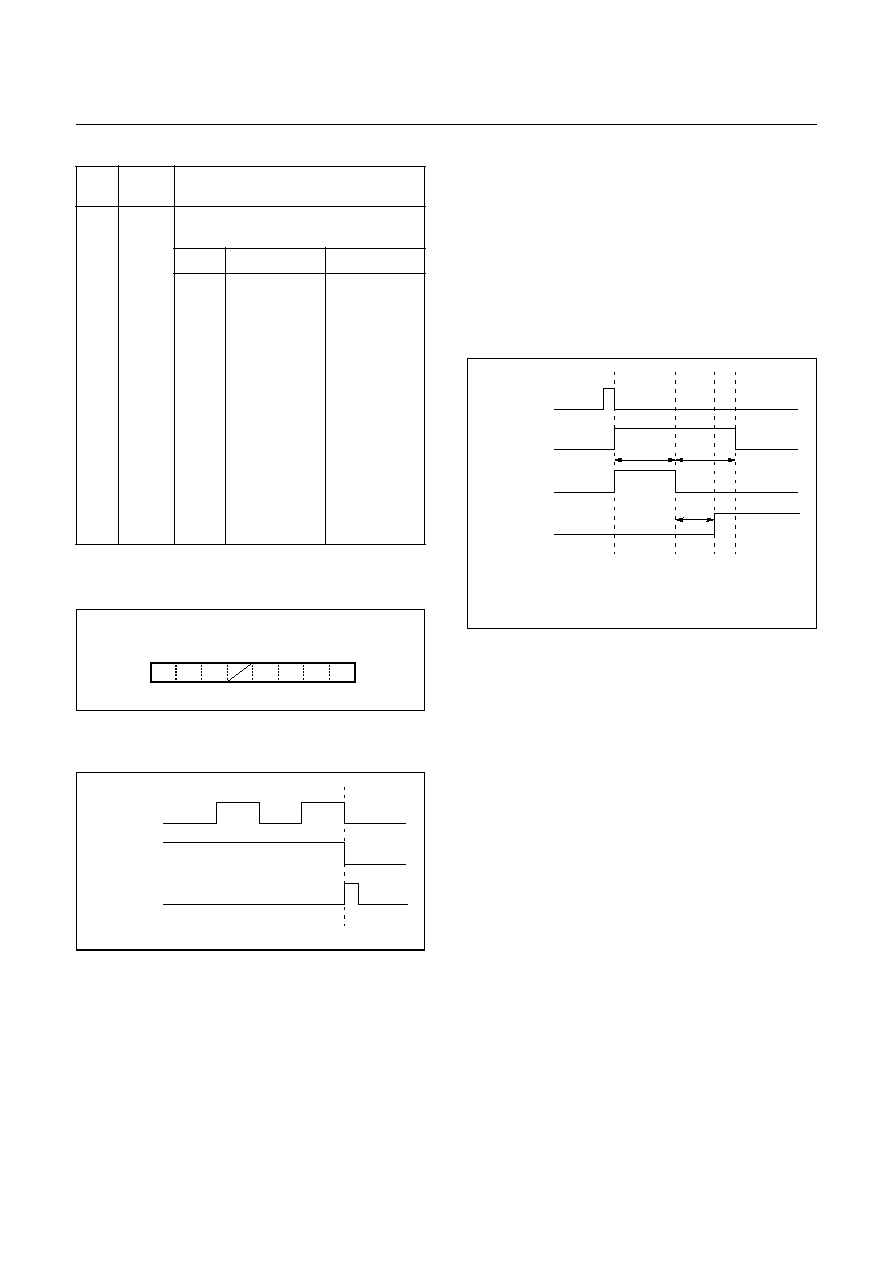

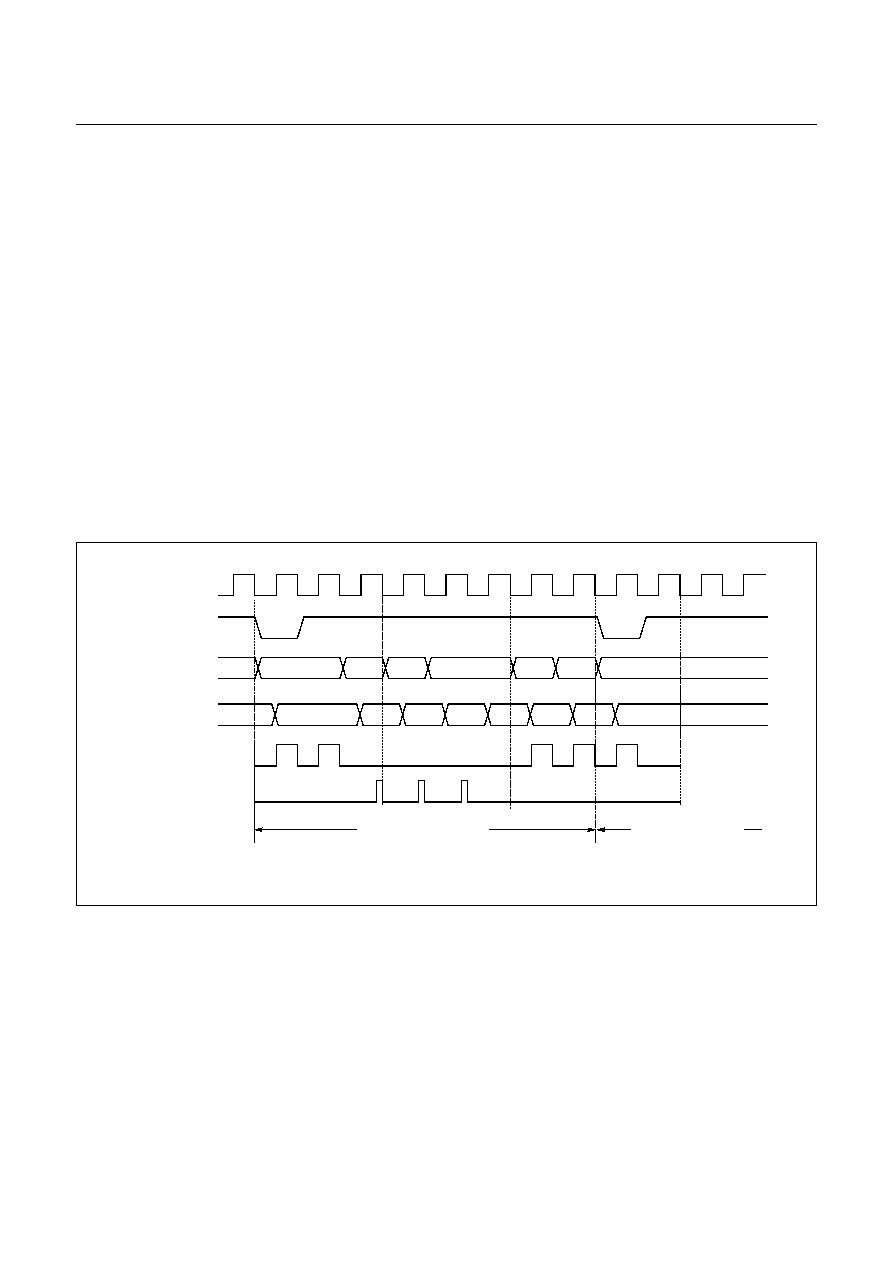

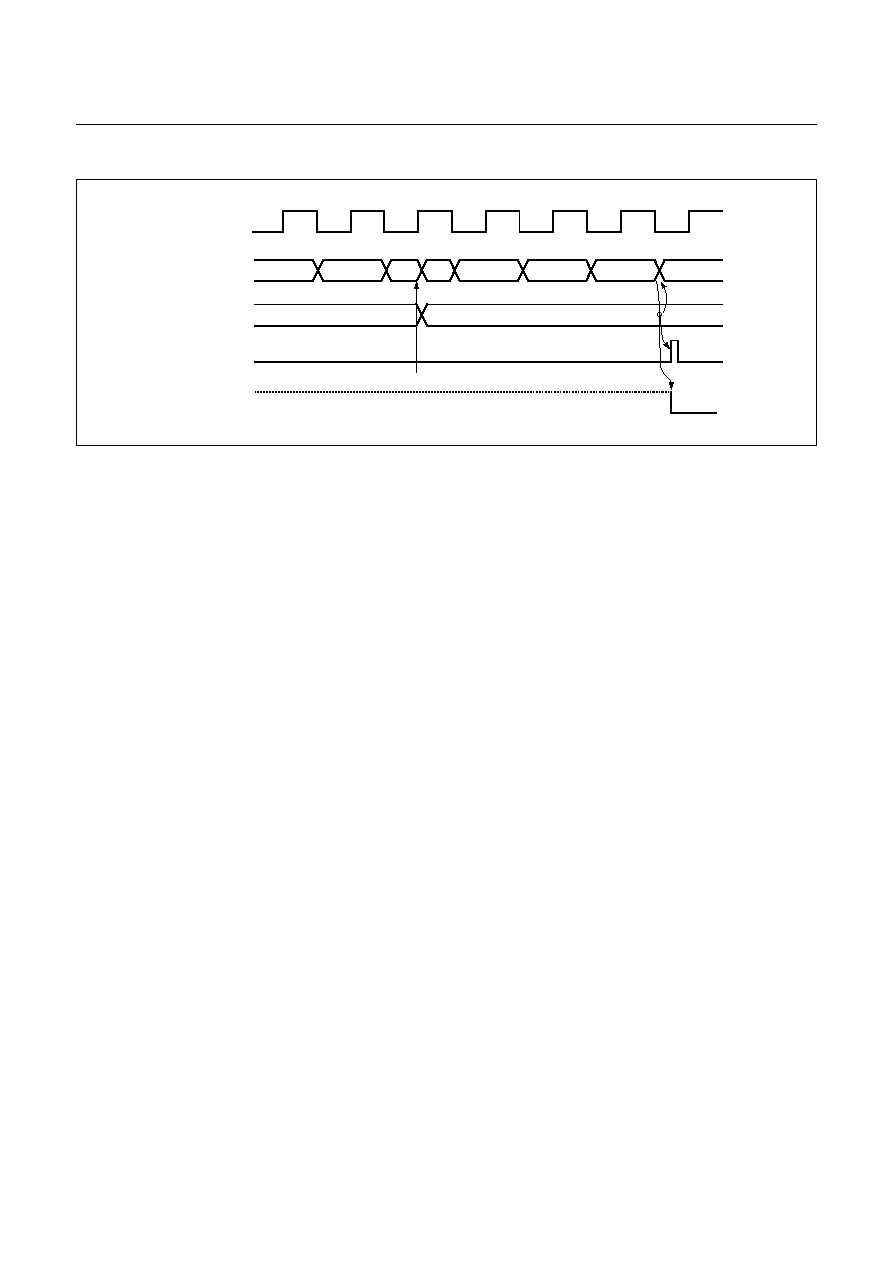

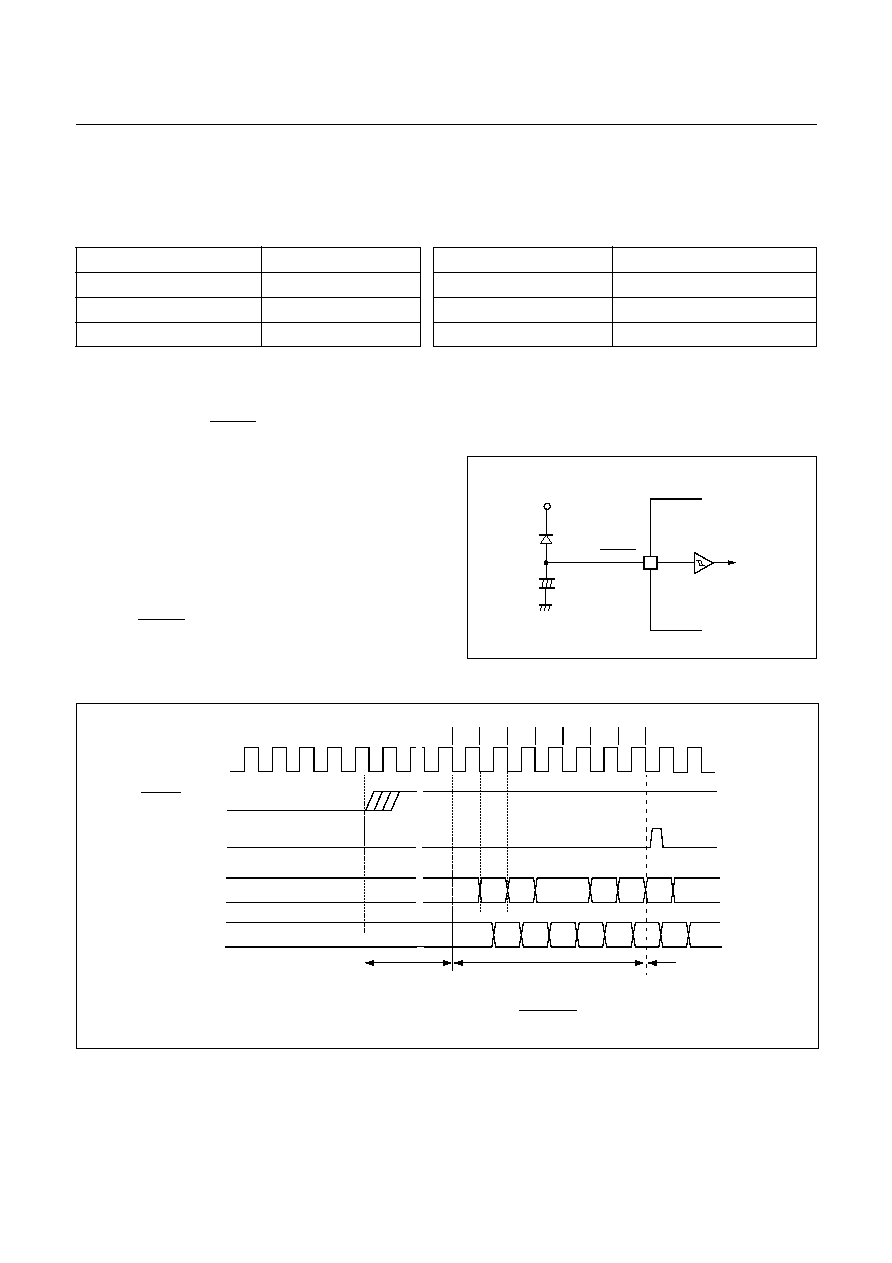

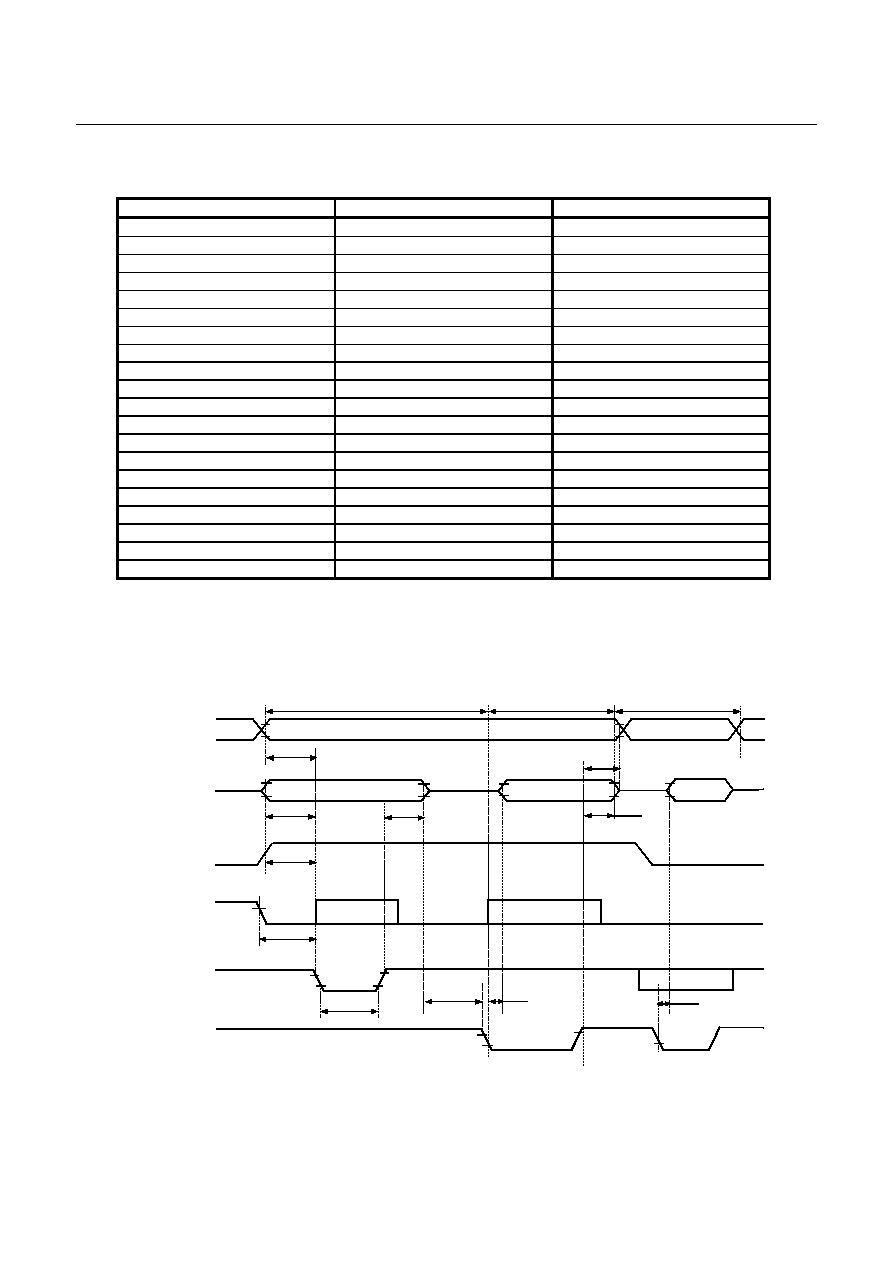

Figure 7-1 Timing Chart

t

MRCP

t

MFCP

X

IN

INT0 ~ 4

0.5V

V

DD

-0.5V

0.2V

DD

0.8V

DD

0.2V

DD

RESET

t

REC

t

FEC

0.2V

DD

0.8V

DD

EC2, EC3

t

IW

t

IW

t

RST

t

ECW

t

ECW

1/f

XIN

t

MCPW

t

MCPW

t

SRCP

t

SFCP

S

CLK

0.5V

V

DD

-0.5V

1/f

SCLK

t

SCPW

t

SCPW

GMS81C4040/87C4060

HYUNDAI

16

May. 2000 Ver 1.0

7.6 Typical Characteristics

This data will generate after evaluation.

Not available at this time.

HYUNDAI

GMS81C4040/87C4060

May. 2000 Ver 1.0

17

8. MEMORY ORGANIZATION

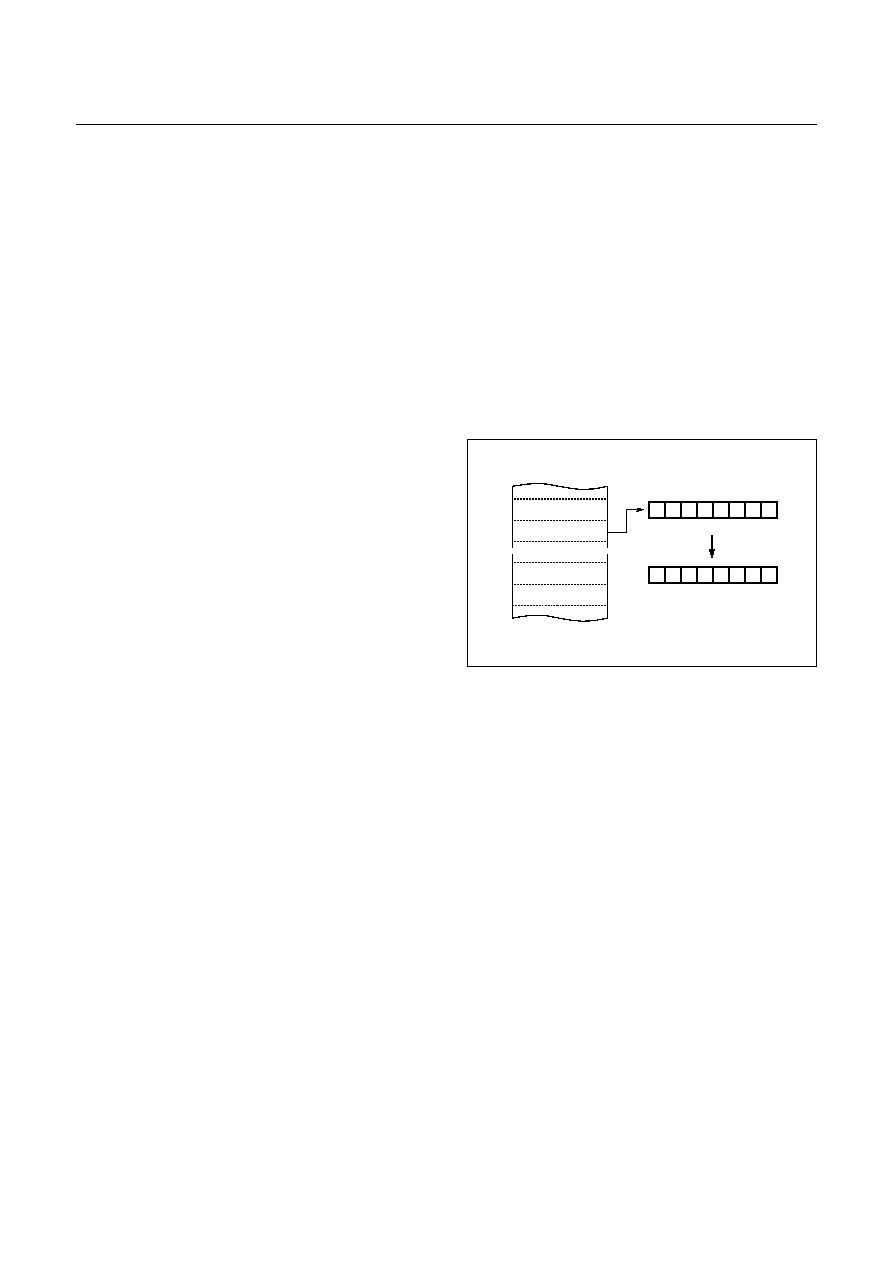

The GMS81C4040/GMS87C4060 has separate address

spaces for Program memory, Data Memory and Display

memory. Program memory can only be read, not written

to. It can be up to 40K/60K bytes of Program memory.

Data memory can be read and written to up to 1,536 bytes

including the stack area. Font memory has prepared 16K

bytes for OSD.

8.1 Registers

This device has six registers that are the Program Counter

(PC), a Accumulator (A), two index registers (X, Y), the

Stack Pointer (SP), and the Program Status Word (PSW).

The Program Counter consists of 16-bit register.

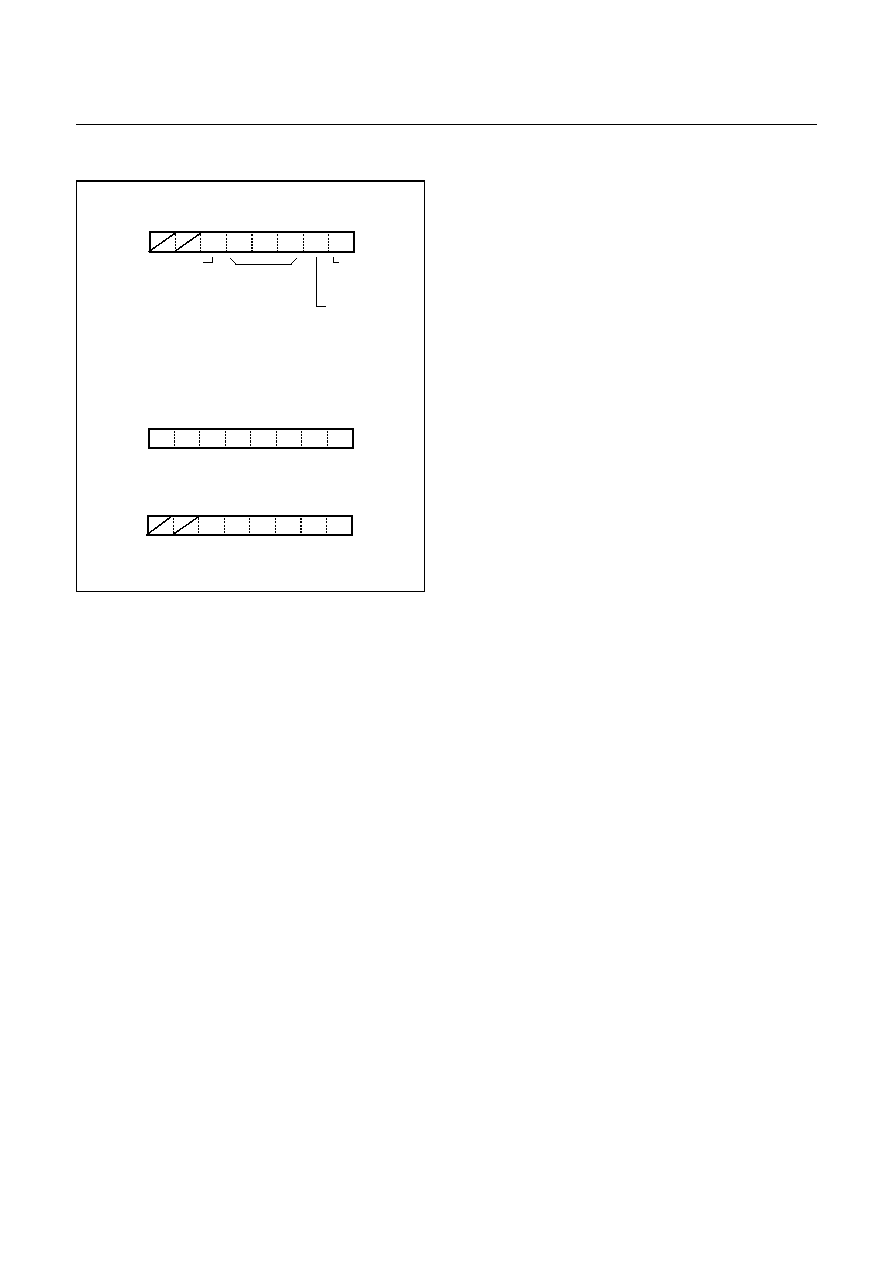

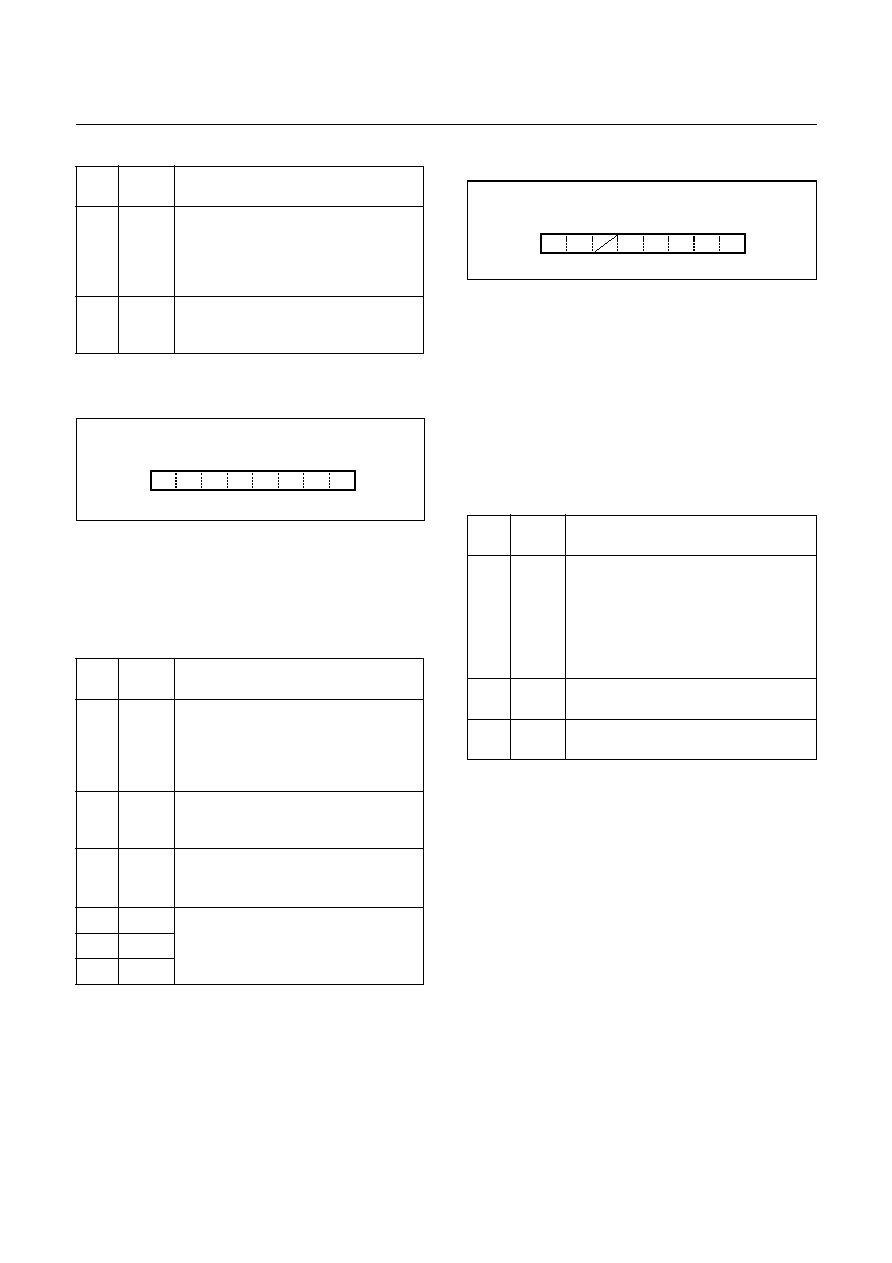

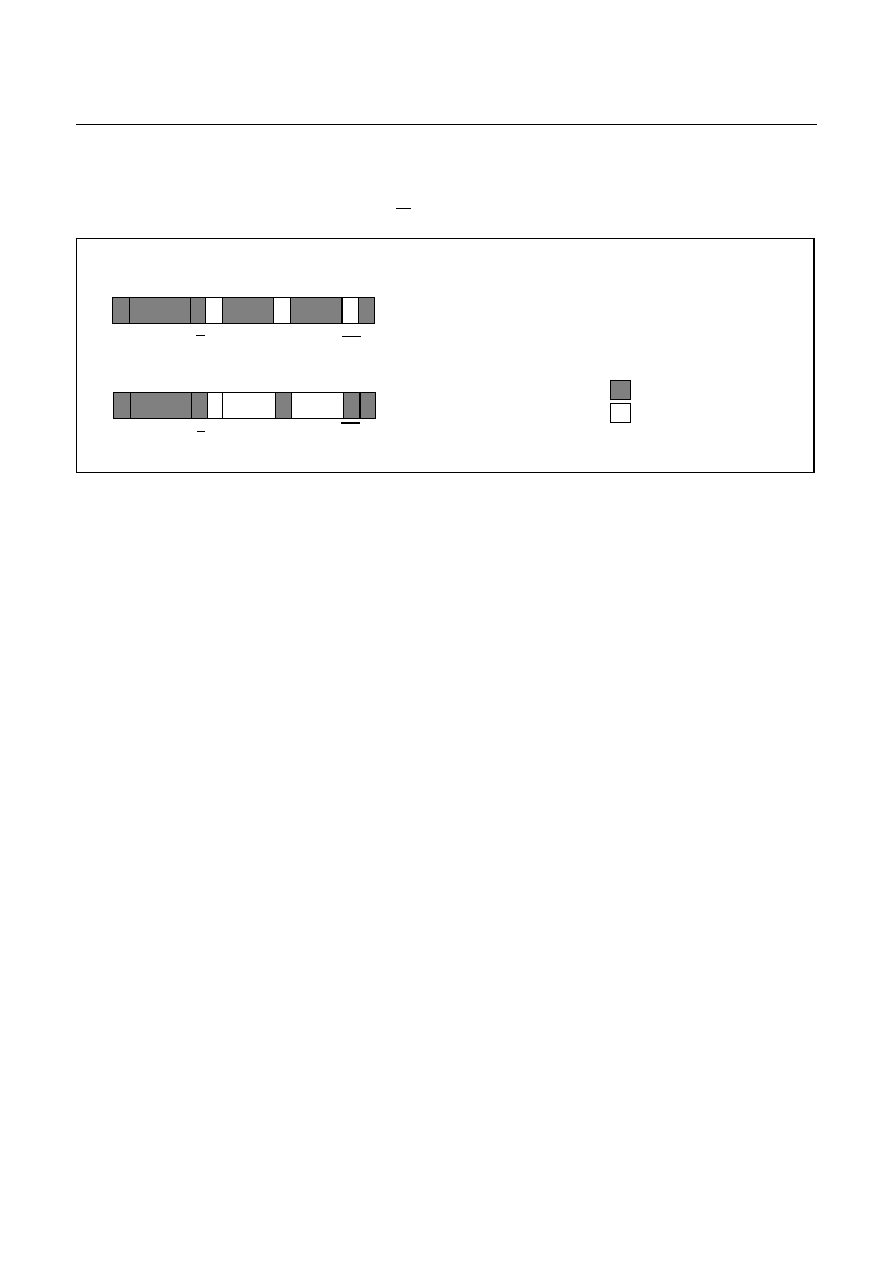

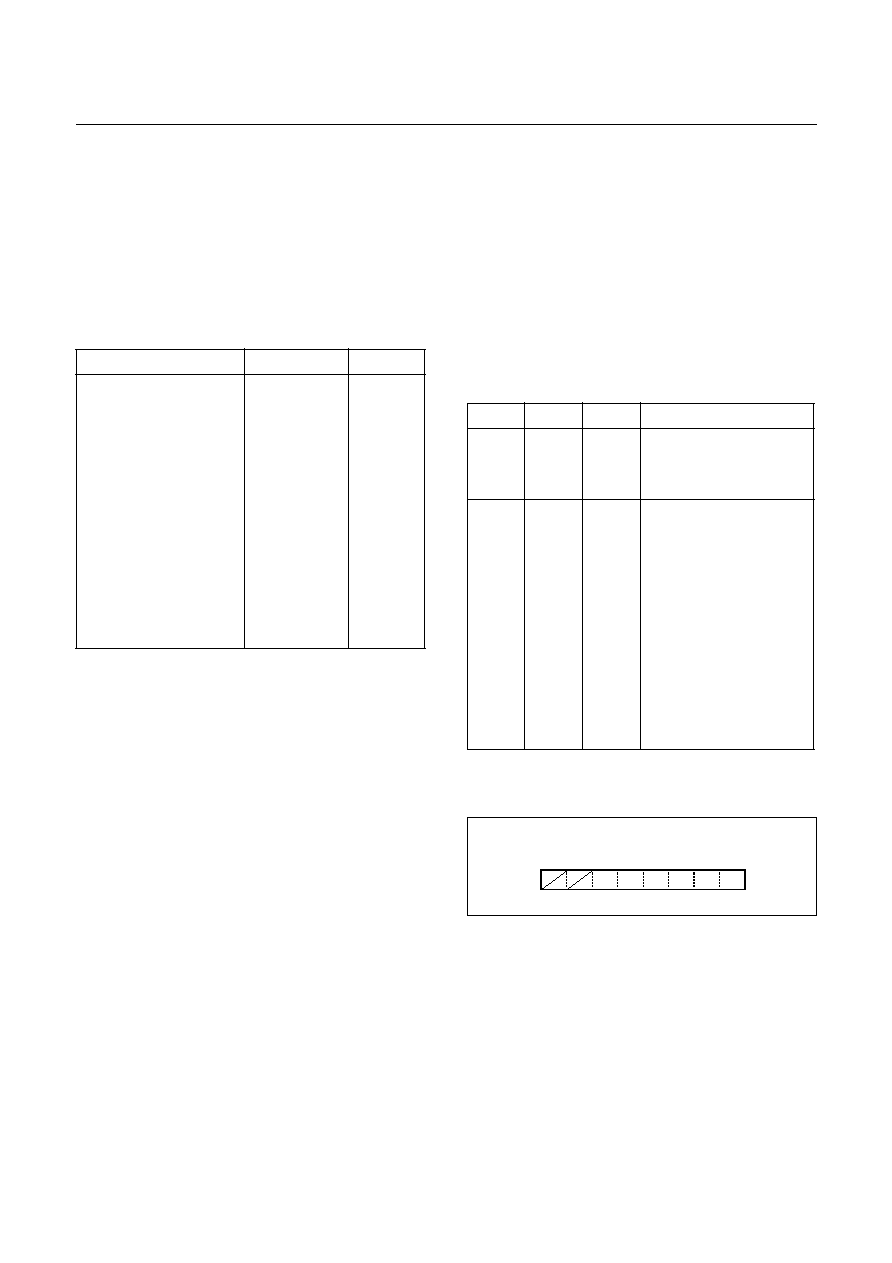

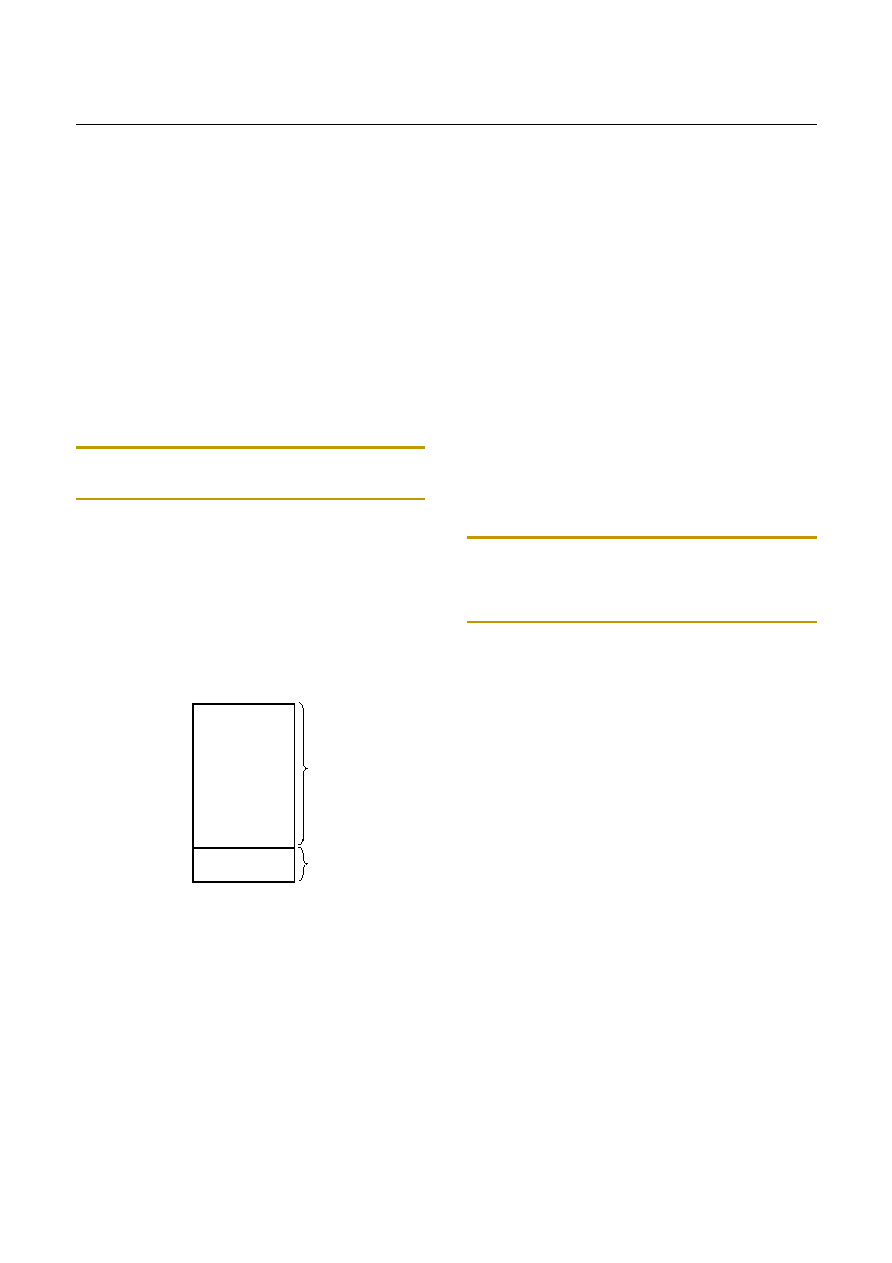

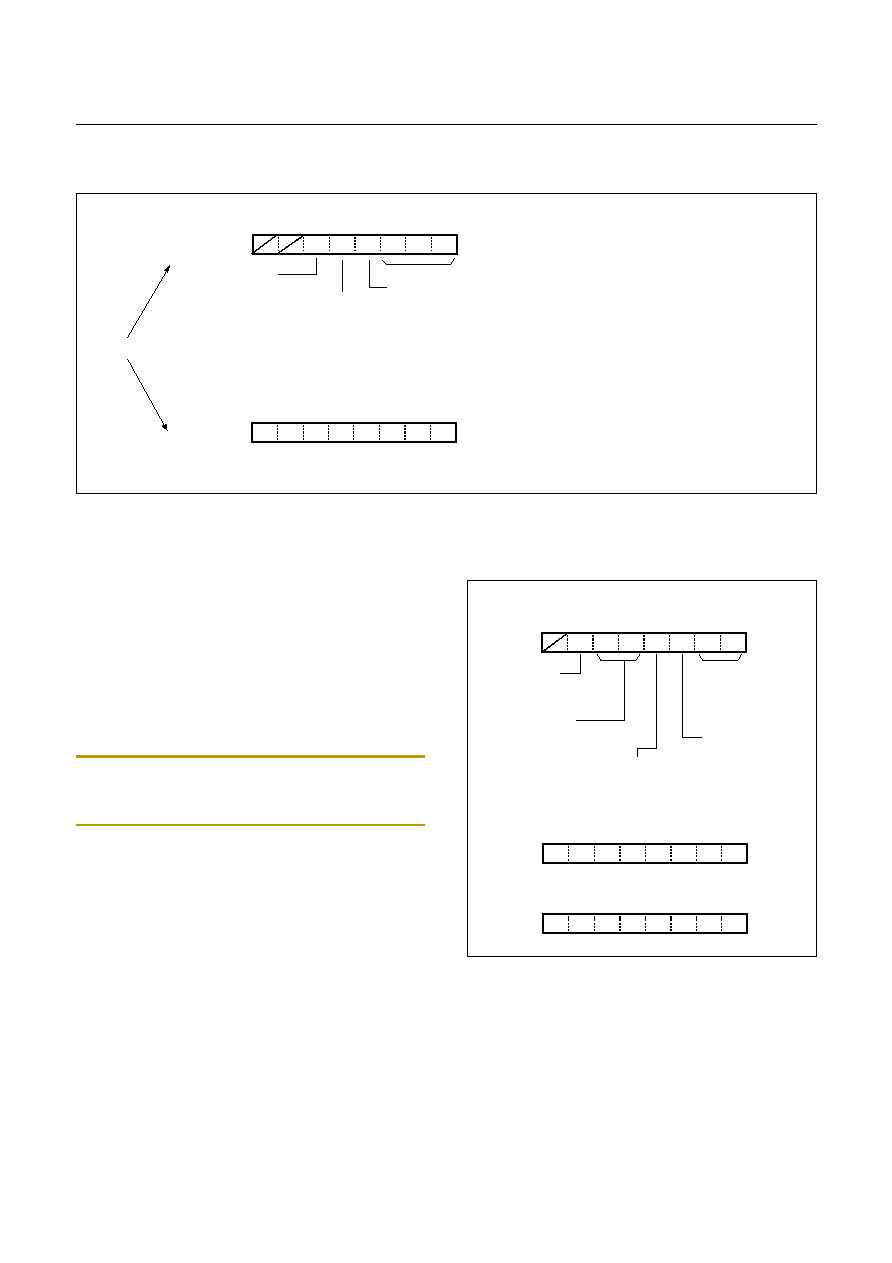

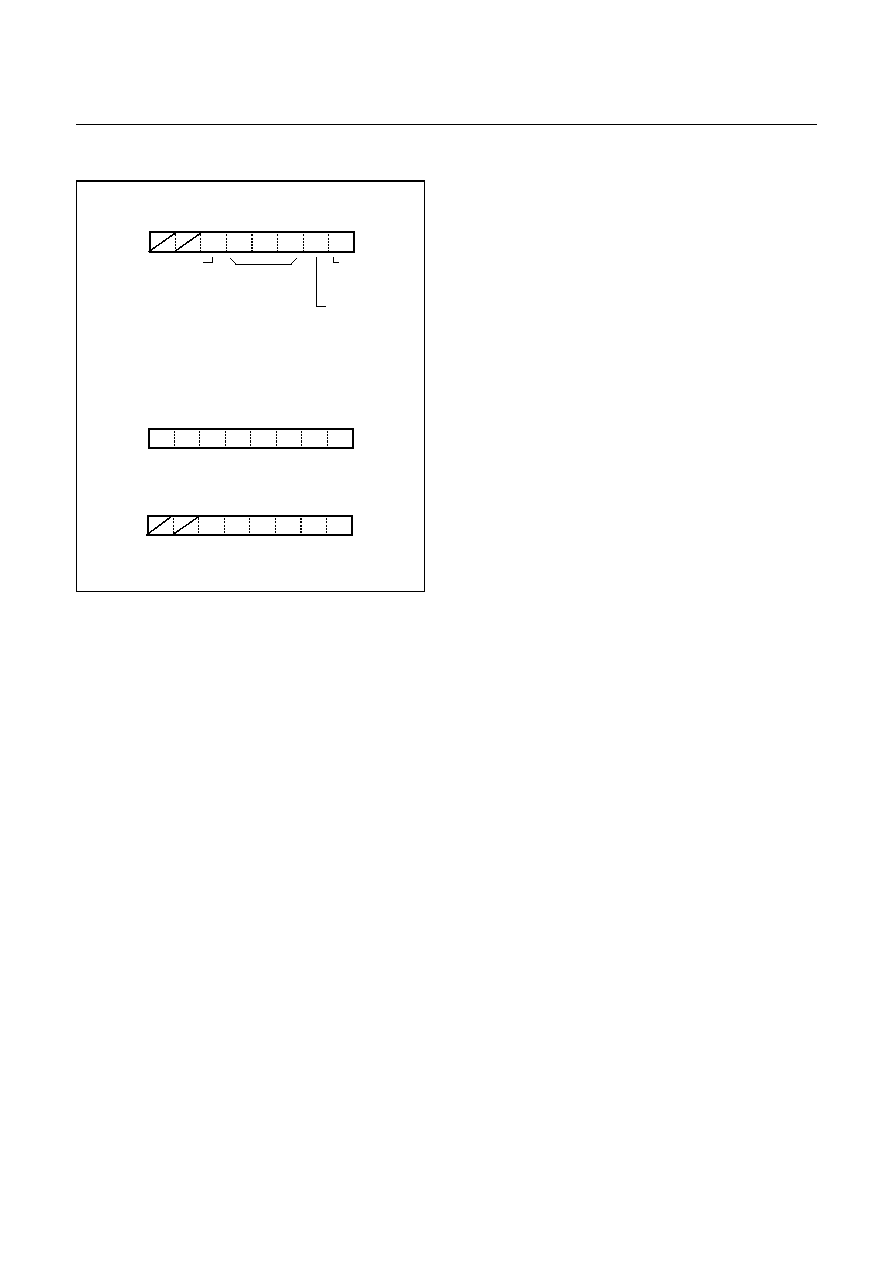

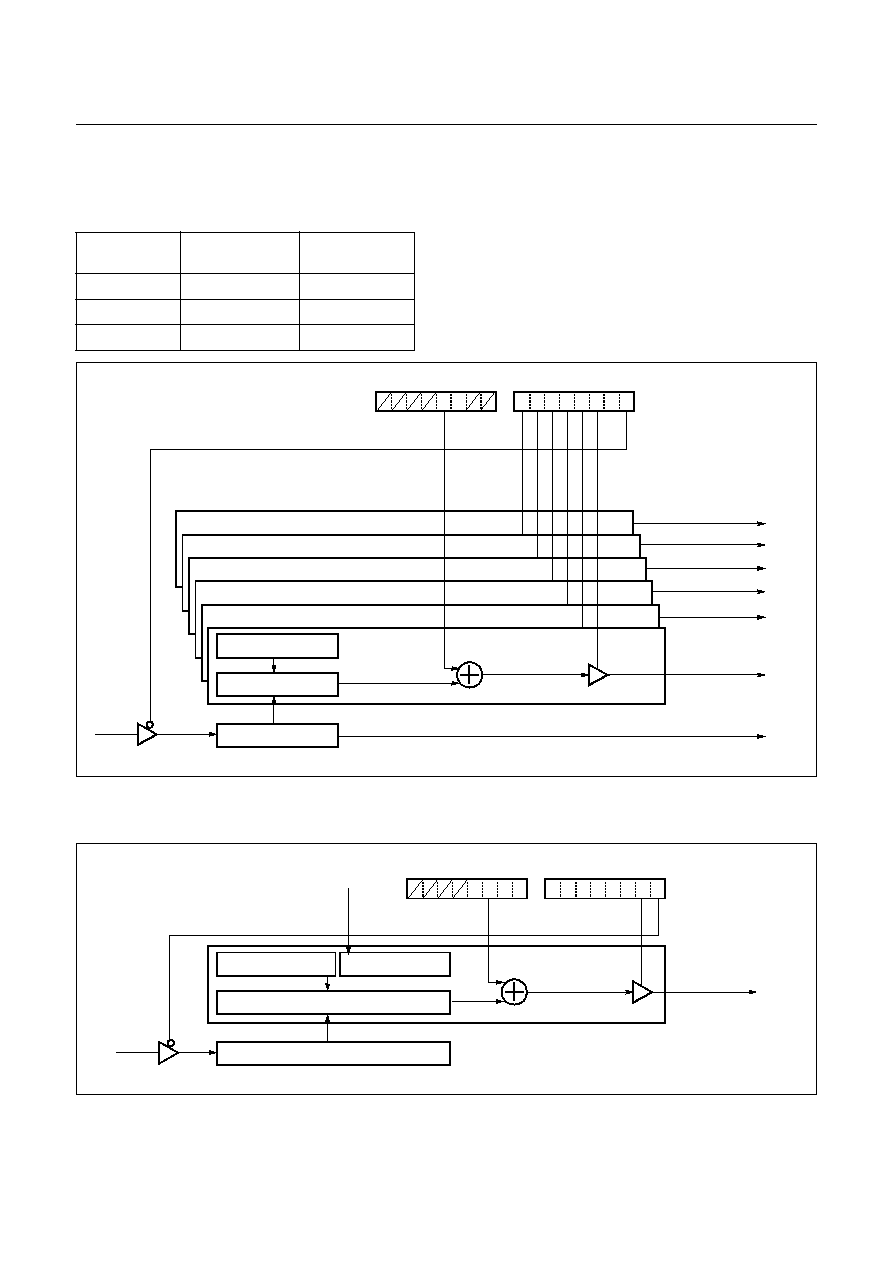

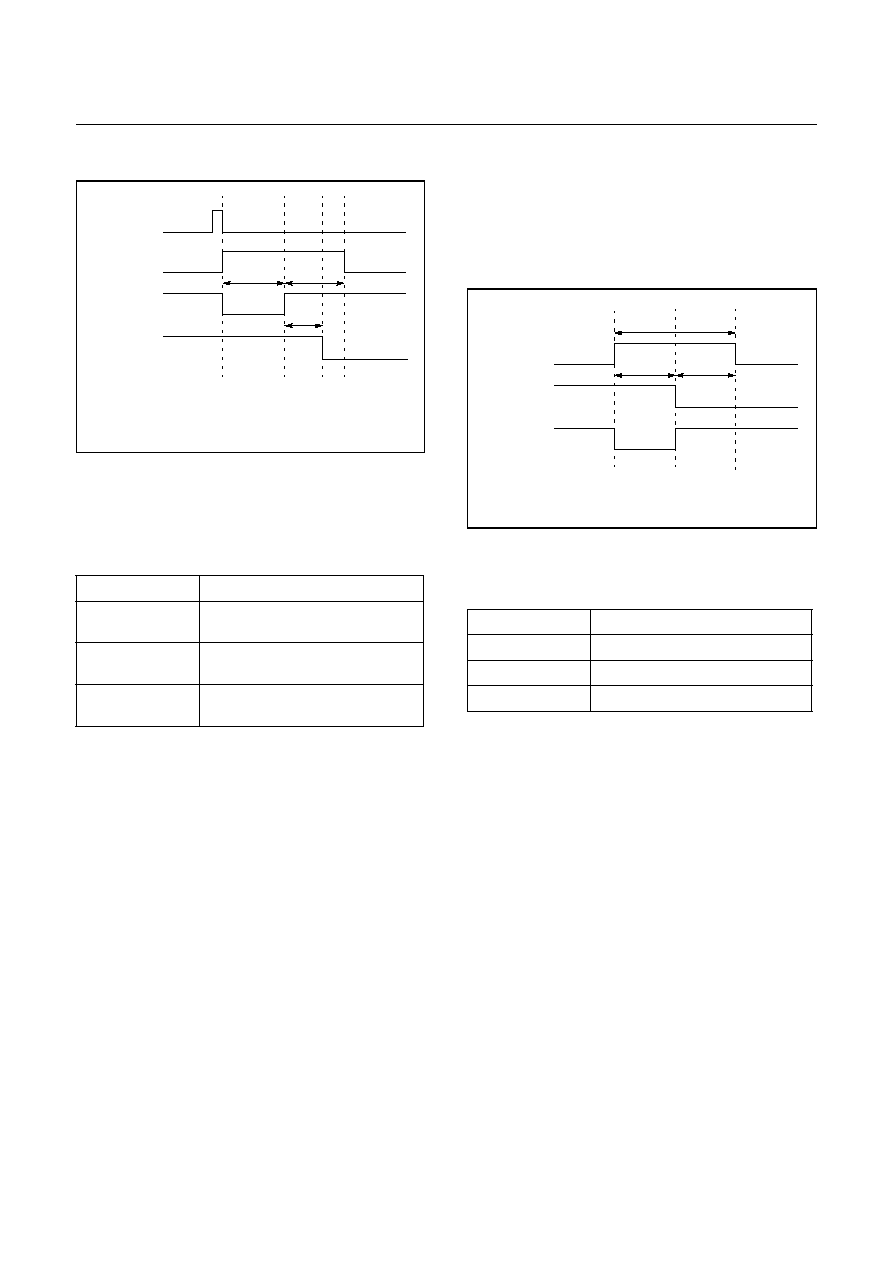

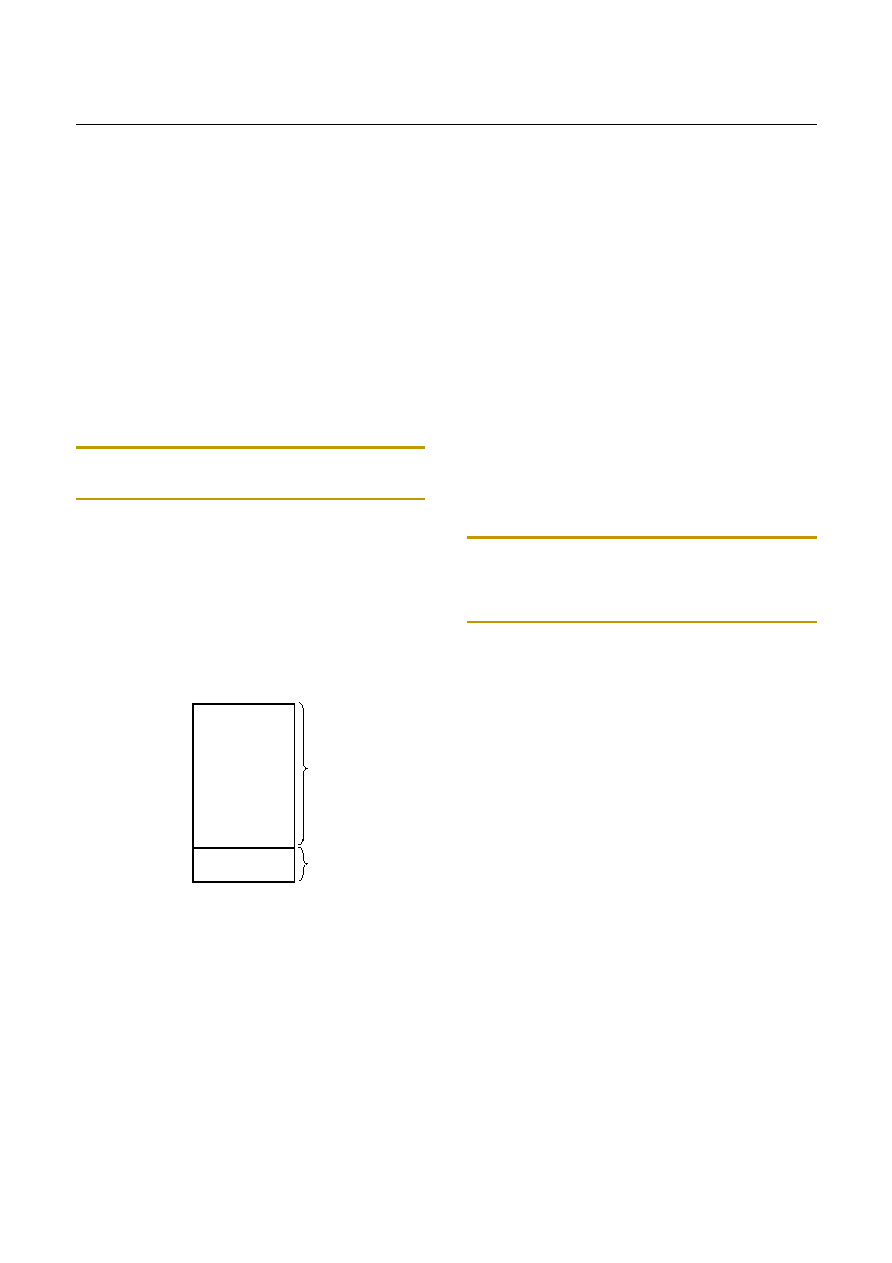

Figure 8-1 Configuration of Registers

Accumulator: The Accumulator is the 8-bit general pur-

pose register, used for data operation such as transfer, tem-

porary saving, and conditional judgement, etc.

The Accumulator can be used as a 16-bit register with Y

Register as shown below.

Figure 8-2 Configuration of YA 16-bit Register

X, Y Registers: In the addressing mode which uses these

index registers, the register contents are added to the spec-

ified address, which becomes the actual address. These

modes are extremely effective for referencing subroutine

tables and memory tables. The index registers also have in-

crement, decrement, comparison and data transfer func-

tions, and they can be used as simple accumulators.

Stack Pointer: The Stack Pointer is an 8-bit register used

for occurrence interrupts and calling out subroutines. Stack

Pointer identifies the location in the stack to be accessed

(save or restore).

Generally, SP is automatically updated when a subroutine

call is executed or an interrupt is accepted. However, if it

is used in excess of the stack area permitted by the data

memory allocating configuration, the user-processed data

may be lost.

The stack can be located at any position within 0100

H

to

01FF

H

of the internal data memory. The SP is not initial-

ized by hardware, requiring to write the initial value (the

location with which the use of the stack starts) by using the

initialization routine. Normally, the initial value of "FF

H

"

is used.

Program Counter: The Program Counter is a 16-bit wide

which consists of two 8-bit registers, PCH and PCL. This

counter indicates the address of the next instruction to be

executed. In reset state, the program counter has reset rou-

tine address (PC

H

:0FF

H

, PC

L

:0FE

H

).

Program Status Word: The Program Status Word (PSW)

contains several bits that reflect the current state of the

CPU. The PSW is described in Figure 8-3 . It contains the

Negative flag, the Overflow flag, the Break flag the Half

Carry (for BCD operation), the Interrupt enable flag, the

Zero flag, and the Carry flag.

[Carry flag C]

This flag stores any carry or borrow from the ALU of CPU

A

ACCUMULATOR

X REGISTER

Y REGISTER

STACK POINTER

PROGRAM COUNTER

PROGRAM STATUS

WORD

X

Y

SP

PCL

PCH

PSW

Two 8-bit Registers can be used as a "YA" 16-bit Register

Y

A

Y

A

Caution:

The Stack Pointer must be initialized by software be-

cause its value is undefined after RESET.

Example: To initialize the SP

LDX

#0FFH

TXSP

; SP

FF

H

SP

01

Stack Address ( 0100

H

~ 01FF

H

)

15

0

8

7

Hardware fixed

GMS81C4040/87C4060

HYUNDAI

18

May. 2000 Ver 1.0

after an arithmetic operation and is also changed by the

Shift Instruction or Rotate Instruction.

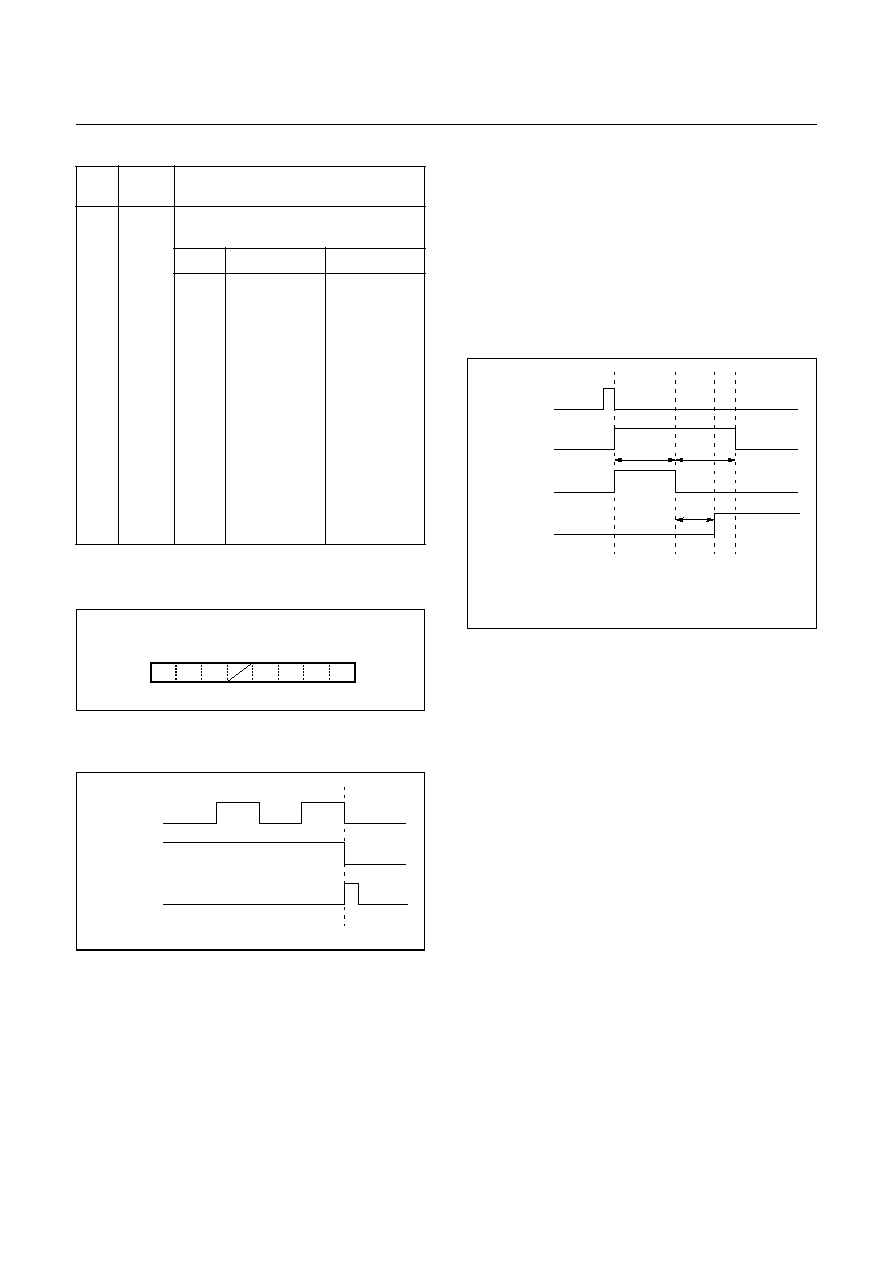

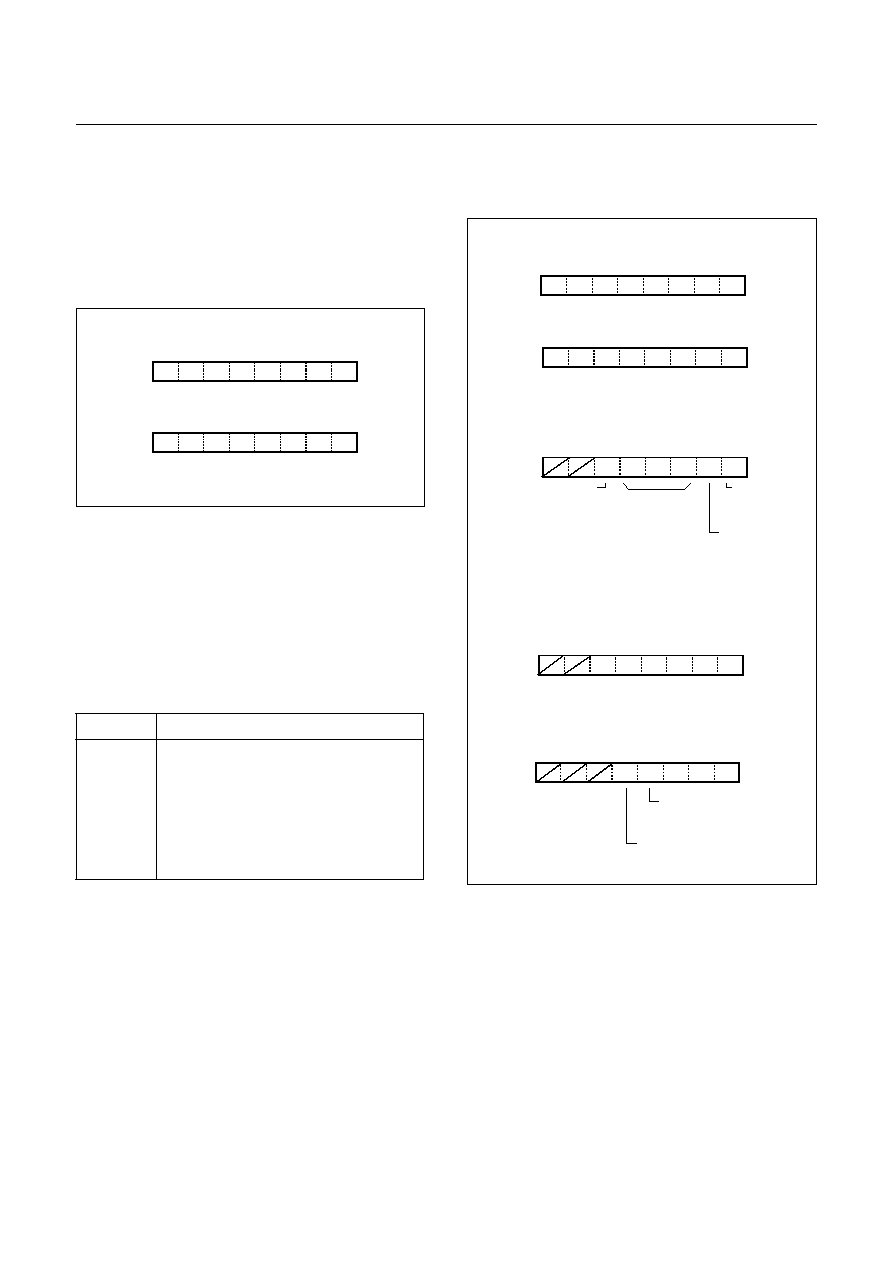

Figure 8-3 PSW (Program Status Word) Register

[Zero flag Z]

This flag is set when the result of an arithmetic operation

or data transfer is "0" and is cleared by any other result.

[Interrupt disable flag I]

This flag enables/disables all interrupts except interrupt

caused by Reset or software BRK instruction. All inter-

rupts are disabled when cleared to "0". This flag immedi-

ately becomes "0" when an interrupt is served. It is set by

the EI instruction and cleared by the DI instruction.

[Half carry flag H]

After operation, this is set when there is a carry from bit 3

of ALU or there is borrow from bit 4 of ALU. This bit can

not be set or cleared except CLRV instruction with Over-

flow flag (V).

[Break flag B]

This flag is set by software BRK instruction to distinguish

BRK from TCALL instruction with the same vector ad-

dress.

[Direct page flag G]

This flag assigns RAM page for direct addressing mode. In

the direct addressing mode, addressing area is from zero

page 00

H

to 0FF

H

when this flag is "0". If it is set to "1",

addressing area is assigned by DPGR register (address

0F8

H

). It is set by SETG instruction and cleared by CLRG.

[Overflow flag V]

This flag is set to "1" when an overflow occurs as the result

of an arithmetic operation involving signs. An overflow

occurs when the result of an addition or subtraction ex-

ceeds +127(7F

H

) or -128(80

H

). The CLRV instruction

clears the overflow flag. There is no set instruction. When

the BIT instruction is executed, bit 6 of memory is copied

to this flag.

[Negative flag N]

This flag is set to match the sign bit (bit 7) status of the re-

sult of a data or arithmetic operation. When the BIT in-

struction is executed, bit 7 of memory is copied to this flag.

N

NEGATIVE FLAG

V

G

B

H

I

Z

C

MSB

LSB

RESET VALUE : 00

H

PSW

OVERFLOW FLAG

BRK FLAG

CARRY FLAG RECEIVES

ZERO FLAG

INTERRUPT ENABLE FLAG

CARRY OUT

HALF CARRY FLAG RECEIVES

CARRY OUT FROM BIT 1 OF

ADDITION OPERLANDS

SELECT DIRECT PAGE

when G=1, page is addressed by RPR

HYUNDAI

GMS81C4040/87C4060

May. 2000 Ver 1.0

19

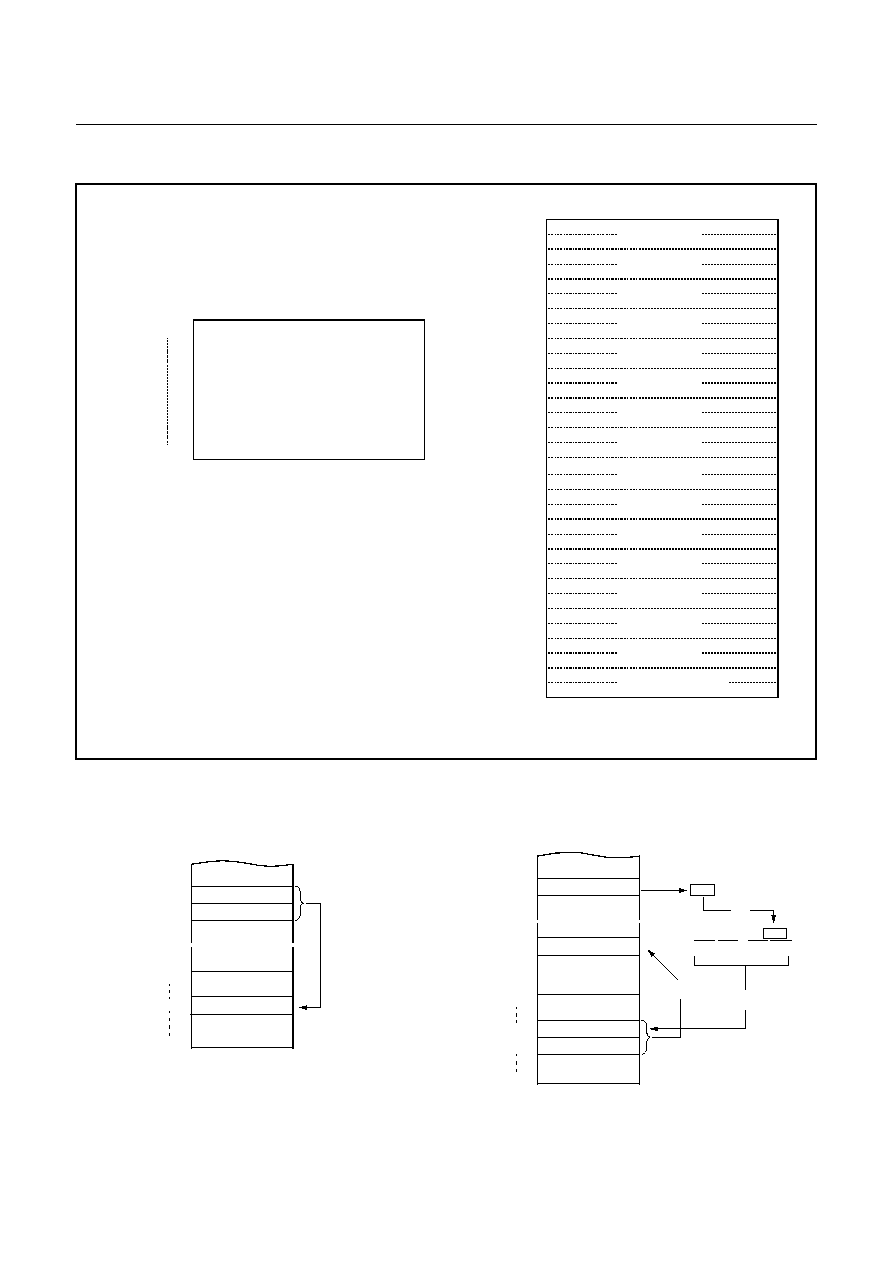

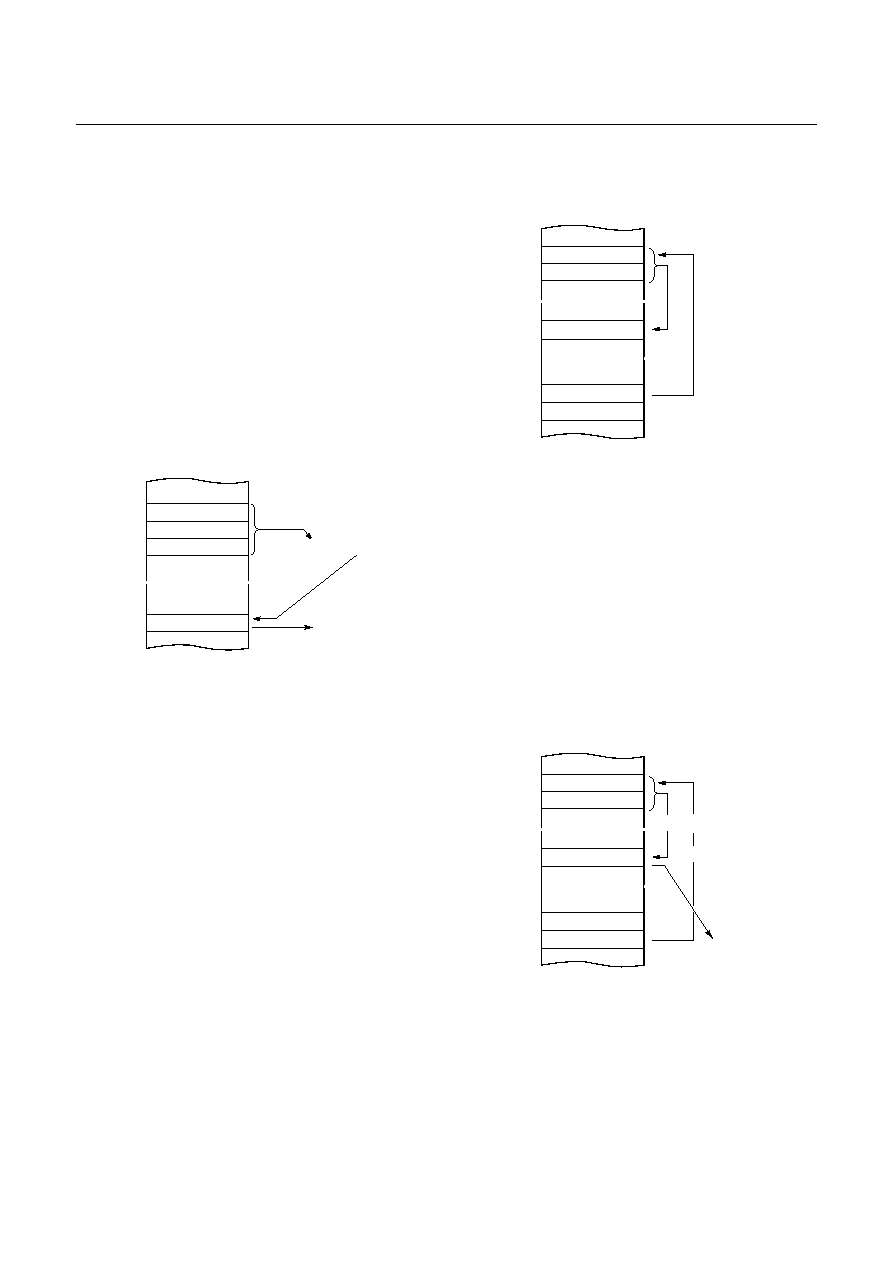

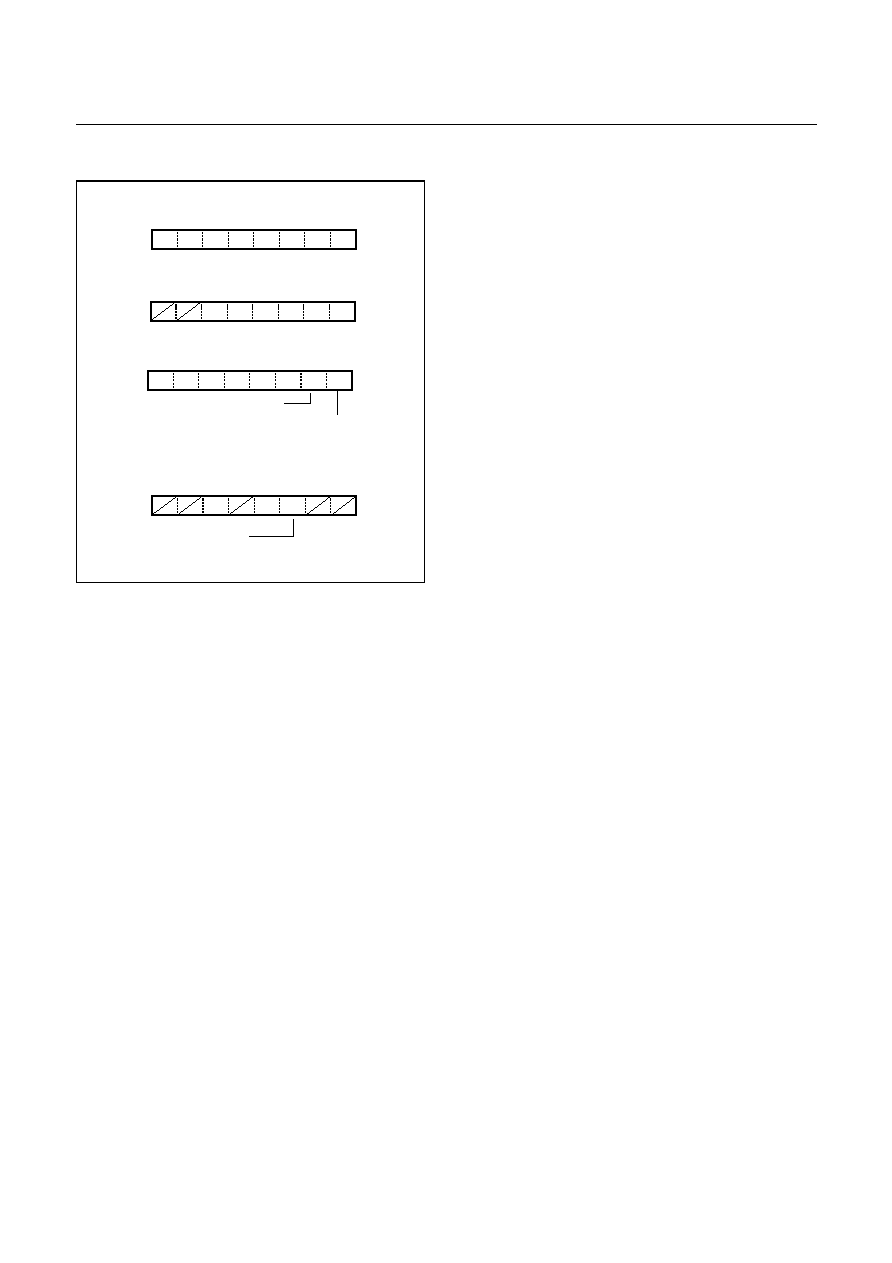

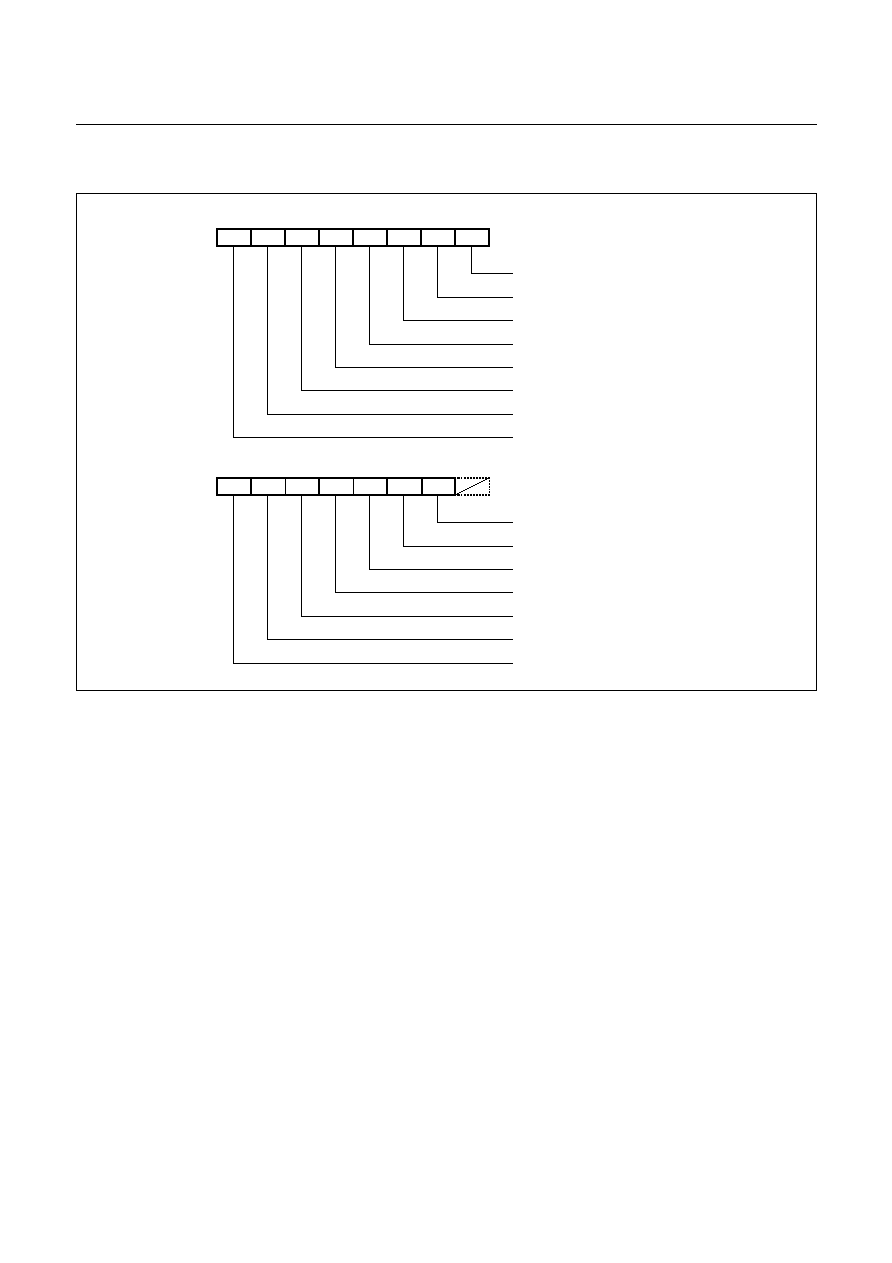

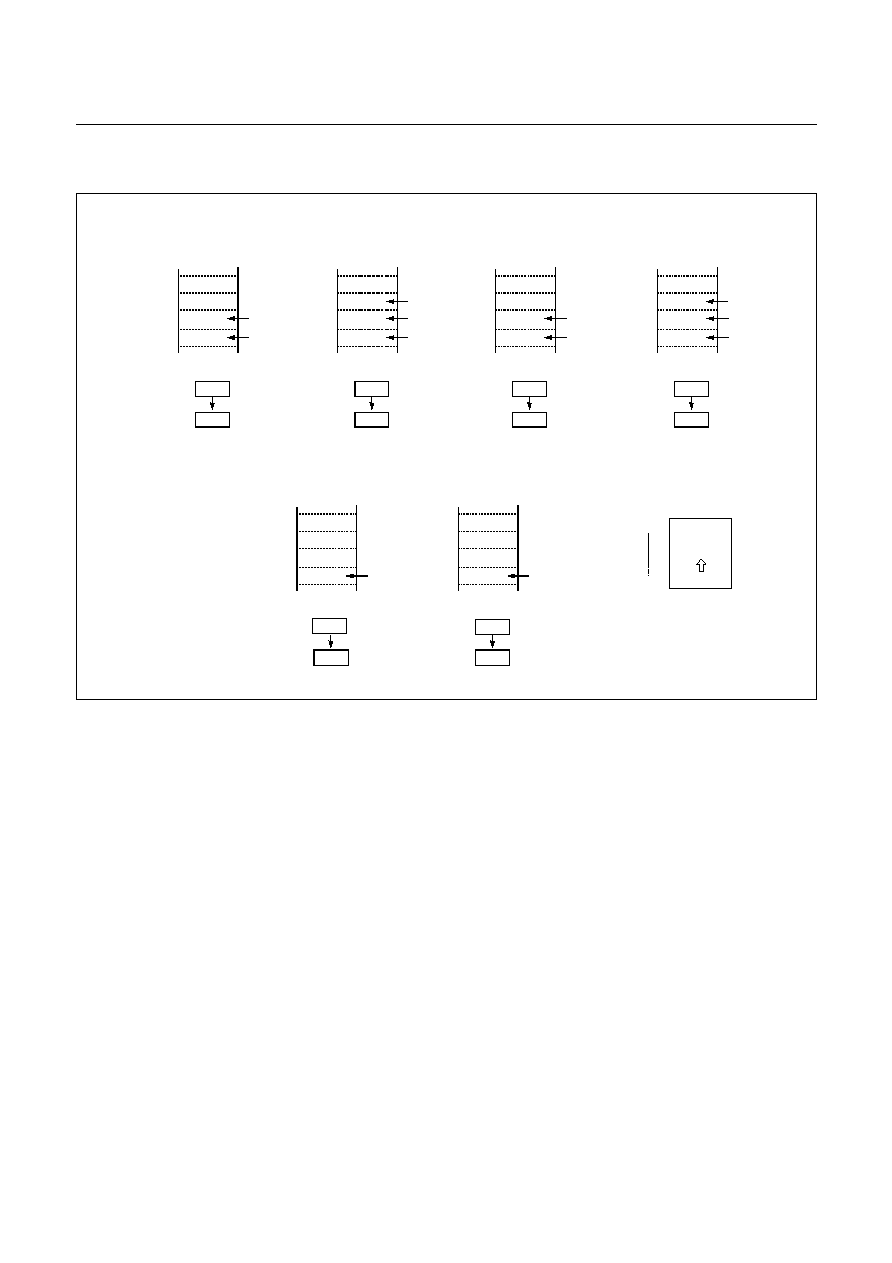

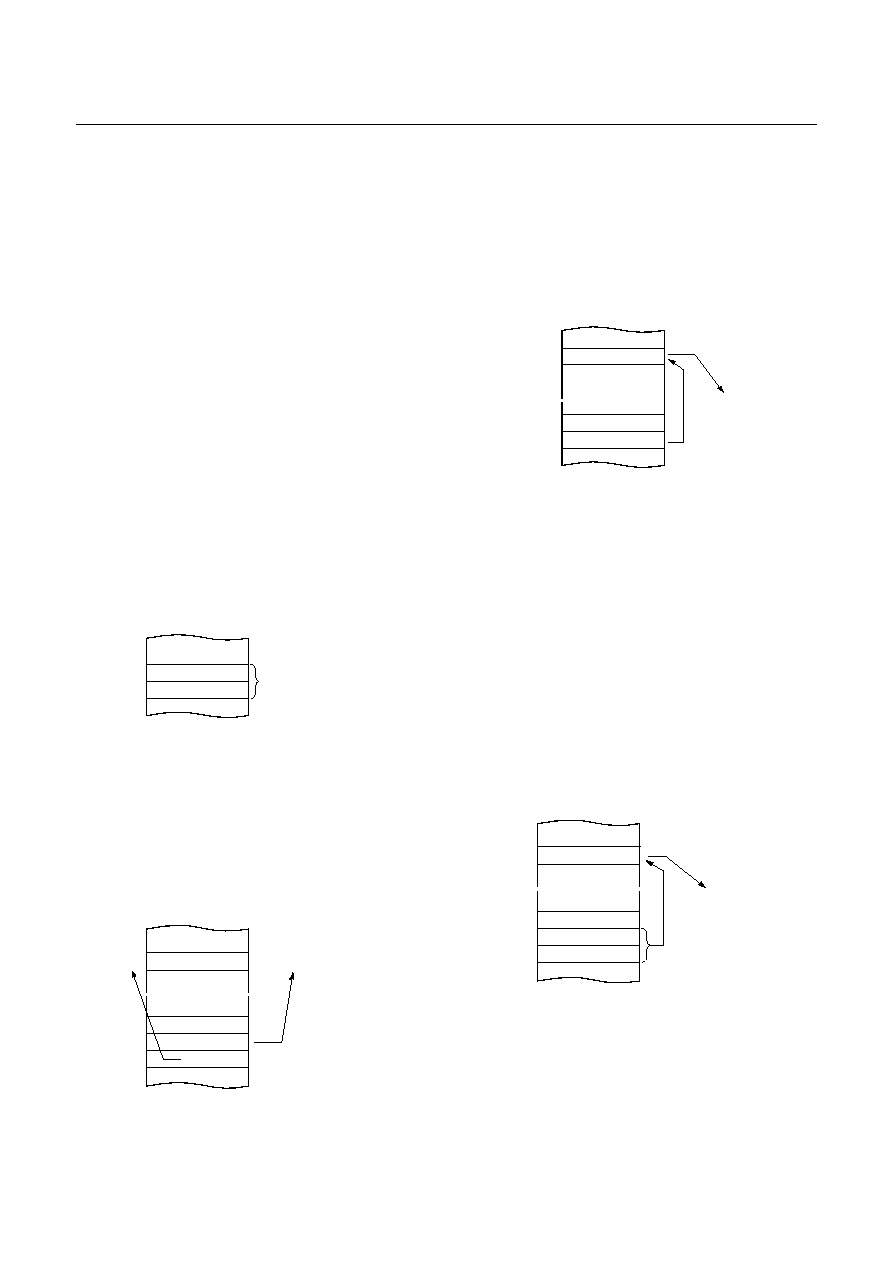

Figure 8-4 Stack Operation

At execution of

a CALL/TCALL/PCALL

PCL

PCH

01FF

SP after

execution

SP before

execution

01FD

01FE

01FD

01FC

01FF

Push

down

At acceptance

of interrupt

PCL

PCH

01FF

01FC

01FE

01FD

01FC

01FF

Push

down

PSW

At execution

of RET instruction

PCL

PCH

01FF

01FF

01FE

01FD

01FC

01FD

Pop

up

At execution

of RETI instruction

PCL

PCH

01FF

01FF

01FE

01FD

01FC

01FC

Pop

up

PSW

0100H

01FFH

Stack

depth

At execution

of PUSH instruction

A

01FF

01FE

01FE

01FD

01FC

01FF

Push

down

SP after

execution

SP before

execution

PUSH A (X,Y,PSW)

At execution

of POP instruction

A

01FF

01FF

01FE

01FD

01FC

01FE

Pop

up

POP A (X,Y,PSW)

GMS81C4040/87C4060

HYUNDAI

20

May. 2000 Ver 1.0

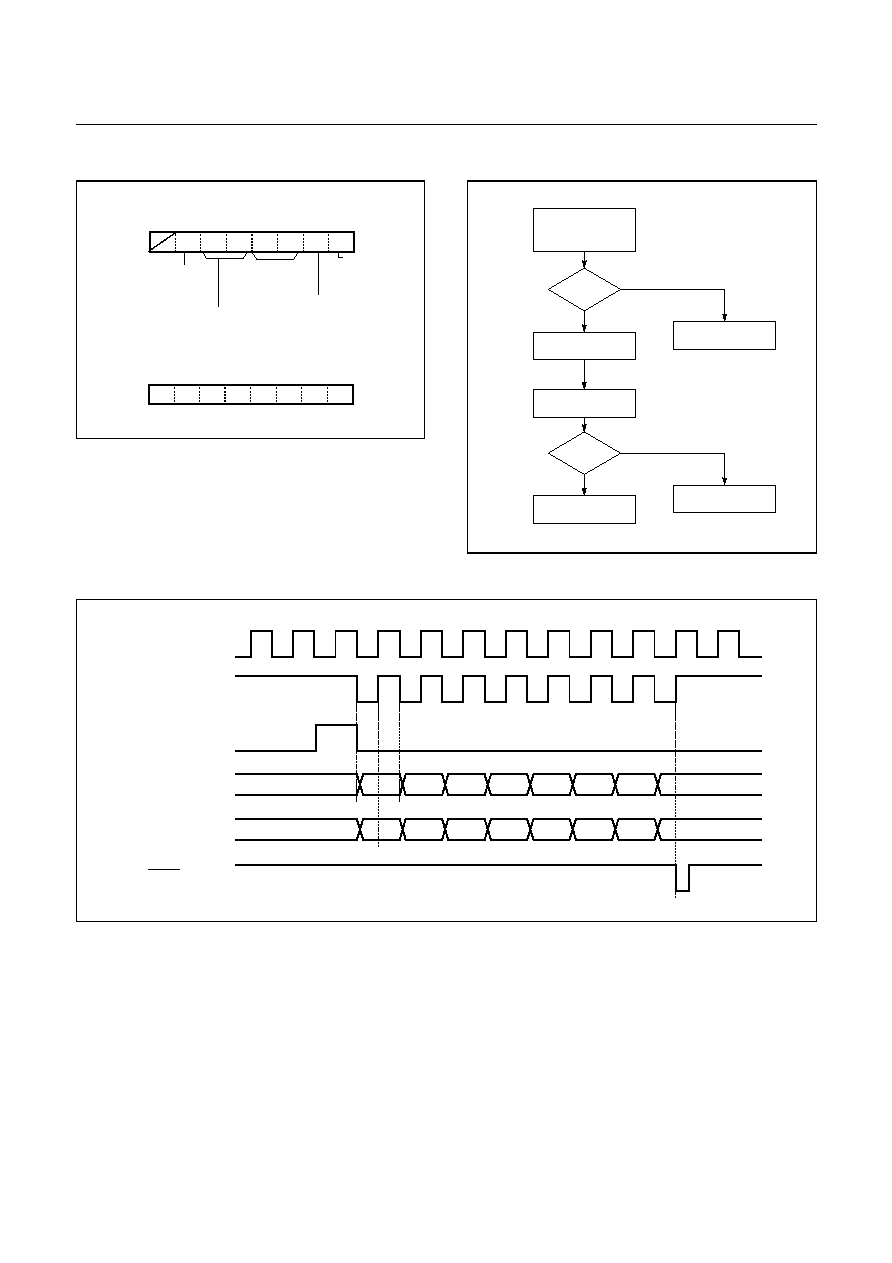

8.2 Program Memory

A 16-bit program counter is capable of addressing up to

64K bytes, but GMS81C4040/GMS87C4060 has 40K/

60K bytes program memory space only physically imple-

mented. Accessing a location above FFFF

H

will cause a

wrap-around to 0000

H

.

Figure 8-5 , shows a map of Program Memory. After reset,

the CPU begins execution from reset vector which is stored

in address FFFE

H

and FFFF

H

as shown in Figure 8-6 .

As shown in Figure 8-5 , each area is assigned a fixed lo-

cation in Program Memory. Program Memory area con-

tains the user program.

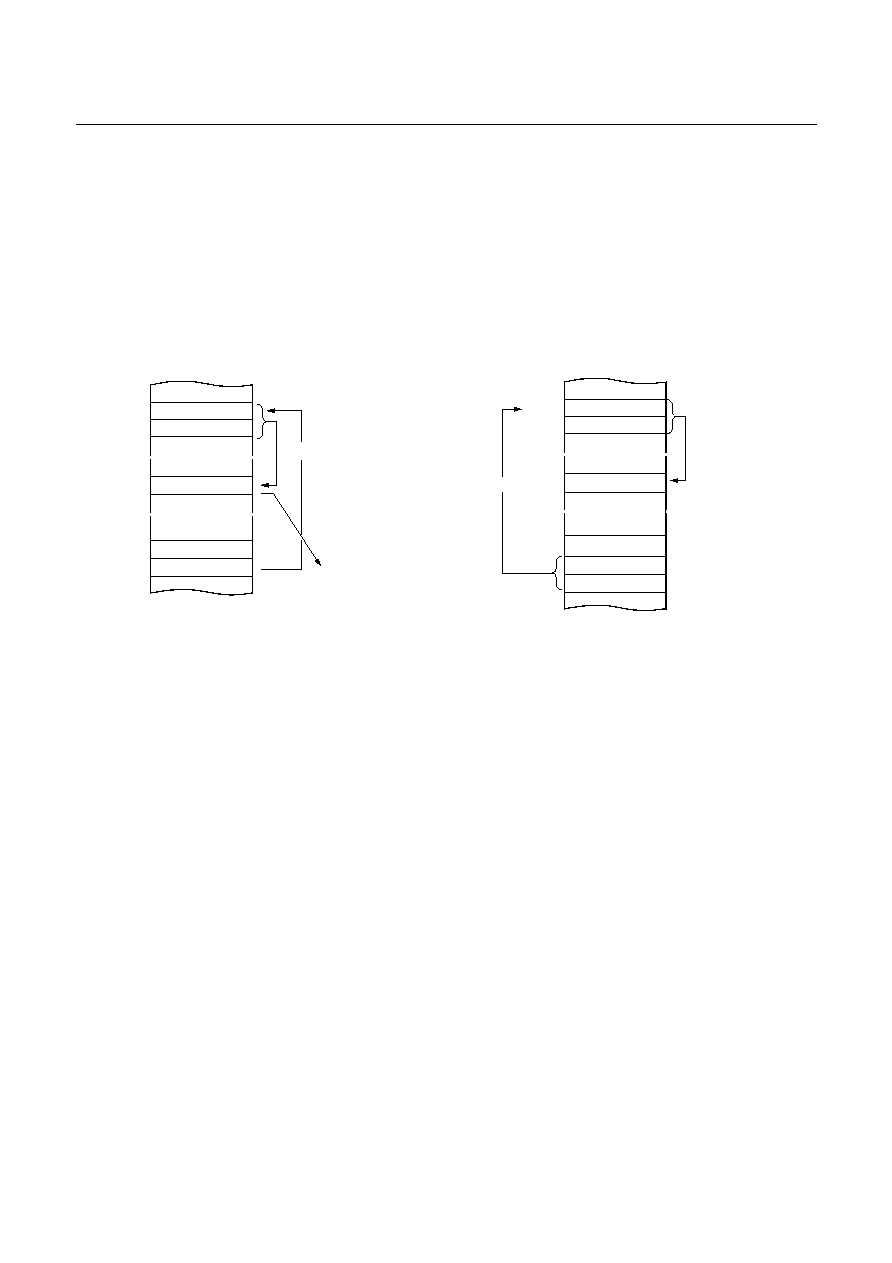

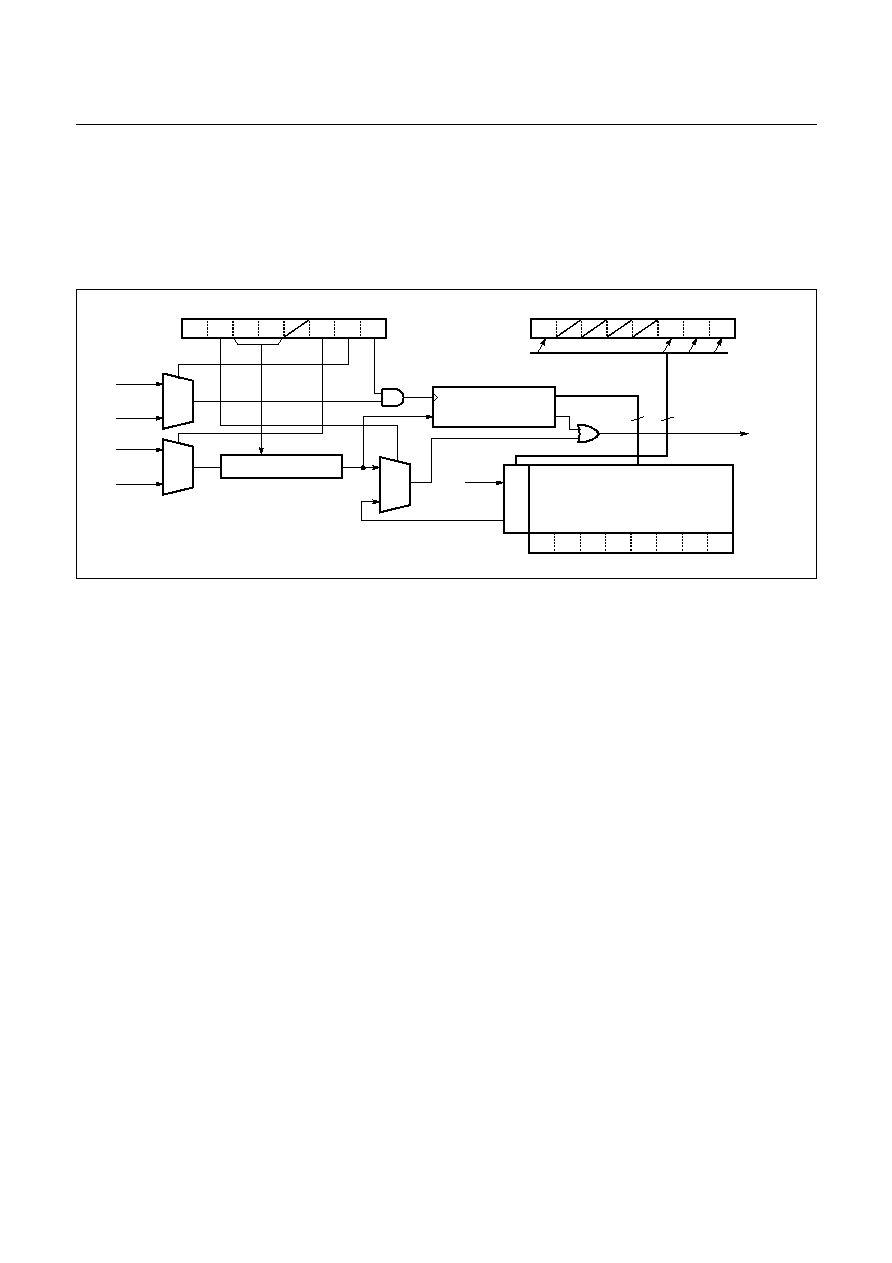

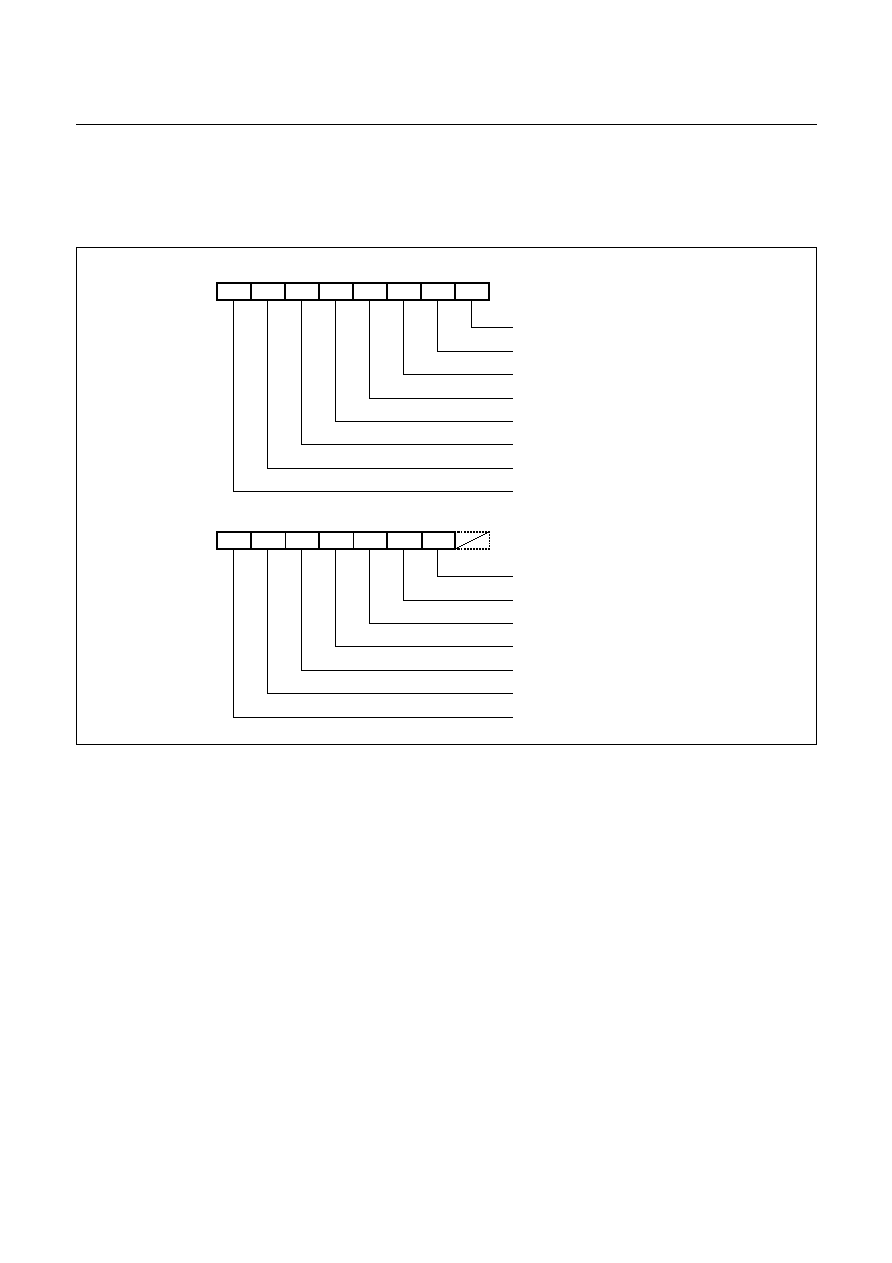

Figure 8-5 Program Memory Map

Page Call (PCALL) area contains subroutine program to

reduce program byte length by using 2 bytes PCALL in-

stead of 3 bytes CALL instruction. If it is frequently called,

it is more useful to save program byte length.

Table Call (TCALL) causes the CPU to jump to each

TCALL address, where it commences the execution of the

service routine. The Table Call service area spaces 2-byte

for every TCALL: 0FFC0

H

for TCALL15, 0FFC2

H

for

TCALL14, etc., as shown in Figure 8-7 .

Example: Usage of TCALL

The interrupt causes the CPU to jump to specific location,

where it commences the execution of the service routine.

The External interrupt 0, for example, is assigned to loca-

tion 0FFFC

H

. The interrupt service locations spaces 2-byte

interval: 0FFF8

H

and 0FFF9

H

for External Interrupt 1,

0FFFC

H

and 0FFFD

H

for External Interrupt 0, etc.

Any area from 0FF00

H

to 0FFFF

H

, if it is not going to be

used, its service location is available as general purpose

Program Memory.

Figure 8-6 Interrupt Vector Area

PROGRAM

MEMORY

TCALL

AREA

INTERRUPT

VECTOR AREA

81C4040:6000H

FEFFH

FF00H

FFC0H

FFDFH

FFE0H

FFFFH

PCALL

AREA

81C4060:1000H

FFBFH

LDA

#5

TCALL

0FH

;

1 B Y TE IN S T R U C T IO N

:

;

IN S TE A D O F 2 B Y TE S

:

;

N O R M A L C A L L

;

;TABLE CALL ROUTINE

;

FUNC_A:

LDA

LRG0

RET

;

FUNC_B:

LDA

LRG1

RET

;

;TABLE CALL ADD. AREA

;

ORG

0FFC0H

;

TC A L L A D D R E SS A R E A

DW

FUNC_A

DW

FUNC_B

1

2

0FFE0

H

E2

Address

Vector Area Memory

E4

E6

E8

EA

EC

EE

F0

F2

F4

F6

F8

FA

FC

FE

I

2

C Bus Interface Interrupt Vector Area

Serial I/O Interrupt Vector Area

Basic Interval Timer Interrupt Vector Area

Watchdog Timer Interrupt Vector Area

Timer/Counter 3 Interrupt Vector Area

Timer/Counter 1 Interrupt Vector Area

V-Sync Interrupt Vector Area

Timer/Counter 2 Interrupt Vector Area

Timer/Counter 0 Interrupt Vector Area

External Interrupt 2 Vector Area

On Screen Display Interrupt Vector Area

External Interrupt 0 Vector Area

RESET Vector Area

External Interrupt 1 Vector Area

1 Frame Timer Interrupt Vector Area

External Interrupt 3/4 Vector Area

"-" means reserved area.

NOTE:

HYUNDAI

GMS81C4040/87C4060

May. 2000 Ver 1.0

21

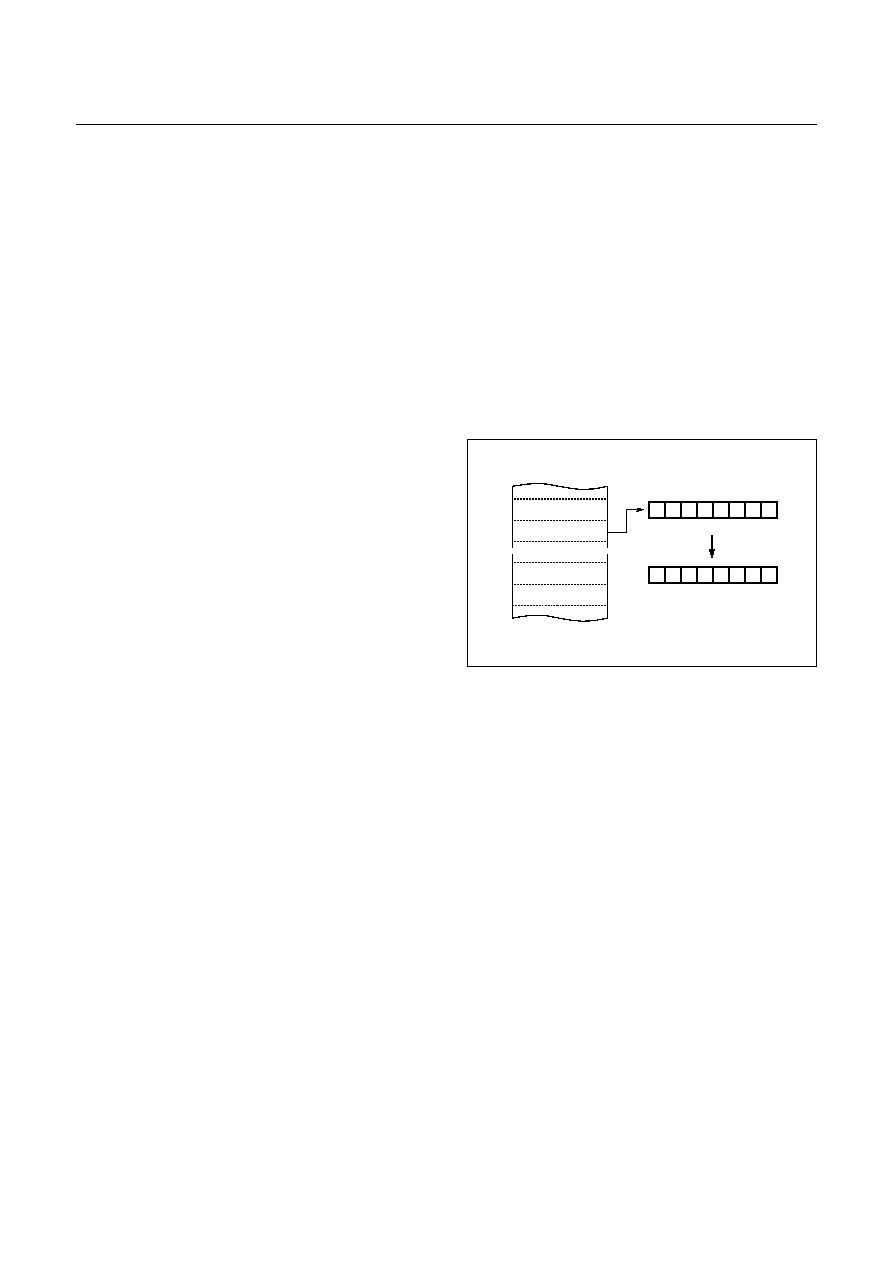

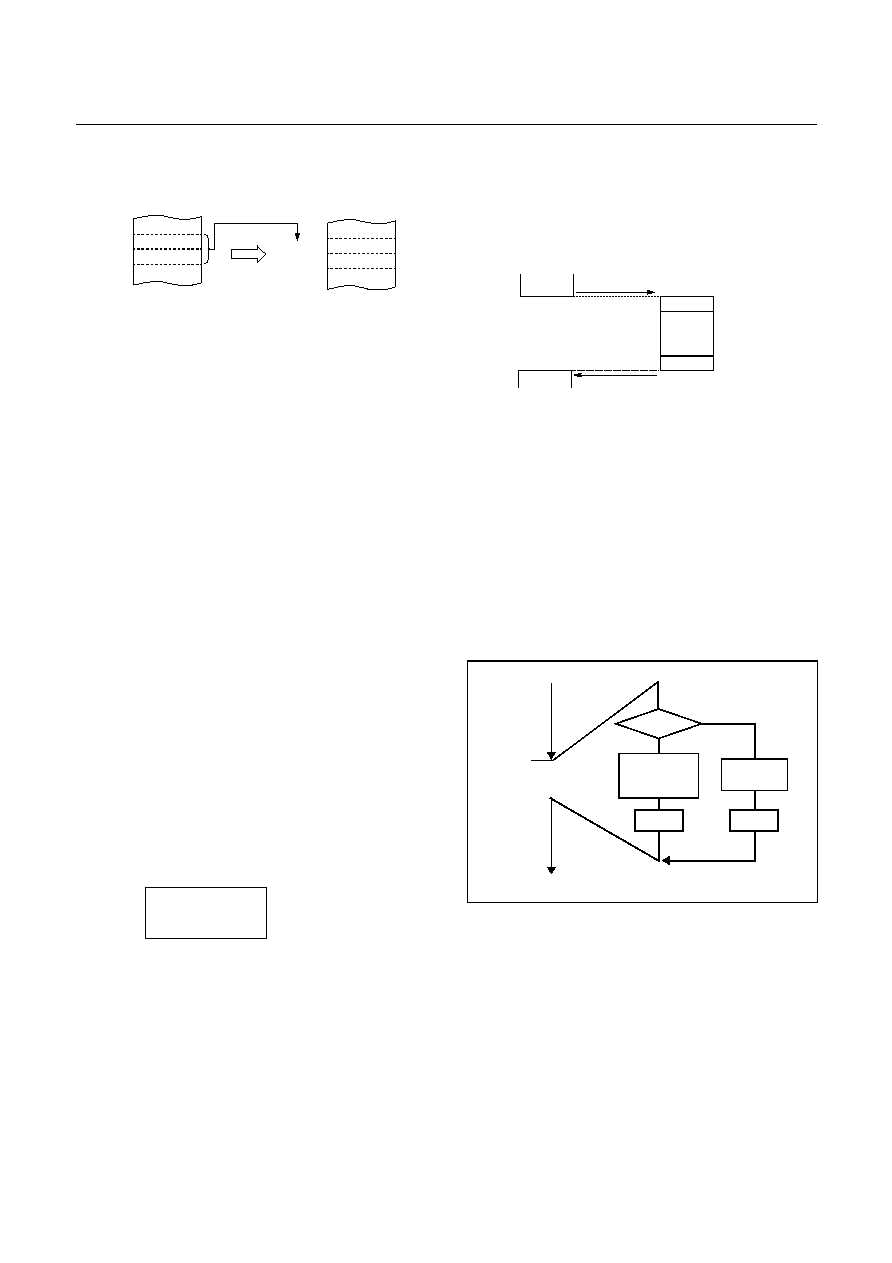

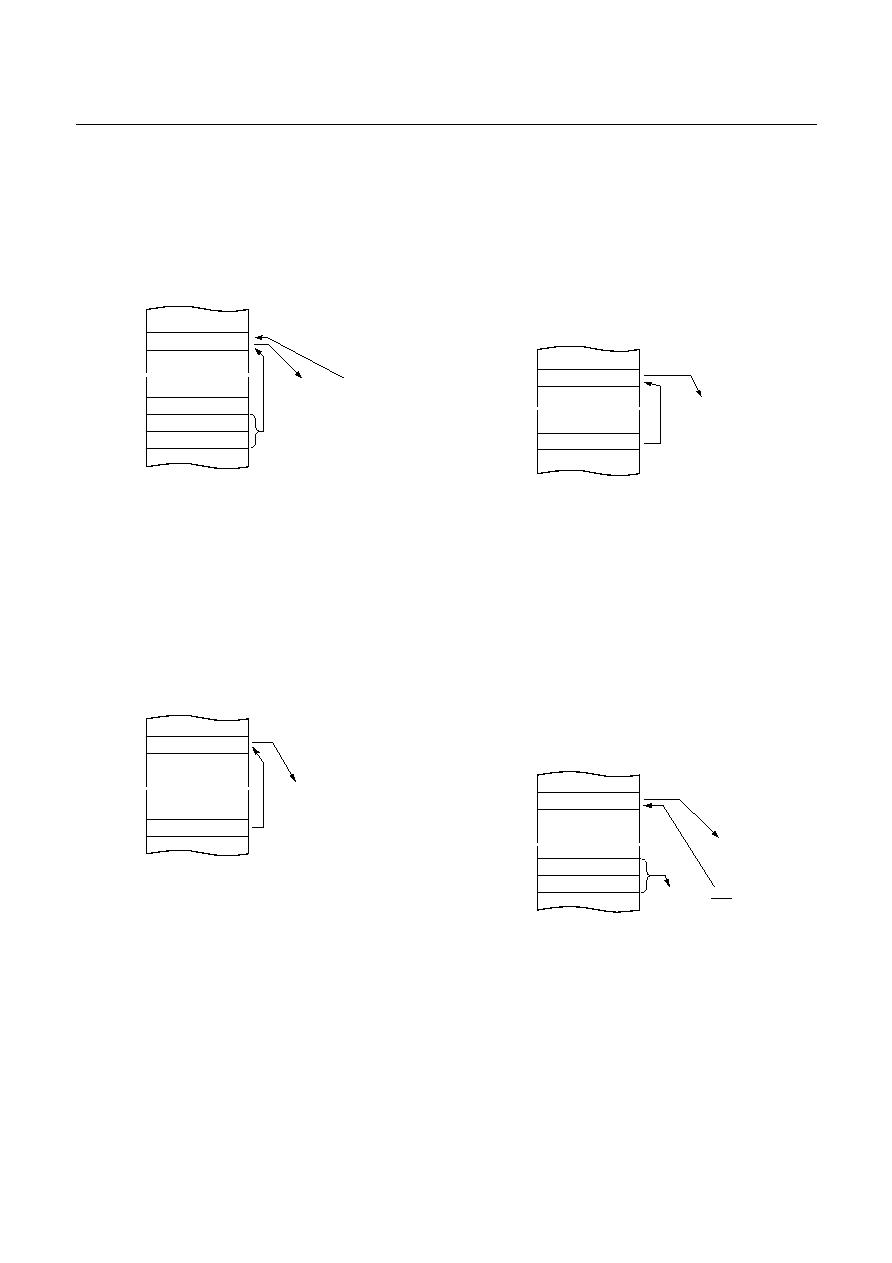

Figure 8-7 PCALL and TCALL Memory Area

PCALL

rel

4F35

PCALL

35H

TCALL

n

4A

TCALL 4

0FFC0

H

C1

Address

Program Memory

C2

C3

C4

C5

C6

C7

C8

0FF00

H

Address

PCALL Area Memory

0FFBF

H

PCALL Area

(192 Bytes)

* means that the BRK software interrupt is using

same address with TCALL0.

NOTE:

TCALL 15

TCALL 14

TCALL 13

TCALL 12

TCALL 11

TCALL 10

TCALL 9

TCALL 8

TCALL 7

TCALL 6

TCALL 5

TCALL 4

TCALL 3

TCALL 2

TCALL 1

TCALL 0 / BRK *

C9

CA

CB

CC

CD

CE

CF

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

DA

DB

DC

DD

DE

DF

4F

~

~

~

~

Sub-routine

35

0FF35H

0FF00H

0FFFFH

Upper address is

assumed 0FF

H.

11111111 11010110

01001010

PC:

F

H

F

H

D

H

6

H

4A

~

~

~

~

25

0FFD6H

0FF00H

0FFFFH

D1

Sub-routine

0FFD7H

�

�

�

0D125H

Reverse

GMS81C4040/87C4060

HYUNDAI

22

May. 2000 Ver 1.0

Example: The usage software example of Vector address and the initialize part.

ORG

0FFE0H

DW

I2C

; I2C

DW

SERIAL

; Serial I/O

DW

BIT

; Basic interval timer

DW

WATCHDOG

; Watch dog timer

DW

INT3_4

; Interrupt 3/4

DW

TIMER3

; Timer 3

DW

TIMER1

; Timer 1

DW

VSYNC

; Vertical Sync.

DW

One_Frame

; 1 Frame interrupt

DW

TIMER2

; Timer 2

DW

TIMER0

; Timer 0

DW

INT2

; Interrupt 2

DW

INT1

; Interrupt 1

DW

OSD

; On Screen Display

DW

INT0

; Interrupt 0

DW

RESET

; Reset

ORG

0F000H

;********************************************

;

MAIN PROGRAM

*

;********************************************

;

RESET:

DI

; Disable All Interrupts

LDX

#0

LDA

#0

; RAM Clear(!0000H->!00BFH)

RAM_CLR:

STA

{X}+

CMPX

#0C0H

BNE

RAM_CLR

;

CALL

LCD_CLR

; Clear LCD display memory

;

LDX

#03FH

; Stack Pointer Initialize

TXSP

LDM

R0, #0

; Normal Port 0

LDM

R0DD,#1000_0010B

; Normal Port Direction

:

:

:

:

HYUNDAI

GMS81C4040/87C4060

May. 2000 Ver 1.0

23

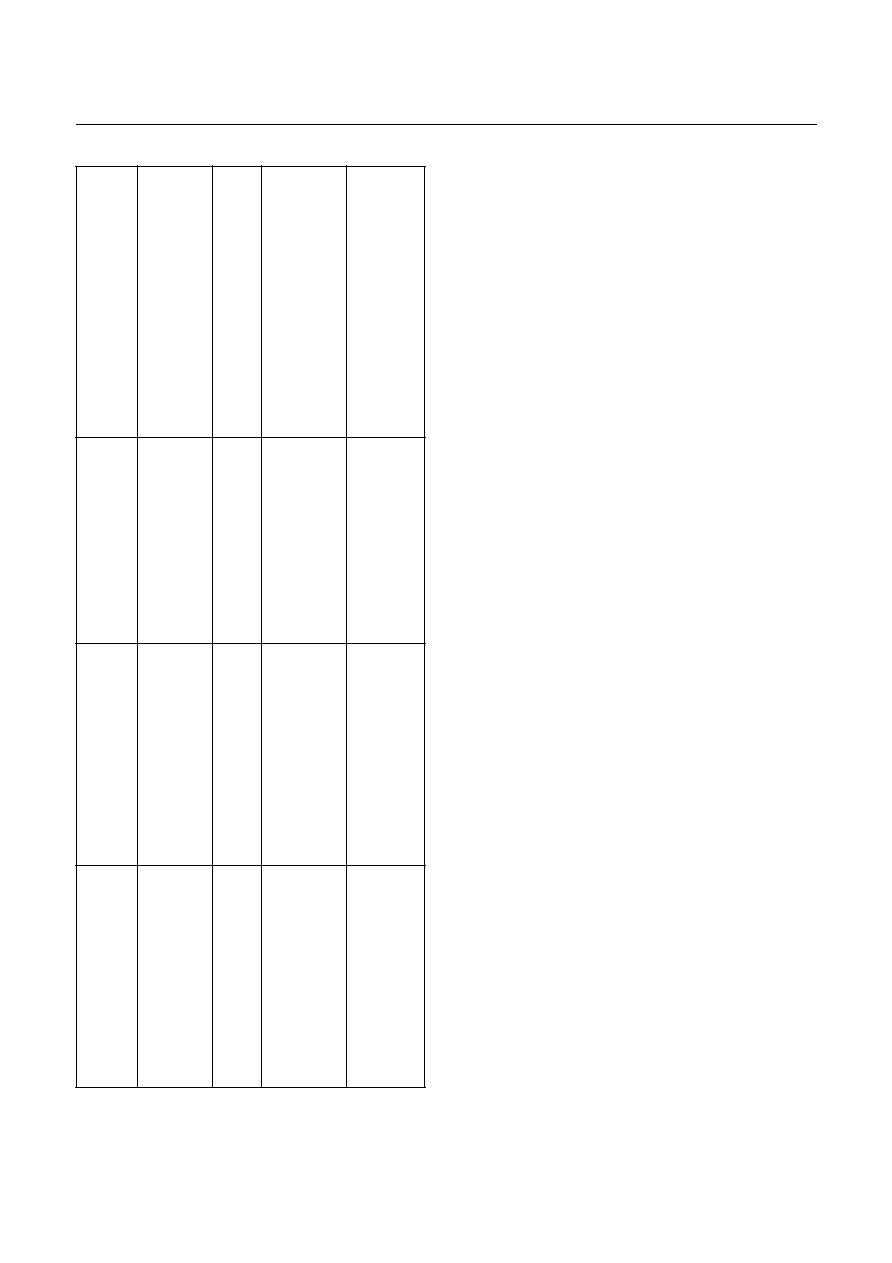

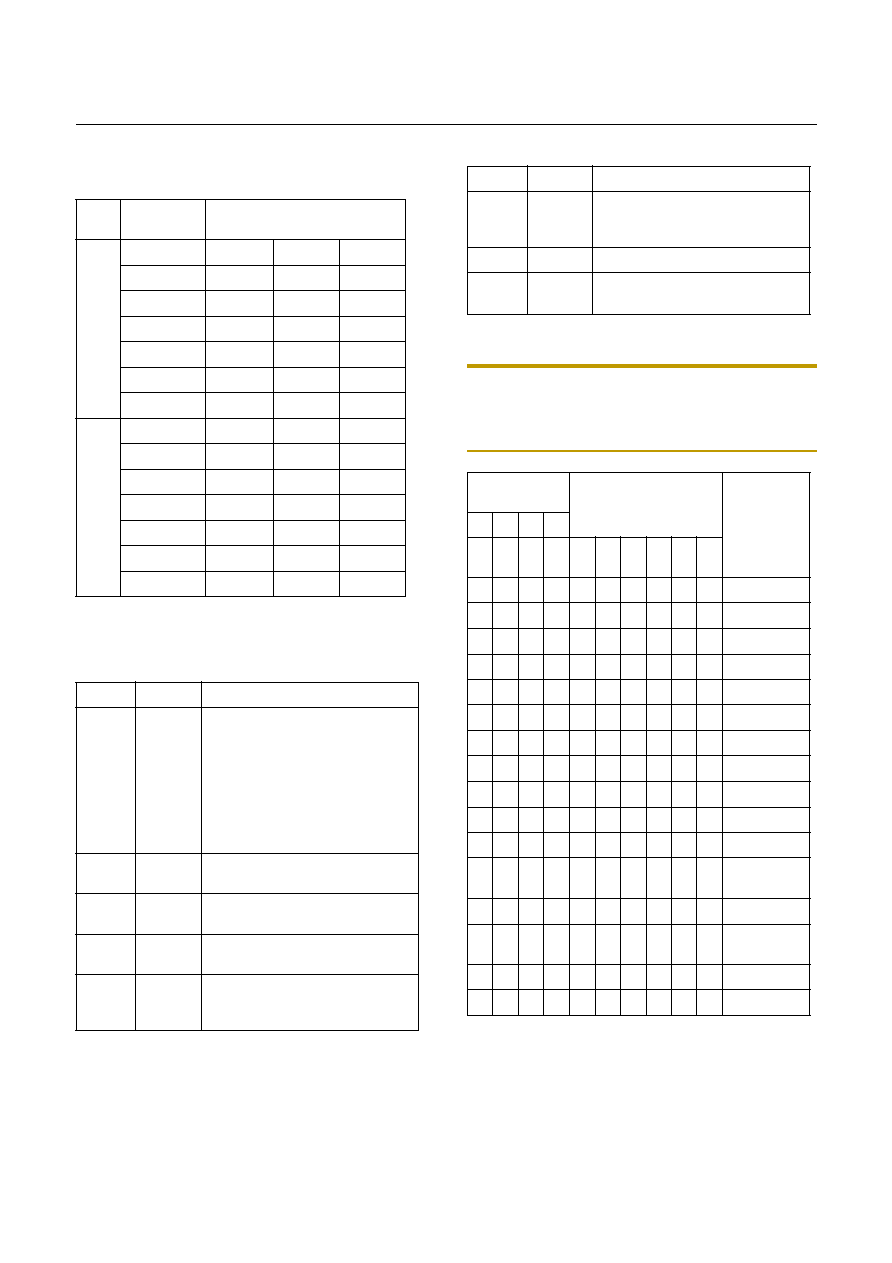

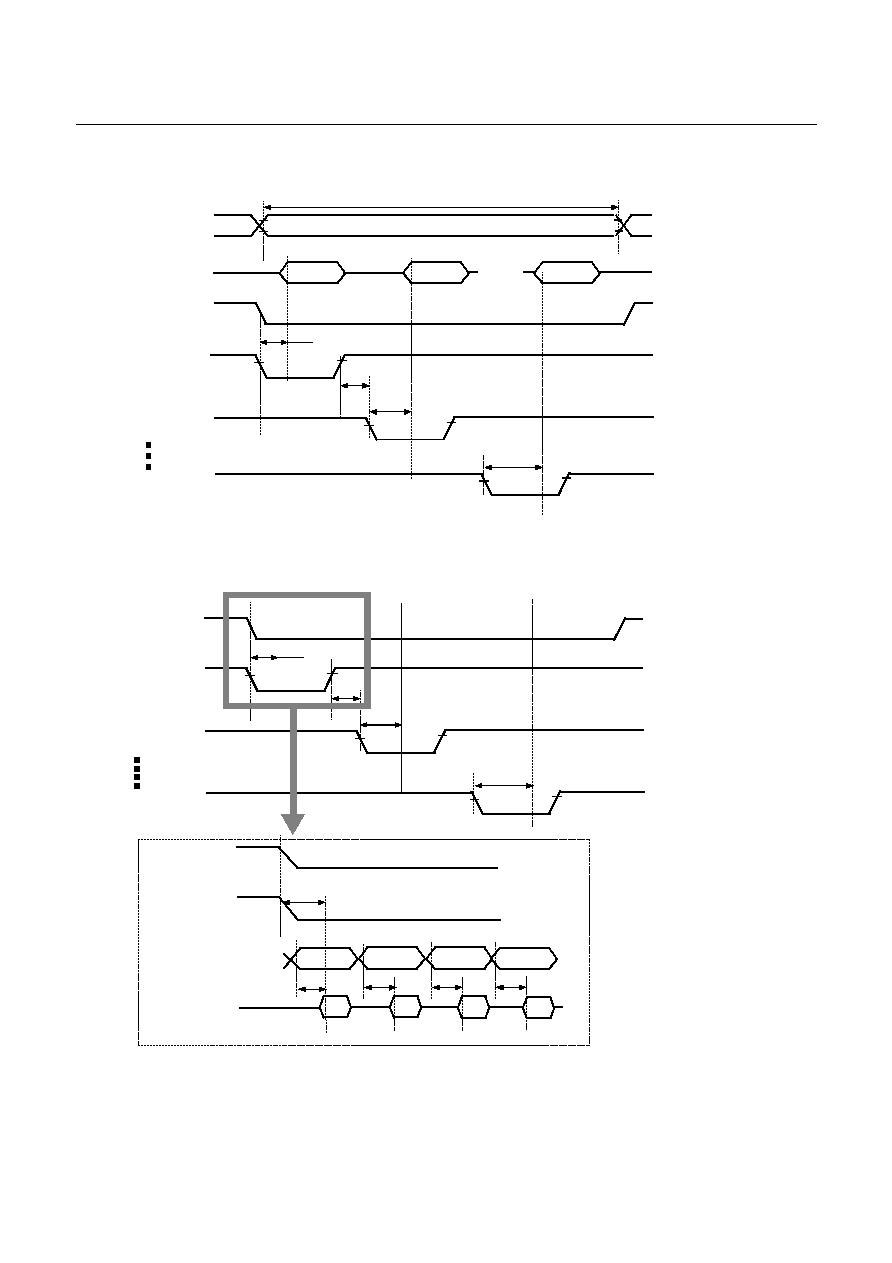

8.3 Data Memory

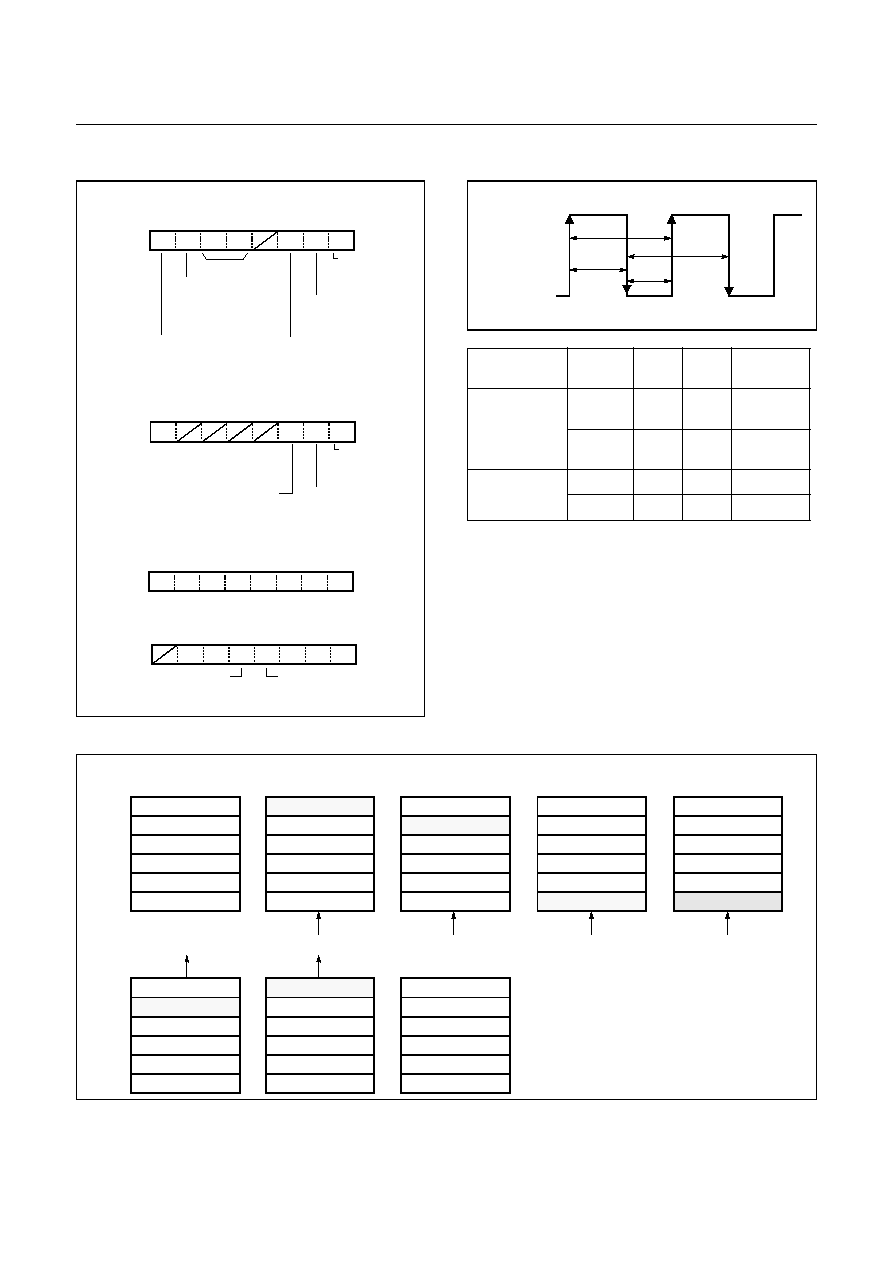

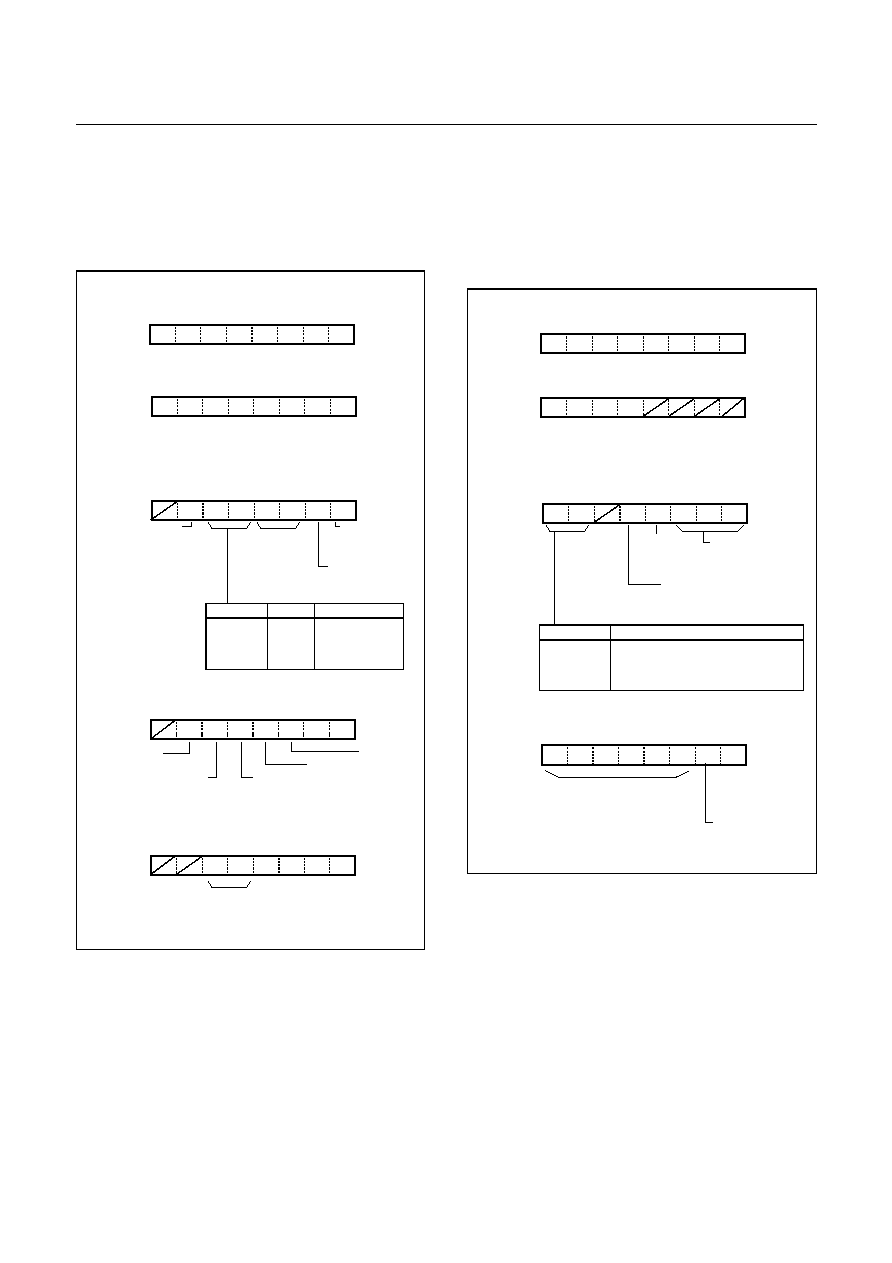

Figure 8-8 shows the internal Data Memory space availa-

ble. Data Memory is divided into four groups, a user RAM,

control registers, Stack, and OSD memory.

Figure 8-8 Data Memory Map

User Memory

The GMS81C4040/GMS87C4060 has 1,536

�

8 bits for

the user memory (RAM).

Control Registers

The control registers are used by the CPU and Peripheral

function blocks for controlling the desired operation of the

device. Therefore these registers contain control and status

bits for the interrupt system, the timer/ counters, analog to

digital converters and I/O ports. The basic control registers

are in address range of 00C0

H

to 00FF

H

. And OSD control

registers are assigned within 0AE0

H

~ 0AFF

H

.

Note that unoccupied addresses may not be implemented

on the chip. Read accesses to these addresses will in gen-

eral return random data, and write accesses will have an in-

determinate effect.

More detailed informations of each register are explained

in each peripheral section.

Note: Write only registers can not be accessed by bit ma-

nipulation instruction. Do not use read-modify-write instruc-

tion. Use byte manipulation instruction.

Example; To write at CKCTLR

LDM

CLCTLR,#09H ;Divide ratio

�

8

Stack Area

The stack provides the area where the return address is

saved before a jump is performed during the processing

routine at the execution of a subroutine call instruction or

the acceptance of an interrupt.

When returning from the processing routine, executing the

subroutine return instruction [RET] restores the contents of

the program counter from the stack; executing the interrupt

return instruction [RETI] restores the contents of the pro-

gram counter and flags.

The save/restore locations in the stack are determined by

the stack pointed (SP). The SP is automatically decreased

after the saving, and increased before the restoring. This

means the value of the SP indicates the stack location

number for the next save. Refer to Figure 8-4 on page 19.

Page0

RAM (192 bytes)

Peripheral Reg. (64 bytes)

0100H

00C0H

0000H

RAM (256 bytes)

0200H

RAM (256 bytes)

0300H

RAM (256 bytes)

0400H

RAM (256 bytes)

0500H

RAM (256 bytes)

0600H

RAM (64 bytes)

0A00H

OSD RAM (192 bytes)

0AE0H

Peripheral Reg. (32 bytes)

0C00H

Sprite RAM (96 bytes)

Empty area

Page1

Page2

Page3

Page4

Page5

Page6

PageA

PageC

063FH

Stack area

0C5FH

Address

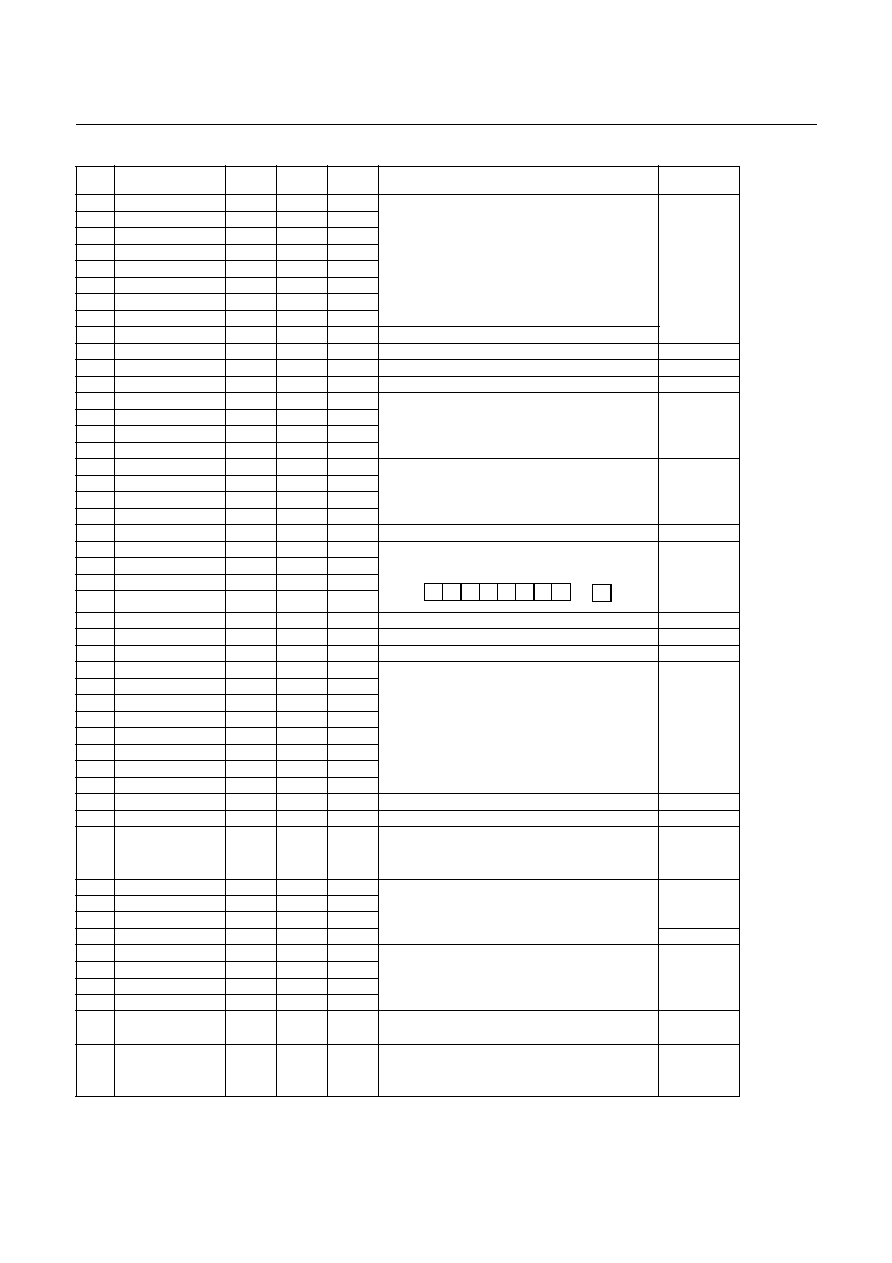

Symbol

R/W

Reset Value

Addressing

mode

00C0H

00C1H

00C2H

00C3H

00C4H

00C5H

00C8H

00C9H

00CAH

00CBH

00CCH

00CDH

00CEH

00CFH

R0

R0DD

R1

R1DD

R2

R2DD

R4

R4DD

R5

R5DD

R6

R6DD

FUNC1

FUNC2

R/W

W

R/W

W

R/W

W

R/W

W

R/W

W

R/W

W

W

W

????????

00000000

????????

00000000

????????

00000000

????????

0000----

????????

----0000

?-------

0-------

-0000000

---00000

byte, bit

1

byte

2

byte, bit

byte

byte, bit

byte

byte, bit

byte

byte, bit

byte

byte, bit

byte

byte

byte

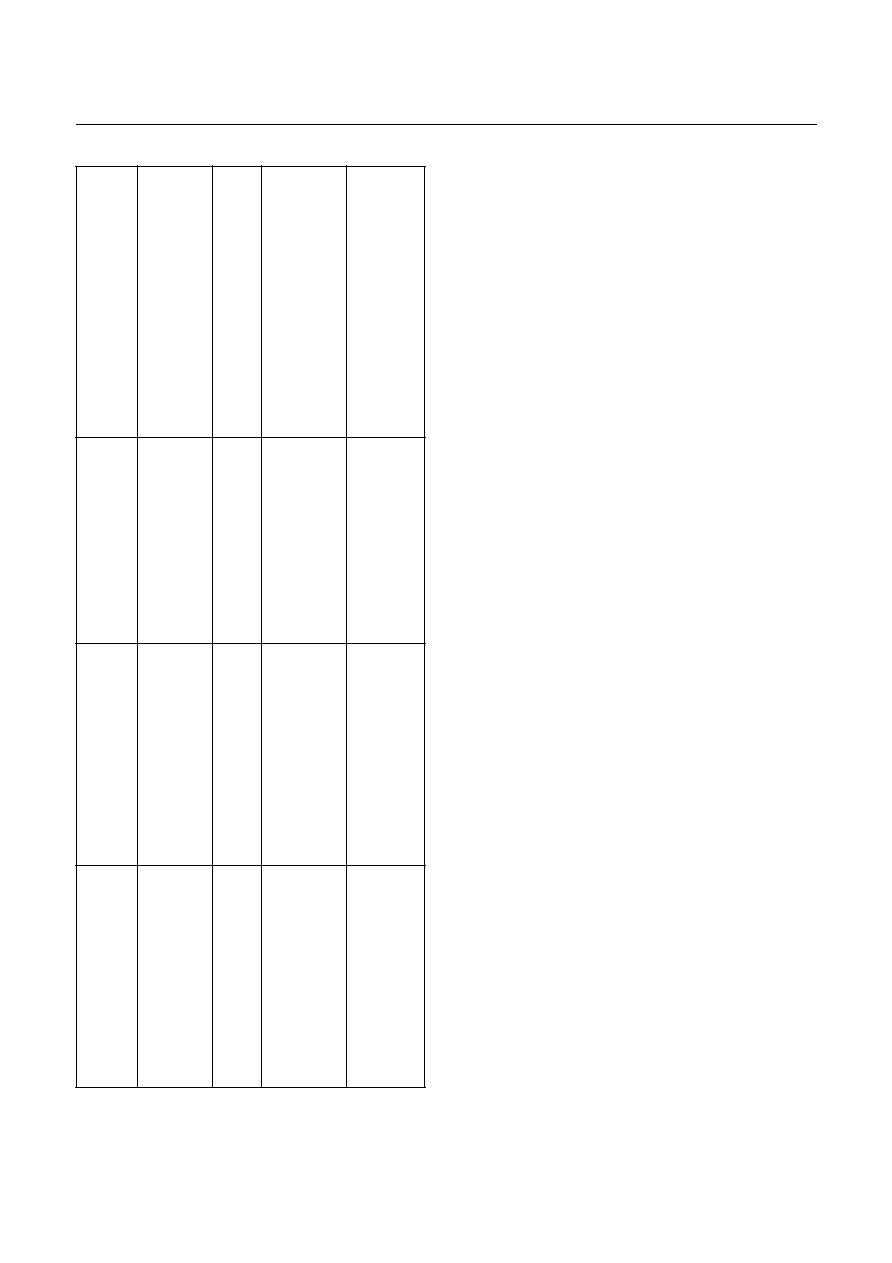

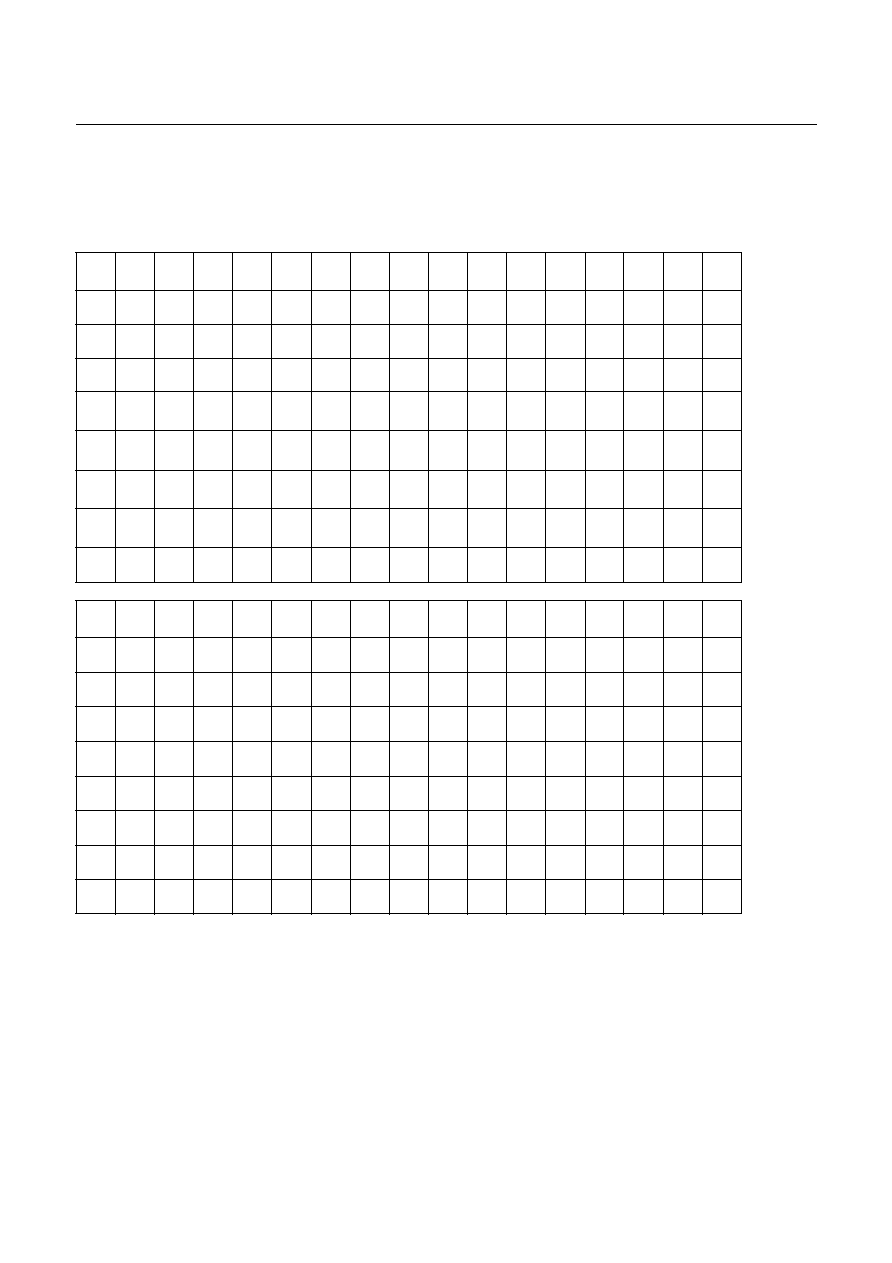

Table 8-1Control registers

GMS81C4040/87C4060

HYUNDAI

24

May. 2000 Ver 1.0

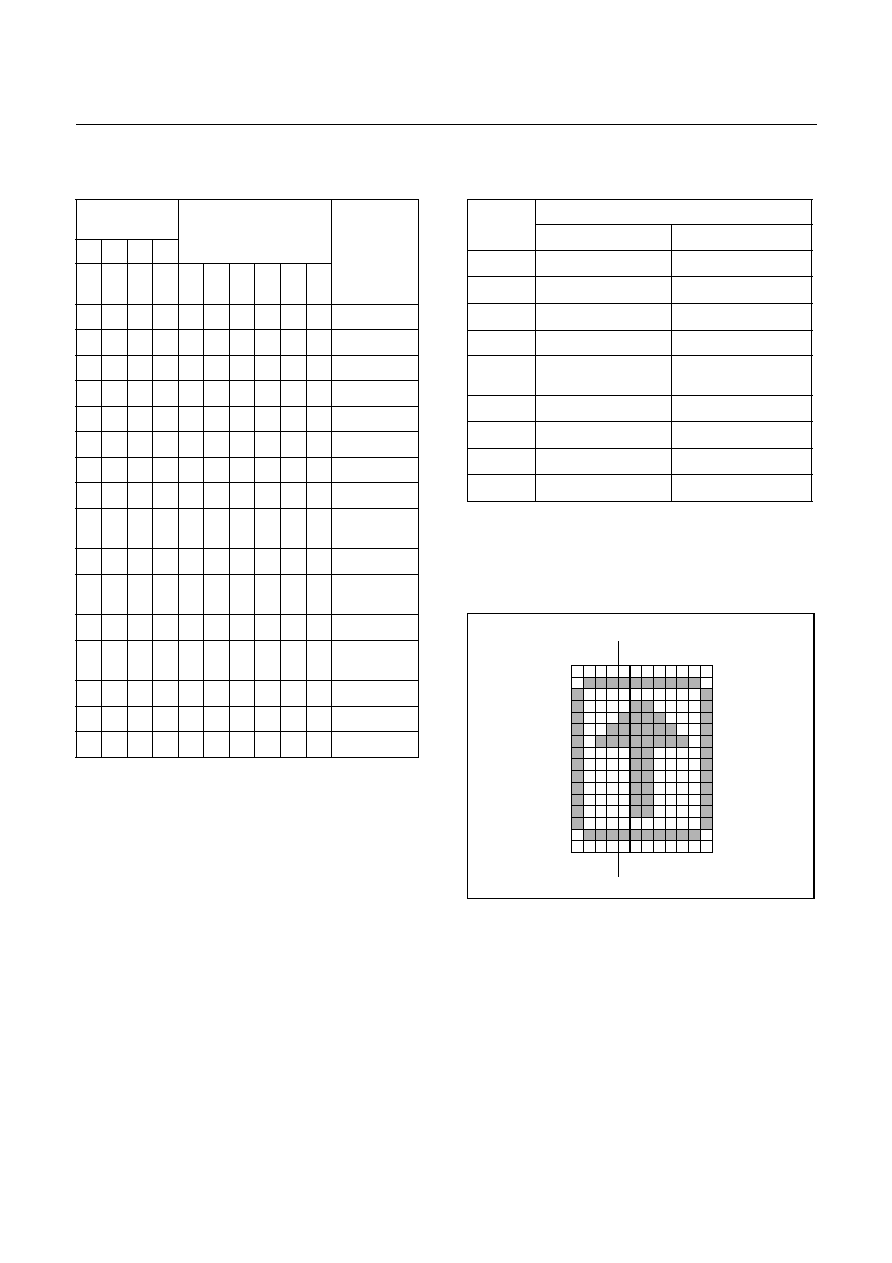

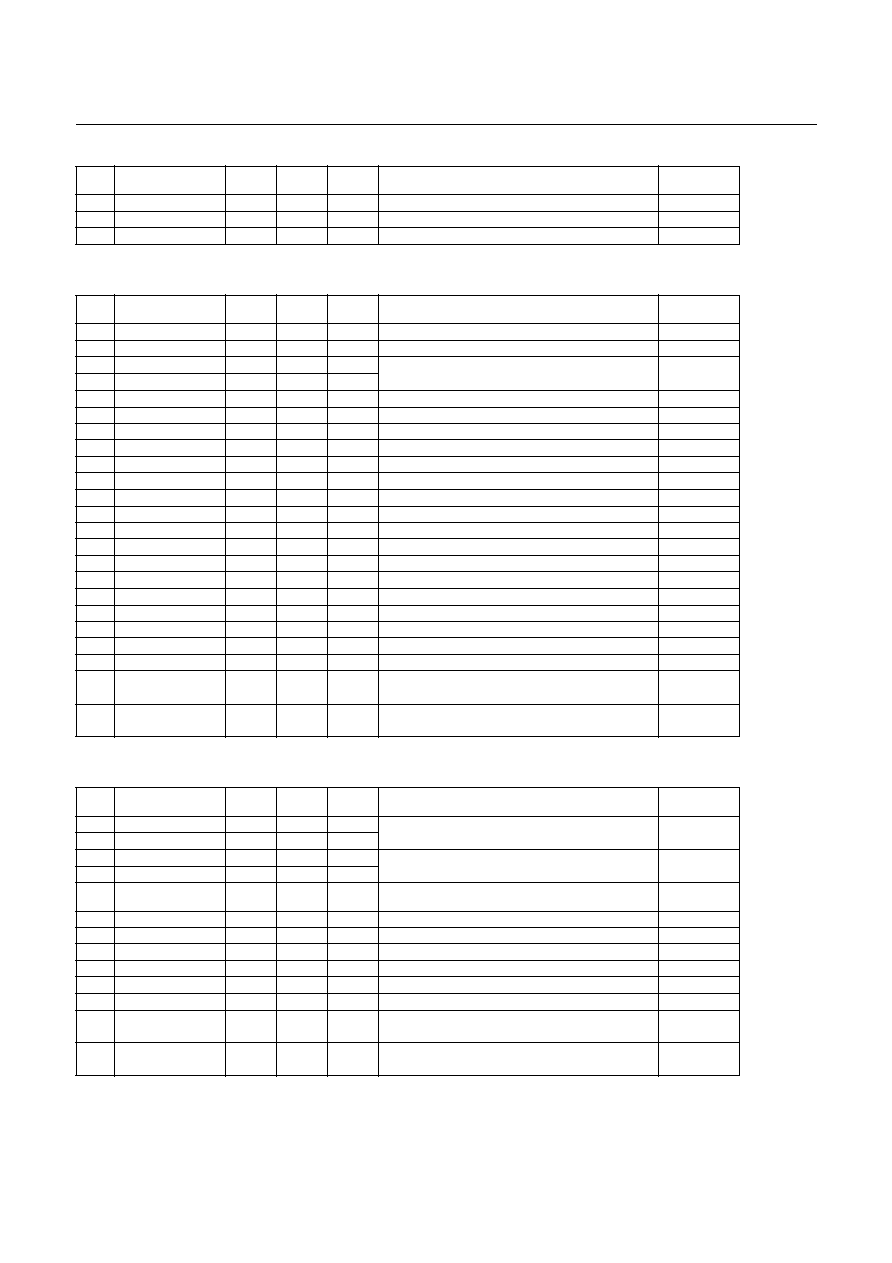

0D0H

0D1H

0D2H

0D3H

0D4H

0D5H

0D6H

0D7H

0D8H

0D9H

0DAH

0DBH

0DCH

0DEH

0DFH

TM0

TM2

TDR0

TDR1

TDR2

TDR3

BITR

CKCTLR

WDTR

ICAR

ICDR

ICSR

ICCR1

ICCR2

SIOM

SIOR

R/W

R/W

R/W

R/W

R/W

R/W

R

W

W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

-0000000

-0000000

????????

????????

????????

????????

????????

--010111

-0111111

00000000

11111111

0001000-

00000000

00000000

-0000001

????????

byte

byte

byte, bit

byte, bit

byte, bit

byte, bit

byte

byte

byte

byte, bit

byte, bit

byte, bit

byte, bit

byte, bit

byte, bit

byte, bit

0E0H

0E1H

0E2H

0E3H

0E4H

0E5H

0E8H

0E9H

0EAH

0EBH

0EEH

0EFH

PWMR0

PWMR1

PWMR2

PWMR3

PWMR4

PWMR5

PWM8H

PWM8L

PWMCR1

PWMCR2

BUR

AIPS

W

W

W

W

W

W

R/W

R/W

R/W

R/W

W

W

????????

????????

????????

????????

????????

????????

????????

--??????

00000000

--0-0000

????????

--000000

byte

byte

byte

byte

byte

byte

byte, bit

byte, bit

byte, bit

byte, bit

byte

byte

0F0H

0F1H

0F2H

0F3H

0F4H

0F5H

0F6H

0F7H

0F9H

0FAH

0FBH

0FCH

0FDH

ADCM

ADR

IEDS

IMOD

IENL

IRQL

IENH

IRQH

IDCR

IDFS

IDR

DPGR

TMR

R/W

R

W

R/W

R/W

R/W

R/W

R/W

R/W

R

R

R/W

W

--011101

????????

--000000

--000000

0000000-

0000000-

00000000

00000000

0000-000

1----001

????????

----0000

????????

byte, bit

byte

byte

byte, bit

byte, bit

byte, bit

byte, bit

byte, bit

byte, bit

byte

byte

byte, bit

byte

0AE0H

0AE1H

0AE2H

0AE3H

0AE4H

0AE5H

0AE6H

0AE8H

0AE9H

0AF0H

0AF1H

0AF3H

0AF4H

OSDcon1

OSDcon2

OSDPOL

FDWSET

EDGEcol

OSDLN

LHPOS

SPVPOS

SPHPOS

L1ATTR

L1VPOS

L2ATTR

L2VPOS

R/W

R/W

W

W

W

R

W

W

W

W

W

W

W

00000000

-0000000

????????

01111010

10000111

---00000

????????

????????

????????

????????

????????

????????

????????

byte, bit

byte, bit

byte

byte

byte

byte

byte

byte

byte

byte

byte

byte

byte

Table 8-1Control registers

1. "byte, bit" means that register can be addressed by not only bit

but byte manipulation instruction.

2. "byte" means that register can be addressed by only byte

manipulation instruction. On the other hand, do not use any

read-modify-write instruction such as bit manipulation for clear-

ing bit.

HYUNDAI

GMS81C4040/87C4060

May. 2000 Ver 1.0

25

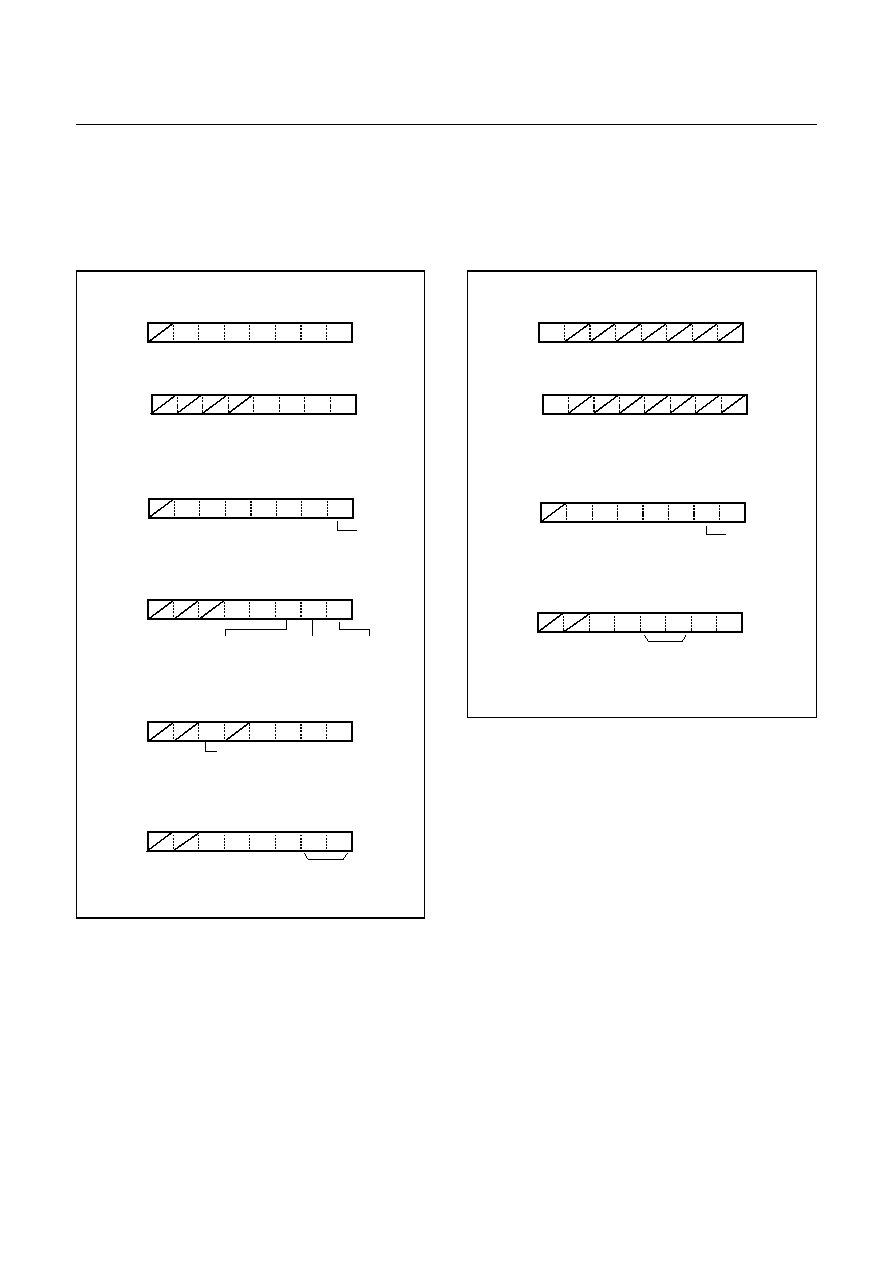

8.4 Addressing Mode

The GMS800 series uses six addressing modes;

� Register addressing

� Immediate addressing

� Direct page addressing

� Absolute addressing

� Indexed addressing

� Register-indirect addressing

(1) Register Addressing

Register addressing accesses the A, X, Y, C and PSW.

(2) Immediate Addressing

#imm

In this mode, second byte (operand) is accessed as a data

immediately.

Example:

FE10: 0435

ADC

#35H

When G-flag is 1, then RAM address is defined by 16-bit

address which is composed of 8-bit direct page accessable

register (DPGR) and 8-bit immediate data.

Example: G=1, DPGR=0CH

F100: E45535

LDM

35H,#55H

(3) Direct Page Addressing

dp

In this mode, a address is specified within direct page.

Example; G=0

E551: C535

LDA

35H;A

RAM[35H]

(4) Absolute Addressing

!abs

Absolute addressing sets corresponding memory data to

Data , i.e. second byte(Operand I) of command becomes

lower level address and third byte (Operand II) becomes

upper level address.

With 3 bytes command, it is possible to access to whole

memory area.

ADC, AND, CMP, CMPX, CMPY, EOR, LDA, LDX,

LDY, OR, SBC, STA, STX, STY

Example;

F100: 0735F0 ADC!0F035H

;A

ROM[0F035H]

35

A+35H+C

A

04

MEMORY

0FE10

H

E4

0F100

H

data

55H

~

~

~

~

data

0C35

H

�

35

0F102

H

55

0F101

H

A

data

35

35

H

0E551

H

data

A

�

�

~

~

~

~

C5

0E550

H

07

0F100

H

~

~

~

~

data

0F035

H

P

F0

0F102

H

35

0F101

H

A

A+data+C

A

address: 0F035

GMS81C4040/87C4060

HYUNDAI

26

May. 2000 Ver 1.0

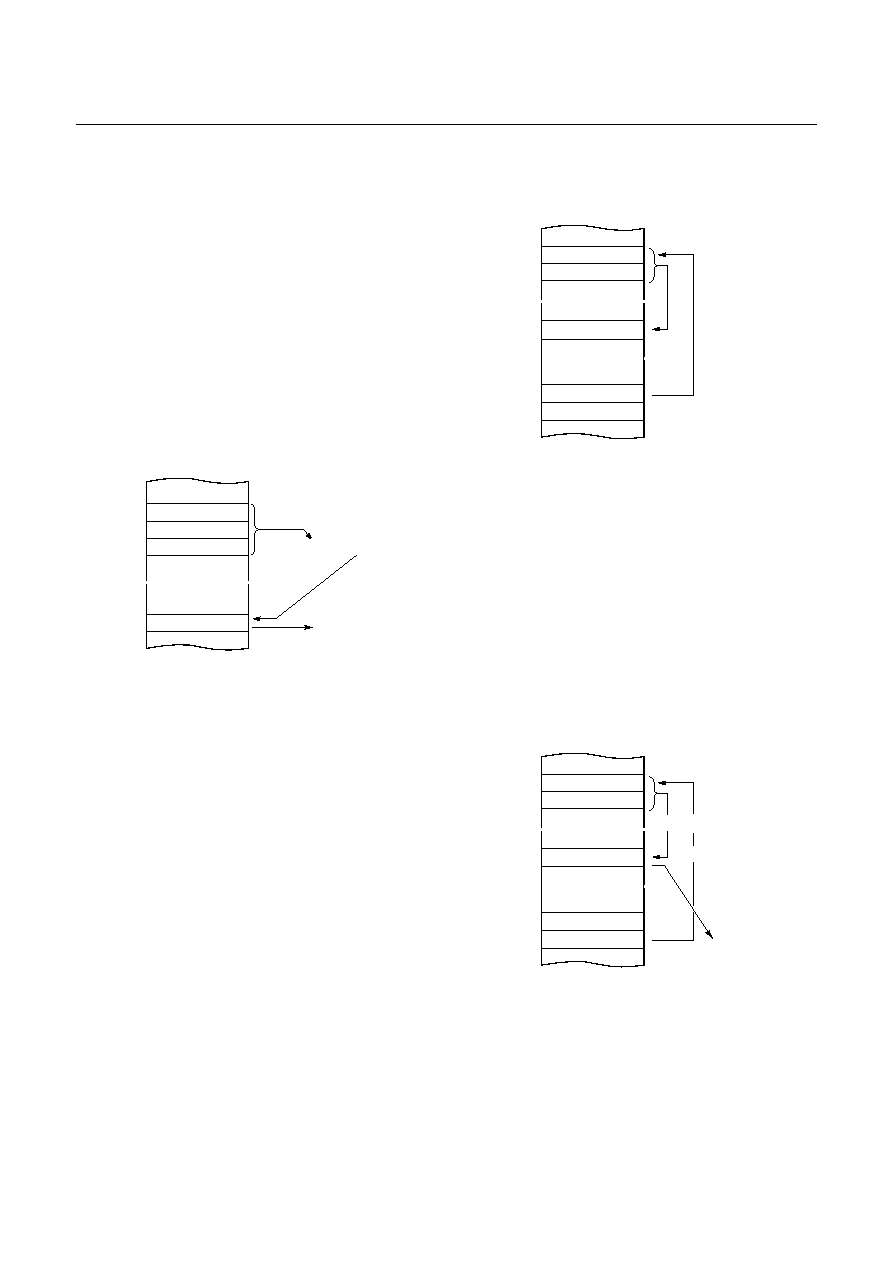

The operation within data memory (RAM)

ASL, BIT, DEC, INC, LSR, ROL, ROR

Example; Addressing accesses the address 0135

H

regard-

less of G-flag and DPGR.

F100: 983501 INC!0135H

;A

ROM[135H]

(5) Indexed Addressing

X indexed direct page (no offset)

{X}

In this mode, a address is specified by the X register.

ADC, AND, CMP, EOR, LDA, OR, SBC, STA, XMA

Example; X=15

H

, G=1, DPGR=03

H

E550: D4

LDA

{X};ACC

RAM[X].

X indexed direct page, auto increment

{X}+

In this mode, a address is specified within direct page by

the X register and the content of X is increased by 1.

LDA, STA

Example; G=0, X=35

H

F100: DB

LDA

{X}+

X indexed direct page (8 bit offset)

dp+X

This address value is the second byte (Operand) of com-

mand plus the data of

-register. And it assigns the mem-

ory in Direct page.

ADC, AND, CMP, EOR, LDA, LDY, OR, SBC, STA

STY, XMA, ASL, DEC, INC, LSR, ROL, ROR

Example; G=0, X=0F5

H

E550: C645

LDA

45H+X

98

0F100

H

~

~

~

~

data

135

H

�

01

0F102

H

35

0F101

H

�

data+1

data

�

address: 0135

data

D4

315

H

0E550

H

data

A

�

�

~

~

~

~

data

DB

35

H

data

A

�

�

~

~

~

~

36H

X

0F100

H

data

45

3A

H

0E551

H

data

A

�

�

~

~

~

~

C6

0E550

H

45H+0F5H=13AH

�

HYUNDAI

GMS81C4040/87C4060

May. 2000 Ver 1.0

27

Y indexed direct page (8 bit offset)

dp+Y

This address value is the second byte (Operand) of com-

mand plus the data of Y-register, which assigns Memory in

Direct page.

This is same with above (2). Use Y register instead of X.

Y indexed absolute

!abs+Y

Sets the value of 16-bit absolute address plus Y-register

data as Memory. This addressing mode can specify mem-

ory in whole area.

Example; Y=55

H

F100: D500FA

LDA

!0FA00H+Y

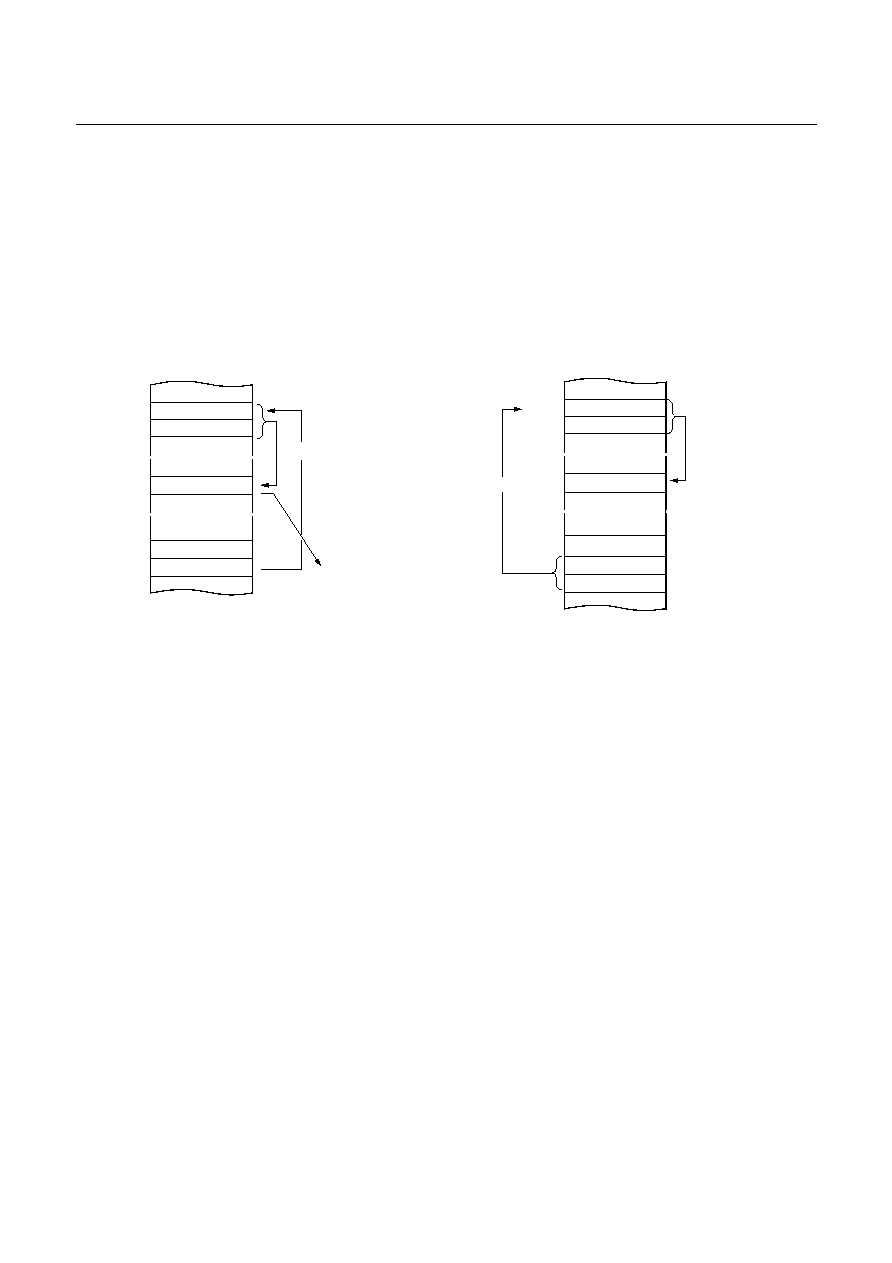

(6) Indirect Addressing

Direct page indirect

[dp]

Assigns data address to use for accomplishing command

which sets memory data(or pair memory) by Operand.

Also index can be used with Index register X,Y.

JMP, CALL

Example; G=0

FA00: 3F35

JMP

[35H]

X indexed indirect

[dp+X]

Processes memory data as Data, assigned by 16-bit pair

m e m o r y w h i c h i s d e t e r m i n e d b y p a i r d a t a

[dp+X+1][dp+X] Operand plus X-register data in Direct

page.

ADC, AND, CMP, EOR, LDA, OR, SBC, STA

Example; G=0, X=10

H

FA00: 1625

ADC

[25H+X]

D5

0F100

H

data

A

�

~

~

~

~

data

0FA55

H

0FA00H+55H=0FA55H

�

FA

0F102

H

00

0F101

H

�

0A

35

H

jump to address 0E30A

H

�

~

~

~

~

35

0FA00

H

E3

36

H

�

3F

0E30A

H

NEXT

~

~

~

~

05

35

H

0E005

H

~

~

~

~

25

0FA00

H

E0

36

H

16

0E005

H

data

~

~

~

~

�

A + data + C

A

25 + X(10) = 35

H

�

�

GMS81C4040/87C4060

HYUNDAI

28

May. 2000 Ver 1.0

Y indexed indirect

[dp]+Y

Processes momory data as Data, assigned by the data

[dp+1][dp] of 16-bit pair memory paired by Operand in Di-

rect page plus Y-register data.

ADC, AND, CMP, EOR, LDA, OR, SBC, STA

Example; G=0, Y=10

H

FA00: 1725

ADC

[25H]+Y

Absolute indirect

[!abs]

The program jumps to address specified by 16-bit absolute

address.

JMP

Example; G=0

FA00: 1F25E0

JMP

[!0C025H]

05

25

H

0E005

H

+ Y(10) = 0E015

H

�

~

~

~

~

25

0FA00

H

E0

26

H

�

17

0E015

H

data

~

~

~

~

�

A + data + C

A

25

0E025

H

jump to

~

~

~

~

E0

0FA00

H

E7

0E026

H

�

25

0E725

H

NEXT

~

~

~

~

1F

PROGRAM MEMORY

�

address 0E30A

H

HYUNDAI

GMS81C4040/87C4060

May. 2000 Ver 1.0

29

9. I/O PORTS

The GMS81C4040/GMS87C4060 has digital ports (R0,

R1, R2, R4, R5 and R6) and OSD ports (R,G,B).

These ports pins may be multiplexed with an alternate

function for the peripheral features on the device. In gen-

eral, in a initial reset state, R ports are used as a general

purpose digital port.

9.1 Registers for Port

Port Data Registers

The Port Data Registers in I/O buffer in each R ports are

represented as a Type D flip-flop, which will clock in a val-

ue from the internal bus in response to a "write to data reg-

ister" signal from the CPU. The Q output of the flip-flop is

placed on the internal bus in response to a "read data reg-

ister" signal from the CPU. The level of the port pin itself

is placed on the internal bus in response to "read data reg-

ister" signal from the CPU. Some instructions that read a

port activating the "read register" signal, and others acti-

vating the "read pin" signal

Port Direction Registers

All pins have data direction registers which can define

these ports as output or input. A "1" in the port direction

register configure the corresponding port pin as output.

Conversely, write "0" to the corresponding bit to specify it

as input pin. For example, to use the even numbered bit of

R0 as output ports and the odd numbered bits as input

ports, write "55

H

" to address 0C1

H

(R0 port direction reg-

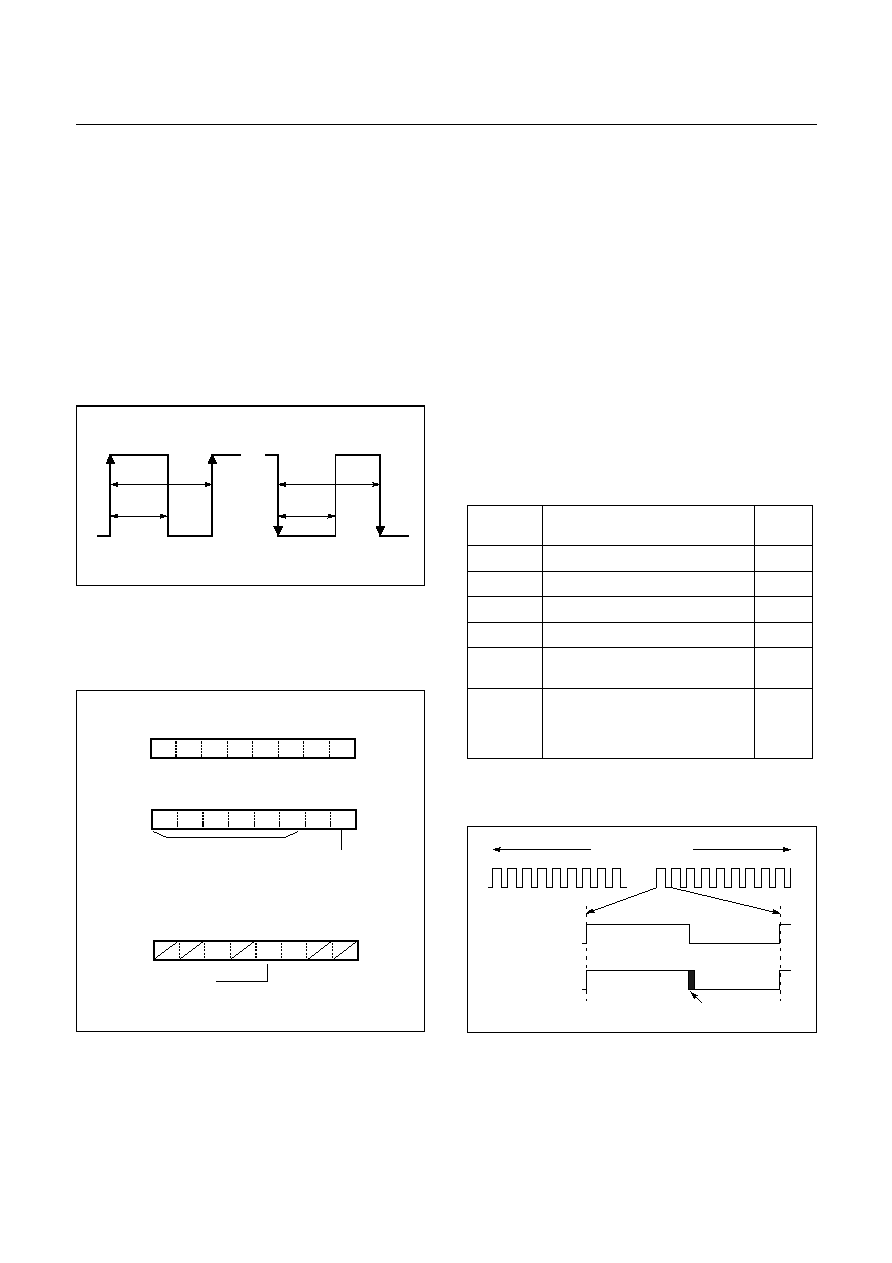

ister) during initial setting as shown in Figure 9-1 .

All the port direction registers in the GMS81C4040/

GMS87C4060 have 0 written to them by reset function. On

the other hand, its initial status is input.

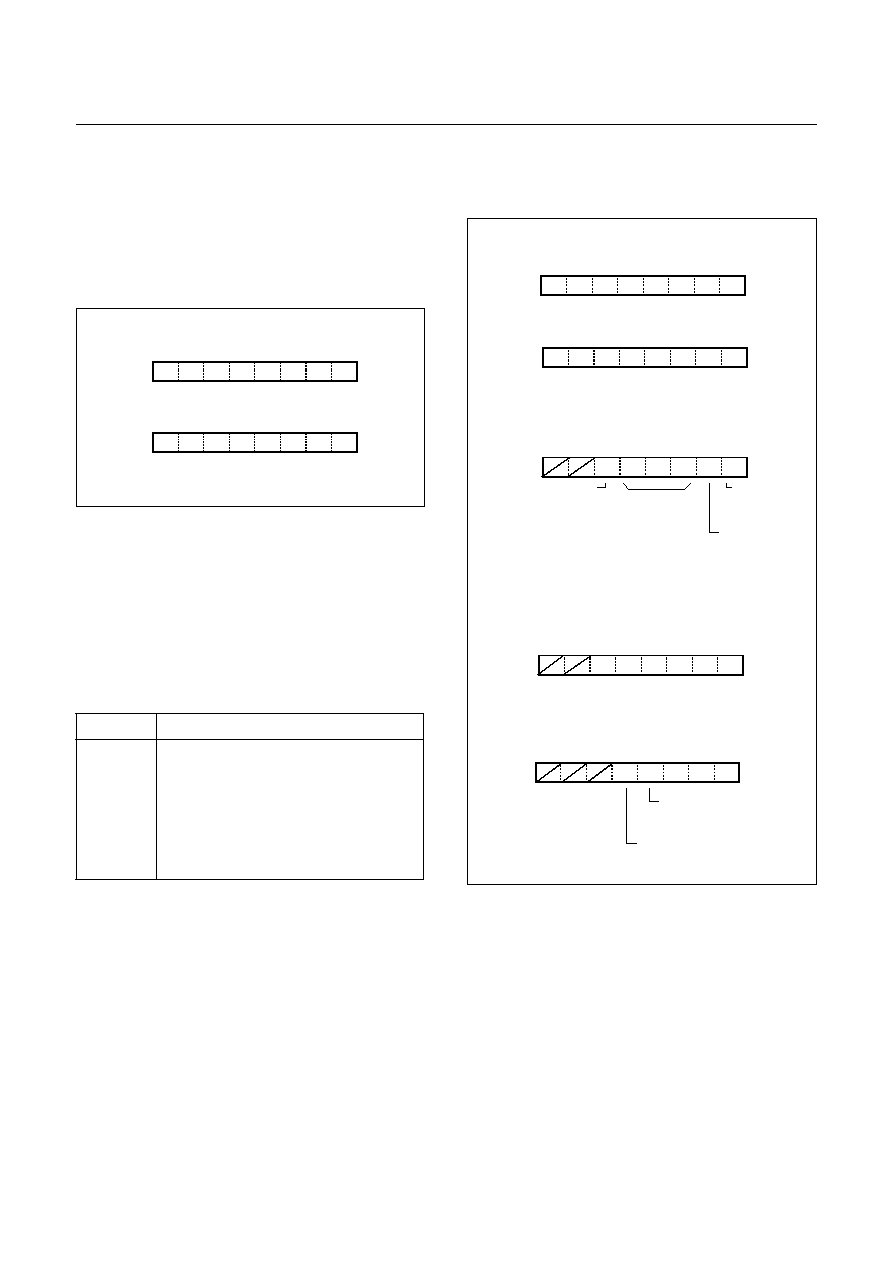

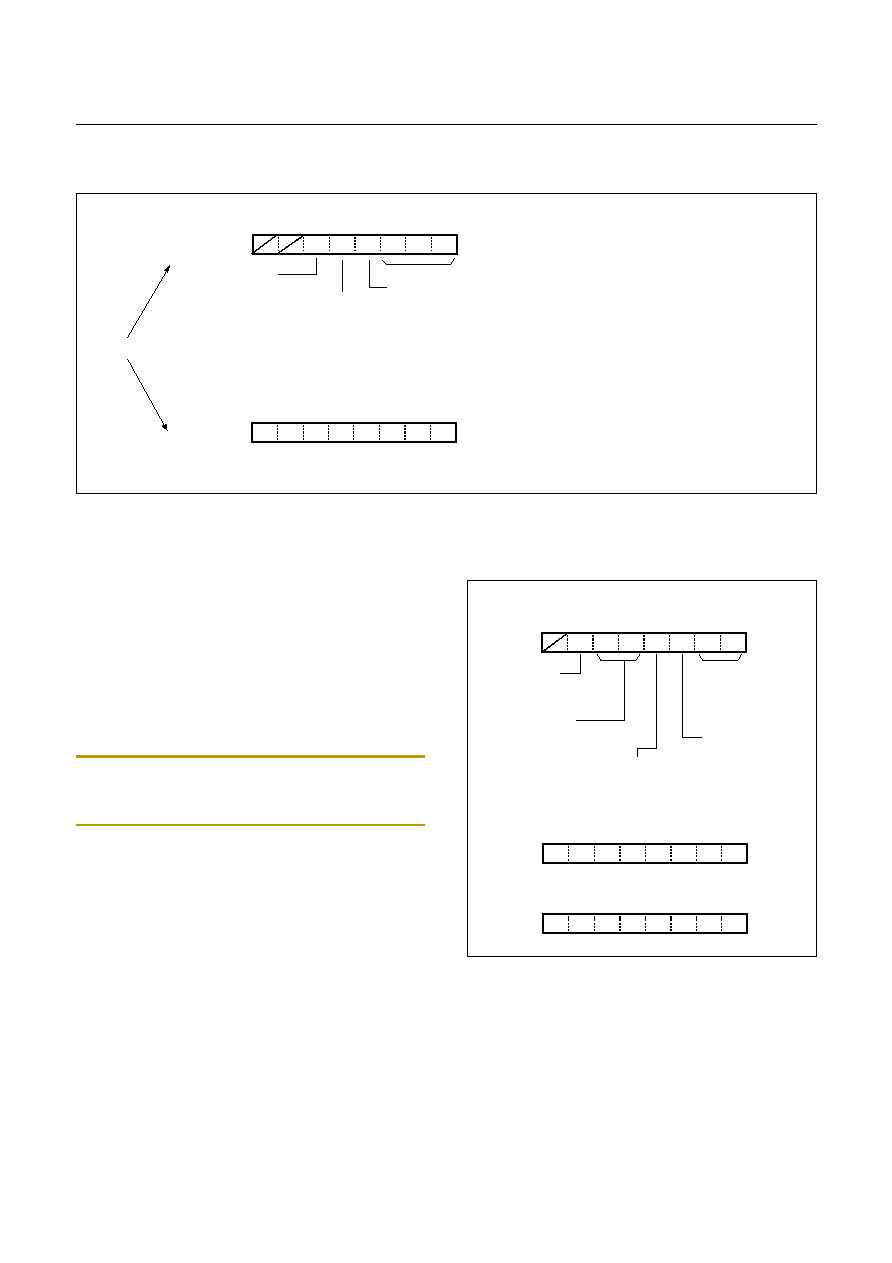

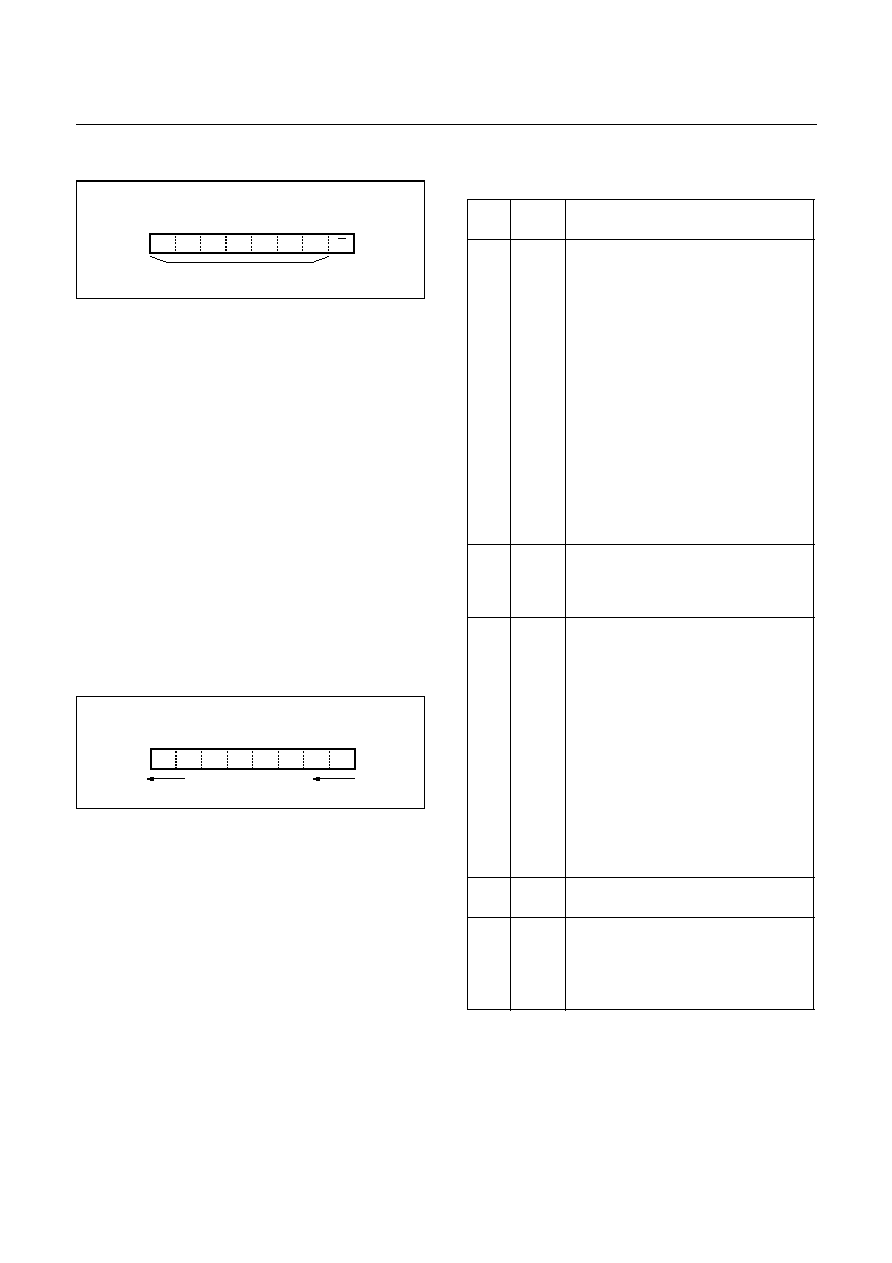

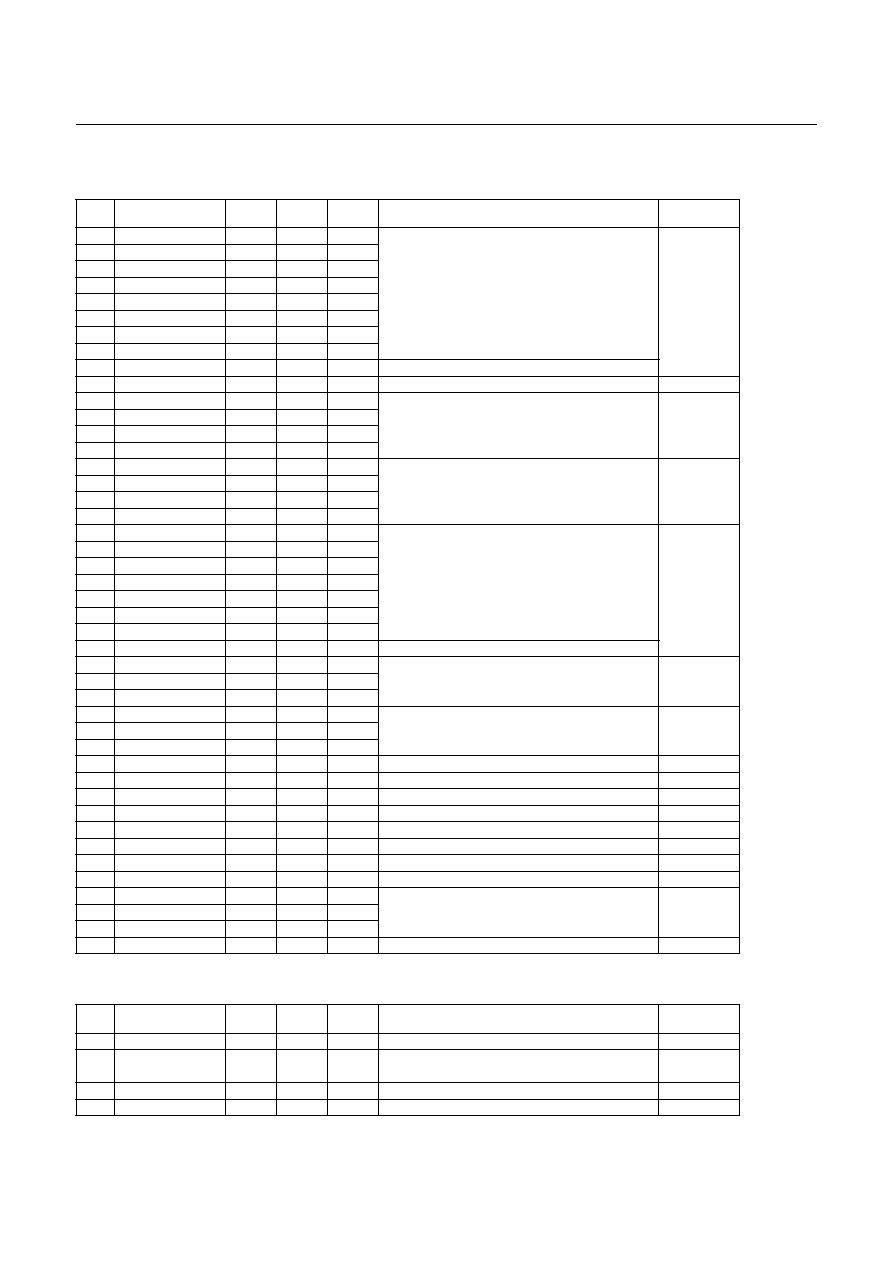

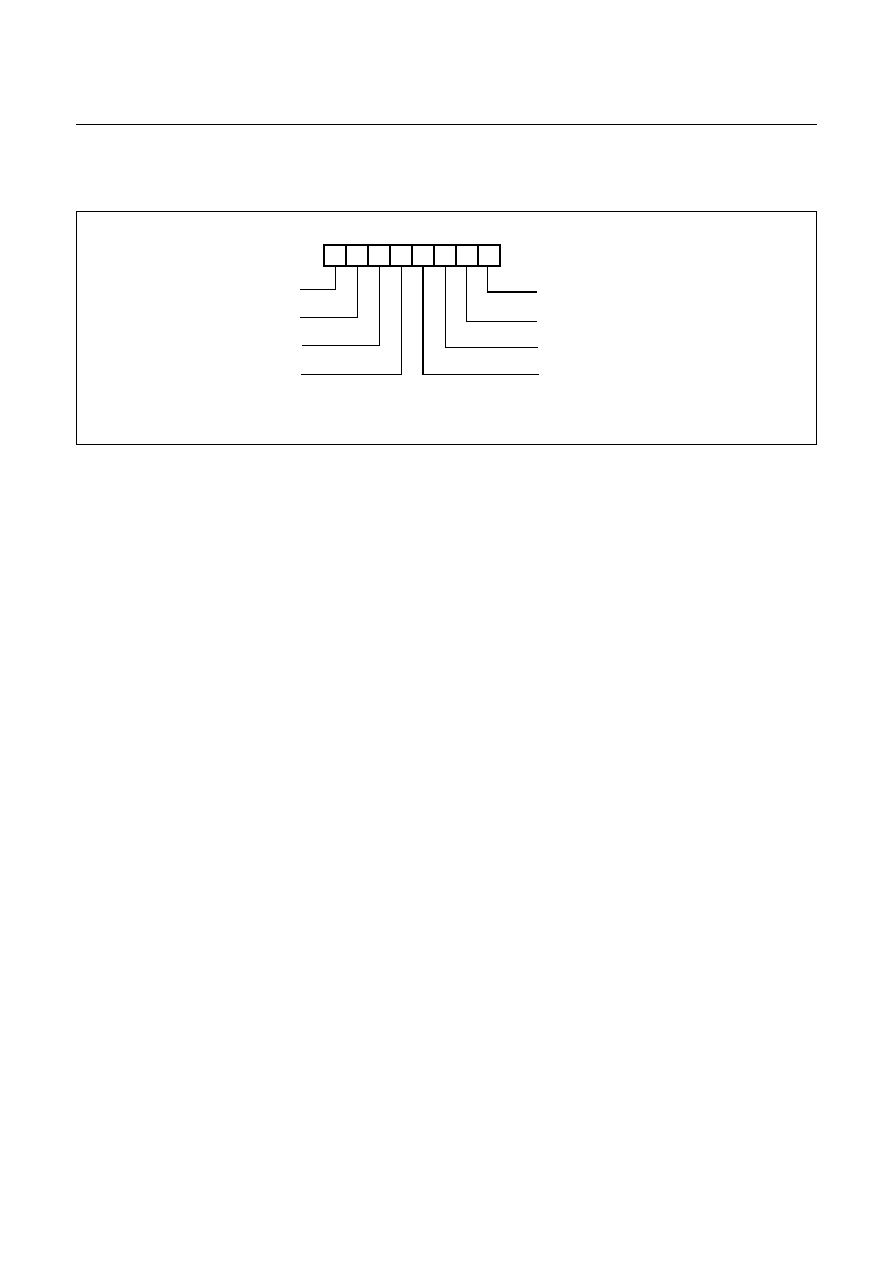

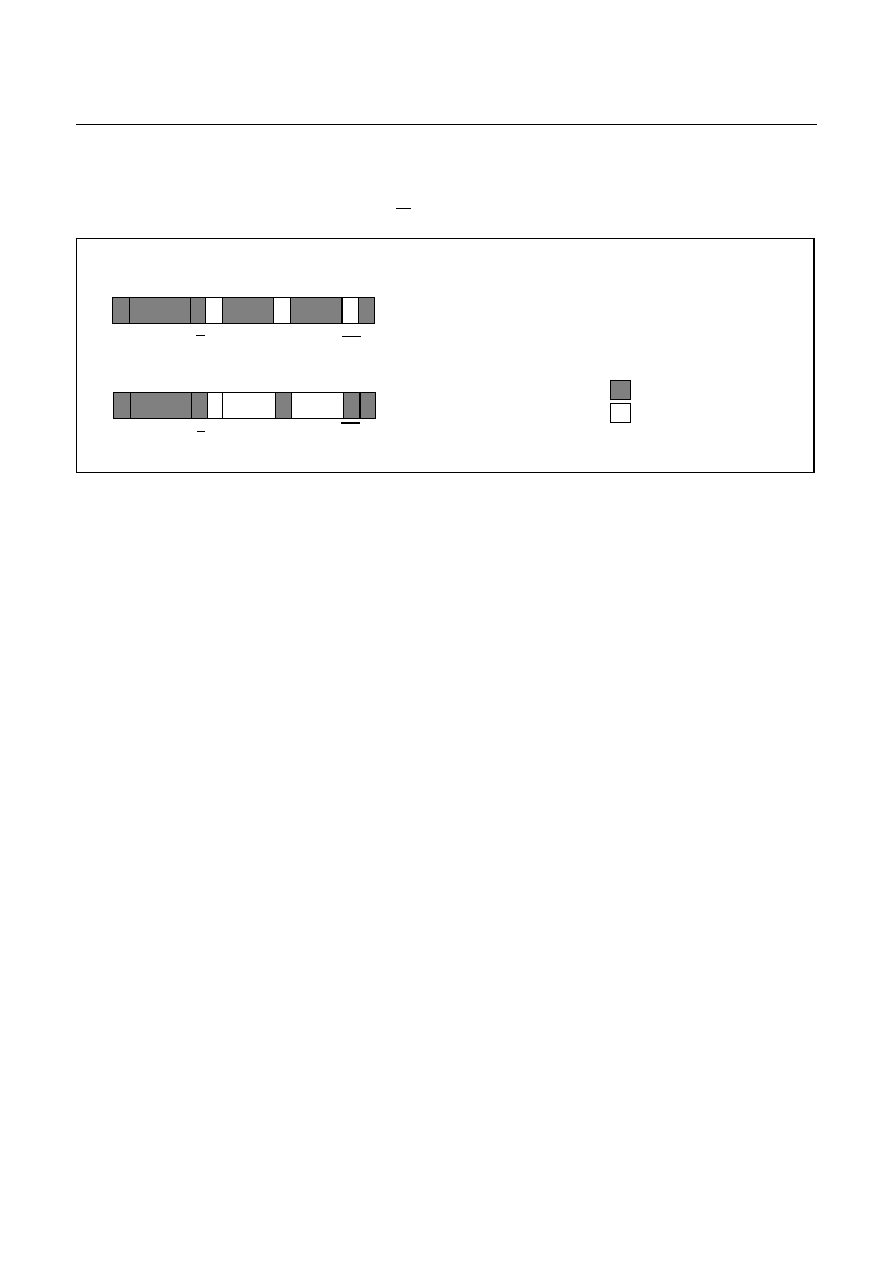

Figure 9-1 Example of port I/O assignment

I : INPUT PORT

WRITE "55

H

" TO PORT R0 DIRECTION REGISTER

0

1

0

1

0

1

0

1

I

O

I

O

I

O

I

O

R0 DATA

R4 DATA

R0 DIRECTION

R4 DIRECTION

0C0H

0C1H

0C8H

0C9H

7

6

5

4

3

2

1

0

BIT

7

6

5

4

3

2

1

0

PORT

O : OUTPUT PORT

~

~

~

~

GMS81C4040/87C4060

HYUNDAI

30

May. 2000 Ver 1.0

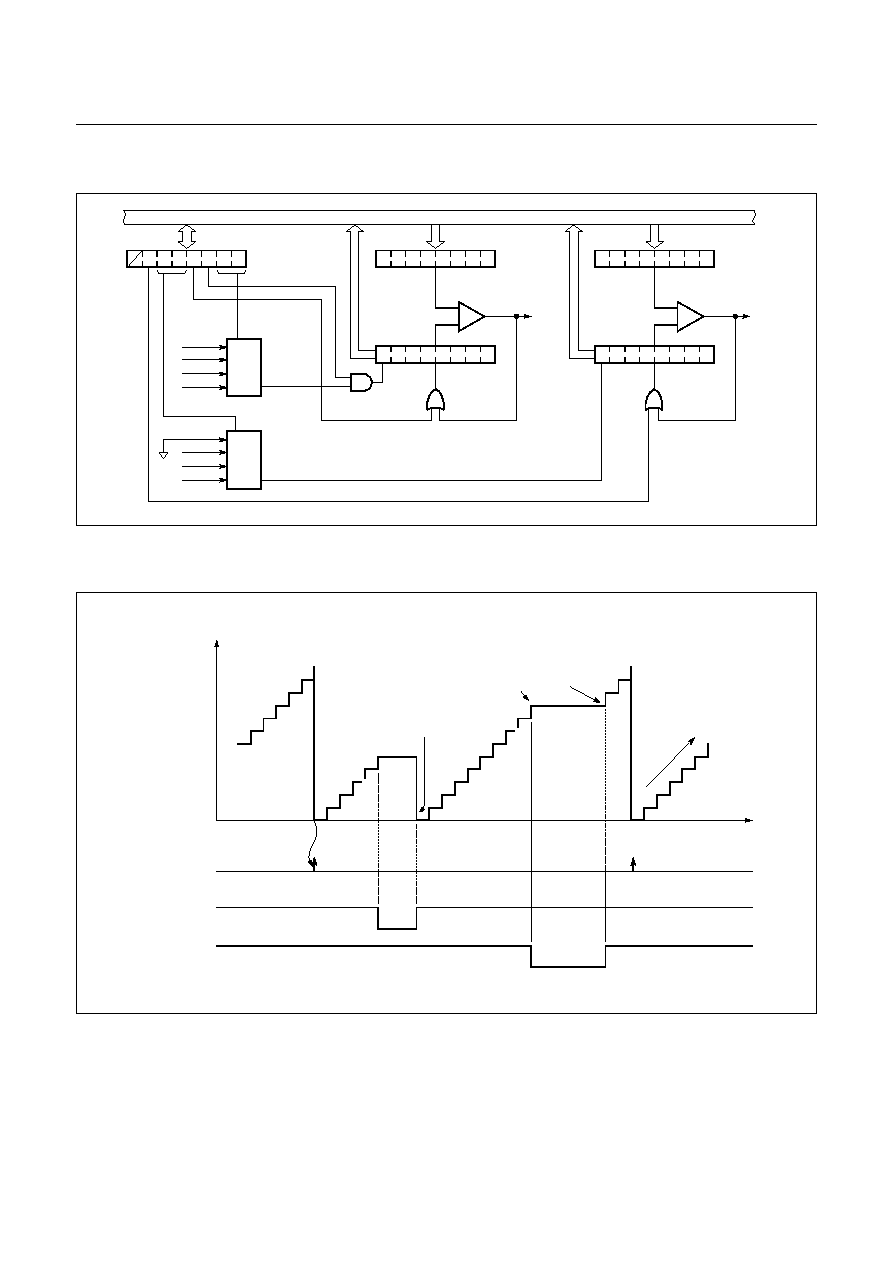

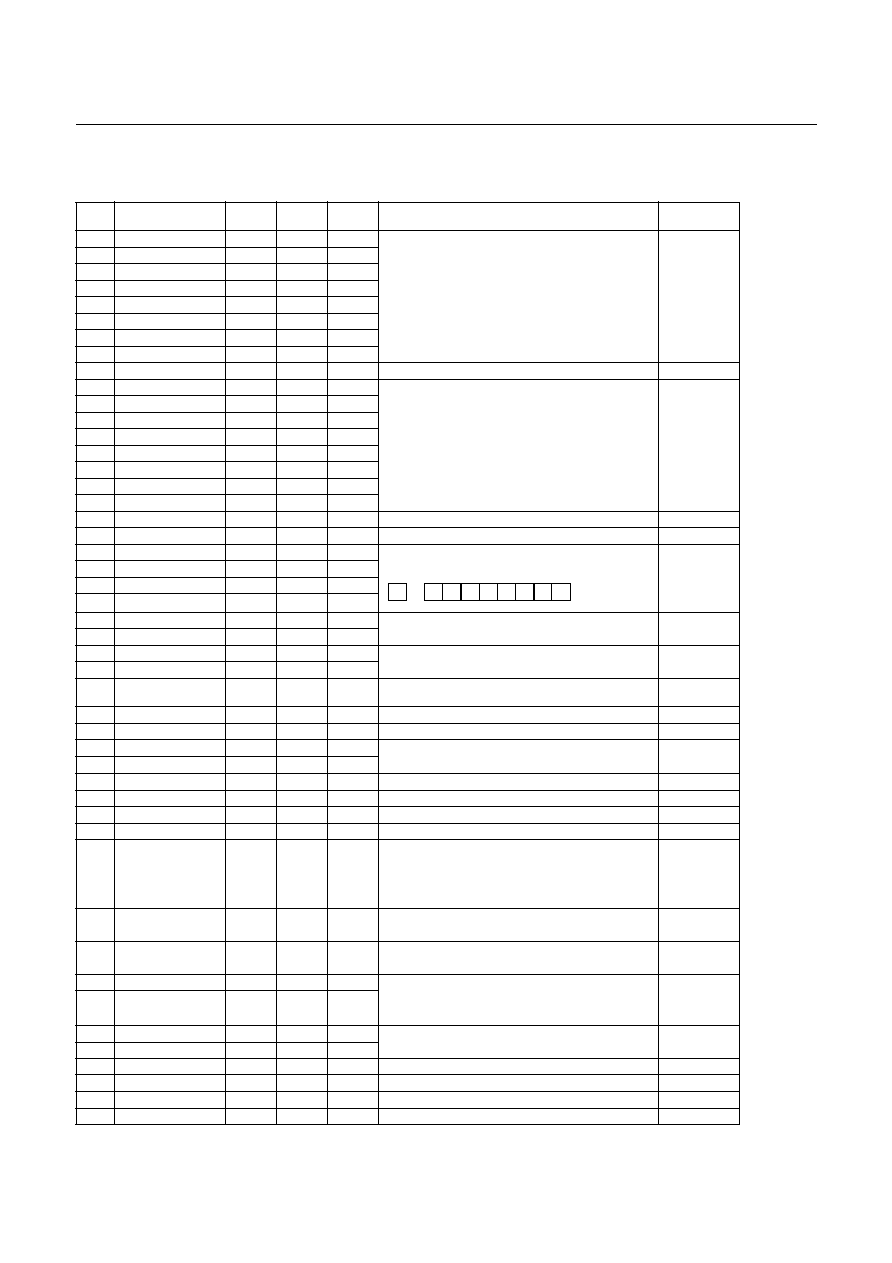

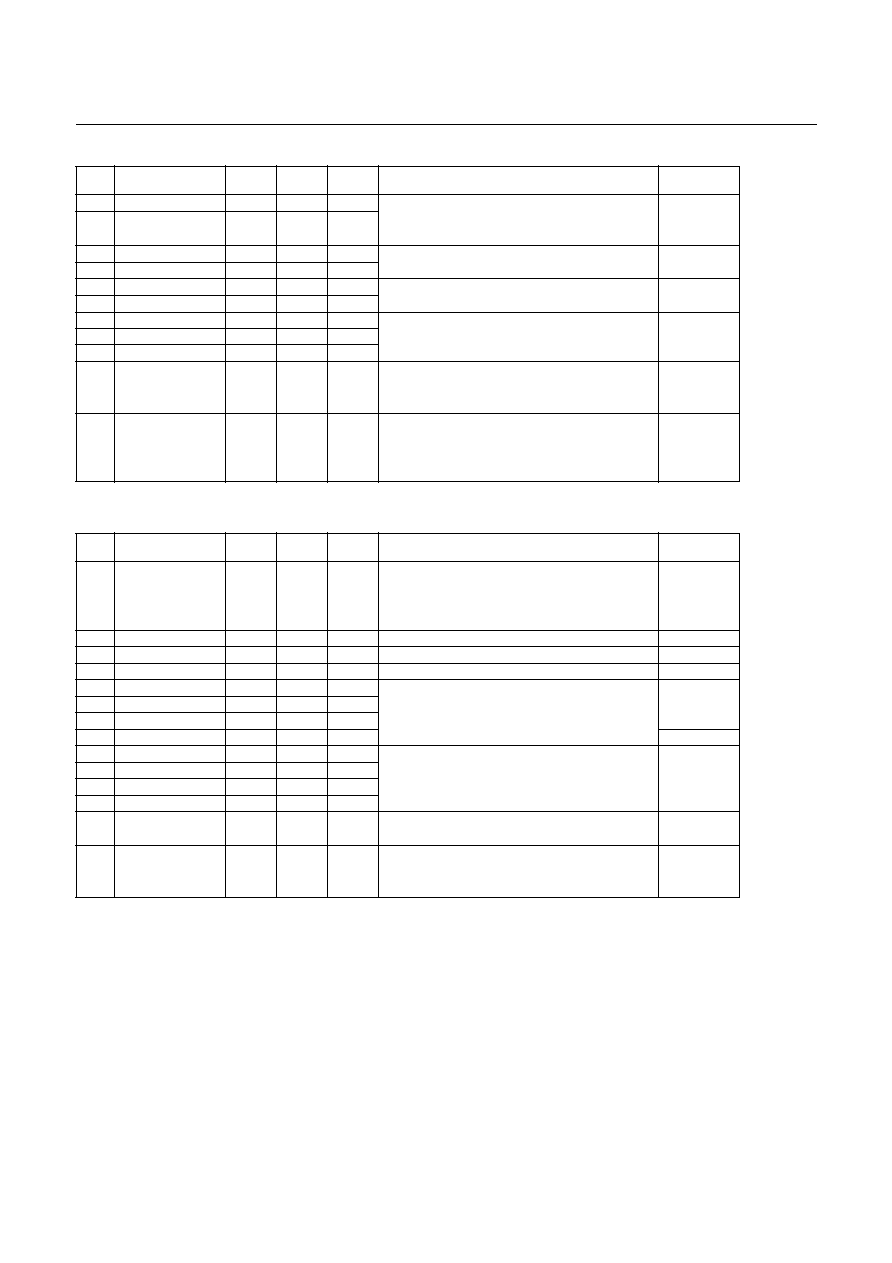

9.2 I/O Ports Configuration

R0 Ports

R0 is an 8-bit CMOS bidirectional I/O port (address

0C0

H

). Each I/O pin can independently used as an input or

an output through the R0DD register (address 0C1

H

).

The control registers for R0 are shown below.

In addition, Port R0 is only digital I/O. After reset, R0DD

value is "0", R0 acts as normal digital input port.

R1 Ports

R1 is an 8-bit CMOS bidirectional I/O port (address

0C2

H

). Each I/O pin can independently used as an input or

an output through the R1DD register (address 0C3

H

).

R1 port have secondary functions as following table.

The control registers for R1 are shown below.

Port R1 is multiplexed with various special features.The

control registers controls the selection of alternate func-

tion. After reset, R1 port acts as normal digital input port.

The way to select alternate function such as A/D input or

HD,VD will be shown in each peripheral section.

Port Pin

Alternate Function

R10

R11

R12

R13

R14

R15

R16

R17

AN0 (A/D input 0)

AN1 (A/D input 1)

AN2 (A/D input 2)

AN3 (A/D input 3)

AN4 (A/D input 4)

AN5 (A/D input 5)

VD (Vertical Sync. input)

HD (Horizontal Sync. input)

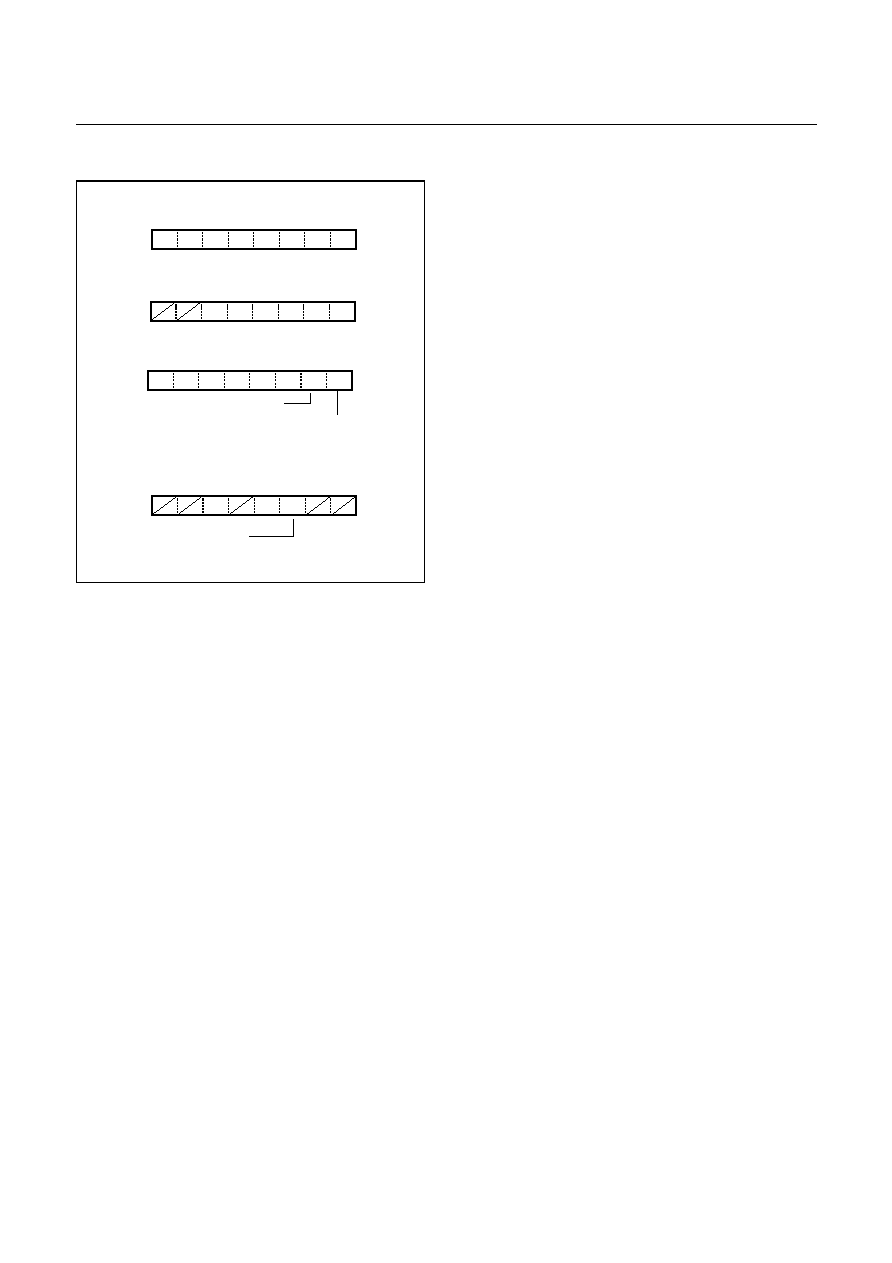

R0 Data Register

R0

ADDRESS : 00C0

H

RESET VALUE : Undefined

R07

R06

R05

R04

R03

R02

R01

R00

Port Direction

R0 Direction Register

R0DD

ADDRESS : 00C1

H

RESET VALUE : 0000 0000

b

0: Input

1: Output

RW

RW

RW

RW

RW

RW

RW

RW

W

W

W

W

W

W

W

W

R1 Data Register

R1

ADDRESS : 00C2

H

RESET VALUE : Undefined

R17

R16

R15

R14

R13

R12

R11

R10

Port Direction

R1 Direction Register

R1DD

ADDRESS : 00C3

H

RESET VALUE : 0000 0000

b

0: Input

1: Output

A/D Convertor mode Register

ADCM

ADDRESS : 00F0

H

RESET VALUE : --01 1101

b

Port Property

Analog input pin selector Register

AIPS

ADDRESS : 00EF

H

RESET VALUE : --00 0000

b

0: Digital I/O

1: Analog Input

R16/VD select

Port function select Register 2

FUNC2

ADDRESS : 00CF

H

RESET VALUE : ---0 0000

b

0: R16 I/O

1: VD Input

ADEN ADS2 ADS1 ADS0 ADST ADSF

HDS

VDS

YMS

YSS

IS

A/D Status

0: Busy

1: Finish

A/D Start

0: Ignore

1: A/D start

A/D Port select

000: AN0

001: AN1

A/D Enable

0: Disable

1: Enable

010: AN2

011: AN3

100: AN4

101: AN5

110: AN6

111: No Analog port

R17/HD select

0: R17 I/O

1: HD Input

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

R

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

HYUNDAI

GMS81C4040/87C4060

May. 2000 Ver 1.0

31

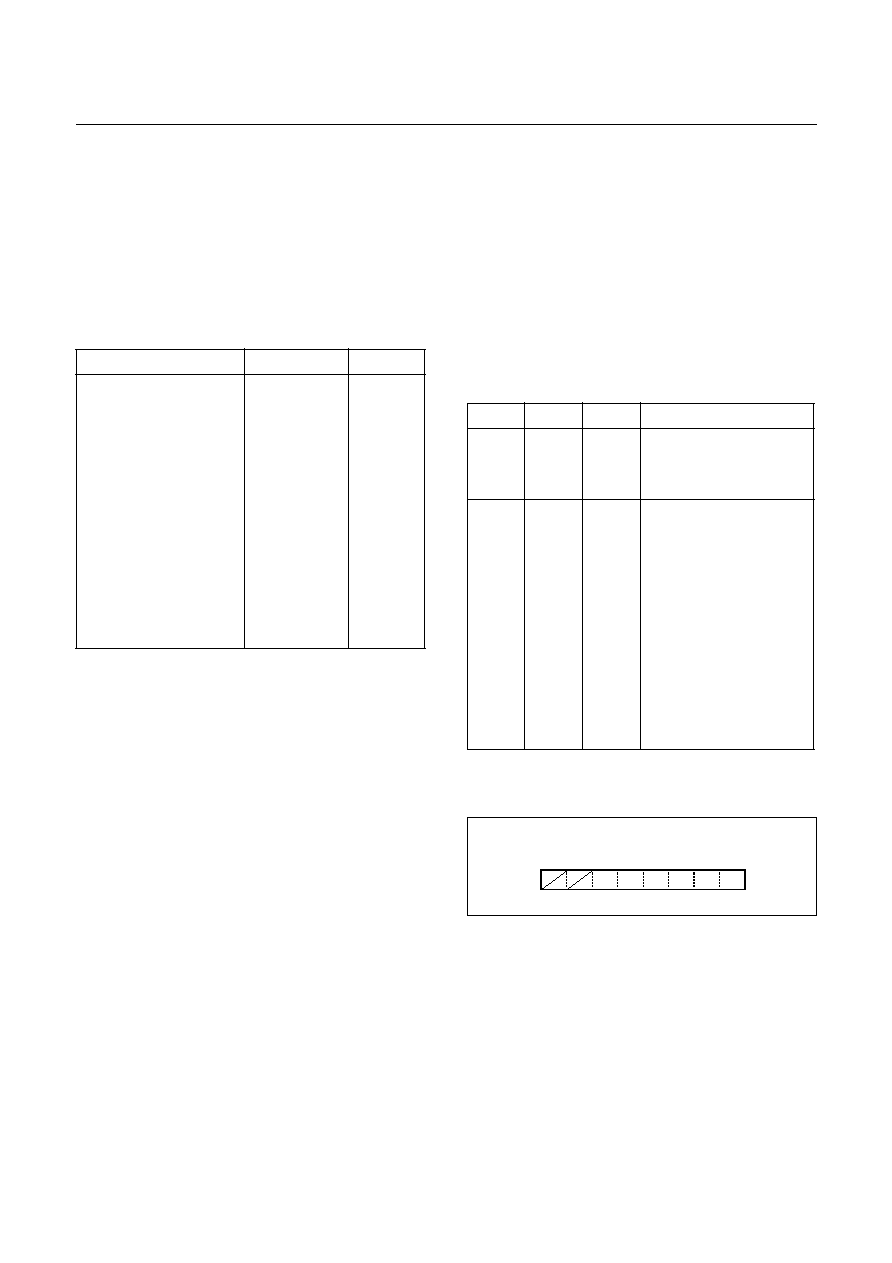

R2 Port

R2 is an 8-bit CMOS bidirectional I/O port (address

0C4

H

). Each I/O pin can independently used as an input or

an output through the R2DD register (address 00C5

H

).

The control registers for R2 are shown below.

R4 Port

R4 is consrutced with 4-bit Open drain Output port and 4-

bit CMOS bidirectional I/O port (address 0C8

H

). Each I/O

pin can independently used as an input or an output

through the R4DD register (address 0C9

H

).

The control registers for R4 are shown below.

R2 Data Register

R2

ADDRESS : 00C4

H

RESET VALUE : Undefined

R27

R26

R25

R24

R23

R22

R21

R20

Port Direction

R2 Direction Register

R2DD

ADDRESS : 00C5

H

RESET VALUE : 0000 0000

b

0: Input

1: Output

Serial I/O mode Register

SIOM

ADDRESS : 00DE

H

RESET VALUE : -000 0001

b

00: Ignore edge

Ext. interrupt edge selection Register

IEDS

ADDRESS : 00F2

H

RESET VALUE : --00 0000

b

01: Falling edge

10: Rising edge

R20/INT2

Port function select Register 1

FUNC1

ADDRESS : 00CE

H

RESET VALUE : -000 0000

b

0: R20

1: INT2

SM1

SM0

SCK1 SCK0 SIOST SIOSF

INT4S INT3S INT2S INT1S INT0S

Seriial Status

0: Busy

1: Finish

Serial Start

0: Ignore

1: Serial start

Clock select

00: PS3

01: PS4

Serial I/O

0: Serial In

1: Serial Out

10: PS5

11: External

IOSW

EC2S

EC3S

SM1

0

0

1

1

SM0

0

1

0

1

Mode

-

Send

Receive

-

R21

R21

Sclk

Sclk

R21

R22

R22

Sout

R22

R22

R23

R23

R23

Sin

R23

R24/INT3

0: R24

1: INT3

R26/INT4

0: R26

1: INT4

R27/EC3

0: R27

1: EC3

R25/EC2

0: R25

1: EC2

IED2H IED2L

IED1H IED1L IED0H IED0L

11: Falling/Rising edge

INT2

RW

RW

RW

RW

RW

RW

RW

RW

W

W

W

W

W

W

W

W

RW

RW

RW

RW

RW

RW

R

W

W

W

W

W

W

W

W

W

W

W

W

W

R4 Data Register

R4

ADDRESS : 00C8

H

RESET VALUE : Undefined

R47

R46

R45

R44

R43

R42

R41

R40

Port Direction

R4 Direction Register

R4DD

ADDRESS : 00C9

H

RESET VALUE : 0000 ----

b

0: Input

1: Output

I

2

C Control Register 1

ICCR1

ADDRESS : 00DB

H

RESET VALUE : 00-0 0000

b

EN5,4,3,2,1 : R47,45,43,42,41,40

PWM control Register 1

PWMCR1

ADDRESS : 00EA

H

RESET VALUE : 0000 0000

b

0: R4x acts normal digital port

1: R4x acts PWM output port

ALS

ESO

BC2

BC1

BC0

EN2

EN1

EN0

EN8

CNT

Bit count

000

b

(8bit)

I

2

C enable

0: Disable

1: Enable

BSW0

EN3

EN4

EN5

BSW1

0

0

1

1

BSW0

0

1

0

1

R44

R44

SCL0

R44

SCL

R45

R45/PWM4

R45/PWM4

SCL1

SCL

R46

R46

SDA0

R46

SDA

BSW1

001

b

~111

b

(1~7bit)

R47

R47/PWM5

R47/PWM5

SDA1

SDA

Slave address identification

0: Accept (Addressing format)

1: Decline (Free data format)

RW

RW

RW

RW

RW

RW

RW

RW

W

W

W

W

W

W

W

W

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

RW

14/8bit PWM count

0: Count start

1: Count stop

R51/PWM8 select

0: R51

1: PWM8

GMS81C4040/87C4060

HYUNDAI

32

May. 2000 Ver 1.0

R5 Port

R5 is an 7-bit port (address 0CA

H

). Each I/O pin can inde-

pendently used as an input or an output through the R5DD

register (address 0CB

H

).

The control registers for R5 are shown below

R6 Port

R6 is an 1-bit CMOS bidirectional I/O port (address

0CC

H

). Each I/O pin can independently used as an input or

an output through the R6DD register (address 0CD

H

).

The control registers for R6 are shown below

R5 Data Register

R5

ADDRESS : 00CA

H

RESET VALUE : Undefined

R56

R55

R54

R53

R52

R51

R50

Port Direction

R5 Direction Register

R5DD

ADDRESS : 00CB

H

RESET VALUE : ---- 0000

b

0: Input

1: Output

00: Ignore edge

Ext. interrupt edge selection Register

IEDS

ADDRESS : 00F2

H

RESET VALUE : --00 0000

b

01: Falling edge

10: Rising edge

R52/INT0

Port function select Register 1

FUNC1

ADDRESS : 00CE

H

RESET VALUE : -000 0000

b

0: R52

1: INT0

INT4S INT3S INT2S INT1S INT0S

EC2S

EC3S

IED2H IED2L

IED1H IED1L IED0H IED0L

11: Falling/Rising edge

R56/I

Port function select Register 2

FUNC2

ADDRESS : 00CF

H

RESET VALUE : ---0 0000

b

0: R56

1: I Output

HDS

VDS

YMS

YSS

IS

R55/YS

0: R55

1: YS Output

R54/YM

0: R56

1: YM Output

PWM control Register 2

PWMCR2

ADDRESS : 00EB

H

RESET VALUE : --0- 0000

b

POL2 POL1

EN7

EN6

BUZS

INT2

R50/BUZZ

0: R50

1: BUZZ

RW

RW

RW

RW

RW

RW

RW

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

RW

RW

RW

RW

RW

W

W

W

W

W

W

R6 Data Register

R6

ADDRESS : 00CC

H

RESET VALUE : Undefined

Port Direction

R6 Direction Register

R6DD

ADDRESS : 00CD

H

RESET VALUE : 0--- ----

b

0: Input

1: Output

00: Ignore edge

Ext. interrupt edge selection Register

IEDS

ADDRESS : 00F2

H

RESET VALUE : --00 0000

b

01: Falling edge

10: Rising edge

R67/INT1

Port function select Register 1

FUNC1

ADDRESS : 00CE

H

RESET VALUE : -000 0000

b

0: R67

1: INT1

INT4S INT3S INT2S INT1S INT0S

EC2S

EC3S

IED2H IED2L

IED1H IED1L IED0H IED0L

11: Falling/Rising edge

INT1

RW

W

W

W

W

W

W

W

W

W

W

W

W

W

R67

W

HYUNDAI

GMS81C4040/87C4060

May. 2000 Ver 1.0

33

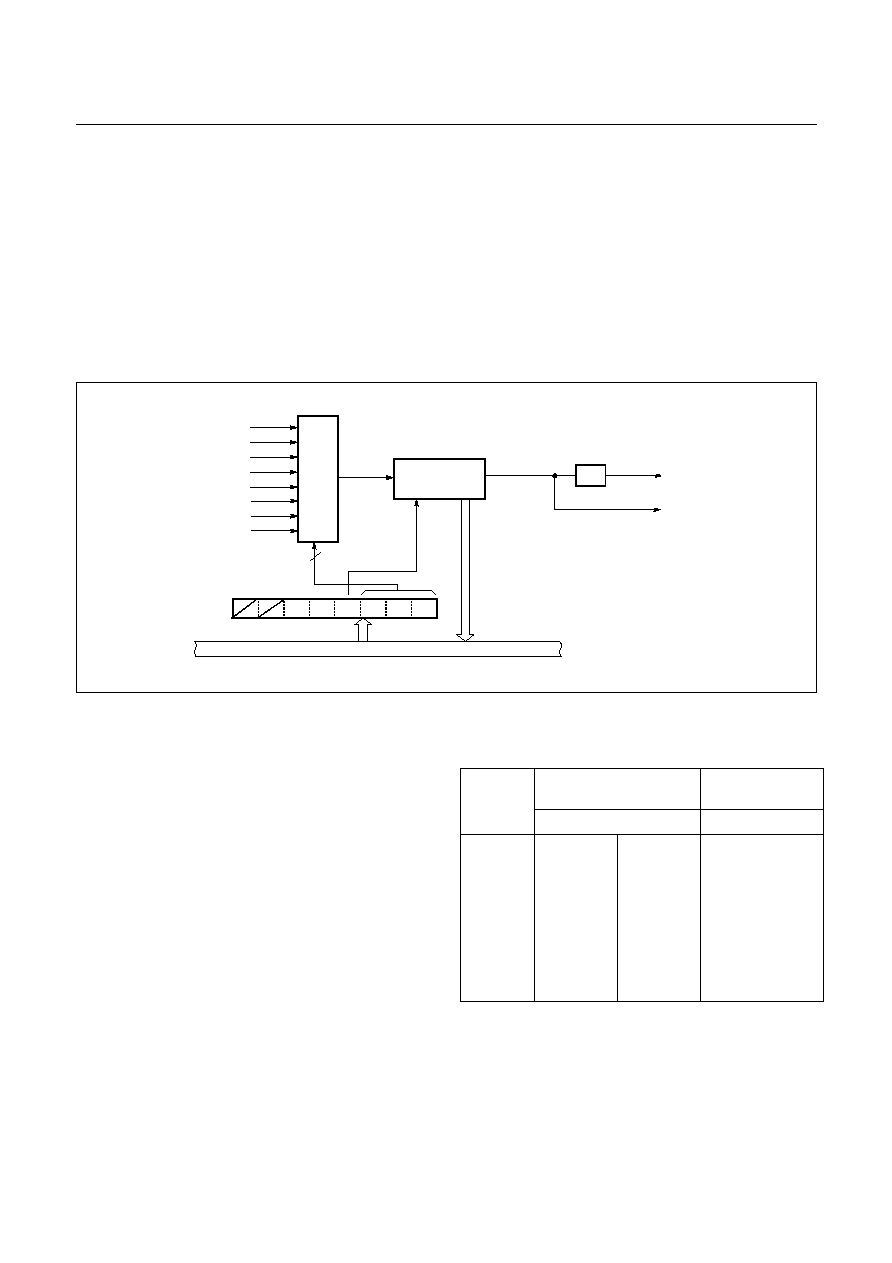

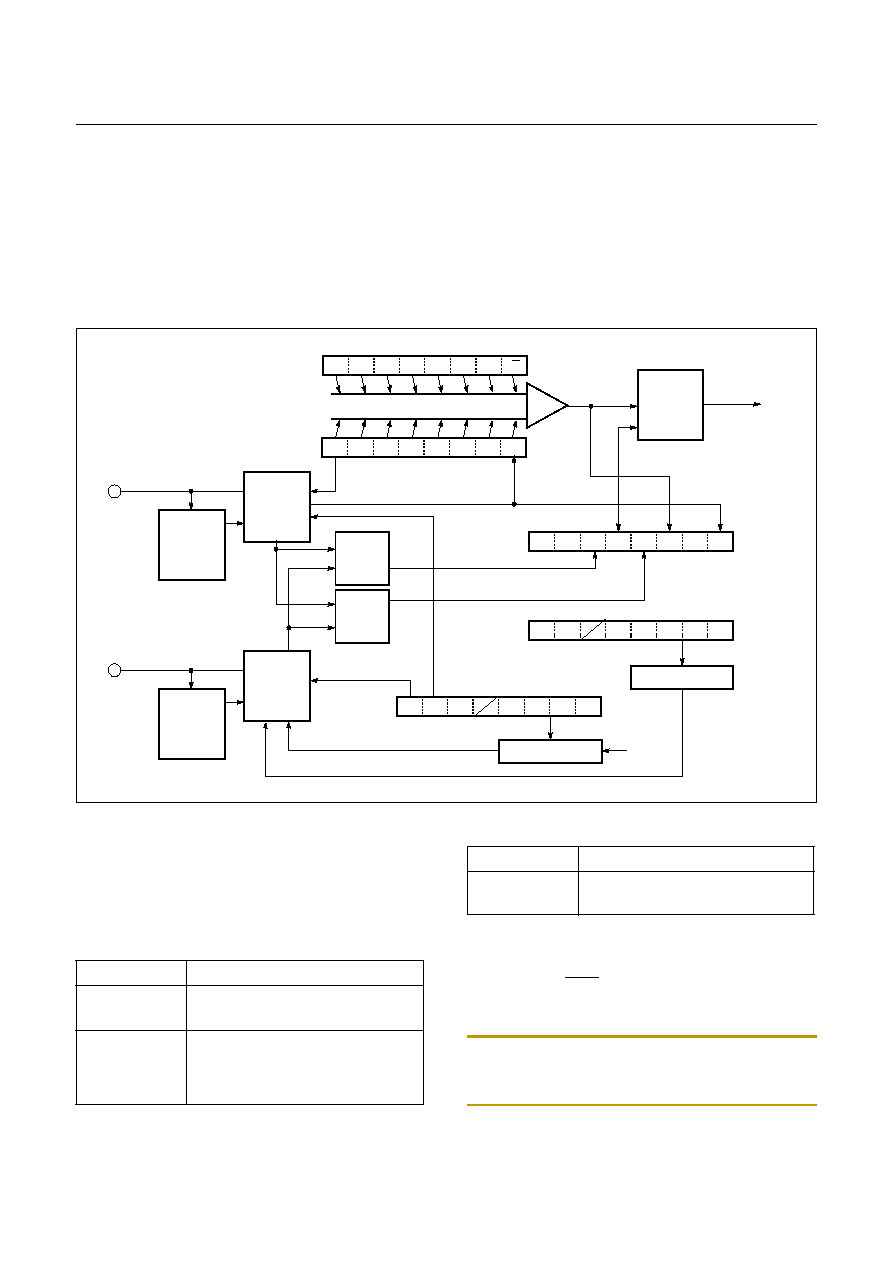

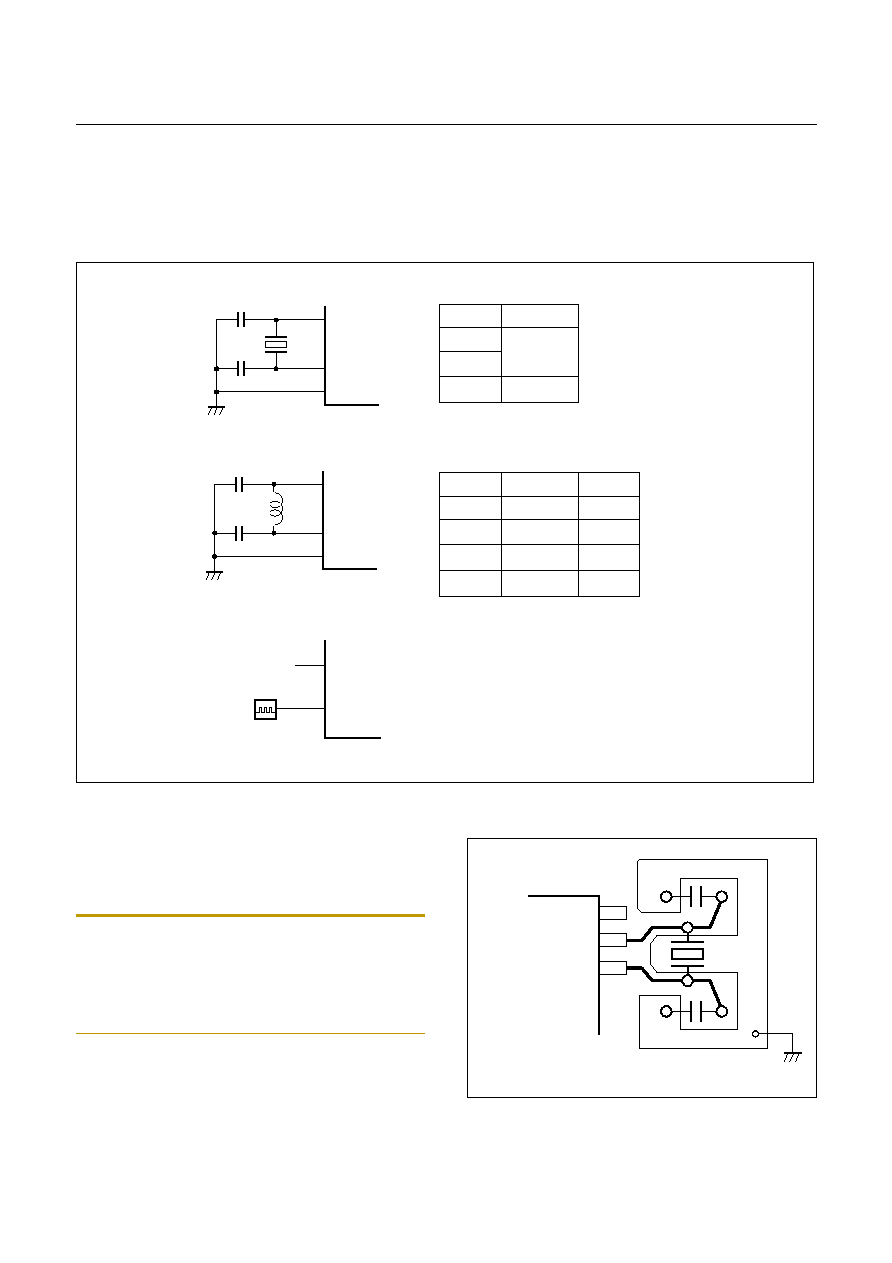

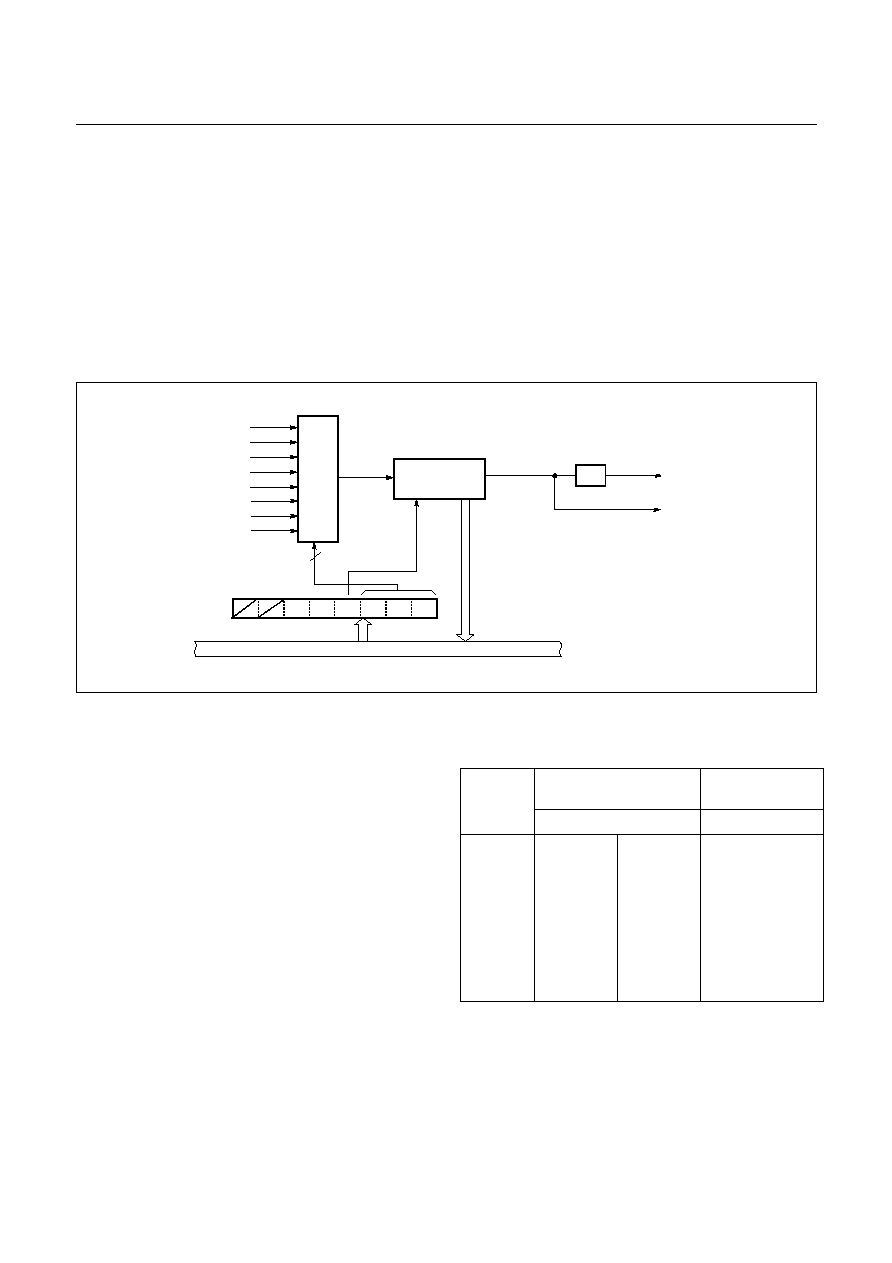

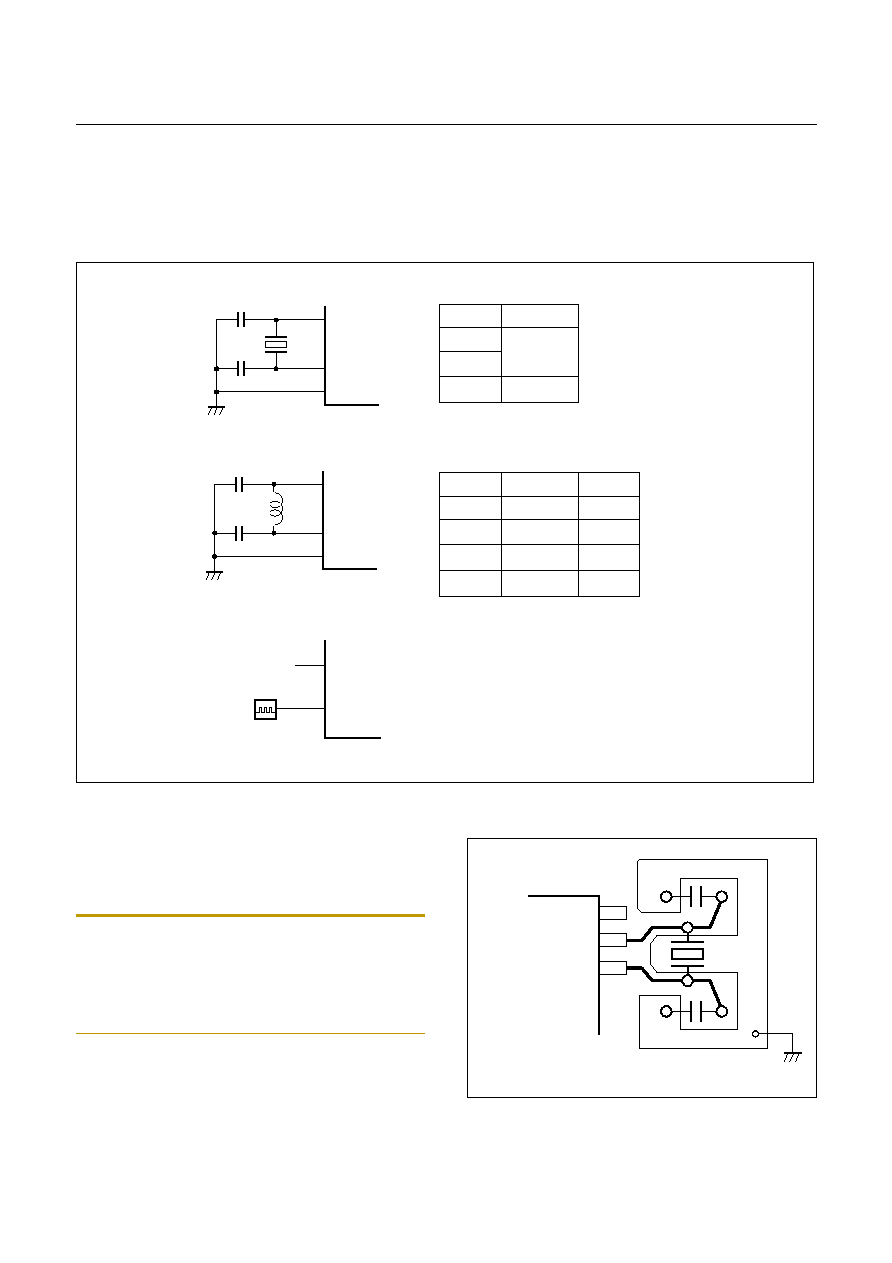

10. CLOCK GENERATOR

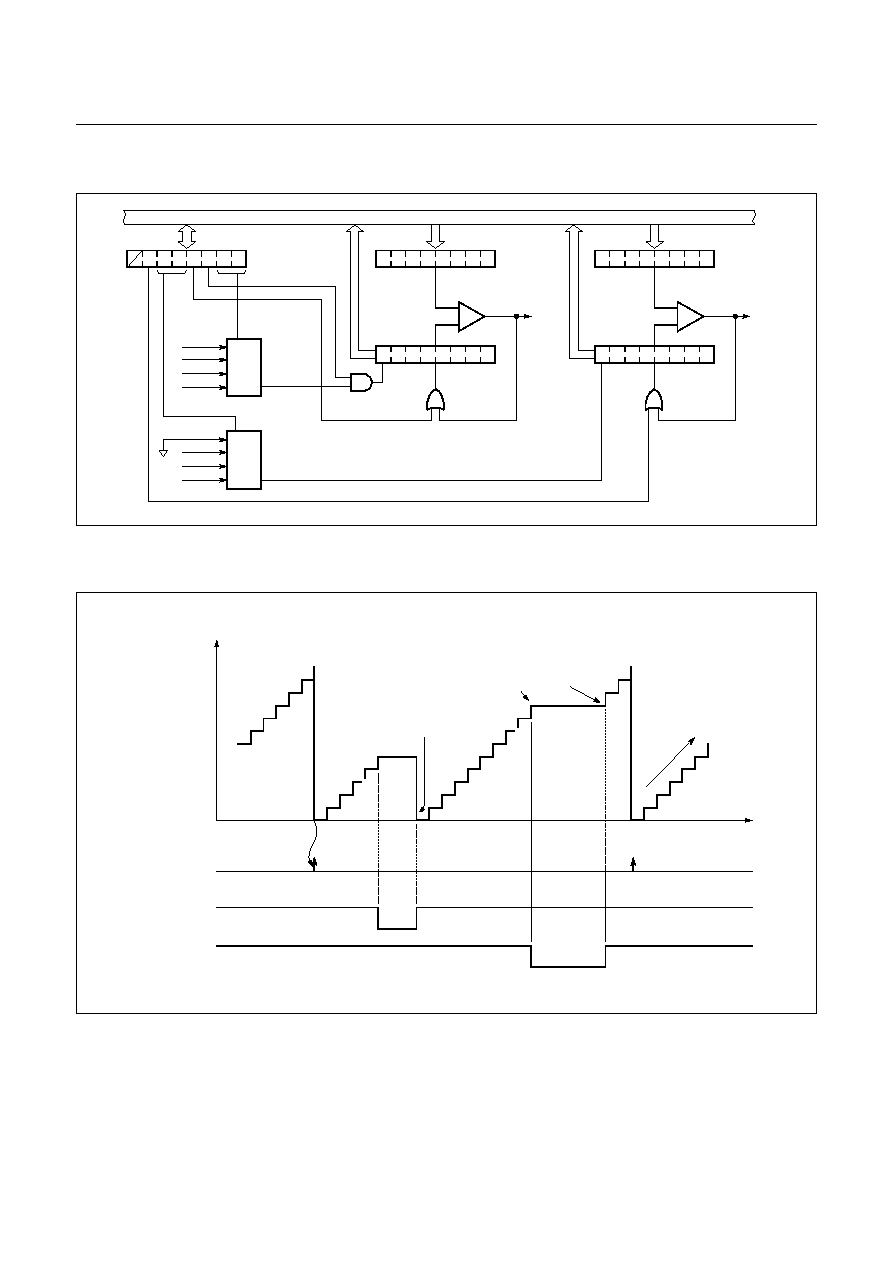

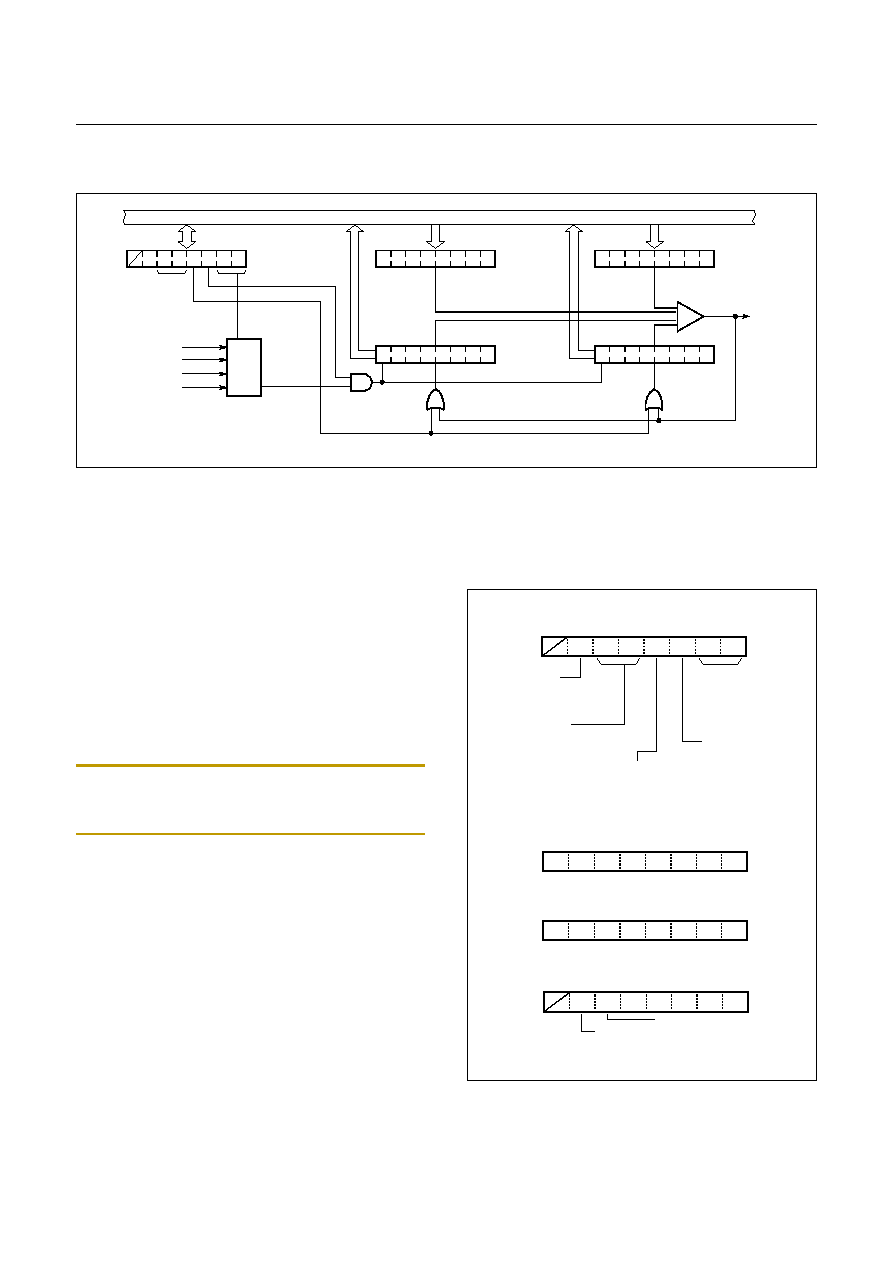

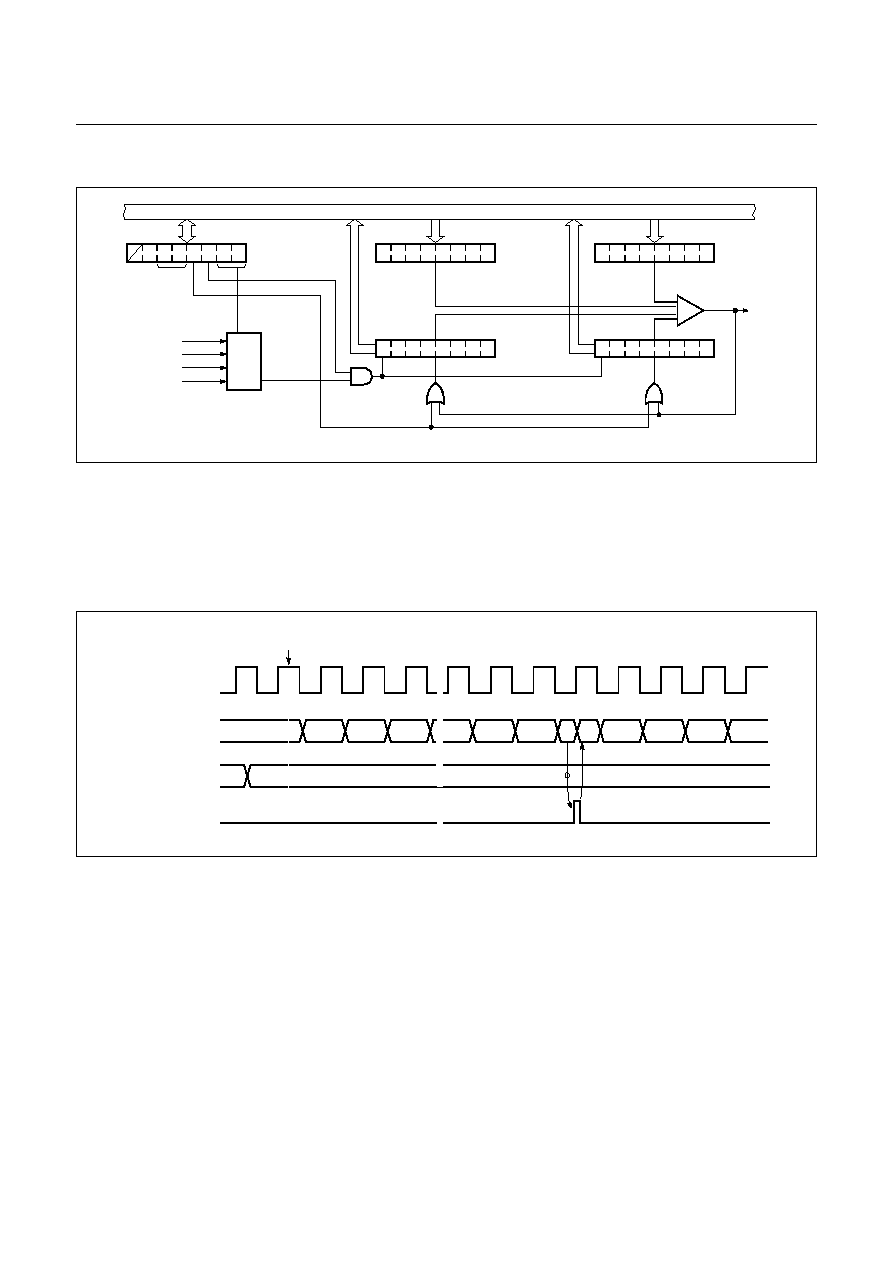

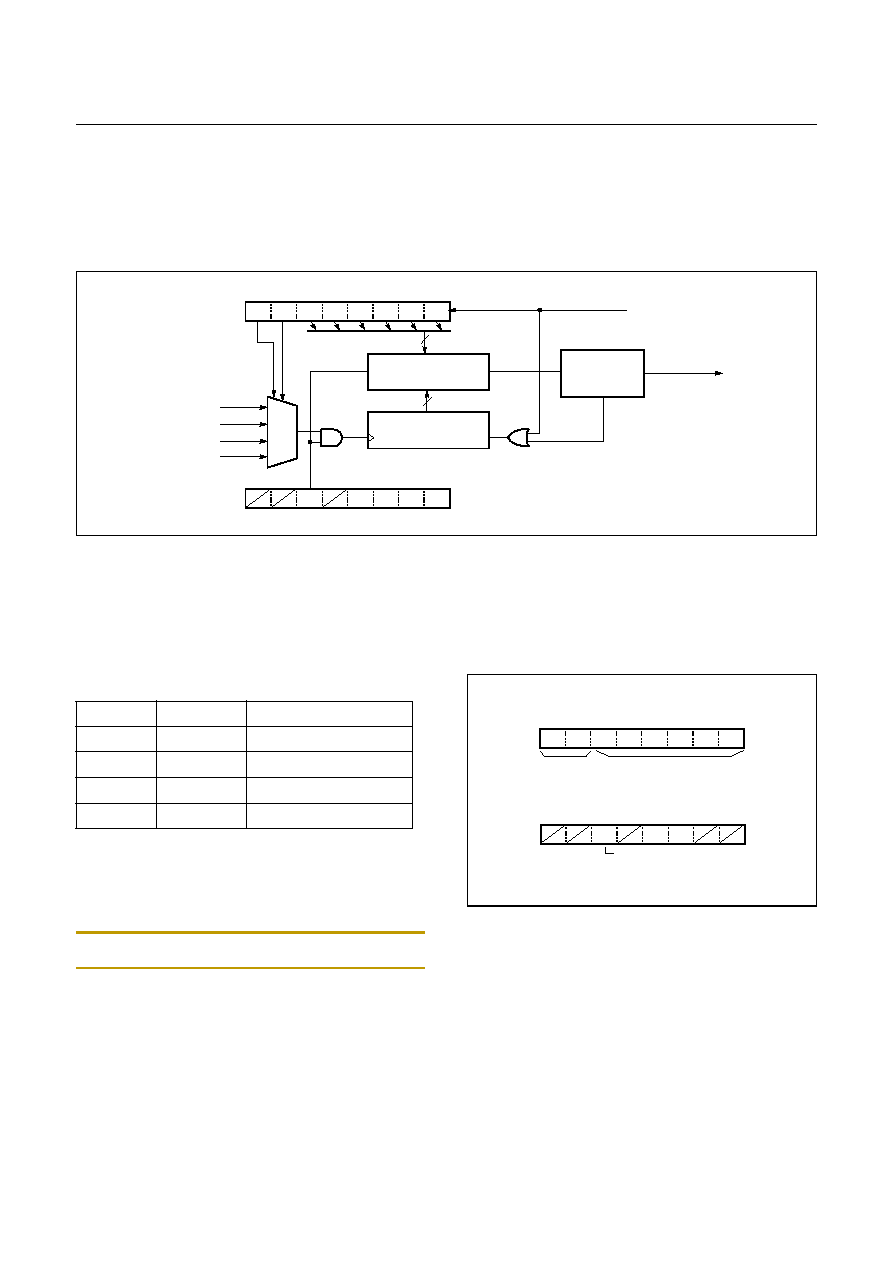

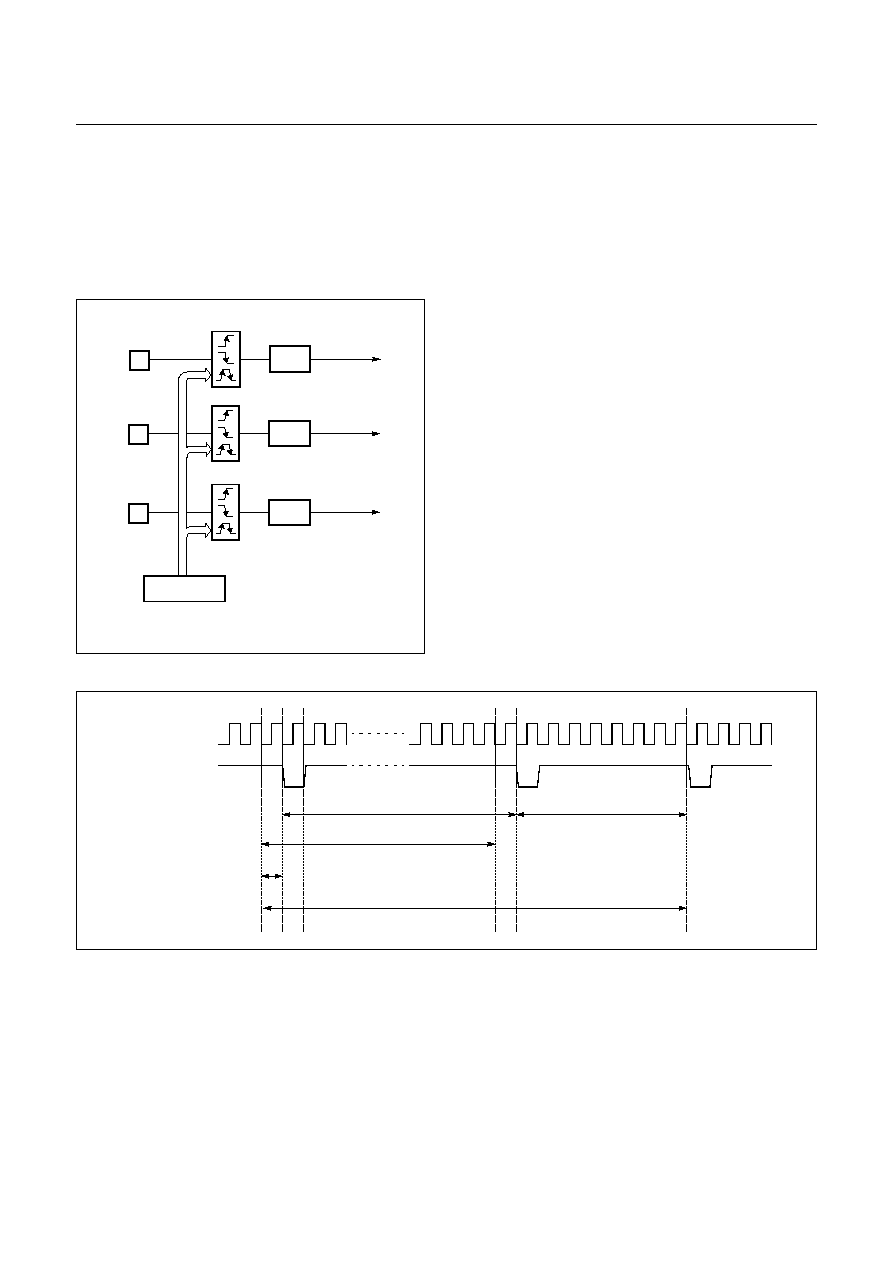

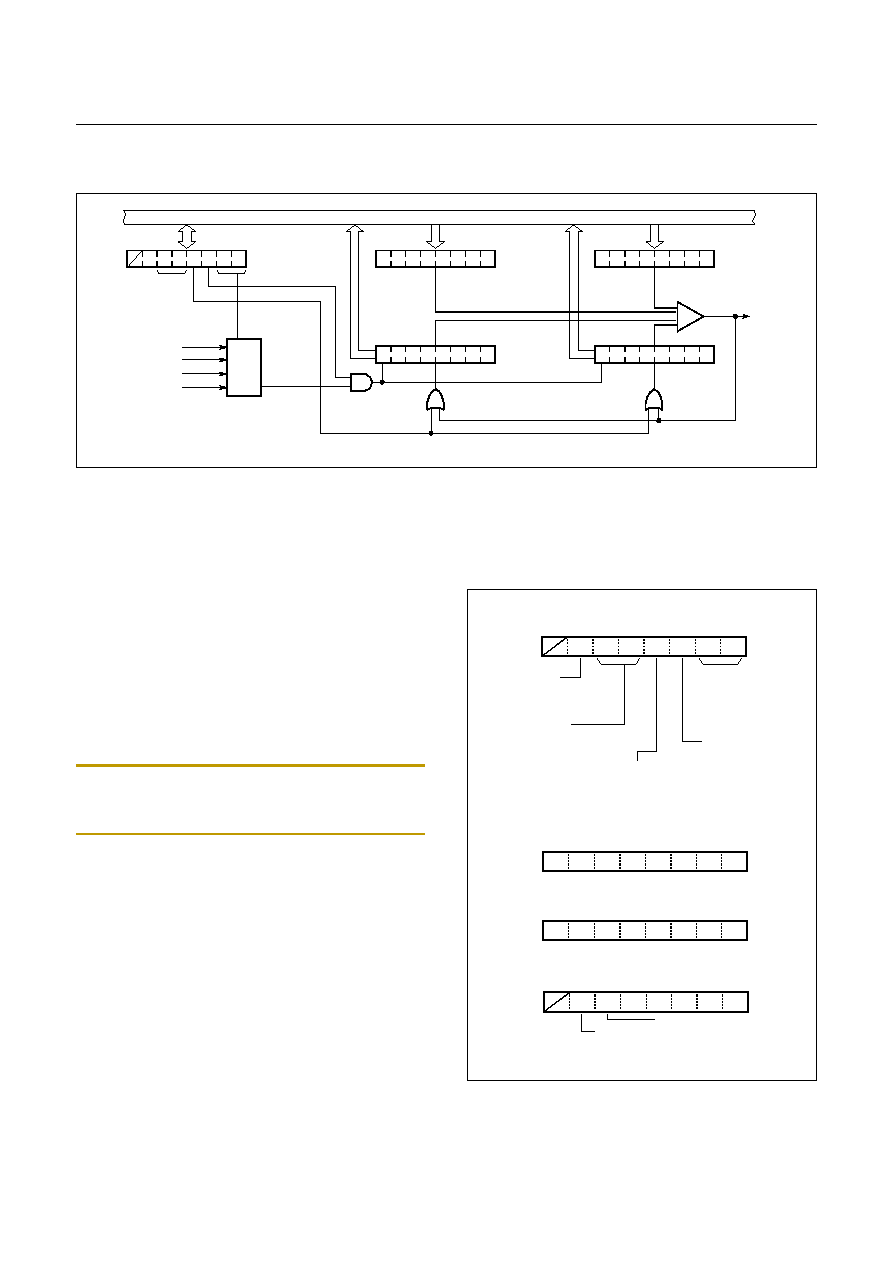

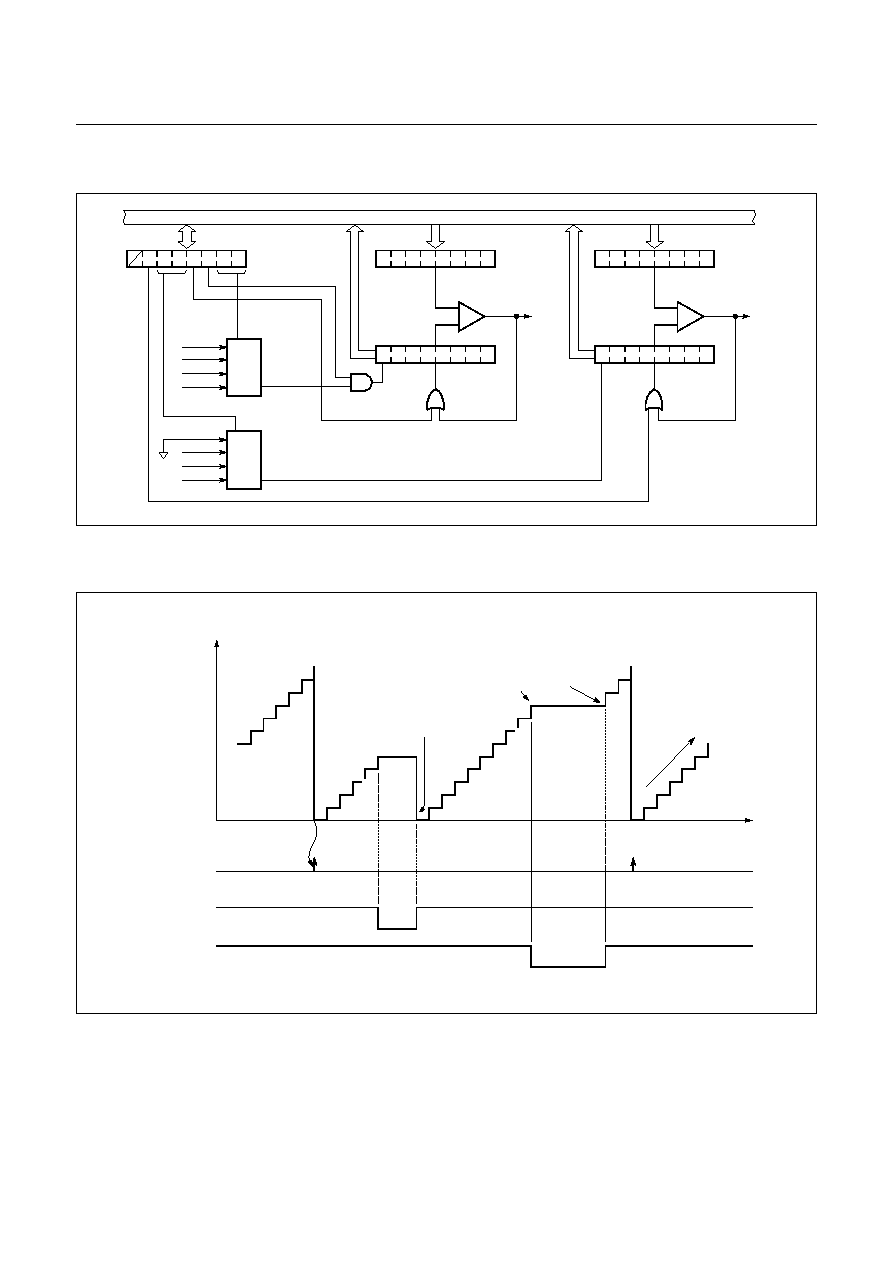

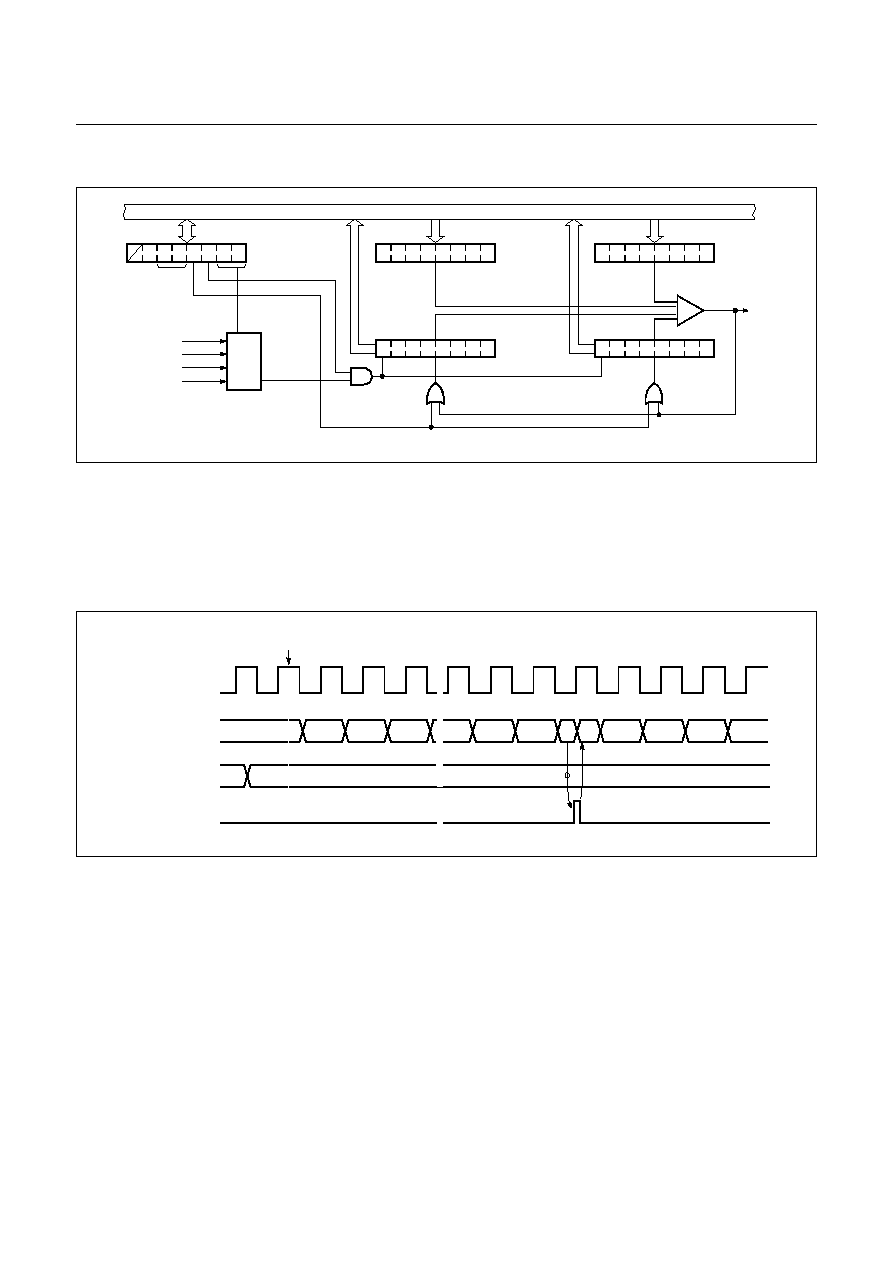

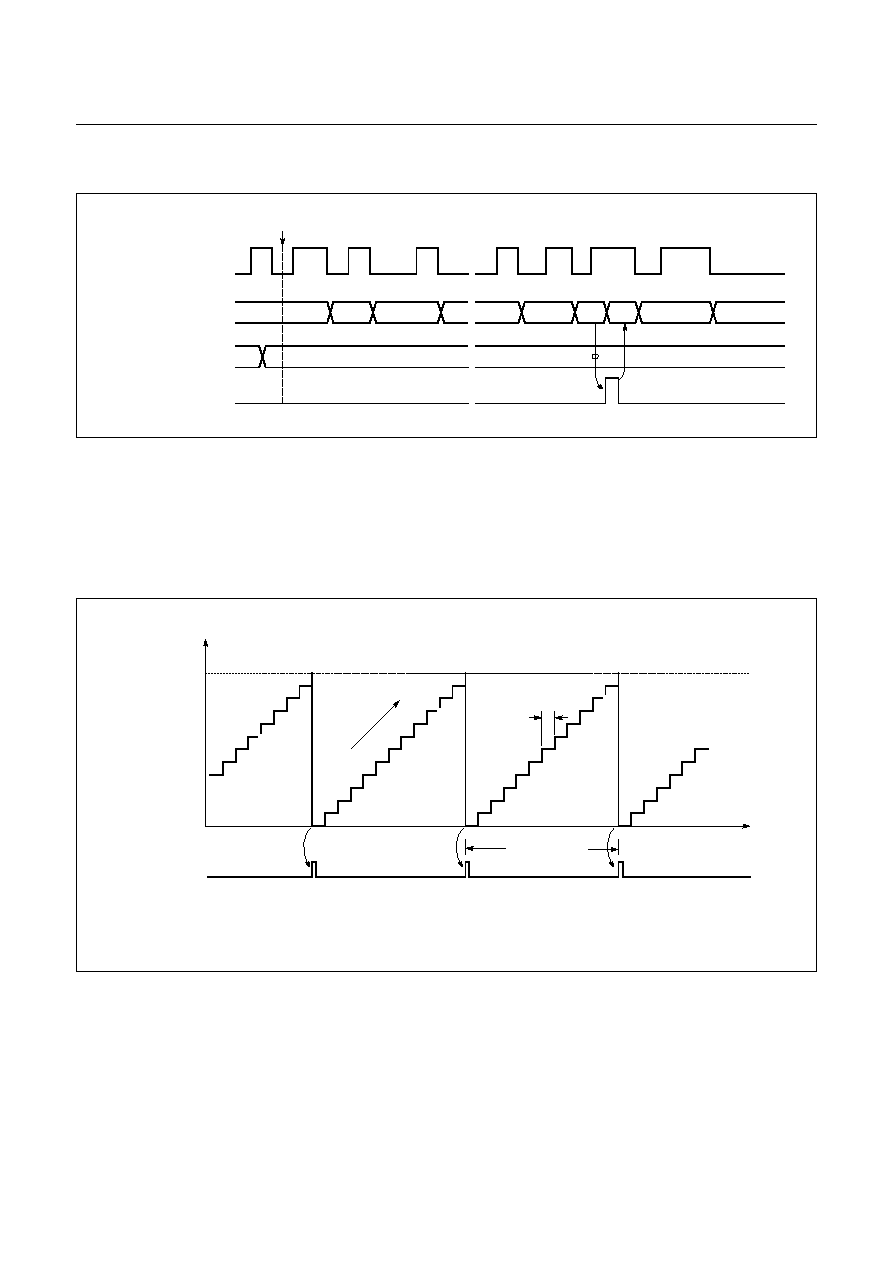

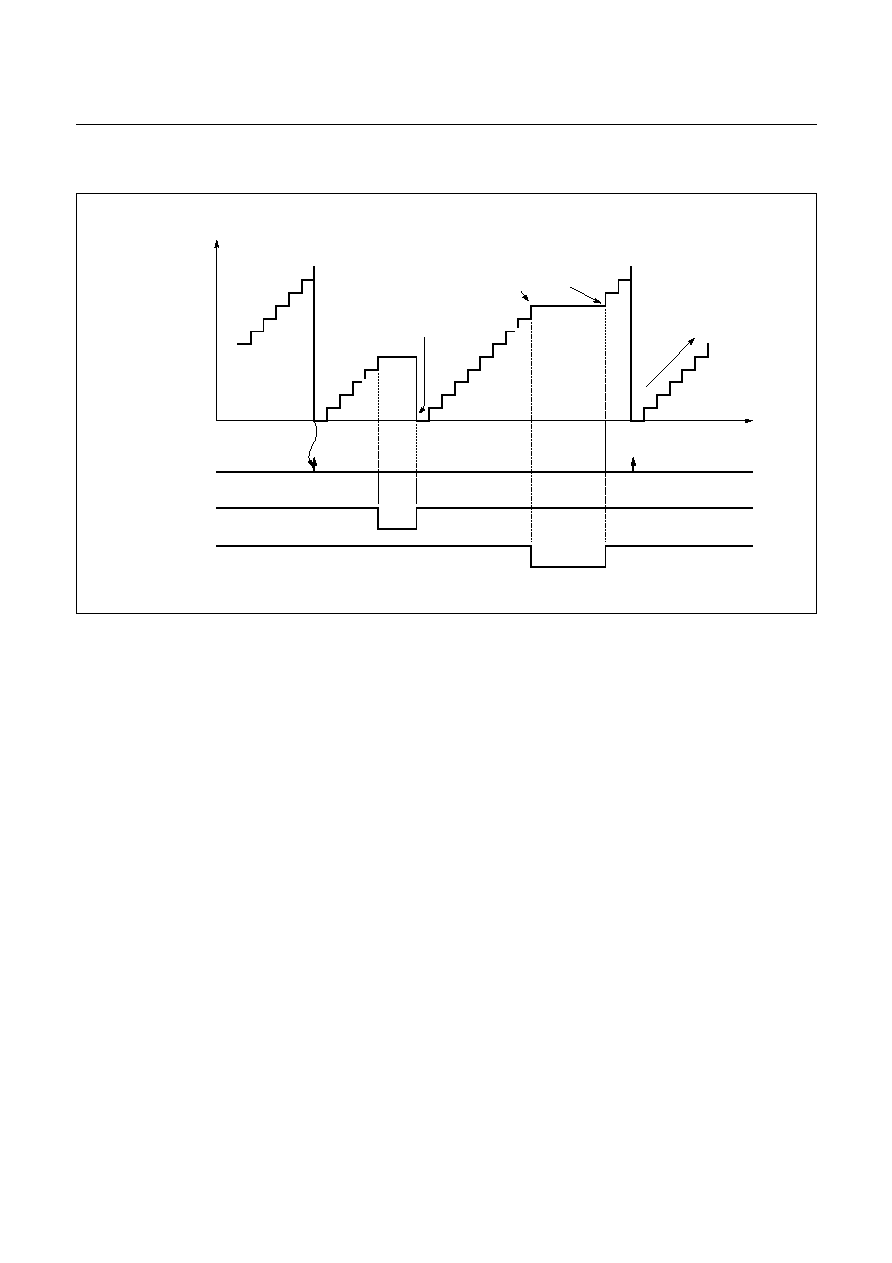

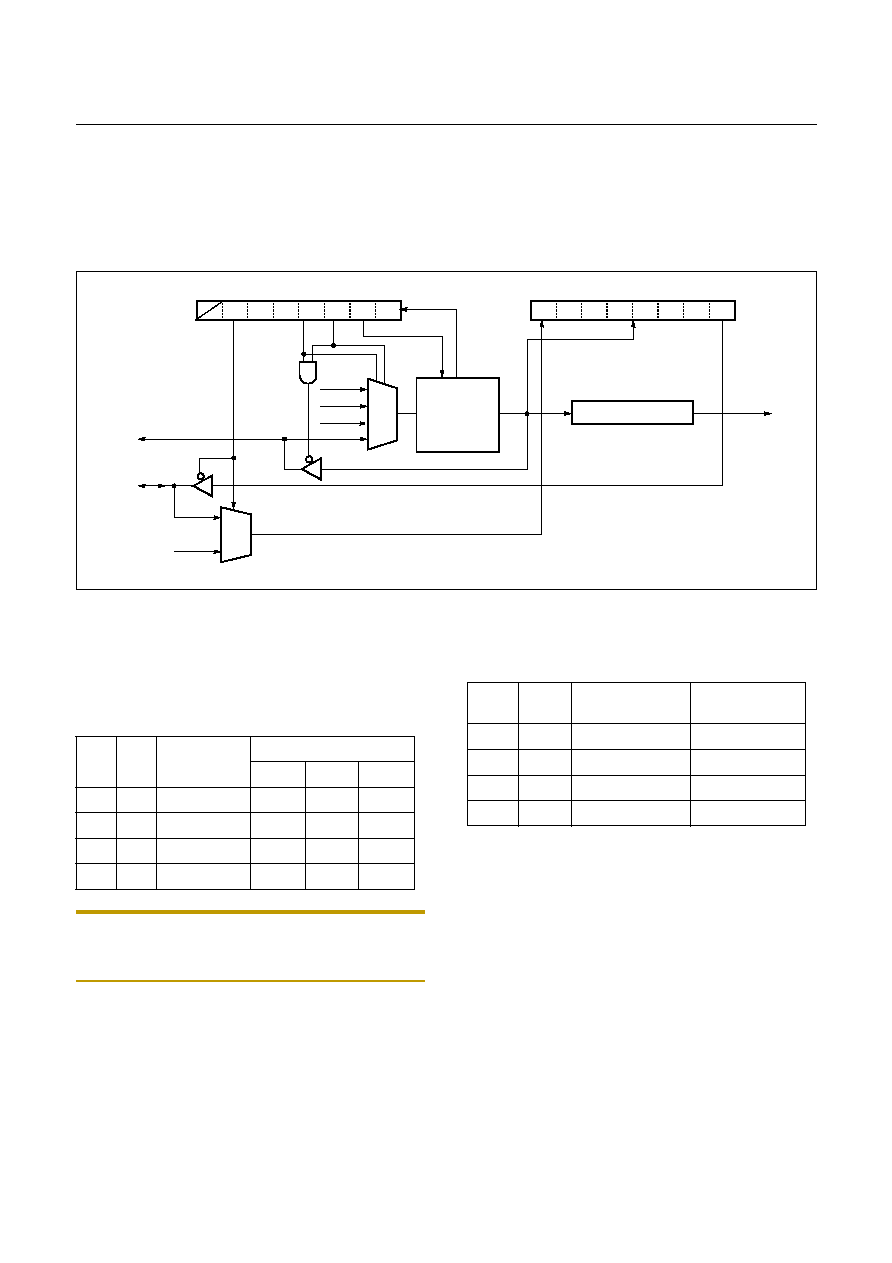

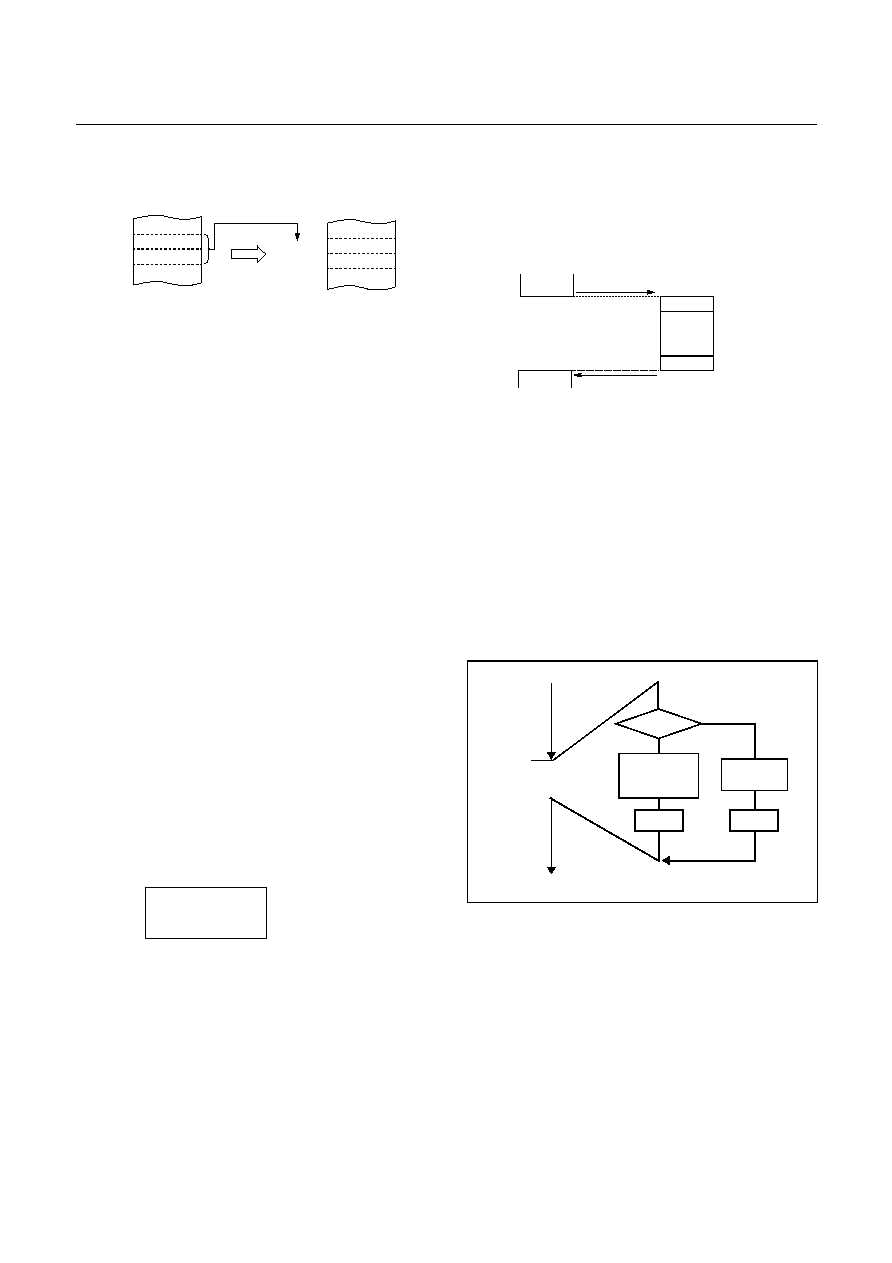

As shown in Figure 10-1 , the clock generator produces the

basic clock pulses which provide the system clock to be

supplied to the CPU and the peripheral hardware. It con-

tains two oscillators: a main-frequency clock oscillator and

a sub-frequency clock oscillator. The system clock can

also be obtained from the external oscillator.

The clock generator produces the system clocks forming

clock pulse, which are supplied to the CPU and the periph-

eral hardware.

To the peripheral block, the clock among the not-divided

original clocks, divided by

2

, 4,...,

up to 1024 can be pro-