8-BIT SINGLE-CHIP MICROCONTROLLERS

HMS87C1304(2)A

HMS87C1204(2)A

HMS87C1104(2)A

User's Manual

Apr. 2001

Ver 1.0

HMS87C130XA/120XA/110XA

Apr. 2001 ver1.0

1. OVERVIEW ....................................................................................................................... 1

1.1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.3 Development Tools . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

1.4 Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2. BLOCK DIAGRAM ........................................................................................................... 4

3. PIN ASSIGNMENT ........................................................................................................... 5

4. PACKAGE DIAGRAM ...................................................................................................... 6

5. PIN FUNCTION ................................................................................................................. 9

6. PORT STRUCTURES ..................................................................................................... 11

7. ELECTRICAL CHARACTERISTICS .............................................................................. 16

7.1 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

7.2 Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

7.3 A/D Converter Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

7.4 DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

7.5 AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

7.6 Typical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

8. MEMORY ORGANIZATION ........................................................................................... 22

8.1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

8.2 Program Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

8.3 Data Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

8.4 Addressing Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

9. I/O PORTS ...................................................................................................................... 34

9.1 RA and RAIO registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

9.2 RB and RBIO registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

9.3 RC and RCIO registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

9.4 RD and RDIO registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

10. CLOCK GENERATOR ................................................................................................. 38

10.1 Oscillation Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

11. BASIC INTERVAL TIMER ............................................................................................ 40

12. TIMER / COUNTER ...................................................................................................... 41

12.1 8-bit Timer/Counter Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Apr. 2001 ver 1.0

HMS87C130XA/120XA/110XA

12.2 16-bit Timer/Counter Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

12.3 8-bit Compare Output (16-bit) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

12.4 8-bit Capture Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

12.5 16-bit Capture Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

12.6 PWM Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

13. BUZZER OUTPUT FUNCTION .................................................................................... 50

14. ANALOG TO DIGITAL CONVERTER .......................................................................... 51

15. INTERRUPTS ............................................................................................................... 54

15.1 Interrupt Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

15.2 External Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

16. WATCHDOG TIMER .................................................................................................... 59

17. POWER SAVING MODE .............................................................................................. 60

17.1 Minimizing Current Consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

18. RESET .......................................................................................................................... 66

19. POWER FAIL PROCESSOR ........................................................................................ 68

20. OTP PROGRAMMING .................................................................................................. 70

20.1 DEVICE CONFIGURATION AREA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

APPENDIX

Instruction Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . i

Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ii

HMS87C130XA/120XA/110XA

Apr. 2001 ver1.0

1

HMS87C1304A / HMS87C1302A

HMS87C1204A / HMS87C1202A

HMS87C1104A / HMS87C1102A

CMOS SINGLE-CHIP 8-BIT MICROCONTROLLER

1. OVERVIEW

1.1 Description

The HMS87C1X0XA is an advanced CMOS 8-bit microcontroller with 4K/2K bytes of EPROM. The Hynix

HMS87C1X0XA is a powerful microcontroller which provide a highly flexible and cost effective solution to many small

applications such as controller for battery charger. The HMS87C1X0XA provides the following standard features: 4K/2K

bytes of EPROM, 128bytes of RAM, 8-bit timer/counter, 8-bit A/D converter, 10-bit high speed PWM output, programmable

buzzer driving port, power-on reset circuit, on-chip oscillator and clock circuitry. In addition, the HMS87C1X0XA supports

power saving modes to reduce power consumption.

This document is only explained for the base of HMS87C1304A, the other's eliminated functions are same as below.

1.2 Features

� 4K/2K Bytes On-chip Program Memory

� 128 Bytes of On-chip Data RAM

(Included stack memory)

� Instruction Cycle Time:

- 250nS at 8MHz

� Programmable I/O pins

(LED direct driving can be source and sink)

- HMS87C1304A/1302A : 19

- HMS87C1204A/1202A : 15

- HMS87C1104A/1102A : 11

� 2.0V to 5.5V Wide Operating Range

� 8-bit A/D Converter

- 8 channels

� One 8-bit Basic Interval Timer

� Two 8-bit Timer / Counters

� One 10-bit High Speed PWM Outputs

� Watchdog timer

� Seven Interrupt sources

- External input: 2 ( 1 for HMS87C1104/2A )

- A/D Conversion: 1

- Timer: 4

� One Programmable Buzzer Driving port

( except HMS87C1104/2A )

- 500Hz ~ 130kHz

Device name

EPROM

RAM

EXT.INT

BUZ

I/O

Operating

Voltage

Package

HMS87C1304A

4K bytes

128bytes

2

O

19

2.0 ~ 5.5V

24 SKDIP or SOP

HMS87C1302A

2K bytes

128bytes

2

O

19

2.0 ~ 5.5V

24 SKDIP or SOP

HMS87C1204A

4K bytes

128bytes

2

O

15

2.0 ~ 5.5V

20 PDIP or SOP

HMS87C1202A

2K bytes

128bytes

2

O

15

2.0 ~ 5.5V

20 PDIP or SOP

HMS87C1104A

4K bytes

128bytes

1

X

11

2.0 ~ 5.5V

16 PDIP or SOP

HMS87C1102A

2K bytes

128bytes

1

X

11

2.0 ~ 5.5V

16 PDIP or SOP

2

Apr. 2001 ver 1.0

HMS87C130XA/120XA/110XA

� Oscillator Type

- Crystal

- Ceramic Resonator

- RC-oscillation ( C can be omitted )

� Power-On Reset

� Noise Immunity Circuit

- Power Fail Processor

� Power Down Mode

- STOP mode

- Wake-up Timer mode

- Internal RC-WDT mode

1.3 Development Tools

The HMS87C1X0XA is supported by a full-featured mac-

ro assembler, an in-circuit emulator CHOICE-Dr

TM

and

OTP programmers.

The marco assembler operates under the MS-Windows 95/

98

TM

.

The OTP programmer can be supplied three types of pro-

grammer such as emulator add-on board type single pro-

grammer (Dr.Writer

TM

), univeral stand-alone type single

programmer (CHOICE-SIGMA

TM

) and gang type pro-

grammer (CHOICE-SIGMA

TM

). .

Figure 1-1 In Circuit Emulator CHOICE-Dr.

TM

Figure 1-2 OTP Single Programmer Dr.Writer

TM

Figure 1-3 OTP Gang Programmer CHOICE-GANG4

TM

In Circuit

Emulators

CHOICE-Dr.

TM

Assembler

Hynix Macro Assembler

OTP

Programmer

Single Programmer : Dr. Writer

TM

Universal Programmer : CHOICE-

SIGMA

TM

Gang Programmer : CHOICE-GANG4

TM

HMS87C130XA/120XA/110XA

Apr. 2001 ver1.0

3

1.4 Ordering Information

ROM Size

Package Type

Ordering Device Code

Operating Temperature

4K bytes (OTP)

24 SKDIP

HMS87C1304A SK

-20 ~ +85

�

C

24 SOP

HMS87C1304A D

20 PDIP

HMS87C1204A

20 SOP

HMS87C1204A D

16 PDIP

HMS87C1104A

16 SOP

HMS87C1104A D

2K bytes (OTP)

24 SKDIP

HMS87C1302A SK

24 SOP

HMS87C1302A D

20 PDIP

HMS87C1202A

20 SOP

HMS87C1202A D

16 PDIP

HMS87C1102A

16 SOP

HMS87C1102A D

4

Apr. 2001 ver 1.0

HMS87C130XA/120XA/110XA

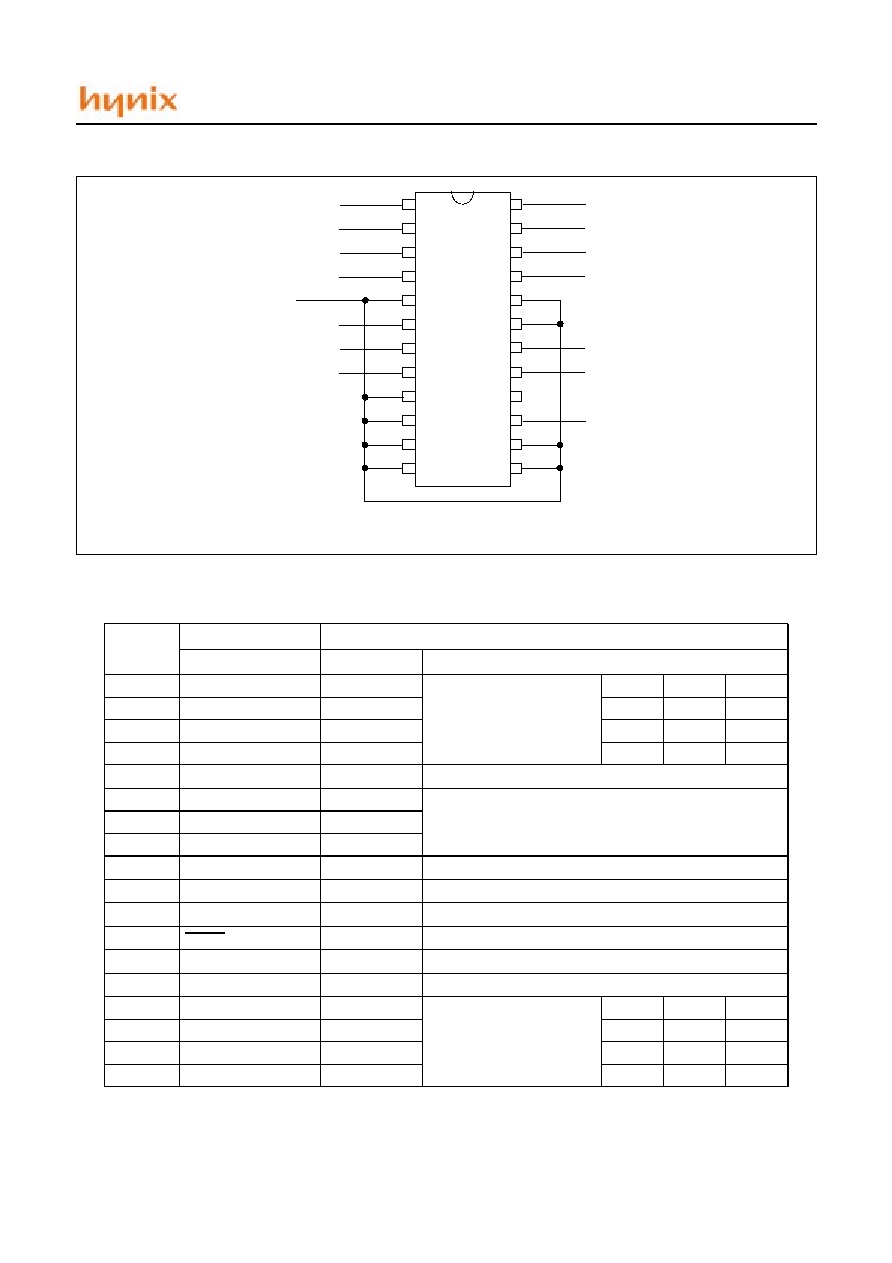

2. BLOCK DIAGRAM

ALU

Accumulator

Stack Pointer

Inte rrupt C ontroller

Data

Memory

8-bit

Converter

A/D

8-bit

Counter

Timer/

Program

Memory

Data Table

PC

8-bit Basic

Timer

Interval

Watch-dog

Timer

Instruction

RA

RB

RC

B u zzer

D rive r

PSW

System controller

Timing generator

System

Clock Controller

Clock Generator

RESET

X

IN

X

OUT

RA0 / EC0

RA1 / AN1

RA2 / AN2

RA3 / AN3

RA4 / AN4

RA5 / AN5

RA6 / AN6

RA7 / AN7

RB0 / AN0 / AV

REF

RB1 / BUZ

RB2 / INT0

RB3 / INT1

RB4 / CMP0 / PWM0

RC0

RC1

V

DD

V

SS

Power

Supply

Decoder

High

PWM

Speed

RD

RD0

,

RD1

,

RD2

,

RD3

,

These pins are not available in HMS87C1204(2)A.

These pins are not available in HMS87C1104(2)A.

Note

HMS87C130XA/120XA/110XA

Apr. 2001 ver1.0

5

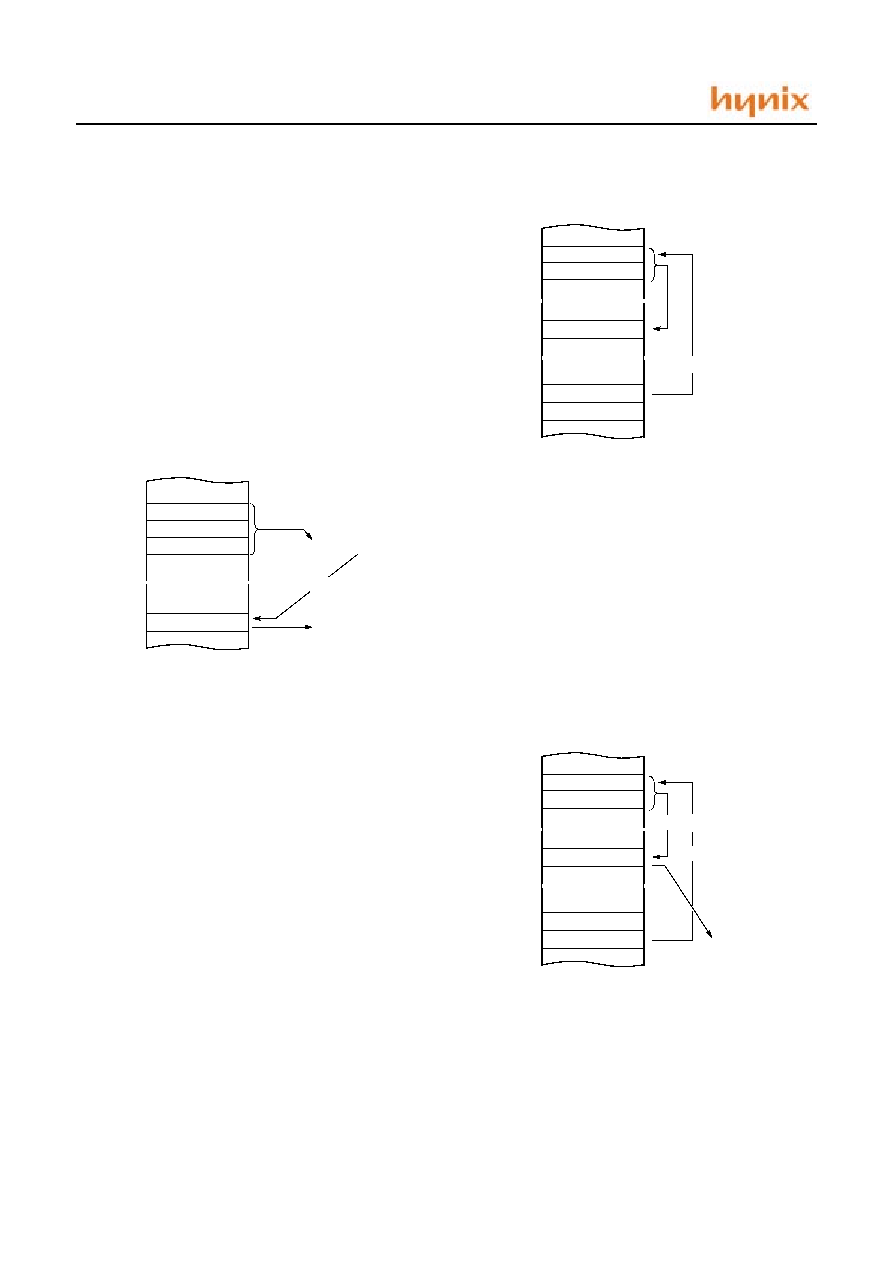

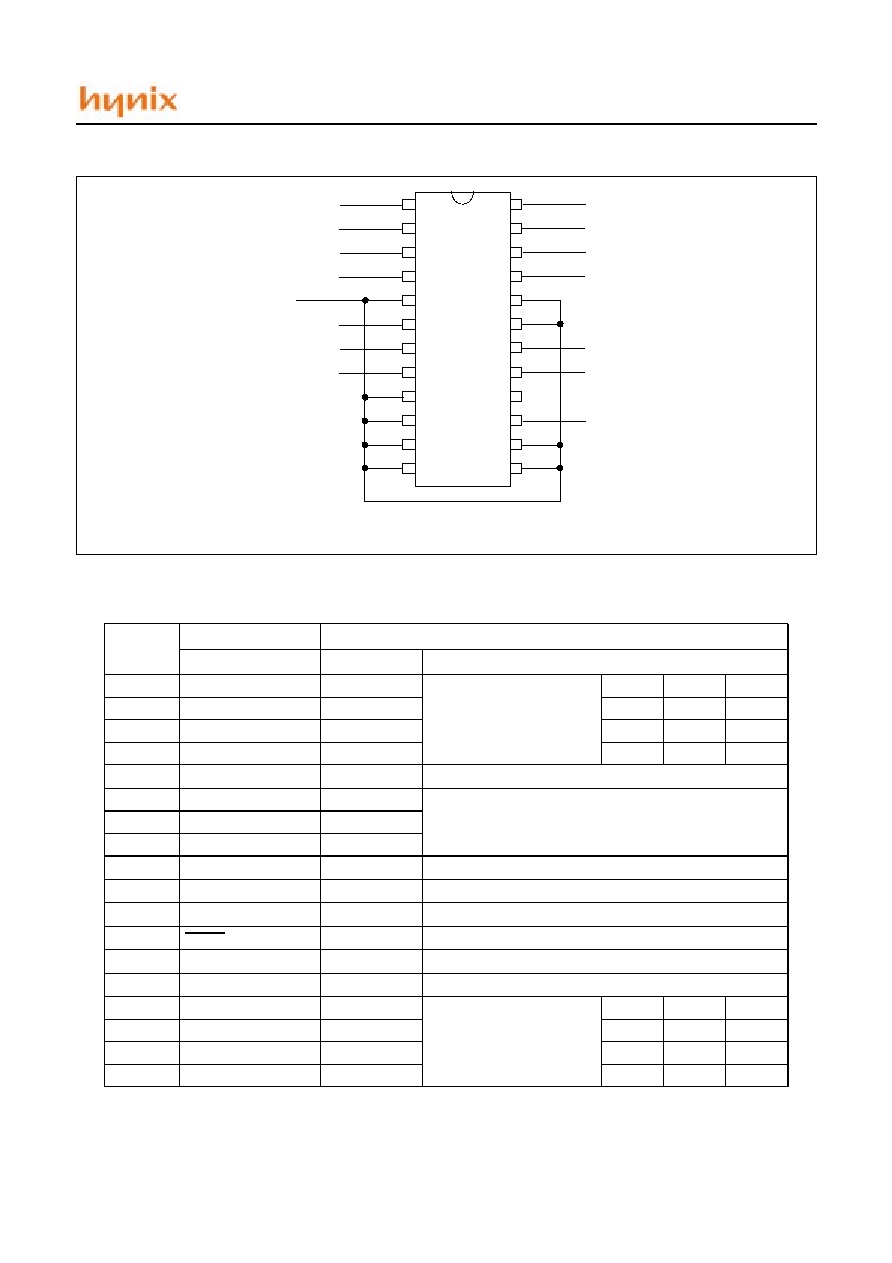

3. PIN ASSIGNMENT

RA3 / AN3

RA2 / AN2

RA1 / AN1

RA0 / EC0

RC1

RC0

V

SS

RESET

X

OUT

X

IN

AN4 / RA4

AN5 / RA5

AN6 / RA6

AN7 / RA7

V

DD

RD0

RD1

24 SKDIP

1

2

3

4

5

6

7

8

9

10

24

23

22

21

20

19

18

17

16

15

11

12

RD3

RD2

14

13

RA3 / AN3

RA2 / AN2

RA1 / AN1

RA0 / EC0

RC1

RC0

V

SS

RESET

X

OUT

X

IN

AN4 / RA4

AN5 / RA5

AN6 / RA6

AN7 / RA7

V

DD

AN0 / AV

REF

/ RB0

BUZ / RB1

INT0 / RB2

INT1 / RB3

PWM0 / COMP0 / RB4

24 SOP

1

2

3

4

5

6

7

8

9

10

24

23

22

21

20

19

18

17

16

15

11

12

RD3

RD2

14

13

AN0 / AV

REF

/ RB0

BUZ / RB1

INT0 / RB2

INT1 / RB3

PWM0 / COMP0 / RB4

RD1

RD0

RA3 / AN3

RA2 / AN2

RA1 / AN1

RA0 / EC0

RC1

RC0

V

SS

RESET

X

OUT

X

IN

AN4 / RA4

AN5 / RA5

AN6 / RA6

AN7 / RA7

V

DD

20 PDIP

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

RA3 / AN3

RA2 / AN2

RA1 / AN1

RA0 / EC0

RC1

RC0

V

SS

RESET

X

OUT

X

IN

AN4 / RA4

AN5 / RA5

AN6 / RA6

AN7 / RA7

V

DD

AN0 / AV

REF

/ RB0

BUZ / RB1

INT0 / RB2

INT1 / RB3

PWM0 / COMP0 / RB4

20 SOP

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

AN0 / AV

REF

/ RB0

BUZ / RB1

INT0 / RB2

INT1 / RB3

PWM0 / COMP0 / RB4

RA3 / AN3

RA2 / AN2

RA1 / AN1

RA0 / EC0

V

SS

RESET

X

OUT

X

IN

AN4 / RA4

AN5 / RA5

AN6 / RA6

AN7 / RA7

V

DD

16 PDIP

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

RA3 / AN3

RA2 / AN2

RA1 / AN1

RA0 / EC0

V

SS

RESET

X

OUT

X

IN

AN4 / RA4

AN5 / RA5

AN6 / RA6

AN7 / RA7

V

DD

AN0 / AV

REF

/ RB0

INT0 / RB2

PWM0 / COMP0 / RB4

16 SOP

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

AN0 / AV

REF

/ RB0

INT0 / RB2

PWM0 / COMP0 / RB4

HMS87C1304(2)A SK

HMS87C1304(2)A D

HMS87C1204(2)A

HMS87C1204(2)A D

HMS87C1104(2)A

HMS87C1104(2)A D

6

Apr. 2001 ver 1.0

HMS87C130XA/120XA/110XA

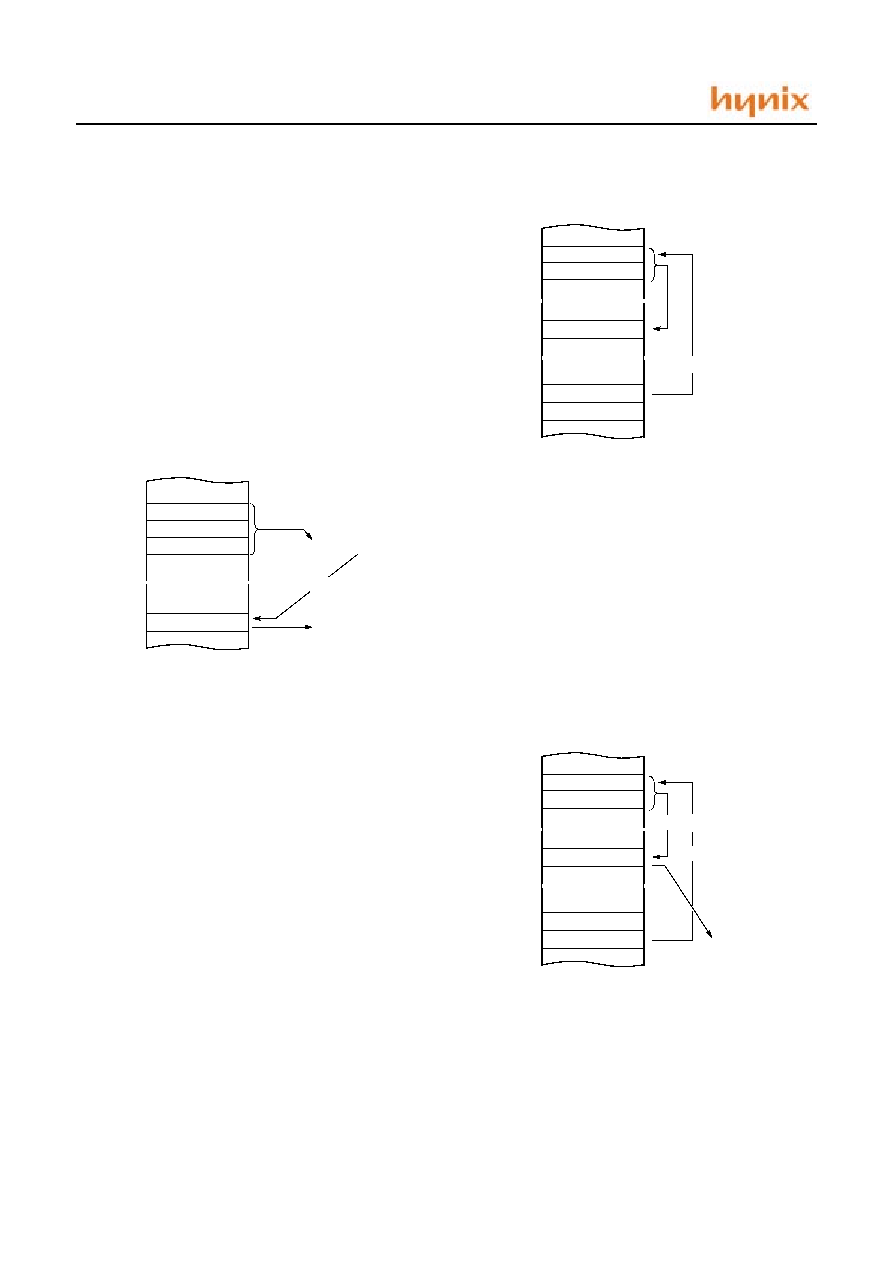

4. PACKAGE DIAGRAM

1.265

0.045

TYP 0.100

TYP 0.300

0.300

0.01

4

0 ~ 15�

MA

X 0.

180

MIN 0.015

0.120

0.292

0.

3

9

8

0.614

0.104

0.0138

TYP 0.050

0.004

0.

009

0 ~ 8�

0.016

24 SKDIP

24 SOP

unit: inch

MAX

MIN

1.160

0.021

0.140

0.065

0.00

8

0.250

0.419

0.299

0.593

0.093

0.019

0.042

0.

0125

0.01

18

0.015

HMS87C130XA/120XA/110XA

Apr. 2001 ver1.0

7

1.043

0.050

TYP 0.100

TYP 0.300

0.270

0.01

4

0 ~ 15�

M

A

X

0.180

MIN 0.

015

0.

120

0.

291

0.398

0.5118

0

.

104

0.013

TYP 0.050

0.

004

0.0091

0 ~ 8�

0.016

20 PDIP

20 SOP

unit: inch

MAX

MIN

1.010

0.021

0.

140

0.065

0.00

8

0.245

0.

419

0.

299

0.4961

0

.

093

0.020

0.042

0.0125

0.

01

18

0.015

8

Apr. 2001 ver 1.0

HMS87C130XA/120XA/110XA

0.765

0.050

TYP 0.100

TYP 0.300

0.260

0.01

4

0 ~ 15�

M

A

X

0.180

MIN 0.

015

0.

120

0.

292

0.398

0.412

0

.

104

0.014

TYP 0.050

0.

004

0.0091

0 ~ 8�

0.016

16 PDIP

16 SOP

unit: inch

MAX

MIN

0.745

0.022

0.

140

0.065

0.00

8

0.240

0.

416

0.

299

0.402

0

.

094

0.019

0.040

0.0125

0.

01

18

0.015

HMS87C130XA/120XA/110XA

Apr. 2001 ver1.0

9

5. PIN FUNCTION

V

DD

: Supply voltage.

V

SS

: Circuit ground.

RESET: Reset the MCU.

X

IN

: Input to the inverting oscillator amplifier and input to

the internal main clock operating circuit.

X

OUT

: Output from the inverting oscillator amplifier.

RA0~RA7: RA is an 8-bit, CMOS, bidirectional I/O port.

RA pins can be used as outputs or inputs according to "1"

or "0" written the their Port Direction Register(RAIO).

In addition, RA serves the functions of the various special

features in Table 5-1.

RB0~RB4: RB is an 8-bit, CMOS, bidirectional I/O port.

RB pins can be used as outputs or inputs according to "1"

or "0" written the their Port Direction Register(RBIO).

RB serves the functions of the various following special

features

in

Table 5-2.

RC0, RC1: RC is a 2-bit, CMOS, bidirectional I/O port.

RC pins can be used as outputs or inputs according to "1"

or "0" written the their Port Direction Register(RCIO).

And these pins are not available in HMS87C1104(2)A.

RD0~RD3: RD is a 4-bit, CMOS, bidirectional I/O port.

RC pins can be used as outputs or inputs according to "1"

or "0" written the their Port Direction Register(RDIO).

And these pins are not available in HMS87C1204(2)A and

HMS87C1104(2)A.

Port pin

Alternate function

RA0

RA1

RA2

RA3

RA4

RA5

RA6

RA7

EC0 ( Event Counter Input Source )

AN1 ( Analog Input Port 1 )

AN2 ( Analog Input Port 2 )

AN3 ( Analog Input Port 3 )

AN4 ( Analog Input Port 4 )

AN5 ( Analog Input Port 5 )

AN6 ( Analog Input Port 6 )

AN7 ( Analog Input Port 7 )

Table 5-1 RA Port

Port pin

Alternate function

RB0

RB1

1

RB2

RB3

1

RB4

1. These pins are not available in HMS87C1104(2)A.

AN0 ( Analog Input Port 0 )

AV

REF

( External Analog Reference Pin

)

BUZ ( Buzzer Driving Output Port )

INT0 ( External Interrupt Input Port 0 )

INT1 ( External Interrupt Input Port 1 )

PWM0 (PWM0 Output)

COMP0 (Timer1 Compare Output)

Table 5-2 RB Port

10

Apr. 2001 ver 1.0

HMS87C130XA/120XA/110XA

PIN NAME

PIN NUMBER

In/Out

Function

87C1304(2)A

87C1204(2)A

87C1104(2)A

Basic

Sencondary

V

DD

5

5

5

-

Supply voltage

V

SS

18

14

12

-

Circuit ground

RESET

17

13

11

I

Reset signal input

X

IN

15

11

9

I

X

OUT

16

12

10

O

RA0 (EC0)

21

17

13

I/O (Input)

8-bit general

I/O ports

External Event Counter input 0

RA1 (AN1)

22

18

14

I/O (Input)

Analog Input Port 1

RA2 (AN2)

23

19

15

I/O (Input)

Analog Input Port 2

RA3 (AN3)

24

20

16

I/O (Input)

Analog Input Port 3

RA4 (AN4)

1

1

1

I/O (Input)

Analog Input Port 4

RA5 (AN5)

2

2

2

I/O (Input)

Analog Input Port 5

RA6 (AN6)

3

3

3

I/O (Input)

Analog Input Port 6

RA7 (AN7)

4

4

4

I/O (Input)

Analog Input Port 7

RB0 (AVref/AN0)

8

6

6

I/O (Input)

5-bit general

I/O ports

Analog Input Port 0

/ Analog Reference

RB1 (BUZ)

9

7

I/O (Input)

Buzzer Driving Output

RB2 (INT0)

10

8

I/O (Input)

External Interrupt Input 0

RB3 (INT1)

11

9

I/O (Output)

External Interrupt Input 1

RB4 (PWM0/

COMP0)

12

10

I/O (Output/

Output)

PWM0 Output or Timer1

Compare Output

RC0

19

15

I/O

2-bit general

I/O ports

RC1

20

16

I/O

RD0 6

I/O

4-bit general

I/O ports

RD1

7

I/O

RD2

13

I/O

RD3

14

I/O

Table 5-3 Pin Description

HMS87C130XA/120XA/110XA

Apr. 2001 ver1.0

11

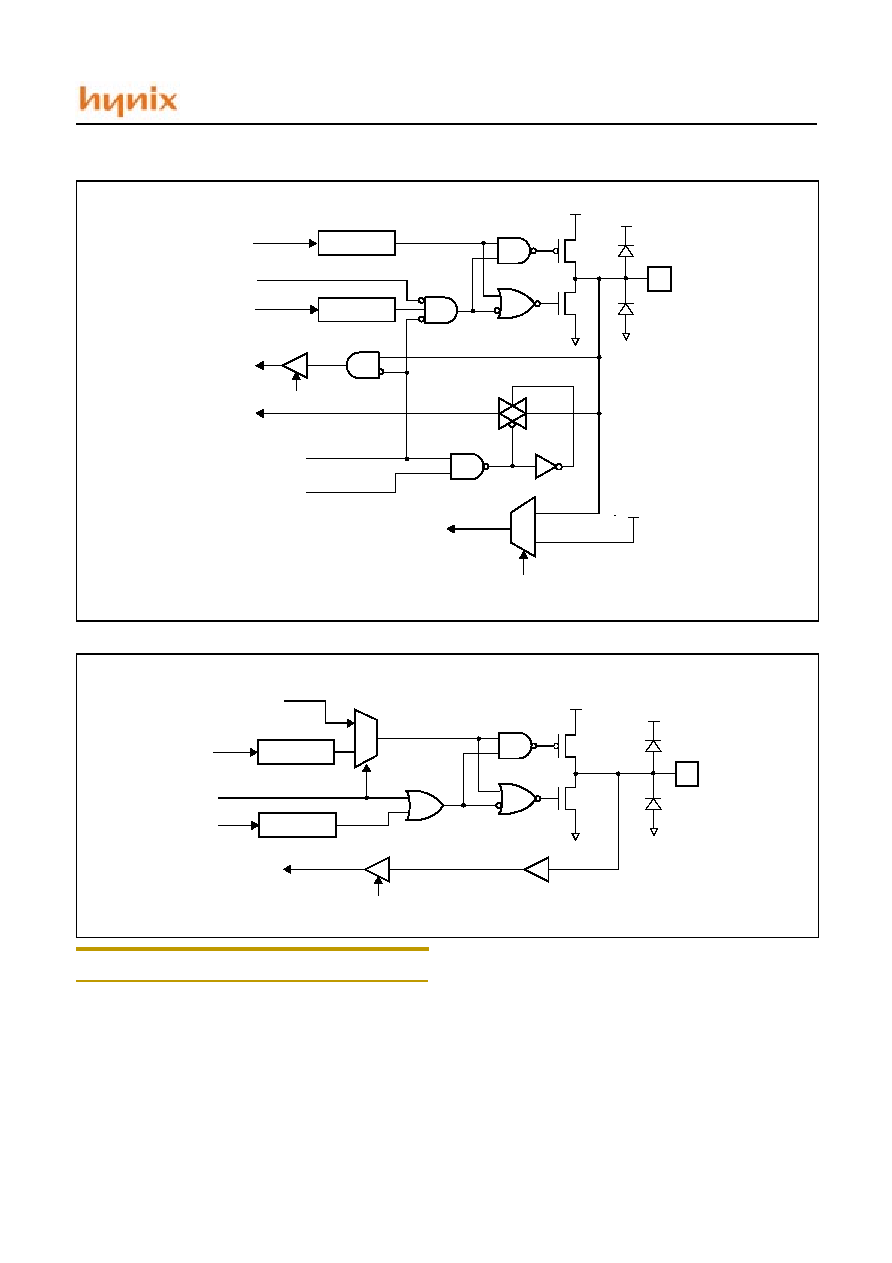

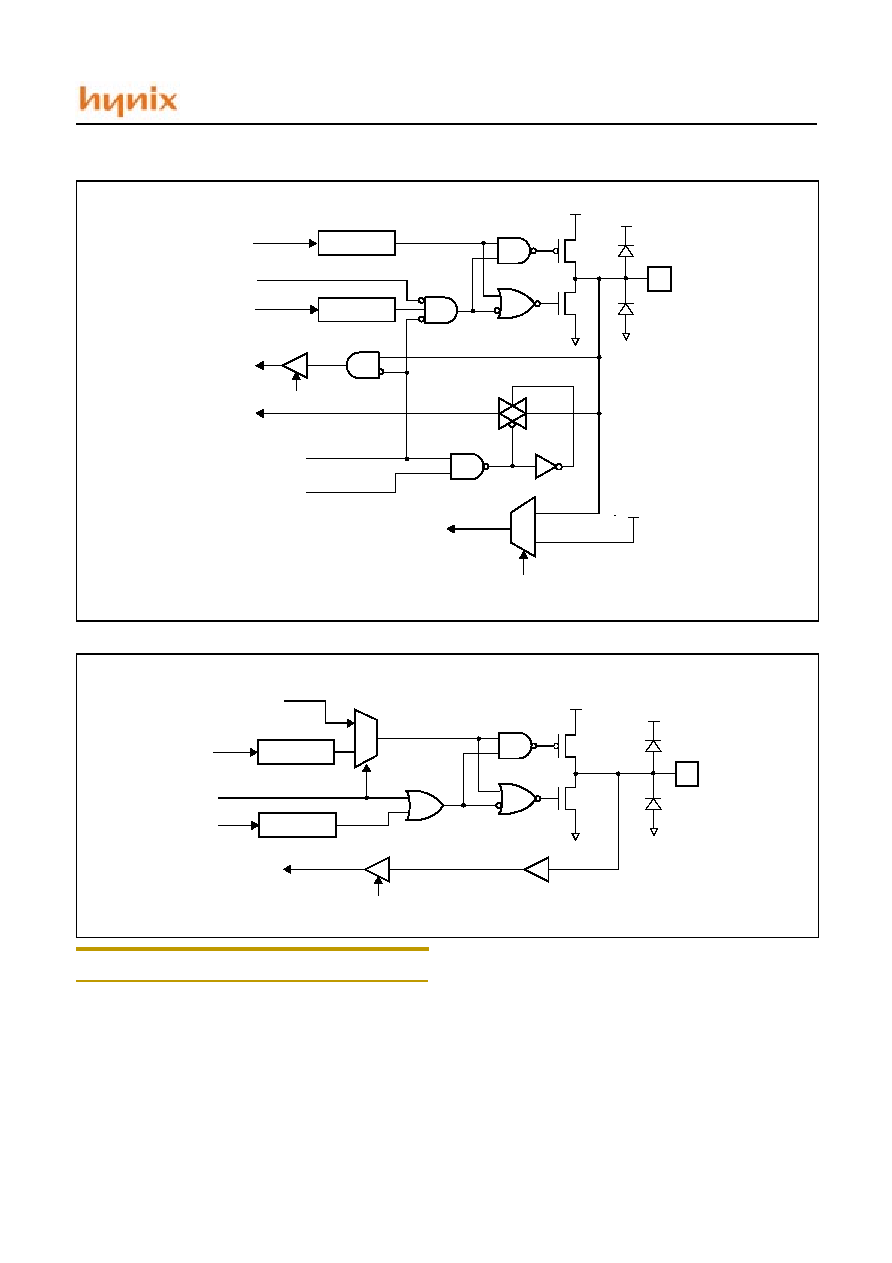

6. PORT STRUCTURES

� RESET

� Xin, Xout

V

SS

Internal RESET

V

SS

Xout

Xin

STOP

To System CLK

V

DD

V

SS

Xout

Xin

STOP

To System CLK

V

DD

Internal Capacitor 6 pF

Crystal or Ceramic

RC Oscillation (refer to Configuration Area)

12

Apr. 2001 ver 1.0

HMS87C130XA/120XA/110XA

� RA0/EC0

� RA1/AN1 ~ RA7/AN7

Data Bus

Data Bus

Data Bus

Data Reg.

Direction Reg.

Read

EC0

Schmitt Trigger

Open Drain

V

DD

V

SS

Data Bus

Data Bus

Data Bus

Read

To A/D Converter

Analog Input Mode

(ANSEL7 ~ 1)

Analog CH. Selection

(ADCM.4 ~ 2)

Data Reg.

Direction Reg.

HMS87C130XA/120XA/110XA

Apr. 2001 ver1.0

13

� RB0 / AN0 / AVref

� RB1/BUZ, RB4/PWM0/COMP0

Note: RB1/BUZ pin is not available in HMS87C1104(2)A.

V

DD

V

SS

Data Bus

Data Bus

Data Bus

Read

To A/D Converter

Analog Input Mode

(ANSEL0)

Analog CH0 Selection

(ADCM.4 ~ 2)

AVREFS

AVREFS

Internal V

DD

0

1

To Vref of A/D

Data Reg.

Direction Reg.

V

DD

V

SS

Data Bus

Data Bus

Data Bus

Read

0

1

Function

Select

PWM/COMP

BUZ

Data Reg.

Direction Reg.

14

Apr. 2001 ver 1.0

HMS87C130XA/120XA/110XA

� RB2/INT0, RB3/INT1

Note: RB3/INT1 pin is not available in HMS87C1104(2)A .

� RC0, RD2, RD3

Note: RC0, RD2, RD3 pins are not available in

HMS87C1104(2)A

Note: RD2, RD3 pins are not available in HMS87C1204(2)

V

DD

V

SS

Data Bus

Data Bus

Data Bus

Read

Function

Select

Pull-up

Select

INT0, INT1

Schmitt Trigger

Weak Pull-up

Data Reg.

Direction Reg.

Open Drain

Data Bus

Data Bus

Data Bus

Data Reg.

Direction Reg.

Read

HMS87C130XA/120XA/110XA

Apr. 2001 ver1.0

15

� RC1

� RD0, RD1

V

DD

V

SS

Data Bus

Data Bus

Data Bus

Read

Data Reg.

Direction Reg.

Open Drain

V

DD

V

SS

Data Bus

Data Bus

Data Bus

Read

Pull-up

Select

Weak Pull-up

Data Reg.

Direction Reg.

16

Apr. 2001 ver 1.0

HMS87C130XA/120XA/110XA

7. ELECTRICAL CHARACTERISTICS

7.1 Absolute Maximum Ratings

Supply voltage ........................................... -0.3 to +6.0 V

Storage Temperature ................................-40 to +125

�

C

Voltage on any pin with respect to Ground (V

SS

)

............................................................... -0.3 to V

DD

+0.3

Maximum current out of V

SS

pin ........................200 mA

Maximum current into V

DD

pin ..........................150 mA

Maximum current sunk by (I

OL

per I/O Pin) ........25 mA

Maximum output current sourced by (I

OH

per I/O Pin)

...............................................................................15 mA

Maximum current (

I

OL

) ....................................150 mA

Maximum current (

I

OH

).................................... 100 mA

Note: Stresses above those listed under "Absolute Maxi-

mum Ratings" may cause permanent damage to the

device. This is a stress rating only and functional op-

eration of the device at any other conditions above

those indicated in the operational sections of this

specification is not implied. Exposure to absolute

maximum rating conditions for extended periods

may affect device reliability.

7.2 Recommended Operating Conditions

7.3 A/D Converter Characteristics

(T

A

=25

�

C, V

SS

=0V, V

DD

=5.12V @

f

XIN

=8MHz, V

DD

=3.072V @

f

XIN

=4MHz)

Parameter

Symbol

Condition

Specifications

Unit

Min.

Max.

Supply Voltage

V

DD

f

XIN

=8MHz

4.5

5.5

V

f

XIN

=4.2MHz

2.0

5.5

V

Operating Frequency

f

XIN

V

DD

=4.5~5.5V

1

8

MHz

V

DD

=2.0~5.5V

1

4.2

MHz

Operating Temperature

T

OPR

-20

85

�

C

Parameter

Symbol

Condition

Specifications

Unit

Min.

Typ.

Max.

Analog Input Voltage Range

V

AIN

AVREFS=0

V

SS

-

V

DD

V

AVREFS=1

V

SS

-

V

REF

Analog Power Supply Input Voltage Range

V

REF

V

DD

=5V

3

-

V

DD

V

V

DD

=3V

2.4

-

V

DD

V

Overall Accuracy

N

ACC

-

�

1.0

�

1.5

LSB

Non-Linearity Error

N

NLE

-

�

1.0

�

1.5

LSB

Differential Non-Linearity Error

N

DNLE

-

�

1.0

�

1.5

LSB

Zero Offset Error

N

ZOE

-

�

0.5

�

1.5

LSB

Full Scale Error

N

FSE

-

�

0.25

�

0.5

LSB

Gain Error

N

NLE

-

�

1.0

�

1.5

LSB

Conversion Time

T

CONV

f

XIN

=8MHz

-

-

10

�

S

f

XIN

=4MHz

-

-

20

AV

REF

Input Current

I

REF

AVREFS=1

-

0.5

1.0

mA

HMS87C130XA/120XA/110XA

Apr. 2001 ver1.0

17

7.4 DC Electrical Characteristics

(T

A

=-20~85

�

C, V

DD

=2.0~5.5V

,

V

SS

=0V)

,

Parameter

Symbol

Pin

Condition

Specifications

Unit

Min.

Typ.

Max.

Input High Voltage

V

IH1

RESET

0.8 V

DD

-

V

DD

V

V

IH2

X

IN

, Hysteresis Input

1

0.8 V

DD

-

V

DD

V

IH3

Normal Input

0.7 V

DD

-

V

DD

Input Low Voltage

V

IL1

RESET

0

-

0.2 V

DD

V

V

IL2

X

IN

, Hysteresis Input

1

0

-

0.2 V

DD

V

IL3

Normal Input

0

-

0.3 V

DD

Output High Voltage

V

OH

All Output Port

V

DD

=5V, I

OH

=-5mA

V

DD

-1

-

-

V

Output Low Voltage

V

OL

All Output Port

V

DD

=5V, I

OL

=10mA

-

-

1

V

Input Pull-up Current

2

I

P

RB2, RB3, RD0, RD1

V

DD

=5V

-450

-380

-300

�

A

Input High

Leakage Current

I

IH1

All Pins (except X

IN

)

V

DD

=5V

-

-

5

�

A

I

IH2

X

IN

V

DD

=5V

-

-

15

�

A

Input Low

Leakage Current

I

IL1

All Pins (except X

IN

)

V

DD

=5V

-5

-

-

�

A

I

IL2

X

IN

V

DD

=5V

-15

-

-

�

A

Hysteresis

| V

T

|

Hysteresis Input

1

V

DD

=5V

0.5

-

-

V

PFD Voltage

V

PFD1

V

DD

PFD Level = 0, V

DD

=5V

2.0

2.5

3.0

V

V

PFD2

V

DD

PFD Level = 1, V

DD

=3V

1.5

1.7

1.9

Internal RC WDT

Period

T

RCWDT

V

DD

=5.0V, f

XIN

=8MHz

60

200

�

S

V

DD

=3.0V, f

XIN

=4MHz

150

300

Operating Current

3

I

DD

V

DD

V

DD

=5.5V, f

XIN

=8MHz

-

2

5

mA

V

DD

=3.0V, f

XIN

=4MHz

-

1

2

Wake-up Timer Mode

Current

I

WKUP

V

DD

V

DD

=5.5V, f

XIN

=8MHz

-

0.1

0.5

mA

V

DD

=3.0V, f

XIN

=4MHz

-

0.03

0.1

RCWDT Mode

Current at STOP

Mode

I

RCWDT

V

DD

V

DD

=5.5V

-

-

50

�

A

V

DD

=3.0V

-

-

30

Stop Mode Current

I

STOP

V

DD

V

DD

=5.5V, f

XIN

=8MHz

-

0.7

1.6

�

A

V

DD

=3.0V, f

XIN

=4MHz

-

0.2

0.8

External RC

Oscillator Frequency

F

RC

X

OUT

V

DD

=5V,

R=10K

, C=20pF

3

5

MHz

V

DD

=5V,

R=10K

5

9

1. Hysteresis Input: RA0, RB2, RB3

2. This parameter is valid when the bit PUPSELx is selected and set the input mode or interrupt input function.

3. This value is measured under NOP instruction execution.

18

Apr. 2001 ver 1.0

HMS87C130XA/120XA/110XA

7.5 AC Characteristics

(T

A

=-20~+85

�

C, V

DD

=5V

�

10%

,

V

SS

=0V)

Figure 7-1 Timing Chart

Parameter

Symbol

Pins

Specifications

Unit

Min.

Typ.

Max.

Operating Frequency

f

CP

X

IN

1

-

8

MHz

External Clock Pulse Width

t

CPW

X

IN

80

-

-

nS

External Clock Transition Time

t

RCP,

t

FCP

X

IN

-

-

20

nS

Oscillation Stabilizing Time

t

ST

X

IN

, X

OUT

-

-

20

mS

External Input Pulse Width

t

EPW

INT0, INT1, EC0

2

-

-

t

SYS

RESET Input Width

t

RST

RESET

8

-

-

t

SYS

t

RCP

t

FCP

X

IN

INT0, INT1

0.5V

V

DD

-0.5V

0.2V

DD

RESET

0.2V

DD

0.8V

DD

EC0

t

RST

t

EPW

t

EPW

1/f

CP

t

CPW

t

CPW

t

SYS

HMS87C130XA/120XA/110XA

Apr. 2001 ver1.0

19

7.6 Typical Characteristics

This graphs and tables provided in this section are for de-

sign guidance only and are not tested or guaranteed.

In some graphs or tables the data presented are out-

side specified operating range (e.g. outside specified

V

DD

range). This is for information only and devices

are guaranteed to operate properly only within the

specified range.

The data presented in this section is a statistical summary

of data collected on units from different lots over a period

of time. "Typical" represents the mean of the distribution

while "max" or "min" represents (mean + 3

) and (mean

-

3

) respectively where

is standard deviation

Ta= 25

�

C

Ta=25

�

C

I

DD

-

V

DD

4

3

2

1

0

(mA)

I

DD

2

3

4

5

6

V

DD

(V)

Normal Operation (NOP)

8

6

4

2

0

(MHz)

f

XIN

2

3

4

5

6

V

DD

(V)

Operating Area

f

XIN

= 8MHz

4MHz

10

I

WKUP

-

V

DD

2.0

1.5

1.0

0.5

0

(mA)

I

DD

2

3

4

5

6

V

DD

(V)

Wake-up Timer Mode

I

RCWDT

-

V

DD

20

15

10

5

0

(

�

A)

I

DD

2

3

4

5

6

V

DD

(V)

RC-WDT in Stop Mode

Ta=25

�

C

f

XIN

= 8MHz

4MHz

Ta=25

�

C

I

STOP

-

V

DD

2.0

1.5

1.0

0.5

0

(

�

A)

I

DD

2

3

4

5

6

V

DD

(V)

STOP Mode

f

XIN

= 8MHz

-25

�

C

85

�

C

25

�

C

T

RCWDT

= 180uS

20

Apr. 2001 ver 1.0

HMS87C130XA/120XA/110XA

I

OL

-

V

OL

, V

DD

=5V

40

30

20

10

0

(mA)

I

OL

V

OL

(V)

I

OH

-

V

OH

, V

DD

=5V

-20

-15

-10

-5

0

(mA)

I

OH

2

3

4

5

6

V

OH

(V)

0.5

1

1.5

2

2.5

f

XIN

=4MHz

V

DD

-

V

IH1

4

3

2

1

0

(V)

V

IH1

2

3

4

5

6

V

DD

(V)

V

DD

-

V

IH2

4

3

2

1

0

(V)

V

IH2

2

3

4

5

6

V

DD

(V)

Ta=25

�

C

f

X IN

= 4M H z

Ta=25

�

C

1

X

IN

, RESET

Hysteresis input

-25

�

C

85

�

C

25

�

C

-25

�

C

85

�

C

25

�

C

V

DD

-

V

IH3

4

3

2

1

0

(V)

V

IH3

2

3

4

5

6

V

DD

(V)

f

X IN

=4M H z

Ta=25

�

C

Normal input

f

XIN

=4MHz

V

DD

-

V

IL1

4

3

2

1

0

(V)

V

IL1

2

3

4

5

6

V

DD

(V)

V

DD

-

V

IL2

4

3

2

1

0

(V)

V

IL2

2

3

4

5

6

V

DD

(V)

Ta=25

�

C

f

X IN

=4M H z

Ta=25

�

C

1

X

IN

, RESET

Hysteresis input

V

DD

-

V

IL3

4

3

2

1

0

(V)

V

IL3

2

3

4

5

6

V

DD

(V)

f

X IN

=4M H z

Ta=25

�

C

Normal input

HMS87C130XA/120XA/110XA

Apr. 2001 ver1.0

21

With External Capacitor

Without External Capcitor

R

EXT

C

EXT

f

OSC

@

5V,25

�

C

f

OSC

@

3V,25

�

C

f

OSC

@

5V,25

�

C

f

OSC

@

3V,25

�

C

10K

10pF

4.9MHz

3.94MHz

7.29MHz

5.1MHz

20pF

3.35MHz

2.72MHz

40pF

2.12MHz

1.74MHz

30K

10pF

1.81MHz

1.57MHz

2.96MHz

2.37MHz

20pF

1.21MHz

1.04MHz

40pF

0.75MHz

0.65MHz

50K

10pF

1.11MHz

0.98MHz

1.85MHz

1.55MHz

20pF

0.74MHz

0.65MHz

40pF

0.46MHz

0.40MHz

Table 7-1 RC Oscillation Frequencies (with C

EXT

and without C

EXT)

22

Apr. 2001 ver 1.0

HMS87C130XA/120XA/110XA

8. MEMORY ORGANIZATION

The HMS87C1X0XA has separate address spaces for Pro-

gram memory and Data Memory. Program memory can

only be read, not written to. It can be up to 2K/4K bytes of

Program memory. Data memory can be read and written to

up to 128 bytes including the stack area.

8.1 Registers

This device has six registers that are the Program Counter

(PC), a Accumulator (A), two index registers (X, Y), the

Stack Pointer (SP), and the Program Status Word (PSW).

The Program Counter consists of 16-bit register.

Figure 8-1 Configuration of Registers

Accumulator: The Accumulator is an 8-bit general pur-

pose register, used for data operation such as transfer, tem-

porary saving, and conditional judgement, etc.

The Accumulator can be used as a 16-bit register with Y

Register as shown below.

Figure 8-2 Configuration of YA 16-bit Register

X, Y Registers: In the addressing mode which uses these

index registers, the register contents are added to the spec-

ified address, which becomes the actual address. These

modes are extremely effective for referencing subroutine

tables and memory tables. The index registers also have in-

crement, decrement, comparison and data transfer func-

tions, and they can be used as simple accumulators.

Stack Pointer: The Stack Pointer is an 8-bit register used

for occurrence interrupts and calling out subroutines. Stack

Pointer identifies the location in the stack to be accessed

(save or restore).

Generally, SP is automatically updated when a subroutine

call is executed or an interrupt is accepted. However, if it

is used in excess of the stack area permitted by the data

memory allocating configuration, the user-processed data

may be lost.

The stack can be located at any position within 00

H

to 7F

H

of the internal data memory. The SP is not initialized by

hardware, requiring to write the initial value (the location

with which the use of the stack starts) by using the initial-

ization routine. Normally, the initial value of "7F

H

" is

used.

Note: The Stack Pointer must be initialized by software be-

cause its value is undefined after RESET.

Example: To initialize the SP

LDX

#07FH

TXSP

; SP

7F

H

Program Counter: The Program Counter is a 16-bit wide

which consists of two 8-bit registers, PCH and PCL. This

counter indicates the address of the next instruction to be

executed. In reset state, the program counter has reset rou-

tine address (PC

H

:0FF

H

, PC

L

:0FE

H

).

Program Status Word: The Program Status Word (PSW)

contains several bits that reflect the current state of the

CPU. The PSW is described in Figure 8-3. It contains the

Negative flag, the Overflow flag, the Break flag the Half

Carry (for BCD operation), the Interrupt enable flag, the

Zero flag, and the Carry flag.

[Carry flag C]

This flag stores any carry or borrow from the ALU of CPU

after an arithmetic operation and is also changed by the

Shift Instruction or Rotate Instruction.

[Zero flag Z]

This flag is set when the result of an arithmetic operation

or data transfer is "0" and is cleared by any other result.

A

ACCUMULATOR

X REGISTER

Y REGISTER

STACK POINTER

PROGRAM COUNTER

PROGRAM STATUS

WORD

X

Y

SP

PCL

PCH

PSW

Two 8-bit Registers can be used as a "YA" 16-bit Register

Y

A

Y

A

SP

0

Stack Address (000

H

~ 07F

H

)

15

0

8

7

Hardware fixed

HMS87C130XA/120XA/110XA

Apr. 2001 ver1.0

23

Figure 8-3 PSW (Program Status Word) Register

[Interrupt disable flag I]

This flag enables/disables all interrupts except interrupt

caused by Reset or software BRK instruction. All inter-

rupts are disabled when cleared to "0". This flag immedi-

ately becomes "0" when an interrupt is served. It is set by

the EI instruction and cleared by the DI instruction.

[Half carry flag H]

After operation, this is set when there is a carry from bit 3

of ALU or there is no borrow from bit 4 of ALU. This bit

can not be set or cleared except CLRV instruction with

Overflow flag (V).

[Break flag B]

This flag is set by software BRK instruction to distinguish

BRK from TCALL instruction with the same vector ad-

dress.

[Overflow flag V]

This flag is set to "1" when an overflow occurs as the result

of an arithmetic operation involving signs. An overflow

occurs when the result of an addition or subtraction ex-

ceeds +127(7F

H

) or -128(80

H

). The CLRV instruction

clears the overflow flag. There is no set instruction. When

the BIT instruction is executed, bit 6 of memory is copied

to this flag.

[Negative flag N]

This flag is set to match the sign bit (bit 7) status of the re-

sult of a data or arithmetic operation. When the BIT in-

struction is executed, bit 7 of memory is copied to this flag.

N

NEGATIVE FLAG

V

-

B

H

I

Z

C

MSB

LSB

RESET VALUE: 00

H

PSW

OVERFLOW FLAG

BRK FLAG

CARRY FLAG RECEIVES

ZERO FLAG

INTERRUPT ENABLE FLAG

CARRY OUT

HALF CARRY FLAG RECEIVES

CARRY OUT FROM BIT 1 OF

ADDITION OPERLANDS

24

Apr. 2001 ver 1.0

HMS87C130XA/120XA/110XA

8.2 Program Memory

A 16-bit program counter is capable of addressing up to

64K bytes, but these devices have 4K/2K bytes program

memory space only physically implemented. Accessing a

location above FFFF

H

will cause a wrap-around to 0000

H

.

Figure 8-4, shows a map of Program Memory. After reset,

the CPU begins execution from reset vector which is stored

in address FFFE

H

and FFFF

H

as shown in Figure 8-5.

As shown in Figure 8-4, each area is assigned a fixed loca-

tion in Program Memory. Program Memory area contains

the user program.

Figure 8-4 Program Memory Map

Page Call (PCALL) area contains subroutine program to

reduce program byte length by using 2 bytes PCALL in-

stead of 3 bytes CALL instruction. If it is frequently called,

it is more useful to save program byte length.

Table Call (TCALL) causes the CPU to jump to each

TCALL address, where it commences the execution of the

service routine. The Table Call service area spaces 2-byte

for every TCALL: 0FFC0

H

for TCALL15, 0FFC2

H

for

TCALL14, etc., as shown in Figure 8-6.

Example: Usage of TCALL

The interrupt causes the CPU to jump to specific location,

where it commences the execution of the service routine.

The External interrupt 0, for example, is assigned to loca-

tion 0FFFA

H

. The interrupt service locations spaces 2-byte

interval: 0FFF8

H

and 0FFF9

H

for External Interrupt 1,

0FFFA

H

and 0FFFB

H

for External Interrupt 0, etc.

As for the area from 0FF00

H

to 0FFFF

H

, if any area of

them is not going to be used, its service location is avail-

able as general purpose Program Memory.

Figure 8-5 Interrupt Vector Area

PROGRAM

MEMORY

TCALL

AREA

INTERRUPT

VECTOR AREA

F000H

FEFFH

FF00H

FFC0H

FFDFH

FFE0H

FFFFH

PCALL

AREA

F800H

H

M

S

8

7C

1

302

A

H

M

S

8

7

C

13

04A

LDA

#5

TCALL

0FH

;

1BYTE INSTR UCTIO N

:

;

INSTEAD O F 3 BYTES

:

;

NO R M AL C ALL

;

;TABLE CALL ROUTINE

;

FUNC_A:

LDA

LRG0

RET

;

FUNC_B:

LDA

LRG1

RET

;

;TABLE CALL ADD. AREA

;

ORG

0FFC0H

;

TCALL ADDRESS AREA

DW

FUNC_A

DW

FUNC_B

1

2

0FFE0

H

E2

Address

Vector Area Memory

E4

E6

E8

EA

EC

EE

F0

F2

F4

F6

F8

FA

FC

FE

-

-

-

Basic Interval Interrupt Vector Area

A/D Converter Interrupt Vector Area

-

-

-

Timer/Counter 1 Interrupt Vector Area

Timer/Counter 0 Interrupt Vector Area

External Interrupt 0 Vector Area

-

RESET Vector Area

External Interrupt 1 Vector Area

-

Watchdog Timer Interrupt Vector Area

"-" means reserved area.

NOTE:

HMS87C130XA/120XA/110XA

Apr. 2001 ver1.0

25

Figure 8-6 PCALL and TCALL Memory Area

PCALL

rel

4F35

PCALL 35H

TCALL

n

4A

TCALL

4

0FFC0

H

C1

Address

Program Memory

C2

C3

C4

C5

C6

C7

C8

0FF00

H

Address

PCALL Area Memory

0FFFF

H

PCALL Area

(256 Bytes)

* means that the BRK software interrupt is using

same address with TCALL0.

NOTE:

TCALL 15

TCALL 14

TCALL 13

TCALL 12

TCALL 11

TCALL 10

TCALL 9

TCALL 8

TCALL 7

TCALL 6

TCALL 5

TCALL 4

TCALL 3

TCALL 2

TCALL 1

TCALL 0 / BRK *

C9

CA

CB

CC

CD

CE

CF

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

DA

DB

DC

DD

DE

DF

4F

~

~

~

~

NEXT

35

0FF35H

0FF00H

0FFFFH

11111111 11010110

01001010

PC:

F

H

F

H

D

H

6

H

4A

~

~

~

~

25

0FFD6H

0FF00H

0FFFFH

F1

NEXT

0FFD7H

0F125H

Reverse

26

Apr. 2001 ver 1.0

HMS87C130XA/120XA/110XA

Example: The usage software example of Vector address and the initialize part.

ORG

0FFE0H

DW

NOT_USED

; (0FFE0)

DW

NOT_USED

; (0FFE2)

DW

NOT_USED

; (0FFE4)

DW

BIT_INT

; (0FFE6) Basic Interval Timer

DW

WDT_INT

; (0FFE8) Watchdog Timer

DW

AD_INT

; (0FFEA) A/D

DW

NOT_USED

; (0FFEC)

DW

NOT_USED

; (0FFEE)

DW

NOT_USED

; (0FFF0)

DW

NOT_USED

; (0FFF2)

DW

TMR1_INT

; (0FFF4) Timer-1

DW

TMR0_INT

; (0FFF6) Timer-0

DW

INT1

; (0FFF8) Int.1

DW

INT0

; (0FFFA) Int.0

DW

NOT_USED

; (0FFFC)

DW

RESET

; (0FFFE) Reset

ORG

0F000H

;********************************************

;

MAIN PROGRAM

*

;*******************************************

;

RESET:

DI

;Disable All Interrupts

LDX

#0

RAM_CLR: LDA

#0

;RAM Clear(!0000H->!007FH)

STA

{X}+

CMPX

#080H

BNE

RAM_CLR

;

LDX

#07FH

;Stack Pointer Initialize

TXSP

;

CALL

INITIAL

;

;

LDM

RA, #0

;Normal Port A

LDM

RAIO,#1000_0010B

;Normal Port Direction

LDM

RB, #0

;Normal Port B

LDM

RBIO,#0000_0010B

;Normal Port Direction

:

:

LDM

PFDR,#0

;Enable Power Fail Detector

:

:

HMS87C130XA/120XA/110XA

Apr. 2001 ver1.0

27

8.3 Data Memory

Figure 8-7 shows the internal Data Memory space availa-

ble. Data Memory is divided into two groups, a user RAM

(including Stack) and control registers.

Figure 8-7 Data Memory Map

User Memory

The HMS87C1X0XA has 128

�

8 bits for the user memory

(RAM).

Control Registers

The control registers are used by the CPU and Peripheral

function blocks for controlling the desired operation of the

device. Therefore these registers contain control and status

bits for the interrupt system, the timer/ counters, analog to

digital converters and I/O ports. The control registers are in

address range of 0C0

H

to 0FF

H

.

Note that unoccupied addresses may not be implemented

on the chip. Read accesses to these addresses will in gen-

eral return random data, and write accesses will have an in-

determinate effect.

More detailed informations of each register are explained

in each peripheral section.

Note: Write only registers can not be accessed by bit ma-

nipulation instruction. Do not use read-modify-write

instruction. Use byte manipulation instruction.

Example; To write at CKCTLR

LDM

CKCTLR,#09H ;Divide ratio

�

16

USER

MEMORY

CONTROL

REGISTERS

0000H

00BFH

00C0H

00FFH

PAGE0

(including STACK)

007FH

0080H

Address

Symbol

R/W

RESET

Value

Addressing

m ode

0C0H

0C1H

0C2H

0C3H

0C4H

0C5H

0C6H

0C7H

0CAH

0CBH

0CCH

RA

RAIO

RB

RBIO

RC

RCIO

RD

RDIO

RAFUNC

RBFUNC

PUPSEL

R/W

W

R/W

W

R/W

W

R/W

W

W

W

W

Undefined

0000_0000

Undefined

0000_0000

Undefined

----_--00

Undefined

----_0000

0000_0000

0000_0000

----_0000

byte, bit

1

byte

2

byte, bit

byte

byte, bit

byte

byte, bit

byte

byte

byte

byte

0D0H

0D1H

0D1H

0D1H

0D2H

0D3H

0D3H

0D4H

0D4H

0D4H

0D5H

TM0

T0

TDR0

CDR0

TM1

TDR1

T1PPR

T1

CDR1

T1PDR

PWM0HR

R/W

R

W

R

R/W

W

W

R

R

R/W

W

--00_0000

0000_0000

1111_1111

0000_0000

0000_0000

1111_1111

1111_1111

0000_0000

0000_0000

0000_0000

----_0000

byte, bit

byte

byte

byte

byte, bit

byte

byte

byte

byte

byte, bit

byte

0DEH

BUR

W

1111_1111

byte

0E2H

0E3H

0E4H

0E5H

0E6H

0EAH

0EBH

0ECH

0ECH

0EDH

0EDH

0EFH

IENH

IENL

IRQH

IRQL

IEDS

ADCM

ADCR

BITR

CKCTLR

WDTR

WDTR

PFDR

R/W

R/W

R/W

R/W

R/W

R/W

R

R

W

R

W

R/W

0000_----

000-_----

0000_----

000-_----

----_0000

--00_0001

Undefined

0000_0000

-001_0111

0000_0000

0111_1111

----_0100

byte, bit

byte, bit

byte, bit

byte, bit

byte, bit

byte, bit

byte

byte

byte

byte

byte

byte, bit

Table 8-1 Control Registers

1. "byte, bit" means that register can be addressed by not only bit

but byte manipulation instruction.

2. "byte" means that register can be addressed by only byte

manipulation instruction. On the other hand, do not use any

read-modify-write instruction such as bit manipulation for

clearing bit.

28

Apr. 2001 ver 1.0

HMS87C130XA/120XA/110XA

Note: Several names are given at same address. Refer to

below table.

Stack Area

The stack provides the area where the return address is

saved before a jump is performed during the processing

routine at the execution of a subroutine call instruction or

the acceptance of an interrupt.

When returning from the processing routine, executing the

subroutine return instruction [RET] restores the contents of

the program counter from the stack; executing the interrupt

return instruction [RETI] restores the contents of the pro-

gram counter and flags.

The save/restore locations in the stack are determined by

the stack pointed (SP). The SP is automatically decreased

after the saving, and increased before the restoring. This

means the value of the SP indicates the stack location

number for the next save.

Addr.

When read

When write

Timer

Mode

Capture

Mode

PWM

Mode

Timer

Mode

PWM

Mode

D1H

T0

CDR0

-

TDR0

-

D3H

-

TDR1

T1PPR

D4H

T1

CDR1

T1PDR

-

T1PDR

ECH

BITR

CKCTLR

Table 8-2 Various Register Name in Same Address

HMS87C130XA/120XA/110XA

Apr. 2001 ver1.0

29

Address

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

C0H

RA

RA Port Data Register

C1H

RAIO

RA Port Direction Register

C2H

RB

RB Port Data Register

C3H

RBIO

RB Port Direction Register

C4H

RC

RC Port Data Register

C5H

RCIO

RC Port Direction Register

C6H

RD

RD Port Data Register

C7H

RDIO

RD Port Direction Register

CAH

RAFUNC

ANSEL7

ANSEL6

ANSEL5

ANSEL4

ANSEL3

ANSEL2

ANSEL1

ANSEL0

CBH

RBFUNC

TMR2OV

EC1I

PWM1O

PWM0O

INT1I

INT0I

BUZO

AVREFS

CCH

PUPSEL

-

-

-

-

PUPSEL3 PUPSEL2 PUPSEL1 PUPSEL0

D0H

TM0

-

-

CAP0

T0CK2

T0CK1

T0CK0

T0CN

T0ST

D1H

T0/TDR0/

CDR0

Timer0 Register / Timer0 Data Register / Capture0 Data Register

D2H

TM1

POL

16BIT

PWM0E

CAP1

T1CK1

T1CK0

T1CN

T1ST

D3H

TDR1/

T1PPR

Timer1 Data Register / PWM0 Period Register

D4H

T1/CDR1/

T1PDR

Timer1 Register / Capture1 Data Register / PWM0 Duty Register

D5H

PWM0HR

PWM0 High Register

DEH

BUR

BUCK1

BUCK0

BUR5

BUR4

BUR3

BUR2

BUR1

BUR0

E2H

IENH

INT0E

INT1E

T0E

T1E

-

-

-

-

E3H

IENL

ADE

WDTE

BITE

-

-

-

-

-

E4H

IRQH

INT0IF

INT1IF

T0IF

T1IF

-

-

-

-

E5H

IRQL

ADIF

WDTIF

BITIF

-

-

-

-

-

E6H

IEDS

-

-

-

-

IED1H

IED1L

IED0H

IED0L

EAH

ADCM

-

-

ADEN

ADS2

ADS1

ADS0

ADST

ADSF

EBH

ADCR

ADC Result Data Register

ECH

BITR

1

Basic Interval Timer Data Register

ECH

CKCTLR

1

-

WAKEUP

RCWDT

WDTON

BTCL

BTS2

BTS1

BTS0

EDH

WDTR

WDTCL

7-bit Watchdog Counter Register

EFH

PFDR

2

-

-

-

-

PFDOPR

PFDIS

PFDM

PFDS

Table 8-3 Control Registers of HMS87C1X0XA

These registers of shaded area can not be accessed by bit manipulation instruction as "SET1, CLR1", but should be accessed by

register operation instruction as "LDM dp,#imm".

1.The register BITR and CKCTLR are located at same address. Address ECH is read as BITR, written to CKCTLR.

2.The register PFDR only be implemented on devices, not on In-circuit Emulator.

30

Apr. 2001 ver 1.0

HMS87C130XA/120XA/110XA

8.4 Addressing Mode

The HMS87C1X0XA uses six addressing modes;

� Register addressing

� Immediate addressing

� Direct page addressing

� Absolute addressing

� Indexed addressing

� Register-indirect addressing

(1) Register Addressing

Register addressing accesses the A, X, Y, C and PSW.

(2) Immediate Addressing

#imm

In this mode, second byte (operand) is accessed as a data

immediately.

Example:

0435

ADC

#35H

E45535

LDM

35H,#55H

(3) Direct Page Addressing

dp

In this mode, a address is specified within direct page.

Example;

C535

LDA

35H

;A

RAM[35H]

(4) Absolute Addressing

!abs

Absolute addressing sets corresponding memory data to

Data, i.e. second byte(Operand I) of command becomes

lower level address and third byte (Operand II) becomes

upper level address.

With 3 bytes command, it is possible to access to whole

memory area.

ADC, AND, CMP, CMPX, CMPY, EOR, LDA, LDX,

LDY, OR, SBC, STA, STX, STY

Example;

0735F0

ADC

!0F035H

;A

ROM[0F035H]

35

A+35H+C

A

04

MEMORY

E4

0F100

H

data

55H

~

~

~

~

data

0035

H

35

0F102

H

55

0F101

H

data

35

0035

H

0F551

H

data

A

~

~

~

~

C5

0F550

H

07

0F100

H

~

~

~

~

data

0F035

H

F0

0F102

H

35

0F101

H

A+data+C

A

address: 0F035

HMS87C130XA/120XA/110XA

Apr. 2001 ver1.0

31

The operation within data memory (RAM)

ASL, BIT, DEC, INC, LSR, ROL, ROR

Example; Addressing accesses the address 0135

H

.

983500

INC

!0035H

;A

RAM[035H]

(5) Indexed Addressing

X indexed direct page (no offset)

{X}

In this mode, a address is specified by the X register.

ADC, AND, CMP, EOR, LDA, OR, SBC, STA, XMA

Example; X=15

H

D4

LDA

{X}

;ACC

RAM[X].

X indexed direct page, auto increment

{X}+

In this mode, a address is specified within direct page by

the X register and the content of X is increased by 1.

LDA, STA

Example; X=35

H

DB

LDA

{X}+

X indexed direct page (8 bit offset)

dp+X

This address value is the second byte (Operand) of com-

mand plus the data of

-register. And it assigns the mem-

ory in Direct page.

ADC, AND, CMP, EOR, LDA, LDY, OR, SBC, STA

STY, XMA, ASL, DEC, INC, LSR, ROL, ROR

Example; X=015

H

C645

LDA

45H+X

98

0F100

H

~

~

~

~

data

0035

H

00

0F102

H

35

0F101

H

data+1

data

address: 0035

data

D4

15

H

0F550

H

data

A

~

~

~

~

data

DB

35

H

data

A

~

~

~

~

36H

X

data

45

5A

H

0F551

H

data

A

~

~

~

~

C6

0F550

H

45H+15H=5AH

32

Apr. 2001 ver 1.0

HMS87C130XA/120XA/110XA

Y indexed direct page (8 bit offset)

dp+Y

This address value is the second byte (Operand) of com-

mand plus the data of Y-register, which assigns Memory in

Direct page.

This is same with above (2). Use Y register instead of X.

Y indexed absolute

!abs+Y

Sets the value of 16-bit absolute address plus Y-register

data as Memory. This addressing mode can specify mem-

ory in whole area.

Example; Y=55

H

D500FA

LDA

!0FA00H+Y

(6) Indirect Addressing

Direct page indirect

[dp]

Assigns data address to use for accomplishing command

which sets memory data(or pair memory) by Operand.

Also index can be used with Index register X,Y.

JMP, CALL

Example;

3F35

JMP

[35H]

X indexed indirect

[dp+X]

Processes memory data as Data, assigned by 16-bit pair

m e m o r y w h i c h i s d e t e r m i n e d b y p a i r d a t a

[dp+X+1][dp+X] Operand plus

X-register data in Direct

page.

ADC, AND, CMP, EOR, LDA, OR, SBC, STA

Example; X=10

H

1625

ADC

[25H+X]

D5

0F100

H

data

A

~

~

~

~

data

0FA55

H

0FA00H+55H=0FA55H

FA

0F102

H

00

0F101

H

0A

35

H

jump to address 0F30A

H

~

~

~

~

35

0FA00

H

F3

36

H

3F

0F30A

H

NEXT

~

~

~

~

05

35

H

0F405

H

~

~

~

~

25

0FA00

H

F4

36

H

16

0F405

H

data

~

~

~

~

A + data + C

A

25 + X(10) = 35

H

HMS87C130XA/120XA/110XA

Apr. 2001 ver1.0

33

Y indexed indirect

[dp]+Y

Processes memory data as Data, assigned by the data

[dp+1][dp] of 16-bit pair memory paired by Operand in Di-

rect page

plus Y-register data.

ADC, AND, CMP, EOR, LDA, OR, SBC, STA

Example; Y=10

H

1725

ADC

[25H]+Y

Absolute indirect

[!abs]

The program jumps to address specified by 16-bit absolute

address.

JMP

Example;

1F25F0

JMP

[!0F025H]

05

25

H

0F705

H

+ Y(10) = 0F715

H

~

~

~

~

25

0FA00

H

F7

26

H

17

0F715

H

data

~

~

~

~

A + data + C

A

25

0F025

H

jump to

~

~

~

~

F0

0FA00

H

F8

0F026

H

25

0F825

H

NEXT

~

~

~

~

1F

PROGRAM MEMORY

address 0F80A

H

34

Apr. 2001 ver 1.0

HMS87C130XA/120XA/110XA

9. I/O PORTS

The HMS87C1X0XA has four ports, RA, RB, RC and RD.

These ports pins may be multiplexed with an alternate

function for the peripheral features on the device. In gen-

eral, when a initial reset state, all ports are used as a general

purpose input port.

All pins have data direction registers which can set these

ports as output or input. An "1" in the port direction regis-

ter defines the corresponding port pin as output. Converse-

ly, write "0" to the corresponding bit to specify as an input

pin. For example, to use the even numbered bit of RA as

output ports and the odd numbered bits as input ports, write

"55

H

" to address C1

H

(RA direction register) during initial

setting as shown in Figure 9-1.

Reading data register reads the status of the pins whereas

writing to it will write to the port latch.

Figure 9-1 Example of port I/O assignment

9.1 RA and RAIO registers

RA is an 8-bit bidirectional I/O port (address C0

H

). Each

port can be set individually as input and output through the

RAIO register (address C1

H

).

RA1~RA7 ports are multiplexed with Analog Input Port

(AN1~AN7) and RA0 port is multiplexed with Event

Counter Input Port (EC0)

.

Figure 9-2 Registers of Port RA

The control register RAFUNC (address CA

H

) controls to

select alternate function. After reset, this value is "0", port

may be used as general I/O ports. To select alternate func-

tion such as Analog Input or External Event Counter Input,

write "1" to the corresponding bit of RAFUNC.Regardless

of the direction register RAIO, RAFUNC is selected to use

as alternate functions, port pin can be used as a correspond-

ing alternate features (RA0/EC0 is controlled by RB-

FUNC)

I: INPUT PORT

WRITE "55H" TO PORT RA DIRECTION REGISTER

0

1

0

1

0

1

0

1

I

O

I

O

I

O

I

O

RA DATA

RB DATA

RA DIRECTION

RB DIRECTION

C0H

C1H

C2H

C3H

7

6

5

4

3

2

1

0

BIT

7

6

5

4

3

2

1

0 PORT

O: OUTPUT PORT

RA7 RA6 RA5 RA4 RA3 RA2 RA1 RA0

INPUT / OUTPUT DATA

0 : INPUT PORT

1 : OUTPUT PORT

DIRECTION SELECT

RA Data Register

RA

ADDRESS : C0H

RESET VALUE : Undefined

RA Direction Register

RAIO

ADDRESS : C1H

RESET VALUE : 00000000

ANSEL0

RA Function Selection Register

RAFUNC

ADDRESS : CAH

RESET VALUE : 00000000

ANSEL7

ANSEL1

ANSEL2

ANSEL3

ANSEL4

ANSEL5

ANSEL6

0 : RB0

1 : AN0

0 : RA1

1 : AN1

0 : RA2

1 : AN2

0 : RA3

1 : AN3

0 : RA4

1 : AN4

0 : RA5

1 : AN5

0 : RA6

1 : AN6

0 : RA7

1 : AN7

PORT

RAFUNC.7~0

Description

RA7/AN7

0

RA7 (Normal I/O Port)

1

AN7 (ADS2~0=111)

RA6/AN6

0

RA6 (Normal I/O Port)

1

AN6 (ADS2~0=110)

RA5/AN5

0

RA5 (Normal I/O Port)

1

AN5 (ADS2~0=101)

RA4/AN4

0

RA4 (Normal I/O Port)

1

AN4 (ADS2~0=100)

RA3/AN3

0

RA3 (Normal I/O Port)

1

AN3 (ADS2~0=011)

RA2/AN2

0

RA2 (Normal I/O Port)

1

AN2 (ADS2~0=010)

RA1/AN1

0

RA1 (Normal I/O Port)

1

AN1 (ADS2~0=001)

RA0/EC0

1

1. This port is not an Analog Input port, but Event Counter clock

source input port. EC0 is controlled by setting TOCK2~0 = 111.

The bit RAFUNC.0 (ANSEL0) controls the RB0/AN0/AVref port

(Refer to Port RB).

RA0 (Normal I/O Port)

EC0 (T0CK2~0=111)

HMS87C130XA/120XA/110XA

Apr. 2001 ver1.0

35

9.2 RB and RBIO registers

RB is a 5-bit bidirectional I/O port (address C2

H

). Each pin

can be set individually as input and output through the

RBIO register (address C3

H

). In addition, Port RB is mul-

tiplexed with various special features. The control register

RBFUNC (address CB

H

) controls to select alternate func-

tion. After reset, this value is "0", port may be used as gen-

eral I/O ports. To select alternate function such as External

interrupt or Timer compare output, write "1" to the corre-

sponding bit of RBFUNC.

Regardless of the direction register RBIO, RBFUNC is se-

lected to use as alternate functions, port pin can be used as

a corresponding alternate features.

And RB2/INT0, RB3/INT1 have a function of pull-up

transistor by setting the PUPSEL0 and PUPSEL1 of

PUPSEL register.

Figure 9-3 Registers of Port RB

-

RB4

RB3 RB2 RB1 RB0

INPUT / OUTPUT DATA

0 : INPUT PORT

1 : OUTPUT PORT

DIRECTION SELECT

RB Data Register

RB

ADDRESS : C2H

RESET VALUE : Undefined

RB Direction Register

RBIO

ADDRESS : C3H

RESET VALUE : ---00000

AVREFS

RB Function Selection Register

RBFUNC

ADDRESS : CBH

RESET VALUE : ---00000

BUZO

INT0I

INT1I

PWM0O

0 : RB0 when ANSEL0 = 0

1 : AV

REF

0 : RB1

1 : BUZ Output

0 : RB4

1 : PWM0 Output or

0 : RB2

1 : INT0

0 : RB3

1 : INT1

PUPSEL0

Pull-up Selection Register

PUPSEL

ADDRESS : CCH

RESET VALUE : ----0000

-

PUPSEL1

-

-

-

0 : No Pull-up

1 : With Pull-up

0 : No Pull-up

1 : With Pull-up

IED0L

Interrupt Edge Selection Register

IEDS

ADDRESS : E6H

RESET VALUE : ----0000

IED0H

IED1L

IED1H

External Interrupt Edge Select

INT0

INT1

00 : Normal I/O port

01 : Falling (1-to-0 transition)

10 : Rising (0-to-1 transition)

11 : Both (Rising & Falling)

Compare Output

RB0 / INT0 Pull-up

RB1 / INT1 Pull-up

AN0 when ANSEL0 = 1

-

-

-

-

-

-

-

-

-

-

-

-

-

-

36

Apr. 2001 ver 1.0

HMS87C130XA/120XA/110XA

9.3 RC and RCIO registers

RC is a 2-bit bidirectional I/O port (address C4

H

). Each

pin can be set individually as input and output through the

RCIO register (address C5

H

).

Figure 9-4 Registers of Port RC

PORT

RBFUNC.4~0

Description

RB4/

PWM0/

COMP0

0

RB4 (Normal I/O Port)

1

PWM0 Output /

Timer1 Compare Output

RB3/INT1

0

RB3 (Normal I/O Port)

1

External Interrupt Input 1

RB2/INT0

0

RB2 (Normal I/O Port)

1

External Interrupt Input 0

RB1/BUZ

0

RB1 (Normal I/O Port)

1

Buzzer Output

RB0/AN0/

AV

REF

0

1

1. When ANSEL0 = "0", this port is defined for normal I/O port

(RB0).

When ANSEL0 = "1" and ADS2~0 = "000", this port can be

used Analog Input Port (AN0).

RB0 (Normal I/O Port)/

AN0 (ANSEL0=1)

1

2

2. When this bit set to "1", this port defined for AV

REF

, so it can

not be used Analog Input Port AN0 and Normal I/O Port

RB0.

External Analog Reference

Voltage

-

RC1

RC0

INPUT / OUTPUT DATA

0 : INPUT PORT

1 : OUTPUT PORT

DIRECTION SELECT

RC Data Register

RC

ADDRESS : C4H

RESET VALUE : Undefined

RC Direction Register

RCIO

ADDRESS : C5H

RESET VALUE : ------00

-

-

-

-

-

-

-

-

-

-

-

HMS87C130XA/120XA/110XA

Apr. 2001 ver1.0

37

9.4 RD and RDIO registers

RD is a 4-bit bidirectional I/O port (address C6

H

). Each

pin can be set individually as input and output through the

RDIO register (address C7

H

)

And RD0, RD1 have a function of pull-up transistor by set-

ting the PUPSEL2 and PUPSEL3 of PUPSEL register.

.

Figure 9-5 Registers of Port RD

RD2 RD1 RD0

INPUT / OUTPUT DATA

0 : INPUT PORT

1 : OUTPUT PORT

DIRECTION SELECT

RD Data Register

RD

ADDRESS : C6H

RESET VALUE : Undefined

RD Direction Register

RDIO

ADDRESS : C7H

RESET VALUE : -----0000

RD3

-

-

-

-

-

Pull-up Selection Register

PUPSEL

ADDRESS : CCH

RESET VALUE : ----0000

-

-

-

-

-

0 : No Pull-up

1 : With Pull-up

0 : No Pull-up

1 : With Pull-up

RD0 Pull-up

RD1 Pull-up

PUPSEL2

PUPSEL3

-

-

-

-

38

Apr. 2001 ver 1.0

HMS87C130XA/120XA/110XA

10. CLOCK GENERATOR

The clock generator produces the basic clock pulses which

provide the system clock to be supplied to the CPU and pe-

ripheral hardware.

The main system clock oscillator oscillates

with a crystal resonator or a ceramic resonator

connected to the

Xin and Xout pins. External clocks can be input to the main

system clock oscillator. In this case, input a clock signal to

the Xin pin and open the Xout pin.

Figure 10-1 Block Diagram of Clock Pulse Generator