KEY FEATURES

n

Single Power Supply Operation

≠ Read, program and erase operations from

2.7 to 3.6 volts

≠ Ideal for battery-powered applications

n

High Performance

≠ 70, 80, 90 and 120 ns access time

versions

n

Ultra-low Power Consumption (Typical

Values At 5 Mhz)

≠ Automatic sleep mode current: 1 µA

≠ Standby mode current: 1 µA

≠ Read current: 9 mA

≠ Program/erase current: 20 mA

n

Flexible Sector Architecture:

≠ One 16 KB, two 8 KB, one 32 KB and

thirty-one 64 KB sectors in byte mode

≠ One 8 KW, two 4 KW, one 16 KW and

thirty-one 32 KW sectors in word mode

≠ Top or bottom boot block configurations

available

n

Sector Protection

≠ Allows locking of a sector or sectors to

prevent program or erase operations

within that sector

≠ Sectors lockable in-system or via

programming equipment

≠ Temporary Sector Unprotect allows

changes in locked sectors (requires high

voltage on RESET# pin)

n

Fast Program and Erase Times

≠ Sector erase time: 0.25 sec typical for

each sector

≠ Chip erase time: 8 sec typical

≠ Byte program time: 9

µ

s typical

n

Unlock Bypass Program Command

≠ Reduces programming time when issuing

multiple program command sequences

n

Automatic Erase Algorithm Preprograms

and Erases Any Combination of Sectors

or the Entire Chip

n

Erase Suspend/Erase Resume

≠ Suspends an erase operation to allow

reading data from, or programming data

to, a sector that is not being erased

≠ Erase Resume can then be invoked to

complete suspended erasure

n

Automatic Program Algorithm Writes and

Verifies Data at Specified Addresses

Preliminary

Revision 1.2, May 2001

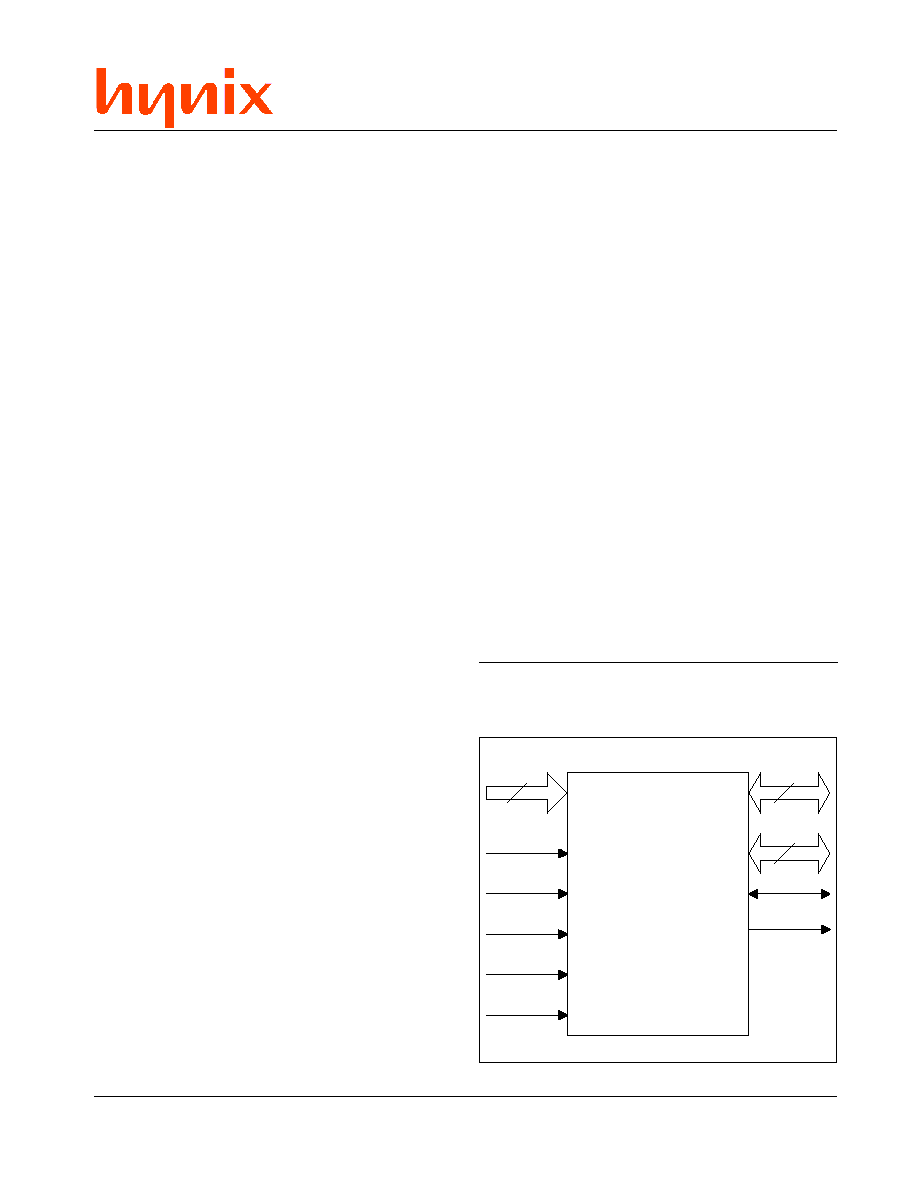

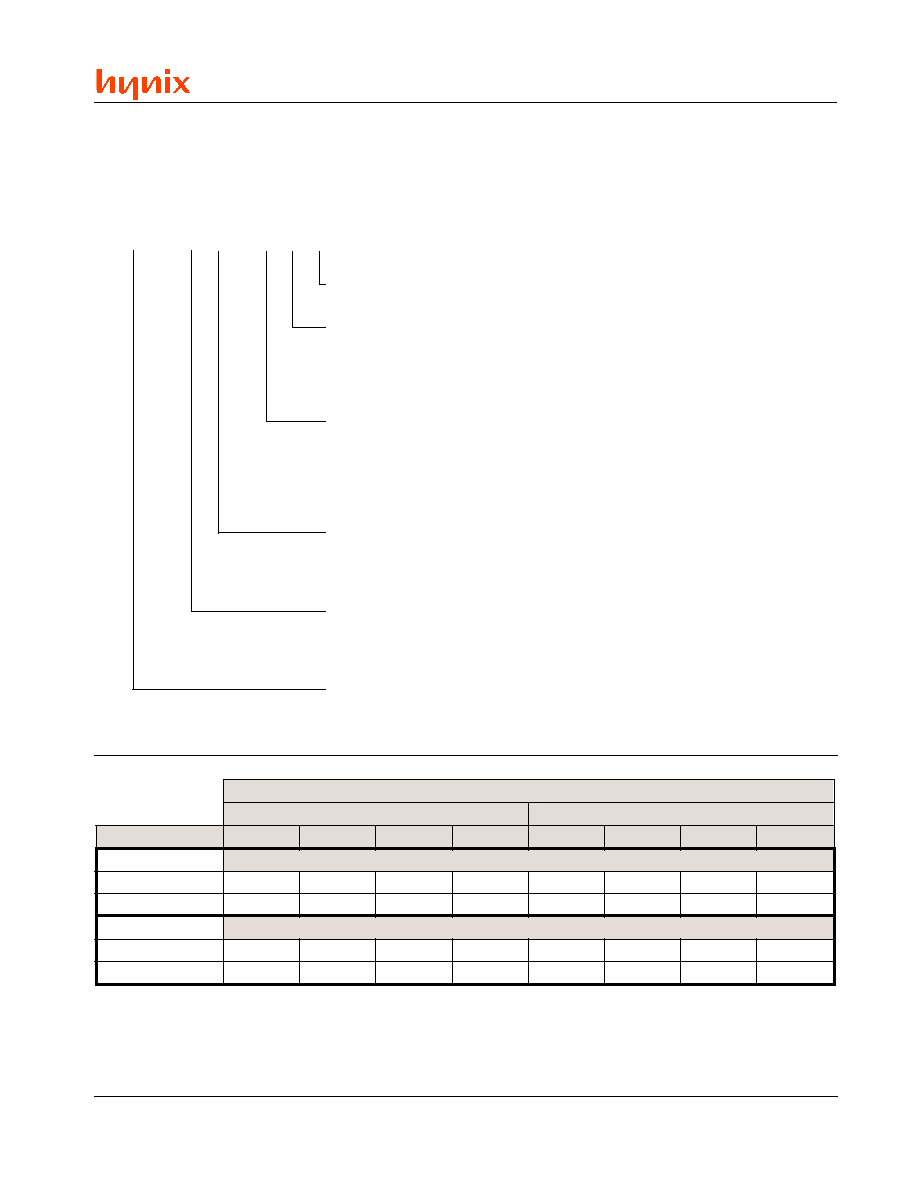

A[19:0]

2 0

C E #

O E #

R E S E T #

B Y T E #

W E #

8

7

D Q [ 7 : 0 ]

D Q [ 1 4 : 8 ]

D Q 1 5 / A - 1

R Y / B Y #

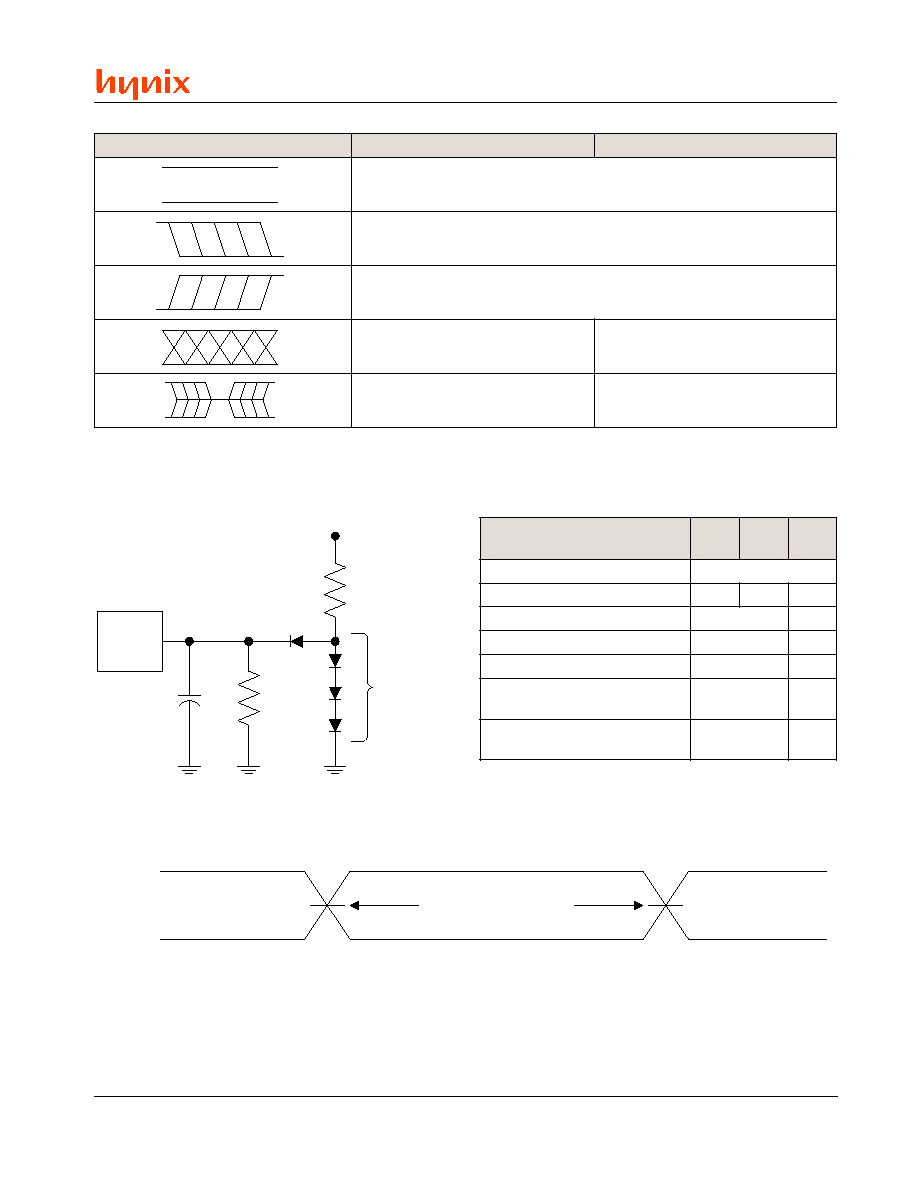

LOGIC DIAGRAM

n

100,000 Write Cycles per Sector Minimum

n

Data# Polling and Toggle Bits

≠ Provide software confirmation of

completion of program and erase

operations

n

Ready/Busy# Pin

≠ Provides hardware confirmation of

completion of program and erase

operations

n

Hardware Reset Pin (RESET#) Resets the

Device to Reading Array Data

n

Compliant With Common Flash Memory

Interface (CFI) Specification

≠ Flash device parameters stored directly

on the device

≠ Allows software driver to identify and use

a variety of different current and future

Flash products

n

Compatible With JEDEC standards

≠ Pinout and software compatible with

single-power supply Flash devices

≠ Superior inadvertent write protection

n

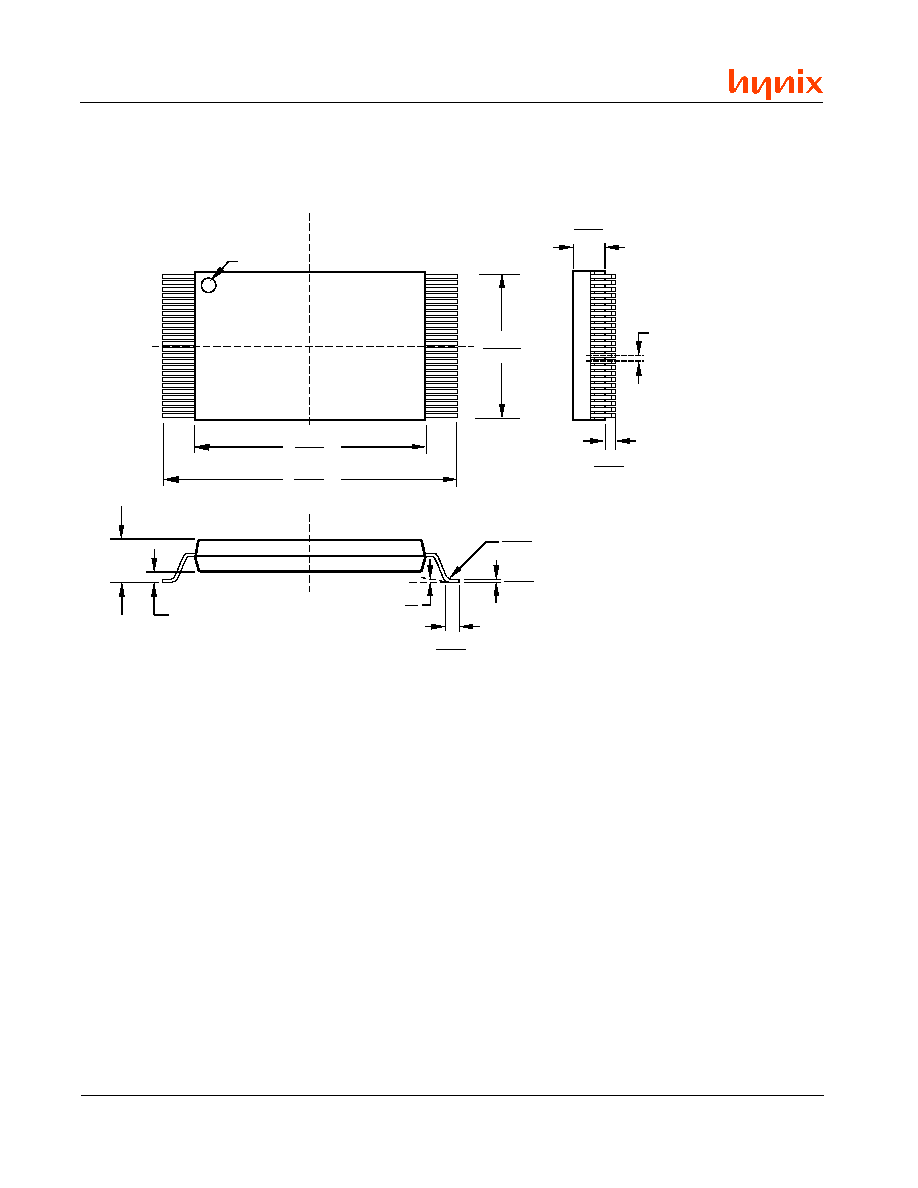

Space Efficient Packaging

≠ 48-pin TSOP and 48-ball FBGA packages

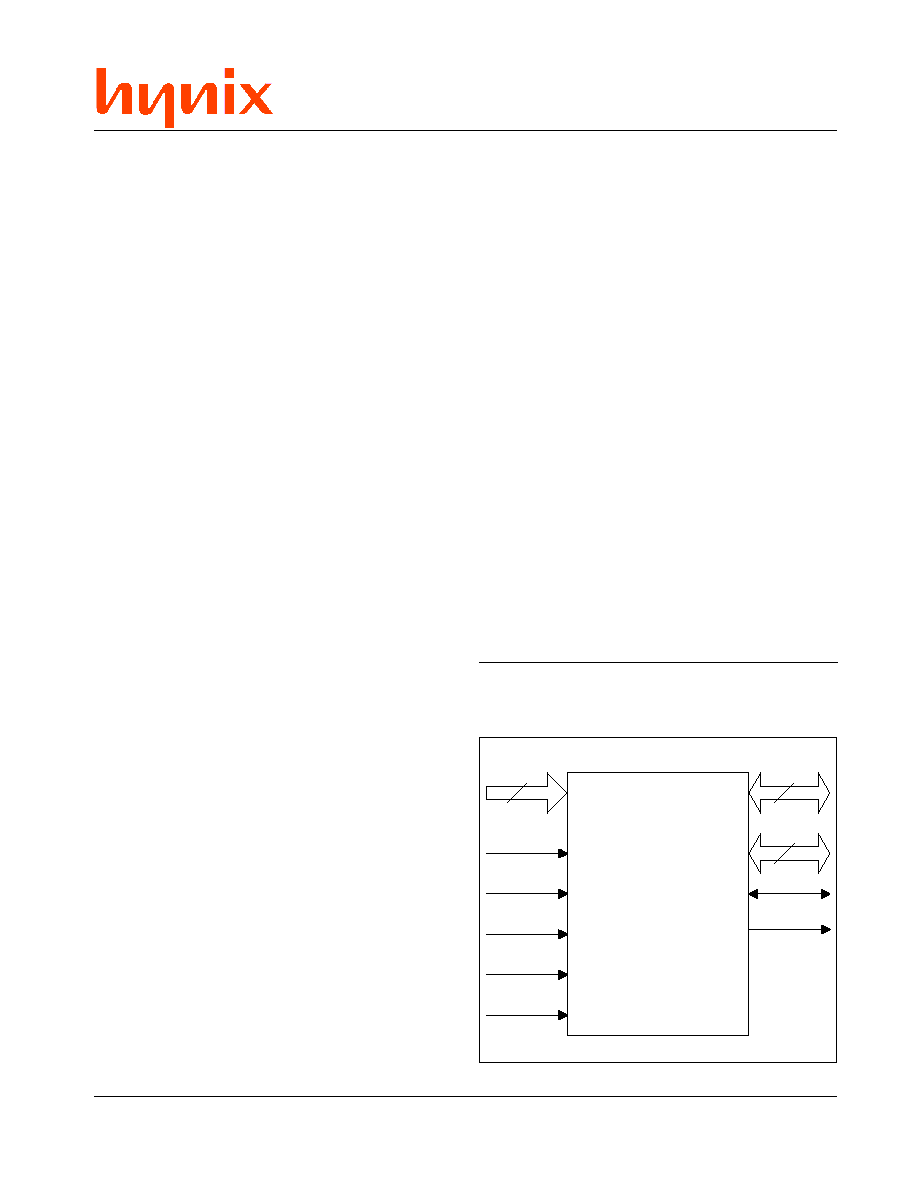

HY29LV160

16 Mbit (2M x 8/1M x 16) Low Voltage Flash Memory

2

Rev. 1.2/May 01

HY29LV160

GENERAL DESCRIPTION

The HY29LV160 is a 16 Mbit, 3 volt-only, CMOS

Flash memory organized as 2,097,152 (2M) bytes

or 1,048,576 (1M) words that is available in 48-

pin TSOP and 48-ball FBGA packages. Word-

wide data (x16) appears on DQ[15:0] and byte-

wide (x8) data appears on DQ[7:0].

The HY29LV160 can be programmed and erased

in-system with a single 3 volt V

CC

supply. Inter-

nally generated and regulated voltages are pro-

vided for program and erase operations, so that

the device does not require a higher voltage V

PP

power supply to perform those functions. The de-

vice can also be programmed in standard EPROM

programmers. Access times as low as 80 ns over

the full operating voltage range of 2.7 - 3.6 volts,

and 70 ns with a limited voltage range of 3.0 - 3.6

volts, are offered for timing compatibility with the

zero wait state requirements of high speed mi-

croprocessors. To eliminate bus contention, the

HY29LV160 has separate chip enable (CE#), write

enable (WE#) and output enable (OE#) controls.

The device is compatible with the JEDEC single-

power-supply Flash memory command set stan-

dard. Commands are written to the command reg-

ister using standard microprocessor write timings.

They are then routed to an internal state-machine

that controls the erase and programming circuits.

Device programming is performed a byte/word at

a time by executing the four-cycle Program Com-

mand write sequence. This initiates an internal al-

gorithm that automatically times the program pulse

widths and verifies proper cell margin. Faster pro-

gramming times can be achieved by placing the

HY29LV160 in the Unlock Bypass mode, which

requires only two write cycles to program data in-

stead of four.

The HY29LV160's sector erase architecture allows

any number of array sectors to be erased and re-

programmed without affecting the data contents

of other sectors. Device erasure is initiated by

executing the Erase Command sequence. This

initiates an internal algorithm that automatically

preprograms the array (if it is not already pro-

grammed) before executing the erase operation.

As during programming cycles, the device auto-

matically times the erase pulse widths and veri-

fies proper cell margin. Hardware Sector Protec-

tion optionally disables both program and erase

operations in any combination of the sectors of

the memory array, while Temporary Sector Un-

protect allows in-system erasure and code

changes in previously protected sectors. Erase

Suspend enables the user to put erase on hold for

any period of time to read data from, or program

data to, any sector that is not selected for era-

sure. True background erase can thus be

achieved. The device is fully erased when shipped

from the factory.

Addresses and data needed for the programming

and erase operations are internally latched during

write cycles, and the host system can detect

completion of a program or erase operation by

observing the RY/BY# pin, or by reading the DQ[7]

(Data# Polling) or DQ[6] (Toggle) status bits. Hard-

ware data protection measures include a low V

CC

detector that automatically inhibits write operations

during power transitions.

After a program or erase cycle has been com-

pleted, or after assertion of the RESET# pin (which

terminates any operation in progress), the device

is ready to read data or to accept another com-

mand. Reading data out of the device is similar to

reading from other Flash or EPROM devices.

Two power-saving features are embodied in the

HY29LV160. When addresses have been stable

for a specified amount of time, the device enters

Automatic Sleep mode. The host can also place

the device into Standby mode. Power consump-

tion is greatly reduced in both of these modes.

Common Flash Memory Interface (CFI)

To make Flash memories interchangeable and to

encourage adoption of new Flash technologies,

major Flash memory suppliers developed a flex-

ible method of identifying Flash memory sizes and

configurations in which all necessary Flash device

parameters are stored directly on the device.

Parameters stored include memory size, byte/word

configuration, sector configuration, necessary volt-

ages and timing information. This allows one set

of software drivers to identify and use a variety of

different current and future Flash products. The

standard which details the software interface nec-

essary to access the device to identify it and to

determine its characteristics is the Common Flash

Memory Interface (CFI) Specification. The

HY29LV160 is fully compliant with this specification.

3

Rev. 1.2/May 01

HY29LV160

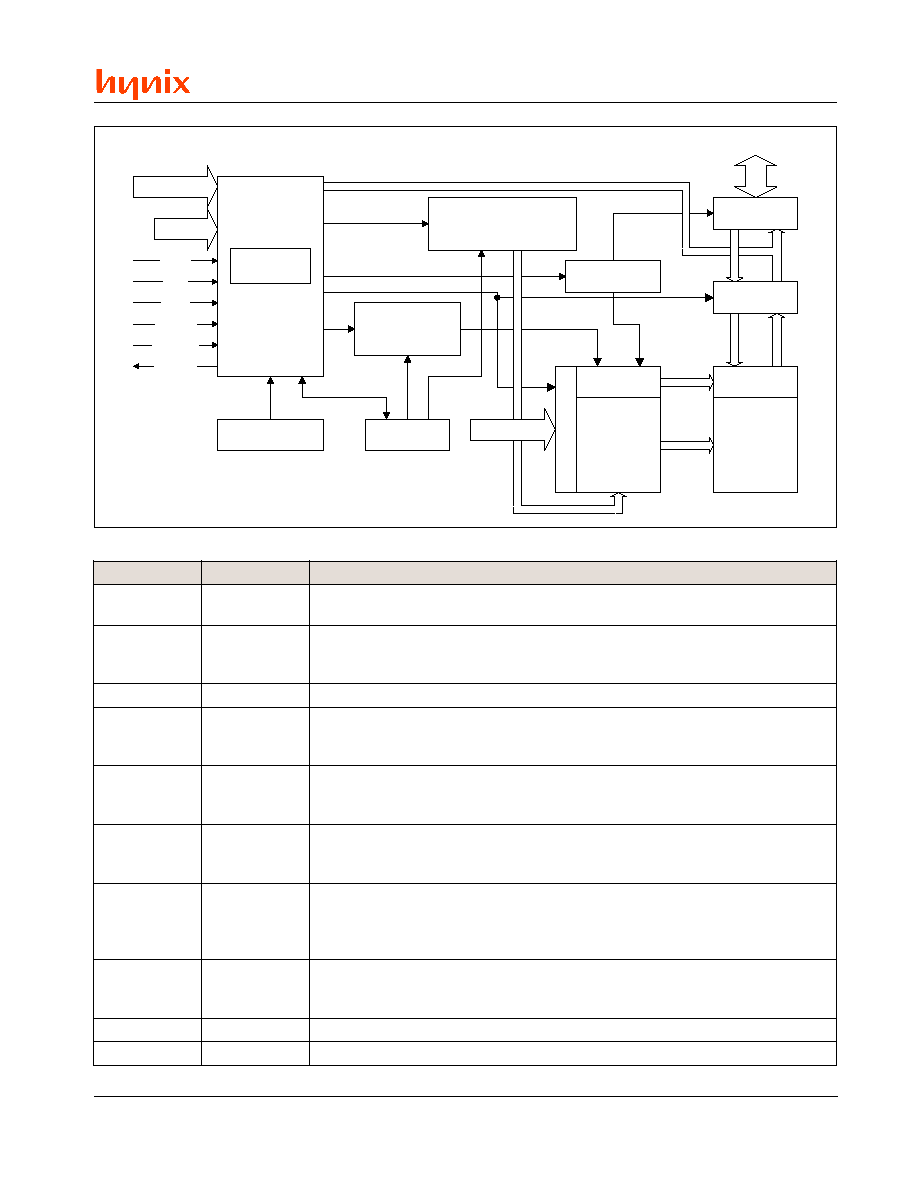

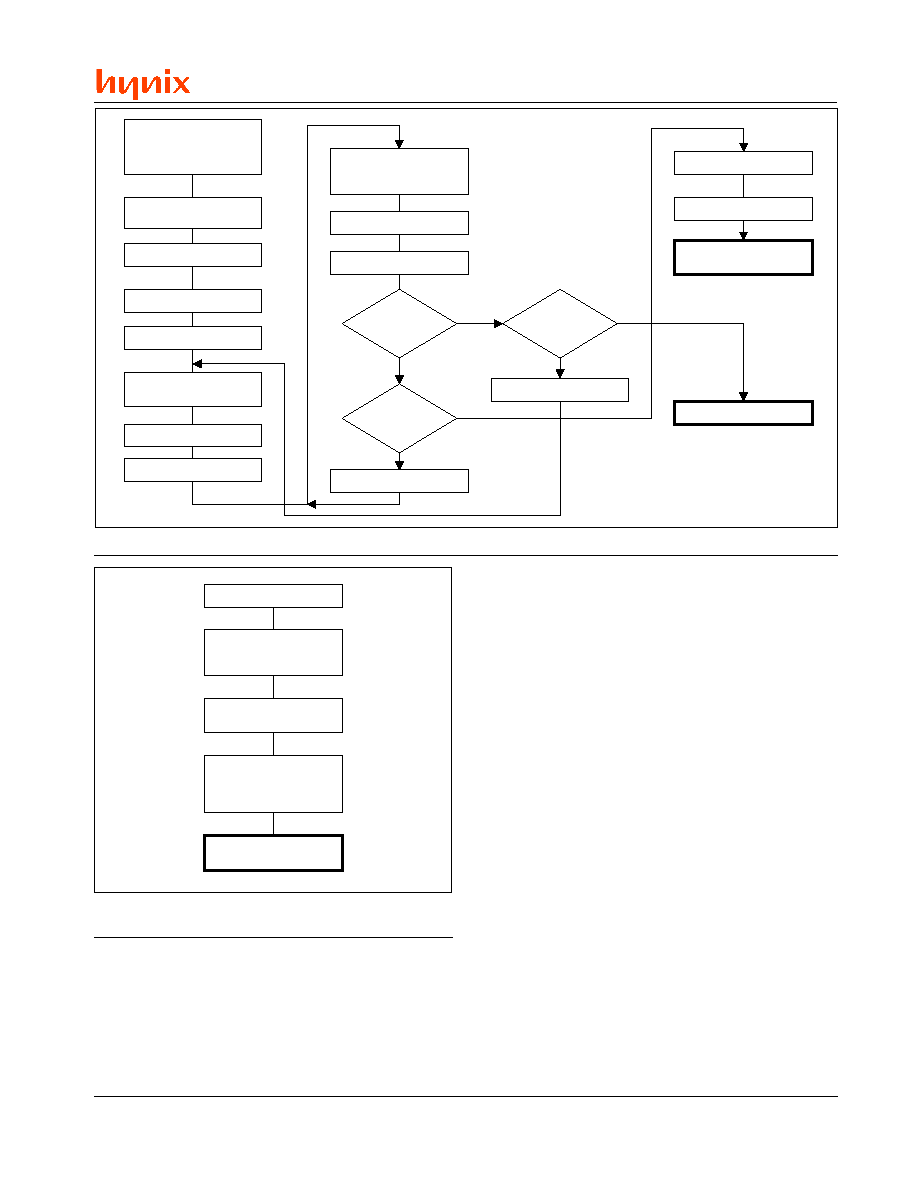

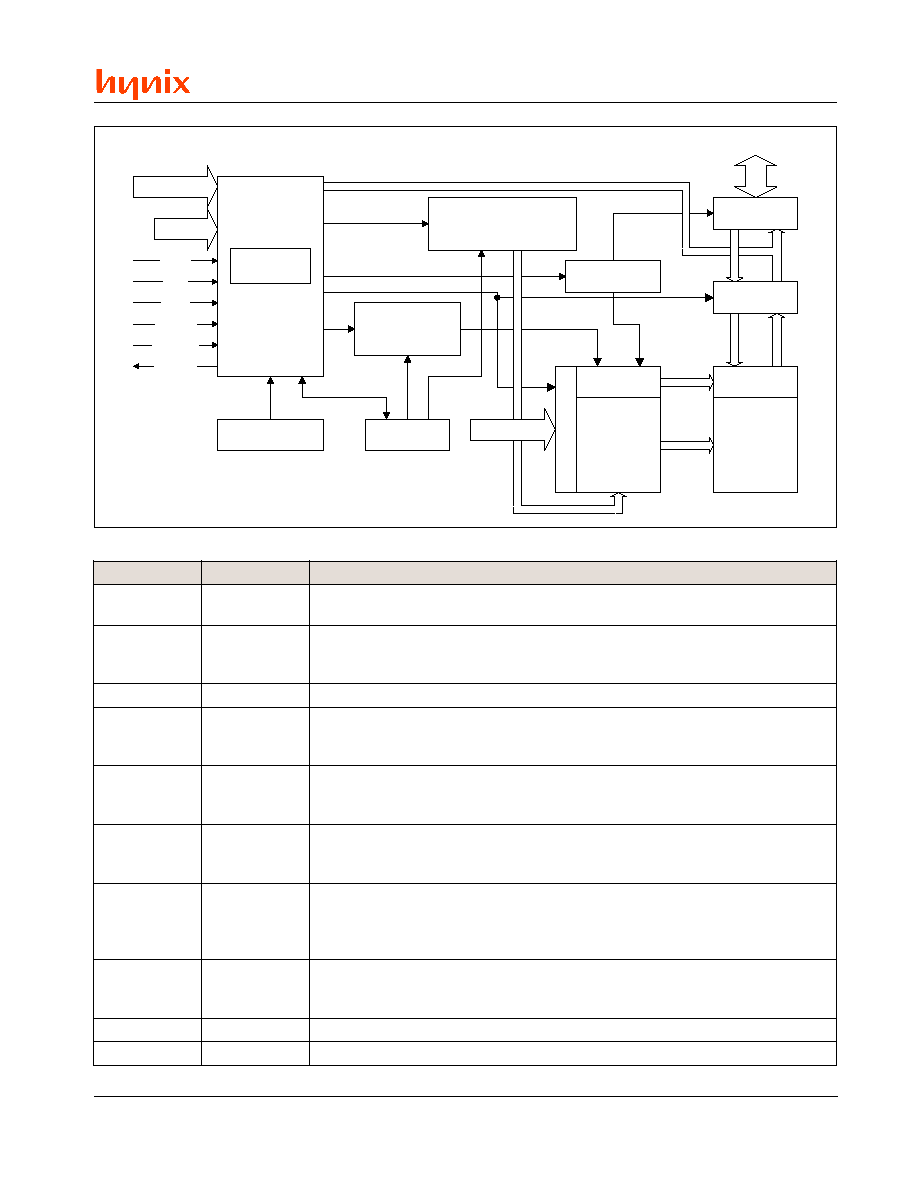

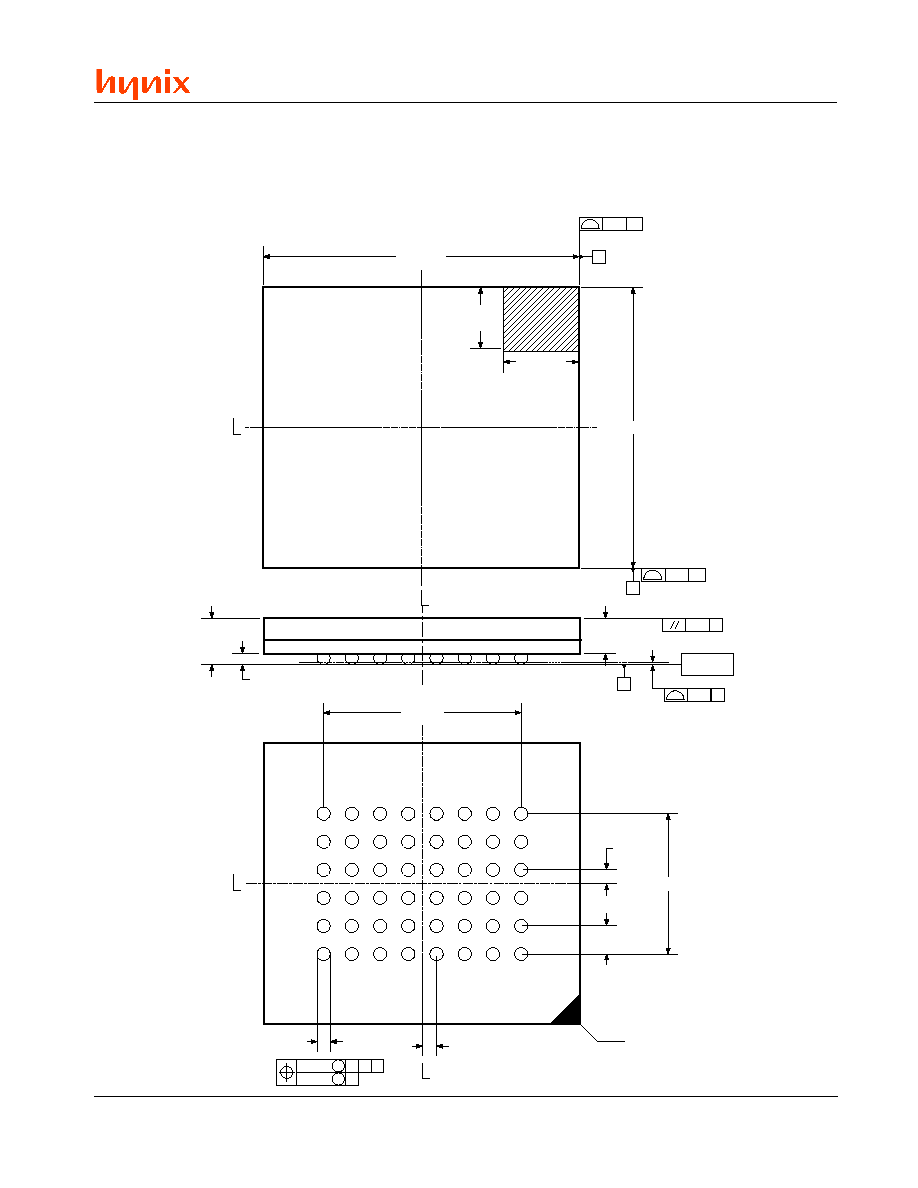

BLOCK DIAGRAM

STATE

C O N T R O L

W E #

C E #

OE#

BYTE#

C O M M A N D

R E G I S T E R

DQ[15:0]

A[19:0], A-1

V

C C

D E T E C T O R

T I M E R

E R A S E V O L T A G E

G E N E R A T O R A N D

S E C T O R S W I T C H E S

P R O G R A M

V O L T A G E

G E N E R A T O R

ADDRESS LATCH

X - D E C O D E R

Y - D E C O D E R

16 Mb FLASH

M E M O R Y

A R R A Y

Y-GATING

D A T A L A T C H

I/O BUFFERS

I/O CONTROL

R E S E T #

DQ[15:0]

A[19:0], A-1

RY/BY#

SIGNAL DESCRIPTIONS

e

m

a

N

e

p

y

T

n

o

i

t

p

i

r

c

s

e

D

]

0

:

9

1

[

A

s

t

u

p

n

I

.

h

g

i

H

e

v

i

t

c

a

,

s

s

e

r

d

d

A

n

i

t

u

p

n

i

]

1

-

[

A

/

]

5

1

[

Q

D

e

h

t

h

t

i

w

d

e

n

i

b

m

o

c

,

s

t

u

p

n

i

0

2

e

s

e

h

T

.

s

n

o

i

t

a

r

e

p

o

e

t

i

r

w

r

o

d

a

e

r

r

o

f

y

a

r

r

a

e

h

t

n

i

h

t

i

w

n

o

i

t

a

c

o

l

e

n

o

t

c

e

l

e

s

,

e

d

o

m

e

t

y

B

,

]

1

-

[

A

/

]

5

1

[

Q

D

]

0

:

4

1

[

Q

D

s

t

u

p

t

u

O

/

s

t

u

p

n

I

e

t

a

t

s

-

i

r

T

h

g

i

H

e

v

i

t

c

a

,

s

u

B

a

t

a

D

d

a

e

r

r

o

f

h

t

a

p

a

t

a

d

t

i

b

-

6

1

r

o

-

8

n

a

e

d

i

v

o

r

p

s

n

i

p

e

s

e

h

T

.

t

i

b

-

1

2

e

h

t

f

o

B

S

L

e

h

t

s

a

d

e

s

u

s

i

]

1

-

[

A

/

]

5

1

[

Q

D

,

e

d

o

m

e

t

y

B

n

I

.

s

n

o

i

t

a

r

e

p

o

e

t

i

r

w

d

n

a

.

e

d

o

m

e

t

y

B

n

i

d

e

t

a

t

s

-

i

r

t

n

i

a

m

e

r

d

n

a

d

e

s

u

n

u

e

r

a

]

8

:

4

1

[

Q

D

.

t

u

p

n

i

s

s

e

r

d

d

a

e

t

y

b

#

E

T

Y

B

t

u

p

n

I

.

w

o

L

e

v

i

t

c

a

,

e

d

o

M

e

t

y

B

.

e

d

o

m

d

r

o

W

s

t

c

e

l

e

s

h

g

i

H

,

e

d

o

m

e

t

y

B

s

t

c

e

l

e

s

w

o

L

#

E

C

t

u

p

n

I

.

w

o

L

e

v

i

t

c

a

,

e

l

b

a

n

E

p

i

h

C

r

o

m

o

r

f

a

t

a

d

d

a

e

r

o

t

d

e

t

r

e

s

s

a

e

b

t

s

u

m

t

u

p

n

i

s

i

h

T

e

h

t

d

n

a

d

e

t

a

t

s

-

i

r

t

s

i

s

u

b

a

t

a

d

e

h

t

,

h

g

i

H

n

e

h

W

.

0

6

1

V

L

9

2

Y

H

e

h

t

o

t

a

t

a

d

e

t

i

r

w

.

e

d

o

m

y

b

d

n

a

t

S

e

h

t

n

i

d

e

c

a

l

p

s

i

e

c

i

v

e

d

#

E

O

t

u

p

n

I

w

o

L

e

v

i

t

c

a

,

e

l

b

a

n

E

t

u

p

t

u

O

r

o

f

d

e

t

a

g

e

n

d

n

a

s

n

o

i

t

a

r

e

p

o

d

a

e

r

r

o

f

d

e

t

r

e

s

s

A

.

g

n

i

r

u

d

d

a

e

r

s

i

d

r

o

w

a

r

o

e

t

y

b

a

r

e

h

t

e

h

w

s

e

n

i

m

r

e

t

e

d

#

E

T

Y

B

.

s

n

o

i

t

a

r

e

p

o

e

t

i

r

w

.

n

o

i

t

a

r

e

p

o

d

a

e

r

e

h

t

#

E

W

t

u

p

n

I

.

w

o

L

e

v

i

t

c

a

,

e

l

b

a

n

E

e

t

i

r

W

s

e

c

n

e

u

q

e

s

d

n

a

m

m

o

c

r

o

s

d

n

a

m

m

o

c

f

o

g

n

i

t

i

r

w

s

l

o

r

t

n

o

C

n

o

i

t

a

r

e

p

o

e

t

i

r

w

A

.

y

a

r

r

a

y

r

o

m

e

m

e

h

t

f

o

s

r

o

t

c

e

s

e

s

a

r

e

r

o

a

t

a

d

m

a

r

g

o

r

p

o

t

r

e

d

r

o

n

i

h

g

i

H

s

i

#

E

O

d

n

a

w

o

L

s

i

#

E

C

e

li

h

w

d

e

t

r

e

s

s

a

s

i

#

E

W

n

e

h

w

e

c

a

l

p

s

e

k

a

t

.

#

T

E

S

E

R

t

u

p

n

I

.

w

o

L

e

v

i

t

c

a

,

t

e

s

e

R

e

r

a

w

d

r

a

H

e

h

t

g

n

i

t

t

e

s

e

r

f

o

d

o

h

t

e

m

e

r

a

w

d

r

a

h

a

s

e

d

i

v

o

r

P

y

l

e

t

a

i

d

e

m

m

i

t

i

,

t

e

s

e

r

s

i

e

c

i

v

e

d

e

h

t

n

e

h

W

.

e

t

a

t

s

y

a

r

r

a

d

a

e

r

e

h

t

o

t

0

6

1

V

L

9

2

Y

H

e

c

i

v

e

d

e

h

t

,

d

e

t

r

e

s

s

a

s

i

#

T

E

S

E

R

e

li

h

W

.

s

s

e

r

g

o

r

p

n

i

n

o

i

t

a

r

e

p

o

y

n

a

s

e

t

a

n

i

m

r

e

t

.

e

d

o

m

y

b

d

n

a

t

S

e

h

t

n

i

e

b

ll

i

w

#

Y

B

/

Y

R

t

u

p

t

u

O

n

i

a

r

D

n

e

p

O

.

s

u

t

a

t

S

y

s

u

B

/

y

d

a

e

R

n

i

s

i

d

n

a

m

m

o

c

e

s

a

r

e

r

o

e

t

i

r

w

a

r

e

h

t

e

h

w

s

e

t

a

c

i

d

n

I

y

l

e

v

i

t

c

a

s

i

e

c

i

v

e

d

e

h

t

e

li

h

w

w

o

L

s

n

i

a

m

e

R

.

d

e

t

e

l

p

m

o

c

n

e

e

b

s

a

h

r

o

s

s

e

r

g

o

r

p

.

a

t

a

d

y

a

r

r

a

d

a

e

r

o

t

y

d

a

e

r

s

i

t

i

n

e

h

w

h

g

i

H

s

e

o

g

d

n

a

,

g

n

i

s

a

r

e

r

o

a

t

a

d

g

n

i

m

m

a

r

g

o

r

p

V

C

C

-

-

.

y

l

p

p

u

s

r

e

w

o

p

)

l

a

n

i

m

o

n

(

t

l

o

v

-

3

V

S

S

-

-

.

d

n

u

o

r

g

l

a

n

g

i

s

d

n

a

r

e

w

o

P

4

Rev. 1.2/May 01

HY29LV160

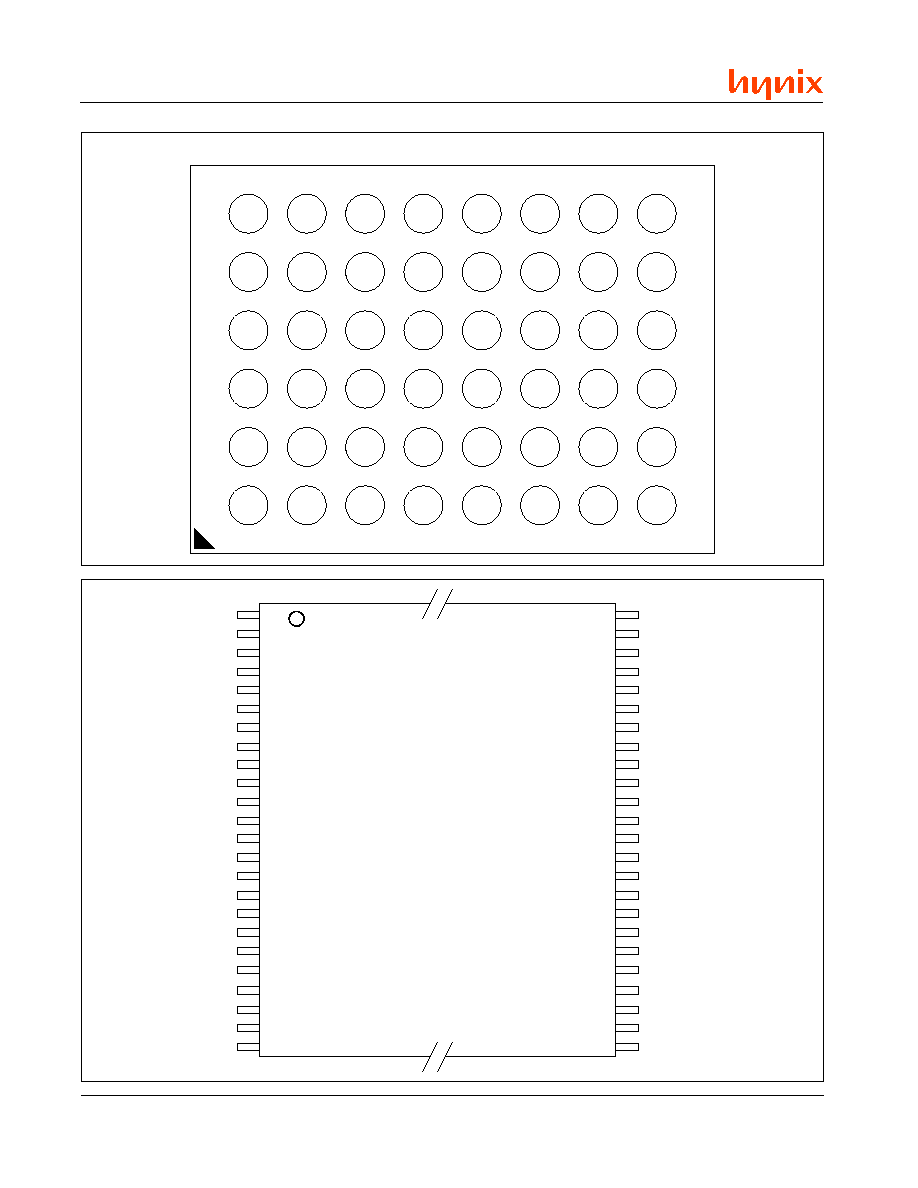

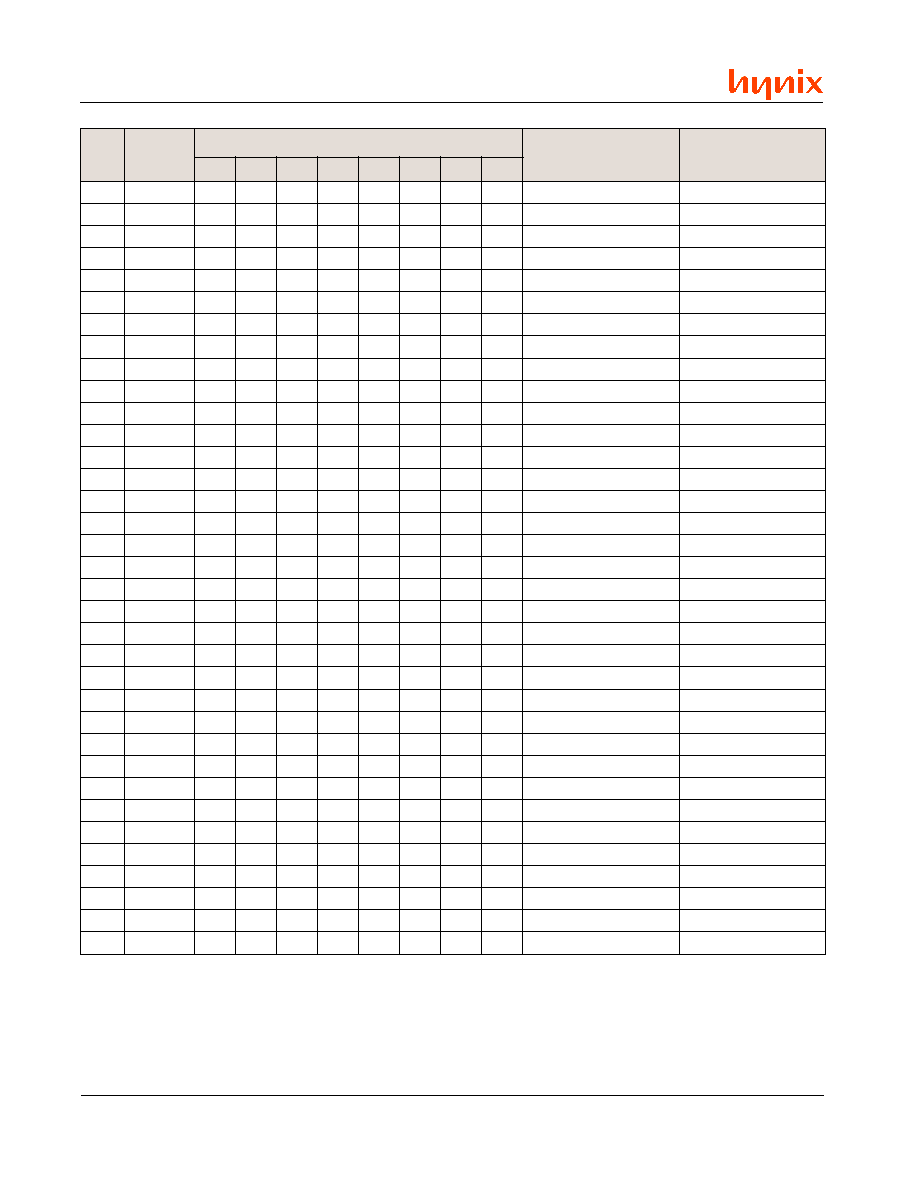

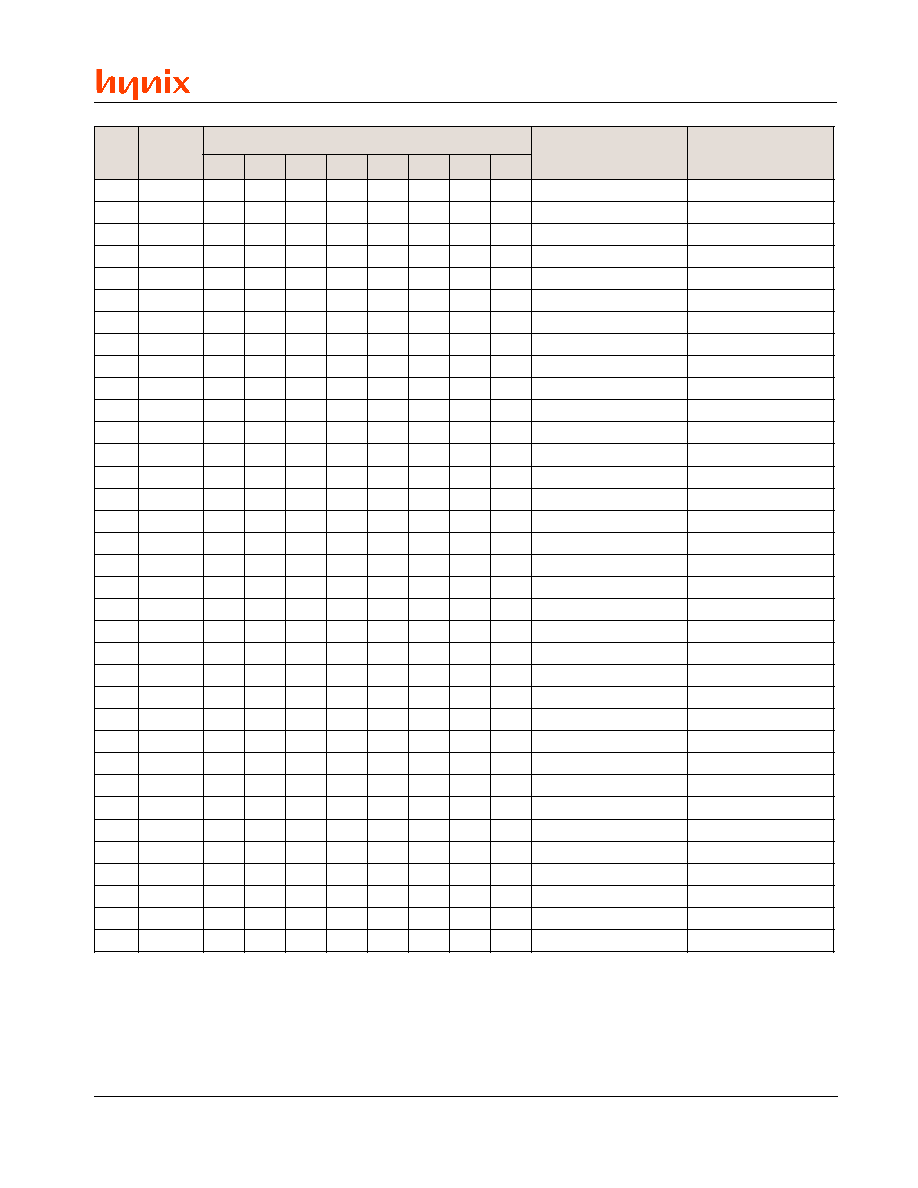

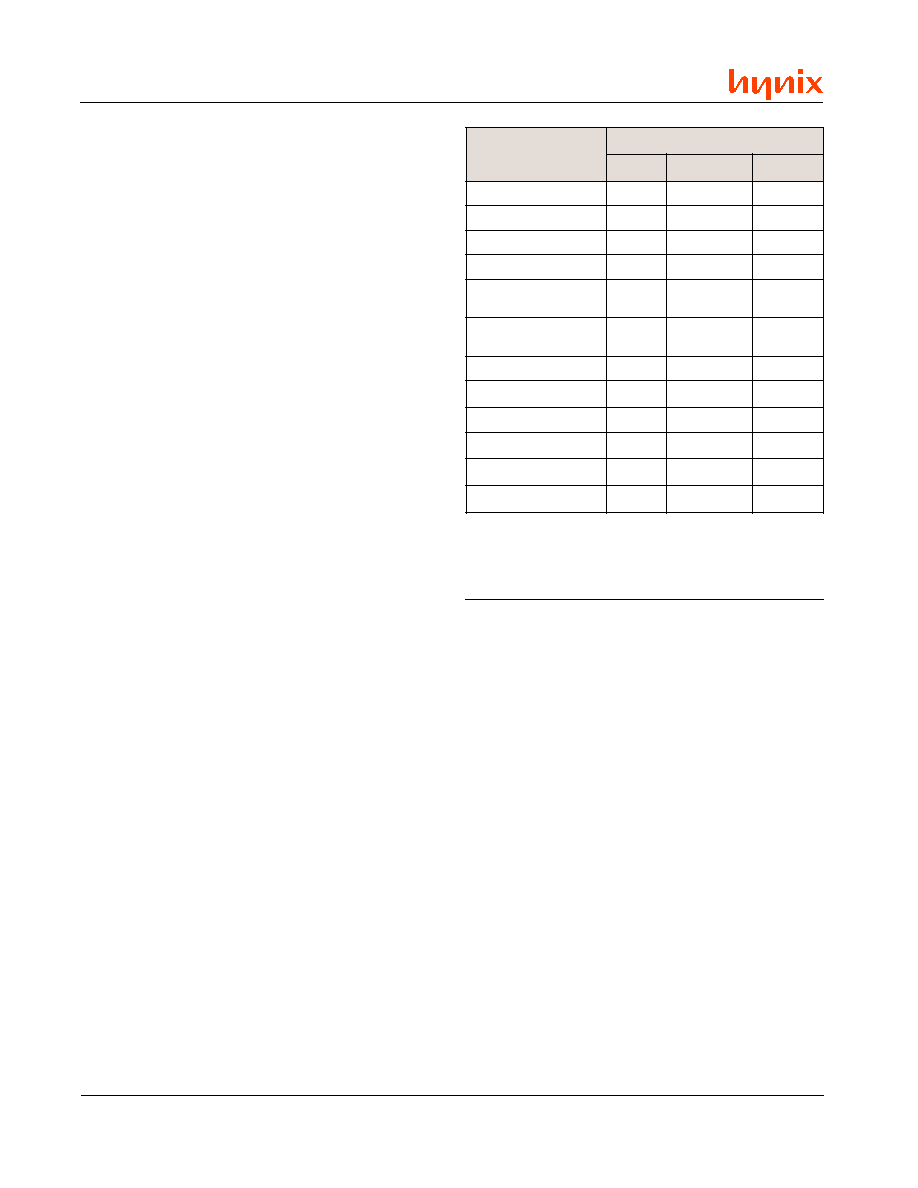

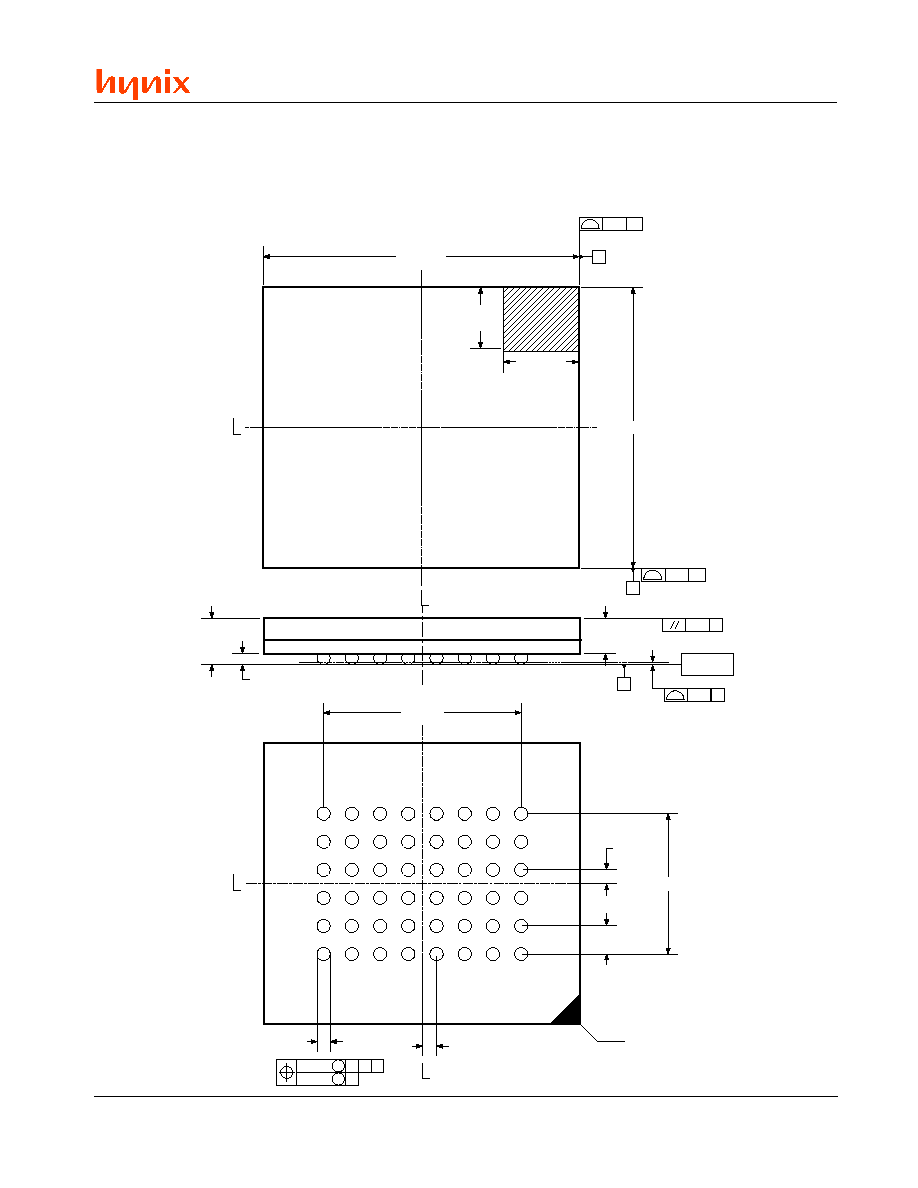

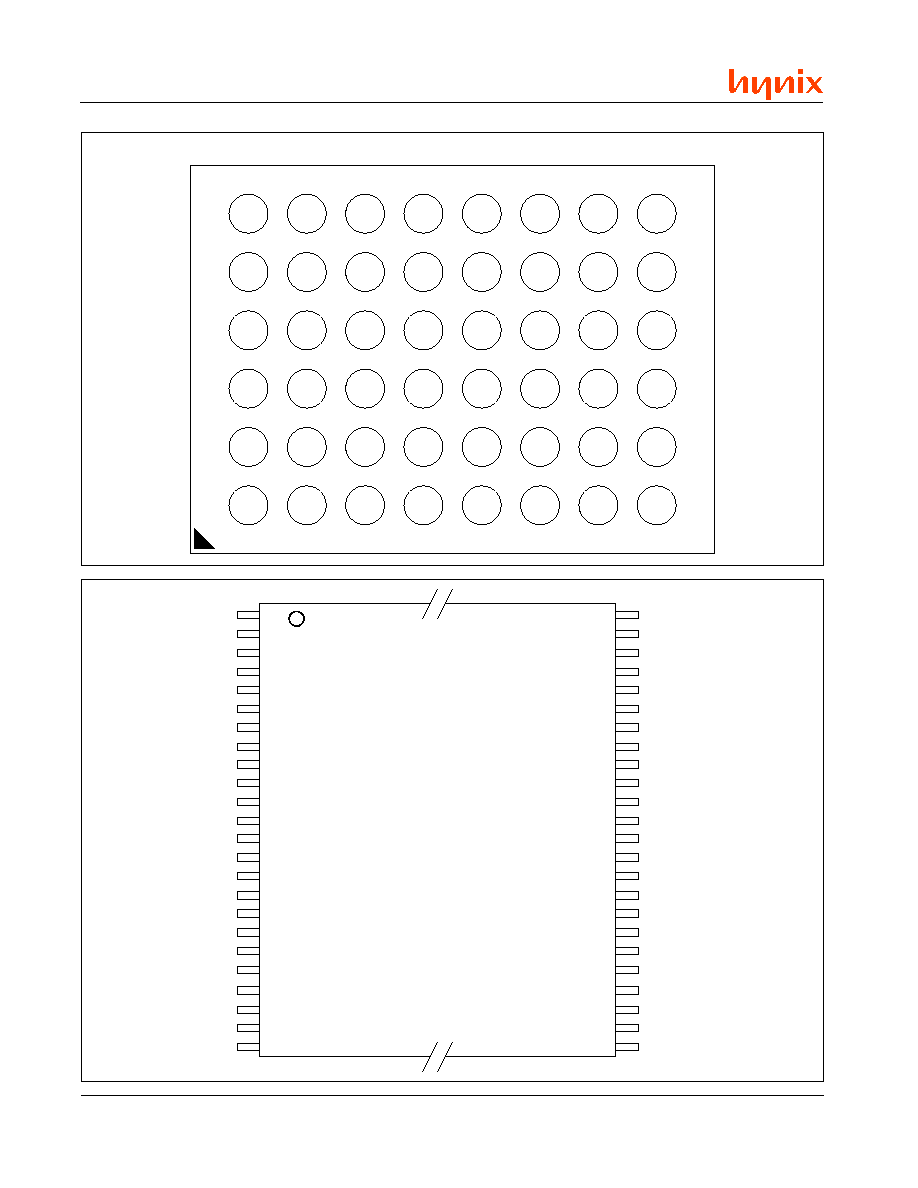

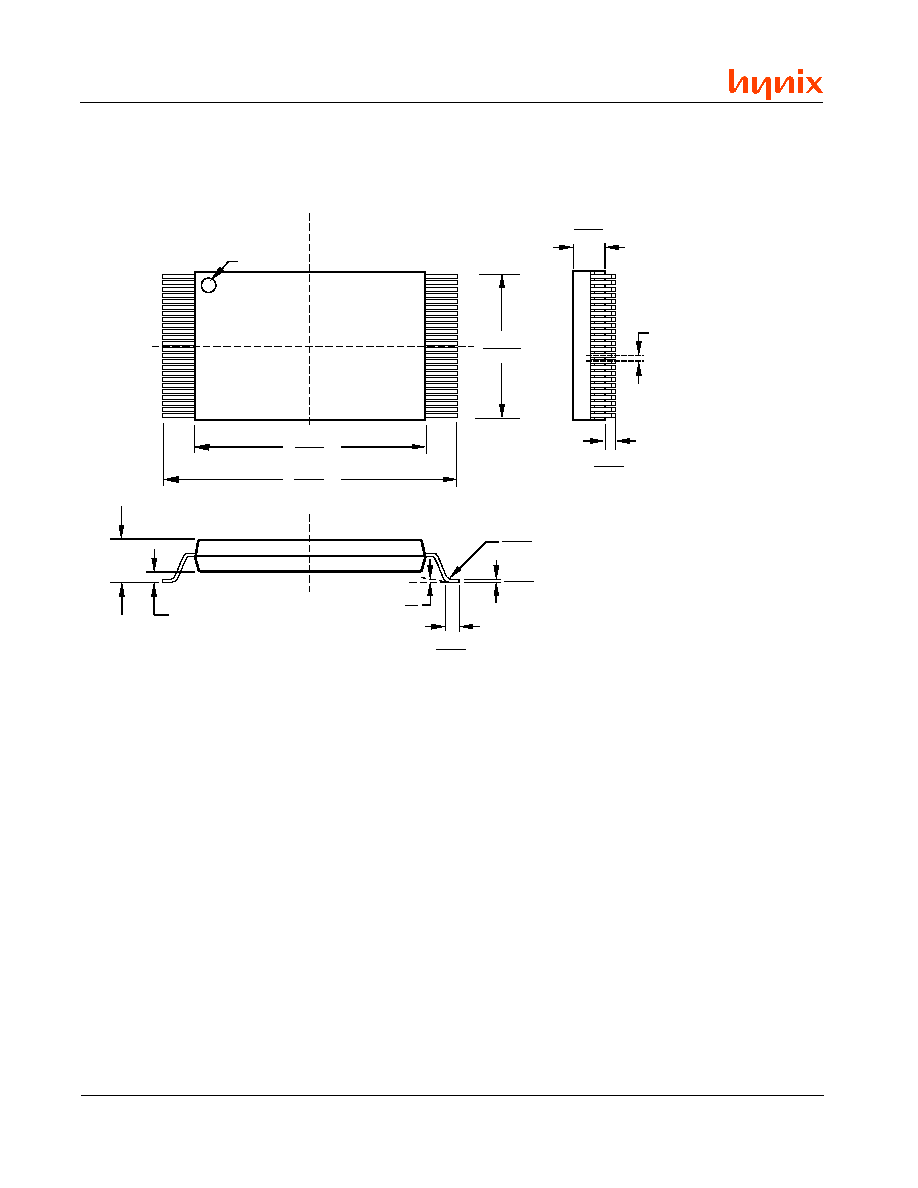

PIN CONFIGURATIONS

A 6

B 6

C 6

D 6

E 6

F 6

G 6

H 6

A 5

B 5

C 5

D 5

E 5

F 5

G 5

H 5

A 4

B 4

C 4

D 4

E 4

F 4

G 4

H 4

A 3

B 3

C 3

D 3

E 3

F 3

G 3

H 3

A 2

B 2

C 2

D 2

E 2

F 2

G 2

H 2

A 1

B 1

C 1

D 1

E 1

F 1

G 1

H 1

A [ 1 3 ]

A [ 1 2 ]

A [ 1 4 ]

A [ 1 5 ]

A [ 1 6 ]

B Y T E #

D Q [ 1 5 ] / A [ - 1 ]

V

S S

A[9]

A[8]

A[10]

A[11]

D Q [ 7 ]

D Q [ 1 4 ]

D Q [ 1 3 ]

D Q [ 6 ]

W E #

R E S E T #

N C

A [ 1 9 ]

D Q [ 5 ]

D Q [ 1 2 ]

V

C C

D Q [ 4 ]

R Y / B Y #

N C

A [ 1 8 ]

N C

D Q [ 2 ]

D Q [ 1 0 ]

D Q [ 1 1 ]

D Q [ 3 ]

A[7]

A[17]

A[6]

A[5]

D Q [ 0 ]

D Q [ 8 ]

D Q [ 9 ]

D Q [ 1 ]

A[3]

A[4]

A[2]

A[1]

A[0]

C E #

O E #

V

S S

48-Ball FBGA (Top View, Balls Facing Down)

TSOP48

A[11]

A[10]

5

6

A[9]

A[8]

7

8

A[19]

N C

9

10

W E #

RESET#

11

12

N C

N C

13

14

RY/BY#

A[18]

15

16

A[17]

A[7]

17

18

A[6]

A[5]

19

20

A[15]

A[14]

1

2

A[13]

A[12]

3

4

A[4]

A[3]

21

22

A[2]

A[1]

23

24

DQ[7]

DQ[14]

44

43

DQ[6]

DQ[13]

42

41

DQ[5]

DQ[12]

40

39

DQ[4]

V

C C

38

37

DQ[11]

DQ[3]

36

35

DQ[10]

DQ[2]

34

33

DQ[9]

DQ[1]

32

31

DQ[8]

DQ[0]

30

29

A[16]

BYTE#

48

47

V

S S

DQ[15]/A[-1]

46

45

O E #

V

S S

28

27

CE#

A[0]

26

25

5

Rev. 1.2/May 01

HY29LV160

CONVENTIONS

Unless otherwise noted, a positive logic (active

High) convention is assumed throughout this docu-

ment, whereby the presence at a pin of a higher,

more positive voltage (V

IH

) causes assertion of the

signal. A `#' symbol following the signal name, e.g.,

RESET#, indicates that the signal is asserted in

the Low state (V

IL

). See DC specifications for V

IH

and V

IL

values.

Whenever a signal is separated into numbered

bits, e.g., DQ[7], DQ[6], ..., DQ[0], the family of

bits may also be shown collectively, e.g., as

DQ[7:0].

The designation 0xNNNN (N = 0, 1, 2, . . . , 9, A, .

. . , E, F) indicates a number expressed in hexadeci-

mal notation. The designation 0bXXXX indicates a

number expressed in binary notation (X = 0, 1).

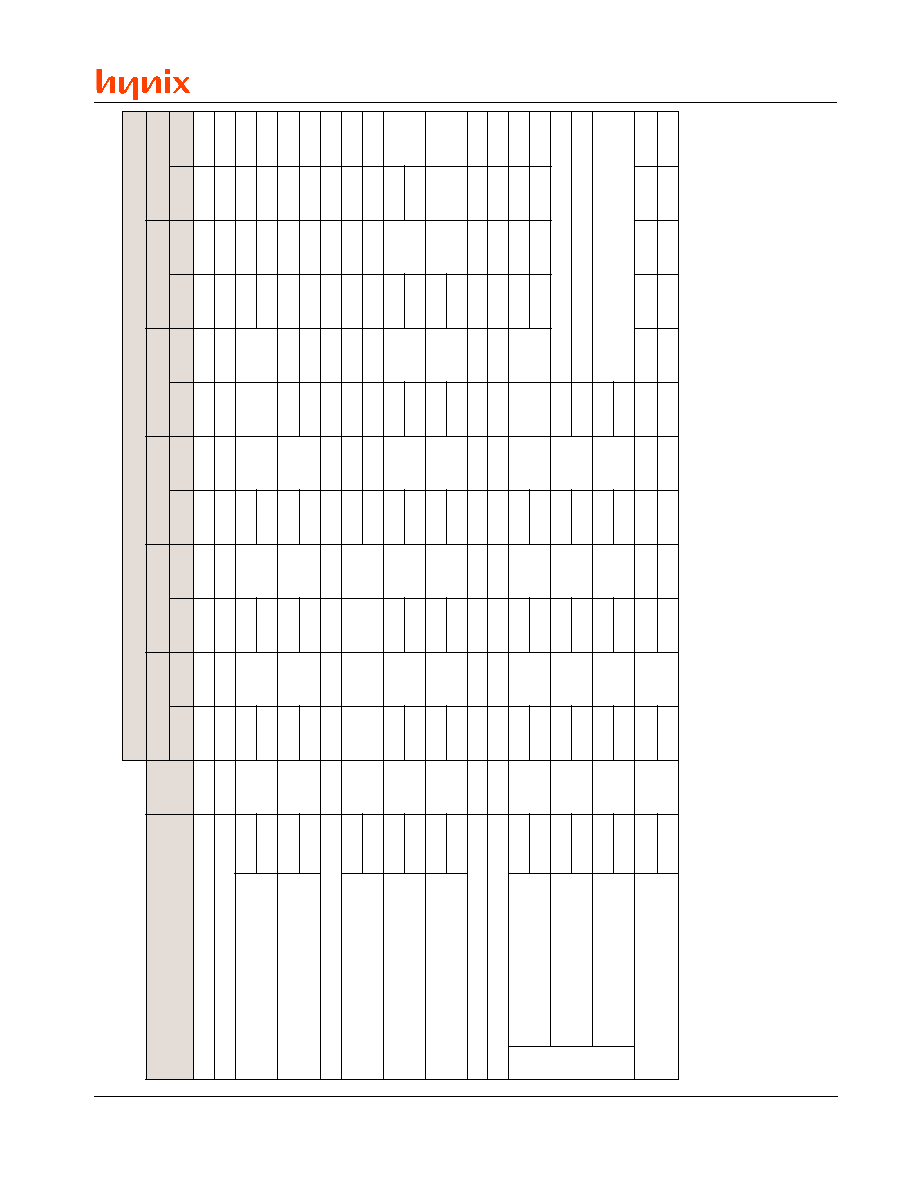

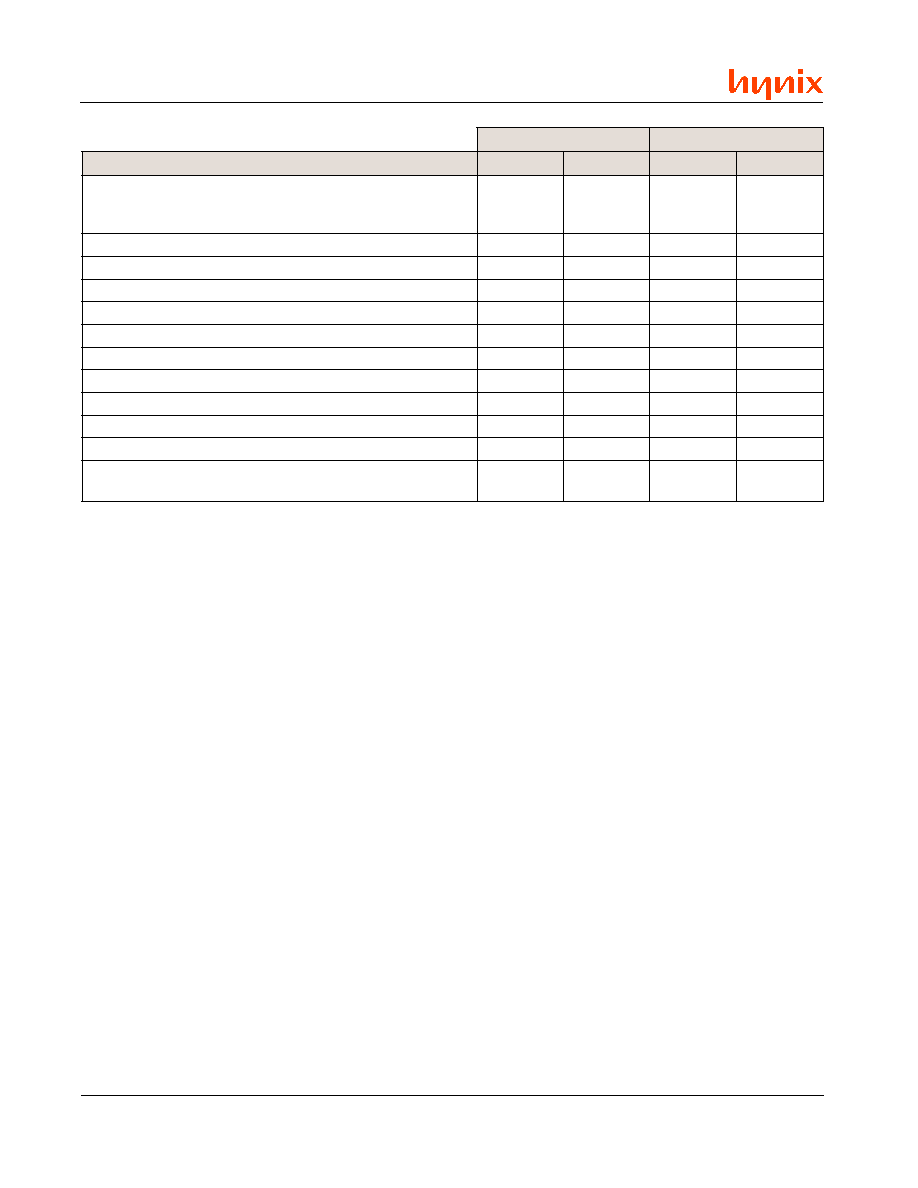

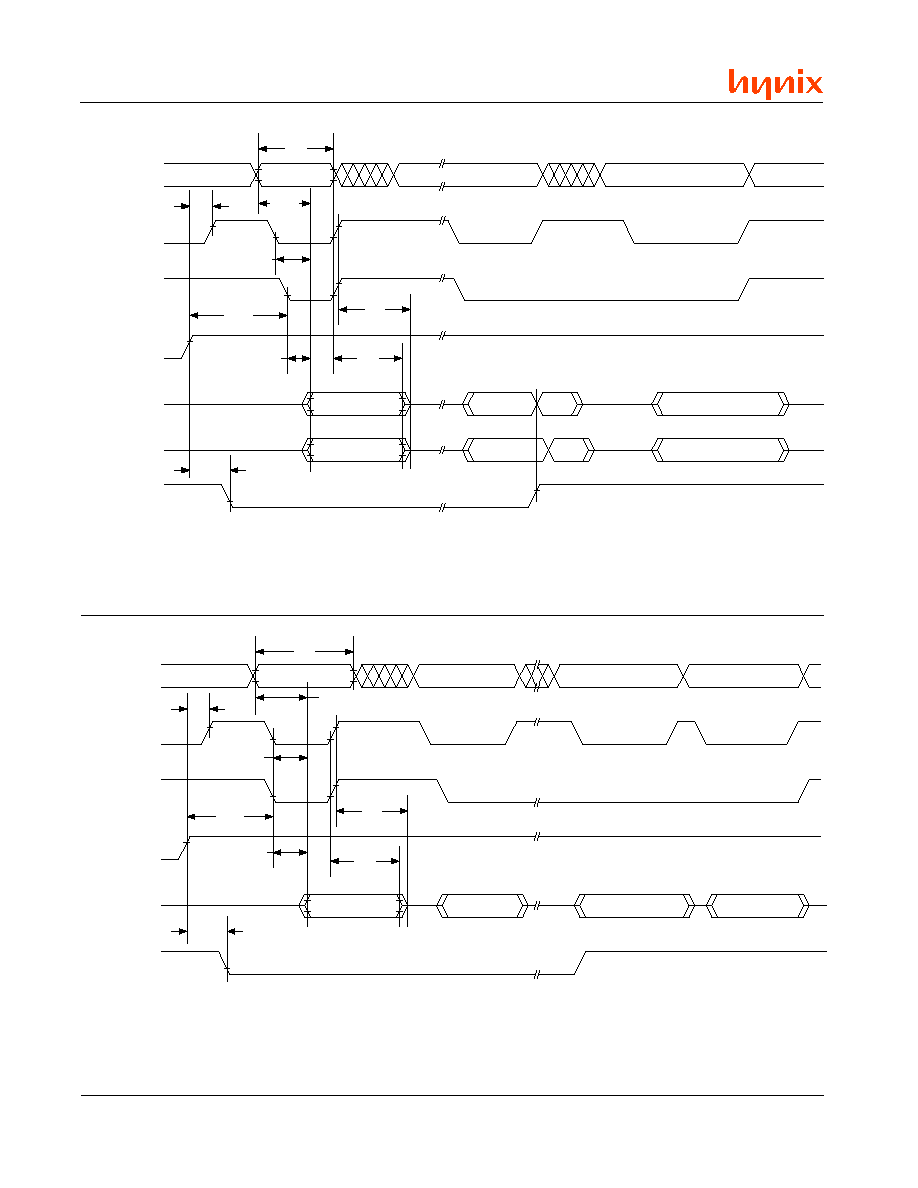

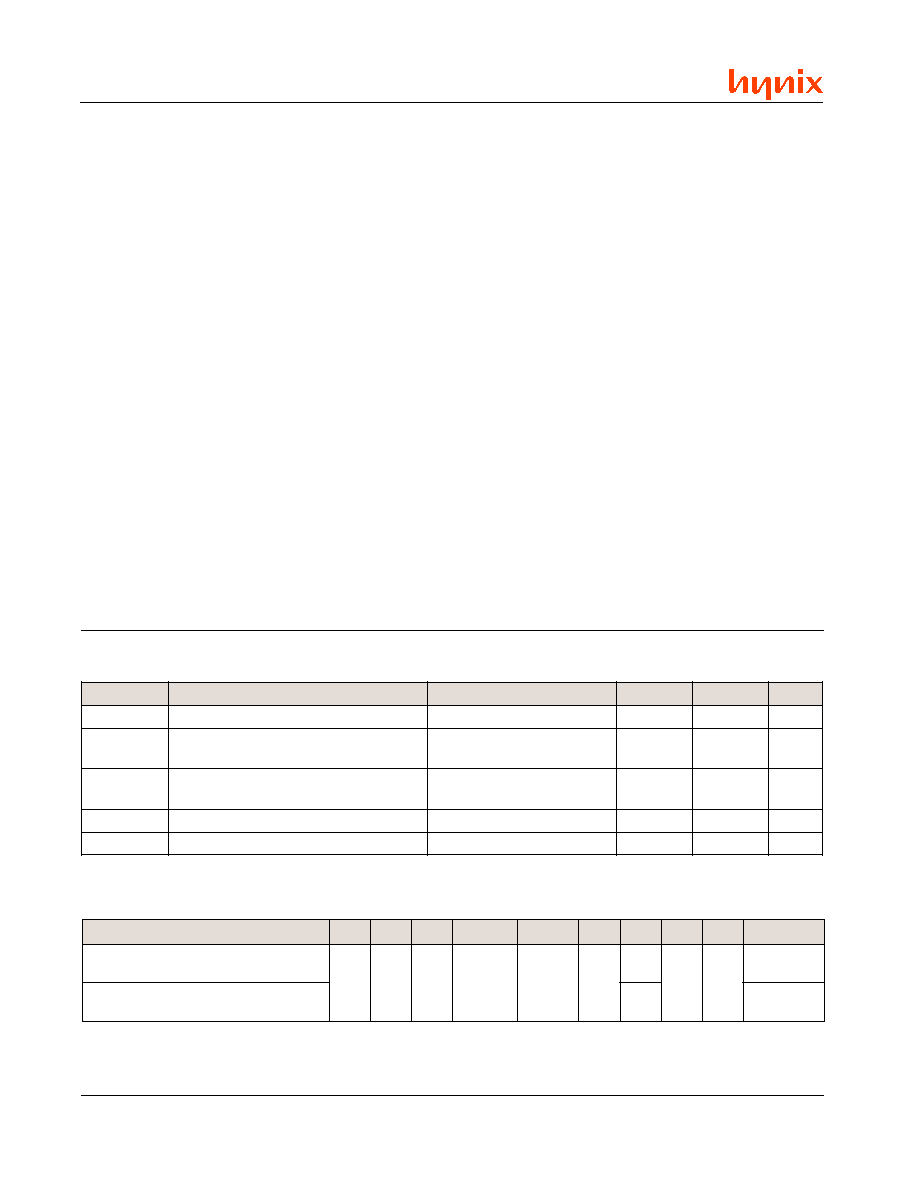

MEMORY ARRAY ORGANIZATION

The 16 Mbit Flash memory array is organized into

35 blocks called sectors (S0, S1, . . . , S34). A

sector is the smallest unit that can be erased and

that can be protected to prevent accidental or un-

authorized erasure. See the `Bus Operations' and

`Command Definitions' sections of this document

for additional information on these functions.

In the HY29LV160, four of the sectors, which com-

prise the boot block, vary in size from 8 to 32

Kbytes (4 to 16 Kwords), while the remaining 31

sectors are uniformly sized at 64 Kbytes (32

Kwords). The boot block can be located at the

bottom of the address range (HY29LV160B) or at

the top of the address range (HY29LV160T).

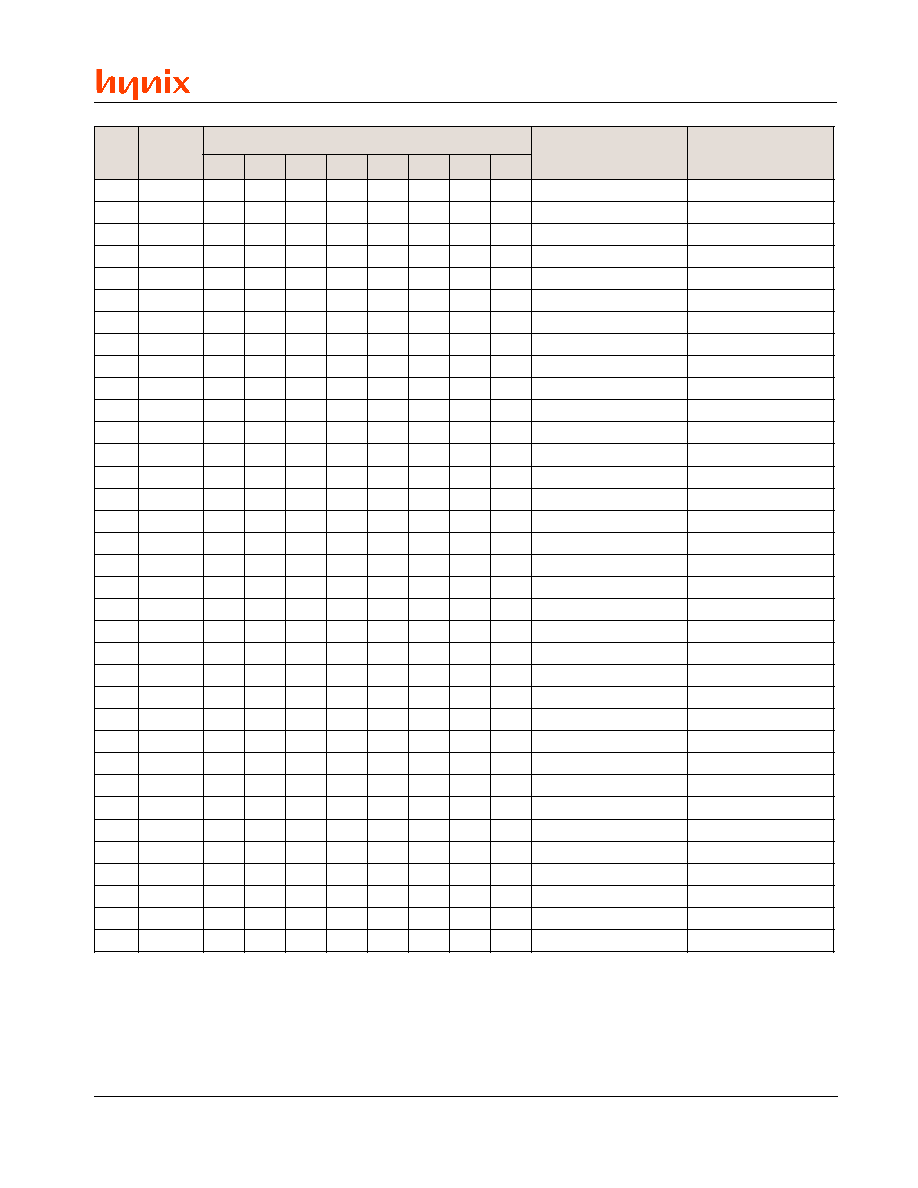

Tables 1 and 2 define the sector addresses and

corresponding address ranges for the top and bot-

tom boot block versions of the HY29LV160.

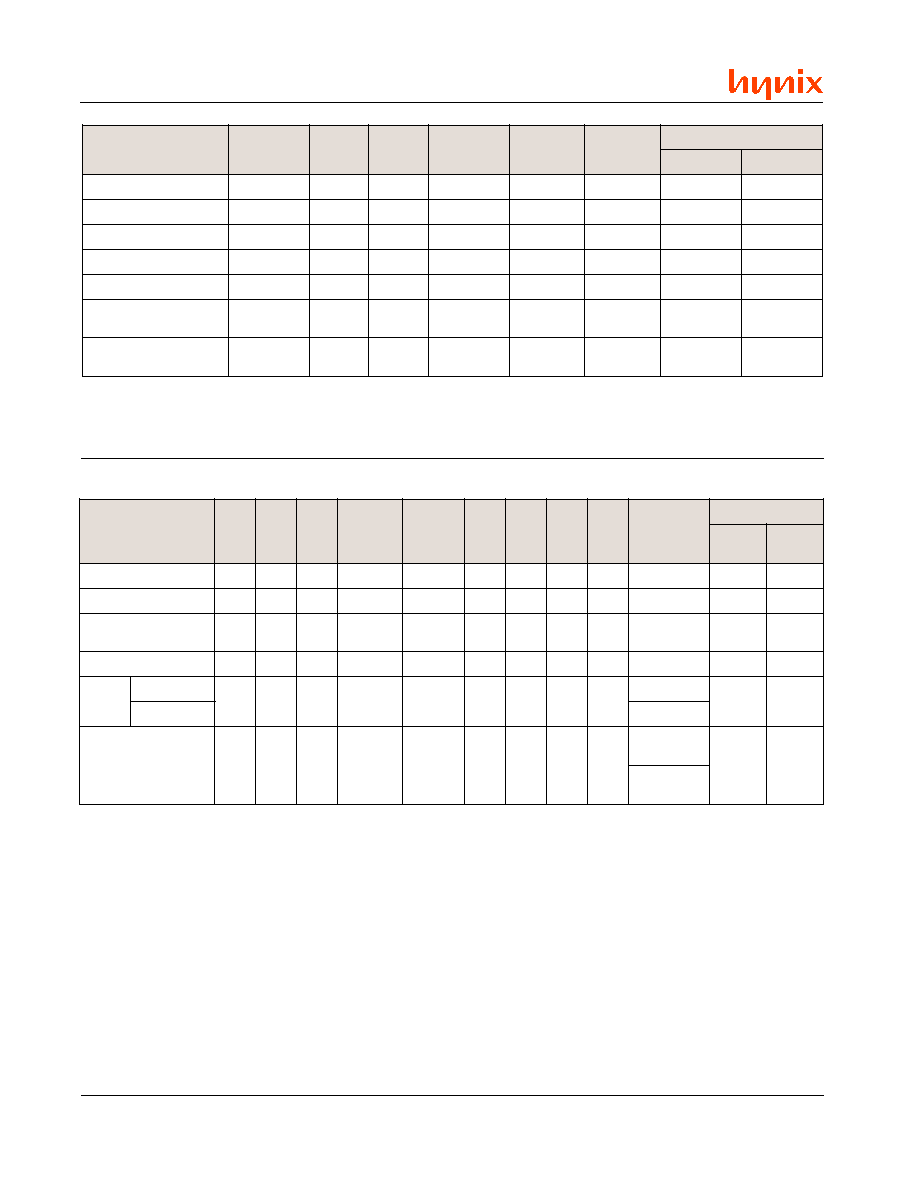

BUS OPERATIONS

Device bus operations are initiated through the

internal command register, which consists of sets

of latches that store the commands, along with

the address and data information, if any, needed

to execute the specific command. The command

register itself does not occupy any addressable

memory location. The contents of the command

register serve as inputs to an internal state ma-

chine whose outputs control the operation of the

device. Table 3 lists the normal bus operations,

the inputs and control levels they require, and the

resulting outputs. Certain bus operations require

a high voltage on one or more device pins. Those

are described in Table 4.

Read Operation

Data is read from the HY29LV160 by using stan-

dard microprocessor read cycles while placing the

byte or word address on the device's address in-

puts. The host system must drive the CE# and

OE# pins LOW and drive WE# high for a valid

read operation to take place. The BYTE# pin de-

termines whether the device outputs array data in

words (DQ[15:0]) or in bytes (DQ[7:0]).

The HY29LV160 is automatically set for reading

array data after device power-up and after a hard-

ware reset to ensure that no spurious alteration of

the memory content occurs during the power tran-

sition. No command is necessary in this mode to

obtain array data, and the device remains enabled

for read accesses until the command register con-

tents are altered.

This device features an Erase Suspend mode.

While in this mode, the host may read the array

data from any sector of memory that is not marked

for erasure. If the host reads from an address

within an erase-suspended (or erasing) sector, or

while the device is performing a byte or word pro-

gram operation, the device outputs status data

instead of array data. After completing an Auto-

matic Program or Automatic Erase algorithm within

a sector, that sector automatically returns to the

read array data mode. After completing a program-

ming operation in the Erase Suspend mode, the

system may once again read array data with the

same exception noted above.

The host must issue a hardware reset or the soft-

ware reset command to return a sector to the read

array data mode if DQ[5] goes high during a pro-

gram or erase cycle, or to return the device to the

read array data mode while it is in the Electronic

ID mode.

6

Rev. 1.2/May 01

HY29LV160

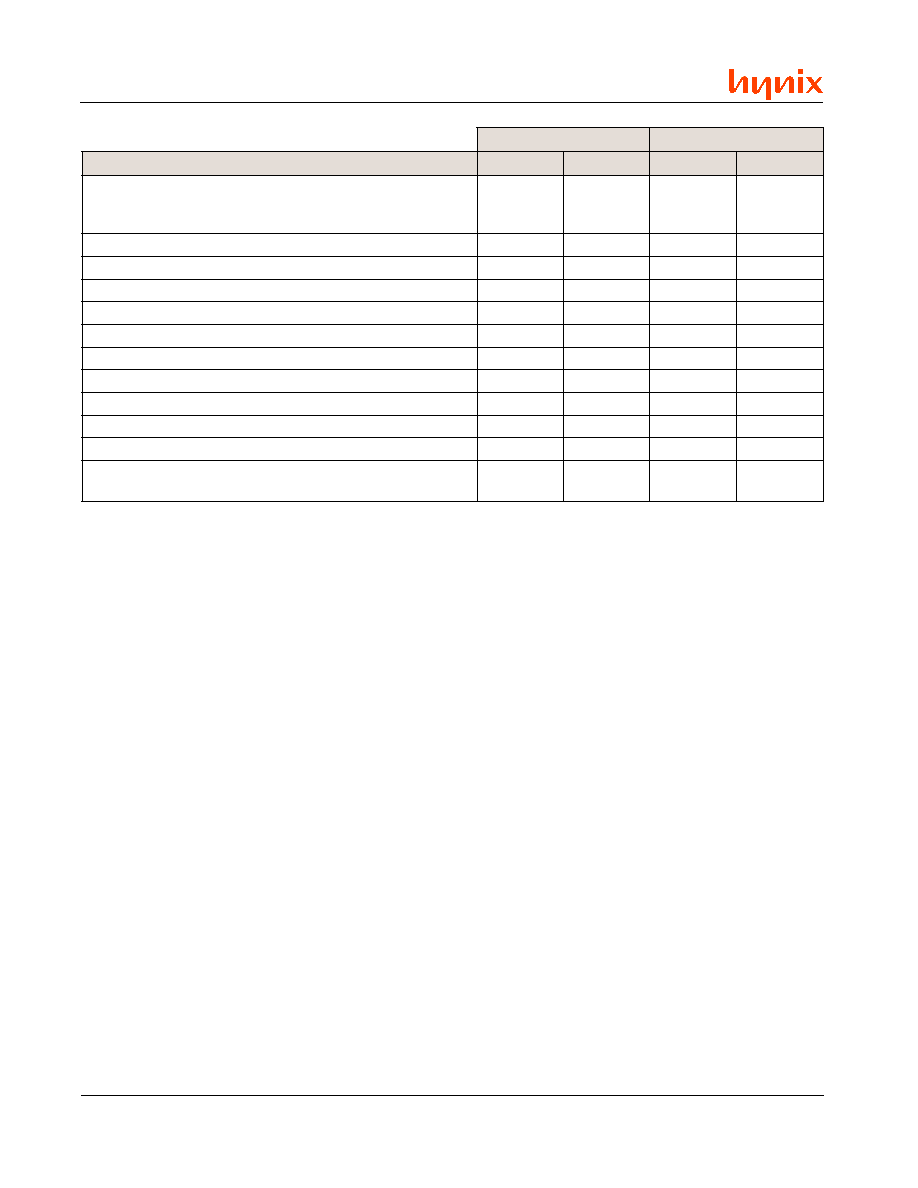

Table 1. HY29LV160T (Top Boot Block) Memory Array Organization

-

t

c

e

S

r

o

e

z

i

S

)

W

K

/

B

K

(

s

s

e

r

d

d

A

r

o

t

c

e

S

1

e

d

o

M

e

t

y

B

e

g

n

a

R

s

s

e

r

d

d

A

2

e

d

o

M

d

r

o

W

e

g

n

a

R

s

s

e

r

d

d

A

3

]

9

1

[

A

]

8

1

[

A

]

7

1

[

A

]

6

1

[

A

]

5

1

[

A

]

4

1

[

A

]

3

1

[

A

]

2

1

[

A

0

S

2

3

/

4

6

0

0

0

0

0

X

X

X

F

F

F

F

0

0

x

0

-

0

0

0

0

0

0

x

0

F

F

F

7

0

x

0

-

0

0

0

0

0

x

0

1

S

2

3

/

4

6

0

0

0

0

1

X

X

X

F

F

F

F

1

0

x

0

-

0

0

0

0

1

0

x

0

F

F

F

F

0

x

0

-

0

0

0

8

0

x

0

2

S

2

3

/

4

6

0

0

0

1

0

X

X

X

F

F

F

F

2

0

x

0

-

0

0

0

0

2

0

x

0

F

F

F

7

1

x

0

-

0

0

0

0

1

x

0

3

S

2

3

/

4

6

0

0

0

1

1

X

X

X

F

F

F

F

3

0

x

0

-

0

0

0

0

3

0

x

0

F

F

F

F

1

x

0

-

0

0

0

8

1

x

0

4

S

2

3

/

4

6

0

0

1

0

0

X

X

X

F

F

F

F

4

0

x

0

-

0

0

0

0

4

0

x

0

F

F

F

7

2

x

0

-

0

0

0

0

2

x

0

5

S

2

3

/

4

6

0

0

1

0

1

X

X

X

F

F

F

F

5

0

x

0

-

0

0

0

0

5

0

x

0

F

F

F

F

2

x

0

-

0

0

0

8

2

x

0

6

S

2

3

/

4

6

0

0

1

1

0

X

X

X

F

F

F

F

6

0

x

0

-

0

0

0

0

6

0

x

0

F

F

F

7

3

x

0

-

0

0

0

0

3

x

0

7

S

2

3

/

4

6

0

0

1

1

1

X

X

X

F

F

F

F

7

0

x

0

-

0

0

0

0

7

0

x

0

F

F

F

F

3

x

0

-

0

0

0

8

3

x

0

8

S

2

3

/

4

6

0

1

0

0

0

X

X

X

F

F

F

F

8

0

x

0

-

0

0

0

0

8

0

x

0

F

F

F

7

4

x

0

-

0

0

0

0

4

x

0

9

S

2

3

/

4

6

0

1

0

0

1

X

X

X

F

F

F

F

9

0

x

0

-

0

0

0

0

9

0

x

0

F

F

F

F

4

x

0

-

0

0

0

8

4

x

0

0

1

S

2

3

/

4

6

0

1

0

1

0

X

X

X

F

F

F

F

A

0

x

0

-

0

0

0

0

A

0

x

0

F

F

F

7

5

x

0

-

0

0

0

0

5

x

0

1

1

S

2

3

/

4

6

0

1

0

1

1

X

X

X

F

F

F

F

B

0

x

0

-

0

0

0

0

B

0

x

0

F

F

F

F

5

x

0

-

0

0

0

8

5

x

0

2

1

S

2

3

/

4

6

0

1

1

0

0

X

X

X

F

F

F

F

C

0

x

0

-

0

0

0

0

C

0

x

0

F

F

F

7

6

x

0

-

0

0

0

0

6

x

0

3

1

S

2

3

/

4

6

0

1

1

0

1

X

X

X

F

F

F

F

D

0

x

0

-

0

0

0

0

D

0

x

0

F

F

F

F

6

x

0

-

0

0

0

8

6

x

0

4

1

S

2

3

/

4

6

0

1

1

1

0

X

X

X

F

F

F

F

E

0

x

0

-

0

0

0

0

E

0

x

0

F

F

F

7

7

x

0

-

0

0

0

0

7

x

0

5

1

S

2

3

/

4

6

0

1

1

1

1

X

X

X

F

F

F

F

F

0

x

0

-

0

0

0

0

F

0

x

0

F

F

F

F

7

x

0

-

0

0

0

8

7

x

0

6

1

S

2

3

/

4

6

1

0

0

0

0

X

X

X

F

F

F

F

0

1

x

0

-

0

0

0

0

0

1

x

0

F

F

F

7

8

x

0

-

0

0

0

0

8

x

0

7

1

S

2

3

/

4

6

1

0

0

0

1

X

X

X

F

F

F

F

1

1

x

0

-

0

0

0

0

1

1

x

0

F

F

F

F

8

x

0

-

0

0

0

8

8

x

0

8

1

S

2

3

/

4

6

1

0

0

1

0

X

X

X

F

F

F

F

2

1

x

0

-

0

0

0

0

2

1

x

0

F

F

F

7

9

x

0

-

0

0

0

0

9

x

0

9

1

S

2

3

/

4

6

1

0

0

1

1

X

X

X

F

F

F

F

3

1

x

0

-

0

0

0

0

3

1

x

0

F

F

F

F

9

x

0

-

0

0

0

8

9

x

0

0

2

S

2

3

/

4

6

1

0

1

0

0

X

X

X

F

F

F

F

4

1

x

0

-

0

0

0

0

4

1

x

0

F

F

F

7

A

x

0

-

0

0

0

0

A

x

0

1

2

S

2

3

/

4

6

1

0

1

0

1

X

X

X

F

F

F

F

5

1

x

0

-

0

0

0

0

5

1

x

0

F

F

F

F

A

x

0

-

0

0

0

8

A

x

0

2

2

S

2

3

/

4

6

1

0

1

1

0

X

X

X

F

F

F

F

6

1

x

0

-

0

0

0

0

6

1

x

0

F

F

F

7

B

x

0

-

0

0

0

0

B

x

0

3

2

S

2

3

/

4

6

1

0

1

1

1

X

X

X

F

F

F

F

7

1

x

0

-

0

0

0

0

7

1

x

0

F

F

F

F

B

x

0

-

0

0

0

8

B

x

0

4

2

S

2

3

/

4

6

1

1

0

0

0

X

X

X

F

F

F

F

8

1

x

0

-

0

0

0

0

8

1

x

0

F

F

F

7

C

x

0

-

0

0

0

0

C

x

0

5

2

S

2

3

/

4

6

1

1

0

0

1

X

X

X

F

F

F

F

9

1

x

0

-

0

0

0

0

9

1

x

0

F

F

F

F

C

x

0

-

0

0

0

8

C

x

0

6

2

S

2

3

/

4

6

1

1

0

1

0

X

X

X

F

F

F

F

A

1

x

0

-

0

0

0

0

A

1

x

0

F

F

F

7

D

x

0

-

0

0

0

0

D

x

0

7

2

S

2

3

/

4

6

1

1

0

1

1

X

X

X

F

F

F

F

B

1

x

0

-

0

0

0

0

B

1

x

0

F

F

F

F

D

x

0

-

0

0

0

8

D

x

0

8

2

S

2

3

/

4

6

1

1

1

0

0

X

X

X

F

F

F

F

C

1

x

0

-

0

0

0

0

C

1

x

0

F

F

F

7

E

x

0

-

0

0

0

0

E

x

0

9

2

S

2

3

/

4

6

1

1

1

0

1

X

X

X

F

F

F

F

D

1

x

0

-

0

0

0

0

D

1

x

0

F

F

F

F

E

x

0

-

0

0

0

8

E

x

0

0

3

S

2

3

/

4

6

1

1

1

1

0

X

X

X

F

F

F

F

E

1

x

0

-

0

0

0

0

E

1

x

0

F

F

F

7

F

x

0

-

0

0

0

0

F

x

0

1

3

S

6

1

/

2

3

1

1

1

1

1

0

X

X

F

F

F

7

F

1

x

0

-

0

0

0

0

F

1

x

0

F

F

F

B

F

x

0

-

0

0

0

8

F

x

0

2

3

S

4

/

8

1

1

1

1

1

1

0

0

F

F

F

9

F

1

x

0

-

0

0

0

8

F

1

x

0

F

F

F

C

F

x

0

-

0

0

0

C

F

x

0

3

3

S

4

/

8

1

1

1

1

1

1

0

1

F

F

F

B

F

1

x

0

-

0

0

0

A

F

1

x

0

F

F

F

D

F

x

0

-

0

0

0

D

F

X

0

4

3

S

8

/

6

1

1

1

1

1

1

1

1

X

F

F

F

F

F

1

x

0

-

0

0

0

C

F

1

x

0

F

F

F

F

F

x

0

-

0

0

0

E

F

x

0

Notes:

1. `X' indicates don't care.

2. `0xN. . . N' indicates an address in hexadecimal notation.

3. The address range in byte mode is A[19:0, -1]. The address range in word mode is A[19:0].

7

Rev. 1.2/May 01

HY29LV160

Table 2. HY29LV160B (Bottom Boot Block) Memory Array Organization

Notes:

1. `X' indicates don't care.

2. `0xN. . . N' indicates an address in hexadecimal notation.

3. The address range in byte mode is A[19:0, -1]. The address range in word mode is A[19:0].

-

t

c

e

S

r

o

e

z

i

S

)

W

K

/

B

K

(

s

s

e

r

d

d

A

r

o

t

c

e

S

1

e

d

o

M

e

t

y

B

e

g

n

a

R

s

s

e

r

d

d

A

2

e

d

o

M

d

r

o

W

e

g

n

a

R

s

s

e

r

d

d

A

3

]

9

1

[

A

]

8

1

[

A

]

7

1

[

A

]

6

1

[

A

]

5

1

[

A

]

4

1

[

A

]

3

1

[

A

]

2

1

[

A

0

S

8

/

6

1

0

0

0

0

0

0

0

X

F

F

F

3

0

0

x

0

-

0

0

0

0

0

0

x

0

F

F

F

1

0

x

0

-

0

0

0

0

0

x

0

1

S

4

/

8

0

0

0

0

0

0

1

0

F

F

F

5

0

0

x

0

-

0

0

0

4

0

0

x

0

F

F

F

2

0

x

0

-

0

0

0

2

0

x

0

2

S

4

/

8

0

0

0

0

0

0

1

1

F

F

F

7

0

0

x

0

-

0

0

0

6

0

0

x

0

F

F

F

3

0

x

0

-

0

0

0

3

0

X

0

3

S

6

1

/

2

3

0

0

0

0

0

1

X

X

F

F

F

F

0

0

x

0

-

0

0

0

8

0

0

x

0

F

F

F

7

0

x

0

-

0

0

0

4

0

x

0

4

S

2

3

/

4

6

0

0

0

0

1

X

X

X

F

F

F

F

1

0

x

0

-

0

0

0

0

1

0

x

0

F

F

F

F

0

x

0

-

0

0

0

8

0

x

0

5

S

2

3

/

4

6

0

0

0

1

0

X

X

X

F

F

F

F

2

0

x

0

-

0

0

0

0

2

0

x

0

F

F

F

7

1

x

0

-

0

0

0

0

1

x

0

6

S

2

3

/

4

6

0

0

0

1

1

X

X

X

F

F

F

F

3

0

x

0

-

0

0

0

0

3

0

x

0

F

F

F

F

1

x

0

-

0

0

0

8

1

x

0

7

S

2

3

/

4

6

0

0

1

0

0

X

X

X

F

F

F

F

4

0

x

0

-

0

0

0

0

4

0

x

0

F

F

F

7

2

x

0

-

0

0

0

0

2

x

0

8

S

2

3

/

4

6

0

0

1

0

1

X

X

X

F

F

F

F

5

0

x

0

-

0

0

0

0

5

0

x

0

F

F

F

F

2

x

0

-

0

0

0

8

2

x

0

9

S

2

3

/

4

6

0

0

1

1

0

X

X

X

F

F

F

F

6

0

x

0

-

0

0

0

0

6

0

x

0

F

F

F

7

3

x

0

-

0

0

0

0

3

x

0

0

1

S

2

3

/

4

6

0

0

1

1

1

X

X

X

F

F

F

F

7

0

x

0

-

0

0

0

0

7

0

x

0

F

F

F

F

3

x

0

-

0

0

0

8

3

x

0

1

1

S

2

3

/

4

6

0

1

0

0

0

X

X

X

F

F

F

F

8

0

x

0

-

0

0

0

0

8

0

x

0

F

F

F

7

4

x

0

-

0

0

0

0

4

x

0

2

1

S

2

3

/

4

6

0

1

0

0

1

X

X

X

F

F

F

F

9

0

x

0

-

0

0

0

0

9

0

x

0

F

F

F

F

4

x

0

-

0

0

0

8

4

x

0

3

1

S

2

3

/

4

6

0

1

0

1

0

X

X

X

F

F

F

F

A

0

x

0

-

0

0

0

0

A

0

x

0

F

F

F

7

5

x

0

-

0

0

0

0

5

x

0

4

1

S

2

3

/

4

6

0

1

0

1

1

X

X

X

F

F

F

F

B

0

x

0

-

0

0

0

0

B

0

x

0

F

F

F

F

5

x

0

-

0

0

0

8

5

x

0

5

1

S

2

3

/

4

6

0

1

1

0

0

X

X

X

F

F

F

F

C

0

x

0

-

0

0

0

0

C

0

x

0

F

F

F

7

6

x

0

-

0

0

0

0

6

x

0

6

1

S

2

3

/

4

6

0

1

1

0

1

X

X

X

F

F

F

F

D

0

x

0

-

0

0

0

0

D

0

x

0

F

F

F

F

6

x

0

-

0

0

0

8

6

x

0

7

1

S

2

3

/

4

6

0

1

1

1

0

X

X

X

F

F

F

F

E

0

x

0

-

0

0

0

0

E

0

x

0

F

F

F

7

7

x

0

-

0

0

0

0

7

x

0

8

1

S

2

3

/

4

6

0

1

1

1

1

X

X

X

F

F

F

F

F

0

x

0

-

0

0

0

0

F

0

x

0

F

F

F

F

7

x

0

-

0

0

0

8

7

x

0

9

1

S

2

3

/

4

6

1

0

0

0

0

X

X

X

F

F

F

F

0

1

x

0

-

0

0

0

0

0

1

x

0

F

F

F

7

8

x

0

-

0

0

0

0

8

x

0

0

2

S

2

3

/

4

6

1

0

0

0

1

X

X

X

F

F

F

F

1

1

x

0

-

0

0

0

0

1

1

x

0

F

F

F

F

8

x

0

-

0

0

0

8

8

x

0

1

2

S

2

3

/

4

6

1

0

0

1

0

X

X

X

F

F

F

F

2

1

x

0

-

0

0

0

0

2

1

x

0

F

F

F

7

9

x

0

-

0

0

0

0

9

x

0

2

2

S

2

3

/

4

6

1

0

0

1

1

X

X

X

F

F

F

F

3

1

x

0

-

0

0

0

0

3

1

x

0

F

F

F

F

9

x

0

-

0

0

0

8

9

x

0

3

2

S

2

3

/

4

6

1

0

1

0

0

X

X

X

F

F

F

F

4

1

x

0

-

0

0

0

0

4

1

x

0

F

F

F

7

A

x

0

-

0

0

0

0

A

x

0

4

2

S

2

3

/

4

6

1

0

1

0

1

X

X

X

F

F

F

F

5

1

x

0

-

0

0

0

0

5

1

x

0

F

F

F

F

A

x

0

-

0

0

0

8

A

x

0

5

2

S

2

3

/

4

6

1

0

1

1

0

X

X

X

F

F

F

F

6

1

x

0

-

0

0

0

0

6

1

x

0

F

F

F

7

B

x

0

-

0

0

0

0

B

x

0

6

2

S

2

3

/

4

6

1

0

1

1

1

X

X

X

F

F

F

F

7

1

x

0

-

0

0

0

0

7

1

x

0

F

F

F

F

B

x

0

-

0

0

0

8

B

x

0

7

2

S

2

3

/

4

6

1

1

0

0

0

X

X

X

F

F

F

F

8

1

x

0

-

0

0

0

0

8

1

x

0

F

F

F

7

C

x

0

-

0

0

0

0

C

x

0

8

2

S

2

3

/

4

6

1

1

0

0

1

X

X

X

F

F

F

F

9

1

x

0

-

0

0

0

0

9

1

x

0

F

F

F

F

C

x

0

-

0

0

0

8

C

x

0

9

2

S

2

3

/

4

6

1

1

0

1

0

X

X

X

F

F

F

F

A

1

x

0

-

0

0

0

0

A

1

x

0

F

F

F

7

D

x

0

-

0

0

0

0

D

x

0

0

3

S

2

3

/

4

6

1

1

0

1

1

X

X

X

F

F

F

F

B

1

x

0

-

0

0

0

0

B

1

x

0

F

F

F

F

D

x

0

-

0

0

0

8

D

x

0

1

3

S

2

3

/

4

6

1

1

1

0

0

X

X

X

F

F

F

F

C

1

x

0

-

0

0

0

0

C

1

x

0

F

F

F

7

E

x

0

-

0

0

0

0

E

x

0

2

3

S

2

3

/

4

6

1

1

1

0

1

X

X

X

F

F

F

F

D

1

x

0

-

0

0

0

0

D

1

x

0

F

F

F

F

E

x

0

-

0

0

0

8

E

x

0

3

3

S

2

3

/

4

6

1

1

1

1

0

X

X

X

F

F

F

F

E

1

x

0

-

0

0

0

0

E

1

x

0

F

F

F

7

F

x

0

-

0

0

0

0

F

x

0

4

3

S

2

3

/

4

6

1

1

1

1

1

X

X

X

F

F

F

F

F

1

x

0

-

0

0

0

0

F

1

x

0

F

F

F

F

F

x

0

-

0

0

0

8

F

x

0

8

Rev. 1.2/May 01

HY29LV160

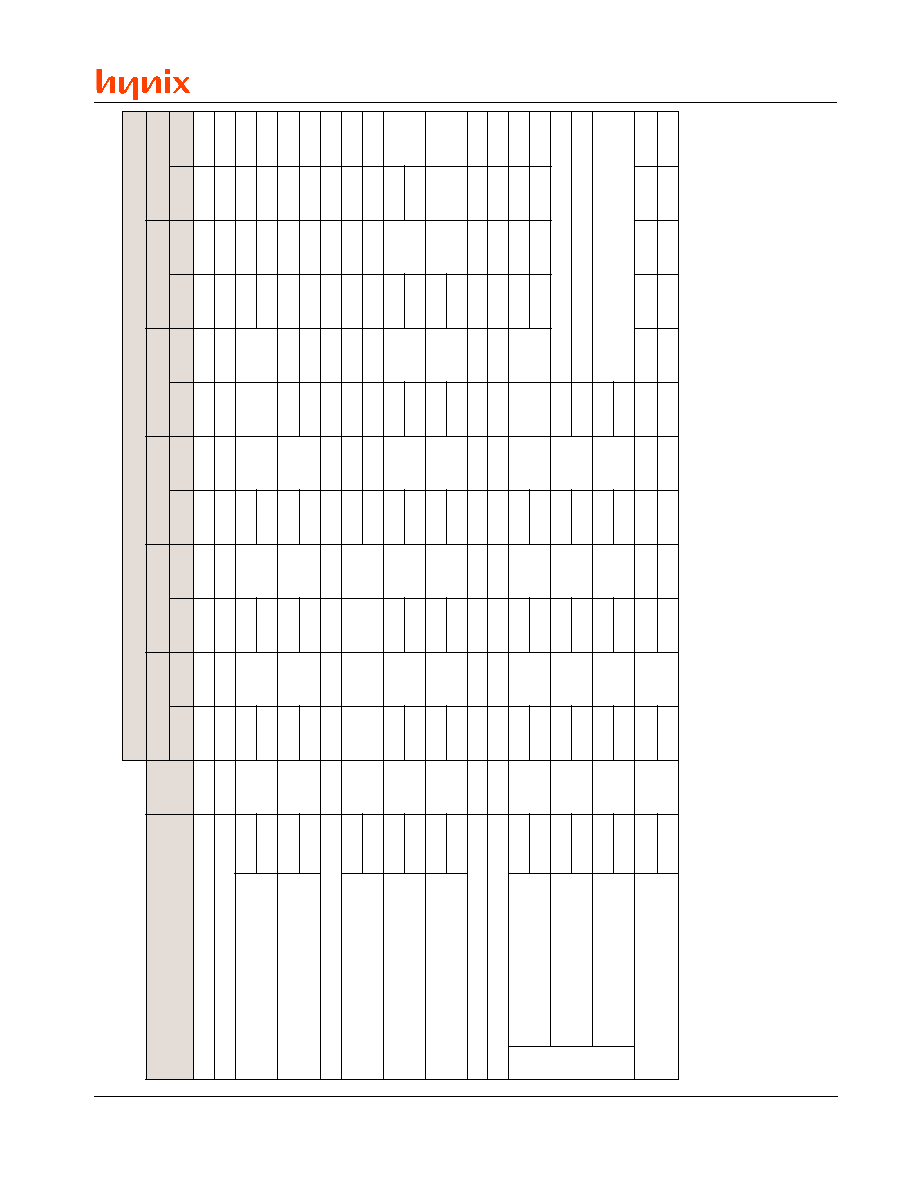

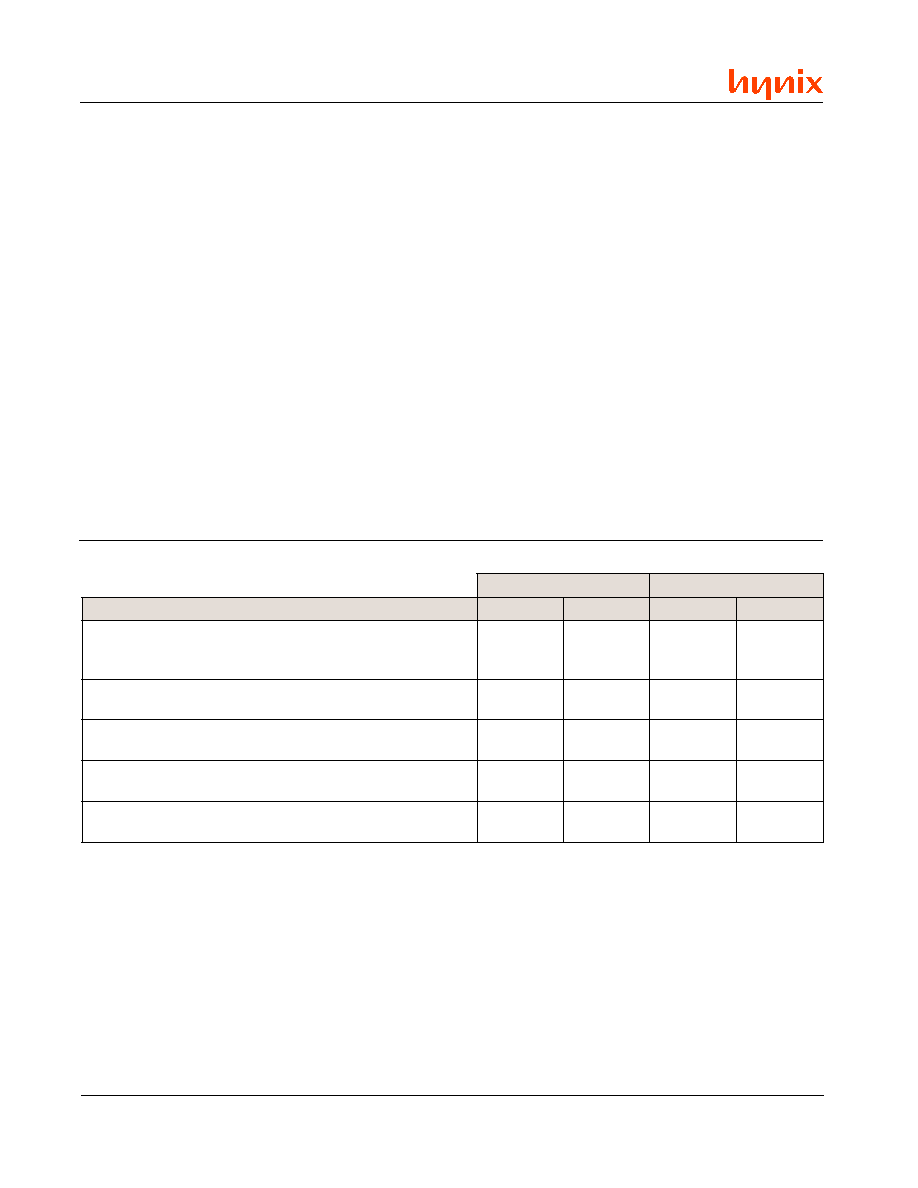

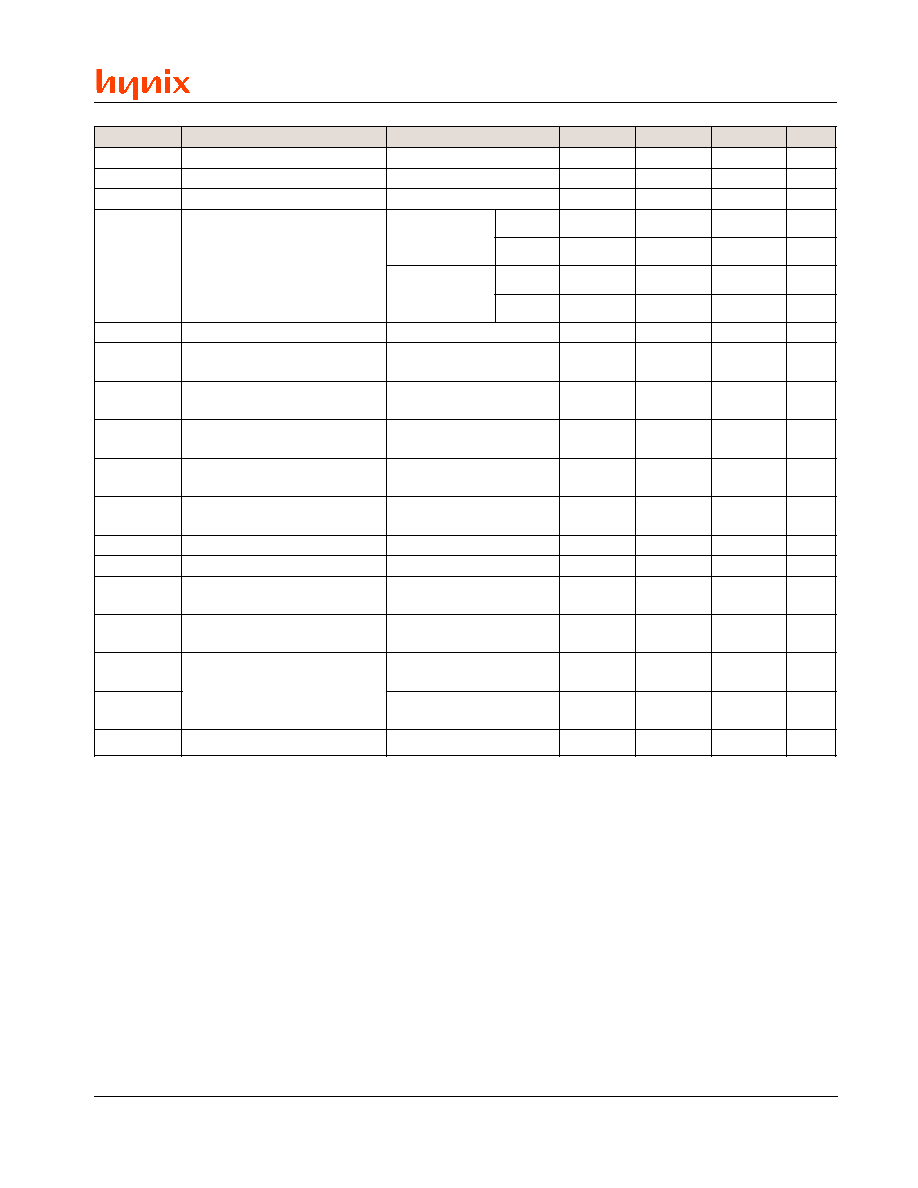

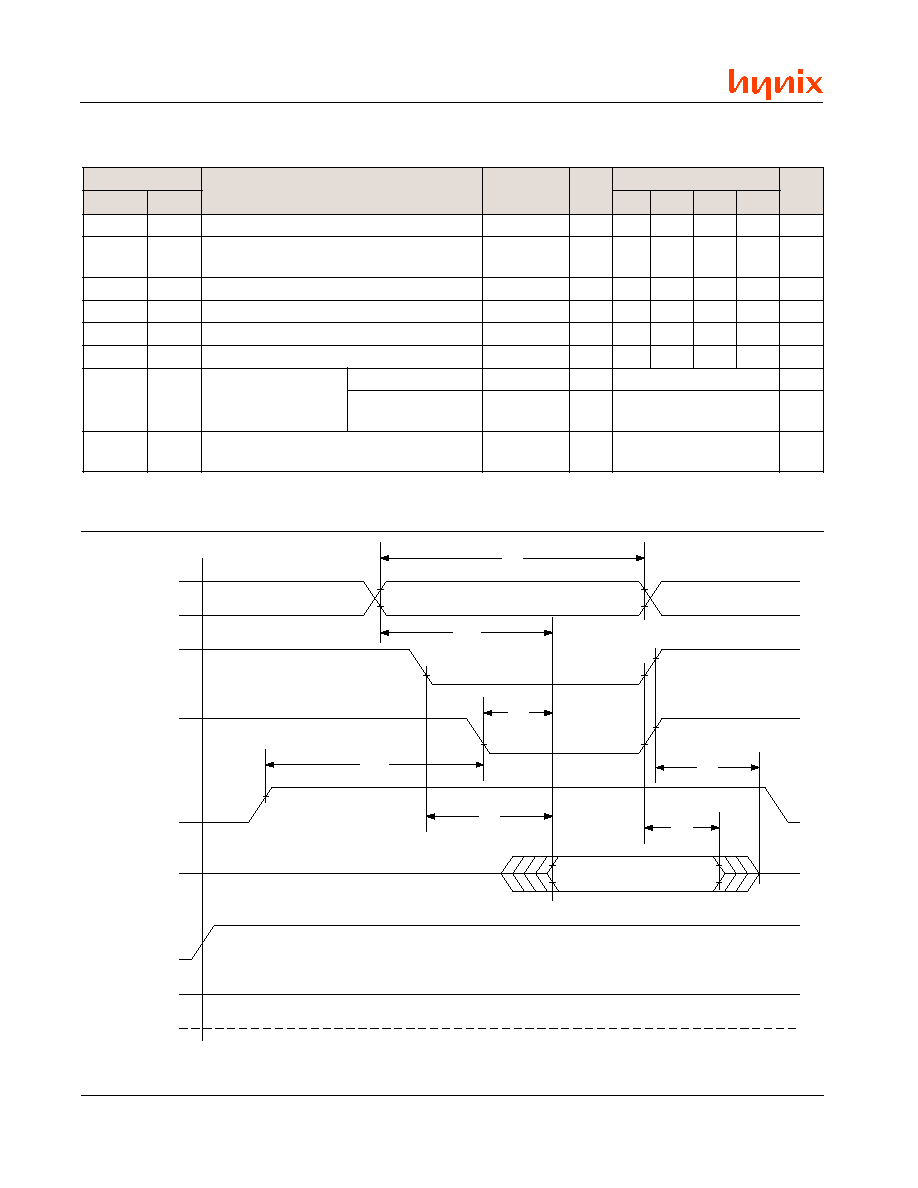

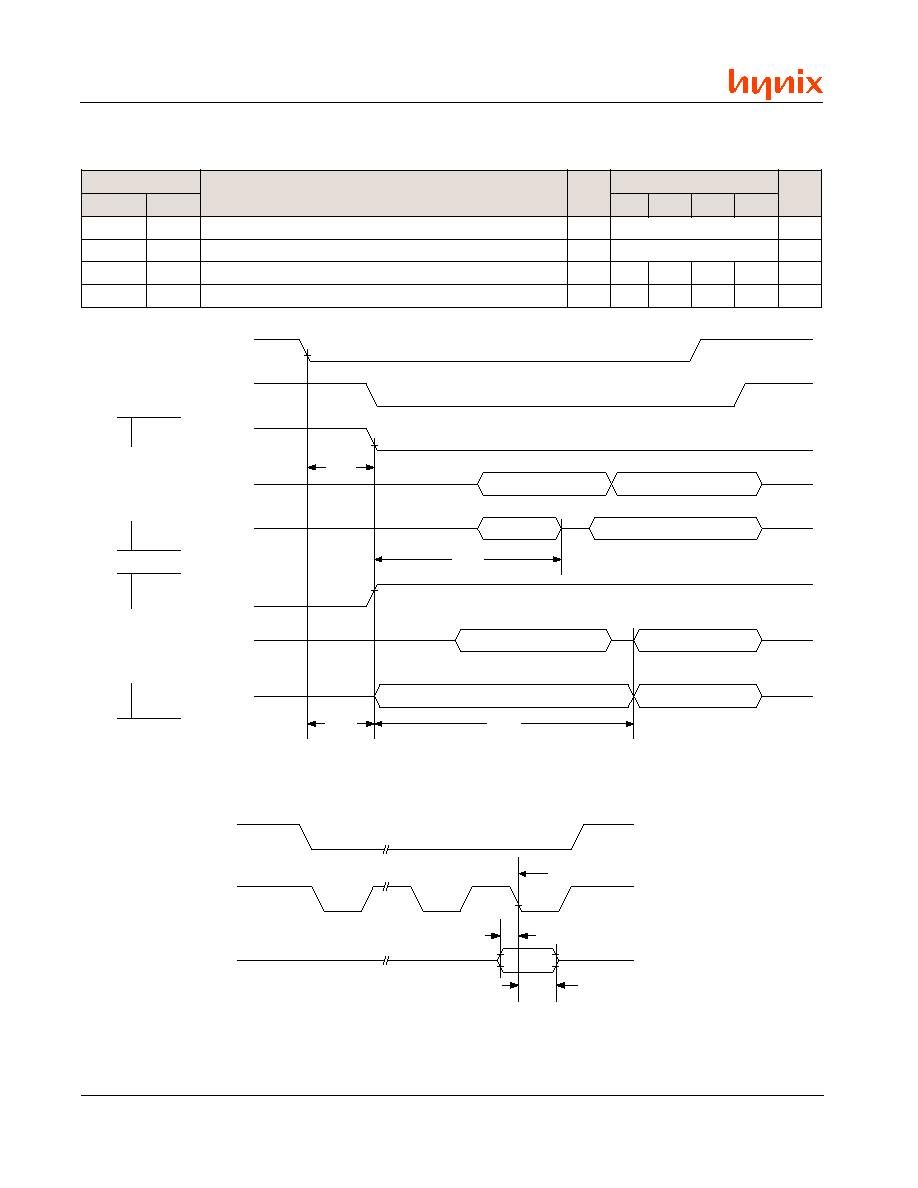

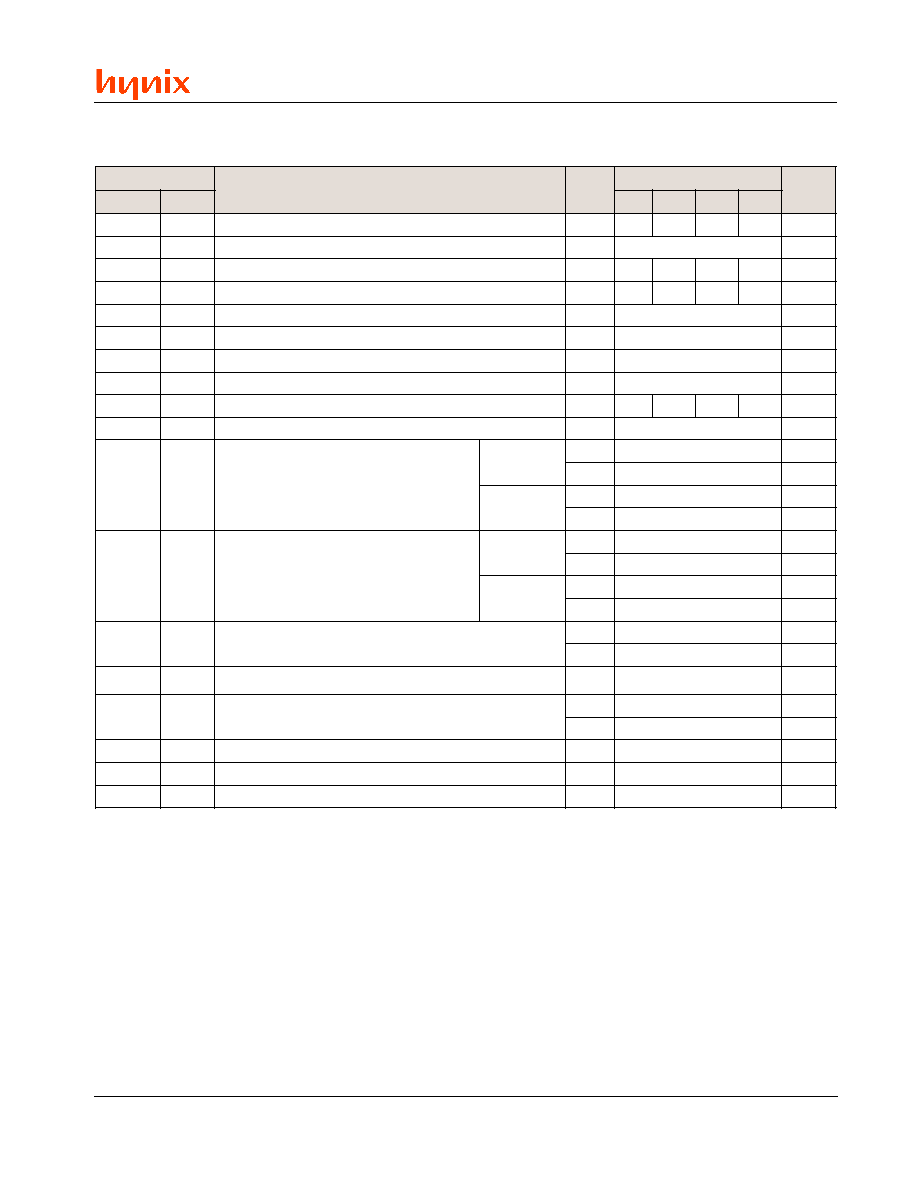

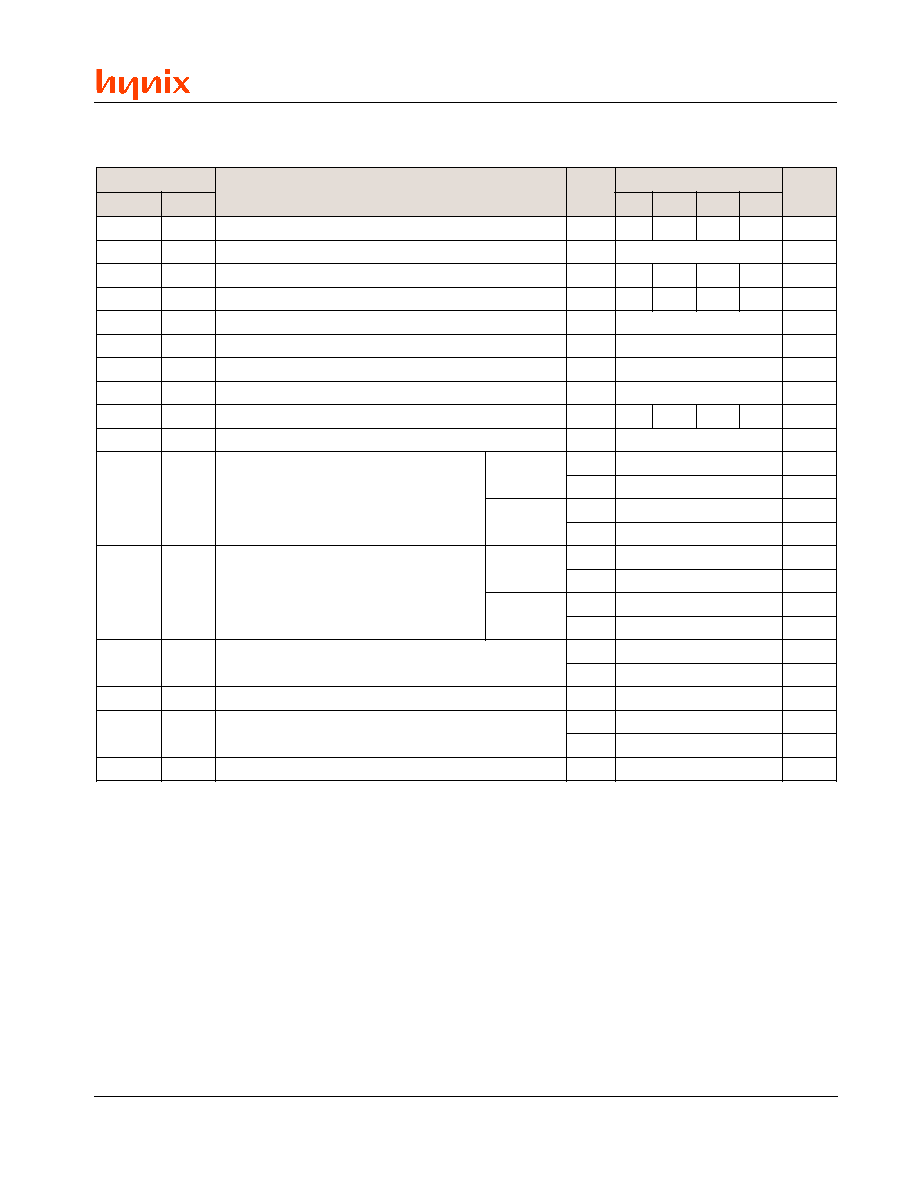

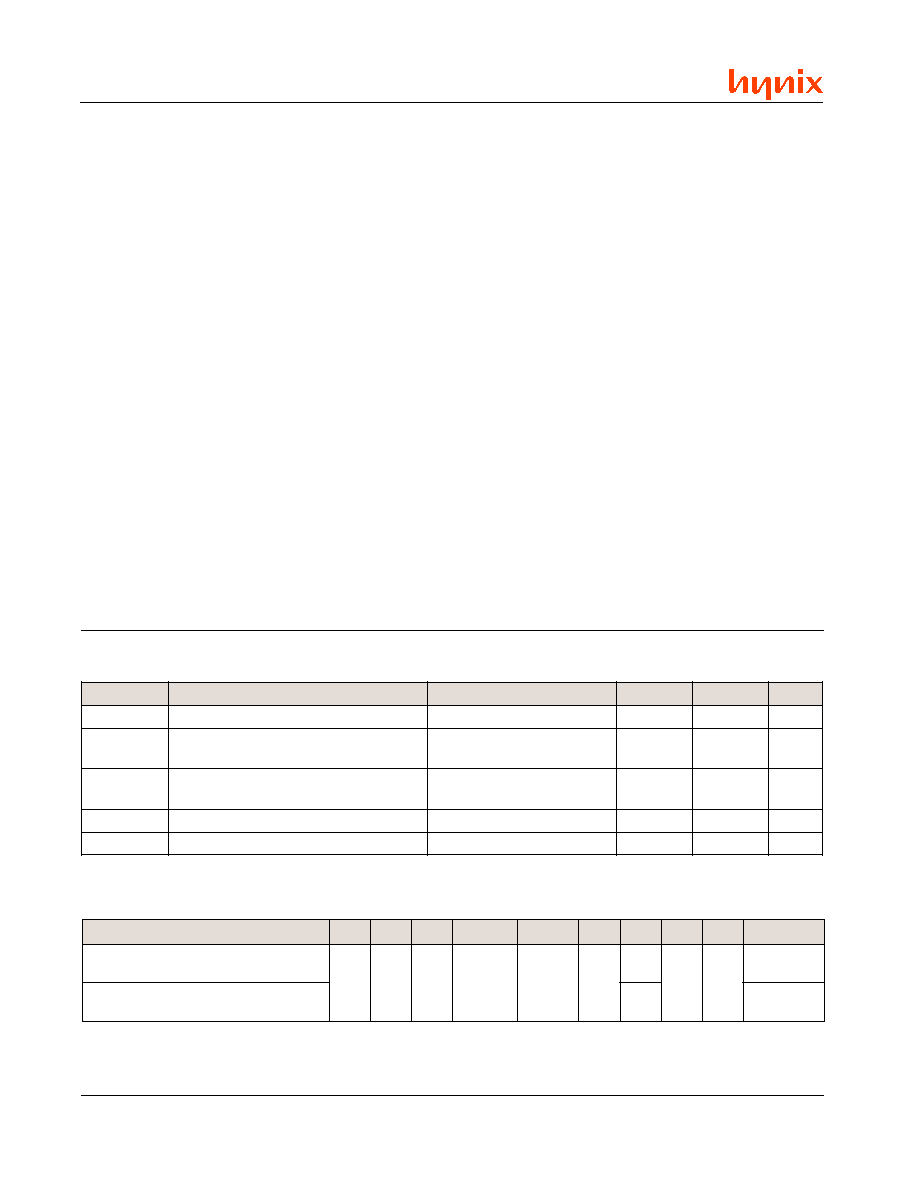

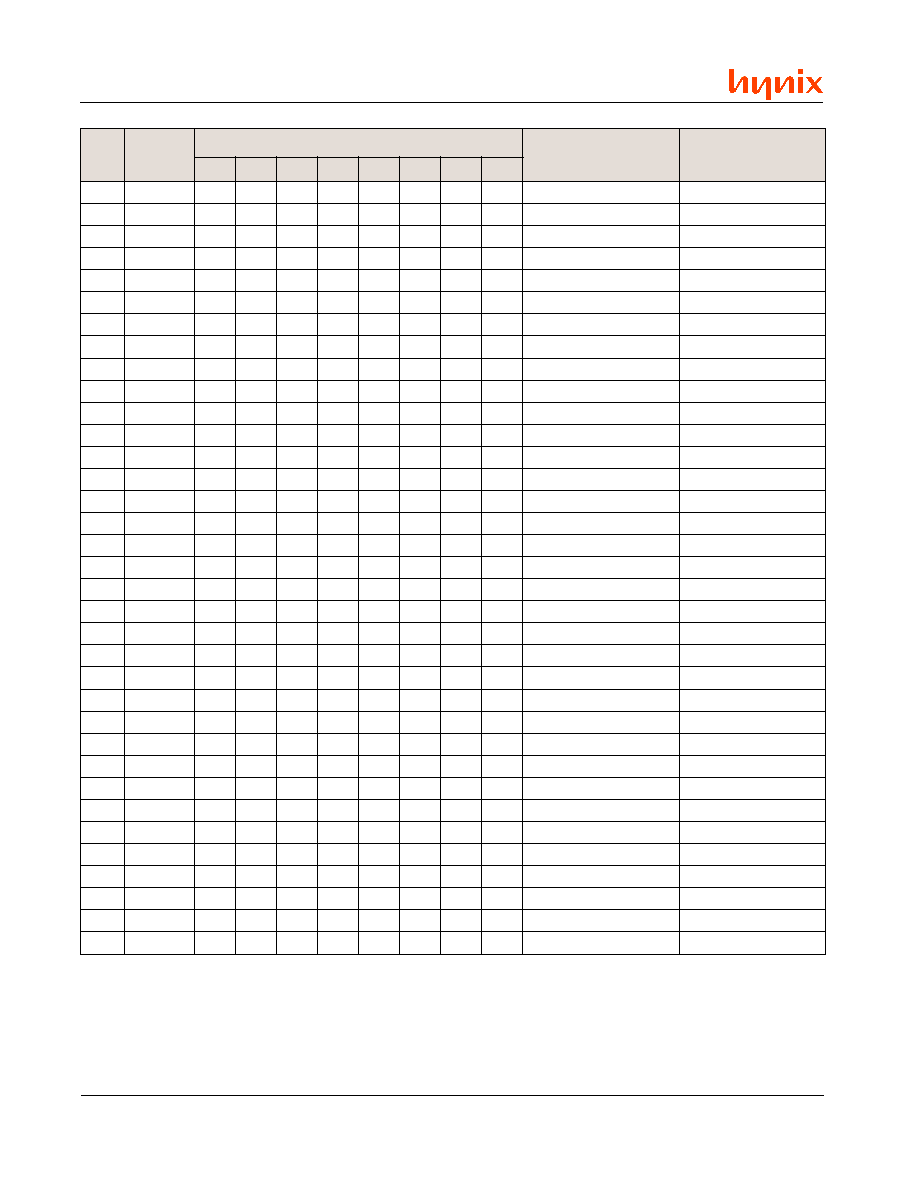

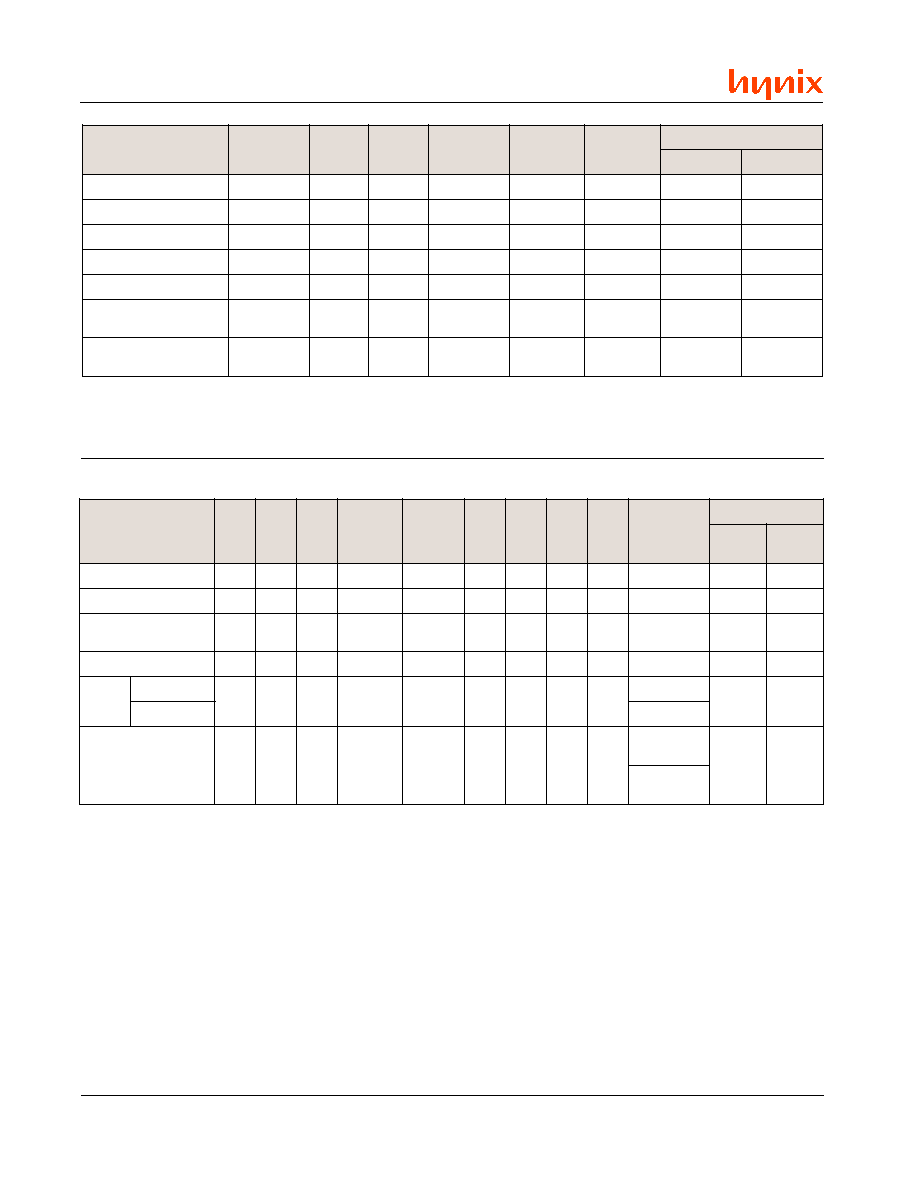

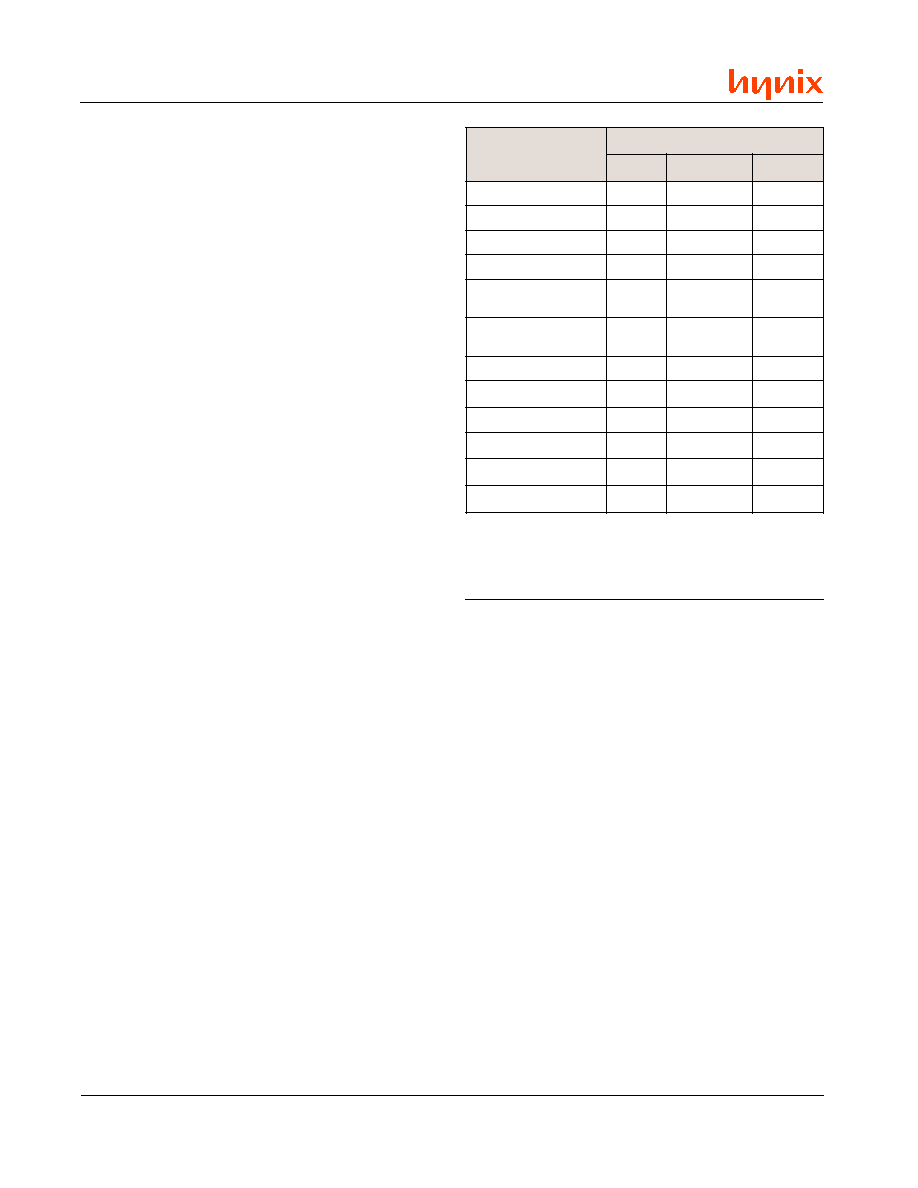

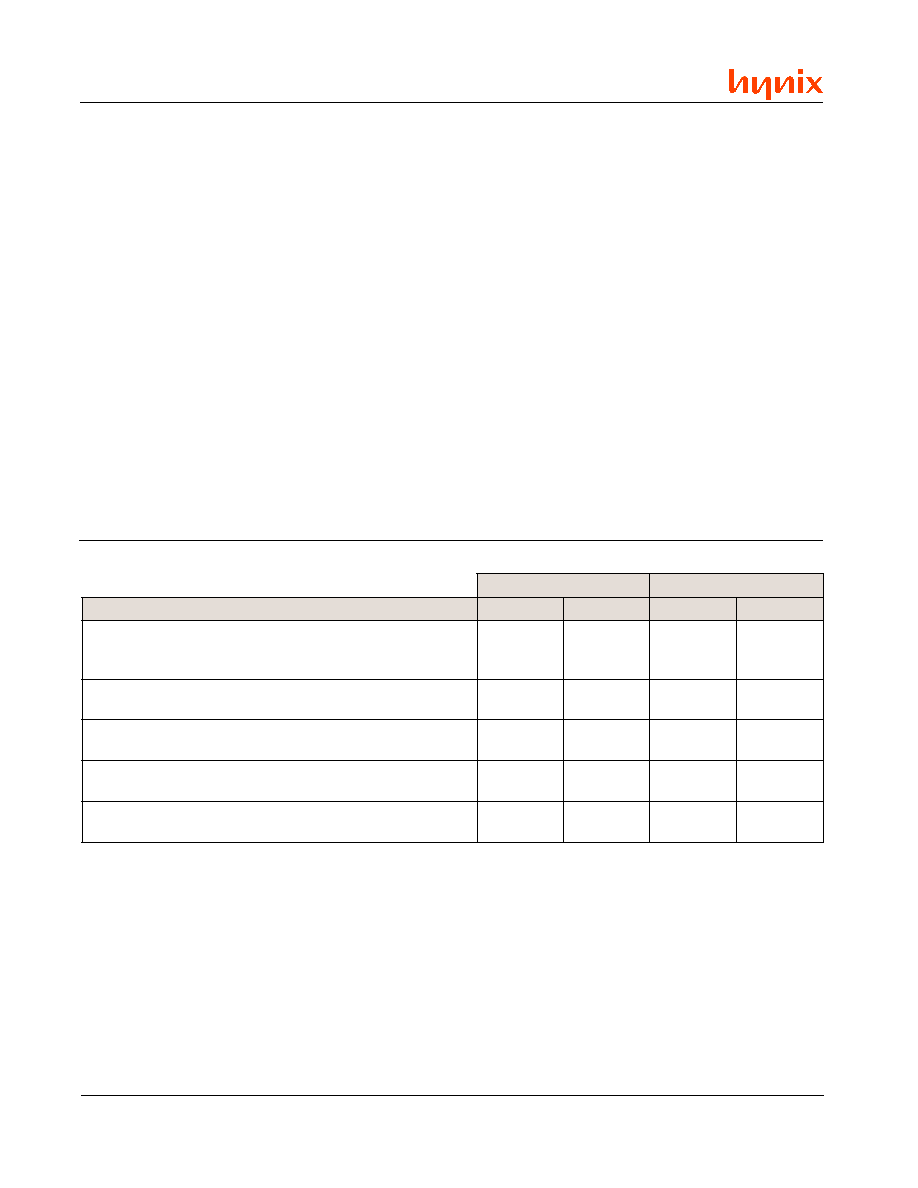

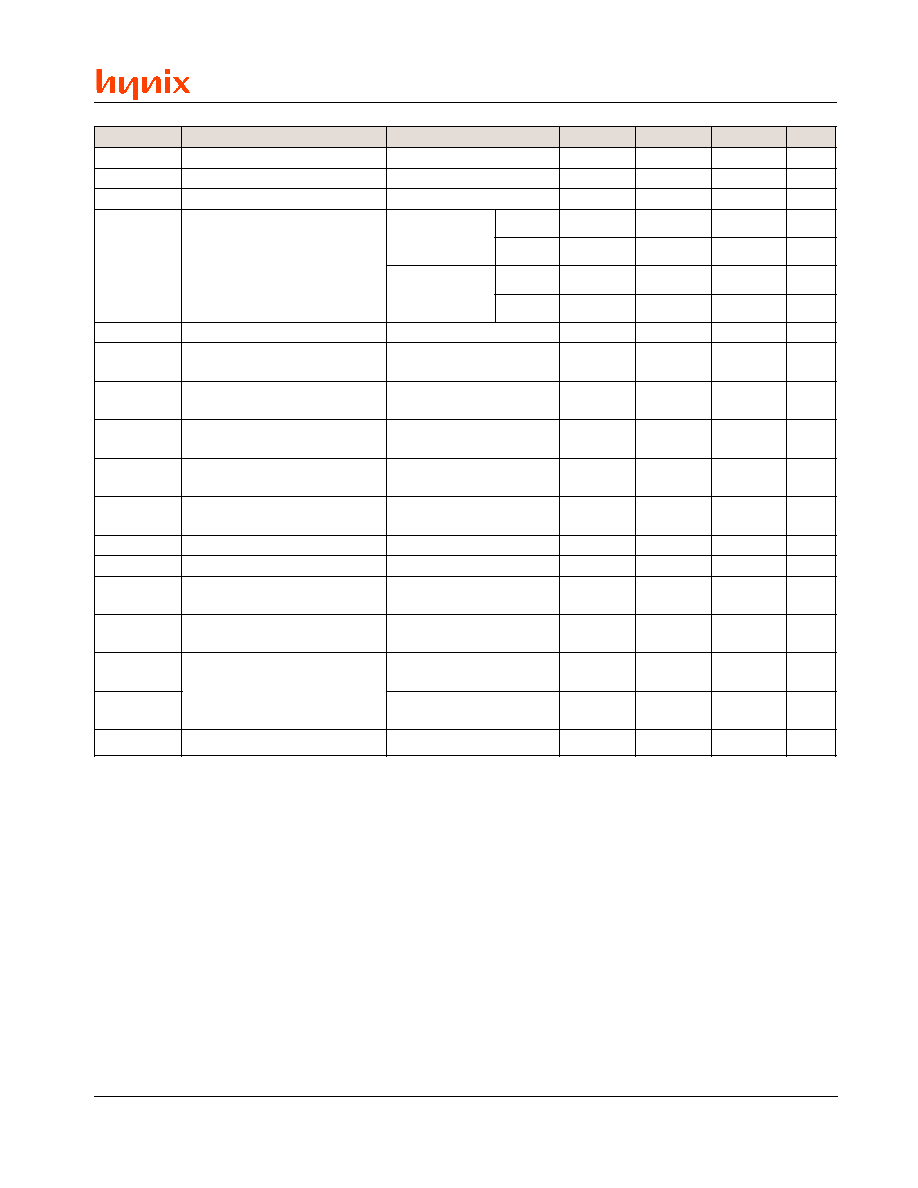

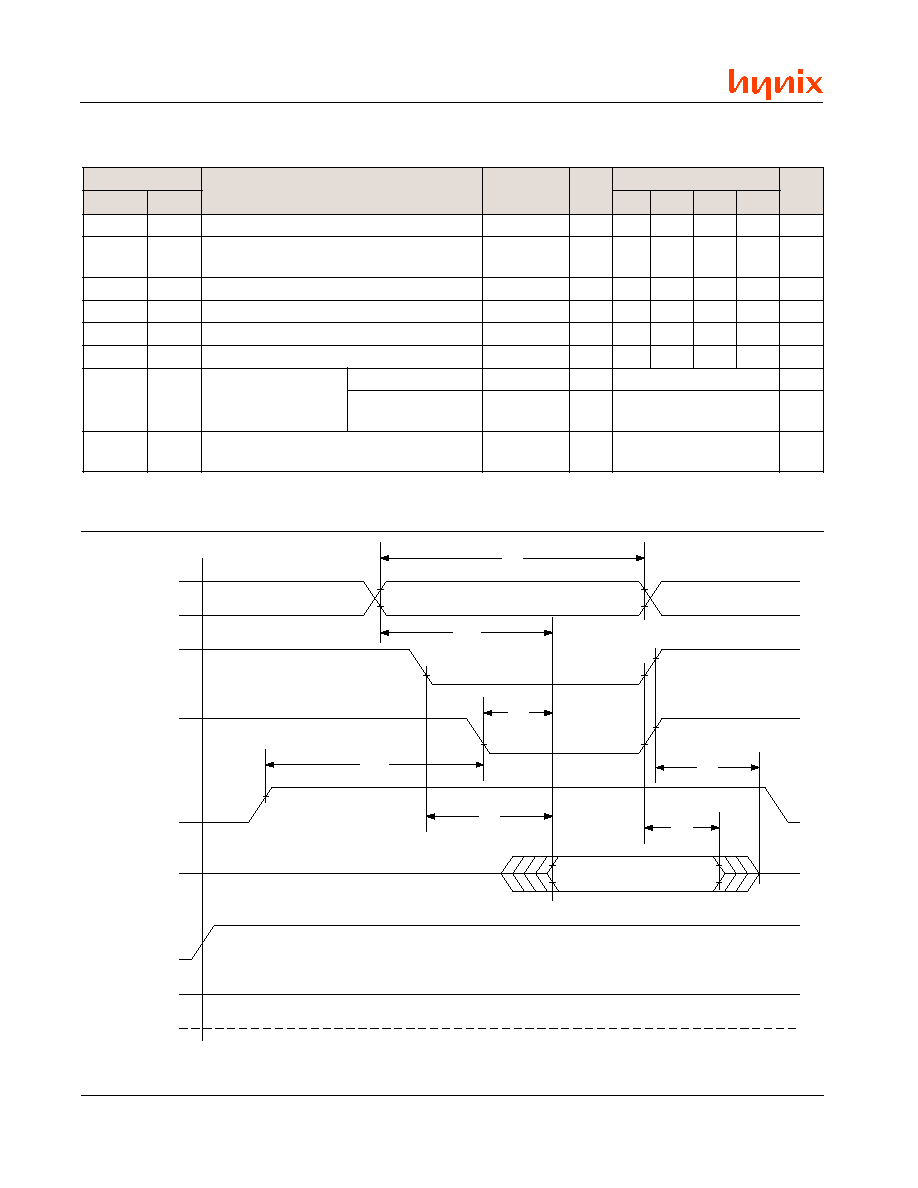

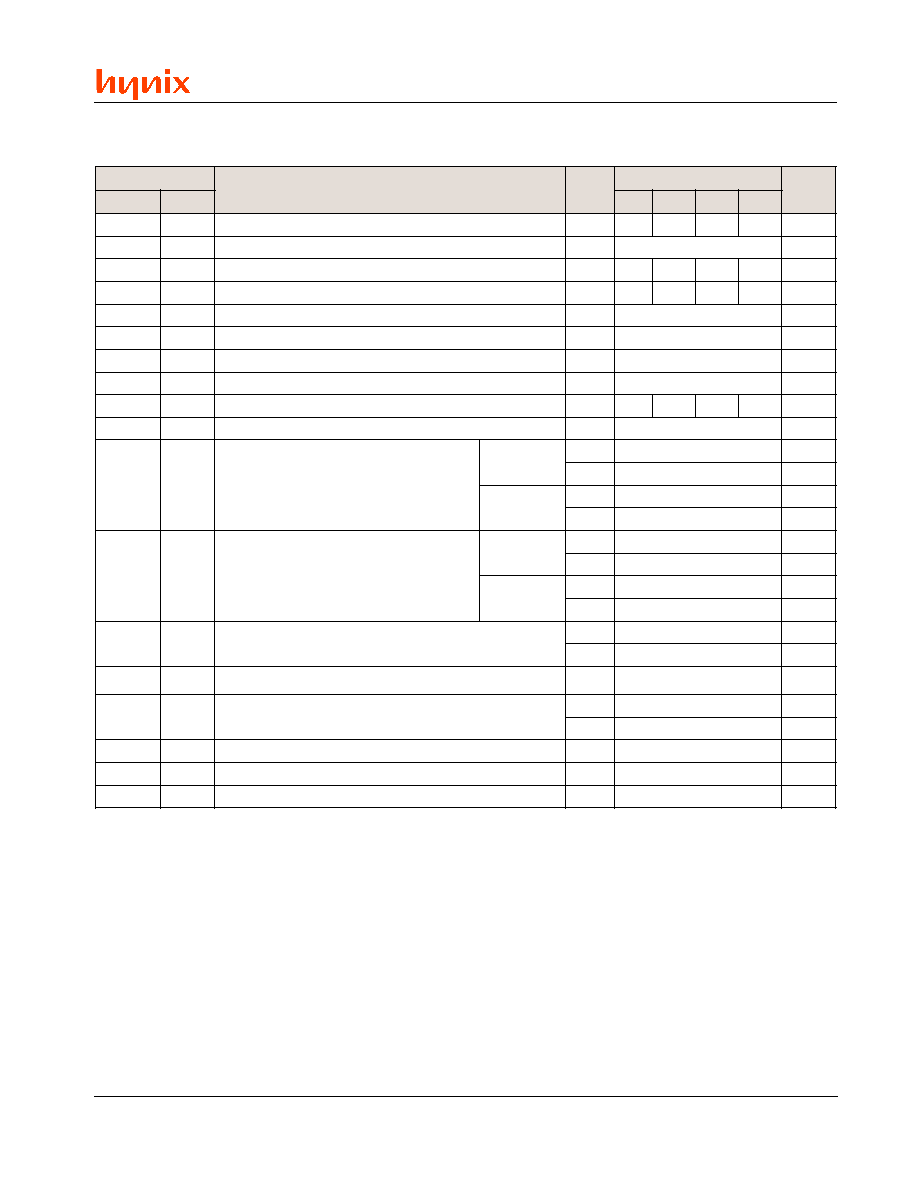

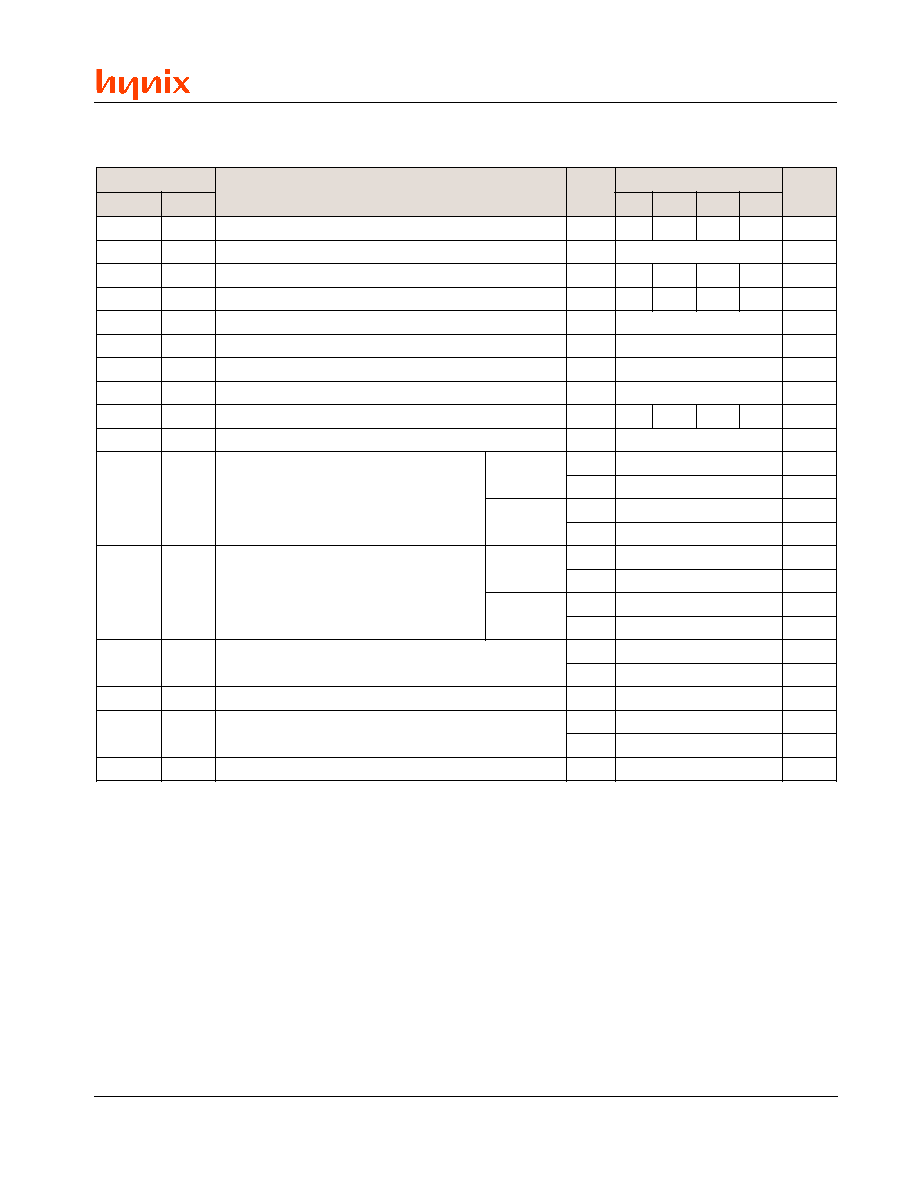

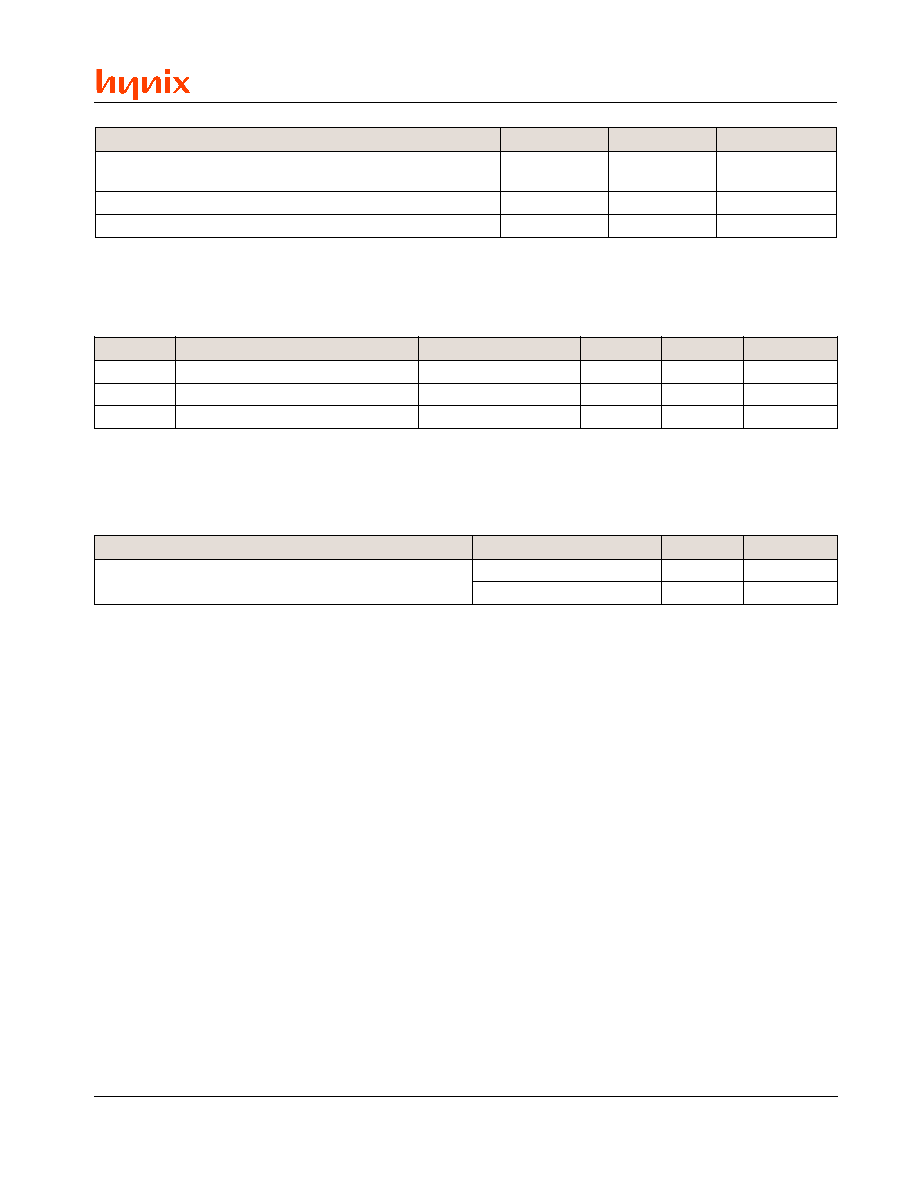

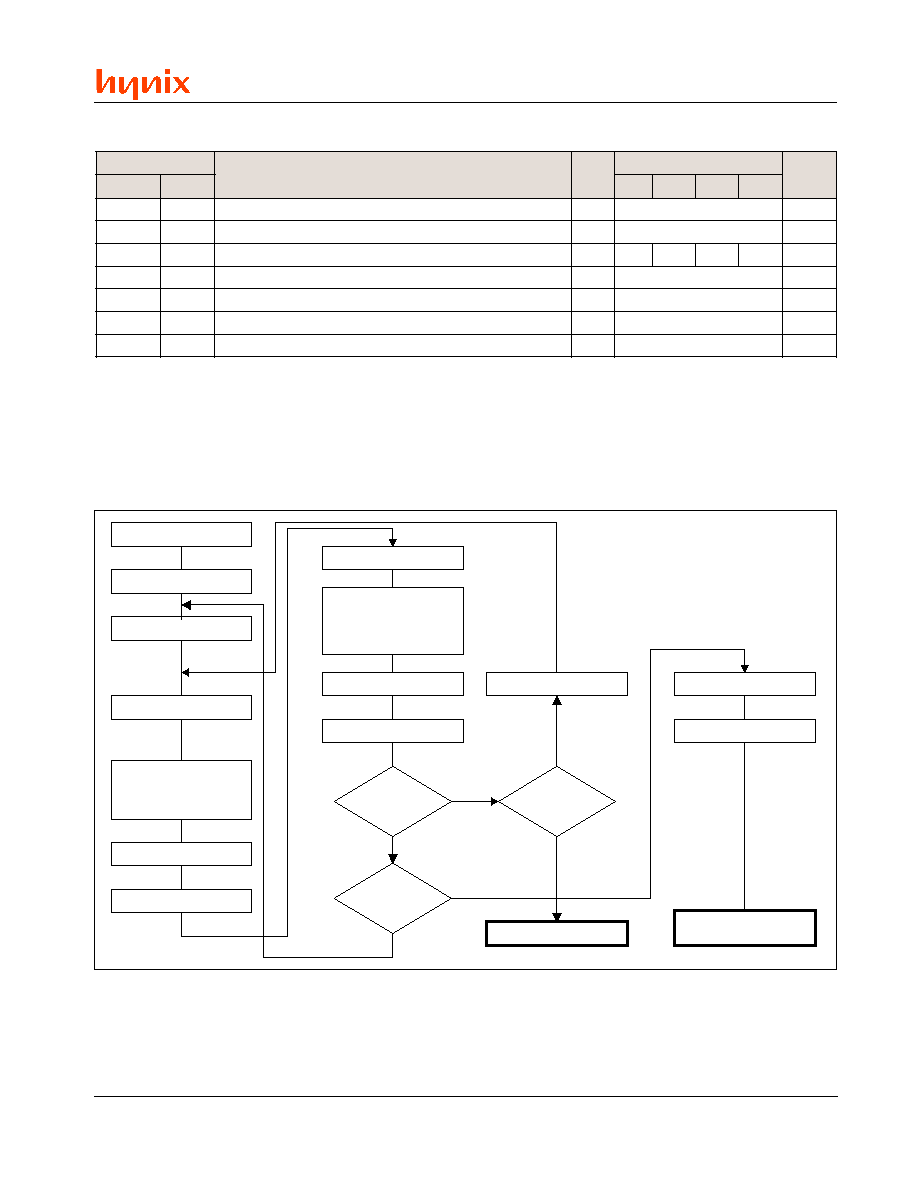

Table 3. HY29LV160 Normal Bus Operations

1

Notes:

1. L = V

IL

, H = V

IH

, X = Don't Care (L or H), D

OUT

= Data Out, D

IN

= Data In. See DC Characteristics for voltage levels.

2. Address is A[19:0, -1] in Byte Mode and A[19:0] in Word Mode.

3. DQ[15] is the A[-1] input in Byte Mode (BYTE# = L).

n

o

i

t

a

r

e

p

O

#

E

C

#

E

O

#

E

W

#

T

E

S

E

R

s

s

e

r

d

d

A

2

]

0

:

7

[

Q

D

]

8

:

5

1

[

Q

D

3

H

=

#

E

T

Y

B

L

=

#

E

T

Y

B

d

a

e

R

L

L

H

H

A

N

I

D

T

U

O

D

T

U

O

Z

-

h

g

i

H

e

t

i

r

W

L

H

L

H

A

N

I

D

N

I

D

N

I

Z

-

h

g

i

H

e

l

b

a

s

i

D

t

u

p

t

u

O

L

H

H

H

X

Z

-

h

g

i

H

Z

-

h

g

i

H

Z

-

h

g

i

H

y

b

d

n

a

t

S

l

a

m

r

o

N

#

E

C

H

X

X

H

X

Z

-

h

g

i

H

Z

-

h

g

i

H

Z

-

h

g

i

H

y

b

d

n

a

t

S

p

e

e

D

#

E

C

V

C

C

V

3

.

0

±

X

X

V

C

C

V

3

.

0

±

X

Z

-

h

g

i

H

Z

-

h

g

i

H

Z

-

h

g

i

H

t

e

s

e

R

e

r

a

w

d

r

a

H

)

y

b

d

n

a

t

S

l

a

m

r

o

N

(

X

X

X

L

X

Z

-

h

g

i

H

Z

-

h

g

i

H

Z

-

h

g

i

H

t

e

s

e

R

e

r

a

w

d

r

a

H

)

y

b

d

n

a

t

S

p

e

e

D

(

X

X

X

V

S

S

V

3

.

0

±

X

Z

-

h

g

i

H

Z

-

h

g

i

H

Z

-

h

g

i

H

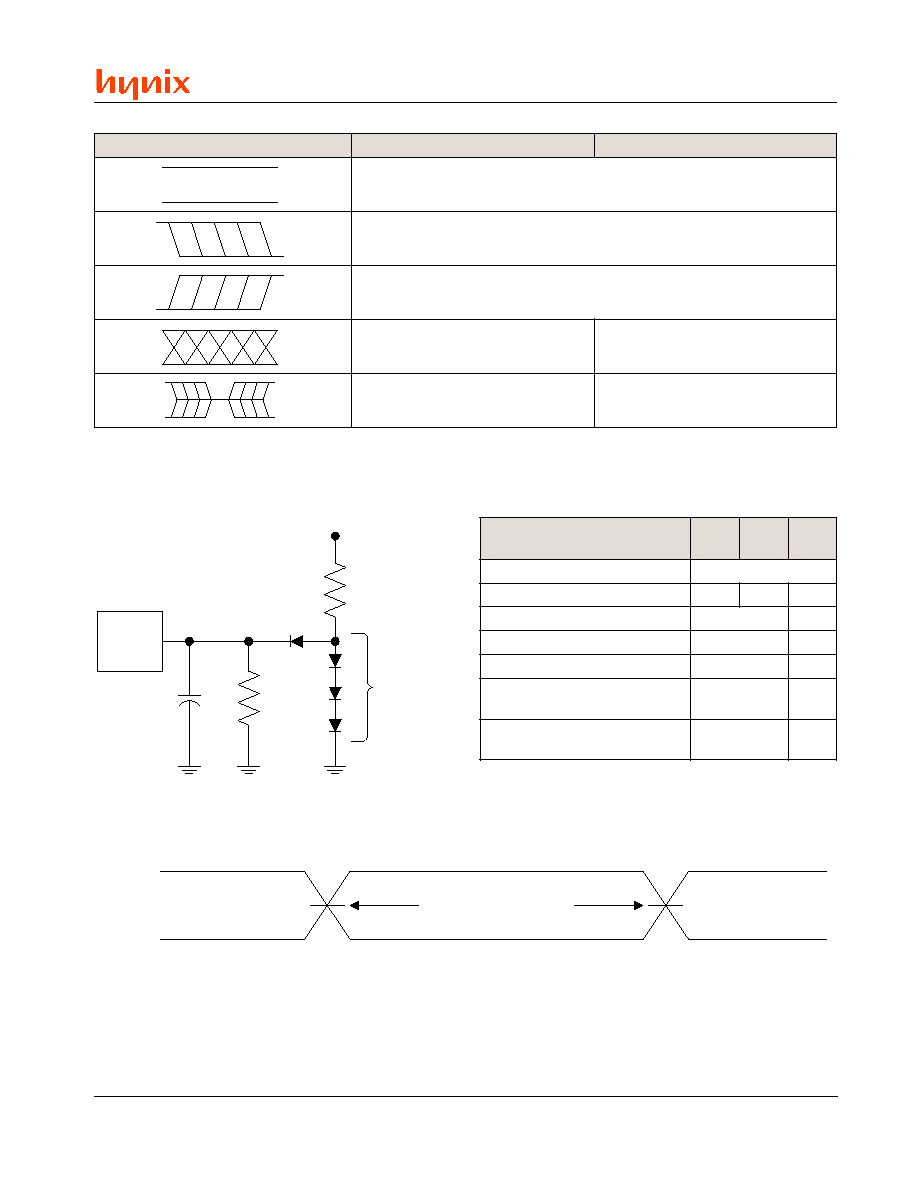

Table 4. HY29LV160 Bus Operations Requiring High Voltage

1, 2

Notes:

1. L = V

IL

, H = V

IH

, X = Don't Care (L OR H). See DC Characteristics for voltage levels.

2. Address bits not specified are Don't Care.

3. See text and Appendix A for additional information.

4. SA = Sector Address. See Tables 1 and 2.

5. DQ[15] is the A[-1] input in Byte Mode (BYTE# = L).

6. Normal read, write and output disable operations are used in this mode. See Table 3.

n

o

i

t

a

r

e

p

O

3

#

E

C

#

E

O

#

E

W

#

T

E

S

E

R

]

2

1

:

9

1

[

A

]

9

[

A

]

6

[

A

]

1

[

A

]

0

[

A

]

0

:

7

[

Q

D

]

8

:

5

1

[

Q

D

#

E

T

Y

B

H

=

#

E

T

Y

B

L

=

5

t

c

e

t

o

r

P

r

o

t

c

e

S

L

H

L

V

D

I

A

S

4

X

L

H

L

D

N

I

X

X

t

c

e

t

o

r

p

n

U

r

o

t

c

e

S

L

H

L

V

D

I

X

X

H

H

L

D

N

I

X

X

r

o

t

c

e

S

y

r

a

r

o

p

m

e

T

t

c

e

t

o

r

p

n

U

6

-

-

-

-

-

-

V

D

I

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

e

d

o

C

r

e

r

u

t

c

a

f

u

n

a

M

L

L

H

H

X

V

D

I

L

L

L

D

A

x

0

X

Z

-

h

g

i

H

e

c

i

v

e

D

e

d

o

C

B

0

6

1

V

L

9

2

Y

H

L

L

H

H

X

V

D

I

L

L

H

9

4

x

0

2

2

x

0

Z

-

h

g

i

H

T

0

6

1

V

L

9

2

Y

H

4

C

x

0

n

o

i

t

c

e

t

o

r

P

r

o

t

c

e

S

n

o

i

t

a

c

i

f

i

r

e

V

L

L

H

H

A

S

4

V

D

I

L

H

L

=

0

0

x

0

d

e

t

c

e

t

o

r

p

n

U

X

Z

-

h

g

i

H

=

1

0

x

0

d

e

t

c

e

t

o

r

P

9

Rev. 1.2/May 01

HY29LV160

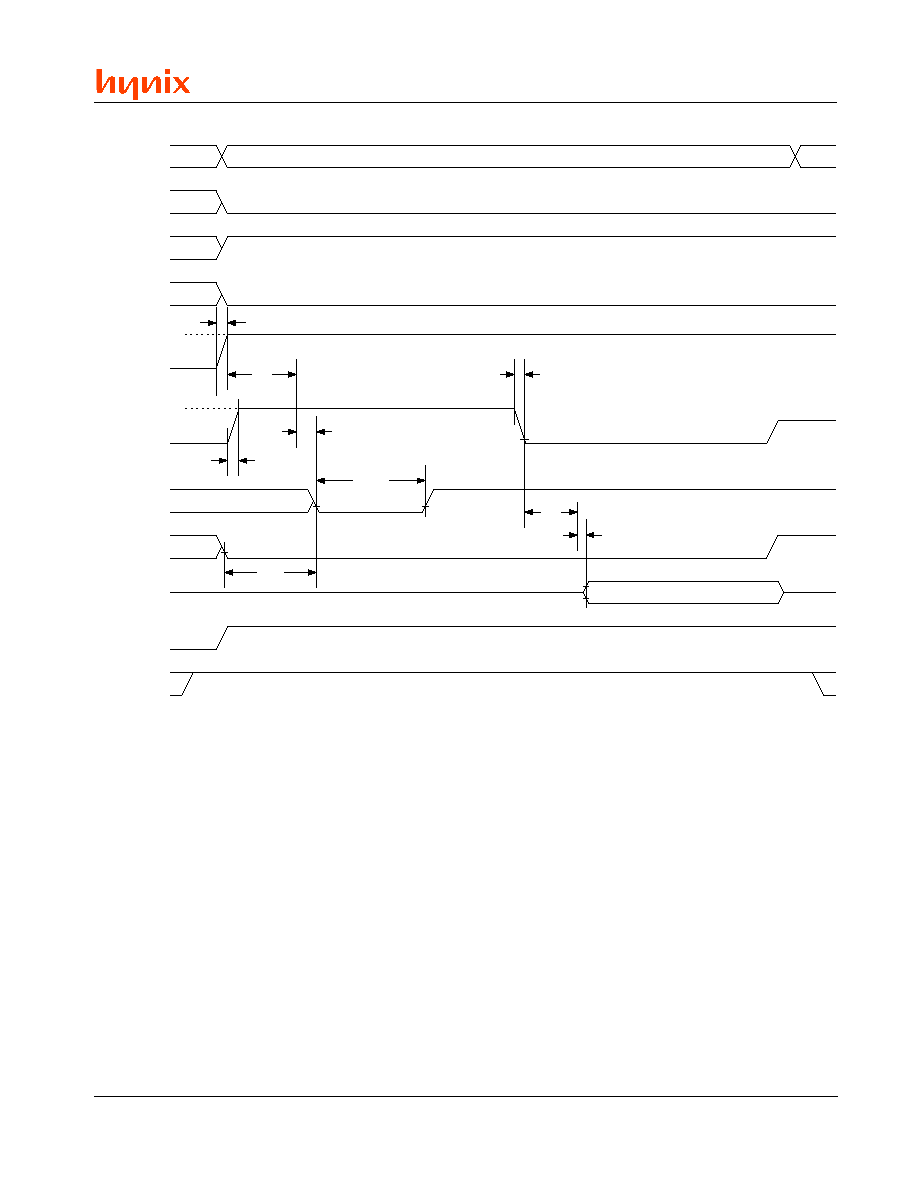

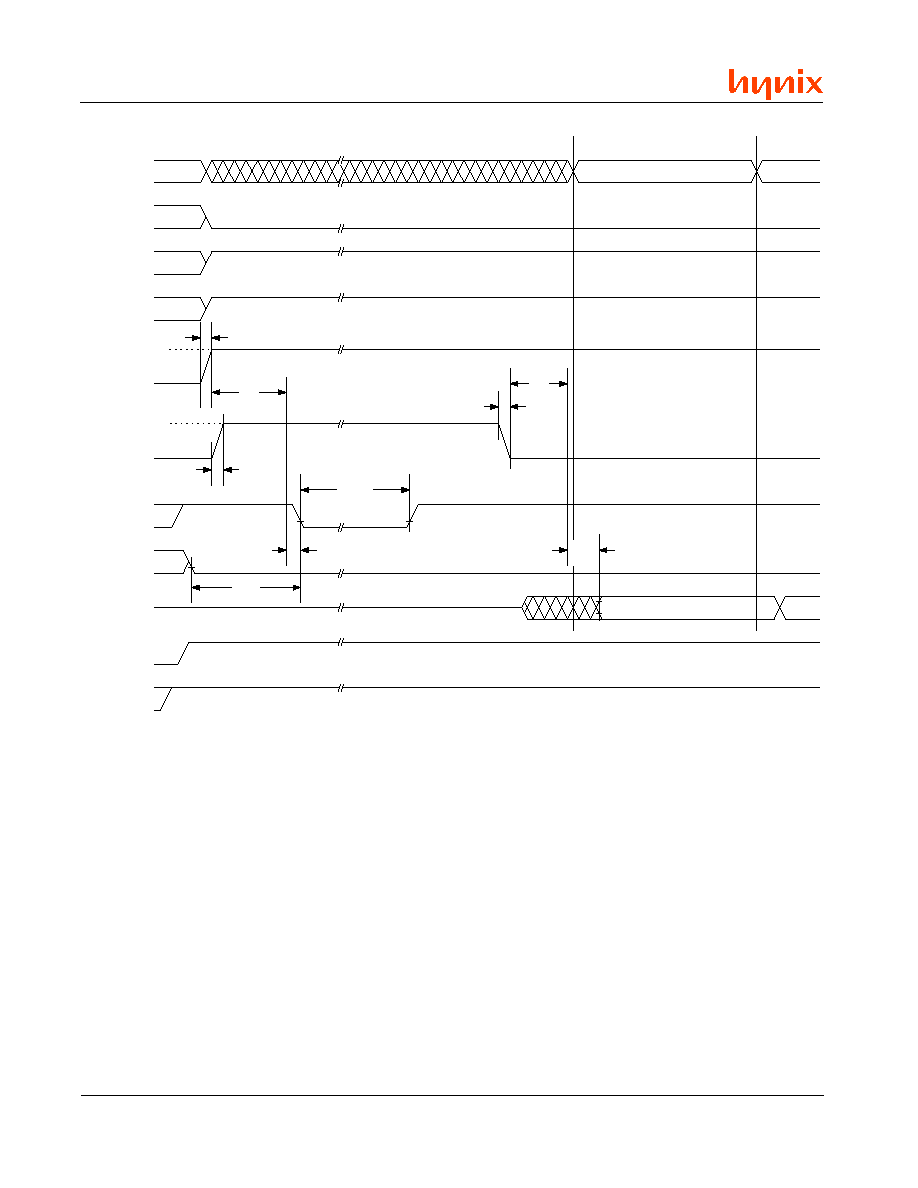

Write Operation

Certain operations, including programming data

and erasing sectors of memory, require the host

to write a command or command sequence to the

HY29LV160. Writes to the device are performed

by placing the byte or word address on the device's

address inputs while the data to be written is input

on DQ[15:0] (BYTE# = High) or DQ[7:0] (BYTE#

= Low). The host system must drive the CE# and

WE# pins Low and drive OE# High for a valid write

operation to take place. All addresses are latched

on the falling edge of WE# or CE#, whichever

happens later. All data is latched on the rising edge

of WE# or CE#, whichever happens first.

The "Device Commands" section of this data sheet

provides details on the specific device commands

implemented in the HY29LV160.

Standby Operation

When the system is not reading or writing to the

device, it can place the HY29LV160 in the Standby

mode. In this mode, current consumption is greatly

reduced, and the data bus outputs are placed in

the high impedance state, independent of the OE#

input. The Standby mode can be invoked using

two methods.

The device enters the CE# Deep Standby mode

when the CE# and RESET# pins are both held at

V

CC

± 0.3V. Note that this is a more restricted

voltage range than V

IH

. If both CE# and RESET#

are held at V

IH

, but not within V

CC

± 0.3V, the de-

vice will be in the CE# Normal Standby mode, but

the standby current will be greater.

The device enters the RESET# Deep Standby

mode when the RESET# pin is held at V

SS

± 0.3V.

If RESET# is held at V

IL

but not within V

SS

± 0.3V,

the device will be in the RESET# Normal Standby

mode, but the standby current will be greater. See

Reset Operation for additional information.

The device requires standard access time (t

CE

) for

read access when the device is in either of the

standby modes, before it is ready to read data. If

the device is deselected during erasure or pro-

gramming, it continues to draw active current until

the operation is completed.

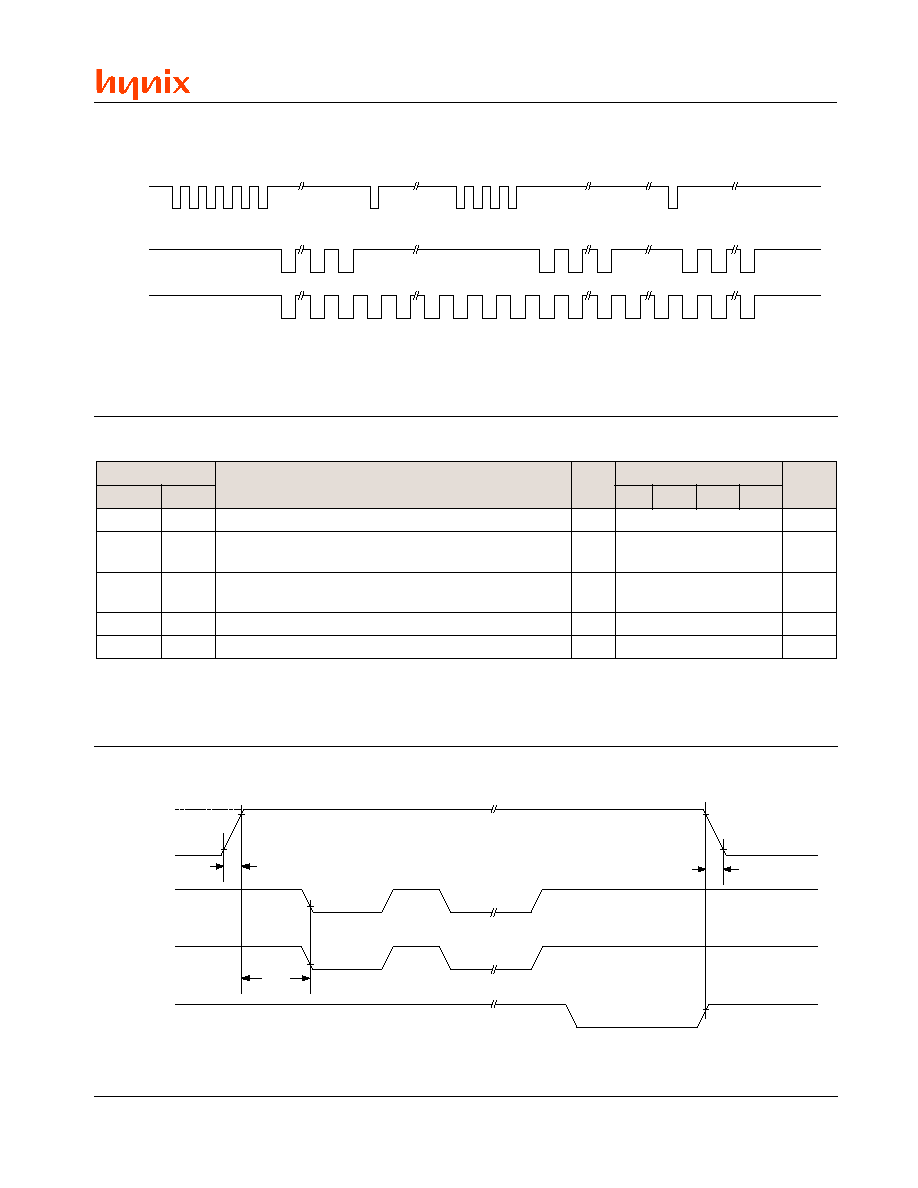

Sleep Mode

The sleep mode automatically minimizes device

power consumption. This mode is automatically

entered when addresses remain stable for t

ACC

+

30 ns (typical) and is independent of the state of

the CE#, WE#, and OE# control signals. Stan-

dard address access timings provide new data

when addresses are changed. While in sleep

mode, output data is latched and always available

to the system.

NOTE: Sleep mode is entered only when the device is

in read mode. It is not entered if the device is executing

an automatic algorithm, if it is in erase suspend mode,

or during receipt of a command sequence.

Output Disable Operation

When the OE# input is at V

IH

, output data from the

device is disabled and the data bus pins are placed

in the high impedance state.

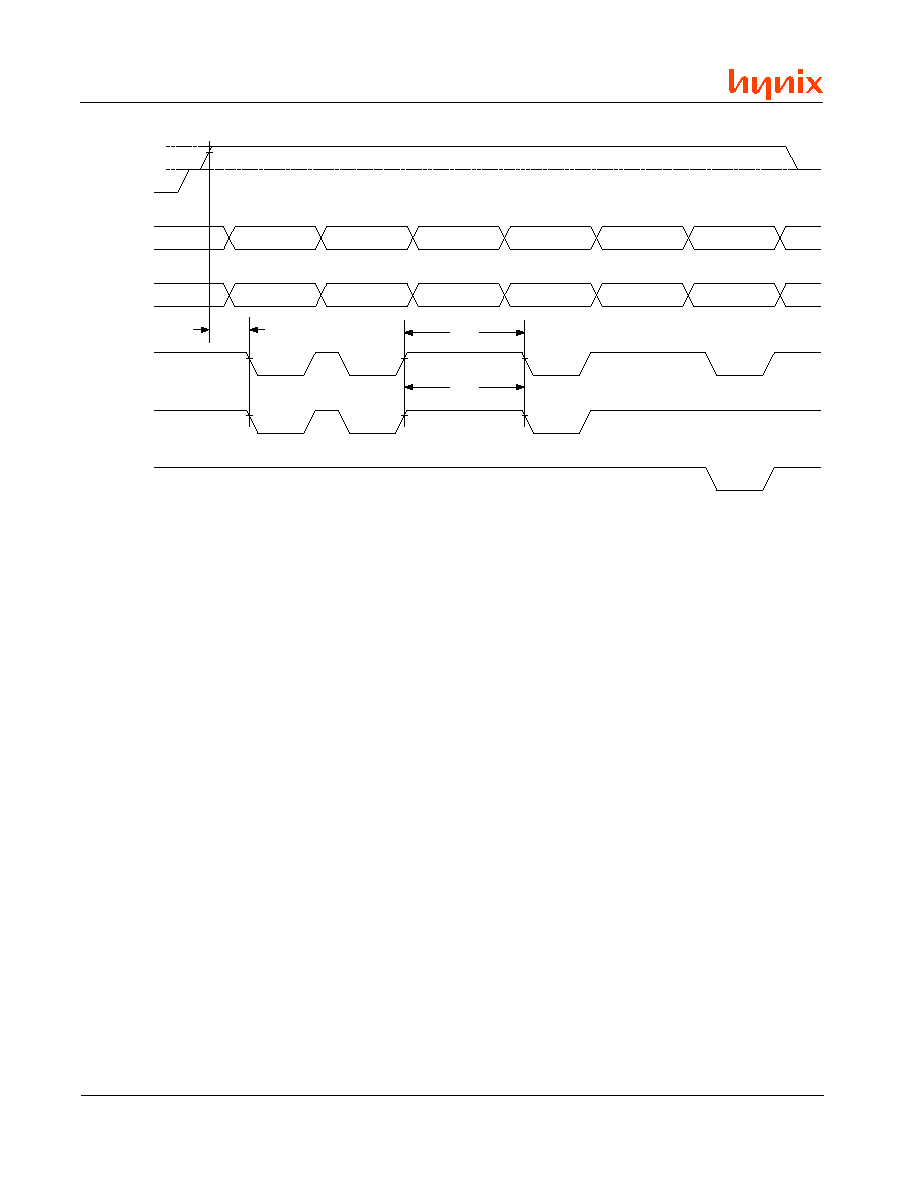

Reset Operation

The RESET# pin provides a hardware method of

resetting the device to reading array data. When

the RESET# pin is driven low for the minimum

specified period, the device immediately termi-

nates any operation in progress, tri-states the data

bus pins, and ignores all read/write commands for

the duration of the RESET# pulse. The device also

resets the internal state machine to reading array

data. If an operation was interrupted by the as-

sertion of RESET#, it should be reinitiated once

the device is ready to accept another command

sequence to ensure data integrity.

Current is reduced for the duration of the RESET#

pulse as described in the Standby Operation sec-

tion above.

If RESET# is asserted during a program or erase

operation, the RY/BY# pin remains Low (busy) until

the internal reset operation is complete, which re-

quires a time of t

READY

(during Automatic Algo-

rithms). The system can thus monitor RY/BY# to

determine when the reset operation completes,

and can perform a read or write operation t

RB

after

RY/BY# goes High. If RESET# is asserted when

a program or erase operation is not executing (RY/

BY# pin is High), the reset operation is completed

within a time of t

RP

. In this case, the host can per-

form a read or write operation t

RH

after the RE-

SET# pin returns High .

The RESET# pin may be tied to the system reset

signal. Thus, a system reset would also reset the

device, enabling the system to read the boot-up

firmware from the Flash memory.

10

Rev. 1.2/May 01

HY29LV160

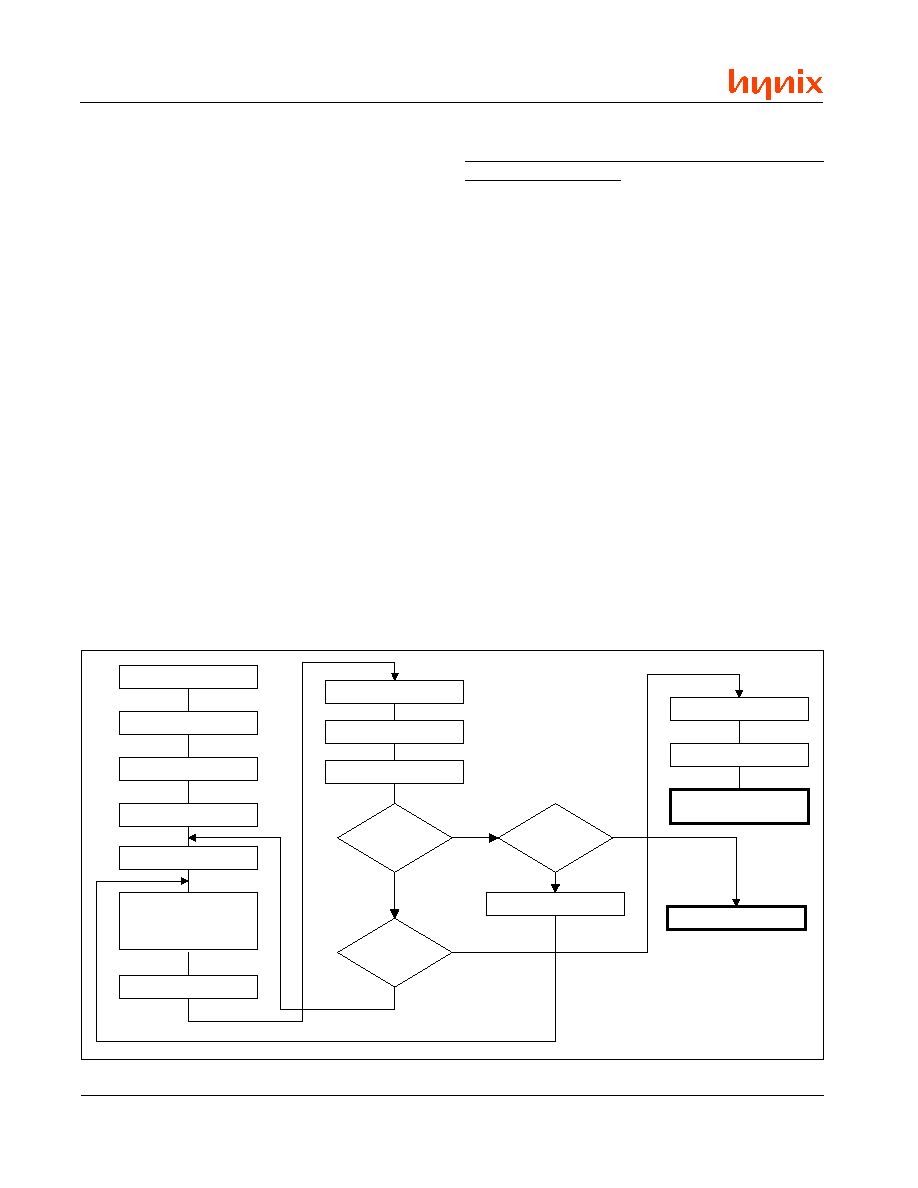

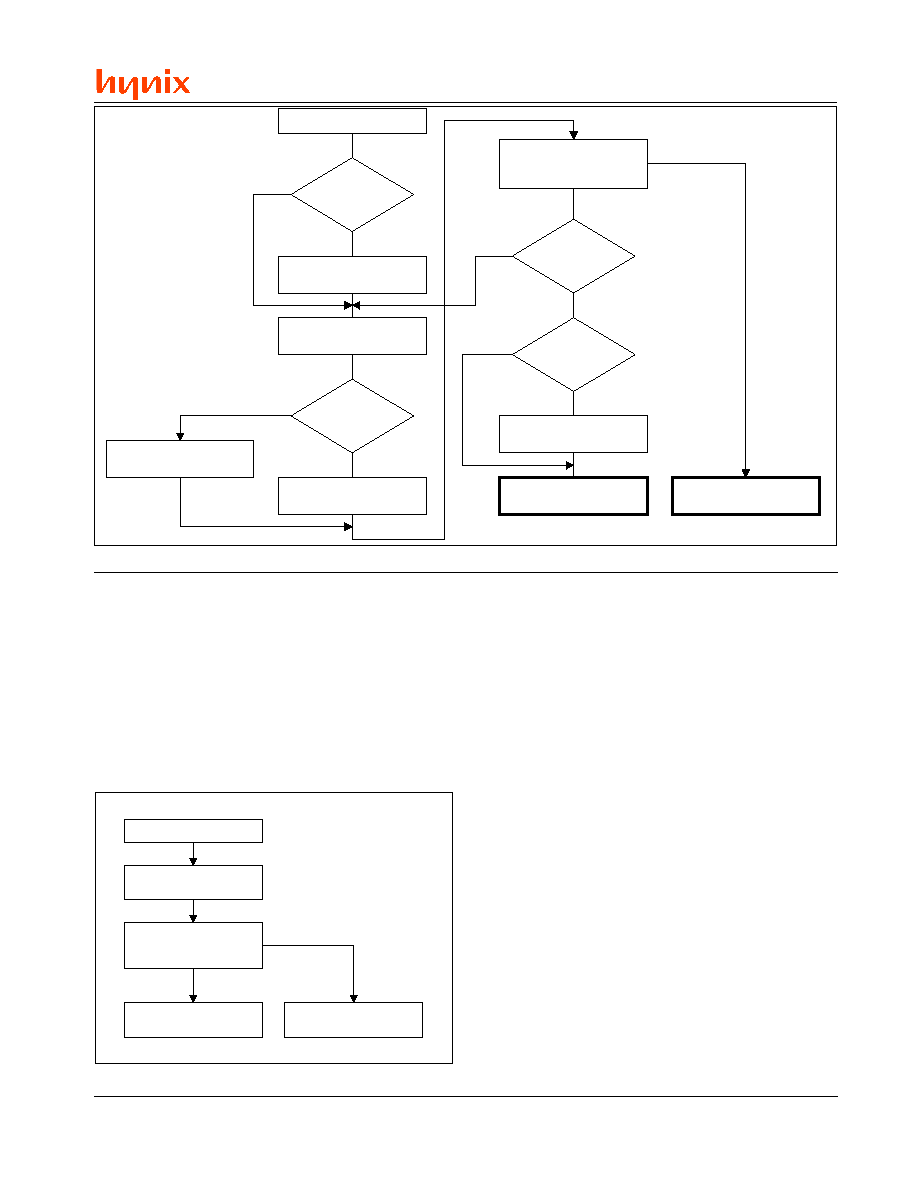

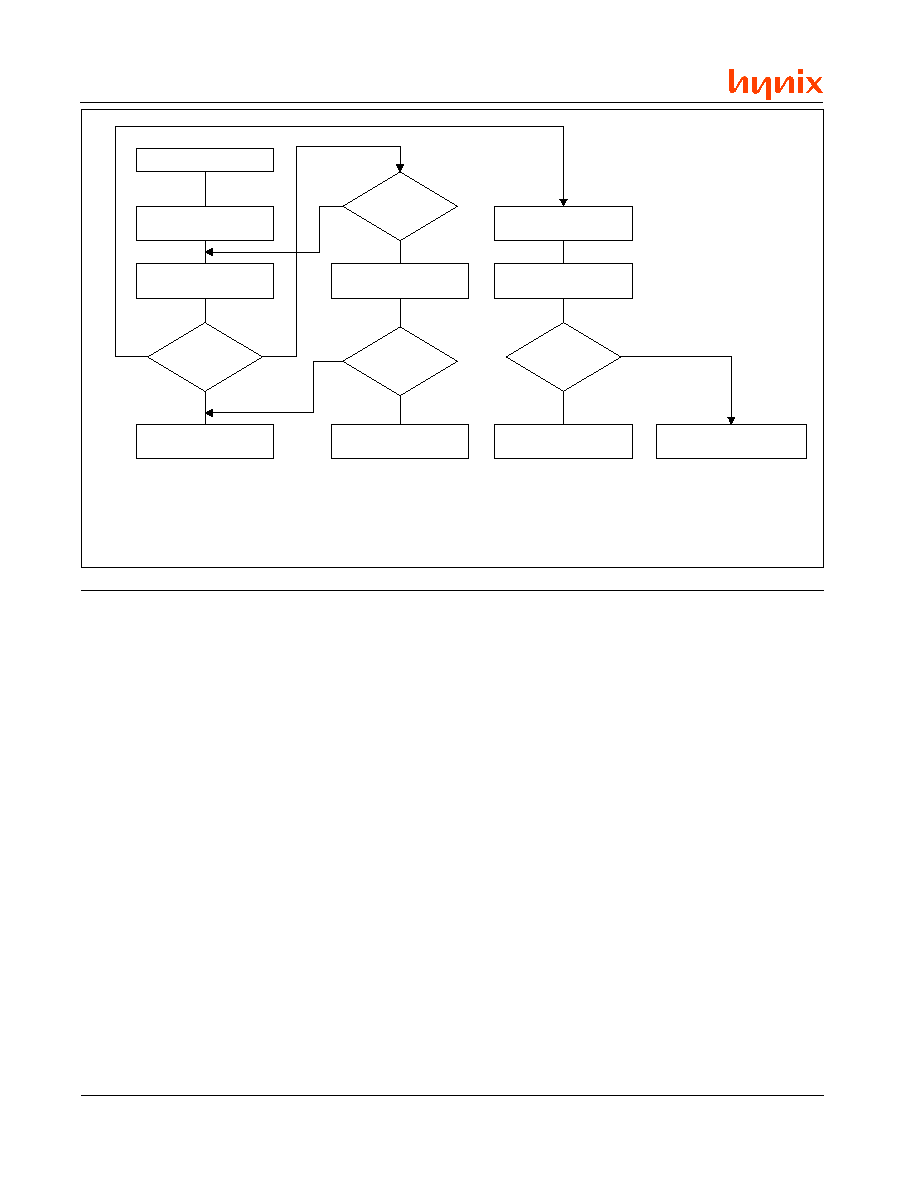

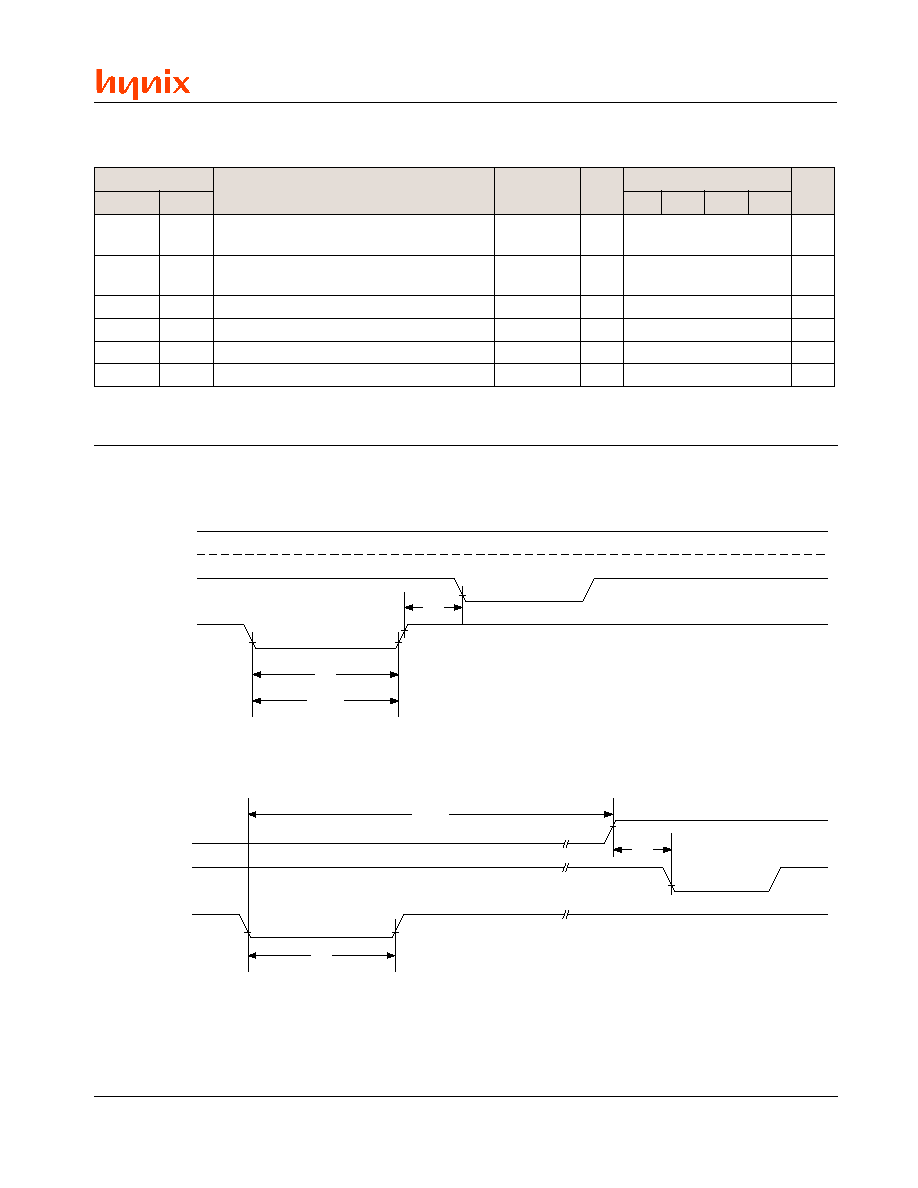

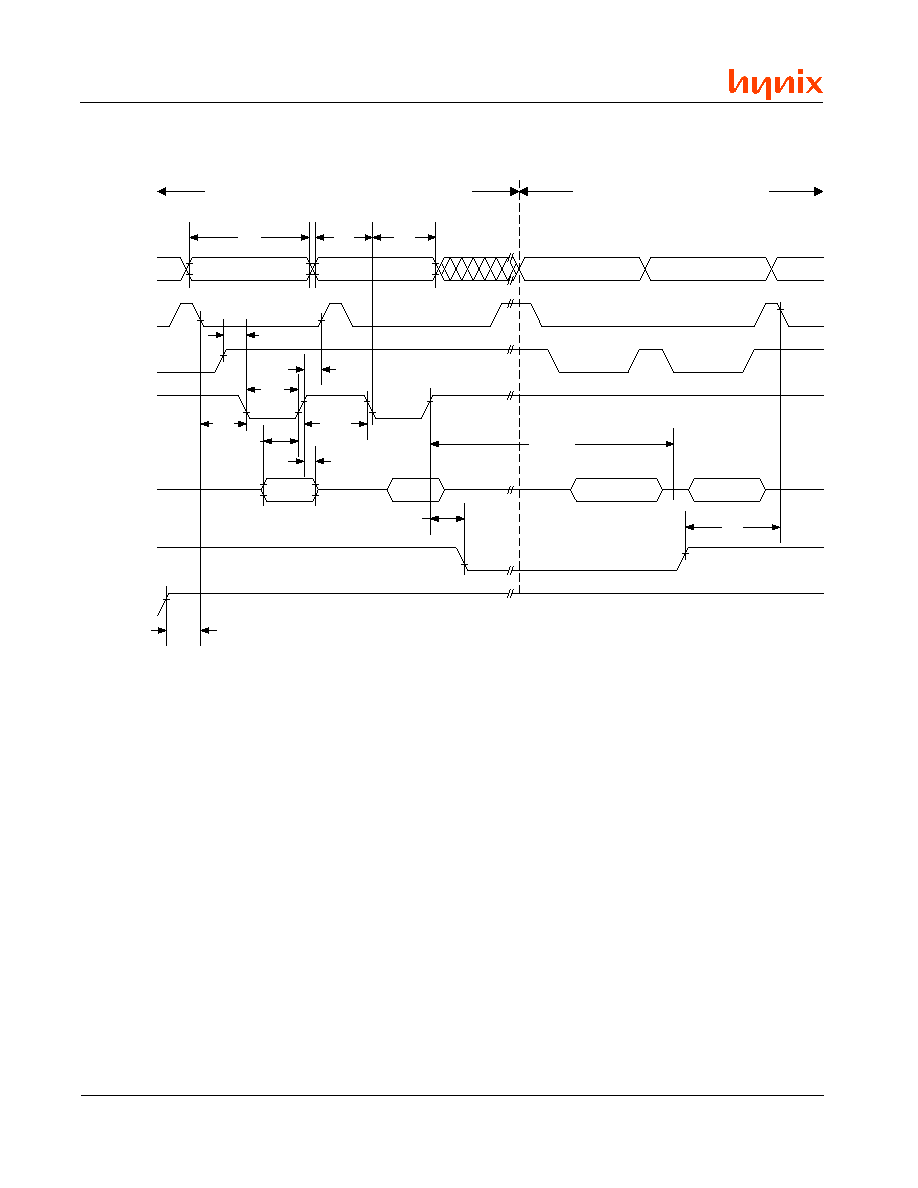

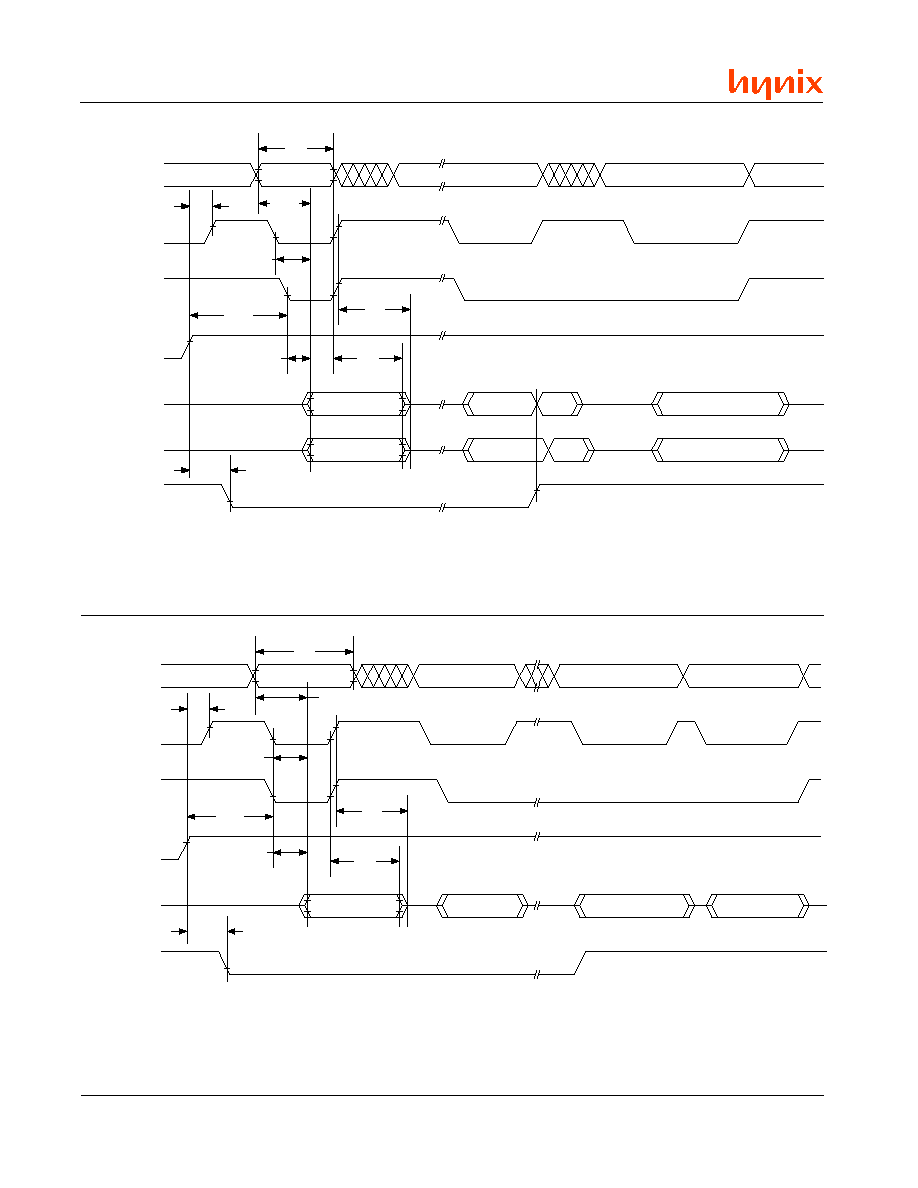

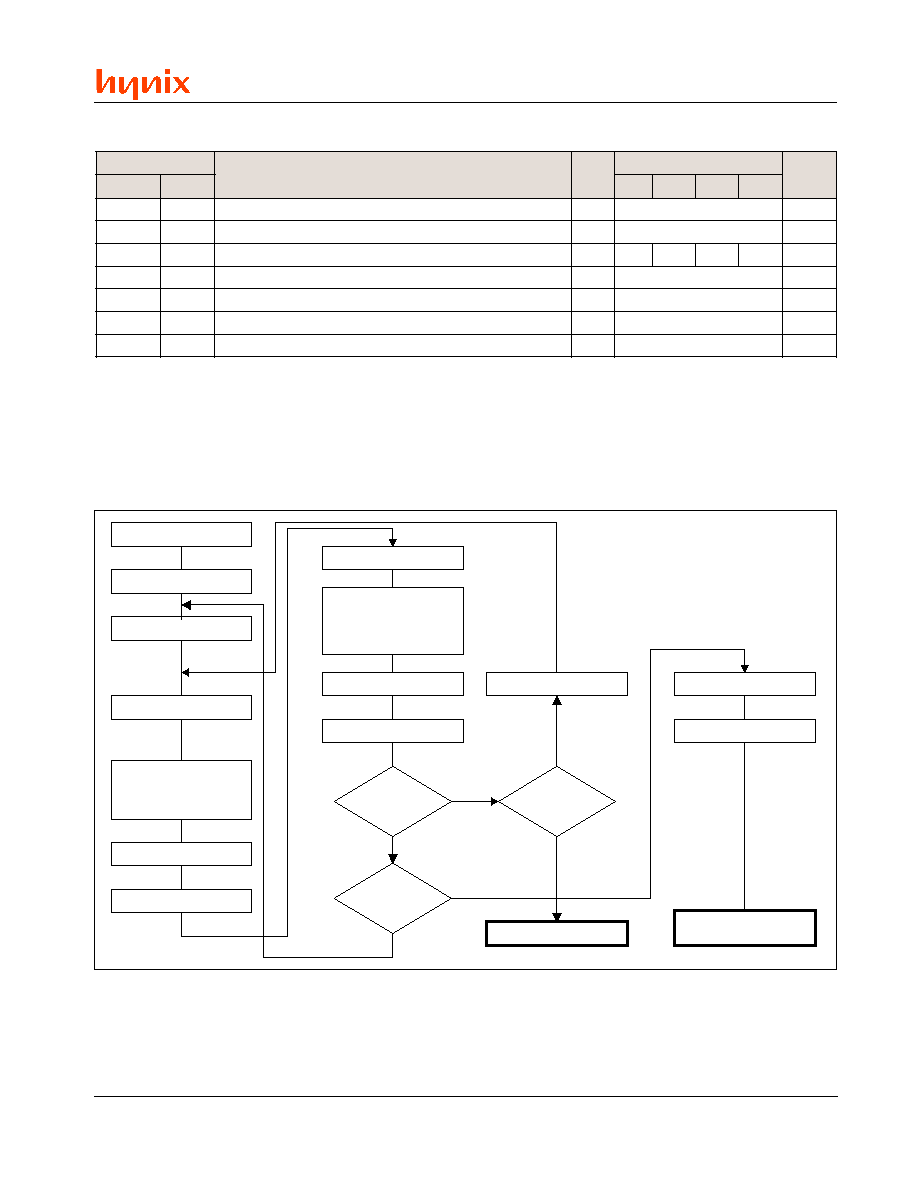

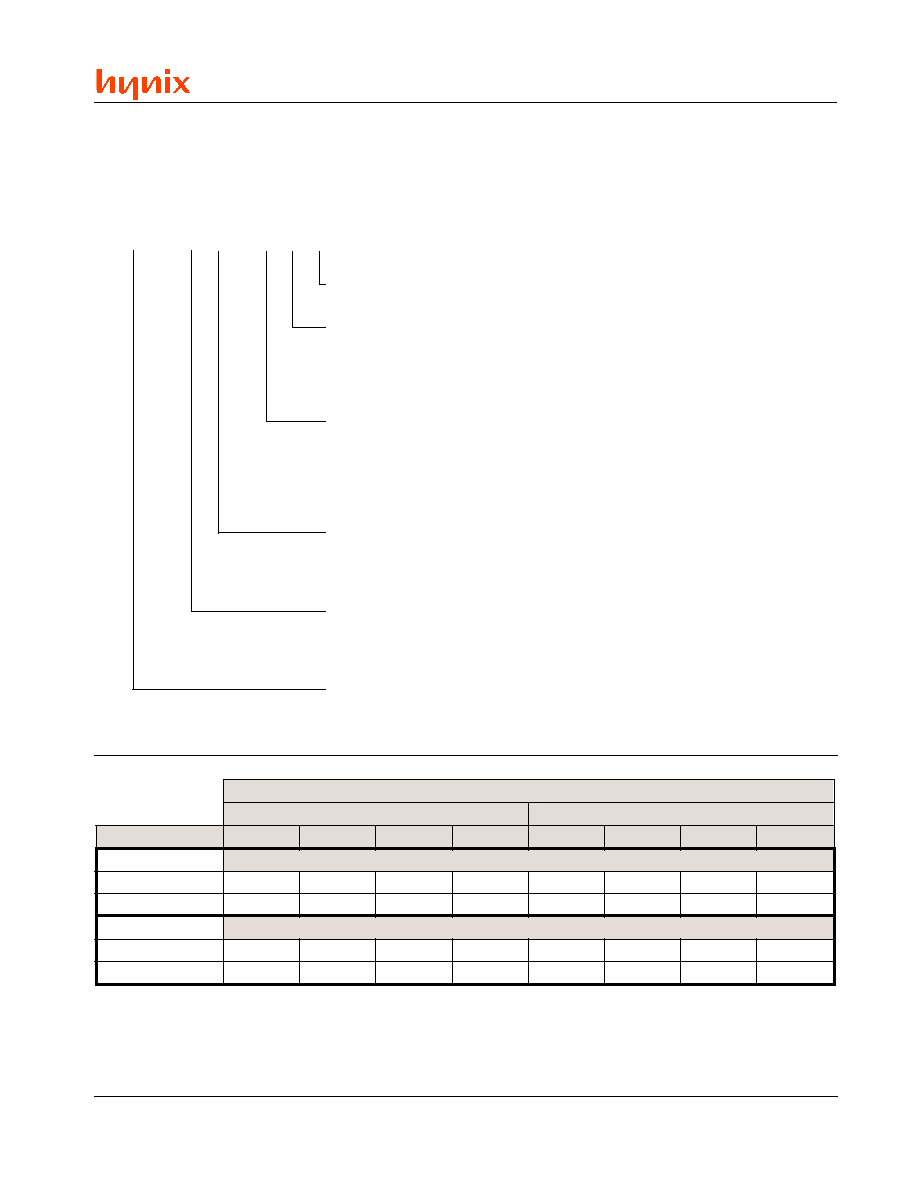

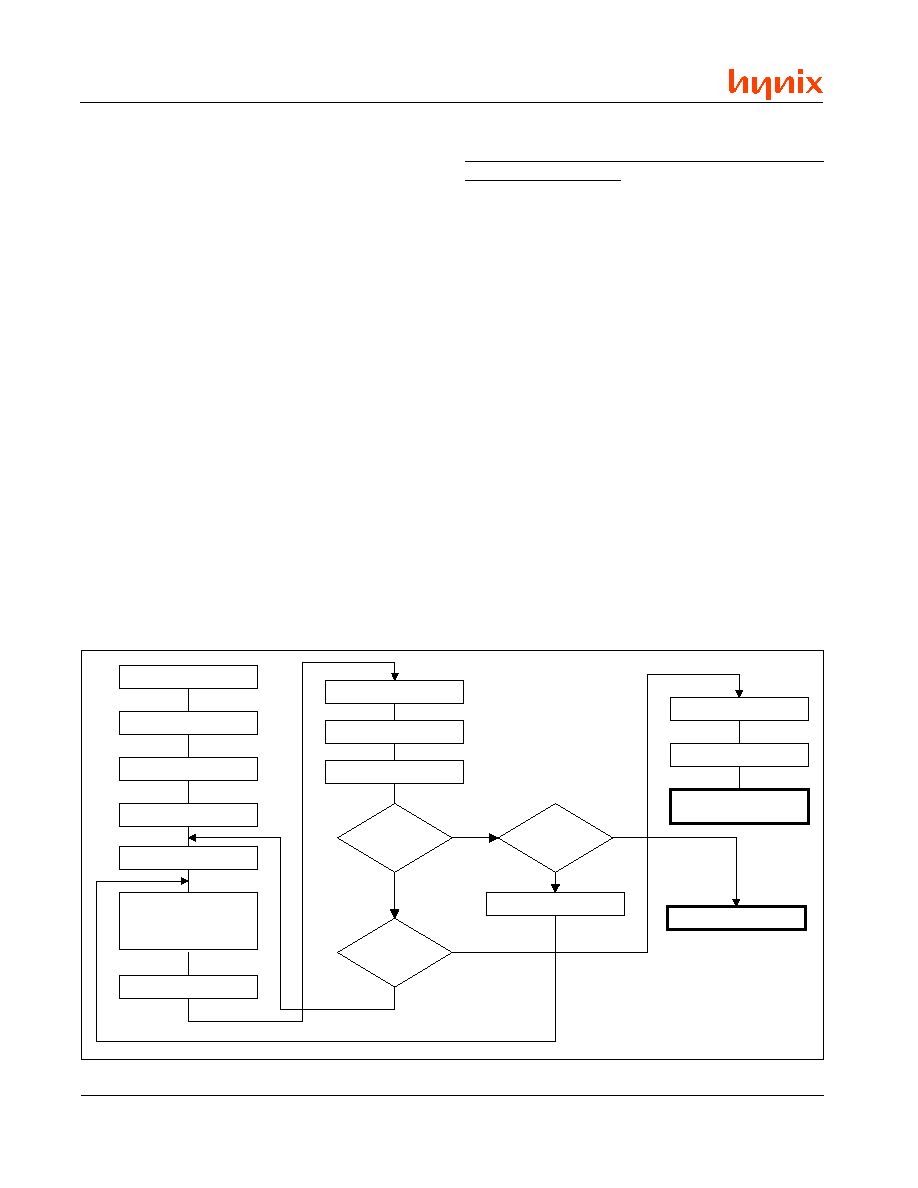

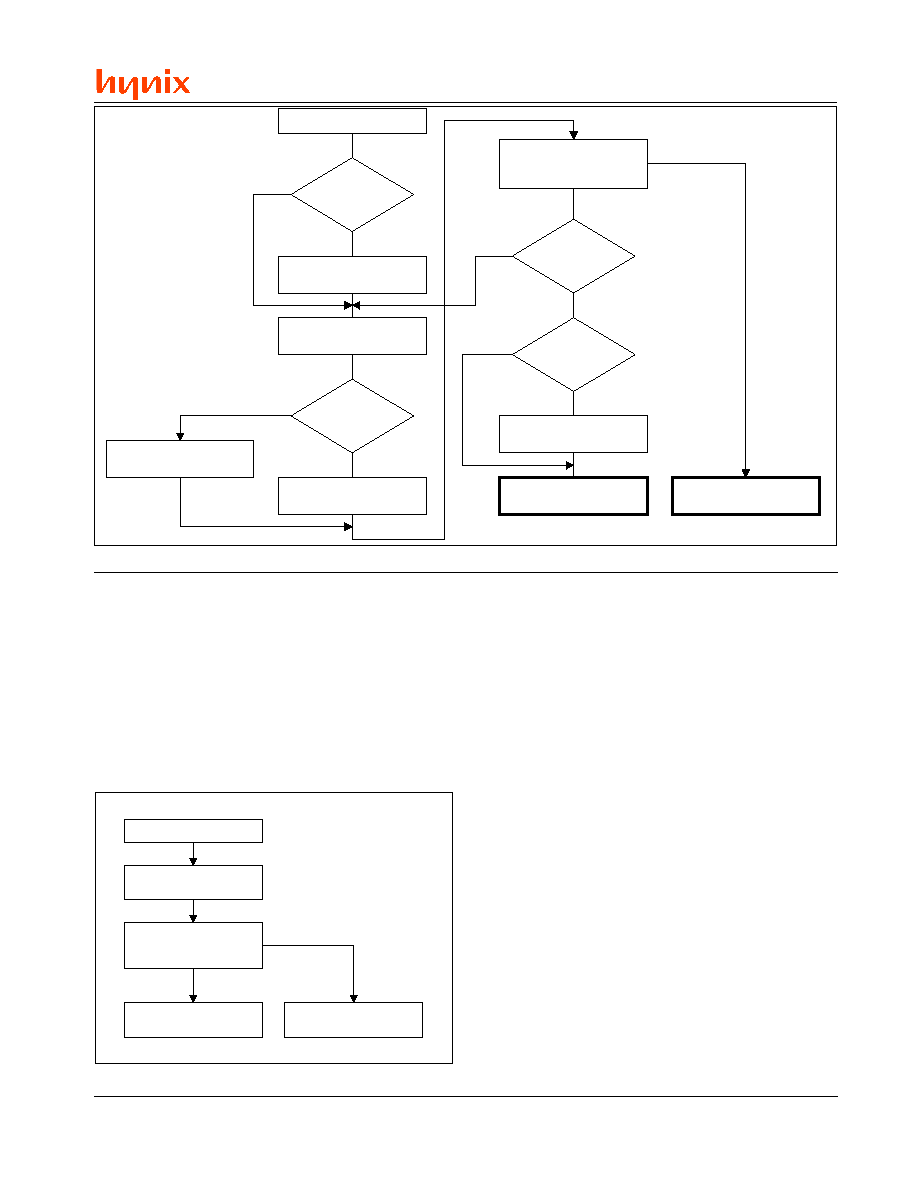

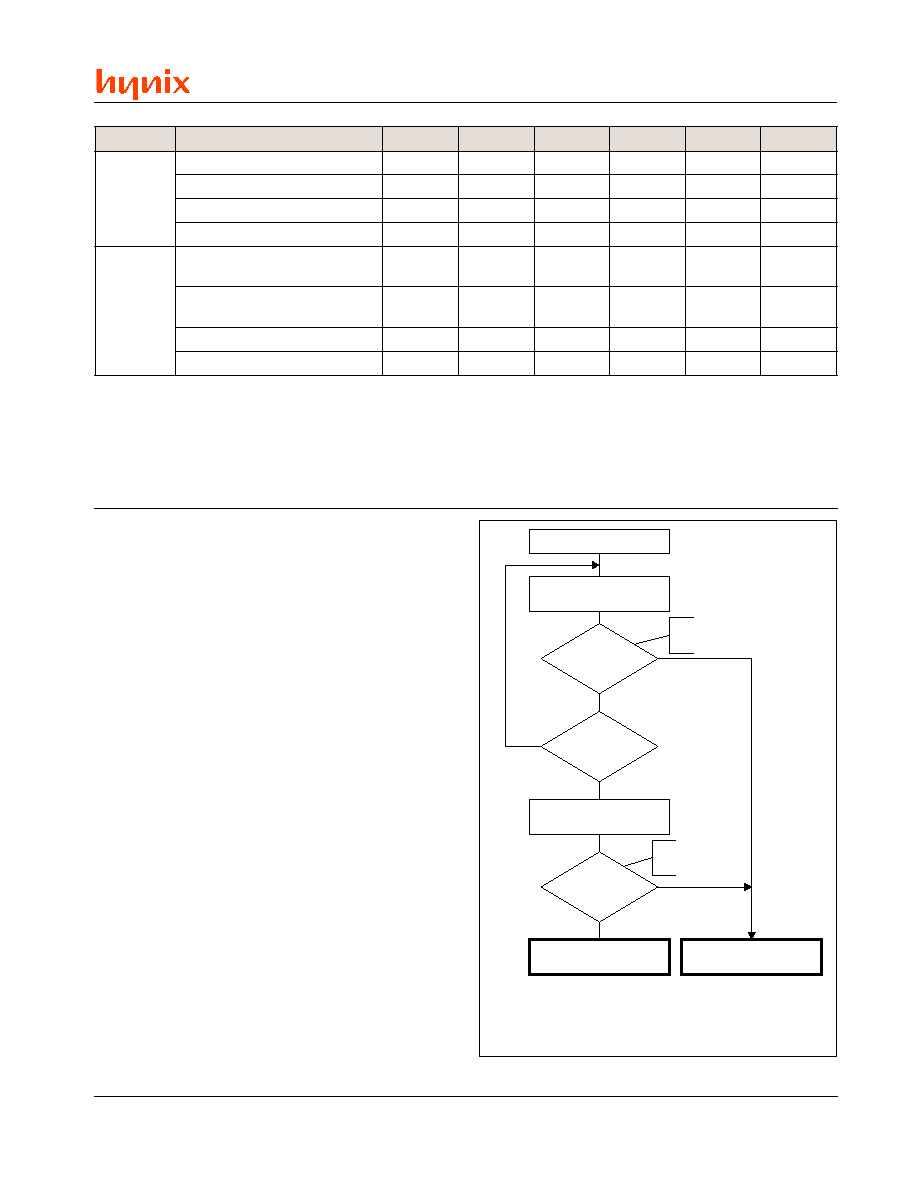

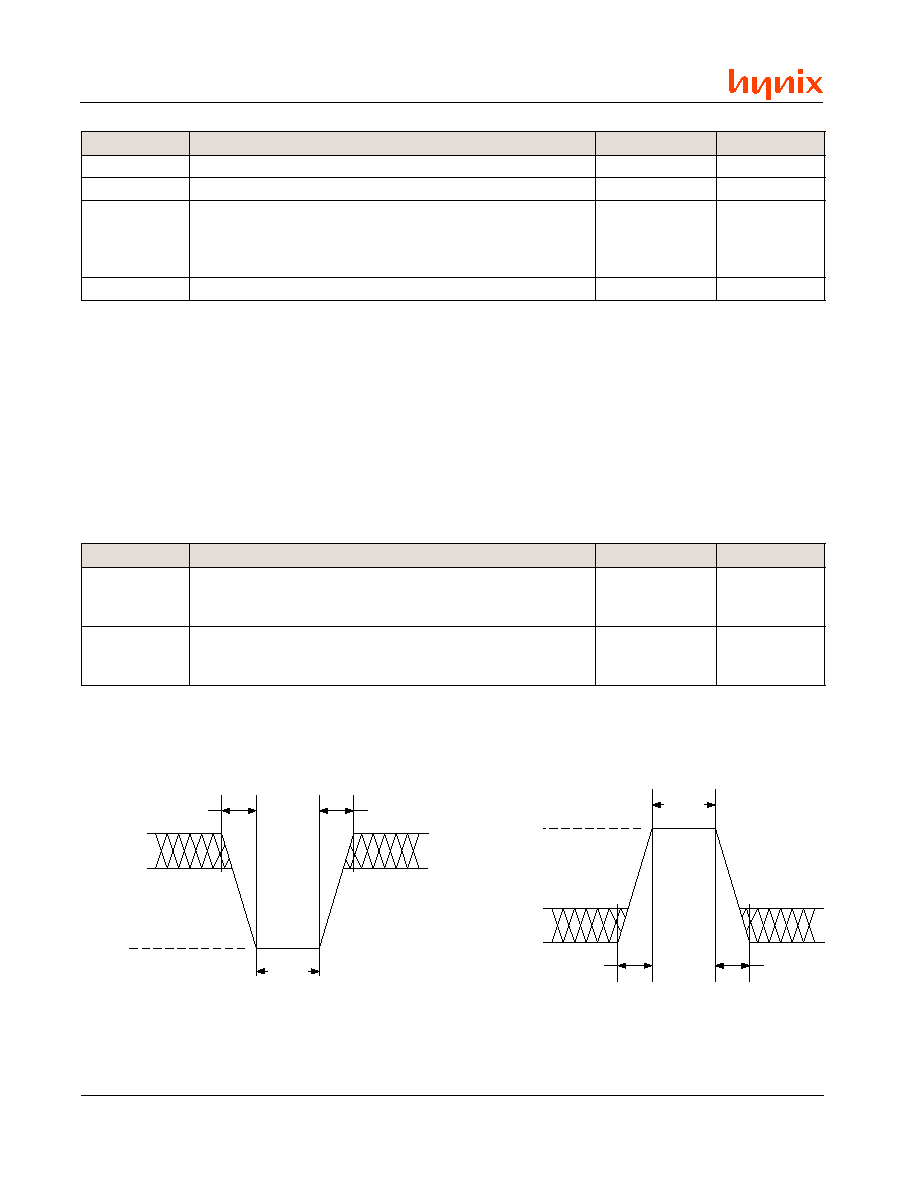

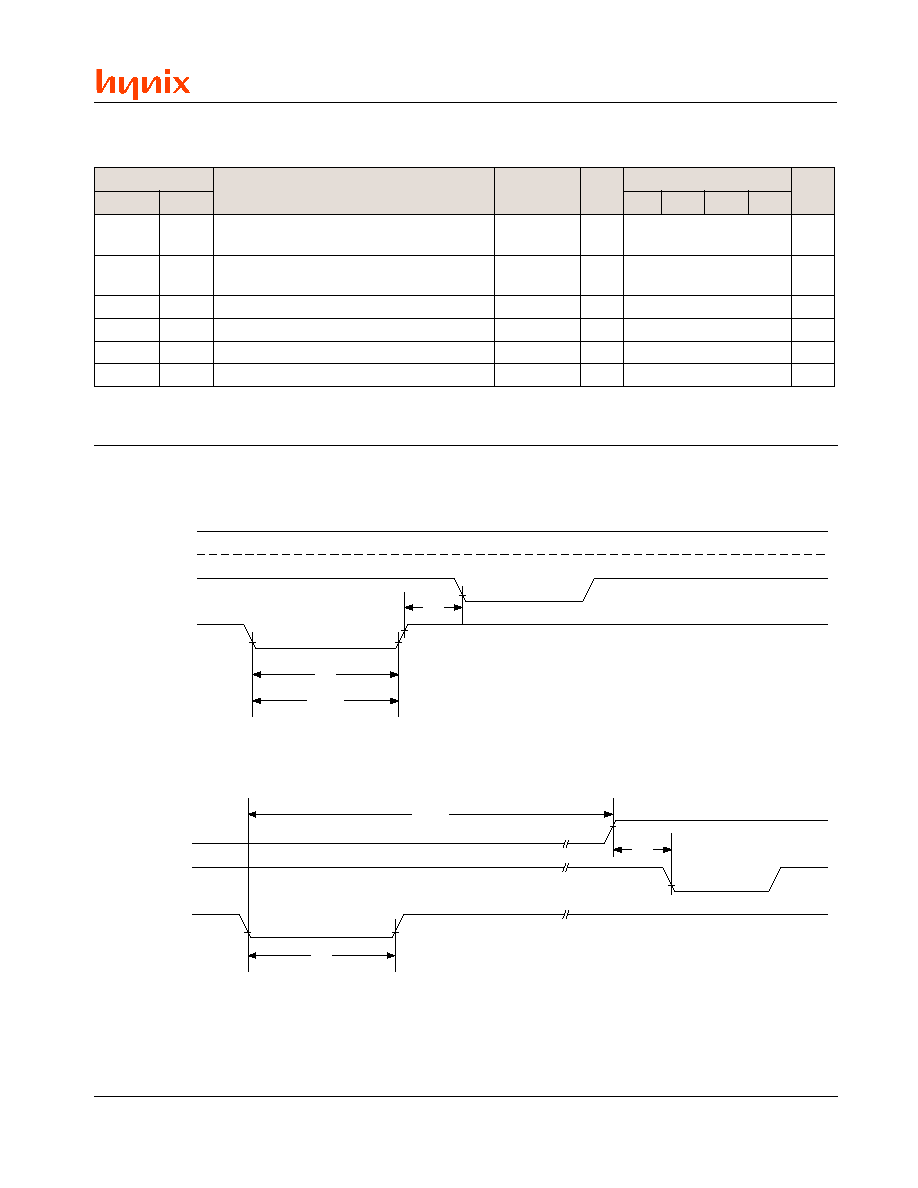

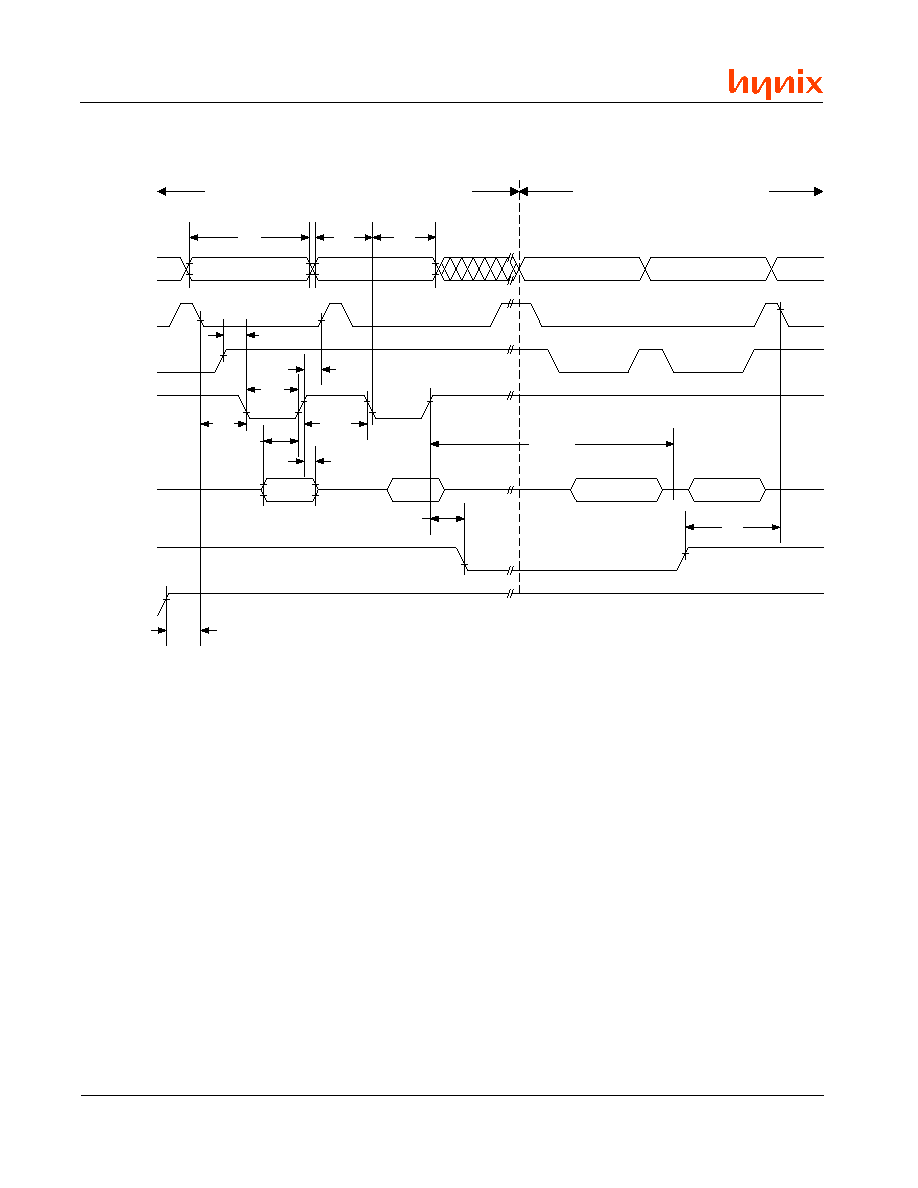

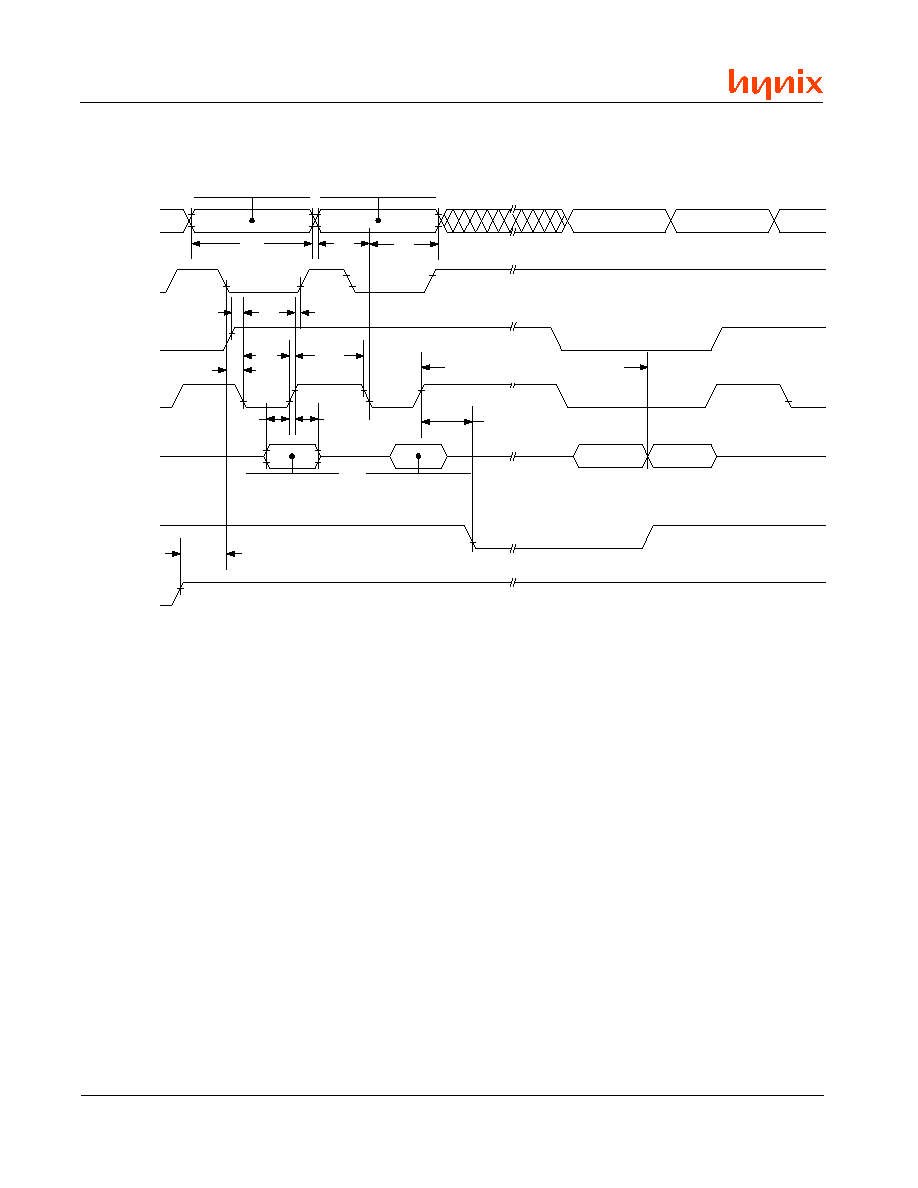

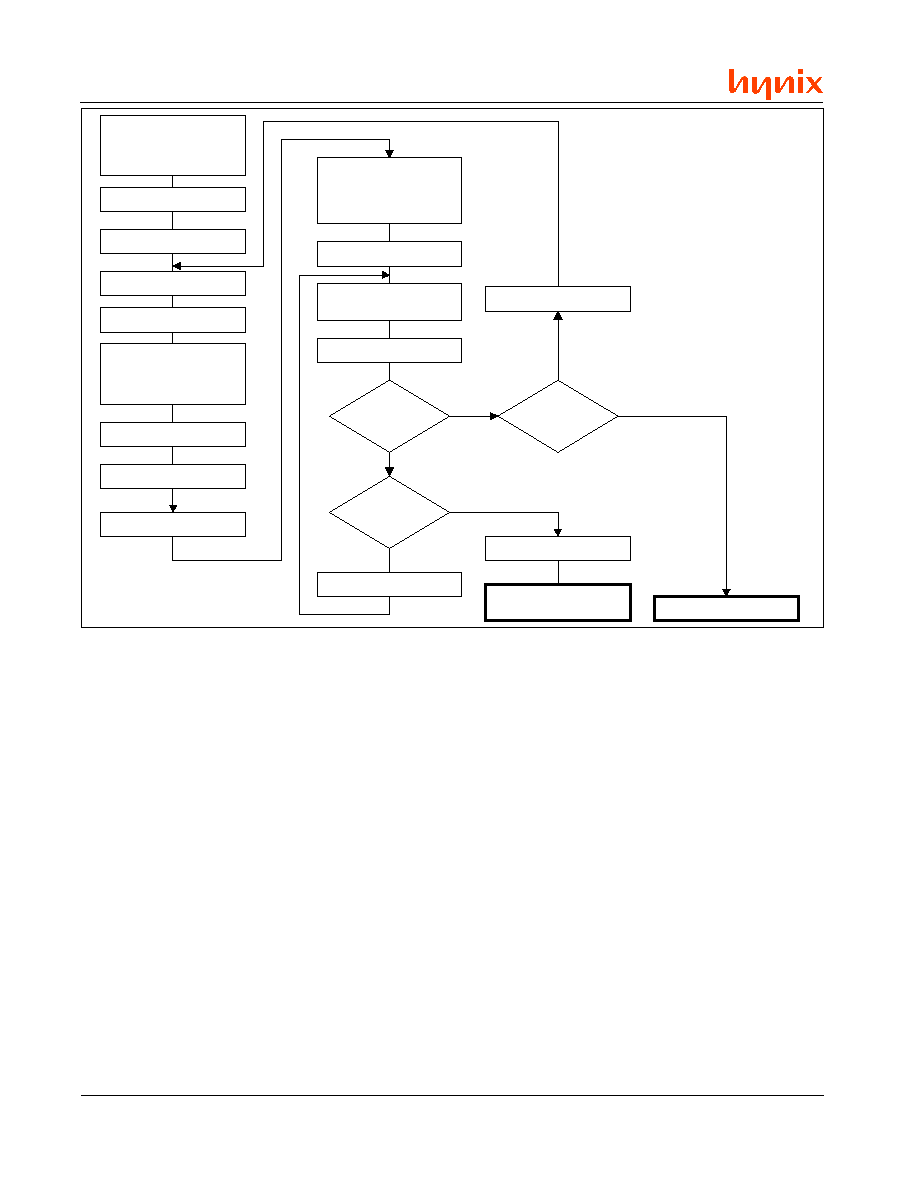

Sector Protect Operation

The hardware sector protection feature disables

both program and erase operations in any sector

or combination of sectors. This function can be

implemented either in-system or by using program-

ming equipment.

The method intended for programming equipment

requires a high voltage (V

ID

) on address pin A[9]

and the control pins. Refer to the Appendix at the

end of this document for additional information.

The in-system method requires V

ID

only on the

RESET# pin and uses standard microprocessor

bus cycle timing to implement sector protection.

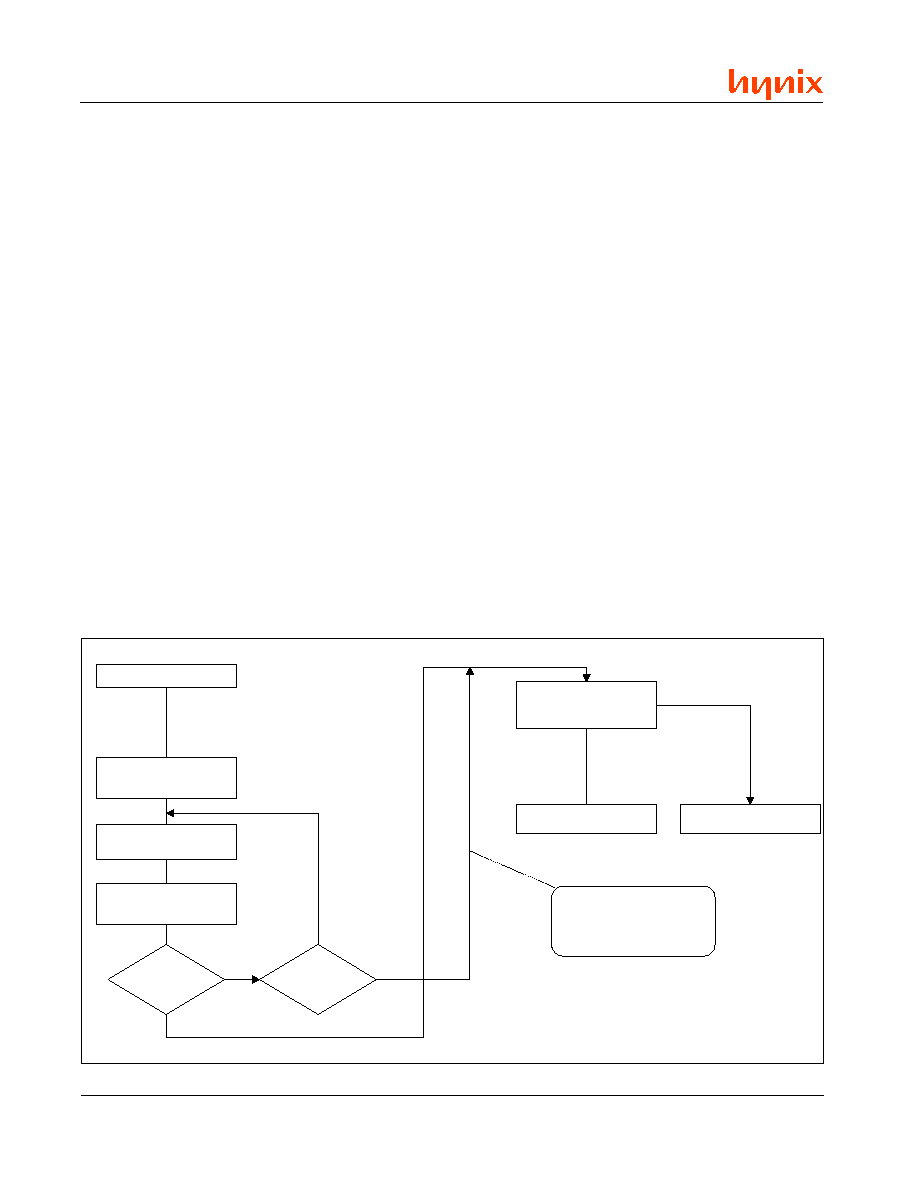

The flow chart in Figure 1 illustrates the algorithm.

The HY29LV160 is shipped with all sectors un-

protected. It is possible to determine whether a

sector is protected or unprotected. See the Elec-

tronic ID Mode section for details.

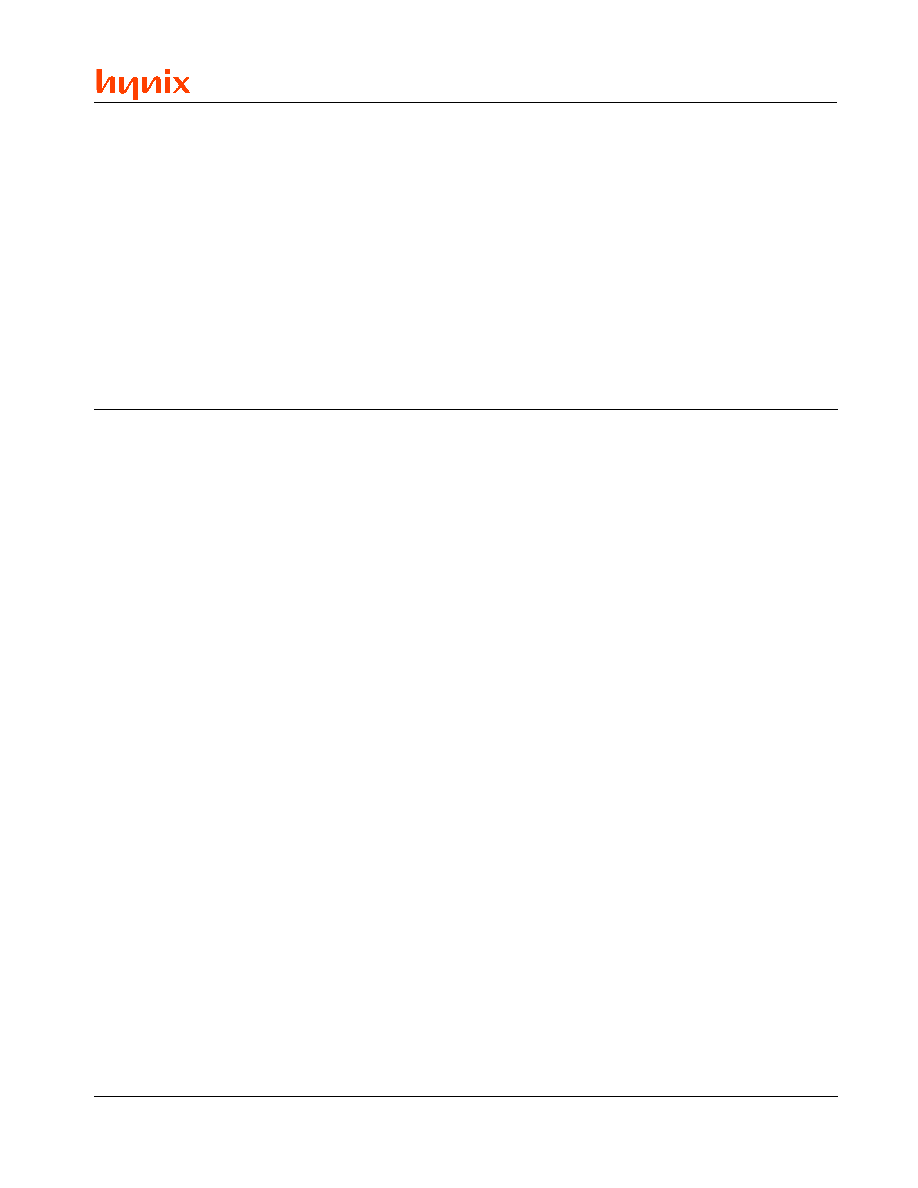

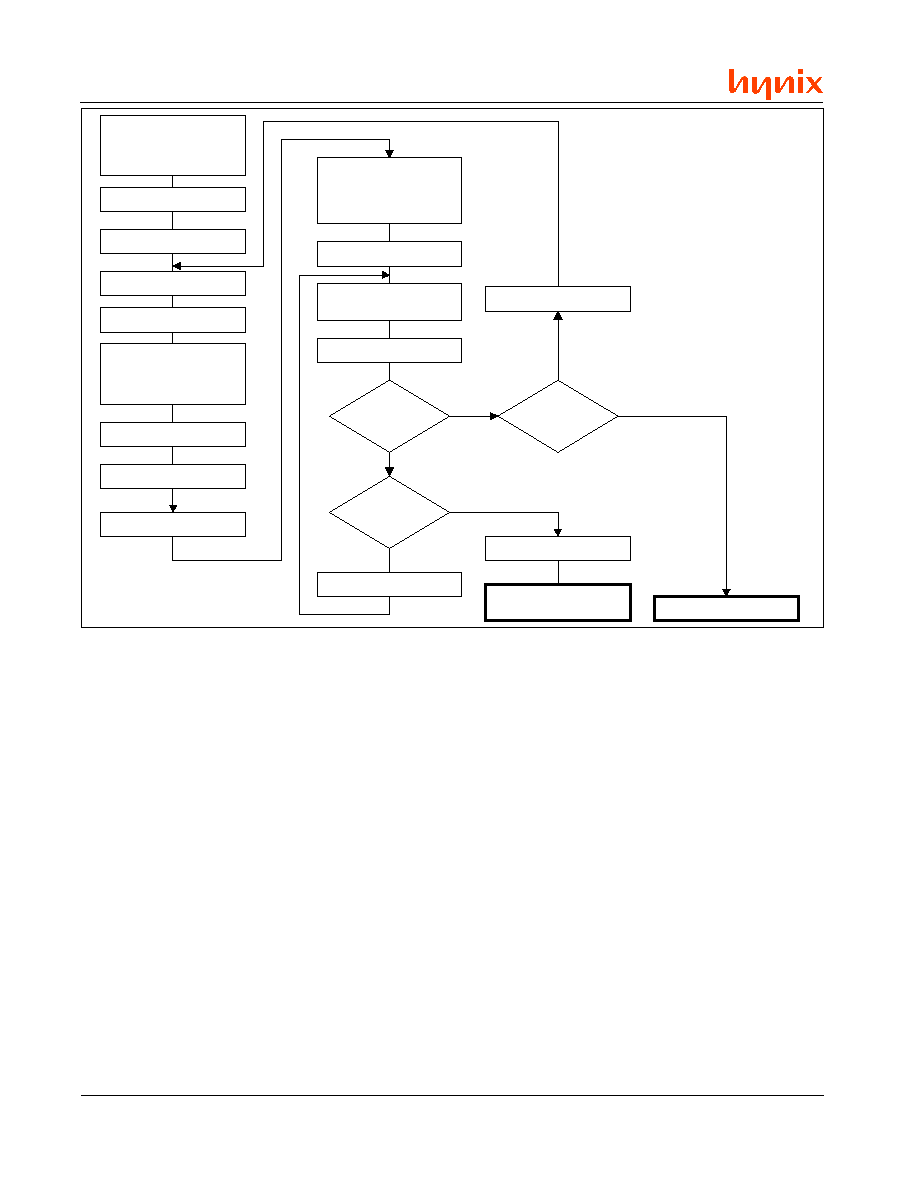

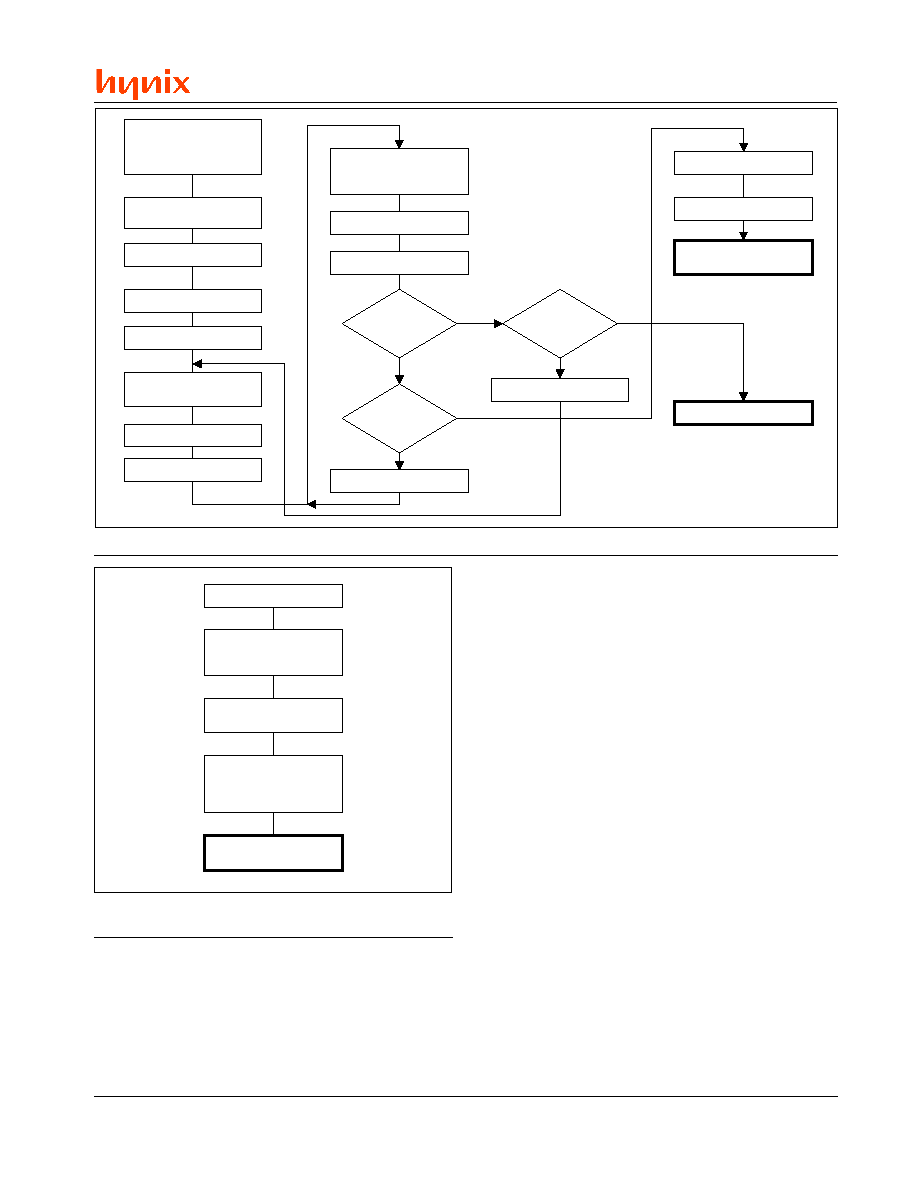

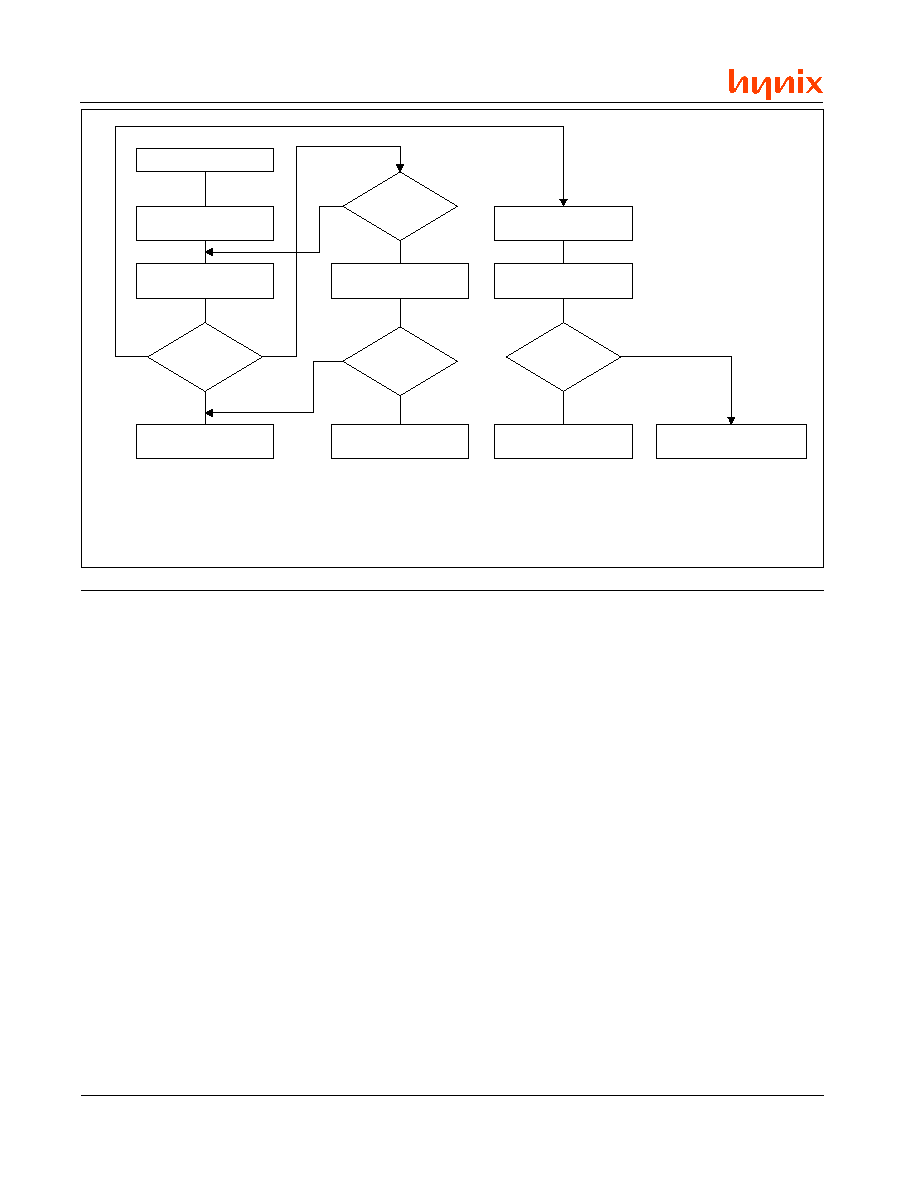

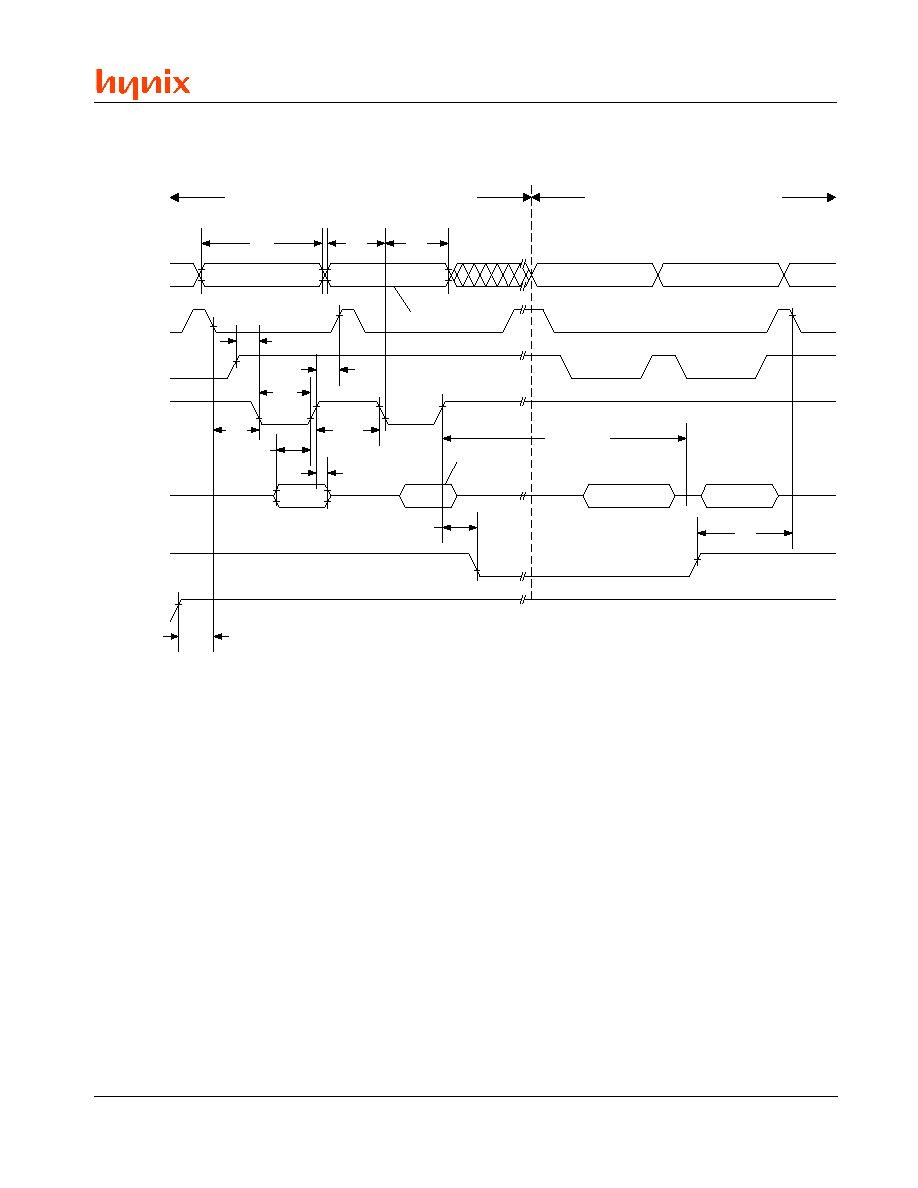

Sector Unprotect Operation

The hardware sector unprotection feature re-en-

ables both program and erase operations in pre-

viously protected sectors. This function can be

implemented either in-system or by using program-

ming equipment. Note that to unprotect any sec-

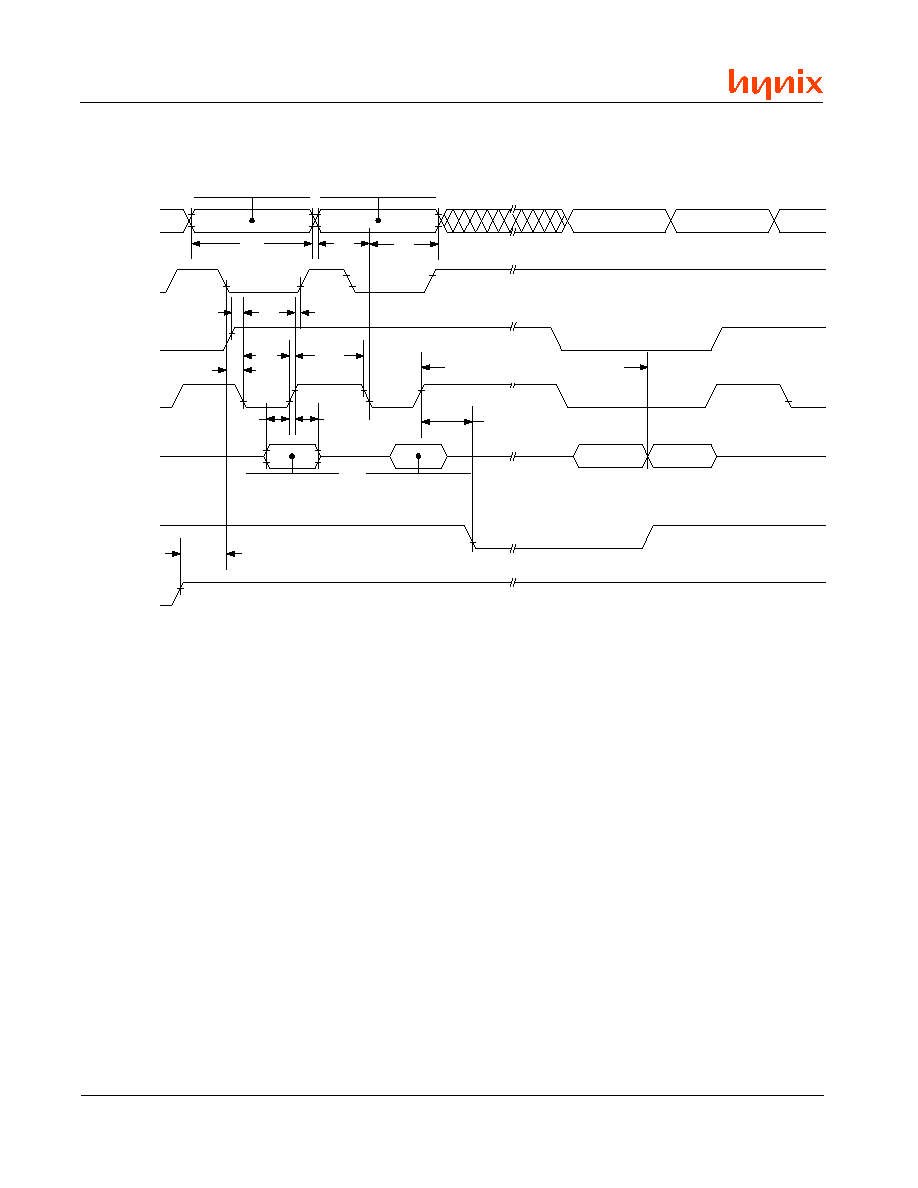

S T A R T

R E S E T # = V

ID

Wait 1 us

Write 0x60 to device

Write 0x60 to Address

Wait 150 us

Write 0x40 to Address

R e a d f r o m A d d r e s s

Data = 0x01?

Protect Another

Sector?

Y E S

T R Y C N T = 2 5 ?

N O

I n c r e m e n t T R Y C N T

N O

Y E S

DEVICE FAILURE

Y E S

N O

R E S E T # = V

IH

W r i t e R e s e t C o m m a n d

SECTOR PROTECT

C O M P L E T E

T R Y C N T = 1

Set Address:

A[19:12] = Sector to Protect

A[6] = 0, A[1] = 1, A[0] = 0

Figure 1. Sector Protect Algorithm

tor, all unprotected sectors must first be protected

prior to the first sector unprotect write cycle. Also,

the unprotect procedure will cause all sectors to

become unprotected, thus, sectors that require

protection must be protected again after the un-

protect procedure is run.

The method intended for programming equipment

requires a high voltage (V

ID

) on address pin A[9]

and the control pins. Refer to the Appendix for

additional information.

The in-system method requires V

ID

only on the

RESET# pin and uses standard microprocessor

bus cycle timing to implement sector unprotection.

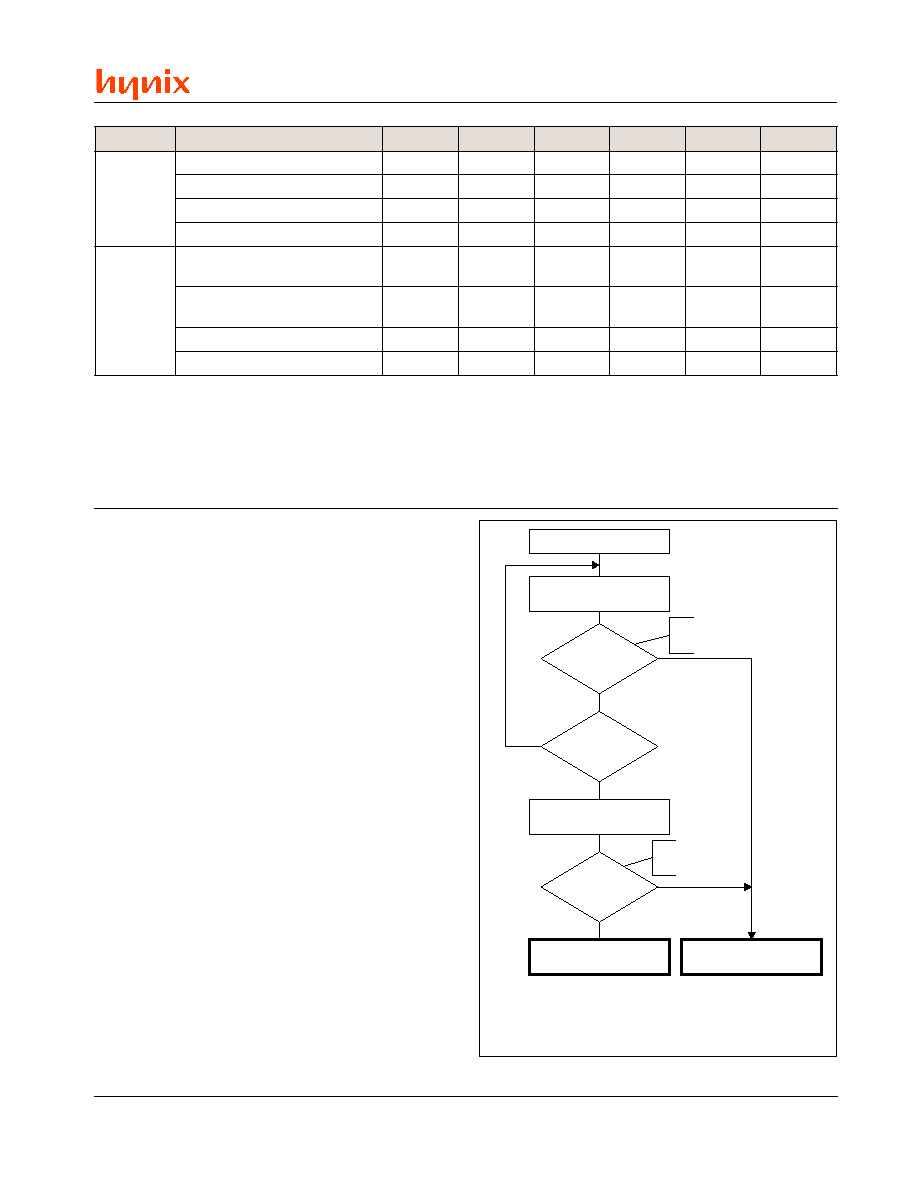

The flow chart in Figure 2 illustrates the algorithm.

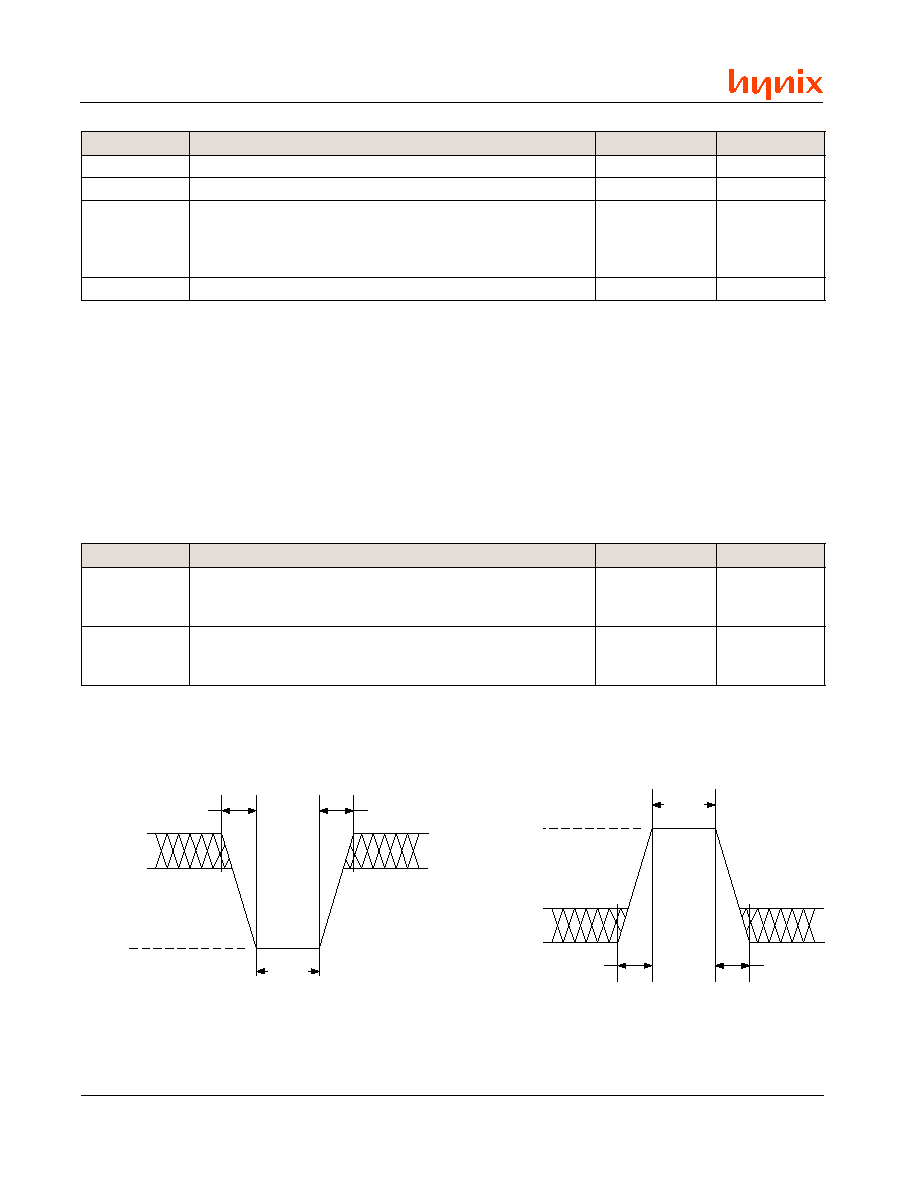

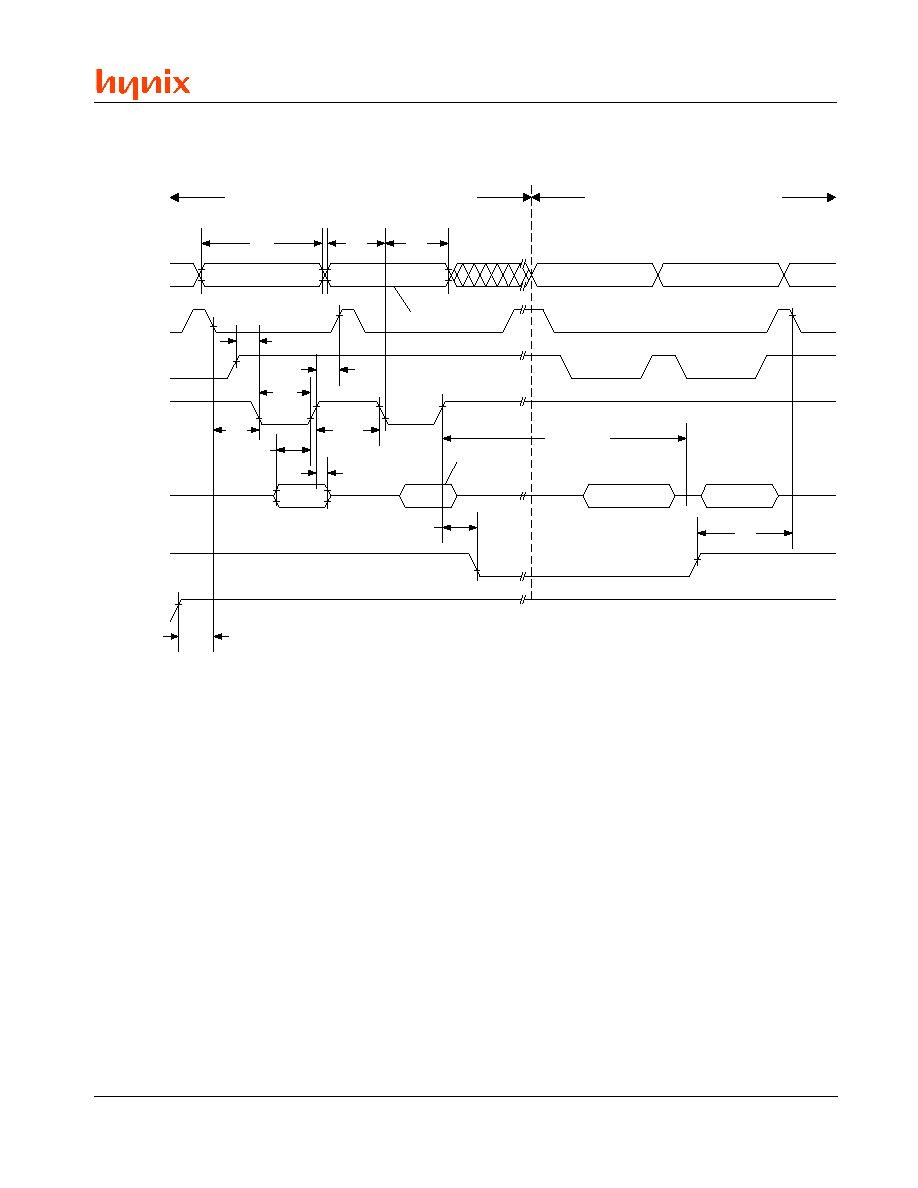

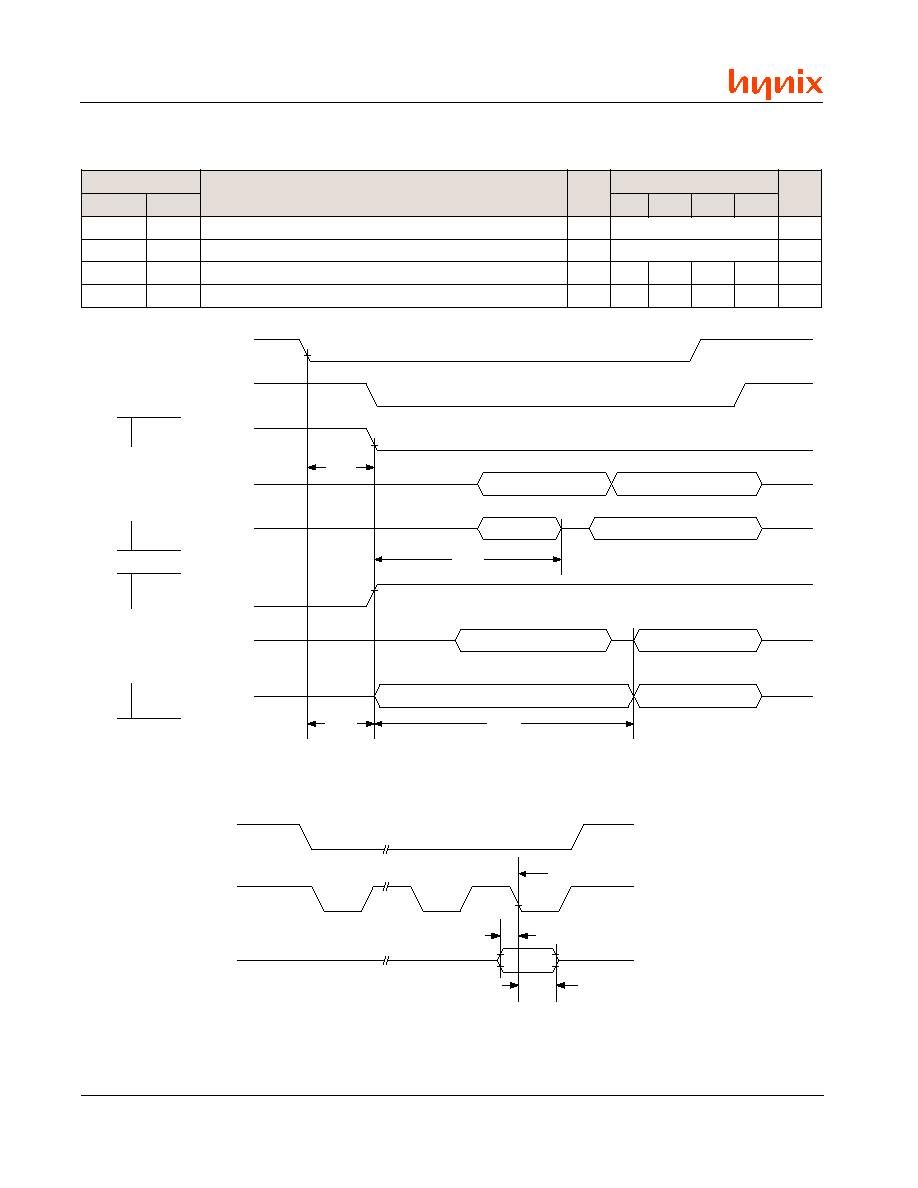

Temporary Sector Unprotect Operation

This feature allows temporary unprotection of pre-

viously protected sectors to allow changing the

data in-system. Sector Unprotect mode is activated

by setting the RESET# pin to V

ID

. While in this

mode, formerly protected sectors can be pro-

grammed or erased by invoking the appropriate

commands (see Device Commands section).

Once V

ID

is removed from RESET#, all the previ-

ously protected sectors are protected again. Fig-

ure 3 illustrates the algorithm.

11

Rev. 1.2/May 01

HY29LV160

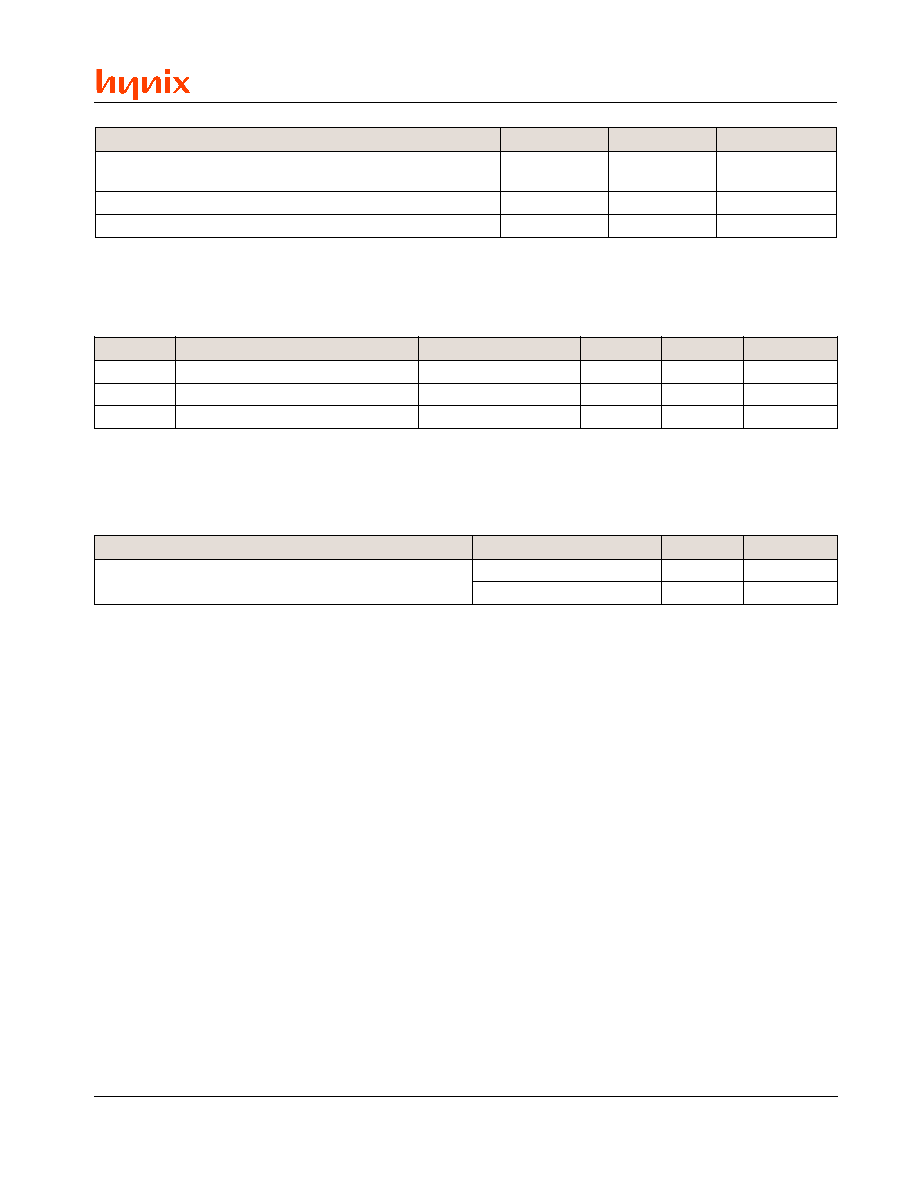

S T A R T

(Note: All sectors must be

protected prior to

unprotecting any sector)

T R Y C N T = 1

S N U M = 0

R E S E T # = V

ID

Wait 1 us

Write 0x60 to device

Write 0x60 to Address

Set Address:

A[19:12] = Sector SNUM

A[6] = 1, A]1] = 1, A]0] = 0

Write 0x40 to Address

R e a d f r o m A d d r e s s

Data = 0x00?

S N U M = 3 4 ?

Y E S

T R Y C N T = 1 0 0 0 ?

N O

I n c r e m e n t T R Y C N T

N O

Y E S

DEVICE FAILURE

Y E S

N O

R E S E T # = V

IH

W r i t e R e s e t C o m m a n d

SECTOR UNPROTECT

C O M P L E T E

S N U M = S N U M + 1

W a i t 1 5 m s

Set Address:

A[6] = 1, A]1] = 1, A]0] = 0

Figure 2. Sector Unprotect Algorithm

S T A R T

R E S E T # = V

ID

(All protected sectors

b e c o m e u n p r o t e c t e d )

Perform Program or Erase

Operations

R E S E T # = V

IH

(All previously protected

sectors return to protected

state)

T E M P O R A R Y S E C T O R

U N P R O T E C T C O M P L E T E

Figure 3. Temporary Sector Unprotect

Algorithm

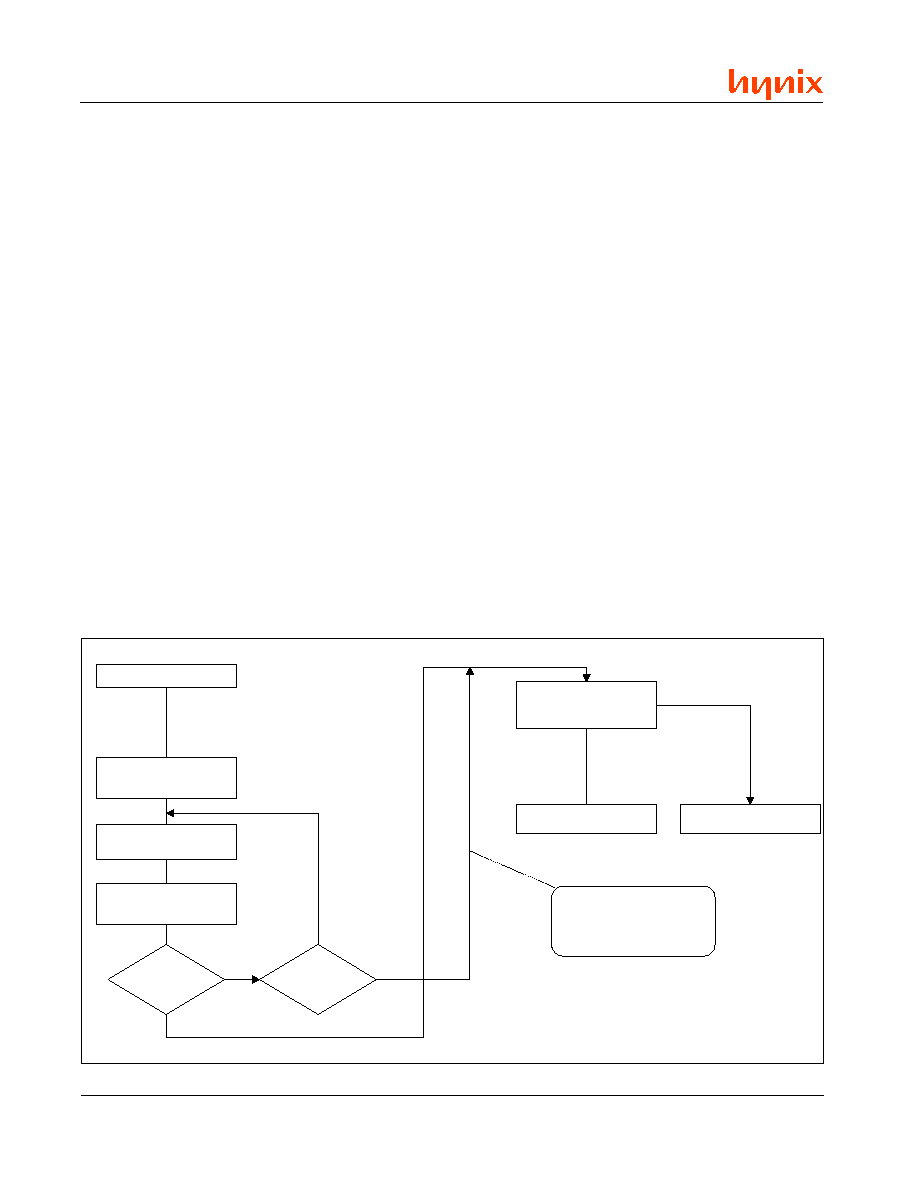

Electronic ID Operation (High Voltage Method)

The Electronic ID mode provides manufacturer and

device identification and sector protection verifi-

cation through codes output on DQ[15:0]. This

mode is intended primarily for programming equip-

ment to automatically match a device to be pro-

grammed with its corresponding programming al-

gorithm.

Two methods are provided for accessing the Elec-

tronic ID data. The first requires V

ID

on address

pin A[9], with additional requirements for obtain-

ing specific data items listed in Table 4. The Elec-

tronic ID data can also be obtained by the host

through specific commands issued via the com-

mand register, as described in the `Device Com-

mands' section of this data sheet.

While in the high-voltage Electronic ID mode, the

system may read at specific addresses to obtain

certain device identification and status informa-

tion:

A read cycle at address 0xXXX00 retrieves the

manufacturer code.

A read cycle at address 0xXXX01 in Word

mode or 0xXXX02 in Byte mode returns the

device code.

A read cycle containing a sector address (SA)

in A[19:12] and the address 0x02 in Word mode

or 0x04 in Byte mode, returns 0x01 if that sec-

tor is protected, or 0x00 if it is unprotected.

12

Rev. 1.2/May 01

HY29LV160

DEVICE COMMANDS