| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 405EP | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

3/19/03

Preliminary

PowerPC 405EP Embedded Processor Data Sheet

1

Features

∑ IBM PowerPC

405 32-bit RISC processor core

operating up to 266MHz with 16KB D- and I-

caches

∑ PC-133 synchronous DRAM (SDRAM) interface

- 32-bit interface for non-ECC applications

∑ 4 KB on-chip memory (OCM)

∑ External peripheral bus

- Flash ROM/Boot ROM interface

- Direct support for 8- or 16-bit SRAM and

external peripherals

- Up to five devices

∑ DMA support for memory and UARTs.

- Scatter-gather chaining supported

- Four channels

∑ PCI Revision 2.2 compliant interface (32-bit, up

to 66 MHz)

- Asynchronous PCI Bus interface

- Internal or external PCI Bus Arbiter

∑ Two Ethernet 10/100 Mbps (full-duplex) ports

with media independent interface (MII)

∑ Programmable interrupt controller supports

seven external and 19 internal edge triggered or

level-sensitive interrupts

∑ Programmable timers

∑ Software accessible event counters

∑ Two serial ports (16750 compatible UART)

∑ One IIC interface

∑ General purpose I/O (GPIO) available

∑ Supports JTAG for board level testing

∑ Internal processor local Bus (PLB) runs at

SDRAM interface frequency

∑ Supports PowerPC processor boot from PCI

memory

Description

Designed specifically to address embedded

applications, the PowerPC 405EP (PPC405EP)

provides a high-performance, low-power solution

that interfaces to a wide range of peripherals by

incorporating on-chip power management features

and lower power dissipation requirements.

This chip contains a high-performance RISC

processor core, SDRAM controller, PCI bus

interface, Ethernet interface, control for external

ROM and peripherals, DMA with scatter-gather

support, serial ports, IIC interface, and general

purpose I/O.

Technology: IBM CMOS SA-27E, 0.18

µ

m

(0.11

µ

m L

eff

)

Package: 31mm, 385-ball, enhanced plastic ball

grid array (E-PBGA)

Power (typical): 1.2W at 200MHz

While the information contained herein is believed to be accurate, such information is preliminary, and should not be

relied upon for accuracy or completeness, and no representations or warranties of accuracy or completeness are made.

Preliminary

PowerPC 405EP Embedded Processor Data Sheet

2

3/19/03

Contents

Ordering, PVR, and JTAG Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Address Map Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

On-Chip Memory (OCM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

PLB to PCI Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

SDRAM Memory Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

External Peripheral Bus Controller (EBC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

DMA Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

IIC Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

General Purpose IO (GPIO) Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Universal Interrupt Controller (UIC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

10/100 Mbps Ethernet MAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Signal List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Spread Spectrum Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Tables

System Memory Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

DCR Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Signals Listed Alphabetically . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Signals Listed by Ball Assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Pin Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Signal Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Package Thermal Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Recommended DC Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Input Capacitance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Clocking Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Peripheral Interface Clock Timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

I/O Specifications--Group 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

I/O Specifications--Group 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Strapping Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Preliminary

PowerPC 405EP Embedded Processor Data Sheet

3/19/03

3

Figures

PPC405EP Embedded Controller Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

31mm, 385-Ball E-PBGA Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

5V-Tolerant Input Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Input Setup and Hold Timing Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Output Delay and Float Timing Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Preliminary

PowerPC 405EP Embedded Processor Data Sheet

4

3/19/03

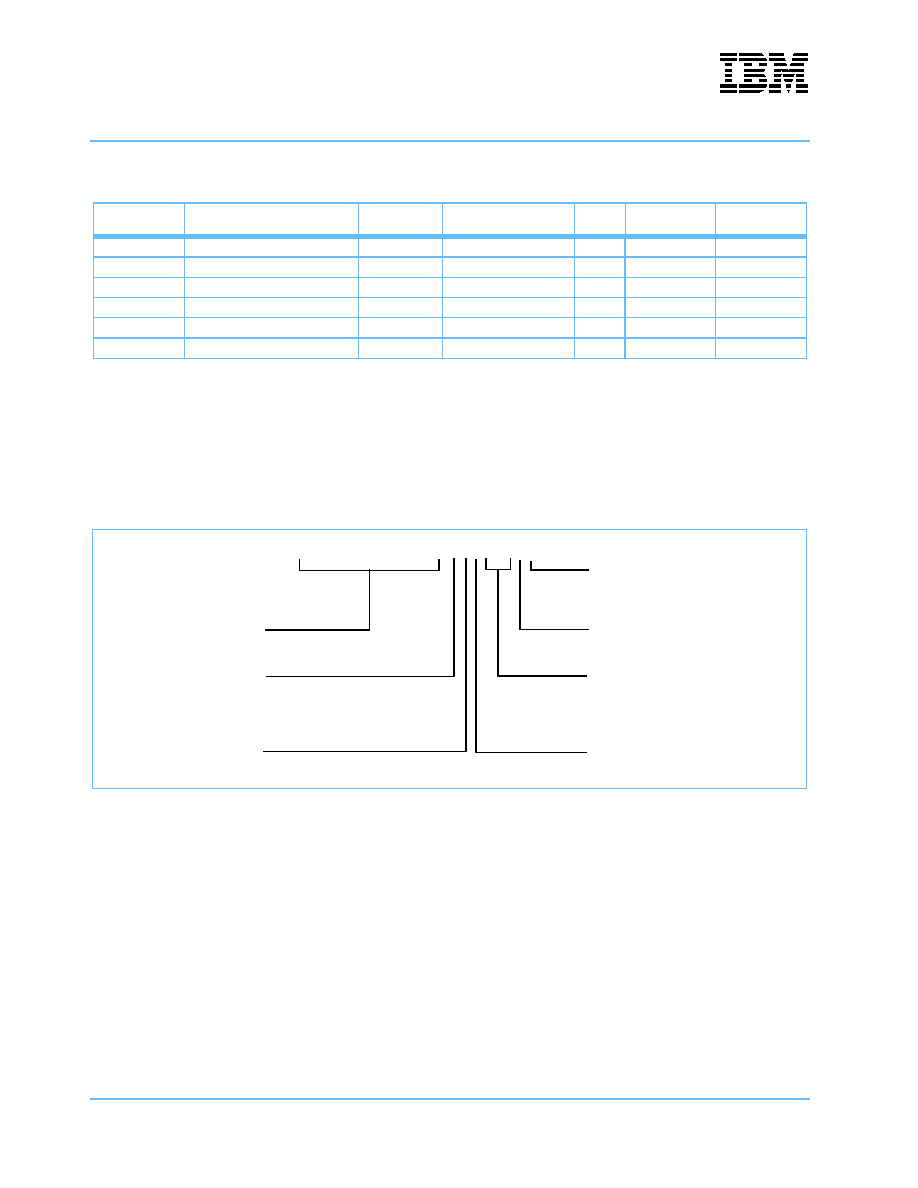

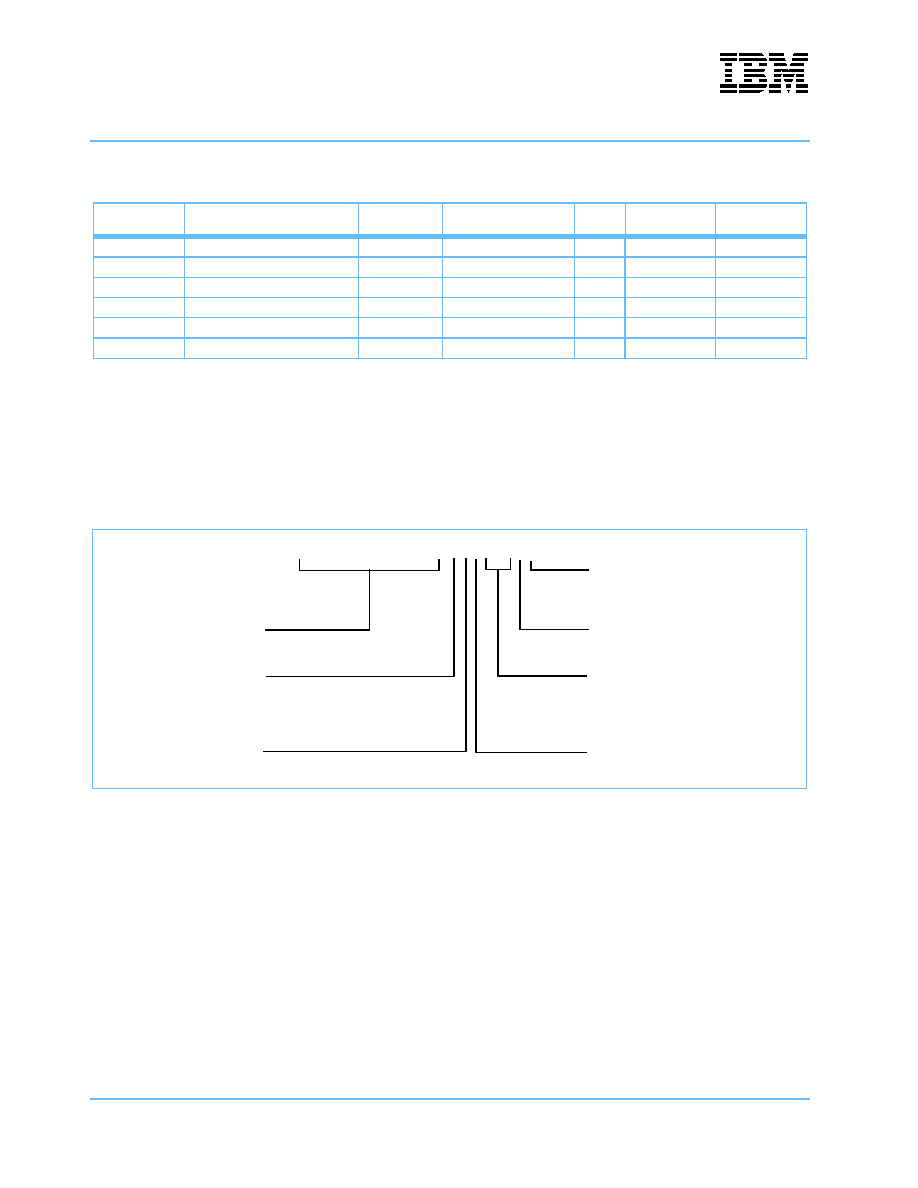

Ordering, PVR, and JTAG Information

This section provides the part number nomenclature. For availability, contact your local IBM sales office.

The part number contains a part modifier. Included in the modifier is a revision code. This refers to the die

mask revision number and is specified in the part numbering scheme for identification purposes only.

The PVR (Processor Version Register) and the JTAG ID register are software accessible (read-only) and

contain information that uniquely identifies the part. Refer to the

PowerPC 405EP Embedded Processor

User's Manual for details on accessing these registers.

Order Part Number Key

Product Name

Order Part Number

1

Processor

Frequency

Package

Rev

Level

PVR Value

JTAG ID

PPC405EP

IBM25PPC405EP-3GB133C

133 MHz

31mm, 385 E-PBGA

B

0x51210950

0x20267049

PPC405EP

IBM25PPC405EP-3GB133CZ

133 MHz

31mm, 385 E-PBGA

B

0x51210950

0x20267049

PPC405EP

IBM25PPC405EP-3GB200C

200 MHz

31mm, 385 E-PBGA

B

0x51210950

0x20267049

PPC405EP

IBM25PPC405EP-3GB200CZ

200 MHz

31mm, 385 E-PBGA

B

0x51210950

0x20267049

PPC405EP

IBM25PPC405EP-3GB266C

266 MHz

31mm, 385 E-PBGA

B

0x51210950

0x20267049

PPC405EP

IBM25PPC405EP-3GB266CZ

266 MHz

31mm, 385 E-PBGA

B

0x51210950

0x20267049

Note 1: Z at the end of the Order Part Number indicates a tape and reel shipping package. Otherwise, the chips are shipped in a tray.

IBM Part Number

IBM25PPC405EP-3GB266Cx

Package

Processor Speed

Grade 3 Reliability

Operational Case Temperature

Shipping Package

Blank = Tray

Z = Tape and reel

(-40 ∞C to +85 ∞C)

Range

266 = 266MHz

31mm, 385 E-PBGA

200 = 200MHz

Revision Level

133 = 133MHz

Preliminary

PowerPC 405EP Embedded Processor Data Sheet

3/19/03

5

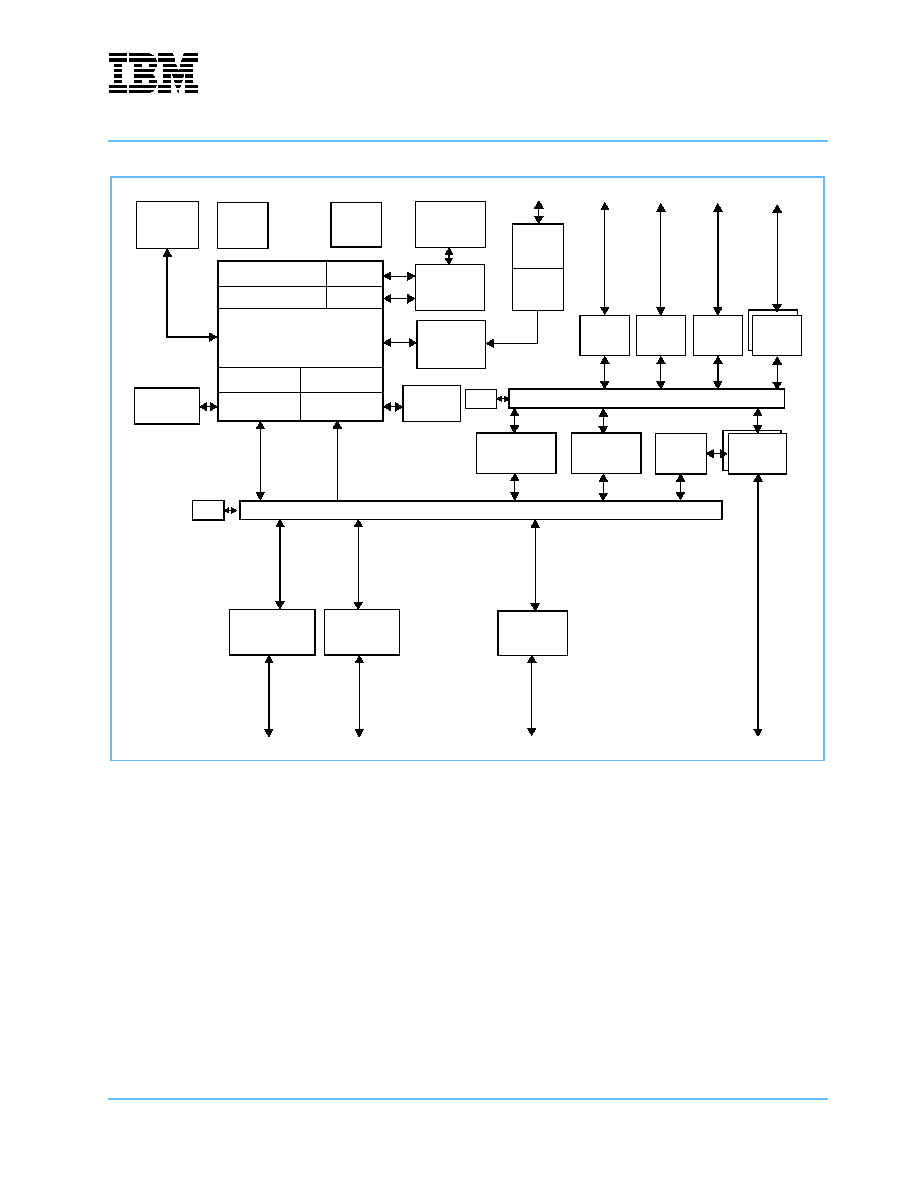

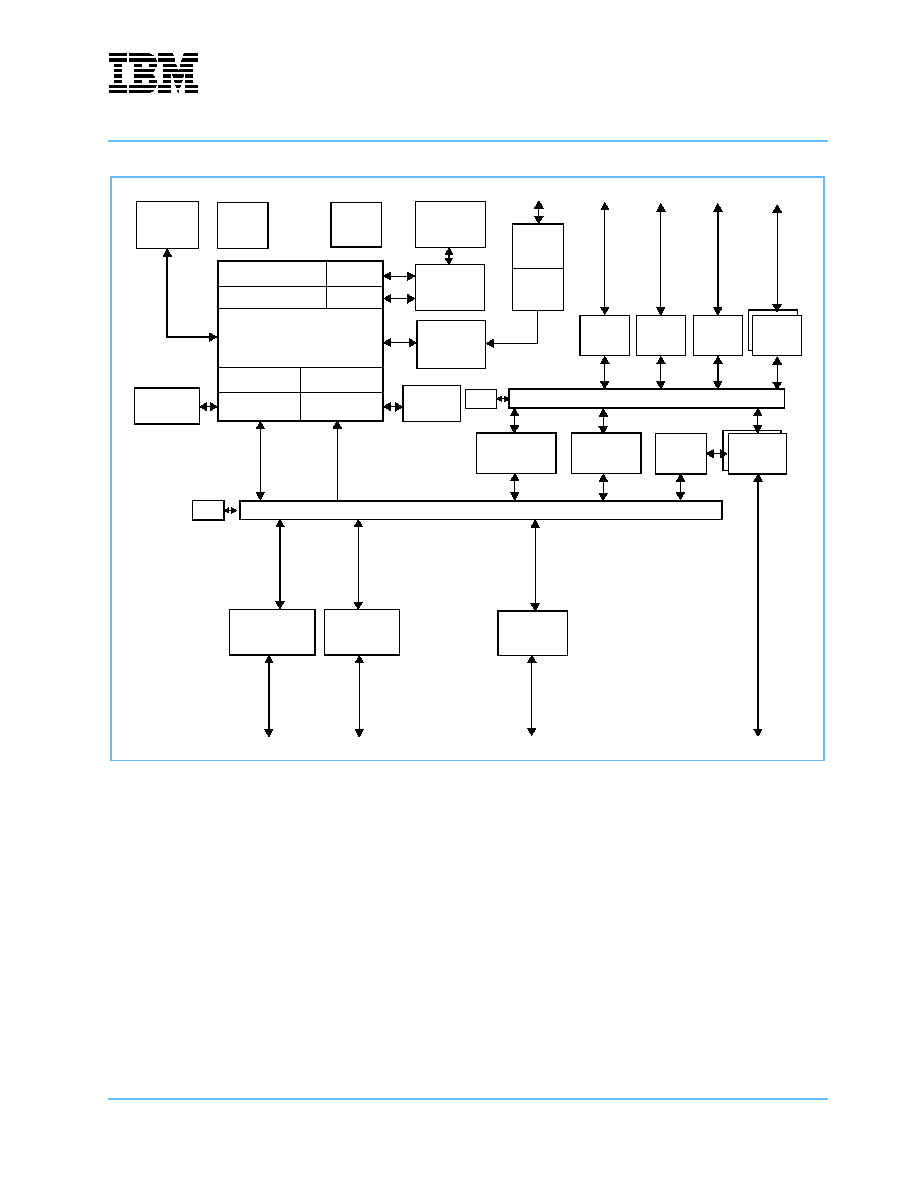

PPC405EP Embedded Controller Functional Block Diagram

The PPC405EP is designed using the IBM Microelectronics Blue Logic

TM

methodology in which major

functional blocks are integrated together to create an application-specific ASIC product. This approach

provides a consistent way to create complex ASICs using IBM CoreConnect

TM

Bus Architecture.

PPC405

Processor Core

DOCM

IOCM

DCU

ICU

OCM

Control

OCM

SRAM

DCR Bus

16KB

On-chip Peripheral Bus (OPB)

GPIO

IIC

GPT

UART

MAL

Ethernet

DMA

Bridge

Processor Local Bus (PLB)

SDRAM

PCI Bridge

External

Bus

Controller

Controller

Clock

Control

Reset

Power

Mgmt

JTAG

Trace

Timers

MMU

MII

Controller

OPB

Interrupt

Controller

Arb

29-bit addr

16-bit data

13-bit addr

32-bit data

Universal

I-Cache

D-Cache

(4-Channel)

66 MHz max (async)

DCRs

16KB

Arb

x2

x2

Event

Counters