| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 440GX | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

A feature-rich processor optimized for high-speed

networking and storage applications

PowerPC 440GX Embedded Processor

Delivers 500 to 667MHz

performance ≠ with low power in

a small form factor

Provides 256KB on-chip SRAM,

configurable as an L2 cache or as

packet/code-store memory for

low-latency access

Integrates state-of-the-art

peripherals, such as PCI-X and

DDR SDRAM

Offers four Ethernet interfaces,

including two 10/100/1Gb MACs

with jumbo frame support, for

increased bandwidth and

connectivity

Embeds TCP/IP Acceleration

Hardware (TAH), freeing CPU

core cycles for other application

demands

Includes a messaging unit that

facilitates communications over

the PCI, for increased application

performance

Ensures PowerPC

Æ

application

code compatibility, as well as

offering enhanced data integrity

through processor parity

Highlights

Advanced processing capability for

high-performance embedded systems

The IBM PowerPC 440GX processor

offers the versatility and bandwidth

required for today's demanding

networking and storage applications.

This highly integrated device delivers

CPU performance of up to 667MHz

and executes up to two instructions per

cycle. A PCI-X interface that supports

frequencies of up to 133MHz and

an on-chip double data rate (DDR)

SDRAM controller, supporting up to

DDR333, further enhance processor

capabilities. With embedded state-of-

the-art peripheral cores, the 440GX

processor is ideal for networking control

plane applications, RAID controllers,

iSCSI processing, and storage area

networking (SAN) equipment.

I/O processing applications can benefit

from the integrated messaging unit,

designed to the I2O specification.

This messaging unit improves system

performance by enabling the 440GX

processor to communicate via I2O

messages with a host system on the PCI

bus. This allows the processor to work

as an intelligent I/O adapter controller.

The 256KB on-chip SRAM can be

configured either as a performance-

enhancing L2 cache, or as memory-

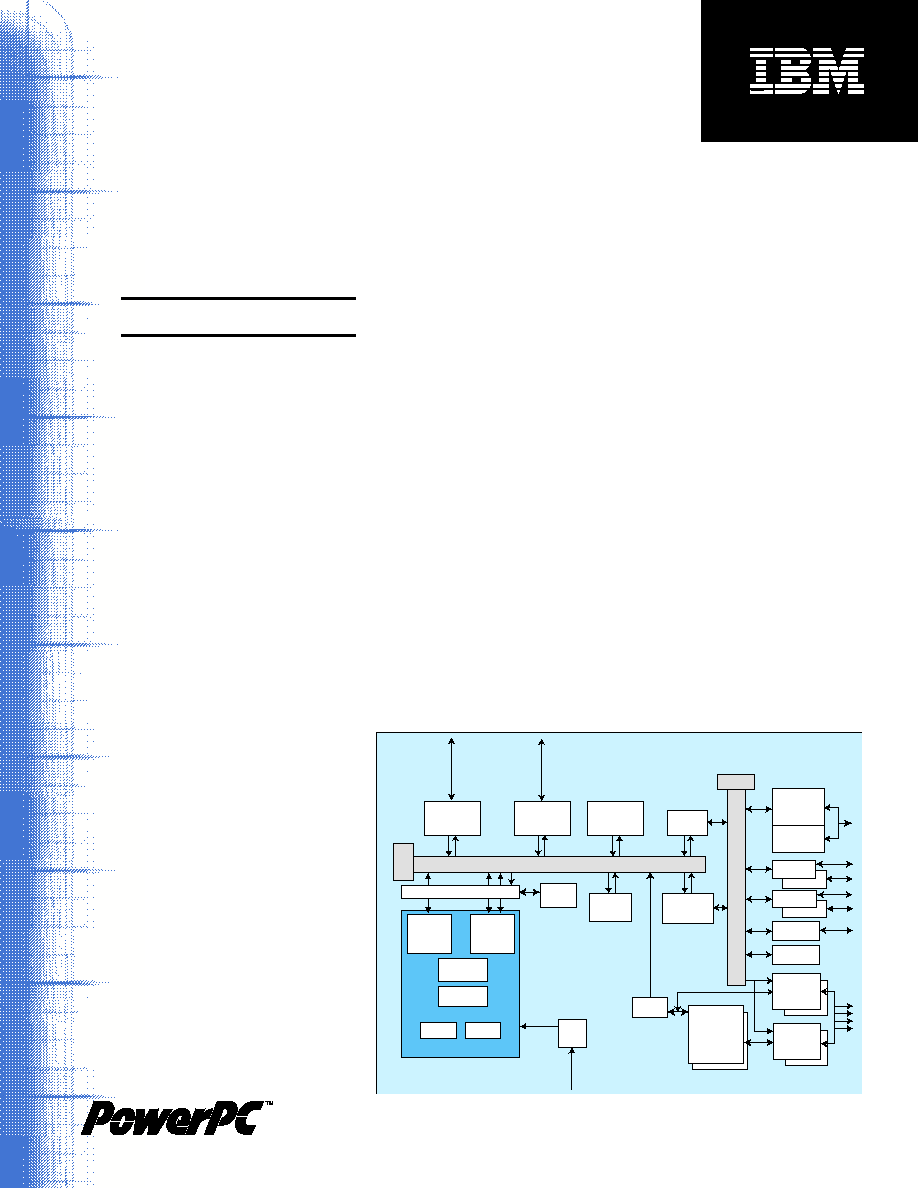

PowerPC 440GX Embedded Processor block diagram

PCI-X

Bridge

DDR

SDRAM

Controller

I2

O

Messaging

Unit

32KB

I-Cache

w/parity

10/100

Ethernet

MAC

10/100/1G

Ethernet

MAC

TCP/IP

Accel.,

Jumbo

Frame

32KB

D-Cache

w/parity

RAM/ROM/

Peripheral

controller

On-chip Peripher

al Bus (O

PB)

Up to 83 MHz

Arbiter

OPB

Bridge

DMA

Controller

PLB Perf

Monitor

MAL

MMU

w/parity

Timers

JTAG

Trace

UIC

440 CPU Core

External bus

master cntlr.

UART

IIC

GPIO

GPT

L2/SRAM Control

256KB

SRAM

Up to 166MHz

Processor Local Bus (PLB)

128-bit

Arbiter

Gigabit Ethernet and TCP/IP assist

extend application capability

The 440GX integrates four Ethernet

media access controllers (MACs),

including two 10/100Mb interfaces and

two 10/100/1Gb interfaces with support

for jumbo packets and TCP/IP assist.

These MACs offer both flexibility and

high performance. For example, they

can be configured to provide four SMII

interfaces for maximum connectivity; or

dual gigabit interfaces for high-speed

communications, plus one or two Fast

Ethernet interfaces for other application

requirements.

Many networking and storage

applications will benefit from the

PowerPC 440GX software-enabled

TCP/IP hardware-assist state

machine that accelerates data packet

processing. This TCP/IP engine relieves

the CPU of the checksum and transmit

segmentation workload, making it

available to handle other application

demands.

Code compatibility facilitates

application migration

The PowerPC 440GX processor is a

32-bit implementation of the Book E

Enhanced PowerPC ArchitectureTM

that ensures code compatibility across

all PowerPC processors. The 440GX

design implements the CoreConnectTM

bus architecture with a 166MHz

Processor Local Bus (PLB) that includes

a 128-bit data bus and a separate 36-

bit address bus. The processor also

has an 83MHz On-chip Peripheral

Bus (OPB) that supports the 36-bit

address bus, as well as a 32-bit data

bus that can dynamically resize to 16

or 8 bits, depending on the transaction.

Conformance to these architectures

facilitates and helps to reduce the

cost of application development and

migration.

PowerPC tools support fast

time-to-market

PowerPC embedded processors are

supported by IBM and more than

100 third-party vendors through the

PowerPC Embedded Tools Program.

This program provides compilers,

debuggers, real-time operating systems,

emulators, logic analyzers, and a full

range of tools to help manufacturers

develop products quickly and efficiently.

mapped SRAM for low-latency

access. Used as L2, the 256KB

SRAM is a 4-way set-associative,

unified data/instruction cache, which

can benefit many applications. As

memory-mapped SRAM, it has

lower memory access latency than

the SDRAM, offering quick access

to crucial code or data. Software-

controlled and with parity support,

this memory is ideal for storing data

packets, critical code segments,

Ethernet or DMA descriptors, or

other application-specific data. When

configured as a memory-mapped

region, this SRAM is accessible from

any PLB master, which can further

improve application performance.

PowerPC 440GX Specifications

Technology 0.13µm CMOS CU-11 Copper

Performance (est.) 500 to 667MHz

1334 DMIPs @ 667MHz

Frequency

CPU 500 to 667MHz

Memory, 32-bit width 800MBps (DDR200) to 1.3GBps (DDR333)

Memory, 64-bit width 1.6GBps (DDR200) to 2.6GBps (DDR333)

PCI 33 to 66MHz

PCI-X 50 to 133MHz

Typical Power Dissipation (est.) 4.5W

Case Temperature Range -40 to 85∞ C

Power Supply

Core logic 1.5V

I/O 2.5V or 3.3V, depending on interface

I/O Signals 406

Packaging 552-ball, 25mm x 25mm CBGA

(with 1.0mm pad pitch)

A PowerPC 440GX reference board kit

is available to help expedite product

evaluation and project development.

PowerPC 440GX features

The PowerPC 440GX processor

provides the ability to develop high-

performance, high-functionality

networking and storage applications:

∑

PowerPC 440 Core

- 500 to 667MHz, 2.0 DMIPS/MHz

- 32K/32K I-cache/D-cache with

parity (tags and arrays)

- Dual-issue, superscalar, 7-stage

pipeline

- Book E architecture, 32-bit

implementation

- Memory management unit with

parity

∑

CoreConnect

- Up to 166MHz CoreConnect

Processor Local Bus (128-bit

PLB) with separate read and write

databases

- Up to 83MHz CoreConnect On-

chip Peripheral Bus (32-bit OPB)

- 36-bit address, 64GB memory

map

∑

32/64-bit DDR200-DDR333

SDRAM Controller

- Up to four 512MB logical banks, for

a total of 2GB

- Optional 8-bit ECC protection

- Sustainable 2.6GBps peak

bandwidth at DDR333

∑

32/64-bit PCI-X Interface, up to

133MHz

- 800 MBps sustained bandwidth,

1.1GBps peak bandwidth

- Support for PCI v2.3, up to 66MHz

- Ability to boot from PCI-X bus

memory

∑

Messaging Unit (I2O specification)

that facilitates communication

between 440 core and PCI-X

∑

256KB on-chip SRAM

- Configurable as either L2 cache

or packet/code store memory

- L2 cache: Unified, 4-way set-

associative

- Packet/code store: PLB-attached,

accessible by 440 core and

peripheral cores

- Parity support on SRAM

∑

External Bus Control (EBC)

Interface

- Up to 83MHz, 32-bit address bus,

32-bit data bus

- Support for up to 8 ROM, RAM, or

slave peripheral I/O devices

- 4-channel DMA support for

external peripherals

- External bus master controller for

access to internal peripherals

∑

DMA Controller

- Four independent channels,

supporting internal and external

peripherals

- Support for memory-to-memory,

peripheral-to-memory, and

memory-to-peripheral transfers

- Scatter/gather capability

- 128-byte buffer with

programmable thresholds

∑

Up to Four Ethernet Ports, including

Two Gigabit Ports

- Two 10/100/1Gb Ethernet ports with

jumbo frame support and TCP/IP

assist, configurable as either

2 SMII, 2 RGMII/RTBI, or 1 GMII/TBI

interface

- 2 10/100 Ethernet Ports, con-

figurable as one MII or two RMII/

SMII

∑

TCP/IP acceleration hardware (TAH)

- Available on the two 10/100/1Gb

Ethernet ports

- Checksum processing of packet

- Transmit packet segmentation

∑

On-chip Peripherals

- Two serial ports, one 9-pin and one

5-pin

- Two IIC controllers, designed to

Phillips IIC specification

- Up to 32 GPIO

- Up to 18 external interrupts

- General purpose timers

∑

L1 Cache Array and Tag Parity

- Option to enable semi-recoverable

or fully recoverable modes

∑

Universal Programmable Interrupt

Controller

∑

Debug Support

- JTAG

- RISCTraceTM

- RISCWatchTM support

For more information, visit our Web site at

ibm.com/powerpc.

G224-7128-00

© Copyright IBM Corporation 2002

All Rights Reserved

Printed in the United States of America 8-02

The following are trademarks of International

Business Machines Corporation in the United

States, or other countries, or both:

IBM

IBM Logo

CoreConnect

PowerPC PowerPC Architecture PowerPC

Logo

RISCTrace

RISCWatch

Other company, product and service names

may be trademarks or service marks of others.

All information contained in this document is

subject to change without notice. The products

described in this document are NOT intended

for use in implantation or other life support appli-

cations where malfunction may result in injury or

death to persons. The information contained in

this document does not affect or change IBM

product specifications or warranties. Nothing in

this document shall operate as an express or

implied license or indemnity under the intel-

lectual property rights of IBM or third parties.

All information contained in this document was

obtained in specific environments, and is pre-

sented as an illustration. The results obtained in

other operating environments may vary.

THE INFORMATION CONTAINED IN THIS

DOCUMENT IS PROVIDED ON AN "AS IS"

BASIS. In no event will IBM be liable for dam-

ages arising directly or indirectly from any use of

the information contained in this document.

IBM Microelectronics Division

2070 Route 52, Bldg. 330

Hopewell Junction, NY 12533-6351

The IBM home page can be found at

ibm.com.

The IBM Microelectronics Division home page

can be found at

ibm.com/chips.

To receive the latest updates to

PowerPC technical information from IBM

Microelectronics, subscribe to tech