| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: iC-NF | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

iC-NF

ENCODER PROCESSOR

FEATURES

APPLICATIONS

Digital inputs with noise suppression for the incremental

shaft encoder signals A, B and index Z (up to 500kHz)

Revolution capture with two presetable 16-bit counters

Evaluation of the rotational direction

Separate supervisor counters for tracks A and B

Position sensing with fourfold edge evaluation and variable

counter depth from 10 to 16 bits

Double target position registers and comparators for setting

target markers during the drive operation

Versatile interrupt generation from 8 sources with outputs via

status registers

Two selectable ports for interrupt messages

System test possible without input signals

µ

P interface with an 8-bit/16-bit data bus

16-bit internal data bus

HCT-compatible CMOS inputs

TTL/CMOS-compatible outputs with tristate function

Protective circuitry against damage by ESD

Evaluation of incremental shaft

encoder signals for servo con-

trollers

PACKAGES

PLCC44

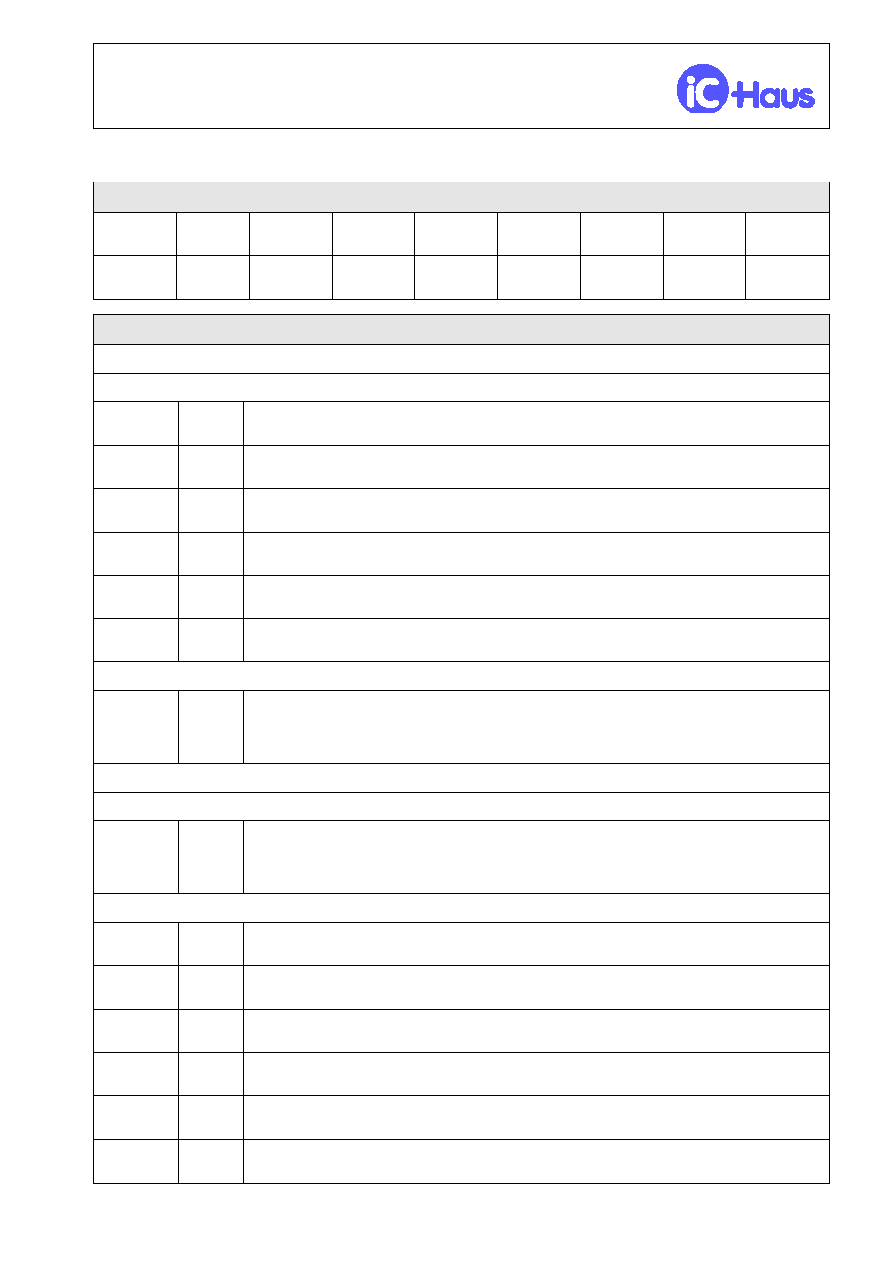

BLOCK DIAGRAM

©1997

Rev A0

POS2

16-bit

>15 T

>15 T

RES(1:0)

00

01

10

11

10/12/14/16

reset

up/down

DIR1 DIR2

16-bit

Timer 1

Timer 2

CLK25

TG

:1..255

:1..2

:2

PREDIV

DIV2

SEL(1:0)

11

01

00

ZF

ROT

AFIL

AB2

SYNB

SYNA

PDO

Q

D

D

Q

EXCH

DIR1

:2

:4

:8

>3 T

CLK5

CLK25

CLK125

T

POS1

Monitor

Rotary

Track Filter

Clock Divider

Index Filter

Track B

Tachobyte

Interrupt

Bus

Signal Processing

Supervisor Counter

Tachobyte

10

Control Word 1

Control Word 2

Revolution Capture

Predivisor

Down Counter

Track A

Down Counter

-bit Counter

Position Sensing

Detection

cw / ccw

Edge &

A

42

A0

41

A4

37

B

43

CLK

2

D0

13

30

GND1

1

GND2

4

GND3

11

GND4

23

GND5

31

INT1

10

INT2

8

NCS

33

NRD

36

NRES

32

Interrupt Word

NTEST

3

NWR

35

OUTA

6

OUTB

7

VCC1

5

VCC2

9

VCC3

12

VCC4

21

VCC5

34

Z

44

D15

iC-NF

µ

P

Interface

Interrupt Controller

iC-Haus GmbH

Tel

+49-6135-9292-0

Integrated Circuits

Fax +49-6135-9292-192

Am Kuemmerling 18, D-55294 Bodenheim

http://www.ichaus.com

iC-NF

ENCODER PROCESSOR

Rev A0, Page 2/13

DESCRIPTION

The iC-NF device evaluates the signals from an incremental shaft encoder with the A and B data tracks

and an index i.e. zero impulse track Z. The

µ

P interface works externally with an 8- or 16-bit data bus; the

widths of the internal bus and registers are 16 bit.

For programming, only the L-byte (lower byte DO..7) is relevant in the 8-bit mode; the 16-bit registers are

loaded sequentially. In this mode, the H-byte ports (higher byte D8..15) must be pulled up by external

resistors.

The device is controlled by two control words which can be written and read. In the status register, the

interrupt word locates the cause of the interrupt from the 8 possible sources. An enabled interrupt message

is assigned to the output pins INT1 or INT2.

Information on the current condition of the unsynchronised encoder signals and on the rotational direction

can be read out from the tachobyte register.

The signal processing produces clock-synchronised signals from the encoder tracks A and B and recog-

nises the rotational direction. A multiplexer at the input allows the A and B signals to be exchanged. The

track filter following can be set for clockwise or counter clockwise rotation and consequently it only passes

on correct bit patterns. Two filter outputs with cycle durations which are the same as and the half of track

A, as well as the unfiltered encoder signals, can be accessed for the revolution capture. A filter also

suppresses short disturbances of the zero impulse.

Two 16-bit counters are available as a timer for the revolution capture. One counter is permanently active

whereas the other one can be preset or read. Filtered or unfiltered input signals can be selected with a

multiplexer. The gate time for the clock inputs of the counters can be varied with the programmable

predivisor. After an interrupt message via the predivisor output (PDO) the inactive counter can be read out

and set again. The counter result is proportional to the revolution. Overflows are also passed on to the

interrupt controller.

The position sensing uses variable counter depths from 10 to 16 bits and counts up when running clock-

wise and down when running counter clockwise; a zero impulse resets the counter. Each edge of the

synchronised encoder signal counts (fourfold edge evaluation). Deviation from the preset direction and a

reaching of the set target marker are signalled to the interrupt controller. There are two target position

registers and two comparators, enabling target markers to be set during drive operation.

Additional supervisor counters for both encoder tracks record the unfiltered A and B signals.

A logic low at the reset input NRES resets all counters and registers and switches all outputs bar the

OUTB to tristate. In order to check the input thresholds NRES= LOW is maintained; all inputs are thus OR

gated to the OUTB output.

With pin NTEST not connected, the test mode is deactivated by an internal pull-up source (NTEST=

HIGH). For NTEST= LOW, the variable 10- to 16-bit counter of the position sensing is divided into four 4-

bit counters to reduce the counter depth.

All data inputs are compatible with TTL and CMOS levels. The

µ

P interface is bidirectional with Schmitt

trigger inputs. The outputs are CMOS compatible (HCT) and drive 4mA d.c. push-pull with a low saturation

voltage.

All inputs and outputs are protected against damage by ESD.

iC-NF

ENCODER PROCESSOR

Rev A0, Page 3/13

PACKAGES PLCC44 to JEDEC Standard

PIN CONFIGURATION PLCC44 (top view)

PIN FUNCTIONS PLCC44

No

Name

Function

No

Name

Function

1

GND1

Ground

23

GND4

Ground

2

CLK

Clock

24

D9

Data Bus Bit 9

3

NTEST

Test Mode, active low

25

D10

Data Bus Bit 10

4

GND2

Ground

26

D11

Data Bus Bit 11

5

VCC1

5V Supply Voltage

27

D12

Data Bus Bit 12

6

OUTA

Output Track A

28

D13

Data Bus Bit 13

7

OUTB

Output Track B

29

D14

Data Bus Bit 14

8

INT2

Interrupt 2, active high

30

D15

Data Bus Bit 15

9

VCC2

5V Supply Voltage

31

GND5

Ground

10

INT1

Interrupt 1, active high

32

NRES

Reset, active low

11

GND3

Ground

33

NCS

Chip Select, active low

12

VCC3

5V Supply Voltage

34

VCC5

5V Supply Voltage

13

D0

Data Bus Bit 0

35

NWR

Write Signal, active low

14

D1

Data Bus Bit 1

36

NRD

Read Signal, active low

15

D2

Data Bus Bit 2

37

A4

Address Bus Bit 4

16

D3

Data Bus Bit 3

38

A3

Address Bus Bit 3

17

D4

Data Bus Bit 4

39

A2

Address Bus Bit 2

18

D5

Data Bus Bit 5

40

A1

Address Bus Bit 1

19

D6

Data Bus Bit 6

41

A0

Address Bus Bit 0

20

D7

Data Bus Bit 7

42

A

Input Track A

21

VCC4

5V Supply Voltage

43

B

Input Track B

22

D8

Data Bus Bit 8

44

Z

Input Index Track Z

iC-NF

ENCODER PROCESSOR

Rev A0, Page 4/13

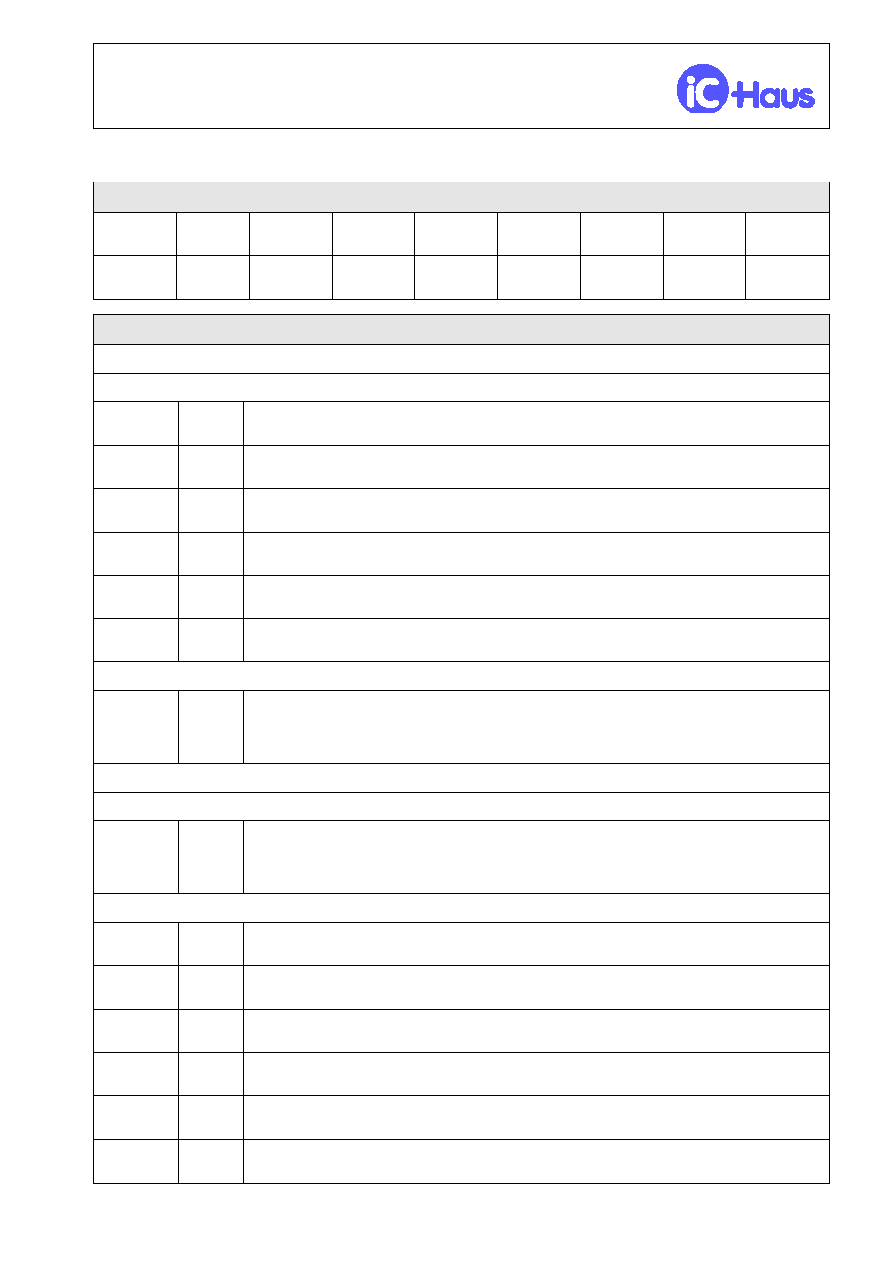

PROGRAMMING

Functional Select

Functional Block

Address

Mode= 0

(16-bit environment)

Mode= 1

(8-bit environment)

A4

A3

A2

A1

A0 Write

Read

Write

Read

Timer 1

0

0

0

0

0

0

0

0

0

1

Word

*

Word

*

L-byte

H-byte

L-byte

H-byte

Timer 2

0

0

0

0

0

0

1

1

0

1

Word

*

Word

*

L-byte

H-byte

L-byte

H-byte

Supervisor Counter Track A

0

0

1

1

0

0

0

0

0

1

Word

*

Word

*

L-byte

H-byte

L-byte

H-byte

Supervisor Counter Track B

0

0

1

1

0

0

1

1

0

1

Word

*

Word

*

L-byte

H-byte

L-byte

H-byte

Predivisor Revolution Capture

(PREDIV)

0

1

1

0

X

Byte

-

Byte

-

Target Position 1

1

1

0

0

0

0

0

0

0

1

Word

*

-

-

L-byte

H-byte

-

-

Target Position 2

1

1

0

0

0

0

1

1

0

1

Word

*

-

-

L-byte

H-byte

-

-

Position Counter

1

1

0

0

1

1

0

0

0

1

-

-

Word

*

-

-

L-byte

H-byte

Interrupt

1

1

0

0

1

1

1

1

0

1

-

-

Word

*

-

-

L-byte

H-byte

Tachobyte

1

1

0

0

X

-

Byte

-

Byte

Control Word 1

1

1

1

1

0

0

1

1

0

1

Word

*

Word

*

L-byte

H-byte

L-byte

H-byte

Control Word 2

1

1

1

1

1

1

0

0

0

1

Word

*

Word

*

L-byte

H-byte

L-byte

H-byte

1= high, 0= low, x= not relevant

*

illegal addressing: each word must begin on an even address

8-bit mode: the L-byte of a word must be on an even address and be written first

-

not legal; this functional block can either be written or read

iC-NF

ENCODER PROCESSOR

Rev A0, Page 5/13

Control Word 1

Bit

L-byte

7

SEL1

6

SEL0

5

EN5

4

EN1

3

EN7

2

EN2

1

DIR1

0

EN0

Bit

H-byte

15

EN9

14

EN6

13

EN8

12

DIR2

11

EN12

10

EN13

9

RES1

8

RES0

Control Word 1

L-byte

Interrupt enable for port INT1

Bit 0

EN0

0

1

disabled

enabled (check for target position 1)

Bit 1

DIR1

0

1

direction set: clockwise (track A ahead of track B)

direction set: counter clockwise

Bit 2

EN2

0

1

disabled

enabled (predivisor output PDO)

Bit 3

EN7

0

1

disabled

enabled (revolving sense contrary to DIR1 sets interrupt)

Bit 4

EN1

0

1

disabled

enabled (index pulse ZF)

Bit 5

EN5

0

1

disabled

enabled (check for target position 2)

Input select for revolution capture

Bit 7,6

SEL(1:0)

0 1

1 1

1 0

0 0

AFIL

(track A filtered)

AB2

(track A and B gated, filtered, doubled frequency)

SYNB

(track B)

SYNA

(track A)

H-byte

Counter resolution for position sensing

Bit 9,8

RES(1:0)

0 0

1 0

0 1

1 1

10 Bit

12 Bit

14 Bit

16 Bit

Interrupt enable for port INT2

Bit 10

EN13

0

1

disabled

enabled (check for target position 2)

Bit 11

EN12

0

1

disabled

enabled (check for target position 1)

Bit 12

DIR2

0

1

direction set: clockwise (track A ahead of track B)

direction set: counter clockwise

Bit 13

EN8

0

1

disabled

enabled (revolving sense contrary to DIR2 sets interrupt)

Bit 14

EN6

0

1

disabled

enabled (index pulse ZF)

Bit 15

EN9

0

1

disabled

enabled (predivisor output PDO)