843252AG-04

www.icst.com/products/hiperclocks.html

REV. A JANUARY 25, 2006

1

Integrated

Circuit

Systems, Inc.

ICS843252-04

F

EMTO

C

LOCKS

TM C

RYSTAL

-

TO

-

3.3V LVPECL C

LOCK

G

ENERATOR

PRELIMINARY

G

ENERAL

D

ESCRIPTION

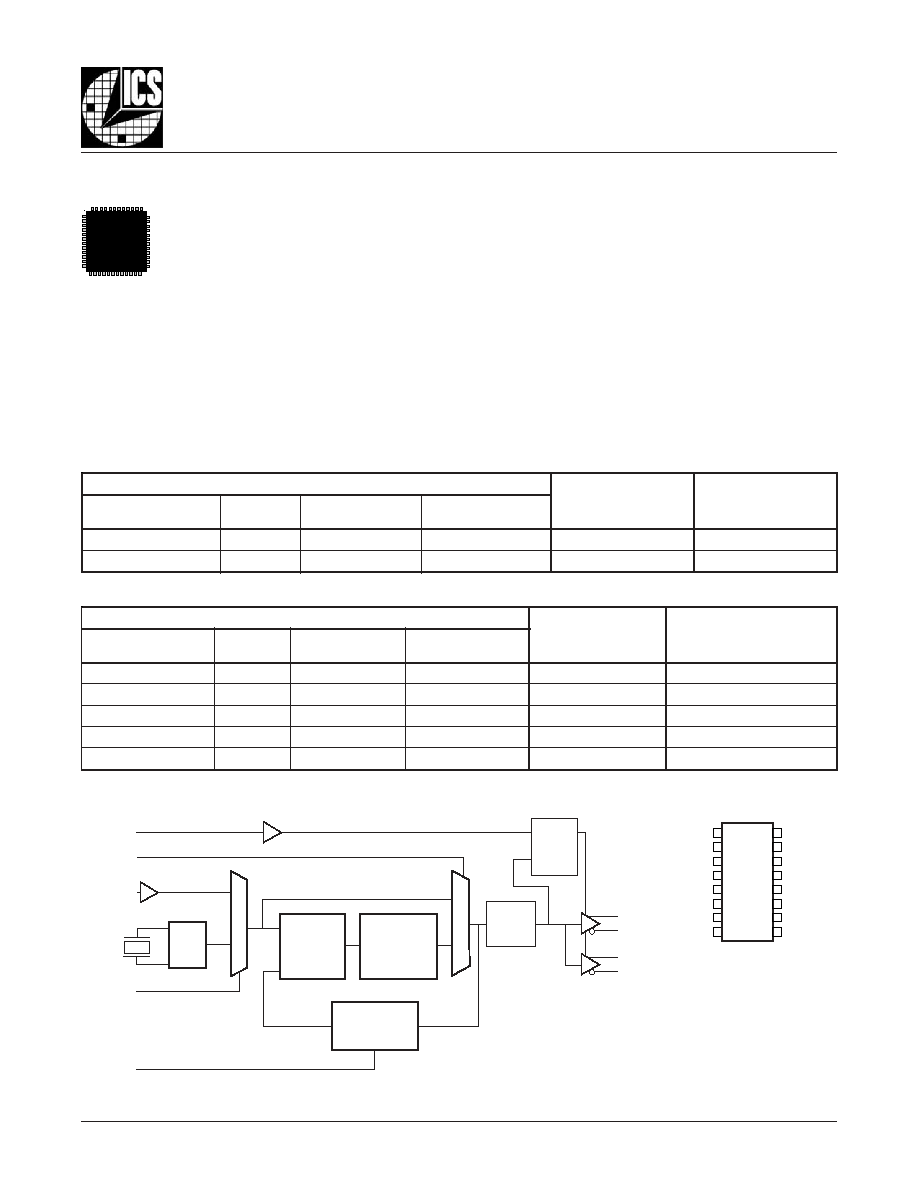

The ICS843252-04 is a 10Gb/12Gb Ethernet

Clock Generator and a member of the

HiPerClocks

TM

family of high perfor mance

devices from ICS. The ICS843252-04 can

synthesize 10 Gigabit Ethernet and 12 Gigabit

Ethernet with a 25MHz crystal. It can also generate SATA

and 10Gb Fibre Channel reference clock frequencies with

the appropriate choice of crystals. The ICS843252-04 has

excellent phase jitter performance and is packaged in a

small 16-pin TSSOP, making it ideal for use in systems with

limited board space.

F

EATURES

� Two differential 3.3V LVPECL output

� Crystal oscillator interface designed for

18pF parallel resonant crystals

� Crystal input frequency range: 19.33MHz - 30MHz

� Output frequency range: 145MHz - 187.5MHz

� VCO frequency range: 580MHz - 750MHz

� RMS phase jitter at 156.25MHz (1.875MHz - 20MHz):

0.39ps (typical)

� 3.3V operating supply

� 0�C to 70�C ambient operating temperature

� Industrial temperature information available upon request

� Available in both standard and lead-free compliant

packages

HiPerClockSTM

ICS

Pulldown

Pulldown

Pulldown

Pullup

Pulldown

1

0

1

0

Phase

Detector

VCO

580MHz-750MHz

OSC

0 = �25

(default)

1 = �30

DIV. N

�4

D

LE

Q

XTAL_IN

XTAL_OUT

Q0

nQ0

Q1

nQ1

FREQ_SEL

B

LOCK

D

IAGRAM

P

IN

A

SSIGNMENT

C

ONFIGURATION

T

ABLE

WITH

25MH

Z

C

RYSTAL

s

t

u

p

n

I

y

c

n

e

u

q

e

r

F

t

u

p

t

u

O

)

z

H

M

(

n

o

i

t

a

c

i

l

p

p

A

y

c

n

e

u

q

e

r

F

l

a

t

s

y

r

C

)

z

H

M

(

k

c

a

b

d

e

e

F

e

d

i

v

i

D

y

c

n

e

u

q

e

r

F

O

C

V

)

z

H

M

(

e

d

i

v

i

D

t

u

p

t

u

O

N

5

2

0

3

0

5

7

4

5

.

7

8

1

t

e

n

r

e

h

t

E

t

i

b

a

g

i

G

2

1

5

2

5

2

5

2

6

4

5

2

.

6

5

1

t

e

n

r

e

h

t

E

t

i

b

a

g

i

G

0

1

C

ONFIGURATION

T

ABLE

WITH

S

ELECTABLE

C

RYSTALS

s

t

u

p

n

I

y

c

n

e

u

q

e

r

F

t

u

p

t

u

O

)

z

H

M

(

n

o

i

t

a

c

i

l

p

p

A

y

c

n

e

u

q

e

r

F

l

a

t

s

y

r

C

)

z

H

M

(

k

c

a

b

d

e

e

F

e

d

i

v

i

D

y

c

n

e

u

q

e

r

F

O

C

V

)

z

H

M

(

e

d

i

v

i

D

t

u

p

t

u

O

N

0

2

0

3

0

0

6

4

0

5

1

A

T

A

S

5

2

.

1

2

0

3

5

.

7

3

6

4

5

7

3

.

9

5

1

l

e

n

n

a

h

C

e

r

b

i

F

t

i

b

a

g

i

G

0

1

4

2

5

2

0

0

6

4

0

5

1

A

T

A

S

5

.

5

2

5

2

5

.

7

3

6

4

5

7

3

.

9

5

1

l

e

n

n

a

h

C

e

r

b

i

F

t

i

b

a

g

i

G

0

1

0

3

5

2

0

5

7

4

5

.

7

8

1

t

e

n

r

e

h

t

E

t

i

b

a

g

i

G

2

1

CLK_SEL

REF_CLK

nPLL_SEL

OE

nQ1

Q1

V

CCO

OE

nPLL_SEL

V

CCO

Q0

nQ0

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

XTAL_IN

XTAL_OUT

V

EE

REF_CLK

CLK_SEL

V

CC

V

CCA

FREQ_SEL

ICS843252-04

16-Lead TSSOP

4.4mm x 5.0mm x 0.92mm

package body

G Package

Top View

The Preliminary Information presented herein represents a product in prototyping or pre-production. The noted characteristics are based on

initial product characterization. Integrated Circuit Systems, Incorporated (ICS) reserves the right to change any circuitry or specifications

without notice.

843252AG-04

www.icst.com/products/hiperclocks.html

REV. A JANUARY 25, 2006

2

Integrated

Circuit

Systems, Inc.

ICS843252-04

F

EMTO

C

LOCKS

TM C

RYSTAL

-

TO

-

3.3V LVPECL C

LOCK

G

ENERATOR

PRELIMINARY

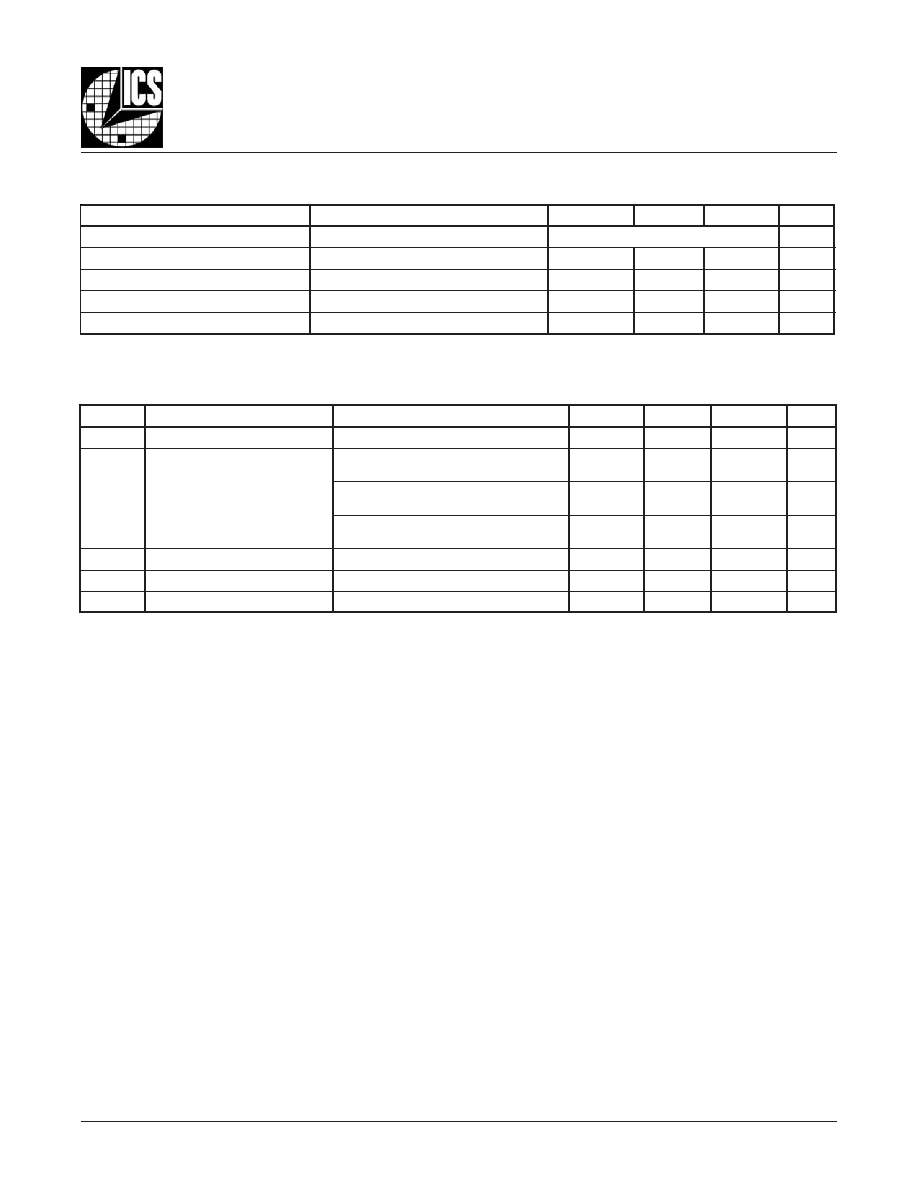

T

ABLE

2. P

IN

C

HARACTERISTICS

T

ABLE

1. P

IN

D

ESCRIPTIONS

r

e

b

m

u

N

e

m

a

N

e

p

y

T

n

o

i

t

p

i

r

c

s

e

D

2

,

1

1

Q

,

1

Q

n

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

C

E

P

V

L

.

s

t

u

p

t

u

o

k

c

o

l

c

l

a

i

t

n

e

r

e

f

f

i

D

6

,

3

V

O

C

C

r

e

w

o

P

.

s

n

i

p

y

l

p

p

u

s

t

u

p

t

u

O

4

E

O

t

u

p

n

I

p

u

ll

u

P

.

t

u

p

n

i

k

c

o

l

c

w

o

ll

o

f

s

t

u

p

t

u

o

k

c

o

l

c

,

H

G

I

H

n

e

h

W

.

e

l

b

a

n

e

t

u

p

t

u

O

.

h

g

i

h

d

e

c

r

o

f

e

r

a

s

t

u

p

t

u

o

x

Q

n

,

w

o

l

d

e

c

r

o

f

e

r

a

s

t

u

p

t

u

o

x

Q

,

W

O

L

n

e

h

W

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

5

L

E

S

_

L

L

P

n

t

u

p

n

I

n

w

o

d

ll

u

P

.

r

e

d

i

v

i

d

e

h

t

o

t

t

u

p

n

i

s

a

k

c

o

l

c

e

c

n

e

r

e

f

e

r

d

n

a

L

L

P

e

h

t

n

e

e

w

t

e

b

s

t

c

e

l

e

S

.

k

c

o

l

c

e

c

n

e

r

e

f

e

r

s

t

c

e

l

e

s

,

h

g

i

H

n

e

h

W

.

L

L

P

s

t

c

e

l

e

s

,

w

o

L

n

e

h

W

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

8

,

7

0

Q

n

,

0

Q

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

C

E

P

V

L

.

s

t

u

p

t

u

o

k

c

o

l

c

l

a

i

t

n

e

r

e

f

f

i

D

9

L

E

S

_

Q

E

R

F

t

u

p

n

I

n

w

o

d

ll

u

P

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

n

i

p

t

c

e

l

e

s

y

c

n

e

u

q

e

r

F

0

1

V

A

C

C

r

e

w

o

P

.

n

i

p

y

l

p

p

u

s

g

o

l

a

n

A

1

1

V

C

C

r

e

w

o

P

.

n

i

p

y

l

p

p

u

s

e

r

o

C

2

1

L

E

S

_

K

L

C

t

u

p

n

I

n

w

o

d

ll

u

P

,

h

g

i

H

n

e

h

W

.

s

t

u

p

n

i

l

a

t

s

y

r

c

s

t

c

e

l

e

s

,

w

o

L

n

e

h

W

.

t

u

p

n

i

t

c

e

l

e

s

k

c

o

l

C

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

K

L

C

_

F

E

R

s

t

c

e

l

e

s

3

1

K

L

C

_

F

E

R

t

u

p

n

I

n

w

o

d

ll

u

P

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

t

u

p

n

i

k

c

o

l

c

e

c

n

e

r

e

f

e

R

4

1

V

E

E

r

e

w

o

P

.

n

i

p

y

l

p

p

u

s

e

v

i

t

a

g

e

N

6

1

,

5

1

,

T

U

O

_

L

A

T

X

N

I

_

L

A

T

X

t

u

p

n

I

,

t

u

p

n

i

e

h

t

s

i

N

I

_

L

A

T

X

.

e

c

a

f

r

e

t

n

i

r

o

t

a

ll

i

c

s

o

l

a

t

s

y

r

C

.

t

u

p

t

u

o

e

h

t

s

i

T

U

O

_

L

A

T

X

:

E

T

O

N

n

w

o

d

ll

u

P

d

n

a

p

u

ll

u

P

.

s

e

u

l

a

v

l

a

c

i

p

y

t

r

o

f

,

s

c

i

t

s

i

r

r

e

t

c

a

r

a

h

C

n

i

P

,

2

e

l

b

a

T

e

e

S

.

s

r

o

t

s

i

s

e

r

t

u

p

n

i

l

a

n

r

e

t

n

i

o

t

r

e

f

e

r

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

C

N

I

e

c

n

a

t

i

c

a

p

a

C

t

u

p

n

I

4

F

p

R

P

U

L

L

U

P

r

o

t

s

i

s

e

R

p

u

ll

u

P

t

u

p

n

I

1

5

k

R

N

W

O

D

L

L

U

P

r

o

t

s

i

s

e

R

n

w

o

d

ll

u

P

t

u

p

n

I

1

5

k

843252AG-04

www.icst.com/products/hiperclocks.html

REV. A JANUARY 25, 2006

3

Integrated

Circuit

Systems, Inc.

ICS843252-04

F

EMTO

C

LOCKS

TM C

RYSTAL

-

TO

-

3.3V LVPECL C

LOCK

G

ENERATOR

PRELIMINARY

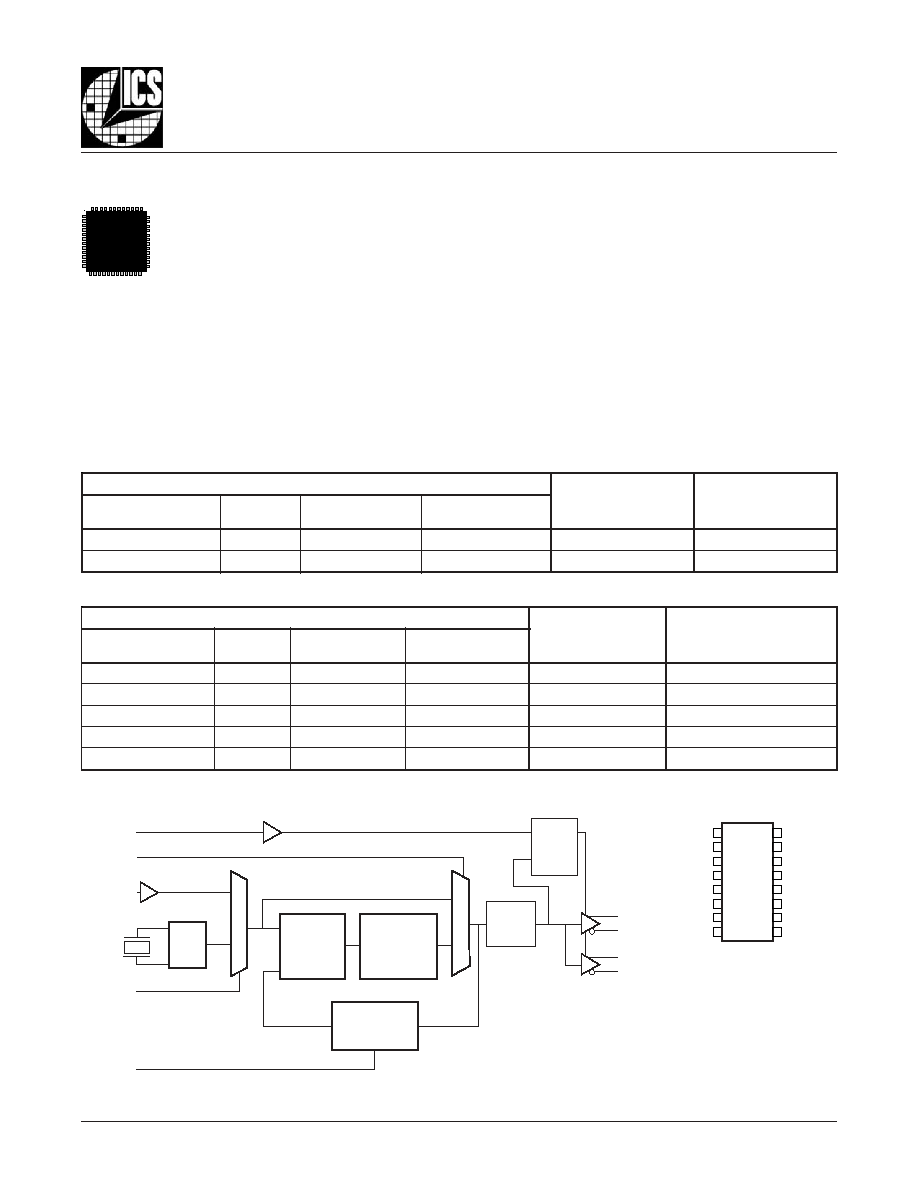

T

ABLE

3A. P

OWER

S

UPPLY

DC C

HARACTERISTICS

,

V

CC

= V

CCA

= V

CCO

= 3.3V�5%, T

A

= 0�C

TO

70�C

T

ABLE

3C. LVPECL DC C

HARACTERISTICS

,

V

CC

= V

CCA

= V

CCO

= 3.3V�5%, T

A

= 0�C

TO

70�C

A

BSOLUTE

M

AXIMUM

R

ATINGS

Supply Voltage, V

CC

4.6V

Inputs, V

I

-0.5V to V

CC

+ 0.5V

Outputs, I

O

Continuous Current

50mA

Surge Current

100mA

Package Thermal Impedance,

JA

89�C/W (0 lfpm)

Storage Temperature, T

STG

-65�C to 150�C

NOTE: Stresses beyond those listed under Absolute

Maximum Ratings may cause permanent damage to the

device. These ratings are stress specifications only. Functional

operation of product at these conditions or any conditions be-

yond those listed in the

DC Characteristics

or

AC Character-

istics

is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect product reliability.

T

ABLE

3B. LVCMOS/LVTTL DC C

HARACTERISTICS

,

V

CC

= V

CCA

= V

CCO

= 3.3V�5%, T

A

= 0�C

TO

70�C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

H

I

e

g

a

t

l

o

V

h

g

i

H

t

u

p

n

I

2

V

C

C

3

.

0

+

V

V

L

I

e

g

a

t

l

o

V

w

o

L

t

u

p

n

I

3

.

0

-

8

.

0

V

I

H

I

t

n

e

r

r

u

C

h

g

i

H

t

u

p

n

I

,

K

L

C

_

F

E

R

,

L

E

S

_

K

L

C

,

L

E

S

_

Q

E

R

F

L

E

S

_

L

L

P

n

V

C

C

V

=

N

I

V

5

6

4

.

3

=

0

5

1

A

�

E

O

V

C

C

V

=

N

I

V

5

6

4

.

3

=

5

A

�

I

L

I

t

n

e

r

r

u

C

w

o

L

t

u

p

n

I

,

K

L

C

_

F

E

R

,

L

E

S

_

K

L

C

,

L

E

S

_

Q

E

R

F

L

E

S

_

L

L

P

n

V

C

C

V

,

V

5

6

4

.

3

=

N

I

V

0

=

5

-

A

�

E

O

V

C

C

V

,

V

5

6

4

.

3

=

N

I

V

0

=

0

5

1

-

A

�

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

H

O

1

E

T

O

N

;

e

g

a

t

l

o

V

h

g

i

H

t

u

p

t

u

O

V

O

C

C

4

.

1

-

V

O

C

C

9

.

0

-

V

V

L

O

1

E

T

O

N

;

e

g

a

t

l

o

V

w

o

L

t

u

p

t

u

O

V

O

C

C

0

.

2

-

V

O

C

C

7

.

1

-

V

V

G

N

I

W

S

g

n

i

w

S

e

g

a

t

l

o

V

t

u

p

t

u

O

k

a

e

P

-

o

t

-

k

a

e

P

6

.

0

0

.

1

V

0

5

h

t

i

w

d

e

t

a

n

i

m

r

e

t

s

t

u

p

t

u

O

:

1

E

T

O

N

V

o

t

O

C

C

.

V

2

-

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

C

C

e

g

a

t

l

o

V

y

l

p

p

u

S

e

r

o

C

5

3

1

.

3

3

.

3

5

6

4

.

3

V

V

A

C

C

e

g

a

t

l

o

V

y

l

p

p

u

S

g

o

l

a

n

A

5

3

1

.

3

3

.

3

5

6

4

.

3

V

I

C

C

t

n

e

r

r

u

C

y

l

p

p

u

S

r

e

w

o

P

0

6

A

m

I

A

C

C

t

n

e

r

r

u

C

y

l

p

p

u

S

g

o

l

a

n

A

1

1

A

m

I

E

E

t

n

e

r

r

u

C

y

l

p

p

u

S

r

e

w

o

P

0

8

A

m

843252AG-04

www.icst.com/products/hiperclocks.html

REV. A JANUARY 25, 2006

4

Integrated

Circuit

Systems, Inc.

ICS843252-04

F

EMTO

C

LOCKS

TM C

RYSTAL

-

TO

-

3.3V LVPECL C

LOCK

G

ENERATOR

PRELIMINARY

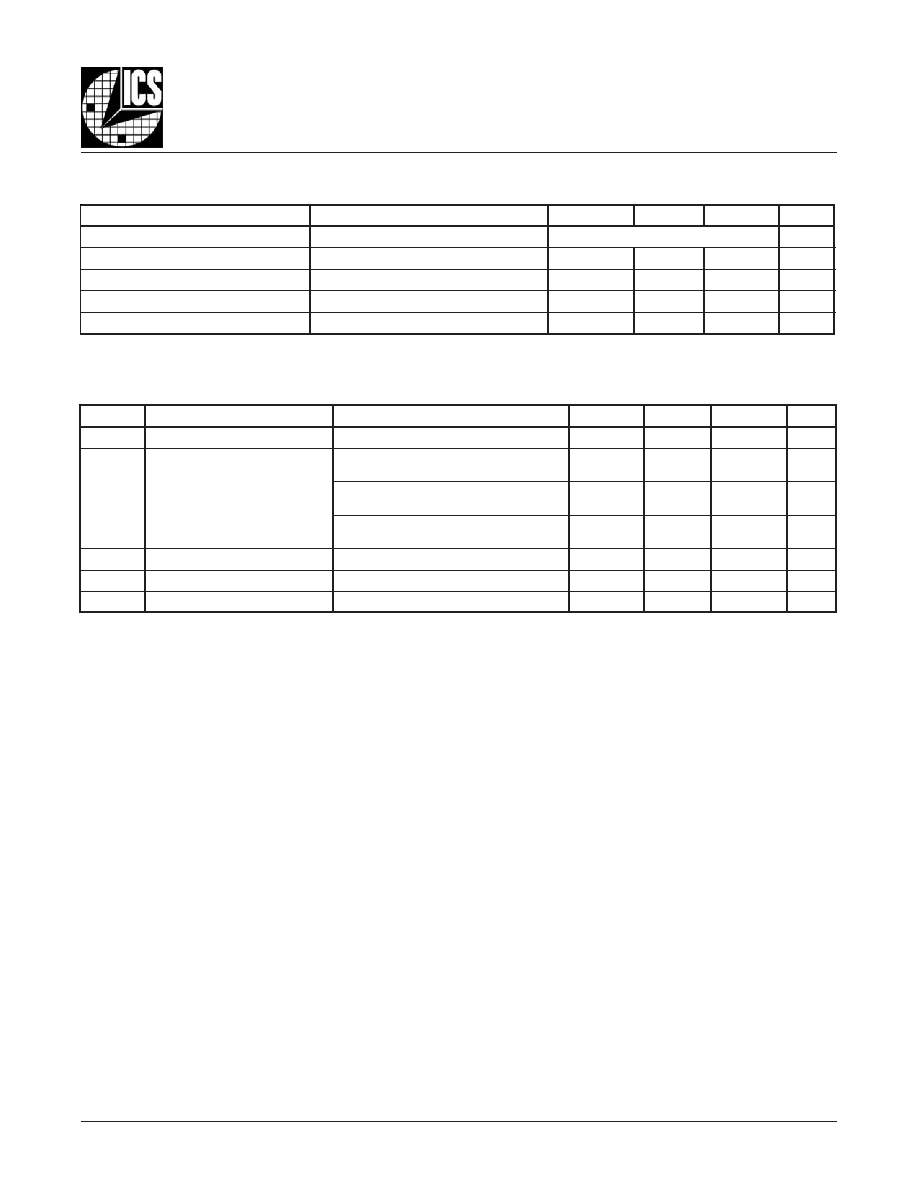

T

ABLE

5. AC C

HARACTERISTICS

,

V

CC

= V

CCA

= V

CCO

= 3.3V�5%, T

A

= 0�C

TO

70�C

T

ABLE

4. C

RYSTAL

C

HARACTERISTICS

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

n

o

i

t

a

ll

i

c

s

O

f

o

e

d

o

M

l

a

t

n

e

m

a

d

n

u

F

y

c

n

e

u

q

e

r

F

3

3

.

9

1

0

3

z

H

M

)

R

S

E

(

e

c

n

a

t

s

i

s

e

R

s

e

i

r

e

S

t

n

e

l

a

v

i

u

q

E

0

5

e

c

n

a

t

i

c

a

p

a

C

t

n

u

h

S

7

F

p

l

e

v

e

L

e

v

i

r

D

1

W

m

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

f

T

U

O

y

c

n

e

u

q

e

r

F

t

u

p

t

u

O

5

4

1

5

.

7

8

1

z

H

M

t

)

�

(

t

ij

;

)

m

o

d

n

a

R

(

r

e

t

t

i

J

e

s

a

h

P

S

M

R

1

E

T

O

N

:

e

g

n

a

R

n

o

i

t

a

r

g

e

t

n

I

@

z

H

M

5

2

.

6

5

1

z

H

M

0

2

-

z

H

M

5

7

8

.

1

9

3

.

0

s

p

:

e

g

n

a

R

n

o

i

t

a

r

g

e

t

n

I

@

z

H

M

5

7

3

.

9

5

1

z

H

M

0

2

-

z

H

M

5

7

8

.

1

8

3

.

0

s

p

:

e

g

n

a

R

n

o

i

t

a

r

g

e

t

n

I

@

z

H

M

5

.

7

8

1

z

H

M

0

2

-

z

H

M

5

7

8

.

1

8

3

.

0

s

p

t

)

o

(

k

s

3

,

2

E

T

O

N

;

w

e

k

S

t

u

p

t

u

O

D

B

T

s

p

t

R

t

/

F

e

m

i

T

ll

a

F

/

e

s

i

R

t

u

p

t

u

O

%

0

8

o

t

%

0

2

0

0

4

s

p

c

d

o

e

l

c

y

C

y

t

u

D

t

u

p

t

u

O

0

5

%

.

n

o

i

t

c

e

s

s

i

h

t

g

n

i

w

o

ll

o

f

s

t

o

l

P

e

s

i

o

N

e

s

a

h

P

e

h

t

o

t

r

e

f

e

r

e

s

a

e

l

P

:

1

E

T

O

N

.

s

n

o

i

t

i

d

n

o

c

d

a

o

l

l

a

u

q

e

h

t

i

w

d

n

a

e

g

a

t

l

o

v

y

l

p

p

u

s

e

m

a

s

e

h

t

t

a

s

t

u

p

t

u

o

n

e

e

w

t

e

b

w

e

k

s

s

a

d

e

n

i

f

e

D

:

2

E

T

O

N

V

t

a

d

e

r

u

s

a

e

M

O

C

C

.

2

/

.

n

o

i

t

c

u

d

o

r

p

n

i

d

e

t

s

e

t

t

o

N

.

n

o

i

t

a

z

i

r

e

t

c

a

r

a

h

c

y

b

d

e

e

t

n

a

r

a

u

g

e

r

a

s

r

e

t

e

m

a

r

a

p

e

s

e

h

T

:

3

E

T

O

N

843252AG-04

www.icst.com/products/hiperclocks.html

REV. A JANUARY 25, 2006

5

Integrated

Circuit

Systems, Inc.

ICS843252-04

F

EMTO

C

LOCKS

TM C

RYSTAL

-

TO

-

3.3V LVPECL C

LOCK

G

ENERATOR

PRELIMINARY

P

ARAMETER

M

EASUREMENT

I

NFORMATION

O

UTPUT

S

KEW

O

UTPUT

R

ISE

/F

ALL

T

IME

3.3V O

UTPUT

L

OAD

AC T

EST

C

IRCUIT

SCOPE

Qx

nQx

LVPECL

2V

-1.3V � 0.165V

Clock

Outputs

20%

80%

80%

20%

t

R

t

F

V

SW I N G

t

PW

t

PERIOD

t

PW

t

PERIOD

odc =

x 100%

Q0, Q1

nQ0, nQ1

V

EE

V

CC,

V

CCA,

V

CCO

RMS P

HASE

J

ITTER

Phase Noise Mask

Offset Frequency

f

1

f

2

Phase Noise Plot

RMS Jitter = Area Under the Masked Phase Noise Plot

Noise P

o

w

er

t

sk(o)

nQy

Qy

nQx

Qx

O

UTPUT

D

UTY

C

YCLE

/P

ULSE

W

IDTH

/P

ERIOD