85222AM-02

www.icst.com/products/hiperclocks.html

REV. A JANUARY 25, 2006

1

Integrated

Circuit

Systems, Inc.

ICS85222-02

1-

TO

-2 LVCMOS / LVTTL-

TO

-

D

IFFERENTIAL

HSTL T

RANSLATOR

PRELIMINARY

G

ENERAL

D

ESCRIPTION

The ICS85222-02 is a 1-to-2 LVCMOS / LVTTL-

to-Differential HSTL translator and a member of

the HiPerClocksTM family of High Performance

Clock Solutions from ICS. The ICS85222-02 has

one single ended clock input. The single ended

clock input accepts LVCMOS or LVTTL input levels and trans-

lates them to HSTL levels. The small outline 8-pin SOIC pack-

age makes this device ideal for applications where space,

high performance and low power are important.

F

EATURES

� Two differential HSTL outputs

� One LVCMOS/LVTTL clock input

� CLK input can accept the following input levels:

LVCMOS or LVTTL

� Maximum output frequency: 350MHz

� Part-to-part skew: TBD

� Propagation delay: 1ns (typical)

� V

OH

: 1.4V (maximum)

� Full 3.3V operating supply voltage

� 0�C to 70�C ambient operating temperature

� Industrial temperature information available upon request

� Available in both standard and lead-free RoHS compliant

packages

B

LOCK

D

IAGRAM

P

IN

A

SSIGNMENT

ICS85222-02

8-Lead SOIC

3.90mm x 4.92mm x 1.37mm body package

M Package

Top View

Q0

nQ0

Q1

nQ1

1

2

3

4

Q0

nQ0

CLK

HiPerClockSTM

ICS

V

DD

CLK

nc

GND

8

7

6

5

The Preliminary Information presented herein represents a product in prototyping or pre-production. The noted characteristics are based on

initial product characterization. Integrated Circuit Systems, Incorporated (ICS) reserves the right to change any circuitry or specifications

without notice.

Q1

nQ1

Pullup

85222AM-02

www.icst.com/products/hiperclocks.html

REV. A JANUARY 25, 2006

2

Integrated

Circuit

Systems, Inc.

ICS85222-02

1-

TO

-2 LVCMOS / LVTTL-

TO

-

D

IFFERENTIAL

HSTL T

RANSLATOR

PRELIMINARY

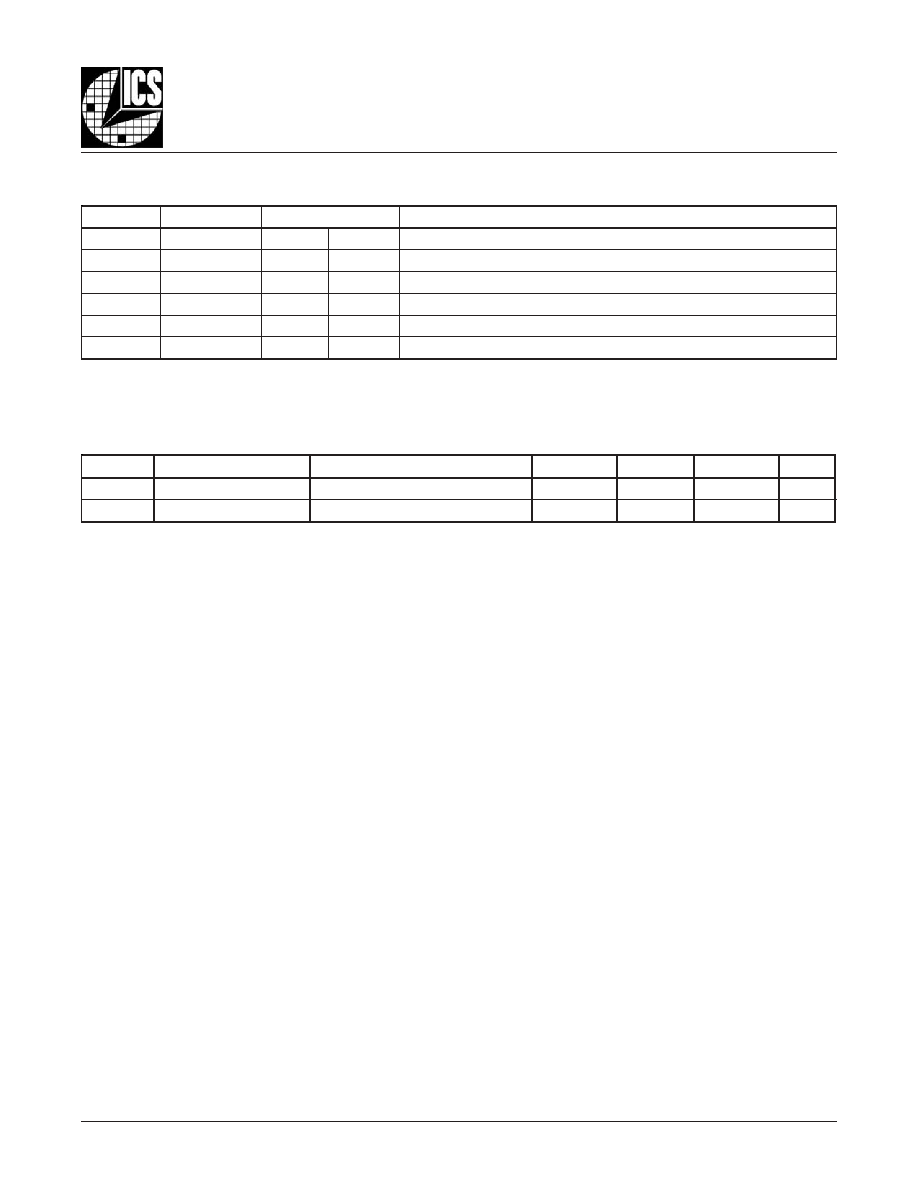

T

ABLE

1. P

IN

D

ESCRIPTIONS

T

ABLE

2. P

IN

C

HARACTERISTICS

r

e

b

m

u

N

e

m

a

N

e

p

y

T

n

o

i

t

p

i

r

c

s

e

D

2

,

1

0

Q

n

,

0

Q

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

S

H

.

r

i

a

p

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

D

4

,

3

1

Q

n

,

1

Q

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

S

H

.

r

i

a

p

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

D

5

D

N

G

r

e

w

o

P

.

d

n

u

o

r

g

y

l

p

p

u

s

r

e

w

o

P

6

K

L

C

t

u

p

n

I

p

u

ll

u

P

.

t

u

p

n

i

k

c

o

l

c

L

T

T

V

L

/

S

O

M

C

V

L

7

c

n

d

e

s

u

n

U

.

t

c

e

n

n

o

c

o

N

8

V

D

D

r

e

w

o

P

.

n

i

p

y

l

p

p

u

s

e

v

i

t

i

s

o

P

:

E

T

O

N

p

u

ll

u

P

.

s

e

u

l

a

v

l

a

c

i

p

y

t

r

o

f

,

s

c

i

t

s

i

r

e

t

c

a

r

a

h

C

n

i

P

,

2

e

l

b

a

T

e

e

S

.

s

r

o

t

s

i

s

e

r

t

u

p

n

i

l

a

n

r

e

t

n

i

o

t

s

r

e

f

e

r

.

d

e

t

a

n

i

m

r

e

t

e

b

t

s

u

m

s

r

i

a

p

t

u

p

t

u

o

d

e

s

u

n

U

:

E

T

O

N

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

C

N

I

e

c

n

a

t

i

c

a

p

a

C

t

u

p

n

I

4

F

p

R

P

U

L

L

U

P

r

o

t

s

i

s

e

R

p

u

ll

u

P

t

u

p

n

I

1

5

k

85222AM-02

www.icst.com/products/hiperclocks.html

REV. A JANUARY 25, 2006

3

Integrated

Circuit

Systems, Inc.

ICS85222-02

1-

TO

-2 LVCMOS / LVTTL-

TO

-

D

IFFERENTIAL

HSTL T

RANSLATOR

PRELIMINARY

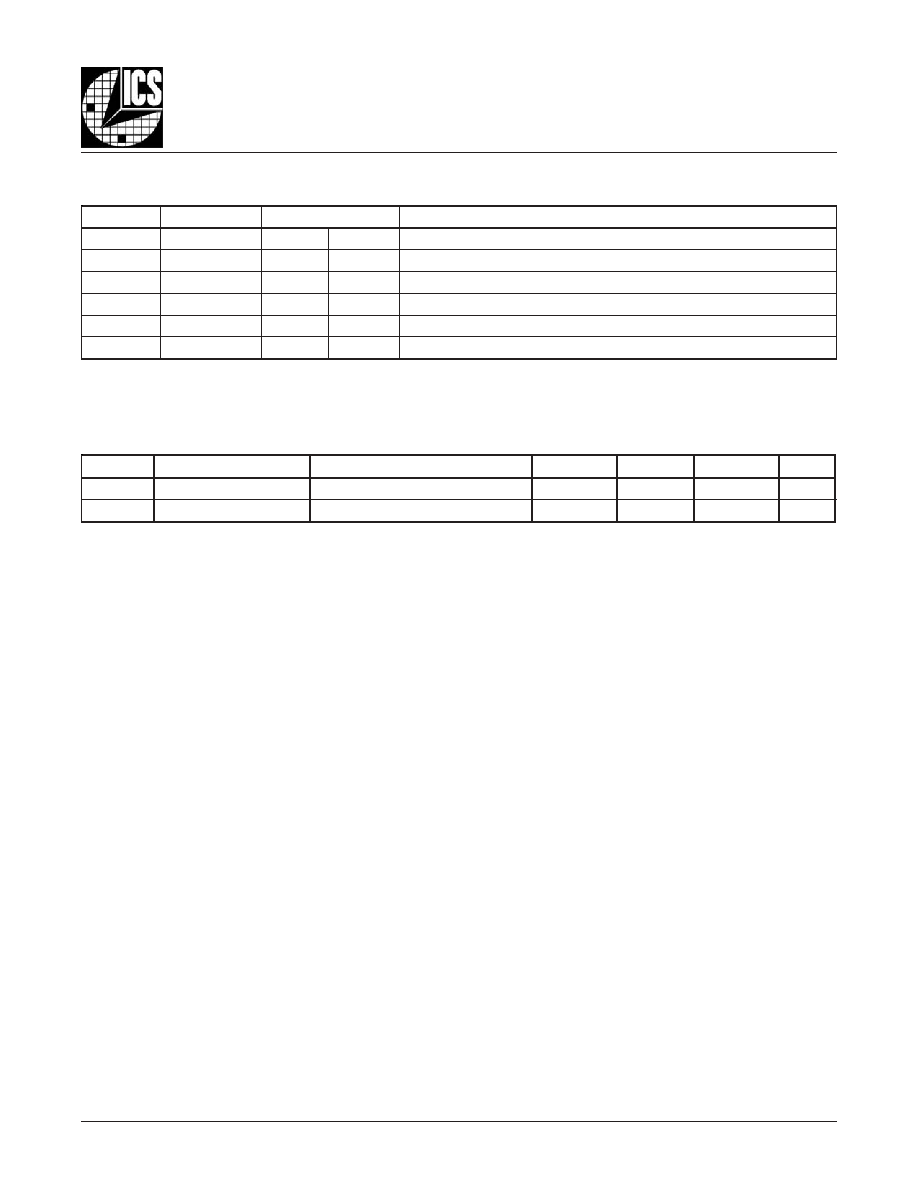

T

ABLE

3A. P

OWER

S

UPPLY

DC C

HARACTERISTICS

,

V

DD

= 3.3V�5%, T

A

= 0�C

TO

70�C

T

ABLE

3B. LVCMOS / LVTTL DC C

HARACTERISTICS

,

V

DD

= 3.3V�5%, T

A

= 0�C

TO

70�C

T

ABLE

3C. HSTL DC C

HARACTERISTICS

,

V

DD

= 3.3V�5%, T

A

= 0�C

TO

70�C

A

BSOLUTE

M

AXIMUM

R

ATINGS

Supply Voltage, V

DD

4.6V

Inputs, V

I

-0.5V to V

DD

+ 0.5V

Outputs, I

O

Continuous Current

50mA

Surge Current

100mA

Package Thermal Impedance,

JA

112.7�C/W (0 lfpm)

Storage Temperature, T

STG

-65�C to 150�C

NOTE: Stresses beyond those listed under Absolute

Maximum Ratings may cause permanent damage to the

device. These ratings are stress specifications only. Functional

operation of product at these conditions or any conditions be-

yond those listed in the

DC Characteristics

or

AC Character-

istics

is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect product reliability.

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

e

v

i

t

i

s

o

P

5

3

1

.

3

3

.

3

5

6

4

.

3

V

I

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

r

e

w

o

P

0

9

A

m

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

H

I

e

g

a

t

l

o

V

h

g

i

H

t

u

p

n

I

2

V

D

D

3

.

0

+

V

V

L

I

e

g

a

t

l

o

V

w

o

L

t

u

p

n

I

3

.

0

-

8

.

0

V

I

H

I

t

n

e

r

r

u

C

h

g

i

H

t

u

p

n

I

K

L

C

V

D

D

V

=

N

I

V

5

6

4

.

3

=

5

A

�

I

L

I

t

n

e

r

r

u

C

w

o

L

t

u

p

n

I

K

L

C

V

D

D

V

,

5

6

4

.

3

=

N

I

V

0

=

0

5

1

-

A

�

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

H

O

1

E

T

O

N

;

e

g

a

t

l

o

V

h

g

i

H

t

u

p

t

u

O

1

4

.

1

V

V

L

O

1

E

T

O

N

;

e

g

a

t

l

o

V

w

o

L

t

u

p

t

u

O

0

4

.

0

V

V

G

N

I

W

S

g

n

i

w

S

e

g

a

t

l

o

V

t

u

p

t

u

O

k

a

e

P

-

o

t

-

k

a

e

P

6

.

0

4

.

1

V

0

5

h

t

i

w

d

e

t

a

n

i

m

r

e

t

s

t

u

p

t

u

O

:

1

E

T

O

N

.

D

N

G

o

t

T

ABLE

4. AC C

HARACTERISTICS

,

V

DD

= 3.3V�5%, T

A

= 0�C

TO

70�C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

f

X

A

M

y

c

n

e

u

q

e

r

F

t

u

p

t

u

O

0

5

3

z

H

M

t

D

P

1

E

T

O

N

;

y

a

l

e

D

n

o

i

t

a

g

a

p

o

r

P

0

.

1

s

n

t

)

p

p

(

k

s

3

,

2

E

T

O

N

;

w

e

k

S

t

r

a

P

-

o

t

-

t

r

a

P

D

B

T

s

p

t

R

t

/

F

e

m

i

T

ll

a

F

/

e

s

i

R

t

u

p

t

u

O

%

0

8

o

t

%

0

2

5

7

3

s

p

c

d

o

e

l

c

y

C

y

t

u

D

t

u

p

t

u

O

0

5

%

V

m

o

r

f

d

e

r

u

s

a

e

M

:

1

E

T

O

N

D

D

.

t

n

i

o

p

g

n

i

s

s

o

r

c

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

d

e

h

t

o

t

t

u

p

n

i

e

h

t

f

o

2

/

d

a

o

l

l

a

u

q

e

h

t

i

w

d

n

a

s

e

g

a

t

l

o

v

y

l

p

p

u

s

e

m

a

s

e

h

t

t

a

g

n

i

t

a

r

e

p

o

s

e

c

i

v

e

d

t

n

e

r

e

f

f

i

d

n

o

s

t

u

p

t

u

o

n

e

e

w

t

e

b

w

e

k

s

s

a

d

e

n

i

f

e

D

:

2

E

T

O

N

.

s

t

n

i

o

p

s

s

o

r

c

l

a

i

t

n

e

r

e

f

f

i

d

e

h

t

t

a

d

e

r

u

s

a

e

m

e

r

a

s

t

u

p

t

u

o

e

h

t

,

e

c

i

v

e

d

h

c

a

e

n

o

s

t

u

p

n

i

f

o

e

p

y

t

e

m

a

s

e

h

t

g

n

i

s

U

.

s

n

o

i

t

i

d

n

o

c

.

5

6

d

r

a

d

n

a

t

S

C

E

D

E

J

h

t

i

w

e

c

n

a

d

r

o

c

c

a

n

i

d

e

n

i

f

e

d

s

i

r

e

t

e

m

a

r

a

p

s

i

h

T

:

3

E

T

O

N

85222AM-02

www.icst.com/products/hiperclocks.html

REV. A JANUARY 25, 2006

4

Integrated

Circuit

Systems, Inc.

ICS85222-02

1-

TO

-2 LVCMOS / LVTTL-

TO

-

D

IFFERENTIAL

HSTL T

RANSLATOR

PRELIMINARY

P

ARAMETER

M

EASUREMENT

I

NFORMATION

P

ART

-

TO

-P

ART

S

KEW

P

ROPAGATION

D

ELAY

Clock

Outputs

20%

80%

80%

20%

t

R

t

F

V

SW I N G

3.3V C

ORE

/3.3V O

UTPUT

L

OAD

AC T

EST

C

IRCUIT

SCOPE

HSTL

Qx

nQx

t

sk(pp)

nQx

Qx

nQy

Qy

PART 1

PART 2

CLK

nQ0, nQ1

Q0, Q1

t

PD

V

DD

2

V

DD

0V

3.3V � 5%

O

UTPUT

D

UTY

C

YCLE

/P

ULSE

W

IDTH

/P

ERIOD

t

PW

t

PERIOD

t

PW

t

PERIOD

odc =

x 100%

nQ0, nQ1

Q0, Q1

GND

O

UTPUT

R

ISE

/F

ALL

T

IME

85222AM-02

www.icst.com/products/hiperclocks.html

REV. A JANUARY 25, 2006

5

Integrated

Circuit

Systems, Inc.

ICS85222-02

1-

TO

-2 LVCMOS / LVTTL-

TO

-

D

IFFERENTIAL

HSTL T

RANSLATOR

PRELIMINARY

O

UTPUTS

:

HSTL O

UTPUT

All unused HSTL outputs can be left floating. We recommend

that there is no trace attached. Both sides of the differential

output pair should either be left floating or terminated.

R

ECOMMENDATIONS

FOR

U

NUSED

O

UTPUT

P

INS

A

PPLICATION

I

NFORMATION