Document Outline

- General Description

- Features

- Block Diagram

- Pin Assignment

- Pin Descriptions

- Pin Characteristics

- Control Input Function Table

- CLK_EN Timing Diagram

- Clock Input Function Table

- Absolute Maximum Ratings

- Power Supply DC Characteristics

- LVCMOS DC Characteristics

- Differential DC Characteristics

- LVPECL DC Characteristics

- LVDS DC Characteristics

- AC Characteristics

- Parameter Measurement Information

- 3.3V Output Load Test Circuit Diagram

- Output Skew Diagram

- Part-to-Part Skew Diagram

- Output Rise/Fall Time Diagram

- Propagation Delay Diagram

- odc & tPeriod Diagram

- Differential Input Level Diagram

- Differential Output Level Diagram

- VOS Setup Diagram

- VOD Setup Diagram

- IOSD Setup Diagram

- IOS Setup Diagram

- IOFF Setup Diagram

- IOZ Setup Diagram

- Application Information

- Wiring the Differential Input to Accept Single Ended Levels

- Single Ended Signal Driving Differential Input

- Reliability Information

- Transistor Count

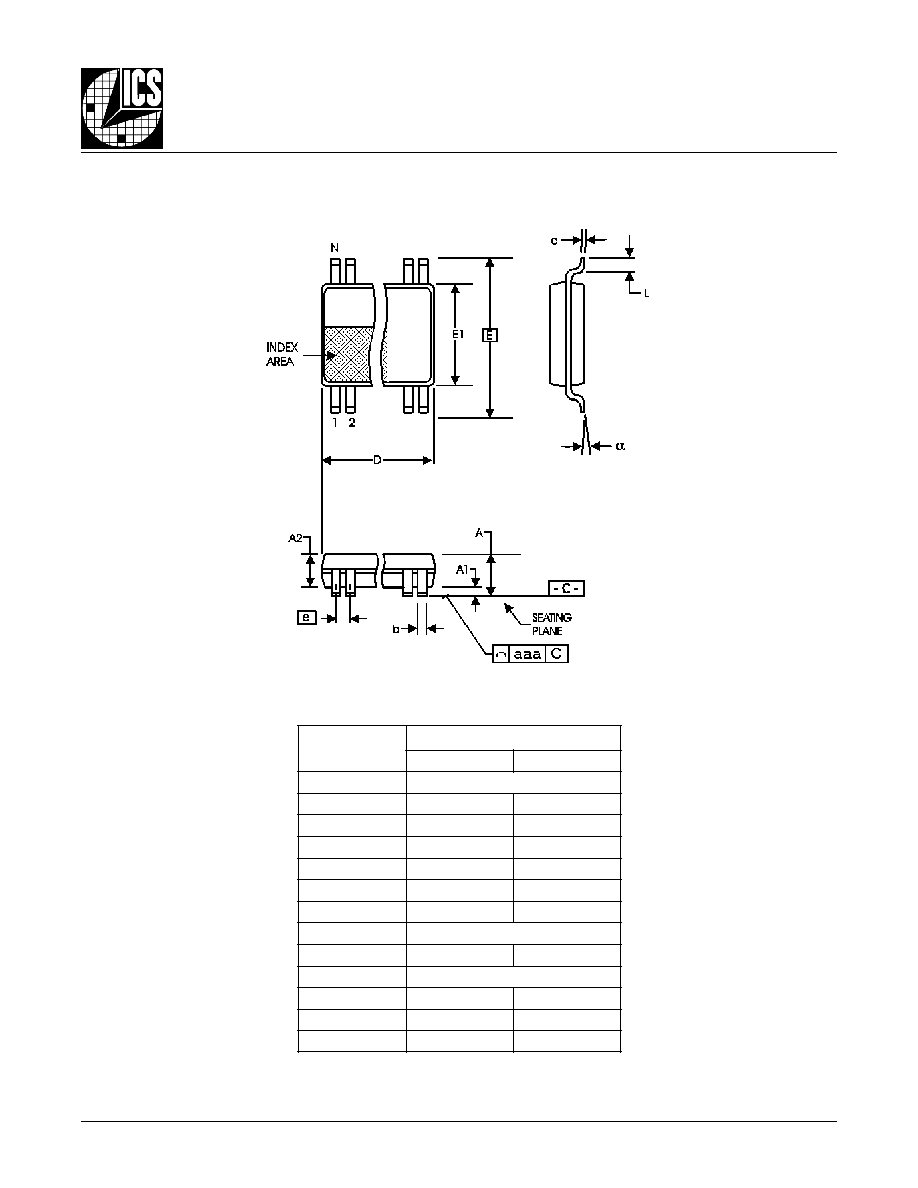

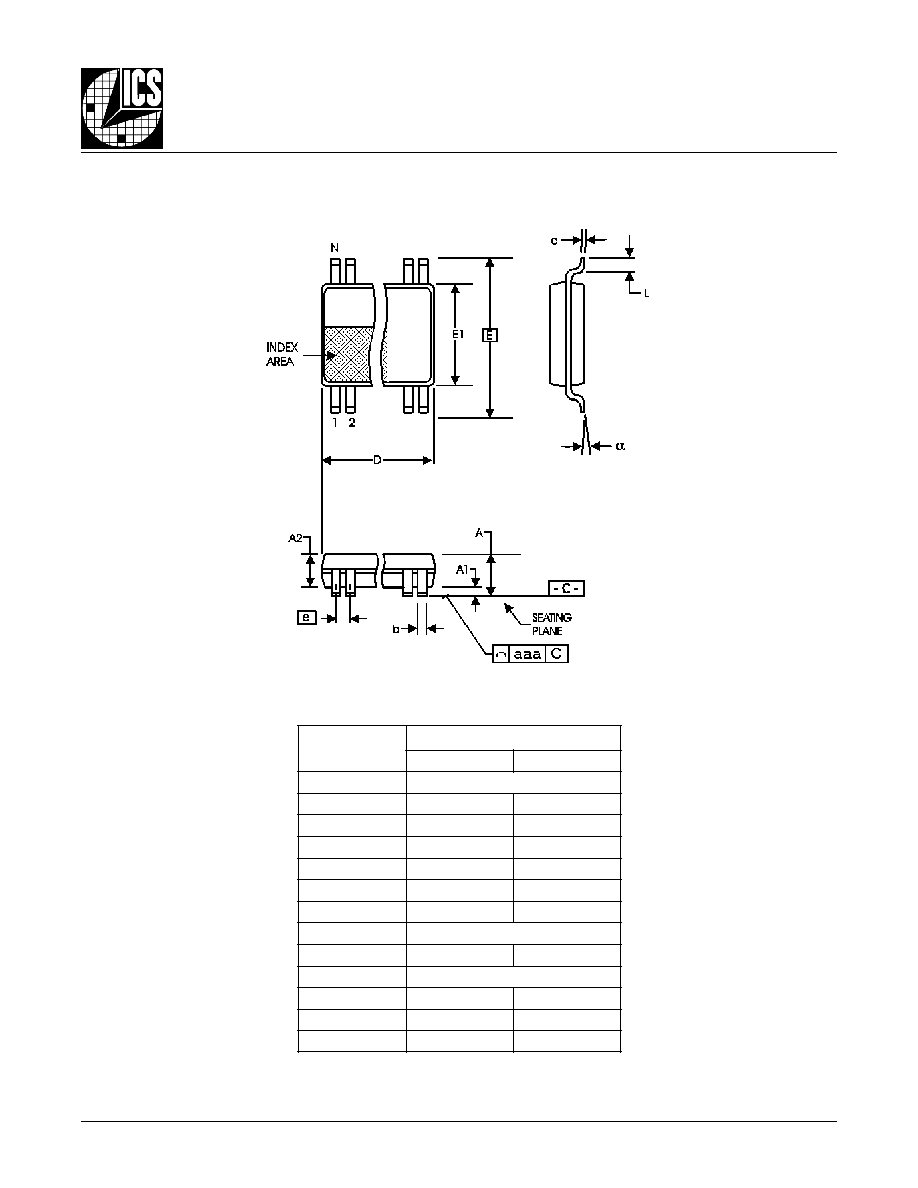

- Package Outline

- Package Dimensions

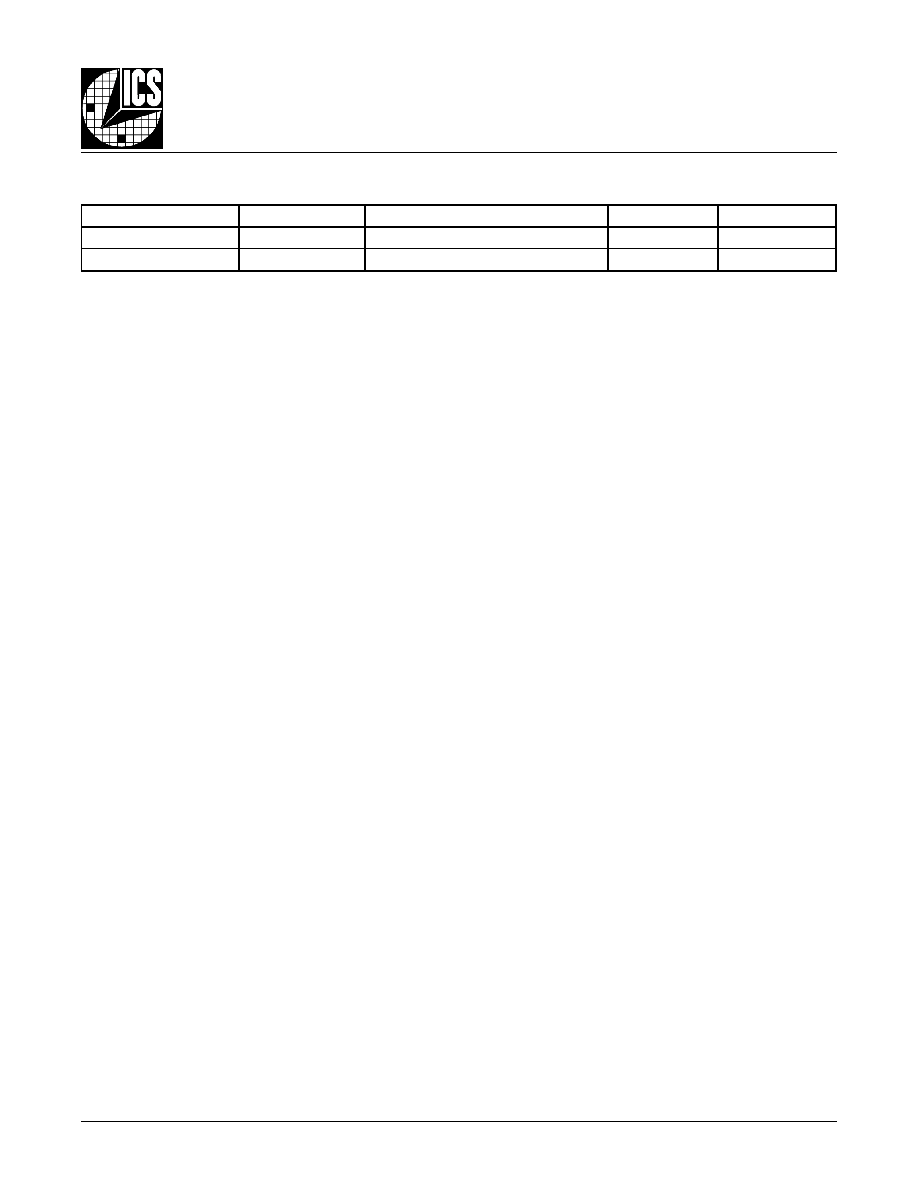

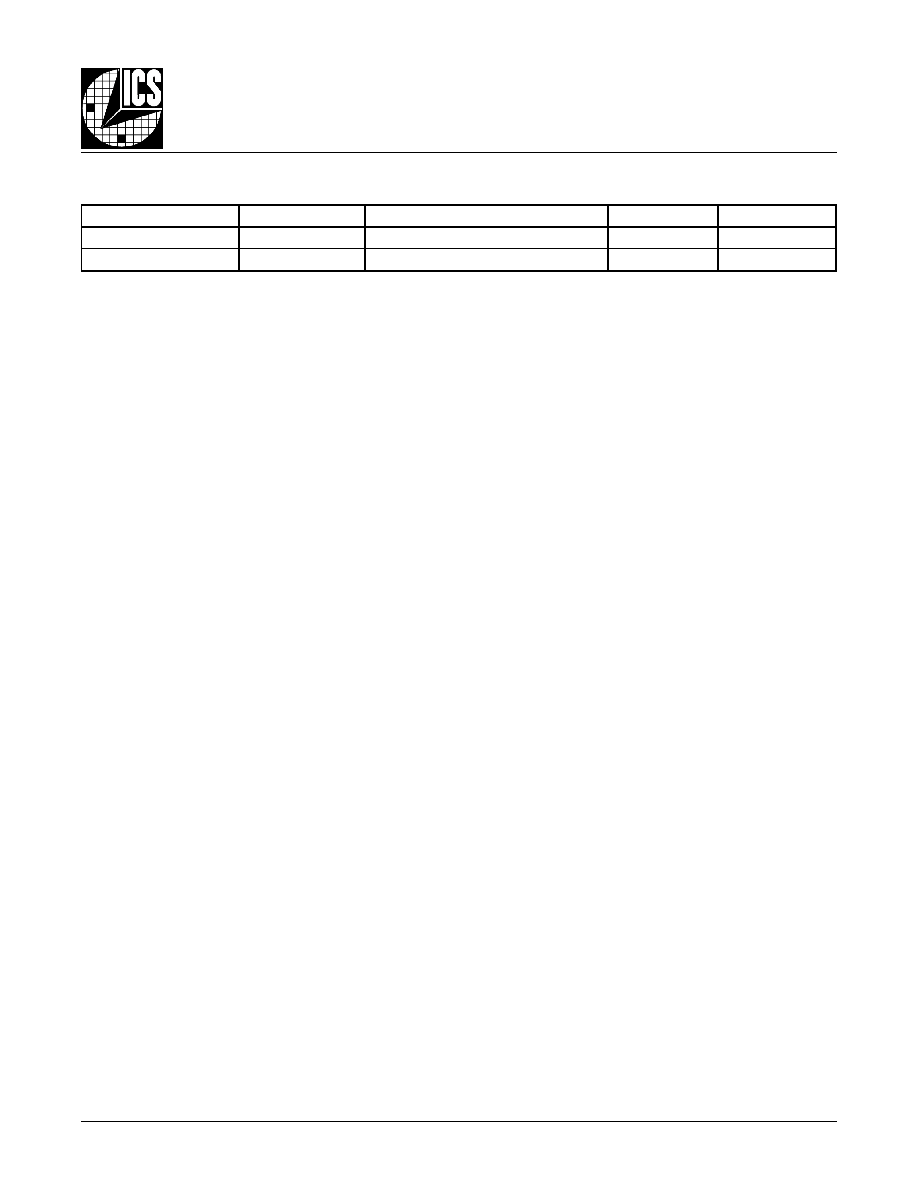

- Ordering Information

- Revision History Sheet

8543BG

www.icst.com/products/hiperclocks.html

REV. C SEPTEMBER 19, 2002

1

Integrated

Circuit

Systems, Inc.

ICS8543

L

OW

S

KEW

, 1-

TO

-4

D

IFFERENTIAL

-

TO

-LVDS F

ANOUT

B

UFFER

G

ENERAL

D

ESCRIPTION

The ICS8543 is a low skew, high performance

1-to-4 Differential-to-LVDS clock fanout buffer

and a member of the HiPerClockSTM family of

High Performance Clock Solutions from ICS.

Utilizing Low Voltage Differential Signaling

(LVDS) the ICS8543 provides a low power, low noise, solu-

tion for distributing clock signals over controlled impedances

of 100

. The ICS8543 has two selectable clock inputs. The

CLK, nCLK pair can accept most standard differential input

levels. The PCLK, nPCLK pair can accept LVPECL, CML, or

SSTL input levels. The clock enable is internally synchronized

to eliminate runt pulses on the outputs during asynchronous

assertion/deassertion of the clock enable pin.

Guaranteed output and part-to-part skew characteristics

make the ICS8543 ideal for those applications demanding

well defined performance and repeatability.

F

EATURES

�

4 differential LVDS outputs

�

Selectable differential CLK, nCLK or LVPECL clock inputs

�

CLK, nCLK pair can accept the following differential

input levels: LVDS, LVPECL, LVHSTL, SSTL, HCSL

�

PCLK, nPCLK supports the following input types:

LVPECL, CML, SSTL

�

Maximum output frequency: 800MHz

�

Translates any single ended input signal to LVDS levels

with resistor bias on nCLK input

�

Output skew: 40ps (maximum)

�

Part-to-part skew: 500ps (maximum)

�

Propagation delay: 2.6ns (maximum)

�

3.3V operating supply

�

0�C to 70�C ambient operating temperature

�

Industrial temperature information available upon request

B

LOCK

D

IAGRAM

P

IN

A

SSIGNMENT

ICS8543

20-Lead TSSOP

4.4mm x 6.5mm x 0.92mm body package

G Package

Top View

GND

CLK_EN

CLK_SEL

CLK

nCLK

PCLK

nPCLK

OE

GND

V

DD

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

Q0

nQ0

V

DD

Q1

nQ1

Q2

nQ2

GND

Q3

nQ3

HiPerClockSTM

,&6

OE

CLK

nCLK

PCLK

nPCLK

Q0

nQ0

Q1

nQ1

Q2

nQ2

Q3

nQ3

0

1

CLK_EN

CLK_SEL

D

Q

LE

8543BG

www.icst.com/products/hiperclocks.html

REV. C SEPTEMBER 19, 2002

2

Integrated

Circuit

Systems, Inc.

ICS8543

L

OW

S

KEW

, 1-

TO

-4

D

IFFERENTIAL

-

TO

-LVDS F

ANOUT

B

UFFER

T

ABLE

2. P

IN

C

HARACTERISTICS

T

ABLE

1. P

IN

D

ESCRIPTIONS

r

e

b

m

u

N

e

m

a

N

e

p

y

T

n

o

i

t

p

i

r

c

s

e

D

3

1

,

9

,

1

D

N

G

r

e

w

o

P

.

d

n

u

o

r

g

y

l

p

p

u

s

r

e

w

o

P

2

N

E

_

K

L

C

t

u

p

n

I

p

u

ll

u

P

k

c

o

l

c

s

w

o

ll

o

f

s

t

u

p

t

u

o

k

c

o

l

c

,

H

G

I

H

n

e

h

W

.

e

l

b

a

n

e

k

c

o

l

c

g

n

i

z

i

n

o

r

h

c

n

y

S

d

e

c

r

o

f

e

r

a

s

t

u

p

t

u

o

Q

n

,

w

o

l

d

e

c

r

o

f

e

r

a

s

t

u

p

t

u

o

Q

,

W

O

L

n

e

h

W

.

t

u

p

n

i

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

h

g

i

h

3

L

E

S

_

K

L

C

t

u

p

n

I

n

w

o

d

ll

u

P

.

s

t

u

p

n

i

K

L

C

P

n

,

K

L

C

P

s

t

c

e

l

e

s

,

H

G

I

H

n

e

h

W

.

t

u

p

n

i

t

c

e

l

e

s

k

c

o

l

C

.

s

t

u

p

n

i

K

L

C

n

,

K

L

C

s

t

c

e

l

e

s

W

O

L

n

e

h

W

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

4

K

L

C

t

u

p

n

I

n

w

o

d

ll

u

P

.

t

u

p

n

i

k

c

o

l

c

l

a

i

t

n

e

r

e

f

f

i

d

g

n

i

t

r

e

v

n

i

-

n

o

N

5

K

L

C

n

t

u

p

n

I

p

u

ll

u

P

.

t

u

p

n

i

k

c

o

l

c

l

a

i

t

n

e

r

e

f

f

i

d

g

n

i

t

r

e

v

n

I

6

K

L

C

P

t

u

p

n

I

n

w

o

d

ll

u

P

.

t

u

p

n

i

k

c

o

l

c

L

C

E

P

V

L

l

a

i

t

n

e

r

e

f

f

i

d

g

n

i

t

r

e

v

n

i

-

n

o

N

7

K

L

C

P

n

t

u

p

n

I

p

u

ll

u

P

.

t

u

p

n

i

k

c

o

l

c

L

C

E

P

V

L

l

a

i

t

n

e

r

e

f

f

i

d

g

n

i

t

r

e

v

n

I

8

E

O

t

u

p

n

I

p

u

ll

u

P

0

Q

n

,

0

Q

s

t

u

p

t

u

o

f

o

g

n

il

b

a

s

i

d

d

n

a

g

n

il

b

a

n

e

s

l

o

r

t

n

o

C

.

e

l

b

a

n

e

t

u

p

t

u

O

.

3

Q

n

,

3

Q

h

g

u

o

r

h

t

8

1

,

0

1

V

D

D

r

e

w

o

P

.

s

n

i

p

y

l

p

p

u

s

e

v

i

t

i

s

o

P

2

1

,

1

1

3

Q

,

3

Q

n

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

S

D

V

L

.

r

i

a

p

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

D

5

1

,

4

1

2

Q

,

2

Q

n

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

S

D

V

L

.

r

i

a

p

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

D

7

1

,

6

1

1

Q

,

1

Q

n

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

S

D

V

L

.

r

i

a

p

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

D

0

2

,

9

1

0

Q

,

0

Q

n

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

S

D

V

L

.

r

i

a

p

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

D

:

E

T

O

N

p

u

ll

u

P

d

n

a

w

o

d

ll

u

P

.

s

e

u

l

a

v

l

a

c

i

p

y

t

r

o

f

,

s

c

i

t

s

i

r

e

t

c

a

r

a

h

C

n

i

P

,

2

e

l

b

a

T

e

e

S

.

s

r

o

t

s

i

s

e

r

t

u

p

n

i

l

a

n

r

e

t

n

i

o

t

r

e

f

e

r

n

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

C

N

I

e

c

n

a

t

i

c

a

p

a

C

t

u

p

n

I

4

F

p

R

P

U

L

L

U

P

r

o

t

s

i

s

e

R

p

u

ll

u

P

t

u

p

n

I

1

5

K

R

N

W

O

D

L

L

U

P

r

o

t

s

i

s

e

R

n

w

o

d

ll

u

P

t

u

p

n

I

1

5

K

8543BG

www.icst.com/products/hiperclocks.html

REV. C SEPTEMBER 19, 2002

3

Integrated

Circuit

Systems, Inc.

ICS8543

L

OW

S

KEW

, 1-

TO

-4

D

IFFERENTIAL

-

TO

-LVDS F

ANOUT

B

UFFER

T

ABLE

3B. C

LOCK

I

NPUT

F

UNCTION

T

ABLE

T

ABLE

3A. C

ONTROL

I

NPUT

F

UNCTION

T

ABLE

s

t

u

p

n

I

s

t

u

p

t

u

O

E

O

N

E

_

K

L

C

L

E

S

_

K

L

C

e

c

r

u

o

S

d

e

t

c

e

l

e

S

3

Q

:

0

Q

3

Q

n

:

0

Q

n

0

X

X

Z

i

H

Z

i

H

1

0

0

K

L

C

n

,

K

L

C

w

o

L

;

d

e

l

b

a

s

i

D

h

g

i

H

;

d

e

l

b

a

s

i

D

1

0

1

K

L

C

P

n

,

K

L

C

P

w

o

L

;

d

e

l

b

a

s

i

D

h

g

i

H

;

d

e

l

b

a

s

i

D

1

1

0

K

L

C

n

,

K

L

C

d

e

l

b

a

n

E

d

e

l

b

a

n

E

1

1

1

K

L

C

P

n

,

K

L

C

P

d

e

l

b

a

n

E

d

e

l

b

a

n

E

n

w

o

h

s

s

a

e

g

d

e

k

c

o

l

c

t

u

p

n

i

g

n

il

l

a

f

d

n

a

g

n

i

s

i

r

a

g

n

i

w

o

ll

o

f

d

e

l

b

a

n

e

r

o

d

e

l

b

a

s

i

d

e

r

a

s

t

u

p

t

u

o

k

c

o

l

c

e

h

t

,

s

e

h

c

t

i

w

s

N

E

_

K

L

C

r

e

t

f

A

n

i

.

1

e

r

u

g

i

F

n

i

d

e

b

i

r

c

s

e

d

s

a

s

t

u

p

n

i

K

L

C

P

n

,

K

L

C

P

d

n

a

K

L

C

n

,

K

L

C

e

h

t

f

o

n

o

i

t

c

n

u

f

a

e

r

a

s

t

u

p

t

u

o

e

h

t

f

o

e

t

a

t

s

e

h

t

,

e

d

o

m

e

v

i

t

c

a

e

h

t

n

I

.

B

3

e

l

b

a

T

s

t

u

p

n

I

s

t

u

p

t

u

O

e

d

o

M

t

u

p

t

u

O

o

t

t

u

p

n

I

y

t

i

r

a

l

o

P

K

L

C

P

,

K

L

C

K

L

C

P

n

,

K

L

C

n

3

Q

:

0

Q

3

Q

n

:

0

Q

n

0

1

W

O

L

H

G

I

H

l

a

i

t

n

e

r

e

f

f

i

D

o

t

l

a

i

t

n

e

r

e

f

f

i

D

g

n

i

t

r

e

v

n

I

n

o

N

1

0

H

G

I

H

W

O

L

l

a

i

t

n

e

r

e

f

f

i

D

o

t

l

a

i

t

n

e

r

e

f

f

i

D

g

n

i

t

r

e

v

n

I

n

o

N

0

1

E

T

O

N

;

d

e

s

a

i

B

W

O

L

H

G

I

H

l

a

i

t

n

e

r

e

f

f

i

D

o

t

d

e

d

n

E

e

l

g

n

i

S

g

n

i

t

r

e

v

n

I

n

o

N

1

1

E

T

O

N

;

d

e

s

a

i

B

H

G

I

H

W

O

L

l

a

i

t

n

e

r

e

f

f

i

D

o

t

d

e

d

n

E

e

l

g

n

i

S

g

n

i

t

r

e

v

n

I

n

o

N

1

E

T

O

N

;

d

e

s

a

i

B

0

H

G

I

H

W

O

L

l

a

i

t

n

e

r

e

f

f

i

D

o

t

d

e

d

n

E

e

l

g

n

i

S

g

n

i

t

r

e

v

n

I

1

E

T

O

N

;

d

e

s

a

i

B

1

W

O

L

H

G

I

H

l

a

i

t

n

e

r

e

f

f

i

D

o

t

d

e

d

n

E

e

l

g

n

i

S

g

n

i

t

r

e

v

n

I

.

"

s

l

e

v

e

L

d

e

d

n

E

e

l

g

n

i

S

t

p

e

c

c

A

o

t

t

u

p

n

I

l

a

i

t

n

e

r

e

f

f

i

D

e

h

t

g

n

i

r

i

W

"

n

o

i

t

c

e

s

n

o

i

t

a

m

r

o

f

n

I

n

o

i

t

a

c

il

p

p

A

e

h

t

o

t

r

e

f

e

r

e

s

a

e

l

P

:

1

E

T

O

N

Enabled

Disabled

F

IGURE

1 - CLK_EN T

IMING

D

IAGRAM

nCLK, nPCLK

CLK, PCLK

CLK_EN

nQ0:nQ3

Q0:Q3

8543BG

www.icst.com/products/hiperclocks.html

REV. C SEPTEMBER 19, 2002

4

Integrated

Circuit

Systems, Inc.

ICS8543

L

OW

S

KEW

, 1-

TO

-4

D

IFFERENTIAL

-

TO

-LVDS F

ANOUT

B

UFFER

A

BSOLUTE

M

AXIMUM

R

ATINGS

Supply Voltage, V

DDx

4.6V

Inputs, V

I

-0.5V to V

DD

+ 0.5V

Outputs, V

O

-0.5V to V

DD

+ 0.5V

Package Thermal Impedance,

JA

73.2�C/W (0 lfpm)

Storage Temperature, T

STG

-65�C to 150�C

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings

are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in the

DC Characteristics or AC Characteristics is not implied. Exposure to absolute maximum rating conditions for extended peri-

ods may affect product reliability.

T

ABLE

4A. P

OWER

S

UPPLY

DC C

HARACTERISTICS

,

V

DD

= 3.3V�5%, T

A

=0�C

TO

70�C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

e

v

i

t

i

s

o

P

5

3

1

.

3

3

.

3

5

6

4

.

3

V

I

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

r

e

w

o

P

0

5

A

m

T

ABLE

4B. LVCMOS / LVTTL DC C

HARACTERISTICS

,

V

DD

= 3.3V�5%, T

A

=0�C

TO

70�C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

H

I

e

g

a

t

l

o

V

h

g

i

H

t

u

p

n

I

E

O

,

L

E

S

_

K

L

C

,

N

E

_

K

L

C

2

5

6

7

.

3

V

V

L

I

e

g

a

t

l

o

V

w

o

L

t

u

p

n

I

E

O

,

L

E

S

_

K

L

C

,

N

E

_

K

L

C

8

.

0

V

I

H

I

t

n

e

r

r

u

C

h

g

i

H

t

u

p

n

I

E

O

,

N

E

_

K

L

C

5

A

�

L

E

S

_

K

L

C

0

5

1

A

�

I

L

I

t

n

e

r

r

u

C

w

o

L

t

u

p

n

I

E

O

,

N

E

_

K

L

C

0

5

1

-

A

�

L

E

S

_

K

L

C

5

-

A

�

T

ABLE

4C. D

IFFERENTIAL

DC C

HARACTERISTICS

,

V

DD

= 3.3V�5%, T

A

=0�C

TO

70�C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

I

H

I

t

n

e

r

r

u

C

h

g

i

H

t

u

p

n

I

K

L

C

V

D

D

V

=

N

I

V

5

6

4

.

3

=

0

5

1

A

�

K

L

C

n

V

D

D

V

=

N

I

V

5

6

4

.

3

=

5

A

�

I

L

I

t

n

e

r

r

u

C

w

o

L

t

u

p

n

I

K

L

C

V

D

D

V

,

V

5

6

4

.

3

=

N

I

V

0

=

5

-

A

�

K

L

C

n

V

D

D

V

,

V

5

6

4

.

3

=

N

I

V

0

=

0

5

1

-

A

�

V

P

P

e

g

a

t

l

o

V

t

u

p

n

I

k

a

e

P

-

o

t

-

k

a

e

P

5

1

.

0

3

.

1

V

V

R

M

C

2

,

1

E

T

O

N

;

e

g

a

t

l

o

V

t

u

p

n

I

e

d

o

M

n

o

m

m

o

C

5

.

0

V

D

D

5

8

.

0

-

V

V

s

a

d

e

n

i

f

e

d

s

i

e

g

a

t

l

o

v

e

d

o

m

n

o

m

m

o

C

:

1

E

T

O

N

H

I

.

V

s

i

K

L

C

n

,

K

L

C

r

o

f

e

g

a

t

l

o

v

t

u

p

n

i

m

u

m

i

x

a

m

e

h

t

,

s

n

o

i

t

a

c

il

p

p

a

d

e

d

n

e

e

l

g

n

i

s

r

o

F

:

2

E

T

O

N

D

D

.

V

3

.

0

+

8543BG

www.icst.com/products/hiperclocks.html

REV. C SEPTEMBER 19, 2002

5

Integrated

Circuit

Systems, Inc.

ICS8543

L

OW

S

KEW

, 1-

TO

-4

D

IFFERENTIAL

-

TO

-LVDS F

ANOUT

B

UFFER

T

ABLE

5. AC C

HARACTERISTICS

,

V

DD

= 3.3V�5%, T

A

=0�C

TO

70�C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

f

X

A

M

y

c

n

e

u

q

e

r

F

t

u

p

t

u

O

0

0

8

z

H

M

t

D

P

1

E

T

O

N

;

y

a

l

e

D

n

o

i

t

a

g

a

p

o

r

P

f

z

H

M

0

0

8

7

.

1

6

.

2

s

n

t

)

o

(

k

s

4

,

2

E

T

O

N

;

w

e

k

S

t

u

p

t

u

O

0

4

s

p

t

)

p

p

(

k

s

4

,

3

E

T

O

N

;

w

e

k

S

t

r

a

P

-

o

t

-

t

r

a

P

0

0

5

s

p

t

R

e

m

i

T

e

s

i

R

t

u

p

t

u

O

z

H

M

0

5

@

%

0

8

o

t

%

0

2

0

5

1

0

5

3

s

p

t

F

e

m

i

T

ll

a

F

t

u

p

t

u

O

z

H

M

0

5

@

%

0

8

o

t

%

0

2

0

5

1

0

5

3

s

p

c

d

o

e

l

c

y

C

y

t

u

D

t

u

p

t

u

O

5

4

0

5

5

5

%

.

z

H

M

0

0

5

t

a

d

e

r

u

s

a

e

m

s

r

e

t

e

m

a

r

a

p

ll

A

.

t

n

i

o

p

g

n

i

s

s

o

r

c

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

d

e

h

t

o

t

t

n

i

o

p

g

n

i

s

s

o

r

c

t

u

p

n

i

l

a

i

t

n

e

r

e

f

f

i

d

e

h

t

m

o

r

f

d

e

r

u

s

a

e

M

:

1

E

T

O

N

.

s

n

o

i

t

i

d

n

o

c

d

a

o

l

l

a

u

q

e

h

t

i

w

d

n

a

e

g

a

t

l

o

v

y

l

p

p

u

s

e

m

a

s

e

h

t

t

a

s

t

u

p

t

u

o

n

e

e

w

t

e

b

w

e

k

s

s

a

d

e

n

i

f

e

D

:

2

E

T

O

N

.

s

t

n

i

o

p

s

s

o

r

c

l

a

i

t

n

e

r

e

f

f

i

d

t

u

p

t

u

o

e

h

t

d

e

r

u

s

a

e

M

s

e

g

a

t

l

o

v

y

l

p

p

u

s

e

m

a

s

e

h

t

t

a

g

n

i

t

a

r

e

p

o

s

e

c

i

v

e

d

t

n

e

r

e

f

f

i

d

n

o

s

t

u

p

t

u

o

n

e

e

w

t

e

b

w

e

k

s

s

a

d

e

n

i

f

e

D

:

3

E

T

O

N

d

e

r

u

s

a

e

m

e

r

a

s

t

u

p

t

u

o

e

h

t

,

e

c

i

v

e

d

h

c

a

e

n

o

s

t

u

p

n

i

f

o

e

p

y

t

e

m

a

s

e

h

t

g

n

i

s

U

.

s

n

o

i

t

i

d

n

o

c

d

a

o

l

l

a

u

q

e

h

t

i

w

d

n

a

.

s

t

n

i

o

p

s

s

o

r

c

l

a

i

t

n

e

r

e

f

f

i

d

e

h

t

t

a

.

5

6

d

r

a

d

n

a

t

S

C

E

D

E

J

h

t

i

w

e

c

n

a

d

r

o

c

c

a

n

i

d

e

n

i

f

e

d

s

i

r

e

t

e

m

a

r

a

p

s

i

h

T

:

4

E

T

O

N

T

ABLE

4D. LVPECL DC C

HARACTERISTICS

,

V

DD

= 3.3V�5%, T

A

=0�C

TO

70�C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

I

H

I

t

n

e

r

r

u

C

h

g

i

H

t

u

p

n

I

K

L

C

P

V

D

D

V

=

N

I

V

5

6

4

.

3

=

0

5

1

A

�

K

L

C

P

n

V

D

D

V

=

N

I

V

5

6

4

.

3

=

5

A

�

I

L

I

t

n

e

r

r

u

C

w

o

L

t

u

p

n

I

K

L

C

P

V

D

D

V

,

V

5

6

4

.

3

=

N

I

V

0

=

5

-

A

�

K

L

C

P

n

V

D

D

V

,

V

5

6

4

.

3

=

N

I

V

0

=

0

5

1

-

A

�

V

P

P

e

g

a

t

l

o

V

t

u

p

n

I

k

a

e

P

-

o

t

-

k

a

e

P

3

.

0

1

V

V

R

M

C

2

,

1

E

T

O

N

;

e

g

a

t

l

o

V

t

u

p

n

I

e

d

o

M

n

o

m

m

o

C

5

.

1

V

D

D

V

V

s

a

d

e

n

i

f

e

d

s

i

e

g

a

t

l

o

v

e

d

o

m

n

o

m

m

o

C

:

1

E

T

O

N

H

I

.

V

s

i

K

L

C

P

n

d

n

a

K

L

C

P

r

o

f

e

g

a

t

l

o

v

t

u

p

n

i

m

u

m

i

x

a

m

e

h

t

,

s

n

o

i

t

a

c

il

p

p

a

d

e

d

n

e

e

l

g

n

i

s

r

o

F

:

2

E

T

O

N

D

D

.

V

3

.

0

+

T

ABLE

4E. LVDS DC C

HARACTERISTICS

,

V

DD

= 3.3V�5%, T

A

=0�C

TO

70�C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

D

O

e

g

a

t

l

o

V

t

u

p

t

u

O

l

a

i

t

n

e

r

e

f

f

i

D

0

0

2

0

8

2

0

6

3

V

m

V

D

O

e

g

n

a

h

C

e

d

u

t

i

n

g

a

M

D

O

V

0

0

4

V

m

V

S

O

e

g

a

t

l

o

V

t

e

s

f

f

O

5

2

1

.

1

5

2

.

1

5

7

3

.

1

V

V

S

O

e

g

n

a

h

C

e

d

u

t

i

n

g

a

M

S

O

V

5

5

2

V

m

I

Z

O

t

n

e

r

r

u

C

e

g

a

k

a

e

L

e

c

n

a

d

e

p

m

I

h

g

i

H

0

1

-

0

1

+

A

�

I

F

F

O

e

g

a

k

a

e

L

f

f

O

r

e

w

o

P

0

2

-

1

�

0

2

+

A

�

I

D

S

O

t

n

e

r

r

u

C

t

i

u

c

r

i

C

t

r

o

h

S

t

u

p

t

u

O

l

a

i

t

n

e

r

e

f

f

i

D

5

.

3

-

5

-

A

m

I

S

O

t

n

e

r

r

u

C

t

i

u

c

r

i

C

t

r

o

h

S

t

u

p

t

u

O

5

.

3

-

5

-

A

m

V

H

O

h

g

i

H

e

g

a

t

l

o

V

t

u

p

t

u

O

4

3

.

1

6

.

1

V

V

L

O

w

o

L

e

g

a

t

l

o

V

t

u

p

t

u

O

9

.

0

6

0

.

1

V

8543BG

www.icst.com/products/hiperclocks.html

REV. C SEPTEMBER 19, 2002

6

Integrated

Circuit

Systems, Inc.

ICS8543

L

OW

S

KEW

, 1-

TO

-4

D

IFFERENTIAL

-

TO

-LVDS F

ANOUT

B

UFFER

P

ARAMETER

M

EASUREMENT

I

NFORMATION

3.3V O

UTPUT

L

OAD

T

EST

C

IRCUIT

V

DD

GND

SCOPE

Qx

nQx

LVDS

3.3V�5% POWER SUPPLY

+

-

Float GND

O

UTPUT

S

KEW

2.1V � -0.135V

-1.2V

tsk(o)

nQx

Qx

nQy

Qy

8543BG

www.icst.com/products/hiperclocks.html

REV. C SEPTEMBER 19, 2002

7

Integrated

Circuit

Systems, Inc.

ICS8543

L

OW

S

KEW

, 1-

TO

-4

D

IFFERENTIAL

-

TO

-LVDS F

ANOUT

B

UFFER

P

ART

-

TO

-P

ART

S

KEW

nQx

Qx

nQy

Qy

PART 1

PART 2

tsk(pp)

O

UTPUT

R

ISE

AND

F

ALL

T

IME

Clock Outputs

20%

80%

80%

20%

t

R

t

F

V

S W I N G

P

ROPAGATION

D

ELAY

t

PD

nCLK, nPCLK

CLK, PCLK

nQ0:nQ3

Q0:Q3

odc & t

P

ERIOD

Pulse Width

t

PERIOD

t

PW

t

PERIOD

odc =

nQ0:nQ3

Q0:Q3

8543BG

www.icst.com/products/hiperclocks.html

REV. C SEPTEMBER 19, 2002

8

Integrated

Circuit

Systems, Inc.

ICS8543

L

OW

S

KEW

, 1-

TO

-4

D

IFFERENTIAL

-

TO

-LVDS F

ANOUT

B

UFFER

V

OS

/

D

VOS

S

ETUP

out

out

LVDS

DC Input

V

OS

/

V

OS

V

DD

D

IFFERENTIAL

O

UTPUT

L

EVEL

V

OS

Cross Points

V

OD

nQx

Qx

V

DD

GND

D

IFFERENTIAL

I

NPUT

L

EVEL

V

CMR

Cross Points

V

PP

nCLK, nPCLK

CLK, PCLK

GND

V

DD

8543BG

www.icst.com/products/hiperclocks.html

REV. C SEPTEMBER 19, 2002

9

Integrated

Circuit

Systems, Inc.

ICS8543

L

OW

S

KEW

, 1-

TO

-4

D

IFFERENTIAL

-

TO

-LVDS F

ANOUT

B

UFFER

V

OD

/

D

VOD

S

ETUP

out

out

LVDS

DC Input

V

OD

/

V

OD

V

DD

100

I

OSD

S

ETUP

out

out

LVDS

DC Input

I

OSD

V

DD

I

OS

S

ETUP

out

LVDS

DC Input

I

OS

V

DD

8543BG

www.icst.com/products/hiperclocks.html

REV. C SEPTEMBER 19, 2002

10

Integrated

Circuit

Systems, Inc.

ICS8543

L

OW

S

KEW

, 1-

TO

-4

D

IFFERENTIAL

-

TO

-LVDS F

ANOUT

B

UFFER

I

OZ

S

ETUP

out

out

LVDS

DC Input

3.3V�5% POWER SUPPLY

Float GND

+

_

I

OZ

I

OZ

I

OFF

S

ETUP

LVDS

I

OFF

V

DD

8543BG

www.icst.com/products/hiperclocks.html

REV. C SEPTEMBER 19, 2002

11

Integrated

Circuit

Systems, Inc.

ICS8543

L

OW

S

KEW

, 1-

TO

-4

D

IFFERENTIAL

-

TO

-LVDS F

ANOUT

B

UFFER

A

PPLICATION

I

NFORMATION

Figure 2 shows how the differential input can be wired to accept single ended levels. The reference voltage V_REF = V

DD

/2 is

generated by the bias resistors R1, R2 and C1. This bias circuit should be located as close as possible to the input pin. The ratio of

R1 and R2 might need to be adjusted to position the V_REF in the center of the input voltage swing. For example, if the input clock

swing is only 2.5V and V

DD

= 3.3V, V_REF should be 1.25V and R2/R1 = 0.609.

F

IGURE

2 - S

INGLE

E

NDED

S

IGNAL

D

RIVING

D

IFFERENTIAL

I

NPUT

R2

1K

V

DD

CLK_IN

+

-

R1

1K

C1

0.1uF

V_REF

W

IRING

THE

D

IFFERENTIAL

I

NPUT

TO

A

CCEPT

S

INGLE

E

NDED

L

EVELS

8543BG

www.icst.com/products/hiperclocks.html

REV. C SEPTEMBER 19, 2002

12

Integrated

Circuit

Systems, Inc.

ICS8543

L

OW

S

KEW

, 1-

TO

-4

D

IFFERENTIAL

-

TO

-LVDS F

ANOUT

B

UFFER

R

ELIABILITY

I

NFORMATION

T

RANSISTOR

C

OUNT

The transistor count for ICS8543 is: 636

T

ABLE

6.

JA

VS

. A

IR

F

LOW

T

ABLE

q

JA

by Velocity (Linear Feet per Minute)

0

200

500

Single-Layer PCB, JEDEC Standard Test Boards

114.5�C/W

98.0�C/W

88.0�C/W

Multi-Layer PCB, JEDEC Standard Test Boards

73.2�C/W

66.6�C/W

63.5�C/W

NOTE: Most modern PCB designs use multi-layered boards. The data in the second row pertains to most designs.

8543BG

www.icst.com/products/hiperclocks.html

REV. C SEPTEMBER 19, 2002

13

Integrated

Circuit

Systems, Inc.

ICS8543

L

OW

S

KEW

, 1-

TO

-4

D

IFFERENTIAL

-

TO

-LVDS F

ANOUT

B

UFFER

P

ACKAGE

O

UTLINE

- G S

UFFIX

T

ABLE

7. P

ACKAGE

D

IMENSIONS

Reference Document: JEDEC Publication 95, MO-153

l

o

b

m

y

S

s

r

e

t

e

m

i

l

l

i

M

m

u

m

i

n

i

M

m

u

m

i

x

a

M

N

0

2

A

-

-

0

2

.

1

1

A

5

0

.

0

5

1

.

0

2

A

0

8

.

0

5

0

.

1

b

9

1

.

0

0

3

.

0

c

9

0

.

0

0

2

.

0

D

0

4

.

6

0

6

.

6

E

C

I

S

A

B

0

4

.

6

1

E

0

3

.

4

0

5

.

4

e

C

I

S

A

B

5

6

.

0

L

5

4

.

0

5

7

.

0

�

0

�

8

a

a

a

-

-

0

1

.

0

8543BG

www.icst.com/products/hiperclocks.html

REV. C SEPTEMBER 19, 2002

14

Integrated

Circuit

Systems, Inc.

ICS8543

L

OW

S

KEW

, 1-

TO

-4

D

IFFERENTIAL

-

TO

-LVDS F

ANOUT

B

UFFER

T

ABLE

8. O

RDERING

I

NFORMATION

While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems, Incorporated (ICS) assumes no responsibility for either its use

or for infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use

in normal commercial applications. Any other applications such as those requiring extended temperature range, high reliability, or other extraordinary environmental requirements are

not recommended without additional processing by ICS. ICS reserves the right to change any circuitry or specifications without notice. ICS does not authorize or warrant any ICS

product for use in life support devices or critical medical instruments.

r

e

b

m

u

N

r

e

d

r

O

/

t

r

a

P

g

n

i

k

r

a

M

e

g

a

k

c

a

P

t

n

u

o

C

e

r

u

t

a

r

e

p

m

e

T

G

B

3

4

5

8

S

C

I

G

B

3

4

5

8

S

C

I

P

O

S

S

T

d

a

e

l

0

2

e

b

u

t

r

e

p

2

7

C

�

0

7

o

t

C

�

0

T

G

B

3

4

5

8

S

C

I

G

B

3

4

5

8

S

C

I

l

e

e

R

d

n

a

e

p

a

T

n

o

P

O

S

S

T

d

a

e

l

0

2

0

0

5

2

C

�

0

7

o

t

C

�

0

8543BG

www.icst.com/products/hiperclocks.html

REV. C SEPTEMBER 19, 2002

15

Integrated

Circuit

Systems, Inc.

ICS8543

L

OW

S

KEW

, 1-

TO

-4

D

IFFERENTIAL

-

TO

-LVDS F

ANOUT

B

UFFER

T

E

E

H

S

Y

R

O

T

S

I

H

N

O

I

S

I

V

E

R

v

e

R

e

l

b

a

T

e

g

a

P

e

g

n

a

h

C

f

o

n

o

i

t

p

i

r

c

s

e

D

e

t

a

D

A

E

4

5

V

e

h

t

n

I

L

O

m

u

m

i

x

a

m

e

h

t

m

o

r

f

n

m

u

l

o

c

l

a

c

i

p

y

T

e

h

t

o

t

d

e

v

o

m

n

e

e

b

s

a

h

6

0

.

1

,

w

o

r

.

n

m

u

l

o

c

1

0

/

8

1

/

9

A

3

.

m

a

r

g

a

i

D

g

n

i

m

i

T

N

E

_

K

L

C

,

1

e

r

u

g

i

F

d

e

t

a

d

p

U

1

0

/

7

1

/

0

1

A

3

.

m

a

r

g

a

i

D

g

n

i

m

i

T

N

E

_

K

L

C

,

1

e

r

u

g

i

F

d

e

t

a

d

p

U

1

0

/

2

/

1

1

A

1

0

1

-

6

.

L

C

E

P

V

L

f

o

d

a

e

t

s

n

i

s

l

e

v

e

l

S

D

V

L

V

3

.

3

d

a

e

r

o

t

6

t

e

ll

u

B

,

n

o

i

t

c

e

s

s

e

r

u

t

a

e

F

.

s

e

r

u

g

i

f

n

o

i

t

a

m

r

o

f

n

I

t

n

e

m

r

u

s

a

e

M

r

e

t

e

m

a

r

a

P

d

e

t

a

d

U

2

0

/

6

/

5

B

5

5

.

z

H

M

0

0

8

o

t

z

H

M

0

5

6

m

o

r

f

y

c

n

e

u

q

e

r

F

t

u

p

t

u

O

d

e

s

i

v

e

r

-

e

l

b

a

t

s

c

i

t

s

i

r

e

t

c

a

r

a

h

C

C

A

2

0

/

5

/

6

C

E

4

1

5

f

o

s

t

n

e

m

e

r

i

u

q

e

r

e

h

t

d

e

e

c

x

e

r

o

t

e

e

m

o

t

d

e

n

g

i

s

e

D

"

t

e

ll

u

b

d

e

t

e

l

e

d

-

s

e

r

u

t

a

e

F

.

"

4

4

6

-

A

I

E

/

A

I

T

I

S

N

A

V

d

e

g

n

a

h

c

-

e

l

b

a

T

S

D

V

L

D

O

.

V

m

0

8

2

o

t

V

m

0

5

3

m

o

r

f

e

u

l

a

v

l

a

c

i

p

y

t

2

0

/

9

1

/

9