| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 8701CY | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Document Outline

- General Description

- Features

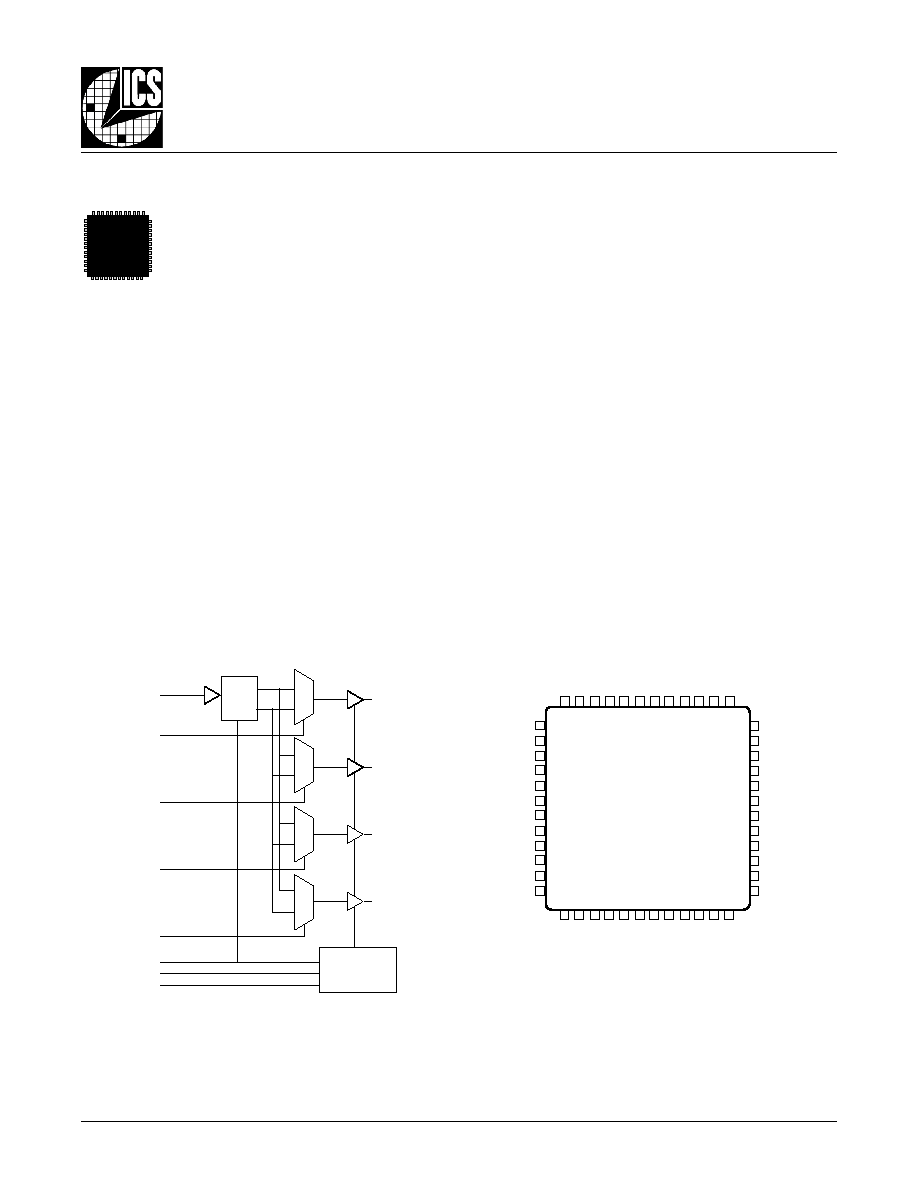

- Block Diagram

- Pin Assignment

- Pin Descriptions

- Pin Characteristics

- Function Table

- Absolute Maximum Ratings

- Power Supply 3.3V DC Characteristics

- LVCMOS 3.3V DC Characteristics

- 3.3V AC Characteristics

- Power Supply 3.3V/2.5V DC Characteristics

- LVCMOS 3.3V/2.5V DC Characteristics

- 3.3V/2.5V AC Characteristics

- Parameter Measurement Information

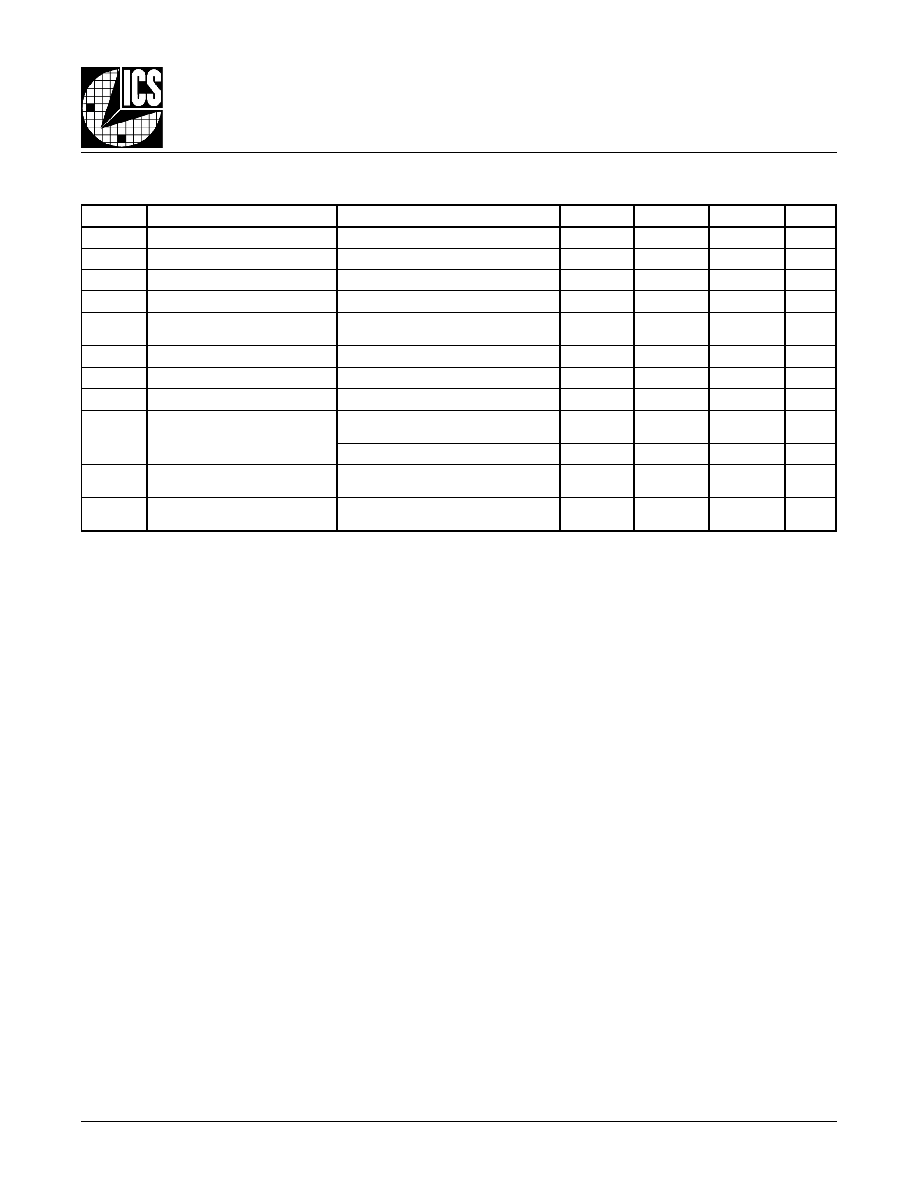

- 3.3V Output Load Test Circuit Diagram

- 3.3V/2.5V Output Load Test Circuit Diagram

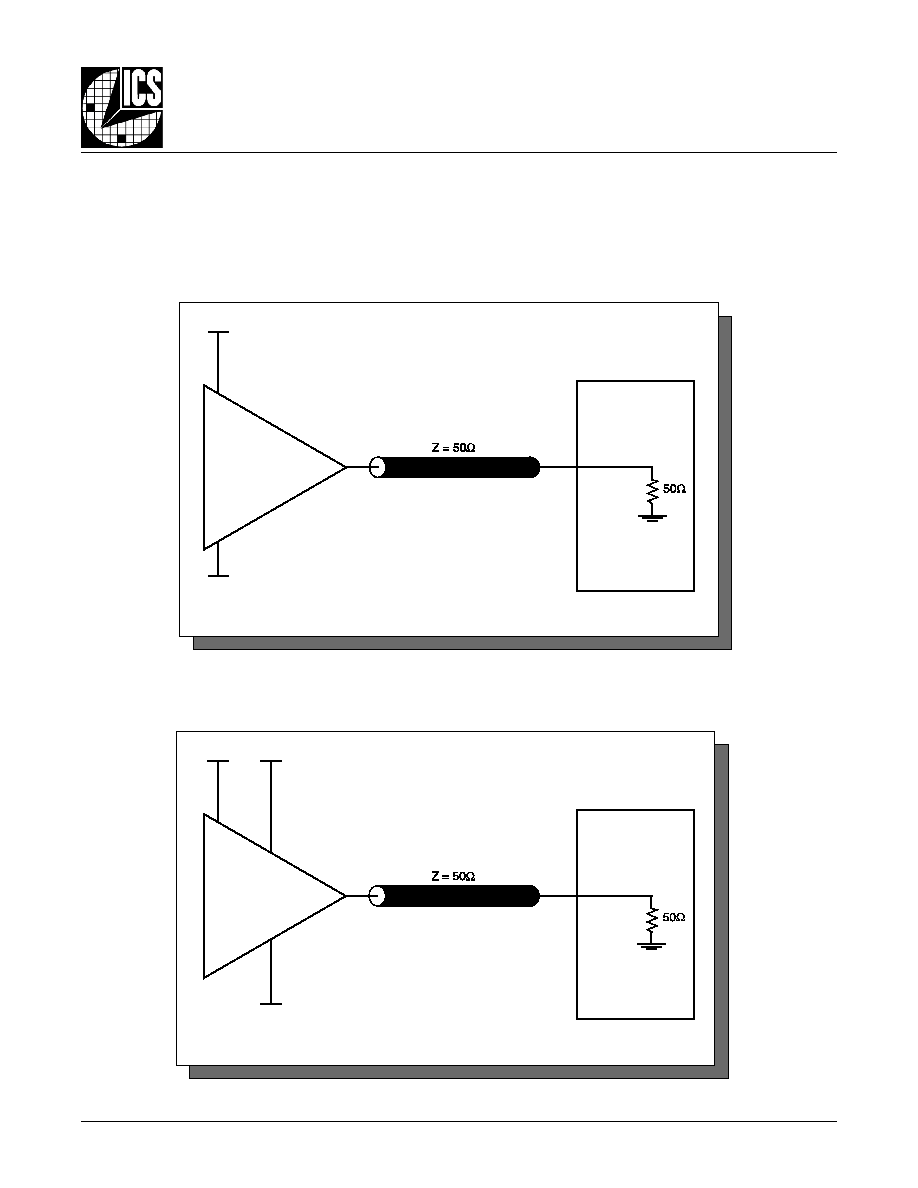

- Output Skew Diagram

- Part-to-Part Skew Diagram

- Output Rise/Fall Time Diagram

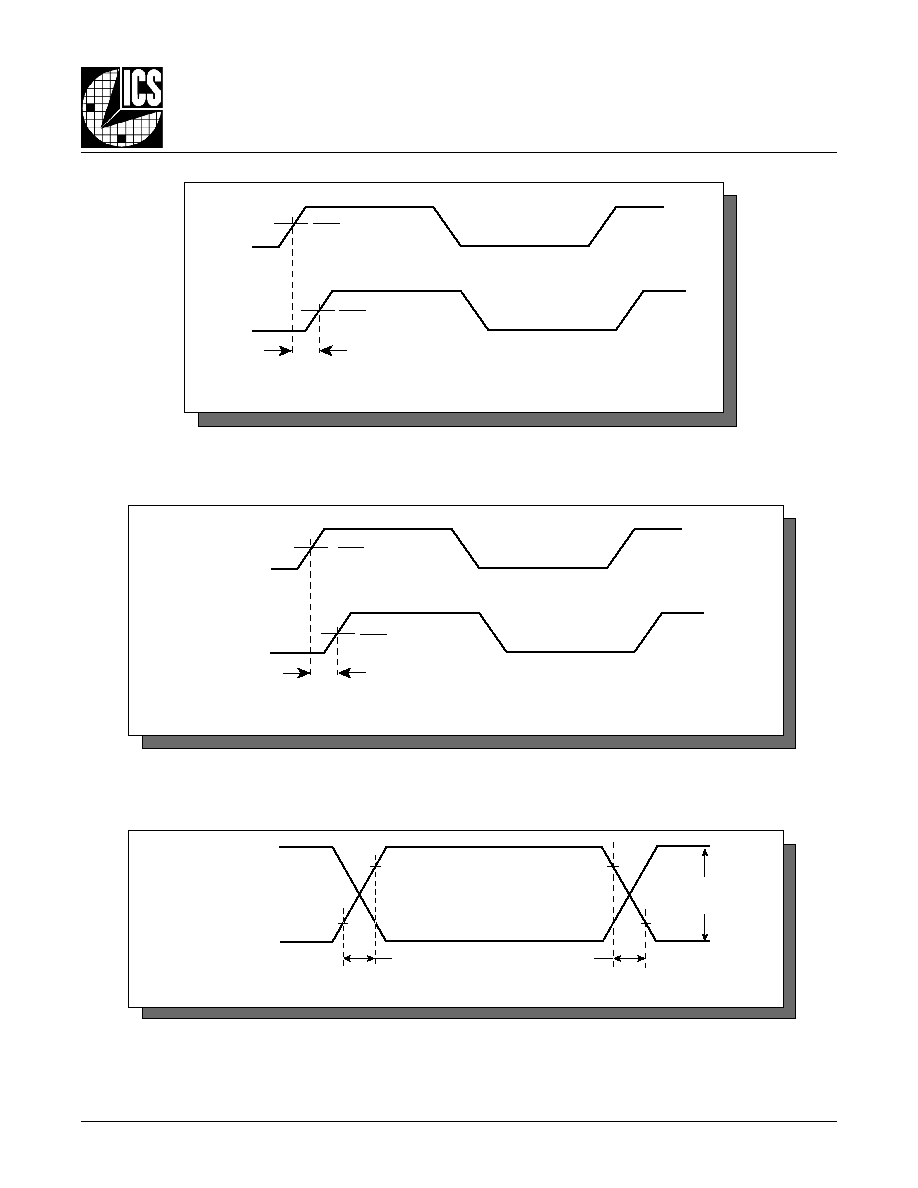

- Propagation Delay Diagram

- odc & tPeriod Diagram

- Power Considerations

- Driver Termination

- Reliability Information

- Transistor Count

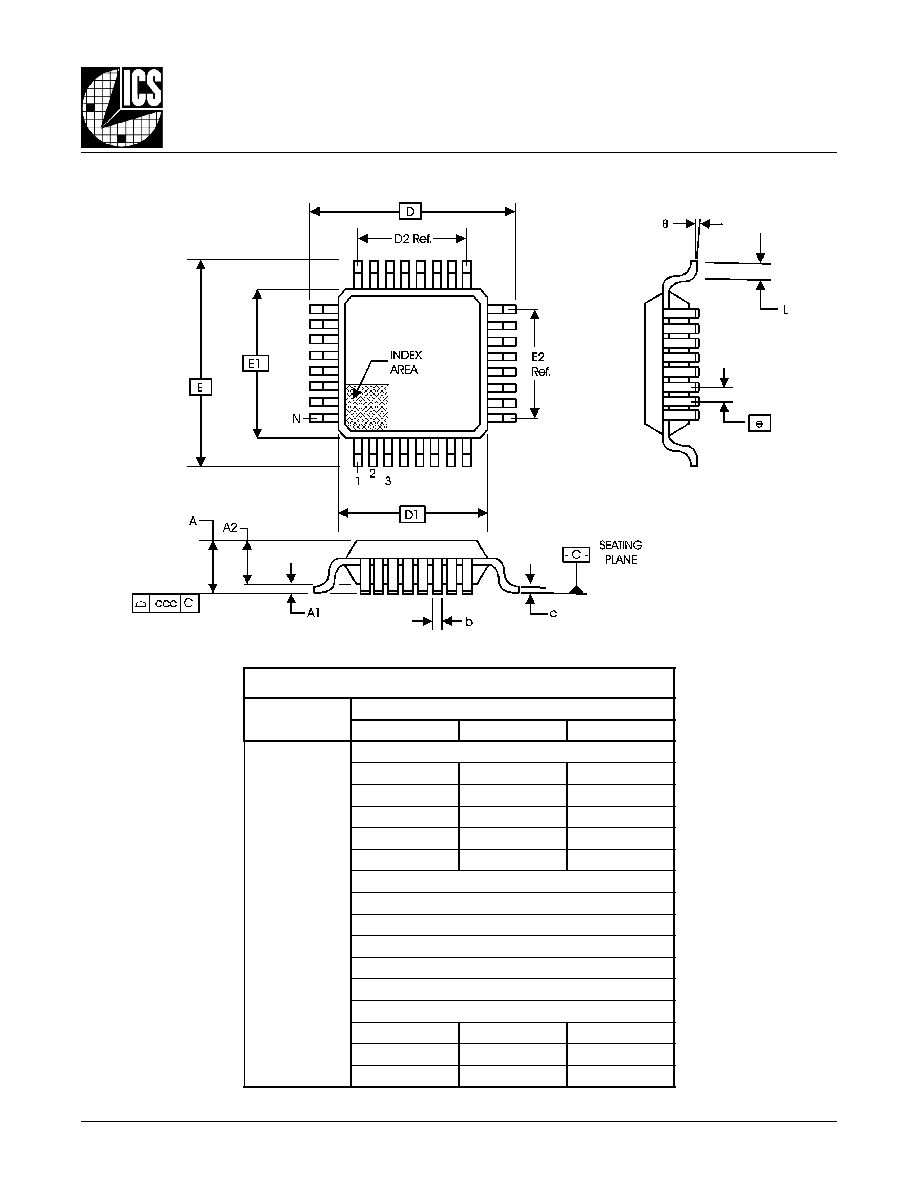

- Package Outline

- Package Dimensions

- Ordering Information

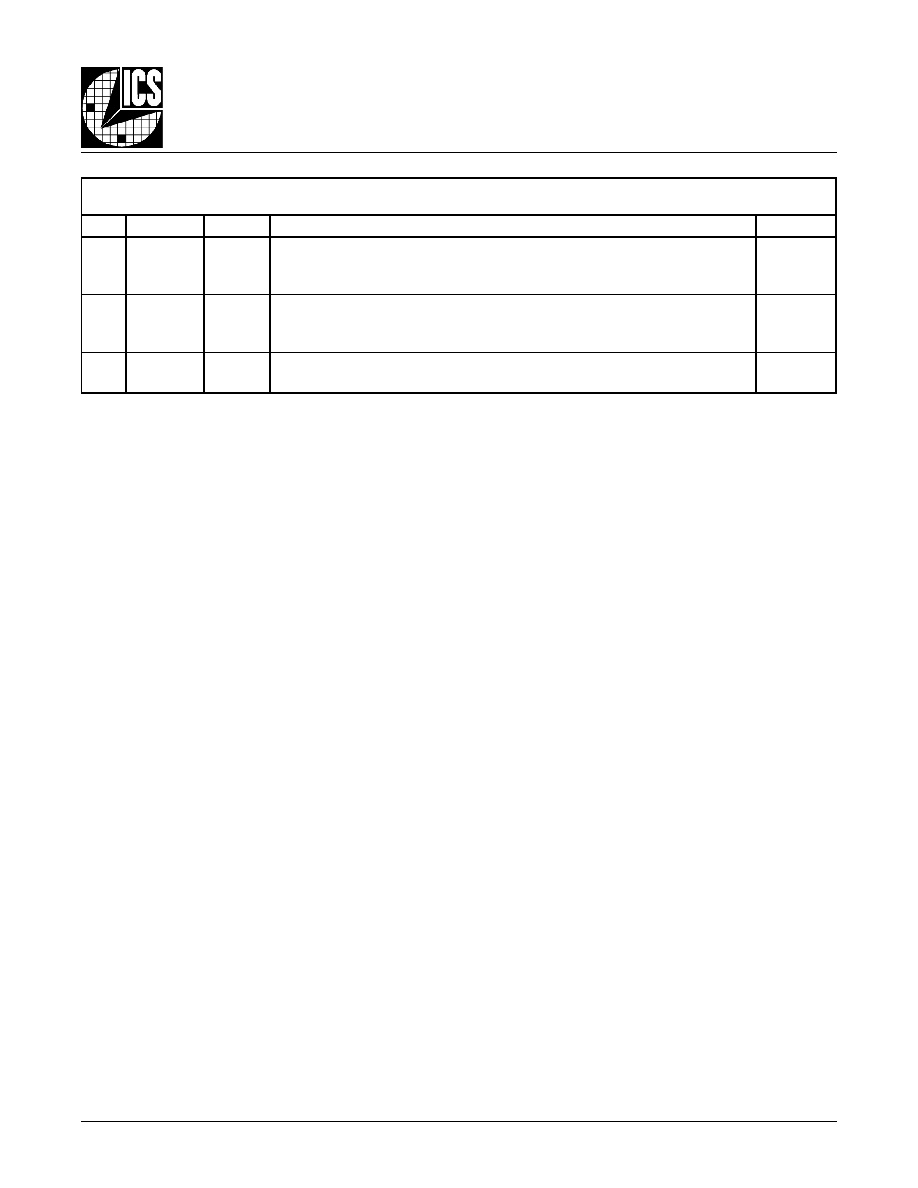

- Revision History Sheet

8701CY

www.icst.com/products/hiperclocks.html

REV. C AUGUST 19, 2002

1

Integrated

Circuit

Systems, Inc.

ICS8701

L

OW

S

KEW

,

˜

1,

˜

2

LVCMOS C

LOCK

G

ENERATOR

G

ENERAL

D

ESCRIPTION

The ICS8701 is a low skew, ˜1, ˜2 LVCMOS

C l o c k G e n e r a t o r a n d a m e m b e r o f t h e

HiPerClockSTM family of High Performance Clock

Solutions from ICS. The low impedance LVCMOS

outputs are designed to drive 50

series or

parallel terminated transmission lines. The effective fanout can

be increased from 20 to 40 by utilizing the ability of the out-

puts to drive two series terminated lines.

The divide select inputs, DIV_SELx, control the output fre-

quency of each bank. The outputs can be utilized in the ˜1,

˜2 or a combination of ˜1 and ˜2 modes. The bank enable

inputs, BANK_EN0:1, support enabling and disabling each

bank of outputs individually. The master reset input, nMR/

OE, resets the internal frequency dividers and also con-

trols the active and high impedance states of all outputs.

The ICS8701 is characterized at 3.3V and mixed 3.3V input

supply, and 2.5V output supply operating modes. Guaranteed

bank, output and part-to-part skew characteristics make the

ICS8701 ideal for those clock distribution applications de-

manding well defined performance and repeatability.

F

EATURES

∑ 20 LVCMOS outputs, 7

typical output impedance

∑ 1 LVCMOS clock input

∑ Maximum output frequency: 250MHz

∑ Bank enable logic allows unused banks to be disabled

in reduced fanout applications

∑ Output skew: 250ps (maximum)

∑ Part-to-part skew: 600ps (maximum)

∑ Bank skew: 200ps (maximum)

∑ Multiple frequency skew: 300ps (maximum)

∑ 3.3V or mixed 3.3V input, 2.5V output operating

supply modes

∑ 0∞C to 70∞C ambient operating temperature

∑ Other divide values available on request

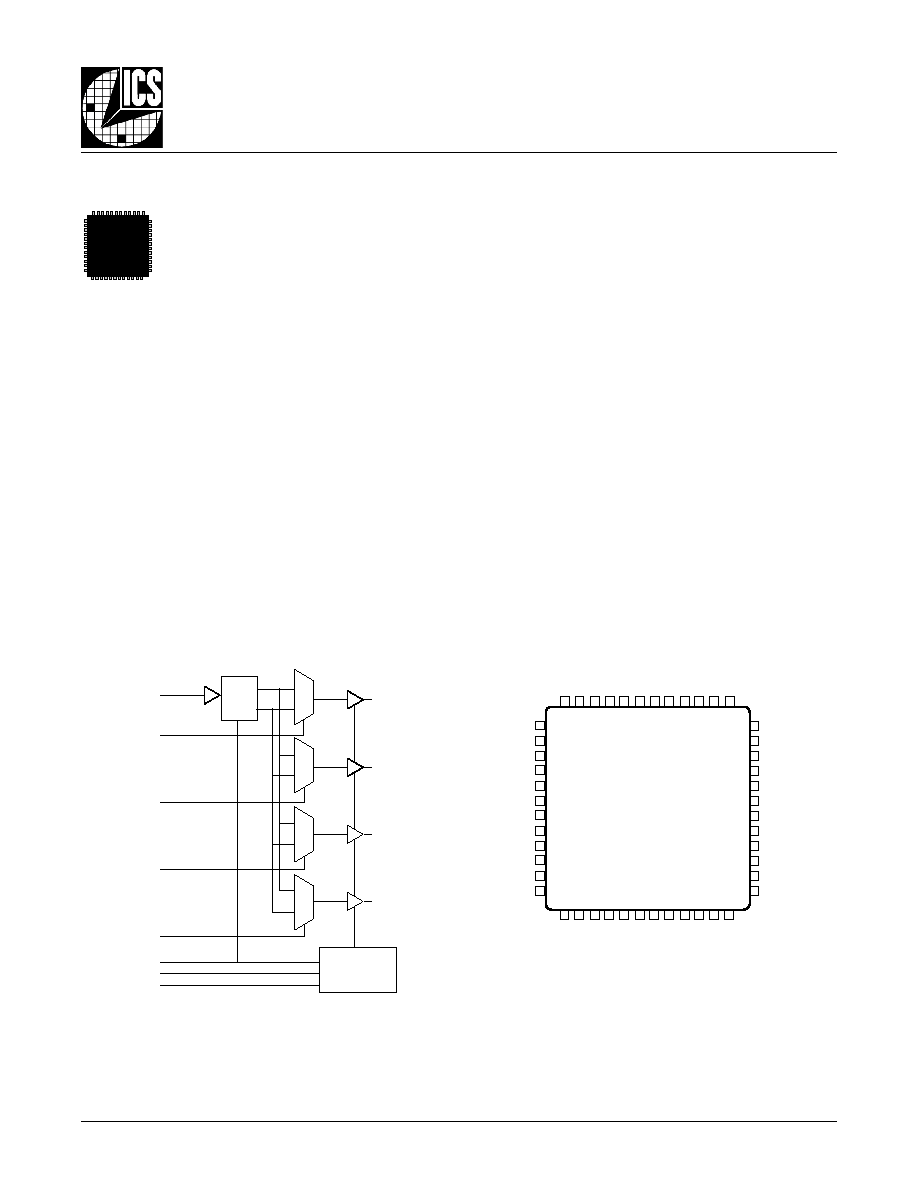

B

LOCK

D

IAGRAM

P

IN

A

SSIGNMENT

DIV_SELA

DIV_SELB

DIV_SELC

DIV_SELD

nMR/OE

BANK_EN0

BANK_EN1

QA0:QA4

QB0:QB4

QC0:QC4

QD0:QD4

CLK

48 47 46 45 44 43 42 41 40 39 38 37

13 14 15 16 17 18 19 20 21 22 23 24

1

2

3

4

5

6

7

8

9

10

11

12

36

35

34

33

32

31

30

29

28

27

26

25

QC3

V

DDO

QC4

QD0

V

DDO

QD1

GND

QD2

GND

QD3

V

DDO

QD4

QB1

V

DDO

QB0

QA4

V

DDO

QA3

GND

QA2

GND

QA1

V

DDO

QA0

DIV_SELA

DIV_SELB

CLK

GND

V

DD

BANK_EN0

GND

BANK_EN1

V

DD

nMR/OE

DIV_SELC

DIV_SELD

GND

QB2

GND

QB3

V

DDO

QB4

QC0

V

DDO

QC1

GND

QC2

GND

48-Pin LQFP

7mm x 7mm x 1.4mm

Y Package

Top View

ICS8701

HiPerClockSTM

,&6

1

0

˜

1

˜

2

1

0

1

0

1

0

Bank Enable

Logic

8701CY

www.icst.com/products/hiperclocks.html

REV. C AUGUST 19, 2002

2

Integrated

Circuit

Systems, Inc.

ICS8701

L

OW

S

KEW

,

˜

1,

˜

2

LVCMOS C

LOCK

G

ENERATOR

T

ABLE

1. P

IN

D

ESCRIPTIONS

r

e

b

m

u

N

e

m

a

N

e

p

y

T

n

o

i

t

p

i

r

c

s

e

D

,

1

1

,

5

,

2

,

5

3

,

2

3

,

6

2

4

4

,

1

4

V

O

D

D

r

e

w

o

P

.

s

n

i

p

y

l

p

p

u

s

t

u

p

t

u

O

,

1

2

,

8

1

,

9

,

7

,

7

3

,

0

3

,

8

2

8

4

,

6

4

,

9

3

D

N

G

r

e

w

o

P

.

d

n

u

o

r

g

y

l

p

p

u

s

r

e

w

o

P

0

2

,

6

1

V

D

D

r

e

w

o

P

.

s

n

i

p

y

l

p

p

u

s

e

v

i

t

i

s

o

P

,

9

2

,

7

2

,

5

2

3

3

,

1

3

,

2

A

Q

,

1

A

Q

,

0

A

Q

4

A

Q

,

3

A

Q

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

s

t

u

p

t

u

o

A

k

n

a

B

7

.

e

c

n

a

d

e

p

m

i

t

u

p

t

u

o

l

a

c

i

p

y

t

,

8

3

,

6

3

,

4

3

2

4

,

0

4

,

2

B

Q

,

1

B

Q

,

0

B

Q

4

B

Q

,

3

B

Q

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

s

t

u

p

t

u

o

B

k

n

a

B

7

.

e

c

n

a

d

e

p

m

i

t

u

p

t

u

o

l

a

c

i

p

y

t

,

7

4

,

5

4

,

3

4

3

,

1

,

2

C

Q

,

1

C

Q

,

0

C

Q

4

C

Q

,

3

C

Q

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

s

t

u

p

t

u

o

C

k

n

a

B

7

.

e

c

n

a

d

e

p

m

i

t

u

p

t

u

o

l

a

c

i

p

y

t

,

8

,

6

,

4

2

1

,

0

1

,

2

D

Q

,

1

D

Q

,

0

D

Q

4

D

Q

,

3

D

Q

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

s

t

u

p

t

u

o

D

k

n

a

B

7

.

e

c

n

a

d

e

p

m

i

t

u

p

t

u

o

l

a

c

i

p

y

t

2

2

K

L

C

t

u

p

n

I

n

w

o

d

ll

u

P

.

t

u

p

n

i

k

c

o

l

c

L

T

T

V

L

/

S

O

M

C

V

L

3

1

D

L

E

S

_

V

I

D

t

u

p

n

I

p

u

ll

u

P

.

s

t

u

p

t

u

o

D

k

n

a

B

r

o

f

n

o

i

s

i

v

i

d

y

c

n

e

u

q

e

r

f

s

l

o

r

t

n

o

C

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

4

1

C

L

E

S

_

V

I

D

t

u

p

n

I

p

u

ll

u

P

.

s

t

u

p

t

u

o

C

k

n

a

B

r

o

f

n

o

i

s

i

v

i

d

y

c

n

e

u

q

e

r

f

s

l

o

r

t

n

o

C

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

3

2

B

L

E

S

_

V

I

D

t

u

p

n

I

p

u

ll

u

P

.

s

t

u

p

t

u

o

B

k

n

a

B

r

o

f

n

o

i

s

i

v

i

d

y

c

n

e

u

q

e

r

f

s

l

o

r

t

n

o

C

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

4

2

A

L

E

S

_

V

I

D

t

u

p

n

I

p

u

ll

u

P

.

s

t

u

p

t

u

o

A

k

n

a

B

r

o

f

n

o

i

s

i

v

i

d

y

c

n

e

u

q

e

r

f

s

l

o

r

t

n

o

C

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

9

1

,

7

1

,

1

N

E

_

K

N

A

B

0

N

E

_

K

N

A

B

t

u

p

n

I

p

u

ll

u

P

.

s

k

n

a

b

y

b

s

t

u

p

t

u

o

s

e

l

b

a

s

i

d

d

n

a

s

e

l

b

a

n

E

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

5

1

E

O

/

R

M

n

t

u

p

n

I

p

u

ll

u

P

e

r

a

s

r

e

v

i

r

d

t

u

p

t

u

o

,

H

G

I

H

n

e

h

W

.

e

l

b

a

n

e

t

u

p

t

u

o

d

n

a

t

e

s

e

R

r

e

t

s

a

M

.

t

e

s

e

r

e

r

a

s

r

e

d

i

v

i

d

d

n

a

Z

i

H

n

i

e

r

a

s

r

e

v

i

r

d

t

u

p

t

u

o

,

W

O

L

e

h

W

.

d

e

l

b

a

n

e

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

:

E

T

O

N

p

u

ll

u

P

d

n

a

n

w

o

d

ll

u

P

.

s

e

u

l

a

v

l

a

c

i

p

y

t

r

o

f

,

s

c

i

t

s

i

r

e

t

c

a

r

a

h

C

n

i

P

,

2

e

l

b

a

T

e

e

S

.

s

r

o

t

s

i

s

e

r

t

u

p

n

i

l

a

n

r

e

t

n

i

o

t

r

e

f

e

r

8701CY

www.icst.com/products/hiperclocks.html

REV. C AUGUST 19, 2002

3

Integrated

Circuit

Systems, Inc.

ICS8701

L

OW

S

KEW

,

˜

1,

˜

2

LVCMOS C

LOCK

G

ENERATOR

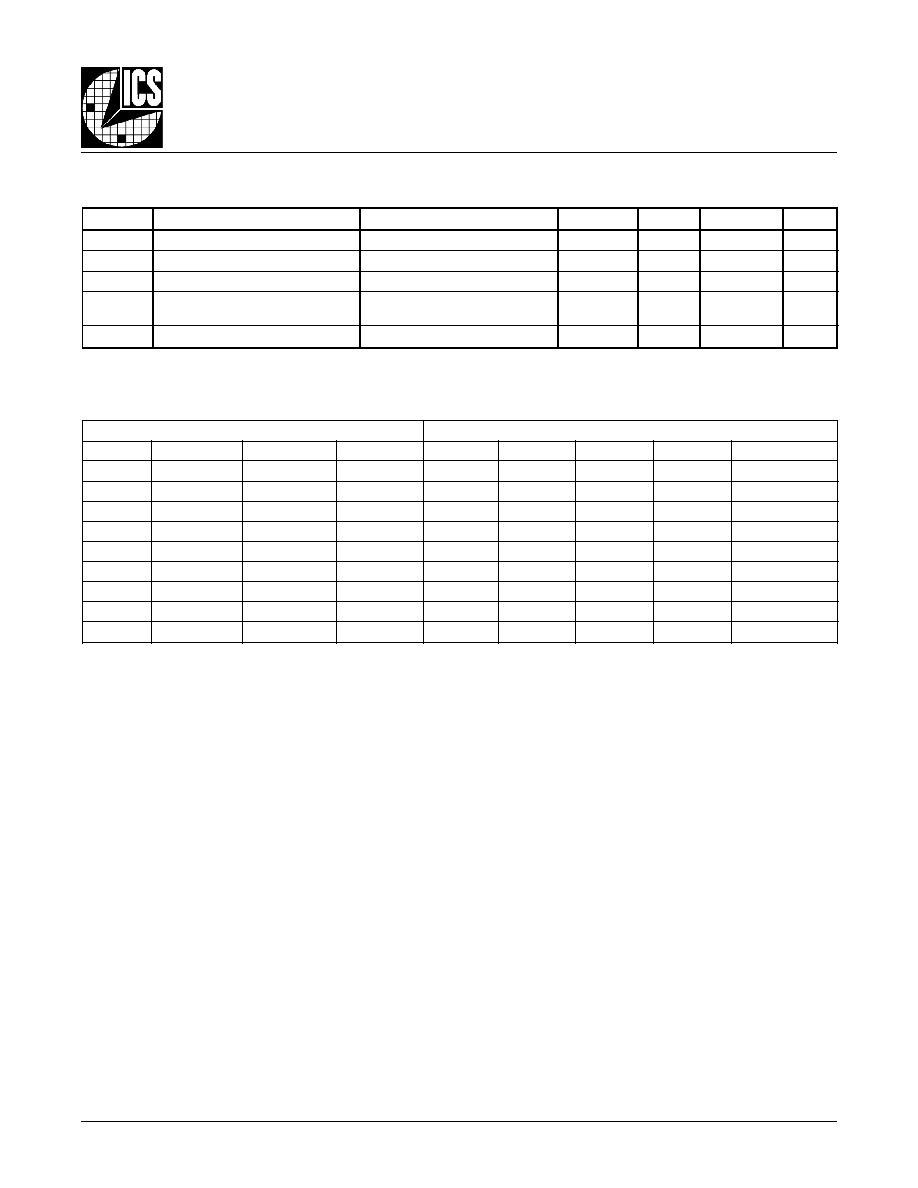

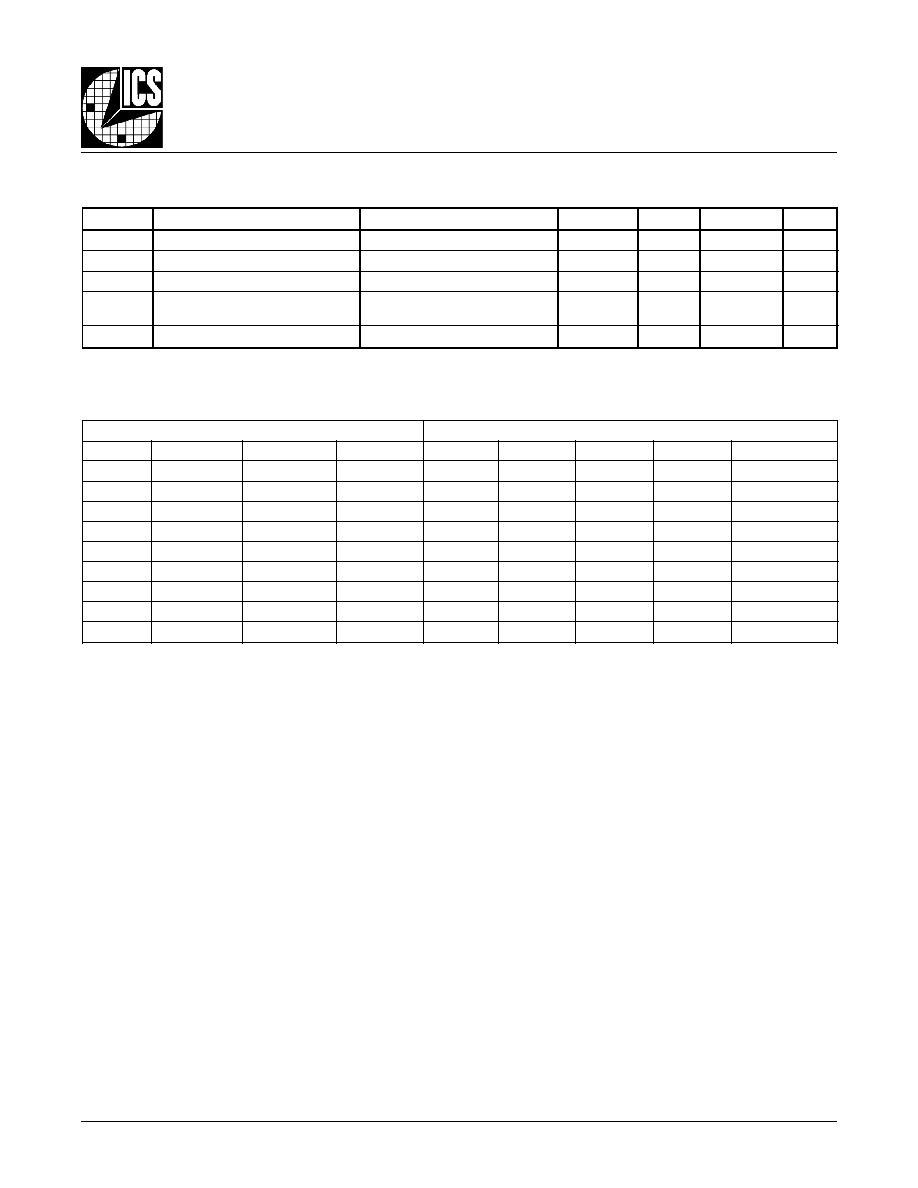

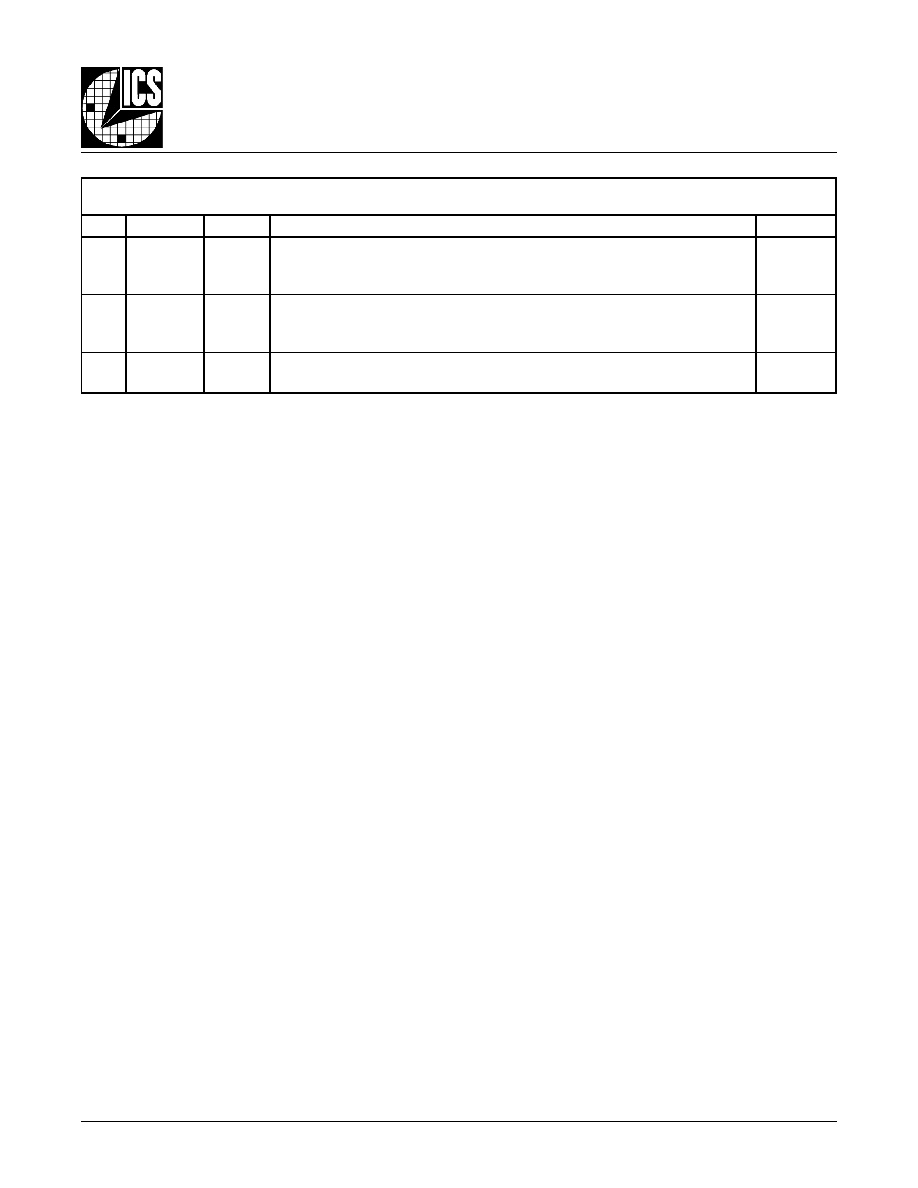

T

ABLE

2. P

IN

C

HARACTERISTICS

T

ABLE

3. F

UNCTION

T

ABLE

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

C

N

I

e

c

n

a

t

i

c

a

p

a

C

t

u

p

n

I

4

F

p

R

P

U

L

L

U

P

r

o

t

s

i

s

e

R

p

u

ll

u

P

t

u

p

n

I

1

5

K

R

N

W

O

D

L

L

U

P

r

o

t

s

i

s

e

R

n

w

o

d

ll

u

P

t

u

p

n

I

1

5

K

C

D

P

e

c

n

a

t

i

c

a

p

a

C

n

o

i

t

a

p

i

s

s

i

D

r

e

w

o

P

)

t

u

p

t

u

o

r

e

p

(

V

D

D

V

,

O

D

D

V

5

6

4

.

3

=

5

1

F

p

R

T

U

O

e

c

n

a

d

e

p

m

I

t

u

p

t

u

O

7

s

t

u

p

n

I

s

t

u

p

t

u

O

E

O

/

R

M

n

1

N

E

_

K

N

A

B

0

N

E

_

K

N

A

B

x

L

E

S

_

V

I

D

4

A

Q

:

0

A

Q

4

B

Q

:

0

B

Q

4

C

Q

:

0

C

Q

4

D

Q

:

0

D

Q

y

c

n

e

u

q

e

r

F

x

Q

0

X

X

X

Z

i

H

Z

i

H

Z

i

H

Z

i

H

o

r

e

z

1

0

0

0

e

v

i

t

c

A

Z

i

H

Z

i

H

Z

i

H

2

/

N

I

f

1

1

0

0

e

v

i

t

c

A

e

v

i

t

c

A

Z

i

H

Z

i

H

2

/

N

I

f

1

0

1

0

e

v

i

t

c

A

e

v

i

t

c

A

e

v

i

t

c

A

Z

i

H

2

/

N

I

f

1

1

1

0

e

v

i

t

c

A

e

v

i

t

c

A

e

v

i

t

c

A

e

v

i

t

c

A

2

/

N

I

f

1

0

0

1

e

v

i

t

c

A

Z

i

H

Z

i

H

Z

i

H

N

I

f

1

1

0

1

e

v

i

t

c

A

e

v

i

t

c

A

Z

i

H

Z

i

H

N

I

f

1

0

1

1

e

v

i

t

c

A

e

v

i

t

c

A

e

v

i

t

c

A

Z

i

H

N

I

f

1

1

1

1

e

v

i

t

c

A

e

v

i

t

c

A

e

v

i

t

c

A

e

v

i

t

c

A

N

I

f

8701CY

www.icst.com/products/hiperclocks.html

REV. C AUGUST 19, 2002

4

Integrated

Circuit

Systems, Inc.

ICS8701

L

OW

S

KEW

,

˜

1,

˜

2

LVCMOS C

LOCK

G

ENERATOR

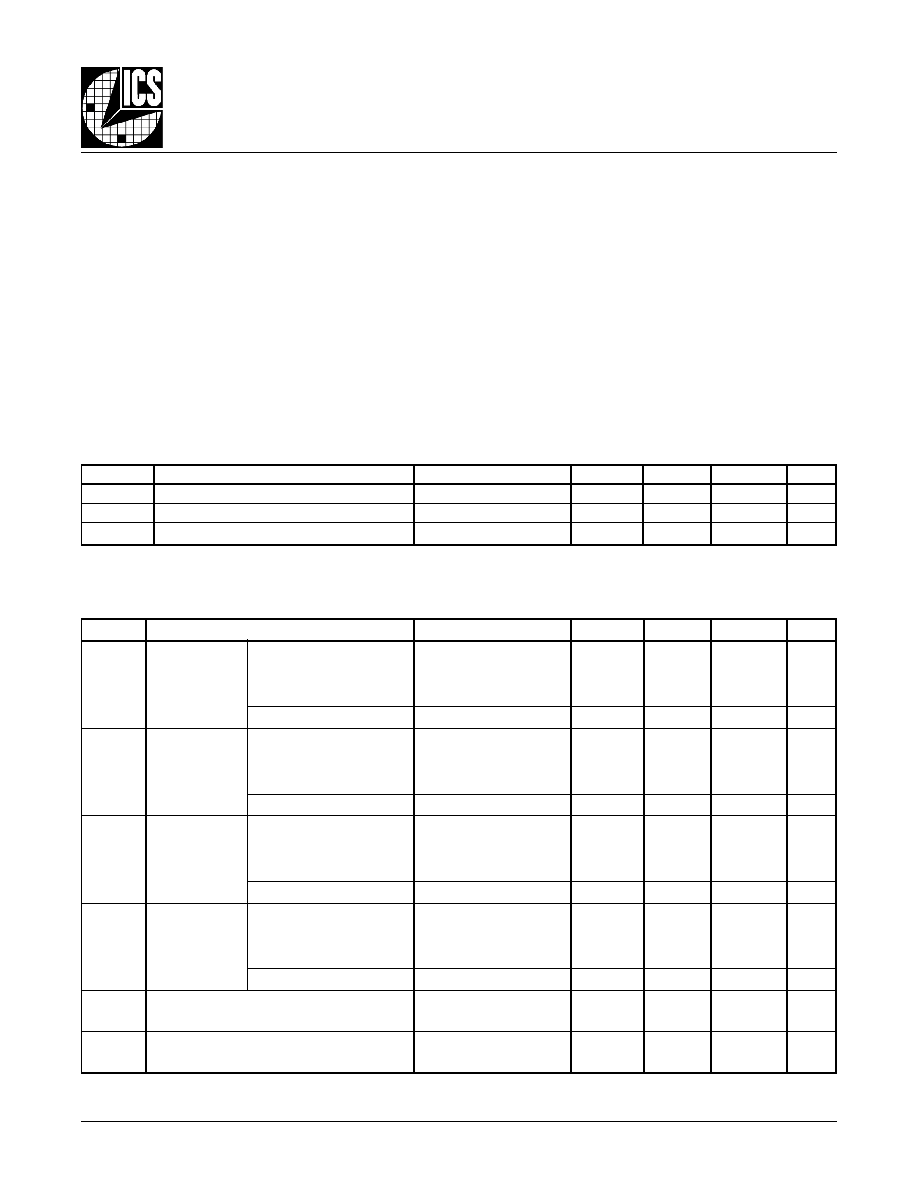

A

BSOLUTE

M

AXIMUM

R

ATINGS

Supply Voltage, V

DDx

4.6V

Inputs, V

I

-0.5V to V

DD

+ 0.5V

Outputs, V

O

-0.5V to V

DDO

+ 0.5V

Package Thermal Impedance,

JA

47.9∞C/W (0 lfpm)

Storage Temperature, T

STG

-65∞C to 150∞C

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings

are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in

the

DC Characteristics or AC Characteristics is not implied. Exposure to absolute maximum rating conditions for extended

periods may affect product reliability.

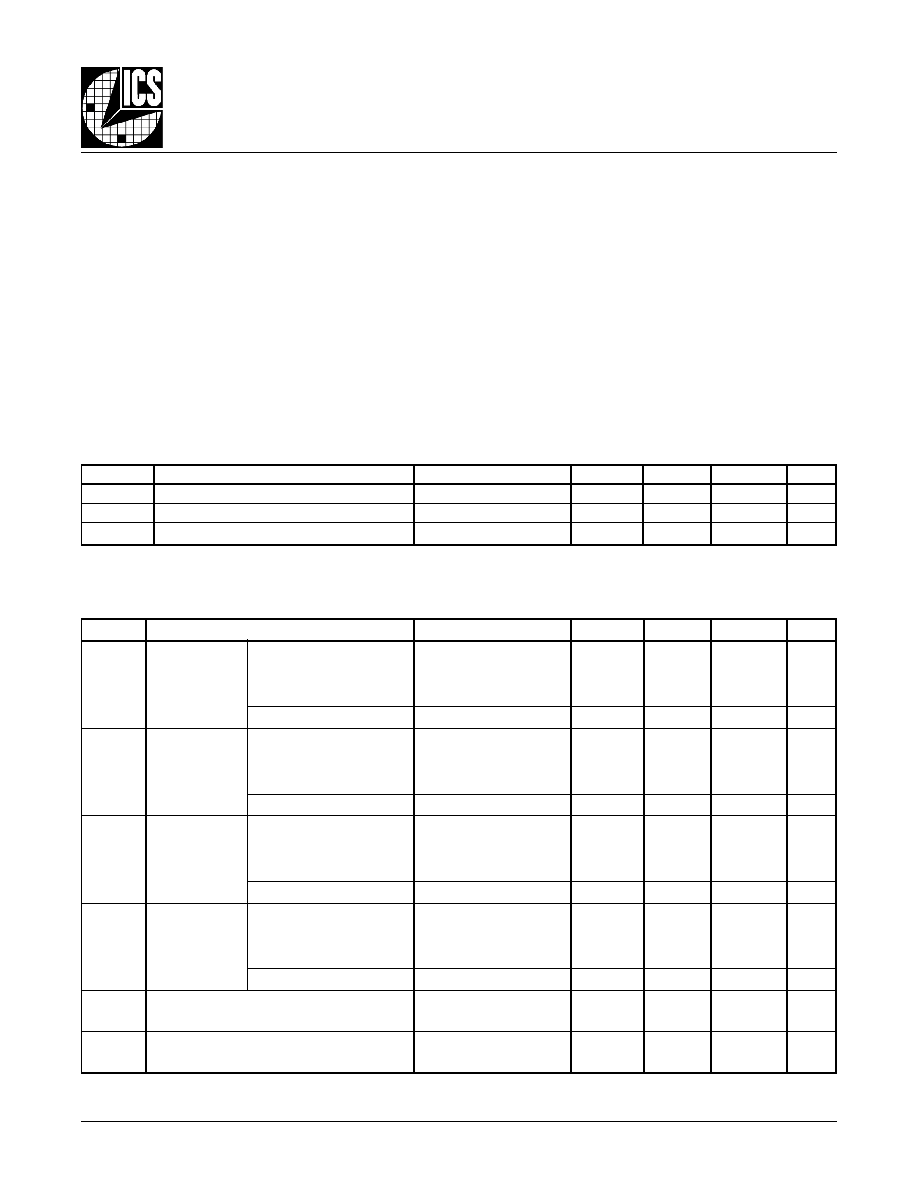

T

ABLE

4A. P

OWER

S

UPPLY

DC C

HARACTERISTICS

,

V

DD

= V

DDO

= 3.3V±5%, T

A

=0∞C

TO

70∞C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

H

I

t

u

p

n

I

e

g

a

t

l

o

V

h

g

i

H

,

B

L

E

S

_

V

I

D

,

A

L

E

S

_

V

I

D

,

D

L

E

S

_

V

I

D

,

C

L

E

S

_

V

I

D

,

1

N

E

_

K

N

A

B

,

0

N

E

_

K

N

A

B

E

O

/

R

M

n

2

V

D

D

3

.

0

+

V

K

L

C

2

V

D

D

3

.

0

+

V

V

L

I

t

u

p

n

I

e

g

a

t

l

o

V

w

o

L

,

B

L

E

S

_

V

I

D

,

A

L

E

S

_

V

I

D

,

D

L

E

S

_

V

I

D

,

C

L

E

S

_

V

I

D

,

1

N

E

_

K

N

A

B

,

0

N

E

_

K

N

A

B

E

O

/

R

M

n

3

.

0

-

8

.

0

V

K

L

C

3

.

0

-

3

.

1

V

I

H

I

t

u

p

n

I

t

n

e

r

r

u

C

h

g

i

H

,

B

L

E

S

_

V

I

D

,

A

L

E

S

_

V

I

D

,

D

L

E

S

_

V

I

D

,

C

L

E

S

_

V

I

D

,

1

N

E

_

K

N

A

B

,

0

N

E

_

K

N

A

B

E

O

/

R

M

n

V

D

D

= V

N

I

V

5

6

4

.

3

=

5

A

µ

K

L

C

V

D

D

= V

N

I

V

5

6

4

.

3

=

0

5

1

A

µ

I

L

I

t

u

p

n

I

t

n

e

r

r

u

C

w

o

L

,

B

L

E

S

_

V

I

D

,

A

L

E

S

_

V

I

D

,

D

L

E

S

_

V

I

D

,

C

L

E

S

_

V

I

D

,

1

N

E

_

K

N

A

B

,

0

N

E

_

K

N

A

B

E

O

/

R

M

n

V

D

D

,

V

5

6

4

.

3

=

V

N

I

V

0

=

0

5

1

-

A

µ

K

L

C

V

D

D

,

V

5

6

4

.

3

=

V

N

I

V

0

=

5

-

A

µ

V

H

O

e

g

a

t

l

o

V

h

g

i

H

t

u

p

t

u

O

V

D

D

V

=

O

D

D

V

5

3

1

.

3

=

I

H

O

A

m

6

3

-

=

6

.

2

V

V

L

O

e

g

a

t

l

o

V

w

o

L

t

u

p

t

u

O

V

D

D

V

=

O

D

D

V

5

3

1

.

3

=

I

L

O

A

m

6

3

=

5

.

0

V

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

e

v

i

t

i

s

o

P

5

3

1

.

3

3

.

3

5

6

4

.

3

V

V

O

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

t

u

p

t

u

O

5

3

1

.

3

3

.

3

5

6

4

.

3

V

I

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

r

e

w

o

P

5

9

A

m

T

ABLE

4B. LVCMOS DC C

HARACTERISTICS

,

V

DD

= V

DDO

= 3.3V±5%, T

A

=0∞C

TO

70∞C

8701CY

www.icst.com/products/hiperclocks.html

REV. C AUGUST 19, 2002

5

Integrated

Circuit

Systems, Inc.

ICS8701

L

OW

S

KEW

,

˜

1,

˜

2

LVCMOS C

LOCK

G

ENERATOR

T

ABLE

5A. AC C

HARACTERISTICS

,

V

DD

= V

DDO

= 3.3V±5%, T

A

=0∞C

TO

70∞C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

f

X

A

M

y

c

n

e

u

q

e

r

F

t

u

p

t

u

O

0

5

2

z

H

M

t

D

P

1

E

T

O

N

;

y

a

l

e

D

n

o

i

t

a

g

a

p

o

r

P

f

z

H

M

0

0

2

2

.

2

4

.

3

s

n

t

)

b

(

k

s

7

,

2

E

T

O

N

;

w

e

k

S

k

n

a

B

t

a

e

g

d

e

g

n

i

s

i

r

n

o

d

e

r

u

s

a

e

M

V

O

D

D

2

/

0

0

2

s

p

t

)

o

(

k

s

7

,

3

E

T

O

N

;

w

e

k

S

t

u

p

t

u

O

t

a

e

g

d

e

g

n

i

s

i

r

n

o

d

e

r

u

s

a

e

M

V

O

D

D

2

/

0

5

2

s

p

t

(

k

s w)

;

w

e

k

S

y

c

n

e

u

q

e

r

F

e

l

p

i

t

l

u

M

7

,

4

E

T

O

N

t

a

e

g

d

e

g

n

i

s

i

r

n

o

d

e

r

u

s

a

e

M

V

O

D

D

2

/

0

0

3

s

p

t

)

p

p

(

k

s

7

,

5

E

T

O

N

;

w

e

k

S

t

r

a

P

-

o

t

-

t

r

a

P

t

a

e

g

d

e

g

n

i

s

i

r

n

o

d

e

r

u

s

a

e

M

V

O

D

D

2

/

0

0

6

s

p

t

R

6

E

T

O

N

;

e

m

i

T

e

s

i

R

t

u

p

t

u

O

%

0

7

o

t

%

0

3

0

8

2

0

5

8

s

p

t

F

6

E

T

O

N

;

e

m

i

T

ll

a

F

t

u

p

t

u

O

%

0

7

o

t

%

0

3

0

8

2

0

5

8

s

p

c

d

o

e

l

c

y

C

y

t

u

D

t

u

p

t

u

O

f

z

H

M

0

0

2

2

/

E

L

C

Y

C

t

5

.

0

-

2

/

E

L

C

Y

C

t

2

/

E

L

C

Y

C

t

5

.

0

+

s

n

z

H

M

0

0

2

=

f

2

5

.

2

3

s

n

t

N

E

;

e

m

i

T

e

l

b

a

n

E

t

u

p

t

u

O

6

E

T

O

N

z

H

M

0

1

=

f

6

s

n

t

S

I

D

;

e

m

i

T

e

l

b

a

s

i

D

t

u

p

t

u

O

6

E

T

O

N

z

H

M

0

1

=

f

6

s

n

.

e

s

i

w

r

e

h

t

o

d

e

t

o

n

s

s

e

l

n

u

z

H

M

0

0

2

t

a

d

e

r

u

s

a

e

m

s

r

e

t

e

m

a

r

a

p

ll

A

e

h

t

m

o

r

f

d

e

r

u

s

a

e

M

:

1

E

T

O

N

V

D

D

o

t

t

u

p

n

i

e

h

t

f

o

2

/

V

O

D

D

/

.

t

u

p

t

u

o

e

h

t

f

o

2

.

s

n

o

i

t

i

d

n

o

c

d

a

o

l

l

a

u

q

e

h

t

i

w

d

n

a

s

e

g

a

t

l

o

v

y

l

p

p

u

s

e

m

a

s

e

h

t

t

a

s

t

u

p

t

u

o

f

o

k

n

a

b

a

n

i

h

t

i

w

w

e

k

s

s

a

d

e

n

i

f

e

D

:

2

E

T

O

N

.

s

n

o

i

t

i

d

n

o

c

d

a

o

l

l

a

u

q

e

h

t

i

w

d

n

a

e

g

a

t

l

o

v

y

l

p

p

u

s

e

m

a

s

e

h

t

t

a

s

t

u

p

t

u

o

n

e

e

w

t

e

b

w

e

k

s

s

a

d

e

n

i

f

e

D

:

3

E

T

O

N

V

t

a

d

e

r

u

s

a

e

M

O

D

D

.

2

/

s

e

g

a

t

l

o

v

y

l

p

p

u

s

e

m

a

s

e

h

t

h

t

i

w

y

c

n

e

u

q

e

r

f

t

n

e

r

e

f

f

i

d

t

a

g

n

i

t

a

r

e

p

o

s

t

u

p

t

u

o

f

o

s

k

n

a

b

s

s

o

r

c

a

w

e

k

s

s

a

d

e

n

i

f

e

D

:

4

E

T

O

N

.

s

n

o

i

t

i

d

n

o

c

d

a

o

l

l

a

u

q

e

d

n

a

d

n

a

s

e

g

a

t

l

o

v

y

l

p

p

u

s

e

m

a

s

e

h

t

t

a

g

n

i

t

a

r

e

p

o

s

e

c

i

v

e

d

t

n

e

r

e

f

f

i

d

n

o

s

t

u

p

t

u

o

n

e

e

w

t

e

b

w

e

k

s

s

a

d

e

n

i

f

e

D

:

5

E

T

O

N

V

t

a

d

e

r

u

s

a

e

m

e

r

a

s

t

u

p

t

u

o

e

h

t

,

e

c

i

v

e

d

h

c

a

e

n

o

s

t

u

p

n

i

f

o

e

p

y

t

e

m

a

s

e

h

t

g

n

i

s

U

.

s

n

o

i

t

i

d

n

o

c

d

a

o

l

l

a

u

q

e

h

t

i

w

O

D

D

.

2

/

.

n

o

i

t

c

u

d

o

r

p

n

i

d

e

t

s

e

t

t

o

N

.

n

o

i

t

a

z

i

r

e

t

c

a

r

a

h

c

y

b

d

e

e

t

n

a

r

a

u

g

e

r

a

s

r

e

t

e

m

a

r

a

p

e

s

e

h

T

:

6

E

T

O

N

.

5

6

d

r

a

d

n

a

t

S

C

E

D

E

J

h

t

i

w

e

c

n

a

d

r

o

c

c

a

n

i

d

e

n

i

f

e

d

s

i

r

e

t

e

m

a

r

a

p

s

i

h

T

:

7

E

T

O

N

8701CY

www.icst.com/products/hiperclocks.html

REV. C AUGUST 19, 2002

6

Integrated

Circuit

Systems, Inc.

ICS8701

L

OW

S

KEW

,

˜

1,

˜

2

LVCMOS C

LOCK

G

ENERATOR

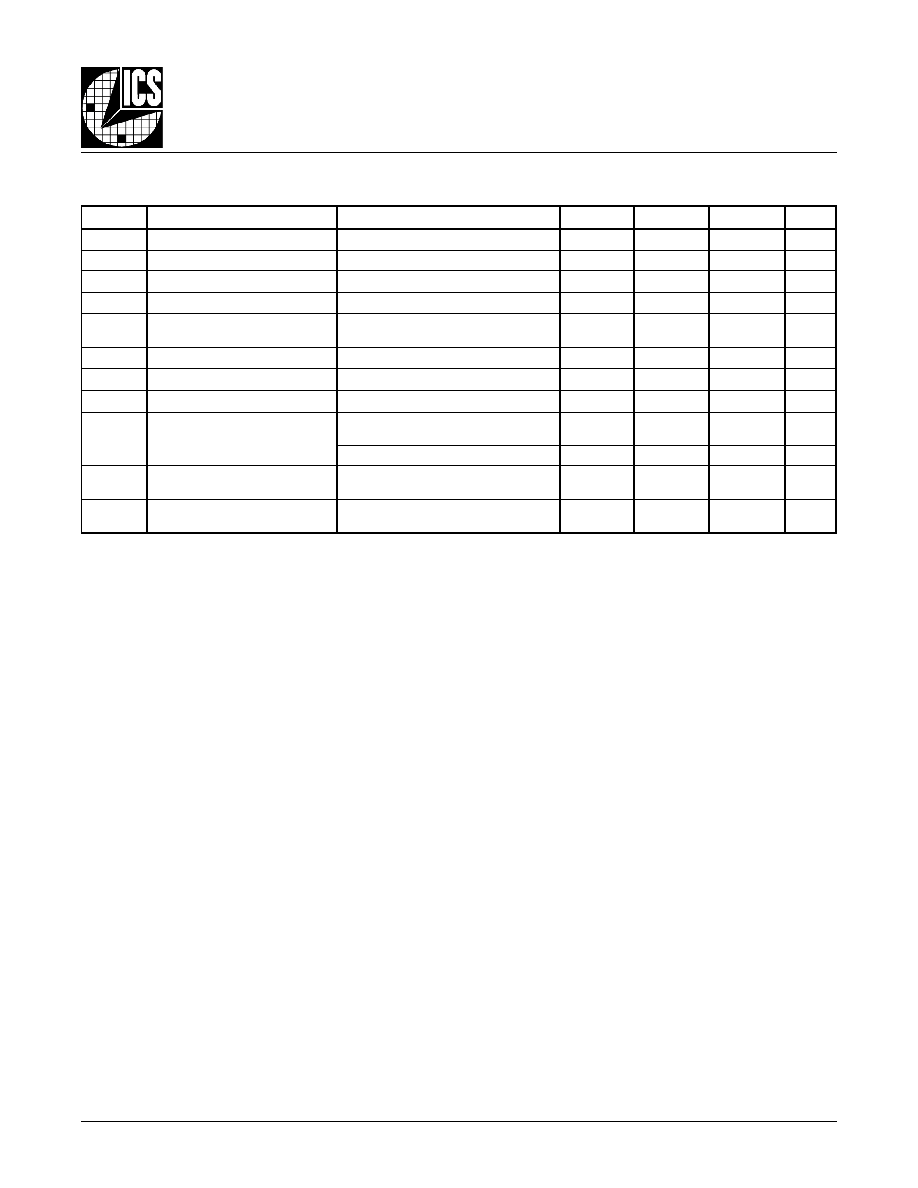

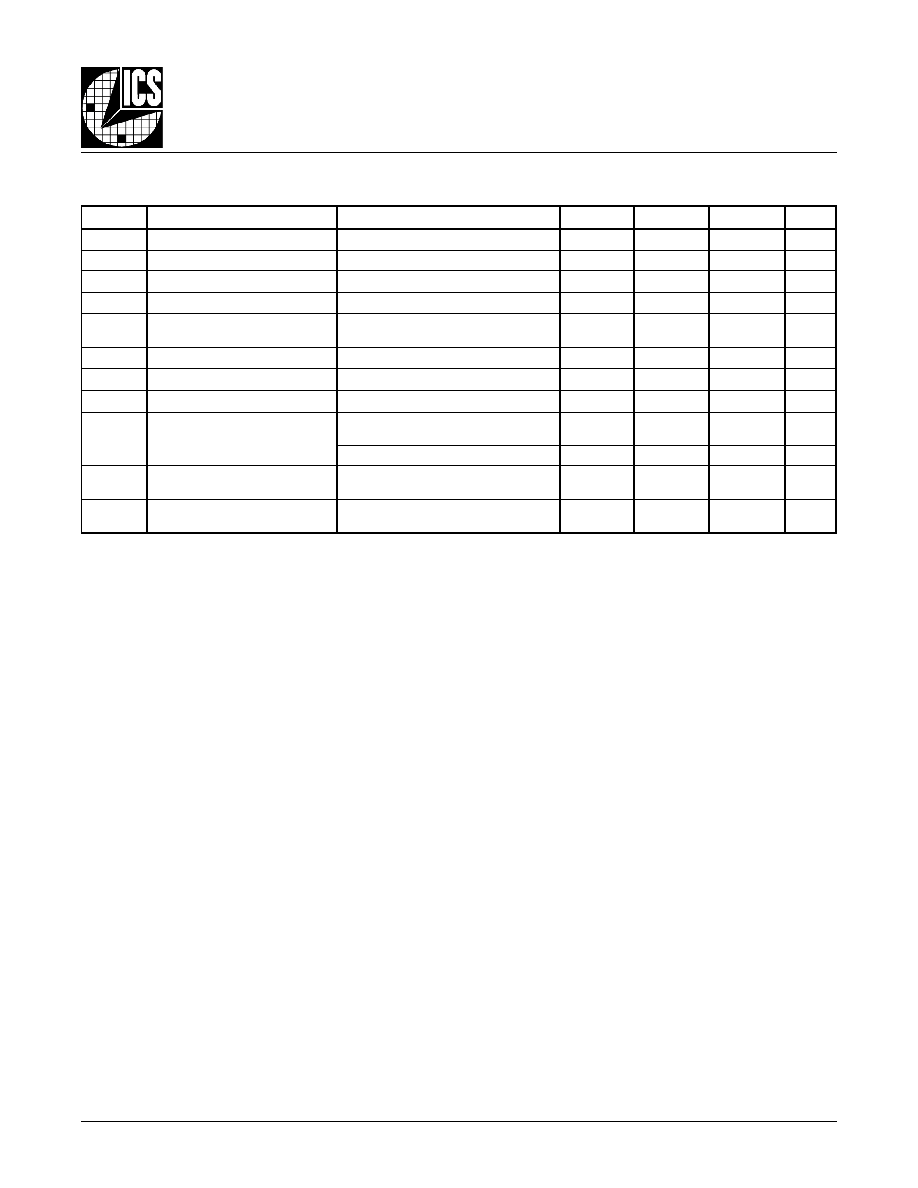

T

ABLE

4C. P

OWER

S

UPPLY

DC C

HARACTERISTICS

,

V

DD

= 3.3V±5%, V

DDO

= 2.5V±5%, T

A

= 0∞C

TO

70∞C

T

ABLE

4D. LVCMOS DC C

HARACTERISTICS

,

V

DD

= 3.3V±5%, V

DDO

= 2.5V±5%, T

A

= 0∞C

TO

70∞C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

e

v

i

t

i

s

o

P

5

3

1

.

3

3

.

3

5

6

4

.

3

V

V

O

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

t

u

p

t

u

O

5

7

3

.

2

5

.

2

5

2

6

.

2

V

I

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

r

e

w

o

P

5

9

A

m

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

H

I

t

u

p

n

I

e

g

a

t

l

o

V

h

g

i

H

,

B

L

E

S

_

V

I

D

,

A

L

E

S

_

V

I

D

,

D

L

E

S

_

V

I

D

,

C

L

E

S

_

V

I

D

,

1

N

E

_

K

N

A

B

,

0

N

E

_

K

N

A

B

E

O

/

R

M

n

2

V

D

D

3

.

0

+

V

K

L

C

2

V

D

D

3

.

0

+

V

V

L

I

t

u

p

n

I

e

g

a

t

l

o

V

w

o

L

,

B

L

E

S

_

V

I

D

,

A

L

E

S

_

V

I

D

,

D

L

E

S

_

V

I

D

,

C

L

E

S

_

V

I

D

,

1

N

E

_

K

N

A

B

,

0

N

E

_

K

N

A

B

E

O

/

R

M

n

3

.

0

-

8

.

0

V

K

L

C

3

.

0

-

3

.

1

V

I

H

I

t

u

p

n

I

t

n

e

r

r

u

C

h

g

i

H

,

B

L

E

S

_

V

I

D

,

A

L

E

S

_

V

I

D

,

D

L

E

S

_

V

I

D

,

C

L

E

S

_

V

I

D

,

1

N

E

_

K

N

A

B

,

0

N

E

_

K

N

A

B

E

O

/

R

M

n

V

D

D

= V

N

I

V

5

6

4

.

3

=

5

A

µ

K

L

C

V

D

D

= V

N

I

V

5

6

4

.

3

=

0

5

1

A

µ

I

L

I

t

u

p

n

I

t

n

e

r

r

u

C

w

o

L

,

B

L

E

S

_

V

I

D

,

A

L

E

S

_

V

I

D

,

D

L

E

S

_

V

I

D

,

C

L

E

S

_

V

I

D

,

1

N

E

_

K

N

A

B

,

0

N

E

_

K

N

A

B

E

O

/

R

M

n

V

D

D

,

V

5

6

4

.

3

=

V

N

I

V

0

=

0

5

1

-

A

µ

K

L

C

V

D

D

,

V

5

6

4

.

3

=

V

N

I

V

0

=

5

-

A

µ

V

H

O

e

g

a

t

l

o

V

h

g

i

H

t

u

p

t

u

O

V

D

D

,

V

5

3

1

.

3

=

V

O

D

D

5

7

3

.

2

=

I

H

O

A

m

7

2

-

=

8

.

1

V

V

L

O

e

g

a

t

l

o

V

w

o

L

t

u

p

t

u

O

V

D

D

,

V

5

3

1

.

3

=

V

O

D

D

5

7

3

.

2

=

I

L

O

A

m

7

2

=

5

.

0

V

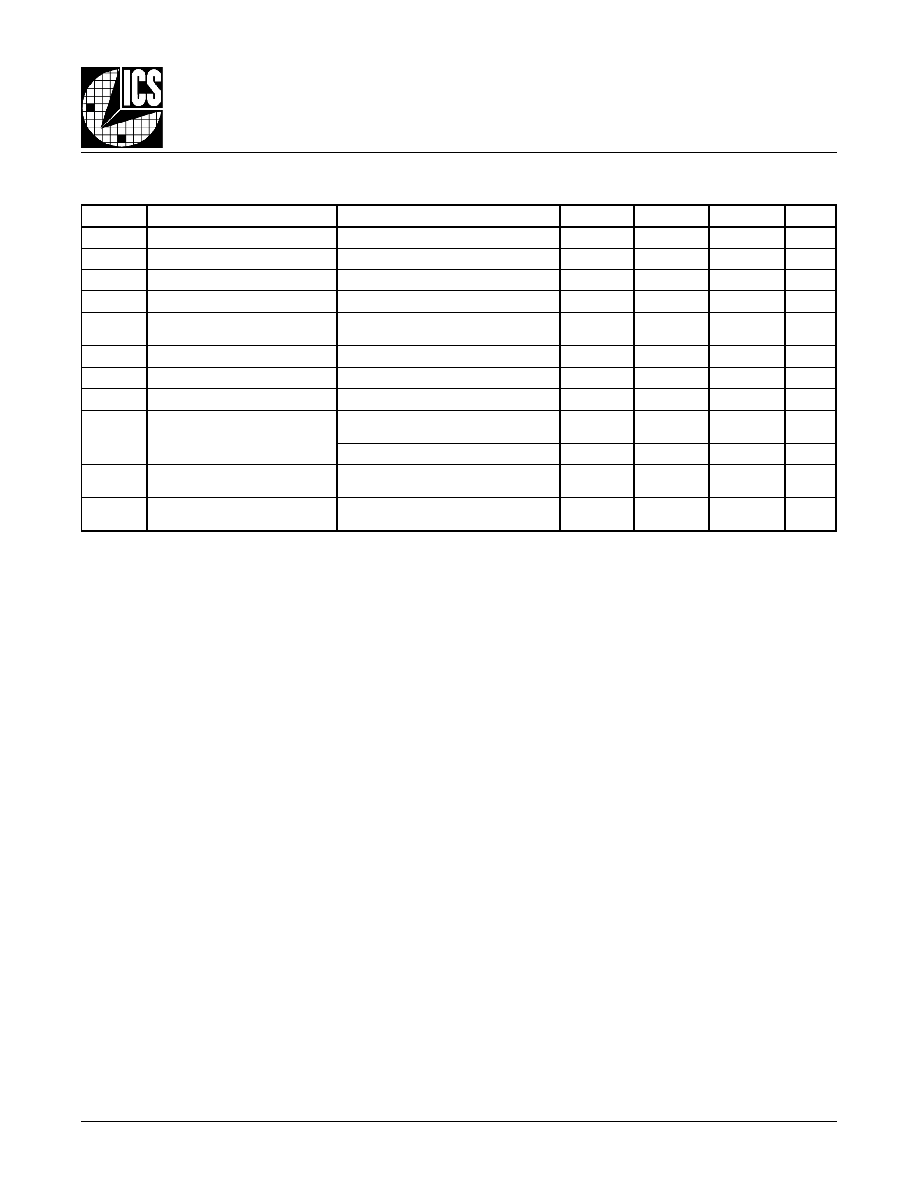

8701CY

www.icst.com/products/hiperclocks.html

REV. C AUGUST 19, 2002

7

Integrated

Circuit

Systems, Inc.

ICS8701

L

OW

S

KEW

,

˜

1,

˜

2

LVCMOS C

LOCK

G

ENERATOR

T

ABLE

5B. AC C

HARACTERISTICS

,

V

DD

= 3.3V±5%, V

DDO

= 2.5V±5%, T

A

= 0∞C

TO

70∞C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

f

X

A

M

y

c

n

e

u

q

e

r

F

t

u

p

t

u

O

0

5

2

z

H

M

t

D

P

1

E

T

O

N

;

y

a

l

e

D

n

o

i

t

a

g

a

p

o

r

P

f

z

H

M

0

0

2

6

.

2

6

.

3

s

n

t

)

b

(

k

s

7

,

2

E

T

O

N

;

w

e

k

S

k

n

a

B

t

a

e

g

d

e

g

n

i

s

i

r

n

o

d

e

r

u

s

a

e

M

V

O

D

D

2

/

5

2

2

s

p

t

)

o

(

k

s

7

,

3

E

T

O

N

;

w

e

k

S

t

u

p

t

u

O

t

a

e

g

d

e

g

n

i

s

i

r

n

o

d

e

r

u

s

a

e

M

V

O

D

D

2

/

0

5

2

s

p

t

(

k

s w)

;

w

e

k

S

y

c

n

e

u

q

e

r

F

e

l

p

i

t

l

u

M

7

,

4

E

T

O

N

t

a

e

g

d

e

g

n

i

s

i

r

n

o

d

e

r

u

s

a

e

M

V

O

D

D

2

/

0

0

3

s

p

t

)

p

p

(

k

s

7

,

5

E

T

O

N

;

w

e

k

S

t

r

a

P

-

o

t

-

t

r

a

P

t

a

e

g

d

e

g

n

i

s

i

r

n

o

d

e

r

u

s

a

e

M

V

O

D

D

2

/

0

0

6

s

p

t

R

6

E

T

O

N

;

e

m

i

T

e

s

i

R

t

u

p

t

u

O

%

0

7

o

t

%

0

3

0

8

2

0

5

8

s

p

t

F

6

E

T

O

N

;

e

m

i

T

ll

a

F

t

u

p

t

u

O

%

0

7

o

t

%

0

3

0

8

2

0

5

8

s

p

c

d

o

e

l

c

y

C

y

t

u

D

t

u

p

t

u

O

f

z

H

M

0

0

2

2

/

E

L

C

Y

C

t

5

.

0

-

2

/

E

L

C

Y

C

t

2

/

E

L

C

Y

C

t

5

.

0

+

s

n

z

H

M

0

0

2

=

f

2

5

.

2

3

s

n

t

N

E

;

e

m

i

T

e

l

b

a

n

E

t

u

p

t

u

O

6

E

T

O

N

z

H

M

0

1

=

f

6

s

n

t

S

I

D

;

e

m

i

T

e

l

b

a

s

i

D

t

u

p

t

u

O

6

E

T

O

N

z

H

M

0

1

=

f

6

s

n

.

e

s

i

w

r

e

h

t

o

d

e

t

o

n

s

s

e

l

n

u

z

H

M

0

0

2

t

a

d

e

r

u

s

a

e

m

s

r

e

t

e

m

a

r

a

p

ll

A

V

e

h

t

m

o

r

f

d

e

r

u

s

a

e

M

:

1

E

T

O

N

D

D

V

o

t

t

u

p

n

i

e

h

t

f

o

2

/

O

D

D

.

t

u

p

t

u

o

e

h

t

f

o

2

/

.

s

n

o

i

t

i

d

n

o

c

d

a

o

l

l

a

u

q

e

h

t

i

w

d

n

a

s

e

g

a

t

l

o

v

y

l

p

p

u

s

e

m

a

s

e

h

t

t

a

s

t

u

p

t

u

o

f

o

k

n

a

b

a

n

i

h

t

i

w

w

e

k

s

s

a

d

e

n

i

f

e

D

:

2

E

T

O

N

.

s

n

o

i

t

i

d

n

o

c

d

a

o

l

l

a

u

q

e

h

t

i

w

d

n

a

e

g

a

t

l

o

v

y

l

p

p

u

s

e

m

a

s

e

h

t

t

a

s

t

u

p

t

u

o

n

e

e

w

t

e

b

w

e

k

s

s

a

d

e

n

i

f

e

D

:

3

E

T

O

N

V

t

a

d

e

r

u

s

a

e

M

O

D

D

.

2

/

s

e

g

a

t

l

o

v

y

l

p

p

u

s

e

m

a

s

e

h

t

h

t

i

w

y

c

n

e

u

q

e

r

f

t

n

e

r

e

f

f

i

d

t

a

g

n

i

t

a

r

e

p

o

s

t

u

p

t

u

o

f

o

s

k

n

a

b

s

s

o

r

c

a

w

e

k

s

s

a

d

e

n

i

f

e

D

:

4

E

T

O

N

.

s

n

o

i

t

i

d

n

o

c

d

a

o

l

l

a

u

q

e

d

n

a

d

n

a

s

e

g

a

t

l

o

v

y

l

p

p

u

s

e

m

a

s

e

h

t

t

a

g

n

i

t

a

r

e

p

o

s

e

c

i

v

e

d

t

n

e

r

e

f

f

i

d

n

o

s

t

u

p

t

u

o

n

e

e

w

t

e

b

w

e

k

s

s

a

d

e

n

i

f

e

D

:

5

E

T

O

N

V

t

a

d

e

r

u

s

a

e

m

e

r

a

s

t

u

p

t

u

o

e

h

t

,

e

c

i

v

e

d

h

c

a

e

n

o

s

t

u

p

n

i

f

o

e

p

y

t

e

m

a

s

e

h

t

g

n

i

s

U

.

s

n

o

i

t

i

d

n

o

c

d

a

o

l

l

a

u

q

e

h

t

i

w

O

D

D

.

2

/

.

n

o

i

t

c

u

d

o

r

p

n

i

d

e

t

s

e

t

t

o

N

.

n

o

i

t

a

z

i

r

e

t

c

a

r

a

h

c

y

b

d

e

e

t

n

a

r

a

u

g

e

r

a

s

r

e

t

e

m

a

r

a

p

e

s

e

h

T

:

6

E

T

O

N

.

5

6

d

r

a

d

n

a

t

S

C

E

D

E

J

h

t

i

w

e

c

n

a

d

r

o

c

c

a

n

i

d

e

n

i

f

e

d

s

i

r

e

t

e

m

a

r

a

p

s

i

h

T

:

7

E

T

O

N

8701CY

www.icst.com/products/hiperclocks.html

REV. C AUGUST 19, 2002

8

Integrated

Circuit

Systems, Inc.

ICS8701

L

OW

S

KEW

,

˜

1,

˜

2

LVCMOS C

LOCK

G

ENERATOR

P

ARAMETER

M

EASUREMENT

I

NFORMATION

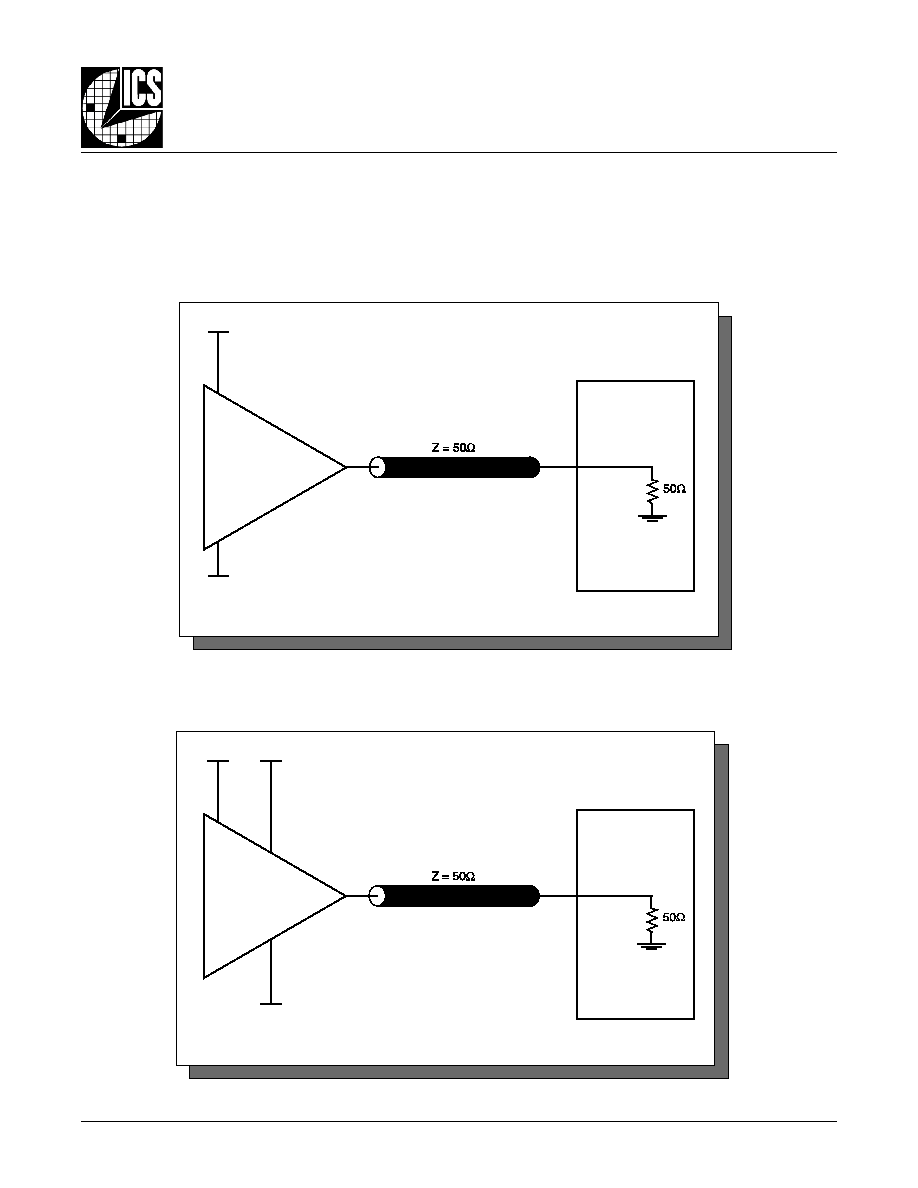

3.3V O

UTPUT

L

OAD

T

EST

C

IRCUIT

SCOPE

Qx

LVCMOS

V

DDO

= +1.25V

1.65V ± 5%

GND = -1.25V ± 5%

3.3V/2.5 O

UTPUT

L

OAD

T

EST

C

IRCUIT

SCOPE

Qx

LVCMOS

V

DD,

V

DDO

V

DD

-1.25V ± 5%

V

DDO

2.05V ± 5%

GND

1.25V ± 5%

8701CY

www.icst.com/products/hiperclocks.html

REV. C AUGUST 19, 2002

9

Integrated

Circuit

Systems, Inc.

ICS8701

L

OW

S

KEW

,

˜

1,

˜

2

LVCMOS C

LOCK

G

ENERATOR

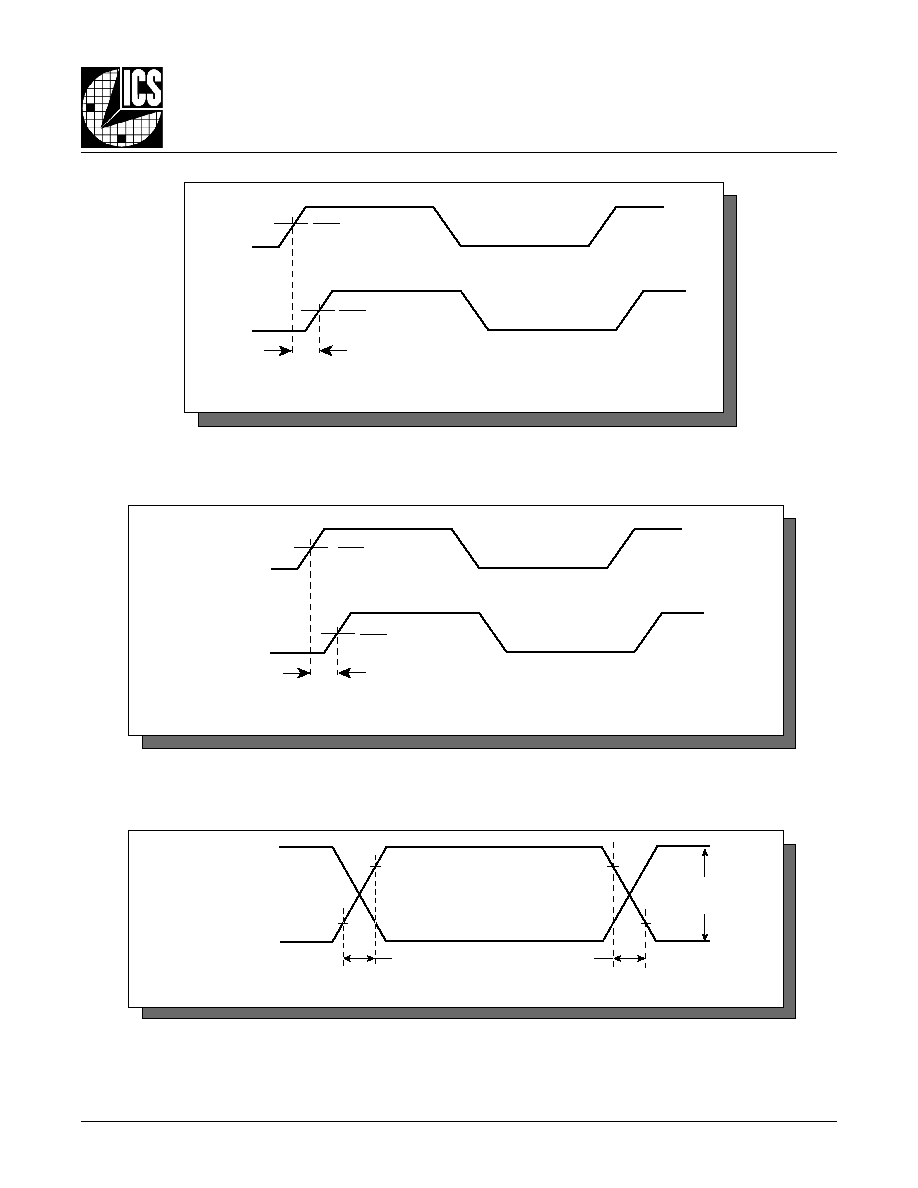

O

UTPUT

S

KEW

tsk(o)

Qx

Qy

P

ART

-

TO

-P

ART

S

KEW

Qx

Qy

PART 1

PART 2

tsk(pp)

V

DDO

2

O

UTPUT

R

ISE

AND

F

ALL

T

IME

Clock Outputs

30%

70%

70%

30%

t

R

t

F

V

S W I N G

V

DDO

2

V

DDO

2

V

DDO

2

8701CY

www.icst.com/products/hiperclocks.html

REV. C AUGUST 19, 2002

10

Integrated

Circuit

Systems, Inc.

ICS8701

L

OW

S

KEW

,

˜

1,

˜

2

LVCMOS C

LOCK

G

ENERATOR

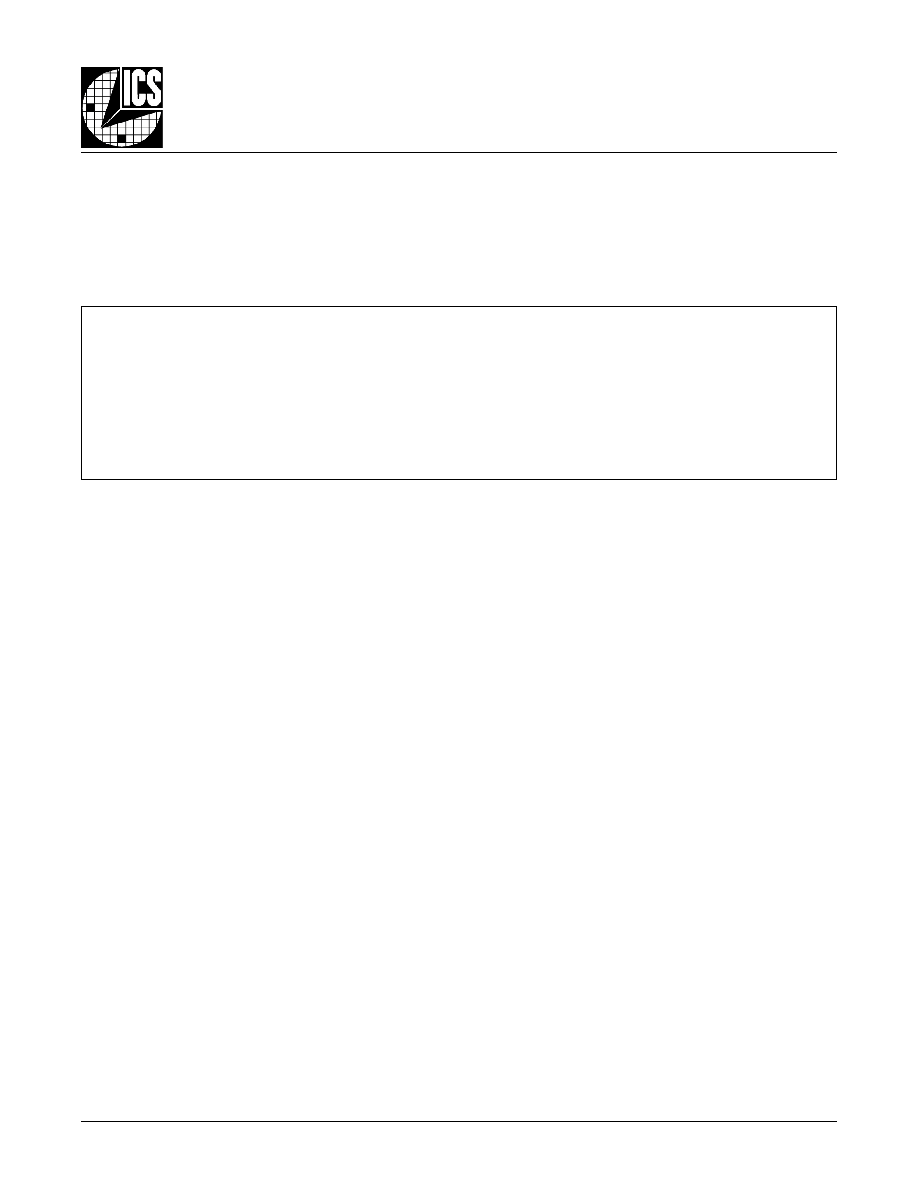

P

ROPAGATION

D

ELAY

t

PD

V

DD

2

V

DDO

2

CLK

QAx, QBx, QCx, QDx

odc & t

P

ERIOD

Pulse Width

t

PERIOD

V

DDO

2

QAx, QBx, QCx, QDx

P

OWER

C

ONSIDERATIONS

For Power Dissipation, please refer to a separate Application Note:

Power Dissipation for LVCMOS Buffer.

D

RIVER

T

ERMINATION

For LVCMOS Output Termination, please refer to a separate Application Note:

LVCMOS Driver Termination.

8701CY

www.icst.com/products/hiperclocks.html

REV. C AUGUST 19, 2002

11

Integrated

Circuit

Systems, Inc.

ICS8701

L

OW

S

KEW

,

˜

1,

˜

2

LVCMOS C

LOCK

G

ENERATOR

R

ELIABILITY

I

NFORMATION

T

RANSISTOR

C

OUNT

The transistor count for ICS8701 is: 1743

T

ABLE

6.

JA

VS

. A

IR

F

LOW

T

ABLE

q

JA

by Velocity (Linear Feet per Minute)

0

200

500

Single-Layer PCB, JEDEC Standard Test Boards

67.8∞C/W

55.9∞C/W

50.1∞C/W

Multi-Layer PCB, JEDEC Standard Test Boards

47.9∞C/W

42.1∞C/W

39.4∞C/W

NOTE: Most modern PCB designs use multi-layered boards. The data in the second row pertains to most designs.

8701CY

www.icst.com/products/hiperclocks.html

REV. C AUGUST 19, 2002

12

Integrated

Circuit

Systems, Inc.

ICS8701

L

OW

S

KEW

,

˜

1,

˜

2

LVCMOS C

LOCK

G

ENERATOR

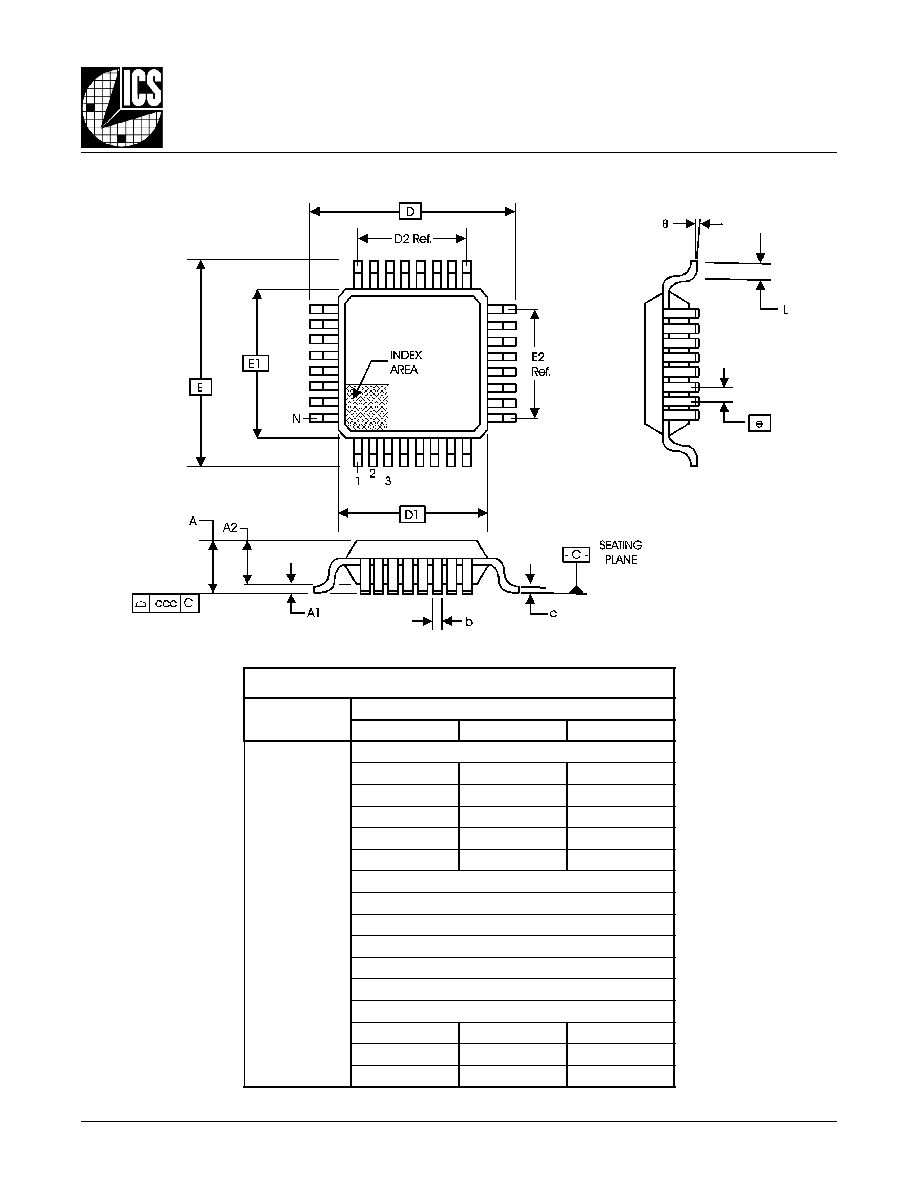

N

O

I

T

A

I

R

A

V

C

E

D

E

J

S

R

E

T

E

M

I

L

L

I

M

N

I

S

N

O

I

S

N

E

M

I

D

L

L

A

L

O

B

M

Y

S

C

B

B

M

U

M

I

N

I

M

L

A

N

I

M

O

N

M

U

M

I

X

A

M

N

8

4

A

-

-

-

-

0

6

.

1

1

A

5

0

.

0

-

-

5

1

.

0

2

A

5

3

.

1

0

4

.

1

5

4

.

1

b

7

1

.

0

2

2

.

0

7

2

.

0

c

9

0

.

0

-

-

0

2

.

0

D

C

I

S

A

B

0

0

.

9

1

D

C

I

S

A

B

0

0

.

7

2

D

.

f

e

R

0

5

.

5

E

C

I

S

A

B

0

0

.

9

1

E

C

I

S

A

B

0

0

.

7

2

E

.

f

e

R

0

5

.

5

e

C

I

S

A

B

0

5

.

0

L

5

4

.

0

0

6

.

0

5

7

.

0

q

0

∞

-

-

7

∞

c

c

c

-

-

-

-

8

0

.

0

P

ACKAGE

O

UTLINE

- Y S

UFFIX

T

ABLE

7. P

ACKAGE

D

IMENSIONS

Reference Document: JEDEC Publication 95, MS-026

8701CY

www.icst.com/products/hiperclocks.html

REV. C AUGUST 19, 2002

13

Integrated

Circuit

Systems, Inc.

ICS8701

L

OW

S

KEW

,

˜

1,

˜

2

LVCMOS C

LOCK

G

ENERATOR

T

ABLE

8. O

RDERING

I

NFORMATION

r

e

b

m

u

N

r

e

d

r

O

/

t

r

a

P

g

n

i

k

r

a

M

e

g

a

k

c

a

P

t

n

u

o

C

e

r

u

t

a

r

e

p

m

e

T

Y

C

1

0

7

8

S

C

I

Y

C

1

0

7

8

S

C

I

P

F

Q

L

d

a

e

L

8

4

y

a

r

t

r

e

p

0

5

2

C

∞

0

7

o

t

C

∞

0

T

Y

C

1

0

7

8

S

C

I

Y

C

1

0

7

8

S

C

I

l

e

e

R

d

n

a

e

p

a

T

n

o

P

F

Q

L

d

a

e

L

8

4

0

0

0

1

C

∞

0

7

o

t

C

∞

0

While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems, Incorporated (ICS) assumes no responsibility for either its use

or for infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use

in normal commercial applications. Any other applications such as those requiring extended temperature range, high reliability, or other extraordinary environmental requirements are

not recommended without additional processing by ICS. ICS reserves the right to change any circuitry or specifications without notice. ICS does not authorize or warrant any ICS

product for use in life support devices or critical medical instruments.

8701CY

www.icst.com/products/hiperclocks.html

REV. C AUGUST 19, 2002

14

Integrated

Circuit

Systems, Inc.

ICS8701

L

OW

S

KEW

,

˜

1,

˜

2

LVCMOS C

LOCK

G

ENERATOR

T

E

E

H

S

Y

R

O

T

S

I

H

N

O

I

S

I

V

E

R

v

e

R

e

l

b

a

T

e

g

a

P

e

g

n

a

h

C

f

o

n

o

i

t

p

i

r

c

s

e

D

e

t

a

D

B

A

5

B

5

5

7

0

1

-

8

.

s

e

t

o

n

d

e

t

a

d

p

U

.

s

e

t

o

n

d

e

t

a

d

p

U

.

s

g

n

i

w

a

r

d

d

e

t

a

d

p

U

1

0

/

4

/

0

1

C

B

4

D

4

4

6

1

1

V

d

e

s

i

v

e

R

H

I

V

o

t

m

u

m

i

x

a

M

8

.

3

m

o

r

f

s

w

o

r

D

D

.

m

u

m

i

x

a

M

3

.

0

+

V

d

e

s

i

v

e

R

H

I

V

o

t

m

u

m

i

x

a

M

8

.

3

m

o

r

f

s

w

o

r

D

D

.

m

u

m

i

x

a

M

3

.

0

+

.

s

e

t

o

n

n

o

i

t

a

n

i

m

r

e

T

r

e

v

i

r

D

d

n

a

n

o

i

t

a

p

i

s

s

i

D

r

e

w

o

P

d

e

d

d

A

1

0

/

8

2

/

1

1

C

1

2

9

.

n

o

i

t

p

i

r

c

s

e

d

E

O

/

R

M

n

d

e

s

i

v

e

r

,

e

l

b

a

T

n

o

i

t

p

i

r

c

s

e

D

n

i

P

.

m

a

r

g

a

i

D

e

m

i

T

ll

a

F

/

e

s

i

R

t

u

p

t

u

O

d

e

t

a

d

p

U

2

0

/

9

1

/

8