Document Outline

- General Description

- Features

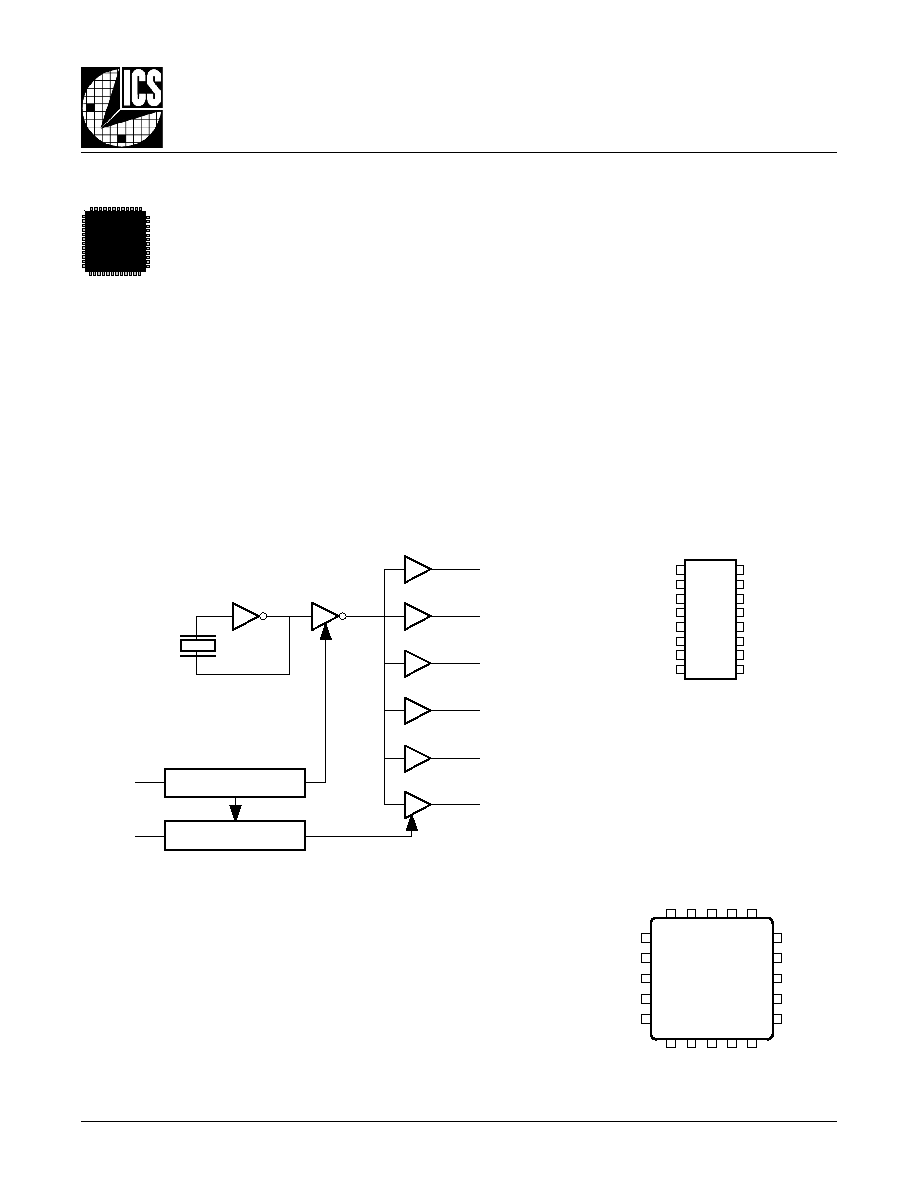

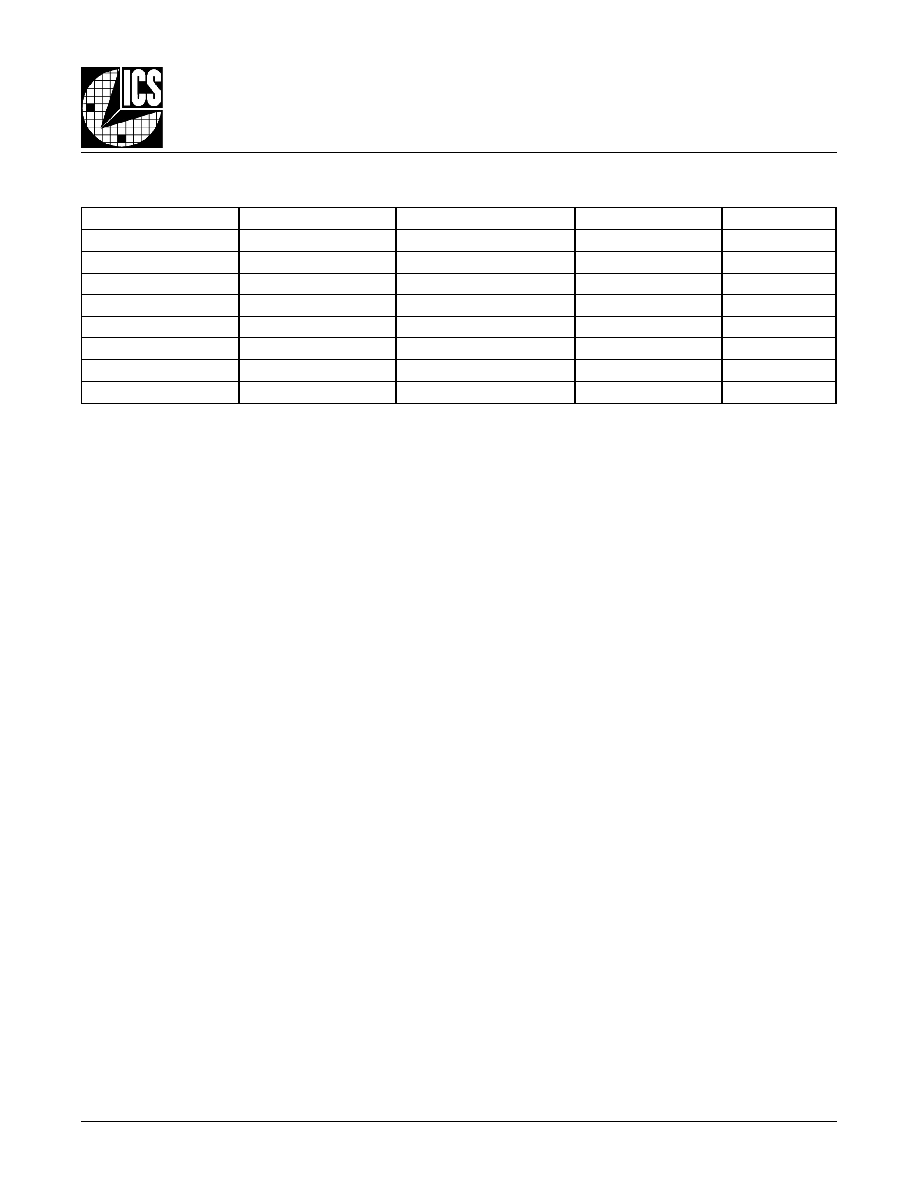

- Block Diagram

- Pin Assignments

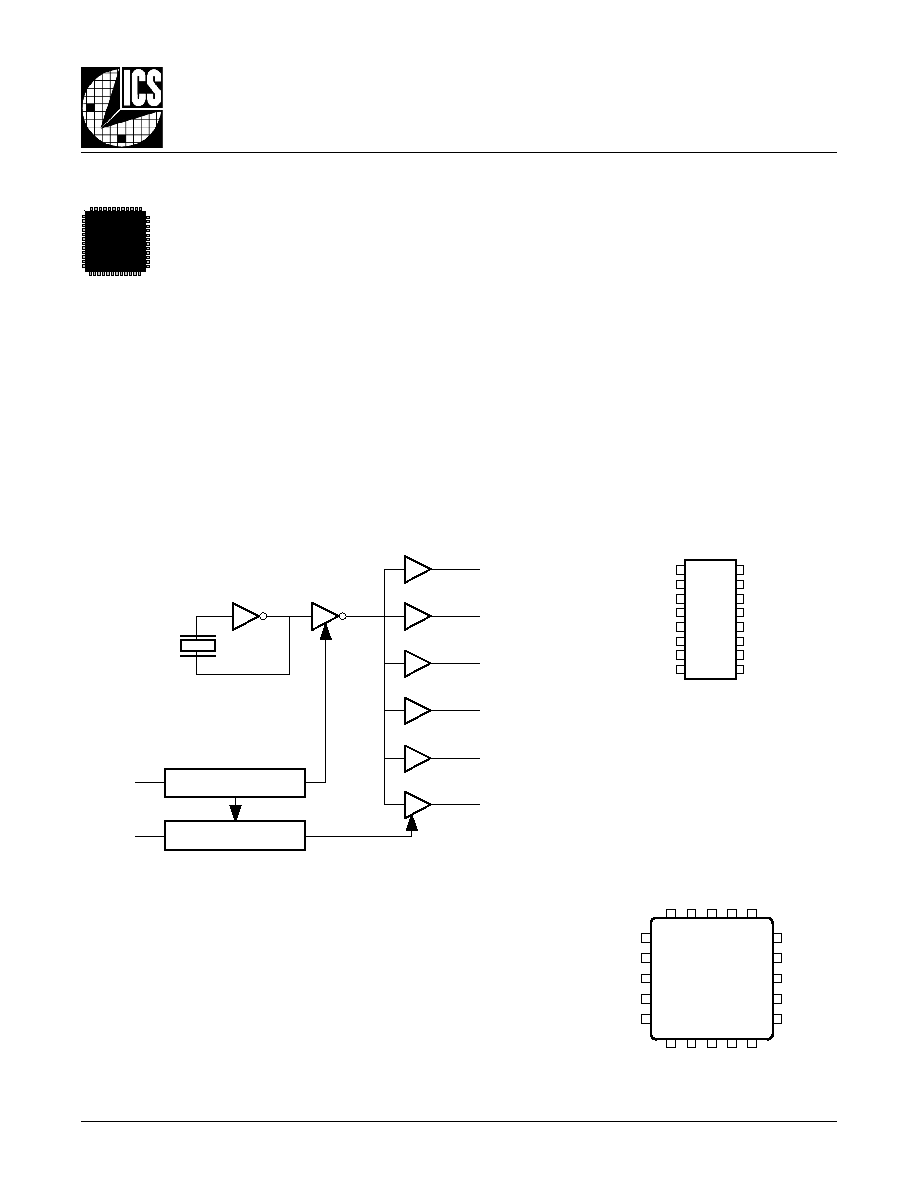

- Pin Descriptions

- Pin Characteristics

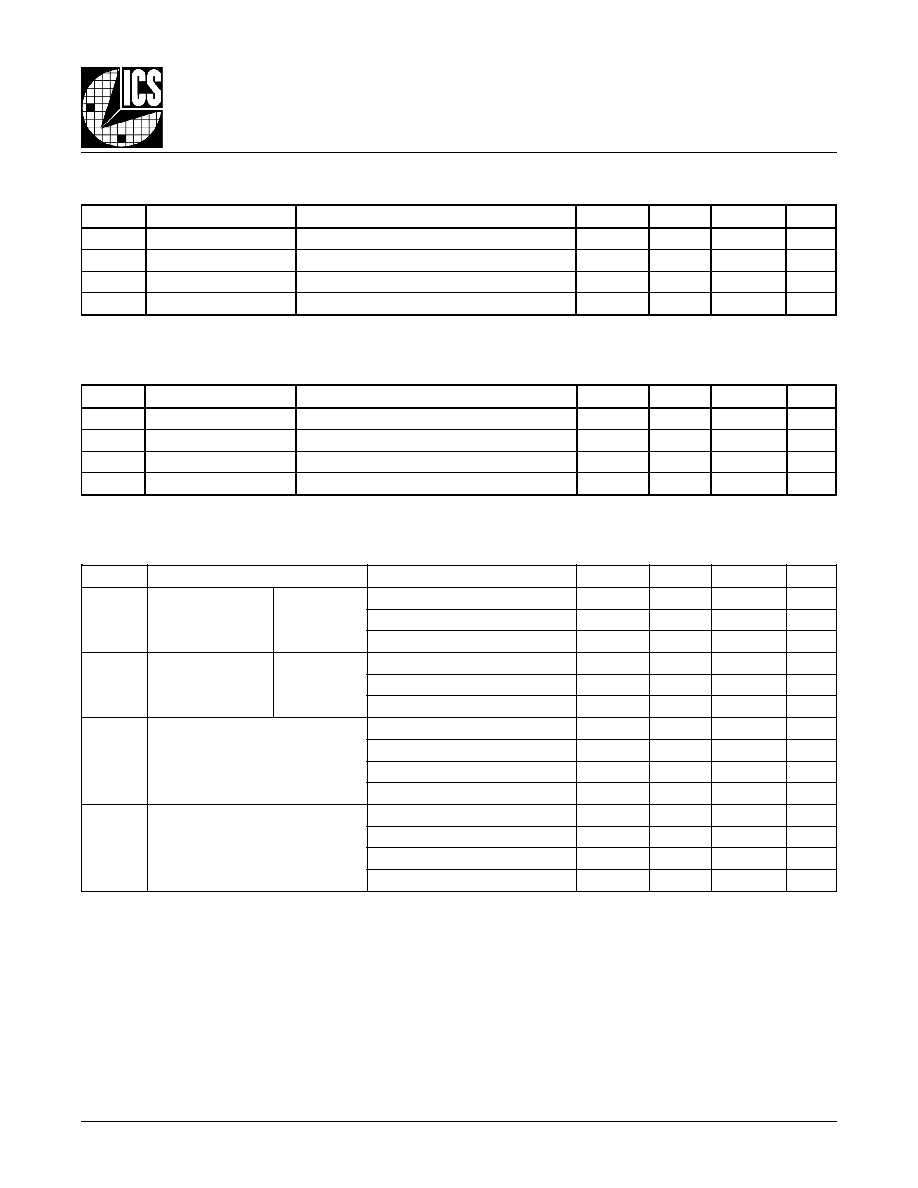

- Output Enable & Clock Enable Function Table

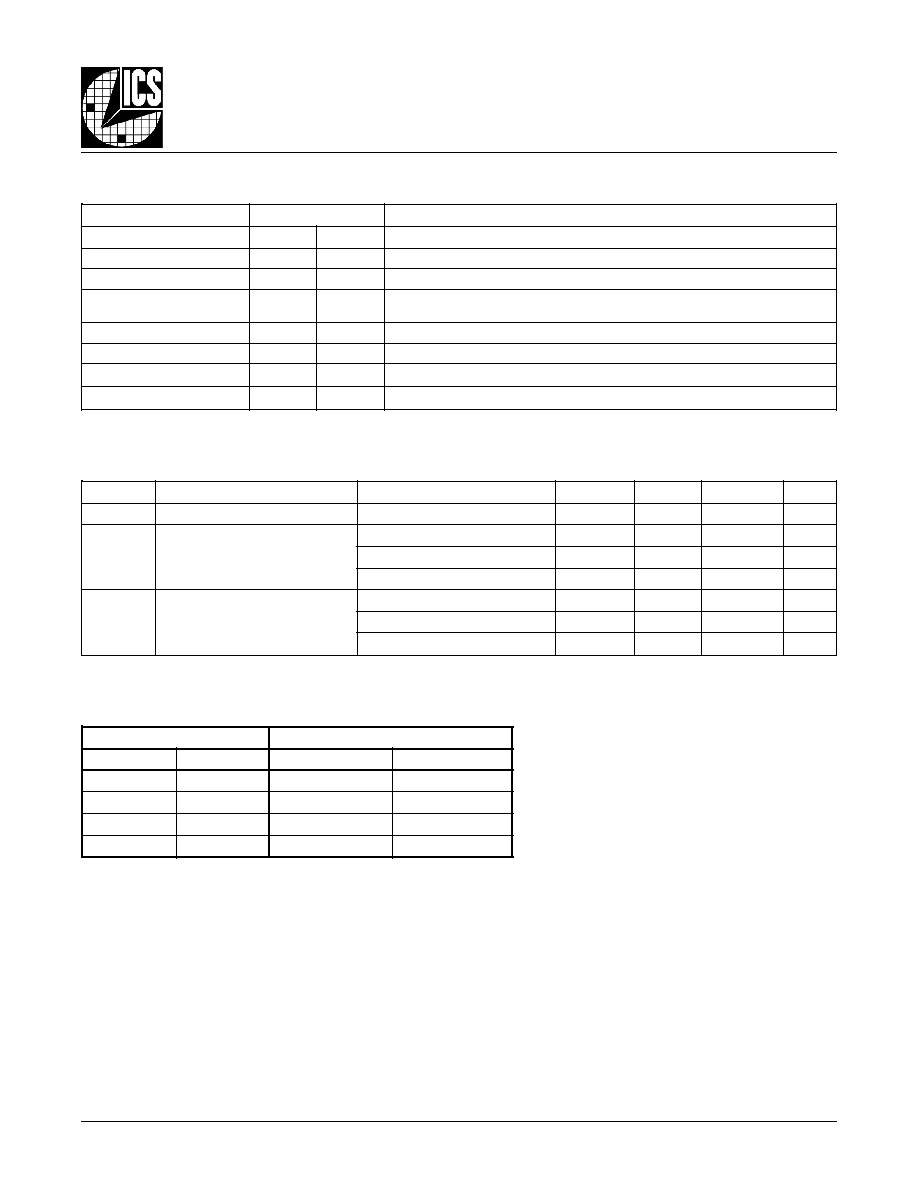

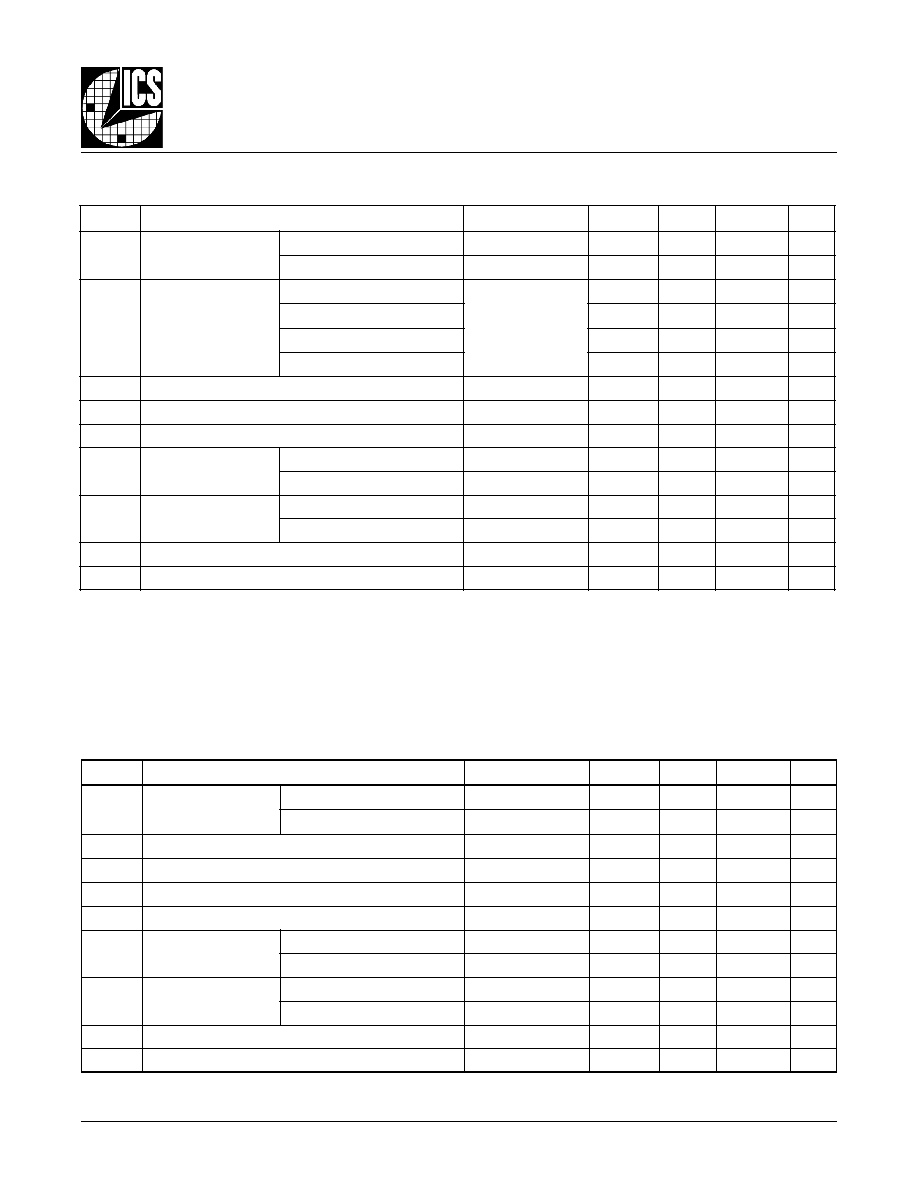

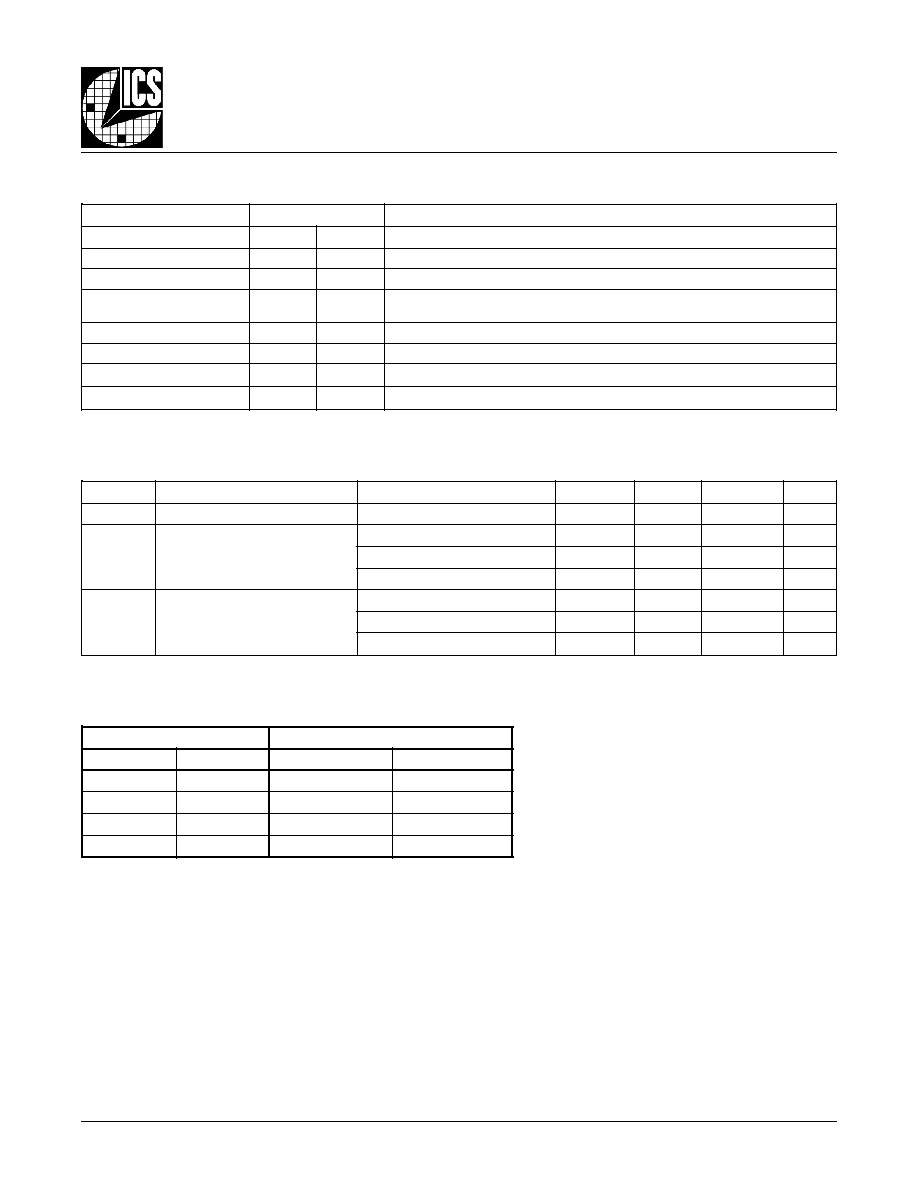

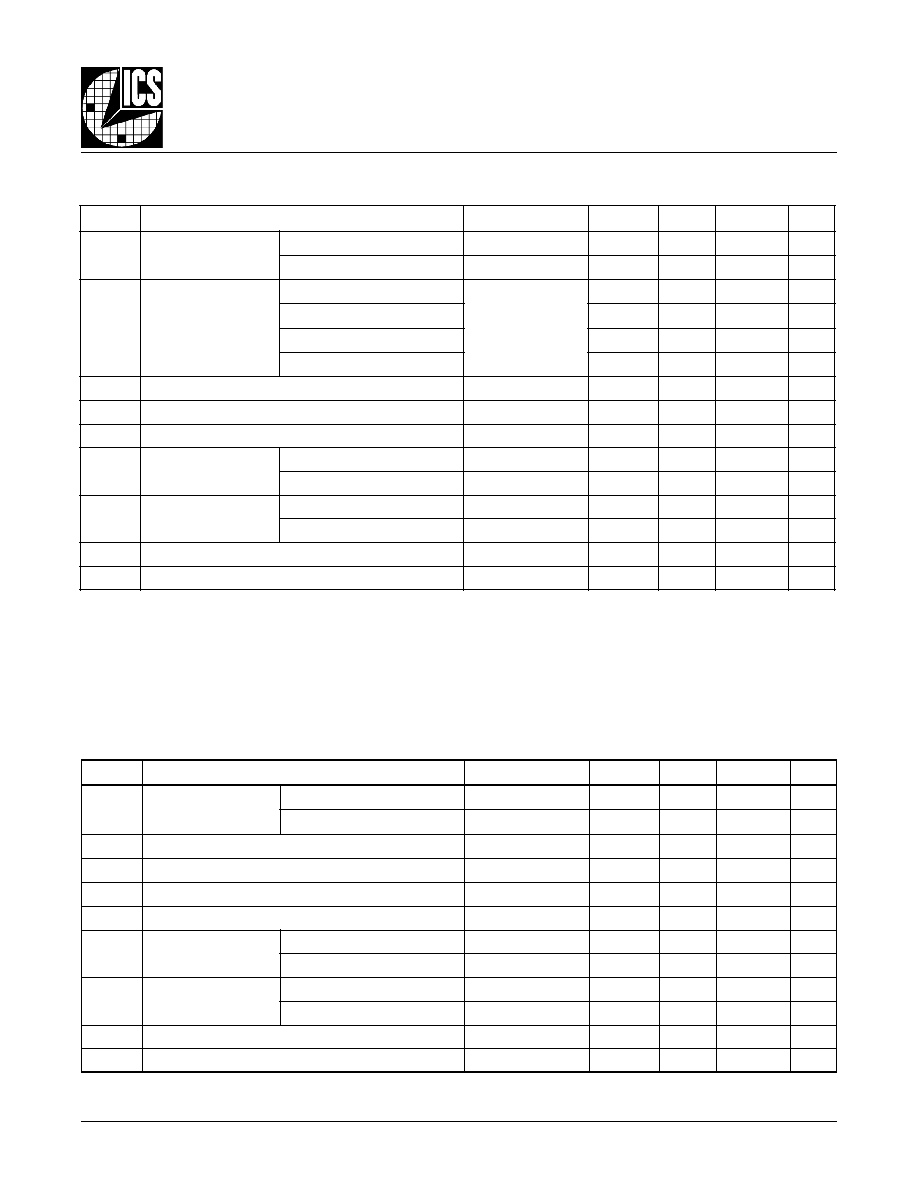

- Power Supply 3.3V DC Characteristics

- Power Supply 2.5V DC Characteristics

- Power Supply 1.8V DC Characteristics

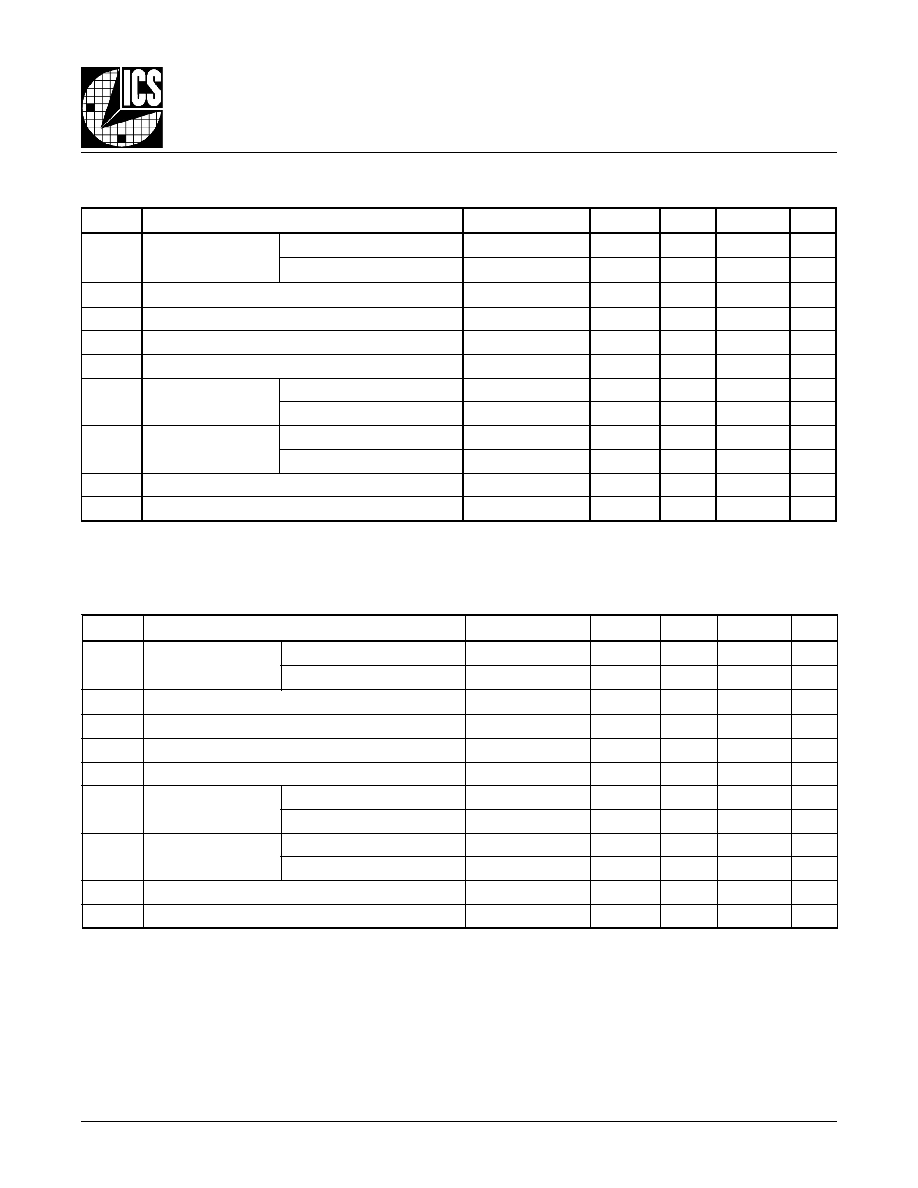

- Power Supply 3.3V/2.5V DC Characteristics

- Power Supply 3.3V/1.8V DC Characteristics

- Power Supply 2.5V/1.8V DC Characteristics

- LVCMOS DC Characteristics

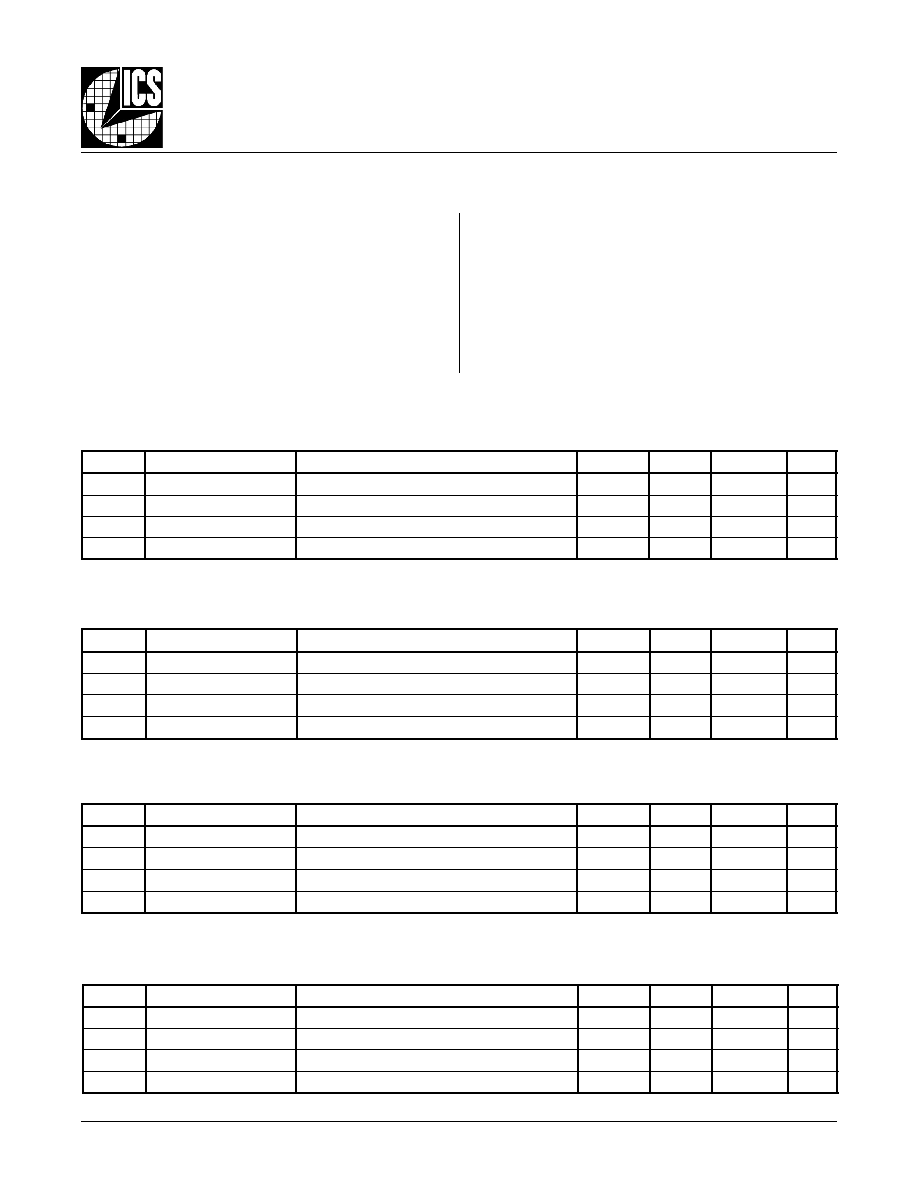

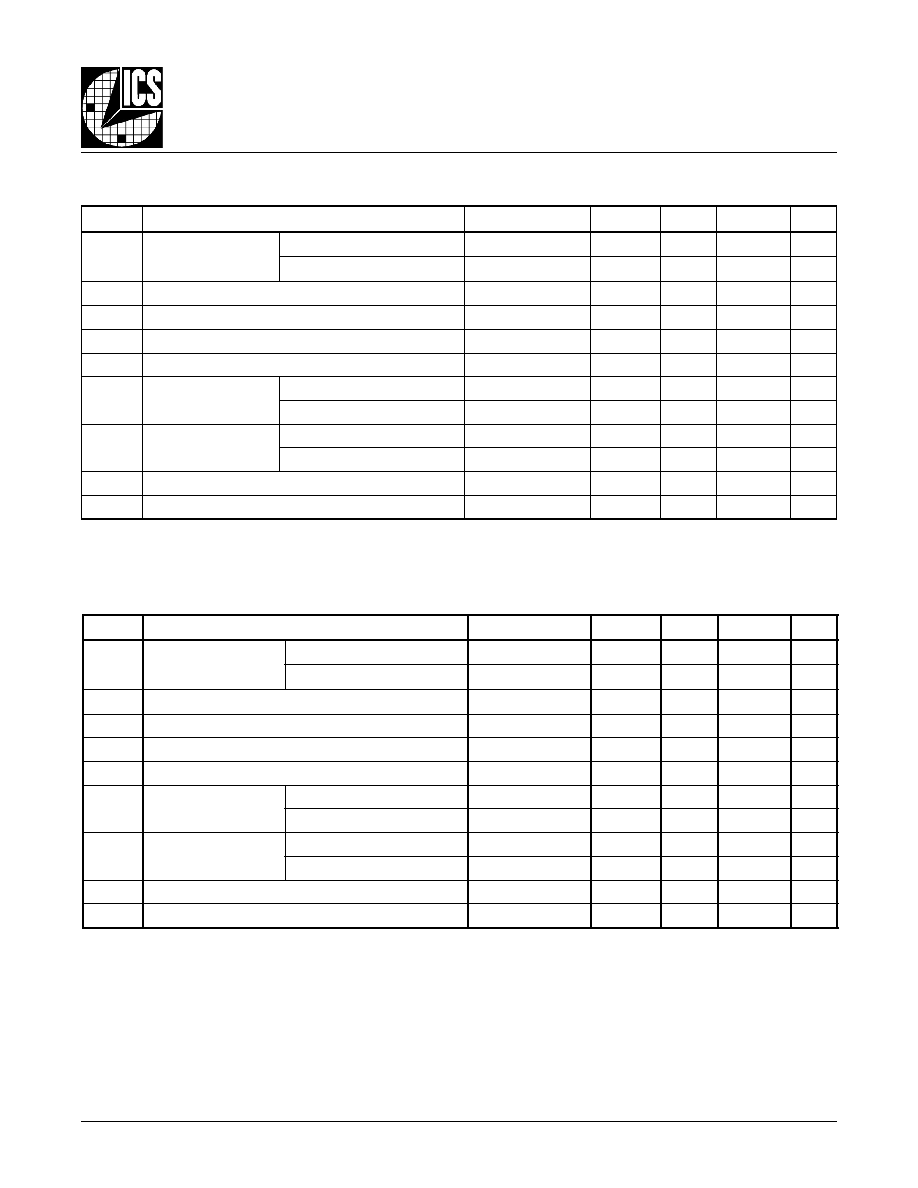

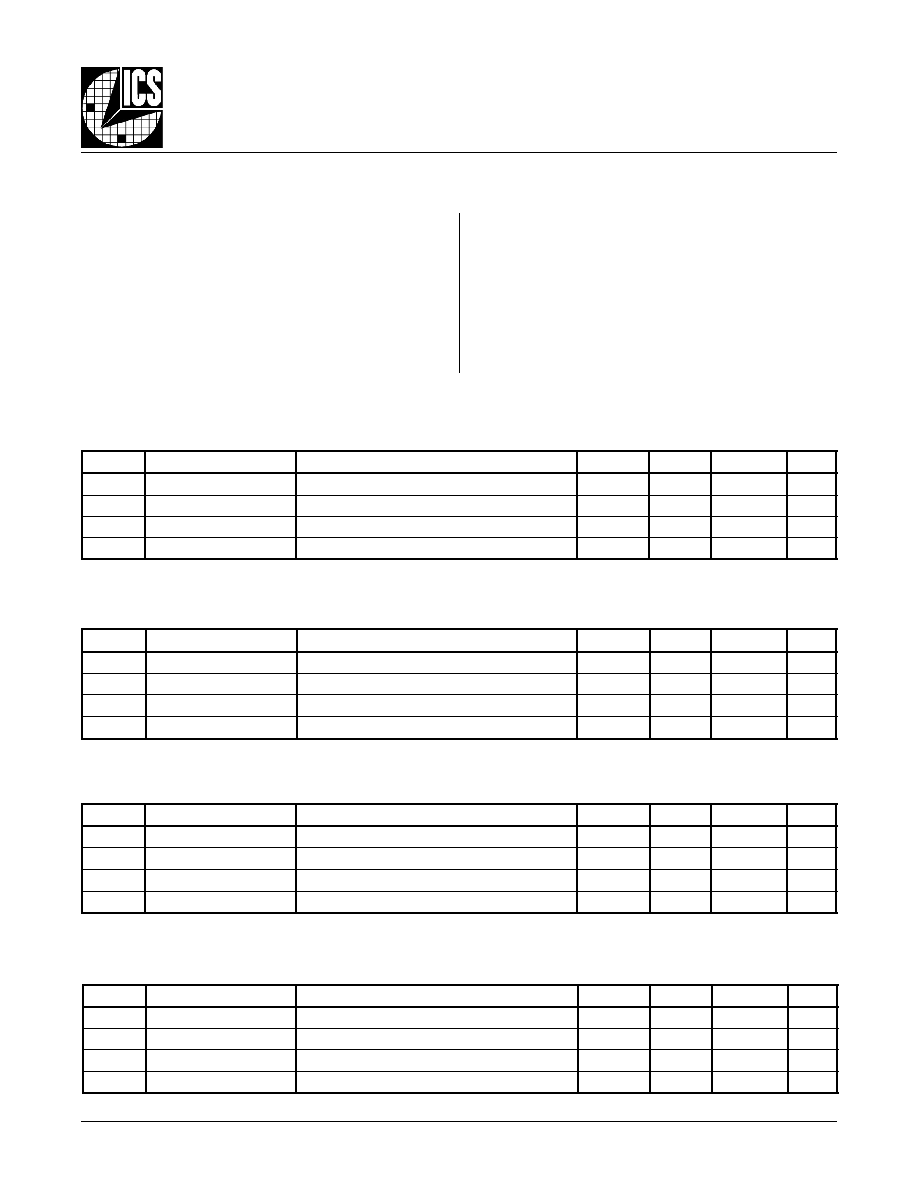

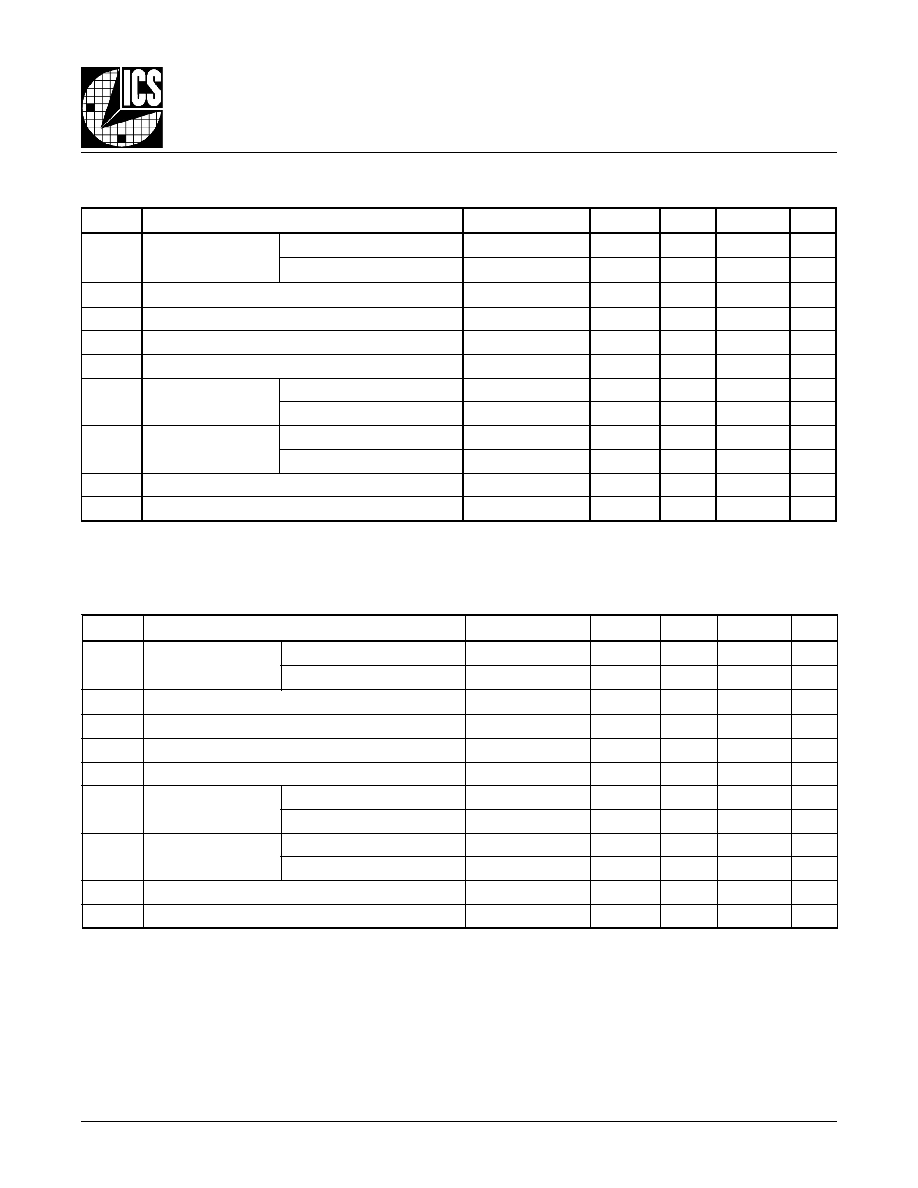

- 3.3V AC Characteristics

- 2.5V AC Characteristics

- 1.8V AC Characteristics

- 3.3V/2.5V AC Characteristics

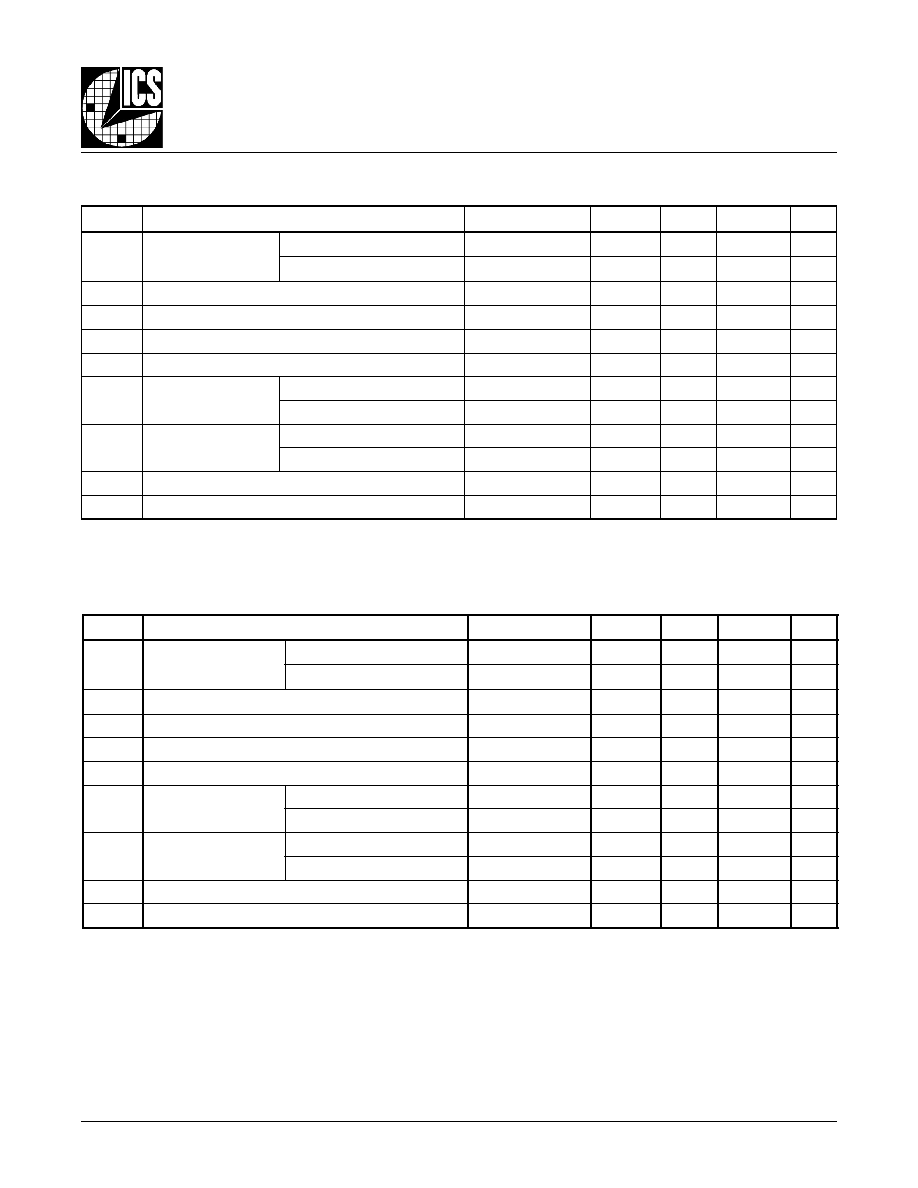

- 3.3V/1.8V AC Characteristics

- 2.5V/1.8V AC Characteristics

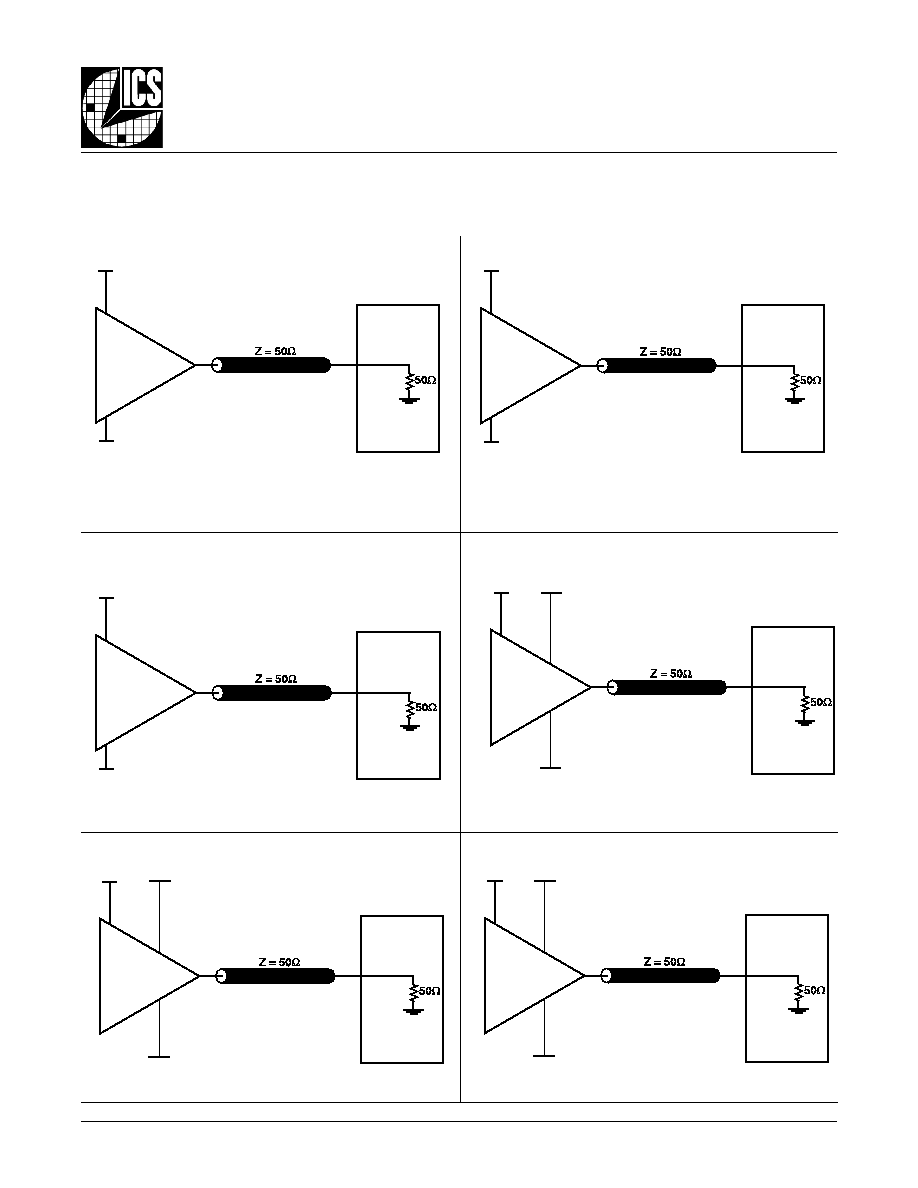

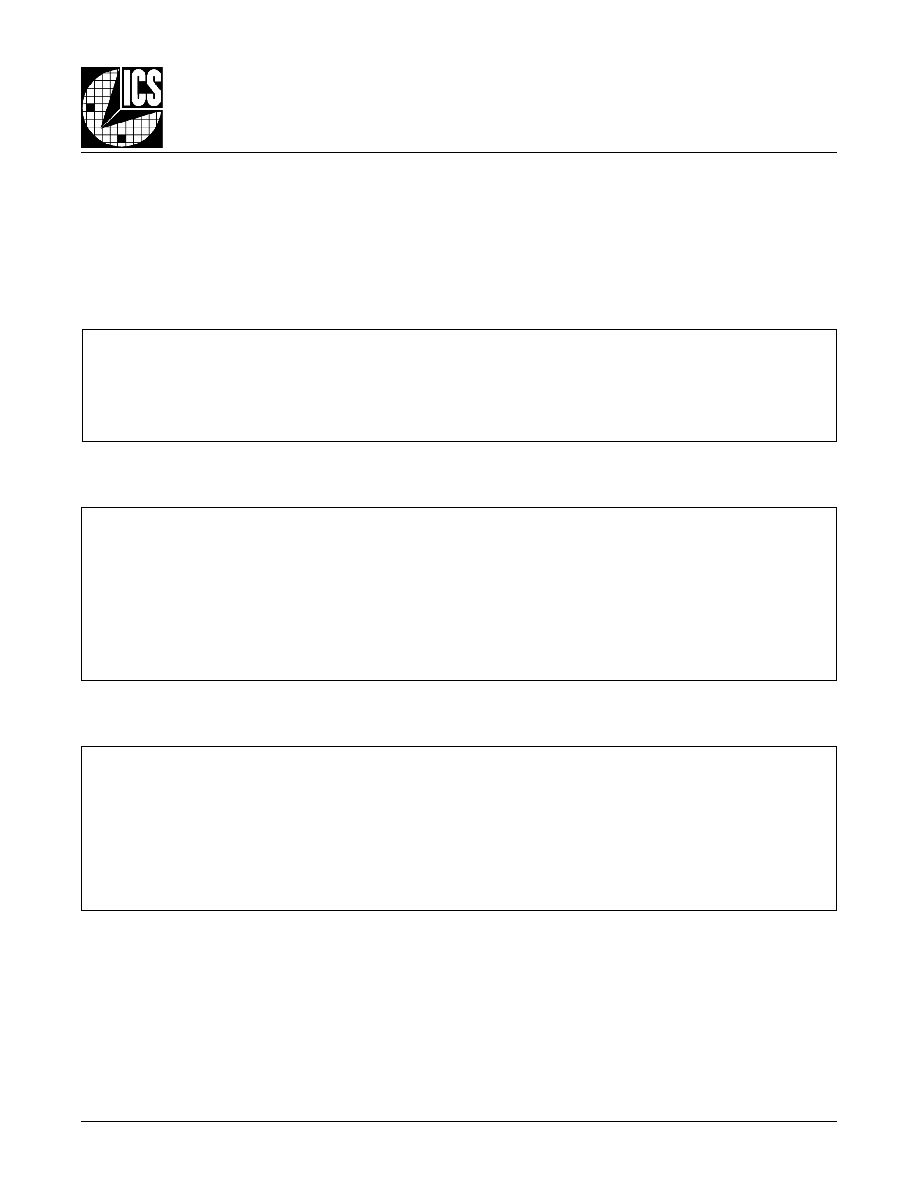

- Parameter Measurement Information

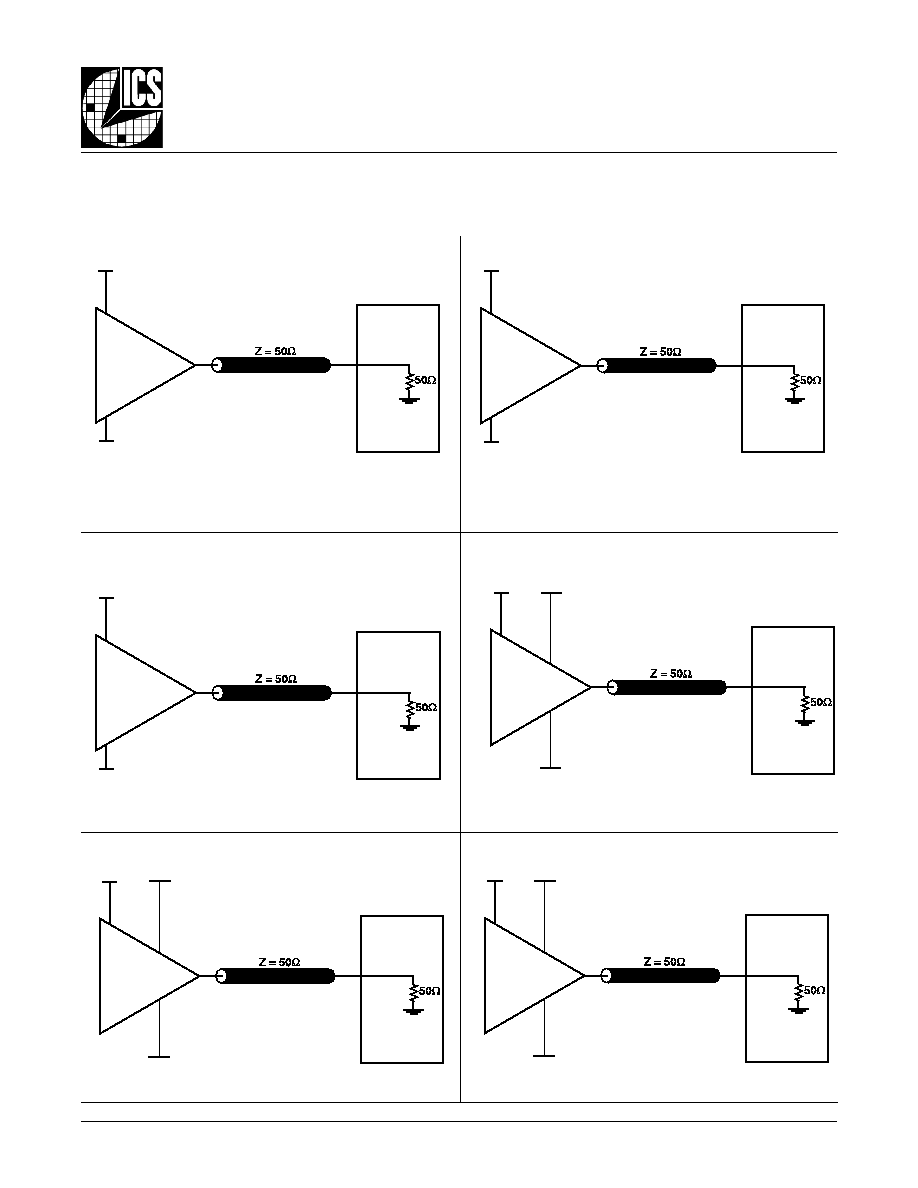

- 3.3V Core/3.3V Output Load AC Test Circuit Diagram

- 2.5V Core/2.5V Output Load AC Test Circuit Diagram

- 1.8V Core/1.8V Output Load AC Test Circuit Diagram

- 3.3V Core/2.5V Output Load AC Test Circuit Diagram

- 3.3V Core/1.8V Output Load AC Test Circuit Diagram

- 2.5V Core/1.8V Output Load AC Test Circuit Diagram

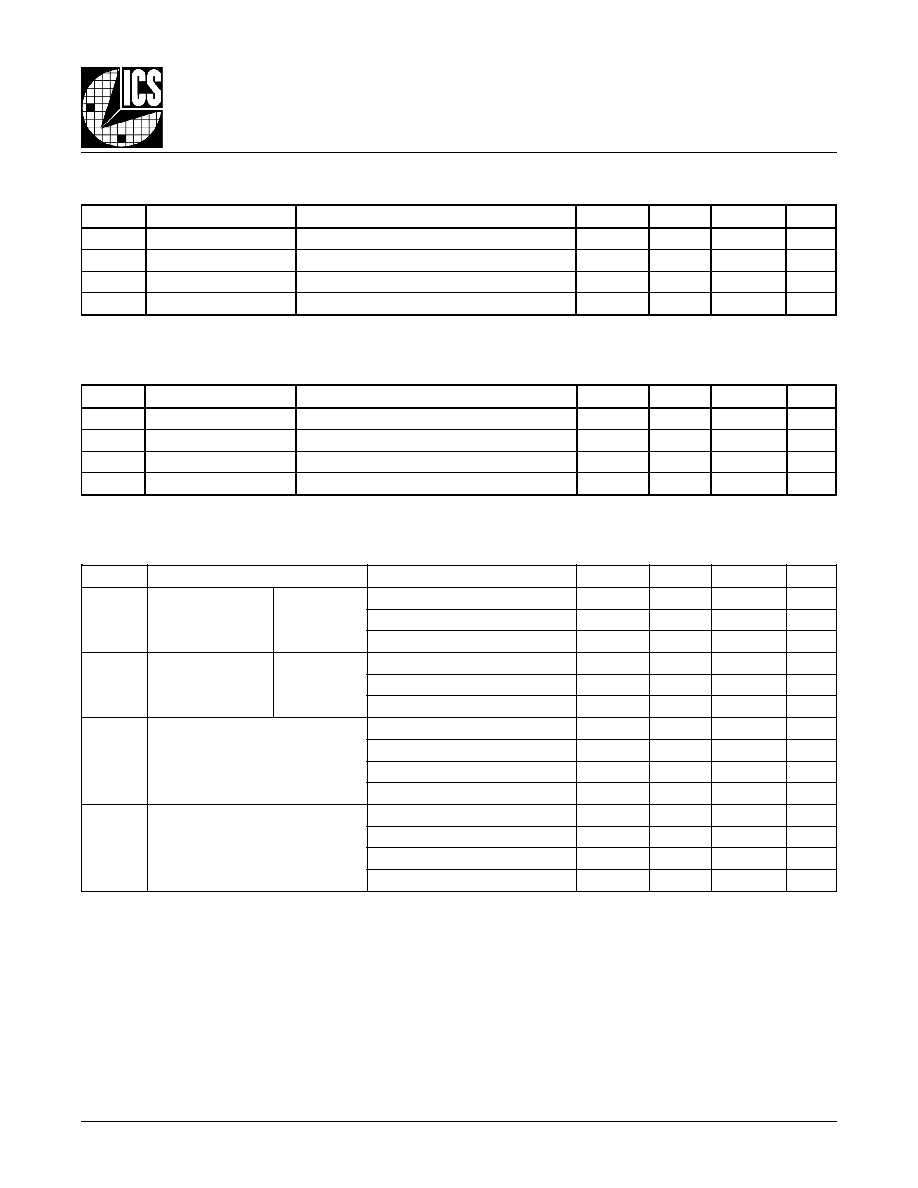

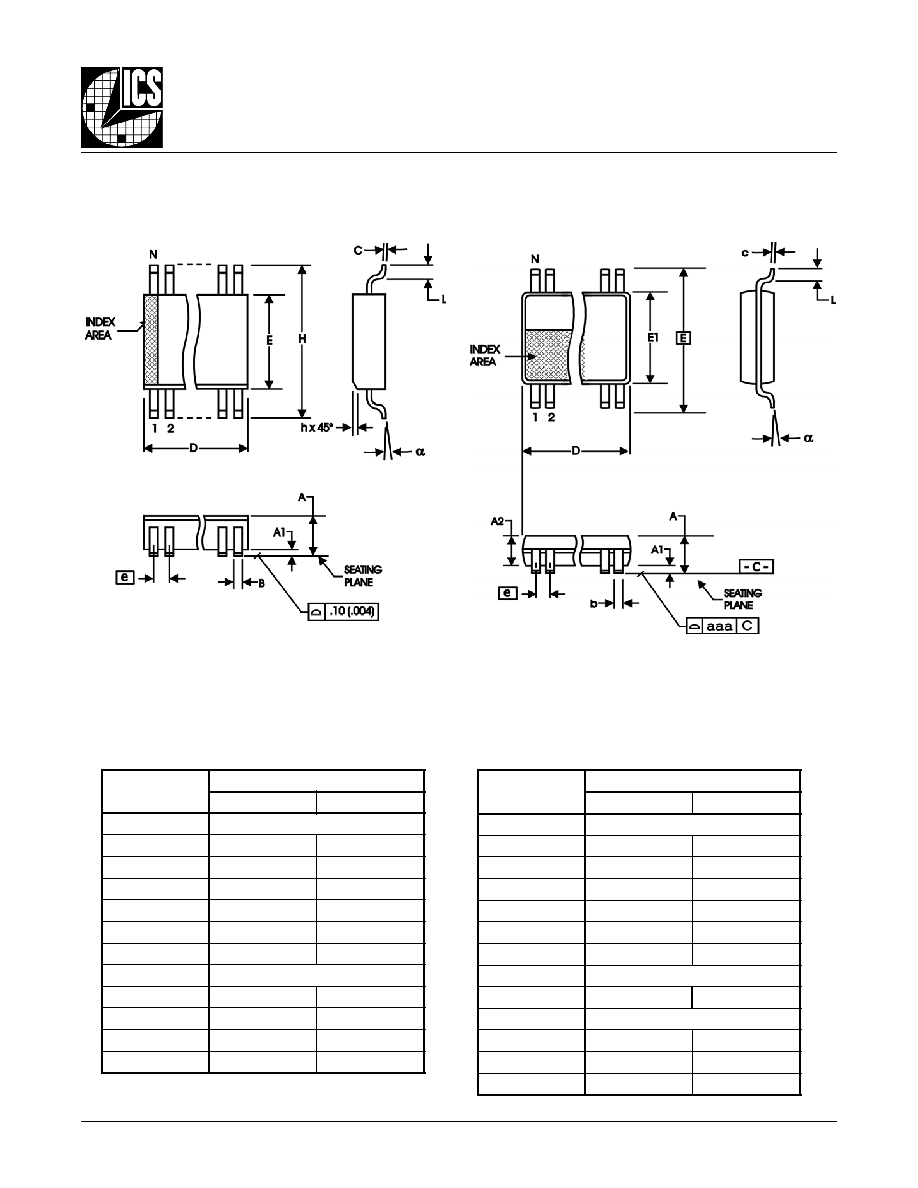

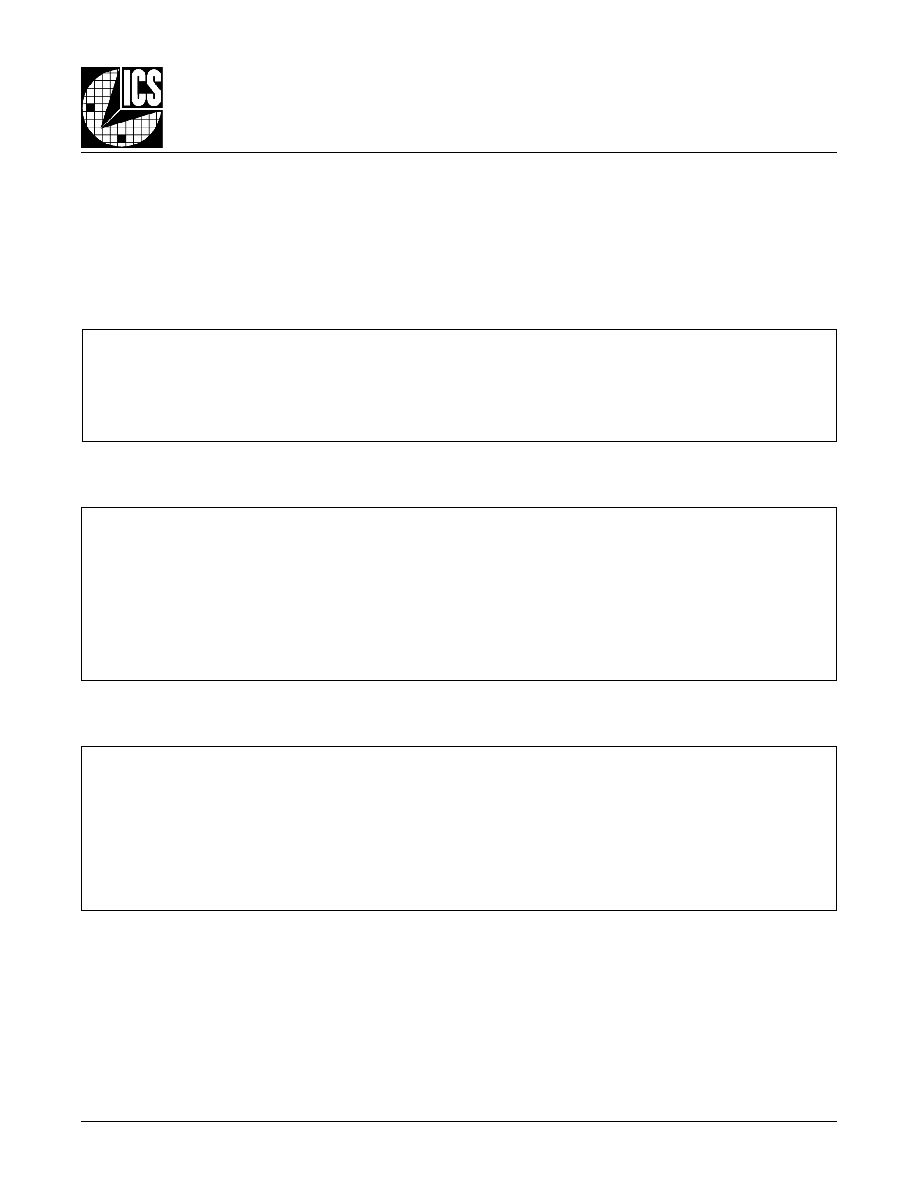

- Output Skew Diagram

- Output Duty Cycle/Pulse Width/Period Diagram

- Output Rise/Fall Time Diagram

- Application Information

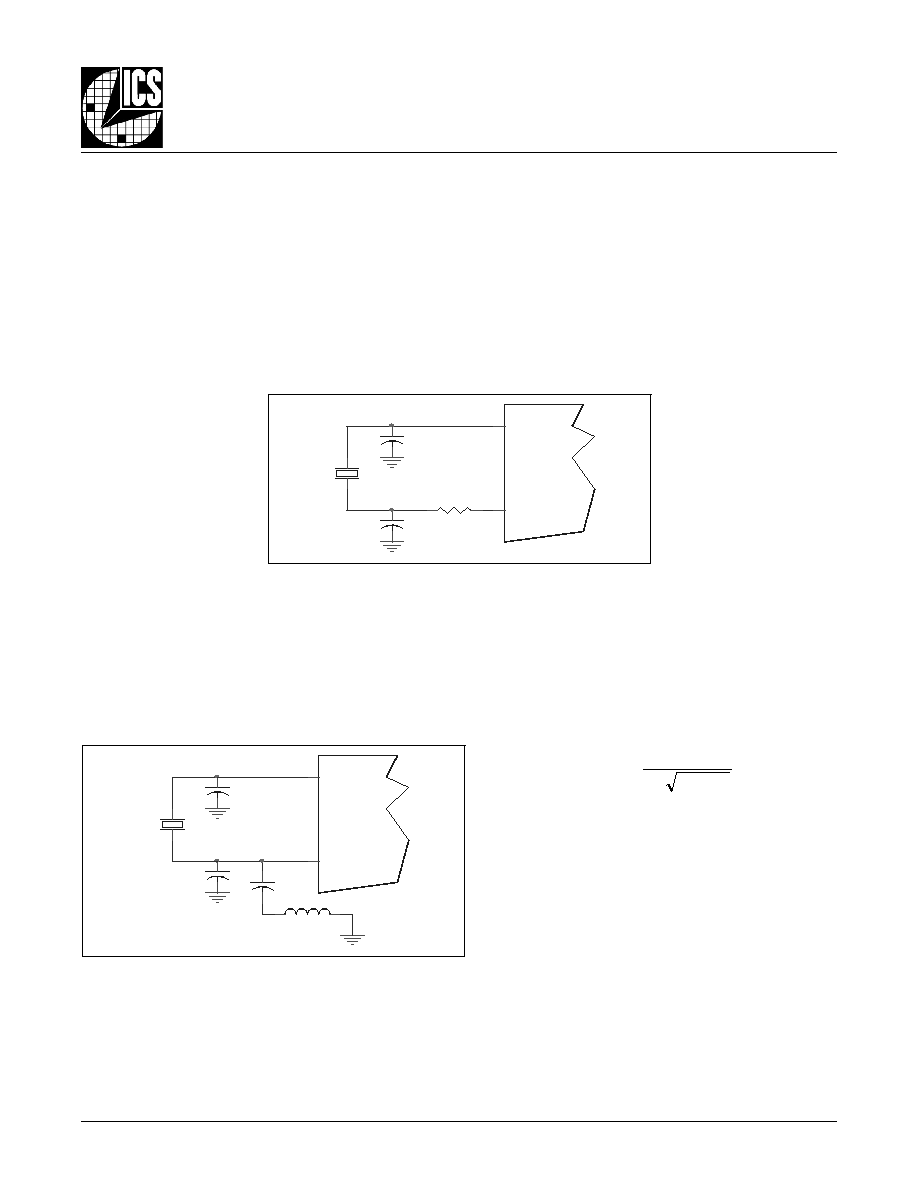

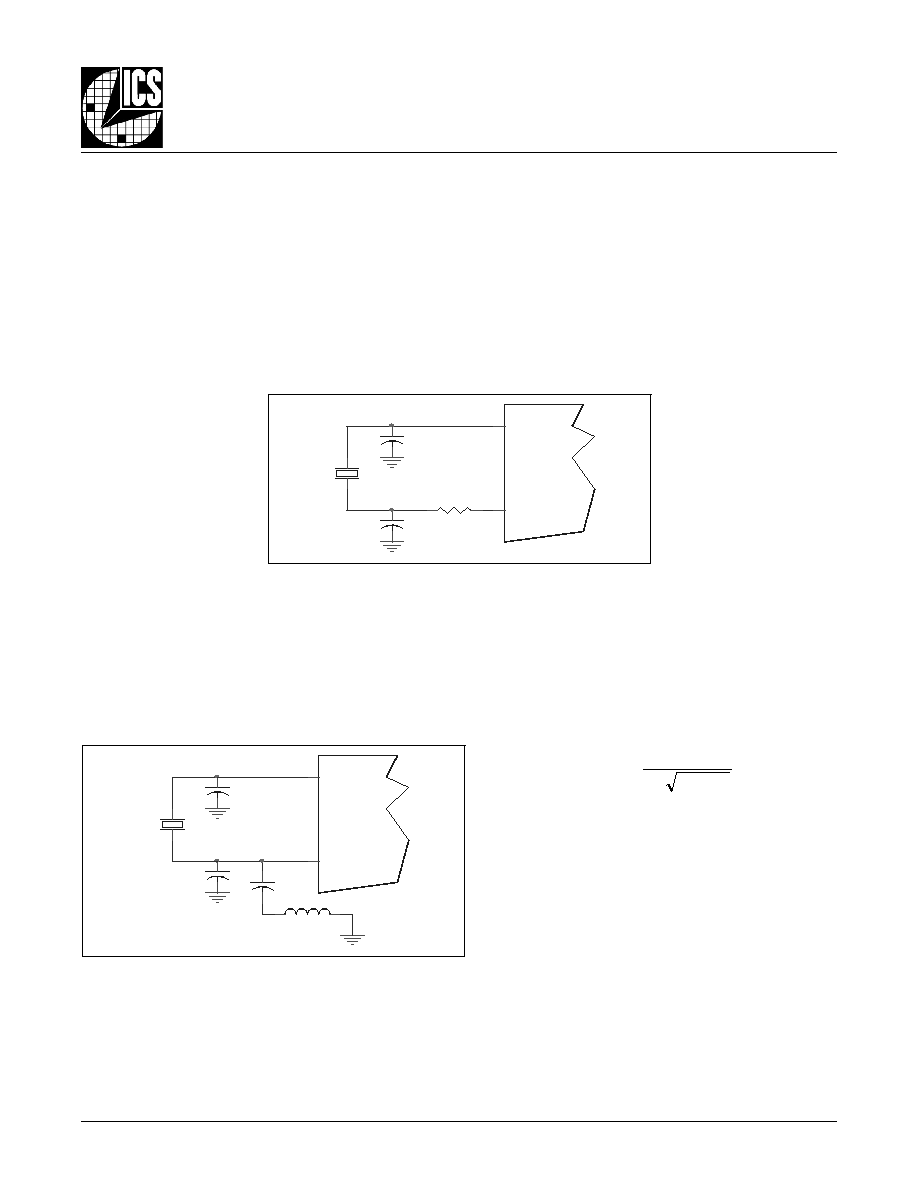

- Crystal Input Interface, Fundamental

- Crystal Input Interface 3rd Overtone

- Reliability Information

- Transistor Count

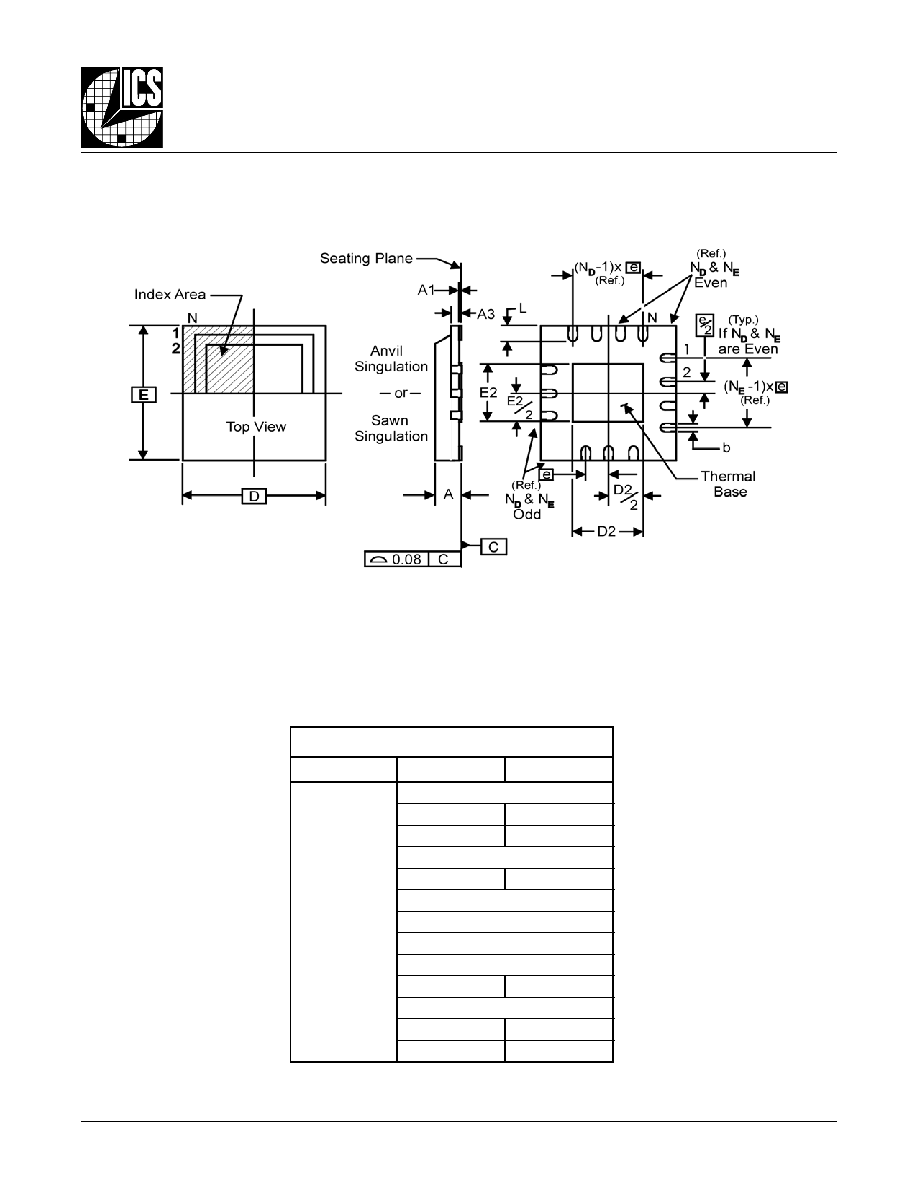

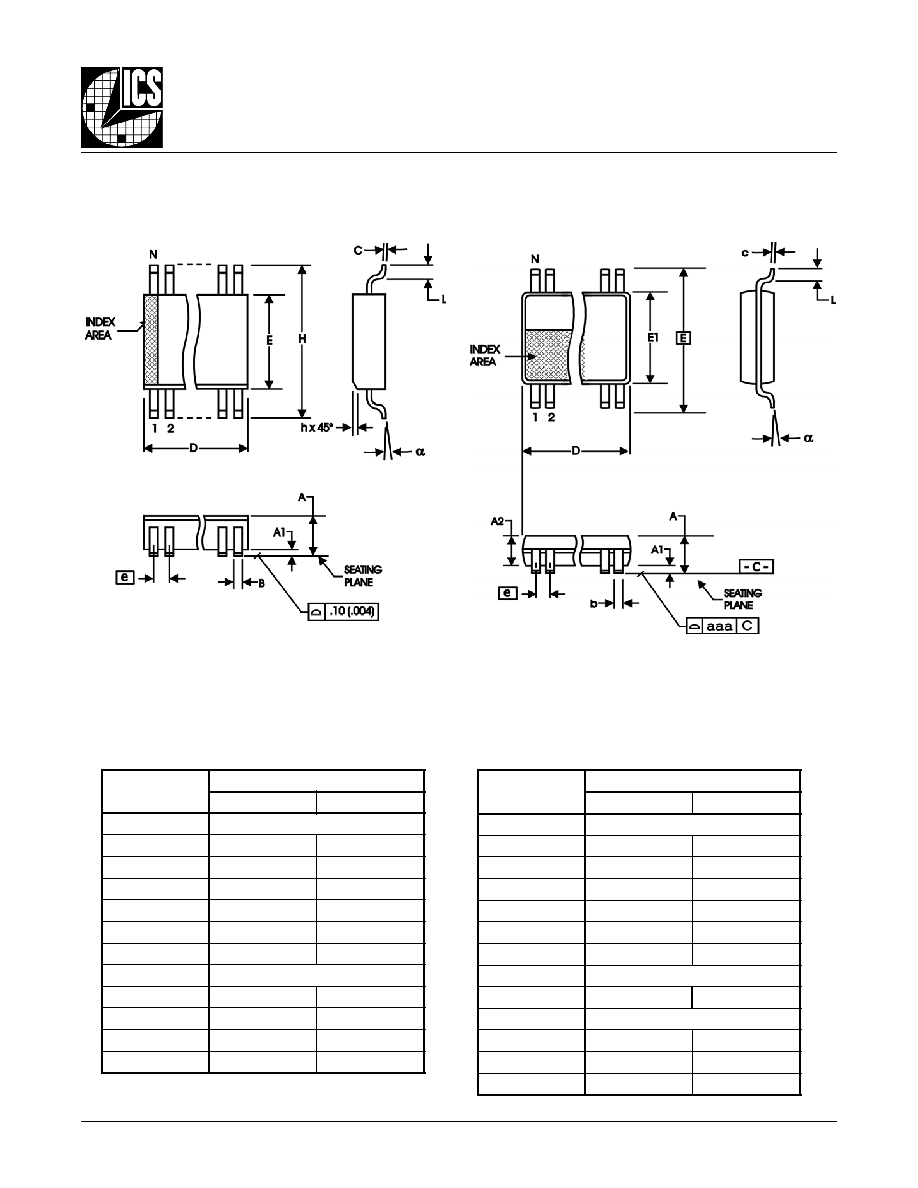

- Package Outline, SOIC

- Package Dimensions, SOIC

- Package Outline, TSSOP

- Package Dimensions, TSSOP

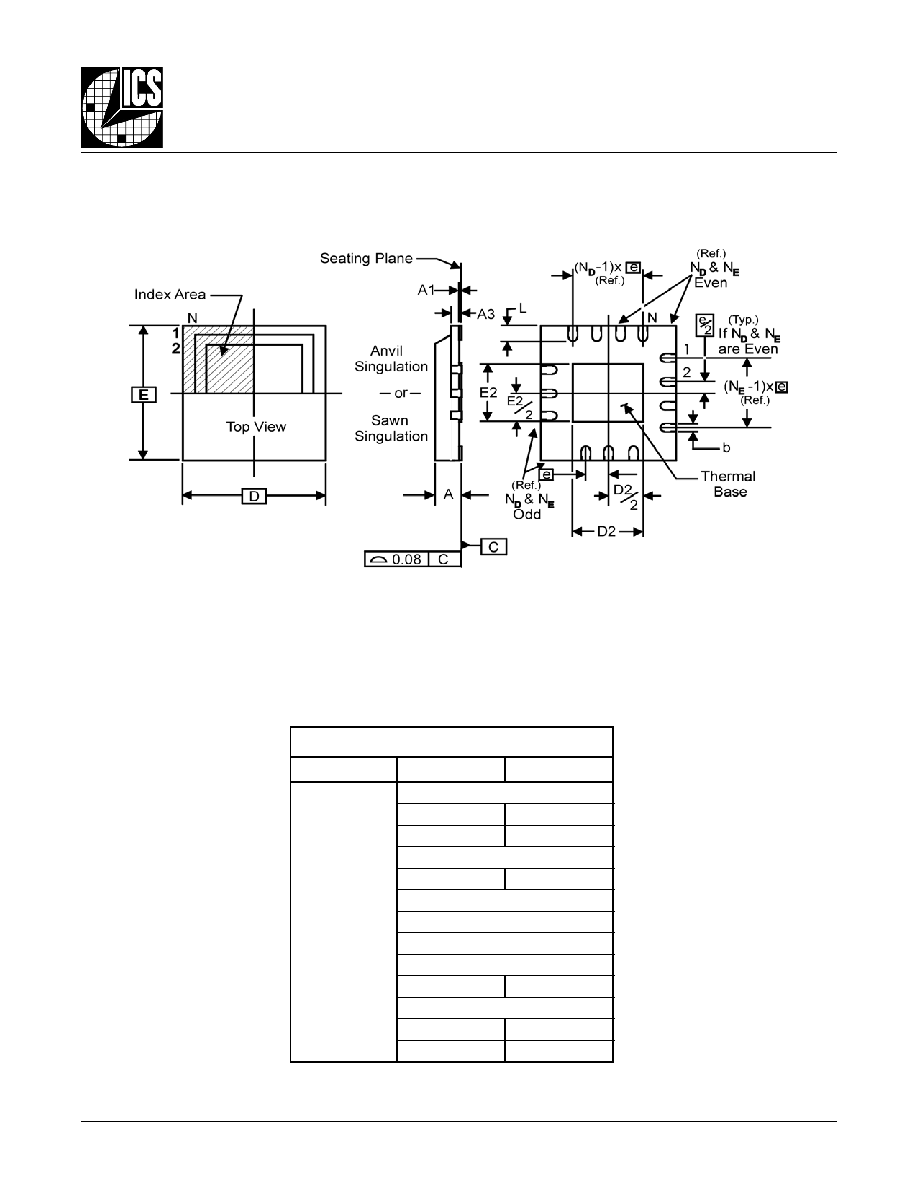

- Package Outline, VFQFN

- Package Dimensions, VFQFN

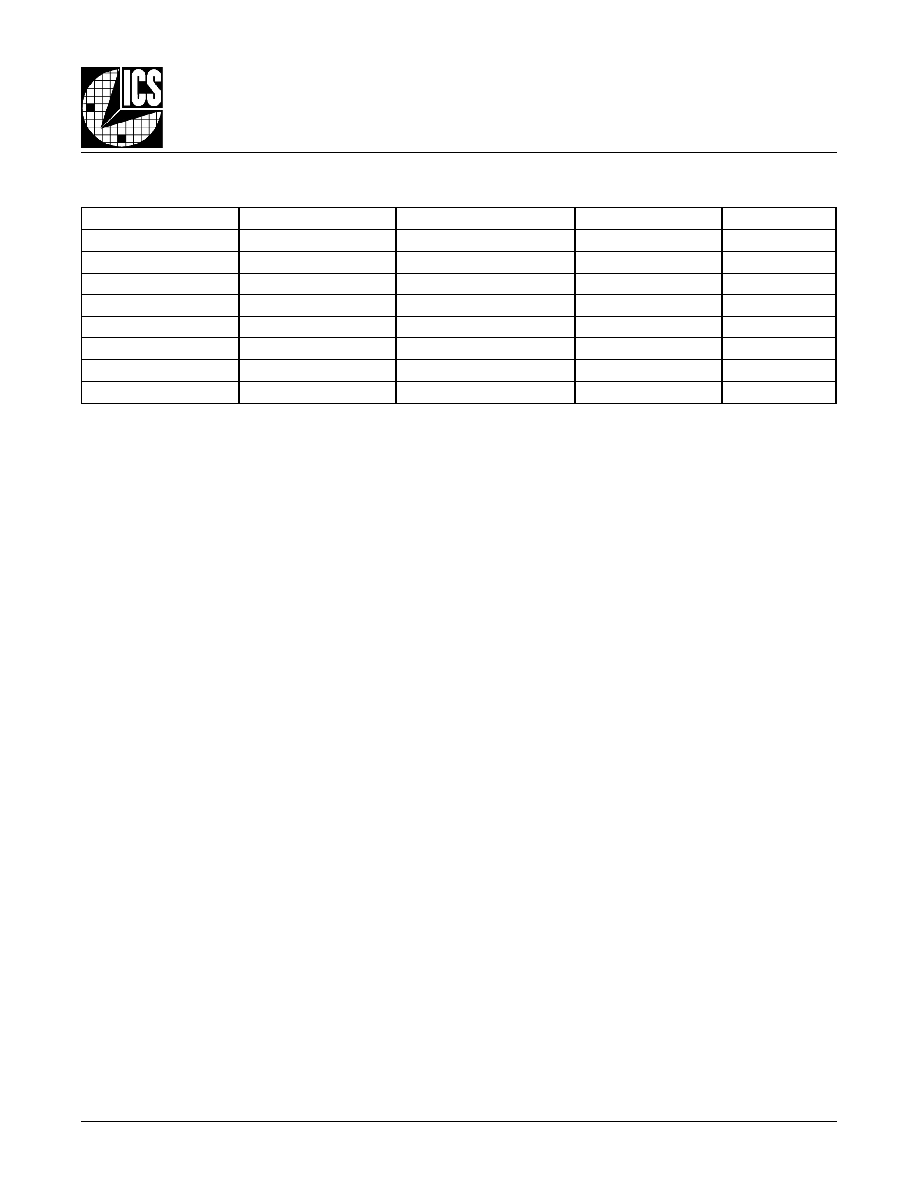

- Ordering Information

83905AM

http://www.icst.com/products/hiperclocks.html

REV. A JANUARY 20, 2005

1

Integrated

Circuit

Systems, Inc.

ICS83905

L

OW

S

KEW

, 1:6 C

RYSTAL

I

NTERFACE

-

TO

-

LVCMOS / LVTTL F

ANOUT

B

UFFER

PRELIMINARY

G

ENERAL

D

ESCRIPTION

The ICS83905 is a low skew, 1-to-6 LVCMOS /

LVTTL Fanout Buffer and a member of the

HiPerClockSTM family of High Performance Clock

Solutions from ICS. The ICS83905 single ended

clock input accepts LVCMOS or LVTTL input lev-

els. The low impedance LVCMOS/LVTTL outputs are designed

to drive 50

series or parallel terminated transmission lines.

The effective fanout can be increased from 6 to 12 by utilizing

the ability of the outputs to drive two series terminated lines.

The ICS83905 is characterized at full 3.3V, 2.5V, and 1.8V,

mixed 3.3V/2.5V, 3.3V/1.8V and 2.5V/1.8V output operating

supply mode. Guaranteed output and part-to-part skew char-

acteristics along with the 1.8V output capabilities makes the

ICS83905 ideal for high performance, single ended applica-

tions that also require a limited output voltage.

B

LOCK

D

IAGRAM

P

IN

A

SSIGNMENT

F

EATURES

∑ 6 LVCMOS / LVTTL outputs

∑ Crystal oscillator interface

∑ Output frequency range: 10MHz to 50MHz

∑ Crystal input frequency range: 10MHz to 50MHz

∑ Output skew: 10ps (typical)

∑ 5V tolerant enable inputs

∑ Synchronous output enables

∑ Operating supply modes: Full 3.3V, 2.5V and 1.8V,

mixed 3.3Vcore/2.5V or1.8V operating supply, and

mixed 2.5V core/1.8V operating supply

∑ 0∞C to 70∞C ambient operating temperature

∑ Lead-Free package fully RoHS compliant

∑ Pin compatible to MPC905

∑ Industrial version available upon request

HiPerClockSTM

ICS

ICS83905

16-Lead SOIC

3.9mm x 9.9mm x 1.38mm body package

M Pacakge

Top View

ICS83905

16-Lead TSSOP

4.4mm x 3.0mm x 0.92mm body package

G Pacakge

Top View

SYNCHRONIZE

SYNCHRONIZE

BCLK0

BCLK1

BCLK2

BCLK3

BCLK4

BCLK5

ENABLE 1

ENABLE 2

XTAL_IN

XTAL_OUT

XTAL_OUT

ENABLE 2

GND

BCLK0

V

DD

o

BCLK1

GND

BCLK2

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

XTAL_IN

ENABLE 1

BCLK5

V

DDO

BCLK4

GND

BCLK3

V

DD

The Preliminary Information presented herein represents a product in prototyping or pre-production. The noted characteristics are based on initial

product characterization. Integrated Circuit Systems, Incorporated (ICS) reserves the right to change any circuitry or specifications without notice.

20 19 18 17 16

6 7 8 9 10

1

2

3

4

5

15

14

13

12

11

ENABLE2

XT

AL_OUT

XT

AL_IN

ENABLE1

nc

BCLK5

V

DDO

BCLK4

GND

GND

GND

GND

BCLK0

V

DDO

BCLK1

GND

GND

BCLK2

V

DD

BCLK3

ICS83905

20-Lead VFQFN

4mm x 4mm x 0.9mm

body package

K Package

Top View

83905AM

http://www.icst.com/products/hiperclocks.html

REV. A JANUARY 20, 2005

2

Integrated

Circuit

Systems, Inc.

ICS83905

L

OW

S

KEW

, 1:6 C

RYSTAL

I

NTERFACE

-

TO

-

LVCMOS / LVTTL F

ANOUT

B

UFFER

PRELIMINARY

T

ABLE

1. P

IN

D

ESCRIPTIONS

T

ABLE

2. P

IN

C

HARACTERISTICS

T

ABLE

3. O

UTPUT

E

NABLE

AND

C

LOCK

E

NABLE

F

UNCTION

T

ABLE

e

m

a

N

e

p

y

T

n

o

i

t

p

i

r

c

s

e

D

T

U

O

_

L

A

T

X

t

u

p

t

u

O

.

t

u

p

t

u

o

e

h

t

s

i

T

U

O

_

L

A

T

X

.

e

c

a

f

r

e

t

n

i

r

o

t

a

ll

i

c

s

o

l

a

t

s

y

r

C

N

I

_

L

A

T

X

t

u

p

n

I

.

t

u

p

n

i

e

h

t

s

i

N

I

_

L

A

T

X

.

e

c

a

f

r

e

t

n

i

r

o

t

a

ll

i

c

s

o

l

a

t

s

y

r

C

2

E

L

B

A

N

E

,

1

E

L

B

A

N

E

t

u

p

n

I

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

e

l

b

a

n

e

t

u

p

t

u

O

,

2

K

L

C

B

,

1

K

L

C

B

,

0

K

L

C

B

5

K

L

C

B

,

4

K

L

C

B

,

3

K

L

C

B

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

s

t

u

p

t

u

o

k

c

o

l

C

D

N

G

r

e

w

o

P

.

d

n

u

o

r

g

y

l

p

p

u

s

r

e

w

o

P

V

D

D

r

e

w

o

P

.

n

i

p

y

l

p

p

u

s

e

r

o

C

V

O

D

D

r

e

w

o

P

.

n

i

p

y

l

p

p

u

s

t

u

p

t

u

O

c

/

n

d

e

s

u

n

U

.

t

c

e

n

n

o

c

o

N

s

t

u

p

n

I

l

o

r

t

n

o

C

s

t

u

p

t

u

O

1

E

L

B

A

N

E

2

E

L

B

A

N

E

4

K

L

C

B

:

0

K

L

C

B

5

K

L

C

B

0

0

W

O

L

W

O

L

0

1

W

O

L

g

n

il

g

g

o

T

1

0

g

n

il

g

g

o

T

W

O

L

1

1

g

n

il

g

g

o

T

g

n

il

g

g

o

T

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

C

N

I

e

c

n

a

t

i

c

a

p

a

C

t

u

p

n

I

4

F

p

C

D

P

e

c

n

a

t

i

c

a

p

a

C

n

o

i

t

a

p

i

s

s

i

D

r

e

w

o

P

)

t

u

p

t

u

o

r

e

p

(

V

O

D

D

V

5

6

4

.

3

=

9

1

F

p

V

O

D

D

V

5

2

6

.

2

=

8

1

F

p

V

O

D

D

V

2

=

6

1

F

p

R

T

U

O

e

c

n

a

d

e

p

m

I

t

u

p

t

u

O

V

O

D

D

%

5

±

V

3

.

3

=

5

7

2

1

V

O

D

D

%

5

±

V

5

.

2

=

7

V

O

D

D

V

2

.

0

±

V

8

.

1

=

0

1

83905AM

http://www.icst.com/products/hiperclocks.html

REV. A JANUARY 20, 2005

3

Integrated

Circuit

Systems, Inc.

ICS83905

L

OW

S

KEW

, 1:6 C

RYSTAL

I

NTERFACE

-

TO

-

LVCMOS / LVTTL F

ANOUT

B

UFFER

PRELIMINARY

T

ABLE

4A. P

OWER

S

UPPLY

DC C

HARACTERISTICS

,

V

DD

= V

DDO

= 3.3V±5%, T

A

= 0∞C

TO

70∞C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

e

r

o

C

5

3

1

.

3

3

.

3

5

6

4

.

3

V

V

O

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

t

u

p

t

u

O

5

3

1

.

3

3

.

3

5

6

4

.

3

V

I

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

r

e

w

o

P

D

B

T

A

µ

I

O

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

t

u

p

t

u

O

D

B

T

A

µ

T

ABLE

4B. P

OWER

S

UPPLY

DC C

HARACTERISTICS

,

V

DD

= V

DDO

= 2.5V±5%, T

A

= 0∞C

TO

70∞C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

e

r

o

C

5

7

3

.

2

5

.

2

5

2

6

.

2

V

V

O

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

t

u

p

t

u

O

5

7

3

.

2

5

.

2

5

2

6

.

2

V

I

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

r

e

w

o

P

D

B

T

A

µ

I

O

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

t

u

p

t

u

O

D

B

T

A

µ

T

ABLE

4C. P

OWER

S

UPPLY

DC C

HARACTERISTICS

,

V

DD

= V

DDO

= 1.8V±0.2V, T

A

= 0∞C

TO

70∞C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

e

r

o

C

6

.

1

8

.

1

0

.

2

V

V

O

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

t

u

p

t

u

O

6

.

1

8

.

1

0

.

2

V

I

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

r

e

w

o

P

D

B

T

A

µ

I

O

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

t

u

p

t

u

O

D

B

T

A

µ

A

BSOLUTE

M

AXIMUM

R

ATINGS

Supply Voltage, V

DD

4.6V

Inputs, V

I

-0.5V to V

DD

+ 0.5 V

Outputs, V

O

-0.5V to V

DDO

+ 0.5V

Package Thermal Impedance,

JA

16 Lead SOIC package

78.8∞C/W (0 mps)

16 Lead TSSOP package

89∞C/W (0 lfpm)

20 Lead VFQFN package

38.5∞C/W (0 mps)

Storage Temperature, T

STG

-65∞C to 150∞C

NOTE: Stresses beyond those listed under Absolute

Maximum Ratings may cause permanent damage to the

device. These ratings are stress specifications only. Functional

operation of product at these conditions or any conditions be-

yond those listed in the

DC Characteristics or AC Character-

istics is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect product reliability.

T

ABLE

4D. P

OWER

S

UPPLY

DC C

HARACTERISTICS

,

V

DD

= 3.3V±5%, V

DDO

= 2.5V±5%, T

A

= 0∞C

TO

70∞C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

e

r

o

C

5

3

1

.

3

3

.

3

5

6

4

.

3

V

V

O

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

t

u

p

t

u

O

5

7

3

.

2

5

.

2

5

2

6

.

2

V

I

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

r

e

w

o

P

D

B

T

A

µ

I

O

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

t

u

p

t

u

O

D

B

T

A

µ

83905AM

http://www.icst.com/products/hiperclocks.html

REV. A JANUARY 20, 2005

4

Integrated

Circuit

Systems, Inc.

ICS83905

L

OW

S

KEW

, 1:6 C

RYSTAL

I

NTERFACE

-

TO

-

LVCMOS / LVTTL F

ANOUT

B

UFFER

PRELIMINARY

T

ABLE

4G. LVCMOS/LVTTL DC C

HARACTERISTICS

,

T

A

= 0∞C

TO

70∞C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

H

I

e

g

a

t

l

o

V

h

g

i

H

t

u

p

n

I

,

1

E

L

B

A

N

E

2

E

L

B

A

N

E

V

D

D

%

5

±

V

3

.

3

=

2

V

D

D

3

.

0

+

V

V

D

D

%

5

±

V

5

.

2

=

7

.

1

V

D

D

3

.

0

+

V

V

D

D

V

2

.

0

±

V

8

.

1

=

V

*

5

6

.

0

D

D

V

D

D

3

.

0

+

V

V

L

I

e

g

a

t

l

o

V

w

o

L

t

u

p

n

I

,

1

E

L

B

A

N

E

2

E

L

B

A

N

E

V

D

D

%

5

±

V

3

.

3

=

3

.

0

-

3

.

1

V

V

D

D

%

5

±

V

5

.

2

=

3

.

0

-

7

.

0

V

V

D

D

V

2

.

0

±

V

8

.

1

=

3

.

0

-

V

*

5

3

.

0

D

D

V

V

H

O

h

g

i

H

t

u

p

t

u

O

e

g

a

t

l

o

V

V

O

D

D

1

E

T

O

N

;

%

5

±

V

3

.

3

=

6

.

2

V

V

O

D

D

I

;

%

5

±

V

5

.

2

=

H

O

A

m

1

-

=

2

V

V

O

D

D

1

E

T

O

N

;

%

5

±

V

5

.

2

=

8

.

1

V

V

O

D

D

1

E

T

O

N

;

V

2

.

0

±

V

8

.

1

=

V

D

D

3

.

0

-

V

V

L

O

e

g

a

t

l

o

V

w

o

L

t

u

p

t

u

O

V

O

D

D

1

E

T

O

N

;

%

5

±

V

3

.

3

=

5

.

0

V

V

O

D

D

I

;

%

5

±

V

5

.

2

=

L

O

A

m

1

=

4

.

0

V

V

O

D

D

1

E

T

O

N

;

%

5

±

V

5

.

2

=

5

4

.

0

V

V

O

D

D

1

E

T

O

N

;

V

2

.

0

±

V

8

.

1

=

5

3

.

0

V

0

5

h

t

i

w

d

e

t

a

n

i

m

r

e

t

s

t

u

p

t

u

O

:

1

E

T

O

N

V

o

t

O

D

D

.

s

m

a

r

g

a

i

d

"

t

i

u

c

r

i

C

t

s

e

T

d

a

o

L

"

,

n

o

i

t

c

e

s

t

n

e

m

e

r

u

s

a

e

M

r

e

t

e

m

a

r

a

P

e

e

S

.

2

/

T

ABLE

4E. P

OWER

S

UPPLY

DC C

HARACTERISTICS

,

V

DD

= 3.3V±5%, V

DDO

= 1.8V±0.2V, T

A

= 0∞C

TO

70∞C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

e

r

o

C

5

3

1

.

3

3

.

3

5

6

4

.

3

V

V

O

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

t

u

p

t

u

O

6

.

1

8

.

1

0

.

2

V

I

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

r

e

w

o

P

D

B

T

A

µ

I

O

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

t

u

p

t

u

O

D

B

T

A

µ

T

ABLE

4F. P

OWER

S

UPPLY

DC C

HARACTERISTICS

,

V

DD

= 2.5V±5%, V

DDO

= 1.8V±0.2V, T

A

= 0∞C

TO

70∞C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

e

r

o

C

5

7

3

.

2

5

.

2

5

2

6

.

2

V

V

O

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

t

u

p

t

u

O

6

.

1

8

.

1

0

.

2

V

I

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

r

e

w

o

P

D

B

T

A

µ

I

O

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

t

u

p

t

u

O

D

B

T

A

µ

83905AM

http://www.icst.com/products/hiperclocks.html

REV. A JANUARY 20, 2005

5

Integrated

Circuit

Systems, Inc.

ICS83905

L

OW

S

KEW

, 1:6 C

RYSTAL

I

NTERFACE

-

TO

-

LVCMOS / LVTTL F

ANOUT

B

UFFER

PRELIMINARY

T

ABLE

5A. AC C

HARACTERISTICS

,

V

DD

= V

DDO

= 3.3V±5%, T

A

= 0∞C

TO

70∞C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

f

X

A

M

y

c

n

e

u

q

e

r

F

t

u

p

t

u

O

l

a

t

s

y

r

C

l

a

n

r

e

t

x

E

g

n

i

s

U

0

1

0

5

z

H

M

e

c

r

u

o

S

k

c

o

l

C

l

a

n

r

e

t

x

E

g

n

i

s

U

C

D

0

0

1

z

H

M

t

W

P

h

t

d

i

W

e

s

l

u

P

t

u

p

t

u

O

1

E

T

O

N

;

)

V

2

e

v

o

b

a

(

H

G

I

H

s

d

o

i

r

e

P

=

T

T

5

.

0

2

E

T

O

N

,

)

V

8

.

0

w

o

l

e

b

(

W

O

L

T

5

.

0

1

E

T

O

N

;

)

V

2

e

v

o

b

a

(

H

G

I

H

T

5

.

0

2

E

T

O

N

,

)

V

8

.

0

w

o

l

e

b

(

W

O

L

T

5

.

0

t

R

E

P

d

o

i

r

e

P

t

u

p

t

u

O

d

o

i

r

e

P

d

e

r

i

s

e

d

=

T

D

B

T

t

)

o

(

k

s

5

,

3

E

T

O

N

;

w

e

k

S

t

u

p

t

u

O

0

1

s

p

t

R

/t

F

e

m

i

T

ll

a

F

/

e

s

i

R

t

u

p

t

u

O

%

0

8

o

t

%

0

2

0

0

5

s

p

t

N

E

;

e

m

i

T

e

l

b

a

n

E

t

u

p

t

u

O

4

E

T

O

N

1

E

L

B

A

N

E

D

B

T

s

m

2

E

L

B

A

N

E

D

B

T

s

m

t

S

I

D

;

e

m

i

T

e

l

b

a

s

i

D

t

u

p

t

u

O

4

E

T

O

N

1

E

L

B

A

N

E

D

B

T

s

m

2

E

L

B

A

N

E

D

B

T

s

m

A

C

S

O

n

i

a

G

r

o

t

a

ll

i

c

s

O

T

U

O

_

L

A

T

X

o

t

N

I

_

L

A

T

X

D

B

T

b

d

e

s

a

h

P

+

∞

0

6

3

o

l

u

d

o

M

t

f

i

h

S

e

s

a

h

P

p

o

o

L

D

B

T

∞

f

t

a

d

e

r

u

s

a

e

m

s

r

e

t

e

m

a

r

a

p

ll

A

X

A

M

.

e

s

i

w

r

e

h

t

o

d

e

t

o

n

s

s

e

l

n

u

.

t

e

m

e

r

a

e

l

b

a

t

s

n

o

t

i

d

n

o

C

g

n

i

t

a

r

e

p

O

d

e

d

n

e

m

m

o

c

e

R

m

o

r

f

s

c

e

p

s

e

l

c

y

c

y

t

u

d

t

u

p

n

i

g

n

i

m

u

s

s

A

:

1

E

T

O

N

.

d

e

s

u

s

i

e

c

n

e

r

e

f

e

r

l

a

n

r

e

t

x

e

e

l

c

y

c

y

t

u

d

%

0

5

r

o

l

a

t

s

y

r

c

l

a

n

r

e

t

x

e

g

n

i

m

u

s

s

A

:

2

E

T

O

N

V

t

a

d

e

r

u

s

a

e

M

.

s

n

o

i

t

i

d

n

o

c

d

a

o

l

l

a

u

q

e

h

t

i

w

d

n

a

e

g

a

t

l

o

v

y

l

p

p

u

s

e

m

a

s

e

h

t

t

a

s

t

u

p

t

u

o

n

e

e

w

t

e

b

w

e

k

s

s

a

d

e

n

i

f

e

D

:

3

E

T

O

N

O

D

D

.

2

/

.

n

o

i

t

c

u

d

o

r

p

n

i

d

e

t

s

e

t

t

o

N

.

n

o

i

t

a

z

i

r

e

t

c

a

r

a

h

c

y

b

d

e

e

t

n

a

r

a

u

g

e

r

a

s

r

e

t

e

m

a

r

a

p

e

s

e

h

T

:

4

E

T

O

N

.

5

6

d

r

a

d

n

a

t

S

C

E

D

E

J

h

t

i

w

e

c

n

a

d

r

o

c

c

a

n

i

d

e

n

i

f

e

d

s

i

r

e

t

e

m

a

r

a

p

s

i

h

T

:

5

E

T

O

N

T

ABLE

5B. AC C

HARACTERISTICS

,

V

DD

= V

DDO

= 2.5V±5%, T

A

= 0∞C

TO

70∞C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

f

X

A

M

y

c

n

e

u

q

e

r

F

t

u

p

t

u

O

l

a

t

s

y

r

C

l

a

n

r

e

t

x

E

g

n

i

s

U

0

1

0

5

z

H

M

e

c

r

u

o

S

k

c

o

l

C

l

a

n

r

e

t

x

E

g

n

i

s

U

C

D

0

0

1

z

H

M

c

d

o

e

l

c

y

C

y

t

u

D

t

u

p

t

u

O

0

5

%

t

R

E

P

d

o

i

r

e

P

t

u

p

t

u

O

D

B

T

t

)

o

(

k

s

5

,

3

E

T

O

N

;

w

e

k

S

t

u

p

t

u

O

0

1

s

p

t

R

/t

F

e

m

i

T

ll

a

F

/

e

s

i

R

t

u

p

t

u

O

%

0

8

o

t

%

0

2

0

0

5

s

p

t

N

E

;

e

m

i

T

e

l

b

a

n

E

t

u

p

t

u

O

4

E

T

O

N

1

E

L

B

A

N

E

D

B

T

s

m

2

E

L

B

A

N

E

D

B

T

s

m

t

S

I

D

;

e

m

i

T

e

l

b

a

s

i

D

t

u

p

t

u

O

4

E

T

O

N

1

E

L

B

A

N

E

D

B

T

s

m

2

E

L

B

A

N

E

D

B

T

s

m

A

C

S

O

n

i

a

G

r

o

t

a

ll

i

c

s

O

T

U

O

_

L

A

T

X

o

t

N

I

_

L

A

T

X

D

B

T

b

d

e

s

a

h

P

+

∞

0

6

3

o

l

u

d

o

M

t

f

i

h

S

e

s

a

h

P

p

o

o

L

D

B

T

∞

.

A

5

e

l

b

a

T

m

o

r

f

s

e

t

o

n

e

e

S

83905AM

http://www.icst.com/products/hiperclocks.html

REV. A JANUARY 20, 2005

6

Integrated

Circuit

Systems, Inc.

ICS83905

L

OW

S

KEW

, 1:6 C

RYSTAL

I

NTERFACE

-

TO

-

LVCMOS / LVTTL F

ANOUT

B

UFFER

PRELIMINARY

T

ABLE

5D. AC C

HARACTERISTICS

,

V

DD

= 3.3V±5%, V

DDO

= 2.5V±5%, T

A

= 0∞C

TO

70∞C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

f

X

A

M

y

c

n

e

u

q

e

r

F

t

u

p

t

u

O

l

a

t

s

y

r

C

l

a

n

r

e

t

x

E

g

n

i

s

U

0

1

0

5

z

H

M

e

c

r

u

o

S

k

c

o

l

C

l

a

n

r

e

t

x

E

g

n

i

s

U

C

D

0

0

1

z

H

M

c

d

o

e

l

c

y

C

y

t

u

D

t

u

p

t

u

O

0

5

%

t

R

E

P

d

o

i

r

e

P

t

u

p

t

u

O

D

B

T

t

)

o

(

k

s

5

,

3

E

T

O

N

;

w

e

k

S

t

u

p

t

u

O

0

1

s

p

t

R

/t

F

e

m

i

T

ll

a

F

/

e

s

i

R

t

u

p

t

u

O

%

0

8

o

t

%

0

2

0

0

5

s

p

t

N

E

;

e

m

i

T

e

l

b

a

n

E

t

u

p

t

u

O

4

E

T

O

N

1

E

L

B

A

N

E

D

B

T

s

m

2

E

L

B

A

N

E

D

B

T

s

m

t

S

I

D

;

e

m

i

T

e

l

b

a

s

i

D

t

u

p

t

u

O

4

E

T

O

N

1

E

L

B

A

N

E

D

B

T

s

m

2

E

L

B

A

N

E

D

B

T

s

m

A

C

S

O

n

i

a

G

r

o

t

a

ll

i

c

s

O

T

U

O

_

L

A

T

X

o

t

N

I

_

L

A

T

X

D

B

T

b

d

e

s

a

h

P

+

∞

0

6

3

o

l

u

d

o

M

t

f

i

h

S

e

s

a

h

P

p

o

o

L

D

B

T

∞

.

A

5

e

l

b

a

T

m

o

r

f

s

e

t

o

n

e

e

S

T

ABLE

5C. AC C

HARACTERISTICS

,

V

DD

= V

DDO

= 1.8V±0.2V, T

A

= 0∞C

TO

70∞C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

f

X

A

M

y

c

n

e

u

q

e

r

F

t

u

p

t

u

O

l

a

t

s

y

r

C

l

a

n

r

e

t

x

E

g

n

i

s

U

0

1

0

5

z

H

M

e

c

r

u

o

S

k

c

o

l

C

l

a

n

r

e

t

x

E

g

n

i

s

U

C

D

0

0

1

z

H

M

c

d

o

e

l

c

y

C

y

t

u

D

t

u

p

t

u

O

0

5

%

t

R

E

P

d

o

i

r

e

P

t

u

p

t

u

O

D

B

T

t

)

o

(

k

s

5

,

3

E

T

O

N

;

w

e

k

S

t

u

p

t

u

O

0

1

s

p

t

R

/t

F

e

m

i

T

ll

a

F

/

e

s

i

R

t

u

p

t

u

O

%

0

8

o

t

%

0

2

0

5

5

s

p

t

N

E

;

e

m

i

T

e

l

b

a

n

E

t

u

p

t

u

O

4

E

T

O

N

1

E

L

B

A

N

E

D

B

T

s

m

2

E

L

B

A

N

E

D

B

T

s

m

t

S

I

D

;

e

m

i

T

e

l

b

a

s

i

D

t

u

p

t

u

O

4

E

T

O

N

1

E

L

B

A

N

E

D

B

T

s

m

2

E

L

B

A

N

E

D

B

T

s

m

A

C

S

O

n

i

a

G

r

o

t

a

ll

i

c

s

O

T

U

O

_

L

A

T

X

o

t

N

I

_

L

A

T

X

D

B

T

b

d

e

s

a

h

P

+

∞

0

6

3

o

l

u

d

o

M

t

f

i

h

S

e

s

a

h

P

p

o

o

L

D

B

T

∞

.

A

5

e

l

b

a

T

m

o

r

f

s

e

t

o

n

e

e

S

83905AM

http://www.icst.com/products/hiperclocks.html

REV. A JANUARY 20, 2005

7

Integrated

Circuit

Systems, Inc.

ICS83905

L

OW

S

KEW

, 1:6 C

RYSTAL

I

NTERFACE

-

TO

-

LVCMOS / LVTTL F

ANOUT

B

UFFER

PRELIMINARY

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

f

X

A

M

y

c

n

e

u

q

e

r

F

t

u

p

t

u

O

l

a

t

s

y

r

C

l

a

n

r

e

t

x

E

g

n

i

s

U

0

1

0

5

z

H

M

e

c

r

u

o

S

k

c

o

l

C

l

a

n

r

e

t

x

E

g

n

i

s

U

C

D

0

0

1

z

H

M

t

W

P

h

t

d

i

W

e

s

l

u

P

t

u

p

t

u

O

0

5

%

t

R

E

P

d

o

i

r

e

P

t

u

p

t

u

O

D

B

T

t

)

o

(

k

s

5

,

3

E

T

O

N

;

w

e

k

S

t

u

p

t

u

O

0

1

s

p

t

R

/t

F

e

m

i

T

ll

a

F

/

e

s

i

R

t

u

p

t

u

O

%

0

8

o

t

%

0

2

0

5

5

s

p

t

N

E

;

e

m

i

T

e

l

b

a

n

E

t

u

p

t

u

O

4

E

T

O

N

1

E

L

B

A

N

E

D

B

T

s

m

2

E

L

B

A

N

E

D

B

T

s

m

t

S

I

D

;

e

m

i

T

e

l

b

a

s

i

D

t

u

p

t

u

O

4

E

T

O

N

1

E

L

B

A

N

E

D

B

T

s

m

2

E

L

B

A

N

E

D

B

T

s

m

A

C

S

O

n

i

a

G

r

o

t

a

ll

i

c

s

O

T

U

O

_

L

A

T

X

o

t

N

I

_

L

A

T

X

D

B

T

b

d

e

s

a

h

P

+

∞

0

6

3

o

l

u

d

o

M

t

f

i

h

S

e

s

a

h

P

p

o

o

L

D

B

T

∞

.

A

5

e

l

b

a

T

m

o

r

f

s

e

t

o

n

e

e

S

T

ABLE

5E. AC C

HARACTERISTICS

,

V

DD

= 3.3V±5%, V

DDO

= 1.8V±0.2V, T

A

= 0∞C

TO

70∞C

T

ABLE

5F. AC C

HARACTERISTICS

,

V

DD

= 2.5V±5%, V

DDO

= 1.8V±0.2V, T

A

= 0∞C

TO

70∞C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

f

X

A

M

y

c

n

e

u

q

e

r

F

t

u

p

t

u

O

l

a

t

s

y

r

C

l

a

n

r

e

t

x

E

g

n

i

s

U

0

1

0

5

z

H

M

e

c

r

u

o

S

k

c

o

l

C

l

a

n

r

e

t

x

E

g

n

i

s

U

C

D

0

0

1

z

H

M

c

d

o

e

l

c

y

C

y

t

u

D

t

u

p

t

u

O

0

5

%

t

R

E

P

d

o

i

r

e

P

t

u

p

t

u

O

D

B

T

t

)

o

(

k

s

5

,

3

E

T

O

N

;

w

e

k

S

t

u

p

t

u

O

0

1

s

p

t

R

/t

F

e

m

i

T

ll

a

F

/

e

s

i

R

t

u

p

t

u

O

%

0

8

o

t

%

0

2

0

5

5

s

p

t

N

E

;

e

m

i

T

e

l

b

a

n

E

t

u

p

t

u

O

4

E

T

O

N

1

E

L

B

A

N

E

D

B

T

s

m

2

E

L

B

A

N

E

D

B

T

s

m

t

S

I

D

;

e

m

i

T

e

l

b

a

s

i

D

t

u

p

t

u

O

4

E

T

O

N

1

E

L

B

A

N

E

D

B

T

s

m

2

E

L

B

A

N

E

D

B

T

s

m

A

C

S

O

n

i

a

G

r

o

t

a

ll

i

c

s

O

T

U

O

_

L

A

T

X

o

t

N

I

_

L

A

T

X

D

B

T

b

d

e

s

a

h

P

+

∞

0

6

3

o

l

u

d

o

M

t

f

i

h

S

e

s

a

h

P

p

o

o

L

D

B

T

∞

.

A

5

e

l

b

a

T

m

o

r

f

s

e

t

o

n

e

e

S

83905AM

http://www.icst.com/products/hiperclocks.html

REV. A JANUARY 20, 2005

8

Integrated

Circuit

Systems, Inc.

ICS83905

L

OW

S

KEW

, 1:6 C

RYSTAL

I

NTERFACE

-

TO

-

LVCMOS / LVTTL F

ANOUT

B

UFFER

PRELIMINARY

P

ARAMETER

M

EASUREMENT

I

NFORMATION

SCOPE

Qx

LVCMOS

1.8V C

ORE

/1.8V O

UTPUT

L

OAD

AC T

EST

C

IRCUIT

2.4±0.9V

V

DDO

-0.9V±0.1V

V

DD

0.9V±0.1V

SCOPE

Qx

LVCMOS

2.5V C

ORE

/2.5V O

UTPUT

L

OAD

AC T

EST

C

IRCUIT

2.05V±5%

V

DDO

-1.25V±5%

V

DD

1.25V±5%

3.3V

CORE

/3.3V O

UTPUT

L

OAD

AC T

EST

C

IRCUIT

SCOPE

Qx

LVCMOS

1.65V±5%

-1.165V±5%

3.3V C

ORE

/2.5V O

UTPUT

L

OAD

AC T

EST

C

IRCUIT

3.3V C

ORE

/1.8V O

UTPUT

L

OAD

AC T

EST

C

IRCUIT

2.5 C

ORE

/1.8V O

UTPUT

L

OAD

AC T

EST

C

IRCUIT

SCOPE

Qx

LVCMOS

1.25V±5%

-1.25V±5%

SCOPE

Qx

LVCMOS

0.9V±0.1V

-0.9V ± 0.1V

SCOPE

Qx

LVCMOS

1.6V±0.025%

V

DDO

-0.9V±0.1V

V

DD

0.9V±0.1V

V

DD

,

V

DDO

GND

V

DD

,

V

DDO

GND

V

DD

,

V

DDO

GND

GND

GND

GND

83905AM

http://www.icst.com/products/hiperclocks.html

REV. A JANUARY 20, 2005

9

Integrated

Circuit

Systems, Inc.

ICS83905

L

OW

S

KEW

, 1:6 C

RYSTAL

I

NTERFACE

-

TO

-

LVCMOS / LVTTL F

ANOUT

B

UFFER

PRELIMINARY

Clock

Outputs

20%

80%

80%

20%

t

R

t

F

Pulse Width

t

PERIOD

t

PW

t

PERIOD

odc =

V

DD

2

BCLKx

O

UTPUT

R

ISE

/F

ALL

T

IME

O

UTPUT

D

UTY

C

YCLE

/P

ULSE

W

IDTH

/P

ERIOD

O

UTPUT

S

KEW

tsk(o)

V

DDO

2

V

DDO

2

Qy

Qx

83905AM

http://www.icst.com/products/hiperclocks.html

REV. A JANUARY 20, 2005

10

Integrated

Circuit

Systems, Inc.

ICS83905

L

OW

S

KEW

, 1:6 C

RYSTAL

I

NTERFACE

-

TO

-

LVCMOS / LVTTL F

ANOUT

B

UFFER

PRELIMINARY

A

PPLICATION

I

NFORMATION

C

RYSTAL

I

NPUT

I

NTERFACE

, F

UNDAMENTAL

Figure 1A shows an example of ICS83905 crystal interface with

parallel resonance crystal using fundamental frequency. The C1,

C2 and R1 values are suggested for the best frequency accu-

R1

100

X1

XTAL_IN

XTAL_OUT

C2

16p

C1

10p

XTAL_IN

XTAL_OUT

C1

10p

L1

X1

C2

16p

C3

C

RYSTAL

I

NPUT

I

NTERFACE

, 3

RD

O

VERTONE

Figure 1B shows an example of ICS83905 crystal interface with

parallel resonance crystal using 3

rd

overtone frequency. The C1,

C2 values are suggested for the best frequency accuracy ppm.

racy ppm. The optimum C1 and C2 values can be adjusted to

improve the frequency accuracy for stray capacitance of differ-

ent board layout.

F

IGURE

1A. C

RYSTAL

O

SCILLATOR

I

NTERFACE

, (F

UNDAMENTAL

)

The optimum C1 and C2 values can be adjusted to improve the

frequency accuracy for stray capacitance of different board lay-

out. The C3 and L1 can be calculated from the given equation.

F

IGURE

1B. C

RYSTAL

O

SCILLATOR

I

NTERFACE

(3

RD

O

VERTONE

)

3

*

1

2

1

_

C

L

fund

F

=

83905AM

http://www.icst.com/products/hiperclocks.html

REV. A JANUARY 20, 2005

11

Integrated

Circuit

Systems, Inc.

ICS83905

L

OW

S

KEW

, 1:6 C

RYSTAL

I

NTERFACE

-

TO

-

LVCMOS / LVTTL F

ANOUT

B

UFFER

PRELIMINARY

R

ELIABILITY

I

NFORMATION

T

RANSISTOR

C

OUNT

The transistor count for ICS83905 is: 339

T

ABLE

6B.

JA

VS

. A

IR

F

LOW

T

ABLE

FOR

16 L

EAD

TSSOP

JA

by Velocity (Linear Feet per Minute)

0

200

500

Single-Layer PCB, JEDEC Standard Test Boards

137.1∞C/W

118.2∞C/W

106.8∞C/W

Multi-Layer PCB, JEDEC Standard Test Boards

89.0∞C/W

81.8∞C/W

78.1∞C/W

NOTE: Most modern PCB designs use multi-layered boards. The data in the second row pertains to most designs.

T

ABLE

6A.

JA

VS

. A

IR

F

LOW

T

ABLE

FOR

16 L

EAD

SOIC

JA

by Velocity (Meters per Second)

0

1

2

Multi-Layer PCB, JEDEC Standard Test Boards

78.8∞C/W

71.1∞C/W

66.2∞C/W

T

ABLE

6C.

JA

VS

. A

IR

F

LOW

T

ABLE

FOR

20 L

EAD

VFQFN

JA

by Velocity (Meters per Second)

0

1

2.5

Single-Layer PCB, JEDEC Standard Test Boards

141.7∞C/W

126∞C/W

116.9∞C/W

Multi-Layer PCB, JEDEC Standard Test Boards

38.5∞C/W

35∞C/W

33.4∞C/W

NOTE: Most modern PCB designs use multi-layered boards. The data in the second row pertains to most designs.

83905AM

http://www.icst.com/products/hiperclocks.html

REV. A JANUARY 20, 2005

12

Integrated

Circuit

Systems, Inc.

ICS83905

L

OW

S

KEW

, 1:6 C

RYSTAL

I

NTERFACE

-

TO

-

LVCMOS / LVTTL F

ANOUT

B

UFFER

PRELIMINARY

P

ACKAGE

O

UTLINE

- G S

UFFIX

FOR

16 L

EAD

TSSOP

Reference Document: JEDEC Publication 95, MO-153

L

O

B

M

Y

S

s

r

e

t

e

m

i

l

l

i

M

m

u

m

i

n

i

M

m

u

m

i

x

a

M

N

6

1

A

-

-

0

2

.

1

1

A

5

0

.

0

5

1

.

0

2

A

0

8

.

0

5

0

.

1

b

9

1

.

0

0

3

.

0

c

9

0

.

0

0

2

.

0

D

0

9

.

4

0

1

.

5

E

C

I

S

A

B

0

4

.

6

1

E

0

3

.

4

0

5

.

4

e

C

I

S

A

B

5

6

.

0

L

5

4

.

0

5

7

.

0

∞

0

∞

8

a

a

a

-

-

0

1

.

0

P

ACKAGE

O

UTLINE

- M S

UFFIX

FOR

16 L

EAD

SOIC

T

ABLE

7A. P

ACKAGE

D

IMENSIONS

FOR

16 L

EAD

SOIC

Reference Document: JEDEC Publication 95, MS-012

L

O

B

M

Y

S

s

r

e

t

e

m

i

l

l

i

M

M

U

M

I

N

I

M

M

U

M

I

X

A

M

N

6

1

A

5

3

.

1

5

7

.

1

1

A

0

1

.

0

5

2

.

0

B

3

3

.

0

1

5

.

0

C

9

1

.

0

5

2

.

0

D

0

8

.

9

0

0

.

0

1

E

0

8

.

3

0

0

.

4

e

C

I

S

A

B

7

2

.

1

H

0

8

.

5

0

2

.

6

h

5

2

.

0

0

5

.

0

L

0

4

.

0

7

2

.

1

∞

0

∞

8

T

ABLE

7B. P

ACKAGE

D

IMENSIONS

FOR

TSSOP

83905AM

http://www.icst.com/products/hiperclocks.html

REV. A JANUARY 20, 2005

13

Integrated

Circuit

Systems, Inc.

ICS83905

L

OW

S

KEW

, 1:6 C

RYSTAL

I

NTERFACE

-

TO

-

LVCMOS / LVTTL F

ANOUT

B

UFFER

PRELIMINARY

T

ABLE

7C. P

ACKAGE

D

IMENSIONS

FOR

20 L

EAD

VFQFN

P

ACKAGE

O

UTLINE

- K S

UFFIX

FOR

20 L

EAD

VFQFN

N

O

I

T

A

I

R

A

V

C

E

D

E

J

S

R

E

T

E

M

I

L

L

I

M

N

I

S

N

O

I

S

N

E

M

I

D

L

L

A

L

O

B

M

Y

S

M

U

M

I

N

I

M

M

U

M

I

X

A

M

N

0

2

A

0

8

.

0

0

.

1

1

A

0

5

0

.

0

3

A

e

c

n

e

r

e

f

e

R

5

2

.

0

b

8

1

.

0

0

3

.

0

e

C

I

S

A

B

0

5

.

0

N

D

5

N

E

5

D

0

.

4

2

D

5

7

.

0

0

8

.

2

E

0

.

4

2

E

5

7

.

0

0

8

.

2

L

5

3

.

0

5

7

.

0

Reference Document: JEDEC Publication 95, MO-220

83905AM

http://www.icst.com/products/hiperclocks.html

REV. A JANUARY 20, 2005

14

Integrated

Circuit

Systems, Inc.

ICS83905

L

OW

S

KEW

, 1:6 C

RYSTAL

I

NTERFACE

-

TO

-

LVCMOS / LVTTL F

ANOUT

B

UFFER

PRELIMINARY

T

ABLE

8. O

RDERING

I

NFORMATION

While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems, Incorporated (ICS) assumes no responsibility for either its use

or for infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use

in normal commercial and industrial applications. Any other applications such as those requiring high reliability or other extraordinary environmental requirements are not

recommended without additional processing by ICS. ICS reserves the right to change any circuitry or specifications without notice. ICS does not authorize or warrant any ICS product

for use in life support devices or critical medical instruments.

r

e

b

m

u

N

r

e

d

r

O

/

t

r

a

P

g

n

i

k

r

a

M

e

g

a

k

c

a

P

g

n

i

g

a

k

c

a

P

g

n

i

p

p

i

h

S

e

r

u

t

a

r

e

p

m

e

T

M

A

5

0

9

3

8

S

C

I

M

A

5

0

9

3

8

C

I

O

S

d

a

e

L

6

1

e

b

u

t

C

∞

0

7

o

t

C

∞

0

T

M

A

5

0

9

3

8

S

C

I

M

A

5

0

9

3

8

C

I

O

S

d

a

e

L

6

1

l

e

e

r

&

e

p

a

t

0

0

5

2

C

∞

0

7

o

t

C

∞

0

F

L

M

A

5

0

9

3

8

S

C

I

L

M

A

5

0

9

3

8

C

I

O

S

"

e

e

r

F

-

d

a

e

L

"

d

a

e

L

6

1

e

b

u

t

C

∞

0

7

o

t

C

∞

0

T

F

L

M

A

5

0

9

3

8

S

C

I

L

M

A

5

0

9

3

8

C

I

O

S

"

e

e

r

F

-

d

a

e

L

"

d

a

e

L

6

1

l

e

e

r

&

e

p

a

t

0

0

5

2

C

∞

0

7

o

t

C

∞

0

G

A

5

0

9

3

8

S

C

I

D

B

T

P

O

S

S

T

d

a

e

L

6

1

e

b

u

t

C

∞

0

7

o

t

C

∞

0

T

G

A

5

0

9

3

8

S

C

I

D

B

T

P

O

S

S

T

d

a

e

L

6

1

l

e

e

r

&

e

p

a

t

0

0

5

2

C

∞

0

7

o

t

C

∞

0

K

A

5

0

9

3

8

S

C

I

A

5

0

9

3

8

N

F

Q

F

V

d

a

e

L

0

2

e

b

u

t

C

∞

0

7

o

t

C

∞

0

T

K

A

5

0

9

3

8

S

C

I

A

5

0

9

3

8

N

F

Q

F

V

d

a

e

L

0

2

l

e

e

r

&

e

p

a

t

0

0

5

2

C

∞

0

7

o

t

C

∞

0

The aforementioned trademark, HiPerClockSTM is a trademark of Integrated Circuit Systems, Inc. or its subsidiaries in the United States and/or other countries.