Document Outline

- General Description

- Features

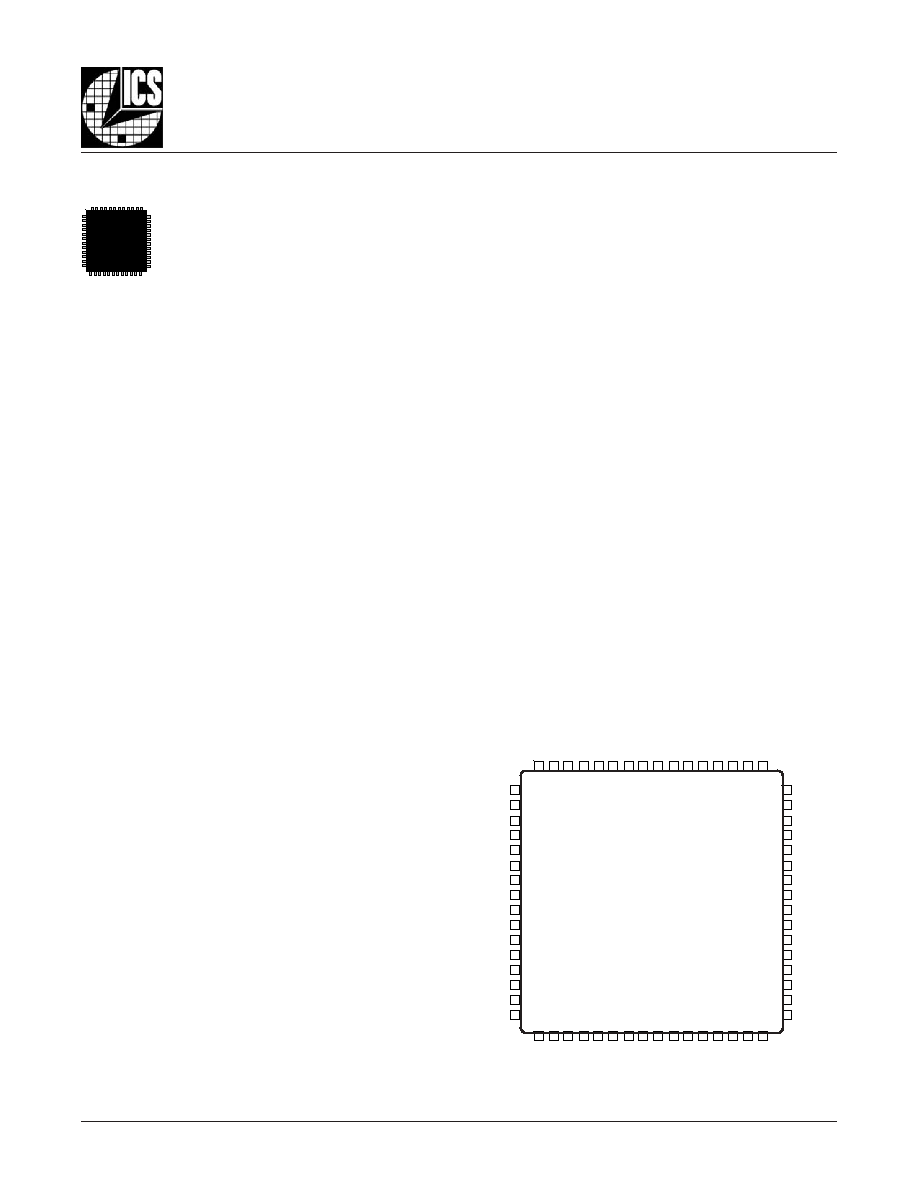

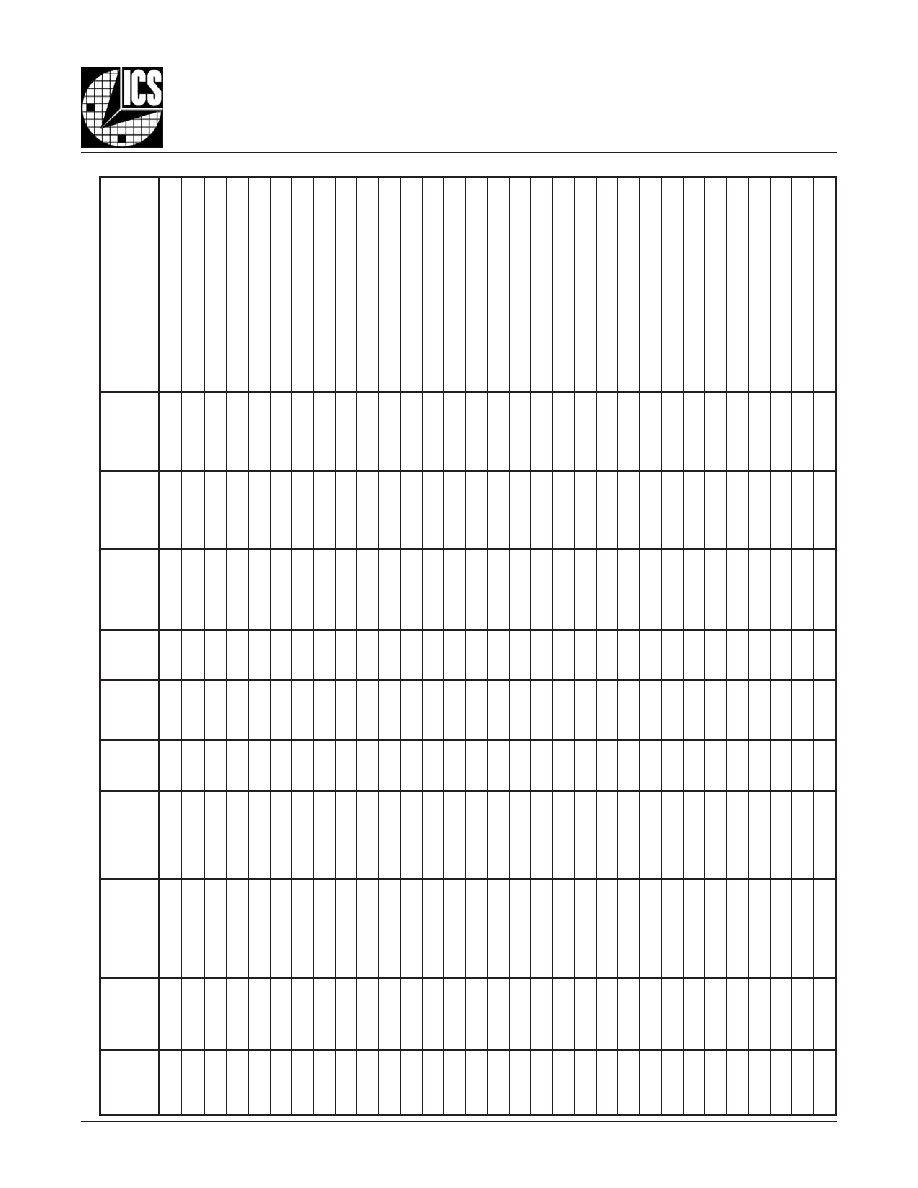

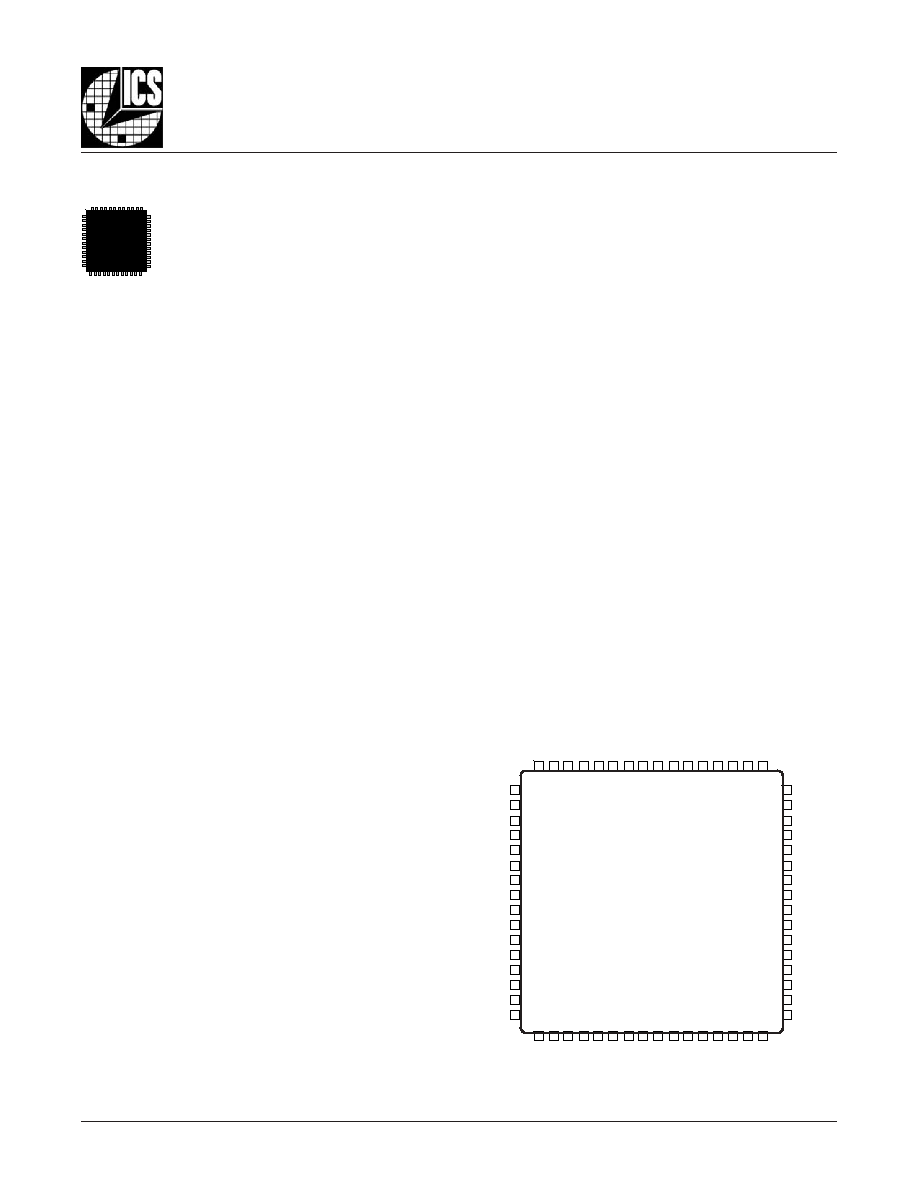

- Pin Assignment

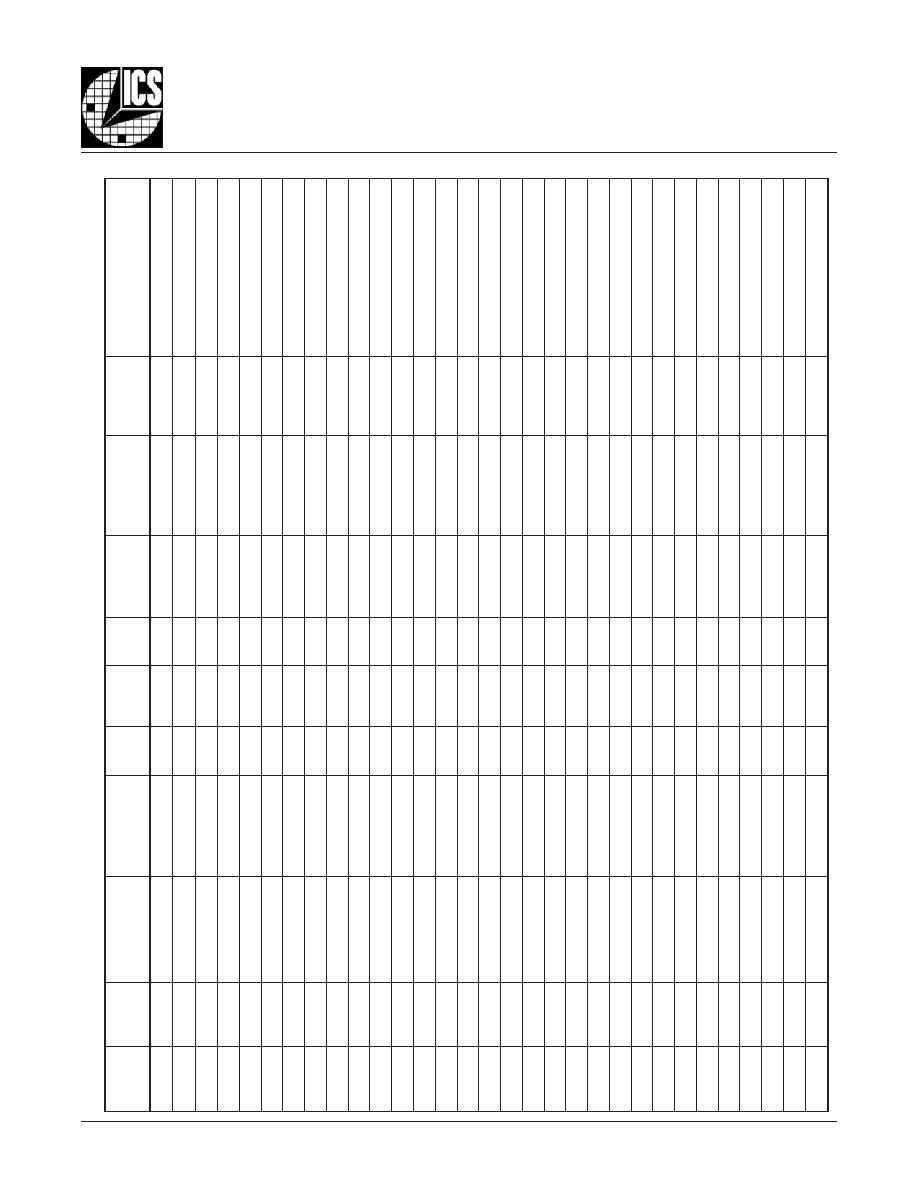

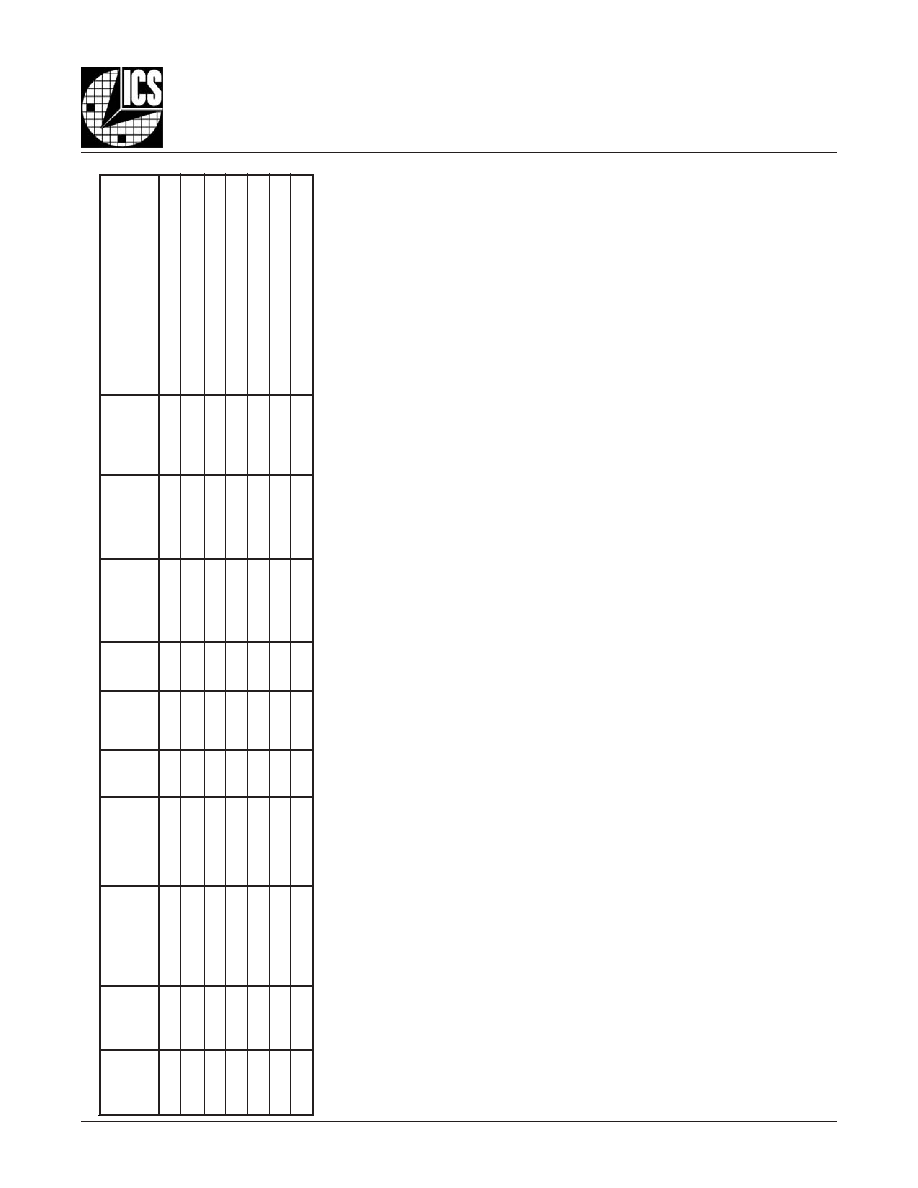

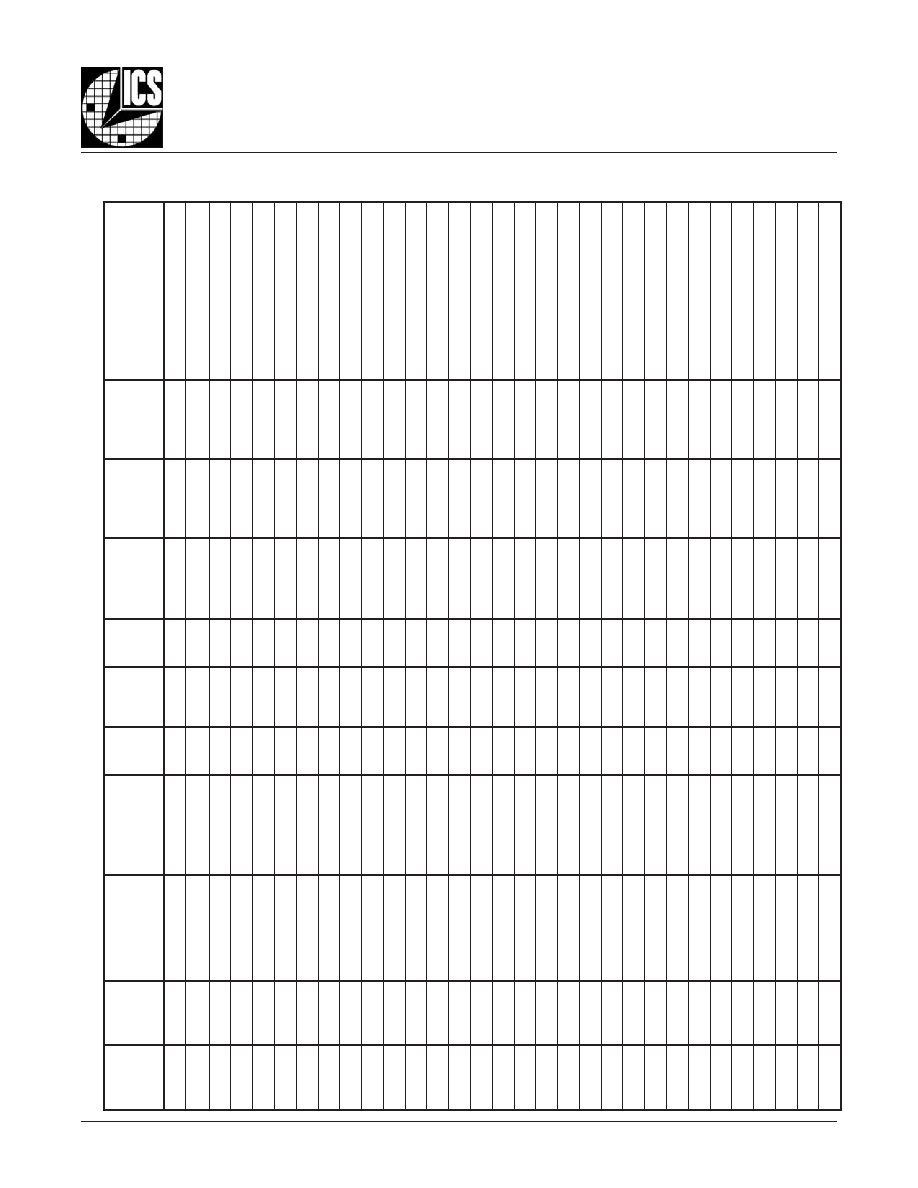

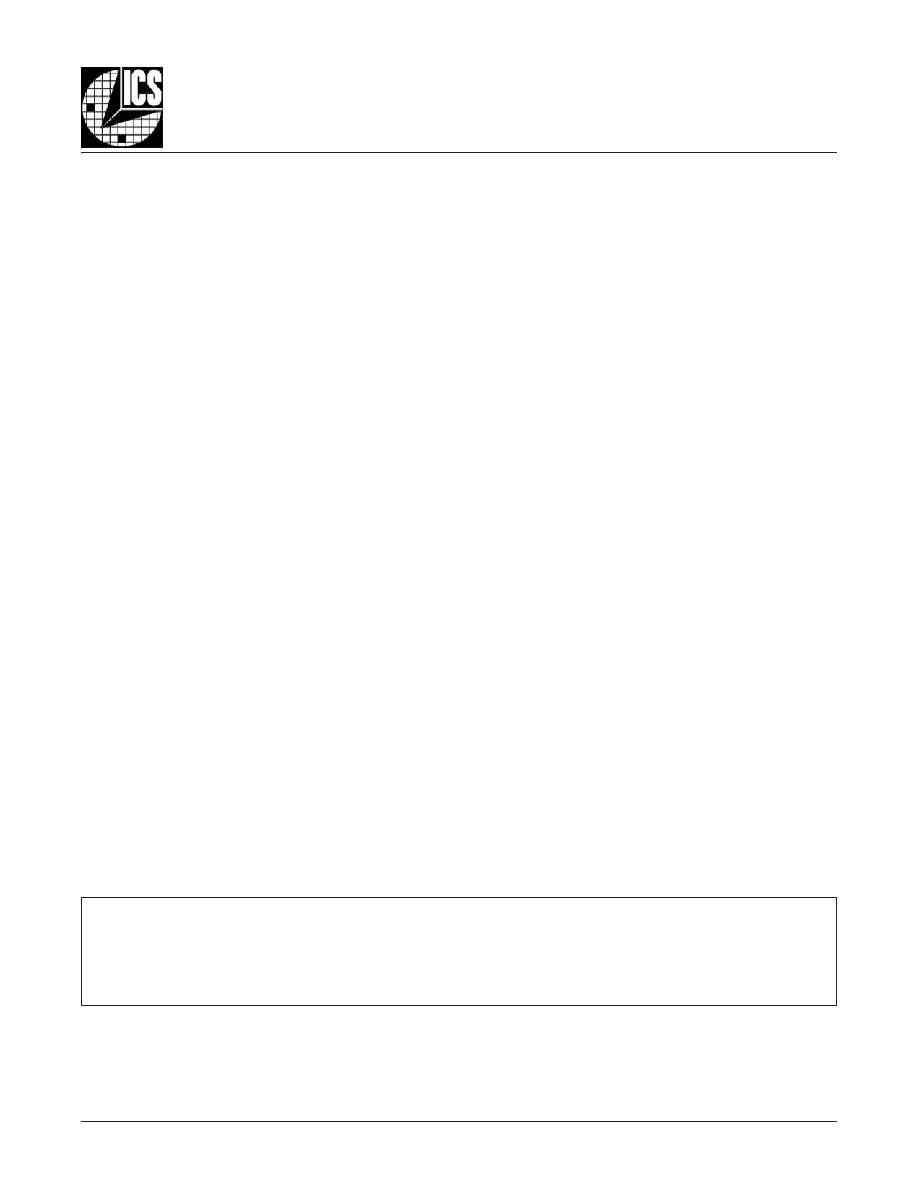

- Block Diagram

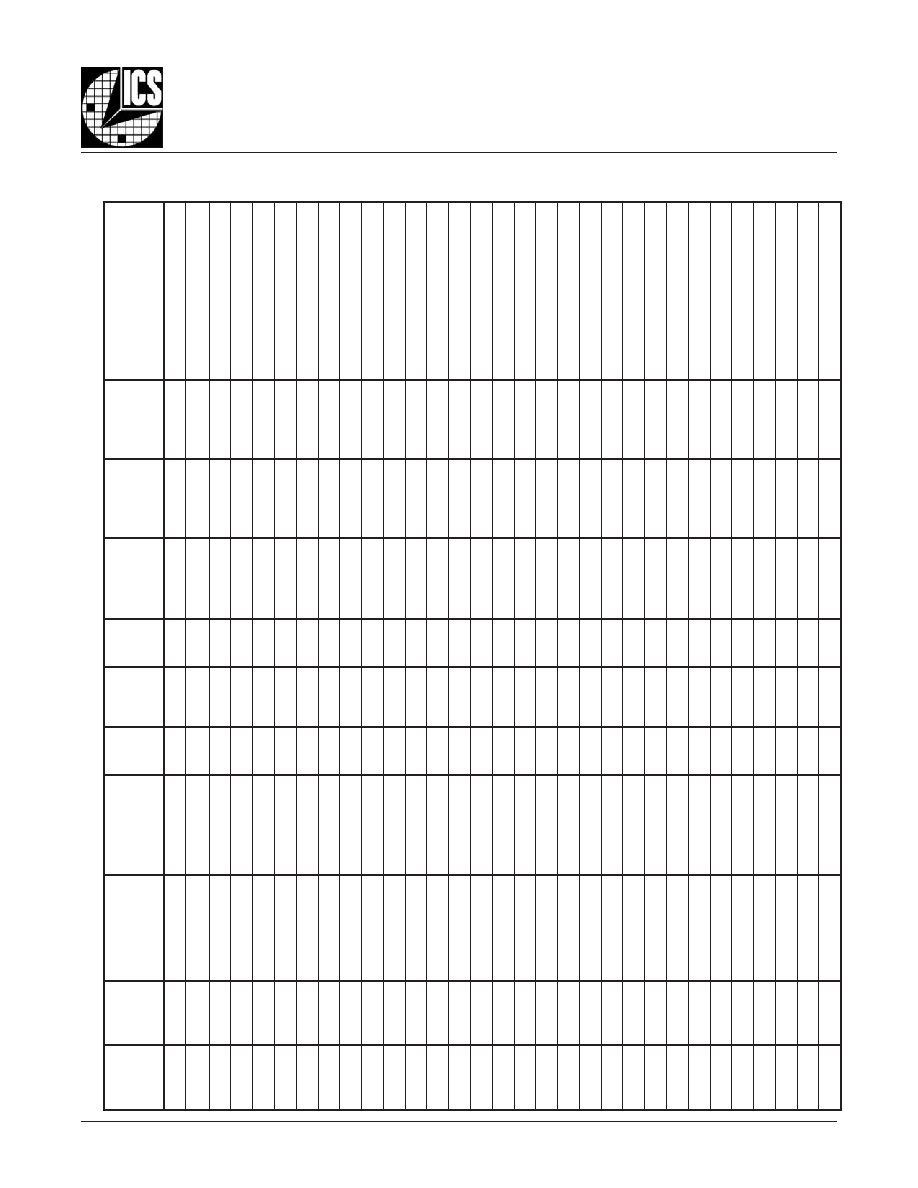

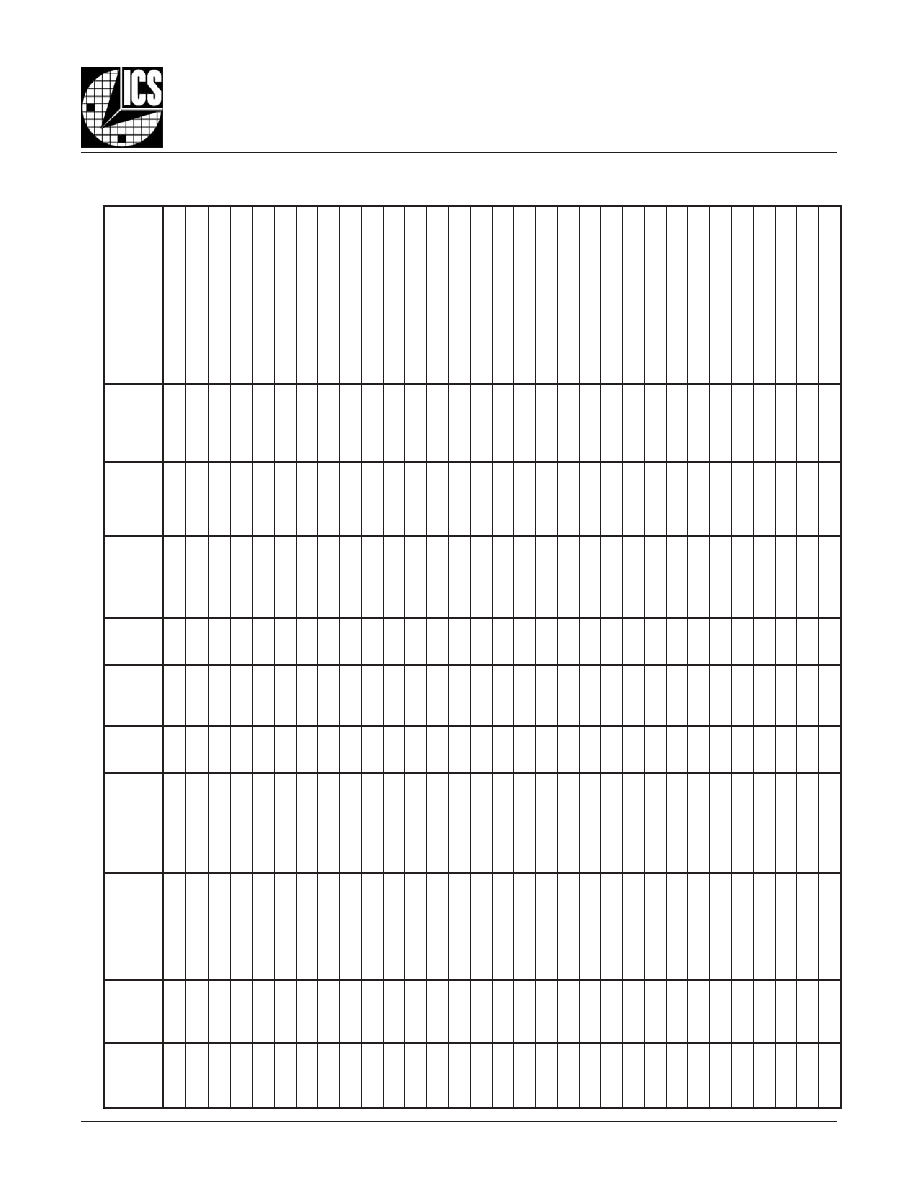

- Simplified Block Diagram

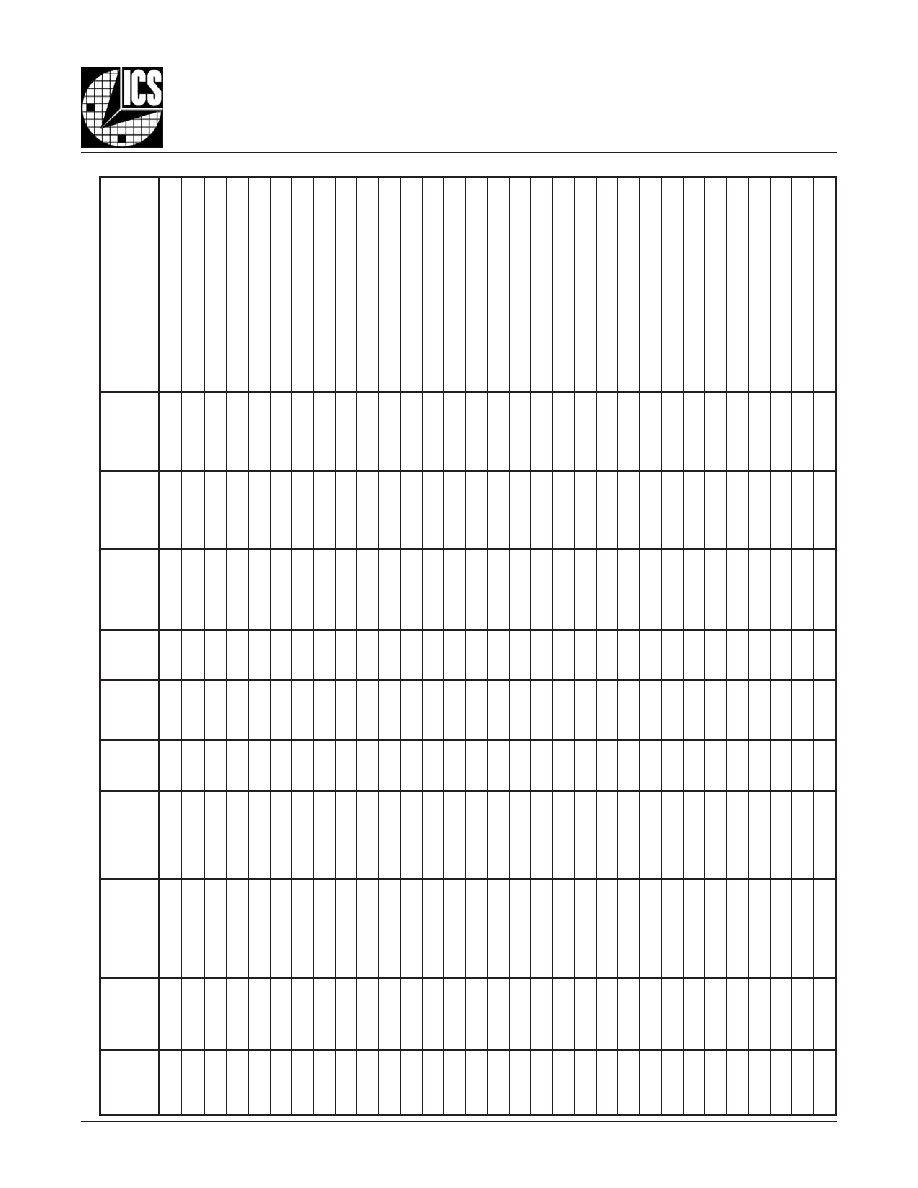

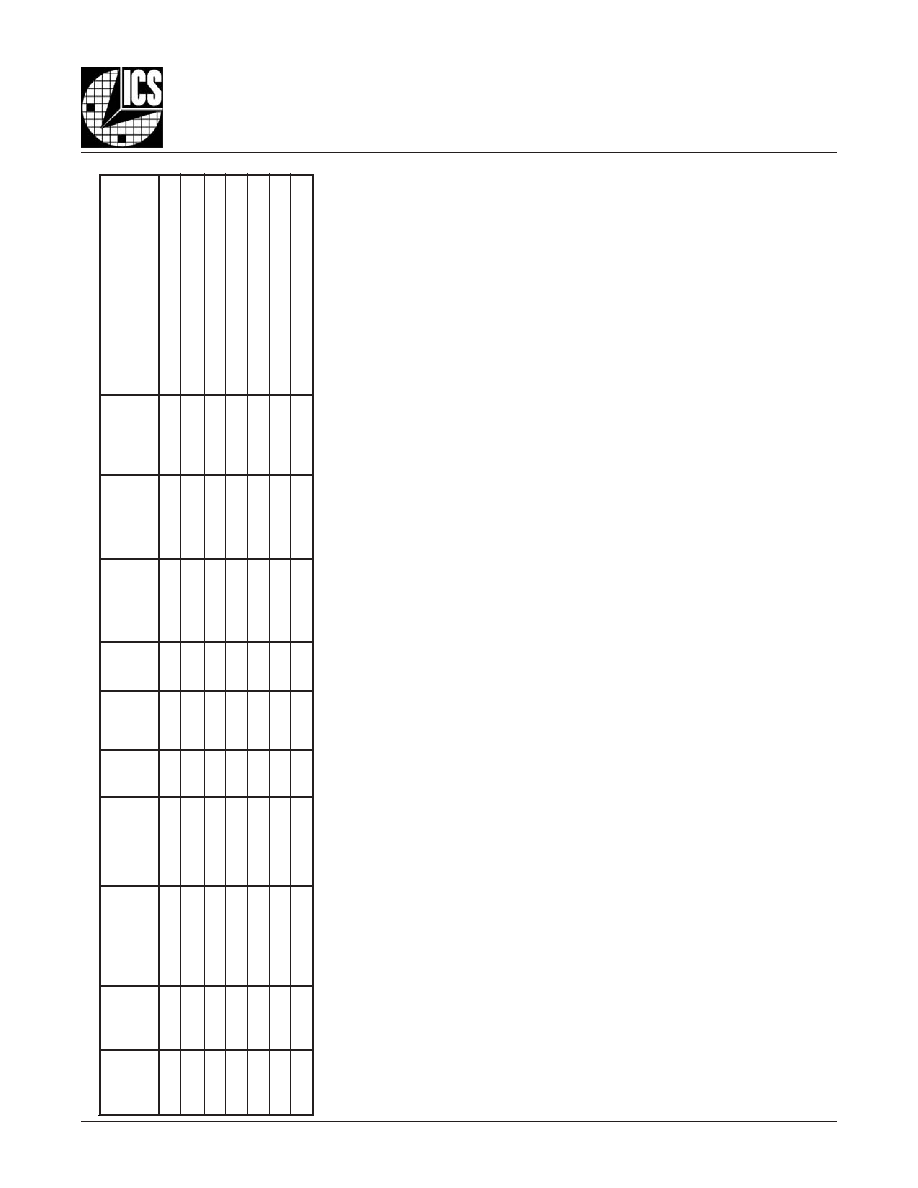

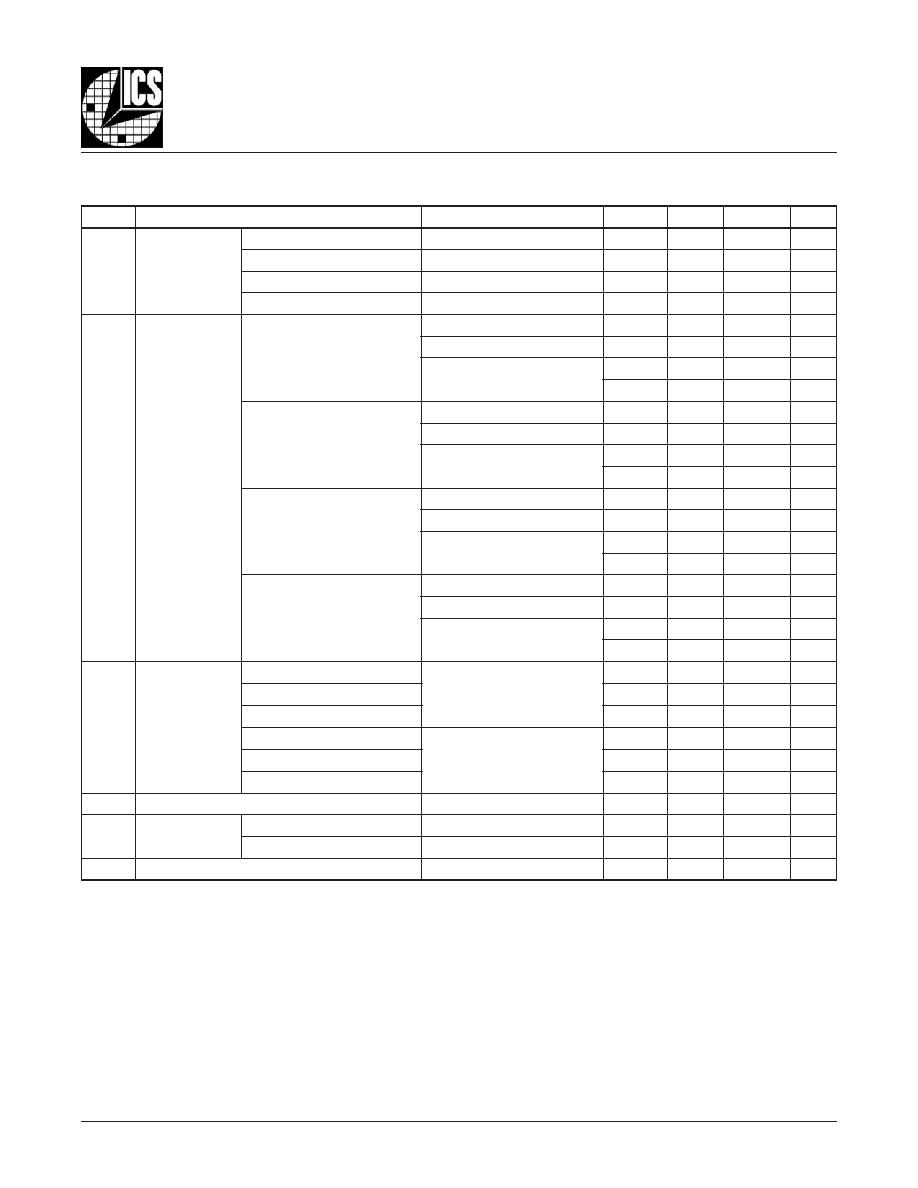

- Pin Descriptions

- Pin Descriptions, continued

- Pin Characteristics

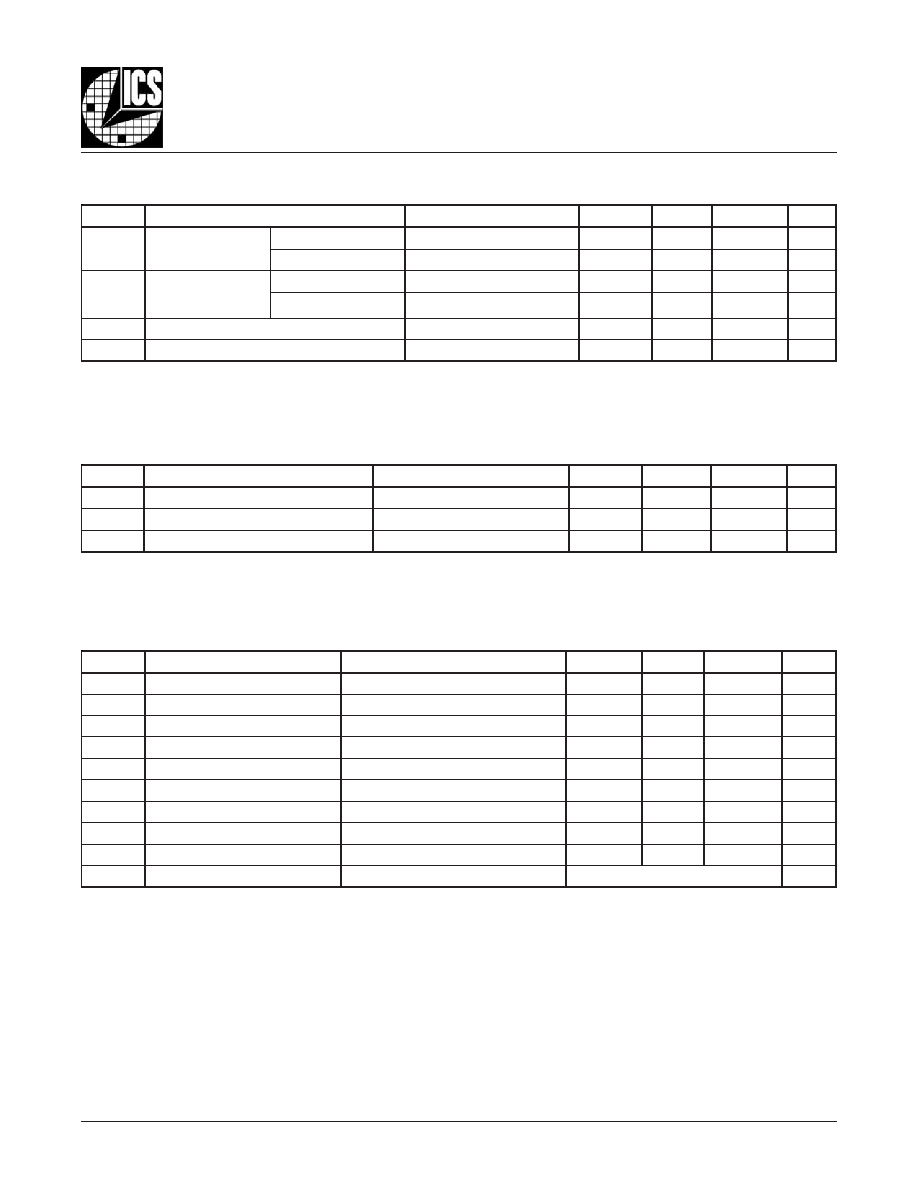

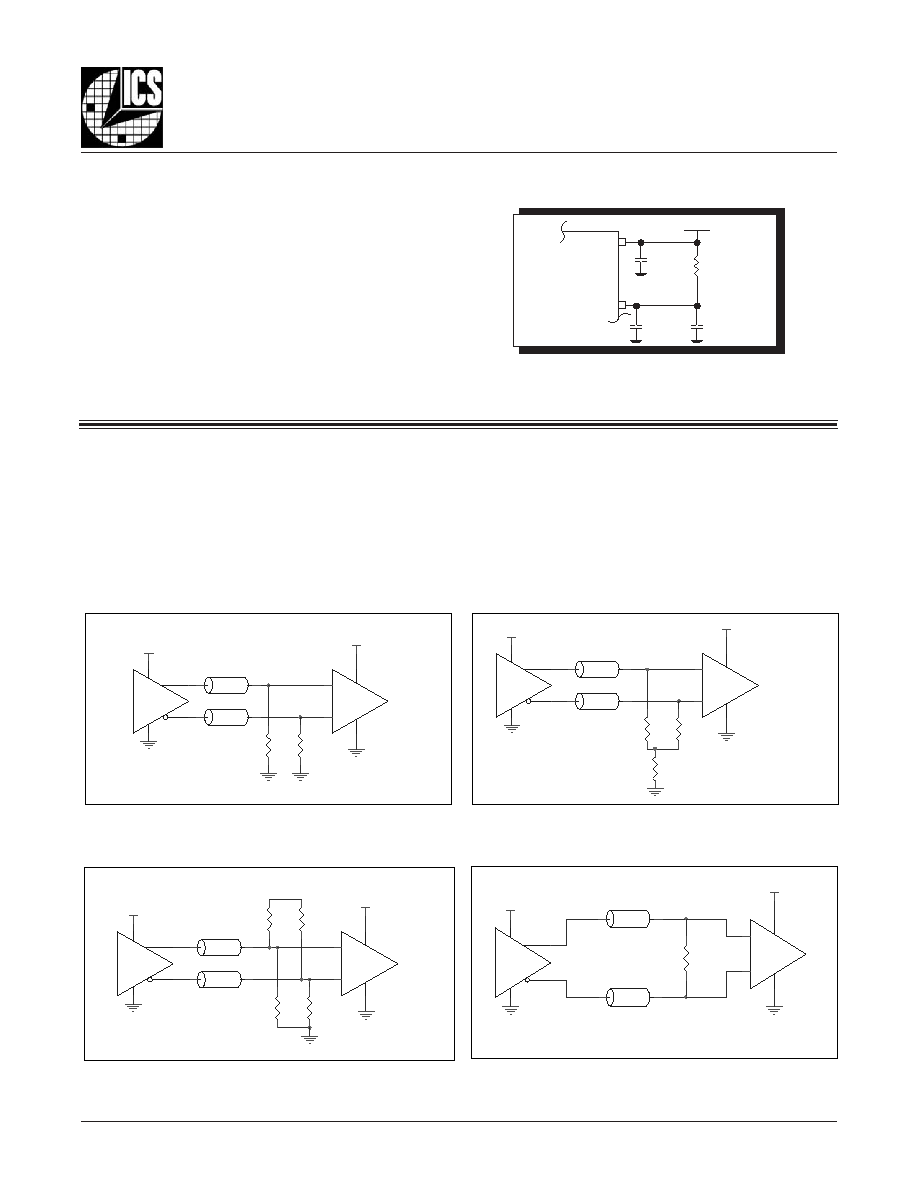

- Frequency Translation

- Frequency Configuration

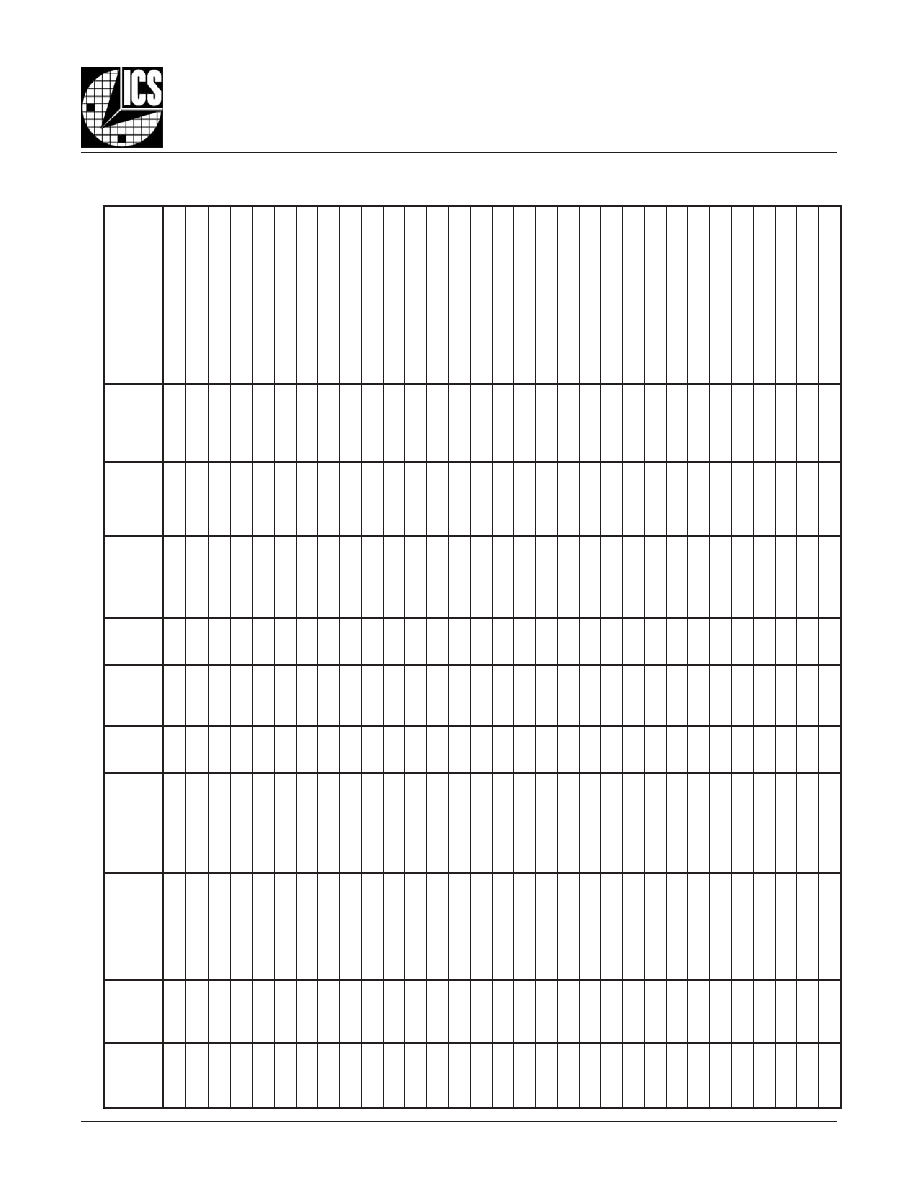

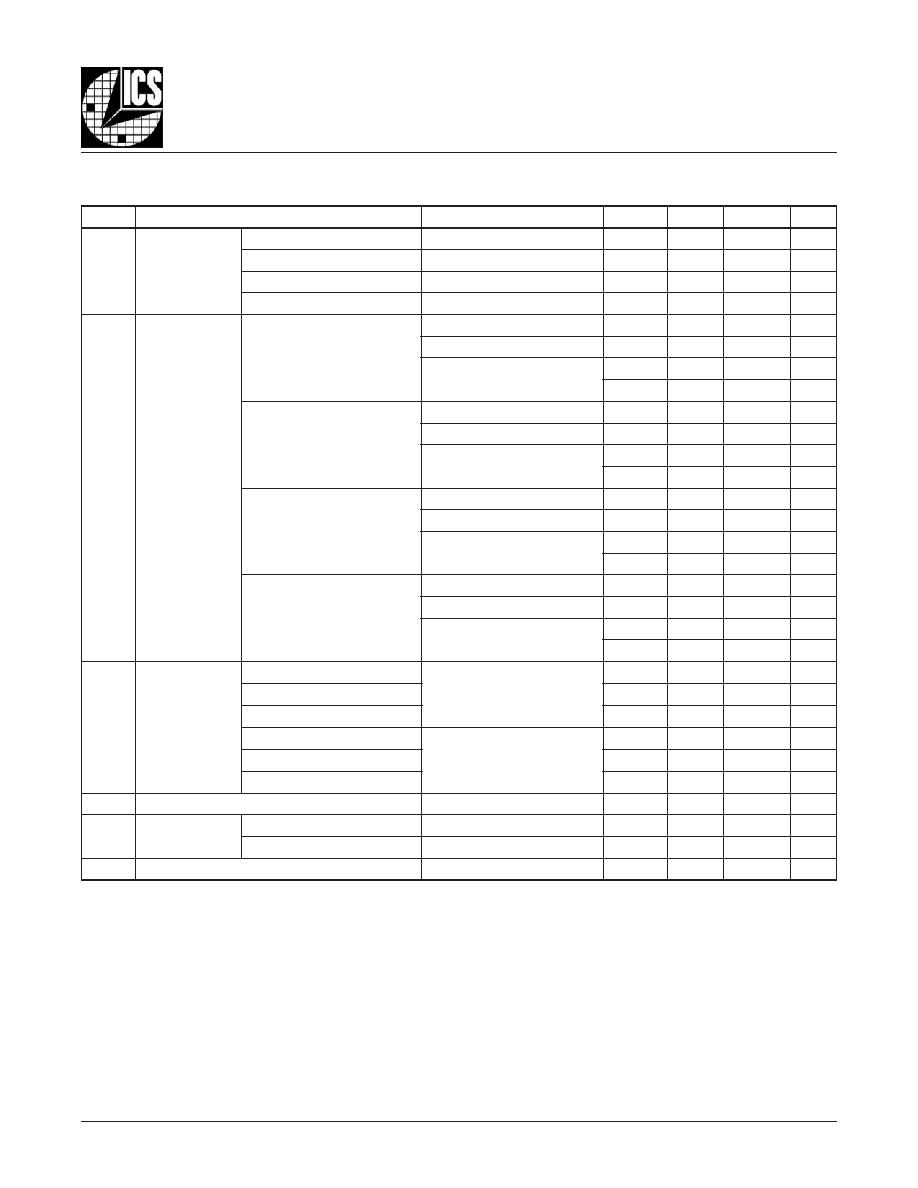

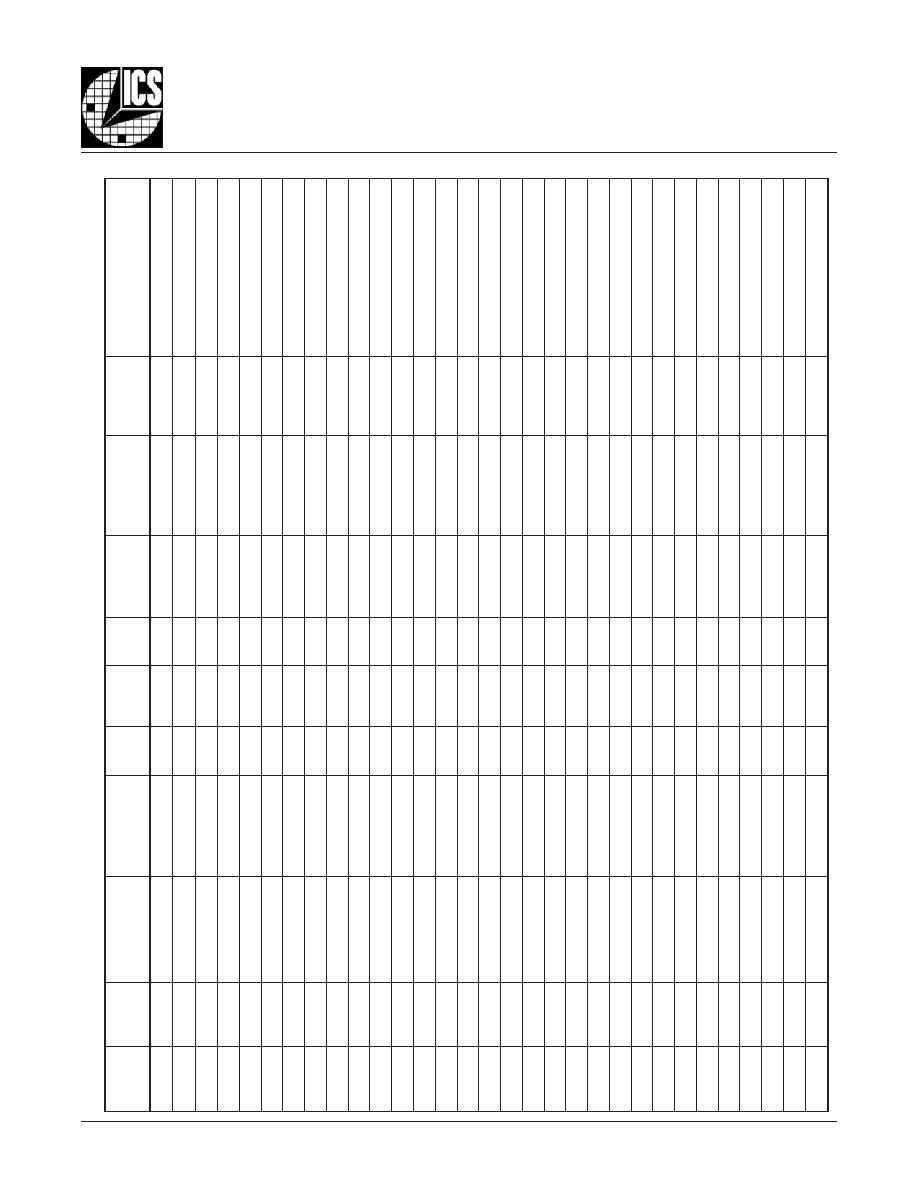

- Frequency Configuration Examples

- Frequency Configuration Examples, continued

- Frequency Configuration Examples, continued

- Frequency Configuration Examples, continued

- Frequency Configuration Examples, continued

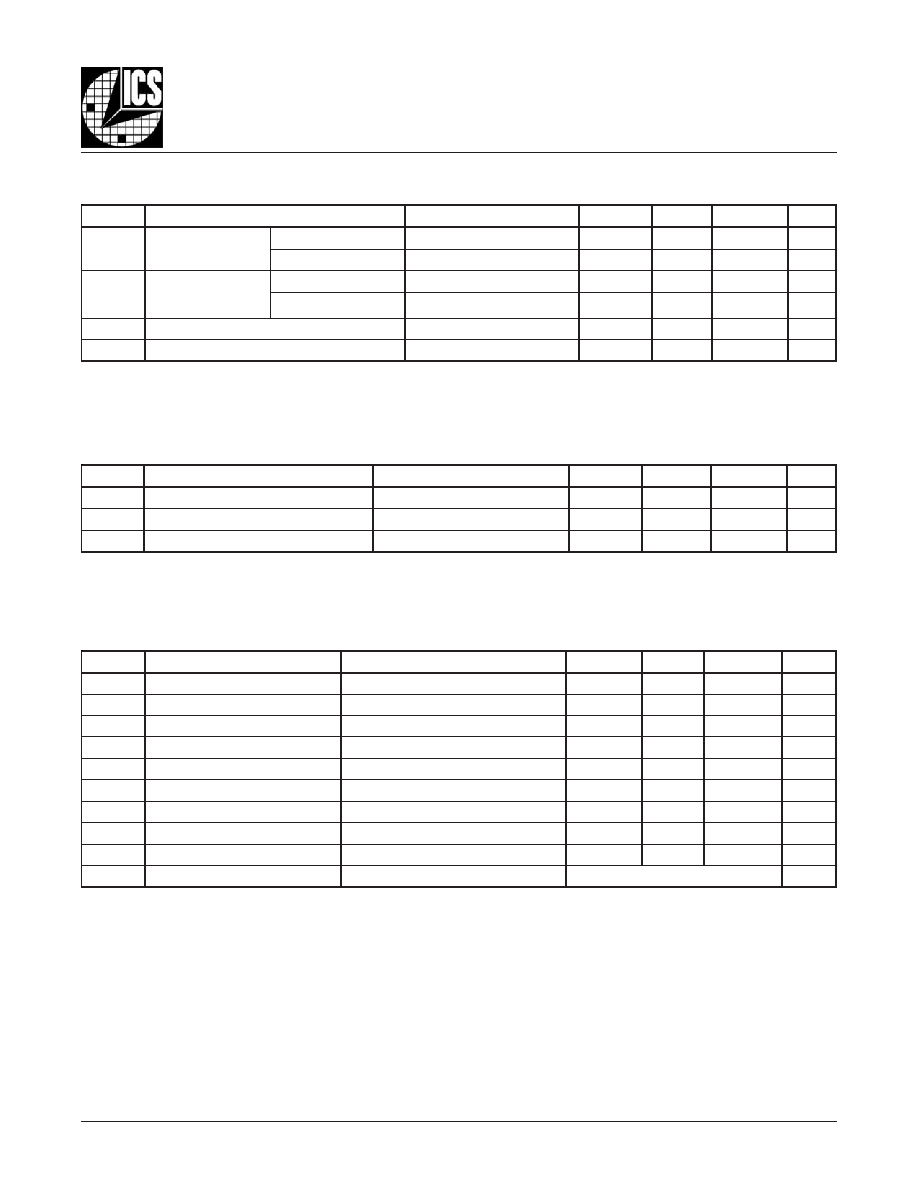

- Absolute Maximum Ratings

- Power Supply DC Characteristics

- LVCMOS DC Characteristics

- Differential DC Characteristics

- LVPECL DC Characteristics

- Crystal Characteristics

- AC Characteristics

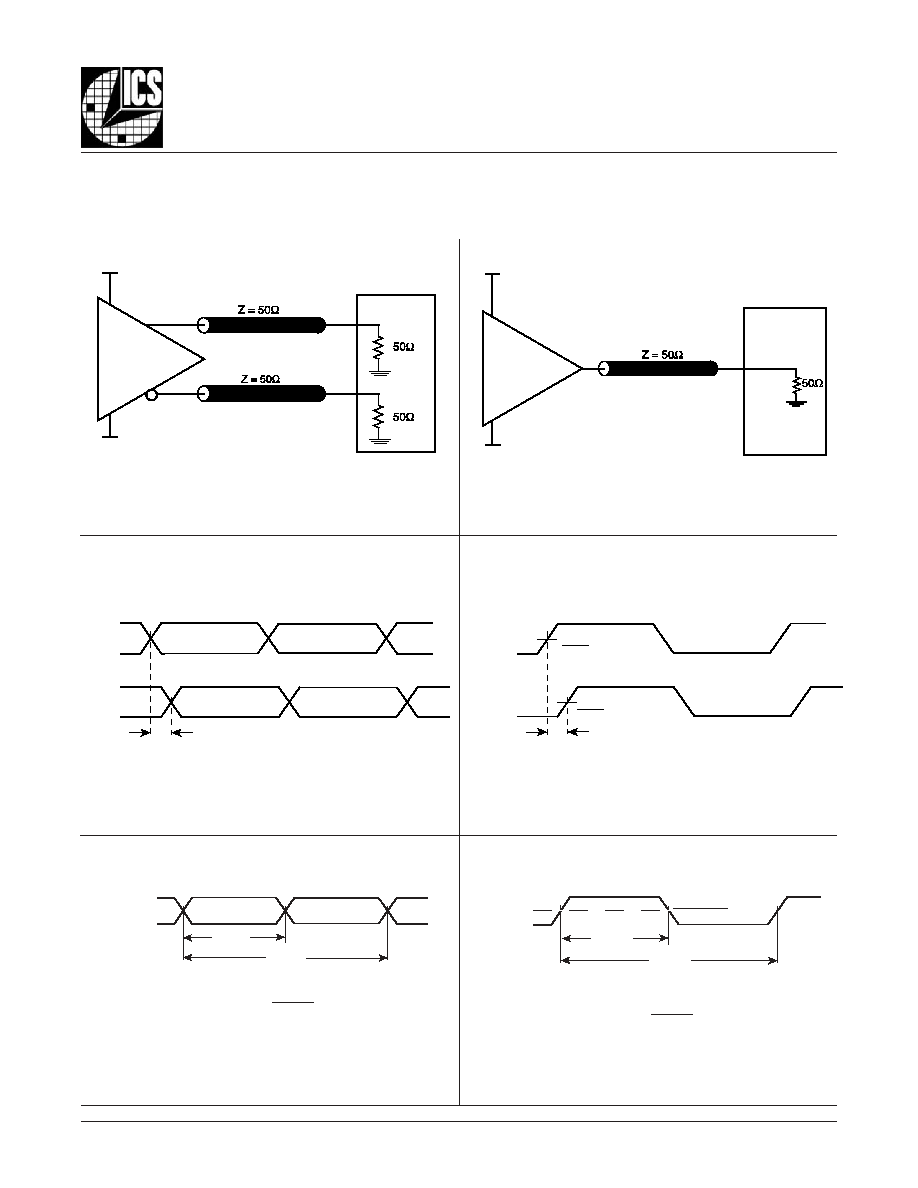

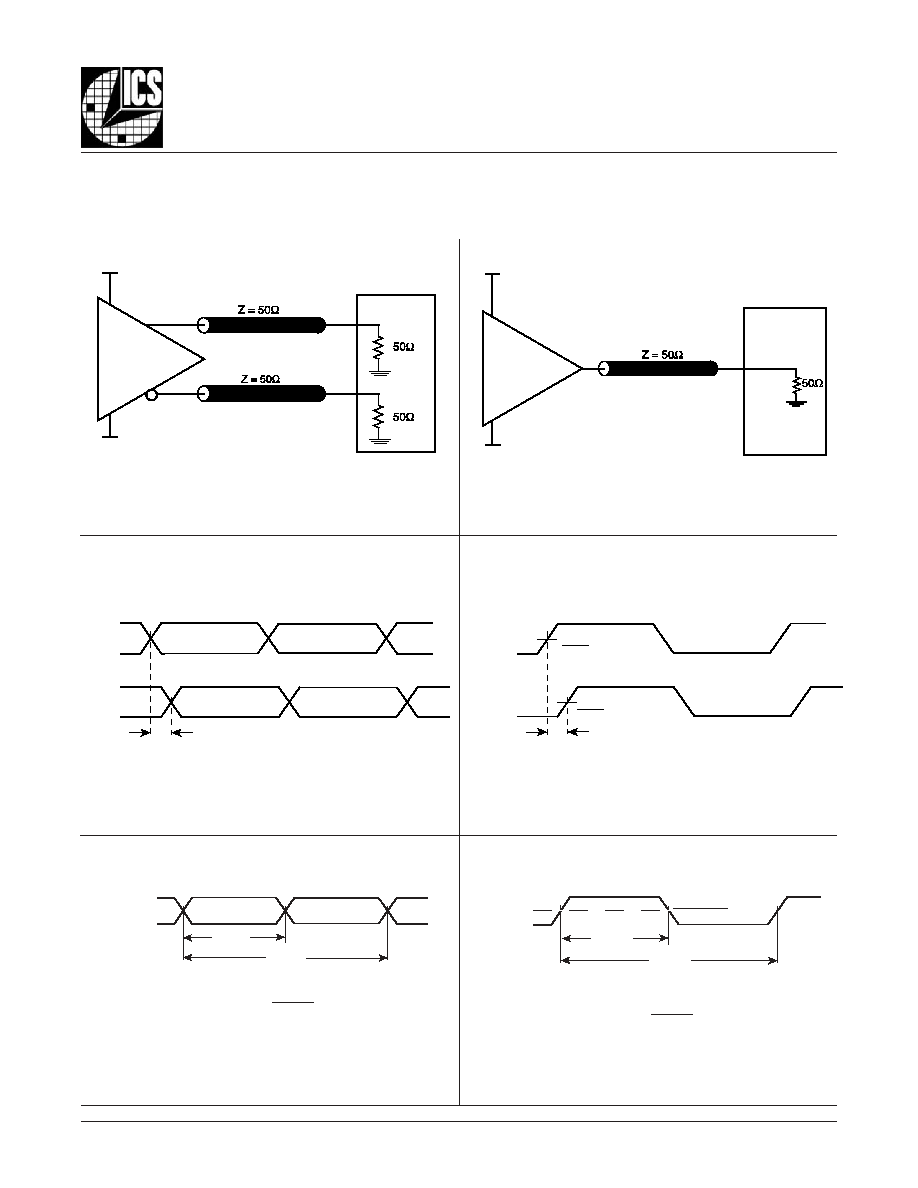

- Parameter Measurement Information

- Parameter Measurement Information, continued

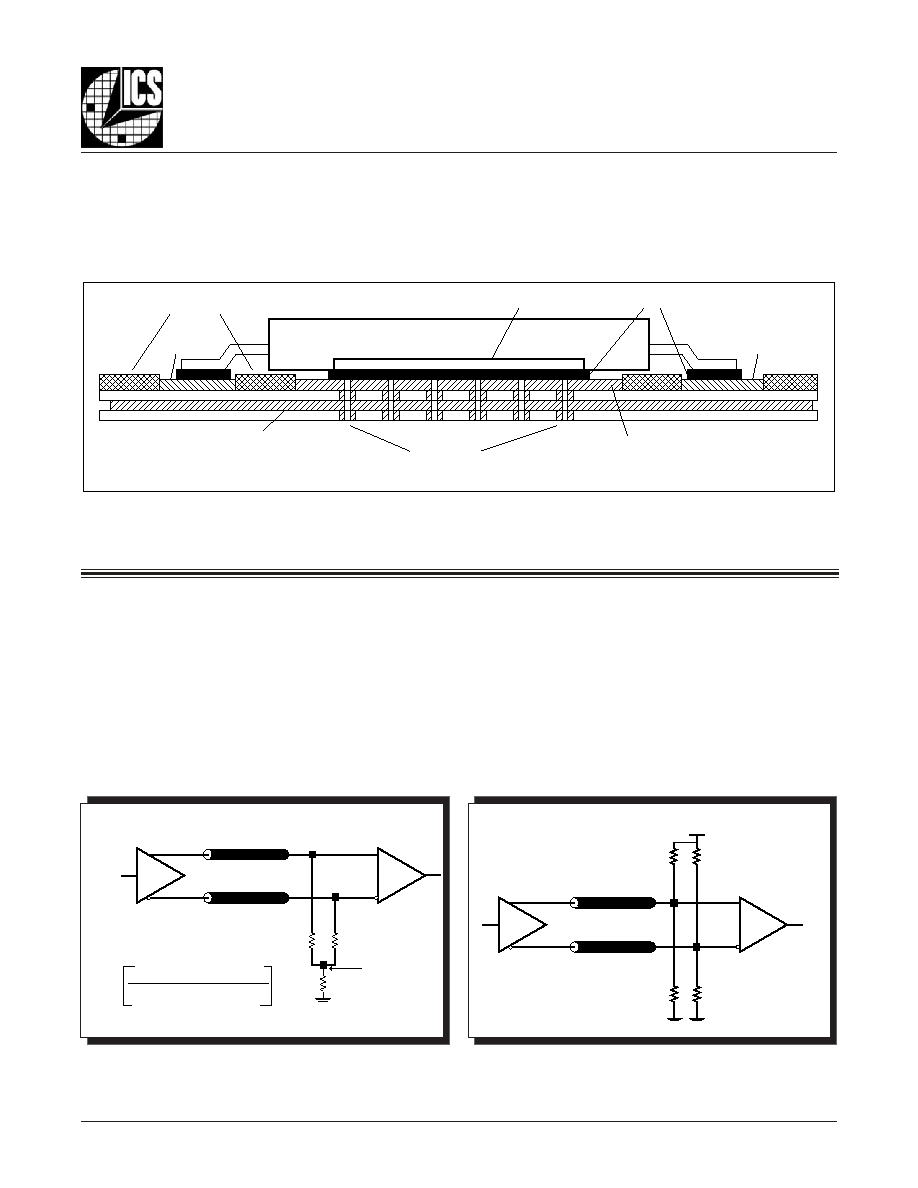

- Application Information

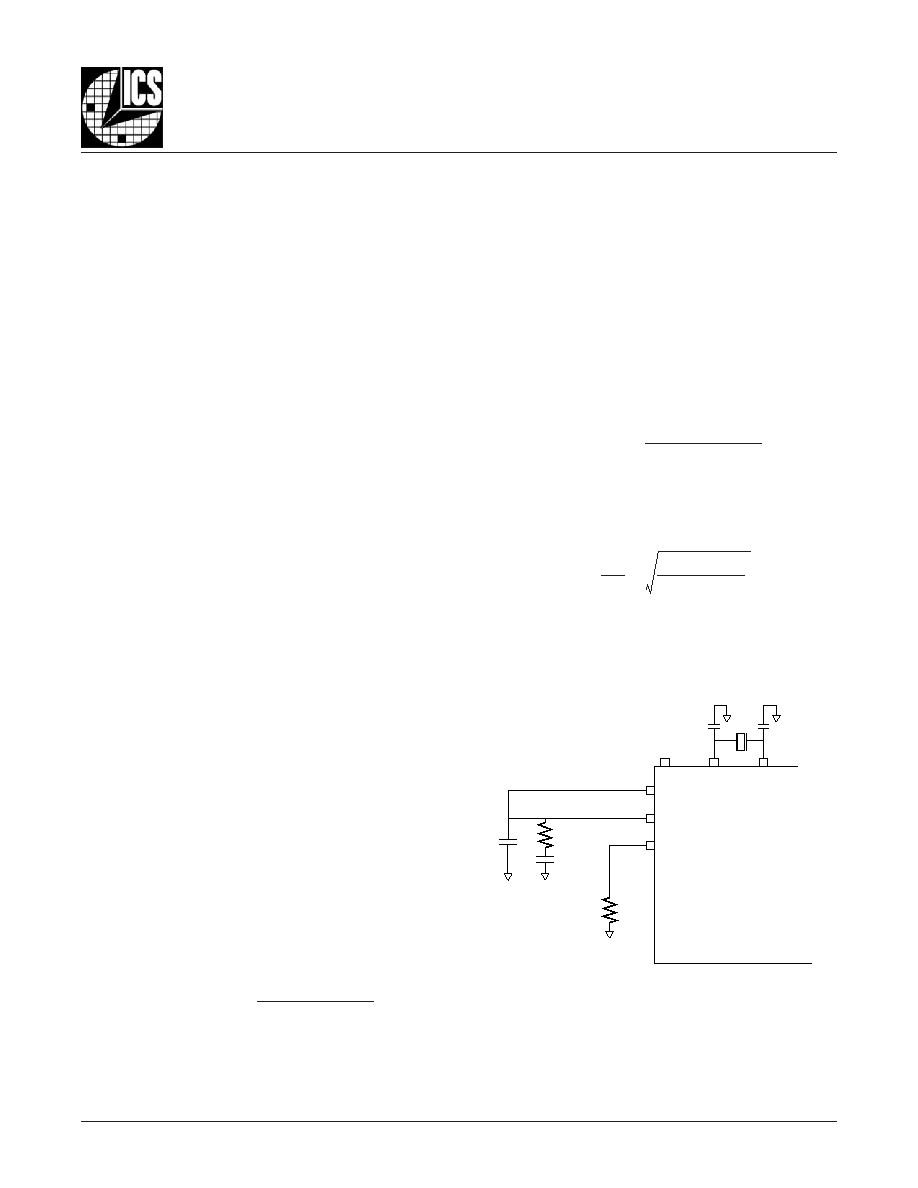

- Description of the PLL Stages

- VCXO PLL Loop Response Considerations

- Setting the VCXO PLL Loop Response

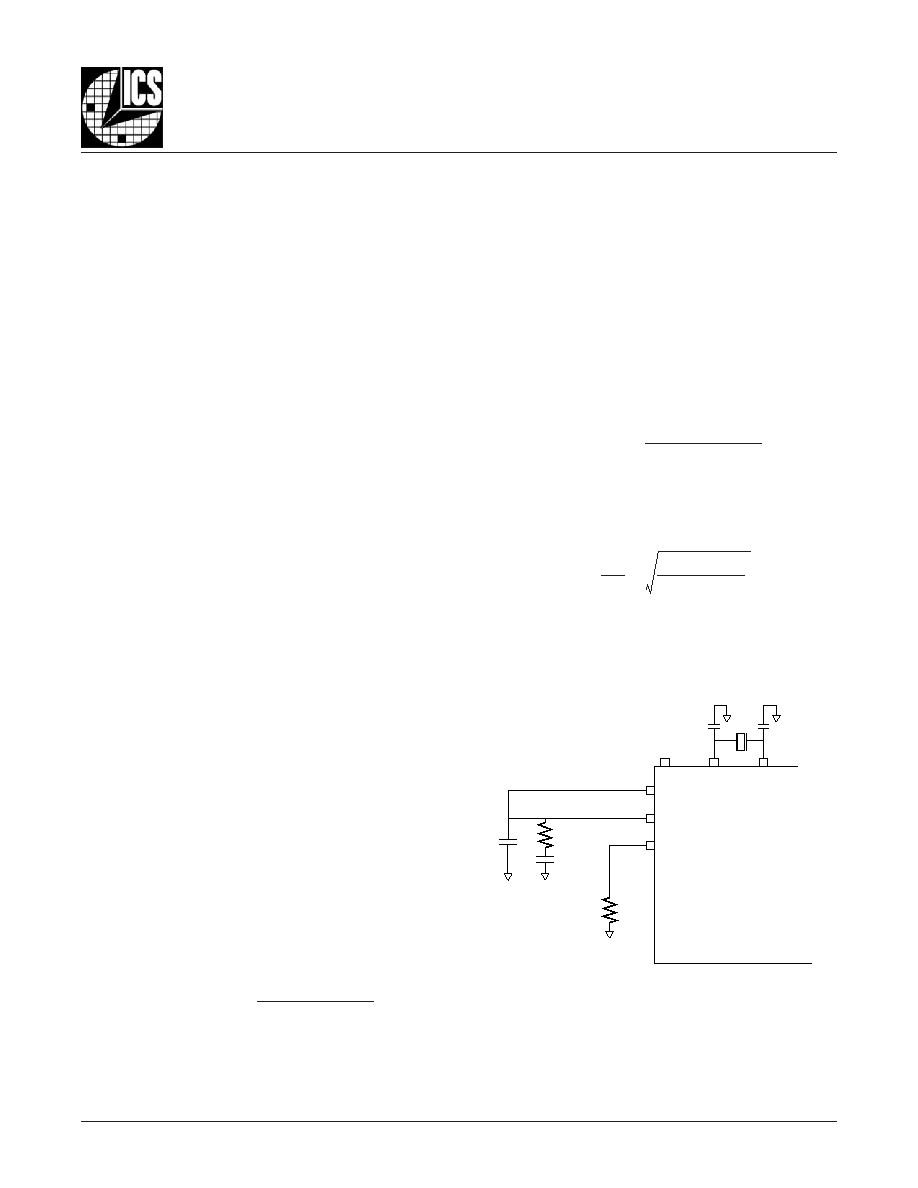

- External VCXO PLL Component Diagram

- Notes on Setting the Value of Cp

- Notes on External Crystal Load Capacitors

- Loop Filter Response Software

- Notes on Setting Charge Pump Current

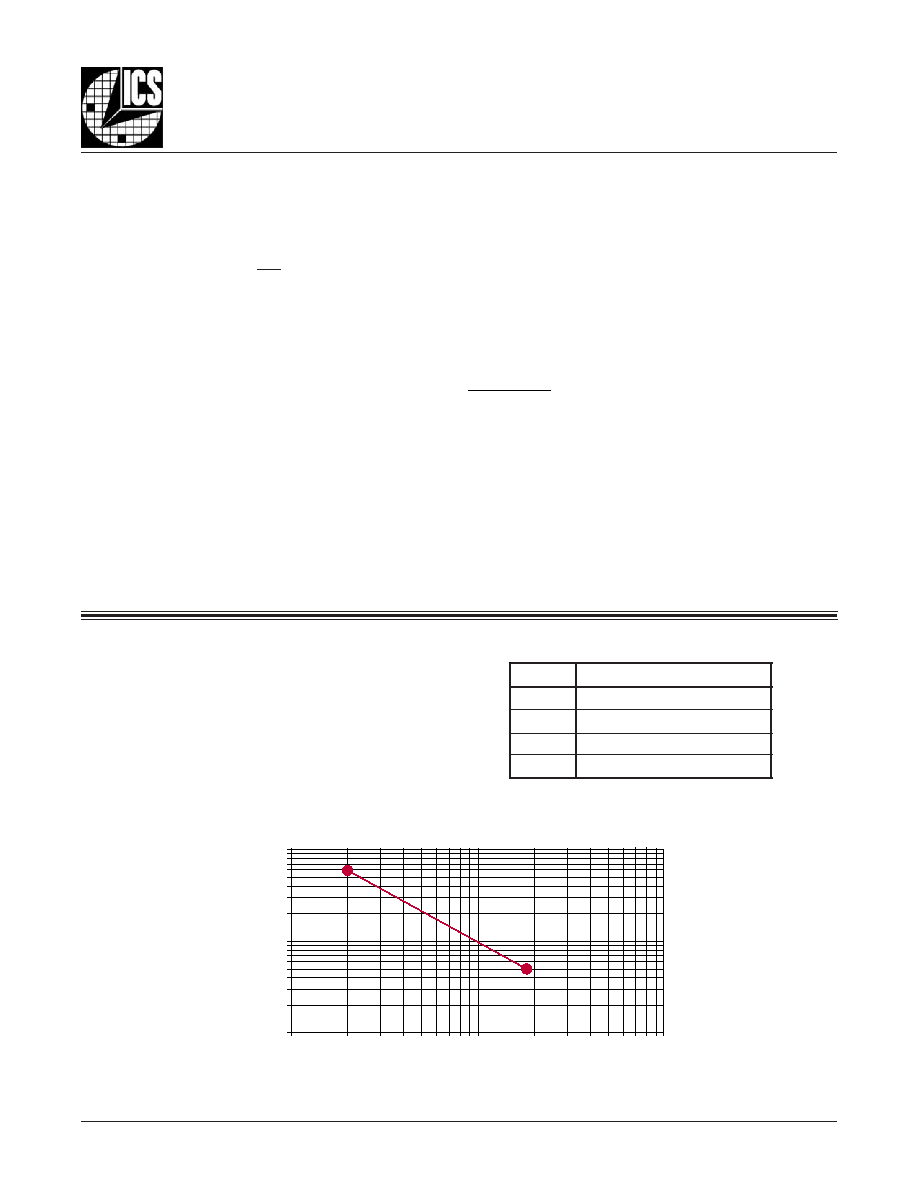

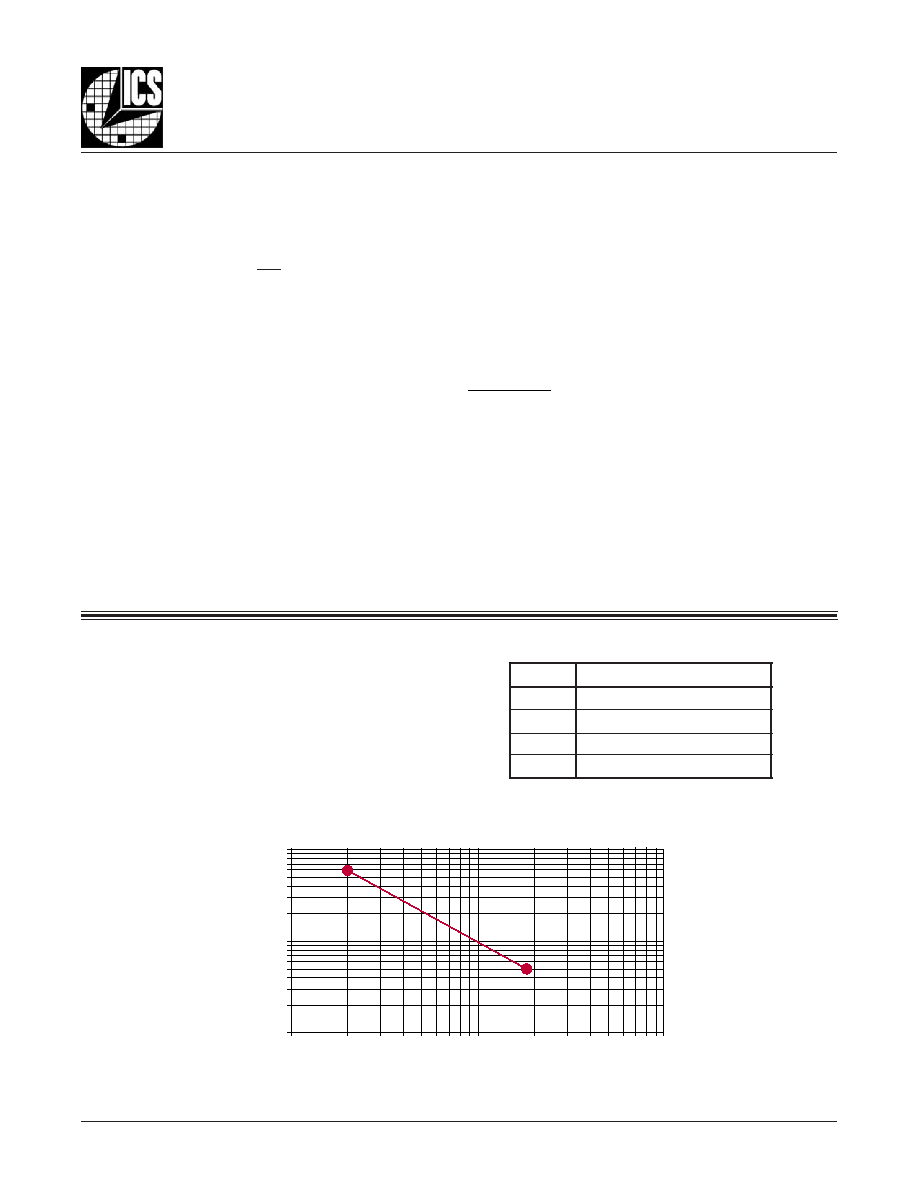

- Charge Pump Current vs Value of Rset Plot

- VCXO Gain vs XTAL Frequency Plot

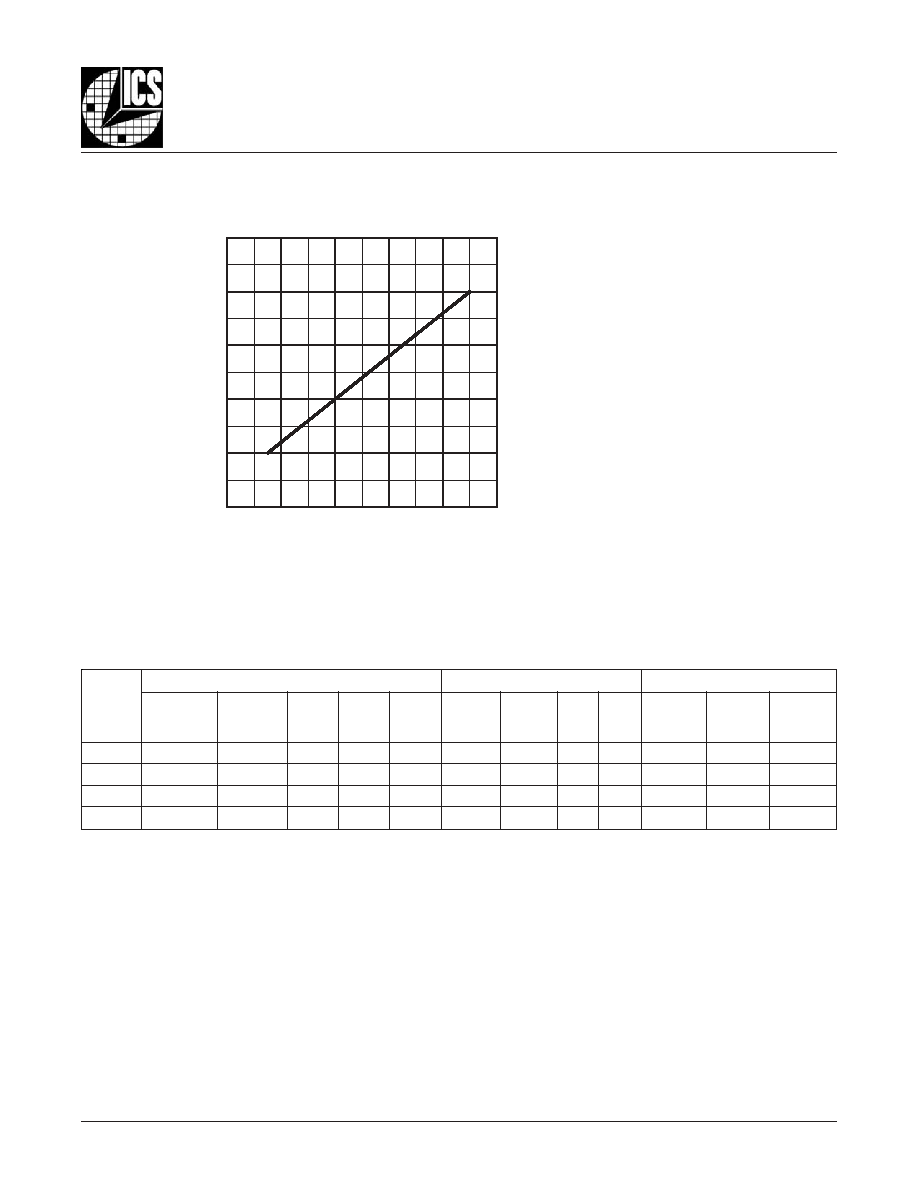

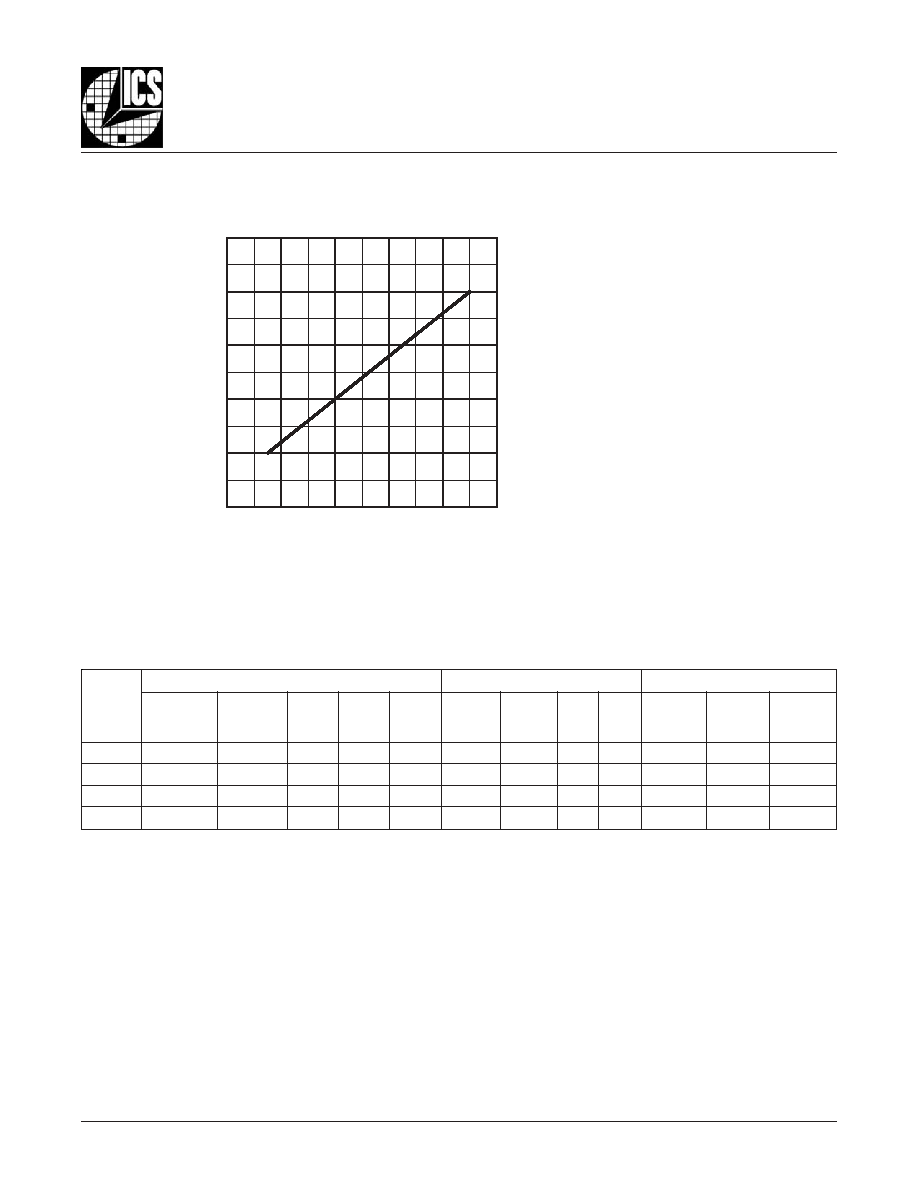

- Example Loop Filter Component Value

- Power Supply Filtering Techniques

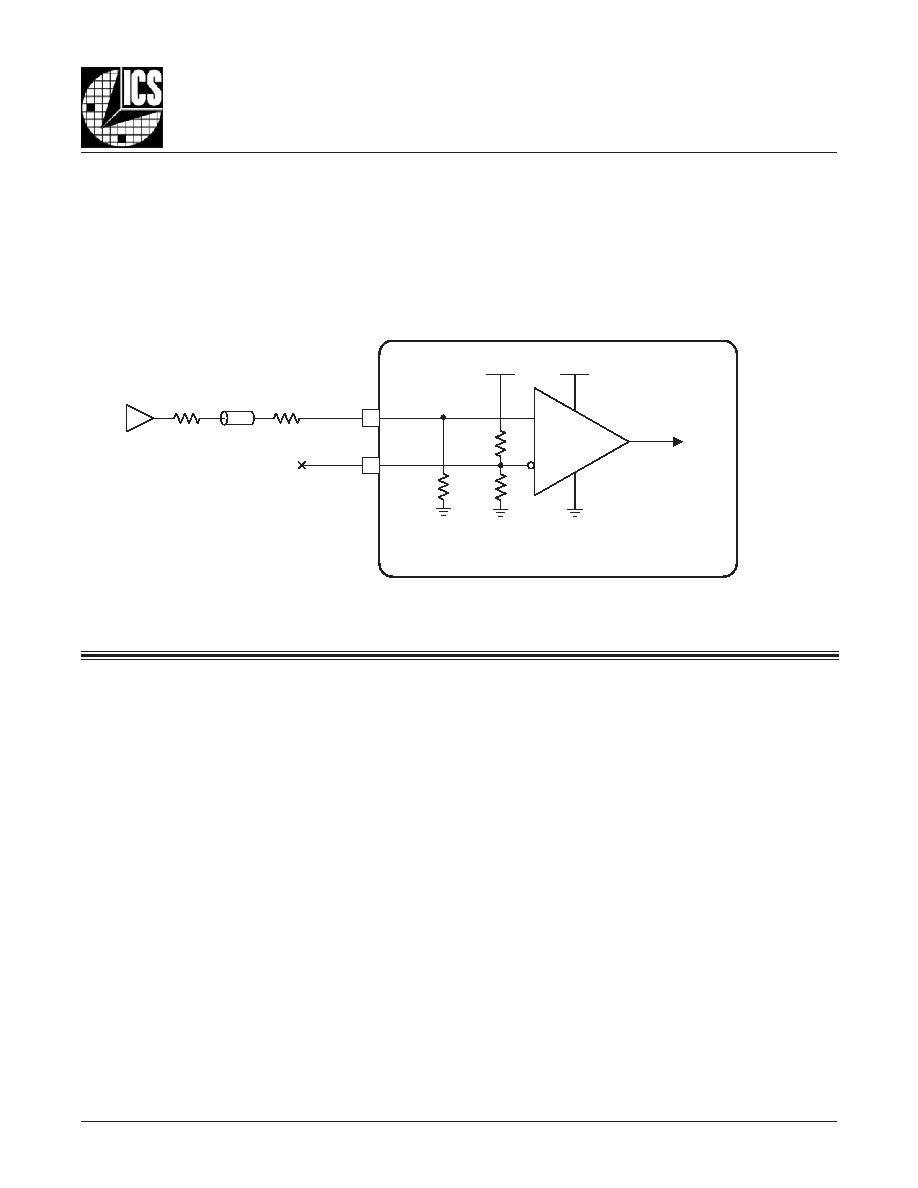

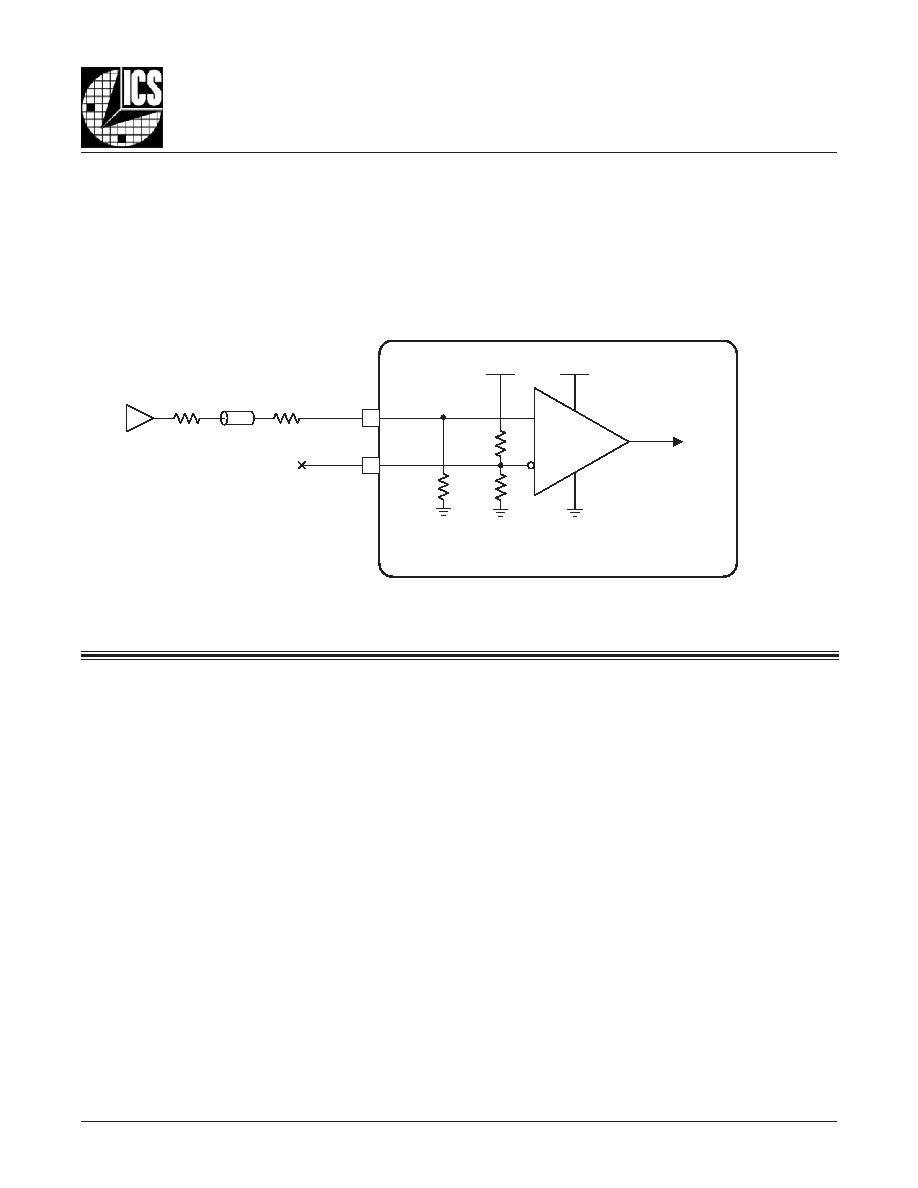

- Differential Clock Input Interface

- Differential Clock Input Circuit

- Recommendations for Unused Input and Output Pins

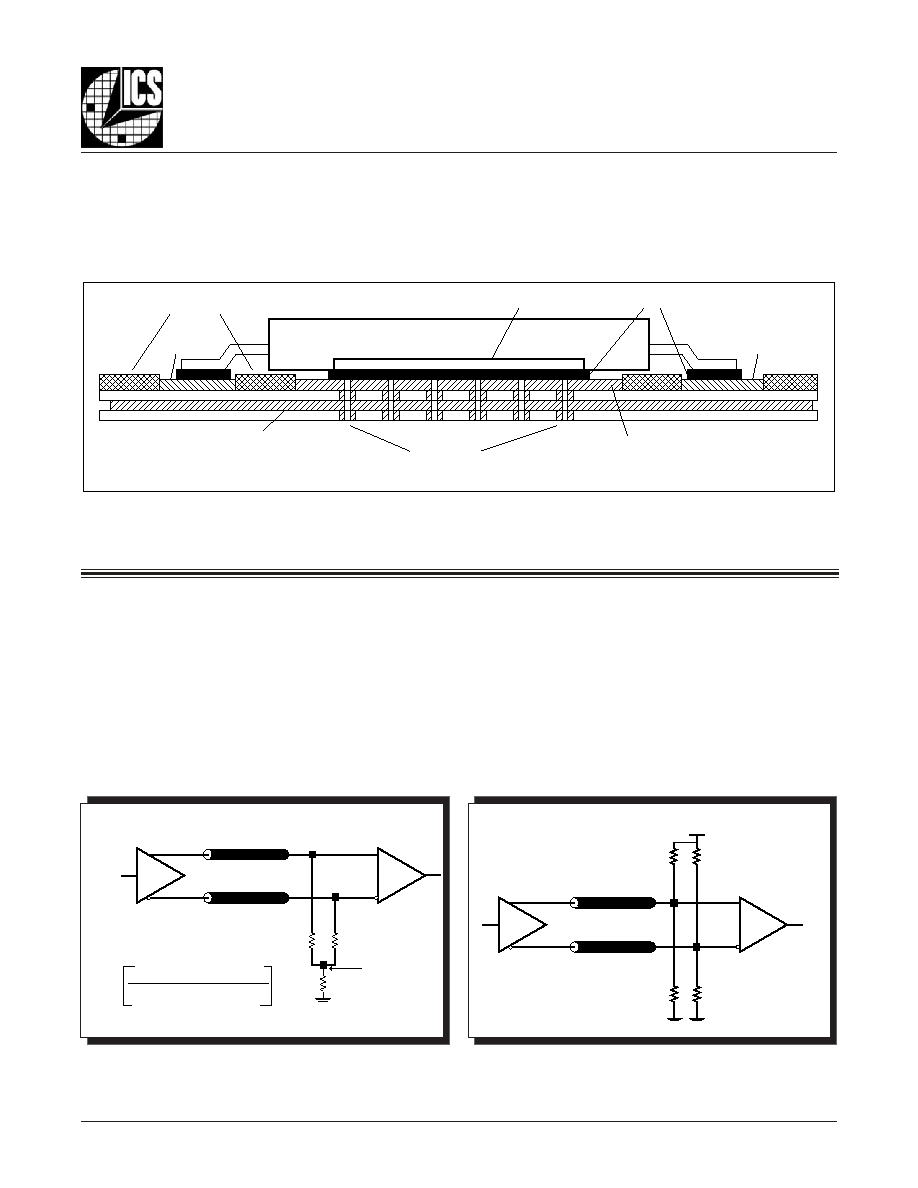

- Thermal Release Path

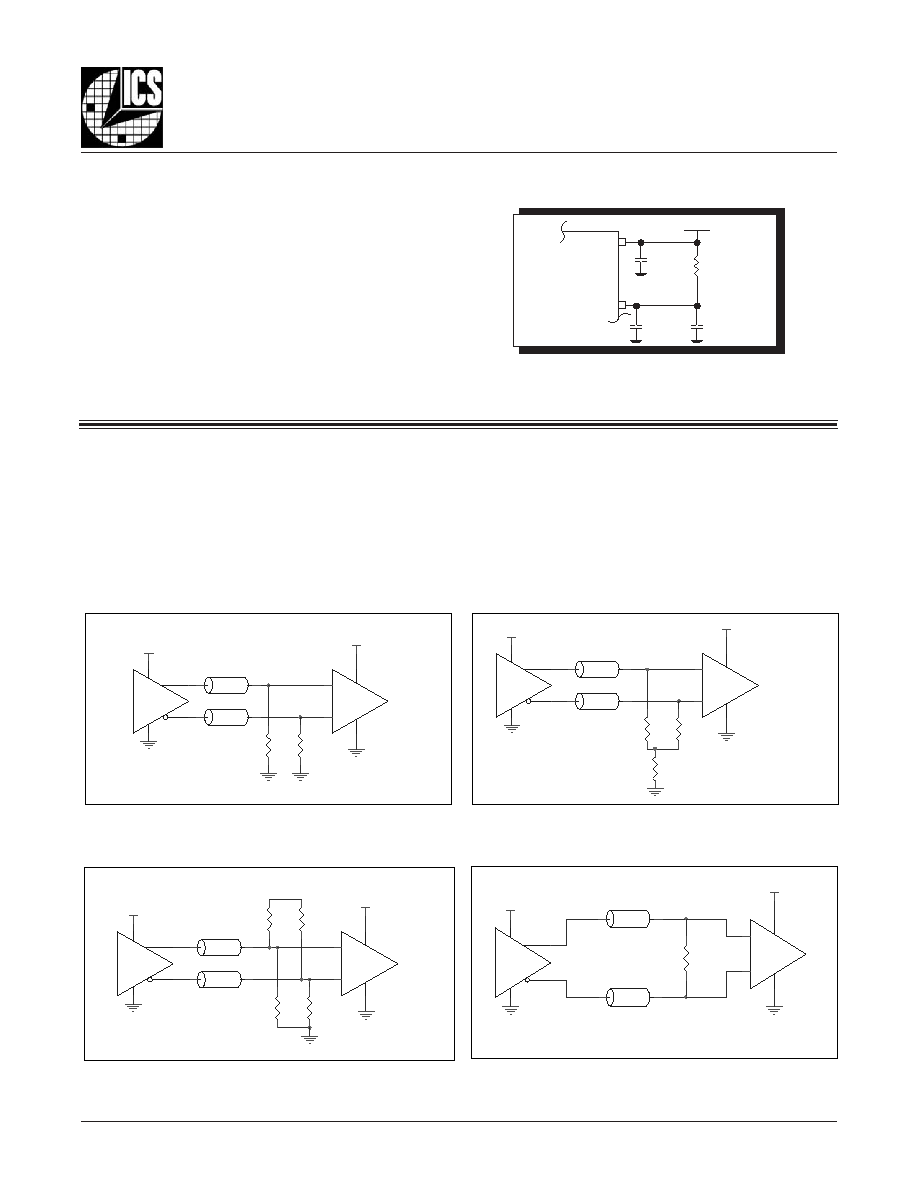

- Termination for LVPECL Outputs

- Reliabilty Information

- Transistor Count

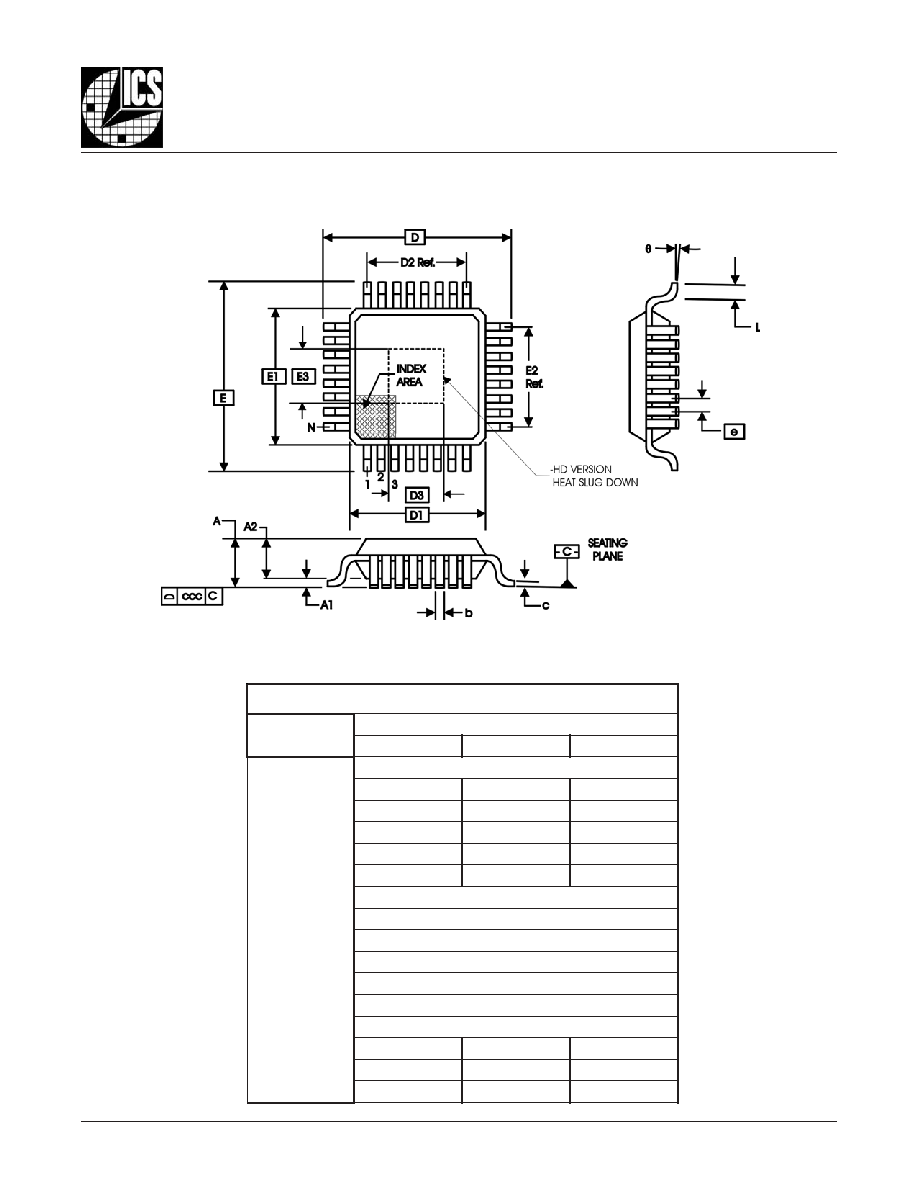

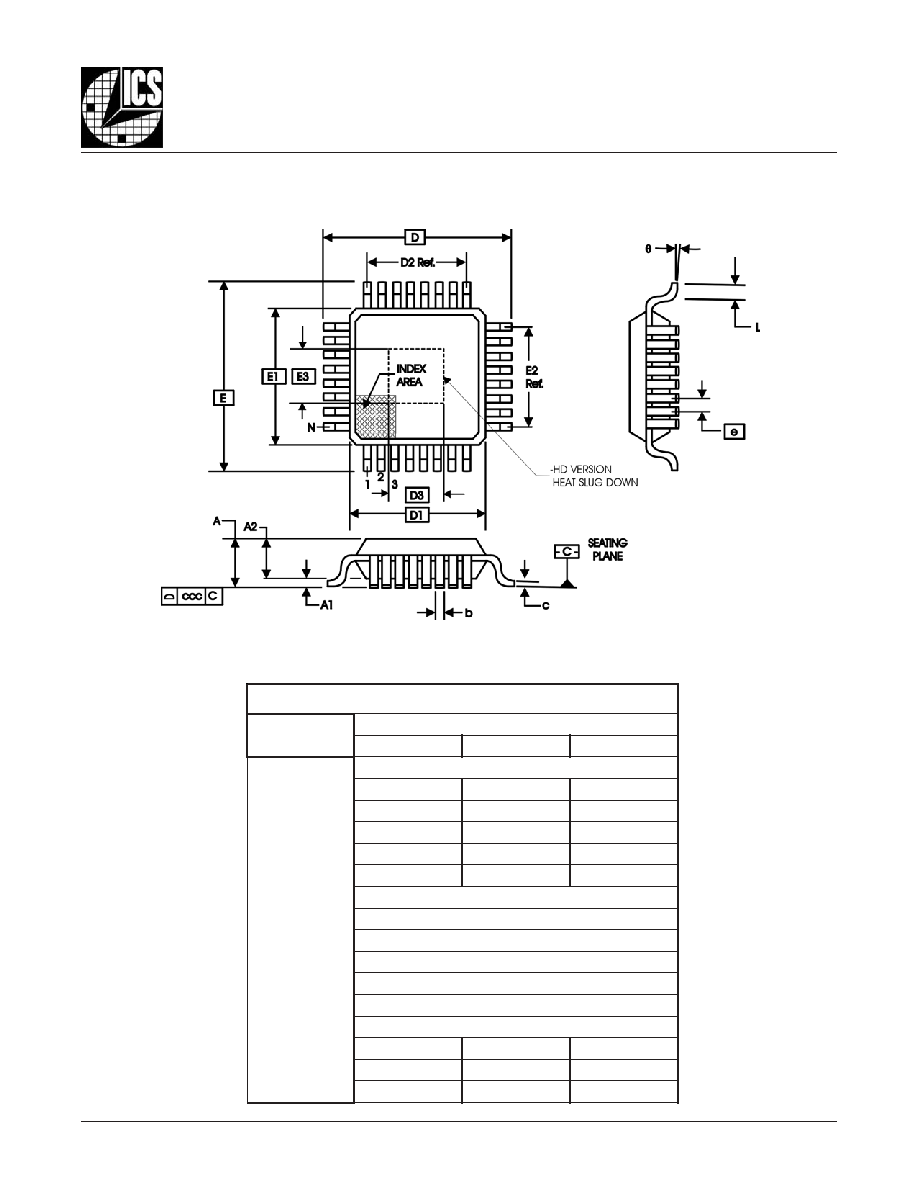

- Package Outline

- Package Dimensions

- Ordering Information

843002CY-31

www.icst.com/products/hiperclocks.html

REV. B NOVEMBER 22, 2005

1

Integrated

Circuit

Systems, Inc.

ICS843002-31

700MH

Z

F

EMTO

C

LOCKS

TM VCXO B

ASED

F

REQUENCY

T

RANSLATOR

AND

J

ITTER

A

TTENUATOR

PRELIMINARY

G

ENERAL

D

ESCRIPTION

T h e I C S 8 4 3 0 0 2 - 3 1 i s a m e m b e r o f t h e

HiperClockSTM family of high performance clock

solutions from ICS. This monolithic device is a

high-performance, PLL-based synchronous

clock generator and jitter attenuation circuit. The

ICS843002-31 contains two clock multiplication stages that

are cascaded in series. The first stage is a VCXO-based PLL

that is optimized to provide reference clock jitter attenuation,

to be jitter tolerant, and to provide a stable reference clock

for the second multiplication stage. The second stage is the

proprietary ICS FemtoClockTM

circuit which is a high-frequency,

sub-picosecond clock multiplier.

The VCXO PLL has an on-chip VCXO circuit that uses an

external, inexpensive pullable crystal in the 17.5 to 25MHz

range. The PLL includes 13 bit reference and feedback

dividers supporting complex PLL multiplication ratios and

input reference clock rates as low as 2.3kHz. External loop

filter components are used (two resistors and two capacitors)

to achieve the low loop bandwidth needed for jitter atten-

uation of a recovered data clock.

The FemtoClock circuit can multiply the VCXO crystal

frequency by a factor of 28 or 32 (selectable) and provide a

clock output of up to 700MHz.

Clock Input/Output Configuration:

� Clock Inputs - one differential pair, two singled ended

(mux selected)

� Differential input pair can support LVPECL, LVDS,

LVHSTL, SSTL, HCSL or single-ended LVCMOS

or LVTTL levels

� Singled ended inputs can support LVCMOS or

LVTTL levels

� Clock Outputs, FemtoClockS two LVPECL pairs

(selectable output dividers)

� Clock Output, VCXO � one single ended output

(at VCXO crystal frequency)

� Clock Output, other � VCXO reference clock

Example Applications:

� SONET/SDH line card clock generator (up to 622.08MHz

for OC-48) using 8kHz frame clock as input reference

� Jitter attenuation of a recovered communications clock

� Complex-ratio clock frequency translation between

various communication protocols, such as:

� For telecom, OC-12 to E3 rate conversion, 622.08MHz

to 34.368MHz, PLL ratio of 179/32

� For digital video, ITU-R601 to SMPTE 252M/59.94,

27MHz to 74.17582MHz, PLL ratio of 250/91

P

IN

A

SSIGNMENT

F

EATURES

� Outputs:

� Two high frequency differential LVPECL outputs

Output frequency: up to 700MHz

� One LVCMOS/LVTTL VCXO PLL output with output

enable

� One Reference clock output with output enable

� One LOCK detect output

� Input mux supports 3 selectable inputs: one differential

input pair and two LVCMOS/LVTTL input clocks

� 13-bit VCXO PLL feedback and reference dividers provide

wide range of frequency translation ratio options

� FemtoClock frequency multiplier supports rate of:

560MHz - 700MHz

� `Lock Detect' output reports lock status of VCXO PLL

� VCXO PLL circuit provides jitter attenuation with

loop bandwidth of 250Hz and below (user adjustable)

� RMS phase jitter, random at 12kHz to 20MHz:

<1ps (design target)

� 3.3V supply voltage

� 0�C to 70�C ambient operating temperature

� Industrial temperature information available upon request

� Available in both standard and lead-free RoHS-compliant

packages

HiPerClockSTM

ICS

64-Lead TQFP, EPAD

10mm x 10mm x 1.0mm

package body

Y package

Top View

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49

17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

ICS843002-31

V

EE

REF_CLK

VCLK

LOCK

V

CCO

_

CMOS

nQB

Q B

V

EE

nQA

Q A

V

CCO

_

PECL

MP

NPB0

NPB1

NPB2

V

CCA

LF1

LF0

ISET

V

EE

NV1

NV0

V

CC

MR

CLK0

nCLK0

OE_REF

CLK1

V

CC

SEL1

SEL0

CLK2

XOIN12

XOIN11

XOIN10

XOIN9

XOIN8

XOIN7

XOIN6

XOIN5

XOIN4

XOIN3

XOIN2

XOIN1

XOIN0

NP

A2

NP

A1

NP

A0

V

CCA

_

XO

XT

AL_IN

X

T

AL_OUT

XOFB0

XOFB1

XOFB2

XOFB3

XOFB4

XOFB5

XOFB6

XOFB7

XOFB8

XOFB9

XOFB10

XOFB11

XOFB12

The Preliminary Information presented herein represents a product in prototyping or pre-production. The noted characteristics are based on initial

product characterization. Integrated Circuit Systems, Incorporated (ICS) reserves the right to change any circuitry or specifications without notice.

843002CY-31

www.icst.com/products/hiperclocks.html

REV. B NOVEMBER 22, 2005

2

Integrated

Circuit

Systems, Inc.

ICS843002-31

700MH

Z

F

EMTO

C

LOCKS

TM VCXO B

ASED

F

REQUENCY

T

RANSLATOR

AND

J

ITTER

A

TTENUATOR

PRELIMINARY

B

LOCK

D

IAGRAM

- N

OMINAL

S

YSTEM

C

ONFIGURATION

00

01

10

11

Bypass

Input Divider

XOIN[12:0]

�1 to �8191

VCXO PLL

FemtoClockTM

Frequency

Multiplier

VCXO PLL

Feedback Divider

XOFB[12:0]

�1 to �8191

VCXO PLL Output

Divider NV[1:0]

00: �1

01: �12

10: �16

11: Disabled Drive Low

QA Output

Divider NPA[2:0]

000: �1

001: �2

010: �4

011: �8

100: �12

101: �14

110: �16

111: Disabled

Drive Low

QB Output

Divider NPB[2:0]

000: QA �1

001: QA �2

010: QA �4

011: QA �8

100: XOIN Output

101: OFB Output

110: MP Output

111: Disabled

Drive Low

LOCK Detect

3

3

2

13

13

ISET

Charge Pump Current

17.5 - 25MHz

External Loop

Filter Connection

XT

AL_IN

XT

AL_OUT

LF0 LF1

>1 1

0: x32

1: x28

NPB[2:0]

NPA[2:0]

NV[1:0]

CLK0

nCLK0

CLK1

CLK2

SEL1

SEL0

XOIN[12:0]

XOFB[12:0]

MP

OE_REF

VCLK

Q A

nQA

Q B

nQB

REF_CLK

LOCK

NOTE 1: For application configuration (non-test/bypass modes).

NOTE 2: Bold lines are primary clock paths (non-control/non-feedback lines).

Not all control lines and signal paths are shown in this simplified block diagram.

843002CY-31

www.icst.com/products/hiperclocks.html

REV. B NOVEMBER 22, 2005

3

Integrated

Circuit

Systems, Inc.

ICS843002-31

700MH

Z

F

EMTO

C

LOCKS

TM VCXO B

ASED

F

REQUENCY

T

RANSLATOR

AND

J

ITTER

A

TTENUATOR

PRELIMINARY

S

IMPLIFIED

B

LOCK

D

IAGRAM

- C

LOCK

S

IGNAL

P

ATHS

IN

B

YPASS

M

ODE

1 1 Bypass

0 1

1 0

Input Divider

XOIN[12:0]

�1 to �8191

ISET

Charge Pump

Current

17.5 - 25MHz

External Loop

Filter Connection

LF0 LF1

XT

AL_OUT

XT

AL_IN

VCXO PLL

VCXO PLL Output

Divider NV[1:0]

00: �1

01: �12

10: �16

11: Disabled Drive Low

VCXO PLL

Feedback Divider

XOFB[12:0]

�1 to �8191

QA Output

Divider NPA[2:0]

NPA[2:0]

000: �1

001: �2

010: �4

011: �8

100: �12

101: �14

110: �16

111: Disabled Drive Low

FemtoClockTM

Feedback Divider

MP

0: �32

1: �28

000: �1

001: �2

010: �4

011: �8

111: Disabled

110: MP

101: XOFB

100: XOIN

FemtoClockTM

Frequency

Multiplier

VCLK

QA

nQA

QB

nQB

CLK0

nCLK0

SEL1 = 1

SEL0 = 1

CLK1

CLK2

NPB2

NPB1

NPB0

NOTE 1: Setting SEL1:SEL0 = 11 enables bypass mode.

Only clock signals on the CLK0/nCLK0 input pair are routed

to the device in bypass mode.

NOTE 2: Bold lines show clock bypass paths.

Not all control lines and signal paths are shown in this

simplified block diagram.

843002CY-31

www.icst.com/products/hiperclocks.html

REV. B NOVEMBER 22, 2005

4

Integrated

Circuit

Systems, Inc.

ICS843002-31

700MH

Z

F

EMTO

C

LOCKS

TM VCXO B

ASED

F

REQUENCY

T

RANSLATOR

AND

J

ITTER

A

TTENUATOR

PRELIMINARY

T

ABLE

1. P

IN

D

ESCRIPTIONS

(

CONTINUED

ON

NEXT

PAGE

)

r

e

b

m

u

N

e

m

a

N

e

p

y

T

n

o

i

t

p

i

r

c

s

e

D

2

,

1

0

F

L

,

1

F

L

g

o

l

a

n

A

t

u

p

t

u

O

/

t

u

p

n

I

.

s

n

i

p

n

o

i

t

c

e

n

n

o

c

r

e

t

li

f

p

o

o

L

3

T

E

S

I

g

o

l

a

n

A

t

u

p

t

u

O

/

t

u

p

n

I

.

n

i

p

g

n

i

t

t

e

s

t

n

e

r

r

u

c

p

m

u

p

e

g

r

a

h

C

8

4

,

1

4

,

4

V

E

E

r

e

w

o

P

.

d

n

u

o

r

g

o

t

d

e

t

c

e

n

n

o

c

y

ll

a

m

r

o

N

.

s

n

i

p

y

l

p

p

u

s

e

v

i

t

a

g

e

N

6

,

5

0

V

N

,

1

V

N

t

u

p

n

I

p

u

ll

u

P

.

s

n

i

p

l

o

r

t

n

o

c

r

e

d

i

v

i

d

t

u

p

t

u

o

L

L

P

O

X

C

V

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

3

1

,

7

V

C

C

r

e

w

o

P

.

s

n

i

p

y

l

p

p

u

s

r

e

w

o

p

e

r

o

C

8

R

M

t

u

p

n

I

n

w

o

d

ll

u

P

d

n

a

s

r

e

d

i

v

i

d

l

a

n

r

e

t

n

i

ll

a

s

t

e

s

e

r

,

H

G

I

H

n

e

h

W

.

t

e

s

e

R

r

e

t

s

a

M

.

e

c

n

a

d

e

p

m

i

h

g

i

h

n

i

e

r

a

s

t

u

p

t

u

o

S

O

M

C

V

L

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

9

0

K

L

C

t

u

p

n

I

n

w

o

d

ll

u

P

.

t

u

p

n

i

k

c

o

l

c

l

a

i

t

n

e

r

e

f

f

i

d

g

n

i

t

r

e

v

n

i

-

n

o

N

0

1

0

K

L

C

n

t

u

p

n

I

/

p

u

ll

u

P

n

w

o

d

ll

u

P

.

t

u

p

n

i

k

c

o

l

c

l

a

i

t

n

e

r

e

f

f

i

d

g

n

i

t

r

e

v

n

I

V

C

C

.

g

n

i

t

a

o

l

f

t

f

e

l

n

e

h

w

e

g

a

t

l

o

v

s

a

i

b

2

/

1

1

F

E

R

_

E

O

t

u

p

n

I

n

w

o

d

ll

u

P

,

W

O

L

c

i

g

o

l

n

e

h

W

.

t

u

p

t

u

o

k

c

o

l

c

e

c

n

e

r

e

f

e

r

r

o

f

l

o

r

t

n

o

c

e

l

b

a

n

e

t

u

p

t

u

O

,

H

G

I

H

c

i

g

o

l

n

e

h

W

.

e

c

n

a

d

e

p

m

i

h

g

i

h

n

i

s

i

t

u

p

t

u

o

k

c

o

l

c

e

c

n

e

r

e

f

e

r

e

h

t

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

d

e

l

b

a

n

e

s

i

t

u

p

t

u

o

e

h

t

2

1

1

K

L

C

t

u

p

n

I

n

w

o

d

ll

u

P

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

t

u

p

n

i

k

c

o

l

C

5

1

,

4

1

0

L

E

S

,

1

L

E

S

t

u

p

n

I

n

w

o

d

ll

u

P

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

t

c

e

l

e

s

k

c

o

l

c

t

u

p

n

I

6

1

2

K

L

C

t

u

p

n

I

n

w

o

d

ll

u

P

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

t

u

p

n

i

k

c

o

l

C

,

8

1

,

7

1

,

0

2

,

9

1

,

2

2

,

1

2

,

4

2

,

3

2

,

6

2

,

5

2

8

2

,

7

2

1

N

I

O

X

:

2

1

N

I

O

X

t

u

p

n

I

n

w

o

d

ll

u

P

.

t

u

p

n

i

l

o

r

t

n

o

c

r

e

d

i

v

i

d

t

u

p

n

i

L

L

P

O

X

C

V

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

9

2

0

N

I

O

X

t

u

p

n

I

p

u

ll

u

P

.

t

u

p

n

i

l

o

r

t

n

o

c

r

e

d

i

v

i

d

t

u

p

n

i

L

L

P

O

X

C

V

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

,

1

3

,

0

3

2

3

,

1

A

P

N

,

2

A

P

N

0

A

P

N

t

u

p

n

I

n

w

o

d

ll

u

P

.

s

t

u

p

t

u

o

A

Q

n

/

A

Q

r

o

f

l

o

r

t

n

o

c

r

e

d

i

v

i

d

t

u

p

t

u

o

L

C

E

P

V

L

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

3

3

V

A

C

C

r

e

w

o

P

.

n

i

p

y

l

p

p

u

s

g

o

l

a

n

A

,

5

3

,

4

3

6

3

,

1

B

P

N

,

2

B

P

N

0

B

P

N

t

u

p

n

I

n

w

o

d

ll

u

P

.

s

t

u

p

t

u

o

B

Q

n

/

B

Q

r

o

f

l

o

r

t

n

o

c

r

e

d

i

v

i

d

t

u

p

t

u

o

L

C

E

P

V

L

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

7

3

P

M

t

u

p

n

I

n

w

o

d

ll

u

P

.

t

u

p

n

i

l

o

r

t

n

o

c

n

o

i

t

a

c

il

p

i

t

l

u

m

k

c

o

l

c

t

i

u

c

r

i

c

TM

k

c

o

l

C

o

t

m

e

F

.

2

3

s

t

c

e

l

e

s

,

W

O

L

n

e

h

W

.

8

2

s

t

c

e

l

e

s

,

H

G

I

H

n

e

h

W

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

,

8

3

V

L

C

E

P

_

O

C

C

r

e

w

o

P

.

s

t

u

p

t

u

o

k

c

o

l

c

L

C

E

P

V

L

r

o

f

n

i

p

y

l

p

p

u

s

r

e

w

o

p

t

u

p

t

u

O

0

4

,

9

3

A

Q

n

,

A

Q

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

C

E

P

V

L

.

r

i

a

p

t

u

p

t

u

o

k

c

o

l

c

l

a

i

t

n

e

r

e

f

f

i

D

3

4

,

2

4

B

Q

n

,

B

Q

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

C

E

P

V

L

.

r

i

a

p

t

u

p

t

u

o

k

c

o

l

c

l

a

i

t

n

e

r

e

f

f

i

D

4

4

V

S

O

M

C

_

O

C

C

r

e

w

o

P

.

s

t

u

p

t

u

o

S

O

M

C

V

L

r

o

f

n

i

p

y

l

p

p

u

s

r

e

w

o

p

t

u

p

t

u

O

5

4

K

C

O

L

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

t

u

p

t

u

o

t

c

e

t

e

d

k

c

o

L

6

4

K

L

C

V

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

t

u

p

t

u

o

k

c

o

l

c

L

L

P

O

X

C

V

7

4

K

L

C

_

F

E

R

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

t

u

p

t

u

o

k

c

o

l

c

e

c

n

e

r

e

f

e

R

:

E

T

O

N

p

u

ll

u

P

d

n

a

n

w

o

d

ll

u

P

.

s

e

u

l

a

v

l

a

c

i

p

y

t

r

o

f

,

s

c

i

t

s

i

r

e

t

c

a

r

a

h

C

n

i

P

,

2

e

l

b

a

T

e

e

S

.

s

r

o

t

s

i

s

e

r

t

u

p

n

i

l

a

n

r

e

t

n

i

o

t

r

e

f

e

r

843002CY-31

www.icst.com/products/hiperclocks.html

REV. B NOVEMBER 22, 2005

5

Integrated

Circuit

Systems, Inc.

ICS843002-31

700MH

Z

F

EMTO

C

LOCKS

TM VCXO B

ASED

F

REQUENCY

T

RANSLATOR

AND

J

ITTER

A

TTENUATOR

PRELIMINARY

T

ABLE

2. P

IN

C

HARACTERISTICS

r

e

b

m

u

N

e

m

a

N

e

p

y

T

n

o

i

t

p

i

r

c

s

e

D

,

0

5

,

9

4

,

2

5

,

1

5

,

4

5

,

3

5

,

6

5

,

5

5

,

8

5

,

7

5

0

6

.

9

5

1

B

F

O

X

:

2

1

B

F

O

X

t

u

p

n

I

n

w

o

d

ll

u

P

.

t

u

p

n

i

l

o

r

t

n

o

c

r

e

d

i

v

i

d

k

c

a

b

d

e

e

f

O

X

C

V

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

1

6

0

B

F

O

X

t

u

p

n

I

p

u

ll

u

P

.

t

u

p

n

i

l

o

r

t

n

o

c

r

e

d

i

v

i

d

k

c

a

b

d

e

e

f

O

X

C

V

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

3

6

,

2

6

,

T

U

O

_

L

A

T

X

N

I

_

L

A

T

X

t

u

p

n

I

.

t

u

p

n

i

e

h

t

s

i

N

I

_

L

A

T

X

.

e

c

a

f

r

e

t

n

i

r

o

t

a

ll

i

c

s

o

l

a

t

s

y

r

c

O

X

C

V

.

t

u

p

t

u

o

e

h

t

s

i

T

U

O

_

L

A

T

X

4

6

V

O

X

_

A

C

C

r

e

w

o

P

.

O

X

C

V

r

o

f

n

i

p

y

l

p

p

u

s

r

e

w

o

p

g

o

l

a

n

A

:

E

T

O

N

p

u

ll

u

P

d

n

a

n

w

o

d

ll

u

P

.

s

e

u

l

a

v

l

a

c

i

p

y

t

r

o

f

,

s

c

i

t

s

i

r

e

t

c

a

r

a

h

C

n

i

P

,

2

e

l

b

a

T

e

e

S

.

s

r

o

t

s

i

s

e

r

t

u

p

n

i

l

a

n

r

e

t

n

i

o

t

r

e

f

e

r

T

ABLE

1. P

IN

D

ESCRIPTIONS

(

CONTINUED

FROM

PREVIOUS

PAGE

)

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

C

N

I

e

c

n

a

t

i

c

a

p

a

C

t

u

p

n

I

4

F

p

C

D

P

e

c

n

a

t

i

c

a

p

a

C

n

o

i

t

a

p

i

s

s

i

D

r

e

w

o

P

)

t

u

p

t

u

o

S

O

M

C

V

L

r

e

p

(

V

,

C

C

V

,

A

C

C

V

,

O

X

_

A

C

C

V

,

S

O

M

C

_

O

C

C

V

L

C

E

P

_

O

C

C

V

5

6

4

.

3

=

D

B

T

F

p

R

P

U

L

L

U

P

r

o

t

s

i

s

e

R

p

u

ll

u

P

t

u

p

n

I

1

5

k

R

N

W

O

D

L

L

U

P

r

o

t

s

i

s

e

R

n

w

o

d

ll

u

P

t

u

p

n

I

1

5

k

R

T

U

O

e

c

n

a

d

e

p

m

I

t

u

p

t

u

O

7

843002CY-31

www.icst.com/products/hiperclocks.html

REV. B NOVEMBER 22, 2005

6

Integrated

Circuit

Systems, Inc.

ICS843002-31

700MH

Z

F

EMTO

C

LOCKS

TM VCXO B

ASED

F

REQUENCY

T

RANSLATOR

AND

J

ITTER

A

TTENUATOR

PRELIMINARY

S

ECTION

1. F

REQUENCY

T

RANSLATION

The ICS843002-31 is a two stage device, a VCXO PLL stage

followed by a low phase noise FemtoClock multiplier stage.

The VCXO uses a pullable crystal to lock to the reference

clock and can provide an output frequency up to 25MHz on

the single-ended VCLK output. For higher frequencies, the low

phase noise FemtoClock can multiply the VCXO PLL out-

put clock up to 700MHz on 2 differential LVPECL output

pairs (QA/nQA, QB/nQB).

The VCXO PLL stage has a 13-bit input divider and a 13-bit

feedback divider to generate large integer ratios needed for

some frequency translation applications. When configuring

the device is to use pullable crystals in the 17.5MHz � 25MHz

range on the VCXO PLL stage, and ensure that the

FemtoClock PLL is kept within its range of 560MHz to 700MHz.

Below are 3 examples:

1. 8kHz to 622.08MHz and 155.52MHz

This frequency translation requires use of both the VCXO

PLL and the FemtoClock circuit. The VCXO PLL can be used

to multiply up to 19.44MHz for use as a reference clock for

the FemtoClock which will do the multiplication from

19.44MHz to 622.08MHz.

Using a 19.44MHz pullable crystal on XTAL_IN/

XTAL_OUT, set the VCXO PLL feedback divider pins,

XOFB[12:0], to 2430. This multiplies the 8kHz refer-

ence clock to 19.44MHz.

Set the FemtoClock multiplication control pin, MP, to

0 which sets the multiplication factor to 32. This sets

the FemtoClock VCO to 622.08MHz.

Set the QA/nQA output divider control pins,

NPA[2:0] = 000 for divide by 1. This sets the QA/nQA

LVPECL output pair for 622.08MHz.

Set the QB/nQB output divider control pins,

NPB[2:0] = 010 for divide by 4. This sets the QB/nQB

LVPECL output pair for 155.52MHz.

2. T1 to T3. (1.544MHz to two 44.736MHz outputs)

Since 44.736MHz is slightly higher than the maximum VCXO

output frequency, the FemtoClock circuit will have to be used.

Using a pullable 22.368MHz on XTAL_IN/XTAL_OUT,

set the VCXO PLL feedback divider pins, XOFB[12:0]

to 2796 and the input divider pins, XOIN[12:0] to 193.

This multiplies the 1.544MHz reference to 22.368MHz

(1.544MHz * 2796/193 = 22.368MHz).

Set the FemtoClock multiplication control pin, MP, to

28 which sets the VCO at 626.304MHz.

Set the QA/nQA output divider control pins,

NPA[2:0] = 101 for divide by 14. This sets the QA/nQA

LVPECL output pair for 44.736MHz.

Set the QB/nQB output divider control pins,

NPB[2:0] = 000 for divide by 1. This sets the QB/nQB

LVPECL output pair for 44.736MHz

3. T1 to E1. (1.544MHz to two 2.048MHz outputs)

The 2.048MHz output frequency requirement is low enough

that the FemtoClock circuit is not required. Only the VCXO

stage is used for this frequency translation.

Using a pullable 24.576MHz on XTAL_IN/XTAL_OUT,

set the VCXO PLL feedback divider pins, XOFB[12:0]

to 3072 and the input divider pins, XOIN[12:0] to 193.

This multiplies the 1.544MHz reference to 2.048MHz

(1.544MHz * 3072/193 = 24.576MHz).

Set the VCXO PLL Output Divider control pins,

NV[1:0] = 01 for /12. This divides the 24.576MHz VCXO

PLL frequency down to 2.048MHz.

The Frequency Configuration Table Examples (see the follow-

ing pages) are intended to show the most common frequency

translation requirements. It is sorted in order of descending

input frequency. It is not intended to be an exhaustive configur-

ation table because that would be impractical with almost 3

billion possible configurations. As far as configuration is

concerned, frequencies <= 25MHz can be generated with the

VCXO PLL while frequencies > 25MHz require the use of the

downstream FemtoClock which can multiply the VCXO PLL

output up to 700MHz. Complex integer ratios are handled with

the VCXO PLL stage and the FemtoClock circuit can be

configured to multiply the VCXO PLL output by 32 or 28. The

following example will illustrate the configuration process.

Assume you have a 1.544MHz T1 clock which needs to be

multiplied up to 622.08MHz (OC12). Obviously, the

FemtoClock multiplier will be needed to achieve 622.08MHz.

Since the FemtoClock has a selectable multiplication factor

of 28 or 32, this means there are 2 viable VCXO PLL crystal

choices which fall within its 17.5MHz � 15MHz range:

22.217143MHz (/28 feedback divider) or 19.44MHz (/32

feedback divider). Use of the /28 feedback divider for the

FemtoClock multiplier will give slightly better phase noise,

but in this case 22.217143/1.544 cannot be exactly

achieved with the 13-bit input and feedback VCXO PLL

dividers. Using the x32 setting of the FemtoClock allows a

ratio of 19.44/1.544 = 2430/193 which is easily achievable.

So the FemtoClock would be set for x32 and a 19.44MHz

crystal would be used. The VCXO PLL input divider would

be set for 193 and the VCXO PLL feedback divider would

be set for 2430. To double check the solution, perform the

following calculation: 1.544 * 2430 * 32/193 = 622.08MHz.

The 2

nd

FemtoClock multiplier output, QB/nQB, can be set to

equal the QA/nQA output frequency or a fraction of its frequency.

The following fractional values are available: /1, /2, /4, /8.

S

ECTION

2. F

REQUENCY

C

ONFIGURATION

843002CY-31

www.icst.com/products/hiperclocks.html

REV. B NOVEMBER 22, 2005

7

Integrated

Circuit

Systems, Inc.

ICS843002-31

700MH

Z

F

EMTO

C

LOCKS

TM VCXO B

ASED

F

REQUENCY

T

RANSLATOR

AND

J

ITTER

A

TTENUATOR

PRELIMINARY

T

ABLE

3A.

F

REQUENCY

C

ONFIGURA

TION

E

XAMPLES

,

CONTINUED

ON

NEXT

PA

G

E

t

u

p

n

I

y

c

n

e

u

q

e

r

F

)

z

H

M

(

t

u

p

t

u

O

y

c

n

e

u

q

e

r

F

)

z

H

M

(

r

o

O

X

C

V

t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F

O

X

C

V

d

e

r

i

u

q

e

R

y

c

n

e

u

q

e

r

F

l

a

t

s

y

r

C

)

z

H

M

(

O

X

C

V

t

u

p

n

I

r

e

d

i

v

i

D

O

X

C

V

k

c

a

b

d

e

e

F

r

e

d

i

v

i

D

O

X

C

V

t

u

p

t

u

O

r

e

d

i

v

i

D

k

c

o

l

C

o

t

m

e

F

n

o

i

t

a

c

i

l

p

i

t

l

u

M

TM

r

o

t

c

a

F

k

c

o

l

C

o

t

m

e

F

y

c

n

e

u

q

e

r

F

t

u

p

t

u

O

)

z

H

M

(

k

c

o

l

C

o

t

m

e

F

t

u

p

t

u

O

r

e

d

i

v

i

D

n

o

i

t

a

c

i

l

p

p

A

8

0

.

2

2

68

0

.

2

2

6t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

12

31

A

/

N2

38

0

.

2

2

61

)

2

1

C

O

(

8

0

.

2

2

6

>

-

8

0

.

2

2

6

8

0

.

2

2

64

0

.

1

1

3t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

12

31

A

/

N2

38

0

.

2

2

62

)

T

E

N

O

S

(

4

0

.

1

1

3

>

-

8

0

.

2

2

6

8

0

.

2

2

62

5

.

5

5

1t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

12

31

A

/

N2

38

0

.

2

2

64

)

3

C

O

o

t

2

1

C

O

(

2

5

.

5

5

1

>

-

8

0

.

2

2

6

8

0

.

2

2

66

7

.

7

7t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

12

31

A

/

N2

38

0

.

2

2

68

)

T

E

N

O

S

(

6

7

.

7

7

>

-

8

0

.

2

2

6

8

0

.

2

2

64

8

.

1

5t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

12

31

A

/

N2

38

0

.

2

2

62

1)

1

C

O

o

t

2

1

C

O

(

4

8

.

1

5

>

-

8

0

.

2

2

6

8

0

.

2

2

68

8

.

8

3t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

12

31

A

/

N2

38

0

.

2

2

66

1)

T

E

N

O

S

(

8

8

.

8

3

>

-

8

0

.

2

2

6

8

0

.

2

2

64

4

.

9

1t

u

p

t

u

O

O

X

C

V4

4

.

9

12

31

1

A

/

NA

/

NA

/

N)

T

E

N

O

S

(

4

4

.

9

1

>

-

8

0

.

2

2

6

8

0

.

2

2

66

3

7

.

4

4t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F8

6

3

.

2

20

8

4

63

3

2A

/

N8

24

0

3

.

6

2

64

1)

3

T

o

t

2

1

C

O

(

6

3

7

.

4

4

>

-

8

0

.

2

2

6

8

0

.

2

2

68

6

3

.

4

3t

u

p

t

u

O

O

X

C

V8

6

3

.

4

30

4

2

39

7

11

A

/

NA

/

NA

/

N)

3

E

o

t

2

1

C

O

(

8

6

3

.

4

3

>

-

8

0

.

2

2

6

8

0

.

2

2

64

6

0

.

2

3t

u

p

t

u

O

O

X

C

V4

6

0

.

2

30

4

2

37

6

11

A

/

NA

/

NA

/

N)

3

J

o

t

2

1

C

O

(

4

6

0

.

2

3

>

-

8

0

.

2

2

6

8

0

.

2

2

68

4

0

.

2t

u

p

t

u

O

O

X

C

V6

7

5

.

4

25

0

46

12

1A

/

NA

/

NA

/

N)

1

E

o

t

2

1

C

O

(

8

4

0

.

2

>

-

8

0

.

2

2

6

8

0

.

2

2

64

4

5

.

1t

u

p

t

u

O

O

X

C

V4

0

7

.

4

20

6

8

43

9

16

1A

/

NA

/

NA

/

N)

1

J

/

1

T

o

t

2

1

C

O

(

4

4

5

.

1

>

-

8

0

.

2

2

6

4

0

.

1

1

34

0

.

1

1

3t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

16

11

A

/

N2

38

0

.

2

2

62

)

T

E

N

O

S

(

4

0

.

1

1

3

>

-

4

0

.

1

1

3

4

0

.

1

1

32

5

.

5

5

1t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

16

11

A

/

N2

38

0

.

2

2

64

)

T

E

N

O

S

(

2

5

.

5

5

1

>

-

4

0

.

1

1

3

4

0

.

1

1

36

7

.

7

7t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

16

11

A

/

N2

38

0

.

2

2

68

)

T

E

N

O

S

(

6

7

.

7

7

>

-

4

0

.

1

1

3

4

0

.

1

1

34

8

.

1

5t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

16

11

A

/

N2

38

0

.

2

2

62

1)

T

E

N

O

S

(

4

8

.

1

5

>

-

4

0

.

1

1

3

4

0

.

1

1

38

8

.

8

3t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

16

11

A

/

N2

38

0

.

2

2

66

1)

T

E

N

O

S

(

8

8

.

8

3

>

-

4

0

.

1

1

3

4

0

.

1

1

34

4

.

9

1t

u

p

t

u

O

O

X

C

V4

4

.

9

16

11

1

A

/

NA

/

NA

/

N)

T

E

N

O

S

(

4

4

.

9

1

>

-

4

0

.

1

1

3

4

0

.

1

1

38

0

.

2

2

6t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

16

11

1

2

38

0

.

2

2

61

)

T

E

N

O

S

(

8

0

.

2

2

6

>

-

4

0

.

1

1

3

4

0

.

1

1

38

0

.

2

2

6t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

16

11

1

2

38

0

.

2

2

61

)

T

E

N

O

S

(

8

0

.

2

2

6

>

-

4

0

.

1

1

3

4

0

.

1

1

36

3

7

.

4

4t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F8

6

3

.

2

20

4

2

33

3

21

8

24

0

3

.

6

2

64

1)

3

T

o

t

T

E

N

O

S

(

6

3

7

.

4

4

>

-

4

0

.

1

1

3

4

0

.

1

1

38

6

3

.

4

3t

u

p

t

u

O

O

X

C

V8

6

3

.

4

30

2

6

19

7

11

A

/

NA

/

NA

/

N)

3

E

o

t

T

E

N

O

S

(

8

6

3

.

4

3

>

-

4

0

.

1

1

3

4

0

.

1

1

34

6

0

.

2

3t

u

p

t

u

O

O

X

C

V4

6

0

.

2

30

2

6

17

6

11

A

/

NA

/

NA

/

N)

3

J

o

t

T

E

N

O

S

(

4

6

0

.

2

3

>

-

4

0

.

1

1

3

4

0

.

1

1

38

4

0

.

2t

u

p

t

u

O

O

X

C

V6

7

5

.

4

25

0

42

32

1A

/

NA

/

NA

/

N)

1

E

o

t

T

E

N

O

S

(

8

4

0

.

2

>

-

4

0

.

1

1

3

4

0

.

1

1

34

4

5

.

1t

u

p

t

u

O

O

X

C

V4

0

7

.

4

20

3

4

23

9

16

1A

/

NA

/

NA

/

N)

1

J

/

1

T

o

t

T

E

N

O

S

(

4

4

5

.

1

>

-

4

0

.

1

1

3

2

5

.

5

5

12

5

.

5

5

1t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

18

1

A

/

N2

38

0

.

2

2

64

)

3

C

O

(

2

5

.

5

5

1

>

-

2

5

.

5

5

1

2

5

.

5

5

16

7

.

7

7t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

18

1

A

/

N2

38

0

.

2

2

68

)

T

E

N

O

S

(

6

7

.

7

7

>

-

2

5

.

5

5

1

2

5

.

5

5

14

8

.

1

5t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

18

1

A

/

N2

38

0

.

2

2

62

1)

1

C

O

o

t

3

C

O

(

4

8

.

1

5

>

-

2

5

.

5

5

1

2

5

.

5

5

18

8

.

8

3t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

18

1

A

/

N2

38

0

.

2

2

66

1)

T

E

N

O

S

(

8

8

.

8

3

>

-

2

5

.

5

5

1

2

5

.

5

5

14

4

.

9

1t

u

p

t

u

O

O

X

C

V4

4

.

9

18

1

1

A

/

NA

/

NA

/

N)

T

E

N

O

S

(

4

4

.

9

1

>

-

2

5

.

5

5

1

2

5

.

5

5

14

0

.

1

1

3t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

18

1

A

/

N2

38

0

.

2

2

62

)

T

E

N

O

S

(

4

0

.

1

1

3

>

-

2

5

.

5

5

1

843002CY-31

www.icst.com/products/hiperclocks.html

REV. B NOVEMBER 22, 2005

8

Integrated

Circuit

Systems, Inc.

ICS843002-31

700MH

Z

F

EMTO

C

LOCKS

TM VCXO B

ASED

F

REQUENCY

T

RANSLATOR

AND

J

ITTER

A

TTENUATOR

PRELIMINARY

T

ABLE

3A.

F

REQUENCY

C

ONFIGURA

TION

E

XAMPLES

,

CONTINUED

ON

NEXT

PA

G

E

t

u

p

n

I

y

c

n

e

u

q

e

r

F

)

z

H

M

(

t

u

p

t

u

O

y

c

n

e

u

q

e

r

F

)

z

H

M

(

r

o

O

X

C

V

t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F

O

X

C

V

d

e

r

i

u

q

e

R

y

c

n

e

u

q

e

r

F

l

a

t

s

y

r

C

)

z

H

M

(

O

X

C

V

t

u

p

n

I

r

e

d

i

v

i

D

O

X

C

V

k

c

a

b

d

e

e

F

r

e

d

i

v

i

D

O

X

C

V

t

u

p

t

u

O

r

e

d

i

v

i

D

k

c

o

l

C

o

t

m

e

F

n

o

i

t

a

c

i

l

p

i

t

l

u

M

TM

r

o

t

c

a

F

k

c

o

l

C

o

t

m

e

F

t

u

p

t

u

O

y

c

n

e

u

q

e

r

F

)

z

H

M

(

k

c

o

l

C

o

t

m

e

F

t

u

p

t

u

O

r

e

d

i

v

i

D

n

o

i

t

a

c

i

l

p

p

A

2

5

.

5

5

18

0

.

2

2

6t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

18

1

A

/

N2

38

0

.

2

2

61

)

2

1

C

O

o

t

3

C

O

(

8

0

.

2

2

6

>

-

2

5

.

5

5

1

2

5

.

5

5

16

3

7

.

4

4t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F8

6

3

.

2

20

2

6

13

3

2A

/

N8

24

0

3

.

6

2

64

1)

3

T

o

t

3

C

O

(

6

3

7

.

4

4

>

-

2

5

.

5

5

1

2

5

.

5

5

18

6

3

.

4

3t

u

p

t

u

O

O

X

C

V8

6

3

.

4

30

1

89

7

11

A

/

NA

/

NA

/

N)

3

E

o

t

3

C

O

(

8

6

3

.

4

3

>

-

2

5

.

5

5

1

2

5

.

5

5

14

6

0

.

2

3t

u

p

t

u

O

O

X

C

V4

6

0

.

2

30

1

87

6

11

A

/

NA

/

NA

/

N)

3

J

o

t

3

C

O

(

4

6

0

.

2

3

>

-

2

5

.

5

5

1

2

5

.

5

5

18

4

0

.

2t

u

p

t

u

O

O

X

C

V6

7

5

.

4

25

0

44

62

1A

/

NA

/

NA

/

N)

1

E

o

t

3

C

O

(

8

4

0

.

2

>

-

2

5

.

5

5

1

2

5

.

5

5

14

4

5

.

1t

u

p

t

u

O

O

X

C

V4

0

7

.

4

25

1

2

13

9

16

1A

/

NA

/

NA

/

N)

1

J

/

1

T

o

t

3

C

O

(

4

4

5

.

1

>

-

2

5

.

5

5

1

6

7

.

7

76

7

.

7

7t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

14

1

A

/

N2

38

0

.

2

2

68

)

T

E

N

O

S

(

6

7

.

7

7

>

-

6

7

.

7

7

6

7

.

7

74

8

.

1

5t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

14

1

A

/

N2

38

0

.

2

2

62

1)

T

E

N

O

S

(

4

8

.

1

5

>

-

6

7

.

7

7

6

7

.

7

78

8

.

8

3t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

14

1

A

/

N2

38

0

.

2

2

66

1)

T

E

N

O

S

(

8

8

.

8

3

>

-

6

7

.

7

7

6

7

.

7

74

4

.

9

1t

u

p

t

u

O

O

X

C

V4

4

.

9

14

1

1

A

/

NA

/

NA

/

N)

T

E

N

O

S

(

4

4

.

9

1

>

-

6

7

.

7

7

6

7

.

7

72

5

.

5

5

1t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

14

1

A

/

N2

38

0

.

2

2

64

)

T

E

N

O

S

(

2

5

.

5

5

1

>

-

6

7

.

7

7

6

7

.

7

74

0

.

1

1

3t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

14

1

A

/

N2

38

0

.

2

2

62

)

T

E

N

O

S

(

4

0

.

1

1

3

>

-

6

7

.

7

7

6

7

.

7

78

0

.

2

2

6t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

14

1

A

/

N2

38

0

.

2

2

61

)

T

E

N

O

S

(

8

0

.

2

2

6

>

-

6

7

.

7

7

6

7

.

7

76

3

7

.

4

4t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F8

6

3

.

2

20

1

83

3

2A

/

N8

24

0

3

.

6

2

64

1)

3

T

o

t

T

E

N

O

S

(

6

3

7

.

4

4

>

-

6

7

.

7

7

6

7

.

7

78

6

3

.

4

3t

u

p

t

u

O

O

X

C

V8

6

3

.

4

35

0

49

7

11

A

/

NA

/

NA

/

N)

3

E

o

t

T

E

N

O

S

(

8

6

3

.

4

3

>

-

6

7

.

7

7

6

7

.

7

74

6

0

.

2

3t

u

p

t

u

O

O

X

C

V4

6

0

.

2

35

0

47

6

11

A

/

NA

/

NA

/

N)

3

J

o

t

T

E

N

O

S

(

4

6

0

.

2

3

>

-

6

7

.

7

7

6

7

.

7

78

4

0

.

2t

u

p

t

u

O

O

X

C

V6

7

5

.

4

25

0

48

2

12

1A

/

NA

/

NA

/

N)

1

E

o

t

T

E

N

O

S

(

8

4

0

.

2

>

-

6

7

.

7

7

6

7

.

7

74

4

5

.

1t

u

p

t

u

O

O

X

C

V4

0

7

.

4

25

1

2

16

8

36

1A

/

NA

/

NA

/

N)

1

E

/

1

T

o

t

T

E

N

O

S

(

4

4

5

.

1

>

-

6

7

.

7

7

4

8

.

1

54

8

.

1

5t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

18

3

A

/

N2

38

0

.

2

2

62

1)

T

E

N

O

S

(

4

8

.

1

5

>

-

4

8

.

1

5

4

8

.

1

58

8

.

8

3t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

18

3

A

/

N2

38

0

.

2

2

66

1)

T

E

N

O

S

(

8

8

.

8

3

>

-

4

8

.

1

5

4

8

.

1

54

4

.

9

1t

u

p

t

u

O

O

X

C

V4

4

.

9

18

3

1

A

/

NA

/

NA

/

N)

T

E

N

O

S

(

4

4

.

9

1

>

-

4

8

.

1

5

4

8

.

1

56

7

.

7

7t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

18

3

A

/

N2

38

0

.

2

2

68

)

T

E

N

O

S

(

6

7

.

7

7

>

-

4

8

.

1

5

4

8

.

1

52

5

.

5

5

1t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

18

3

A

/

N2

38

0

.

2

2

64

)

3

C

O

o

t

1

C

O

(

2

5

.

5

5

1

>

-

4

8

.

1

5

4

8

.

1

54

0

.

1

1

3t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

18

3

A

/

N2

38

0

.

2

2

62

)

T

E

N

O

S

(

4

0

.

1

1

3

>

-

4

8

.

1

5

4

8

.

1

58

0

.

2

2

6t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F4

4

.

9

18

3

A

/

N2

38

0

.

2

2

61

)

2

1

C

O

o

t

1

C

O

(

8

0

.

2

2

6

>

-

4

8

.

1

5

4

8

.

1

56

3

7

.

4

4t

u

p

t

u

O

k

c

o

l

C

o

t

m

e

F8

6

3

.

2

20

4

53

3

2A

/

N8

24

0

3

.

6

2

64

1)

3

T

o

t

1

C

O

(

6

3

7

.

4

4

>

-

4

8

.

1

5

4

8

.

1

58

6

3

.

4

3t

u

p

t

u

O

O

X

C

V8

6

3

.

4

30

7

29

7

11

A

/

NA

/

NA

/

N)

3

E

o

t

1

C

O

(

8

6

3

.

4

3

>

-

4

8

.

1

5

4

8

.

1

54

6

0

.

2

3t

u

p

t

u

O

O

X

C

V4

6

0

.

2

30

7

27

6

11

A

/

NA

/

NA

/

N)

3

J