Document Outline

- General Description

- Features

- Pin Assignment

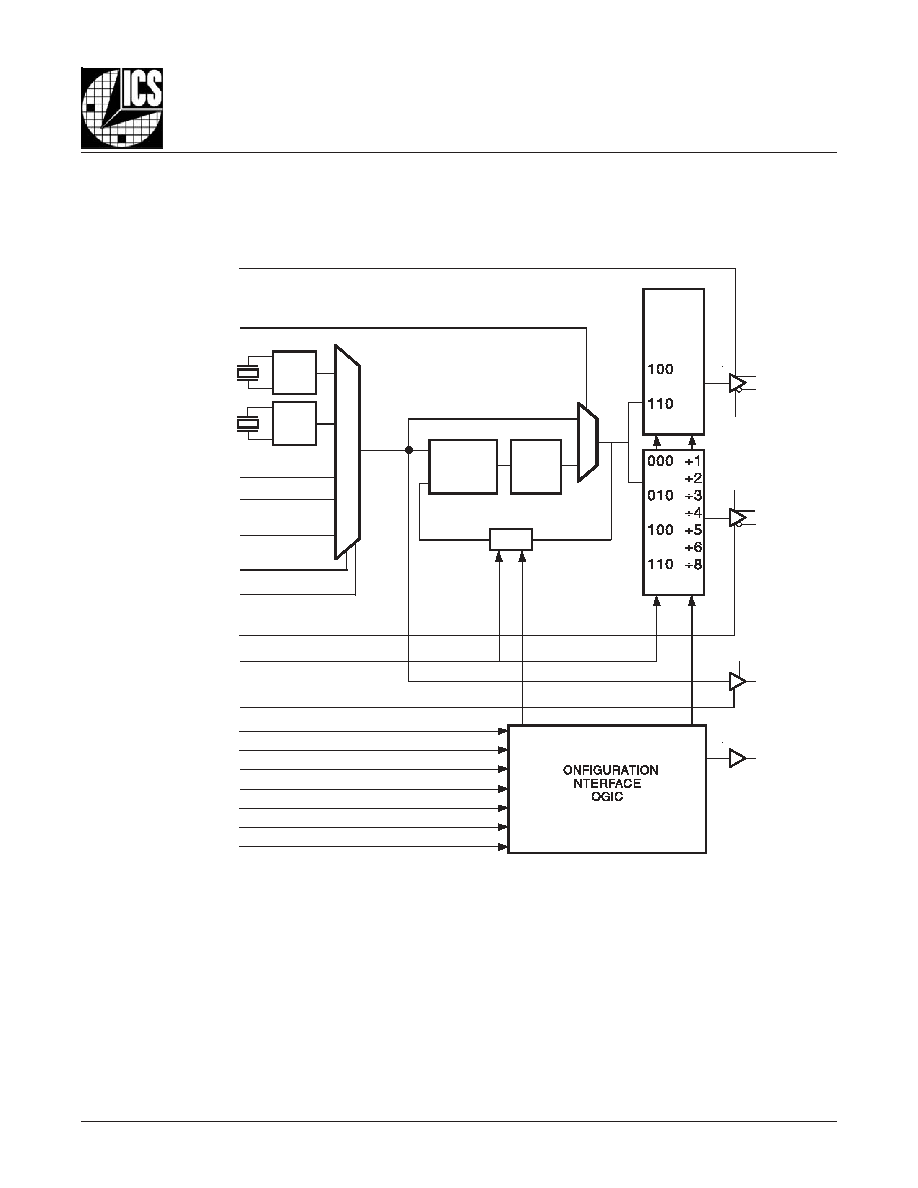

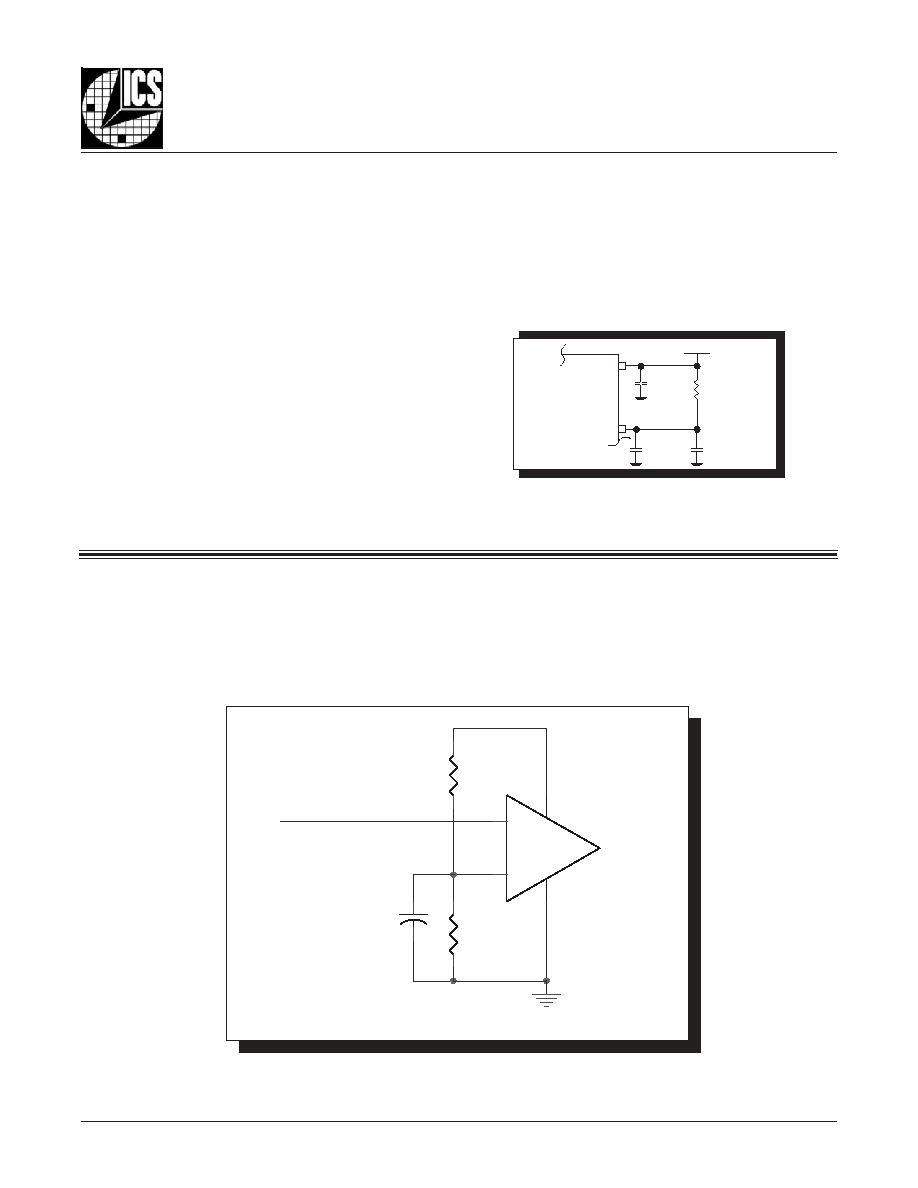

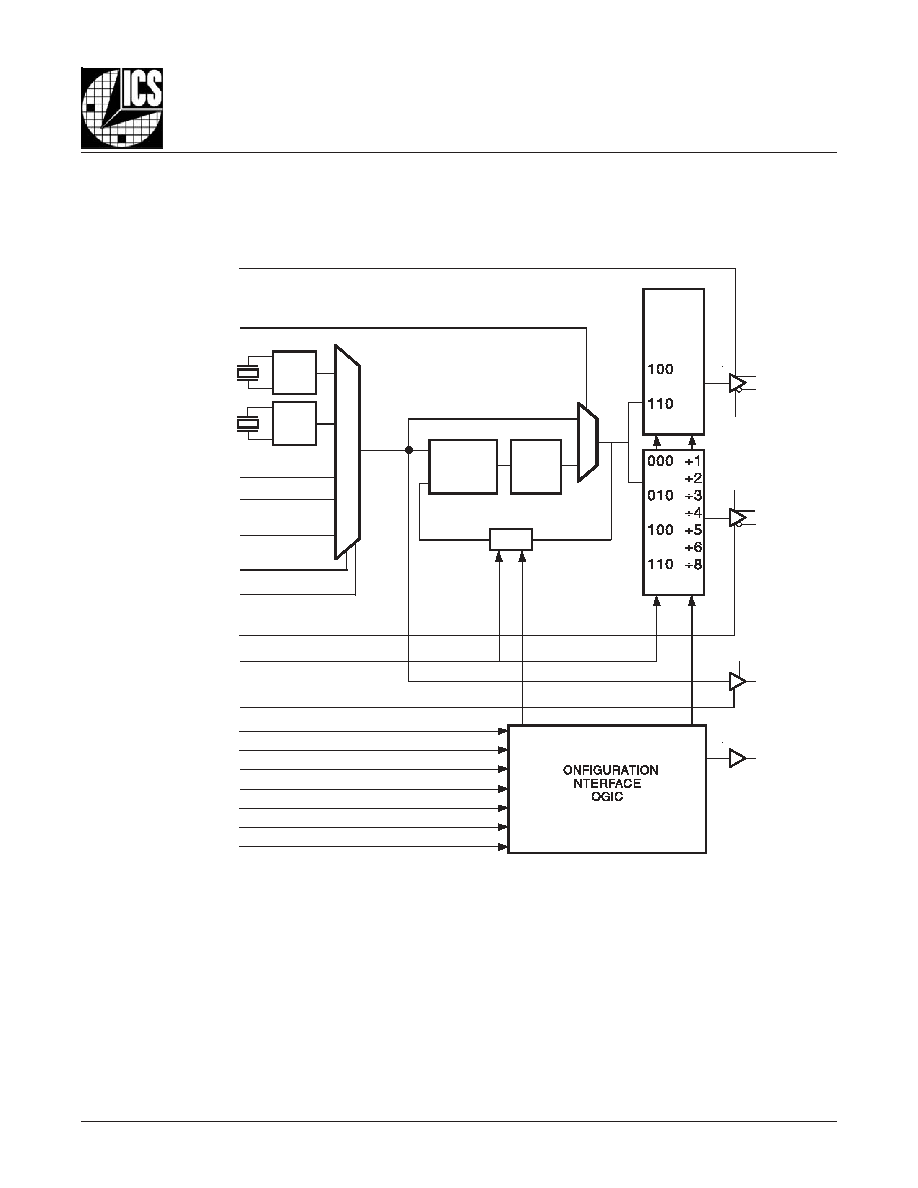

- Block Diagram

- Functional Description

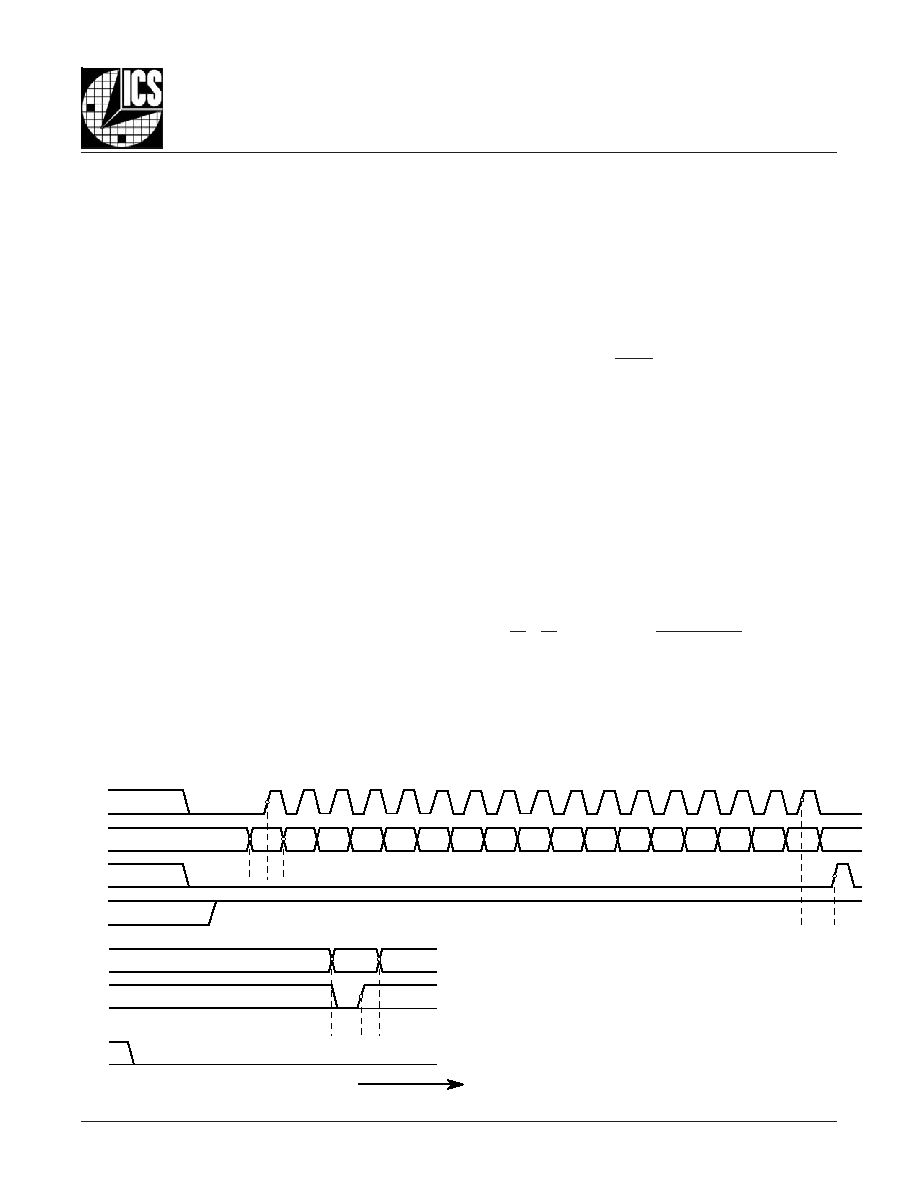

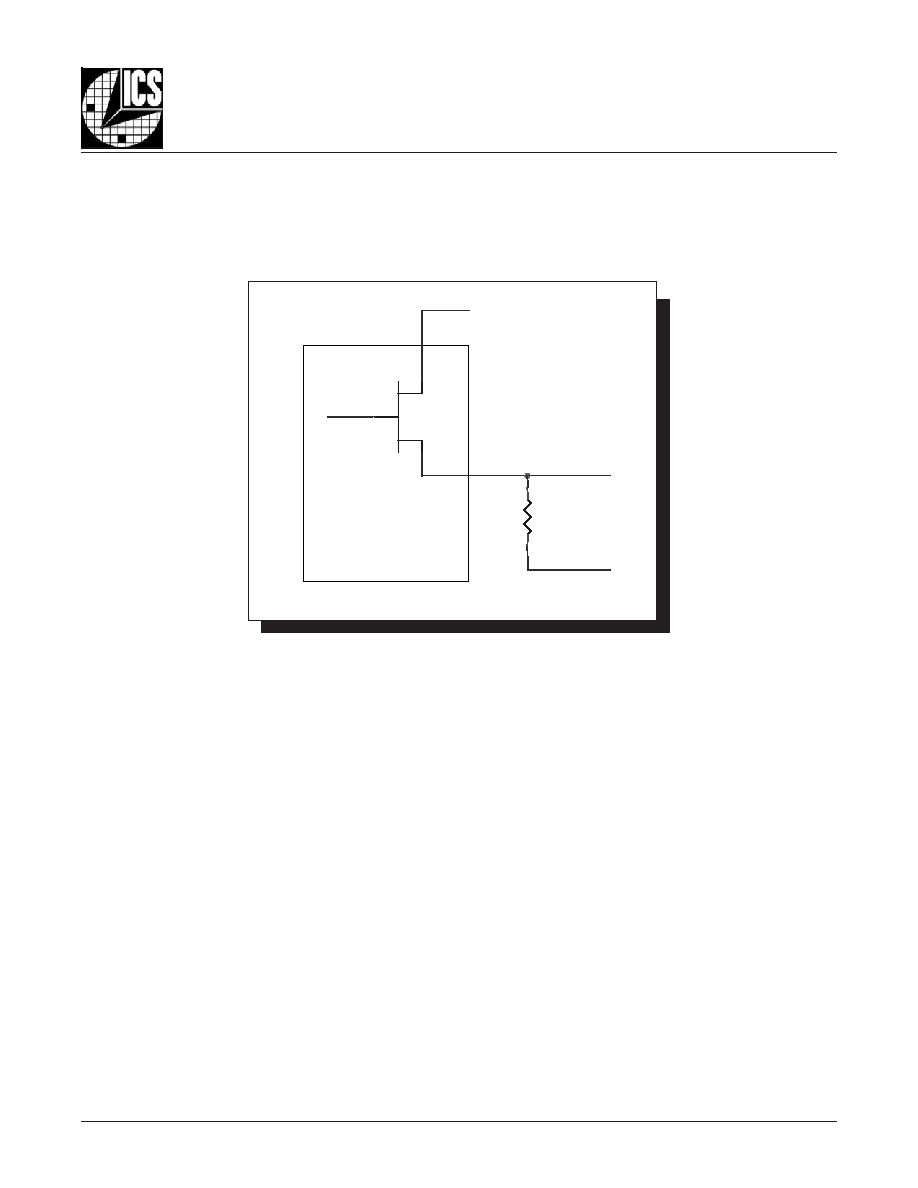

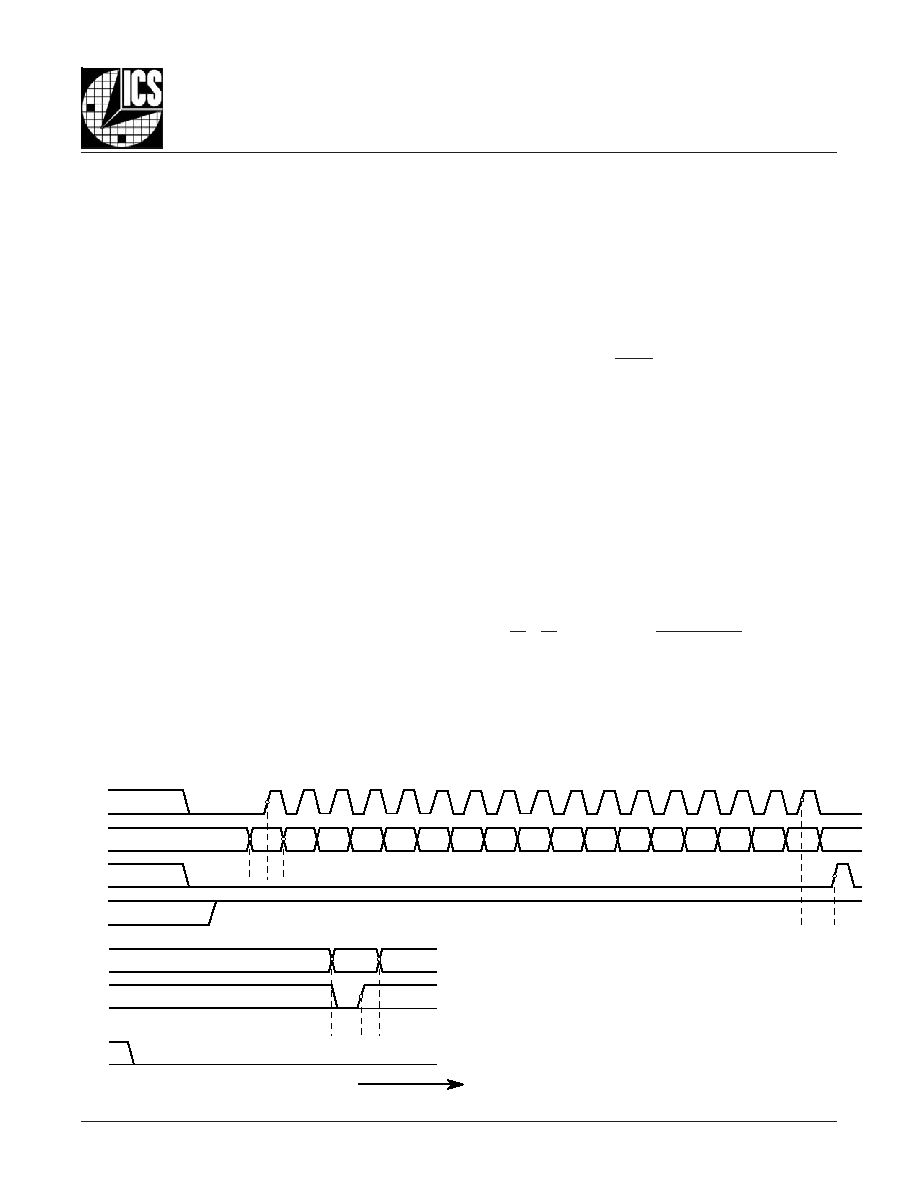

- Parallel & Serial Load Operations Diagram

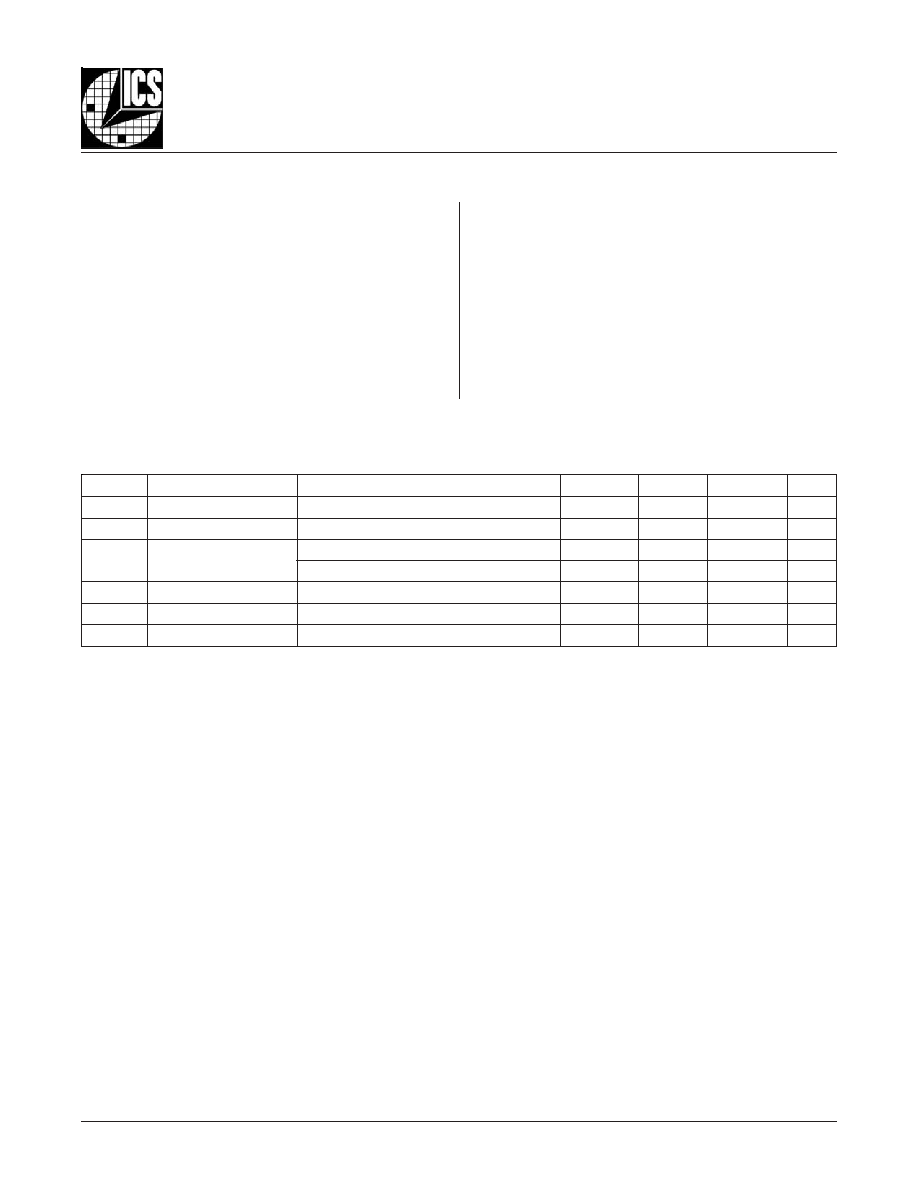

- Pin Descriptions

- Pin Descriptions continued

- Pin Characteristics

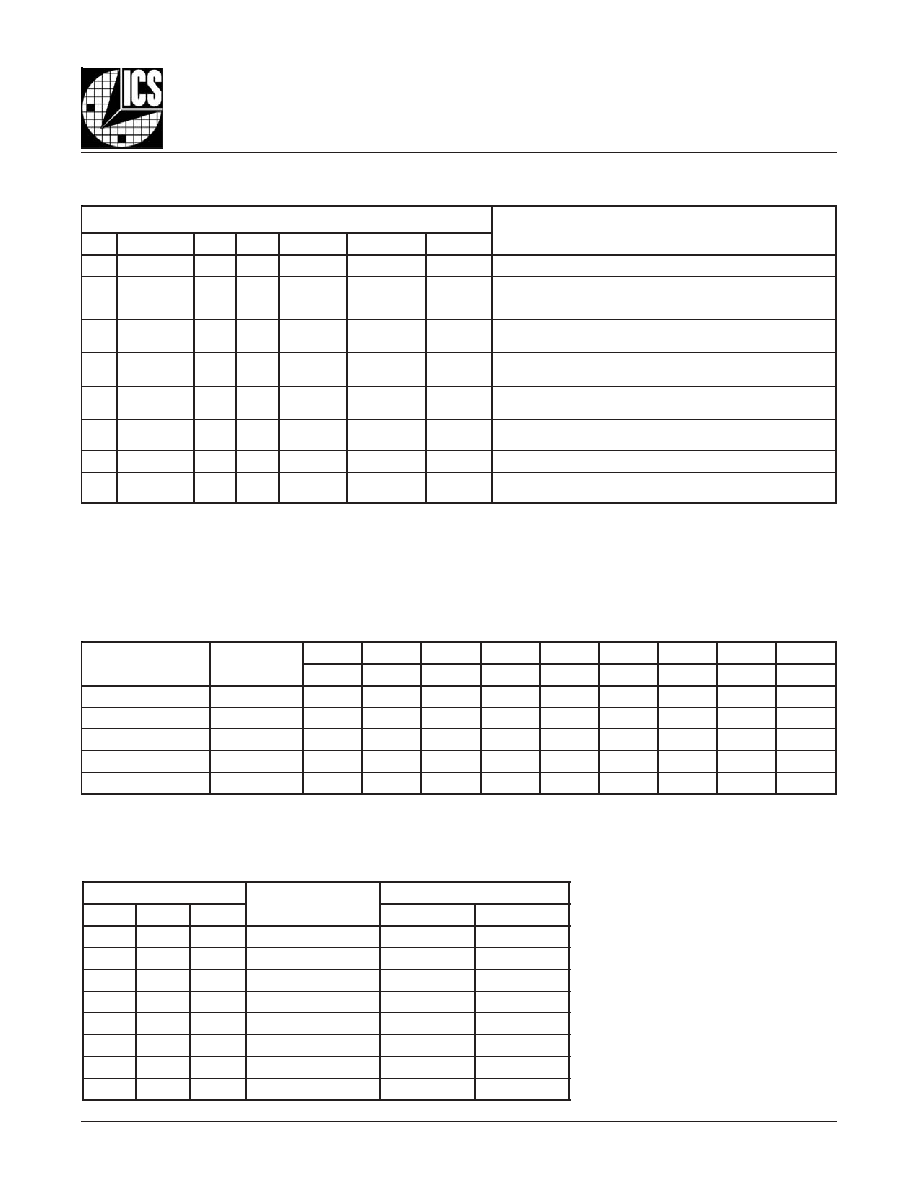

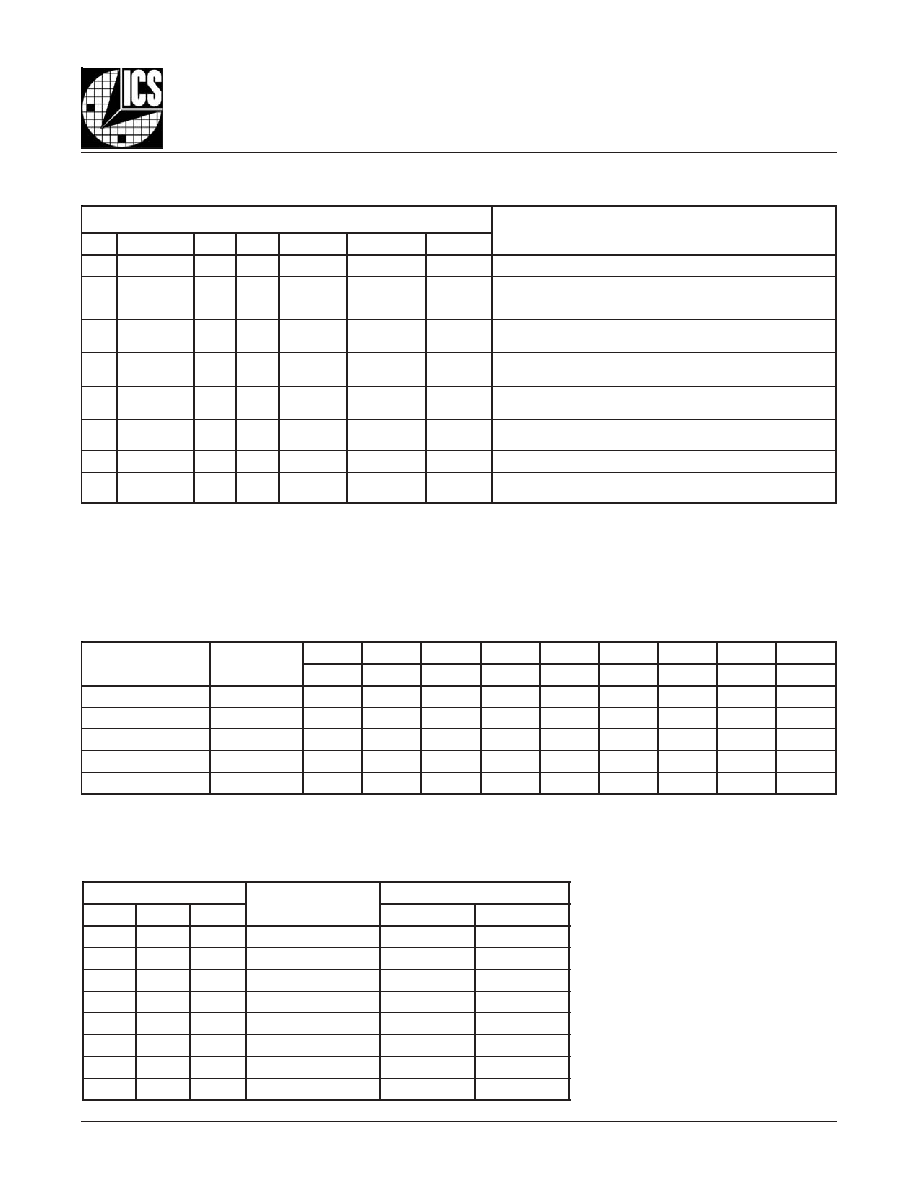

- Parallel & Serial Mode Function Table

- Programmable VCO Frequency Function Table

- Programmable Output Divider Function Table

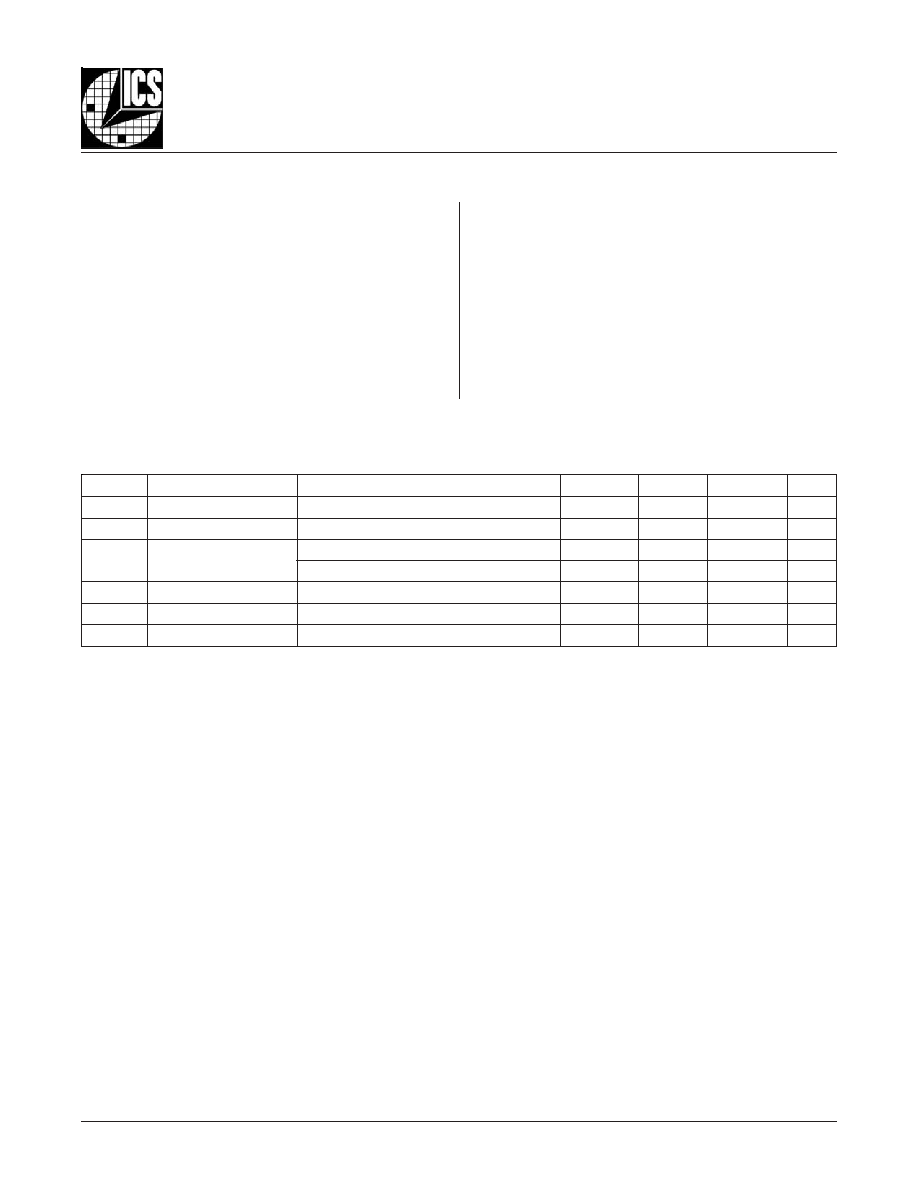

- Absolute Maximum Ratings

- Power Supply DC Characteristics

- LVCMOS DC Characteristics

- Differential DC Characteristics

- LVPECL DC Characteristics

- Input Frequency Characteristics

- Crystal Characteristics

- 3.3V AC Characteristics

- 3.3V/2.5V AC Characteristics

- 3.3V/3.3V/2.5V or 3.3V/2.5V/3.3V AC Characteristics

- Typical Phase Noise Plot

- Parameter Measurement Information

- Application Information

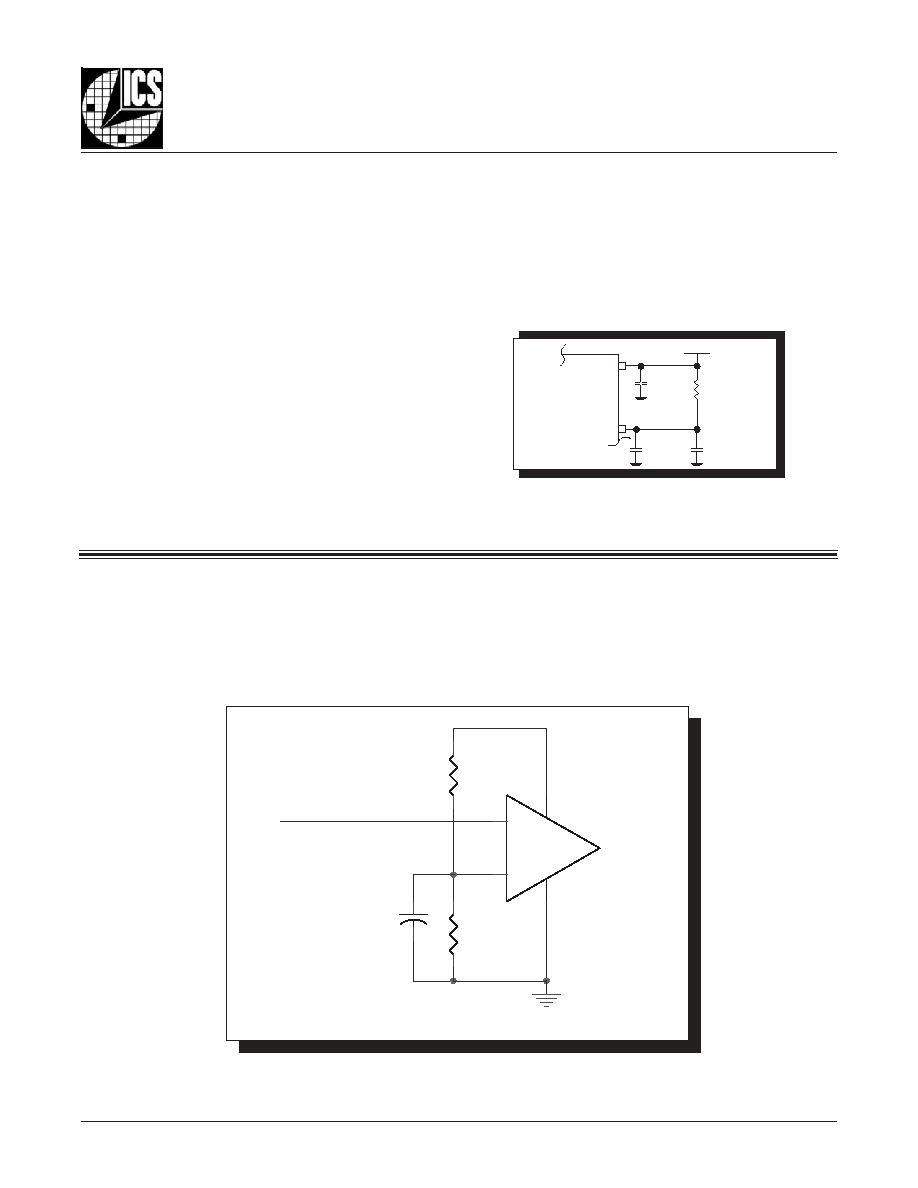

- Power Supply Filtering Techniques

- Wiring the Differential Input to Accept Single Ended LVCMOS/LVTTL Levels

- Differential Clock Input Interface

- Recommendations for unused Input and Output Pins

- Crystal Input Interface

- Termination for 3.3V LVPECL Output

- Termination for 2.5V LVPECL Output

- Application Schematic Example

- Power Considerations

- Power Dissipation

- Junction Temperature

- Thermal Resistance

- Calculations & Equations

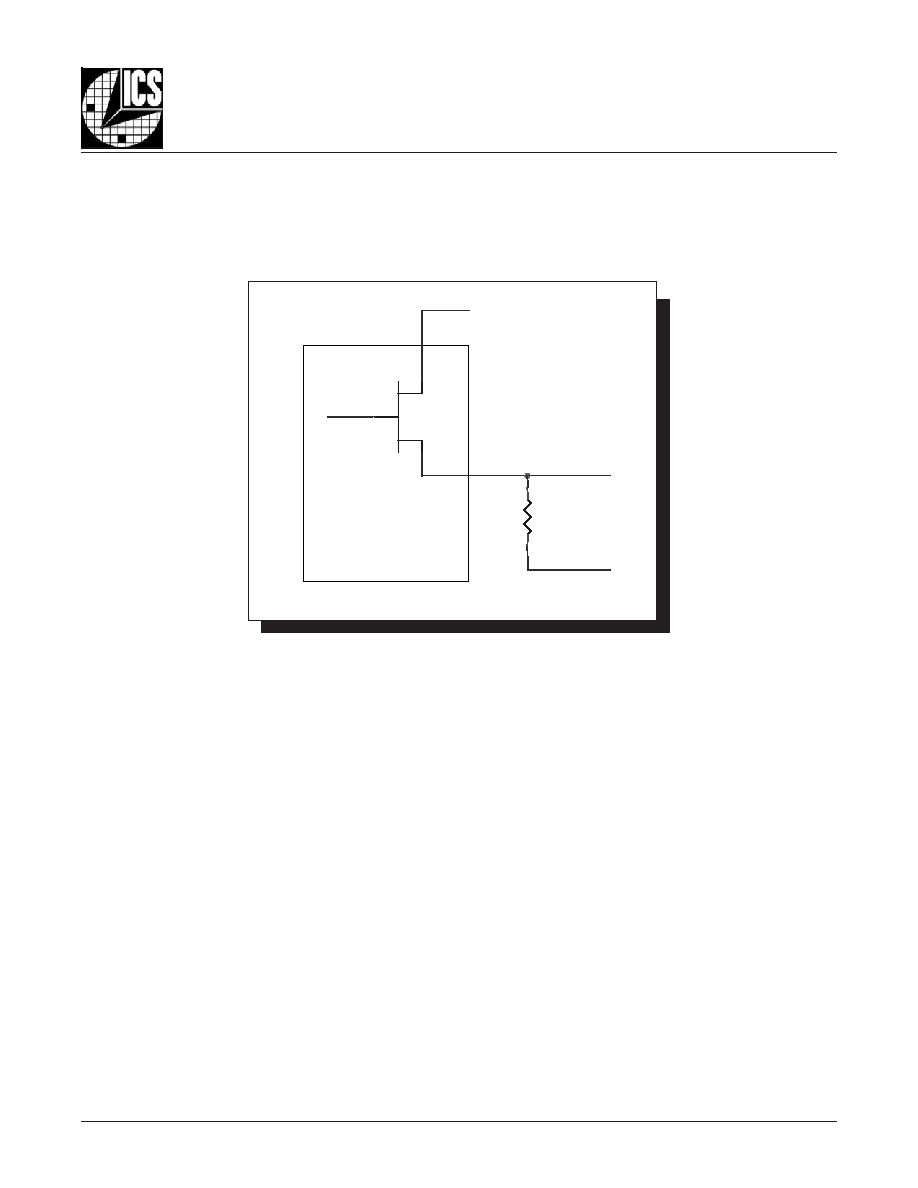

- LVPECL Driver Circuit & Termination

- Reliability Information

- Transistor Count

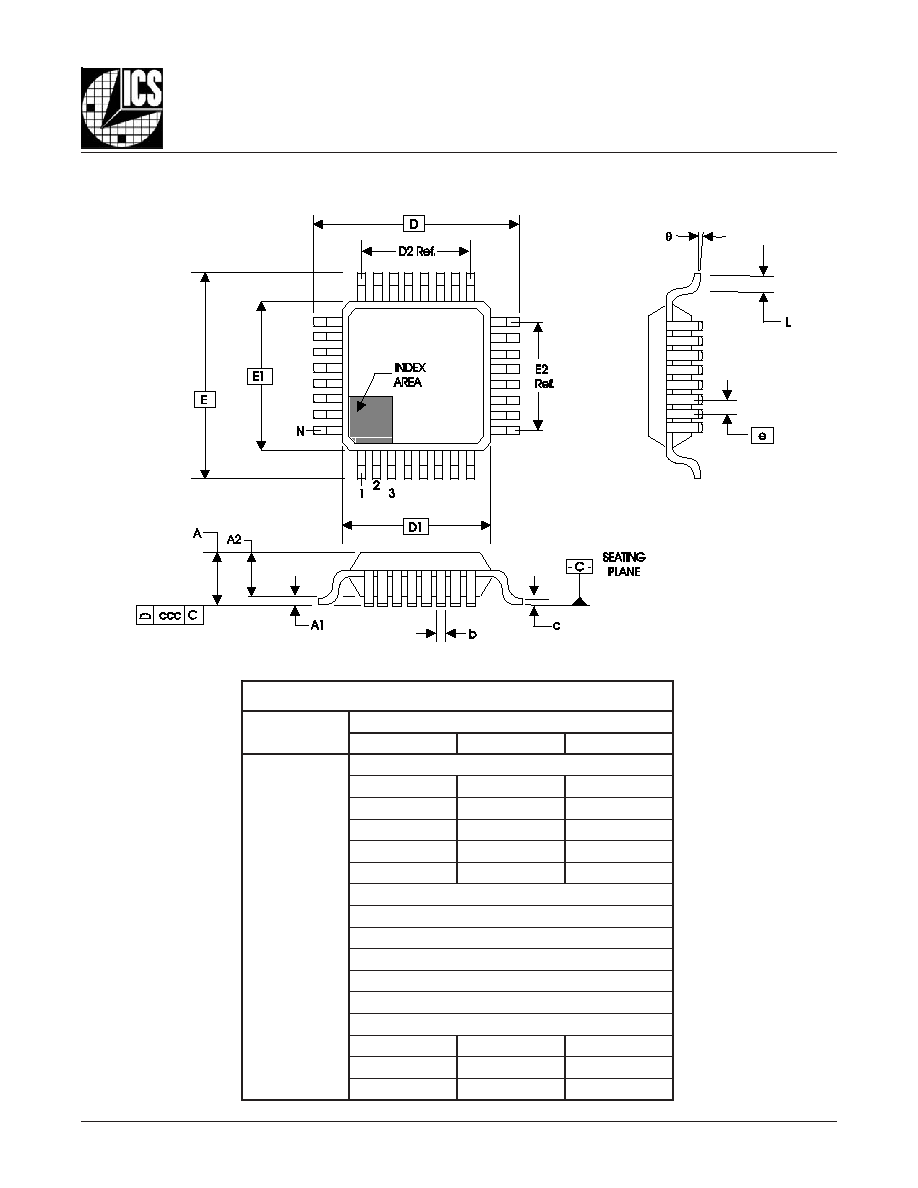

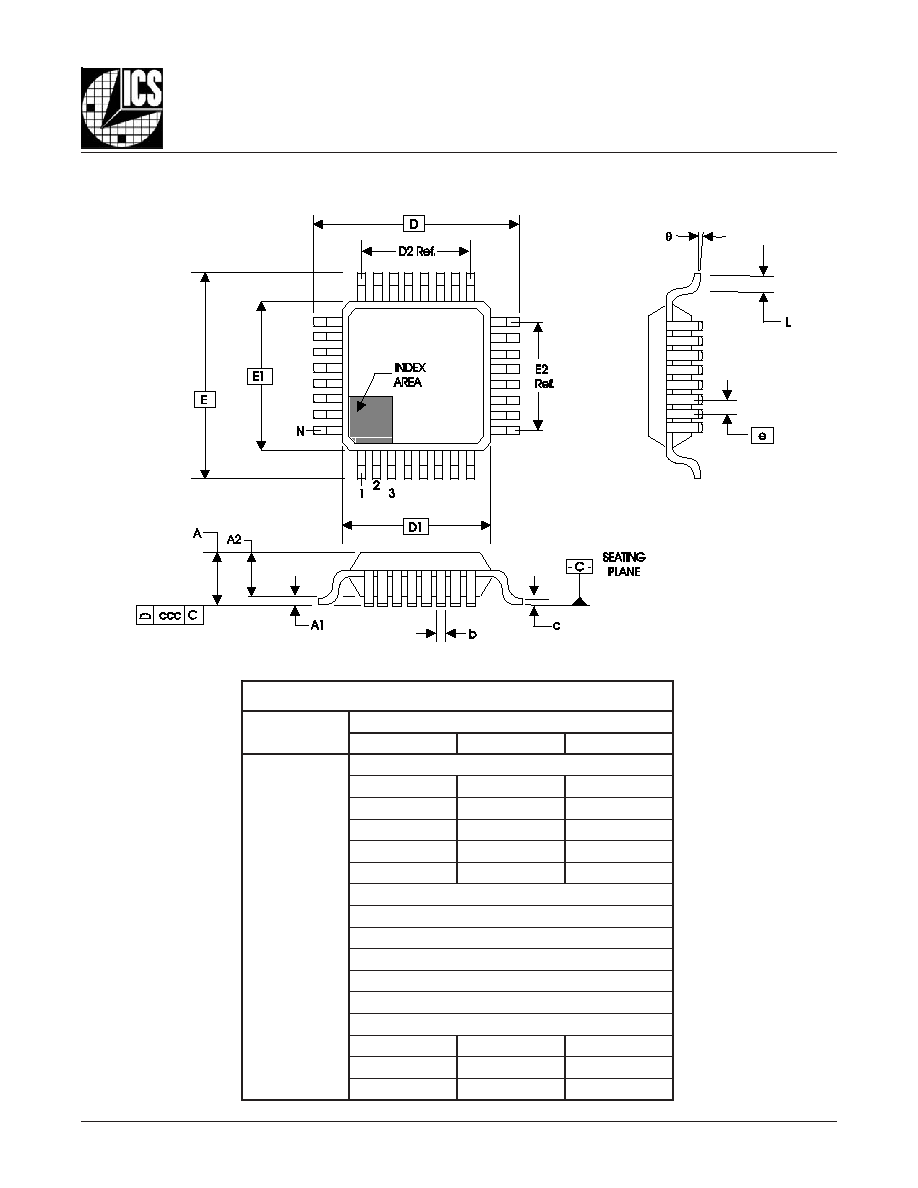

- Package Outline

- Package Dimensions

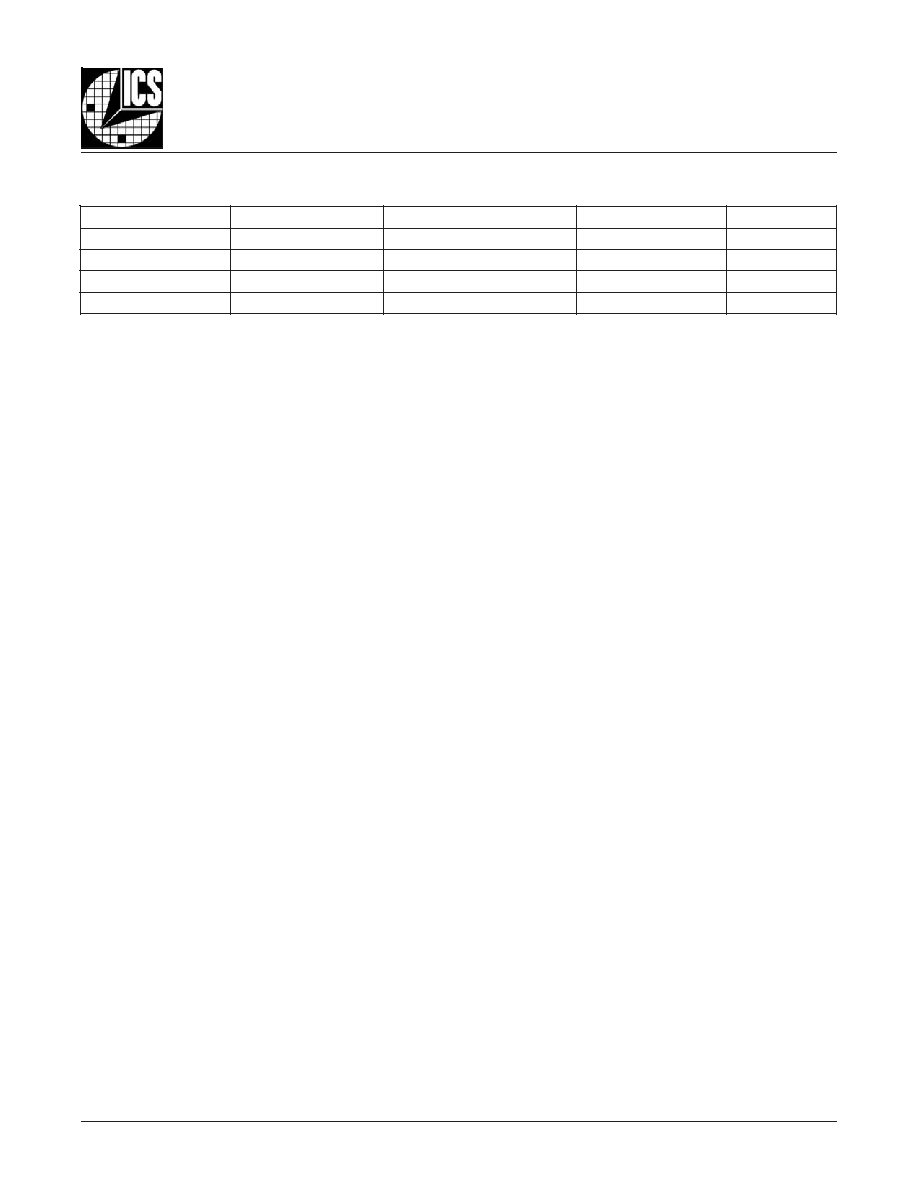

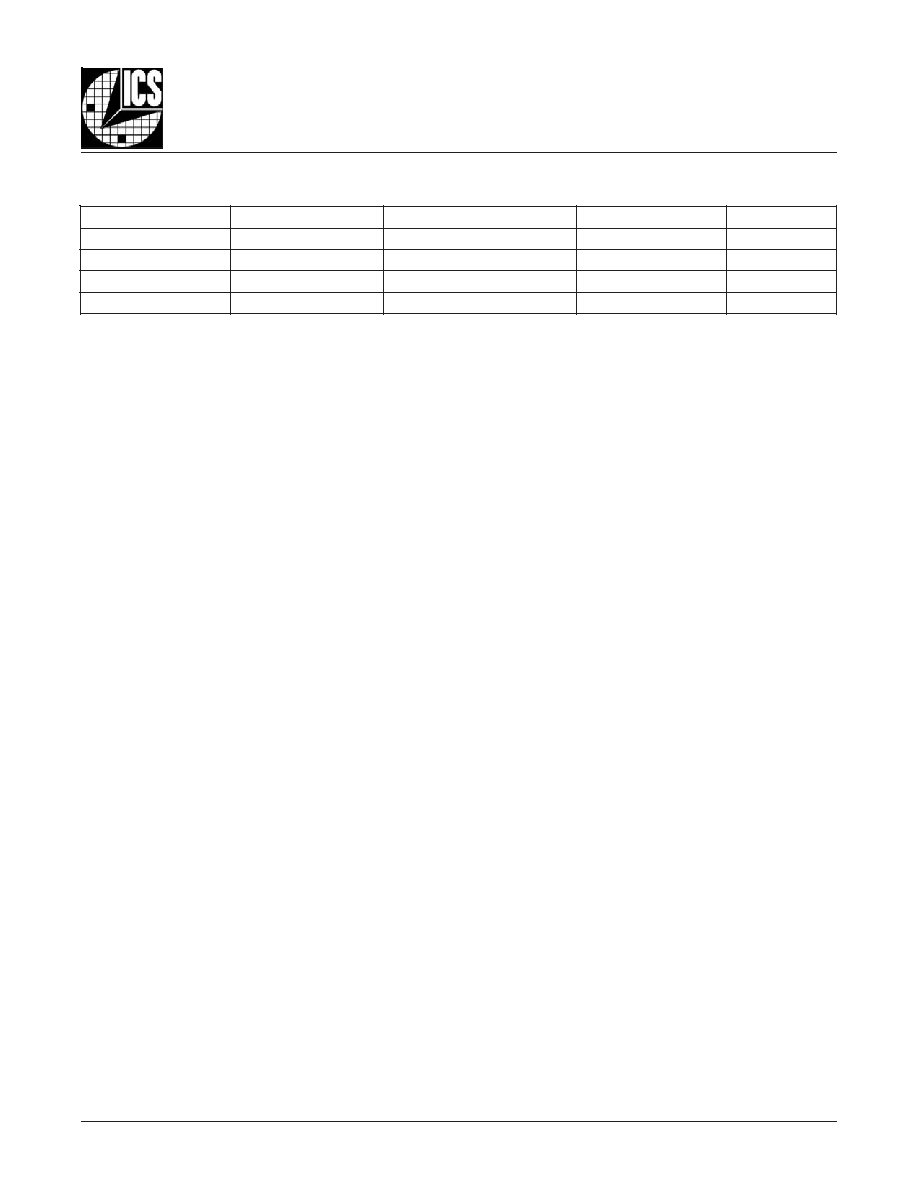

- Ordering Information

843034AY

www.icst.com/products/hiperclocks.html

REV. A JULY 25, 2005

1

Integrated

Circuit

Systems, Inc.

ICS843034

F

EMTO

C

LOCKS

TM

M

ULTI

-R

ATE

3.3V, 2.5V LVPECL F

REQUENCY

S

YNTHESIZER

PRELIMINARY

G

ENERAL

D

ESCRIPTION

The ICS843034 is a general purpose, low phase

noise LVPECL synthesizer which can generate

frequencies for a wide variety of applications. The

ICS843034 has a 4:1 input Multiplexer from which

the following inputs can be selected: 1 differential

input, 1 single-ended input, or two crystal

oscillators, thus making the device ideal for frequency

translation or frequency generation. Each differential LVPECL

output pair has an output divider which can be independently

set so that two different frequencies can be generated.

Additionally, each LVPECL output pair has a dedicated power

supply pin so the outputs can run at 3.3V or 2.5V. The

ICS843034 also supplies a buffered copy of the reference

clock or crystal frequency on the single-ended REF_CLK pin

which can be enabled or disabled (disabled by default). The

output frequency can be programmed using either a serial or

parallel programming interface.

The phase jitter of the ICS843034 is less than 1ps rms, making

it suitable for use in Fibre Channel, SONET, and Ethernet

applications.

Example applications include systems which must support

both FEC and non FEC rates. In 10Gb Fibre Channel, for

example, you can use a 25.5MHz crystal to generate a

159.375MHz reference clock, and then switch to a 20.544MHz

crystal to generate 164.355MHz for 66/64 FEC. Other

applications could include suppor ting both Ether net

frequencies and SONET frequencies in an application. When

Ethernet frequencies are needed, a 25MHz crystal can be

used and when SONET frequencies are needed, the input

MUX can be switched to select a 38.88MHz Crystal.

F

EATURES

� Dual differential 3.3V LVPECL outputs which can be set

independently for either 3.3V or 2.5V

� 4:1 Input Mux:

1 differential input

1 single-ended input

2 crystal oscillator interfaces

� CLK, nCLK pair can accept the following differential

input levels: LVPECL, LVDS, LVHSTL, HCSL, SSTL

� TEST_CLK accepts LVCMOS or LVTTL input levels

� Output frequency range: 35MHz to 750MHz

� Crystal input frequency range: 12MHz to 40MHz

� VCO range: 560MHz to 750MHz

� Parallel or serial interface for programming feedback

divider and output dividers

� RMS phase jitter at 333.33MHz, using a 22.222MHz

crystal (12kHz to 20MHz): 0.80ps (typical)

� Supply voltage modes:

LVPECL outputs (core/outputs):

3.3V/3.3V

3.3V/2.5V

REF_CLK output (core/outputs):

3.3V/3.3V

� 0�C to 70�C ambient operating temperature

� Industrial temperature available upon request

� Available in both, Standard and RoHS/Lead-Free compli-

ant packages

HiPerClockSTM

ICS

P

IN

A

SSIGNMENT

48 47 46 45 44 43 42 41 40 39 38 37

13 14 15 16 17 18 19 20 21 22 23 24

1

2

3

4

5

6

7

8

9

10

11

12

36

35

34

33

32

31

30

29

28

27

26

25

M8

NB0

NB1

NB2

OE_REF

OE_A

OE_B

V

CC

NA0

NA1

NA2

V

EE

XTAL_OUT1

XTAL_IN1

XTAL_OUT0

XTAL_IN0

TEST_CLK

SEL1

SEL0

V

CCA

S_LOAD

S_DATA

S_CLOCK

MR

CLK

nCLK

nP_LOAD

VCO_SEL

M0

M1

M2

M3

M4

M5

M6

M7

ICS843034

48-Pin LQFP

7mm x 7mm x 1.4mm

package body

Y Package

Top View

V

EE

nc

V

CCO

_

REF

REF_CLK

V

CCO

_

B

nFOUTB0

FOUTB0

V

CCO

_

A

nFOUT

A

0

FOUT

A

0

V

CC

TEST

The Preliminary Information presented herein represents a product in prototyping or pre-production. The noted characteristics are based on initial

product characterization. Integrated Circuit Systems, Incorporated (ICS) reserves the right to change any circuitry or specifications without notice.

843034AY

www.icst.com/products/hiperclocks.html

REV. A JULY 25, 2005

2

Integrated

Circuit

Systems, Inc.

ICS843034

F

EMTO

C

LOCKS

TM

M

ULTI

-R

ATE

3.3V, 2.5V LVPECL F

REQUENCY

S

YNTHESIZER

PRELIMINARY

OSC

C

I

L

�M

0

0

1

001

011

101

111

�16

�

000

�1

001

�2

010

�3

011

�4

�5

101

�6

�8

111

�16

�

OSC

P

HASE

D

ETECTOR

VCO

0 0

0 1

1 0

1 1

FOUTA0

nFOUTA0

FOUTB0

nFOUTB0

REF_CLK

TEST

V

CCO_REF

V

CCO_A

V

CCO_B

OE_A

VCO_SEL

XTAL_IN0

XTAL_OUT0

XTAL_IN1

XTAL_OUT1

CLK

nCLK

TEST_CLK

SEL1

SEL0

OE_B

MR

OE_REF

S_LOAD

S_DATA

S_CLOCK

nP_LOAD

M8:M0

NA2:NA0

NB2:NB0

B

LOCK

D

IAGRAM

843034AY

www.icst.com/products/hiperclocks.html

REV. A JULY 25, 2005

3

Integrated

Circuit

Systems, Inc.

ICS843034

F

EMTO

C

LOCKS

TM

M

ULTI

-R

ATE

3.3V, 2.5V LVPECL F

REQUENCY

S

YNTHESIZER

PRELIMINARY

The TEST output is LOW when operating in the parallel input

mode. The relationship between the VCO frequency, the crystal

frequency and the M divider is defined as follows:

The M value and the required values of M0 through M8 are shown

in Table 3B to program the VCO Frequency Function Table.

Valid M values for which the PLL will achieve lock for a 25MHz

reference are defined as 23

M 30. The frequency out is de-

fined as follows:

Serial operation occurs when nP_LOAD is HIGH and S_LOAD

is LOW. The shift register is loaded by sampling the S_DATA

bits with the rising edge of S_CLOCK. The contents of the

shift register are loaded into the M divider and Nx output di-

vider when S_LOAD transitions from LOW-to-HIGH. The M

divide and Nx output divide values are latched on the HIGH-

to-LOW transition of S_LOAD. If S_LOAD is held HIGH, data

at the S_DATA input is passed directly to the M divider and Nx

output divider on each rising edge of S_CLOCK. The serial

mode can be used to program the M and Nx bits and test bits

T1 and T0. The internal registers T0 and T1 determine the state

of the TEST output as follows:

F

UNCTIONAL

D

ESCRIPTION

NOTE: The functional description that follows describes op-

eration using a 25MHz crystal. Valid PLL loop divider values

for different crystal or input frequencies are defined in the In-

put Frequency Characteristics, Table 5, NOTE 1.

The ICS843034 features a fully integrated PLL and therefore

requires no external components for setting the loop band-

width. A fundamental crystal is used as the input to the on-

chip oscillator. The output of the oscillator is fed into the phase

detector. A 25MHz crystal provides a 25MHz phase detector

reference frequency. The VCO of the PLL operates over a

range of 560MHz to 750MHz. The output of the M divider is

also applied to the phase detector.

The phase detector and the M divider force the VCO output fre-

quency to be M times the reference frequency by adjusting the

VCO control voltage. Note that for some values of M (either too

high or too low), the PLL will not achieve lock. The output of the

VCO is scaled by a divider prior to being sent to each of the LVPECL

output buffers. The divider provides a 50% output duty cycle.

The ICS843034 supports either serial or parallel programming

modes to program the M feedback divider and N output divider.

Figure 1 shows the timing diagram for each mode. In parallel

mode, the nP_LOAD input is initially LOW. The data on the M,

NA, and NB inputs are passed directly to the M divider and both

N output dividers. On the LOW-to-HIGH transition of the

nP_LOAD input, the data is latched and the M and N dividers

remain loaded until the next LOW transition on nP_LOAD or

until a serial event occurs. As a result, the M and Nx bits can be

hardwired to set the M divider and Nx output divider to a spe-

cific default state that will automatically occur during power-up.

T1

T0

TEST Output

0

0

LOW

0

1

S_Data, Shift Register Output

1

0

Output of M divider

1

1

FOUTA0 same frequency

F

IGURE

1. P

ARALLEL

& S

ERIAL

L

OAD

O

PERATIONS

T 1

T0

NB2

NB1 NB0

NA2

NA1

NA0

M8

M7

M6

M5

M4

M3

M2

M1

M 0

S_CLOCK

S_DATA

S_LOAD

nP_LOAD

M0:M8, NA0:NA2, NB0:NB2

nP_LOAD

S_LOAD

fVCO = fxtal x M

S

ERIAL

L

OADING

P

ARALLEL

L

OADING

M, N

t

S

t

S

t

H

t

S

t

H

Time

FOUT = fVCO = fxtal x M

N

843034AY

www.icst.com/products/hiperclocks.html

REV. A JULY 25, 2005

4

Integrated

Circuit

Systems, Inc.

ICS843034

F

EMTO

C

LOCKS

TM

M

ULTI

-R

ATE

3.3V, 2.5V LVPECL F

REQUENCY

S

YNTHESIZER

PRELIMINARY

T

ABLE

1. P

IN

D

ESCRIPTIONS

r

e

b

m

u

N

e

m

a

N

e

p

y

T

n

o

i

t

p

i

r

c

s

e

D

,

2

4

,

1

4

,

1

,

4

4

,

3

4

8

4

,

7

4

,

5

4

,

1

M

,

0

M

,

8

M

,

3

M

,

2

M

7

M

,

6

M

,

4

M

t

u

p

n

I

n

w

o

d

ll

u

P

f

o

n

o

i

t

i

s

n

a

r

t

H

G

I

H

-

o

t

-

W

O

L

n

o

d

e

h

c

t

a

l

a

t

a

D

.

t

u

p

n

i

r

e

d

i

v

i

d

M

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

t

u

p

n

i

D

A

O

L

_

P

n

3

,

2

1

B

N

,

0

B

N

t

u

p

n

I

p

u

ll

u

P

,

C

3

e

l

b

a

T

n

i

d

e

n

i

f

e

d

s

a

e

u

l

a

v

r

e

d

i

v

i

d

t

u

p

t

u

o

s

e

n

i

m

r

e

t

e

D

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

e

l

b

a

T

n

o

i

t

c

n

u

F

4

2

B

N

t

u

p

n

I

n

w

o

d

ll

u

P

5

F

E

R

_

E

O

t

u

p

n

I

n

w

o

d

ll

u

P

.

t

u

p

t

u

o

K

L

C

_

F

E

R

f

o

g

n

il

b

a

s

i

d

d

n

a

g

n

il

b

a

n

e

s

l

o

r

t

n

o

C

.

e

l

b

a

n

e

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

6

A

_

E

O

t

u

p

n

I

p

u

ll

u

P

,

0

A

T

U

O

F

f

o

g

n

il

b

a

s

i

d

d

n

a

g

n

il

b

a

n

e

s

l

o

r

t

n

o

C

.

e

l

b

a

n

e

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

s

t

u

p

t

u

o

0

A

T

U

O

F

n

7

B

_

E

O

t

u

p

n

I

p

u

ll

u

P

,

0

B

T

U

O

F

f

o

g

n

il

b

a

s

i

d

d

n

a

g

n

il

b

a

n

e

s

l

o

r

t

n

o

C

.

e

l

b

a

n

e

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

s

t

u

p

t

u

o

0

B

T

U

O

F

n

4

1

,

8

V

C

C

r

e

w

o

P

.

s

n

i

p

y

l

p

p

u

s

e

r

o

C

0

1

,

9

1

A

N

,

0

A

N

t

u

p

n

I

p

u

ll

u

P

,

C

3

e

l

b

a

T

n

i

d

e

n

i

f

e

d

s

a

e

u

l

a

v

r

e

d

i

v

i

d

t

u

p

t

u

o

s

e

n

i

m

r

e

t

e

D

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

e

l

b

a

T

n

o

i

t

c

n

u

F

1

1

2

A

N

t

u

p

n

I

n

w

o

d

ll

u

P

4

2

,

2

1

V

E

E

r

e

w

o

P

.

s

n

i

p

y

l

p

p

u

s

e

v

i

t

a

g

e

N

3

1

T

S

E

T

t

u

p

t

u

O

.

n

o

i

t

a

r

e

p

o

f

o

e

d

o

m

l

a

i

r

e

s

e

h

t

n

i

E

V

I

T

C

A

s

i

h

c

i

h

w

t

u

p

t

u

o

t

s

e

T

.

e

d

o

m

l

e

ll

a

r

a

p

n

i

W

O

L

n

e

v

i

r

d

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

6

1

,

5

1

,

0

A

T

U

O

F

0

A

T

U

O

F

n

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

C

E

P

V

L

.

r

e

z

i

s

e

h

t

n

y

s

e

h

t

r

o

f

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

D

7

1

V

A

_

O

C

C

r

e

w

o

P

.

0

A

T

U

O

F

n

,

0

A

T

U

O

F

r

o

f

n

i

p

y

l

p

p

u

s

t

u

p

t

u

O

9

1

,

8

1

,

0

B

T

U

O

F

0

B

T

U

O

F

n

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

C

E

P

V

L

.

r

e

z

i

s

e

h

t

n

y

s

e

h

t

r

o

f

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

D

0

2

V

B

_

O

C

C

r

e

w

o

P

.

0

B

T

U

O

F

n

,

0

B

T

U

O

F

r

o

f

n

i

p

y

l

p

p

u

s

t

u

p

t

u

O

1

2

K

L

C

_

F

E

R

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

t

u

p

t

u

o

k

c

o

l

c

e

c

n

e

r

e

f

e

R

2

2

V

F

E

R

_

O

C

C

r

e

w

o

P

.

K

L

C

_

F

E

R

r

o

f

n

i

p

y

l

p

p

u

s

t

u

p

t

u

O

3

2

c

n

d

e

s

u

n

U

.

t

c

e

n

n

o

c

o

N

5

2

R

M

t

u

p

n

I

n

w

o

d

ll

u

P

l

a

n

r

e

t

n

i

e

h

t

s

e

c

r

o

f

,

H

G

I

H

c

i

g

o

l

n

e

h

W

.

t

e

s

e

R

r

e

t

s

a

M

h

g

i

H

e

v

i

t

c

A

e

h

t

d

n

a

w

o

l

o

g

o

t

x

T

U

O

F

s

t

u

p

t

u

o

e

u

r

t

e

h

t

g

n

i

s

u

a

c

t

e

s

e

r

e

r

a

s

r

e

d

i

v

i

d

l

a

n

r

e

t

n

i

e

h

t

,

W

O

L

c

i

g

o

l

n

e

h

W

.

h

g

i

h

o

g

o

t

x

T

U

O

F

n

s

t

u

p

t

u

o

d

e

t

r

e

v

n

i

t

o

n

s

e

o

d

R

M

f

o

n

o

i

t

r

e

s

s

A

.

d

e

l

b

a

n

e

e

r

a

s

t

u

p

t

u

o

e

h

t

d

n

a

s

r

e

d

i

v

i

d

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

s

e

u

l

a

v

T

d

n

a

,

N

,

M

d

e

d

a

o

l

t

c

e

f

f

a

6

2

K

C

O

L

C

_

S

t

u

p

n

I

n

w

o

d

ll

u

P

r

e

t

s

i

g

e

r

t

f

i

h

s

e

h

t

o

t

n

i

t

u

p

n

i

A

T

A

D

_

S

t

a

t

n

e

s

e

r

p

a

t

a

d

l

a

i

r

e

s

n

i

s

k

c

o

l

C

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

K

C

O

L

C

_

S

f

o

e

g

d

e

g

n

i

s

i

r

e

h

t

n

o

7

2

A

T

A

D

_

S

t

u

p

n

I

n

w

o

d

ll

u

P

e

g

d

e

g

n

i

s

i

r

e

h

t

n

o

d

e

l

p

m

a

s

a

t

a

D

.

t

u

p

n

i

l

a

i

r

e

s

r

e

t

s

i

g

e

r

t

f

i

h

S

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

K

C

O

L

C

_

S

f

o

8

2

D

A

O

L

_

S

t

u

p

n

I

n

w

o

d

ll

u

P

.

s

r

e

d

i

v

i

d

e

h

t

o

t

n

i

r

e

t

s

i

g

e

r

t

f

i

h

s

m

o

r

f

a

t

a

d

f

o

n

o

i

t

i

s

n

a

r

t

s

l

o

r

t

n

o

C

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

9

2

V

A

C

C

r

e

w

o

P

.

n

i

p

y

l

p

p

u

s

g

o

l

a

n

A

1

3

,

0

3

1

L

E

S

,

0

L

E

S

t

u

p

n

I

n

w

o

d

ll

u

P

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

s

t

u

p

n

i

t

c

e

l

e

s

k

c

o

l

C

2

3

K

L

C

_

T

S

E

T

t

u

p

n

I

n

w

o

d

ll

u

P

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

t

u

p

n

i

k

c

o

l

c

t

s

e

T

4

3

,

3

3

,

0

N

I

_

L

A

T

X

0

T

U

O

_

L

A

T

X

t

u

p

n

I

,

t

u

p

n

i

e

h

t

s

i

0

N

I

_

L

A

T

X

.

e

c

a

f

r

e

t

n

i

r

o

t

a

ll

i

c

s

o

l

a

t

s

y

r

C

.

t

u

p

t

u

o

e

h

t

s

i

0

T

U

O

_

L

A

T

X

6

3

,

5

3

,

1

N

I

_

L

A

T

X

1

T

U

O

_

L

A

T

X

t

u

p

n

I

,

t

u

p

n

i

e

h

t

s

i

1

N

I

_

L

A

T

X

.

e

c

a

f

r

e

t

n

i

r

o

t

a

ll

i

c

s

o

l

a

t

s

y

r

C

.

t

u

p

t

u

o

e

h

t

s

i

1

T

U

O

_

L

A

T

X

.

.

.

e

g

a

p

t

x

e

n

n

o

d

e

u

n

i

t

n

o

C

843034AY

www.icst.com/products/hiperclocks.html

REV. A JULY 25, 2005

5

Integrated

Circuit

Systems, Inc.

ICS843034

F

EMTO

C

LOCKS

TM

M

ULTI

-R

ATE

3.3V, 2.5V LVPECL F

REQUENCY

S

YNTHESIZER

PRELIMINARY

T

ABLE

2. P

IN

C

HARACTERISTICS

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

C

N

I

e

c

n

a

t

i

c

a

p

a

C

t

u

p

n

I

4

F

p

C

D

P

n

o

i

t

a

p

i

s

s

i

D

r

e

w

o

P

e

c

n

a

t

i

c

a

p

a

C

K

L

C

_

F

E

R

V

C

C

V

,

A

C

C

V

,

F

E

R

_

O

C

C

V

5

6

4

.

3

=

D

B

T

F

p

R

P

U

L

L

U

P

r

o

t

s

i

s

e

R

p

u

ll

u

P

t

u

p

n

I

1

5

k

R

N

W

O

D

L

L

U

P

r

o

t

s

i

s

e

R

n

w

o

d

ll

u

P

t

u

p

n

I

1

5

k

R

T

U

O

e

c

n

a

d

e

p

m

I

t

u

p

t

u

O

K

L

C

_

F

E

R

5

7

2

1

r

e

b

m

u

N

e

m

a

N

e

p

y

T

n

o

i

t

p

i

r

c

s

e

D

7

3

K

L

C

t

u

p

n

I

n

w

o

d

ll

u

P

.

t

u

p

n

i

k

c

o

l

c

l

a

i

t

n

e

r

e

f

f

i

d

g

n

i

t

r

e

v

n

i

-

n

o

N

8

3

K

L

C

n

t

u

p

n

I

/

p

u

ll

u

P

n

w

o

d

ll

u

P

V

.

t

u

p

n

i

k

c

o

l

c

l

a

i

t

n

e

r

e

f

f

i

d

g

n

i

t

r

e

v

n

I

C

C

.

g

n

i

t

a

o

l

f

t

f

e

l

n

e

h

w

t

l

u

a

f

e

d

2

/

9

3

D

A

O

L

_

P

n

t

u

p

n

I

n

w

o

d

ll

u

P

s

i

0

M

:

8

M

t

a

t

n

e

s

e

r

p

a

t

a

d

n

e

h

w

s

e

n

i

m

r

e

t

e

D

.

t

u

p

n

i

d

a

o

l

l

e

ll

a

r

a

P

d

n

a

0

A

N

:

2

A

N

t

a

t

n

e

s

e

r

p

a

t

a

d

n

e

h

w

d

n

a

,

r

e

d

i

v

i

d

M

o

t

n

i

d

e

d

a

o

l

.

s

r

e

d

i

v

i

d

t

u

p

t

u

o

N

e

h

t

o

t

n

i

d

e

d

a

o

l

s

i

0

B

N

:

2

B

N

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

0

4

L

E

S

_

O

C

V

t

u

p

n

I

p

u

ll

u

P

.

e

d

o

m

s

s

a

p

y

b

r

o

L

L

P

n

i

s

i

r

e

z

i

s

e

h

t

n

y

s

r

e

h

t

e

h

w

s

e

n

i

m

r

e

t

e

D

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

6

4

5

M

t

u

p

n

I

p

u

ll

u

P

n

o

i

t

i

s

n

a

r

t

H

G

I

H

-

o

t

-

W

O

L

n

o

d

e

h

c

t

a

l

a

t

a

D

.

s

t

u

p

n

i

r

e

d

i

v

i

d

M

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

t

u

p

n

i

D

A

O

L

_

P

n

f

o

:

E

T

O

N

p

u

ll

u

P

d

n

a

n

w

o

d

ll

u

P

.

s

e

u

l

a

v

l

a

c

i

p

y

t

r

o

f

,

s

c

i

t

s

i

r

e

t

c

a

r

a

h

C

n

i

P

,

2

e

l

b

a

T

e

e

S

.

s

r

o

t

s

i

s

e

r

t

u

p

n

i

l

a

n

r

e

t

n

i

o

t

r

e

f

e

r

843034AY

www.icst.com/products/hiperclocks.html

REV. A JULY 25, 2005

6

Integrated

Circuit

Systems, Inc.

ICS843034

F

EMTO

C

LOCKS

TM

M

ULTI

-R

ATE

3.3V, 2.5V LVPECL F

REQUENCY

S

YNTHESIZER

PRELIMINARY

T

ABLE

3A. P

ARALLEL

AND

S

ERIAL

M

ODE

F

UNCTION

T

ABLE

s

t

u

p

n

I

s

n

o

i

t

i

d

n

o

C

R

M

D

A

O

L

_

P

n

M

N

D

A

O

L

_

S

K

C

O

L

C

_

S

A

T

A

D

_

S

H

X

X

X

X

X

X

.

W

O

L

s

t

u

p

t

u

o

s

e

c

r

o

F

.

t

e

s

e

R

L

L

a

t

a

D

a

t

a

D

X

X

X

M

e

h

t

o

t

y

l

t

c

e

r

i

d

d

e

s

s

a

p

s

t

u

p

n

i

N

d

n

a

M

n

o

a

t

a

D

.

W

O

L

d

e

c

r

o

f

t

u

p

t

u

o

T

S

E

T

.

r

e

d

i

v

i

d

t

u

p

t

u

o

N

d

n

a

r

e

d

i

v

i

d

L

a

t

a

D

a

t

a

D

L

X

X

d

e

d

a

o

l

s

n

i

a

m

e

r

d

n

a

s

r

e

t

s

i

g

e

r

t

u

p

n

i

o

t

n

i

d

e

h

c

t

a

l

s

i

a

t

a

D

.

s

r

u

c

c

o

t

n

e

v

e

l

a

i

r

e

s

a

li

t

n

u

r

o

n

o

i

t

i

s

n

a

r

t

W

O

L

t

x

e

n

li

t

n

u

L

H

X

X

L

a

t

a

D

n

o

a

t

a

d

h

t

i

w

d

e

d

a

o

l

s

i

r

e

t

s

i

g

e

r

t

f

i

h

S

.

e

d

o

m

t

u

p

n

i

l

a

i

r

e

S

.

K

C

O

L

C

_

S

f

o

e

g

d

e

g

n

i

s

i

r

h

c

a

e

n

o

A

T

A

D

_

S

L

H

X

X

L

a

t

a

D

e

h

t

o

t

d

e

s

s

a

p

e

r

a

r

e

t

s

i

g

e

r

t

f

i

h

s

e

h

t

f

o

s

t

n

e

t

n

o

C

.

r

e

d

i

v

i

d

t

u

p

t

u

o

N

d

n

a

r

e

d

i

v

i

d

M

L

H

X

X

L

a

t

a

D

.

d

e

h

c

t

a

l

e

r

a

s

e

u

l

a

v

r

e

d

i

v

i

d

t

u

p

t

u

o

N

d

n

a

r

e

d

i

v

i

d

M

L

H

X

X

L

X

X

.

s

r

e

t

s

i

g

e

r

t

f

i

h

s

t

c

e

f

f

a

t

o

n

o

d

t

u

p

n

i

l

a

i

r

e

s

r

o

l

e

ll

a

r

a

P

L

H

X

X

H

a

t

a

D

.

d

e

k

c

o

l

c

s

i

t

i

s

a

r

e

d

i

v

i

d

M

o

t

y

l

t

c

e

r

i

d

d

e

s

s

a

p

A

T

A

D

_

S

W

O

L

=

L

:

E

T

O

N

H

G

I

H

=

H

e

r

a

c

t

'

n

o

D

=

X

n

o

i

t

i

s

n

a

r

t

e

g

d

e

g

n

i

s

i

R

=

n

o

i

t

i

s

n

a

r

t

e

g

d

e

g

n

il

l

a

F

=

T

ABLE

3B. P

ROGRAMMABLE

VCO F

REQUENCY

F

UNCTION

T

ABLE

T

ABLE

3C. P

ROGRAMMABLE

O

UTPUT

D

IVIDER

F

UNCTION

T

ABLE

y

c

n

e

u

q

e

r

F

O

C

V

)

z

H

M

(

e

d

i

v

i

D

M

6

5

2

8

2

1

4

6

2

3

6

1

8

4

2

1

8

M

7

M

6

M

5

M

4

M

3

M

2

M

1

M

0

M

5

7

5

3

2

0

0

0

0

1

0

1

1

1

�

�

�

�

�

�

�

�

�

�

�

0

0

7

8

2

0

0

0

0

1

1

1

0

0

�

�

�

�

�

�

�

�

�

�

�

0

5

7

0

3

0

0

0

0

1

1

1

1

0

f

o

y

c

n

e

u

q

e

r

f

t

u

p

n

i

K

L

C

_

T

S

E

T

r

o

l

a

t

s

y

r

c

o

t

d

n

o

p

s

e

r

r

o

c

s

e

i

c

n

e

u

q

e

r

f

g

n

i

t

l

u

s

e

r

e

h

t

d

n

a

s

e

u

l

a

v

e

d

i

v

i

d

M

e

s

e

h

T

:

1

E

T

O

N

.

z

H

M

5

2

s

t

u

p

n

I

e

u

l

a

V

r

e

d

i

v

i

D

N

)

z

H

M

(

y

c

n

e

u

q

e

r

F

t

u

p

t

u

O

2

X

N

*

1

X

N

*

0

X

N

*

m

u

m

i

n

i

M

m

u

m

i

x

a

M

0

0

0

1

0

6

5

0

5

7

0

0

1

2

0

8

2

5

7

3

0

1

0

3

6

6

.

6

8

1

0

5

2

0

1

1

4

0

4

1

5

.

7

8

1

1

0

0

5

2

1

1

0

5

1

1

0

1

6

3

3

.

3

9

5

2

1

1

1

0

8

0

7

5

7

.

3

9

1

1

1

6

1

5

3

5

7

8

.

6

4

B

k

n

a

B

r

o

A

k

n

a

B

s

e

t

o

n

e

d

X

:

E

T

O

N

*

843034AY

www.icst.com/products/hiperclocks.html

REV. A JULY 25, 2005

7

Integrated

Circuit

Systems, Inc.

ICS843034

F

EMTO

C

LOCKS

TM

M

ULTI

-R

ATE

3.3V, 2.5V LVPECL F

REQUENCY

S

YNTHESIZER

PRELIMINARY

T

ABLE

4A. P

OWER

S

UPPLY

DC C

HARACTERISTICS

,

V

CC

= V

CCA

= 3.3V�5%, V

CCO_A

= V

CCO_B

= 3.3V�5%

OR

2.5V�5%, T

A

= 0�C

TO

70�C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

C

C

e

g

a

t

l

o

V

y

l

p

p

u

S

e

r

o

C

5

3

1

.

3

3

.

3

5

6

4

.

3

V

V

A

C

C

e

g

a

t

l

o

V

y

l

p

p

u

S

g

o

l

a

n

A

5

3

1

.

3

3

.

3

5

6

4

.

3

V

V

,

A

_

O

C

C

V

B

_

O

C

C

e

g

a

t

l

o

V

y

l

p

p

u

S

t

u

p

t

u

O

5

3

1

.

3

3

.

3

5

6

4

.

3

V

5

7

3

.

2

5

.

2

5

2

6

.

2

V

V

F

E

R

_

O

C

C

y

l

p

p

u

S

t

u

p

t

u

O

K

L

C

_

F

E

R

5

3

1

.

3

3

.

3

5

6

4

.

3

V

I

E

E

t

n

e

r

r

u

C

y

l

p

p

u

S

r

e

w

o

P

5

8

1

A

m

I

A

C

C

t

n

e

r

r

u

C

y

l

p

p

u

S

g

o

l

a

n

A

0

2

A

m

NOTE: Stresses beyond those listed under Absolute

Maximum Ratings may cause permanent damage to the

device. These ratings are stress specifications only. Functional

operation of product at these conditions or any conditions be-

yond those listed in the

DC Characteristics or AC Character-

istics is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect product reliability.

A

BSOLUTE

M

AXIMUM

R

ATINGS

Supply Voltage, V

CC

4.6V

Inputs, V

I

-0.5V to V

CC

+ 0.5V

Outputs, V

O

(LVCMOS)

-0.5V to V

CCO

+ 0.5V

Outputs, I

O

(LVPECL)

Continuous Current

50mA

Surge Current

100mA

Package Thermal Impedance,

JA

47.9�C/W (0 lfpm)

Storage Temperature, T

STG

-65�C to 150�C

843034AY

www.icst.com/products/hiperclocks.html

REV. A JULY 25, 2005

8

Integrated

Circuit

Systems, Inc.

ICS843034

F

EMTO

C

LOCKS

TM

M

ULTI

-R

ATE

3.3V, 2.5V LVPECL F

REQUENCY

S

YNTHESIZER

PRELIMINARY

T

ABLE

4B. LVCMOS/LVTTL DC C

HARACTERISTICS

,

V

CC

= V

CCA

= 3.3V�5%, V

CCO_A

= V

CCO_B

= V

CCO_REF

= 3.3V�5%, T

A

= 0�C

TO

70�C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

H

I

e

g

a

t

l

o

V

h

g

i

H

t

u

p

n

I

2

V

C

C

3

.

0

+

V

V

M

I

e

g

a

t

l

o

V

d

i

M

t

u

p

n

I

V

C

C

V

2

.

0

-

2

/

V

C

C

V

2

.

0

+

2

/

V

V

L

I

e

g

a

t

l

o

V

w

o

L

t

u

p

n

I

3

.

0

-

8

.

0

V

I

H

I

t

u

p

n

I

t

n

e

r

r

u

C

h

g

i

H

,

R

M

,

K

L

C

_

T

S

E

T

,

F

E

R

_

E

O

,

]

0

:

1

[

L

E

S

,

A

T

A

D

_

S

,

K

C

O

L

C

_

S

,

D

A

O

L

_

P

n

,

D

A

O

L

_

S

8

M

:

6

M

,

4

M

:

1

M

,

2

x

N

V

C

C

V

=

N

I

V

5

6

4

.

3

=

0

5

1

A

�

,

A

_

E

O

,

5

M

,

1

x

N

,

0

x

N

L

E

S

_

O

C

V

,

B

_

E

O

V

C

C

V

=

N

I

V

5

6

4

.

3

=

5

A

�

I

L

I

t

u

p

n

I

t

n

e

r

r

u

C

w

o

L

,

R

M

,

K

L

C

_

T

S

E

T

,

F

E

R

_

E

O

,

]

0

:

1

[

L

E

S

,

A

T

A

D

_

S

,

K

C

O

L

C

_

S

,

D

A

O

L

_

P

n

,

D

A

O

L

_

S

8

M

:

6

M

,

4

M

:

1

M

,

2

x

N

V

C

C

,

V

5

6

4

.

3

=

V

N

I

V

0

=

5

-

A

�

,

A

_

E

O

,

5

M

,

1

x

N

,

0

x

N

L

E

S

_

O

C

V

,

B

_

E

O

V

C

C

,

V

5

6

4

.

3

=

V

N

I

V

0

=

0

5

1

-

A

�

V

H

O

t

u

p

t

u

O

e

g

a

t

l

o

V

h

g

i

H

1

E

T

O

N

;

T

S

E

T

V

F

E

R

_

O

C

C

%

5

�

V

3

.

3

=

6

.

2

V

K

L

C

_

F

E

R

V

F

E

R

_

O

C

C

V

3

.

0

-

4

.

0

V

V

L

O

t

u

p

t

u

O

e

g

a

t

l

o

V

w

o

L

1

E

T

O

N

;

T

S

E

T

V

F

E

R

_

O

C

C

%

5

�

V

3

.

3

=

5

.

0

V

NOTE 1: Output terminated with 50

to V

CCO_REF

/2.

843034AY

www.icst.com/products/hiperclocks.html

REV. A JULY 25, 2005

9

Integrated

Circuit

Systems, Inc.

ICS843034

F

EMTO

C

LOCKS

TM

M

ULTI

-R

ATE

3.3V, 2.5V LVPECL F

REQUENCY

S

YNTHESIZER

PRELIMINARY

T

ABLE

5. I

NPUT

F

REQUENCY

C

HARACTERISTICS

,

V

CC

= V

CCA

= 3.3V�5%, V

CCO_A

= V

CCO_B

= 3.3V�5%

OR

2.5V�5%, T

A

= 0�C

TO

70�C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

f

N

I

y

c

n

e

u

q

e

r

F

t

u

p

n

I

,

0

T

U

O

_

L

A

T

X

/

0

N

I

_

L

A

T

X

1

T

U

O

_

L

A

T

X

/

1

N

I

_

L

A

T

X

2

1

0

4

z

H

M

K

L

C

_

T

S

E

T

,

K

L

C

n

/

K

L

C

2

1

D

B

T

z

H

M

K

C

O

L

C

_

S

0

5

z

H

M

t

R

t

/

F

ll

a

F

/

e

s

i

R

t

u

p

n

I

e

m

i

T

K

L

C

_

T

S

E

T

D

B

T

s

n

,

A

T

A

D

_

S

,

D

A

O

L

_

S

K

C

O

L

C

_

S

D

B

T

s

n

e

t

a

r

e

p

o

o

t

O

C

V

e

h

t

r

o

f

t

e

s

e

b

t

s

u

m

e

u

l

a

v

M

e

h

t

,

e

g

n

a

r

y

c

n

e

u

q

e

r

f

K

L

C

_

T

S

E

T

d

n

a

K

L

C

n

/

K

L

C

,

l

a

t

s

y

r

c

t

u

p

n

i

e

h

t

r

o

F

:

E

T

O

N

7

4

e

r

a

M

f

o

s

e

u

l

a

v

d

il

a

v

,

z

H

M

2

1

f

o

y

c

n

e

u

q

e

r

f

t

u

p

n

i

m

u

m

i

n

i

m

e

h

t

g

n

i

s

U

.

e

g

n

a

r

z

H

M

0

5

7

o

t

z

H

M

0

6

5

e

h

t

n

i

h

t

i

w

M 2

6

.

4

1

e

r

a

M

f

o

s

e

u

l

a

v

d

il

a

v

,

z

H

M

0

4

f

o

y

c

n

e

u

q

e

r

f

m

u

m

i

x

a

m

e

h

t

g

n

i

s

U

M

.

8

1

T

ABLE

6. C

RYSTAL

C

HARACTERISTICS

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

n

o

i

t

a

ll

i

c

s

O

f

o

e

d

o

M

l

a

t

n

e

m

a

d

n

u

F

y

c

n

e

u

q

e

r

F

2

1

0

4

z

H

M

)

R

S

E

(

e

c

n

a

t

s

i

s

e

R

s

e

i

r

e

S

t

n

e

l

a

v

i

u

q

E

0

5

e

c

n

a

t

i

c

a

p

a

C

t

n

u

h

S

7

F

p

l

e

v

e

L

e

v

i

r

D

1

W

m

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

I

H

I

t

n

e

r

r

u

C

h

g

i

H

t

u

p

n

I

K

L

C

n

V

N

I

V

=

C

C

V

5

6

4

.

3

=

0

5

1

A

�

K

L

C

V

N

I

V

=

C

C

V

5

6

4

.

3

=

0

5

1

A

�

I

L

I

t

n

e

r

r

u

C

w

o

L

t

u

p

n

I

K

L

C

n

V

N

I

V

,

V

0

=

C

C

V

5

6

4

.

3

=

0

5

1

-

A

�

K

L

C

V

N

I

V

,

V

0

=

C

C

V

5

6

4

.

3

=

5

-

A

�

V

P

P

e

g

a

t

l

o

V

t

u

p

n

I

k

a

e

P

-

o

t

-

k

a

e

P

5

1

.

0

3

.

1

V

V

R

M

C

2

,

1

E

T

O

N

;

e

g

a

t

l

o

V

t

u

p

n

I

e

d

o

M

n

o

m

m

o

C

V

E

E

5

.

0

+

V

C

C

5

8

.

0

-

V

s

n

o

i

t

a

c

il

p

p

a

d

e

d

n

e

e

l

g

n

i

s

r

o

F

:

1

E

T

O

N

,

V

s

i

K

L

C

n

,

K

L

C

r

o

f

e

g

a

t

l

o

v

t

u

p

n

i

m

u

m

i

x

a

m

e

h

t

C

C

.

V

3

.

0

+

s

i

e

g

a

t

l

o

v

e

d

o

m

n

o

m

m

o

C

:

2

E

T

O

N

V

s

a

d

e

n

i

f

e

d

H

I

.

T

ABLE

4D. LVPECL DC C

HARACTERISTICS

,

V

CC

= V

CCA

= 3.3V�5%, V

CCO_A

= V

CCO_B

= 3.3V�5%

OR

2.5V�5%, T

A

= 0�C

TO

70�C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

H

O

1

E

T

O

N

;

e

g

a

t

l

o

V

h

g

i

H

t

u

p

t

u

O

V

O

C

C

4

.

1

-

V

O

C

C

9

.

0

-

V

V

L

O

1

E

T

O

N

;

e

g

a

t

l

o

V

w

o

L

t

u

p

t

u

O

V

O

C

C

0

.

2

-

V

O

C

C

7

.

1

-

V

V

G

N

I

W

S

g

n

i

w

S

e

g

a

t

l

o

V

t

u

p

t

u

O

k

a

e

P

-

o

t

-

k

a

e

P

6

.

0

0

.

1

V

0

5

h

t

i

w

d

e

t

a

n

i

m

r

e

t

s

t

u

p

t

u

O

:

1

E

T

O

N

V

o

t

,

A

_

O

C

C

V

B

_

O

C

C

.

V

2

-

T

ABLE

4C. D

IFFERENTIAL

DC C

HARACTERISTICS

,

V

CC

= V

CCA

= 3.3V�5%, V

CCO_A

= V

CCO_B

= 3.3V�5%

OR

2.5V�5%, T

A

= 0�C

TO

70�C

843034AY

www.icst.com/products/hiperclocks.html

REV. A JULY 25, 2005

10

Integrated

Circuit

Systems, Inc.

ICS843034

F

EMTO

C

LOCKS

TM

M

ULTI

-R

ATE

3.3V, 2.5V LVPECL F

REQUENCY

S

YNTHESIZER

PRELIMINARY

T

ABLE

7B. AC C

HARACTERISTICS

,

V

CC

= V

CCA

= 3.3V�5%, V

CCO_A

= V

CCO_B

= 2.5V�5%, T

A

= 0�C

TO

70�C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

F

T

U

O

y

c

n

e

u

q

e

r

F

t

u

p

t

u

O

5

3

0

5

7

z

H

M

t

)

�

(

t

ij

;

)

m

o

d

n

a

R

(

S

M

R

,

r

e

t

t

i

J

e

s

a

h

P

2

,

1

E

T

O

N

,

z

H

M

3

3

.

3

3

3

:

e

g

n

a

R

n

o

i

t

a

r

g

e

t

n

I

z

H

M

0

2

-

z

H

k

2

1

0

8

.

0

s

p

t

)

c

c

(

t

ij

4

,

3

E

T

O

N

;

r

e

t

t

i

J

e

l

c

y

C

-

o

t

-

e

l

c

y

C

D

B

T

s

p

t

)

o

(

k

s

5

,

4

,

2

E

T

O

N

;

w

e

k

S

t

u

p

t

u

O

e

m

a

s

e

h

t

@

d

e

r

u

s

a

e

M

y

c

n

e

u

q

e

r

F

t

u

p

t

u

O

0

5

s

p

t

R

t

/

F

t

u

p

t

u

O

e

m

i

T

ll

a

F

/

e

s

i

R

s

t

u

p

t

u

O

L

C

E

P

V

L

%

0

8

o

t

%

0

2

0

0

2

0

0

7

s

p

K

L

C

_

F

E

R

t

S

e

m

i

T

p

u

t

e

S

D

A

O

L

_

P

n

o

t

N

,

M

5

s

n

K

C

O

L

C

_

S

o

t

A

T

A

D

_

S

5

s

n

D

A

O

L

_

S

o

t

K

C

O

L

C

_

S

5

s

n

t

H

e

m

i

T

d

l

o

H

D

A

O

L

_

P

n

o

t

N

,

M

5

s

n

K

C

O

L

C

_

S

o

t

A

T

A

D

_

S

5

s

n

D

A

O

L

_

S

o

t

K

C

O

L

C

_

S

5

s

n

c

d

o

e

l

c

y

C

y

t

u

D

t

u

p

t

u

O

0

5

%

t

K

C

O

L

e

m

i

T

k

c

o

L

L

L

P

1

s

m

.

n

o

i

t

c

e

s

n

o

i

t

a

m

r

o

f

n

I

t

n

e

m

e

r

u

s

a

e

M

r

e

t

e

m

a

r

a

P

e

e

S

.

t

o

l

P

e

s

i

o

N

e

s

a

h

P

e

h

t

o

t

r

e

f

e

r

e

s

a

e

l

P

:

1

E

T

O

N

.

d

e

l

b

a

s

i

d

t

u

p

t

u

o

K

L

C

_

F

E

R

h

t

i

w

d

e

z

i

r

e

t

c

a

r

a

h

C

:

2

E

T

O

N

.

s

t

u

p

n

i

L

A

T

X

g

n

i

s

u

e

c

n

a

r

o

f

r

e

p

r

e

t

t

i