8442AYI

www.icst.com/products/hiperclocks.html

REV. C MAY 10, 2005

1

Integrated

Circuit

Systems, Inc.

ICS8442I

700MH

Z

, C

RYSTAL

O

SCILLATOR

-

TO

-D

IFFERENTIAL

LVDS F

REQUENCY

S

YNTHESIZER

G

ENERAL

D

ESCRIPTION

The ICS8442I is a general purpose, dual output

Crystal-to-Differential LVDS High Frequency

Synthesizer and a member of the HiPerClockSTM

family of High Performance Clock Solutions from

ICS. The ICS8442I has a selectable TEST_CLK

or crystal input. The TEST_CLK input accepts LVCMOS or

LVTTL input levels and translates them to LVDS levels. The

VCO operates at a frequency range of 250MHz to 700MHz.

The VCO frequency is programmed in steps equal to the value

of the input reference or crystal frequency. The VCO and output

frequency can be programmed using the serial or parallel

interface to the configuration logic. The low phase noise

characteristics of the ICS8442I makes it an ideal clock source

for Gigabit Ethernet and Sonet applications.

F

EATURES

· Dual differential LVDS outputs

· Selectable crystal oscillator interface or

LVCMOS/LVTTL TEST_CLK

· Output frequency range: 31.25MHz to 700MHz

· Crystal input frequency range: 10MHz to 25MHz

· VCO range: 250MHz to 700MHz

· Parallel or serial interface for programming counter

and output dividers

· RMS period jitter: 3.5ps (typical)

· Cycle-to-cycle jitter: 18ps (typical)

· 3.3V supply voltage

· -40°C to 85°C ambient operating temperature

HiPerClockSTM

ICS

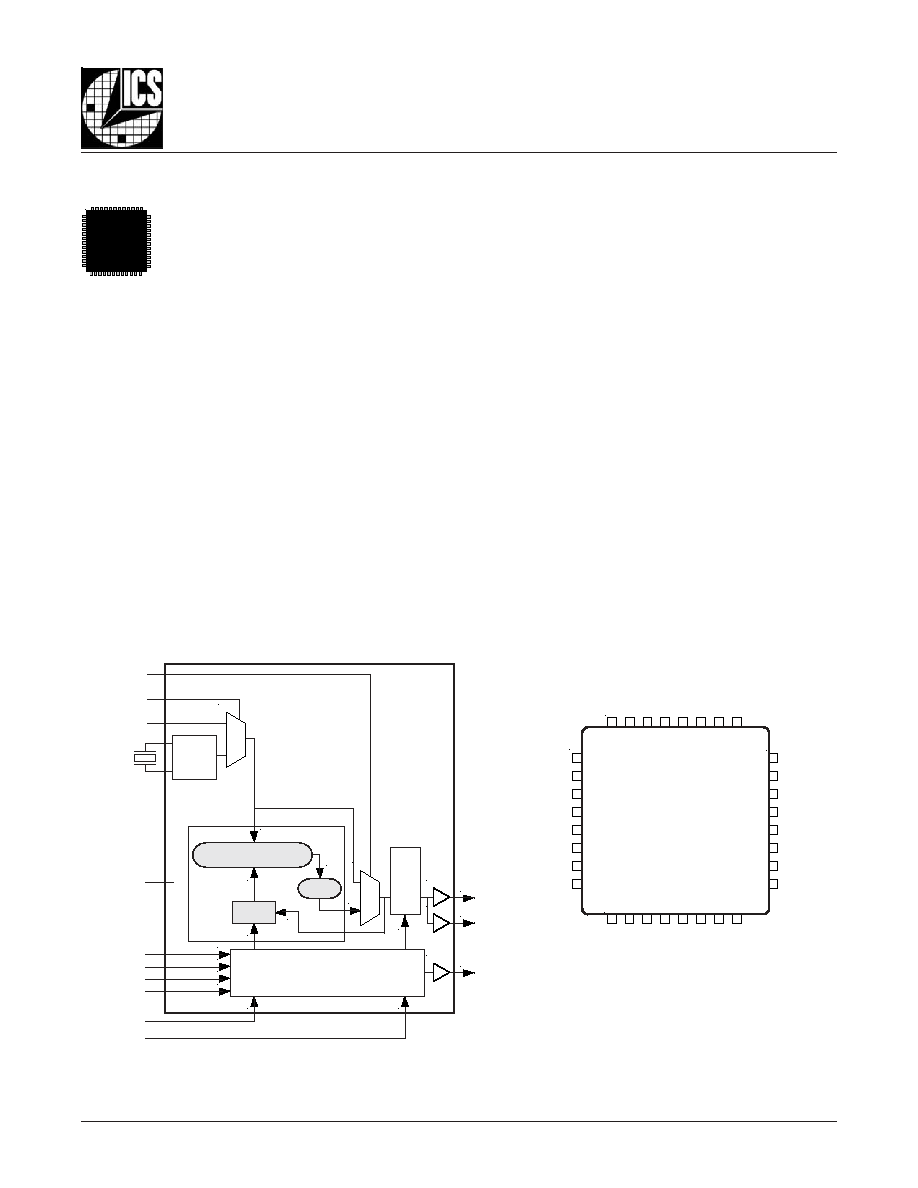

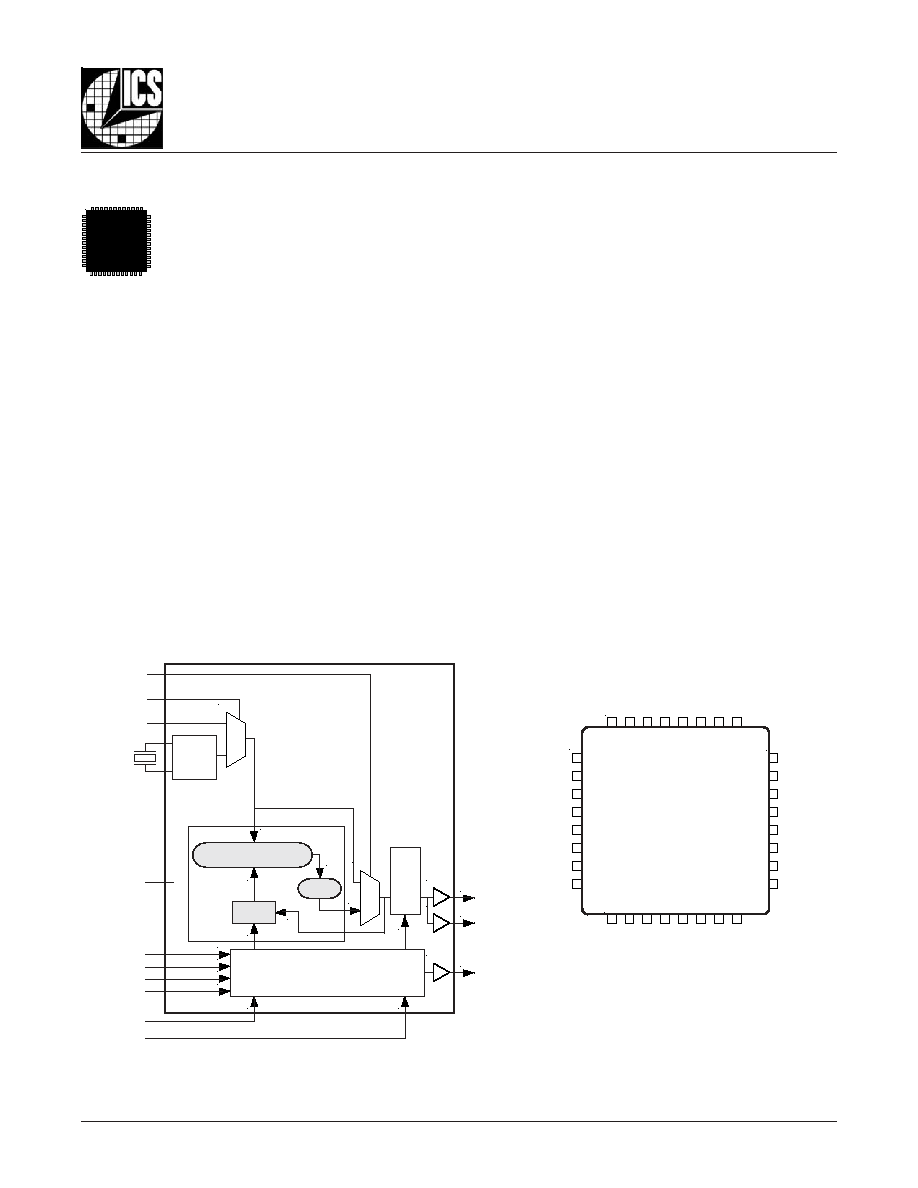

B

LOCK

D

IAGRAM

P

IN

A

SSIGNMENT

32 31 30 29 28 27 26 25

9 10 11 12 13 14 15 16

1

2

3

4

5

6

7

8

24

23

22

21

20

19

18

17

XTAL_OUT

TEST_CLK

XTAL_SEL

V

DDA

S_LOAD

S_DATA

S_CLOCK

MR

M5

M6

M7

M8

N 0

N 1

nc

GND

GND

nFOUT0

FOUT0

V

DD

nFOUT1

FOUT1

V

DD

TEST

X

T

AL_IN

nP_LOAD

VCO_SEL

M0

M1

M2

M3

M4

32-Lead LQFP

7mm x 7mm x 1.4mm package body

Y Package

Top View

ICS8442I

OSC

VCO_SEL

XTAL_SEL

TEST_CLK

XTAL_IN

XTAL_OUT

S_LOAD

S_DATA

S_CLOCK

nP_LOAD

M0:M8

N0:N1

VCO

PLL

FOUT0

nFOUT0

FOUT1

nFOUT1

TEST

CONFIGURATION

INTERFACE

LOGIC

÷ M

0

1

0

1

PHASE DETECTOR

÷ 1

÷ 2

÷ 4

÷ 8

MR

8442AYI

www.icst.com/products/hiperclocks.html

REV. C MAY 10, 2005

2

Integrated

Circuit

Systems, Inc.

ICS8442I

700MH

Z

, C

RYSTAL

O

SCILLATOR

-

TO

-D

IFFERENTIAL

LVDS F

REQUENCY

S

YNTHESIZER

cific default state that will automatically occur during power-

up. The TEST output is LOW when operating in the parallel

input mode. The relationship between the VCO frequency, the

crystal frequency and the M divider is defined as follows:

The M value and the required values of M0 through M8 are

shown in Table 3B, Programmable VCO Frequency Function

Table. Valid M values for which the PLL will achieve lock for a

25MHz reference are defined as 10

M 28. The frequency

out is defined as follows:

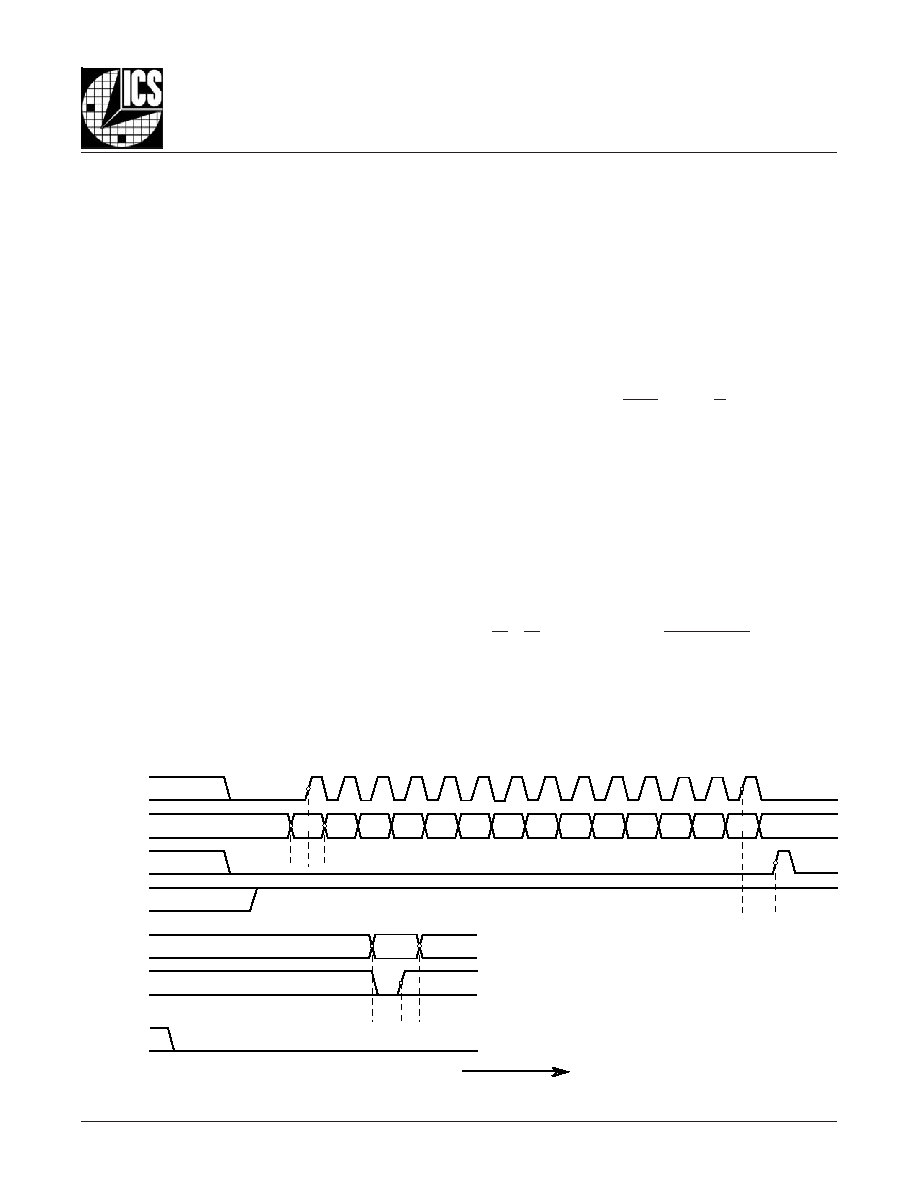

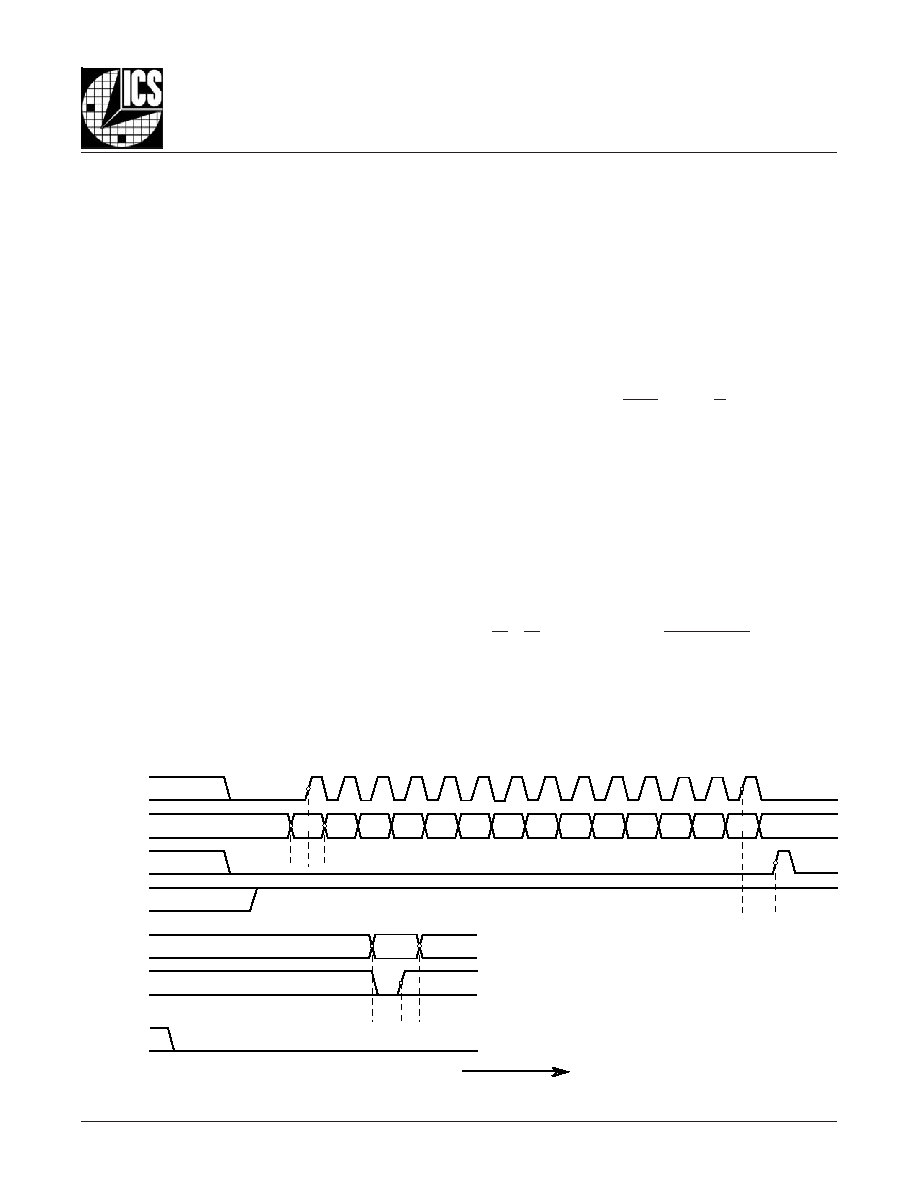

Serial operation occurs when nP_LOAD is HIGH and S_LOAD

is LOW. The shift register is loaded by sampling the S_DATA

bits with the rising edge of S_CLOCK. The contents of the

shift register are loaded into the M divider and N output di-

vider when S_LOAD transitions from LOW-to-HIGH. The M

divide and N output divide values are latched on the HIGH-to-

LOW transition of S_LOAD. If S_LOAD is held HIGH, data at

the S_DATA input is passed directly to the M divider and N

output divider on each rising edge of S_CLOCK. The serial

mode can be used to program the M and N bits and test bits

T1 and T0. The internal registers T0 and T1 determine the state

of the TEST output as follows:

NOTE: The functional description that follows describes op-

eration using a 25MHz crystal. Valid PLL loop divider values

for different crystal or input frequencies are defined in the In-

put Frequency Characteristics, Table 5, NOTE 1.

The ICS8442I features a fully integrated PLL and therefore

requires no external components for setting the loop band-

width. A fundamental crystal is used as the input to the on-

chip oscillator. The output of the oscillator is fed into the phase

detector. A 25MHz crystal provides a 25MHz phase detector

reference frequency. The VCO of the PLL operates over a

range of 250MHz to 700MHz. The output of the M divider is

also applied to the phase detector.

The phase detector and the M divider force the VCO output fre-

quency to be M times the reference frequency by adjusting the

VCO control voltage. Note that for some values of M (either too

high or too low), the PLL will not achieve lock. The output of the

VCO is scaled by a divider prior to being sent to each of the

LVDS output buffers. The divider provides a 50% output duty cycle.

The programmable features of the ICS8442I support two in-

put modes to program the M divider and N output divider. The

two input operational modes are parallel and serial. Figure 1

shows the timing diagram for each mode. In parallel mode,

the nP_LOAD input is initially LOW. The data on inputs M0

through M8 and N0 and N1 is passed directly to the M divider

and N output divider. On the LOW-to-HIGH transition of the

nP_LOAD input, the data is latched and the M divider remains

loaded until the next LOW transition on nP_LOAD or until a

serial event occurs. As a result, the M and N bits can be

hardwired to set the M divider and N output divider to a spe-

F

UNCTIONAL

D

ESCRIPTION

fVCO = fxtal x M

T1

T0

TEST Output

0

0

LOW

0

1

S_Data, Shift Register Input

1

0

Output of M divider

1

1

CMOS FOUT

FOUT = fVCO = fxtal x M

N

N

F

IGURE

1. P

ARALLEL

& S

ERIAL

L

OAD

O

PERATIONS

Time

S

ERIAL

L

OADING

P

ARALLEL

L

OADING

t

S

t

H

t

S

t

H

t

S

M, N

S_CLOCK

S_DATA

S_LOAD

nP_LOAD

M0:M8, N0:N1

nP_LOAD

S_LOAD

*NOTE: The NULL timing slot must be observed.

T1

T0

*NULL

N1

N0

M8

M7

M6

M5

M4

M3

M2

M1

M0

8442AYI

www.icst.com/products/hiperclocks.html

REV. C MAY 10, 2005

5

Integrated

Circuit

Systems, Inc.

ICS8442I

700MH

Z

, C

RYSTAL

O

SCILLATOR

-

TO

-D

IFFERENTIAL

LVDS F

REQUENCY

S

YNTHESIZER

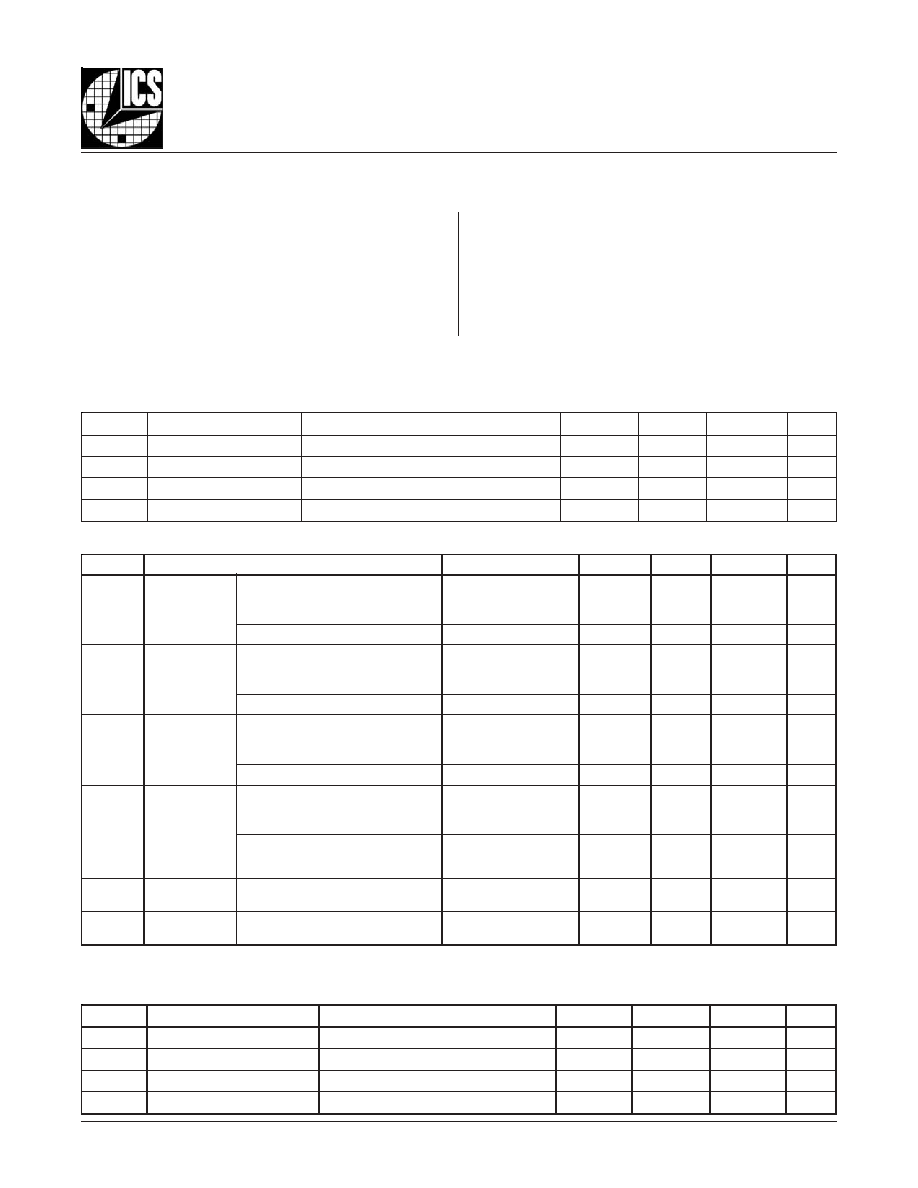

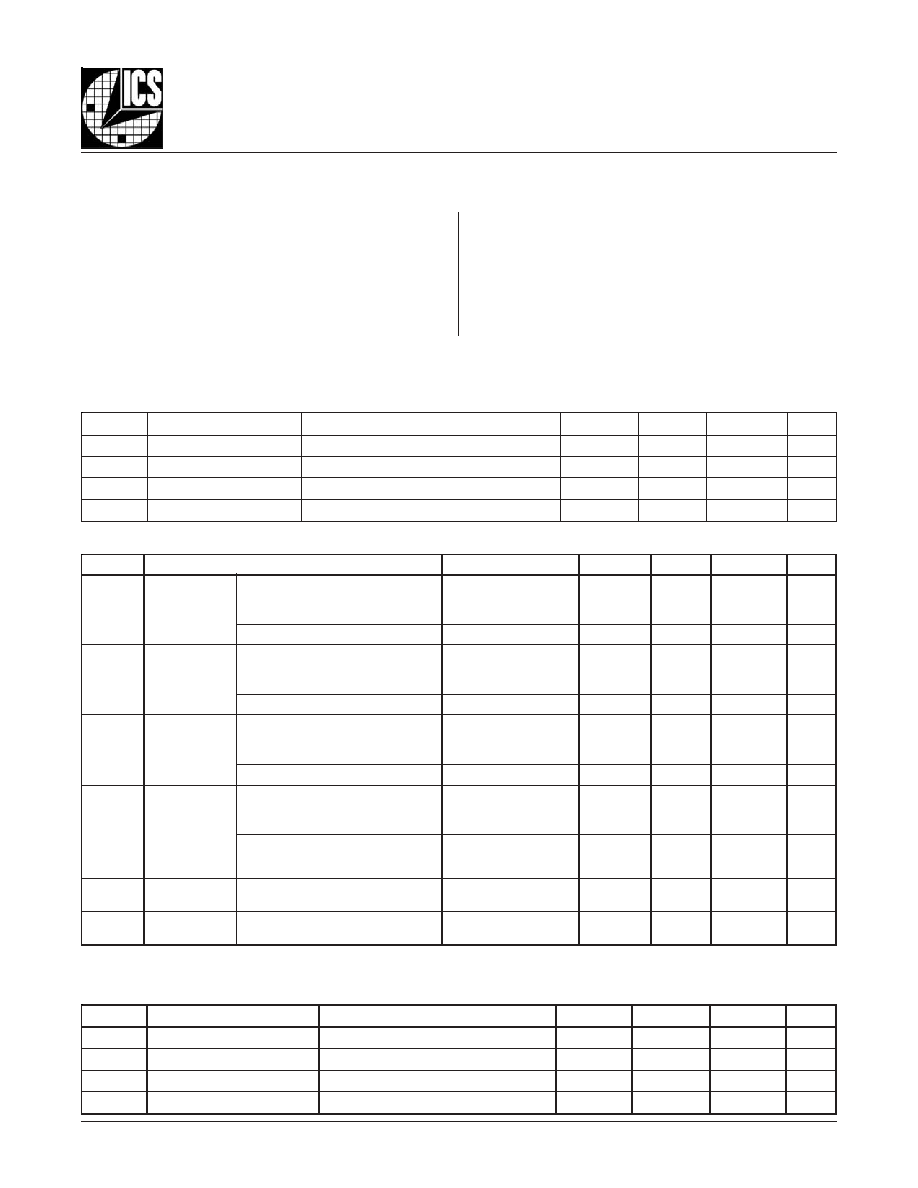

A

BSOLUTE

M

AXIMUM

R

ATINGS

Supply Voltage, V

DD

4.6V

Inputs, V

I

-0.5V to V

DD

+ 0.5 V

Outputs, V

O

-0.5V to V

DD

+ 0.5V

Package Thermal Impedance,

JA

47.9°C/W (0 lfpm)

Storage Temperature, T

STG

-65°C to 150°C

NOTE: Stresses beyond those listed under Absolute

Maximum Ratings may cause permanent damage to the

device. These ratings are stress specifications only. Functional

operation of product at these conditions or any conditions be-

yond those listed in the

DC Characteristics or AC Character-

istics is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect product reliability.

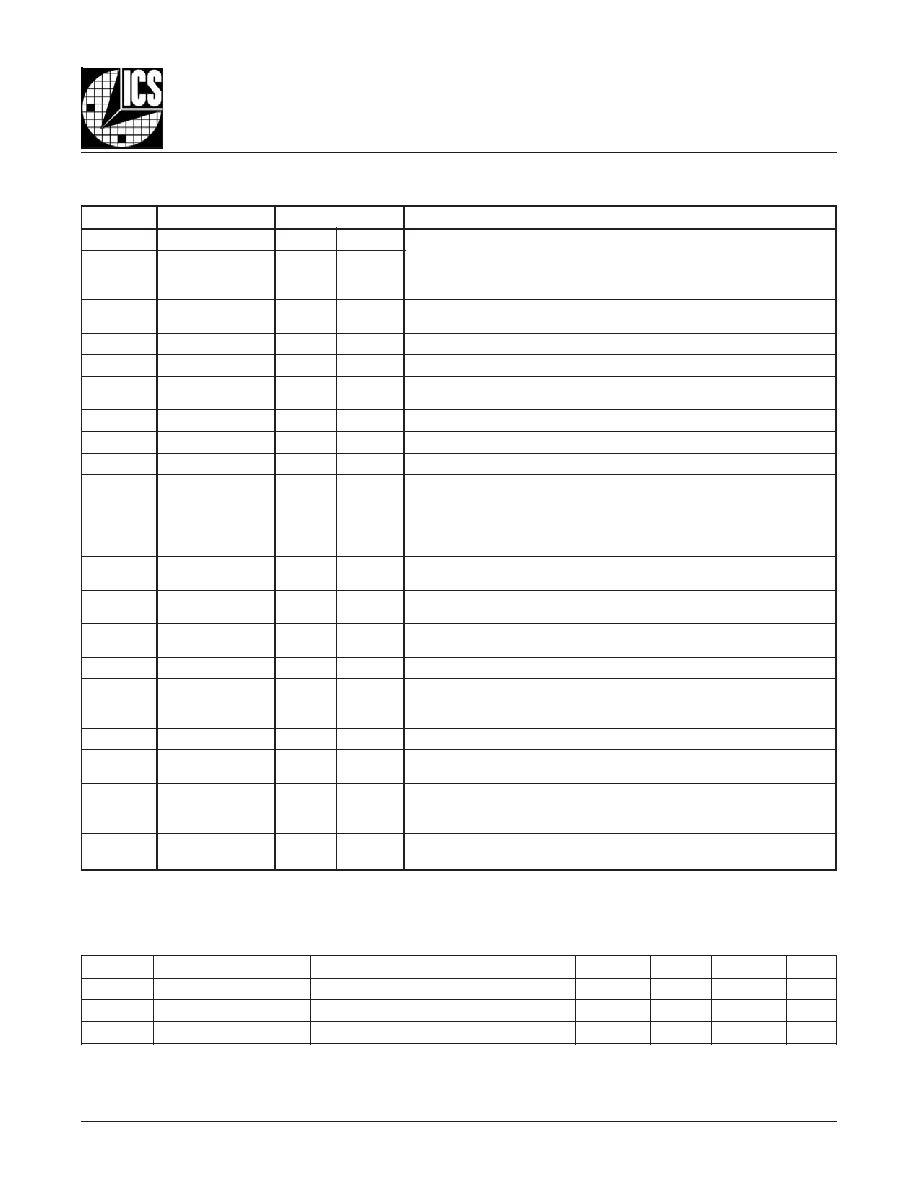

T

ABLE

4A. P

OWER

S

UPPLY

DC C

HARACTERISTICS

,

V

DD

= V

DDA

= 3.3V±5%, T

A

=

-40°C

TO

85°C

T

ABLE

4B. LVCMOS / LVTTL DC C

HARACTERISTICS

,

V

DD

= V

DDA

= 3.3V±5%, T

A

=

-40°C

TO

85°C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

e

r

o

C

5

3

1

.

3

3

.

3

5

6

4

.

3

V

V

A

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

g

o

l

a

n

A

5

3

1

.

3

3

.

3

5

6

4

.

3

V

I

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

r

e

w

o

P

5

5

1

A

m

I

A

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

g

o

l

a

n

A

0

2

A

m

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

H

I

t

u

p

n

I

e

g

a

t

l

o

V

h

g

i

H

,

D

A

O

L

_

P

n

,

R

M

,

1

N

,

0

N

,

8

M

-

0

M

,

D

A

O

L

_

S

,

A

T

A

D

_

S

,

K

C

O

L

C

_

S

L

E

S

_

O

C

V

,

L

E

S

_

L

A

T

X

2

V

D

D

3

.

0

+

V

K

L

C

_

T

S

E

T

2

V

D

D

3

.

0

+

V

V

L

I

t

u

p

n

I

e

g

a

t

l

o

V

w

o

L

,

D

A

O

L

_

P

n

,

R

M

,

1

N

,

0

N

,

8

M

-

0

M

,

D

A

O

L

_

S

,

A

T

A

D

_

S

,

K

C

O

L

C

_

S

L

E

S

_

O

C

V

,

L

E

S

_

L

A

T

X

3

.

0

-

8

.

0

V

K

L

C

_

T

S

E

T

3

.

0

-

3

.

1

V

I

H

I

t

u

p

n

I

t

n

e

r

r

u

C

h

g

i

H

,

R

M

,

1

N

,

0

N

,

8

M

-

6

M

,

4

M

-

0

M

,

A

T

A

D

_

S

,

K

C

O

L

C

_

S

,

D

A

O

L

_

P

n

,

D

A

O

L

_

S

V

D

D

V

=

N

I

V

5

6

4

.

3

=

0

5

1

A

µ

L

E

S

_

O

C

V

,

L

E

S

_

L

A

T

X

,

5

M

V

D

D

V

=

N

I

V

5

6

4

.

3

=

5

I

L

I

t

u

p

n

I

t

n

e

r

r

u

C

w

o

L

,

R

M

,

1

N

,

0

N

,

8

M

-

6

M

,

4

M

-

0

M

,

A

T

A

D

_

S

,

K

C

O

L

C

_

S

,

D

A

O

L

_

P

n

,

D

A

O

L

_

S

V

D

D

,

V

5

6

4

.

3

=

V

N

I

V

0

=

5

-

A

µ

L

E

S

_

O

C

V

,

L

E

S

_

L

A

T

X

,

5

M

V

D

D

,

V

5

6

4

.

3

=

V

N

I

V

0

=

0

5

1

-

V

H

O

t

u

p

t

u

O

e

g

a

t

l

o

V

h

g

i

H

1

E

T

O

N

;

T

S

E

T

6

.

2

V

V

L

O

t

u

p

t

u

O

e

g

a

t

l

o

V

w

o

L

1

E

T

O

N

;

T

S

E

T

5

.

0

V

0

5

h

t

i

w

d

e

t

a

n

i

m

r

e

t

s

t

u

p

t

u

O

:

1

E

T

O

N

V

o

t

D

D

,

n

o

i

t

c

e

s

n

o

i

t

a

m

r

o

f

n

I

t

n

e

m

e

r

u

s

a

e

M

r

e

t

e

m

a

r

a

P

e

e

S

.

2

/

.

"

t

i

u

c

r

i

C

t

s

e

T

d

a

o

L

t

u

p

t

u

O

V

3

.

3

"

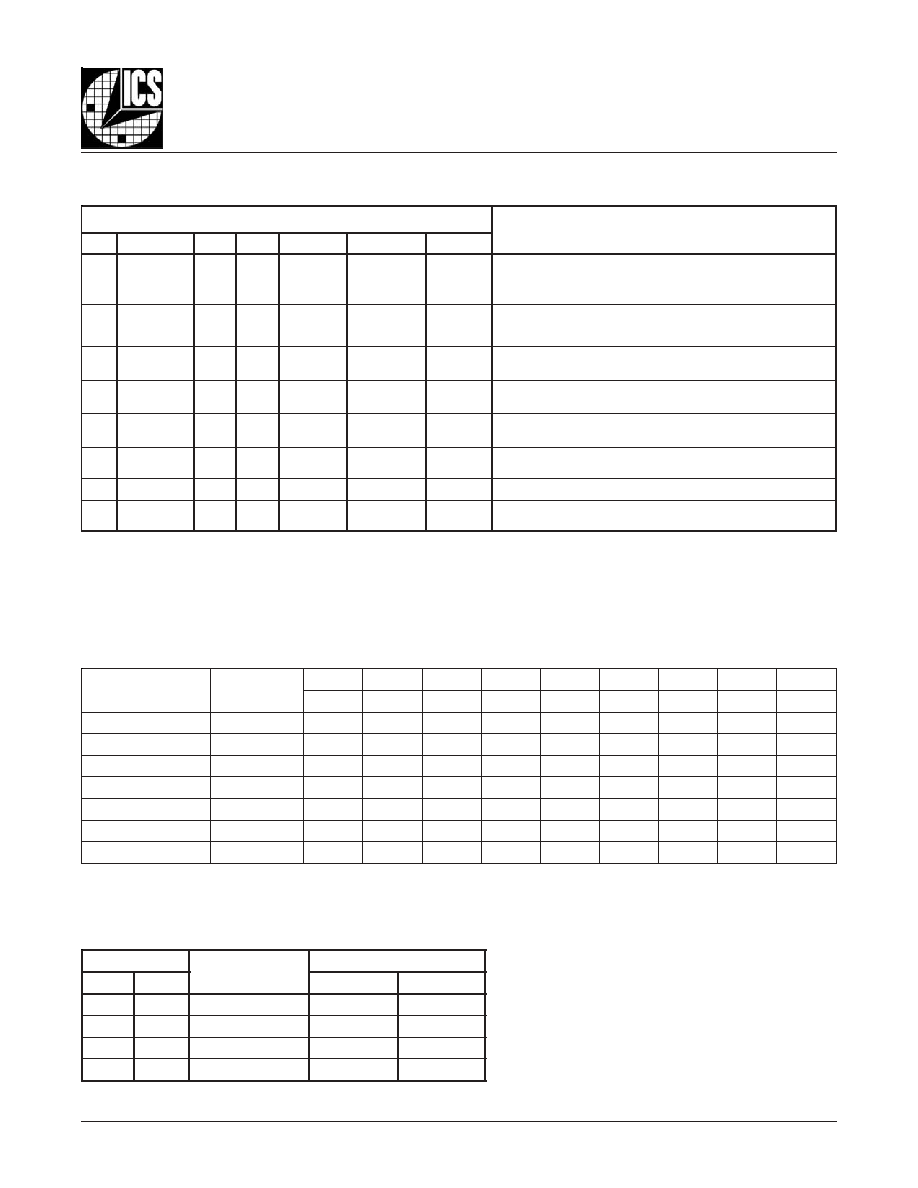

T

ABLE

4C. LVDS DC C

HARACTERISTICS

,

V

DD

= V

DDA

= 3.3V±5%, T

A

=

-40°C

TO

85°C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

D

O

e

g

a

t

l

o

V

t

u

p

t

u

O

l

a

i

t

n

e

r

e

f

f

i

D

0

5

2

0

5

4

0

0

6

V

m

V

D

O

V

D

O

e

g

n

a

h

C

e

d

u

t

i

n

g

a

M

0

5

V

m

V

S

O

e

g

a

t

l

o

V

t

e

s

f

f

O

5

2

1

.

1

4

.

1

6

.

1

V

V

S

O

V

S

O

e

g

n

a

h

C

e

d

u

t

i

n

g

a

M

0

5

V

m