Document Outline

- General Description

- Features

- Block Diagram

- Pin Assignment

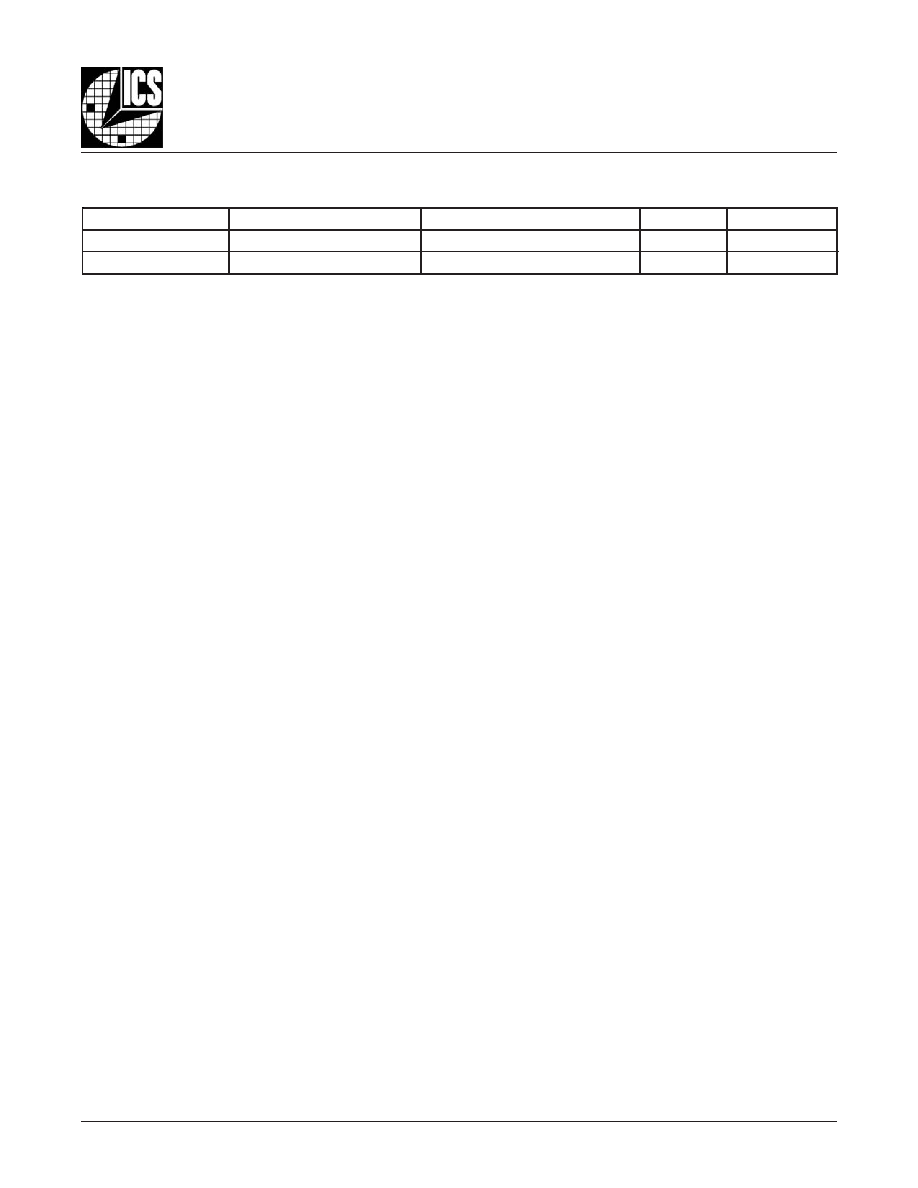

- Pin Descriptions

- Pin Characteristics

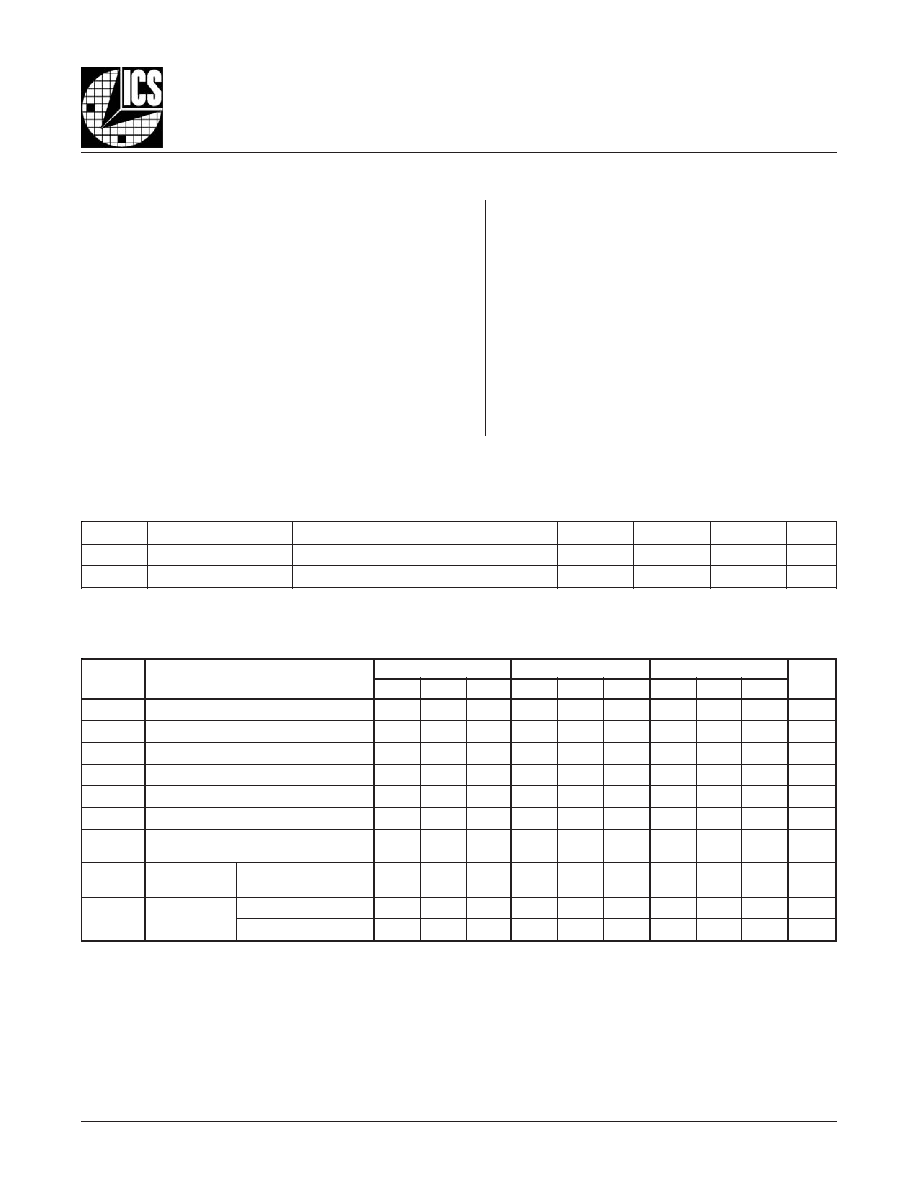

- Clock Input Function Table

- Absolute Maximum Ratings

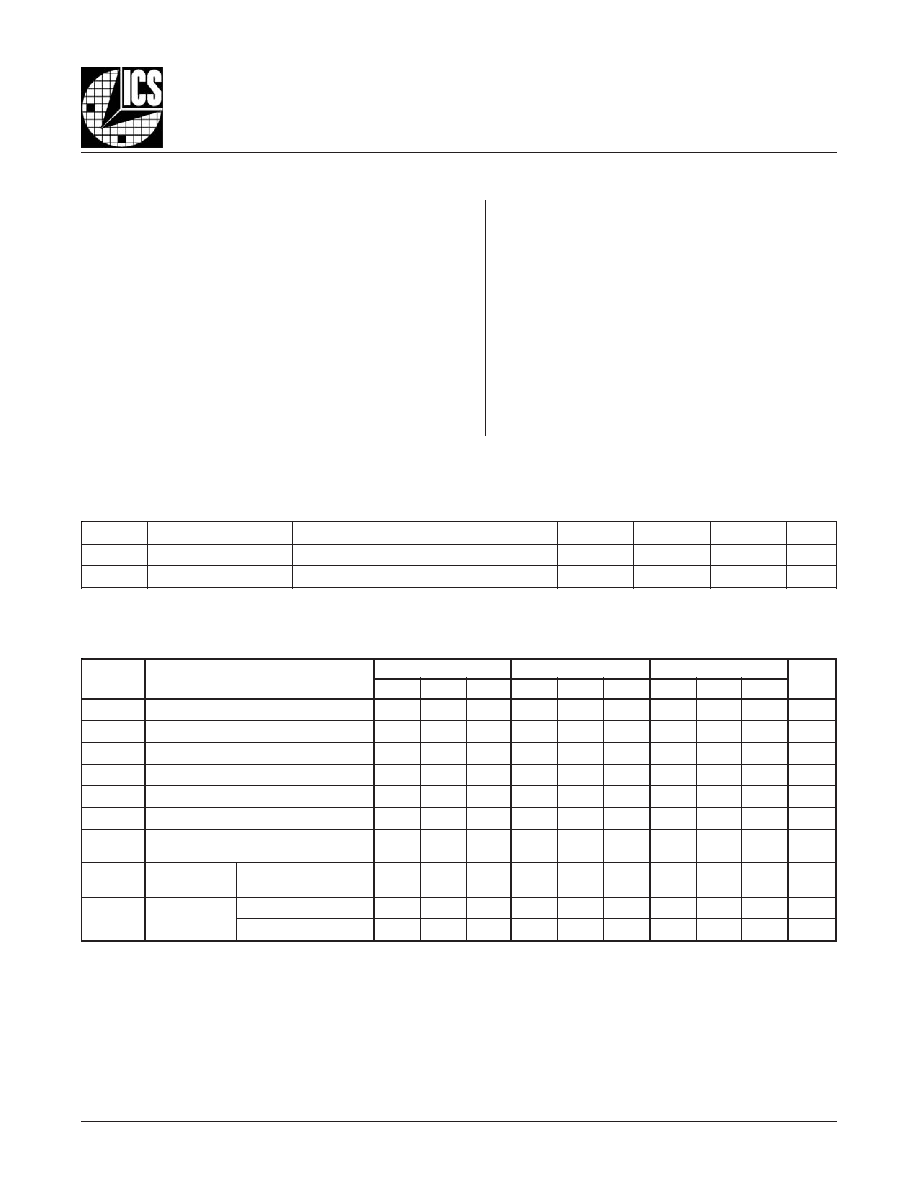

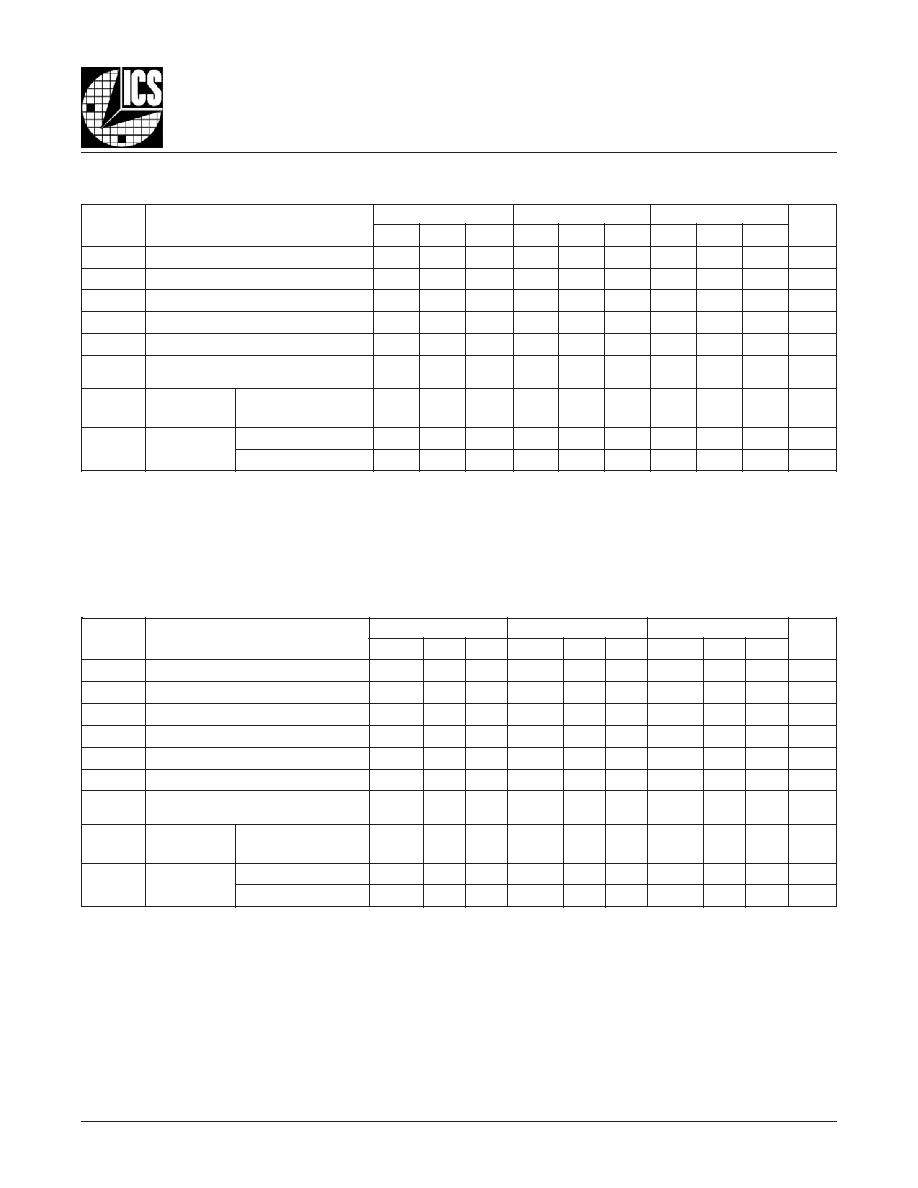

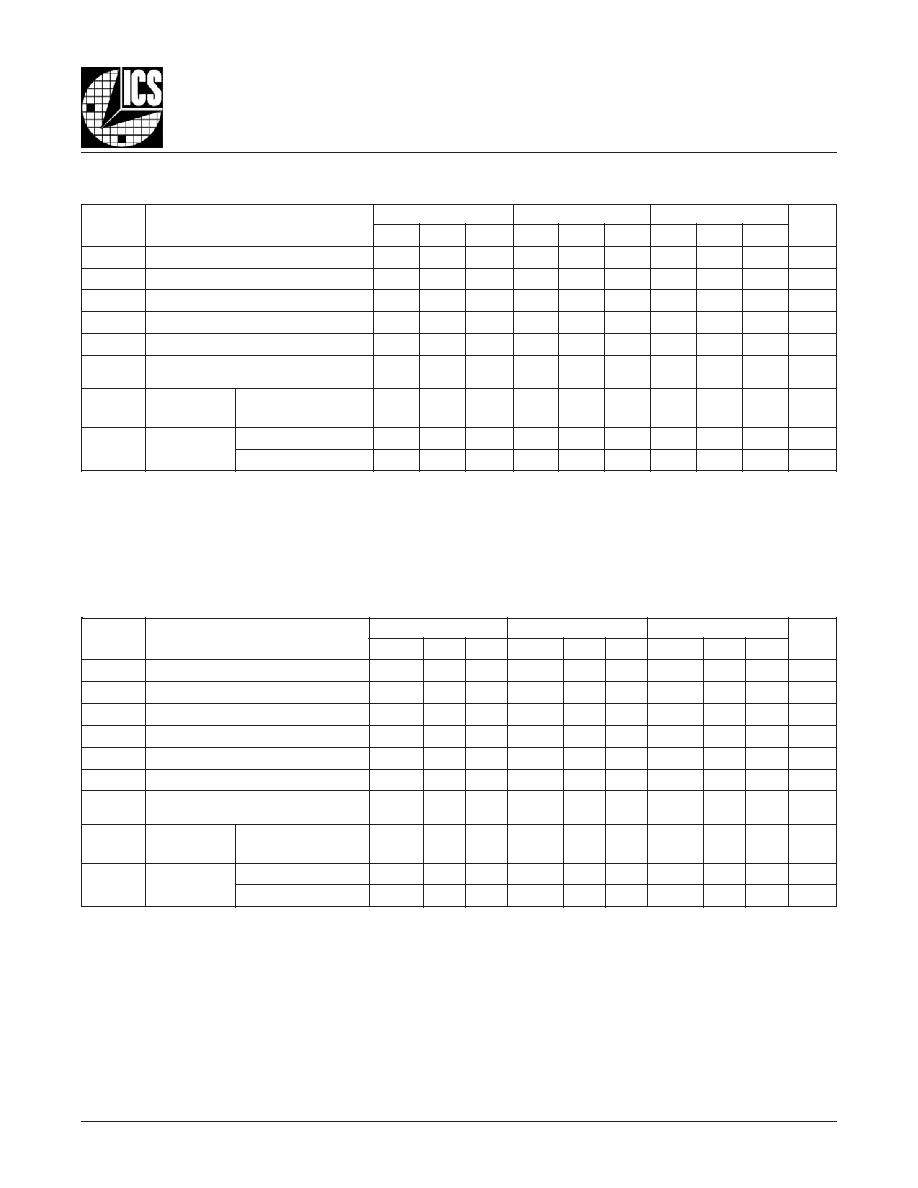

- Power Supply DC Characteristics

- LVPECL 3.3V DC Characteristics

- LVPECL 2.5V DC Characteristics

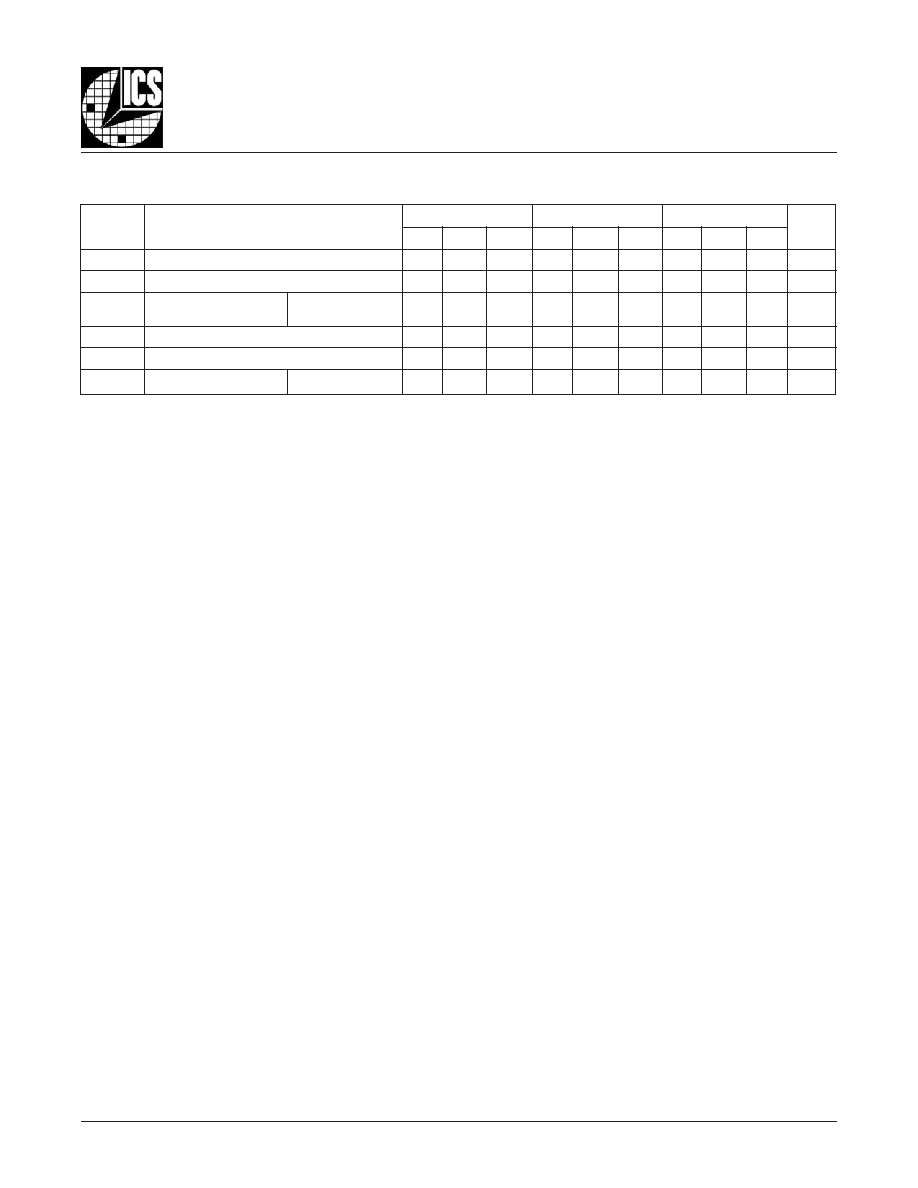

- ECL DC Characteristics

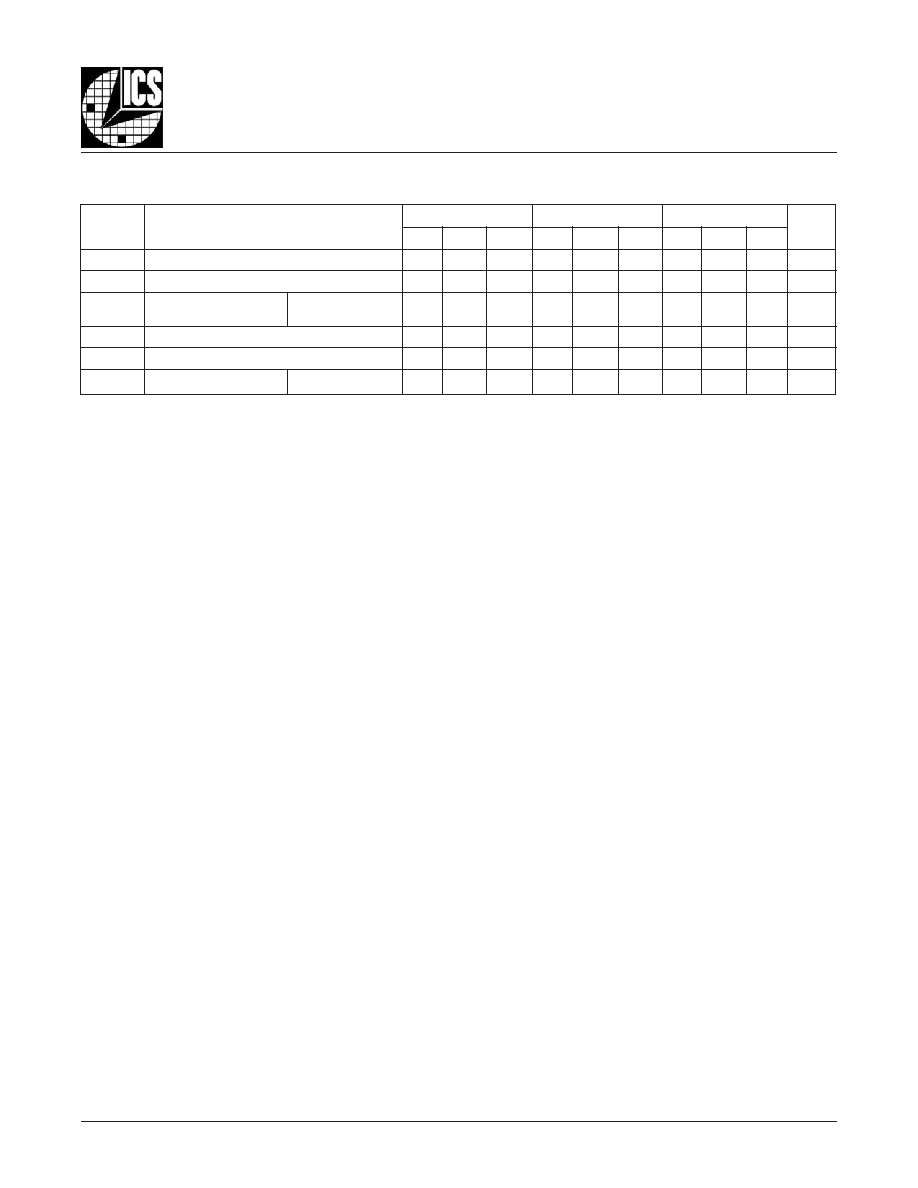

- AC Characteristics

- Parameter Measurement Information

- Output Load AC Test Circuit Diagram

- Differential Input Level Diagram

- Part-to-Part Skew Diagram

- Output Skew Diagram

- Output Rise/Fall Time Diagram

- Propagation Delay Diagram

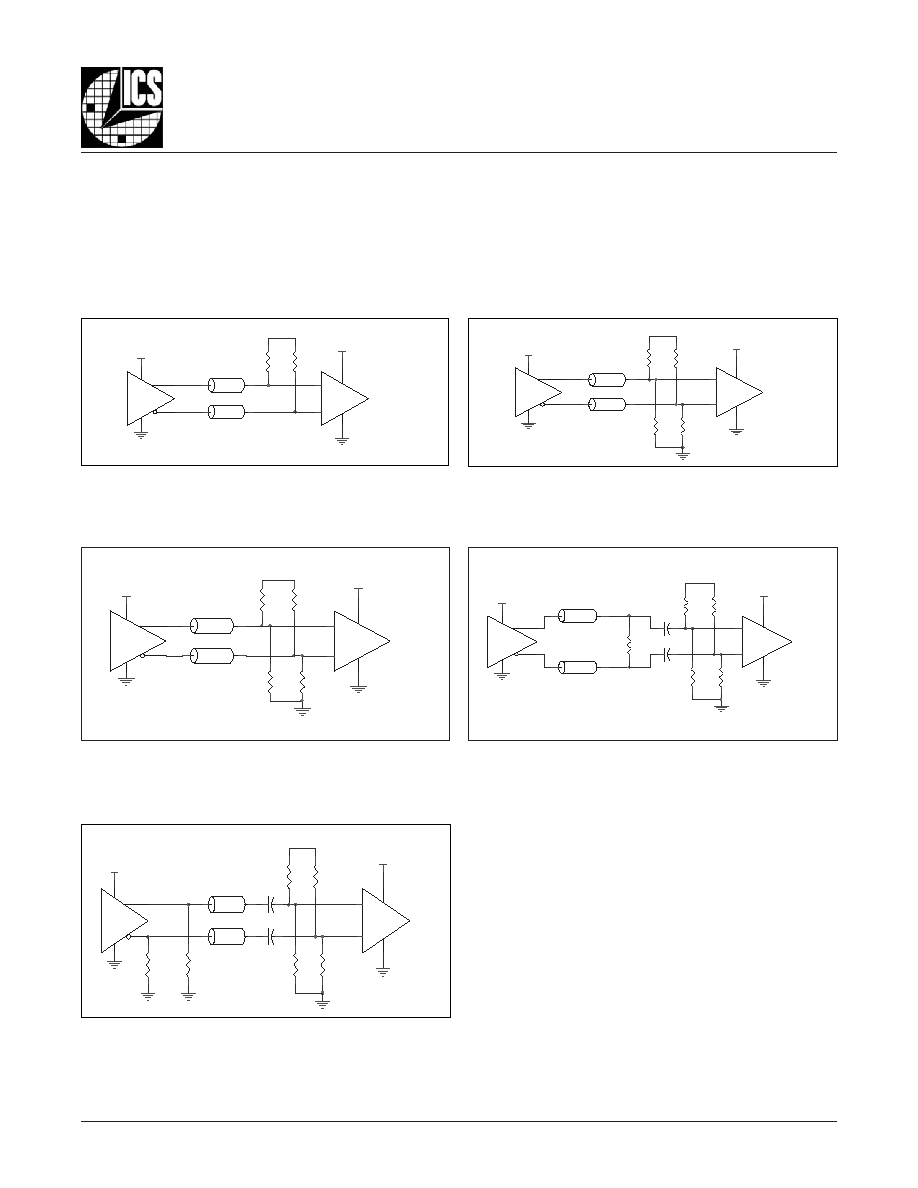

- Application Information

- Wiring the Differential Input to Accept Single Ended LVPECL Levels

- Wiring the Differential Input to Accept Single Ended Levels

- Termination for 3.3V LVPECL Outputs

- Termination for 2.5V LVPECL Outputs

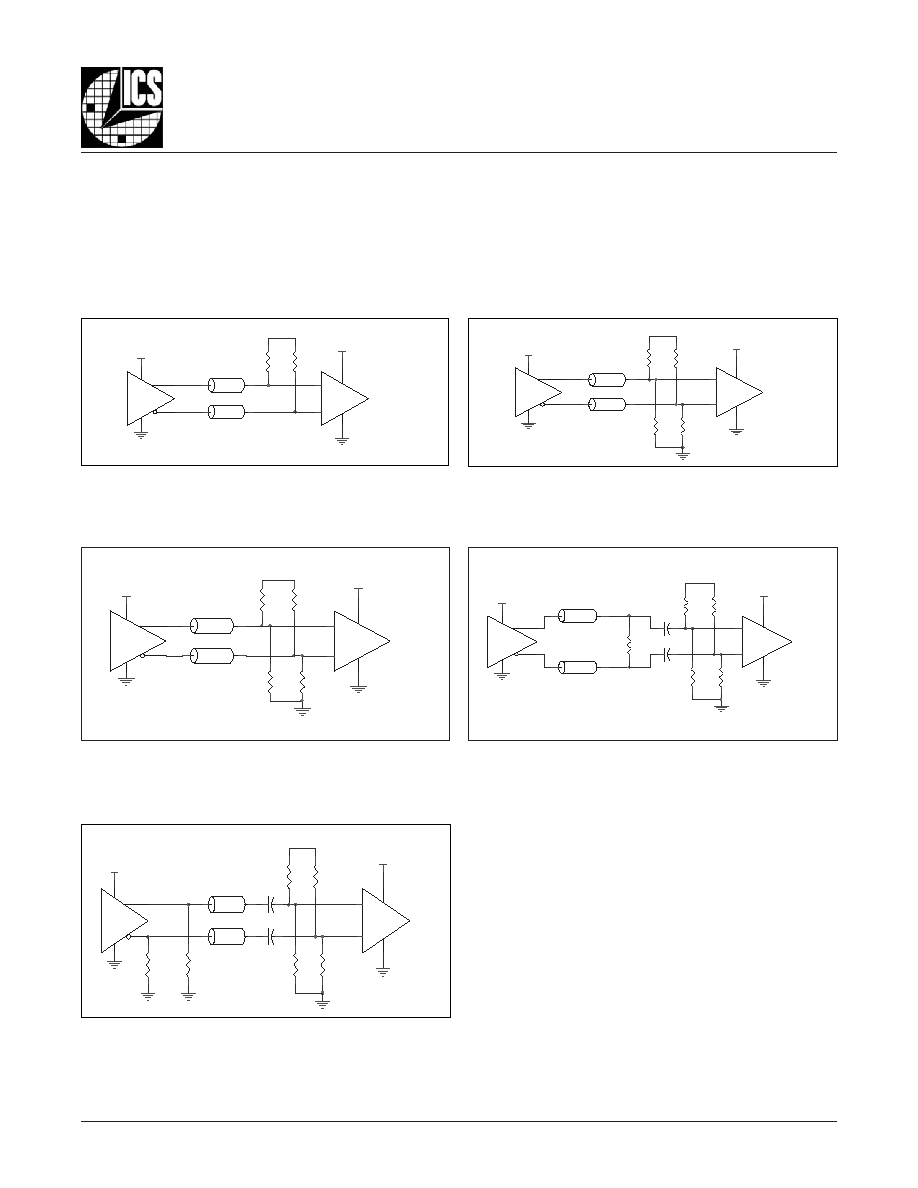

- LVPECL Clock Input Interface

- HiPerClockS PCLK/nPCLK Input Driven by a CML Driver Diagram

- HiPerClockS PCLK/nPCLK Input Driven by an SSTL Driver Diagram

- HiPerClockS PCLK/nPCLK Input Driven by a 3.3V LVPECL Driver Diagram

- HiPerClockS PCLK/nPCLK Input Driven by a 3.3V LVDS Driver Diagram

- HiPerClockS PCLK/nPCLK Input Driven by a 3.3V LVPECL Driver w/AC Couple Diagram

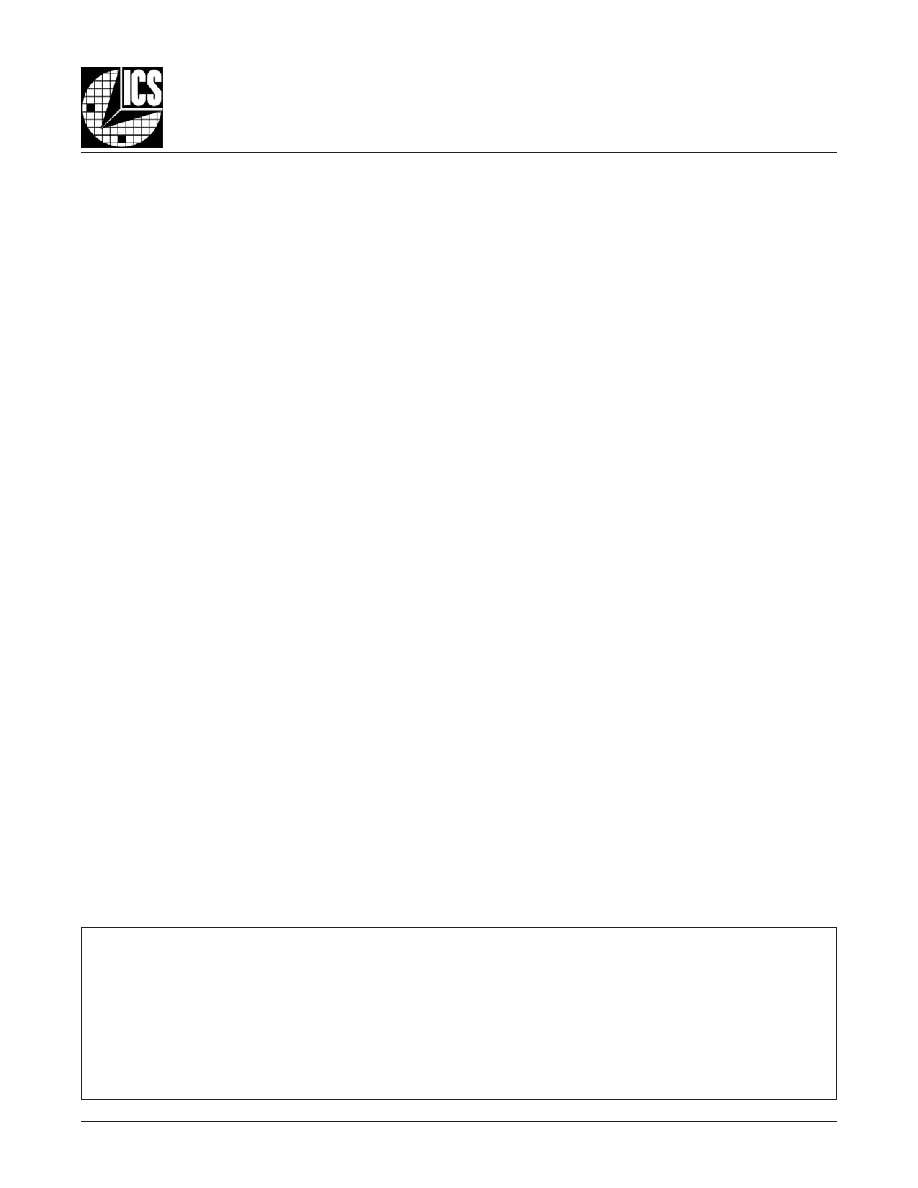

- Power Considerations

- LVPECL Driver Circuit & Termination Diagram

- Calculations & Equations

- Thermal Resistance

- Junction Temperature

- Power Dissipation

- Reliability Information

- Transistor Count

- Package Outline

- Package Dimensions

- Ordering Information

853210AY

www.icst.com/products/hiperclocks.html

REV. A NOVEMBER 12, 2003

1

Integrated

Circuit

Systems, Inc.

ICS853210

L

OW

S

KEW

, D

UAL

, 1-

TO

-5

D

IFFERENTIAL

-

TO

-2.5V/3.3V LVPECL/ECL F

ANOUT

B

UFFER

G

ENERAL

D

ESCRIPTION

The ICS853210 is a low skew, high perfor-

mance dual 1 - t o - 5 Differential-to-2.5V/3.3V

LVPECL/ECL Fanout Buffer and a member of

the HiPerClockSTM family of High Performance

Clock Solutions from ICS. The ICS853210

is characterized to operate from either a 2.5V or a 3.3V

power supply. Guaranteed output and par t-to-par t skew

characteristics make the ICS853210 ideal for those clock

distribution applications demanding well defined perfor-

mance and repeatability.

F

EATURES

∑ 2 differential 2.5V/3.3V LVPECL / ECL bank outputs

∑ 2 differential clock input pairs

∑ PCLKx, nPCLKx pairs can accept the following

differential input levels: LVPECL, LVDS, CML, SSTL

∑ Maximum output frequency: >3GHz

∑ Translates any single ended input signal to 3.3V

LVPECL levels with resistor bias on nPCLKx input

∑ Output skew: 13ps (typical)

∑ Part-to-part skew: 85ps (typical)

∑ Propagation delay: 485ps (typical)

∑ LVPECL mode operating voltage supply range:

V

CC

= 2.375V to 3.8V, V

EE

= 0V

∑ ECL mode operating voltage supply range:

V

CC

= 0V, V

EE

= -2.375V to -3.8V

∑ -40∞C to 85∞C ambient operating temperature

∑ Pin compatible with MC100EP210 and MC100LVEP210

B

LOCK

D

IAGRAM

P

IN

A

SSIGNMENT

HiPerClockSTM

ICS

32-Lead LQFP

7mm x 7mm x 1.4mm package body

Y Package

Top View

QA0

nQA0

QA1

nQA1

QA2

nQA2

QA3

nQA3

QA4

nQA4

PCLKA

nPCLKA

QB0

nQB0

QB1

nQB1

QB2

nQB2

QB3

nQB3

QB4

nQB4

PCLKB

nPCLKB

ICS853210

24 23 22 21 20 19 18 17

1 2 3 4 5 6 7 8

25

26

27

28

29

30

31

32

16

15

14

13

12

11

10

9

QA3

nQA3

QA4

nQA4

QB0

nQB0

QB1

nQB1

V

CCO

QB2

nQB2

QB3

nQB3

QB4

nQB4

V

CCO

V

CCO

nQA2

QA2

nQA1

QA1

nQA0

QA0

V

CCO

V

CC

nc

PCLKA

nPCLKA

VBB

PCLKB

nPCLK

B

V

EE

V

BB

853210AY

www.icst.com/products/hiperclocks.html

REV. A NOVEMBER 12, 2003

2

Integrated

Circuit

Systems, Inc.

ICS853210

L

OW

S

KEW

, D

UAL

, 1-

TO

-5

D

IFFERENTIAL

-

TO

-2.5V/3.3V LVPECL/ECL F

ANOUT

B

UFFER

T

ABLE

1. P

IN

D

ESCRIPTIONS

T

ABLE

2. P

IN

C

HARACTERISTICS

r

e

b

m

u

N

e

m

a

N

e

p

y

T

n

o

i

t

p

i

r

c

s

e

D

1

V

C

C

r

e

w

o

P

.

n

i

p

y

l

p

p

u

s

e

r

o

C

2

c

n

d

e

s

u

n

U

.

t

c

e

n

n

o

c

o

N

3

A

K

L

C

P

t

u

p

n

I

n

w

o

d

ll

u

P

.

t

u

p

n

i

k

c

o

l

c

l

a

i

t

n

e

r

e

f

f

i

d

g

n

i

t

r

e

v

n

i

-

n

o

N

4

A

K

L

C

P

n

t

u

p

n

I

/

p

u

ll

u

P

n

w

o

d

ll

u

P

V

.

t

u

p

n

i

k

c

o

l

C

C

C

.

g

n

i

t

a

o

l

f

t

f

e

l

n

e

h

w

t

l

u

a

f

e

d

2

/

5

V

B

B

t

u

p

t

u

O

.

e

g

a

t

l

o

v

s

a

i

B

6

B

K

L

C

P

t

u

p

n

I

n

w

o

d

ll

u

P

.

t

u

p

n

i

k

c

o

l

c

l

a

i

t

n

e

r

e

f

f

i

d

g

n

i

t

r

e

v

n

i

-

n

o

N

7

B

K

L

C

P

n

t

u

p

n

I

/

p

u

ll

u

P

n

w

o

d

ll

u

P

V

.

t

u

p

n

i

k

c

o

l

C

C

C

.

g

n

i

t

a

o

l

f

t

f

e

l

n

e

h

w

t

l

u

a

f

e

d

2

/

8

V

E

E

r

e

w

o

P

.

n

i

p

y

l

p

p

u

s

e

v

i

t

a

g

e

N

2

3

,

5

2

,

9

V

O

C

C

r

e

w

o

P

.

s

n

i

p

y

l

p

p

u

s

t

u

p

t

u

O

1

1

,

0

1

4

B

Q

,

4

B

Q

n

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

C

E

P

V

L

.

r

i

a

p

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

D

3

1

,

2

1

3

B

Q

,

3

B

Q

n

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

C

E

P

V

L

.

r

i

a

p

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

D

5

1

,

4

1

2

B

Q

,

2

B

Q

n

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

C

E

P

V

L

.

r

i

a

p

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

D

8

1

,

7

1

1

B

Q

,

1

B

Q

n

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

C

E

P

V

L

.

r

i

a

p

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

D

0

2

,

9

1

0

B

Q

,

0

B

Q

n

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

C

E

P

V

L

.

r

i

a

p

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

D

2

2

,

1

2

4

A

Q

,

4

A

Q

n

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

C

E

P

V

L

.

r

i

a

p

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

D

4

2

,

3

2

3

A

Q

,

3

A

Q

n

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

C

E

P

V

L

.

r

i

a

p

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

D

7

2

,

6

2

2

A

Q

,

2

A

Q

n

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

C

E

P

V

L

.

r

i

a

p

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

D

9

2

,

8

2

1

A

Q

,

1

A

Q

n

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

C

E

P

V

L

.

r

i

a

p

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

D

1

3

,

0

3

0

A

Q

,

0

A

Q

n

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

C

E

P

V

L

.

r

i

a

p

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

D

:

E

T

O

N

p

u

ll

u

P

d

n

a

n

w

o

d

ll

u

P

.

s

e

u

l

a

v

l

a

c

i

p

y

t

r

o

f

,

s

c

i

t

s

i

r

e

t

c

a

r

a

h

C

n

i

P

,

2

e

l

b

a

T

e

e

S

.

s

r

o

t

s

i

s

e

r

t

u

p

n

i

l

a

n

r

e

t

n

i

o

t

r

e

f

e

r

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

R

N

W

O

D

L

L

U

P

r

o

t

s

i

s

e

R

n

w

o

d

ll

u

P

t

u

p

n

I

5

7

K

R

2

/

C

C

V

s

r

o

t

s

i

s

e

R

n

w

o

d

ll

u

P

/

p

u

ll

u

P

0

5

K

T

ABLE

3. C

LOCK

I

NPUT

F

UNCTION

T

ABLE

s

t

u

p

n

I

s

t

u

p

t

u

O

e

d

o

M

t

u

p

t

u

O

o

t

t

u

p

n

I

y

t

i

r

a

l

o

P

r

o

A

K

L

C

P

B

K

L

C

P

r

o

A

K

L

C

P

n

B

K

L

C

P

n

,

4

A

Q

:

0

A

Q

4

B

Q

:

0

B

Q

,

4

A

Q

n

:

0

A

Q

n

4

B

Q

n

:

0

B

Q

n

0

1

W

O

L

H

G

I

H

l

a

i

t

n

e

r

e

f

f

i

D

o

t

l

a

i

t

n

e

r

e

f

f

i

D

g

n

i

t

r

e

v

n

I

n

o

N

1

0

H

G

I

H

W

O

L

l

a

i

t

n

e

r

e

f

f

i

D

o

t

l

a

i

t

n

e

r

e

f

f

i

D

g

n

i

t

r

e

v

n

I

n

o

N

0

1

E

T

O

N

;

d

e

s

a

i

B

W

O

L

H

G

I

H

l

a

i

t

n

e

r

e

f

f

i

D

o

t

d

e

d

n

E

e

l

g

n

i

S

g

n

i

t

r

e

v

n

I

n

o

N

1

1

E

T

O

N

;

d

e

s

a

i

B

H

G

I

H

W

O

L

l

a

i

t

n

e

r

e

f

f

i

D

o

t

d

e

d

n

E

e

l

g

n

i

S

g

n

i

t

r

e

v

n

I

n

o

N

1

E

T

O

N

;

d

e

s

a

i

B

0

H

G

I

H

W

O

L

l

a

i

t

n

e

r

e

f

f

i

D

o

t

d

e

d

n

E

e

l

g

n

i

S

g

n

i

t

r

e

v

n

I

1

E

T

O

N

;

d

e

s

a

i

B

1

W

O

L

H

G

I

H

l

a

i

t

n

e

r

e

f

f

i

D

o

t

d

e

d

n

E

e

l

g

n

i

S

g

n

i

t

r

e

v

n

I

.

"

s

l

e

v

e

L

d

e

d

n

E

e

l

g

n

i

S

t

p

e

c

c

A

o

t

t

u

p

n

I

l

a

i

t

n

e

r

e

f

f

i

D

e

h

t

g

n

i

r

i

W

"

,

n

o

i

t

a

m

r

o

f

n

I

n

o

i

t

a

c

il

p

p

A

e

h

t

o

t

r

e

f

e

r

e

s

a

e

l

P

:

1

E

T

O

N

853210AY

www.icst.com/products/hiperclocks.html

REV. A NOVEMBER 12, 2003

3

Integrated

Circuit

Systems, Inc.

ICS853210

L

OW

S

KEW

, D

UAL

, 1-

TO

-5

D

IFFERENTIAL

-

TO

-2.5V/3.3V LVPECL/ECL F

ANOUT

B

UFFER

T

ABLE

4A. P

OWER

S

UPPLY

DC C

HARACTERISTICS

,

V

CC

= 3.3V; V

EE

= 0V

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

C

C

e

g

a

t

l

o

V

y

l

p

p

u

S

e

r

o

C

5

7

3

.

2

3

.

3

8

.

3

V

I

E

E

t

n

e

r

r

u

C

y

l

p

p

u

S

r

e

w

o

P

0

8

A

m

T

ABLE

4B. LVPECL DC C

HARACTERISTICS

,

V

CC

= 3.3V; V

EE

= 0V

A

BSOLUTE

M

AXIMUM

R

ATINGS

NOTE: Stresses beyond those listed under Absolute

Maximum Ratings may cause permanent damage

to the device. These ratings are stress specifi-

cations only. Functional operation of product at

these conditions or any conditions beyond those

listed in the

DC Characteristics or AC Character-

istics is not implied. Exposure to absolute maxi-

mum rating conditions for extended periods may

affect product reliability.

Supply Voltage, V

CC

4.6V (LVPECL mode, V

EE

= 0)

Negative Supply Voltage, V

EE

-4.6V (ECL mode, V

CC

= 0)

Inputs, V

I

(LVPECL mode)

-0.5V to V

CC

+ 0.5V

Inputs, V

I

(ECL mode)

0.5V to V

EE

- 0.5V

Outputs, I

O

Continuous Current

50mA

Surge Current

100mA

V

BB

Sink/Source, I

BB

± 0.5mA

Operating Temperature Range, TA -40∞C to +85∞C

Storage Temperature, T

STG

-65∞C to 150∞C

Package Thermal Impedance,

JA

47.9∞C/W (0 lfpm)

(Junction-to-Ambient)

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

C

∞

0

4

-

C

∞

5

2

C

∞

5

8

s

t

i

n

U

n

i

M

p

y

T

x

a

M

n

i

M

p

y

T

x

a

M

n

i

M

p

y

T

x

a

M

V

H

O

1

E

T

O

N

;

e

g

a

t

l

o

V

h

g

i

H

t

u

p

t

u

O

5

7

1

.

2

5

7

2

.

2

8

3

.

2

5

2

2

.

2

5

9

2

.

2

7

3

.

2

5

9

2

.

2

3

3

.

2

5

6

3

.

2

V

V

L

O

1

E

T

O

N

;

e

g

a

t

l

o

V

w

o

L

t

u

p

t

u

O

5

0

4

.

1

5

4

5

.

1

8

6

.

1

5

2

4

.

1

2

5

.

1

5

1

6

.

1

4

4

.

1

5

3

5

.

1

3

6

.

1

V

V

H

I

e

g

a

t

l

o

V

h

g

i

H

t

u

p

n

I

)

d

e

d

n

E

-

e

l

g

n

i

S

(

5

7

0

.

2

6

3

.

2

5

7

0

.

2

6

3

.

2

5

7

0

.

2

6

3

.

2

V

V

L

I

e

g

a

t

l

o

V

w

o

L

t

u

p

n

I

)

d

e

d

n

E

-

e

l

g

n

i

S

(

3

4

.

1

5

6

7

.

1

3

4

.

1

5

6

7

.

1

3

4

.

1

5

6

7

.

1

V

V

B

B

2

E

T

O

N

;

e

c

n

e

r

e

f

e

R

e

g

a

t

l

o

V

t

u

p

t

u

O

6

8

.

1

8

9

.

1

6

8

.

1

8

9

.

1

6

8

.

1

8

9

.

1

V

V

P

P

e

g

a

t

l

o

V

t

u

p

n

I

k

a

e

P

-

o

t

-

k

a

e

P

0

5

1

0

0

8

0

0

2

1

0

5

1

0

0

8

0

0

2

1

0

5

1

0

0

8

0

0

2

1

m

V

V

R

M

C

e

g

a

t

l

o

V

h

g

i

H

t

u

p

n

I

4

,

3

E

T

O

N

;

e

g

n

a

R

e

d

o

M

n

o

m

m

o

C

2

.

1

3

.

3

2

.

1

3

.

3

2

.

1

3

.

3

V

I

H

I

t

u

p

n

I

t

n

e

r

r

u

C

h

g

i

H

1

K

L

C

P

,

0

K

L

C

P

1

K

L

C

P

n

,

0

K

L

C

P

n

0

5

1

0

5

1

0

5

1

A

µ

I

L

I

t

u

p

n

I

t

n

e

r

r

u

C

w

o

L

1

K

L

C

P

,

0

K

L

C

P

0

1

-

0

1

-

0

1

-

A

µ

1

K

L

C

P

n

,

0

K

L

C

P

n

0

5

1

-

0

5

1

-

0

5

1

-

A

µ

V

h

t

i

w

1

:

1

y

r

a

v

s

r

e

t

e

m

a

r

a

p

t

u

p

t

u

o

d

n

a

t

u

p

n

I

C

C

V

.

E

E

.

V

5

.

0

-

o

t

V

5

2

9

.

0

+

y

r

a

v

n

a

c

0

5

h

t

i

w

d

e

t

a

n

i

m

r

e

t

s

t

u

p

t

u

O

:

1

E

T

O

N

V

o

t

O

C

C

.

V

2

-

V

.

d

e

t

i

m

il

s

i

n

o

i

t

a

r

e

p

o

t

u

p

n

i

d

e

d

n

e

-

e

l

g

n

i

S

:

2

E

T

O

N

C

C

.

e

d

o

m

L

C

E

P

V

L

n

i

V

3

V

s

a

d

e

n

i

f

e

d

s

i

e

g

a

t

l

o

v

e

d

o

m

n

o

m

m

o

C

:

3

E

T

O

N

H

I

.

1

K

L

C

P

n

,

1

K

L

C

P

d

n

a

0

K

L

C

P

n

,

0

K

L

C

P

r

o

f

e

g

a

t

l

o

v

t

u

p

n

i

m

u

m

i

x

a

m

e

h

t

,

s

n

o

i

t

a

c

il

p

p

a

d

e

d

n

e

-

e

l

g

n

i

s

r

o

F

:

4

E

T

O

N

V

s

i

C

C

.

V

3

.

0

+

853210AY

www.icst.com/products/hiperclocks.html

REV. A NOVEMBER 12, 2003

4

Integrated

Circuit

Systems, Inc.

ICS853210

L

OW

S

KEW

, D

UAL

, 1-

TO

-5

D

IFFERENTIAL

-

TO

-2.5V/3.3V LVPECL/ECL F

ANOUT

B

UFFER

T

ABLE

4C. LVPECL DC C

HARACTERISTICS

,

V

CC

= 2.5V; V

EE

= 0V

T

ABLE

4D. ECL DC C

HARACTERISTICS

,

V

CC

= 0V; V

EE

= -2.375

TO

-3.8V

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

C

∞

0

4

-

C

∞

5

2

C

∞

5

8

s

t

i

n

U

n

i

M

p

y

T

x

a

M

n

i

M

p

y

T

x

a

M

n

i

M

p

y

T

x

a

M

V

H

O

1

E

T

O

N

;

e

g

a

t

l

o

V

h

g

i

H

t

u

p

t

u

O

5

7

3

.

1

5

7

4

.

1

8

5

.

1

5

2

4

.

1

5

9

4

.

1

7

5

.

1

5

9

4

.

1

3

5

.

1

5

6

5

.

1

V

V

L

O

1

E

T

O

N

;

e

g

a

t

l

o

V

w

o

L

t

u

p

t

u

O

5

0

6

.

0

5

4

7

.

0

8

8

.

0

5

2

6

.

0

2

7

.

0

5

1

8

.

0

4

6

.

0

5

3

7

.

0

3

8

.

0

V

V

H

I

e

g

a

t

l

o

V

h

g

i

H

t

u

p

n

I

)

d

e

d

n

E

-

e

l

g

n

i

S

(

5

7

2

.

1

6

5

.

1

5

7

2

.

1

6

5

.

1

5

7

2

.

1

3

8

.

0

-

V

V

L

I

e

g

a

t

l

o

V

w

o

L

t

u

p

n

I

)

d

e

d

n

E

-

e

l

g

n

i

S

(

3

6

.

0

5

6

9

.

0

3

6

.

0

5

6

9

.

0

3

6

.

0

5

6

9

.

0

V

V

P

P

e

g

a

t

l

o

V

t

u

p

n

I

k

a

e

P

-

o

t

-

k

a

e

P

0

5

1

0

0

8

0

0

2

1

0

5

1

0

0

8

0

0

2

1

0

5

1

0

0

8

0

0

2

1

m

V

V

R

M

C

e

g

a

t

l

o

V

h

g

i

H

t

u

p

n

I

3

,

2

E

T

O

N

;

e

g

n

a

R

e

d

o

M

n

o

m

m

o

C

2

.

1

5

.

2

2

.

1

5

.

2

2

.

1

5

.

2

V

I

H

I

t

u

p

n

I

t

n

e

r

r

u

C

h

g

i

H

1

K

L

C

P

,

0

K

L

C

P

1

K

L

C

P

n

,

0

K

L

C

P

n

0

5

1

0

5

1

0

5

1

A

µ

I

L

I

t

u

p

n

I

t

n

e

r

r

u

C

w

o

L

1

K

L

C

P

,

0

K

L

C

P

0

1

-

0

1

-

0

1

-

A

µ

1

K

L

C

P

n

,

0

K

L

C

P

n

0

5

1

-

0

5

1

-

0

5

1

-

A

µ

V

h

t

i

w

1

:

1

y

r

a

v

s

r

e

t

e

m

a

r

a

p

t

u

p

t

u

o

d

n

a

t

u

p

n

I

C

C

V

.

E

E

.

V

5

.

0

-

o

t

V

5

2

9

.

0

+

y

r

a

v

n

a

c

0

5

h

t

i

w

d

e

t

a

n

i

m

r

e

t

s

t

u

p

t

u

O

:

1

E

T

O

N

V

o

t

O

C

C

.

V

2

-

V

s

a

d

e

n

i

f

e

d

s

i

e

g

a

t

l

o

v

e

d

o

m

n

o

m

m

o

C

:

2

E

T

O

N

H

I

.

1

K

L

C

P

n

,

1

K

L

C

P

d

n

a

0

K

L

C

P

n

,

0

K

L

C

P

r

o

f

e

g

a

t

l

o

v

t

u

p

n

i

m

u

m

i

x

a

m

e

h

t

,

s

n

o

i

t

a

c

il

p

p

a

d

e

d

n

e

-

e

l

g

n

i

s

r

o

F

:

3

E

T

O

N

V

s

i

C

C

.

V

3

.

0

+

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

C

∞

0

4

-

C

∞

5

2

C

∞

5

8

s

t

i

n

U

n

i

M

p

y

T

x

a

M

n

i

M

p

y

T

x

a

M

n

i

M

p

y

T

x

a

M

V

H

O

1

E

T

O

N

;

e

g

a

t

l

o

V

h

g

i

H

t

u

p

t

u

O

5

2

1

.

1

-

5

2

0

.

1

-

2

9

.

0

-

5

7

0

.

1

-

5

0

0

.

1

-

3

9

.

0

-

5

0

0

.

1

-

7

9

.

0

-

5

3

9

.

0

-

V

V

L

O

1

E

T

O

N

;

e

g

a

t

l

o

V

w

o

L

t

u

p

t

u

O

5

9

8

.

1

-

5

5

7

.

1

-

2

6

.

1

-

5

7

8

.

1

-

8

7

.

1

-

5

8

6

.

1

-

6

8

.

1

-

5

6

7

.

1

-

7

6

.

1

-

V

V

H

I

e

g

a

t

l

o

V

h

g

i

H

t

u

p

n

I

)

d

e

d

n

E

-

e

l

g

n

i

S

(

5

2

2

.

1

-

4

9

.

0

-

5

2

2

.

1

-

4

9

.

0

-

5

2

2

.

1

-

4

9

.

0

-

V

V

L

I

e

g

a

t

l

o

V

w

o

L

t

u

p

n

I

)

d

e

d

n

E

-

e

l

g

n

i

S

(

7

8

.

1

-

5

3

5

.

1

-

7

8

.

1

-

5

3

5

.

1

-

7

8

.

1

-

5

3

5

.

1

-

V

V

B

B

2

E

T

O

N

;

e

c

n

e

r

e

f

e

R

e

g

a

t

l

o

V

t

u

p

t

u

O

4

4

.

1

-

2

3

.

1

-

4

4

.

1

-

2

3

.

1

-

4

4

.

1

-

2

3

.

1

-

V

V

P

P

e

g

a

t

l

o

V

t

u

p

n

I

k

a

e

P

-

o

t

-

k

a

e

P

0

5

1

0

0

8

0

0

2

1

0

5

1

0

0

8

0

0

2

1

0

5

1

0

0

8

0

0

2

1

m

V

V

R

M

C

e

g

a

t

l

o

V

h

g

i

H

t

u

p

n

I

4

,

3

E

T

O

N

;

e

g

n

a

R

e

d

o

M

n

o

m

m

o

C

V

E

E

V

2

.

1

+

0

V

E

E

V

2

.

1

+

0

V

E

E

V

2

.

1

+

0

V

I

H

I

t

u

p

n

I

t

n

e

r

r

u

C

h

g

i

H

1

K

L

C

P

,

0

K

L

C

P

1

K

L

C

P

n

,

0

K

L

C

P

n

0

5

1

0

5

1

0

5

1

A

µ

I

L

I

t

u

p

n

I

t

n

e

r

r

u

C

w

o

L

1

K

L

C

P

,

0

K

L

C

P

0

1

-

0

1

-

0

1

-

A

µ

1

K

L

C

P

n

,

0

K

L

C

P

n

0

5

1

-

0

5

1

-

0

5

1

-

A

µ

V

h

t

i

w

1

:

1

y

r

a

v

s

r

e

t

e

m

a

r

a

p

t

u

p

t

u

o

d

n

a

t

u

p

n

I

C

C

V

.

E

E

.

V

5

.

0

-

o

t

V

5

2

9

.

0

+

y

r

a

v

n

a

c

0

5

h

t

i

w

d

e

t

a

n

i

m

r

e

t

s

t

u

p

t

u

O

:

1

E

T

O

N

V

o

t

O

C

C

.

V

2

-

V

.

d

e

t

i

m

il

s

i

n

o

i

t

a

r

e

p

o

t

u

p

n

i

d

e

d

n

e

-

e

l

g

n

i

S

:

2

E

T

O

N

C

C

.

e

d

o

m

L

C

E

P

V

L

n

i

V

3

V

s

a

d

e

n

i

f

e

d

s

i

e

g

a

t

l

o

v

e

d

o

m

n

o

m

m

o

C

:

3

E

T

O

N

H

I

.

1

K

L

C

P

n

,

1

K

L

C

P

d

n

a

0

K

L

C

P

n

,

0

K

L

C

P

r

o

f

e

g

a

t

l

o

v

t

u

p

n

i

m

u

m

i

x

a

m

e

h

t

,

s

n

o

i

t

a

c

il

p

p

a

d

e

d

n

e

-

e

l

g

n

i

s

r

o

F

:

4

E

T

O

N

V

s

i

C

C

.

V

3

.

0

+

853210AY

www.icst.com/products/hiperclocks.html

REV. A NOVEMBER 12, 2003

5

Integrated

Circuit

Systems, Inc.

ICS853210

L

OW

S

KEW

, D

UAL

, 1-

TO

-5

D

IFFERENTIAL

-

TO

-2.5V/3.3V LVPECL/ECL F

ANOUT

B

UFFER

T

ABLE

5. AC C

HARACTERISTICS

,

V

CC

= 0V; V

EE

= -2.375

TO

-3.8V

OR

V

CC

= 2.375

TO

3.8V; V

EE

= 0V

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

C

∞

0

4

-

C

∞

5

2

C

∞

5

8

s

t

i

n

U

n

i

M

p

y

T

x

a

M

n

i

M

p

y

T

x

a

M

n

i

M

p

y

T

x

a

M

f

X

A

M

y

c

n

e

u

q

e

r

F

t

u

p

t

u

O

3

>

3

>

3

>

z

H

G

P

t

H

L

1

E

T

O

N

;

h

g

i

H

-

o

t

-

w

o

L

,

y

a

l

e

D

n

o

i

t

a

g

a

p

o

r

P

5

1

4

0

7

4

0

2

5

0

3

4

5

8

4

5

4

5

5

3

4

5

1

5

5

8

5

s

p

P

t

L

H

,

y

a

l

e

D

n

o

i

t

a

g

a

p

o

r

P

1

E

T

O

N

;

w

o

L

-

o

t

-

h

g

i

H

V

5

.

2

@

0

0

4

0

7

4

0

4

5

5

2

4

0

9

4

0

5

5

5

4

4

5

1

5

5

8

5

s

p

t

)

o

(

k

s

4

,

2

E

T

O

N

;

w

e

k

S

t

u

p

t

u

O

3

1

5

2

3

1

5

2

3

1

5

2

s

p

t

)

p

p

(

k

s

4

,

3

E

T

O

N

;

w

e

k

S

t

r

a

P

-

o

t

-

t

r

a

P

5

8

0

6

1

5

8

0

6

1

5

8

0

6

1

s

p

t

R

/t

F

e

m

i

T

ll

a

F

/

e

s

i

R

t

u

p

t

u

O

%

0

8

o

t

%

0

2

5

1

1

8

8

1

0

6

2

0

3

1

0

9

1

0

5

2

5

4

1

0

9

1

5

3

2

s

p

d

e

t

s

e

t

s

r

e

t

e

m

a

r

a

p

ll

A

.

d

e

t

o

n

e

s

i

w

r

e

h

t

o

s

s

e

l

n

u

z

H

G

1

.

t

n

i

o

p

g

n

i

s

s

o

r

c

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

d

e

h

t

o

t

t

n

i

o

p

g

n

i

s

s

o

r

c

t

u

p

n

i

l

a

i

t

n

e

r

e

f

f

i

d

e

h

t

m

o

r

f

d

e

r

u

s

a

e

M

:

1

E

T

O

N

.

s

n

o

i

t

i

d

n

o

c

d

a

o

l

l

a

u

q

e

h

t

i

w

d

n

a

e

g

a

t

l

o

v

y

l

p

p

u

s

e

m

a

s

e

h

t

t

a

s

t

u

p

t

u

o

n

e

e

w

t

e

b

w

e

k

s

s

a

d

e

n

i

f

e

D

:

2

E

T

O

N

.

s

t

n

i

o

p

s

s

o

r

c

l

a

i

t

n

e

r

e

f

f

i

d

t

u

p

t

u

o

e

h

t

t

a

d

e

r

u

s

a

e

M

s

e

g

a

t

l

o

v

y

l

p

p

u

s

e

m

a

s

e

h

t

t

a

g

n

i

t

a

r

e

p

o

s

e

c

i

v

e

d

t

n

e

r

e

f

f

i

d

n

o

s

t

u

p

t

u

o

n

e

e

w

t

e

b

w

e

k

s

s

a

d

e

n

i

f

e

D

:

3

E

T

O

N

d

e

r

u

s

a

e

m

e

r

a

s

t

u

p

t

u

o

e

h

t

,

e

c

i

v

e

d

h

c

a

e

n

o

s

t

u

p

n

i

f

o

e

p

y

t

e

m

a

s

e

h

t

g

n

i

s

U

.

s

n

o

i

t

i

d

n

o

c

d

a

o

l

l

a

u

q

e

h

t

i

w

d

n

a

.

s

t

n

i

o

p

s

s

o

r

c

l

a

i

t

n

e

r

e

f

f

i

d

e

h

t

t

a

.

5

6

d

r

a

d

n

a

t

S

C

E

D

E

J

h

t

i

w

e

c

n

a

d

r

o

c

c

a

n

i

d

e

n

i

f

e

d

s

i

r

e

t

e

m

a

r

a

p

s

i

h

T

:

4

E

T

O

N

853210AY

www.icst.com/products/hiperclocks.html

REV. A NOVEMBER 12, 2003

6

Integrated

Circuit

Systems, Inc.

ICS853210

L

OW

S

KEW

, D

UAL

, 1-

TO

-5

D

IFFERENTIAL

-

TO

-2.5V/3.3V LVPECL/ECL F

ANOUT

B

UFFER

P

ARAMETER

M

EASUREMENT

I

NFORMATION

O

UTPUT

L

OAD

AC T

EST

C

IRCUIT

D

IFFERENTIAL

I

NPUT

L

EVEL

O

UTPUT

S

KEW

P

ART

-

TO

-P

ART

S

KEW

O

UTPUT

R

ISE

/F

ALL

T

IME

P

ROPAGATION

D

ELAY

V

CMR

Cross Points

V

PP

V

EE

nPCLKA,

nPCLKB

V

CC

PCLKA,

PCLKB

SCOPE

Qx

nQx

LVPECL

2V

-0.375V to -1.8V

tsk(pp)

t

sk(o)

nQx

Qx

nQy

Qy

PART 1

PART 2

nQx

Qx

nQy

Qy

Clock

Outputs

20%

80%

80%

20%

t

R

t

F

V

SW I N G

tp

LH

tp

HL

nPCLKA,

nPCLKB

QA0:QA4,

QB0:QB4,

nQA0:nQA4,

nQB0:nQB4,

PCLKA,

PCLKB

V

CC

,

V

CCO

V

EE

853210AY

www.icst.com/products/hiperclocks.html

REV. A NOVEMBER 12, 2003

7

Integrated

Circuit

Systems, Inc.

ICS853210

L

OW

S

KEW

, D

UAL

, 1-

TO

-5

D

IFFERENTIAL

-

TO

-2.5V/3.3V LVPECL/ECL F

ANOUT

B

UFFER

Figure 1A shows an example of the differential input that can

be wired to accept single ended levels. The reference voltage

level V

BB

generated from the device is connected to the

A

PPLICATION

I

NFORMATION

W

IRING

THE

D

IFFERENTIAL

I

NPUT

TO

A

CCEPT

S

INGLE

E

NDED

LVPECL L

EVELS

F

IGURE

1A. S

INGLE

E

NDED

LVPECL S

IGNAL

D

RIVING

D

IFFERENTIAL

I

NPUT

negative input. The C1 capacitor should be located as close

as possible to the input pin.

VCC(or VDD)

CLK_IN

PCLK

nPCLK

VBB

Figure 1B shows how the differential input can be wired to accept

single ended levels. The reference voltage V_REF ~ V

CC

/2 is

generated by the bias resistors R1, R2 and C1. This bias circuit

should be located as close as possible to the input pin. The ratio

F

IGURE

1B. S

INGLE

E

NDED

S

IGNAL

D

RIVING

D

IFFERENTIAL

I

NPUT

W

IRING

THE

D

IFFERENTIAL

I

NPUT

TO

A

CCEPT

S

INGLE

E

NDED

L

EVELS

of R1 and R2 might need to be adjusted to position the V_REF in

the center of the input voltage swing. For example, if the input

clock swing is only 2.5V and V

CC

= 3.3V, V_REF should be 1.25V

and R2/R1 = 0.609.

VCC

R2

1K

V_REF

C1

0.1u

R1

1K

Single Ended Clock Input

PCLK

nPCLK

853210AY

www.icst.com/products/hiperclocks.html

REV. A NOVEMBER 12, 2003

8

Integrated

Circuit

Systems, Inc.

ICS853210

L

OW

S

KEW

, D

UAL

, 1-

TO

-5

D

IFFERENTIAL

-

TO

-2.5V/3.3V LVPECL/ECL F

ANOUT

B

UFFER

V

CC

- 2V

50

50

RTT

Z

o

= 50

Z

o

= 50

FOUT

FIN

RTT =

Z

o

1

((V

OH

+ V

OL

) / (V

CC

≠ 2)) ≠ 2

3.3V

125

125

84

84

Z

o

= 50

Z

o

= 50

FOUT

FIN

The clock layout topology shown below is a typical termina-

tion for LVPECL outputs. The two different layouts mentioned

are recommended only as guidelines.

FOUT and nFOUT are low impedance follower outputs that gen-

erate ECL/LVPECL compatible outputs. Therefore, terminating

resistors (DC current path to ground) or current sources must

be used for functionality. These outputs are designed to drive

50

transmission lines. Matched impedance techniques should

be used to maximize operating frequency and minimize signal

distortion.

Figures 2A and 2B show two different layouts which

are recommended only as guidelines. Other suitable clock lay-

outs may exist and it would be recommended that the board

designers simulate to guarantee compatibility across all printed

circuit and clock component process variations.

T

ERMINATION

FOR

3.3V LVPECL O

UTPUTS

F

IGURE

2B. LVPECL O

UTPUT

T

ERMINATION

F

IGURE

2A. LVPECL O

UTPUT

T

ERMINATION

853210AY

www.icst.com/products/hiperclocks.html

REV. A NOVEMBER 12, 2003

9

Integrated

Circuit

Systems, Inc.

ICS853210

L

OW

S

KEW

, D

UAL

, 1-

TO

-5

D

IFFERENTIAL

-

TO

-2.5V/3.3V LVPECL/ECL F

ANOUT

B

UFFER

T

ERMINATION

FOR

2.5V LVPECL O

UTPUT

Figure 3A and Figure 3B show examples of termination for 2.5V

LVPECL driver. These terminations are equivalent to terminat-

ing 50

to V

CC

- 2V. For V

CC

= 2.5V, the V

CC

- 2V is very close to

ground level. The R3 in

Figure 3B can be eliminated and the

termination is shown in

Figure 3C.

F

IGURE

3C. 2.5V LVPECL T

ERMINATION

E

XAMPLE

R2

50

Zo = 50 Ohm

VCCO=2.5V

R1

50

Zo = 50 Ohm

+

-

2.5V

2,5V LVPECL

Driv er

F

IGURE

3B. 2.5V LVPECL D

RIVER

T

ERMINATION

E

XAMPLE

VCCO=2.5V

R1

50

R2

50

Zo = 50 Ohm

R3

18

2,5V LVPECL

Driv er

Zo = 50 Ohm

+

-

2.5V

F

IGURE

3A. 2.5V LVPECL D

RIVER

T

ERMINATION

E

XAMPLE

R2

62.5

2.5V

2,5V LVPECL

Driv er

R3

250

Zo = 50 Ohm

Zo = 50 Ohm

R4

62.5

2.5V

+

-

R1

250

VCCO=2.5V

853210AY

www.icst.com/products/hiperclocks.html

REV. A NOVEMBER 12, 2003

10

Integrated

Circuit

Systems, Inc.

ICS853210

L

OW

S

KEW

, D

UAL

, 1-

TO

-5

D

IFFERENTIAL

-

TO

-2.5V/3.3V LVPECL/ECL F

ANOUT

B

UFFER

LVPECL C

LOCK

I

NPUT

I

NTERFACE

The PCLKx /nPCLKx accepts LVPECL, CML, SSTL and other

differential signals. Both V

SWING

and V

OH

must meet the V

PP

and V

CMR

input requirements.

Figures 4A to 4E show inter-

face examples for the HiPerClockS PCLKx/nPCLKx input

driven by the most common driver types. The input interfaces

suggested here are examples only. If the driver is from an-

other vendor, use their termination recommendation. Please

consult with the vendor of the driver component to confirm

the driver termination requirements.

F

IGURE

4A. H

I

P

ER

C

LOCK

S PCLK/

N

PCLK I

NPUT

D

RIVEN

BY

A

CML D

RIVER

F

IGURE

4B. H

I

P

ER

C

LOCK

S PCLK/

N

PCLK I

NPUT

D

RIVEN

BY

AN

SSTL D

RIVER

F

IGURE

4C. H

I

P

ER

C

LOCK

S PCLK/

N

PCLK I

NPUT

D

RIVEN

BY

A

3.3V LVPECL D

RIVER

F

IGURE

4D. H

I

P

ER

C

LOCK

S PCLK/

N

PCLK I

NPUT

D

RIVEN

BY

A

3.3V LVDS D

RIVER

HiPerClockS

PCLK

nPCLK

PCLK/nPCLK

3.3V

R2

50

R1

50

3.3V

Zo = 50 Ohm

CML

3.3V

Zo = 50 Ohm

PCLK/nPCLK

2.5V

Zo = 60 Ohm

SSTL

HiPerClockS

PCLK

nPCLK

R2

120

3.3V

R3

120

Zo = 60 Ohm

R1

120

R4

120

2.5V

F

IGURE

4E. H

I

P

ER

C

LOCK

S PCLK/

N

PCLK I

NPUT

D

RIVEN

BY

A

3.3V LVPECL D

RIVER

WITH

AC C

OUPLE

3.3V

R5

100 - 200

3.3V

3.3V

HiPerClockS

PCLK

nPCLK

R1

125

PCLK/nPCLK

R2

125

R3

84

C1

C2

Zo = 50 Ohm

R4

84

Zo = 50 Ohm

R6

100 - 200

3.3V LVPECL

3.3V

HiPerClockS

PCLK

nPCLK

R2

84

R3

125

Input

Zo = 50 Ohm

R4

125

R1

84

LVPECL

3.3V

3.3V

Zo = 50 Ohm

C2

R2

1K

R5

100

Zo = 50 Ohm

3.3V

3.3V

C1

R3

1K

LVDS

R4

1K

HiPerClockS

PCLK

nPCLK

R1

1K

Zo = 50 Ohm

3.3V

PC L K /n PC LK

853210AY

www.icst.com/products/hiperclocks.html

REV. A NOVEMBER 12, 2003

11

Integrated

Circuit

Systems, Inc.

ICS853210

L

OW

S

KEW

, D

UAL

, 1-

TO

-5

D

IFFERENTIAL

-

TO

-2.5V/3.3V LVPECL/ECL F

ANOUT

B

UFFER

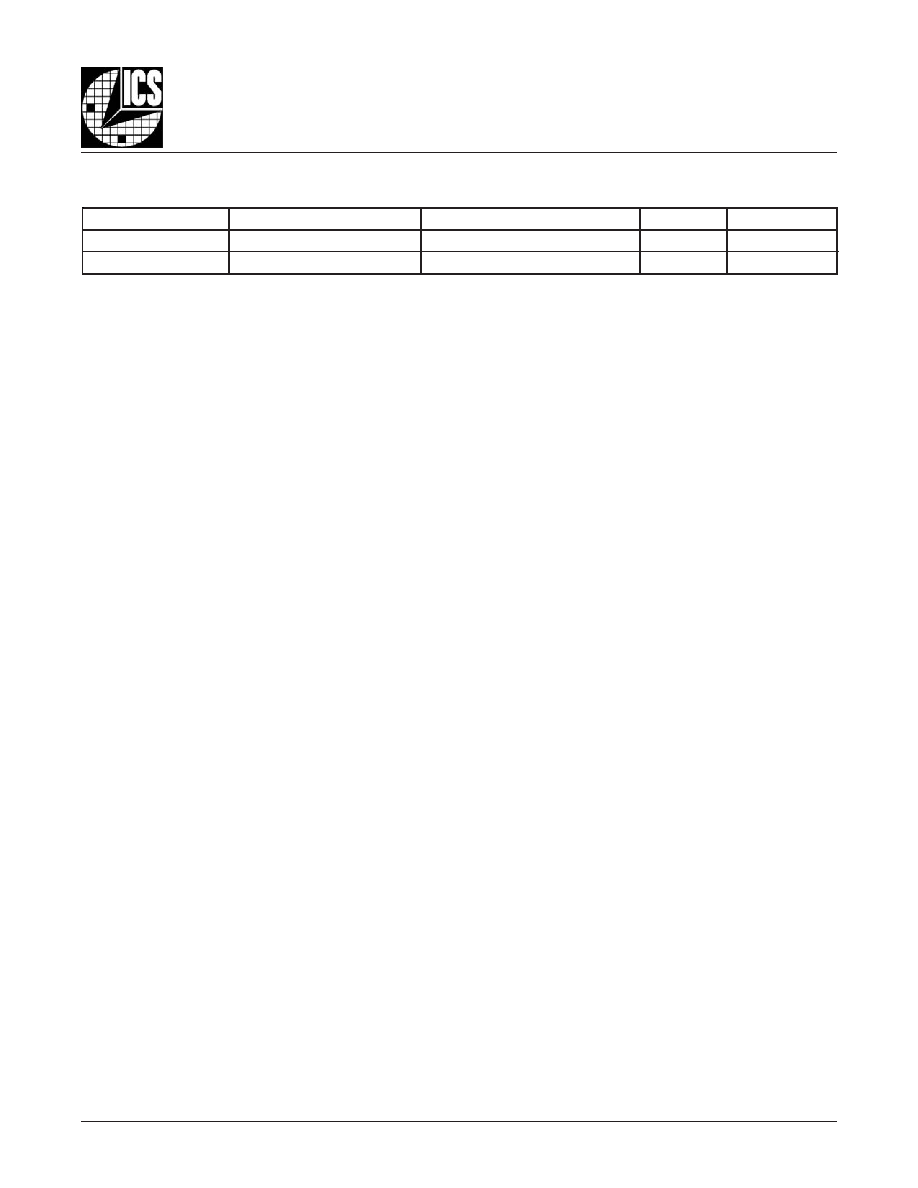

JA

by Velocity (Linear Feet per Minute)

0

200

500

Single-Layer PCB, JEDEC Standard Test Boards

67.8∞C/W

55.9∞C/W

50.1∞C/W

Multi-Layer PCB, JEDEC Standard Test Boards

47.9∞C/W

42.1∞C/W

39.4∞C/W

NOTE: Most modern PCB designs use multi-layered boards. The data in the second row pertains to most designs.

P

OWER

C

ONSIDERATIONS

This section provides information on power dissipation and junction temperature for the ICS853210.

Equations and example calculations are also provided.

1. Power Dissipation.

The total power dissipation for the ICS853210 is the sum of the core power plus the power dissipated in the load(s).

The following is the power dissipation for V

CC

= 3.8V, which gives worst case results.

NOTE: Please refer to Section 3 for details on calculating power dissipated in the load.

∑

Power (core)

MAX

= V

CC_MAX

* I

EE_MAX

= 3.8V * 80mA = 304mW

∑

Power (outputs)

MAX

= 30.94mW/Loaded Output pair

If all outputs are loaded, the total power is 10 * 30.94mW = 309.4mW

Total Power

_MAX

(3.8V, with all outputs switching) = 304mW + 309.4mW = 613.4mW

2. Junction Temperature.

Junction temperature, Tj, is the temperature at the junction of the bond wire and bond pad and directly affects the reliability of the

device. The maximum recommended junction temperature for HiPerClockS

TM

devices is 125∞C.

The equation for Tj is as follows: Tj =

JA

* Pd_total + T

A

Tj = Junction Temperature

JA

= Junction-to-Ambient Thermal Resistance

Pd_total = Total Device Power Dissipation (example calculation is in section 1 above)

T

A

= Ambient Temperature

In order to calculate junction temperature, the appropriate junction-to-ambient thermal resistance

JA

must be used. Assuming a

moderate air flow of 200 linear feet per minute and a multi-layer board, the appropriate value is 42.1∞C/W per Table 6 below.

Therefore, Tj for an ambient temperature of 85∞C with all outputs switching is:

85∞C + 0.613W * 42.1∞C/W = 110.8∞C. This is well below the limit of 125∞C.

This calculation is only an example. Tj will obviously vary depending on the number of loaded outputs, supply voltage, air flow,

and the type of board (single layer or multi-layer).

T

ABLE

6. T

HERMAL

R

ESISTANCE

JA

FOR

32-

PIN

LQFP, F

ORCED

C

ONVECTION

853210AY

www.icst.com/products/hiperclocks.html

REV. A NOVEMBER 12, 2003

12

Integrated

Circuit

Systems, Inc.

ICS853210

L

OW

S

KEW

, D

UAL

, 1-

TO

-5

D

IFFERENTIAL

-

TO

-2.5V/3.3V LVPECL/ECL F

ANOUT

B

UFFER

3. Calculations and Equations.

LVPECL output driver circuit and termination are shown in Figure 5.

T

o calculate worst case power dissipation into the load, use the following equations which assume a 50

load, and a termination

voltage of V

CCO

- 2V.

∑

For logic high, V

OUT

= V

OH_MAX

= V

CCO_MAX

≠ 0.935V

(V

CC_MAX

- V

OH_MAX

) = 0.935V

∑

For logic low, V

OUT

= V

OL_MAX

= V

CCO_MAX

≠ 1.67V

(V

CCO_MAX

- V

OL_MAX

) = 1.67V

Pd_H = [(V

OH_MAX

≠ (V

CCO_MAX

- 2V))/R

L

] * (V

CCO_MAX

- V

OH_MAX

) = [(2V - (V

CCO_MAX

- V

OH_MAX

))/R

L

] * (V

CCO _MAX

- V

OH_MAX

) =

[(2V - 0.935V)/50

] * 0.935V = 19.92mW

Pd_L = [(V

OL_MAX

≠ (V

CCO_MAX

- 2V))/R

L

] * (V

CCO_MAX

- V

OL_MAX

) = [(2V - (V

CCO_MAX

- V

OL_MAX

))/R

L

] * (V

CCO_MAX

- V

OL_MAX

) =

[(2V - 1.67V)/50

] * 1.67V = 11.02mW

Total Power Dissipation per output pair = Pd_H + Pd_L = 30.94mW

Figure 5. LVPECL Driver Circuit and Termination

VCCO - 2V

Q1

VOUT

RL

50

VCCO

853210AY

www.icst.com/products/hiperclocks.html

REV. A NOVEMBER 12, 2003

13

Integrated

Circuit

Systems, Inc.

ICS853210

L

OW

S

KEW

, D

UAL

, 1-

TO

-5

D

IFFERENTIAL

-

TO

-2.5V/3.3V LVPECL/ECL F

ANOUT

B

UFFER

R

ELIABILITY

I

NFORMATION

T

RANSISTOR

C

OUNT

The transistor count for ICS853210 is:

437

T

ABLE

6.

JA

VS

. A

IR

F

LOW

T

ABLE

FOR

32 L

EAD

LQFP

JA

by Velocity (Linear Feet per Minute)

0

200

500

Single-Layer PCB, JEDEC Standard Test Boards

67.8∞C/W

55.9∞C/W

50.1∞C/W

Multi-Layer PCB, JEDEC Standard Test Boards

47.9∞C/W

42.1∞C/W

39.4∞C/W

NOTE: Most modern PCB designs use multi-layered boards. The data in the second row pertains to most designs.

853210AY

www.icst.com/products/hiperclocks.html

REV. A NOVEMBER 12, 2003

14

Integrated

Circuit

Systems, Inc.

ICS853210

L

OW

S

KEW

, D

UAL

, 1-

TO

-5

D

IFFERENTIAL

-

TO

-2.5V/3.3V LVPECL/ECL F

ANOUT

B

UFFER

P

ACKAGE

O

UTLINE

- Y S

UFFIX

FOR

32 L

EAD

LQFP

T

ABLE

7. P

ACKAGE

D

IMENSIONS

Reference Document: JEDEC Publication 95, MS-026

N

O

I

T

A

I

R

A

V

C

E

D

E

J

S

R

E

T

E

M

I

L

L

I

M

N

I

S

N

O

I

S

N

E

M

I

D

L

L

A

L

O

B

M

Y

S

A

B

B

M

U

M

I

N

I

M

L

A

N

I

M

O

N

M

U

M

I

X

A

M

N

2

3

A

-

-

-

-

0

6

.

1

1

A

5

0

.

0

-

-

5

1

.

0

2

A

5

3

.

1

0

4

.

1

5

4

.

1

b

0

3

.

0

7

3

.

0

5

4

.

0

c

9

0

.

0

-

-

0

2

.

0

D

C

I

S

A

B

0

0

.

9

1

D

C

I

S

A

B

0

0

.

7

2

D

.

f

e

R

0

6

.

5

E

C

I

S

A

B

0

0

.

9

1

E

C

I

S

A

B

0

0

.

7

2

E

.

f

e

R

0

6

.

5

e

C

I

S

A

B

0

8

.

0

L

5

4

.

0

0

6

.

0

5

7

.

0

0

∞

-

-

7

∞

c

c

c

-

-

-

-

0

1

.

0

853210AY

www.icst.com/products/hiperclocks.html

REV. A NOVEMBER 12, 2003

15

Integrated

Circuit

Systems, Inc.

ICS853210

L

OW

S

KEW

, D

UAL

, 1-

TO

-5

D

IFFERENTIAL

-

TO

-2.5V/3.3V LVPECL/ECL F

ANOUT

B

UFFER

T

ABLE

8. O

RDERING

I

NFORMATION

While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems, Incorporated (ICS) assumes no responsibility for either its use

or for infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use

in normal commercial and industrial applications. Any other applications such as those requiring high reliability or other extraordinary environmental requirements are not

recommended without additional processing by ICS. ICS reserves the right to change any circuitry or specifications without notice. ICS does not authorize or warrant any ICS product

for use in life support devices or critical medical instruments.

r

e

b

m

u

N

r

e

d

r

O

/

t

r

a

P

g

n

i

k

r

a

M

e

g

a

k

c

a

P

t

n

u

o

C

e

r

u

t

a

r

e

p

m

e

T

Y

A

0

1

2

3

5

8

S

C

I

Y

A

2

0

1

3

5

8

S

C

I

P

F

Q

L

d

a

e

l

2

3

y

a

r

t

r

e

p

0

5

2

C

∞

5

8

o

t

C

∞

0

4

-

T

Y

A

0

1

2

3

5

8

S

C

I

Y

A

0

1

2

3

5

8

S

C

I

l

e

e

R

d

n

a

e

p

a

T

n

o

P

F

Q

L

d

a

e

l

2

3

0

0

0

1

C

∞

5

8

o

t

C

∞

0

4

-