8633AF-01

www.icst.com/products/hiperclocks.html

REV. A JANUARY 26, 2006

1

Integrated

Circuit

Systems, Inc.

ICS8633-01

1-

TO

-3 D

IFFERENTIAL

-

TO

-3.3V LVPECL

Z

ERO

D

ELAY

B

UFFER

G

ENERAL

D

ESCRIPTION

The ICS8633-01 is a high performance 1-to-3

Differential-to-3.3V LVPECL Zero Delay Buffer

and a member of the HiPerClockSTM family of

High Performance Clock Solutions from ICS.

The ICS8633-01 has two selectable clock in-

puts. The CLKx, nCLKx pairs can accept most standard

differential input levels. Utilizing one of the outputs as feed-

back to the PLL, output frequencies up to 700MHz can be

regenerated with zero delay with respect to the input. Dual

reference clock inputs support redundant clock or multiple

reference applications.

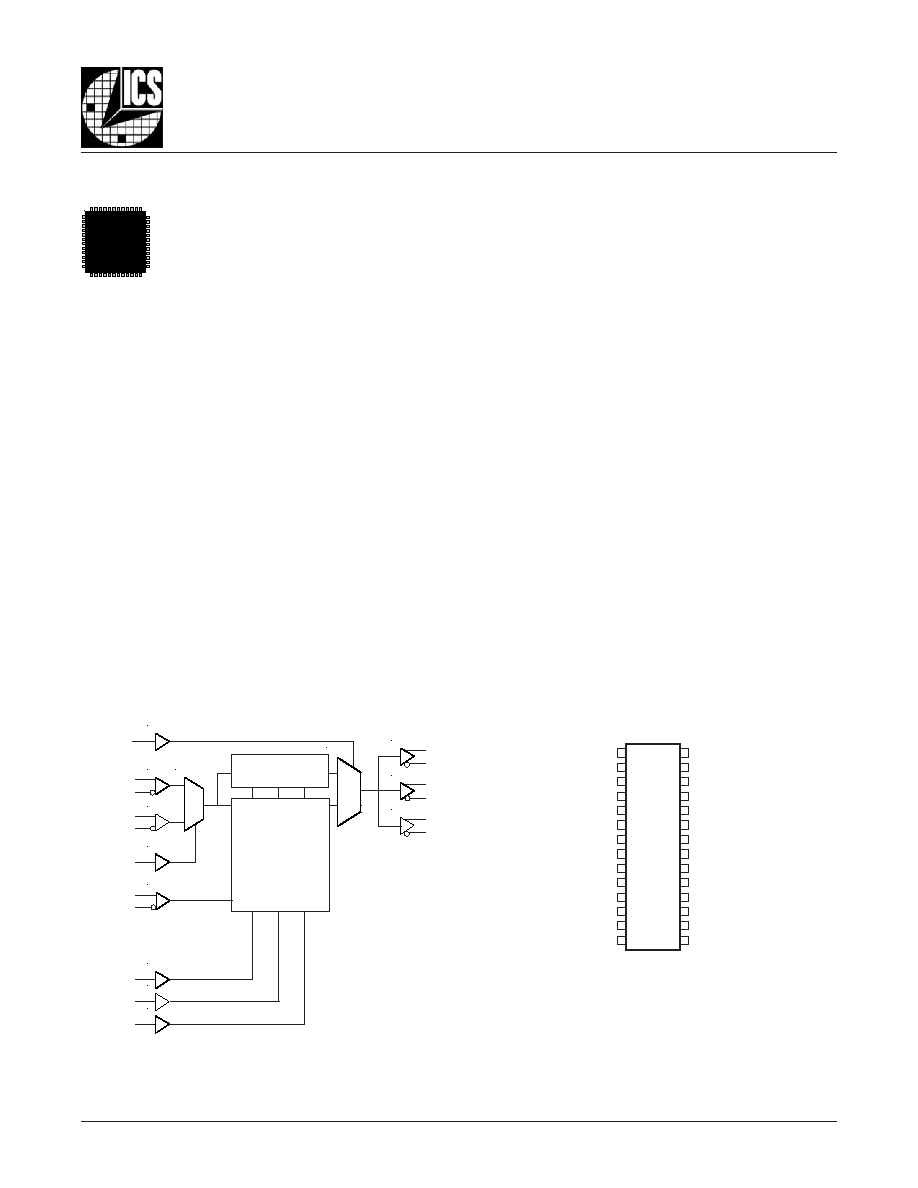

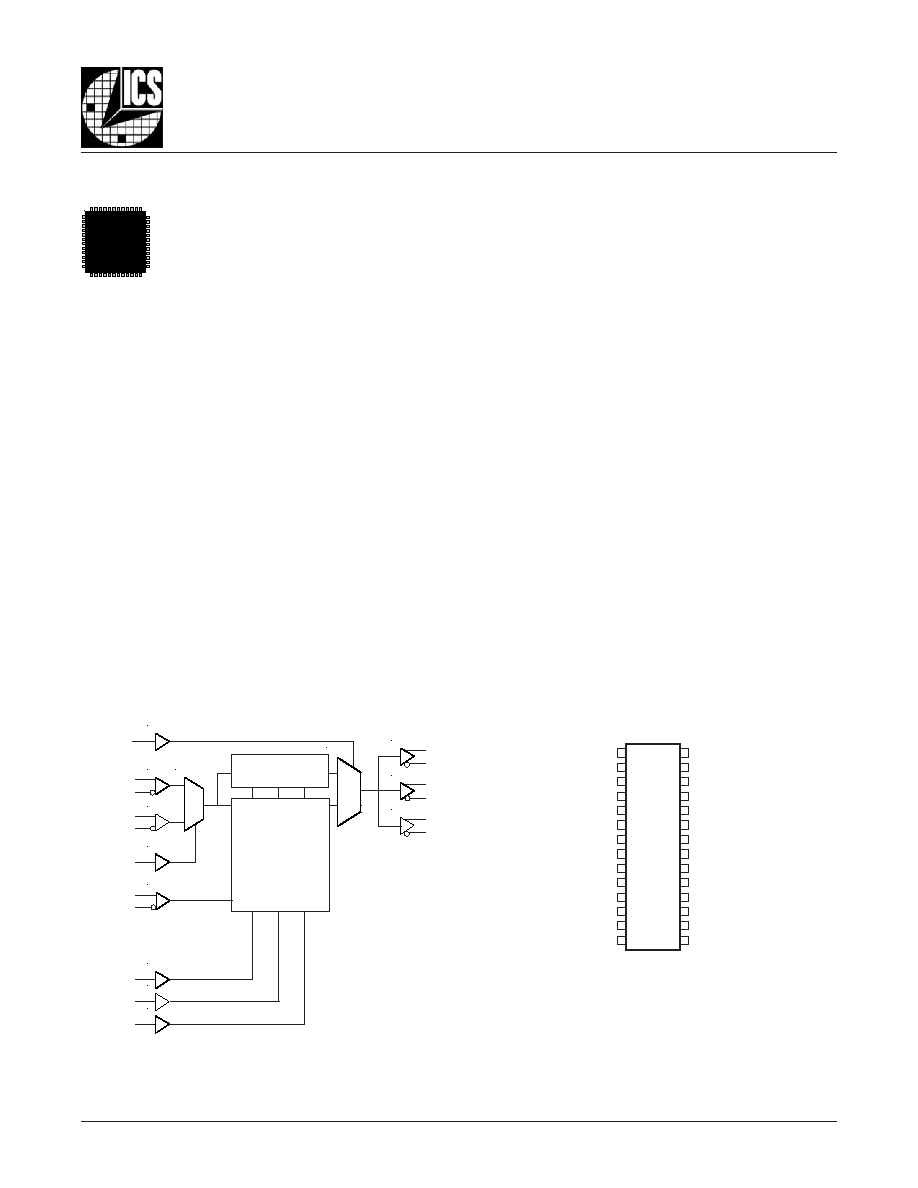

B

LOCK

D

IAGRAM

P

IN

A

SSIGNMENT

F

EATURES

· Three differential 3.3V LVPECL outputs

· Selectable differential clock inputs

· CLKx, nCLKx pairs can accept the following differential

input levels: LVPECL, LVDS, LVHSTL, HCSL, SSTL

· Output frequency range: 31.25MHz to 700MHz

· Input frequency range: 31.25MHz to 700MHz

· VCO range: 250MHz to 700MHz

· External feedback for "zero delay" clock regeneration

· Cycle-to-cycle jitter: 25ps (maximum)

· Output skew: 25ps (maximum)

· PLL reference zero delay: 50ps ± 100ps

· 3.3V operating supply

· 0°C to 70°C ambient operating temperature

· Industrial temperature information available upon request

· Available in both standard and lead-free RoHs-compliant

packages

HiPerClockSTM

ICS

PLL_SEL

CLK0

nCLK0

CLK1

nCLK1

CLK_SEL

FB_IN

nFB_IN

SEL0

SEL1

MR

0

1

PLL

0

1

÷4, ÷8

Q0

nQ0

Q1

nQ1

Q2

nQ2

ICS8633-01

28-Lead, 209-MIL SSOP

5.3mm x 10.2mm x 1.75mm body package

F Package

Top View

PLL_SEL

V

CC

SEL0

SEL1

CLK0

nCLK0

CLK1

nCLK1

CLK_SEL

MR

V

CC

nFB_IN

FB_IN

V

EE

V

CCA

V

EE

V

EE

V

CCO

V

CCO

Q2

nQ2

Q1

nQ1

Vcco

Vcco

Q0

nQ0

V

EE

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

8633AF-01

www.icst.com/products/hiperclocks.html

REV. A JANUARY 26, 2006

2

Integrated

Circuit

Systems, Inc.

ICS8633-01

1-

TO

-3 D

IFFERENTIAL

-

TO

-3.3V LVPECL

Z

ERO

D

ELAY

B

UFFER

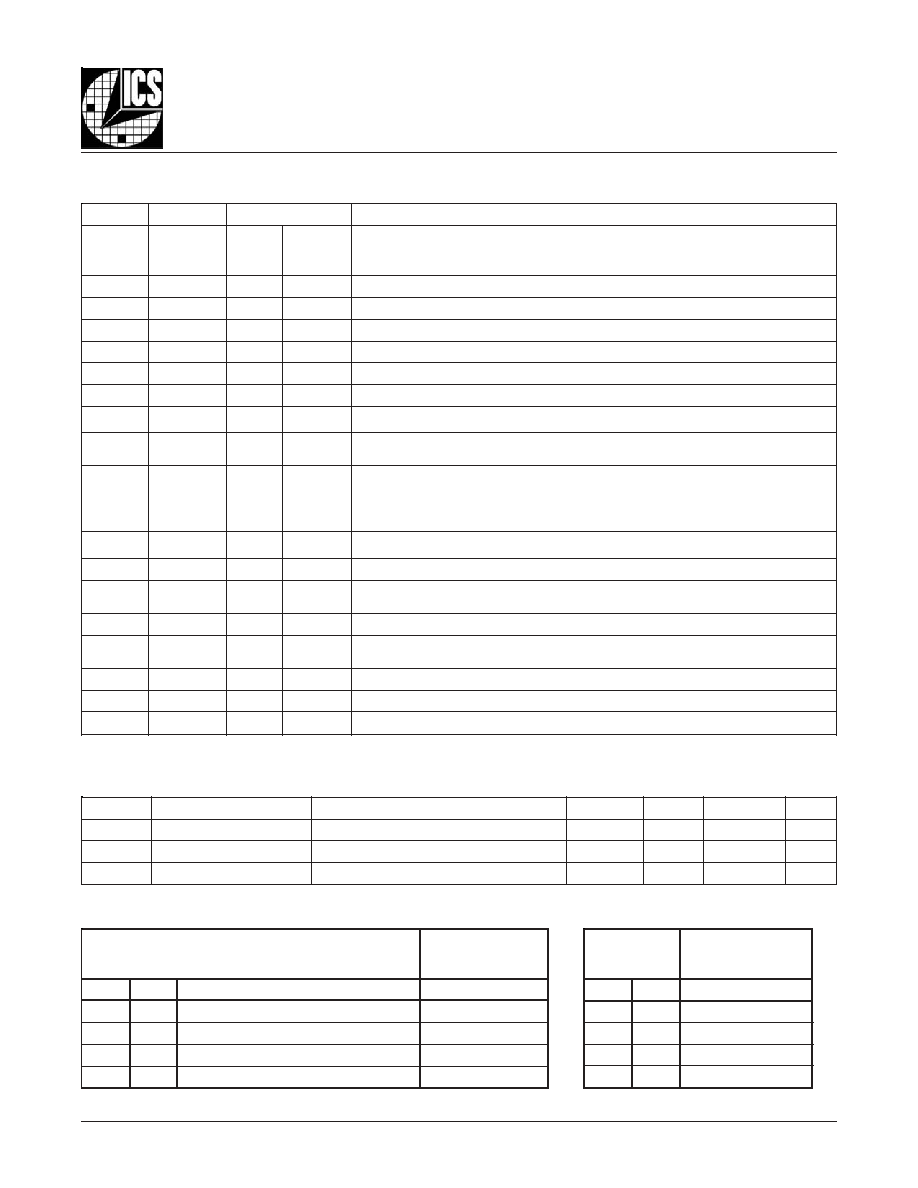

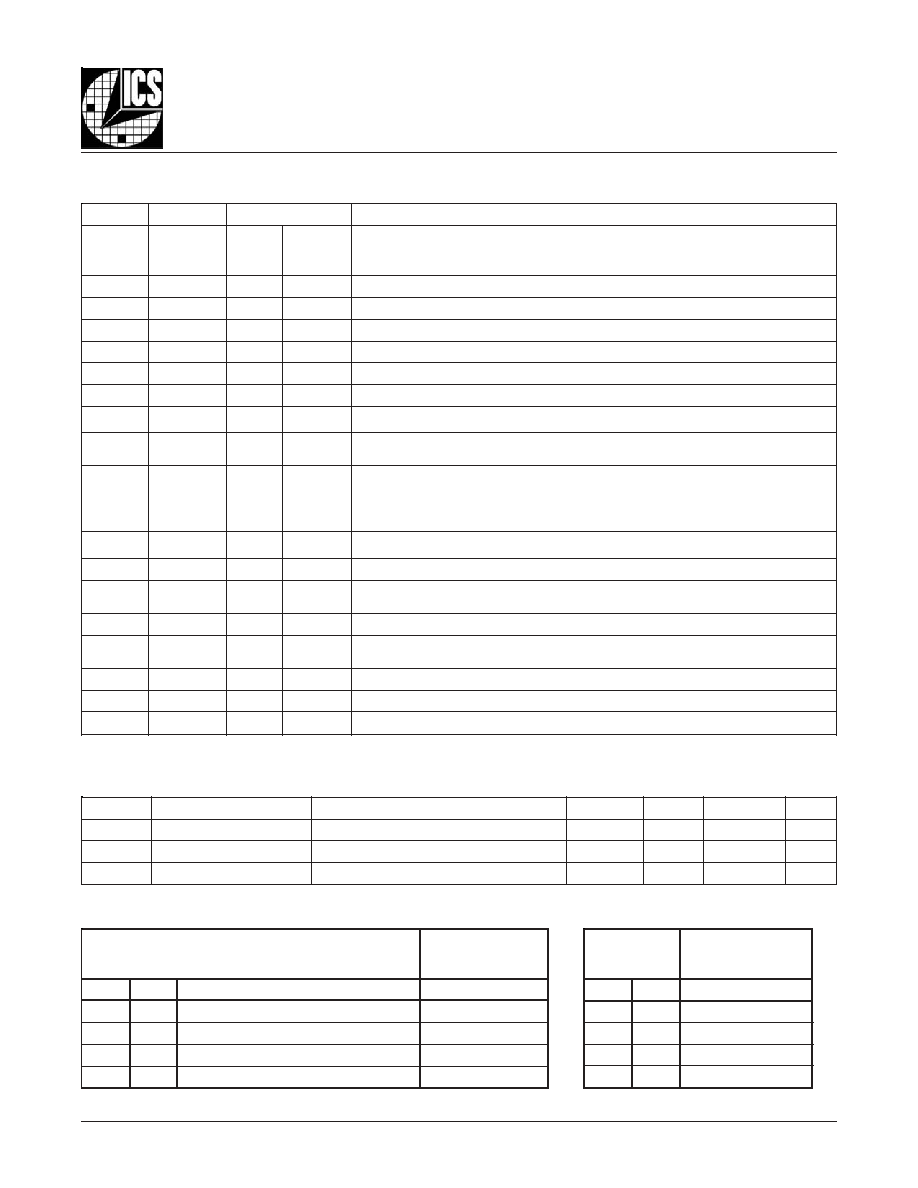

T

ABLE

1. P

IN

D

ESCRIPTIONS

T

ABLE

2. P

IN

C

HARACTERISTICS

r

e

b

m

u

N

e

m

a

N

e

p

y

T

n

o

i

t

p

i

r

c

s

e

D

1

L

E

S

_

L

L

P

t

u

p

n

I

p

u

ll

u

P

.

s

r

e

d

i

v

i

d

e

h

t

o

t

t

u

p

n

i

e

h

t

s

a

k

c

o

l

c

e

c

n

e

r

e

f

e

r

e

h

t

d

n

a

L

L

P

e

h

t

n

e

e

w

t

e

b

s

t

c

e

l

e

S

/

S

O

M

C

V

L

.

k

c

o

l

c

e

c

n

e

r

e

f

e

r

s

t

c

e

l

e

s

,

W

O

L

n

e

h

W

.

L

L

P

s

t

c

e

l

e

s

,

H

G

I

H

n

e

h

W

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

1

1

,

2

V

C

C

r

e

w

o

P

.

s

n

i

p

y

l

p

p

u

s

e

r

o

C

3

0

L

E

S

t

u

p

n

I

n

w

o

d

ll

u

P

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

3

e

l

b

a

T

n

i

s

e

u

l

a

v

r

e

d

i

v

i

d

t

u

p

t

u

o

s

e

n

i

m

r

e

t

e

D

4

1

L

E

S

t

u

p

n

I

n

w

o

d

ll

u

P

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

3

e

l

b

a

T

n

i

s

e

u

l

a

v

r

e

d

i

v

i

d

t

u

p

t

u

o

s

e

n

i

m

r

e

t

e

D

5

0

K

L

C

t

u

p

n

I

n

w

o

d

ll

u

P

.

t

u

p

n

i

k

c

o

l

c

l

a

i

t

n

e

r

e

f

f

i

d

g

n

i

t

r

e

v

n

i

-

n

o

N

6

0

K

L

C

n

t

u

p

n

I

p

u

ll

u

P

.

t

u

p

n

i

k

c

o

l

c

l

a

i

t

n

e

r

e

f

f

i

d

g

n

i

t

r

e

v

n

I

7

1

K

L

C

t

u

p

n

I

n

w

o

d

ll

u

P

.

t

u

p

n

i

k

c

o

l

c

l

a

i

t

n

e

r

e

f

f

i

d

g

n

i

t

r

e

v

n

i

-

n

o

N

8

1

K

L

C

n

t

u

p

n

I

p

u

ll

u

P

.

t

u

p

n

i

k

c

o

l

c

l

a

i

t

n

e

r

e

f

f

i

d

g

n

i

t

r

e

v

n

I

9

L

E

S

_

K

L

C

t

u

p

n

I

n

w

o

d

ll

u

P

.

0

K

L

C

n

,

0

K

L

C

s

t

c

e

l

e

s

,

W

O

L

n

e

h

W

.

t

u

p

n

i

t

c

e

l

e

s

k

c

o

l

C

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

.

1

K

L

C

n

,

1

K

L

C

s

t

c

e

l

e

s

,

H

G

I

H

n

e

h

W

0

1

R

M

t

u

p

n

I

n

w

o

d

ll

u

P

t

e

s

e

r

e

r

a

s

r

e

d

i

v

i

d

l

a

n

r

e

t

n

i

e

h

t

,

H

G

I

H

c

i

g

o

l

n

e

h

W

.

t

e

s

e

R

r

e

t

s

a

M

h

g

i

H

e

v

i

t

c

A

o

g

o

t

x

Q

n

s

t

u

p

t

u

o

d

e

t

r

e

v

n

i

e

h

t

d

n

a

w

o

l

o

g

o

t

x

Q

s

t

u

p

t

u

o

e

u

r

t

e

h

t

g

n

i

s

u

a

c

.

d

e

l

b

a

n

e

e

r

a

s

t

u

p

t

u

o

e

h

t

d

n

a

s

r

e

d

i

v

i

d

l

a

n

r

e

t

n

i

e

h

t

,

W

O

L

c

i

g

o

l

n

e

h

W

.

h

g

i

h

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

T

T

V

L

/

S

O

M

C

V

L

2

1

N

I

_

B

F

n

t

u

p

n

I

p

u

ll

u

P

.

"

y

a

l

e

d

o

r

e

z

"

h

t

i

w

s

k

c

o

l

c

g

n

i

t

a

r

e

n

e

g

e

r

r

o

f

r

o

t

c

e

t

e

d

e

s

a

h

p

o

t

t

u

p

n

i

k

c

a

b

d

e

e

F

3

1

N

I

_

B

F

t

u

p

n

I

n

w

o

d

ll

u

P

.

"

y

a

l

e

d

o

r

e

z

"

h

t

i

w

s

k

c

o

l

c

g

n

i

t

a

r

e

n

e

g

e

r

r

o

f

r

o

t

c

e

t

e

d

e

s

a

h

p

o

t

t

u

p

n

i

k

c

a

b

d

e

e

F

,

5

1

,

4

1

7

2

,

6

2

V

E

E

r

e

w

o

P

.

s

n

i

p

y

l

p

p

u

s

e

v

i

t

a

g

e

N

7

1

,

6

1

0

Q

,

0

Q

n

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

C

E

P

V

L

.

r

i

a

p

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

D

,

9

1

,

8

1

5

2

,

4

2

V

O

C

C

r

e

w

o

P

.

s

n

i

p

y

l

p

p

u

s

t

u

p

t

u

O

1

2

,

0

2

1

Q

,

1

Q

n

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

C

E

P

V

L

.

r

i

a

p

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

D

3

2

,

2

2

2

Q

,

2

Q

n

t

u

p

t

u

O

.

s

l

e

v

e

l

e

c

a

f

r

e

t

n

i

L

C

E

P

V

L

.

r

i

a

p

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

D

8

2

V

A

C

C

r

e

w

o

P

.

n

i

p

y

l

p

p

u

s

g

o

l

a

n

A

:

E

T

O

N

p

u

ll

u

P

d

n

a

n

w

o

d

ll

u

P

.

s

e

u

l

a

v

l

a

c

i

p

y

t

r

o

f

,

s

c

i

t

s

i

r

e

t

c

a

r

a

h

C

n

i

P

,

2

e

l

b

a

T

e

e

S

.

s

r

o

t

s

i

s

e

r

t

u

p

n

i

l

a

n

r

e

t

n

i

o

t

r

e

f

e

r

s

t

u

p

n

I

s

t

u

p

t

u

O

1

=

L

E

S

_

L

L

P

e

d

o

M

e

l

b

a

n

E

L

L

P

1

L

E

S

0

L

E

S

*

)

z

H

M

(

e

g

n

a

R

y

c

n

e

u

q

e

r

F

e

c

n

e

r

e

f

e

R

2

Q

n

:

0

Q

n

,

2

Q

:

0

Q

0

0

0

0

7

-

0

5

2

1

÷

0

1

0

5

3

-

5

2

1

1

÷

1

0

5

7

1

-

5

.

2

6

1

÷

1

1

5

.

7

8

-

5

2

.

1

3

1

÷

s

i

e

v

o

b

a

s

n

o

i

t

a

r

u

g

i

f

n

o

c

ll

a

r

o

f

e

g

n

a

r

y

c

n

e

u

q

e

r

f

O

C

V

:

E

T

O

N

*

.

z

H

M

0

0

7

o

t

z

H

M

0

5

2

s

t

u

p

n

I

s

t

u

p

t

u

O

0

=

L

E

S

_

L

L

P

e

d

o

M

s

s

a

p

y

B

L

L

P

1

L

E

S

0

L

E

S

2

Q

n

:

0

Q

n

,

2

Q

:

0

Q

0

0

4

÷

0

1

4

÷

1

0

4

÷

1

1

8

÷

T

ABLE

3A. C

ONTROL

I

NPUT

F

UNCTION

T

ABLE

T

ABLE

3B. PLL B

YPASS

F

UNCTION

T

ABLE

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

C

N

I

e

c

n

a

t

i

c

a

p

a

C

t

u

p

n

I

4

F

p

R

P

U

L

L

U

P

r

o

t

s

i

s

e

R

p

u

ll

u

P

t

u

p

n

I

1

5

k

R

N

W

O

D

L

L

U

P

r

o

t

s

i

s

e

R

n

w

o

d

ll

u

P

t

u

p

n

I

1

5

k

8633AF-01

www.icst.com/products/hiperclocks.html

REV. A JANUARY 26, 2006

3

Integrated

Circuit

Systems, Inc.

ICS8633-01

1-

TO

-3 D

IFFERENTIAL

-

TO

-3.3V LVPECL

Z

ERO

D

ELAY

B

UFFER

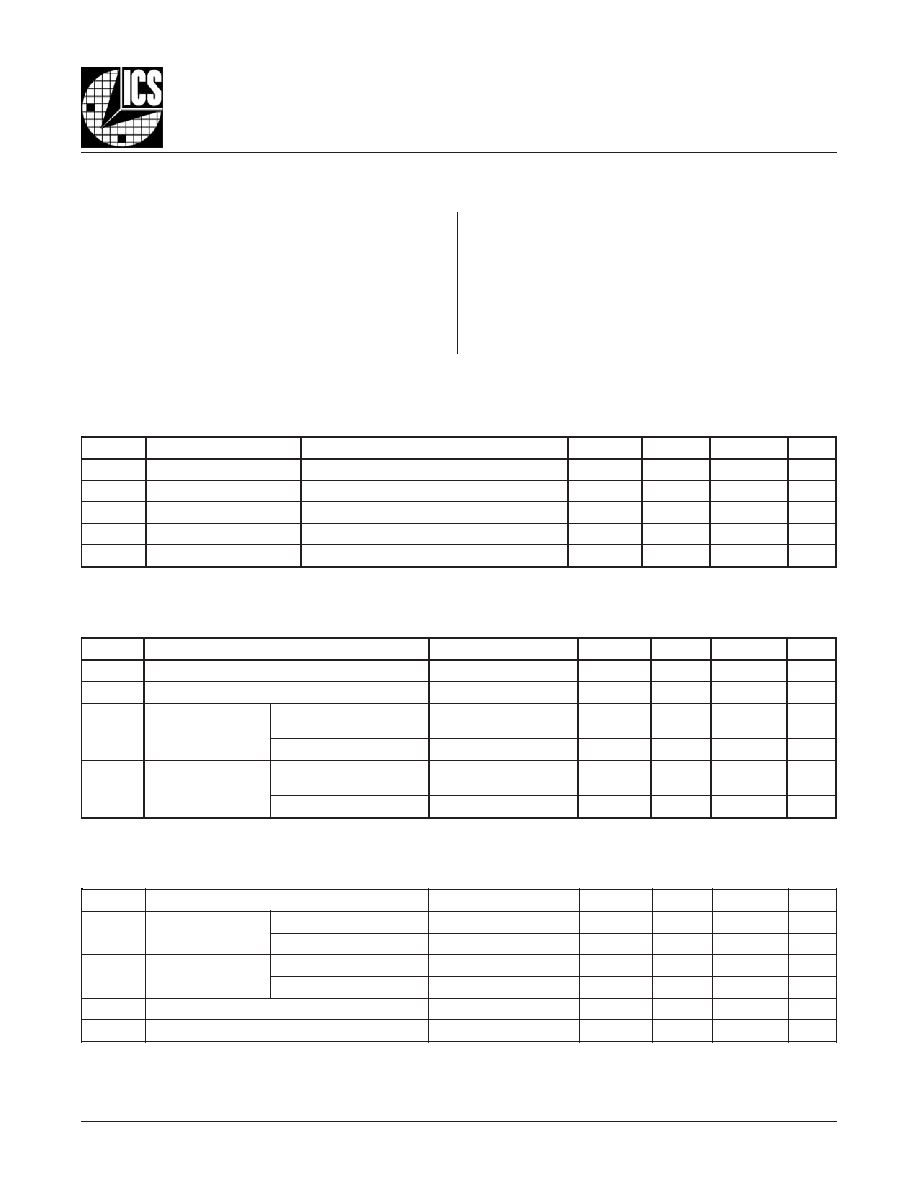

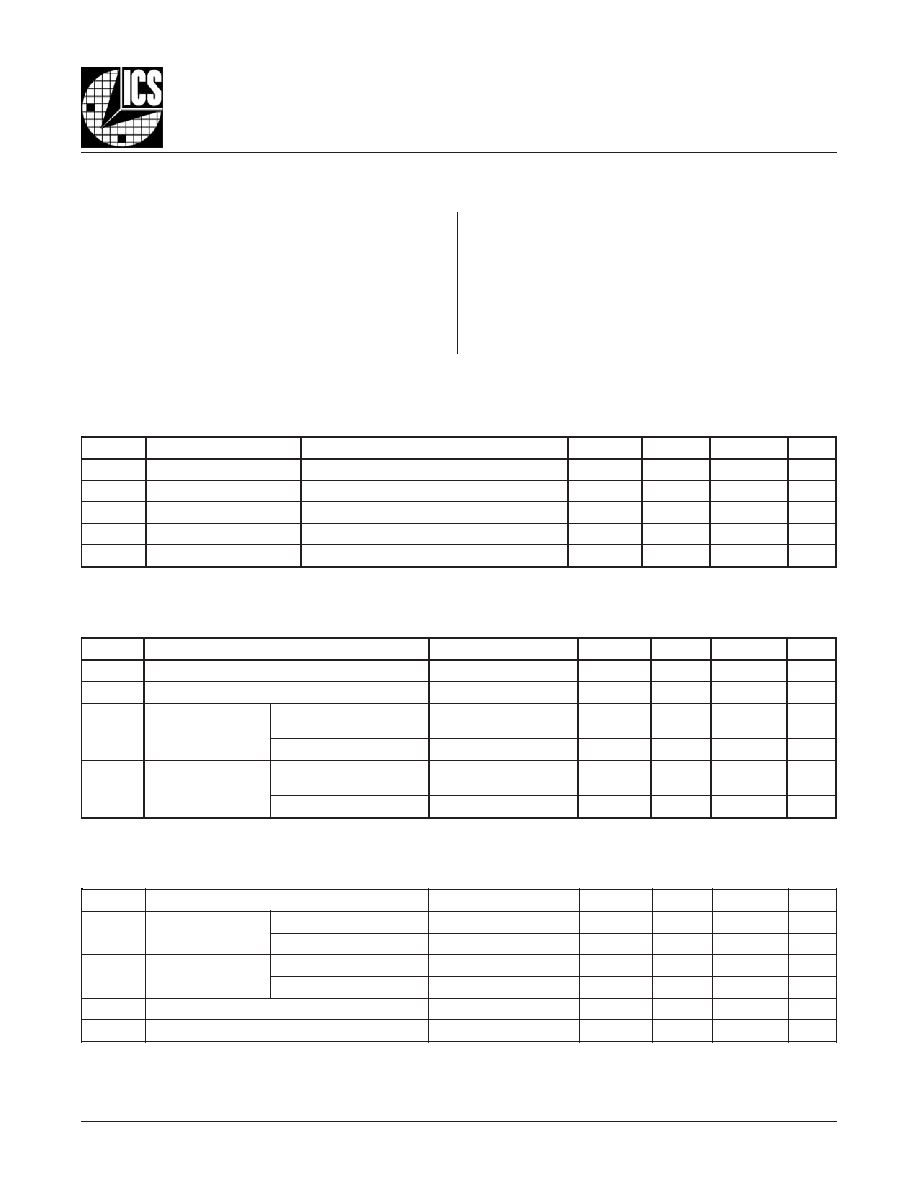

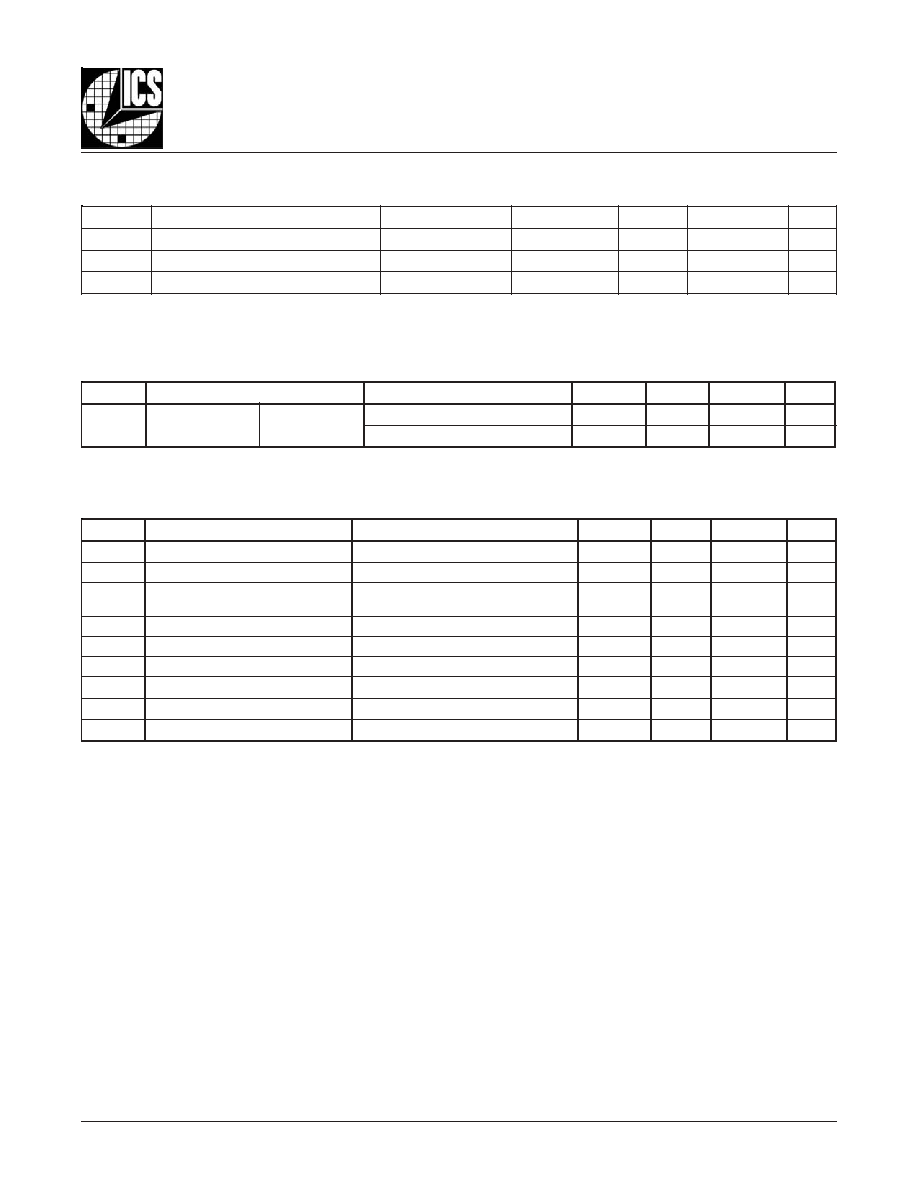

T

ABLE

4A. P

OWER

S

UPPLY

DC C

HARACTERISTICS

,

V

CC

= V

CCA

= V

CCO

= 3.3V±5%, T

A

= 0°C

TO

70°C

T

ABLE

4B. LVCMOS/LVTTL DC C

HARACTERISTICS

,

V

CC

= V

CCA

= V

CCO

= 3.3V±5%, T

A

= 0°C

TO

70°C

T

ABLE

4C. D

IFFERENTIAL

DC C

HARACTERISTICS

,

V

CC

= V

CCA

= V

CCO

= 3.3V±5%, T

A

= 0°C

TO

70°C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

H

I

e

g

a

t

l

o

V

h

g

i

H

t

u

p

n

I

2

V

C

C

3

.

0

+

V

V

L

I

e

g

a

t

l

o

V

w

o

L

t

u

p

n

I

3

.

0

-

8

.

0

V

I

H

I

t

n

e

r

r

u

C

h

g

i

H

t

u

p

n

I

,

1

L

E

S

,

0

L

E

S

R

M

,

L

E

S

_

K

L

C

V

C

C

V

=

N

I

V

5

6

4

.

3

=

0

5

1

A

µ

L

E

S

_

L

L

P

V

C

C

V

=

N

I

V

5

6

4

.

3

=

5

A

µ

I

L

I

t

n

e

r

r

u

C

w

o

L

t

u

p

n

I

,

1

L

E

S

,

0

L

E

S

R

M

,

L

E

S

_

K

L

C

V

C

C

V

,

V

5

6

4

.

3

=

N

I

V

0

=

5

-

A

µ

L

E

S

_

L

L

P

V

C

C

V

,

V

5

6

4

.

3

=

N

I

V

0

=

0

5

1

-

A

µ

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

I

H

I

t

n

e

r

r

u

C

h

g

i

H

t

u

p

n

I

N

I

_

B

F

,

1

K

L

C

,

0

K

L

C

V

C

C

V

=

N

I

V

5

6

4

.

3

=

0

5

1

A

µ

N

I

_

B

F

n

,

1

K

L

C

n

,

0

K

L

C

n

V

C

C

V

=

N

I

V

5

6

4

.

3

=

5

A

µ

I

L

I

t

n

e

r

r

u

C

w

o

L

t

u

p

n

I

N

I

_

B

F

,

1

K

L

C

,

0

K

L

C

V

C

C

V

,

V

5

6

4

.

3

=

N

I

V

0

=

5

-

A

µ

N

I

_

B

F

n

,

1

K

L

C

n

,

0

K

L

C

n

V

C

C

V

,

V

5

6

4

.

3

=

N

I

V

0

=

0

5

1

-

A

µ

V

P

P

e

g

a

t

l

o

V

t

u

p

n

I

k

a

e

P

-

o

t

-

k

a

e

P

5

1

.

0

3

.

1

V

V

R

M

C

2

,

1

E

T

O

N

;

e

g

a

t

l

o

V

t

u

p

n

I

e

d

o

M

n

o

m

m

o

C

V

E

E

5

.

0

+

V

C

C

5

8

.

0

-

V

s

i

1

K

L

C

n

,

1

K

L

C

d

n

a

0

K

L

C

n

,

0

K

L

C

r

o

f

e

g

a

t

l

o

v

t

u

p

n

i

m

u

m

i

x

a

m

e

h

t

,

s

n

o

i

t

a

c

il

p

p

a

d

e

d

n

e

e

l

g

n

i

s

r

o

F

:

1

E

T

O

N

V

C

C

.

V

3

.

0

+

V

s

a

d

e

n

i

f

e

d

s

i

e

g

a

t

l

o

v

e

d

o

m

n

o

m

m

o

C

:

2

E

T

O

N

H

I

.

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

C

C

e

g

a

t

l

o

V

y

l

p

p

u

S

e

r

o

C

5

3

1

.

3

3

.

3

5

6

4

.

3

V

V

A

C

C

e

g

a

t

l

o

V

y

l

p

p

u

S

g

o

l

a

n

A

5

3

1

.

3

3

.

3

5

6

4

.

3

V

V

O

C

C

e

g

a

t

l

o

V

y

l

p

p

u

S

t

u

p

t

u

O

5

3

1

.

3

3

.

3

5

6

4

.

3

V

I

E

E

t

n

e

r

r

u

C

y

l

p

p

u

S

r

e

w

o

P

0

5

1

A

m

I

A

C

C

t

n

e

r

r

u

C

y

l

p

p

u

S

g

o

l

a

n

A

5

1

A

m

A

BSOLUTE

M

AXIMUM

R

ATINGS

Supply Voltage, V

CC

4.6V

Inputs, V

I

-0.5V to V

CC

+ 0.5V

Outputs, I

O

Continuous Current

50mA

Surge Current

100mA

Package Thermal Impedance,

JA

49°C/W (0 lfpm)

Storage Temperature, T

STG

-65°C to 150°C

NOTE: Stresses beyond those listed under Absolute

Maximum Ratings may cause permanent damage to the

device. These ratings are stress specifications only. Functional

operation of product at these conditions or any conditions be-

yond those listed in the

DC Characteristics

or

AC Character-

istics

is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect product reliability.

8633AF-01

www.icst.com/products/hiperclocks.html

REV. A JANUARY 26, 2006

4

Integrated

Circuit

Systems, Inc.

ICS8633-01

1-

TO

-3 D

IFFERENTIAL

-

TO

-3.3V LVPECL

Z

ERO

D

ELAY

B

UFFER

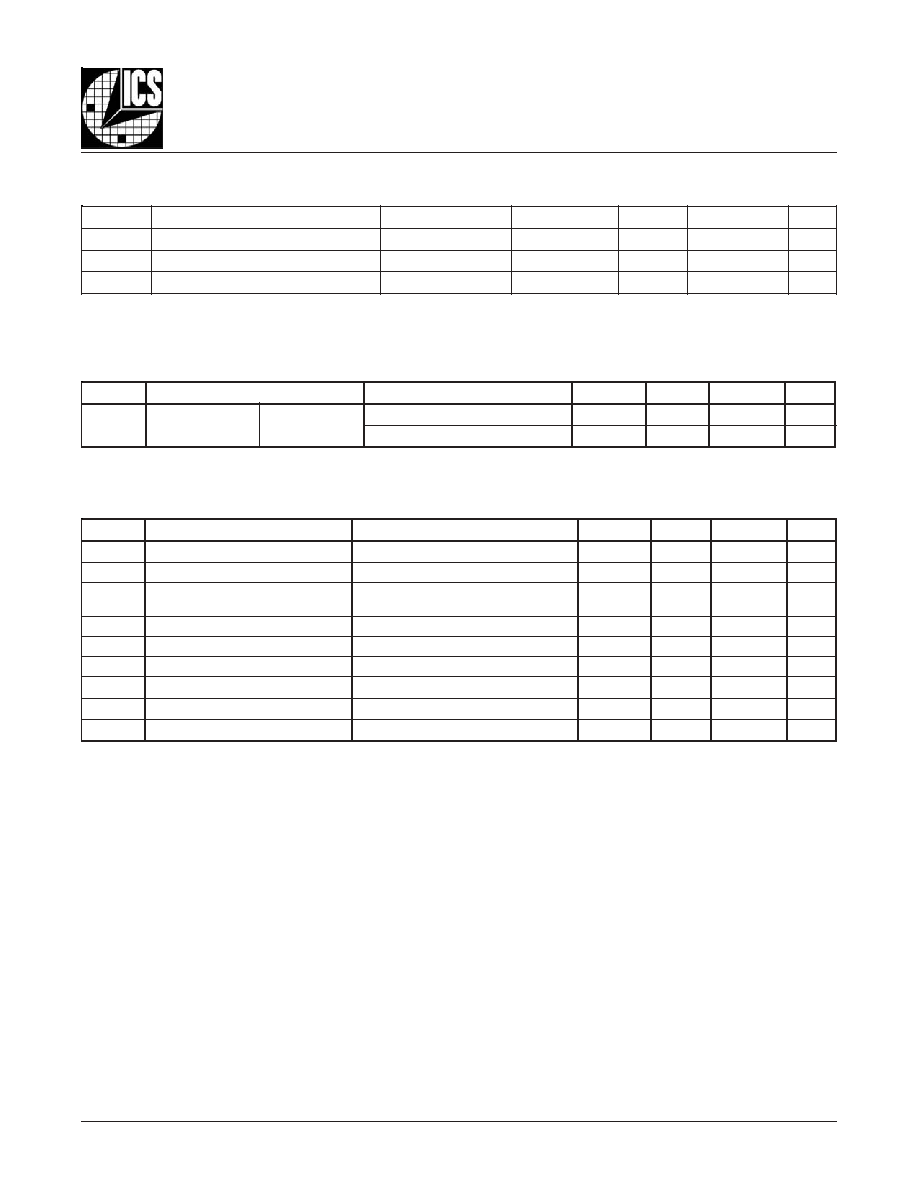

T

ABLE

6. AC C

HARACTERISTICS

,

V

CC

= V

CCA

= V

CCO

= 3.3V±5%, T

A

= 0°C

TO

70°C

T

ABLE

4D. LVPECL DC C

HARACTERISTICS

,

V

CC

= V

CCA

= V

CCO

= 3.3V±5%, T

A

= 0°C

TO

70°C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

H

O

1

E

T

O

N

;

e

g

a

t

l

o

V

h

g

i

H

t

u

p

t

u

O

V

O

C

C

4

.

1

-

V

O

C

C

9

.

0

-

V

V

L

O

1

E

T

O

N

;

e

g

a

t

l

o

V

w

o

L

t

u

p

t

u

O

V

O

C

C

0

.

2

-

V

O

C

C

7

.

1

-

V

V

G

N

I

W

S

g

n

i

w

S

e

g

a

t

l

o

V

t

u

p

t

u

O

k

a

e

P

-

o

t

-

k

a

e

P

6

.

0

0

.

1

V

0

5

h

t

i

w

d

e

t

a

n

i

m

r

e

t

s

t

u

p

t

u

O

:

1

E

T

O

N

V

o

t

O

C

C

.

V

2

-

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

f

X

A

M

y

c

n

e

u

q

e

r

F

t

u

p

t

u

O

0

0

7

z

H

M

t

D

P

1

E

T

O

N

;

y

a

l

e

D

n

o

i

t

a

g

a

p

o

r

P

,

V

0

=

L

E

S

_

L

L

P

z

H

M

0

0

7

8

.

2

9

.

4

s

n

t

)

Ø

(

;

y

a

l

e

D

o

r

e

Z

e

c

n

e

r

e

f

e

R

L

L

P

4

,

2

E

T

O

N

V

3

.

3

=

L

E

S

_

L

L

P

0

5

-

0

5

0

5

1

s

p

t

)

o

(

k

s

4

,

3

E

T

O

N

;

w

e

k

S

t

u

p

t

u

O

5

2

s

p

t

)

c

c

(

t

ij

6

,

4

E

T

O

N

;

r

e

t

t

i

J

e

l

c

y

C

-

o

t

-

e

l

c

y

C

5

2

s

p

t

(

t

ij

)

6

,

5

,

4

E

T

O

N

;

r

e

t

t

i

J

e

s

a

h

P

0

5

±

s

p

t

L

e

m

i

T

k

c

o

L

L

L

P

1

s

m

t

R

t

/

F

e

m

i

T

ll

a

F

/

e

s

i

R

t

u

p

t

u

O

z

H

M

0

5

@

%

0

8

o

t

%

0

2

0

0

3

0

0

7

s

p

c

d

o

e

l

c

y

C

y

t

u

D

t

u

p

t

u

O

7

4

3

5

%

t

a

d

e

r

u

s

a

e

m

s

r

e

t

e

m

a

r

a

p

ll

A

f

X

A

M

.

e

s

i

w

r

e

h

t

o

d

e

t

o

n

s

s

e

l

n

u

.

t

n

i

o

p

g

n

i

s

s

o

r

c

t

u

p

t

u

o

l

a

i

t

n

e

r

e

f

f

i

d

e

h

t

o

t

t

n

i

o

p

g

n

i

s

s

o

r

c

t

u

p

n

i

l

a

i

t

n

e

r

e

f

f

i

d

e

h

t

m

o

r

f

d

e

r

u

s

a

e

M

:

1

E

T

O

N

l

a

n

g

i

s

t

u

p

n

i

k

c

a

b

d

e

e

f

e

g

a

r

e

v

a

e

h

t

d

n

a

k

c

o

l

c

e

c

n

e

r

e

f

e

r

t

u

p

n

i

e

h

t

n

e

e

w

t

e

b

e

c

n

e

r

e

f

f

i

d

e

m

i

t

e

h

t

s

a

d

e

n

i

f

e

D

:

2

E

T

O

N

.

e

l

b

a

t

s

s

i

y

c

n

e

u

q

e

r

f

e

c

n

e

r

e

f

e

r

t

u

p

n

i

e

h

t

d

n

a

d

e

k

c

o

l

s

i

L

L

P

e

h

t

n

e

h

w

.

s

n

o

i

t

i

d

n

o

c

d

a

o

l

l

a

u

q

e

h

t

i

w

d

n

a

e

g

a

t

l

o

v

y

l

p

p

u

s

e

m

a

s

e

h

t

t

a

s

t

u

p

t

u

o

n

e

e

w

t

e

b

w

e

k

s

s

a

d

e

n

i

f

e

D

:

3

E

T

O

N

.

s

t

n

i

o

p

s

s

o

r

c

l

a

i

t

n

e

r

e

f

f

i

d

t

u

p

t

u

o

e

h

t

t

a

d

e

r

u

s

a

e

M

.

5

6

d

r

a

d

n

a

t

S

C

E

D

E

J

h

t

i

w

e

c

n

a

d

r

o

c

c

a

n

i

d

e

n

i

f

e

d

s

i

r

e

t

e

m

a

r

a

p

s

i

h

T

:

4

E

T

O

N

.

d

e

s

u

e

c

r

u

o

s

t

u

p

n

i

e

h

t

n

o

t

n

e

d

n

e

p

e

d

s

i

r

e

t

t

ij

e

s

a

h

P

:

5

E

T

O

N

.

z

H

M

2

2

6

f

o

y

c

n

e

u

q

e

r

f

O

C

V

t

a

d

e

z

i

r

e

t

c

a

r

a

h

C

:

6

E

T

O

N

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

f

N

I

y

c

n

e

u

q

e

r

F

t

u

p

n

I

,

0

K

L

C

n

,

0

K

L

C

1

K

L

C

n

,

1

K

L

C

1

=

L

E

S

_

L

L

P

5

2

.

1

3

0

0

7

z

H

M

0

=

L

E

S

_

L

L

P

0

0

7

z

H

M

T

ABLE

5. I

NPUT

F

REQUENCY

C

HARACTERISTICS

,

V

CC

= V

CCA

= V

CCO

= 3.3V±5%, T

A

= 0°C

TO

70°C

8633AF-01

www.icst.com/products/hiperclocks.html

REV. A JANUARY 26, 2006

5

Integrated

Circuit

Systems, Inc.

ICS8633-01

1-

TO

-3 D

IFFERENTIAL

-

TO

-3.3V LVPECL

Z

ERO

D

ELAY

B

UFFER

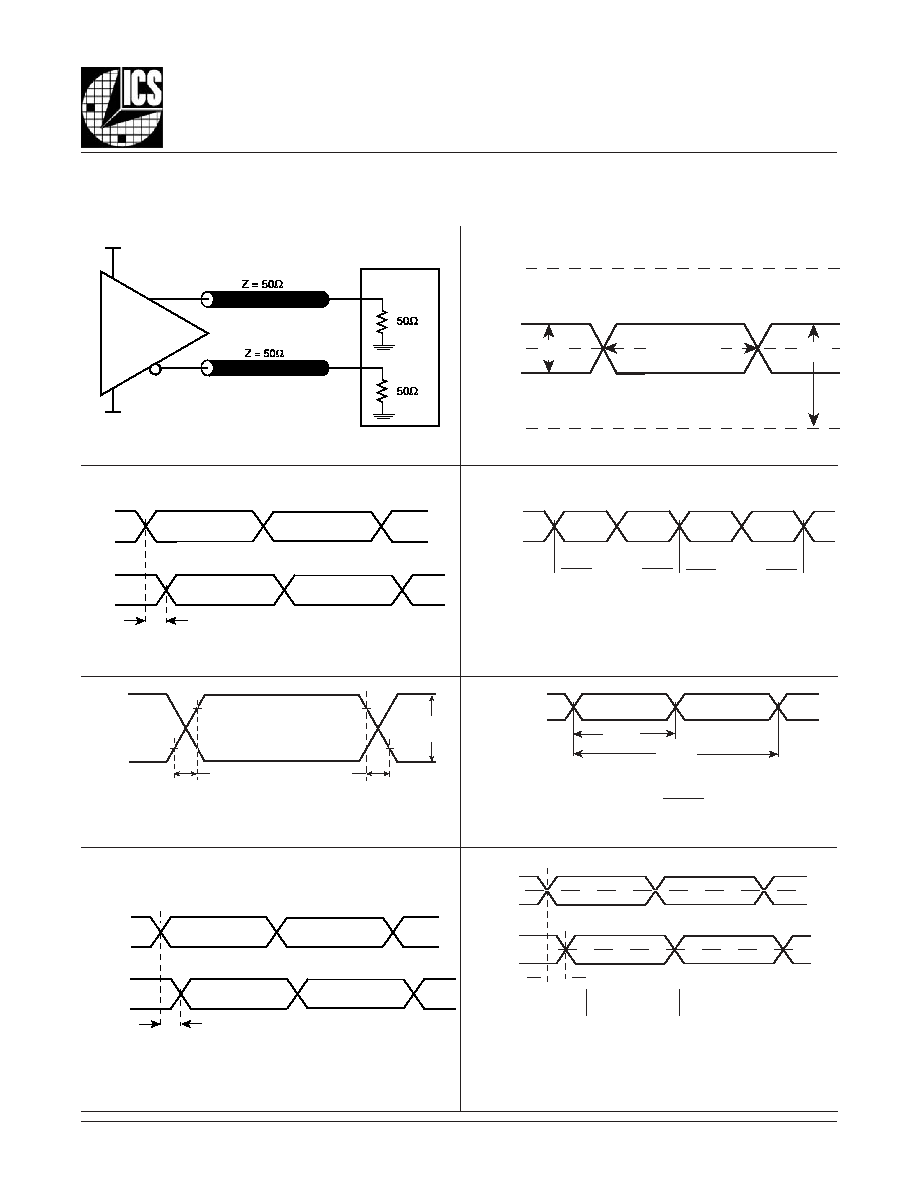

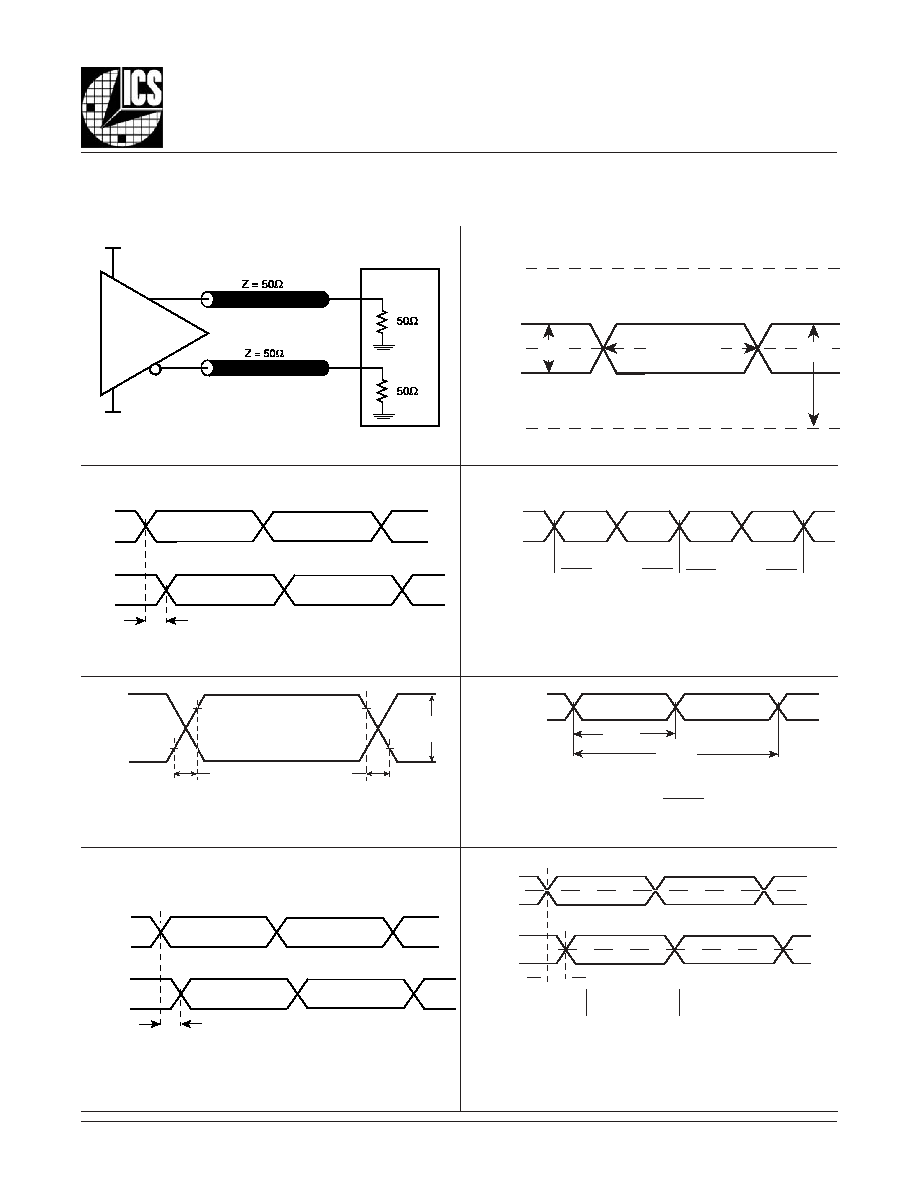

P

ARAMETER

M

EASUREMENT

I

NFORMATION

O

UTPUT

S

KEW

D

IFFERENTIAL

I

NPUT

L

EVEL

3.3V O

UTPUT

L

OAD

AC T

EST

C

IRCUIT

SCOPE

Qx

nQx

LVPECL

2V

C

YCLE

-

TO

-C

YCLE

J

ITTER

-1.3V ± 0.165V

t

sk(o)

nQx

Qx

nQy

Qy

V

CMR

Cross Points

V

PP

V

CC

V

EE

CLK0,

CLK1

nCLK0,

nCLK1

O

UTPUT

R

ISE

/F

ALL

T

IME

O

UTPUT

D

UTY

C

YCLE

/P

ULSE

W

IDTH

/P

ERIOD

P

ROPAGATION

D

ELAY

P

HASE

J

ITTER

& S

TATIC

P

HASE

O

FFSET

Clock

Outputs

20%

80%

80%

20%

t

R

t

F

V

SW I N G

t

PW

t

PERIOD

t

PW

t

PERIOD

odc =

x 100%

Q0:Q2

nQ0:nQ2

t

PD

CLK0,

CLK1

nCLK0,

nCLK1

Q0:Q2

nQ0:nQ2

t

jit(cc) =

t

cycle n

t

cycle n+1

1000 Cycles

t

cycle n

t

cycle n+1

Q0:Q2

nQ0:nQ2

(where

t

(Ø) is any random sample, and

t

(Ø)

mean

is the average

of the sampled cycles measured on controlled edges)

t

(Ø)

mean

= Static Phase Offset

t

(Ø)

V

OH

V

OL

V

OH

V

OL

nCLK0,

nCLK1

nFB_IN

FB_IN

t

jit(Ø) =

t

(Ø) --

t

(Ø)

mean

= Phase Jitter

CLK0,

CLK1

V

CC

,

V

CCA

,

V

CCO

V

EE