Integrated

Circuit

Systems, Inc.

874002AG

www.icst.com/products/hiperclocks.html

REV. A JANUARY 19, 2005

1

ICS874002

PCI E

XPRESS

TM

J

ITTER

A

TTENUATOR

PRELIMINARY

G

ENERAL

D

ESCRIPTION

The ICS874002 is a high performance Differential-

to-LVDS Jitter Attenuator designed for use in PCI

ExpressTM systems. In some PCI ExpressTM

systems, such as those found in desktop PCs,

the PCI ExpressTM clocks are generated from a

low bandwidth, high phase noise PLL frequency synthesizer.

In these systems, a jitter attenuator may be required to

attenuate high frequency random and deterministic jitter

components from the PLL synthesizer and from the system

board. The ICS874002 has 3 PLL bandwidth modes:

200KHz, 400KHz, and 800KHz. The 200KHz mode will pro-

vide maximum jitter attenuation, but with higher PLL tracking

skew and spread spectrum modulation from the motherboard

synthesizer may be attenuated. 400KHz provides an

intermediate bandwidth that can easily track triangular

spread profiles, while providing good jitter attenuation.

800KHz bandwidth provides the best tracking skew and will

pass most spread profiles, but the jitter attenuation will not be

as good as the lower bandwidth modes. Because some 2.5

Gb serdes have x20 multipliers while others have than x25

multipliers, the 874002 can be set for 1:1 mode or 5/4

multiplication mode (i.e. 100MHz input/125MHz output) using

the F_SEL pin.

The ICS874002 uses ICS 3

rd

Generation FemtoClock

TM

PLL technology to achieve the lowest possible phase noise.

The device is packaged in a 20 Lead TSSOP package, making

it ideal for use in space constrained applications such as PCI

ExpressTM add-in cards.

F

EATURES

� (2) Differential LVDS output pairs

� (1) Differential clock input

� CLK and nCLK supports the following input types:

LVPECL, LVDS, LVHSTL, SSTL, HCSL

� Output frequency range: 98MHz - 160MHz

� Input frequency range: 98MHz - 128MHz

� VCO range: 490MHz - 640MHz

� Cycle-to-cycle jitter: 50ps (maximum) design target

� 3.3V operating supply

� 3 bandwidth modes allow the system designer to make jitter

attenuation/tracking skew design trade-offs

� 0�C to 70�C ambient operating temperature

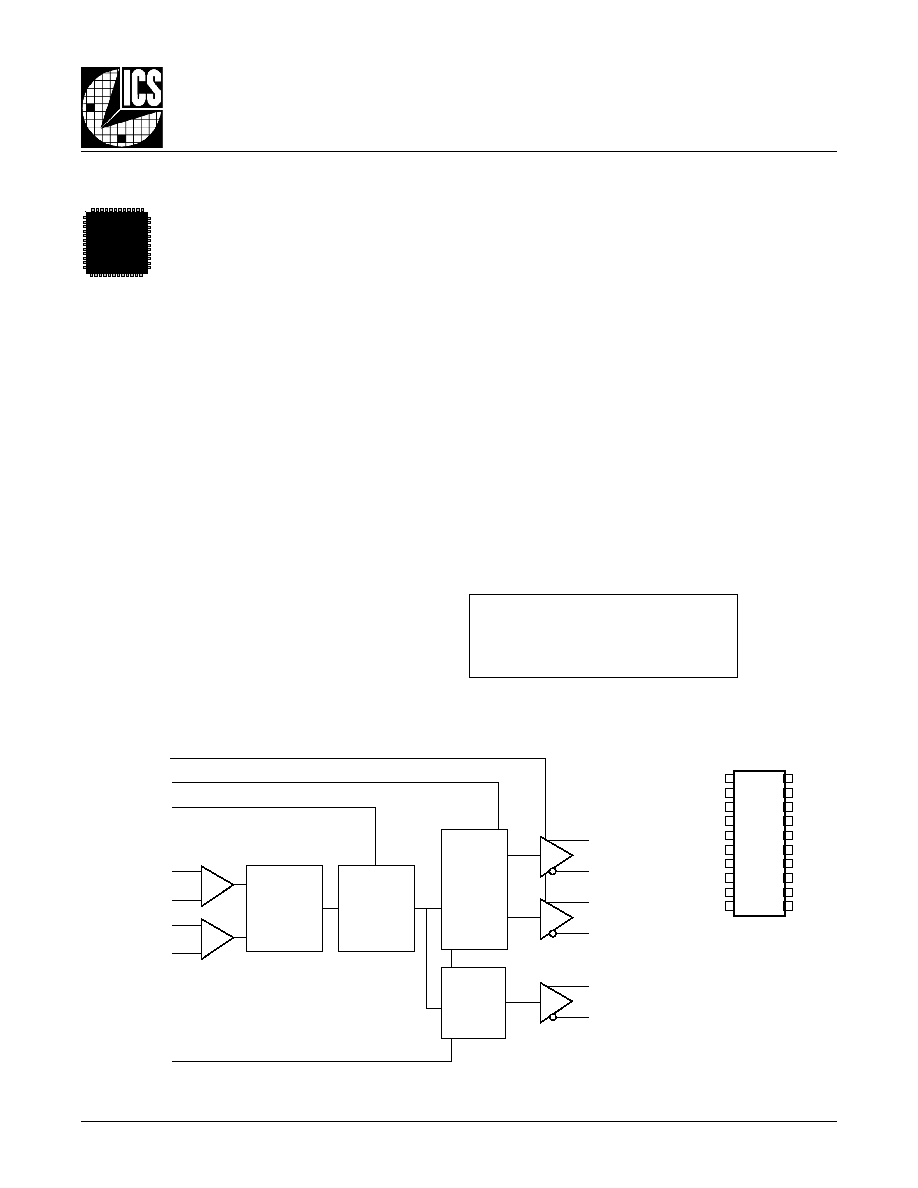

HiPerClockSTM

ICS

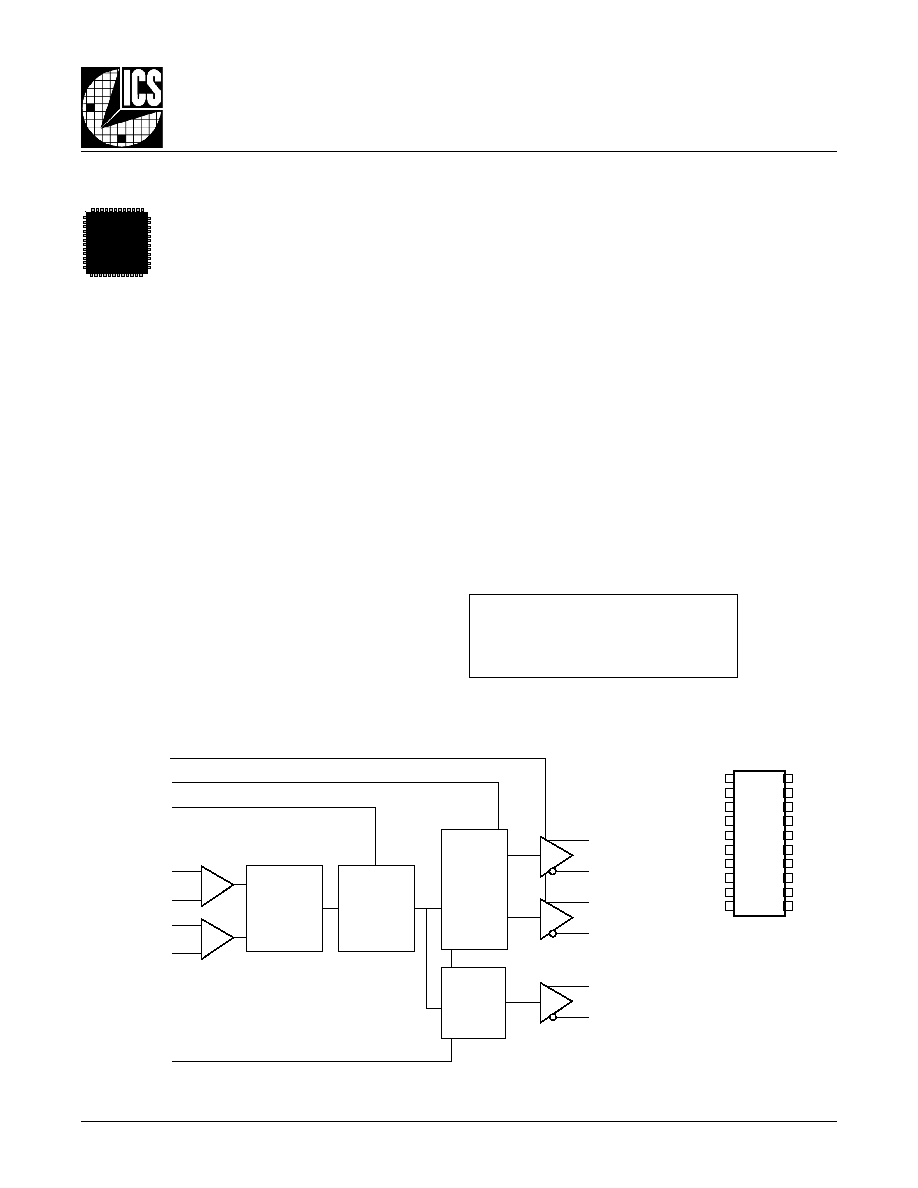

QA0

nQA0

B

LOCK

D

IAGRAM

BW_SEL

0 = PLL Bandwidth: ~200KHz

Float = PLL Bandwidth: ~400KHz (Default)

1 = PLL Bandwidth: ~800KHz

PLL B

ANDWIDTH

0 �5

1 �4

�5

(fixed)

VCO

490 - 640 MHz

Phase

Detector

(default)

PD

OE

F_SEL

BW_SEL

0 = ~200KHz

Float = ~400KHz

1 = ~800KHz

CLK

nCLK

FB_IN

nFB_IN

MR

QA1

nQA1

FB_OUT

nFB_OUT

PD

PD

PD

PU

PU

PU

Float

P

IN

A

SSIGNMENT

ICS874002

20-Lead TSSOP

6.5mm x 4.4mm x 0.92mm

package body

G Package

Top View

nQA0

V

DDO

FB_OUT

nFB_OUT

MR

BW_SEL

nc

V

DDA

F_SEL

V

DD

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

QA0

V

DDO

QA1

nQA1

nFB_IN

FB_IN

GND

nCLK

CLK

OE

The Preliminary Information presented herein represents a product in prototyping or pre-production. The noted characteristics are based on initial

product characterization. Integrated Circuit Systems, Incorporated (ICS) reserves the right to change any circuitry or specifications without notice.

Integrated

Circuit

Systems, Inc.

874002AG

www.icst.com/products/hiperclocks.html

REV. A JANUARY 19, 2005

3

ICS874002

PCI E

XPRESS

TM

J

ITTER

A

TTENUATOR

PRELIMINARY

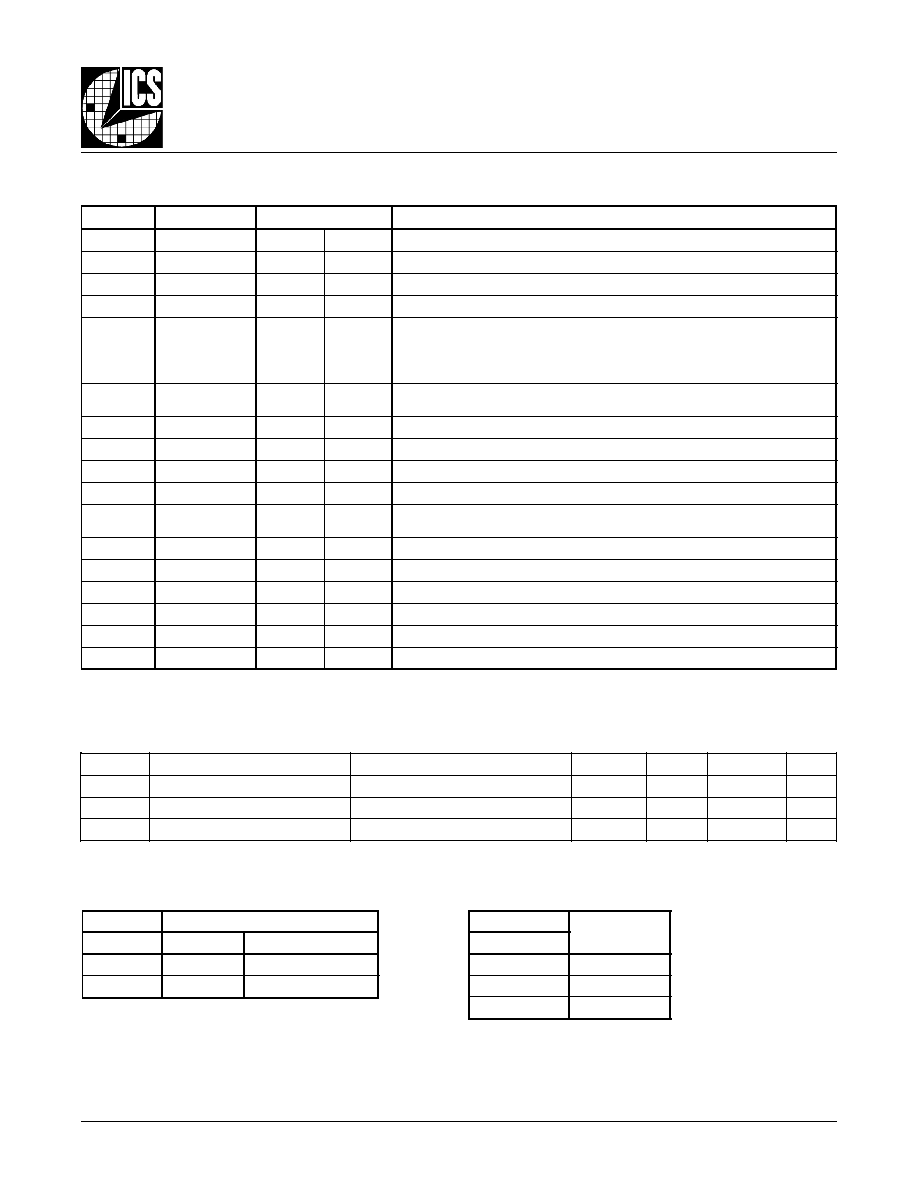

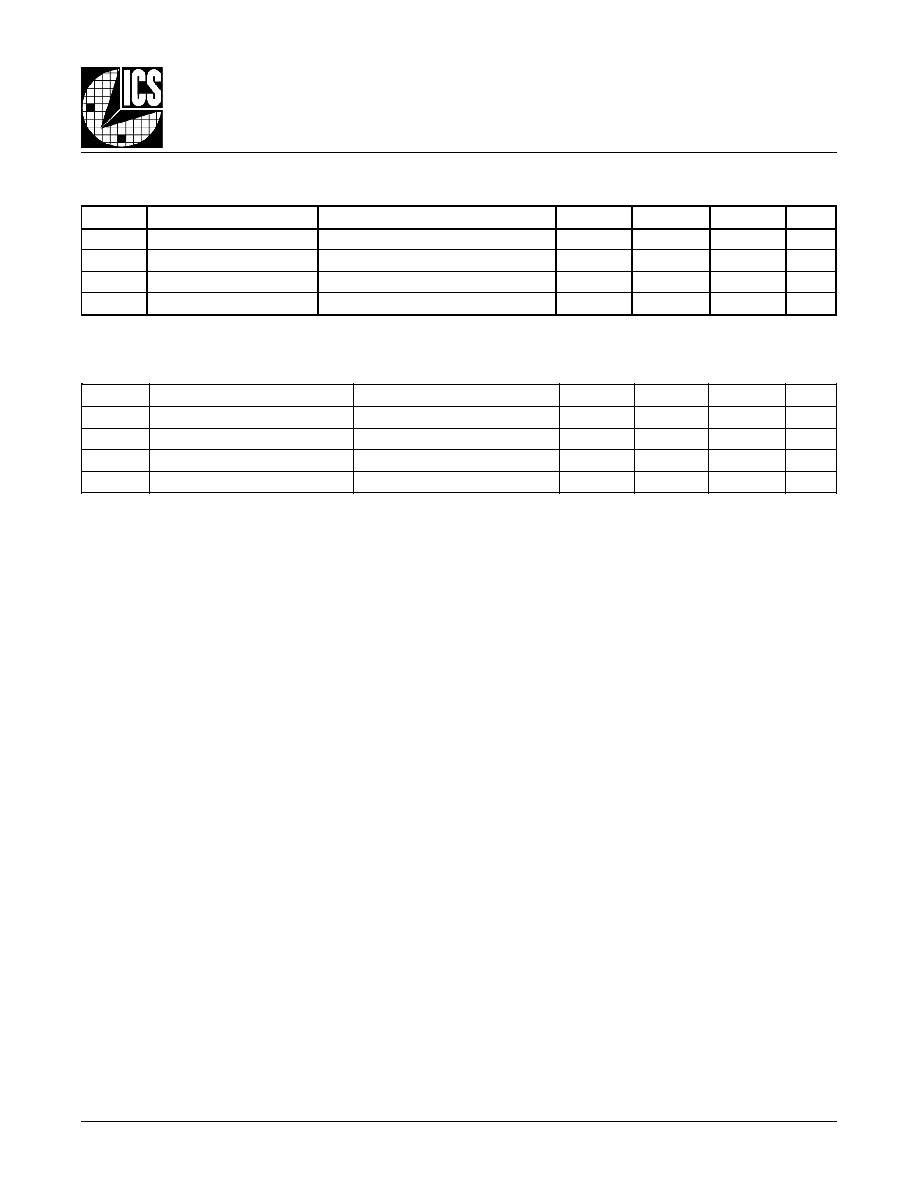

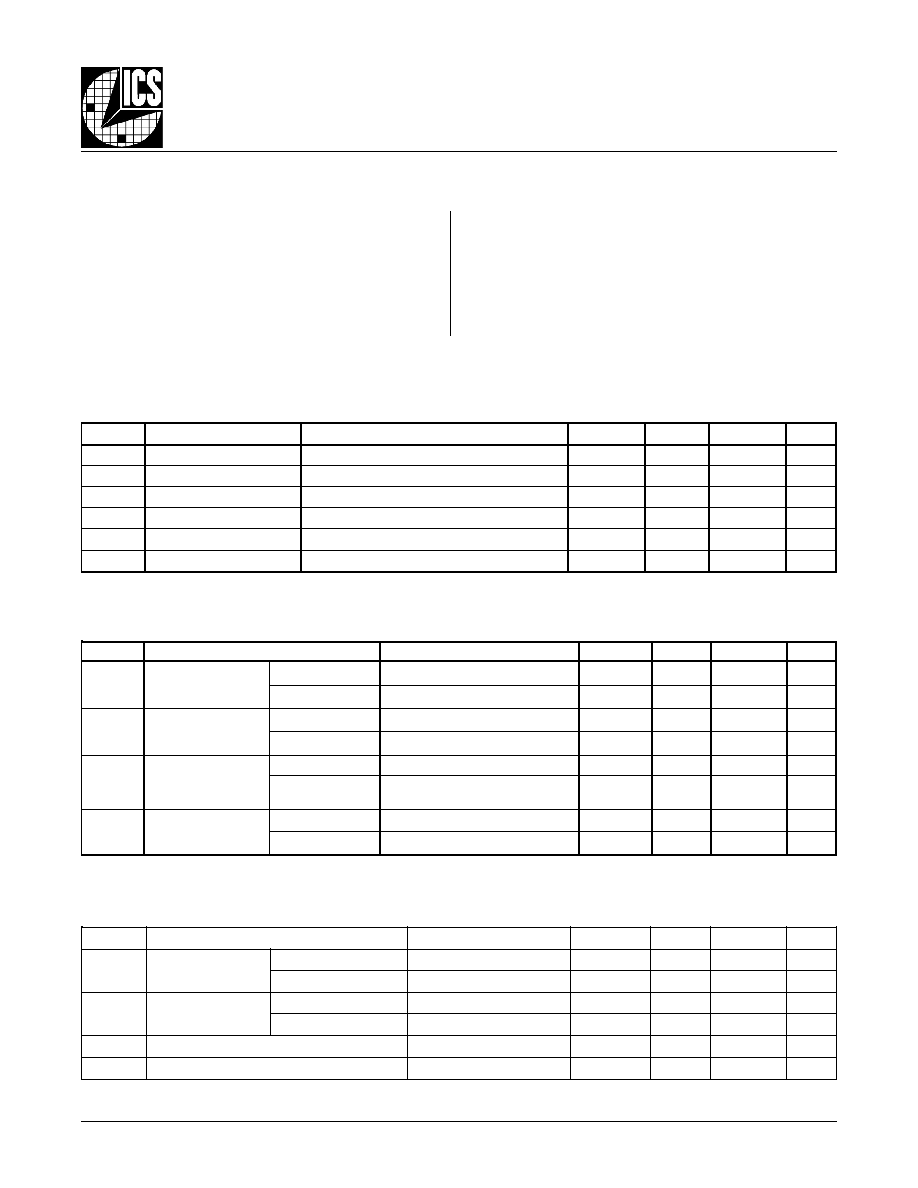

T

ABLE

4B. LVCMOS/LVTTL DC C

HARACTERISTICS

,

V

DD

= V

DDA

= V

DDO

= 3.3V�5%, T

A

= 0�C

TO

70�C

A

BSOLUTE

M

AXIMUM

R

ATINGS

Supply Voltage, V

DD

4.6V

Inputs, V

I

-0.5V to V

DD

+ 0.5 V

Outputs, V

O

-0.5V to V

DD

+ 0.5V

Package Thermal Impedance,

JA

73.2�C/W (0 lfpm)

Storage Temperature, T

STG

-65�C to 150�C

NOTE: Stresses beyond those listed under Absolute

Maximum Ratings may cause permanent damage to the

device. These ratings are stress specifications only. Functional

operation of product at these conditions or any conditions be-

yond those listed in the

DC Characteristics or AC Character-

istics is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect product reliability.

T

ABLE

4A. P

OWER

S

UPPLY

DC C

HARACTERISTICS

,

V

DD

= V

DDA

= V

DDO

= 3.3V�5%, T

A

= 0�C

TO

70�C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

e

r

o

C

5

3

1

.

3

3

.

3

5

6

4

.

3

V

V

A

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

g

o

l

a

n

A

5

3

1

.

3

3

.

3

5

6

4

.

3

V

V

O

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

t

u

p

t

u

O

5

3

1

.

3

3

.

3

5

6

4

.

3

V

I

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

r

e

w

o

P

0

6

A

m

I

A

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

g

o

l

a

n

A

8

A

m

I

O

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

t

u

p

t

u

O

2

8

A

m

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

H

I

e

g

a

t

l

o

V

h

g

i

H

t

u

p

n

I

R

M

,

E

O

,

L

E

S

_

F

2

V

D

D

3

.

0

+

V

L

E

S

_

W

B

V

D

D

3

.

0

-

V

D

D

3

.

0

+

V

V

L

I

e

g

a

t

l

o

V

w

o

L

t

u

p

n

I

R

M

,

E

O

,

L

E

S

_

F

3

.

0

-

8

.

0

V

L

E

S

_

W

B

3

.

0

-

3

.

0

+

V

I

H

I

t

n

e

r

r

u

C

h

g

i

H

t

u

p

n

I

E

O

V

D

D

V

=

N

I

V

5

6

4

.

3

=

5

A

�

,

L

E

S

_

W

B

R

M

,

L

E

S

_

F

V

D

D

V

=

N

I

V

5

6

4

.

3

=

0

5

1

A

�

I

L

I

t

u

p

n

I

t

n

e

r

r

u

C

w

o

L

L

E

S

_

W

B

,

E

O

V

D

D

V

,

V

5

6

4

.

3

=

N

I

V

0

=

0

5

1

-

A

�

R

M

,

L

E

S

_

F

V

D

D

V

,

V

5

6

4

.

3

=

N

I

V

0

=

5

-

A

�

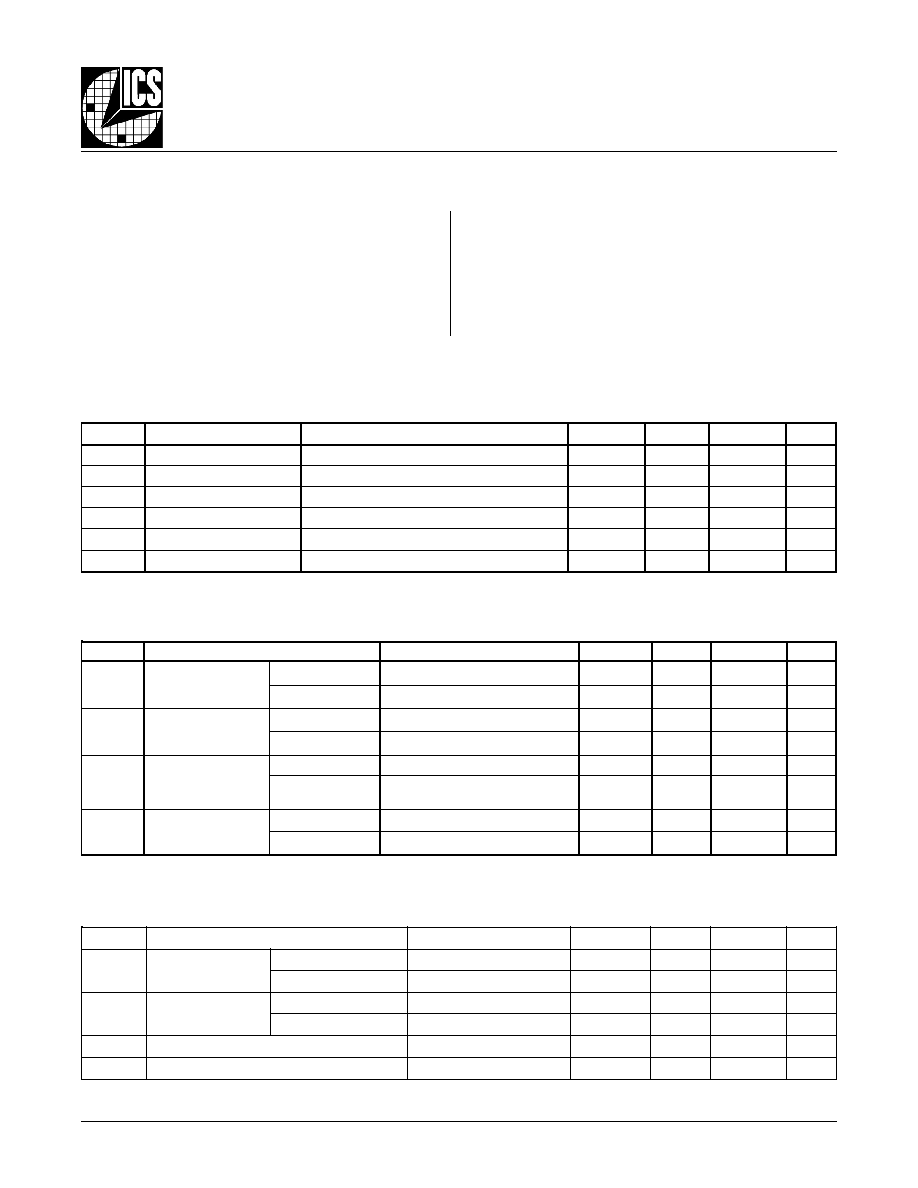

T

ABLE

4C. D

IFFERENTIAL

DC C

HARACTERISTICS

,

V

DD

= V

DDA

= V

DDO

= 3.3V�5%, T

A

= 0�C

TO

70�C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

I

H

I

t

n

e

r

r

u

C

h

g

i

H

t

u

p

n

I

N

I

_

B

F

,

K

L

C

V

D

D

V

=

N

I

V

5

6

4

.

3

=

0

5

1

A

�

N

I

_

B

F

n

,

K

L

C

n

V

D

D

V

=

N

I

V

5

6

4

.

3

=

5

A

�

I

L

I

t

n

e

r

r

u

C

w

o

L

t

u

p

n

I

N

I

_

B

F

,

K

L

C

V

D

D

V

=

N

I

V

5

6

4

.

3

=

0

5

1

A

�

N

I

_

B

F

n

,

K

L

C

n

V

D

D

V

=

N

I

V

5

6

4

.

3

=

0

5

1

-

A

�

V

P

P

e

g

a

t

l

o

V

t

u

p

n

I

k

a

e

P

-

o

t

-

k

a

e

P

5

1

.

0

3

.

1

V

V

R

M

C

2

,

1

E

T

O

N

;

e

g

a

t

l

o

V

t

u

p

n

I

e

d

o

M

n

o

m

m

o

C

5

.

0

+

D

N

G

V

D

D

5

8

.

0

-

V

V

s

a

d

e

n

i

f

e

d

s

i

e

g

a

t

l

o

v

e

d

o

m

n

o

m

m

o

C

:

1

E

T

O

N

H

I

.

V

s

i

N

I

_

B

F

n

,

N

I

_

B

F

d

n

a

K

L

C

n

,

K

L

C

r

o

f

e

g

a

t

l

o

v

t

u

p

n

i

m

u

m

i

x

a

m

e

h

t

,

s

n

o

i

t

a

c

il

p

p

a

d

e

d

n

e

e

l

g

n

i

s

r

o

F

:

2

E

T

O

N

D

D

.

V

3

.

0

+