Integrated

Circuit

Systems, Inc.

ICS9248-151

Third party brands and names are the property of their respective owners.

Block Diagram

9248-151 Rev B 01/29/01

Functionality

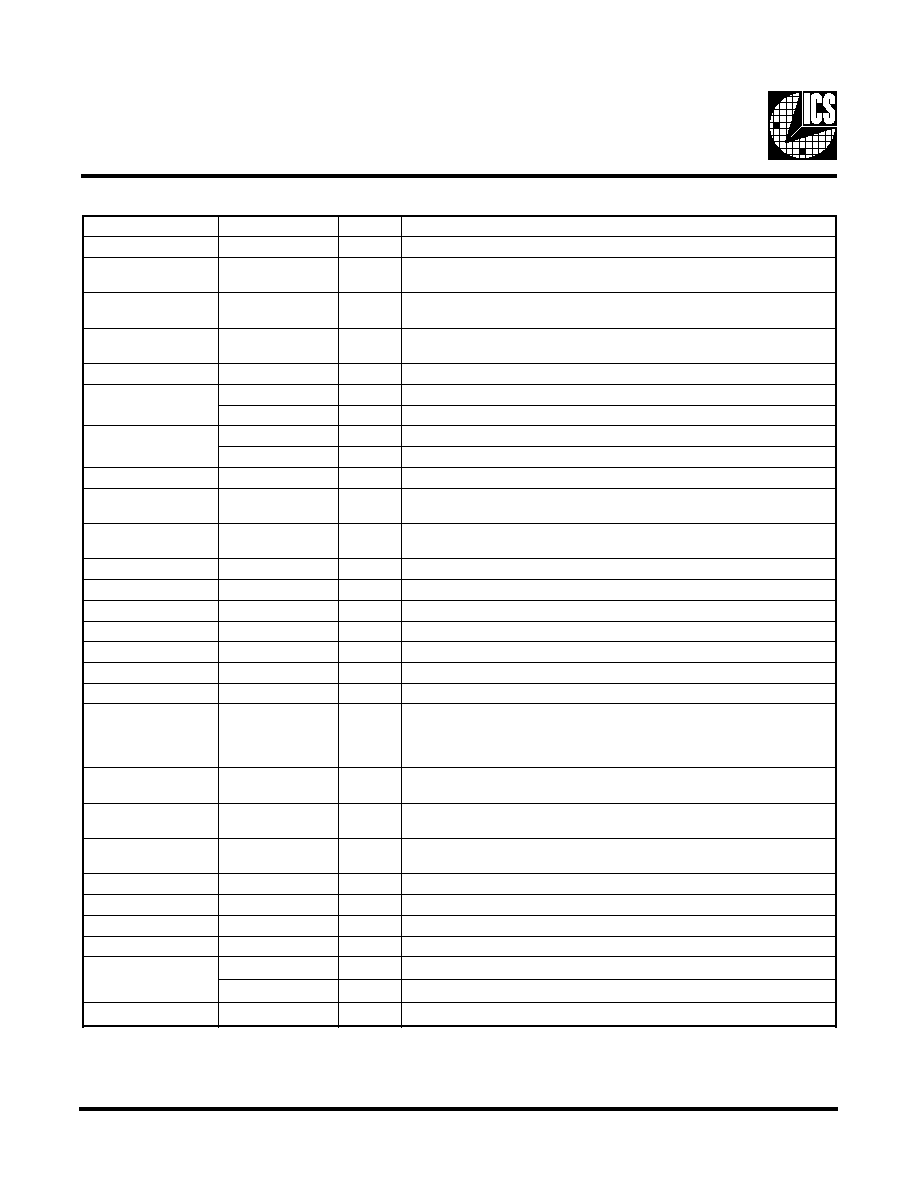

Pin Configuration

48-Pin 300mil SSOP

Recommended Application:

VIA Apollo Pro 266 style chipset.

Output Features:

∑

3 - CPUs @ 2.5V, up to 200MHz.

∑

3 - IOAPIC @ 2.5V, Ω PCI frequency

∑

9 - PCI @ 3.3V,

∑

1 - 48MHz, @ 3.3V fixed.

∑

1 - 24/48MHz @ 3.3V

∑

2 - REF @ 3.3V, 14.318MHz.

∑

3 - AGP @ 3.3V

Features:

∑

Up to 200MHz frequency support

∑

Support power management: PCI, CPU stop

and Power Down.

∑

Spread spectrum for EMI control (0 to -0.5%, ± 0.25%).

∑

Uses external 14.318MHz crystal

Skew Specifications:

∑

CPU ≠ CPU: <175ps

∑

PCI ≠ PCI: <500ps

∑

CPU(early)-PCI: Min=1.0ns, Max=2.5ns

∑

CPU Cycle to cycle jitter: < 250ps

Frequency Generator & Integrated Buffers for Celeron & PII/IIITM

* Internal Pull-up Resistor of 120K to VDD

FS (4:0)

PD#

PCI_STOP#

CPU_STOP#

SDATA

SCLK

PLL2

PLL1

Spread

Spectrum

48MHz

24_48MHz

CPUCLK (1:0)

CPUCLK2/F

IOAPIC (2:0)

AGPCLK (2:0)

PCICLK (7:0)

8

3

3

2

2

PCICLK_F

X1

X2

XTAL

OSC

CPU

DIVDER

IOAPIC

DIVDER

AGP

DIVDER

PCI

DIVDER

Stop

Stop/F

Stop

Control

Logic

Config.

Reg.

/ 2

REF (1:0)

4

S

F

3

S

F

2

S

F

1

S

F

0

S

F

U

P

C

)

z

H

M

(

P

G

A

)

z

H

M

(

K

L

C

I

C

P

)

z

H

M

(

0

0

0

0

0

0

0

.

0

0

2

0

0

.

0

8

0

0

.

0

4

0

0

0

0

1

0

0

.

0

9

1

0

0

.

6

7

0

0

.

8

3

0

0

0

1

0

0

0

.

0

8

1

0

0

.

2

7

0

0

.

6

3

0

0

0

1

1

0

0

.

0

7

1

0

0

.

8

6

0

0

.

4

3

0

0

1

0

0

0

0

.

6

6

1

0

4

.

6

6

0

2

.

3

3

0

0

1

0

1

0

0

.

0

6

1

0

0

.

4

6

0

0

.

2

3

0

0

1

1

0

0

0

.

0

5

1

0

0

.

5

7

0

5

.

7

3

0

0

1

1

1

0

0

.

5

4

1

0

5

.

2

7

5

2

.

6

3

0

1

0

0

0

0

0

.

0

4

1

0

0

.

0

7

0

0

.

5

3

0

1

0

0

1

0

0

.

6

3

1

0

0

.

8

6

0

0

.

4

3

0

1

0

1

0

0

0

.

0

3

1

0

0

.

5

6

0

5

.

2

3

0

1

0

1

1

0

0

.

4

2

1

0

0

.

2

6

0

0

.

1

3

0

1

1

0

0

7

6

.

6

6

7

6

.

6

6

4

3

.

3

3

0

1

1

0

1

0

0

.

0

0

1

7

6

.

6

6

3

3

.

3

3

0

1

1

1

0

0

0

.

8

1

1

7

6

.

8

7

3

3

.

9

3

0

1

1

1

1

3

3

.

3

3

1

7

6

.

6

6

4

3

.

3

3

VDDREF

GND

X1

X2

AVDD48

*FS3/48MHz

*FS2/24_48MHz

GND

PCICLK_F

PCICLK0

PCICLK1

GND

PCICLK2

PCICLK3

VDDPCI

PCICLK4

PCICLK5

PCICLK6

GND

PCICLK7

*FS1

*FS0

AGPCLK0

VDDAGP

REF0

REF1/FS4*

VDDLAPIC

IOAPIC0

IOAPIC1

GND

IOAPIC2

VDDLCPU

GND

CPUCLK0

CPUCLK1

VDDLCPU

GND

CPUCLK2/F

CPU_STOP#*

PCI_STOP#*

PD*

AVDD

GND

SDATA

SCLK

AGPCLK2

AGPCLK1

GND

ICS9248-151

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

ICS reserves the right to make changes in the device data identified in

this publication without further notice. ICS advises its customers to

obtain the latest version of all device data to verify that any

information being relied upon by the customer is current and accurate.

2

ICS9248-151

Third party brands and names are the property of their respective owners.

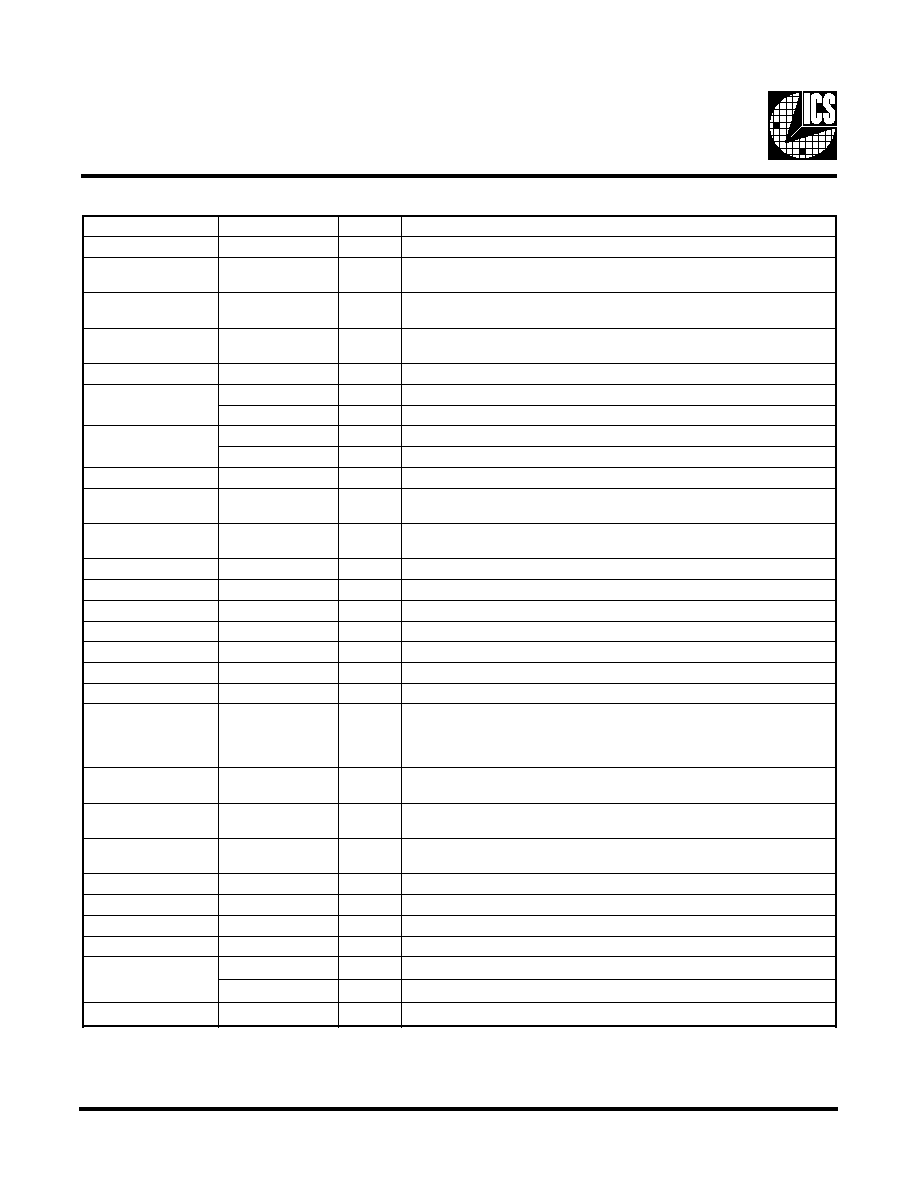

Pin Descriptions

Notes:

1:

Internal Pull-up Resistor of 120K to 3.3V on indicated inputs

2:

Bidirectional input/output pins, input logic levels are latched at internal power-on-reset. Use 10Kohm resistor

to program logic Hi to VDD or GND for logic low.

R

E

B

M

U

N

N

I

P

E

M

A

N

N

I

P

E

P

Y

T

N

O

I

T

P

I

R

C

S

E

D

1

F

E

R

D

D

V

R

W

P

V

3

.

3

l

a

n

i

m

o

n

,

y

l

p

p

u

s

r

e

w

o

p

L

A

T

X

,

f

e

R

,

5

2

,

9

1

,

2

1

,

2

3

4

,

0

4

,

6

3

,

0

3

D

N

G

R

W

P

d

n

u

o

r

G

3

1

X

N

I

k

c

a

b

d

e

e

f

d

n

a

)

F

p

6

3

(

p

a

c

d

a

o

l

l

a

n

r

e

t

n

i

s

a

h

,t

u

p

n

i

l

a

t

s

y

r

C

2

X

m

o

r

f

r

o

t

s

i

s

e

r

4

2

X

T

U

O

d

a

o

l

l

a

n

r

e

t

n

i

s

a

H

.

z

H

M

8

1

3

.

4

1

y

l

l

a

n

i

m

o

n

,t

u

p

t

u

o

l

a

t

s

y

r

C

)

F

p

6

3

(

p

a

c

5

z

H

M

8

4

D

D

V

A

R

W

P

.

e

r

o

c

L

L

P

d

e

x

i

f

d

n

a

s

r

e

f

f

u

b

t

u

p

t

u

o

z

H

M

8

4

&

4

2

r

o

f

r

e

w

o

P

6

3

S

F

N

I

D

D

V

o

t

p

u

-

l

l

u

P

l

a

n

r

e

t

n

I

.t

u

p

n

I

d

e

h

c

t

a

L

.

n

i

p

t

c

e

l

e

s

y

c

n

e

u

q

e

r

F

z

H

M

8

4

T

U

O

k

c

o

l

c

t

u

p

t

u

o

z

H

M

8

4

7

2

S

F

N

I

D

D

V

o

t

p

u

-

l

l

u

P

l

a

n

r

e

t

n

I

.t

u

p

n

I

d

e

h

c

t

a

L

.

n

i

p

t

c

e

l

e

s

y

c

n

e

u

q

e

r

F

z

H

M

8

4

_

4

2

T

U

O

t

u

p

t

u

o

z

H

M

8

4

r

o

4

2

8

z

H

M

8

4

D

N

G

A

R

W

P

.

e

r

o

c

L

L

P

d

e

x

i

f

d

n

a

s

r

e

f

f

u

b

t

u

p

t

u

o

z

H

M

8

4

&

4

2

r

o

f

d

n

u

o

r

G

9

F

_

K

L

C

I

C

P

T

U

O

r

e

w

o

p

r

o

f

#

P

O

T

S

_

I

C

P

y

b

d

e

t

c

e

f

f

a

t

o

n

k

c

o

l

c

I

C

P

g

n

i

n

n

u

r

e

e

r

F

.t

n

e

m

e

g

a

n

a

m

,

4

1

,

6

1

,

7

1

,

8

1

,

0

2

0

1

,

1

1

,

3

1

)

0

:

7

(

K

L

C

I

C

P

T

U

O

w

e

k

s

s

n

2

-

1

h

t

i

w

s

k

c

o

l

c

U

P

C

o

t

s

u

o

n

o

r

e

h

c

n

y

S

.

s

t

u

p

t

u

o

k

c

o

l

c

I

C

P

5

1

I

C

P

D

D

V

R

W

P

V

3

.

3

l

a

n

i

m

o

n

,

K

L

C

I

C

P

d

n

a

F

_

K

L

C

I

C

P

r

o

f

y

l

p

p

u

S

2

2

,

1

2

)

0

:

1

(

S

F

2

,

1

N

I

D

D

V

o

t

p

u

-

l

l

u

P

l

a

n

r

e

t

n

I

.t

u

p

n

I

d

e

h

c

t

a

L

.

n

i

p

t

c

e

l

e

s

y

c

n

e

u

q

e

r

F

3

2

,

6

2

,

7

2

)

0

:

2

(

K

L

C

P

G

A

T

U

O

.

d

e

p

p

o

t

s

e

b

t

o

n

y

a

m

e

s

e

h

T

.

I

C

P

X

2

s

a

d

e

n

i

f

e

d

s

t

u

p

t

u

o

P

G

A

4

2

P

G

A

D

D

V

R

W

P

s

k

c

o

l

c

P

G

A

r

o

f

r

e

w

o

P

8

2

K

L

C

S

N

I

I

f

o

t

u

p

n

i

k

c

o

l

C

2

t

u

p

n

i

t

n

a

r

e

l

o

t

V

5

,t

u

p

n

i

C

9

2

A

T

A

D

S

O

/

I

I

r

o

f

n

i

p

a

t

a

D

2

t

n

a

r

e

l

o

t

V

5

y

r

t

i

u

c

r

i

c

C

1

3

D

D

V

A

R

W

P

V

3

.

3

e

r

o

c

L

L

P

r

o

f

r

e

w

o

P

2

3

#

D

P

N

I

e

h

t

n

w

o

d

r

e

w

o

p

o

t

d

e

s

u

n

i

p

t

u

p

n

i

w

o

l

e

v

i

t

c

a

s

u

o

n

o

r

h

c

n

y

s

A

d

e

l

b

a

s

i

d

e

r

a

s

k

c

o

l

c

l

a

n

r

e

t

n

i

e

h

T

.

e

t

a

t

s

r

e

w

o

p

w

o

l

a

o

t

n

i

e

c

i

v

e

d

e

h

t

f

o

y

c

n

e

t

a

l

e

h

T

.

d

e

p

p

o

t

s

e

r

a

l

a

t

s

y

r

c

e

h

t

d

n

a

O

C

V

e

h

t

d

n

a

.

s

m

3

n

a

h

t

r

e

t

a

e

r

g

e

b

t

o

n

l

l

i

w

n

w

o

d

r

e

w

o

p

3

3

#

P

O

T

S

_

I

C

P

1

N

I

e

l

i

b

o

m

n

I

(

w

o

l

t

u

p

n

i

n

e

h

w

,l

e

v

e

l

0

c

i

g

o

l

t

a

s

k

c

o

l

c

K

L

C

I

C

P

s

t

l

a

H

)

0

=

E

D

O

M

,

e

d

o

m

4

3

#

P

O

T

S

_

U

P

C

N

I

n

e

h

w

l

e

v

e

l

"

0

"

c

i

g

o

l

t

a

s

K

L

C

U

P

C

s

t

l

a

h

t

u

p

n

i

s

u

o

n

o

r

h

c

n

y

s

a

s

i

h

T

.

w

o

l

n

e

v

i

r

d

5

3

F

/

2

K

L

C

U

P

C

T

U

O

g

n

i

n

n

u

r

e

e

r

f

r

o

#

P

O

T

S

_

U

P

C

h

g

u

o

r

h

t

e

l

b

a

p

p

o

t

s

r

e

h

t

i

e

K

L

C

U

P

C

I

n

o

g

n

i

d

n

e

p

e

d

2

e

l

b

a

p

p

o

t

S

=

1

g

n

i

n

n

u

R

e

e

r

F

=

0

,

n

o

i

t

c

e

l

e

s

C

1

4

,

7

3

U

P

C

L

D

D

V

R

W

P

l

a

n

i

m

o

n

V

5

.

2

s

k

c

o

l

c

U

P

C

r

o

f

y

l

p

p

u

S

9

3

,

8

3

)

0

:

1

(

K

L

C

U

P

C

T

U

O

w

o

L

=

#

P

O

T

S

_

U

P

C

f

i

w

o

L

,

s

t

u

p

t

u

o

k

c

o

l

c

U

P

C

5

4

,

4

4

,

2

4

)

0

:

2

(

C

I

P

A

O

I

T

U

O

C

I

P

A

O

I

.

C

I

P

A

O

I

L

D

D

V

y

b

d

e

r

e

w

o

P

z

H

M

8

1

3

.

4

1

.

t

u

p

t

u

o

k

c

o

l

c

6

4

C

I

P

A

L

D

D

V

R

W

P

l

a

n

i

m

o

n

V

5

.

2

,

C

I

P

A

O

I

r

o

f

y

l

p

p

u

S

7

4

4

S

F

2

,

1

N

I

t

u

p

n

I

d

e

h

c

t

a

L

.

n

i

p

t

c

e

l

e

s

y

c

n

e

u

q

e

r

F

1

F

E

R

T

U

O

.

k

c

o

l

c

e

c

n

e

r

e

f

e

r

z

H

M

8

1

3

.

4

1

8

4

0

F

E

R

T

U

O

.

k

c

o

l

c

e

c

n

e

r

e

f

e

r

z

h

M

8

1

3

.

4

1

3

ICS9248-151

Third party brands and names are the property of their respective owners.

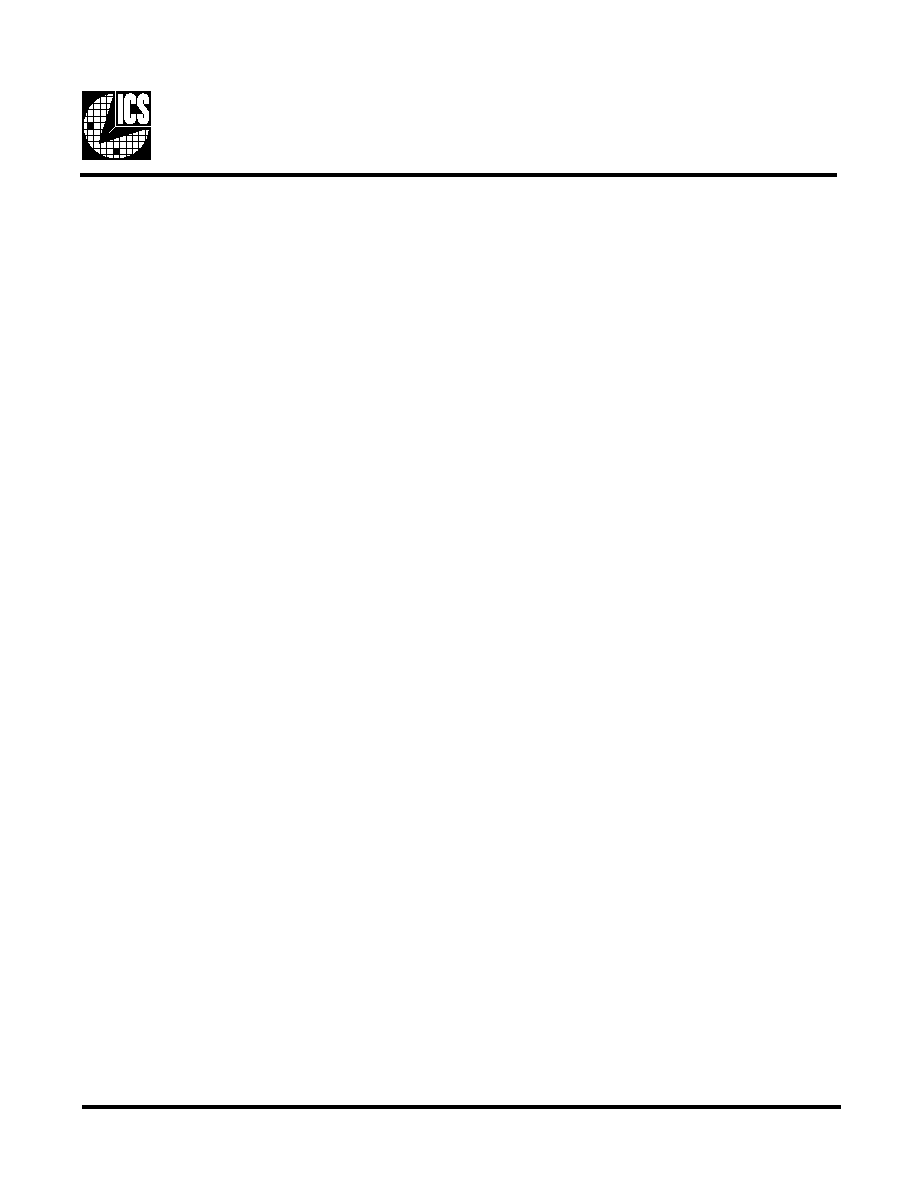

General Description

The ICS9248-151 is a single chip clock solution for Desktop

designs. It provides all necessary clock signals for such a

system.

Spread spectrum may be enabled through I

2

C programming.

Spread spectrum typically reduces system EMI by 8dB to

10dB. This simplifies EMI qualification without resorting to

board design iterations or costly shielding. The ICS9248-151

employs a proprietary closed loop design, which tightly

controls the percentage of spreading over process and

temperature variations.

Serial programming I

2

C interface allows changing functions,

stop clock programming and frequency selection.

Power Groups

AVDD, AGND = Core PLL

AVDD48, AGND48 = 24, 48MHz and fixed PLL

VDDREF, GNDREF = REF clocks, Xtal

4

ICS9248-151

Third party brands and names are the property of their respective owners.

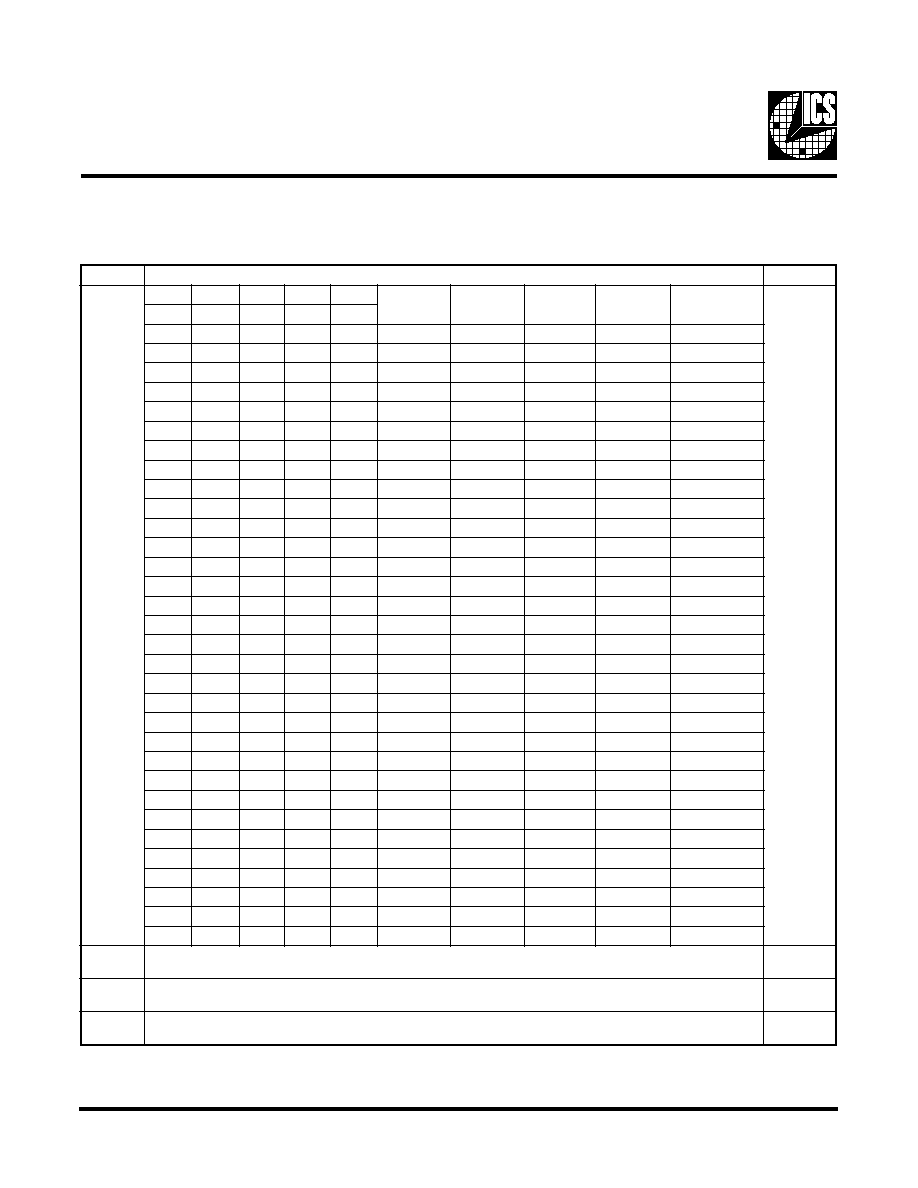

Byte0: Functionality and Frequency Select Register (default = 0)

Serial Configuration Command Bitmap

Note1: Default at power-up will be for latched logic inputs to define frequency, as diplayed by Bit 3.

t

i

B

n

o

i

t

p

i

r

c

s

e

D

D

W

P

1

,

2

t

i

B

4

:

6

t

i

B

2

t

i

B

1

t

i

B

6

t

i

B

5

t

i

B

4

t

i

B

K

L

C

U

P

C

)

z

H

M

(

K

L

C

P

G

A

)

z

H

M

(

K

L

C

I

C

P

)

z

H

M

(

C

I

P

A

O

I

)

z

H

M

(

d

a

e

r

p

S

e

g

a

t

n

e

c

e

r

P

X

X

X

X

1

e

t

o

N

4

S

F

3

S

F

2

S

F

1

S

F

0

S

F

0

0

0

0

0

0

0

.

0

0

2

0

0

.

0

8

0

0

.

0

4

0

0

.

0

2

%

5

2

.

0

-

/

+

0

0

0

0

1

0

0

.

0

9

1

0

0

.

6

7

0

0

.

8

3

0

0

.

9

1

%

5

2

.

0

-

/

+

0

0

0

1

0

0

0

.

0

8

1

0

0

.

2

7

0

0

.

6

3

0

0

.

8

1

%

5

2

.

0

-

/

+

0

0

0

1

1

0

0

.

0

7

1

0

0

.

8

6

0

0

.

4

3

0

0

.

7

1

%

5

2

.

0

-

/

+

0

0

1

0

0

0

0

.

6

6

1

0

4

.

6

6

0

2

.

3

3

0

6

.

6

1

%

5

2

.

0

-

/

+

0

0

1

0

1

0

0

.

0

6

1

0

0

.

4

6

0

0

.

2

3

0

0

.

3

1

%

5

2

.

0

-

/

+

0

0

1

1

0

0

0

.

0

5

1

0

0

.

5

7

0

5

.

7

3

5

7

.

8

1

%

5

2

.

0

-

/

+

0

0

1

1

1

0

0

.

5

4

1

0

5

.

2

7

5

2

.

6

3

2

1

.

8

1

%

5

2

.

0

-

/

+

0

1

0

0

0

0

0

.

0

4

1

0

0

.

0

7

0

0

.

5

3

0

5

.

7

1

%

5

2

.

0

-

/

+

0

1

0

0

1

0

0

.

6

3

1

0

0

.

8

6

0

0

.

4

3

0

0

.

7

1

%

5

2

.

0

-

/

+

0

1

0

1

0

0

0

.

0

3

1

0

0

.

5

6

0

5

.

2

3

5

2

.

6

1

%

5

2

.

0

-

/

+

0

1

0

1

1

0

0

.

4

2

1

0

0

.

2

6

0

0

.

1

3

0

5

.

5

1

%

5

2

.

0

-

/

+

0

1

1

0

0

7

6

.

6

6

7

6

.

6

6

4

3

.

3

3

7

6

.

6

1

%

5

7

.

0

-

/

+

0

1

1

0

1

0

0

.

0

0

1

7

6

.

6

6

3

3

.

3

3

6

6

.

6

1

%

5

7

.

0

-

/

+

0

1

1

1

0

0

0

.

8

1

1

7

6

.

8

7

3

3

.

9

3

6

6

.

9

1

%

5

2

.

0

-

/

+

0

1

1

1

1

3

3

.

3

3

1

7

6

.

6

6

4

3

.

3

3

7

6

.

6

1

%

5

7

.

0

-

/

+

1

0

0

0

0

0

8

.

6

6

0

8

.

6

6

0

4

.

3

3

0

7

.

6

1

%

5

2

.

0

-

/

+

1

0

0

0

1

0

2

.

0

0

1

0

8

.

6

6

0

4

.

3

3

0

7

.

6

1

%

5

2

.

0

-

/

+

1

0

0

1

0

0

0

.

5

1

1

7

6

.

6

7

3

3

.

8

3

6

1

.

9

1

%

5

2

.

0

-

/

+

1

0

0

1

1

0

4

.

3

3

1

0

7

.

6

6

5

3

.

3

3

7

6

.

6

1

%

5

2

.

0

-

/

+

1

0

1

0

0

0

8

.

6

6

0

8

.

6

6

0

4

.

3

3

7

6

.

6

1

%

5

.

0

-

/

+

1

0

1

0

1

0

2

.

0

0

1

0

8

.

6

6

0

4

.

3

3

0

7

.

6

1

%

5

.

0

-

/

+

1

0

1

1

0

0

0

.

0

1

1

3

3

.

3

7

7

6

.

6

3

3

3

.

8

1

%

5

2

.

0

-

/

+

1

0

1

1

1

0

4

.

3

3

1

0

7

.

6

6

5

3

.

3

3

7

6

.

6

1

%

5

.

0

-

/

+

1

1

0

0

0

0

0

.

5

0

1

0

0

.

0

7

0

0

.

5

3

0

5

.

7

1

%

5

2

.

0

-

/

+

1

1

0

0

1

0

0

.

0

9

0

0

.

0

6

0

0

.

0

3

0

0

.

5

1

%

5

2

.

0

-

/

+

1

1

0

1

0

0

0

.

5

8

7

6

.

6

5

3

3

.

8

2

6

1

.

4

1

%

5

2

.

0

-

/

+

1

1

0

1

1

0

0

.

8

7

0

0

.

8

7

0

0

.

9

3

5

.

9

1

%

5

2

.

0

-

/

+

1

1

1

0

0

7

6

.

6

6

7

6

.

6

6

4

3

.

3

3

7

6

.

6

1

%

5

.

0

-

o

t

0

1

1

1

0

1

0

0

.

0

0

1

7

6

.

6

6

3

3

.

3

3

6

6

.

6

1

%

5

.

0

-

o

t

0

1

1

1

1

0

0

0

.

5

7

0

0

.

5

7

0

5

.

7

3

5

7

.

8

1

%

5

2

.

0

-

/

+

1

1

1

1

1

3

3

.

3

3

1

7

6

.

6

6

4

3

.

3

3

7

6

.

6

1

%

5

.

0

-

o

t

0

3

t

i

B

s

t

u

p

n

I

d

e

h

c

t

a

L

,t

c

e

l

e

s

e

r

a

w

d

r

a

h

y

b

d

e

t

c

e

l

e

s

s

i

y

c

n

e

u

q

e

r

F

-

0

]

4

:

6

[

1

,

2

t

i

B

y

b

d

e

t

c

e

l

e

s

s

i

y

c

n

e

u

q

e

r

F

-

1

0

7

t

i

B

l

a

m

r

o

N

-

0

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

±

d

e

l

b

a

n

E

m

u

r

t

c

e

p

S

d

a

e

r

p

S

-

1

1

0

t

i

B

g

n

i

n

n

u

R

-

0

s

t

u

p

t

u

o

l

l

a

e

t

a

t

s

i

r

T

-

1

0

5

ICS9248-151

Third party brands and names are the property of their respective owners.

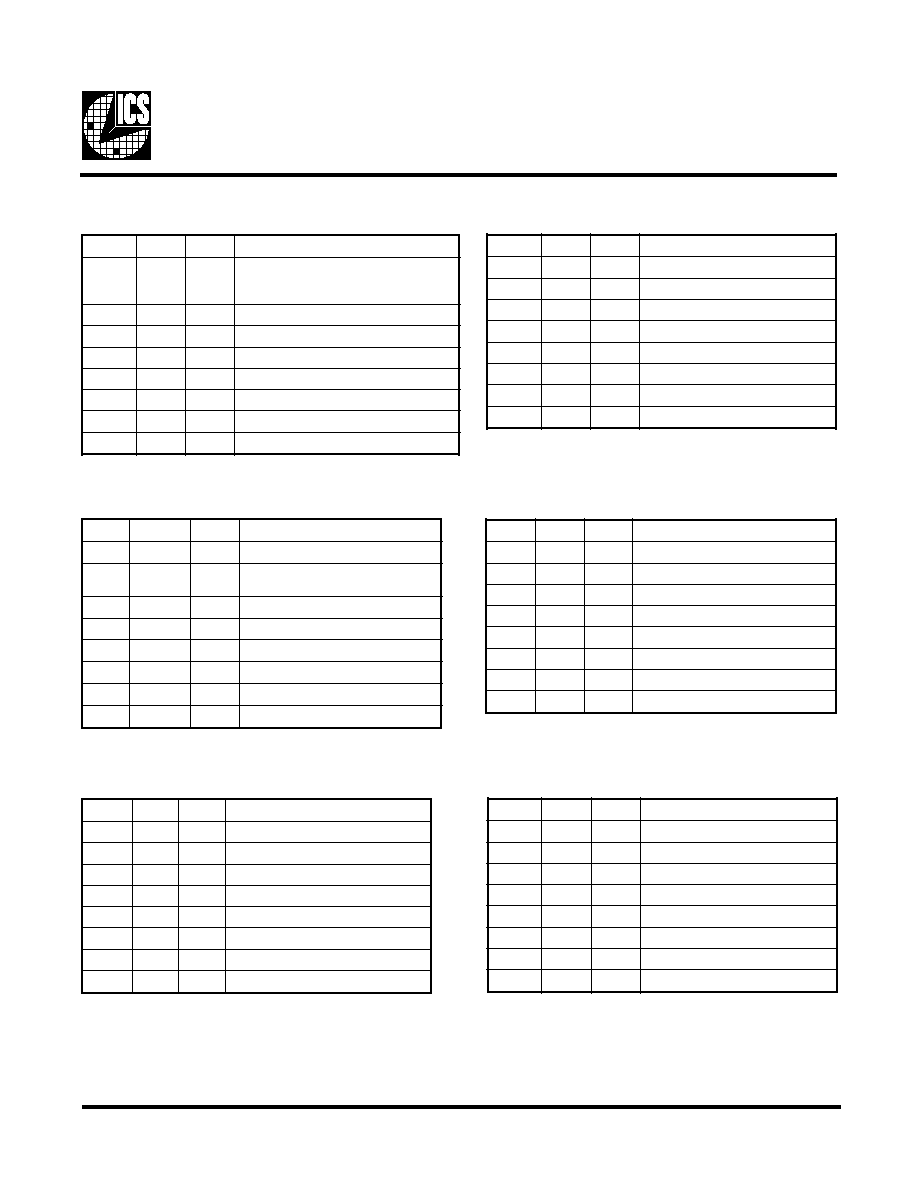

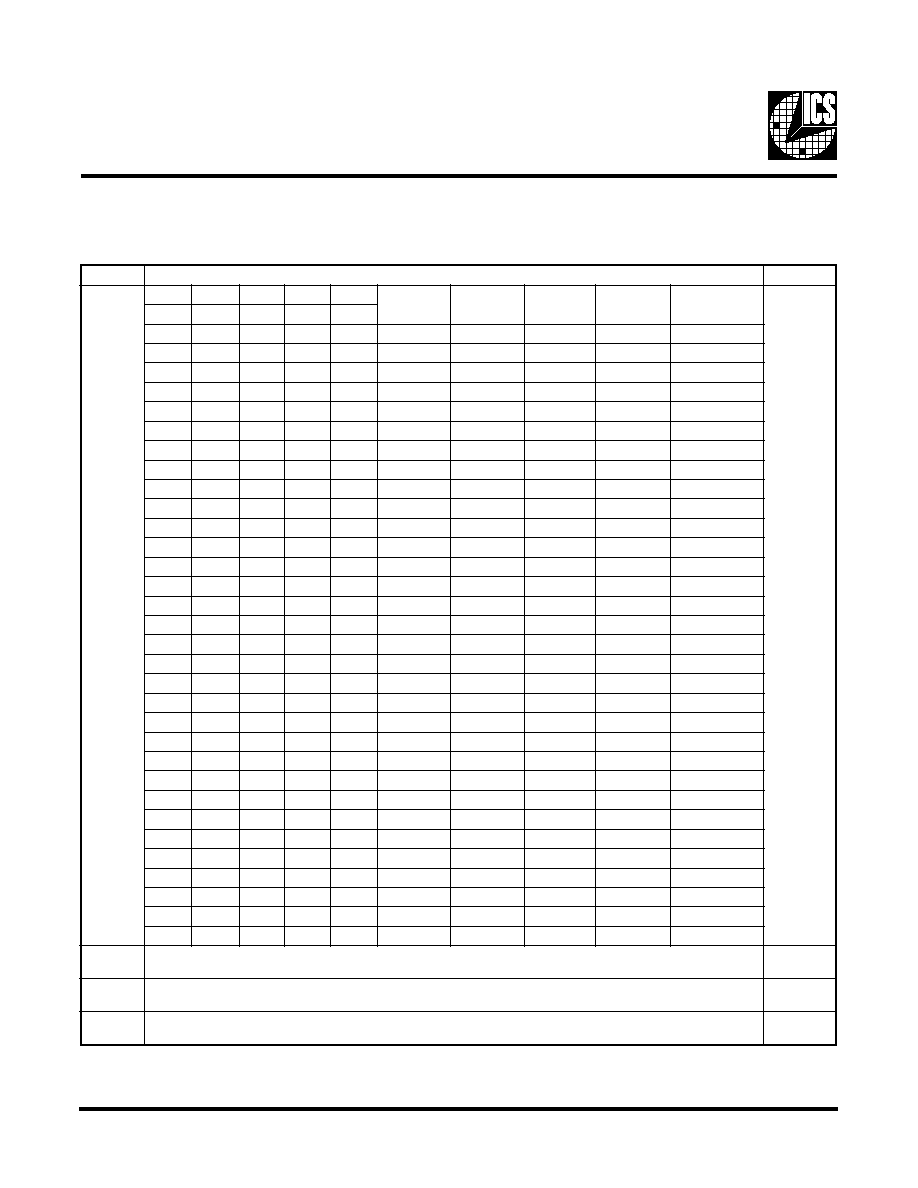

Byte 1: CPU, Active/Inactive Register

(1= enable, 0 = disable)

Byte 2: PCI, Active/Inactive Register

(1= enable, 0 = disable)

T

I

B

#

N

I

P

D

W

P

N

O

I

T

P

I

R

C

S

E

D

7

t

i

B

0

2

1

7

K

L

C

I

C

P

6

t

i

B

8

1

1

6

K

L

C

I

C

P

5

t

i

B

7

1

1

5

K

L

C

I

C

P

4

t

i

B

6

1

1

4

K

L

C

I

C

P

3

t

i

B

4

1

1

3

K

L

C

I

C

P

2

t

i

B

3

1

1

2

K

L

C

I

C

P

1

t

i

B

1

1

1

1

K

L

C

I

C

P

0

t

i

B

0

1

1

0

K

L

C

I

C

P

Notes:

1. Inactive means outputs are held LOW and are disabled

from switching.

2. Latched Frequency Selects (FS#) will be inverted logic

load of the input frequency select pin conditions.

T

I

B

#

N

I

P

D

W

P

N

O

I

T

P

I

R

C

S

E

D

7

t

i

B

-

1

)

d

e

v

r

e

s

e

R

(

6

t

i

B

-

1

)

d

e

v

r

e

s

e

R

(

5

t

i

B

-

1

)

d

e

v

r

e

s

e

R

(

4

t

i

B

-

1

)

d

e

v

r

e

s

e

R

(

3

t

i

B

-

1

)

d

e

v

r

e

s

e

R

(

2

t

i

B

-

1

)

d

e

v

r

e

s

e

R

(

1

t

i

B

-

1

)

d

e

v

r

e

s

e

R

(

0

t

i

B

-

1

)

d

e

v

r

e

s

e

R

(

Byte 4: Reserved , Active/Inactive Register

(1= enable, 0 = disable)

T

I

B

#

N

I

P

D

W

P

N

O

I

T

P

I

R

C

S

E

D

7

t

i

B

-

1

)

d

e

v

r

e

s

e

R

(

6

t

i

B

-

1

)

d

e

v

r

e

s

e

R

(

5

t

i

B

4

4

1

1

C

I

P

A

O

I

4

t

i

B

5

4

1

0

C

I

P

A

O

I

3

t

i

B

-

1

)

d

e

v

r

e

s

e

R

(

2

t

i

B

-

1

)

d

e

v

r

e

s

e

R

(

1

t

i

B

7

4

1

1

F

E

R

0

t

i

B

8

4

1

0

F

E

R

Byte 5: Peripheral , Active/Inactive Register

(1= enable, 0 = disable)

Byte 3: Active/Inactive Register

(1= enable, 0 = disable)

T

I

B

#

N

I

P

D

W

P

N

O

I

T

P

I

R

C

S

E

D

7

ti

B

-

X

#

2

S

F

6

ti

B

-

0

8

4

_

4

2

L

E

S

z

H

M

8

4

=

1

z

H

M

4

2

=

0

5

ti

B

6

1

z

H

M

8

4

4

ti

B

7

1

z

H

M

8

4

_

4

2

3

ti

B

9

1

F

_

K

L

C

I

C

P

2

ti

B

7

2

1

2

K

L

C

P

G

A

1

ti

B

6

2

1

1

K

L

C

P

G

A

0

ti

B

3

2

1

0

K

L

C

P

G

A

T

I

B

#

N

I

P

D

W

P

N

O

I

T

P

I

R

C

S

E

D

7

t

i

B

-

0

)

e

t

o

N

(

d

e

v

r

e

s

e

R

6

t

i

B

-

0

)

e

t

o

N

(

d

e

v

r

e

s

e

R

5

t

i

B

-

0

)

e

t

o

N

(

d

e

v

r

e

s

e

R

4

t

i

B

-

0

)

e

t

o

N

(

d

e

v

r

e

s

e

R

3

t

i

B

-

0

)

e

t

o

N

(

d

e

v

r

e

s

e

R

2

t

i

B

-

1

)

e

t

o

N

(

d

e

v

r

e

s

e

R

1

t

i

B

-

1

)

e

t

o

N

(

d

e

v

r

e

s

e

R

0

t

i

B

-

0

)

e

t

o

N

(

d

e

v

r

e

s

e

R

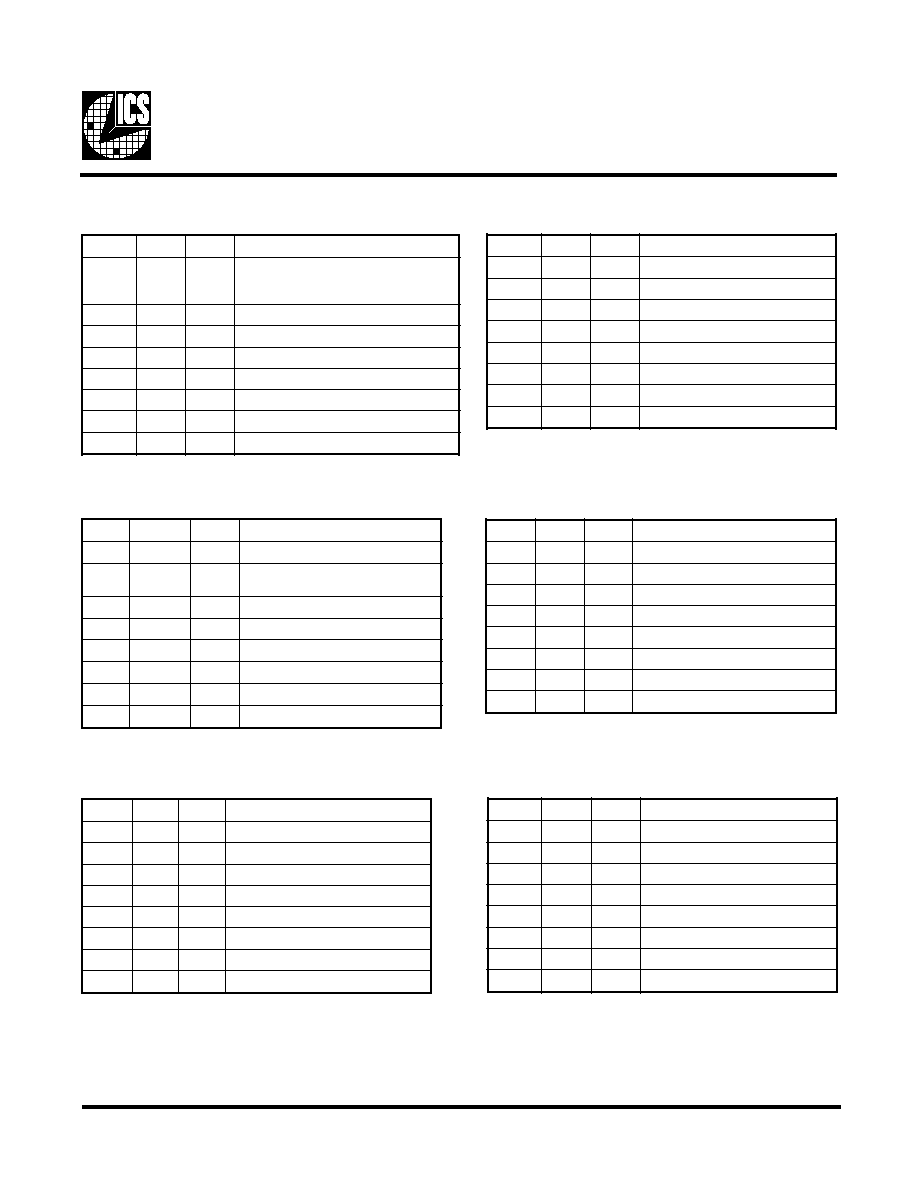

Byte 6: Peripheral , Active/Inactive Register

(1= enable, 0 = disable)

Note: Don't write into this register, writing into this

register can cause malfunction

T

I

B

#

N

I

P

D

W

P

N

O

I

T

P

I

R

C

S

E

D

7

t

i

B

5

3

0

;

#

F

U

P

C

_

L

E

S

g

n

i

n

n

u

r

e

e

r

f

e

b

l

l

i

w

2

K

L

C

U

P

C

=

0

g

n

i

n

n

u

r

e

e

r

f

e

b

t

o

n

l

l

i

w

2

K

L

C

U

P

C

=

1

6

t

i

B

-

1

)

d

e

v

r

e

s

e

R

(

5

t

i

B

-

X

#

4

S

F

4

t

i

B

-

X

#

3

S

F

3

t

i

B

5

3

1

2

K

L

C

U

P

C

2

t

i

B

8

3

1

1

K

L

C

U

P

C

1

t

i

B

9

3

1

0

K

L

C

U

P

C

0

t

i

B

2

4

1

2

C

I

P

A

O

I