| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: ICS93735 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Integrated

Circuit

Systems, Inc.

ICS93735

0579E--08/06/03

Block Diagram

DDR Phase Lock Loop Zero Delay Clock Buffer

Pin Configuration

48-Pin SSOP

Recommended Application:

DDR Zero Delay Clock Buffer

Product Description/Features:

∑

Low skew, low jitter PLL clock driver

∑

Max frequency supported = 266MHz (DDR 533)

∑

I

2

C for functional and output control

∑

Feedback pins for input to output synchronization

∑

Spread Spectrum tolerant inputs

∑

3.3V tolerant CLK_INT input

Switching Characteristics:

∑

CYCLE - CYCLE jitter (66MHz): <120ps

∑

CYCLE - CYCLE jitter (>100MHz): <65ps

∑

CYCLE - CYCLE jitter (>200MHz): <75ps

∑

OUTPUT - OUTPUT skew: <100ps

∑

Output Rise and Fall Time: 500ps - 700ps

∑

DUTY CYCLE: 49.5% - 50.5%

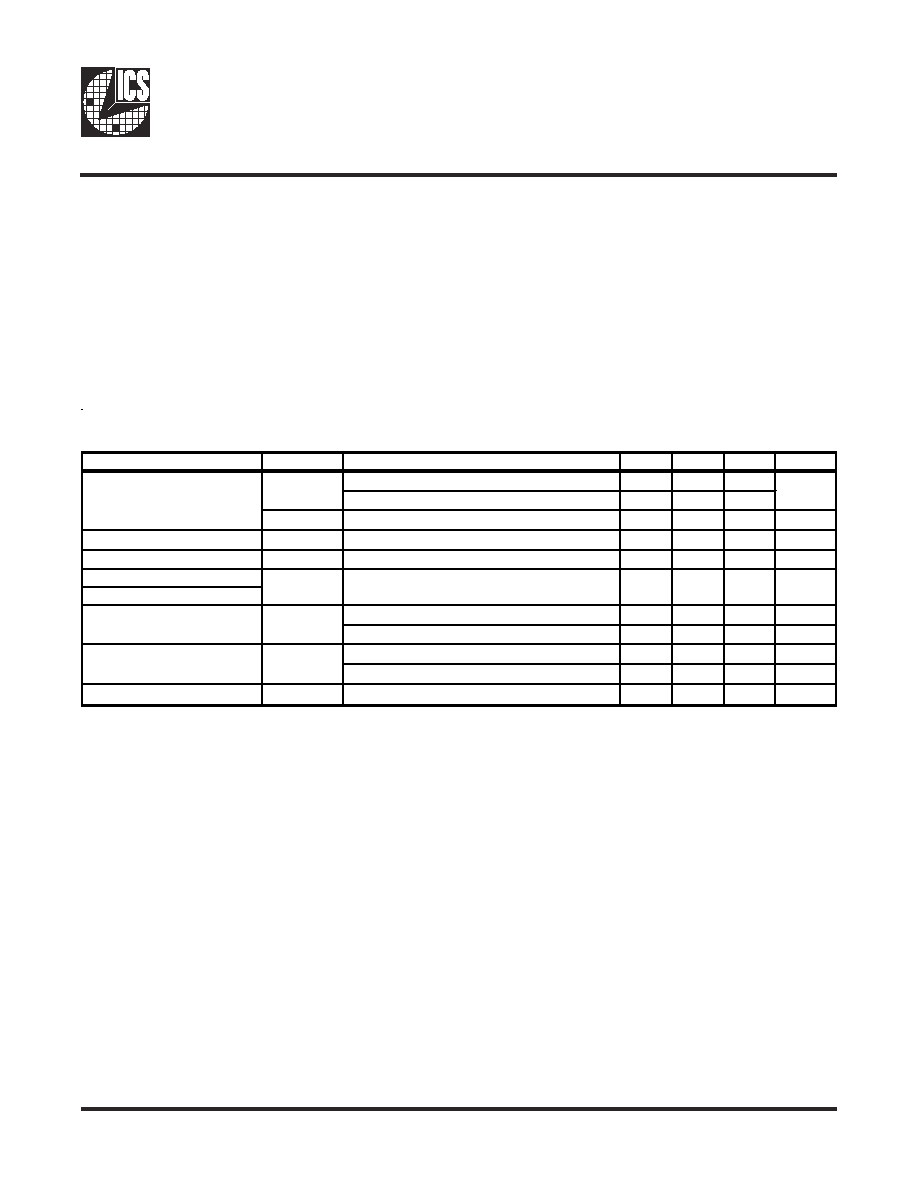

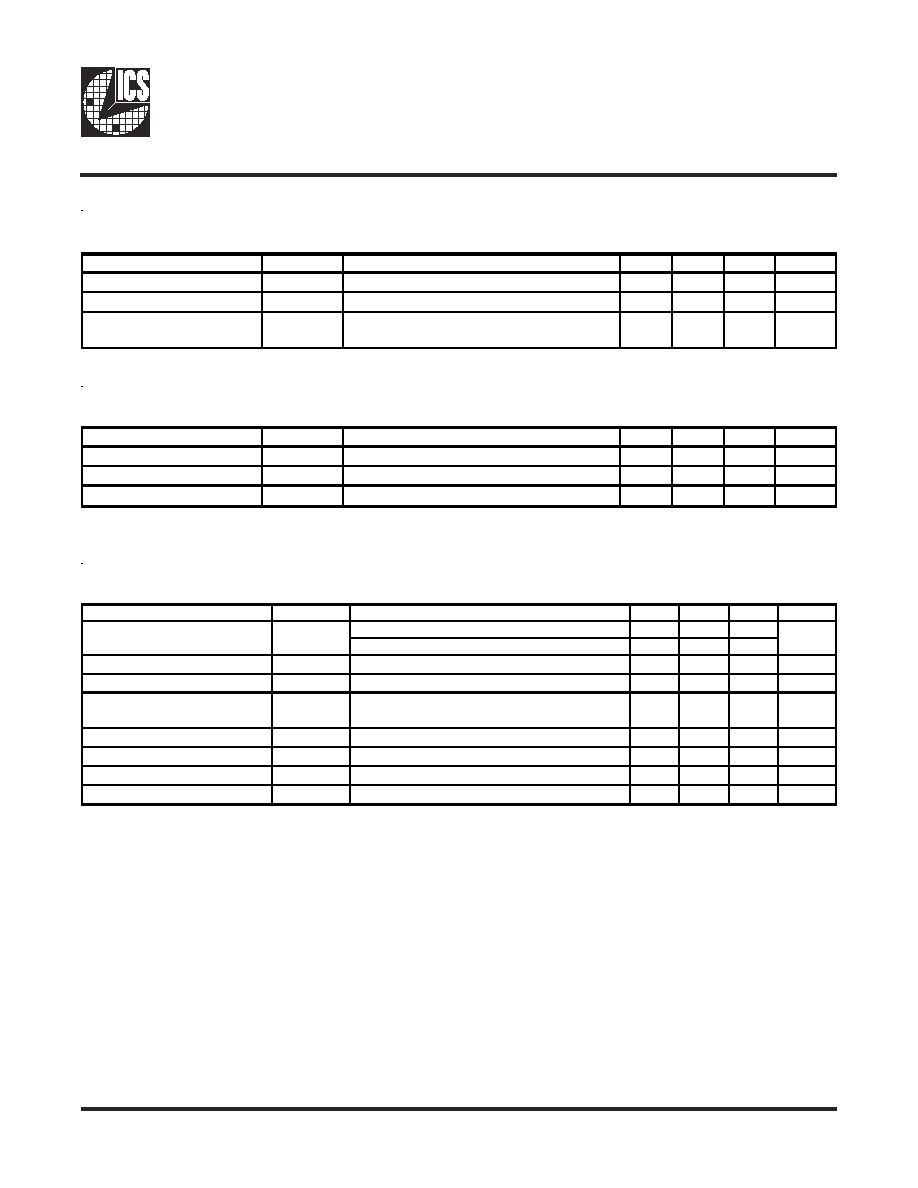

Functionality

FB_INT

CLK_INT

PLL

SCLK

SDATA

Control

Logic

FB_OUTT

CLKT0

CLKT1

CLKT2

CLKT3

CLKT4

CLKT5

CLKT6

CLKT7

CLKT8

CLKT9

CLKC0

CLKC1

CLKC2

CLKC3

CLKC4

CLKC5

CLKC6

CLKC7

CLKC8

CLKC9

AVDD

CLK_INT

CLKT

CLKC

FB_OUTT

2.5V (nom)

L

L

H

L

on

2.5V (nom)

H

H

L

H

on

2.5V (nom)

< offset freq*

offset freq* offset freq* offset freq*

off

GND

L

L

H

L

Bypassed/off

GND

H

H

L

H

Bypassed/off

* The offset frequency is ~ 20 MHz, varying somewhat from part to part.

INPUTS

OUTPUTS

PLL State

2

ICS93735

0579E--08/06/03

Pin Descriptions

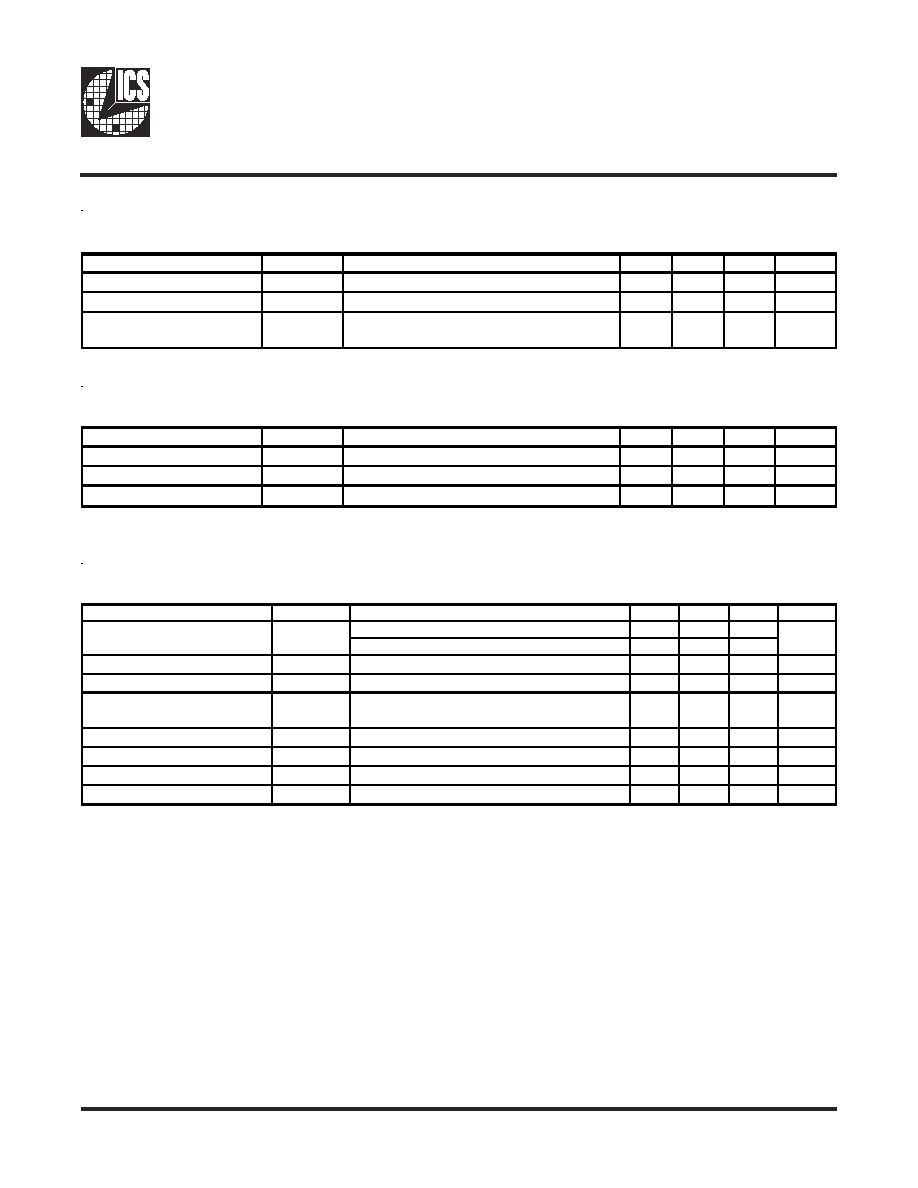

Byte 0: Output Control

(1= enable, 0 = disable)

T

I

B

#

N

I

P

D

W

P

N

O

I

T

P

I

R

C

S

E

D

7

t

i

B

-

1

d

e

v

r

e

s

e

R

6

t

i

B

-

1

d

e

v

r

e

s

e

R

5

t

i

B

-

1

d

e

v

r

e

s

e

R

4

t

i

B

-

1

d

e

v

r

e

s

e

R

3

t

i

B

-

1

d

e

v

r

e

s

e

R

2

t

i

B

-

1

d

e

v

r

e

s

e

R

1

t

i

B

-

1

d

e

v

r

e

s

e

R

0

t

i

B

-

1

d

e

v

r

e

s

e

R

Byte 1: Output Control

(1= enable, 0 = disable)

T

I

B

#

N

I

P

D

W

P

N

O

I

T

P

I

R

C

S

E

D

7

t

i

B

-

1

d

e

v

r

e

s

e

R

6

t

i

B

-

1

d

e

v

r

e

s

e

R

5

t

i

B

-

1

d

e

v

r

e

s

e

R

4

t

i

B

-

1

d

e

v

r

e

s

e

R

3

t

i

B

-

1

d

e

v

r

e

s

e

R

2

t

i

B

-

1

d

e

v

r

e

s

e

R

1

t

i

B

-

1

d

e

v

r

e

s

e

R

0

t

i

B

-

1

d

e

v

r

e

s

e

R

R

E

B

M

U

N

N

I

P

E

M

A

N

N

I

P

E

P

Y

T

N

O

I

T

P

I

R

C

S

E

D

,

5

2

,

4

2

,

8

1

,

8

,

7

,

1

8

4

,

2

4

,

1

4

,

1

3

D

N

G

R

W

P

d

n

u

o

r

G

,

7

4

,

3

4

,

0

4

,

0

3

,

6

2

2

,

6

,

9

,

9

1

,

3

2

)

0

:

9

(

C

K

L

C

T

U

O

.

s

t

u

p

t

u

o

r

i

a

p

l

a

i

t

n

e

r

e

f

f

i

d

f

o

s

k

c

o

l

c

"

y

r

a

t

n

e

m

e

l

p

m

o

C

"

,

6

4

,

4

4

,

9

3

,

9

2

,

7

2

3

,

5

,

0

1

,

0

2

,

2

2

)

0

:

9

(

T

K

L

C

T

U

O

.

s

t

u

p

t

u

o

r

i

a

p

l

a

i

t

n

e

r

e

f

f

i

d

f

o

k

c

o

l

C

"

e

u

r

T

"

,

8

2

,

1

2

,

5

1

,

1

1

,

4

,

5

4

,

8

3

,

4

3

D

D

V

R

W

P

V

5

.

2

y

l

p

p

u

s

r

e

w

o

P

2

1

K

L

C

S

N

I

I

f

o

t

u

p

n

i

k

c

o

l

C

2

t

u

p

n

i

t

n

a

r

e

l

o

t

V

5

,

t

u

p

n

i

C

3

1

T

N

I

_

K

L

C

N

I

t

u

p

n

i

t

n

a

r

e

l

o

t

V

3

.

3

,

t

u

p

n

i

k

c

o

l

c

e

c

n

e

r

e

f

e

r

"

e

u

r

T

"

6

3

,

2

3

,

4

1

C

/

N

-

d

e

t

c

e

n

n

o

c

t

o

N

6

1

D

D

V

A

R

W

P

V

5

.

2

,

y

l

p

p

u

s

r

e

w

o

p

g

o

l

a

n

A

7

1

D

N

G

A

R

W

P

.

d

n

u

o

r

g

g

o

l

a

n

A

3

3

T

T

U

O

_

B

F

T

U

O

s

e

h

c

t

i

w

s

t

I

.

k

c

a

b

d

e

e

f

l

a

n

r

e

t

x

e

r

o

f

d

e

t

a

c

i

d

e

d

,

t

u

p

t

u

o

k

c

a

b

d

e

e

F

"

"

e

u

r

T

"

o

t

d

e

r

i

w

e

b

t

s

u

m

t

u

p

t

u

o

s

i

h

T

.

K

L

C

e

h

t

s

a

y

c

n

e

u

q

e

r

f

e

m

a

s

e

h

t

t

a

.

T

N

I

_

B

F

5

3

T

N

I

_

B

F

N

I

r

o

f

L

L

P

l

a

n

r

e

t

n

i

e

h

t

o

t

l

a

n

g

i

s

k

c

a

b

d

e

e

f

s

e

d

i

v

o

r

p

,

t

u

p

n

i

k

c

a

b

d

e

e

F

"

e

u

r

T

"

.

r

o

r

r

e

e

s

a

h

p

e

t

a

n

i

m

il

e

o

t

T

N

I

_

K

L

C

h

t

i

w

n

o

i

t

a

z

i

n

o

r

h

c

n

y

s

7

3

A

T

A

D

S

O

/

I

I

r

o

f

n

i

p

a

t

a

D

2

t

n

a

r

e

l

o

t

V

5

y

r

t

i

u

c

r

i

c

C

3

ICS93735

0579E--08/06/03

T

I

B

#

N

I

P

D

W

P

N

O

I

T

P

I

R

C

S

E

D

7

t

i

B

-

1

d

e

v

r

e

s

e

R

6

t

i

B

-

1

d

e

v

r

e

s

e

R

5

t

i

B

-

1

d

e

v

r

e

s

e

R

4

t

i

B

-

1

d

e

v

r

e

s

e

R

3

t

i

B

-

1

d

e

v

r

e

s

e

R

2

t

i

B

-

1

d

e

v

r

e

s

e

R

1

t

i

B

-

1

d

e

v

r

e

s

e

R

0

t

i

B

-

1

d

e

v

r

e

s

e

R

Byte 3: Reserved

(1= enable, 0 = disable)

T

I

B

#

N

I

P

D

W

P

N

O

I

T

P

I

R

C

S

E

D

7

t

i

B

-

1

d

e

v

r

e

s

e

R

6

t

i

B

-

1

d

e

v

r

e

s

e

R

5

t

i

B

-

1

d

e

v

r

e

s

e

R

4

t

i

B

-

1

d

e

v

r

e

s

e

R

3

t

i

B

-

1

d

e

v

r

e

s

e

R

2

t

i

B

-

1

d

e

v

r

e

s

e

R

1

t

i

B

-

1

d

e

v

r

e

s

e

R

0

t

i

B

-

1

d

e

v

r

e

s

e

R

Byte 4: Reserved

(1= enable, 0 = disable)

Byte 2: Reserved

(1= enable, 0 = disable)

T

I

B

#

N

I

P

D

W

P

N

O

I

T

P

I

R

C

S

E

D

7

t

i

B

-

1

d

e

v

r

e

s

e

R

6

t

i

B

-

1

d

e

v

r

e

s

e

R

5

t

i

B

-

1

d

e

v

r

e

s

e

R

4

t

i

B

-

1

d

e

v

r

e

s

e

R

3

t

i

B

-

1

d

e

v

r

e

s

e

R

2

t

i

B

-

1

d

e

v

r

e

s

e

R

1

t

i

B

-

1

d

e

v

r

e

s

e

R

0

t

i

B

-

1

d

e

v

r

e

s

e

R

T

I

B

#

N

I

P

D

W

P

N

O

I

T

P

I

R

C

S

E

D

7

t

i

B

2

,

3

1

)

C

&

T

(

0

K

L

C

6

t

i

B

6

,

5

1

)

C

&

T

(

1

K

L

C

5

t

i

B

9

,

0

1

1

)

C

&

T

(

2

K

L

C

4

t

i

B

9

1

,

0

2

1

)

C

&

T

(

3

K

L

C

3

t

i

B

3

2

,

2

2

1

)

C

&

T

(

4

K

L

C

2

t

i

B

6

2

,

7

2

1

)

C

&

T

(

9

K

L

C

1

t

i

B

-

1

d

e

v

r

e

s

e

R

0

t

i

B

-

1

d

e

v

r

e

s

e

R

Byte 5: Reserved

(1= enable, 0 = disable)

T

I

B

#

N

I

P

D

W

P

N

O

I

T

P

I

R

C

S

E

D

7

t

i

B

-

0

)

e

t

o

N

(

d

e

v

r

e

s

e

R

6

t

i

B

-

0

)

e

t

o

N

(

d

e

v

r

e

s

e

R

5

t

i

B

-

0

)

e

t

o

N

(

d

e

v

r

e

s

e

R

4

t

i

B

0

3

,

9

2

1

)

C

&

T

(

8

K

L

C

3

t

i

B

0

4

,

9

3

1

)

C

&

T

(

7

K

L

C

2

t

i

B

3

4

,

4

4

1

)

C

&

T

(

6

K

L

C

1

t

i

B

7

4

,

6

4

1

)

C

&

T

(

5

K

L

C

0

t

i

B

-

1

d

e

v

r

e

s

e

R

Byte 6: Reserved

(1= enable, 0 = disable)

Note: Don't write into these registers (7:5), writing into

these registers can cause malfunction.

4

ICS93735

0579E--08/06/03

1.

The ICS clock generator is a slave/receiver, I

2

C component. It can read back the data stored in the latches

for verification. Read-Back will support Intel PIIX4 "Block-Read" protocol.

2.

The data transfer rate supported by this clock generator is 100K bits/sec or less (standard mode)

3.

The input is operating at 3.3V logic levels.

4.

The data byte format is 8 bit bytes.

5.

To simplify the clock generator I

2

C interface, the protocol is set to use only "Block-Writes" from the

controller. The bytes must be accessed in sequential order from lowest to highest byte with the ability to stop

after any complete byte has been transferred. The Command code and Byte count shown above must be

sent, but the data is ignored for those two bytes. The data is loaded until a Stop sequence is issued.

6.

At power-on, all registers are set to a default condition, as shown.

General I

2

C serial interface information

The information in this section assumes familiarity with I

2

C programming.

For more information, contact ICS for an I

2

C programming application note.

How to Write:

∑ Controller (host) sends a start bit.

∑ Controller (host) sends the write address D4

(H)

∑ ICS clock will acknowledge

∑ Controller (host) sends a dummy command code

∑ ICS clock will acknowledge

∑ Controller (host) sends a dummy byte count

∑ ICS clock will acknowledge

∑ Controller (host) starts sending first byte (Byte 0)

through byte 6

∑ ICS clock will acknowledge each byte one at a time.

∑ Controller (host) sends a Stop bit

How to Read:

∑ Controller (host) will send start bit.

∑ Controller (host) sends the read address D5

(H)

∑ ICS clock will acknowledge

∑ ICS clock will send the byte count

∑ Controller (host) acknowledges

∑ ICS clock sends first byte (Byte 0) through byte 6

∑ Controller (host) will need to acknowledge each byte

∑ Controller (host) will send a stop bit

Notes:

Controller (Host)

ICS (Slave/Receiver)

Start Bit

Address

D4

(H)

ACK

Dummy Command Code

ACK

Dummy Byte Count

ACK

Byte 0

ACK

Byte 1

ACK

Byte 2

ACK

Byte 3

ACK

Byte 4

ACK

Byte 5

ACK

Byte 6

ACK

Stop Bit

How to Write:

Controller (Host)

ICS (Slave/Receiver)

Start Bit

Address

D5

(H)

ACK

Byte Count

ACK

Byte 0

ACK

Byte 1

ACK

Byte 2

ACK

Byte 3

ACK

Byte 4

ACK

Byte 5

ACK

Byte 6

ACK

Stop Bit

How to Read:

5

ICS93735

0579E--08/06/03

Absolute Maximum Ratings

Supply Voltage (VDD & AVDD) . . . . . . . . . . -0.5V to 3.6V

Logic Inputs . . . . . . . . . . . . . . . . . . . . . . . . . GND ≠0.5 V to V

DD

+0.5 V

Ambient Operating Temperature . . . . . . . . . 0∞C to +85∞C

Storage Temperature . . . . . . . . . . . . . . . . . . ≠65∞C to +150∞C

Stresses above those listed under

Absolute Maximum Ratings may cause permanent damage to the device. These

ratings are stress specifications only and functional operation of the device at these or any other conditions above

those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect product reliability.

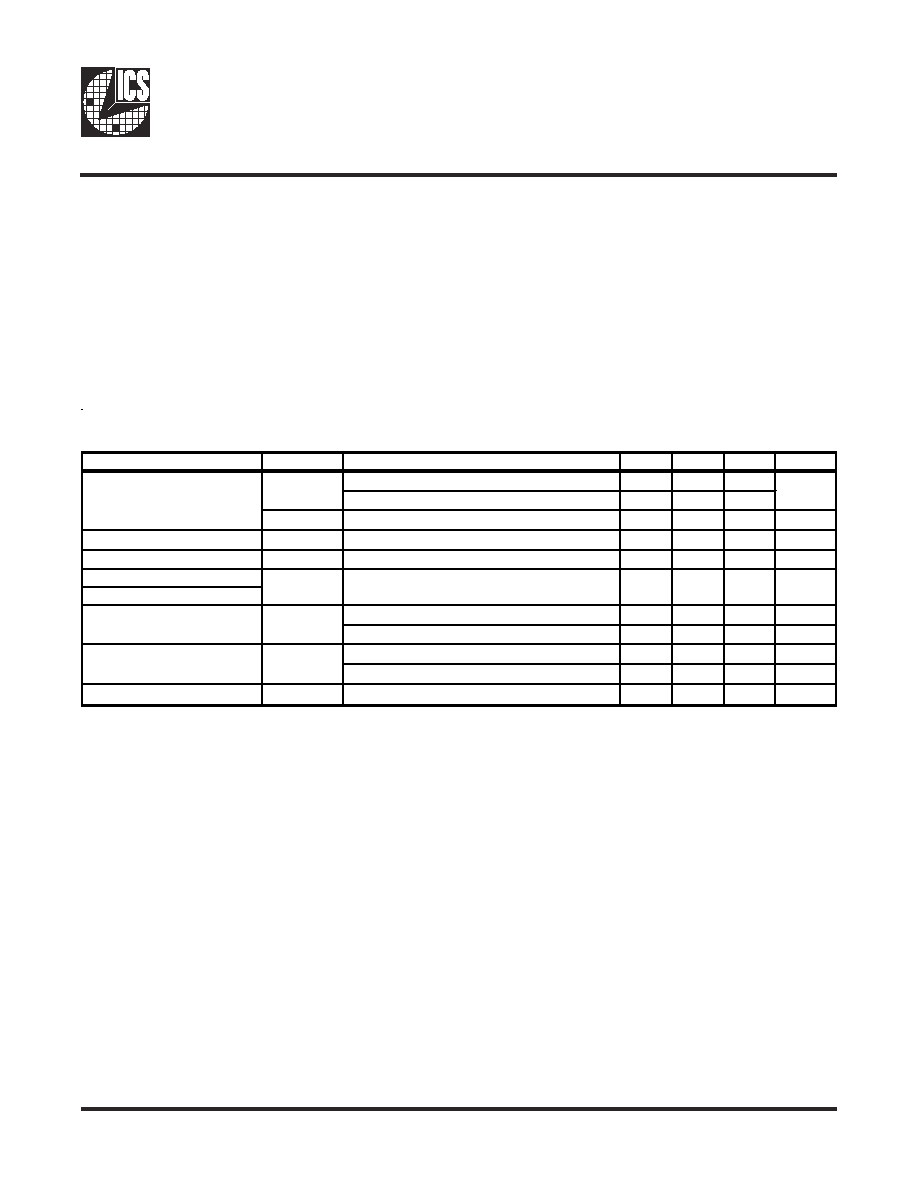

Electrical Characteristics - Input / Supply / Common Output parameters

T

A

= 0 - 70∞C; Supply Voltage AV

DD

, V

DD

= 2.50V ± 0.20V (unless otherwise stated)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

R

T

= 120W, C

L

= 12 pF at 100MHz

236

300

R

T

= 120W, C

L

= 12 pF at 133MHz

263

300

I

DDPD

CL=0 pF

100

mA

Output High Current

I

OH

V

DD

= 2.5V, V

OUT

= 1V

-48

-33

-29

mA

Output Low Current

I

OL

V

DD

= 2.5V, V

OUT

= 1.2V

29

33

37

mA

High Impedance

Ouptut Current

V

DD

= min to max, I

OH

= -1mA

2

2.25

V

V

DD

= 2.3V, I

OH

= -12mA

1.95

V

DD

= min to max, I

OH

= 1mA

0.05

0.1

V

V

DD

= 2.3V, I

OH

= 12mA

0.3

0.4

Output Capacitance

1

C

OUT

V

I

= V

DD

or GND

3

pF

1. Guaranteed by design, not 100% tested in production.

mA

10

V

OH

mA

I

DD2.5

Operating Supply Current

I

OZ

V

DD

= 2.7V, V

OUT

= V

DD

or GND

Low-level Output Voltage

V

OL

High-level Output Voltage

6

ICS93735

0579E--08/06/03

Recommended Operation Conditions

T

A

= 0 - 70∞C; Supply Voltage AV

DD

, V

DD

= 2.50V ± 0.20V (unless otherwise stated)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Analog / Core Supply Voltag

AV

DD

2.3

2.5

2.7

V

Input Voltage Level

V

IN

2

2.5

3

V

Output Differential Pair

Crossing Voltage

1.32

V

V

OC

66/100/133/166MHz, V

DD

=2.50V

1.23

1.25

Timing Requirements

T

A

= 0 - 70∞C; Supply Voltage AV

DD

, V

DD

= 2.50V (unless otherwise stated)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Operating Clock Frequency

1

freq

op

Input Voltage level: 0-2.50V

22

340

MHz

Input Clock Duty Cycle

1

d

tin

40

50

60

%

Clock Stabilization

1

t

STAB

from VDD = 2.5V to 1% target frequency

100

µ

s

1. Guaranteed by design, not 100% tested in production.

Switching Characteristics

T

A

= 0 - 70∞C; Supply Voltage AV

DD

, V

DD

= 2.50V ± 0.20V (unless otherwise stated)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

66 MHz

46

52

63

100 / 125 / 133 MHz

27

33

40

Phase Error

1

t

pe

100MHz, input clock 0-2.5V, 0.8ns rise/fall

-113

ps

Output to output Skew

1

T

skew

input clock 0-2.5V, 0.8ns rise/fall

66

98

ps

Low-to-high level Propagation

CLK_IN to any output,

Delay Time, Bypass Mode

1

100MHz, Load = 120 W / 12 pF

Pulse Skew

1

T

skew

ps

Duty Cycle (Sign Ended)

1,3

DC

no loads, 66 MHz to 167MHz

50.2

51.3

%

Rise Time

1

t

R

Single-ended 20-80 %; Load=120W/12pF

400

490

622

ps

Fall Time

1

t

F

Single-ended 20-80 %; Load=120W/12pF

435

579

711

ps

1. Guaranteed by design, not 100% tested in production.

2. Refers to transistion on non-inverting period.

3. While the pulse skew is almost constant over frequency, the duty cycle error increases at higher frequencies.

This is due to the formular: duty_cycle=t

wH

/t

C

, where the cycle time (t

C

)decreases as the frequency increases.

Cycle to cycle Jitter

1,2

t

c-c

ps

t

PLH

3.67

3.68

ns

7

ICS93735

0579E--08/06/03

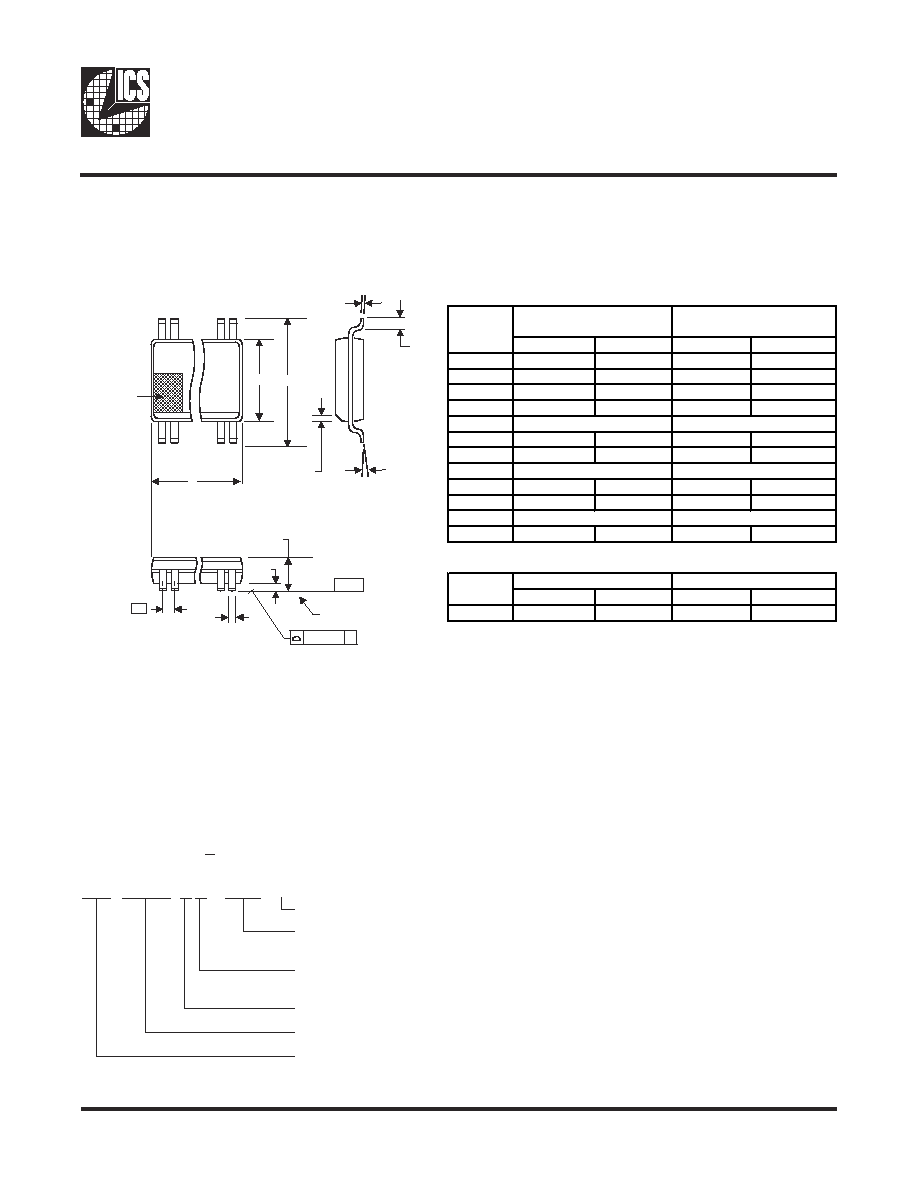

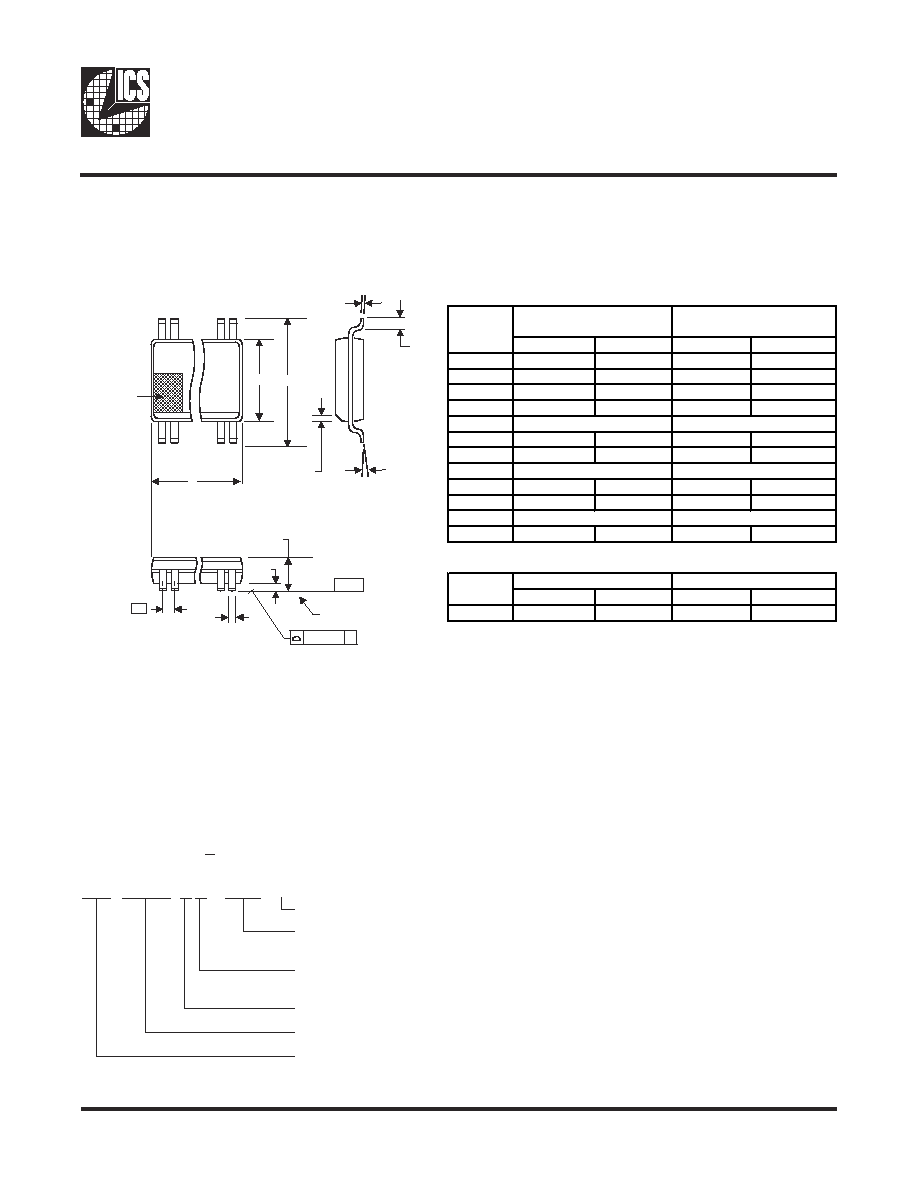

Ordering Information

ICS93735yF-T

Designation for tape and reel packaging

Pattern Number (2 or 3 digit number for parts with ROM code

patterns)

Package Type

F=SSOP

Revision Designator (will not correlate with datasheet revision)

Device Type (consists of 3 or 4 digit numbers)

Prefix

ICS, AV = Standard Device

Example:

ICS XXXX y F - PPP - T

INDEX

AREA

INDEX

AREA

1 2

1 2

N

D

h x 45∞

h x 45∞

E1

E

a

SEATING

PLANE

SEATING

PLANE

A1

A

e

- C -

- C -

b

.10 (.004) C

.10 (.004) C

c

L

300 mil SSOP Package

MIN

MAX

MIN

MAX

A

2.41

2.80

.095

.110

A1

0.20

0.40

.008

.016

b

0.20

0.34

.008

.0135

c

0.13

0.25

.005

.010

D

E

10.03

10.68

.395

.420

E1

7.40

7.60

.291

.299

e

h

0.38

0.64

.015

.025

L

0.50

1.02

.020

.040

N

0∞

8∞

0∞

8∞

MIN

MAX

MIN

MAX

48

15.75

16.00

.620

.630

10-0034

Reference Doc.: JEDEC Publication 95, MO-118

VARIATIONS

SEE VARIATIONS

SEE VARIATIONS

N

D mm.

D (inch)

SEE VARIATIONS

SEE VARIATIONS

0.635 BASIC

0.025 BASIC

SYMBOL

In Millimeters

In Inches

COMMON DIMENSIONS

COMMON DIMENSIONS