| ÐлекÑÑоннÑй компоненÑ: ICS951104 | СкаÑаÑÑ:  PDF PDF  ZIP ZIP |

ICS951104

Integrated

Circuit

Systems, Inc.

ICS951104

Preliminary Product Preview

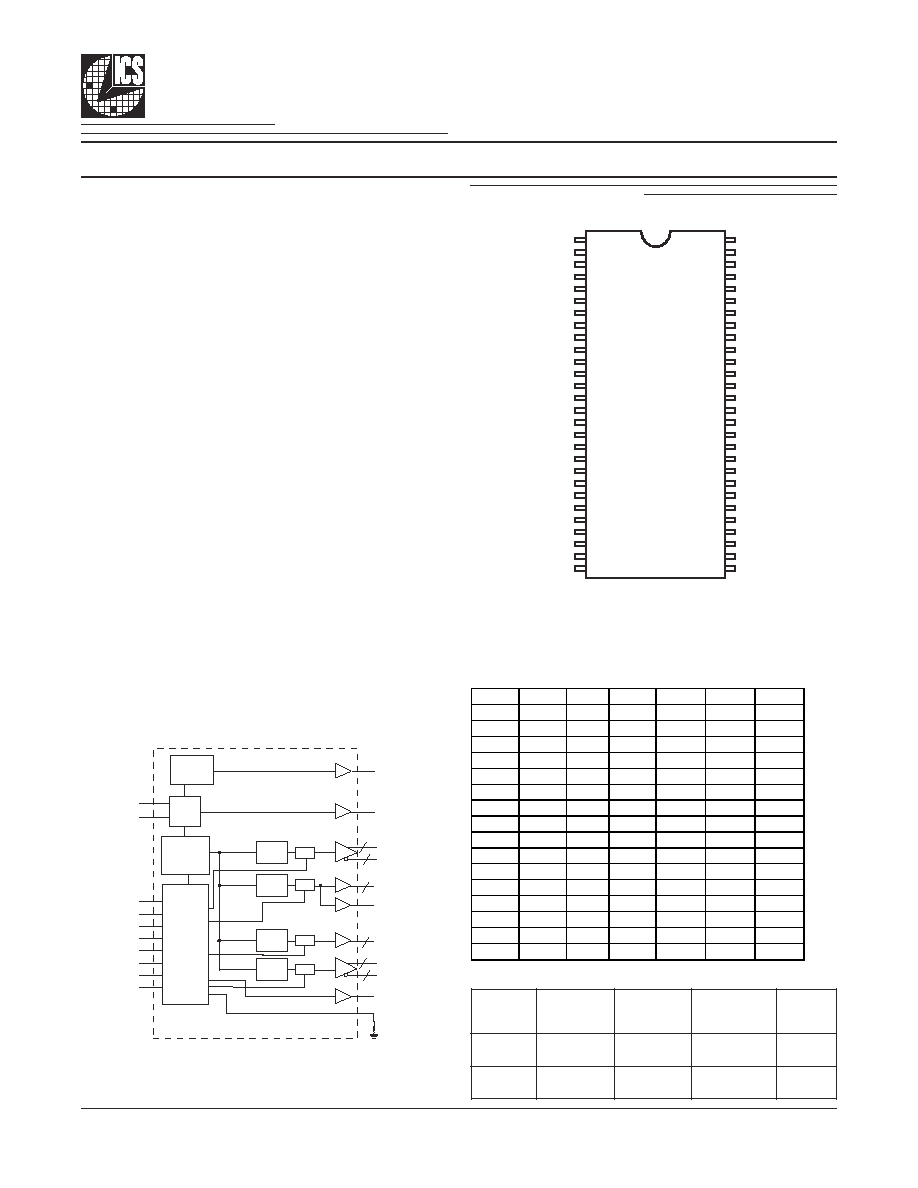

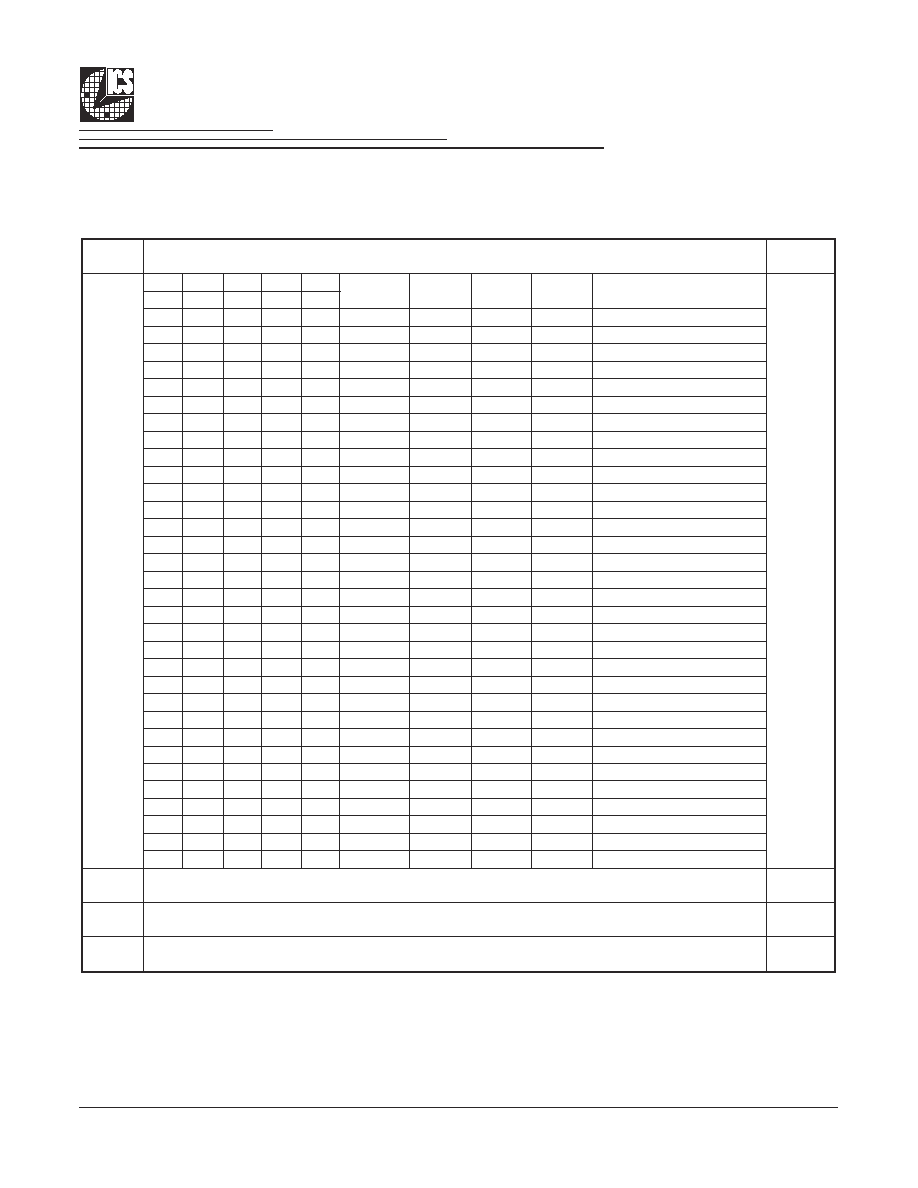

Block Diagram

0485E--04/26/02

Pin Configuration

Recommended Application:

ALI 1671/1672 P4 Chipset

Output Features:

·

2 - Pairs of differential CPU clocks (differential current mode)

·

2 - AGP @ 3.3V

·

7 - PCI @ 3.3V

·

1 - 48MHz @ 3.3V fixed

·

1 - REF @ 3.3V, 14.318MHz

·

7 - Pairs of differential SSTL2 DDR @ 2.5V

Features/Benefits:

·

Programmable output frequency.

·

Programmable output divider ratios.

·

Programmable output rise/fall time.

·

Programmable output skew.

·

Programmable spread percentage for EMI control.

·

Watchdog timer technology to reset system

if system malfunctions.

·

Programmable watch dog safe frequency.

·

Support I

2

C Index read/write and block read/write operations.

·

Uses external 14.318MHz crystal.

Key Specifications:

·

CPU Output Jitter <150ps

·

AGP Output Jitter <250ps

·

DDR Output Jitter <250ps

·

CPU - DDR Skew <250ps

·

CPU - AGP/PCI Skew = 2.5ns ± 500ps

Programmable Timing Control Hub

TM

for P4

TM

56-Pin 300-mil SSOP, 240-mil TSSOP

AVDD_CORE

X1

X2

GND

VDD

MULT_SEL/REF0

RESET#

VDD

FS0/AGP0

AGP1

GND

FS1/PCICLK_E

FS2/PCICLK0

PCICLK1

PCICLK2

GND

VDD

PCICLK3

PCICLK4

PCICLK5

PCI_STOP#

Vtt_PWRGD/PD#

AVDD48

FS3/48MHz

GND

SDATA

SCLK

CLK_STOP#

*

**

*

*

*

**

1

*

CPUCLKT0

CPUCLKC0

VDDCPU

CPUCLKT1

CPUCLKC1

IREF

GNDIREF

GNDCPU

DDRT0

GND

VDDL

VDDL

GND

GND

VDDL

DDRC0

DDRT1

DDRC1

DDRT2

DDRC2

DDRT3

DDRC3

DDRT4

DDRC4

DDRT5

DDRC5

DDRT6

DDRC6

ICS951104

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

PLL2

PLL1

Spread

Spectrum

48MHz

REF0

PCICLK (5:0)

AGP (1:0)

X1

X2

XTAL

OSC

CPU

DIVDER

PCI

DIVDER

AGP

DIVDER

DDR

DIVDER

PD#

MULTSEL

SDATA

SCLK

Vtt_PWRGD

CLK_STOP#

PCI_STOP#

FS (3:0)

I REF

RESET#

Control

Logic

Config.

Reg.

2

7

7

2

2

7

CPUCLKT (1:0)

DDRC (6:0)

CPUCLKC (1:0)

DDRT (6:0)

PCICLK_E

Stop

Stop

Stop

Stop

Functionality

Host Swing Select Functions

0

L

E

S

I

T

L

U

M

t

e

g

r

a

T

d

r

a

o

B

Z

m

r

e

T

/

e

c

a

r

T

,

R

e

c

n

e

r

e

f

e

R

=

f

e

r

I

V

D

D

)

r

R

*

3

(

/

t

u

p

t

u

O

t

n

e

r

r

u

C

Z

@

h

o

V

0

s

m

h

o

0

5

,

%

1

1

2

2

=

r

R

A

m

0

0

.

5

=

f

e

r

I

F

E

R

I

*

4

=

h

o

I

0

5

@

V

0

.

1

1

s

m

h

o

0

5

,

%

1

5

7

4

=

r

R

A

m

2

3

.

2

=

f

e

r

I

F

E

R

I

*

6

=

h

o

I

0

5

@

V

7

.

0

1 These outputs have 2x drive strength

* Internal Pull-up resistor of 120K to VDD

** These inputs have 120K internal pull-down

to GND

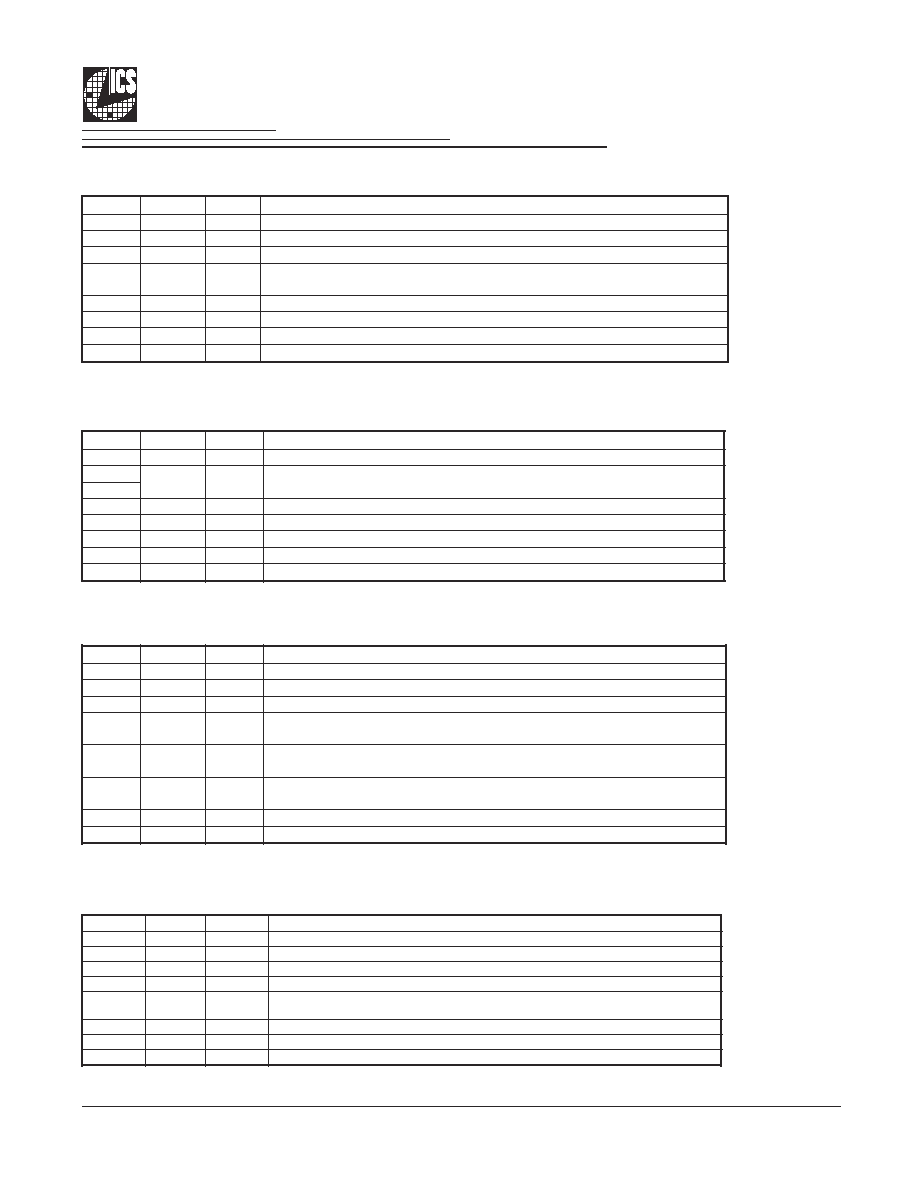

FS3

FS2

FS1

FS0

CPU

DDR

AG P

0

0

0

0

66.66

66.66

66.66

0

0

0

1

66.66

100.00

66.66

0

0

1

0

100.00

66.66

66.66

0

0

1

1

100.00 100.00

66.66

0

1

0

0

100.00 133.33

66.66

0

1

0

1

133.33

66.66

66.66

0

1

1

0

133.33 100.00

66.66

0

1

1

1

133.33 133.33

66.66

1

0

0

0

66.66

66.66

66.66

1

0

0

1

66.66

100.00

66.66

1

0

1

0

100.00

66.66

66.66

1

0

1

1

100.00 100.00

66.66

1

1

0

0

100.00 133.33

66.66

1

1

0

1

133.33

66.66

66.66

1

1

1

0

133.33 100.00

66.66

1

1

1

1

133.33 133.33

66.66

PRODUCT PREVIEW documents contain information on new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to

change without notice.

2

Third party brands and names are the property of their respective owners.

Integrated

Circuit

Systems, Inc.

ICS951104

Preliminary Product Preview

The ICS951104 is a single chip clock solution for desktop designs using the ALI 1671/1672 P4 Chipset. It provides all

necessary clock signals for such a system.

The ICS951104 is part of a whole new line of ICS clock generators and buffers called TCHTM (Timing Control Hub). This part

incorporates ICS's newest clock technology which offers more robust features and functionality. Employing the use of a

serially programmable I

2

C interface, this device can adjust the output clocks by configuring the frequency setting, the output

divider ratios, selecting the ideal spread percentage, the output skew, the output strength, and enabling/disabling each

individual output clock. M/N control can configure output frequency with resolution up to 0.1MHz increment.

General Description

R

E

B

M

U

N

N

I

P

E

M

A

N

N

I

P

E

P

Y

T

N

O

I

T

P

I

R

C

S

E

D

1

E

R

O

C

_

D

D

V

A

R

W

P

V

3

.

3

y

l

p

p

u

s

e

r

o

c

g

o

l

a

n

A

4

5

,

7

1

,

8

,

5

D

D

V

R

W

P

.

y

l

p

p

u

s

r

e

w

o

p

V

3

.

3

2

1

X

N

I

.

2

X

m

o

r

f

r

o

t

s

i

s

e

r

k

c

a

b

d

e

e

f

d

n

a

)

F

p

3

3

(

p

a

c

d

a

o

l

l

a

n

r

e

t

n

i

s

a

h

,t

u

p

n

i

l

a

t

s

y

r

C

3

2

X

T

U

O

.

)

F

p

3

3

(

p

a

c

d

a

o

l

l

a

n

r

e

t

n

i

s

a

H

.

z

H

M

8

1

3

.

4

1

y

ll

a

n

i

m

o

n

,t

u

p

t

u

o

l

a

t

s

y

r

C

,

9

3

,

4

3

,

5

2

,

6

1

,

1

1

,

4

0

5

,

9

4

,

6

4

D

N

G

R

W

P

.

y

l

p

p

u

s

V

3

.

3

r

o

f

s

n

i

p

d

n

u

o

r

G

6

L

E

S

T

L

U

M

N

I

s

t

u

p

t

u

o

U

P

C

r

o

f

r

e

il

p

it

l

u

m

t

n

e

r

r

u

c

e

h

t

g

n

it

c

e

l

e

s

r

o

f

t

u

p

n

i

L

T

T

V

L

V

3

.

3

0

F

E

R

T

U

O

.t

u

p

t

u

o

k

c

o

l

c

e

c

n

e

r

e

f

e

r

z

H

M

8

1

3

.

4

1

,

V

3

.

3

7

#

T

E

S

E

R

T

U

O

s

i

h

T

.t

u

o

e

m

it

r

e

m

m

it

g

o

d

h

c

t

a

w

r

o

e

u

l

a

v

y

c

n

e

u

q

e

rf

r

o

f

l

a

n

g

i

s

t

e

s

e

r

m

e

t

s

y

s

e

m

it

l

a

e

R

.

w

o

l

e

v

it

c

a

s

i

l

a

n

g

i

s

9

0

S

F

N

I

.

n

o

r

e

w

o

p

t

a

d

e

h

c

t

a

l

t

u

p

n

I

.t

i

b

t

c

e

l

e

s

y

c

n

e

u

q

e

r

f

t

u

p

n

i

c

i

g

o

L

0

P

G

A

T

U

O

s

t

u

p

t

u

o

k

c

o

l

c

V

3

.

3

0

1

1

P

G

A

T

U

O

s

t

u

p

t

u

o

k

c

o

l

c

V

3

.

3

2

1

E

_

K

L

C

I

C

P

T

U

O

.t

u

p

t

u

o

k

c

o

l

c

I

C

P

y

lr

a

E

V

3

.

3

1

S

F

N

I

.

n

o

r

e

w

o

p

t

a

d

e

h

c

t

a

l

t

u

p

n

I

.t

i

b

t

c

e

l

e

s

y

c

n

e

u

q

e

r

f

t

u

p

n

i

c

i

g

o

L

3

1

2

S

F

N

I

.

n

o

r

e

w

o

p

t

a

d

e

h

c

t

a

l

t

u

p

n

I

.t

i

b

t

c

e

l

e

s

y

c

n

e

u

q

e

r

f

t

u

p

n

i

c

i

g

o

L

0

K

L

C

I

C

P

T

U

O

.t

u

p

t

u

o

k

c

o

l

c

I

C

P

V

3

.

3

,

8

1

,

9

1

,

0

2

4

1

,

5

1

)

1

:

5

(

K

L

C

I

C

P

T

U

O

.

s

t

u

p

t

u

o

k

c

o

l

c

I

C

P

V

3

.

3

1

2

#

P

O

T

S

_

I

C

P

N

I

s

k

c

o

l

c

F

_

K

L

C

I

C

P

e

h

t

s

e

d

i

s

e

b

w

o

l

t

u

p

n

i

n

e

h

w

,l

e

v

e

l

0

c

i

g

o

l

t

a

s

K

L

C

I

C

P

ll

a

s

p

o

t

S

y

b

d

e

p

p

o

t

s

r

o

g

n

i

n

n

u

r

e

e

r

f

e

r

a

y

e

h

t

r

e

h

t

e

h

w

s

ti

b

C

2

I

y

b

e

l

b

a

ll

o

r

t

n

o

c

e

r

a

h

c

i

h

w

.

P

O

T

S

_

I

C

P

2

2

D

G

R

W

P

_

tt

V

N

I

)

0

:

3

(

S

F

n

e

h

w

e

n

i

m

r

e

t

e

d

o

t

d

e

s

u

e

b

o

rt

s

e

v

it

i

s

n

e

s

l

e

v

e

l

a

s

i

t

u

p

n

i

L

T

T

V

L

V

3

.

3

s

i

h

T

.)

h

g

i

h

e

v

it

c

a

(

d

e

l

p

m

a

s

e

b

o

t

y

d

a

e

r

e

r

a

d

n

a

d

il

a

v

e

r

a

s

t

u

p

n

i

#

D

P

N

I

w

o

l

a

o

t

n

i

e

c

i

v

e

d

e

h

t

n

w

o

d

r

e

w

o

p

o

t

d

e

s

u

n

i

p

t

u

p

n

i

w

o

l

e

v

it

c

a

s

u

o

n

o

r

h

c

n

y

s

A

e

r

a

l

a

t

s

y

r

c

e

h

t

d

n

a

O

C

V

e

h

t

d

n

a

d

e

l

b

a

s

i

d

e

r

a

s

k

c

o

l

c

l

a

n

r

e

t

n

i

e

h

T

.

e

t

a

t

s

r

e

w

o

p

.

s

m

3

n

a

h

t

r

e

t

a

e

r

g

e

b

t

o

n

ll

i

w

n

w

o

d

r

e

w

o

p

e

h

t

f

o

y

c

n

e

t

a

l

e

h

T

.

d

e

p

p

o

t

s

3

2

8

4

D

D

V

A

R

W

P

.

V

3

.

3

t

u

p

t

u

o

z

H

M

8

4

r

o

f

r

e

w

o

p

g

o

l

a

n

A

4

2

3

S

F

N

I

.

n

o

r

e

w

o

p

t

a

d

e

h

c

t

a

l

t

u

p

n

I

.t

i

b

t

c

e

l

e

s

y

c

n

e

u

q

e

r

f

t

u

p

n

i

c

i

g

o

L

z

H

M

8

4

T

U

O

t

u

p

t

u

o

k

c

o

l

c

z

H

M

8

4

d

e

x

i

F

V

3

.

3

6

2

A

T

A

D

S

N

I

I

r

o

f

n

i

p

a

t

a

D

2

.t

n

a

r

e

l

o

t

V

5

y

rt

i

u

c

ri

c

C

7

2

K

L

C

S

O

/I

I

r

o

f

n

i

p

k

c

o

l

C

2

.t

n

a

r

e

l

o

t

V

5

y

rt

i

u

c

ri

c

C

8

2

#

P

O

T

S

_

K

L

C

N

I

n

e

h

w

l

e

v

e

l

"

0

"

c

i

g

o

l

t

a

s

k

c

o

l

c

R

D

D

r

o

P

G

A

,

U

P

C

s

tl

a

h

t

u

p

n

i

s

u

o

n

o

r

h

c

n

y

s

a

s

i

h

T

.

C

II

a

i

v

e

l

b

a

r

u

g

if

n

o

c

e

r

a

s

p

o

t

s

e

s

e

h

T

.

w

o

l

n

e

v

ir

d

,

1

4

,

7

3

,

5

3

,

1

3

,

9

2

7

4

,

3

4

)

0

:

6

(

C

R

D

D

T

U

O

.

s

t

u

p

t

u

o

C

R

D

D

ri

a

p

l

a

it

n

e

r

e

ff

i

d

f

o

s

k

c

o

l

c

"

y

r

o

t

n

e

m

e

l

p

m

o

C

"

,

2

4

,

8

3

,

6

3

,

2

3

,

0

3

8

4

,

4

4

)

0

:

6

(

T

R

D

D

T

U

O

.

s

t

u

p

t

u

o

T

R

D

D

ri

a

p

l

a

it

n

e

r

e

ff

i

d

f

o

s

k

c

o

l

c

"

e

u

r

T

"

5

4

,

0

4

,

3

3

L

D

D

V

R

W

P

V

5

.

2

r

o

f

y

l

p

p

u

s

r

e

w

o

P

1

5

F

E

R

I

T

U

O

a

s

e

ri

u

q

e

r

n

i

p

s

i

h

T

.

s

ri

a

p

K

L

C

U

P

C

e

h

t

r

o

f

t

n

e

r

r

u

c

e

c

n

e

r

e

f

e

r

e

h

t

s

e

h

s

il

b

a

t

s

e

n

i

p

s

i

h

T

.t

n

e

r

r

u

c

e

t

a

ir

p

o

r

p

p

a

e

h

t

h

s

il

b

a

t

s

e

o

t

r

e

d

r

o

n

i

d

n

u

o

r

g

o

t

d

e

it

r

o

t

s

i

s

e

r

n

o

i

s

i

c

e

r

p

d

e

x

if

6

5

,

3

5

)

0

:

1

(

T

K

L

C

U

P

C

T

U

O

d

n

a

s

t

u

p

t

u

o

t

n

e

r

r

u

c

e

r

a

e

s

e

h

T

.

s

t

u

p

t

u

o

U

P

C

ri

a

p

l

a

it

n

e

r

e

ff

i

d

f

o

s

k

c

o

l

c

"

e

u

r

T

"

.

s

a

i

b

e

g

a

tl

o

v

r

o

f

d

e

ri

u

q

e

r

e

r

a

s

r

o

t

s

i

s

e

r

l

a

n

r

e

t

x

e

5

5

,

2

5

)

0

:

1

(

C

K

L

C

U

P

C

T

U

O

s

t

u

p

t

u

o

t

n

e

r

r

u

c

e

r

a

e

s

e

h

T

.

s

t

u

p

t

u

o

U

P

C

ri

a

p

l

a

it

n

e

r

e

ff

i

d

f

o

s

k

c

o

l

c

"

y

r

o

t

n

e

m

e

l

p

m

o

C

"

.

s

a

i

b

e

g

a

tl

o

v

r

o

f

d

e

ri

u

q

e

r

e

r

a

s

r

o

t

s

i

s

e

r

l

a

n

r

e

t

x

e

d

n

a

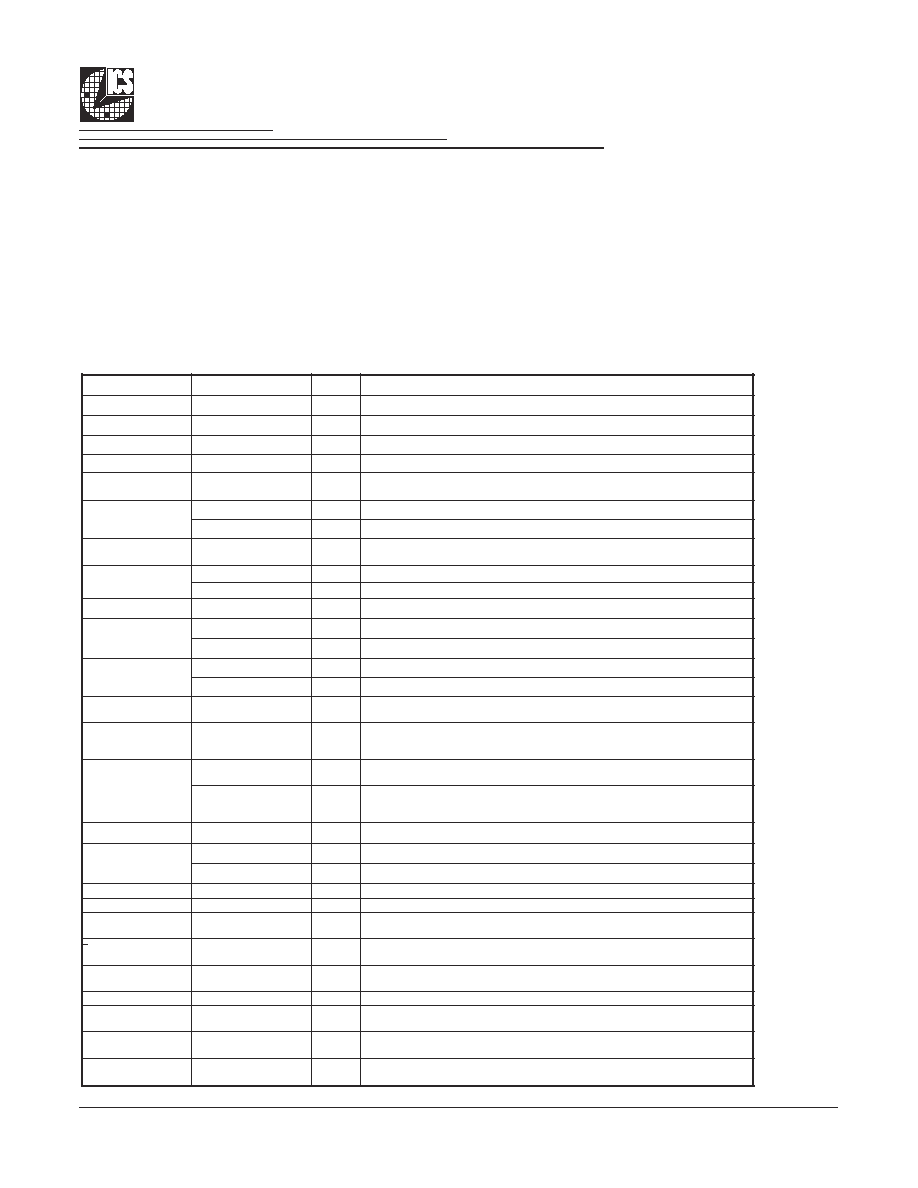

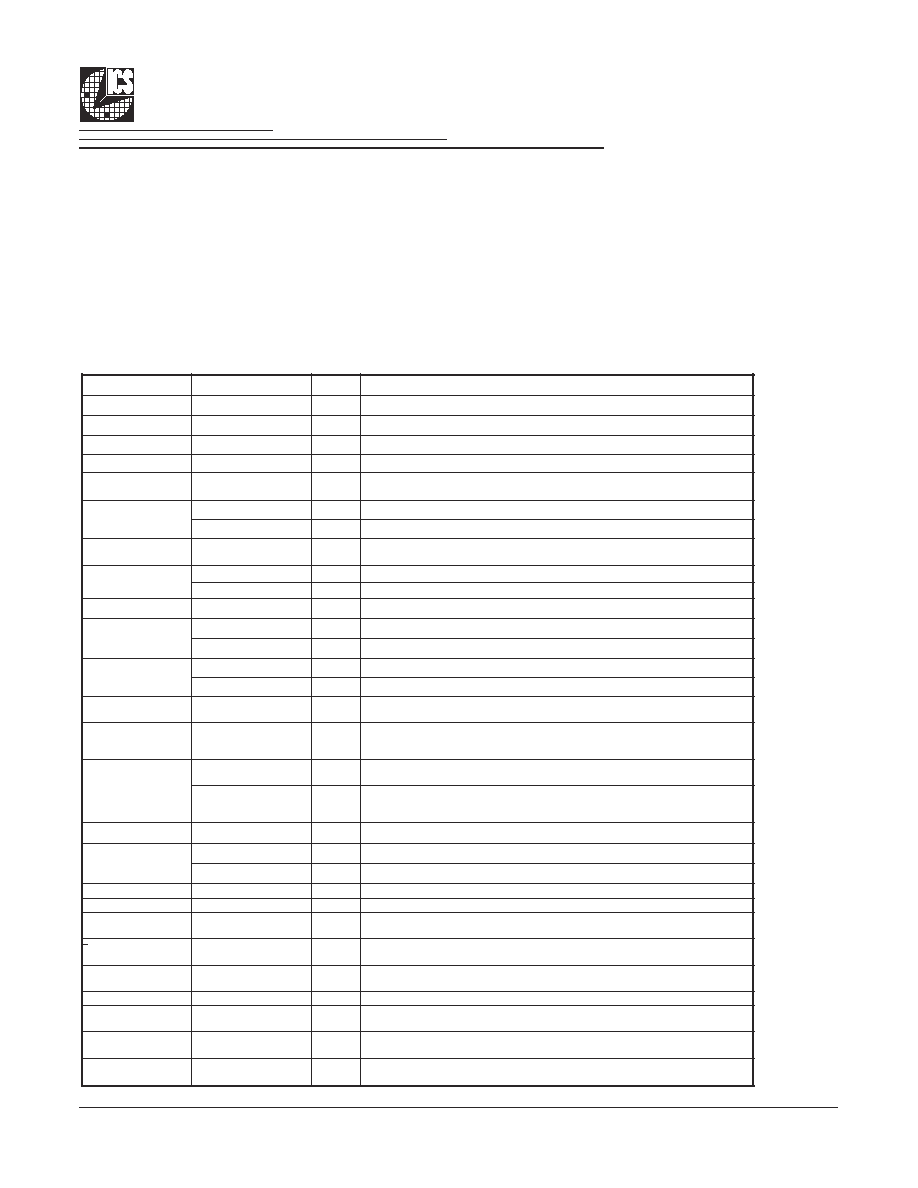

Pin Description

o

3

Third party brands and names are the property of their respective owners.

Integrated

Circuit

Systems, Inc.

ICS951104

Preliminary Product Preview

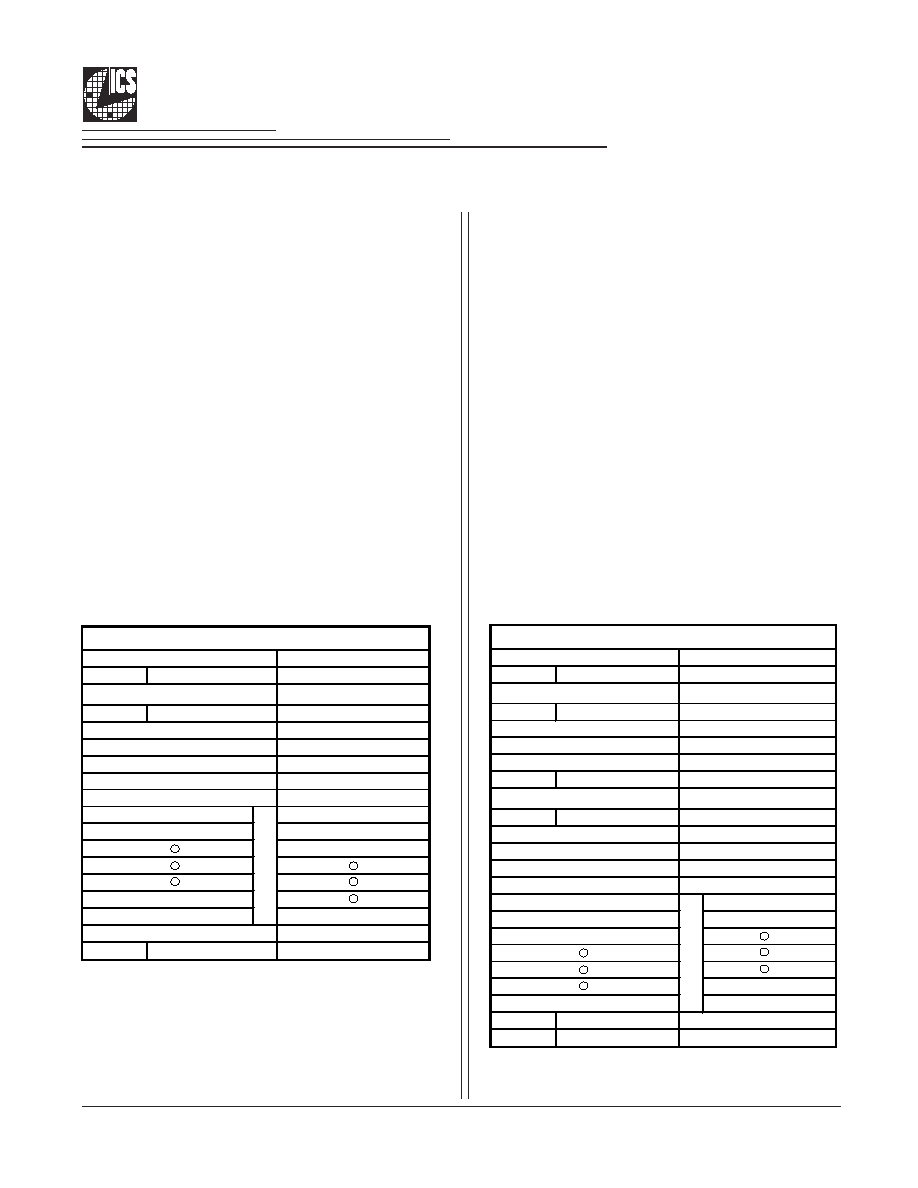

General I

2

C serial interface information

How to Write:

Controller (host) sends a start bit.

· Controller (host) sends the write address D2

(H)

· ICS clock will

acknowledge

· Controller (host) sends the begining byte location = N

· ICS clock will

acknowledge

· Controller (host) sends the data byte count = X

· ICS clock will

acknowledge

· Controller (host) starts sending

Byte N through

Byte N + X -1

(see Note 2)

· ICS clock will

acknowledge each byte one at a time

· Controller (host) sends a Stop bit

How to Read:

· Controller (host) will send start bit.

· Controller (host) sends the write address D2

(H)

· ICS clock will

acknowledge

· Controller (host) sends the begining byte

location = N

· ICS clock will

acknowledge

· Controller (host) will send a separate start bit.

· Controller (host) sends the read address D3

(H)

· ICS clock will

acknowledge

· ICS clock will send the data byte count = X

· ICS clock sends

Byte N + X -1

· ICS clock sends

Byte 0 through byte X (if X

(H)

was written to byte 8)

.

· Controller (host) will need to acknowledge each byte

· Controllor (host) will send a not acknowledge bit

· Controller (host) will send a stop bit

*See notes on the following page

.

ICS (Slave/Receiver)

T

WR

ACK

ACK

ACK

ACK

ACK

P

stoP bit

X Byt

e

Index Block Write Operation

Slave Address D2

(H)

Beginning Byte = N

WRite

starT bit

Controller (Host)

Byte N + X - 1

Data Byte Count = X

Beginning Byte N

T

starT bit

WR

WRite

RT

Repeat starT

RD

ReaD

Beginning Byte N

Byte N + X - 1

N

Not acknowledge

P

stoP bit

Slave Address D3

(H)

Index Block Read Operation

Slave Address D2

(H)

Beginning Byte = N

ACK

ACK

Data Byte Count = X

ACK

ICS (Slave/Receiver)

Controller (Host)

X Byt

e

ACK

ACK

4

Third party brands and names are the property of their respective owners.

Integrated

Circuit

Systems, Inc.

ICS951104

Preliminary Product Preview

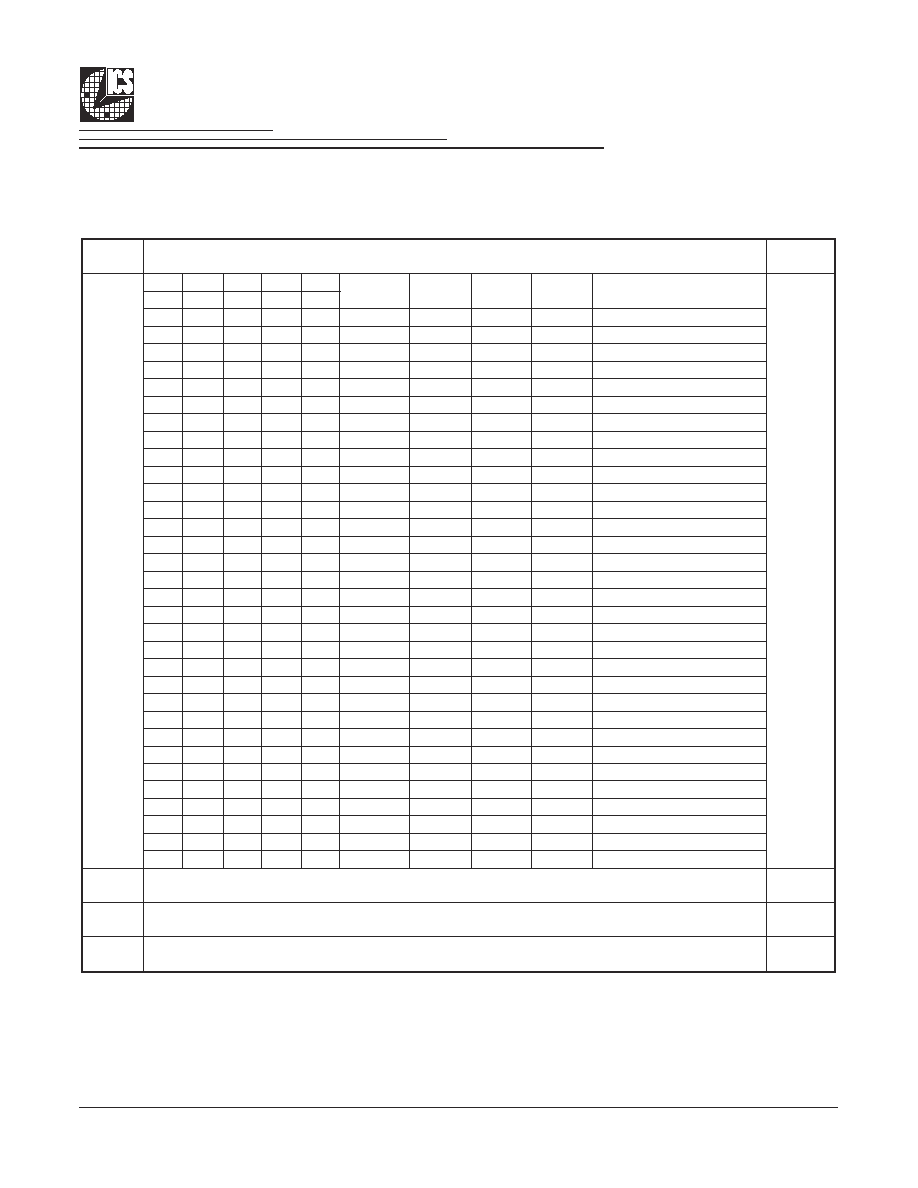

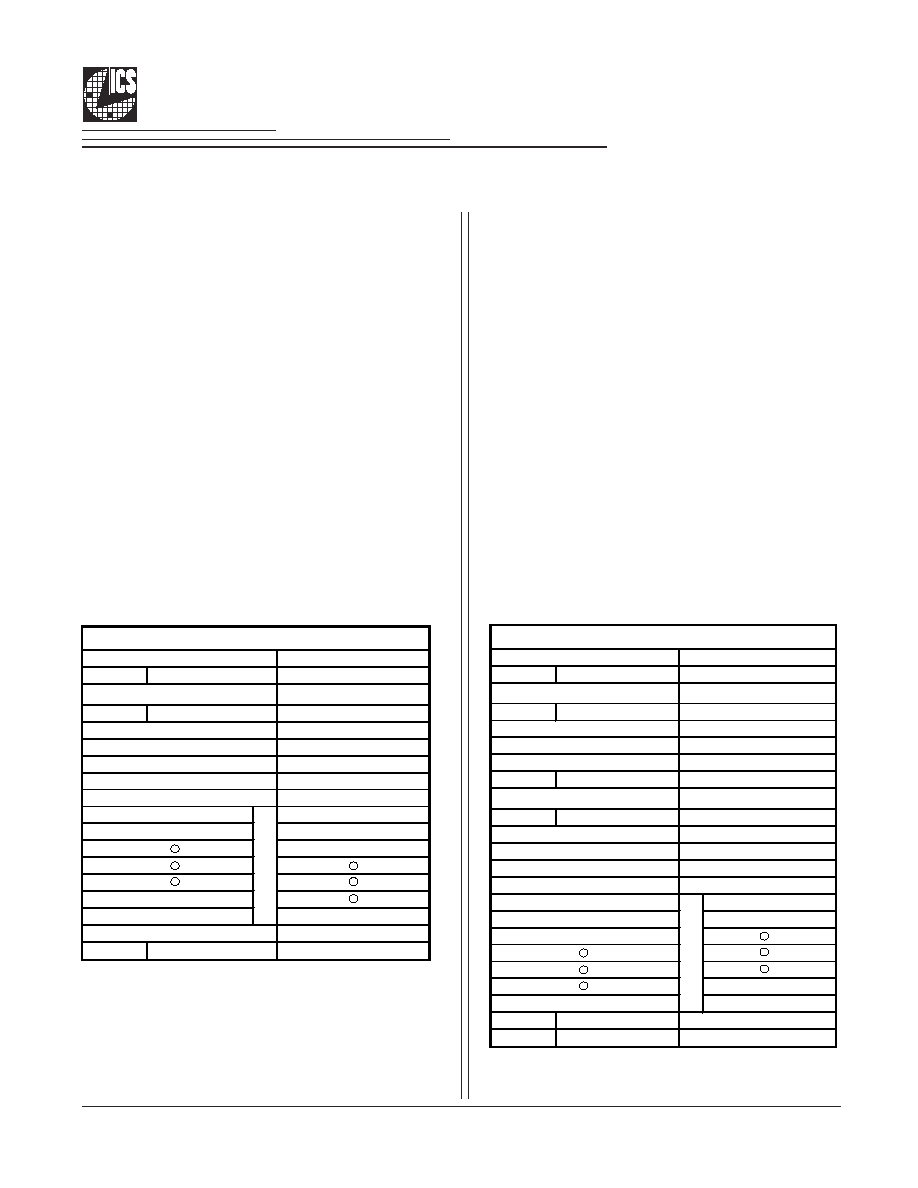

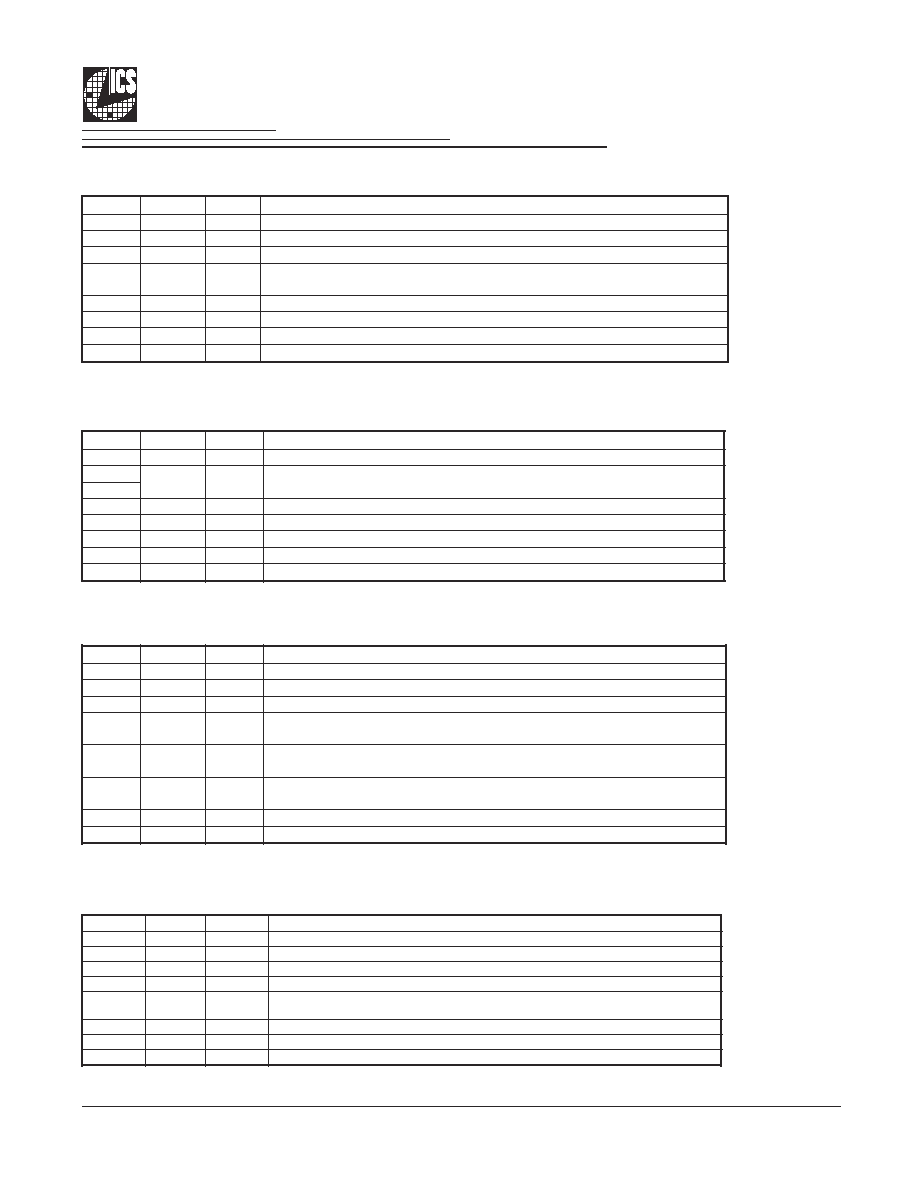

Byte0: Functionality and Frequency Select Register (default = 0)

Serial Configuration Command Bitmap

Note1: Default at power-up will be for latched logic inputs to define frequency, as displayed by Bit 3.

The I

2

C readback of the power up default indicates the revision ID in bits 2, 7:4 as shown.

t

i

B

n

o

i

t

p

i

r

c

s

e

D

D

W

P

,

2

t

i

B

4

:

7

t

i

B

3

S

F

2

S

F

1

S

F

0

S

F

K

L

C

U

P

C

)

z

H

M

(

R

D

D

)

z

H

M

(

P

G

A

)

z

H

M

(

K

L

C

I

C

P

)

z

H

M

(

e

g

a

t

n

e

c

e

r

P

d

a

e

r

p

S

0

0

0

0

0

1

e

t

o

N

2

t

i

B

7

t

i

B

6

t

i

B

5

t

i

B

4

t

i

B

0

0

0

0

0

6

6

.

6

6

6

6

.

6

6

6

6

.

6

6

3

3

.

3

3

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

-

/

+

0

0

0

0

1

6

6

.

6

6

0

0

.

0

0

1

6

6

.

6

6

3

3

.

3

3

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

-

/

+

0

0

0

1

0

0

0

.

0

0

1

6

6

.

6

6

6

6

.

6

6

3

3

.

3

3

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

-

/

+

0

0

0

1

1

0

0

.

0

0

1

0

0

.

0

0

1

6

6

.

6

6

3

3

.

3

3

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

-

/

+

0

0

1

0

0

0

0

.

0

0

1

3

3

.

3

3

1

6

6

.

6

6

3

3

.

3

3

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

-

/

+

0

0

1

0

1

3

3

.

3

3

1

6

6

.

6

6

6

6

.

6

6

3

3

.

3

3

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

-

/

+

0

0

1

1

0

3

3

.

3

3

1

0

0

.

0

0

1

6

6

.

6

6

3

3

.

3

3

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

-

/

+

0

0

1

1

1

3

3

.

3

3

1

3

3

.

3

3

1

6

6

.

6

6

3

3

.

3

3

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

-

/

+

0

1

0

0

0

6

6

.

6

6

6

6

.

6

6

6

6

.

6

6

3

3

.

3

3

d

a

e

r

p

S

n

w

o

D

%

5

.

0

-

o

t

0

0

1

0

0

1

6

6

.

6

6

0

0

.

0

0

1

6

6

.

6

6

3

3

.

3

3

d

a

e

r

p

S

n

w

o

D

%

5

.

0

-

o

t

0

0

1

0

1

0

0

0

.

0

0

1

6

6

.

6

6

6

6

.

6

6

3

3

.

3

3

d

a

e

r

p

S

n

w

o

D

%

5

.

0

-

o

t

0

0

1

0

1

1

0

0

.

0

0

1

0

0

.

0

0

1

6

6

.

6

6

3

3

.

3

3

d

a

e

r

p

S

n

w

o

D

%

5

.

0

-

o

t

0

0

1

1

0

0

0

0

.

0

0

1

3

3

.

3

3

1

6

6

.

6

6

3

3

.

3

3

d

a

e

r

p

S

n

w

o

D

%

5

.

0

-

o

t

0

0

1

1

0

1

3

3

.

3

3

1

6

6

.

6

6

6

6

.

6

6

3

3

.

3

3

d

a

e

r

p

S

n

w

o

D

%

5

.

0

-

o

t

0

0

1

1

1

0

3

3

.

3

3

1

0

0

.

0

0

1

6

6

.

6

6

3

3

.

3

3

d

a

e

r

p

S

n

w

o

D

%

5

.

0

-

o

t

0

0

1

1

1

1

3

3

.

3

3

1

3

3

.

3

3

1

6

6

.

6

6

3

3

.

3

3

d

a

e

r

p

S

n

w

o

D

%

5

.

0

-

o

t

0

1

0

0

0

0

0

0

.

0

7

0

0

.

0

7

0

0

.

0

7

0

0

.

5

3

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

-

/

+

1

0

0

0

1

0

0

.

0

0

1

7

6

.

6

6

1

0

5

.

2

6

5

2

.

1

3

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

-

/

+

1

0

0

1

0

0

0

.

5

0

1

0

0

.

0

7

0

0

.

0

7

0

0

.

5

3

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

-

/

+

1

0

0

1

1

0

0

.

5

0

1

0

0

.

5

0

1

0

0

.

0

7

0

0

.

5

3

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

-

/

+

1

0

1

0

0

0

0

.

5

0

1

0

0

.

0

4

1

0

0

.

0

7

0

0

.

5

3

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

-

/

+

1

0

1

0

1

0

0

.

0

0

1

7

6

.

6

6

1

3

4

.

1

7

2

7

.

5

3

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

-

/

+

1

0

1

1

0

0

0

.

0

4

1

0

0

.

5

0

1

0

0

.

0

7

0

0

.

5

3

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

-

/

+

1

0

1

1

1

0

0

.

0

4

1

0

0

.

0

4

1

0

0

.

0

7

0

0

.

5

3

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

-

/

+

1

1

0

0

0

0

3

.

3

3

1

0

6

.

6

6

1

3

3

.

3

3

5

6

.

6

6

f

f

O

d

a

e

r

p

S

1

1

0

0

1

3

3

.

3

7

0

0

.

0

1

1

3

3

.

3

7

6

6

.

6

3

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

-

/

+

1

1

0

1

0

0

0

.

0

1

1

3

3

.

3

7

3

3

.

3

7

6

6

.

6

3

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

-

/

+

1

1

0

1

1

0

0

.

0

1

1

0

0

.

0

1

1

3

3

.

3

7

6

6

.

6

3

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

-

/

+

1

1

1

0

0

0

0

.

0

1

1

6

6

.

6

4

1

3

3

.

3

7

6

6

.

6

3

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

-

/

+

1

1

1

0

1

6

6

.

6

4

1

3

3

.

3

7

3

3

.

3

7

6

6

.

6

3

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

-

/

+

1

1

1

1

0

6

6

.

6

4

1

0

0

.

0

1

1

3

3

.

3

7

6

6

.

6

3

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

-

/

+

1

1

1

1

1

6

6

.

6

4

1

6

6

.

6

4

1

3

3

.

3

7

6

6

.

6

3

d

a

e

r

p

S

r

e

t

n

e

C

%

5

2

.

0

-

/

+

3

t

i

B

s

t

u

p

n

I

d

e

h

c

t

a

L

,

t

c

e

l

e

s

e

r

a

w

d

r

a

h

y

b

d

e

t

c

e

l

e

s

s

i

y

c

n

e

u

q

e

r

F

-

0

4

:

7

,

2

t

i

B

y

b

d

e

t

c

e

l

e

s

s

i

y

c

n

e

u

q

e

r

F

-

1

0

1

t

i

B

l

a

m

r

o

N

-

0

d

e

l

b

a

n

E

m

u

r

t

c

e

p

S

d

a

e

r

p

S

-

1

0

0

t

i

B

g

n

i

n

n

u

R

-

0

s

t

u

p

t

u

o

ll

a

e

t

a

t

s

i

r

T

-

1

0

5

Third party brands and names are the property of their respective owners.

Integrated

Circuit

Systems, Inc.

ICS951104

Preliminary Product Preview

Byte 1: Output Control Register

(1 = enable, 0 = disable)

Byte 3: Output Control Register

(1 = enable, 0 = disable)

Byte 2: Output Control Register

(1 = enable, 0 = disable)

Byte 4: Output Control Register

(1 = enable, 0 = disable)

ti

B

#

n

i

P

D

W

P

n

o

it

p

i

r

c

s

e

D

7

ti

B

4

2

1

Z

H

M

8

4

6

ti

B

7

4

,

8

4

1

0

C

/

T

R

D

D

5

ti

B

-

1

e

l

b

a

s

i

D

=

0

,

e

l

b

a

n

E

=

1

t

c

e

t

e

d

tf

i

h

s

r

a

e

g

t

e

s

e

R

4

ti

B

,

1

4

,

2

4

3

4

,

4

4

1

)

1

:

2

(

C

/

T

R

D

D

3

ti

B

,

5

3

,

6

3

7

3

,

8

3

1

)

3

:

4

(

C

/

T

R

D

D

2

ti

B

,

9

2

,

0

3

1

3

,

2

3

1

)

5

:

6

(

C

/

T

R

D

D

1

ti

B

0

1

1

1

P

G

A

0

ti

B

9

1

0

P

G

A

ti

B

#

n

i

P

D

W

P

n

o

it

p

i

r

c

s

e

D

7

ti

B

2

1

1

E

_

K

L

C

I

C

P

6

ti

B

0

2

1

5

_

K

L

C

I

C

P

5

ti

B

4

ti

B

9

1

1

4

_

K

L

C

I

C

P

3

ti

B

8

1

1

3

_

K

L

C

I

C

P

2

ti

B

5

1

1

2

_

K

L

C

I

C

P

1

ti

B

4

1

1

1

_

K

L

C

I

C

P

0

ti

B

3

1

1

0

_

K

L

C

I

C

P

t

i

B

#

n

i

P

D

W

P

n

o

i

t

p

i

r

c

s

e

D

7

ti

B

-

0

e

l

b

a

p

p

o

t

S

=

1

;

n

u

R

e

e

r

F

=

0

,

ti

b

e

l

b

a

n

e

P

O

T

S

_

K

L

C

a

i

v

p

o

t

S

0

C

/

T

U

P

C

6

ti

B

-

0

e

l

b

a

p

p

o

t

S

=

1

;

n

u

R

e

e

r

F

=

0

,

ti

b

e

l

b

a

n

e

P

O

T

S

_

K

L

C

a

i

v

p

o

t

S

1

C

/

T

U

P

C

5

ti

B

-

0

e

l

b

a

p

p

o

t

S

=

1

;

n

u

R

e

e

r

F

=

0

,

ti

b

e

l

b

a

n

e

P

O

T

S

_

K

L

C

a

i

v

p

o

t

S

0

P

G

A

4

ti

B

-

0

e

l

b

a

p

p

o

t

S

=

1

;

n

u

R

e

e

r

F

=

0

,

ti

b

e

l

b

a

n

e

P

O

T

S

_

K

L

C

a

i

v

p

o

t

S

1

P

G

A

3

ti

B

-

0

=

1

;

n

u

R

e

e

r

F

=

0

,

ti

b

e

l

b

a

n

e

P

O

T

S

_

K

L

C

a

i

v

p

o

t

S

)

0

:

6

(

C

/

T

R

D

D

e

l

b

a

p

p

o

t

S

2

ti

B

-

0

e

l

b

a

p

p

o

t

S

=

1

;

n

u

R

e

e

r

F

=

0

,

ti

b

e

l

b

a

n

e

P

O

T

S

_

K

L

C

a

i

v

p

o

t

S

0

C

/

T

R

D

D

1

ti

B

-

0

w

o

L

p

o

t

S

=

1

;

h

g

i

H

p

o

t

S

=

0

,l

o

r

t

n

o

c

y

ti

r

a

l

o

p

P

O

T

S

#

D

P

1

T

K

L

C

U

P

C

0

ti

B

-

0

w

o

L

p

o

t

S

=

1

;

h

g

i

H

p

o

t

S

=

0

,l

o

r

t

n

o

c

y

ti

r

a

l

o

p

P

O

T

S

#

D

P

0

T

K

L

C

U

P

C

ti

B

#

n

i

P

D

W

P

n

o

it

p

i

r

c

s

e

D

7

ti

B

-

X

)

k

c

a

b

d

a

e

r

(

L

E

S

_

T

L

U

M

6

ti

B

2

5

,

3

5

1

1

C

/

T

U

P

C

5

ti

B

5

5

,

6

5

1

0

C

/

T

U

P

C

4

ti

B

0

2

1

l

o

rt

n

o

c

h

t

g

n

e

rt

s

e

v

ir

d

5

_

K

L

C

I

C

P

X

1

=

0

,

X

2

=

1

3

ti

B

-

X

k

c

a

b

d

a

e

R

3

S

F

2

ti

B

-

X

k

c

a

b

d

a

e

R

2

S

F

1

ti

B

-

X

k

c

a

b

d

a

e

R

1

S

F

0

ti

B

-

X

k

c

a

b

d

a

e

R

0

S

F