Integrated

Circuit

Systems, Inc.

ICSSSTV32852

0513F--05/13/03

Recommended Application:

∑

DDR Memory Modules

∑

Provides complete DDR DIMM logic solution with

ICS93V857 or ICS95V857

∑

SSTL_2 compatible data registers

Product Features:

∑

Differential clock signals

∑

Supports SSTL_2 class II specifications on inputs

and outputs

∑

Low-voltage operation

- V

DD

= 2.3V to 2.7V

∑

Available in 114 ball BGA package.

DDR 24-Bit to 48-Bit Registered Buffer

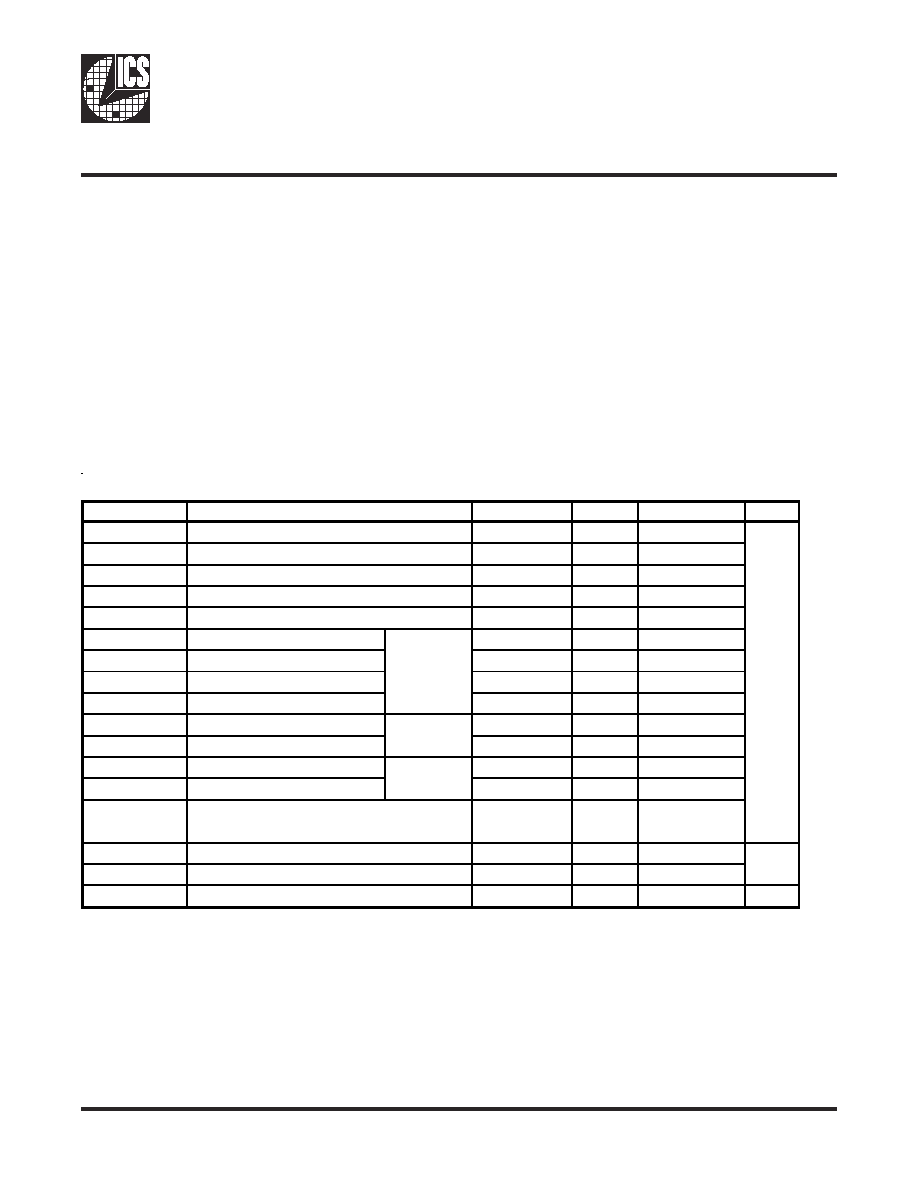

Truth Table

1

Block Diagram

Notes:

1.

H = "High" Signal Level

L = "Low" Signal Level

= Transition "Low"-to-"High"

= Transition "High"-to-"Low"

X = Don't Care

2.

Output level before the indicated

steady state input conditions were

established.

CLK

CLK#

D1

VREF

RESET#

To 23 Other Channels

Q1A

Q1B

CLK

R

D1

A

B

1

2

3

4

5

6

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Pin Configuration

114-Pin Ball BGA

s

t

u

p

n

I

s

t

u

p

t

u

O

Q

#

T

E

S

E

R

K

L

C

#

K

L

C

D

Q

L

r

o

X

g

n

i

t

a

o

l

F

r

o

X

g

n

i

t

a

o

l

F

r

o

X

g

n

i

t

a

o

l

F

L

H

H

H

H

L

L

H

H

r

o

L

H

r

o

L

X

Q

0

)

2

(

Pin Configuration Assignments

1

2

3

4

5

6

A

Q2A

Q1A

CLK

CLK#

Q1B

Q2B

B

Q3A

VDDQ

GND

GND

VDDQ

Q3B

C

Q5A

Q4A

VDDQ

VDDQ

Q4B

Q5B

D

Q7A

Q6A

GND

GND

Q6B

Q7B

E

Q8A

GND

VDDQ

VDDQ

GND

Q8B

F

Q10A

Q9A

VDDQ

VDDQ

Q9B

Q10B

G

Q12A

Q11A

GND

GND

Q11B

Q12B

H

Q13A

VDD

VDDQ

VDDQ

VDD

Q13B

J

Q14A

Q15A

GND

GND

Q15B

Q14B

K

Q17A

Q16A

VDDQ

VDDQ

Q16B

Q17B

L

Q18A

Q19A

GND

GND

Q19B

Q18B

M

Q20A

VDDQ

GND

GND

VDDQ

Q20B

N

Q22A

Q21A

VDDQ

VDDQ

Q21B

Q22B

P

Q23A

VDDQ

GND

GND

VDDQ

Q23B

R

Q24A

VDD

RESET#

VREF

VDD

Q24B

T

D2

D1

D6

D18

D13

D14

U

D4

D3

D10

D22

D15

D16

V

D5

D7

D11

D23

D19

D17

W

D8

D9

D12

D24

D21

D20

2

ICSSSTV32852

0513F--05/13/03

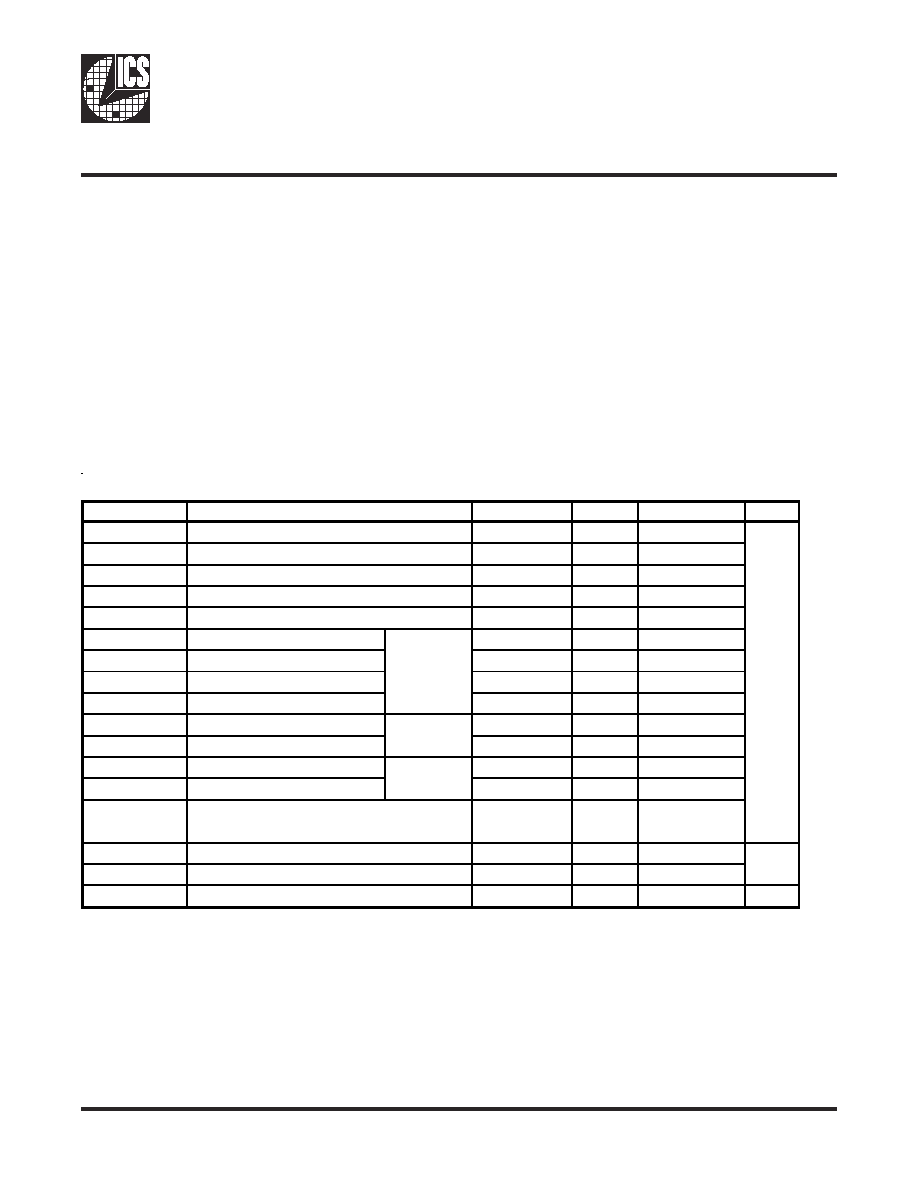

General Description

R

E

B

M

U

N

N

I

P

E

M

A

N

N

I

P

E

P

Y

T

N

O

I

T

P

I

R

C

S

E

D

,

1

K

,

1

L

,

2

L

,

1

M

,

2

N

,

1

N

,

1

P

,

1

R

,

2

F

,

1

F

,

2

G

,

1

G

,

1

H

,

1

J

,

2

J

,

2

K

,

1

A

,

1

B

,

2

C

,

1

C

,

2

D

,

1

D

,

1

E

2

A

A

)

1

:

4

2

(

Q

T

U

P

T

U

O

t

u

p

t

u

o

a

t

a

D

,

6

L

,

5

L

,

6

M

,

5

N

,

6

N

,

6

P

,

6

R

,

5

G

,

6

G

,

6

H

,

6

J

,

5

J

,

5

K

,

6

K

,

5

C

,

6

C

,

5

D

,

6

D

,

6

E

,

5

F

,

6

F

5

A

,

6

A

,

6

B

B

)

1

:

4

2

(

Q

T

U

P

T

U

O

t

u

p

t

u

o

a

t

a

D

,

3

M

,

3

L

,

3

J

,

3

G

,

3

D

,

3

B

,

2

E

,

4

M

,

4

L

,

4

J

,

4

G

,

4

D

,

4

B

,

3

P

5

E

,

4

P

D

N

G

R

W

P

d

n

u

o

r

G

,

3

H

,

3

F

,

3

E

,

3

C

,

2

P

,

2

M

,

2

B

,

4

K

,

4

H

,

4

F

,

4

E

,

4

C

,

3

N

,

3

K

5

P

,

5

M

,

5

B

,

4

N

Q

D

D

V

R

W

P

l

a

n

i

m

o

n

V

5

.

2

,

e

g

a

t

l

o

v

y

l

p

p

u

s

t

u

p

t

u

O

,

4

T

,

5

V

,

6

W

,

5

W

,

4

U

,

4

V

,

4

W

,

3

V

,

3

W

,

5

T

,

6

T

,

5

U

,

6

U

,

6

V

,

1

U

,

1

V

,

3

T

,

2

V

,

1

W

,

2

W

,

3

U

2

T

,

1

T

,

2

U

)

1

:

4

2

(

D

T

U

P

N

I

t

u

p

n

i

a

t

a

D

3

A

K

L

C

T

U

P

N

I

t

u

p

n

i

k

c

o

l

c

r

e

t

s

a

m

e

v

i

t

i

s

o

P

4

A

#

K

L

C

T

U

P

N

I

t

u

p

n

i

k

c

o

l

c

r

e

t

s

a

m

e

v

i

t

a

g

e

N

5

R

,

2

R

,

5

H

,

2

H

D

D

V

R

W

P

l

a

n

i

m

o

n

V

5

.

2

,

e

g

a

t

l

o

v

y

l

p

p

u

s

e

r

o

C

3

R

#

T

E

S

E

R

T

U

P

N

I

)

w

o

l

e

v

i

t

c

a

(

t

e

s

e

R

4

R

F

E

R

V

T

U

P

N

I

l

a

n

i

m

o

n

V

5

2

.

1

,

e

g

a

t

l

o

v

e

c

n

e

r

e

f

e

r

t

u

p

n

I

Pin Configuration

The 24-bit-to-48-bit ICSSSTV32852 is a universal bus driver designed for 2.3V to 2.7V V

DD

operation and SSTL_2 I/

O levels, except for the LVCMOS RESET# input.

Data flow from D to Q is controlled by the differential clock (CLK/CLK#) and a control signal (RESET#). The positive

edge of CLK is used to trigger the data flow and CLK# is used to maintain sufficient noise margins where as RESET#,

an LVCMOS asynchronous signal, is intended for use at the time of power-up only. ICSSSTV32852 supports low-power

standby operation. A logic level "Low" at RESET# assures that all internal registers and outputs (Q) are reset to the

logic "Low" state, and all input receivers, data (D) and clock (CLK/CLK#) are switched off. Please note that RESET#

must always be supported with LVCMOS levels at a valid logic state because VREF may not be stable during power-

up.

To ensure that outputs are at a defined logic state before a stable clock has been supplied, RESET# must be held

at a logic "Low" level during power up.

In the DDR DIMM application, RESET# is specified to be completely asynchronous with respect to CLK and CLK#.

Therefore, no timing relationship can be guaranteed between the two signals. When entering a low-power standby state,

the register will be cleared and the outputs will be driven to a logic "Low" level quickly relative to the time to disable

the differential input receivers. This ensures there are no glitches on the output. However, when coming out of low-power

standby state, the register will become active quickly relative to the time to enable the differential input receivers. When

the data inputs are at a logic level "Low" and the clock is stable during the "Low"-to-"High" transition of RESET# until

the input receivers are fully enabled, the design ensures that the outputs will remain at a logic "Low" level.

3

ICSSSTV32852

0513F--05/13/03

Absolute Maximum Ratings

Storage Temperature . . . . . . . . . . . . . . . . . . . . ≠65∞C to +150∞C

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . -0.5 to 3.6V

Input Voltage

1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

-0.5 to VDD +0.5

Output Voltage

1,2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

-0.5 to VDDQ +0.5

Input Clamp Current . . . . . . . . . . . . . . . . . . . . ±50 mA

Output Clamp Current . . . . . . . . . . . . . . . . . . . ±50mA

Continuous Output Current . . . . . . . . . . . . . . . ±50mA

VDD, VDDQ or GND Current/Pin . . . . . . . . . . ±100mA

Package Thermal Impedance

3

. . . . . . . . . . . . . . .

55∞C/W

Stresses above those listed under

Absolute Maximum Ratings may cause permanent damage to the device. These

ratings are stress specifications only and functional operation of the device at these or any other conditions above those

listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions

for extended periods may affect product reliability.

Notes:

1. The input and output negative voltage

ratings may be excluded if the input

and output clamp ratings are observed.

2. This current will flow only when the

output is in the high state level

V

0

>V

DDQ

.

3. The package thermal impedance is

calculated in accordance with

JESD 51.

Recommended Operating Conditions

PARAMETER

MIN

TYP

MAX

UNITS

V

DD

2.3

2.5

2.7

V

DDQ

2.3

2.5

2.7

V

REF

1.15

1.25

1.35

V

TT

V

REF

- 0.04

V

REF

V

REF

+ 0.04

V

I

Input Voltage

0

V

DDQ

V

IH (DC)

DC Input High Voltage

V

REF

+ 0.15

V

IH (AC)

AC Input High Voltage

V

REF

+ 0.31

V

IL (DC)

DC Input Low Voltage

V

REF

- 0.15

V

IL

(DC)

AC Input Low Voltage

V

REF

- 0.31

V

IH

Input High Voltage Level

1.7

V

IL

Input Low Voltage Level

0.7

V

ICR

Common mode Input Range

0.97

1.53

V

ID

Differential Input Voltage

0.36

V

IX

(V

DDQ

/2) - 0.2

(V

DDQ

/2) + 0.2

I

OH

19

I

OL

19

T

A

0

70

∞C

1

Guarenteed by design, not 100% tested in production.

DESCRIPTION

Supply Voltage

I/O Supply Voltage

Reference Voltage

Operating Free-Air Temperature

RESET#

CLK, CLK#

V

Termination Voltage

Cross Point Voltage of Differential Clock

Pair

High-Level Output Current

Low-Level Output Current

Data Inputs

mA

4

ICSSSTV32852

0513F--05/13/03

Electrical Characteristics - DC

T

A

= 0 - 70∞C; V

DD

= 2.5 +/-0.2V, V

DDQ

=2.5 +/-0.2V; (unless otherwise stated)

SYMBOL

PARAMETERS

V

DDQ

MIN

TYP

MAX

UNITS

V

IK

I

I

= -18mA

2.3V

-1.2

I

OH

= -100µA

2.3V - 2.7V

V

DDQ

- 0.2

I

OH

= -16mA

2.3V

2.05

I

OL

= 100µA

2.3V - 2.7V

0.2

I

OL

= 16mA

2.3V

0.20

I

I

All Inputs

V

I

= V

DD

or GND

2.7V

±5

µA

Standby (Static)

RESET# = GND

0.01

µA

Operating (Static)

V

I

= V

IH(AC)

or V

IL(AC)

,

RESET# = V

DD

40

mA

Dynamic operating

(clock only)

RESET# = V

DD

,

V

I

= V

IH(AC)

or V

IL(AC)

,

CLK and CLK# switching

50% duty cycle.

35

µA/clock

MHz

Dynamic Operating

(per each data input)

RESET# = V

DD

,

V

I

= V

IH(AC)

or V

IL (AC)

,

CLK and CLK# switching

50% duty cycle. One data

input switching at half

clock frequency, 50%

duty cycle

7

µA/ clock

MHz/data

r

OH

Output High

2.3V - 2.7V

12

r

OL

Output Low

2.3V - 2.7V

10

r

O(D)

[r

OH

-

r

OL

] each

separate bit

2.5V

4

Data Inputs

2.5

3.5

CLK and CLK#

2.5

3.5

Notes:

1. Guaranteed by design, not 100% tested in production.

C

i

I

OL

= 20mA

I

O

= 20mA, T

A

= 25∞C

V

OH

V

OL

I

DD

I

DDD

I

O

= 0

CONDITIONS

2.5V

2.5V

V

I

= V

REF

±350mV

V

ICR

= 1.25V, V

I(PP)

= 360mV

pF

I

OH

= -20mA

V

5

ICSSSTV32852

0513F--05/13/03

Timing Requirements

(over recommended operating free-air temperature range, unless otherwise noted)

MIN

MAX

f

clock

Clock frequency

200

MHz

t

PD

Clock to output time

1.9

2.7

ns

t

RST

Reset to output time

4.5

ns

t

SL

Output slew rate

1

4

V/ns

Setup time, fast slew rate

2, 4

0.50

ns

Setup time, slow slew rate

3, 4

0.70

ns

Hold time, fast slew rate

2, 4

0.30

ns

Hold time, slow slew rate

3, 4

0.50

ns

1 - Guaranteed by design, not 100% tested in production.

2 - For data signal input slew rate of 1V/ns.

4 - CLK/CLK# signal input slew rate of 1V/ns.

3 - For data signal input slew rate of 0.5V/ns and < 1V/ns.

V

DD

= 2.5V ±0.2V

UNITS

PARAMETERS

Data before CLK

, CLK#

Data after CLK

, CLK#

SYMBOL

t

S

T

h

Notes:

Switching Characteristics

(over recommended operating free-air temperature range, unless otherwise noted)

MIN

TYP

MAX

fmax

200

MHz

t

PD

CLK, CLK#

Q

1.9

2.7

ns

t

phl

RESET#

Q

4.5

ns

SYMBOL

V

DD

= 2.5V ±0.2V

UNITS

From

(Input)

To

(Output)

6

ICSSSTV32852

0513F--05/13/03

Notes: 1. CL incluces probe and jig capacitance.

2. I

DD

tested with clock and data inputs held at V

DD

or GND, and Io = 0mA.

3. All input pulses are supplied by generators having the following chareacteristics: PRR

10 MHz,

Zo=50

, input slew rate = 1 V/ns ±20% (unless otherwise specified).

4. The outputs are measured one at a time with one transition per measurement.

5. V

TT

= V

REF

= V

DDQ

/2

6. V

IH

= V

REF

+ 310mV (ac voltage levels) for differential inputs. V

IH

= V

DD

for LVCMOS input.

7. V

IL

= V

REF

-310mV (ac voltage levels) for differential inputs. V

IL

= GND for LVCMOS input.

8. t

PLH

and t

PHL

are the same as t

pd

Test Point

Load Circuit

From Output

Under Test

C = 30 pF

(see Note 1)

L

V

TT

R =

L

50

LVCMOS

RESET#

Input

LVCMOS

RESET#

Input

V

/2

DD

t

inact

t

act

I

(see note 2)

DD

I

DDH

I

DDL

10%

90%

Voltage and Current Waveforms

Inputs Active and Inactive Times

Voltage Waveforms - Propagation Delay Times

Voltage Waveforms - Propagation Delay Times

Parameter Measurement Information (V

= 2.5V ±0.2V)

DD

Voltage Waveforms - Pulse Duration

Voltage Waveforms - Setup and Hold Times

V

/2

DD

V

DD

0 V

t

w

t

SU

t

h

V

IH

V

IH

V

OH

V

TT

V

TT

V

TT

V

OH

V

IH

V

IL

V

IL

V

OL

V

OL

V

I(pp)

V

I(pp)

V

IL

V

REF

V

REF

V

REF

V

REF

V

ICR

V

ICR

t

PHL

t

PHL

t

PHL

V

/2

DD

V

ICR

Input

Input

Timing

Input

Timing

Input

Output

Output

7

ICSSSTV32852

0513F--05/13/03

D

E

T Min/Max

e

HORIZ

VERT

TOTAL

d

h Min/Max

b

c

16.00 Bsc

5.50 Bsc

1.30/1.50

0.80 Bsc

6

19

114

0.46

0.31/0.41

0.80

0.75

10-0055

ALL DIMENSIONS IN MILLIMETERS

REF. DIMENSIONS

----- BALL GRID -----

Ordering Information

ICSSSTV32852yHT

Designation for tape and reel packaging

Package Type

H = BGA

Revision Designator (will not correlate with datasheet revision)

Device Type

Prefix

ICS = Standard Device

Example:

ICS XXXX y H - T