APRIL 2004

DSC-6435/0B

1

©

2003 Integrated Device Technology, Inc.

All rights reserved. Product specifications subject to change without notice.

NETWORK SEARCH ENGINE

32K x 72 Entries

Datasheet

Brief

75N43102

Device Description

IDT provides proven, industry-leading network search engines

(NSEs) that enable and accelerate the intelligent processing of network

services in communications equipment. As a part of the complete IDT

classification subsystem that includes content inspection engines, the IDT

family of NSEs delivers high-performance, feature-rich, easy-to-use,

integrated search accelerators.

The IDT 75N43102 is ideally suited for cost-sensitive applications

in the enterprise and access markets. It is a full-ternary 32K x 72 entry

device where each entry location in the NSE has both a Data entry and

an associated Mask entry. The NSE devices integrate content addres-

sable memory (CAM) technology with high-performance logic. The

device can perform Lookup operations plus Read and Write maintenance

operations.

The IDT 75N43102 NSE device has a bi-directional bus that is a

multiplexed address and data bus that can support 62.5 million sustained

searches per second. This device can be configured to enable multiple

width lookups from 72 to 288 bits wide. The IDT 75N43102 requires a

1.5-volt V

DD1

supply and a 2.5-volt V

DD2

supply.

The IDT 75N43102 NSE utilizes the latest high-performance 1.5V

CMOS processing technology and is packaged in a JEDEC Standard,

256 pin low profile Ball Grid Array.

To request the full IDT75N43102 datasheet, please contact your local

IDT Sales Representative or call 1-831-754-4555

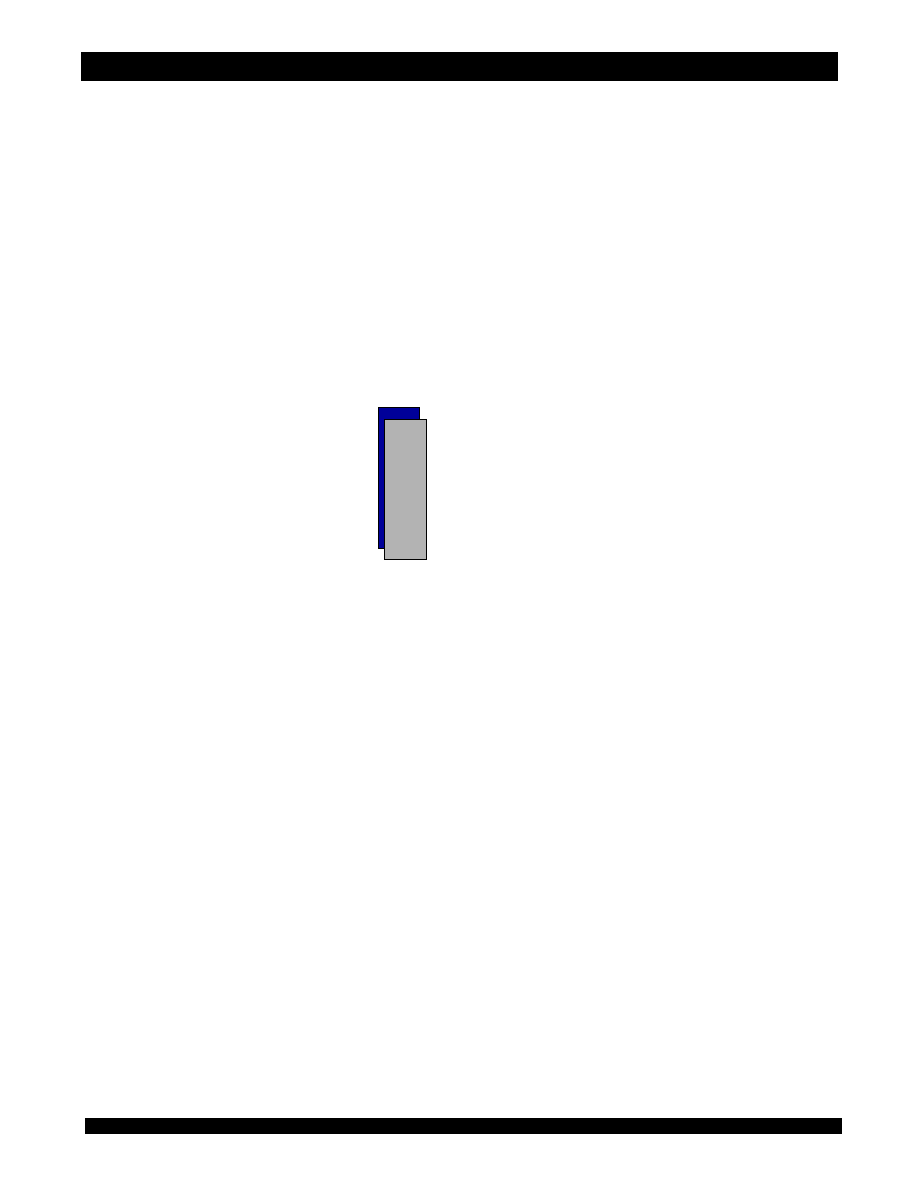

5346 drw02

Figure 1.0 ASIC / FPGA Compatible NSE

Network Interface

IDT 75N43102

Network

Search

Engine

Configuration Registers

CLK2X

˜

CCLK

˜ 2

CONFIGIN

MATCHIN

P

R

I

O

R

I

T

Y

E

N

C

O

D

E

R

S

I

Z

E

L

O

G

I

C

DATA

D

E

C

O

D

E

Address

I N S T R U C T I O N

MATCHOUT

REQDATA

REQSTB

R/W

64 3 5 d r w 0 1

RST

Command Bus

PHASEN

Global Mask Registers

Request

Bus

Index

Bus

CONFIGOUT

32K X 72

Block Diagram

System Configurations

The IDT NSEs are designed to fulfill the needs of various types of

networking systems. In solutions requiring data searching such as

routers, a system configuration as shown in Figure 1.0 may be realized.

In this compatible configuration, the NSE interfaces directly to an

ASIC/ FPGA for lookups and routes an Index directly back to the ASIC/

FPGA. Control of the associated handshake signals is provided by the

NSEs for this configuration.

ASIC

or

FPGA

2

Network Search Engine 32K x 72 Entries Datasheet Brief 75N43102

Registers

There are three basic types of registers supported:

s

Configuration Registers are used at initialization to define the

segmentation of the entries.

s

Global Mask Registers are provided to support Lookup

instructions by masking individual bits during a search.

s

Reply Width Registers are used with Lookup operations.

Functional Highlights

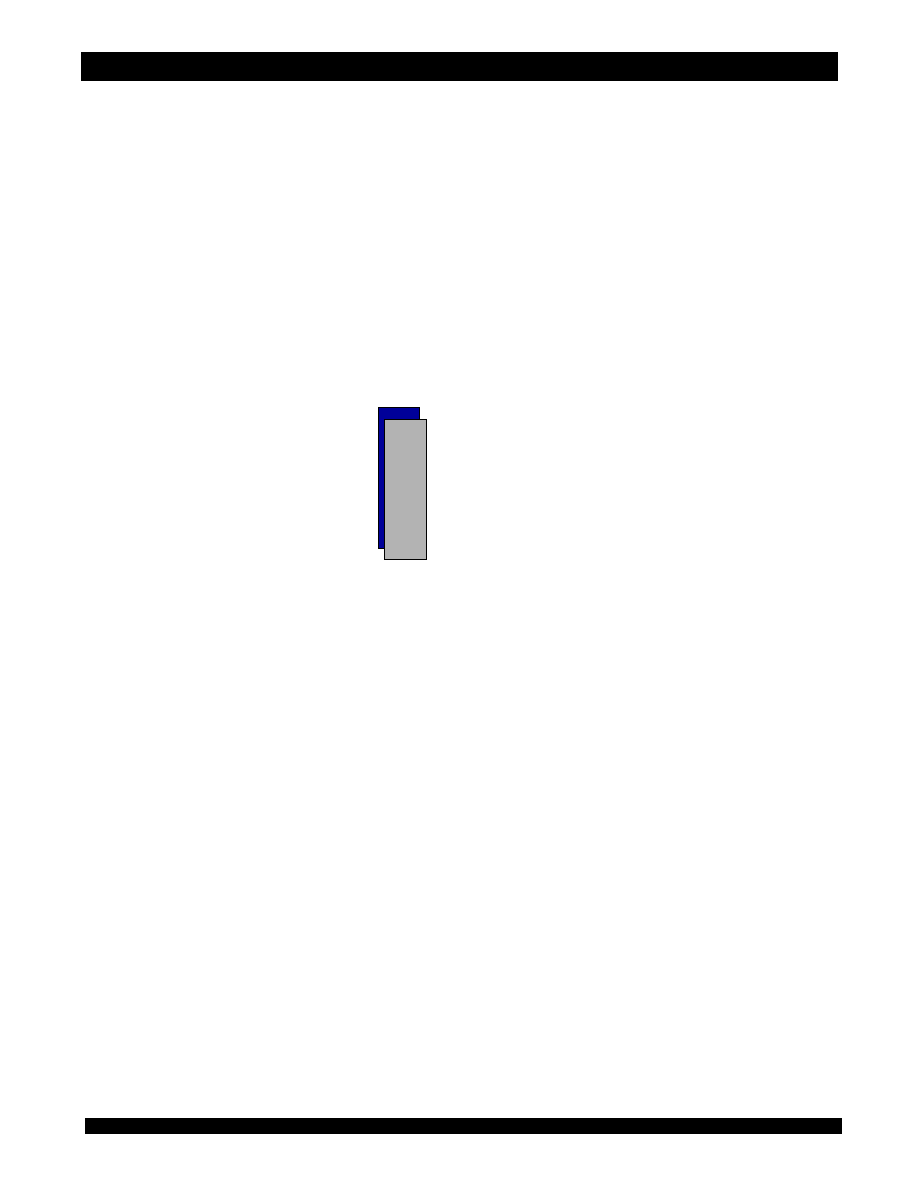

Figure 1.1

Bus Interface

The NSE utilizes a dual bus interface consisting of the NSE Request

Bus and the NSE Response Bus.

The NSE Request Bus is comprised of the Command Bus and the

Request Data Bus. The Command Bus handles the instruction to the NSE

while the Request Data Bus is the main data path to the NSE.

The 72 bit bi-directional Request Data Bus functions as a multiplexed

address and data bus, which performs the writing and reading of NSE

entries, as well as presenting lookup data to the device.

The NSE Response Bus is comprised of an independent unidirec-

tional Index Bus which drives the result of the lookup (or index) to an ASIC.

Data and Mask Array

The NSE has Data cell entries and associ-

ated Mask cell entries as shown in Fig. 1.1. This

combination of Data and Mask cell entries en-

ables the NSE to store 0, 1 or X, making it a full

ternary Network Search Engine. During a

lookup operation, both arrays are used along

with a Global Mask Register to find a match to a

requested data word.

A 6435 drw 03

D at a

Mask

Command Bus

The Command Bus loads the specific instructions into the NSE. These

include:

s

Read or Write

A Read or Write instruction operates on a specified data entry, mask

entry, or register.

s

Lookup

A lookup can be requested in 72-bit, 144-bit or 288-bit widths. A 36-

bit lookup can be accomplished by using two Global Mask Registers.

Features

s

s

s

s

s

Full Ternary 32K x 72 bit content addressable memory

s

s

s

s

s

Global Mask Registers

s

s

s

s

s

72/144/288 multiple width lookups

s

s

s

s

s

62.5M sustained lookups per second at 72 and 144 width lookups

s

s

s

s

s

Dual bus interface

s

s

s

s

s

Cascadable to 2 devices with no glue logic or latency penalty

s

s

s

s

s

Boundary Scan JTAG Interface (IEEE 1149.1compliant)

s

s

s

s

s

1.5V match power supply

s

s

s

s

s

2.5V core and I/O power supply

6.42

3

Network Search Engine 32K x 72 Entries Datasheet Brief 75N43102

Signal Descriptions

Pin Function

I/O

Description

NSE Buses:

Request Strobe

Input

This input sig nifies a valid input request and signals the start of an NSE operation cycle.

Command Bus

Input

This defines the instruction to be performed by the NSE and selects a global mask

register.

Request Data Bus

Input/Output

Three State

The Request Data Bus is a multiplexed address/data bus used to perform reads (and

writes) from (to) the NSE, and to present search data for lookups.

Index Bus

Output

Three State

This bus is used to drive the Lookup result information directly to the NSE's ASIC/FPGA.

The Index Bus contains the encoded location at which the compare was found.

Clock and Initialization:

Clock Input

Input

All inputs and outputs are referenced to the positive edge of this clock.

Clock Phase Enable

Input

This signal is used to generate an internal clock at Ω the frequency of the input clock.

Reset

Input

This pin will fo rce all outputs to a high impedence condition, as well as clearing the NSE

enable bit.

Depth Expansion:

Configuration

Input

Configures the De vice ID at power up.

Configuration

Output

Configures the De vice ID at power up.

Match

Input

Input

The Match Input signal is driven by the upstream Match Output signal. This indicates to the

down stream NSE that a hit in the higher priority NSE has occurred.

Match

Output

Output

The Match Output signal sig nifies that a match has occurred in the NSE. The signal is fed

into the Match Input line of the lower priority NSE.

6435 tbl 01

4

Network Search Engine 32K x 72 Entries Datasheet Brief 75N43102

Revision History

REV

DATE

PAGES

DESCRIPTION

0

7/11/03

p.1-3

Initial release

A

08/14/03

p.4

Updated pinout.

B

04/12/04

All

Updated, removed pinout.