| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 79RC32333 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

1 of 28

December 18, 2002

2002 Integrated Device Technology, Inc.

DSC 6209

IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc.

IDT

TM

Interprise

TM

Integrated

Communications Processor

Features

RC32300 32-bit Microprocessor

≠ Up to 150 MHz operation

≠ Enhanced MIPS-II Instruction Set Architecture (ISA)

≠ Cache prefetch instruction

≠ Conditional move instruction

≠ DSP instructions

≠ Supports big or little endian operation

≠ MMU with 32 page TLB

≠ 8KB Instruction Cache, 2-way set associative

≠ 2KB Data Cache, 2-way set associative

≠ Cache locking per line

≠ Programmable on a page basis to implement a write-through

no write allocate, write-through write allocate, or write-back

algorithms for cache management

≠ Compatible with a wide variety of operating systems

Local Bus Interface

≠ Up to 75 MHz operation

≠ 23-bit address bus

≠ 32-bit data bus

≠ Direct control of local memory and peripherals

≠ Programmable system watch-dog timers

≠ Big or little endian support

Interrupt Controller simplifies exception management

Four general purpose 32-bit timer/counters

Programmable I/O (PIO)

≠ Input/Output/Interrupt source

≠ Individually programmable

SDRAM Controller (32-bit memory only)

≠ 4 banks, non-interleaved

≠ Up to 512MB total SDRAM memory supported

≠ Implements full, direct control of discrete, SODIMM, or DIMM

memories

≠ Supports 16Mb through 512Mb SDRAM device depths

≠ Automatic refresh generation

Serial Peripheral Interface (SPI) master mode interface

UART Interface

≠ 16550 compatible UART

≠ Baud rate support up to 1.5 Mb/s

Memory & Peripheral Controller

≠ 6 banks, up to 8MB per bank

≠ Supports 8-,16-, and 32-bit interfaces

≠ Supports Flash ROM, SRAM, dual-port memory, and

peripheral devices

≠ Supports external wait-state generation

≠ 8-bit boot PROM support

≠ Flexible I/O timing protocols

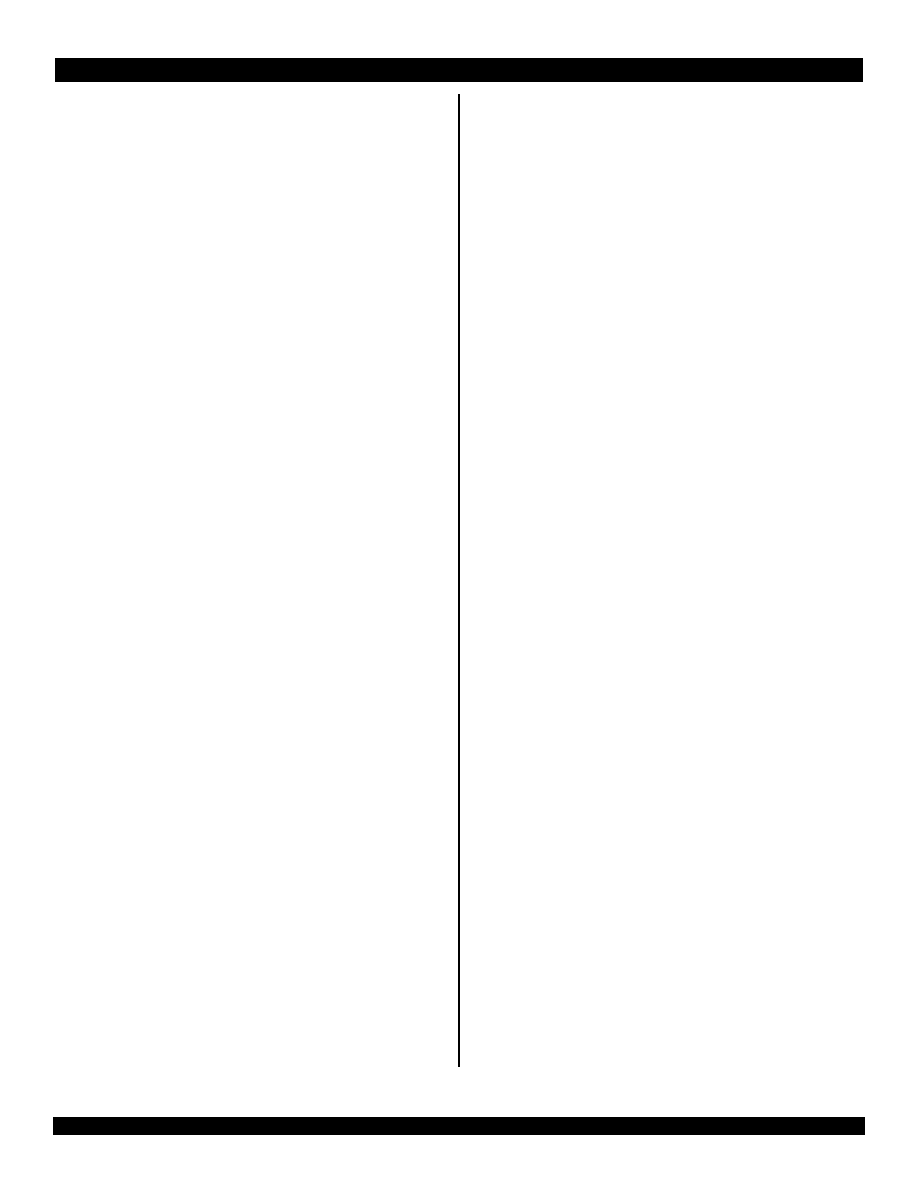

Block Diagram

Figure 1 RC32333 Block Diagram

Local

Memory/IO

Control

Interrupt Control

DMA Control

UART

32-bit Timers

SPI Control

Programmable I/O

PCI Bridge

IDT

Peripheral

Bus

RISCore 32300

Enhanced MIPS-II ISA

Integer CPU

RC5000

Compatible

CP0

32-page

TLB

EJTAG

In-Circuit Emulator Interface

2KB

2-set, Lockable

Data Cache

8KB

2-set

Lockable

Instr. Cache

IPBus

Bridge

SDRAM

Control

79RC32333

2 of 28

December 18, 2002

IDT 79RC32333

4 DMA Channels

≠ 4 general purpose DMA, each with endianess swappers and

byte lane data alignment

≠ Supports scatter/gather, chaining via linked lists of records

≠ Supports memory-to-memory, memory-to-I/O, memory-to-

PCI, PCI-to-PCI, and I/O-to-I/O transfers

≠ Supports unaligned transfers

≠ Supports burst transfers

≠ Programmable DMA bus transactions burst size

(up to 16 bytes)

PCI Bus Interface

≠ 32-bit PCI, up to 50 MHz

≠ Revision 2.2 compatible

≠ Target or master

≠ Host or satellite

≠ Three slot PCI arbiter

≠ Serial EEPROM support, for loading configuration registers

Off-the-shelf development tools

JTAG Interface (IEEE Std. 1149.1 compatible)

208 QFP Package

3.3V operation with 5V compatible I/O

EJTAG in-circuit emulator interface

Device Overview

The IDT RC32333 device is an integrated processor based on the

RC32300 CPU core. This product incorporates a high-performance, low-

cost 32-bit CPU core with functionality common to a large number of

embedded applications. The RC32333 integrates these functions to

enable the use of low-cost PC commodity market memory and I/O

devices, allowing the aggressive price/performance characteristics of

the CPU to be realized quickly into low-cost systems.

CPU Execution Core

The RC32333 integrates the RISCore 32300, the same CPU core

found in the award-winning RC32364 microprocessor.

The RISCore 32300 implements the Enhanced MIPS-II ISA. Thus, it

is upwardly compatible with applications written for a wide variety of

MIPS architecture processors, and it is kernel compatible with the

modern operating systems that support IDT's 64-bit RISController

product family.

The RISCore 32300 was explicitly defined and designed for inte-

grated processor products such as the RC32333. Key attributes of the

execution core found within this product include:

High-speed, 5-stage scalar pipeline executes to 150MHz. This

high performance enables the RC32333 to perform a variety of

performance intensive tasks, such as routing, DSP algorithms,

etc.

32-bit architecture with enhancements of key capabilities. Thus,

the RC32333 can execute existing 32-bit programs, while

enabling designers to take advantage of recent advances in

CPU architecture.

Count leading-zeroes/ones. These instructions are common to a

wide variety of tasks, including modem emulation, voice over IP

compression and decompression, etc.

Cache PREFetch instruction support, including a specialized

form intended to help memory coherency. System programmers

can allocate and stage the use of memory bandwidth to achieve

maximum performance.

8KB of 2-way set associative instruction cache

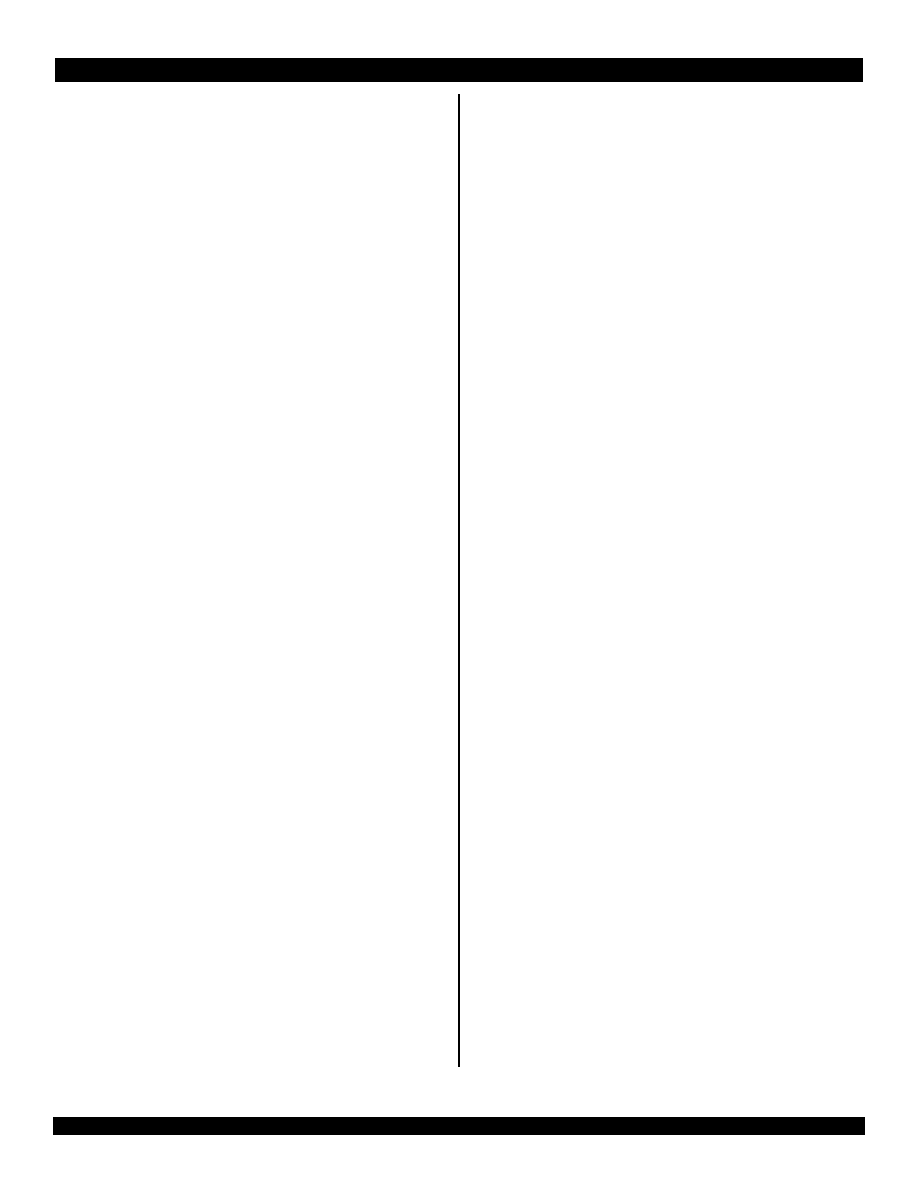

Figure 2 RC32333 Based System Diagram

SDRAM

FLASH

Local I/O

Serial

EEPROM

Serial

Channel

Programmable I/O

RC32333

Integrated

Core

Controller

32-bit, 33MHz PCI

Local

Memory

I/O Bus

3 of 28

December 18, 2002

IDT 79RC32333

2KB of 2-way set associative data cache, capable of write-back

and write-through operation.

Cache locking per line to speed real-time systems and critical

system functions

On-chip TLB to enable multi-tasking in modern operating

systems

EJTAG interface to enable sophisticated low-cost in-circuit

emulation.

Synchronous-DRAM Interface

The RC32333 integrates a SDRAM controller which provides direct

control of system SyncDRAM running at speeds to 75MHz.

Key capabilities of the SDRAM controller include:

Direct control of 4 banks of SDRAM (up to 2 64-bit wide DIMMs)

On-chip page comparators optimize access latency.

Speeds to 75MHz

Programmable address map.

Supports 16, 64, 128, 256, or 512Mb SDRAM devices

Automatic refresh generation driven by on-chip timer

Support for discrete devices, SODIMM, or DIMM modules.

Thus, systems can take advantage of the full range of commodity

memory that is available, enabling system optimization for cost, real-

estate, or other attributes.

Local Memory and I/O Controller

The local memory and I/O controller implements direct control of

external memory devices, including the boot ROM as well as other

memory areas, and also implements direct control of external periph-

erals.

The local memory controller is highly flexible, allowing a wide range

of devices to be directly controlled by the RC32333 processor. For

example, a system can be built using an 8-bit boot ROM, 16-bit FLASH

cards (possibly on PCMCIA), a 32-bit SRAM or dual-port memory, and a

variety of low-cost peripherals.

Key capabilities include:

Direct control of EPROM, FLASH, RAM, and dual-port memories

6 chip-select outputs, supporting up to 8MB per memory space

Supports mixture of 8-, 16-, and 32-bit wide memory regions

Flexible timing protocols allow direct control of a wide variety of

devices

Programmable address map for 2 chip selects

Automatic wait state generation.

PCI Bus Bridge

In order to leverage the wide availability of low-cost peripherals for

the PC market as well as to simplify the design of add-in functions, the

RC32333 integrates a full 32-bit PCI bus bridge. Key attributes of this

bridge include:

50 MHz operation

PCI revision 2.2 compliant

Programmable address mappings between CPU/Local memory

and PCI memory and I/O

On-chip PCI arbiter

Extensive buffering allows PCI to operate concurrently with local

memory transfers

Selectable byte-ordering swapper

5V tolerant I/O.

On-Chip DMA Controller

To minimize CPU exception handling and maximize the efficiency of

system bandwidth, the RC32333 integrates a very sophisticated 4-

channel DMA controller on chip.

The RC32333 DMA controller is capable of:

Chaining and scatter/gather support through the use of a

flexible, linked list of DMA transaction descriptors

Capable of memory<->memory, memory<->I/O, and

PCI<->memory DMA

Unaligned transfer support

Byte, halfword, word, quadword DMA support.

On-Chip Peripherals

The RC32333 also integrates peripherals that are common to a wide

variety of embedded systems.

Single 16550 compatible UART.

SPI master mode interface for direct interface to EEPROM,

A/D, etc.

Interrupt Controller to speed interrupt decode and management

Four 32-bit on-chip Timer/Counters

Programmable I/O module

Debug Support

To facilitate rapid time to market, the RC32333 provides extensive

support for system debug.

First and foremost, this product integrates an EJTAG in-circuit emula-

tion module, allowing a low-cost emulator to interoperate with programs

executing on the controller. By using an augmented JTAG interface, the

RC32333 is able to reuse the same low-cost emulators developed

around the RC32364 CPU.

4 of 28

December 18, 2002

IDT 79RC32333

Secondly, the RC32333 implements additional reporting signals

intended to simplify the task of system debugging when using a logic

analyzer. This product allows the logic analyzer to differentiate transac-

tions initiated by DMA from those initiated by the CPU and further allows

CPU transactions to be sorted into instruction fetches vs. data fetches.

Finally, the RC32333 implements a full boundary scan capability,

allowing board manufacturing diagnostics and debug.

Packaging

The RC32333 is packaged using a 208 Quad Flat Pack (QFP)

package.

Thermal Considerations

The RC32333 consumes less than 2.0 W peak power. The device is

guaranteed in an ambient temperature range of 0

∞ to +70∞ C for

commercial temperature devices; -40

∞ to +85∞ C for industrial tempera-

ture devices.

Revision History

September 18, 2002: Initial publication.

December 18, 2002: In the Reset section of Table 6, AC Timing

Characteristics, setup and hold time categories for cpu_coldreset_n

have been deleted.

5 of 28

December 18, 2002

IDT 79RC32333

Pin Description Table

The following table lists the pins provided on the RC32333. Note that those pin names followed by "_n" are active-low signals. All external pull-ups

and pull-downs require

10 k

resistor.

Name

Type

Reset

State

Status

Drive

Strength

Capability

Description

Local System Interface

mem_data[31:0]

I/O

Z

High

Local system data bus

Primary data bus for memory. I/O and SDRAM.

mem_addr[22:2]

I/O

[22:10] Z

[9:2] L

[22:17] Low

[16:2] High

Memory Address Bus

These signals provide the Memory or DRAM address, during a Memory or DRAM bus transaction. During

each word data, the address increments either in linear or sub-block ordering, depending on the transac-

tion type. The table below indicates how the memory write enable signals are used to address discreet

memory port width types.

mem_addr[22] Alternate function: reset_boot_mode[1].

mem_addr[21] Alternate function: reset_boot_mode[0].

mem_addr[20] Alternate function: reset_pci_host_mode.

mem_addr[19] Alternate function: modebit [9].

mem_addr[18] Alternate function: modebit [8].

mem_addr[17] Alternate function: modebit [7].

mem_addr[16] Alternate function: sdram_addr[16].

mem_addr[15] Alternate function: sdram_addr[15].

mem_addr[14] Alternate function: sdram_addr[14].

mem_addr[13] Alternate function: sdram_addr[13].

mem_addr[11] Alternate function: sdram_addr[11].

mem_addr[10] Alternate function: sdram_addr[10].

mem_addr[9] Alternate function: sdram_addr[9].

mem_addr[8] Alternate function: sdram_addr[8].

mem_addr[7] Alternate function: sdram_addr[7].

mem_addr[6] Alternate function: sdram_addr[6].

mem_addr[5] Alternate function: sdram_addr[5].

mem_addr[4] Alternate function: sdram_addr[4].

mem_addr[3] Alternate function: sdram_addr[3].

mem_addr[2] Alternate function: sdram_addr[2].

mem_cs_n[5:0]

Output

H

Low

Memory Chip Select Negated Recommend an external pull-up.

Signals that a Memory Bank is actively selected.

mem_oe_n

Output

H

High

Memory Output Enable Negated Recommend an external pull-up.

Signals that a Memory Bank can output its data lines onto the cpu_ad bus.

mem_we_n[3:0]

Output

H

High

Memory Write Enable Negated Bus

Signals which bytes are to be written during a memory transaction. Bits act as Byte Enable and

mem_addr[1:0] signals for 8-bit or 16-bit wide addressing.

Table 1 Pin Descriptions (Part 1 of 6)

Port Width

Pin Signals

mem_we_n[3]

mem_we_n[2] mem_we_n[1]

mem_we_n[0]

DMA (32-bit) mem_we_n[3]

mem_we_n[2] mem_we_n[1]

mem_we_n[0]

32-bit

mem_we_n[3]

mem_we_n[2] mem_we_n[1]

mem_we_n[0]

16-bit

Byte High Write Enable mem_addr[1]

Not Used (Driven

Low)

Byte Low Write

Enable

8-bit

Not Used (Driven High) mem_addr[1]

mem_addr[0]

Byte Write Enable