FEATURES:

∑ Fast

Detect

Correct

-- IDT49C460E

10ns (max.)

14ns (max.)

-- IDT49C460D

12ns (max.)

18ns (max.)

-- IDT49C460C

16ns (max.)

24ns (max.)

-- IDT49C460B

25ns (max.)

30ns (max.)

-- IDT49C460A

30ns (max.)

36ns (max.)

-- IDT49C460

40ns (max.)

49ns (max.)

∑ Low-power CMOS

-- Commercial: 95mA (max.)

-- Military: 125mA (max.)

∑ Improves system memory reliability

-- Corrects all single bit errors, detects all double and some

triple-bit errors

∑ Cascadable

-- Data words up to 64-bits

∑ Built-in diagnostics

-- Capable of verifying proper EDC operation via software

control

∑ Simplified byte operations

-- Fast byte writes possible with separate byte enables

∑ Functional replacement for 32- and 64-bit configurations of

the AM29C60 and AM29C660

∑ Available in PGA, PLCC and Fine Pitch Flatpack

∑ Military product compliant to MIL-STD-883, Class B

∑ Standard Military Drawing #5962≠88533

Integrated Device Technology, Inc.

MILITARY AND COMMERCIAL TEMPERATURE RANGES

AUGUST 1995

©

1995 Integrated Device Technology, Inc.

11.6

DSC-9017/8

32-BIT CMOS

ERROR DETECTION

AND CORRECTION UNIT

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

DESCRIPTION:

The IDT49C460s are high-speed, low-power, 32-bit Error

Detection and Correction Units which generate check bits on

a 32-bit data field according to a modified Hamming Code and

correct the data word when check bits are supplied. The

IDT49C460s are performance-enhanced functional replace-

ments for 32-bit versions of the 2960. When performing a read

operation from memory, the IDT49C460s will correct 100% of

all single bit errors and will detect all double bit errors and

some triple bit errors.

The IDT49C460s are easily cascadable to 64-bits. Thirty-

two-bit systems use 7 check bits and 64-bit systems use 8

check bits. For both configurations, the error syndrome is

made available.

The IDT49C460s incorporate two built-in diagnostic modes.

Both simplify testing by allowing for diagnostic data to be

entered into the device and to execute system diagnostics

functions.

They are fabricated using a CMOS technology designed for

high-performance and high-reliability. The devices are pack-

aged in a 68-pin ceramic PGA, PLCC and Ceramic Quad

Flatpack.

Military grade product is manufactured in compliance with

the latest revision of MIL-STD-883, Class B, making it ideally

suited to military temperature applications demanding the

highest level of performance and reliability.

1

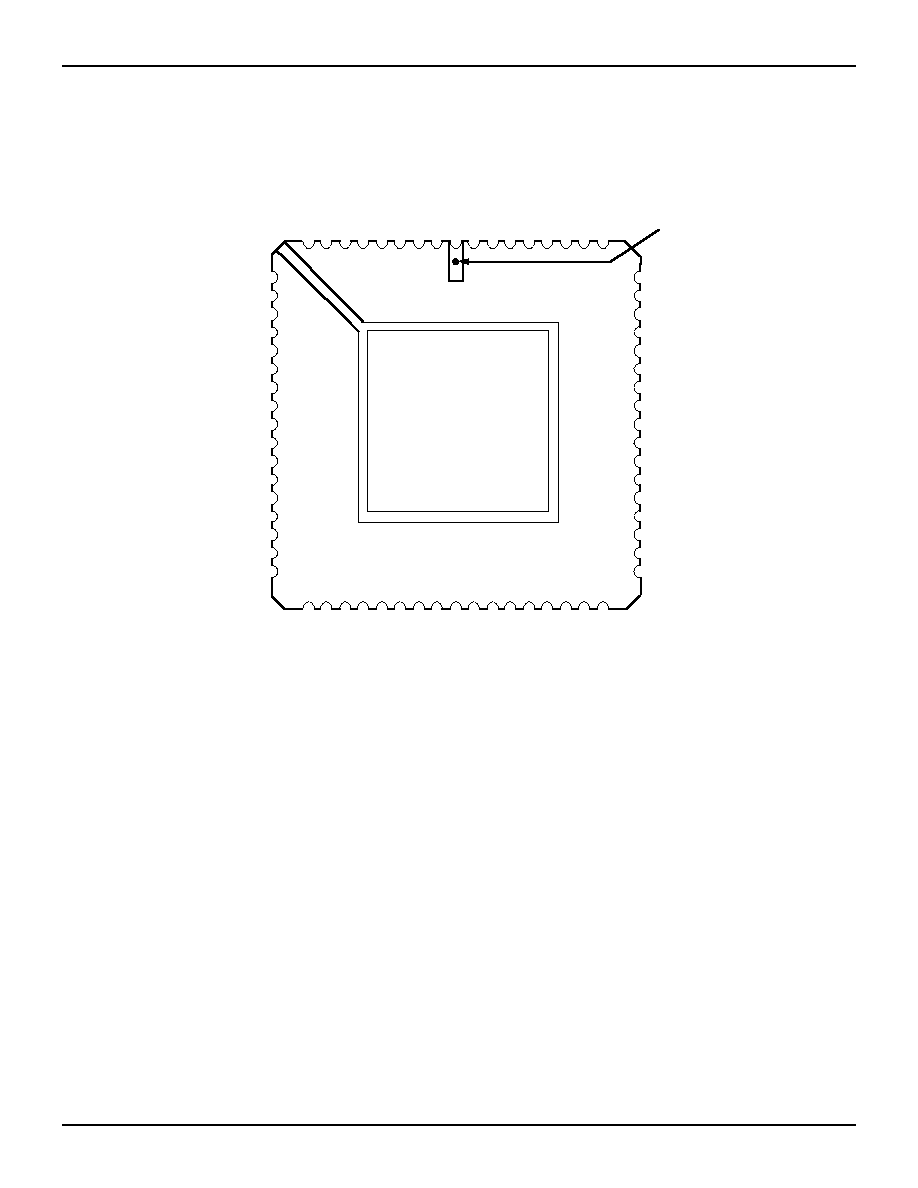

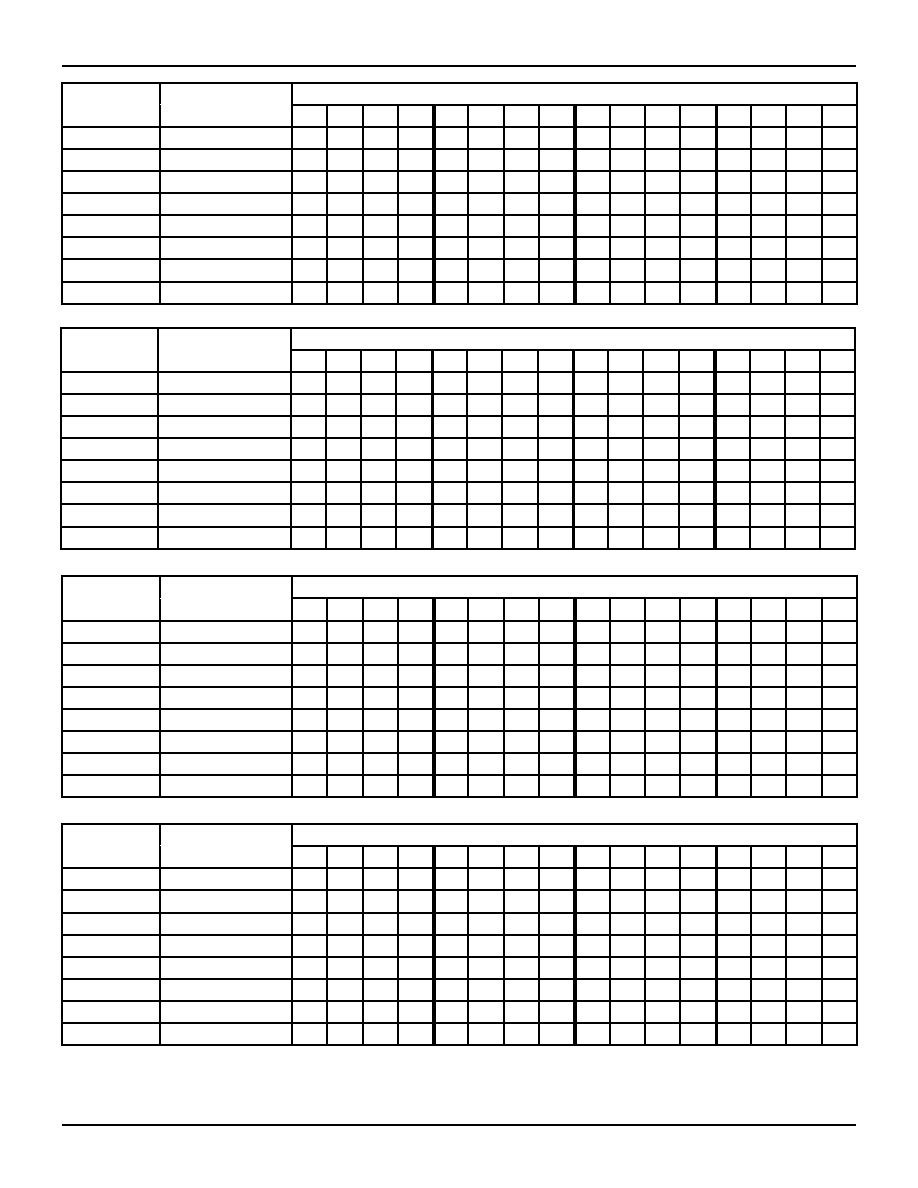

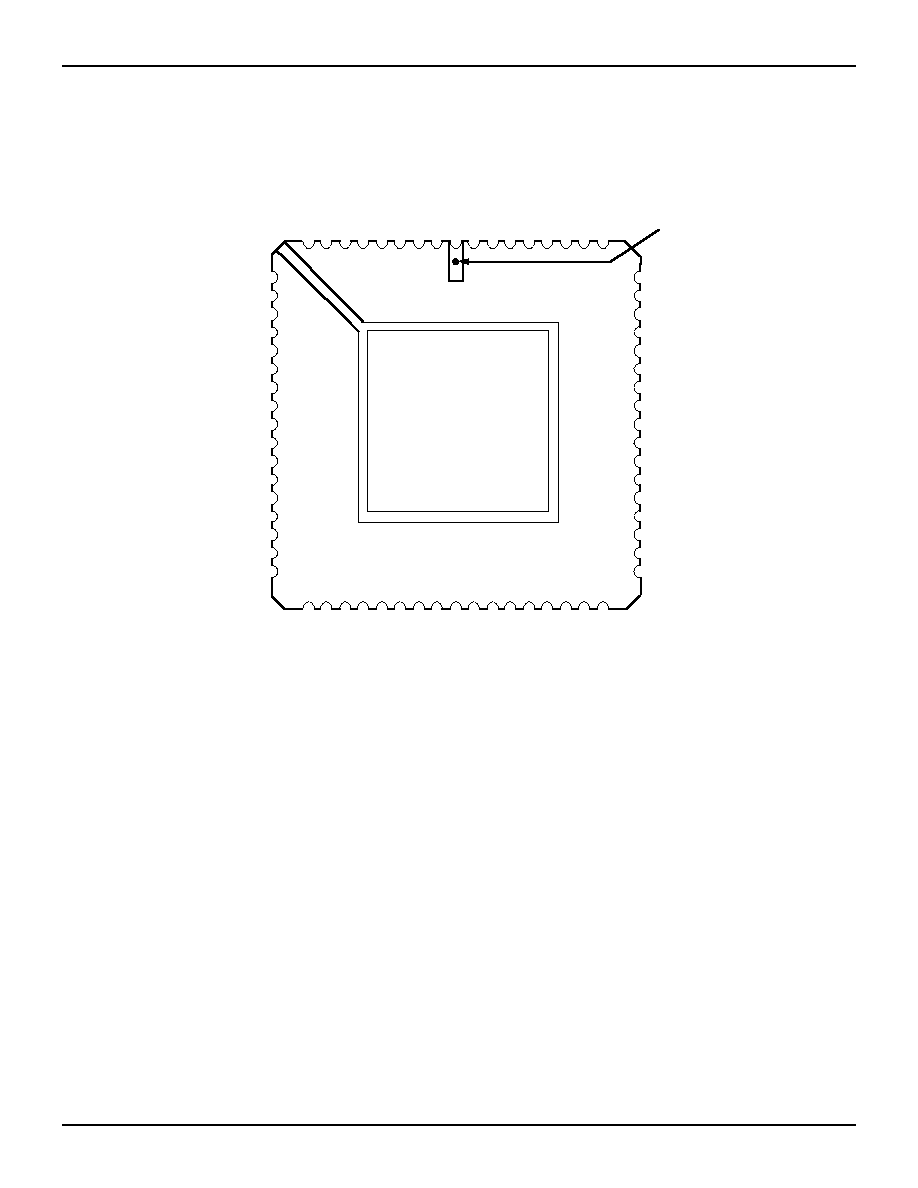

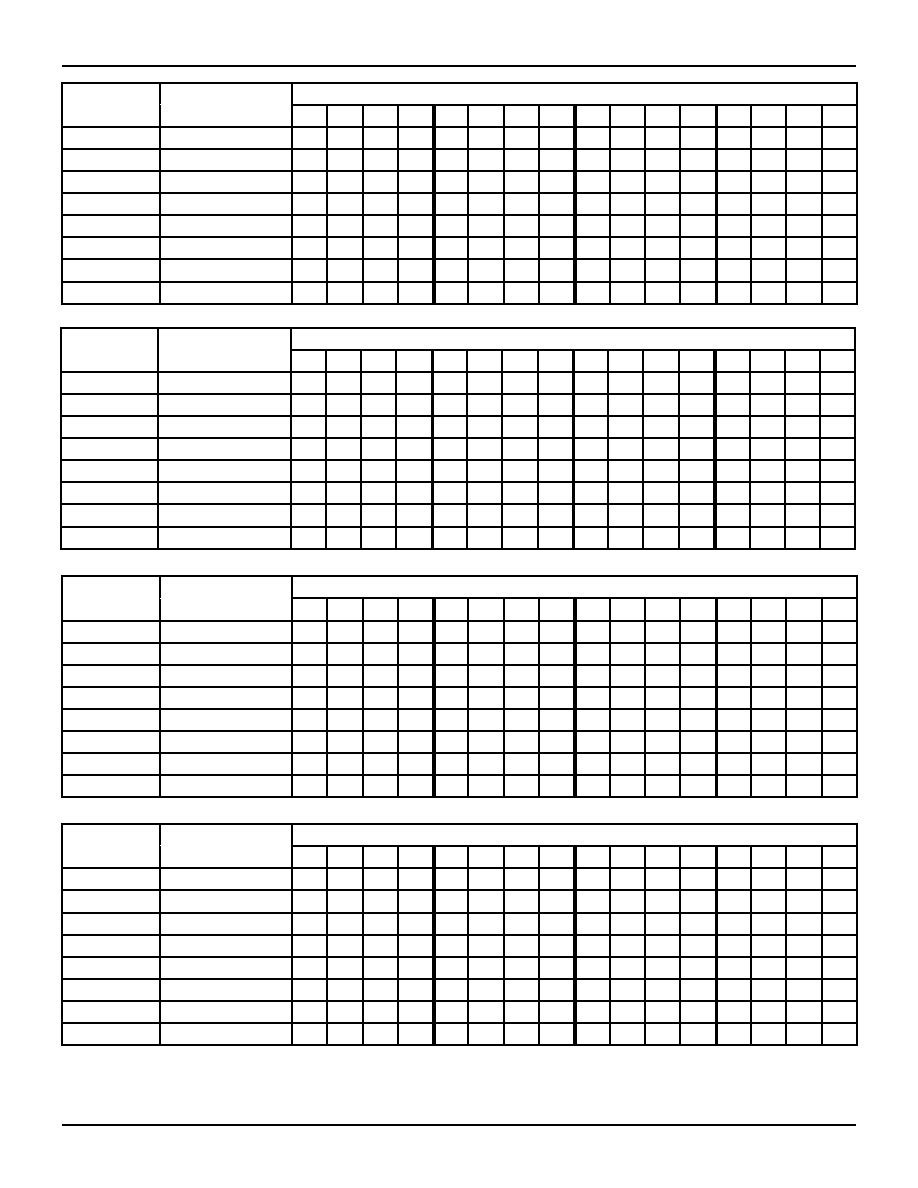

FUNCTIONAL BLOCK DIAGRAM

DATA

LATCH

ERROR

CORRECT

ERROR

DECODE

MUX

DATA

LATCH

CHECK BIT

GENERATE

MUX

MUX

CHECK BIT

IN LATCH

DIAGNOSTIC

LATCH

SYNDROME

GENERATE

ERROR

DETECT

CONTROL

LOGIC

MUX

8

8

8

5

8

8

8

32

32

4

32

13

CB

0≠7

DATA

0≠31

OE

BYTE

0≠3

LE

IN

LE

DIAG

LE

OUT

/

GENERATE

CORRECT

CODE ID

1,0

DIAG MODE

1,0

SC

0≠7

OE

SC

ERROR

MULT ERROR

2584 drw 01

IDT49C460

IDT49C460A

IDT49C460B

IDT49C460C

IDT49C460D

IDT49C460E

11.6

2

IDT49C460/A/B/C/D/E

32-BIT CMOS ERROR DETECTION AND CORRECTION UNIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

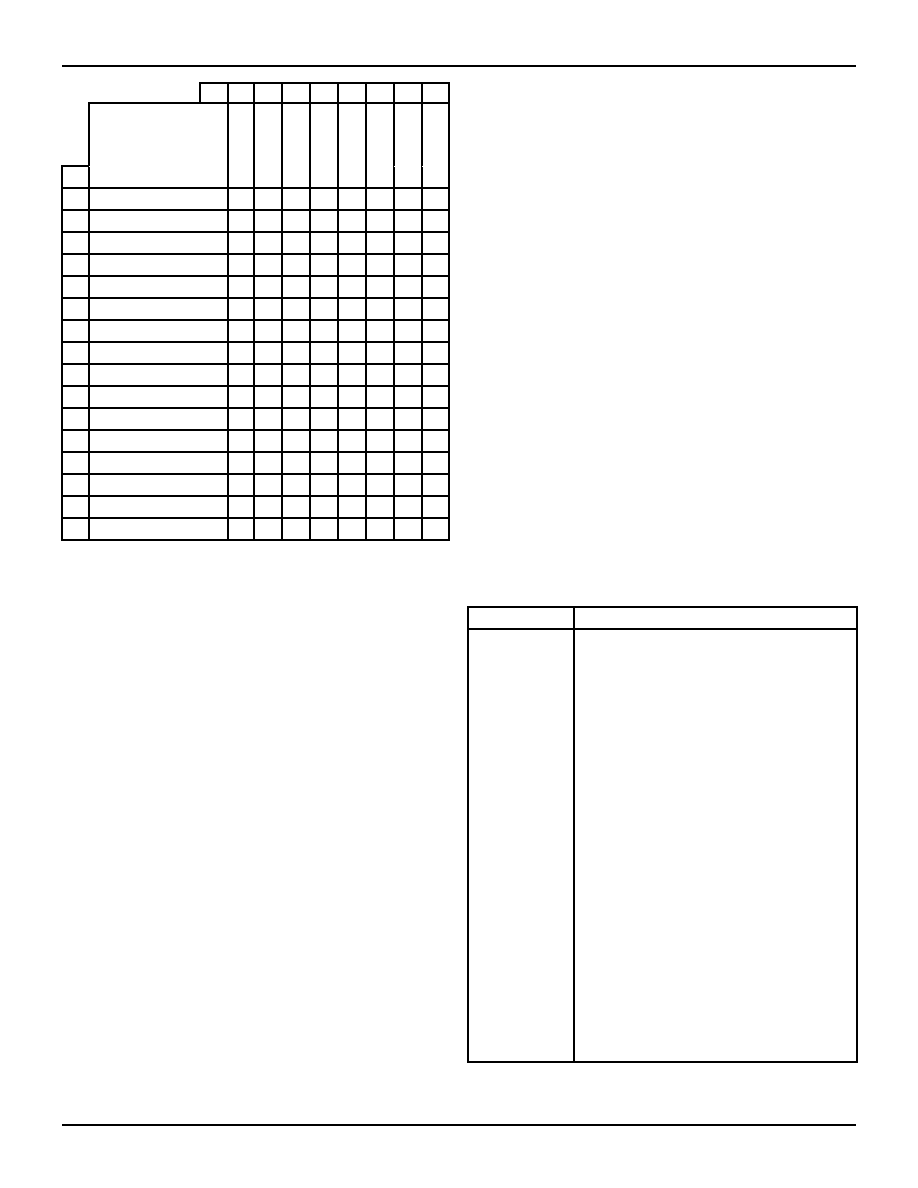

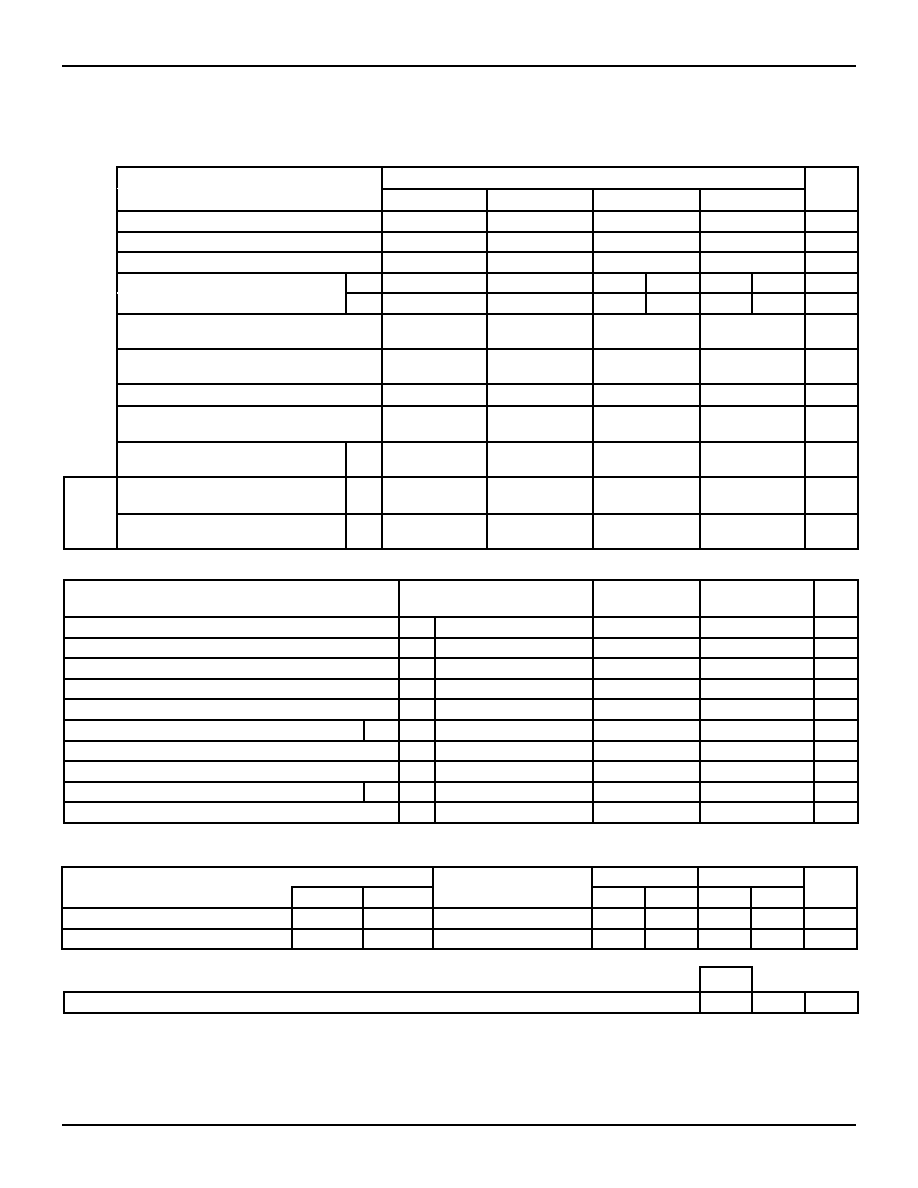

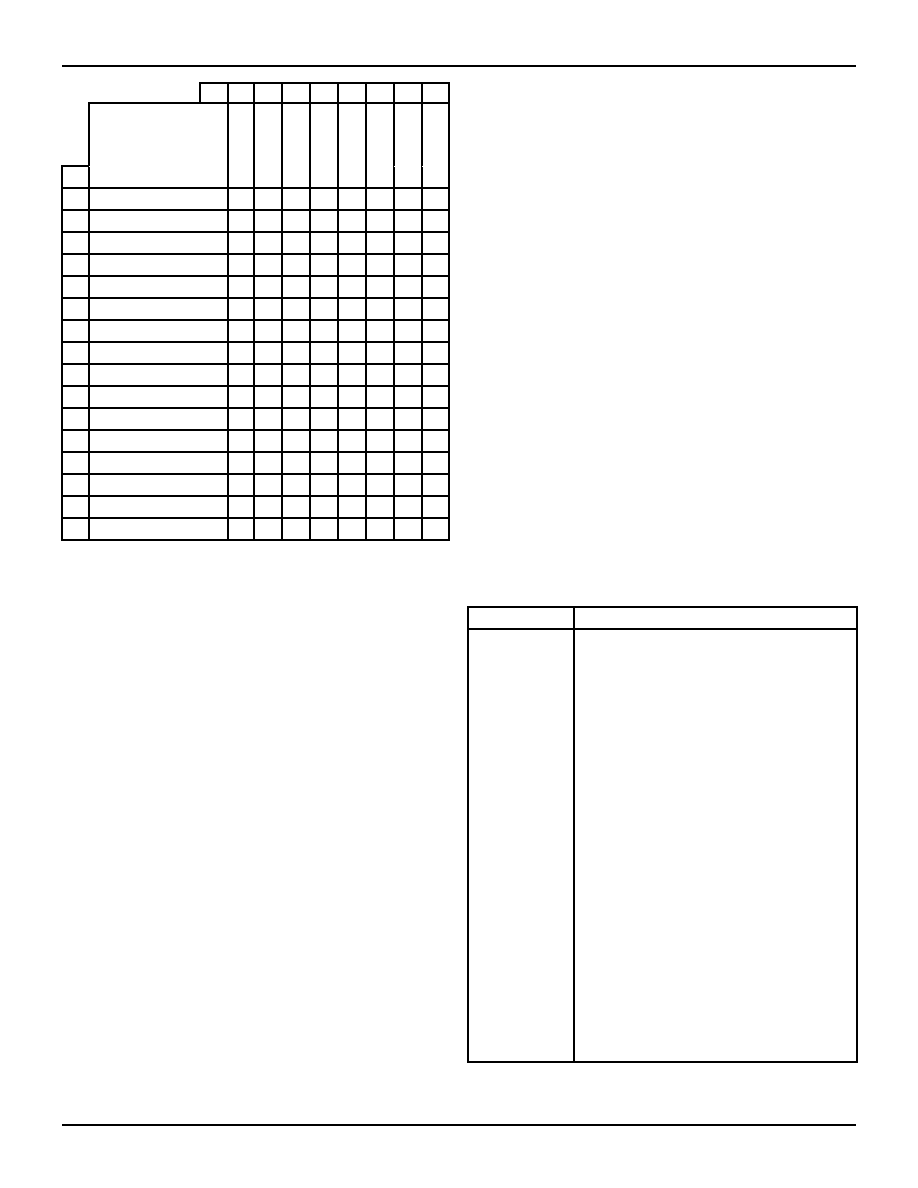

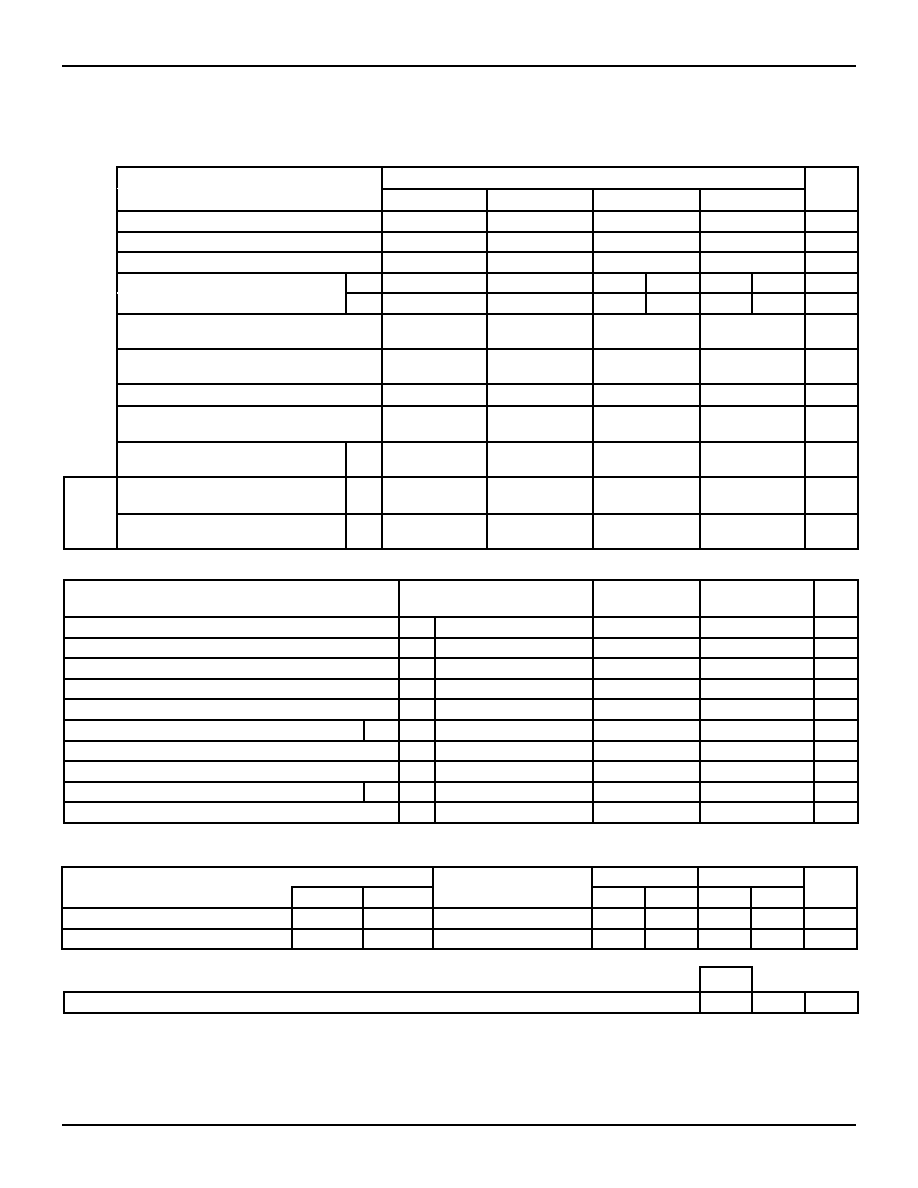

PIN CONFIGURATIONS

PLCC

TOPVIEW

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43

9 8 7 6 5 4 3 2 1 68 67 66 65 64 63 62 61

D

24

D

23

D

22

D

21

D

20

D

19

D

18

D

17

V

CC

D

16

OE

2

LE

OUT

/

GENERATE

CORRECT

LE

DIAG

ERROR

MULT ERROR

GND

D

2

D

3

D

4

D

5

D

6

D

7

D

8

D

9

D

10

D

11

D

12

D

13

D

14

D

15

OE1

V

CC

GND

J68≠1

DESIGNATES

PIN 1 FOR

PLCC ONLY

CB

6

CB

5

CB

4

CB

3

CB

2

CB

1

CB

0

SC

1

SC

2

SC

3

SC

4

SC

5

SC

6

SC

7

OE

SC

CB

7

SC

0

D

1

D

0

OE

0

LE

IN

DIAG MODE

1

DIAG MODE

0

CODE ID

1

CODE ID

0

OE

3

D

31

D

30

D

28

D

27

D

26

D

25

GND

D

29

2584 drw 02

11.6

3

IDT49C460/A/B/C/D/E

32-BIT CMOS ERROR DETECTION AND CORRECTION UNIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

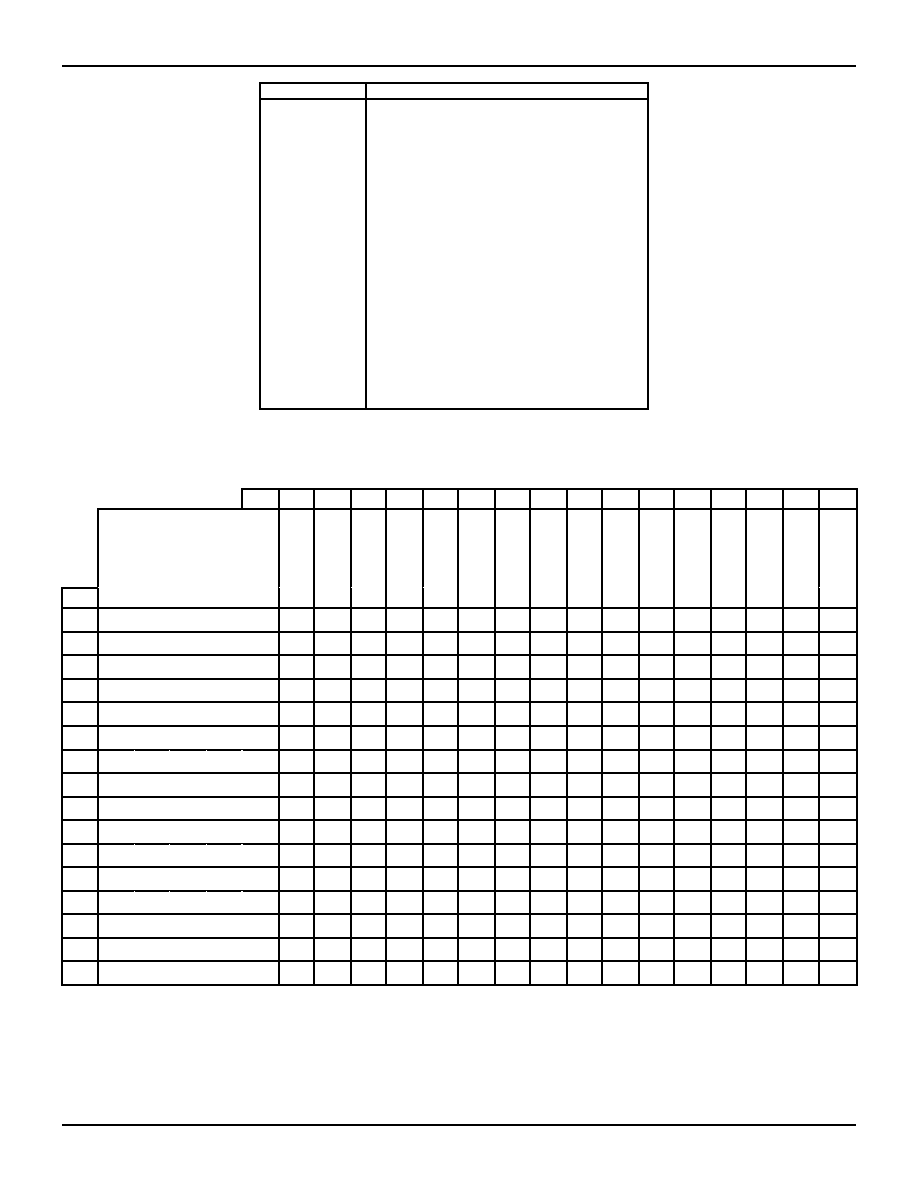

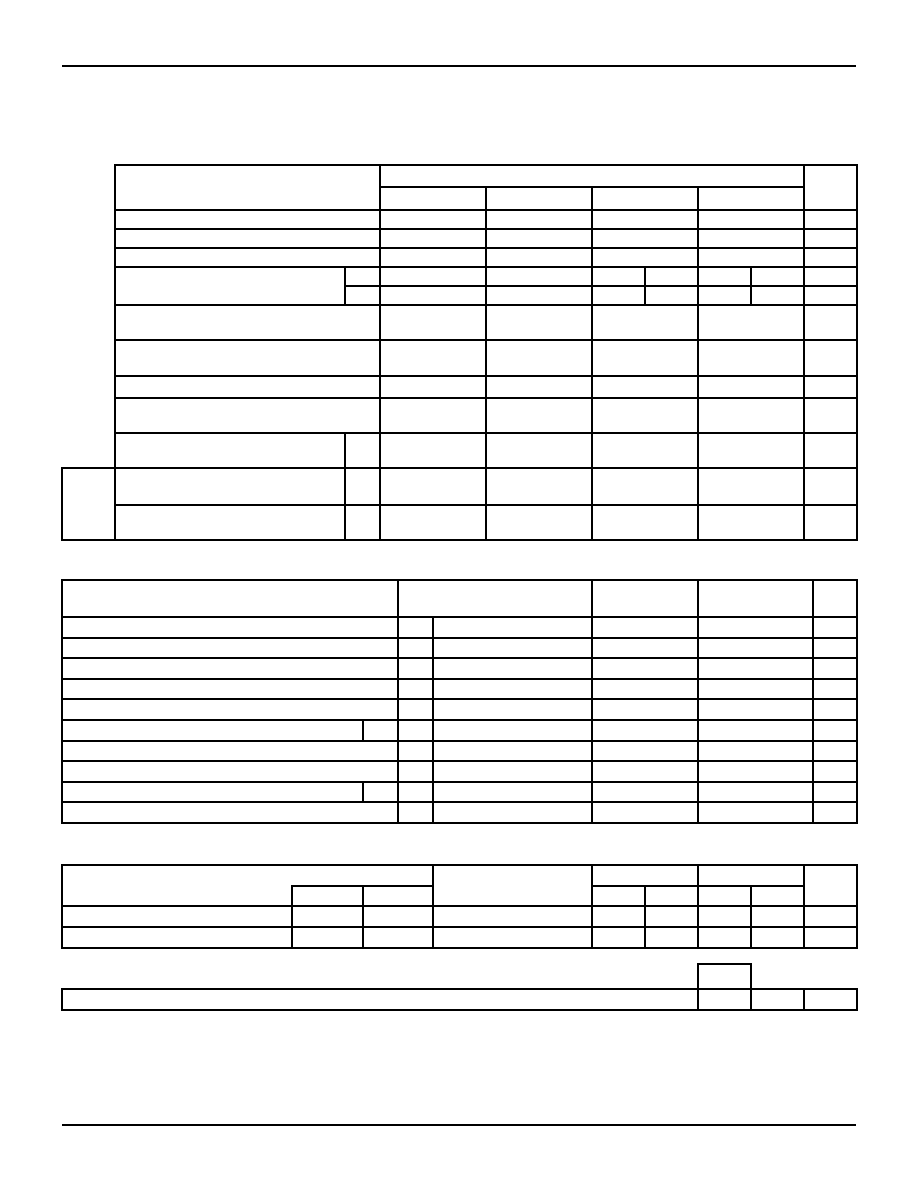

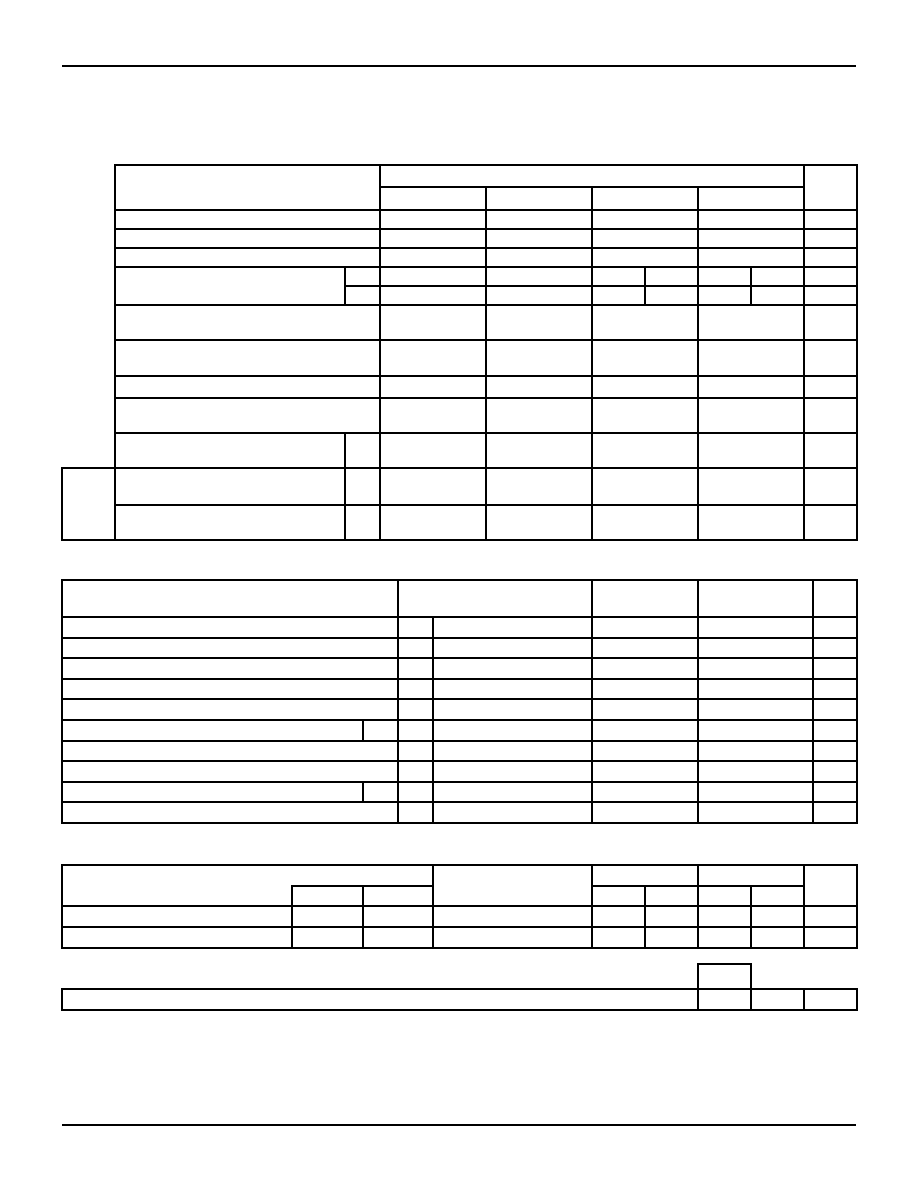

FINE PITCH FLATPACK

TOPVIEW

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43

9 8 7 6 5 4 3 2 1 68 67 66 65 64 63 62 61

F68 - 2

PIN 1 IDENTIFICATION

D

24

D

23

D

22

D

21

D

20

D

19

D

18

D

17

V

CC

D

16

OE

2

LE

OUT

/

GENERATE

CORRECT

LE

DIAG

ERROR

MULT ERROR

GND

D

2

D

3

D

4

D

5

D

6

D

7

D

8

D

9

D

10

D

11

D

12

D

13

D

14

D

15

OE

1

V

CC

GND

CB

6

CB

5

CB

4

CB

3

CB

2

CB

1

CB

0

SC

1

SC

2

SC

3

SC

4

SC

5

SC

6

SC

7

OE

SC

CB

7

SC

0

D

1

D

0

DIAG MODE

1

OE

0

LE

IN

DIAG MODE

0

CODE ID

1

CODE ID

0

OE

3

D

31

D

30

D

28

D

27

D

26

D

25

GND

D

29

2584 drw 03

11.6

4

IDT49C460/A/B/C/D/E

32-BIT CMOS ERROR DETECTION AND CORRECTION UNIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

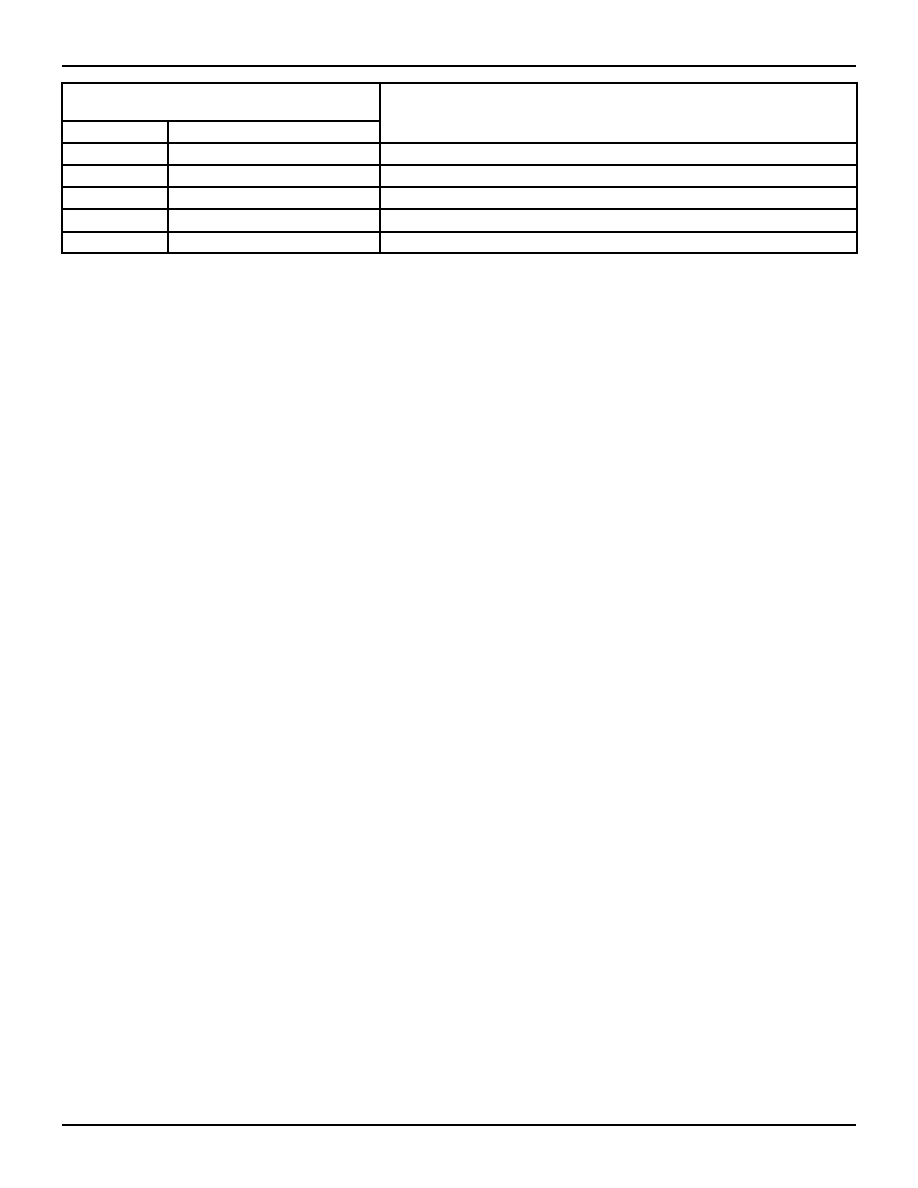

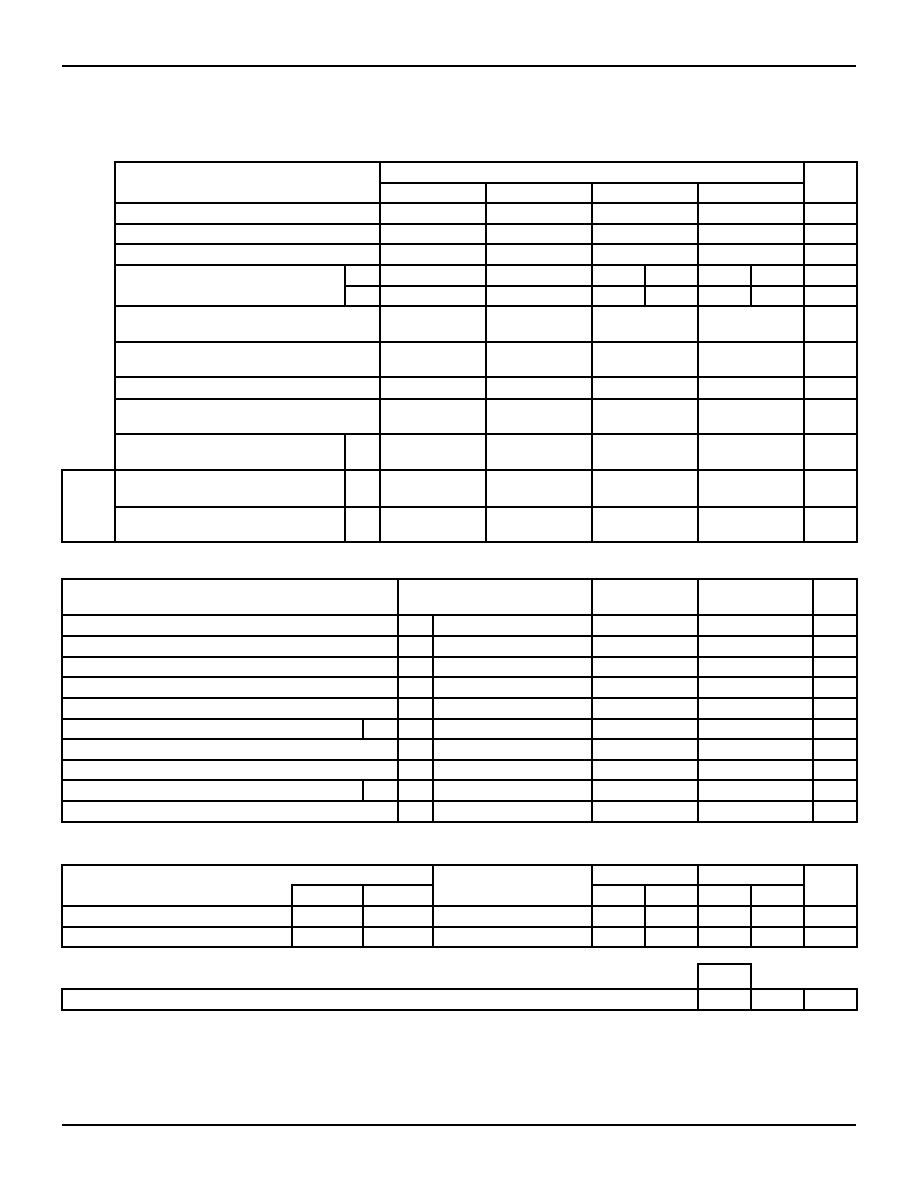

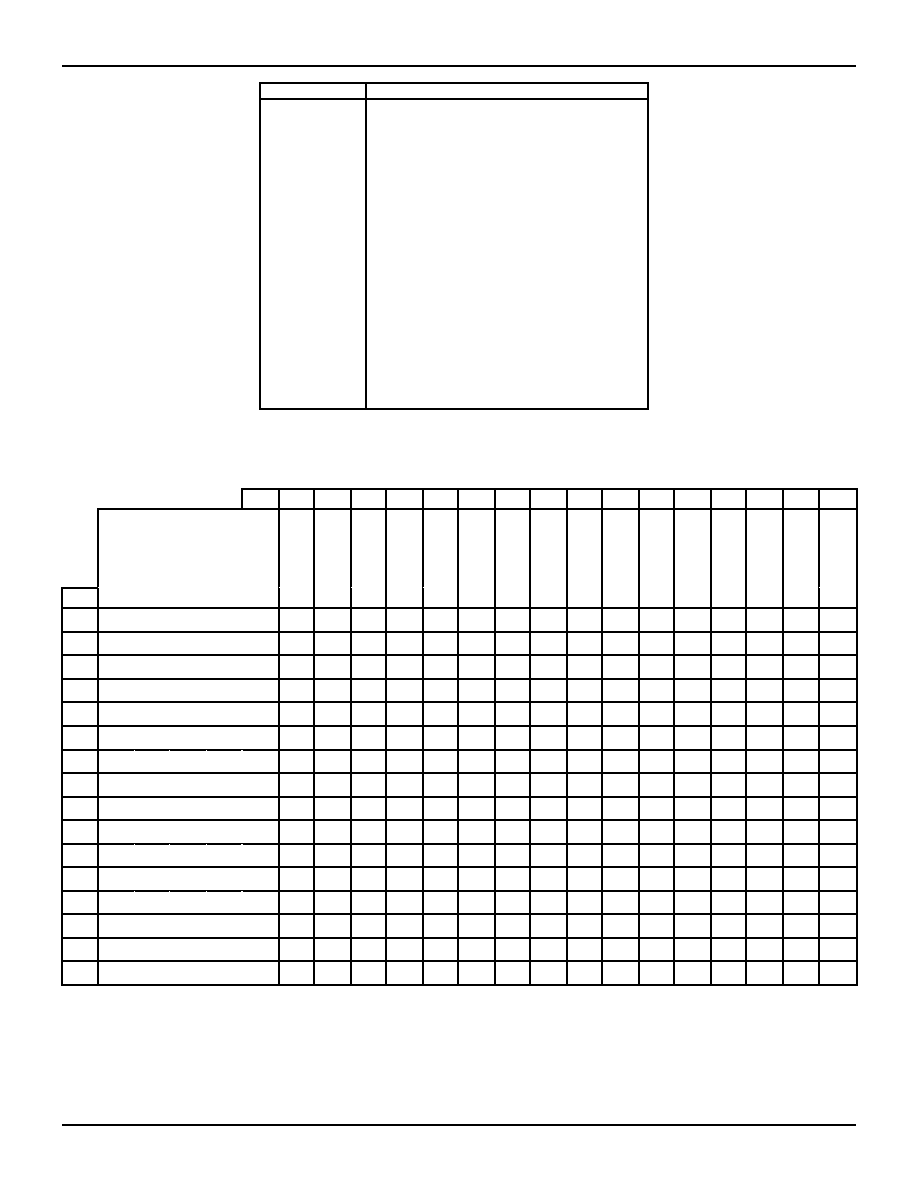

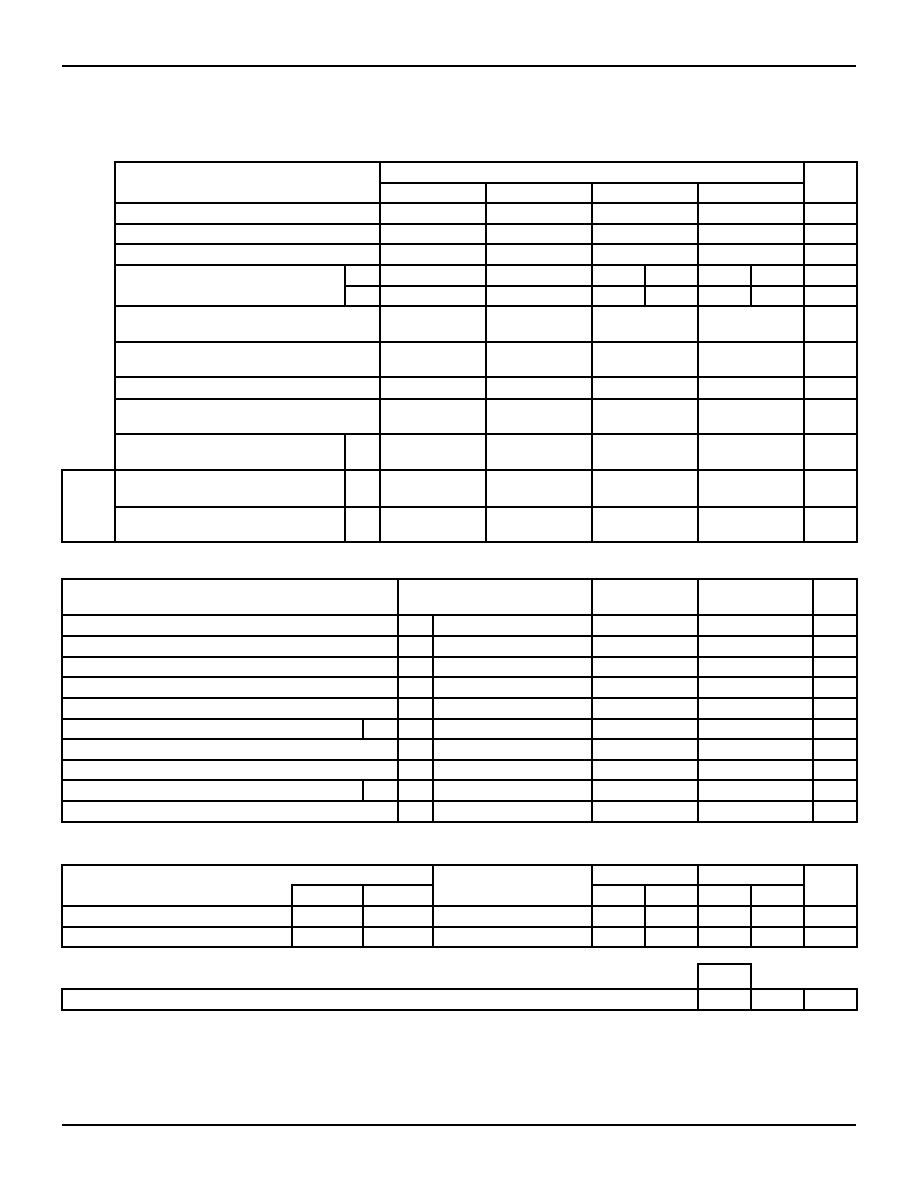

51

52

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

3

4

5

6

7

8

9

10

11

12

13

14

15

16

18

17

1

2

34

53

32

33

55

54

30

31

57

56

28

29

59

58

26

27

61

60

24

25

63

62

22

23

65

64

20

21

67

66

68

19

D

25

D

27

D

26

D

29

D

28

D

31

D

30

CODE ID

0

OE

3

DIAG MODE

0

CODE ID

1

LE

IN

DIAG MODE

1

D

0

OE

0

D

1

OE

SC

SC

7

SC

6

SC

5

SC

4

SC

3

SC

2

SC

1

SC

0

CB

0

CB

1

CB

2

CB

3

CB

4

CB

5

CB

6

G68 ≠ 1

D

23

D

22

D

21

D

20

D

19

D

18

D

17

V

CC

D

16

OE

2

LE

OUT

/

GENERAT

E

CORRECT

LE

DIAG

ERROR

MULT ERROR

GND

GND

D

24

D

3

D

4

D

5

D

6

D

7

D

8

GND

D

9

D

10

D

11

D

12

D

13

D

14

D

15

CB

7

OE

1

D

2

V

CC

2584 drw 04

PGA

TOPVIEW

11.6

5

IDT49C460/A/B/C/D/E

32-BIT CMOS ERROR DETECTION AND CORRECTION UNIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

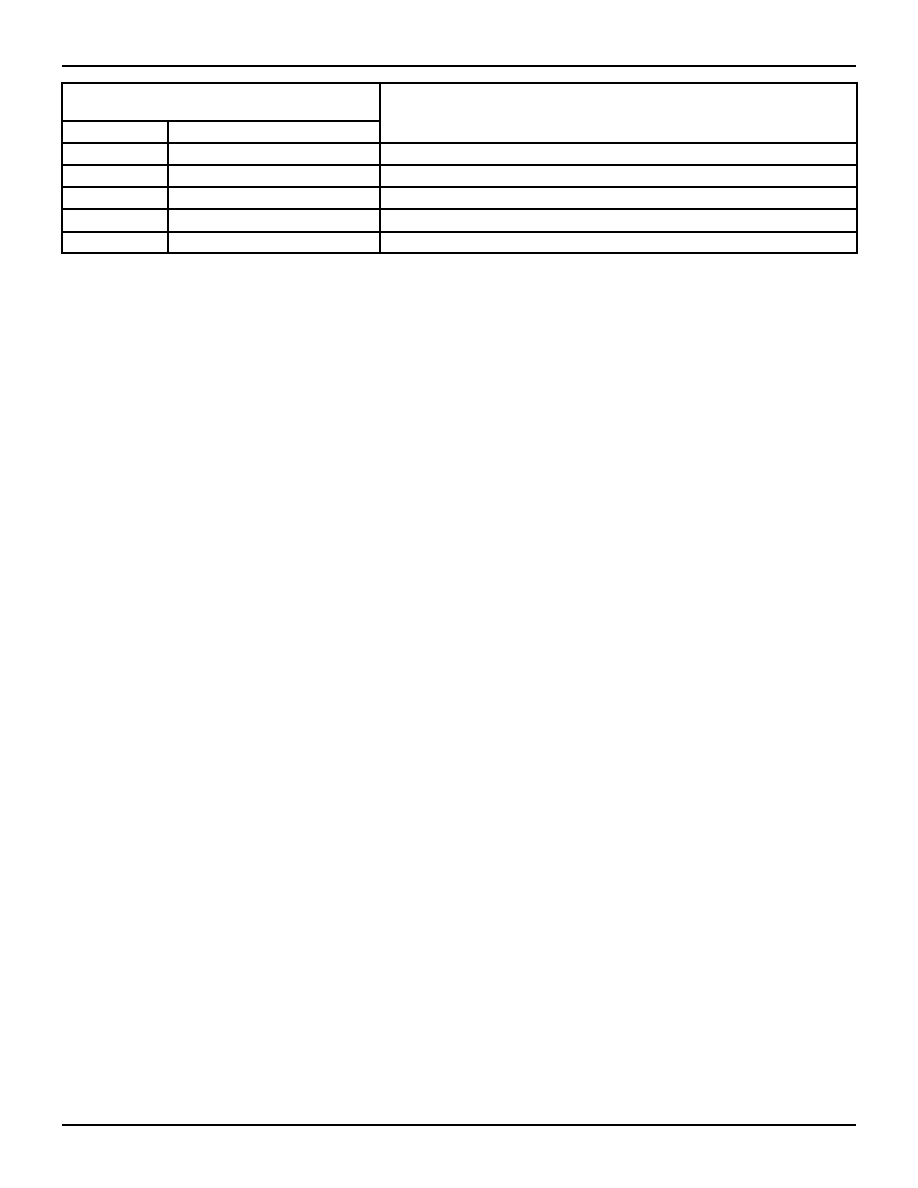

PIN DESCRIPTIONS

Pin Name

I/O

Description

DATA

0≠31

I/O

32 bidirectional data lines provide input to the Data Input Latch and Diagnostic Latch and also receive output from

the Data Output Latch. DATA

0

is the LSB; DATA

31

is the MSB.

CB

0≠7

I

Eight check bit input lines input check bits for error detection and also used to input syndrome bits for error

correction in 64-bit applications.

LE

IN

I

Latch Enable is for the Data Input Latch. Controls latching of the input data. Data Input Latch and Check Bit Input

Latch are latched to their previous state when LOW. When HIGH, the Data Input Latch and Check Bit Input Latch

follow the input data and input check bits.

LE

OUT

/

GENERATE

A multifunction pin which, when LOW, is in the Check Bit Generate Mode. In this mode, the device generates the

check bits or GENERATE partial check bits specific to the data in the Data Input Latch. The generated check bits

are placed on the SC outputs. Also, when LOW, the Data Out Latch is latched to its previous state.

When HIGH, the device is in the Detect or Correct Mode. In this mode, the device detects single and multiple

errors and generates syndrome bits based upon the contents of the Data Input Latch and Check Bit Input Latch.

In the Correct Mode, single bit errors are also automatically corrected and the corrected data is placed at the

inputs of the Data Output Latch. The syndrome result is placed on the SC outputs and indicates in a coded form

the number of errors and the specific bit-in-error. When HIGH, the Data Output Latch follows the output of the

Data Input Latch as modified by the correction logic network. In Correct Mode, single bit errors are corrected by

the network before being loaded into the Data Output Latch. In Detect Mode, the contents of the Data Input Latch

are passed through the correction network unchanged into the Data Output Latch. The Data Output Latch is

disabled, with its contents unchanged, if the EDC is in the Generate Mode.

SC

0≠7

O

Syndrome Check Bit outputs. Eight outputs which hold the check bits and partial check bits when the EDC is in

the Generate Mode and will hold the syndrome/partial syndrome bits when the device is in the Detect or Correct

modes. All are 3-state outputs.

OE

SC

I

Output Enable--Syndrome Check Bits. In the HIGH condition, the SC outputs are in the high impedance state.

When LOW, all SC output lines are enabled.

ERROR

O

In the Detect or Correct Mode, this output will go LOW if one or more data or check bits contain an error. When

HIGH, no errors have been detected. This pin is forced HIGH in the Generate Mode.

MULT

ERROR

O

In the Detect or Correct Mode, this output will go LOW if two or more bit errors have been detected. A HIGH level

indicates that either one or no errors have been detected. This pin is forced HIGH in the Generate Mode.

CORRECT

I

The correct input which, when HIGH, allows the correction network to correct any single-bit error in the Data Input

Latch (by complementing the bit-in-error) before putting it into the Data Output Latch. When LOW, the device will

drive data directly from the Data Input Latch to the Data Output Latch without correction.

OE

BYTE

0≠3

I

Output Enable--Bytes 0, 1, 2, 3. Data Output Latch. Control the three-state output buffers for each of the four

bytes of the Data Output Latch. When LOW, they enable the output buffer of the Data Output Latch. When HIGH,

they force the Data Output Latch buffer into the high impedance mode. One byte of the Data Output Latch is

easily activated by separately selecting the four enable lines.

DIAG

MODE

1,0

I

Select the proper diagnostic mode. They control the initialization, diagnostic and normal operation of the EDC.

CODE ID

1,0

I

These two code identification inputs identify the size of the total data word to be processed. The two allowable

data word sizes are 32 and 64 bits and their respective modified Hamming Codes are designated 32/39 and

64/72. Special CODE ID

1,0

, input 01 is also used to instruct the EDC that the signals CODE ID

1,0

, DIAG MODE

1,0

and CORRECT are to be taken from the Diagnostic Latch rather than from the input control lines.

LE

DIAG

I

This is the Latch Enable for the Diagnostic Latch. When HIGH, the Diagnostic Latch follows the 32-bit data on the

input lines. When LOW, the outputs of the Diagnostic Latch are latched to their previous states. The Diagnostic

Latch holds diagnostic check bits and internal control signals for CODE ID

1,0

, DIAG MODE

1,0

and CORRECT.

2584 tbl 01

11.6

6

IDT49C460/A/B/C/D/E

32-BIT CMOS ERROR DETECTION AND CORRECTION UNIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

EDC ARCHITECTURE SUMMARY

The IDT49C460s are high-performance cascadable EDCs

used for check bit generation, error detection, error correction

and diagnostics. The function blocks for this 32-bit device

consist of the following:

∑ Data Input Latch

∑ Check Bit Input Latch

∑ Check Bit Generation Logic

∑ Syndrome Generation Logic

∑ Error Detection Logic

∑ Error Correction Logic

∑ Data Output Latch

∑ Diagnostic Latch

∑ Control Logic

DATA INPUT/OUTPUT LATCH

The Latch Enable Input, LE

IN

, controls the loading of 32 bits

of data to the Data In Latch. The data from the DATA lines can

be loaded in the Diagnostic Latch under control of the

Diagnostic Latch Enable, LE

DIAG

, giving check bit information

in one byte and control information in another byte. The

Diagnostic Latch is used in the Internal Control Mode or in one

of the diagnostic modes. The Data Output Latch has buffers

that place data on the DATA lines. These buffers are split into

four 8-bit buffers, each having their own output enable con-

trols. This feature facilitates byte read and byte modify

operations.

CHECK BIT GENERATION LOGIC

This generates the appropriate check bits for the 32 bits of

data in the Data Input Latch. The modified Hamming Code is

the basis for generating the proper check bits.

SYNDROME GENERATION LOGIC

In both the Detect and Correct modes, this logic does a

comparison on the check bits read from memory against the

newly generated set of check bits produced for the data read

in from memory. Matching sets of check bits mean no error

was detected. If there is a mismatch, one or more of the data

or check bits is in error. Syndrome bits are produced by an

exclusive-OR of the two sets of check bits. Identical sets of

check bits mean the syndrome bits will be all zeros. If an error

results, the syndrome bits can be decoded to determine the

number of errors and the specific bit-in-error.

ERROR DETECTION LOGIC

This part of the device decodes the syndrome bits

generated by the Syndrome Generation Logic. With no errors

in either the input data or check bits, both the

ERROR

and

MULTERROR

outputs are HIGH. ERROR will go low if one

error is detected.

MULTERROR

and

ERROR

will both go low

if two or more errors are detected.

ERROR CORRECTION LOGIC

In single error cases, this logic complements (corrects) the

single data bit-in-error. This corrected data is loaded into the

Data Output Latch, which can then be read onto the bidirec-

tional data lines. If the error is resulting from one of the check

bits, the correction logic does not place corrected check bits

on the syndrome/check bit outputs. If the corrected check bits

are needed, the EDC must be switched to the Generate Mode.

DATA OUTPUT LATCH AND OUTPUT BUFFERS

The Data Output Latch is used for storing the result of an

error correction operation. The latch is loaded from the

correction logic under control of the Data Output Latch En-

able, LE

OUT

. The Data Output Latch may also be directly

loaded from the Data Input Latch in the PASSTHRU mode.

The Data Output Latch buffer is split into 4 individual buffers

which can be enabled by

OE

0≠3

separately for reading onto

the bidirectional data lines.

DIAGNOSTIC LATCH

The diagnostic latch is loadable under control of the

Diagnostic Latch Enable, LE

DIAG

, from the bidirectional data

lines. Check bit information is contained in one byte while the

other byte contains the control information. The Diagnostic

Latch is used for driving the device when in the Internal Control

Mode, or for supplying check bits when in one of the diagnostic

modes.

CONTROL LOGIC

Specifies in which mode the device will be operating in.

Normal operation is when the control logic is driven by external

control inputs. In the Internal Control Mode, the control signals

are read from the Diagnostic Latch. Since LE

OUT

and

GENERATE

are controlled by the same pin, the latching action

(LE

OUT

from high to low) of the Data Output Latch causes the

EDC to go into the Generate Mode.

11.6

7

IDT49C460/A/B/C/D/E

32-BIT CMOS ERROR DETECTION AND CORRECTION UNIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

DETAILED PRODUCT DESCRIPTION

The IDT49C460 EDC units contain the logic necessary to

generate check bits on 32 bits of data input according to a

modified Hamming Code. The EDC can compare internally

generated check bits against those read with the 32-bit data

to allow correction of any single bit data error and detection of

all double (and some triple) bit errors. The IDT49C460s can

be used for 32-bit data words (7 check bits) and 64-bit (8 check

bits) data words.

WORD SIZE SELECTION

The two code identification pins, CODE ID

1, 0

, are used to

determine the data word size that is 32 or 64 bits. They also

select the Internal Control Mode. Table 4 defines all possible

slice identification codes.

CHECK AND SYNDROME BITS

The IDT49C460s provide either check bits or syndrome

bits on the three-state output pins, SC

0≠7

. Check bits are

generated from a combination of the Data Input bits, while

syndrome bits are an exclusive-OR of the check bits gener-

ated from read data with the read check bits stored with the

data. Syndrome bits can be decoded to determine the single

bit in error or that a double (some triple) error was detected.

The check bits are labeled:

C

0

, C

1

, C

2

, C

3

, C

4

, C

5

, C

6

for the 32-bit configuration

C

0

, C

1

, C

2

, C

3

, C

4

, C

5

, C

6

, C

7

for the 64-bit configuration

Syndrome bits are similarly labeled S

0

through S

7

.

2584 tbl 02

Table 2. Diagnostic Mode Control

NOTES:

2584 tbl 03

1. In Generate Mode, data is read into the EDC unit and the check bits are generated. The same data is written to memory along with the check bits. Since

the DATA

OUT

Latch is not used in the Generate Mode, LE

OUT

(being LOW since it is tied to Generate) does not affect the writing of check bits.

2. Error Dep (Error Dependent):

ERROR

will be low for single or multiple errors, with

MULT ERROR

low for double or multiple errors. Both signals are high

for no errors.

3. LE

IN

is LOW.

Table 3. IDT49C460 Operating Modes

Correct

Diag

Mode

0

Diag

Mode

1

Diagnostic Mode Selected

X

0

0

Non-diagnostic Mode. Normal

EDC function in this mode.

X

0

1

Diagnostic Generate. The con

tents of the Diagnostic Latch are

substituted for the normally

generated check bits when in the

Generate Mode. The EDC

functions normally in the Detect or

Correct modes.

0/1

1

0

Diagnostic Detect/Correct. In

either mode, the contents of the

Diagnostic Latch are substituted

for the check bits normally read

from the Check Bit Input Latch.

The EDC functions normally in the

Generate Mode.

1

1

1

Initialize. The Data Input Latch

outputs are forced to zeros and

latched upon removal of Initialize

Mode.

0

1

1

PASSTHRU.

Operating

Mode

DM

0

DM

1

Generate

Correct

DATA

OUT

Latch

SC

0≠7

(

OE

OE

SC

= LOW)

ERROR

ERROR

MULT ERROR

MULT ERROR

Generate

0

1

0

0

0

X

LE

OUT

= LOW

(1)

Check Bits Generated from

DATA

IN

Latch

High

Detect

0

0

0

1

1

0

DATA

IN

Latch

Syndrome Bits DATA

IN

/

Check Bit Latch

Error Dep

(2)

Correct

0

0

0

1

1

1

DATA

IN

Latch w/

Single Bit Correction

Syndrome Bits DATA

IN

/

Check Bit Latch

Error Dep

PASSTHRU

1

1

1

0

DATA

IN

Latch

Check Bit Latch

High

Diagnostic

Generate

0

1

0

X

--

Check Bits from Diagnostic Latch

High

Diagnostic Detect

1

0

1

0

DATA

IN

Latch

Syndrome Bits DATA

IN

/

Diagnostic Latch

Error Dep

Diagnostic Correct

1

0

1

1

DATA

IN

Latch w/

Single Bit Correction

Syndrome Bits DATA

IN

/

Diagnostic Latch

Error Dep

Initialization

1

1

1

1

DATA

IN

Latch

Set to 0000

(3)

--

--

Internal

CODE ID

1,0

= 01 (Control Signals CODE ID

1,0

, DIAG MODE

1,0

and CORRECT are taken from Diagnostic Latch.)

11.6

8

IDT49C460/A/B/C/D/E

32-BIT CMOS ERROR DETECTION AND CORRECTION UNIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

OPERATING MODE SELECTION

Tables 2 and 3 describe the nine operating modes of the

IDT49C460s. The Diagnostic Mode pins -- DIAG MODE

0,1

-- define four basic areas of operation.

GENERATE

and

CORRECT further divide operation into 8 functions, with

CODE ID

1,0

defining the ninth mode as the Internal Mode.

Generate Mode is used to display the check bits on the

outputs SC

0≠7

. The Diagnostic Generate Mode displays

check bits as stored in the Diagnostic Latch.

Detect Mode provides an indication of errors or multiple

errors on the outputs

ERROR

and

MULT ERROR

. Single bit

errors are not corrected in this mode. The syndrome bits are

provided on the outputs SC

0≠7

. For the Diagnostic Detect

Mode, the syndrome bits are generated by comparing the

internally generated check bits from the Data In Latch with

check bits stored in the diagnostic latch rather than with the

check bit latch contents.

Correct Mode is similar to the Detect Mode except that

single bit errors will be complemented (corrected) and made

available as input to the Data Out Latches. Again, the

Diagnostic Correct Mode will correct single bit errors as

determined by syndrome bits generated from the data input

and contents of the diagnostic latches.

The Initialize Mode provides check bits for all zero bit data.

Data Input Latches are set, latched to a logic zero and made

available as input to the Data Out Latches.

The Internal Mode disables the external control pins DIAG

MODE

0,1

and CORRECT to be defined by the Diagnostic

Latch. Even CODE ID

1,0

, although externally set to the 01

code, can be redefined from the Diagnostic Latch data.

Code ID

1

Code ID

0

Slice Selected

0

0

32-Bit

0

1

Internal Control Mode

1

0

64-Bit, Lower 32≠Bit (0≠31)

1

1

64-Bit, Upper 32-Bit (32≠63)

2584 tbl 04

Table 4. Slice Identification

DATA

0≠31

DATA

0≠31

CB

7

HIGH

CB

6

C

6

CB

5

C

5

CB

4

C

4

CB

3

C

3

CB

2

C

2

CB

1

C

1

CB

0

C

0

SC

7

NC

SC

6

S

6

/C

6

SC

5

S

5

/C

5

SC

4

S

4

/C

4

SC

3

S

3

/C

3

SC

2

S

2

/C

2

SC

1

S

1

/C

1

SC

0

S

0

/C

0

CODE ID

1,0

IDT49C460

0,0

2584 drw 05

Figure 1. 32-Bit Configuration

Figure 2. 64-Bit Configuration

BYTE

3

BYTE

2

BYTE

1

BYTE

0

C

0

C

1

C

2

C

3

C

4

C

5

C

6

DATA

CHECK BITS

0

7

8

15

16

23

24

31

2584 drw 07

BYTE

7

BYTE

6

BYTE

5

BYTE

4

BYTE

3

BYTE

2

BYTE

1

BYTE

0

C

0

C

1

C

2

C

3

C

4

C

5

C

6

C

7

DATA

CHECK BITS

0

7

8

15

16

23

24

31

32

39

40

47

48

55

56

63

2584 drw 08

Figure 3. 32-Bit Data Format

Figure 4. 64-Bit Data Format

DATA

0≠31

DATA

32≠63

DATA INPUT

CHECK≠BIT INPUTS

1/8

IDT74FCT240

DATA

CB

0≠7

OE

SC

CODE ID

1,0

SC

0≠7

IDT49C460

(LOWER 32 BITS)

DATA

CB

0≠7

OE

SC

CODE ID

1,0

SC

0≠7

IDT49C460

(UPPER 32 BITS)

ERROR

MULT

ERROR

MULT

ERROR

ERROR

SYNDROME/

CHECK BITS

1,1

1,0

OE

SC

32

32

8

8

8

2584 drw 06

11.6

9

IDT49C460/A/B/C/D/E

32-BIT CMOS ERROR DETECTION AND CORRECTION UNIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

32-BIT DATA WORD CONFIGURATION

A single IDT49C460 EDC unit, connected as shown in

Figure 1, provides all the logic needed for single bit error

correction and double bit error detection of a 32-bit data field.

The identification code indicates 7 check bits are required.

The CB

7

pin should be HIGH.

Figure 3 indicates the 39-bit data format for two bytes of

data and 7 check bits. Table 3 describes the operating mode

available.

Table 6 indicates the data bits participating in the check bit

generation. For example, check bit C

0

is the exclusive-OR

function of the 16 data input bits marked with an X. Check bits

are generated and output in the Generate and Initialization

Mode. Check bits from the respective latch are passed,

unchanged, in the PASSTHRU or Diagnostic Generate Mode.

Syndrome bits are generated by an exclusive-OR or the

generated check bits with the read check bits. For example,

S

n

is the XOR of check bits C

n

from those read with those

generated. Table 7 indicates the decoding of the seven

syndrome bits to identify the bit-in-error for a single bit error,

or whether a double or triple bit error was detected. The all

zero case indicates no errors detected.

In the Correct Mode, the syndrome bits are used to

complement (correct) single bit errors in the data bits. For

double or multiple error detection, the data available as input

to the Data Out Latch is not defined.

Table 5 defines the bit definition for the Diagnostic Latch.

As defined in Table 3, several modes will use the diagnostic

check bits to determine syndrome bits or to pass as check bits

to the SC

0≠7

outputs. The Internal Mode substitutes the

indicated bit position for the external control signals.

2584 drw 05

Table 5. 32-Bit Diagnostic Latch Coding Format

BIT 0

CB

0

DIAGNOSTIC

BIT 1

CB

1

DIAGNOSTIC

BIT 2

CB

2

DIAGNOSTIC

BIT 3

CB

3

DIAGNOSTIC

BIT 4

CB

4

DIAGNOSTIC

BIT 5

CB

5

DIAGNOSTIC

BIT 6

CB

6

DIAGNOSTIC

BIT 7

CB

7

DIAGNOSTIC

BIT 8

CODE ID

0

BIT 9

CODE ID

1

BIT 10

DIAG MODE

0

BIT 11

DIAG MODE

1

BIT 12

CORRECT

BIT 13≠31

DON'T CARE

Generated

Participating Data Bits

Check Bits

Parity

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

C

0

Even (XOR)

X

X

X

X

X

X

X

X

C

1

Even (XOR)

X

X

X

X

X

X

X

X

C

2

Odd (XNOR)

X

X

X

X

X

X

X

X

C

3

Odd (XNOR)

X

X

X

X

X

X

X

X

C

4

Even (XOR)

X

X

X

X

X

X

X

X

C

5

Even (XOR)

X

X

X

X

X

X

X

X

C

6

Even (XOR)

X

X

X

X

X

X

X

X

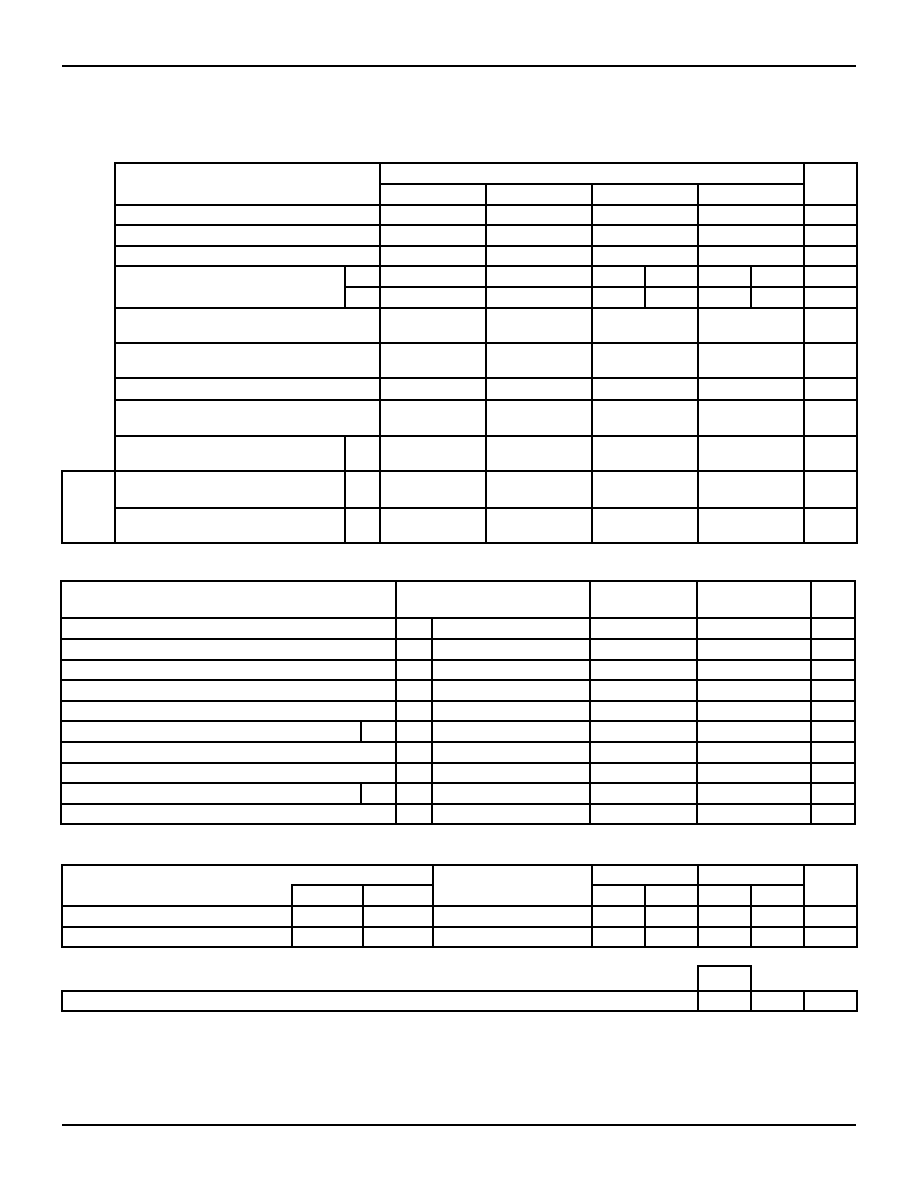

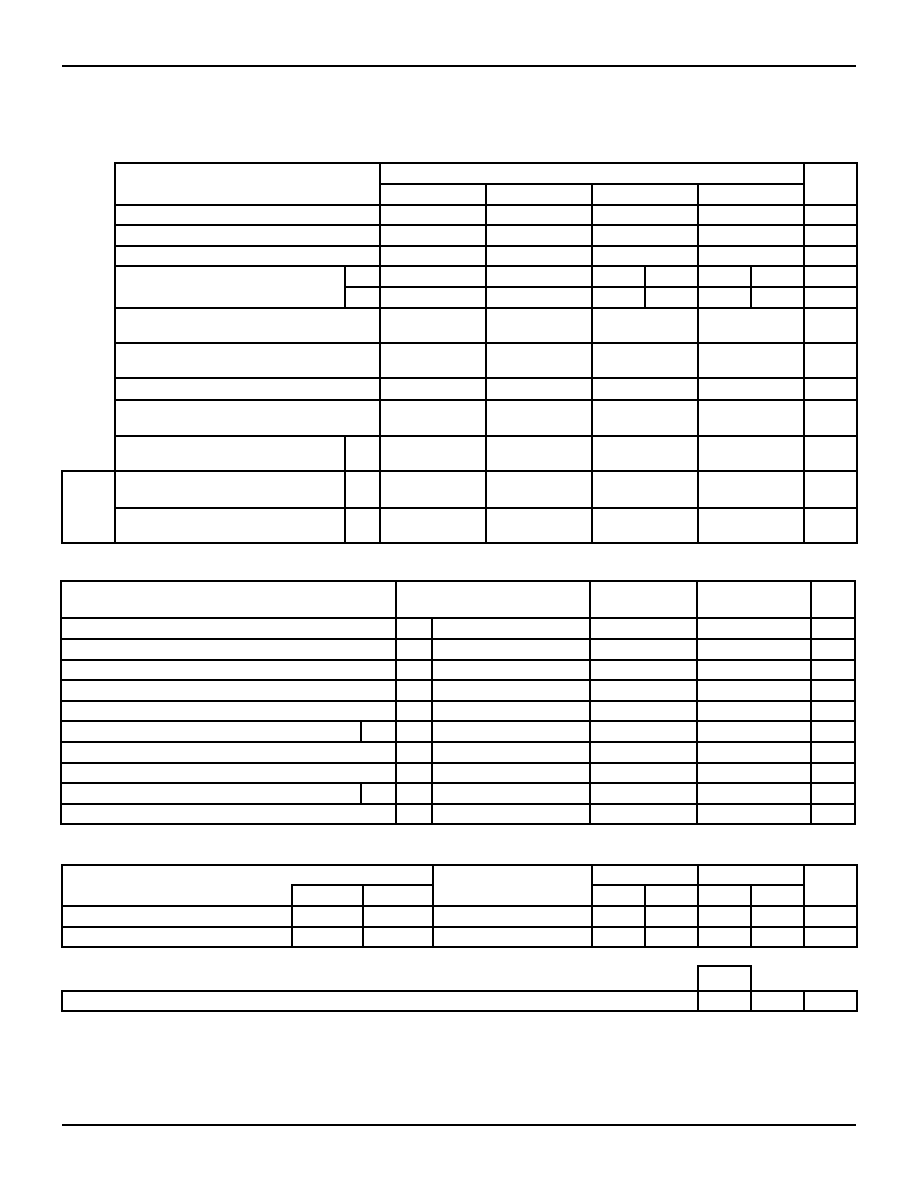

2584 tbl 06

Table 6. 32≠Bit Modified Hamming Code≠Check Bit Encode Chart

2584 tbl 07

Generated

Participating Data Bits

Check Bits

Parity

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

C

0

Even (XOR)

X

X

X

X

X

X

X

X

C

1

Even (XOR)

X

X

X

X

X

X

X

X

C

2

Odd (XNOR)

X

X

X

X

X

X

X

X

C

3

Odd (XNOR)

X

X

X

X

X

X

X

X

C

4

Even (XOR)

X

X

X

X

X

X

X

X

C

5

Even (XOR)

X

X

X

X

X

X

X

X

C

6

Even (XOR)

X

X

X

X

X

X

X

X

11.6

10

IDT49C460/A/B/C/D/E

32-BIT CMOS ERROR DETECTION AND CORRECTION UNIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

Table 3 describes the operating modes available for the 64/

72 configuration.

Table 11 indicates the data bits participating in the check bit

generation. For example, check bit C

0

is the exclusive-OR

function of the 32 data input bits marked with an X. Check bits

are generated and output in the Generate and Initialization

modes. Check bits are passed as stored in the PASSTHRU or

Diagnostic Generate modes.

Syndrome bits are generated by an exclusive-OR of the

generated check bits with the read check bits. For example,

S

n

is the XOR of check bits C

n

from those read with those

generated. Table 9 indicates the decoding of the 8 syndrome

bits to determine the bit in error for a single bit error or whether

a double or triple bit error was detected. The all zero case

indicates no errors detected.

In the Correct Mode, the syndrome bits are used to

complement (correct) single bit errors in the data bits. For

double or multiple error detection, the data available as input

to the Data Out Latch is not defined.

Tables 8A and 8B define the bit definition for the Diagnostic

Latch. As defined in Table 3, several modes will use the

Diagnostic Check Bits to determine syndrome bits or to pass

as check bits to the SC

0≠7

outputs. The Internal Mode sub-

stitutes the indicated bit position for the external control

signals.

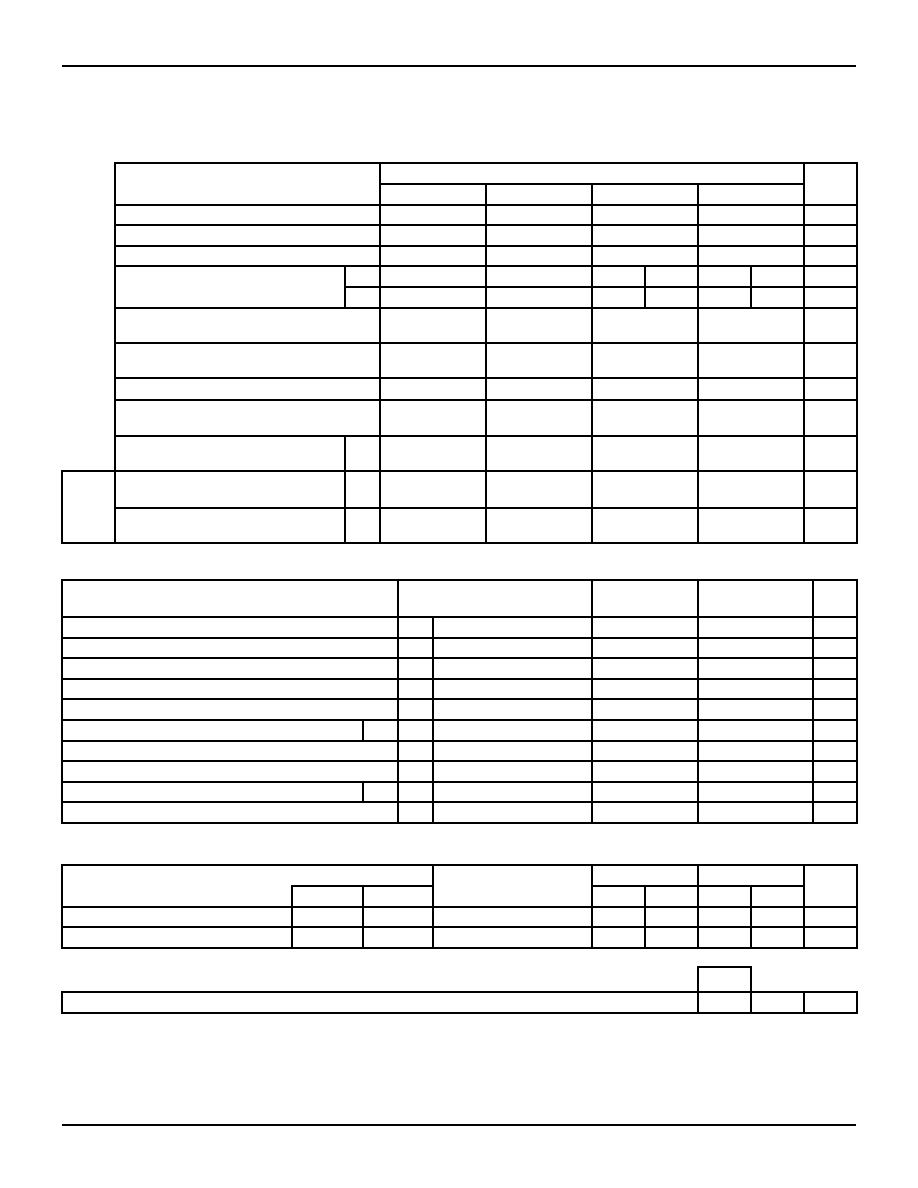

Performance data is provided in Table 10, relating a single

IDT49C460 EDC with the two cascaded units of Figure 2. As

indicated, a summation of propagation delays is required from

the cascading arrangement of EDC units.

NOTES:

2584 tbl 08

1. * = No errors detected

2. Number = The number of the single bit-in-error

3. T = Two errors detected

4. M = Three or more errors detected

Table 7. Syndrome Decode to Bit-in-Error (32-Bit)

64-BIT DATA WORD CONFIGURATION

Two IDT49C460 EDC units, connected as shown in Figure

2, provide all the logic needed for single bit error detection and

double bit error detection of a 64-bit data field. Table 4 gives

the CODE ID

1,0

values needed for distinguishing the upper 32

bits from the lower 32 bits. Valid syndrome, check bits and the

ERROR

and

MULT ERROR

signals come from the IC with the

CODE ID

1,0

= 11. Control signals not indicated are connected

to both units in parallel. The EDC with the CODE ID

1,0

= 10

has the

OE

SC

grounded. The

OE

SC

selects the syndrome bits

from the EDC with CODE ID

1,0

= 11 and also controls the

check bit buffers from memory.

Data In bits 0 through 31 are connected to the same

numbered inputs of the EDC unit with CODE ID

1,0

= 10, while

Data In bits 32 through 63 are connected to Data Inputs 0 to

31, respectively, for the EDC unit with CODE ID

1,0

= 11.

Figure 4 indicates the 72-bit data format of 8 bytes of data

and 8 check bits. Check bits are input to the EDC unit with

CODE ID

1,0

= 10 through a three-state buffer unit such as the

IDT74FCT244. Correction of single bit errors of the 64-bit

configuration requires a feedback of syndrome bits from the

upper EDC unit to the lower EDC unit. The MUX shown on the

functional block diagram is used to select the CB

0≠7

pins as

the syndrome bits rather than internally generated syndrome

bits.

2584 tbl 09

Table 8A. 64-Bit Diagnostic Latch≠Coding Format

(Diagnostic and Correct Mode)

Bit

Internal Function

0

CB

0

DIAGNOSTIC

1

CB

1

DIAGNOSTIC

2

CB

2

DIAGNOSTIC

3

CB

3

DIAGNOSTIC

4

CB

4

DIAGNOSTIC

5

CB

5

DIAGNOSTIC

6

CB

6

DIAGNOSTIC

7

CB

7

DIAGNOSTIC

8

CODE ID

0

LOWER 32-BIT

9

CODE ID

1

LOWER 32-BIT

10

DIAG MODE

0

LOWER 32-BIT

11

DIAG MODE

1

LOWER 32-BIT

12

CORRECT LOWER 32-BIT

13≠31

DON'T CARE

32≠39

DON'T CARE

40

CODE ID

0

UPPER 32-BIT

41

CODE ID

1

UPPER 32-BIT

42

DIAG MODE

0

UPPER 32-BIT

43

DIAG MODE

1

UPPER 32-BIT

44

CORRECT UPPER 32-BIT

45≠63

DON'T CARE

Hex

0

1

2

3

4

5

6

7

Syndrome

S

6

0

0

0

0

1

1

1

1

Bits

S

5

0

0

1

1

0

0

1

1

S

4

0

1

0

1

0

1

0

1

Hex S

3

S

2

S

1

S

0

0

0

0

0

0

*

C4 C5

T

C6

T

T

30

1

0

0

0

1

C0

T

T

14

T

M

M

T

2

0

0

1

0

C1

T

T

M

T

2

24

T

3

0

0

1

1

T

18

8

T

M

T

T

M

4

0

1

0

0

C2

T

T

15

T

3

25

T

5

0

1

0

1

T

19

9

T

M

T

T

31

6

0

1

1

0

T

20

10

T

M

T

T

M

7

0

1

1

1

M

T

T

M

T

4

26

T

8

1

0

0

0

C3

T

T

M

T

5

27

T

9

1

0

0

1

T

21

11

T

M

T

T

M

A

1

0

1

0

T

22

12

T

1

T

T

M

B

1

0

1

1

17

T

T

M

T

6

28

T

C

1

1

0

0

T

23

13

T

M

T

T

M

D

1

1

0

1

M

T

T

M

T

7

29

T

E

1

1

1

0

16

T

T

M

T

M

M

T

F

1

1

1

1

T

M

M

T

0

T

T

M

11.6

11

IDT49C460/A/B/C/D/E

32-BIT CMOS ERROR DETECTION AND CORRECTION UNIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

Bit

Internal Function

0≠7

DON'T CARE

8

CODE ID

0

LOWER 32-BIT

9

CODE ID

1

LOWER 32-BIT

10

DIAG MODE

0

LOWER 32-BIT

11

DIAG MODE

1

LOWER 32-BIT

12

CORRECT LOWER 32-BIT

13≠31

DON'T CARE

32

CB

0

DIAGNOSTIC

33

CB

1

DIAGNOSTIC

34

CB

2

DIAGNOSTIC

35

CB

3

DIAGNOSTIC

36

CB

4

DIAGNOSTIC

37

CB

5

DIAGNOSTIC

38

CB

6

DIAGNOSTIC

39

CB

7

DIAGNOSTIC

40

CODE ID

0

UPPER 32-BIT

41

CODE ID

1

UPPER 32-BIT

42

DIAG MODE

0

UPPER 32-BIT

43

DIAG MODE

1

UPPER 32-BIT

44

CORRECT UPPER 32-BIT

45≠63

DON'T CARE

2584 tbl 10

Table 8B. 64-Bit Diagnostic Latch≠Coding Format (Diagnostic and Correct Mode)

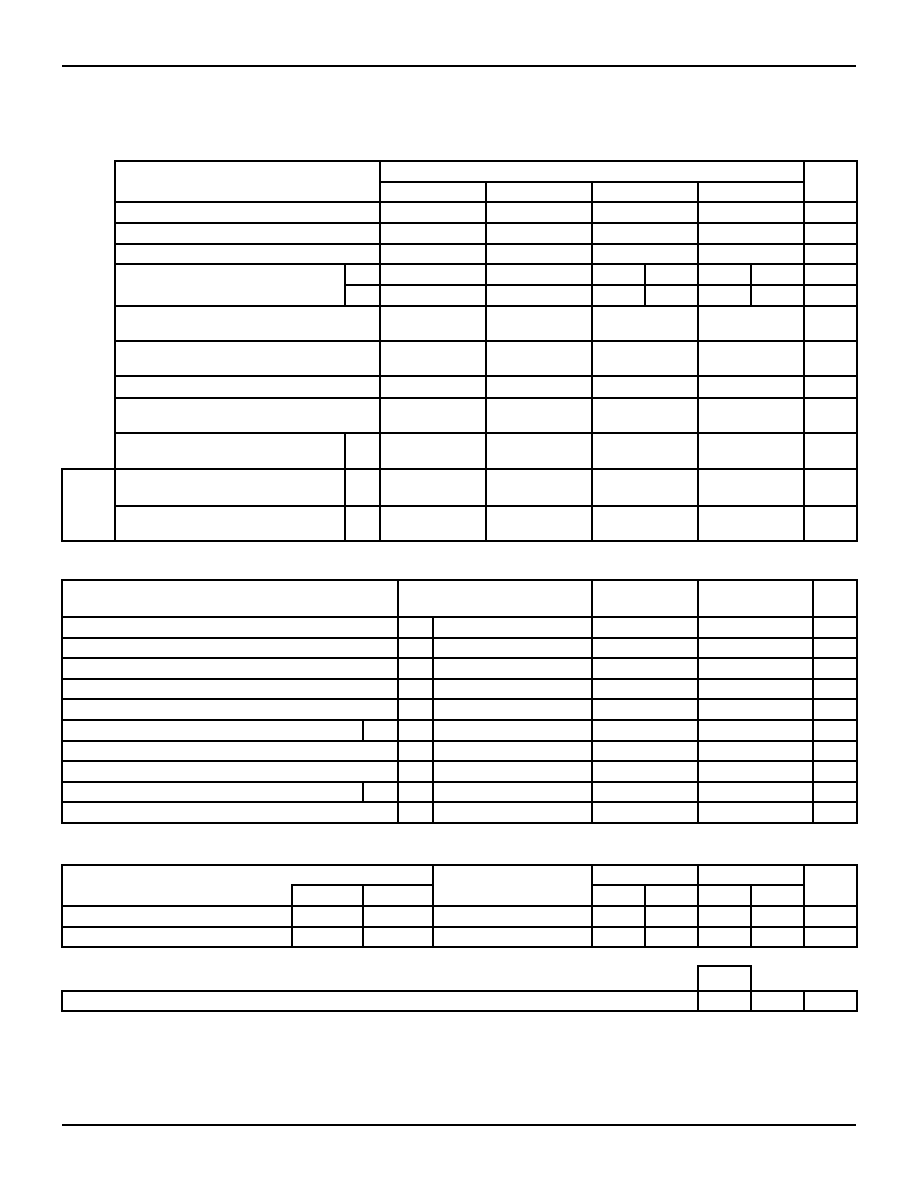

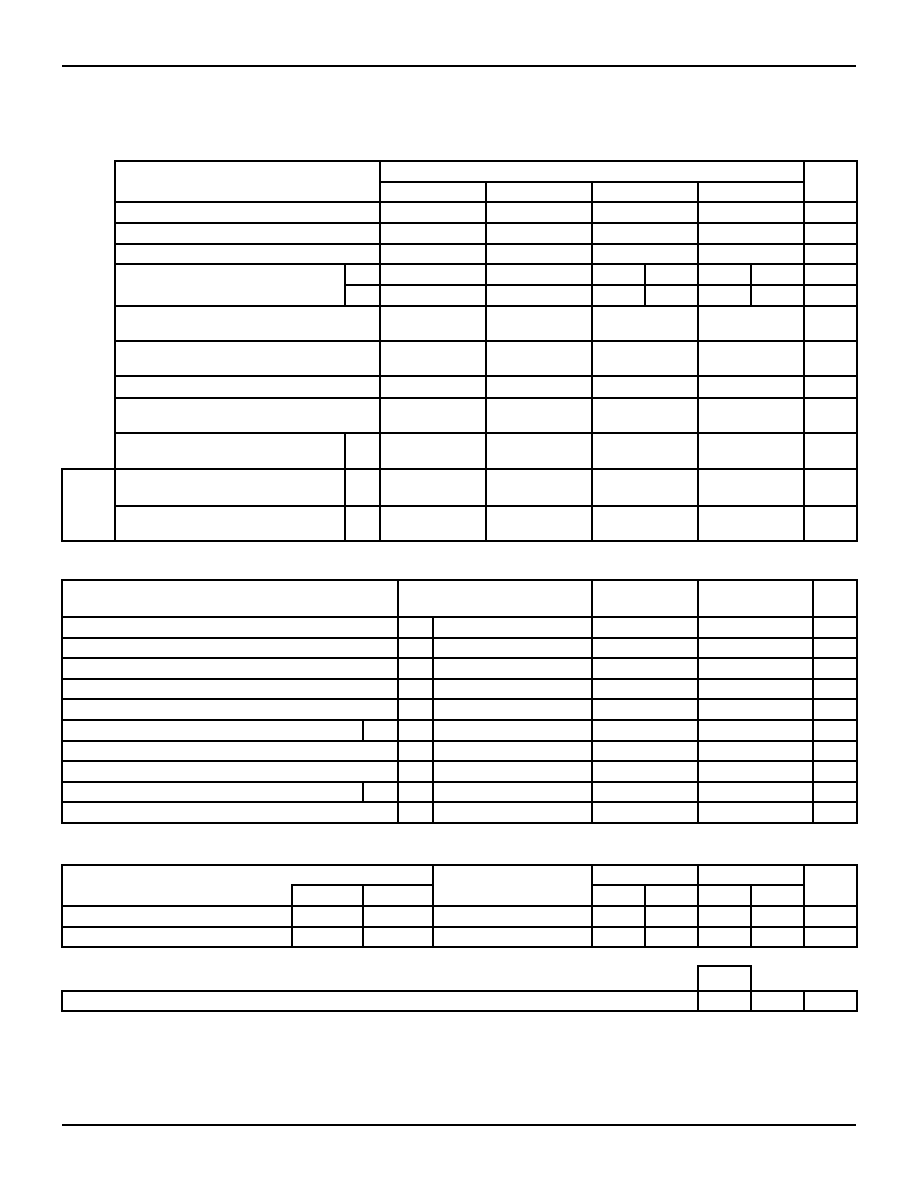

Hex

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

S

7

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

Syndrome

S

6

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

Bits

S

5

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

S

4

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Hex

S

3

S

2

S

1

S

0

0

0

0

0

0

*

C4

C5

T

C6

T

T

62

C7

T

T

46

T

M

M

T

1

0

0

0

1

C0

T

T

14

T

M

M

T

T

M

M

T

M

T

T

30

2

0

0

1

0

C1

T

T

M

T

34

56

T

T

50

40

T

M

T

T

M

3

0

0

1

1

T

18

8

T

M

T

T

M

M

T

T

M

T

2

24

T

4

0

1

0

0

C2

T

T

15

T

35

57

T

T

51

41

T

M

T

T

31

5

0

1

0

1

T

19

9

T

M

T

T

63

M

T

T

47

T

3

25

T

6

0

1

1

0

T

20

10

T

M

T

T

M

M

T

T

M

T

4

26

T

7

0

1

1

1

M

T

T

M

T

36

58

T

T

52

42

T

M

T

T

M

8

1

0

0

0

C3

T

T

M

T

37

59

T

T

53

43

T

M

T

T

M

9

1

0

0

1

T

21

11

T

M

T

T

M

M

T

T

M

T

5

27

T

A

1

0

1

0

T

22

12

T

33

T

T

M

49

T

T

M

T

6

28

T

B

1

0

1

1

17

T

T

M

T

38

60

T

T

54

44

T

1

T

T

M

C

1

1

0

0

T

23

13

T

M

T

T

M

M

T

T

M

T

7

29

T

D

1

1

0

1

M

T

T

M

T

39

61

T

T

55

45

T

M

T

T

M

E

1

1

1

0

16

T

T

M

T

M

M

T

T

M

M

T

0

T

T

M

F

1

1

1

1

T

M

M

T

32

T

T

M

48

T

T

M

T

M

M

T

NOTES:

2584 tbl 11

* = No errors detected

T = Two errors detected

Number = The number of the single bit-in-error

M = Three or more errors detected

Table 9. Syndrome Decode to Bit≠In≠Error (64≠Bit Configuration)

11.6

12

IDT49C460/A/B/C/D/E

32-BIT CMOS ERROR DETECTION AND CORRECTION UNIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

2584 tbl 12

Table 10. Key Calculations for the 64≠Bit Configuration

64≠Bit

Propagation Delay

From

To

Component Delay for IDT49C460 AC Specifications

DATA

Check Bits Out

(DATA TO SC) + (CB TO SC, CODE ID 11)

DATA

Corrected DATA

OUT

(DATA TO SC) + (CB TO SC, CODE ID 11) + (CB TO DATA, CODE ID 10)

DATA

Syndromes Out

(DATA TO SC) + (CB TO SC, CODE ID 11)

DATA

ERROR

for 64 Bits

(DATA TO SC) + (CB TO

ERROR

, CODE ID 11)

DATA

MULT ERROR

for 64 Bits

(DATA TO SC) + (CB TO

MULT ERROR

, CODE ID 11)

11.6

13

IDT49C460/A/B/C/D/E

32-BIT CMOS ERROR DETECTION AND CORRECTION UNIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

Generated

Participating Data Bits

Check Bits

Parity

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

C

0

Even (XOR)

X

X

X

X

X

X

X

X

C

1

Even (XOR)

X

X

X

X

X

X

X

X

C

2

Odd (XNOR)

X

X

X

X

X

X

X

X

C

3

Odd (XNOR)

X

X

X

X

X

X

X

X

C

4

Even (XOR)

X

X

X

X

X

X

X

X

C

5

Even (XOR)

X

X

X

X

X

X

X

X

C

6

Even (XOR)

X

X

X

X

X

X

X

X

C

7

Even (XOR)

X

X

X

X

X

X

X

X

2584 tbl 13

Generated

Participating Data Bits

Check Bits

Parity

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

C

0

Even (XOR)

X

X

X

X

X

X

X

X

C

1

Even (XOR)

X

X

X

X

X

X

X

X

C

2

Odd (XNOR)

X

X

X

X

X

X

X

X

C

3

Odd (XNOR)

X

X

X

X

X

X

X

X

C

4

Even (XOR)

X

X

X

X

X

X

X

X

C

5

Even (XOR)

X

X

X

X

X

X

X

X

C

6

Even (XOR)

X

X

X

X

X

X

X

X

C

7

Even (XOR)

X

X

X

X

X

X

X

X

2584 tbl 14

Generated

Participating Data Bits

Check Bits

Parity

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

C

0

Even (XOR)

X

X

X

X

X

X

X

X

C

1

Even (XOR)

X

X

X

X

X

X

X

X

C

2

Odd (XNOR)

X

X

X

X

X

X

X

X

C

3

Odd (XNOR)

X

X

X

X

X

X

X

X

C

4

Even (XOR)

X

X

X

X

X

X

X

X

C

5

Even (XOR)

X

X

X

X

X

X

X

X

C

6

Even (XOR)

X

X

X

X

X

X

X

X

C

7

Even (XOR)

X

X

X

X

X

X

X

X

2584 tbl 15

Generated

Participating Data Bits

Check Bits

Parity

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

C

0

Even (XOR)

X

X

X

X

X

X

X

X

C

1

Even (XOR)

X

X

X

X

X

X

X

X

C

2

Odd (XNOR)

X

X

X

X

X

X

X

X

C

3

Odd (XNOR)

X

X

X

X

X

X

X

X

C

4

Even (XOR)

X

X

X

X

X

X

X

X

C

5

Even (XOR)

X

X

X

X

X

X

X

X

C

6

Even (XOR)

X

X

X

X

X

X

X

X

C

7

Even (XOR)

X

X

X

X

X

X

X

X

NOTE:

2584 tbl 16

1. The check bit is generated as either an XOR or XNOR of the 32 data bits noted by an "X" in the table.

Table 11. 64≠Bit Modified Hamming Code≠Check Bit Encoding

11.6

14

IDT49C460/A/B/C/D/E

32-BIT CMOS ERROR DETECTION AND CORRECTION UNIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

SC OUTPUTS

The tables below indicate how the SC

0≠7

outputs are

generated in each control mode of various CODE IDs (Internal

Control Mode not applicable).

Correct/

CODE ID

1,0

Detect

00

10

11

SC

0

PH0

C

0

PH1

C

0

PH2

CB

0

SC

1

PA

C

1

PA

C

1

PA

CB

1

SC

2

PB

C

2

PB

C

2

PB

CB

2

SC

3

PC

C

3

PC

C

3

PC

CB

3

SC

4

PD

C

4

PD

C

4

PD

CB

4

SC

5

PE

C

5

PE

C

5

PE

CB

5

SC

6

PF

C

6

PF

C

6

PF

CB

6

SC

7

--

PF

C

7

PG

CB

7

Final

Syndrome

Partial

Syndrome

Final

Syndrome

2584 tbl 17

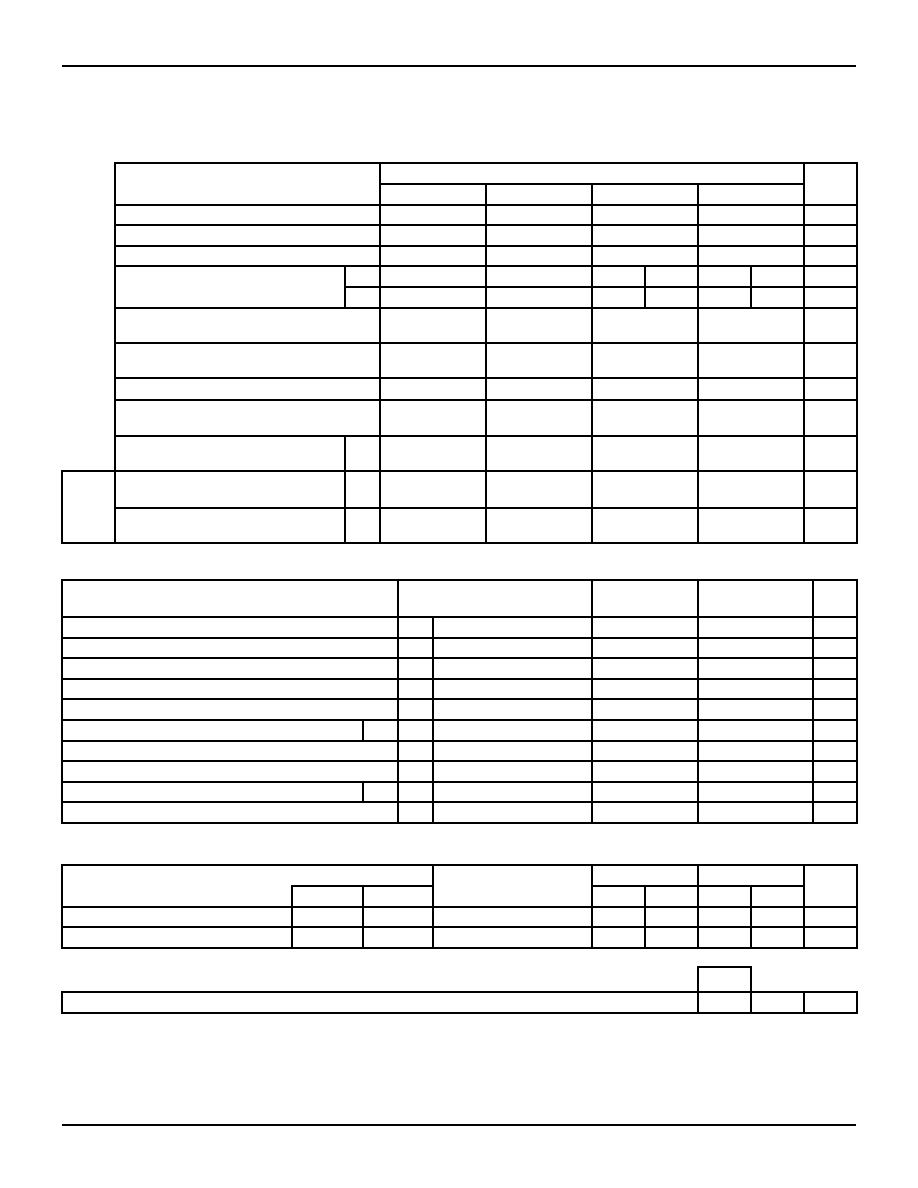

2584 tbl 19

CODE ID

1,0

Generate

00

10

11

SC

0

PH0

PH1

PH2

CB

0

SC

1

PA

PA

PA

CB

1

SC

2

PB

PB

PB

CB

2

SC

3

PC

PC

PC

CB

3

SC

4

PD

PD

PD

CB

4

SC

5

PE

PE

PE

CB

5

SC

6

PF

PF

PF

CB

6

SC

7

--

PF

PG

CB

7

Final

Check Bits

Partial

Check Bits

Final

Check Bits

Diagnostic

Correct/

CODE ID

1,0

Detect

00

10

11

SC

0

PH0

DL0

PH1

DL0

PH2

CB

0

SC

1

PA

DL1

PA

DL1

PA

CB

1

SC

2

PB

DL2

PB

DL2

PB

CB

2

SC

3

PC

DL3

PC

DL3

PC

CB

3

SC

4

PD

DL4

PD

DL4

PD

CB

4

SC

5

PE

DL5

PE

DL5

PE

CB

5

SC

6

PF

DL6

PF

DL6

PF

CB

6

SC

7

--

PF

DL7

PG

CB

7

Final

Syndrome

Partial

Syndrome

Final

Syndrome

Diagnostic

CODE ID

1,0

Generate

00

10

11

SC

0

DL0

DL0

DL32

SC

1

DL1

DL1

DL33

SC

2

DL2

DL2

DL34

SC

3

DL3

DL3

DL35

SC

4

DL4

DL4

DL36

SC

5

DL5

DL5

DL37

SC

6

DL6

DL6

DL38

SC

7

--

DL7

DL39

Final

Check Bits

Partial

Check Bits

Final

Check Bits

2584 tbl 20

2584 tbl 18

CODE ID

1,0

PASSTHRU

00

10

11

SC

0

C0

C0

CB

0

SC

1

C1

C1

CB

1

SC

2

C2

C2

CB

2

SC

3

C3

C3

CB

3

SC

4

C4

C4

CB

4

SC

5

C5

C5

CB

5

SC

6

C6

C6

CB

6

SC

7

--

C7

CB

7

2584 tbl 21

Table 12. SC0-7 Outputs For Different Control Modes

11.6

15

IDT49C460/A/B/C/D/E

32-BIT CMOS ERROR DETECTION AND CORRECTION UNIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

FUNCTIONAL EQUATIONS

The equations below describe the IDT49C460 output val-

ues as defined by the value of the inputs and internal states.

DEFINITIONS

PA = D

0

D

1

D

2

D

4

D

6

D

8

D

10

D

12

D

16

D

17

D

18

D

20

D

22

D

24

D

26

D

28

PB

= D

0

D

3

D

4

D

7

D

9

D

10

D

13

D

15

D

16

D

19

D

20

D

23

D

25

D

26

D

29

D

31

PC

= D

0

D

1

D

5

D

6

D

7

D

11

D

12

D

13

D

16

D

17

D

21

D

22

D

23

D

27

D

28

D

29

PD = D

2

D

3

D

4

D

5

D

6

D

7

D

14

D

15

D

18

D

19

D

20

D

21

D

22

D

23

D

30

D

31

PE = D

8

D

9

D

10

D

11

D

12

D

13

D

14

D

15

D

24

D

25

D

26

D

27

D

28

D

29

D

30

D

31

PF = D

0

D

1

D

2

D

3

D

4

D

5

D

6

D

7

D

24

D

25

D

26

D

27

D

28

D

29

D

30

D

31

PG = D

8

D

9

D

10

D

11

D

12

D

13

D

14

D

15

D

16

D

17

D

18

D

19

D

20

D

21

D

22

D

23

PH0 = D

0

D

4

D

6

D

7

D

8

D

9

D

11

D

14

D

17

D

18

D

19

D

21

D

26

D

28

D

29

D

31

PH1 = D

1

D

2

D

3

D

5

D

8

D

9

D

11

D

14

D

17

D

18

D

19

D

21

D

24

D

25

D

27

D

30

PH2 = D

0

D

4

D

6

D

7

D

10

D

12

D

13

D

15

D

16

D

20

D

22

D

23

D

26

D

28

D

29

D

31

DATA CORRECTION

The tables below indicate which data output bits are

corrected depending upon the syndromes and the CODE

ID

1,0

position. The syndromes that determine data correction

are, in some cases, syndromes input externally via the CB

inputs and, in some cases, syndromes input externally by that

EDC (S

i

are the internal syndromes and are the same as the

value of the SC

i

output of that EDC if enabled).

11.6

16

IDT49C460/A/B/C/D/E

32-BIT CMOS ERROR DETECTION AND CORRECTION UNIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

ABSOLUTE MAXIMUM RATINGS

(1)

CAPACITANCE

(T

A

= + 25

∞

C, f = 1.0MHz)

Symbol

Rating

Com'l.

Mil.

Unit

V

TERM

Terminal Voltage

with Respect to

GND

≠0.5 to

V

CC

+ 0.5V

≠0.5 to

V

CC

+ 0.5V

V

V

CC

Power Supply

Voltage

-0.5 to +7.0

-0.5 to +7.0

V

T

A

Operating

Temperature

0 to +70

≠55 to +125

∞

C

T

BIAS

Temperature

Under Bias

≠55 to +125

≠65 to +135

∞

C

T

STG

Storage

Temperature

≠55 to +125

≠65 to +150

∞

C

I

OUT

DC Output Current

30

30

mA

Symbol

Parameter

(1)

Conditions

Typ.

Unit

C

IN

Input Capacitance

V

IN

= 0V

5

pF

C

OUT

Output Capacitance

V

OUT

= 0V

7

pF

NOTE:

2584 tbl 25

1. This parameter is sampled and not 100% tested.

NOTE:

2584 tbl 24

1. Stresses greater than those listed under ABSOLUTE MAXIMUM

RATINGS may cause permanent damage to the device. This is a stress

rating only and functional operation of the device at these or any other

conditions above those indicated in the operational sections of this

specifications is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability.

DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified: V

LC

= 0.2V; V

HC

= V

CC

≠ 0.2V

Commercial: T

A

= 0

∞

C to +70

∞

C, V

CC

= 5.0V

±

5%; Military: T

A

= ≠55

∞

C to +125

∞

C, V

CC

= 5.0V

±

10%

NOTES:

2584 tbl 26

1. For conditions shown as Max. or Min. use appropriate value specified under Electrical Characteristics for the applicable device type.

2. Typical values are at V

CC

= 5.0V, + 25

∞

C ambient and maximum loading.

3. Not more than one output should be shorted at one time. Duration of the circuit test should not exceed one second.

4. These input levels provide zero noise immunity and should only be static tested in a noise-free environment.

Symbol

Parameter

Test Conditions

(1)

Min.

Typ.

(2)

Max.

Unit

V

IH

Input HIGH Level

Guaranteed Logic HIGH Level

(4)

2.0

--

--

V

V

IL

Input LOW Level

Guaranteed Logic LOW Level

(4)

--

--

0.8

V

I

I H

Input HIGH Current

V

CC

= Max., V

IN

= V

CC

--

0.1

10.0

µ

A

I

I L

Input LOW Current

V

CC

= Max., V

IN

= GND

--

≠0.1

≠10.0

µ

A

V

OH

Output HIGH Voltage

V

CC

= Min.

I

OH

= 300

µ

A

V

CC

--

--

V

I

OH

= ≠12mA Mil.

2.4

4.3

--

I

OH

= ≠15mA Com'l.

2.4

4.3

--

V

OL

Output LOW Voltage

V

CC

= Min.

I

OL

= 300

µ

A

--

--

GND

V

I

OL

= 12mA Mil.

--

0.3

0.5

I

OL

= 16mA Com'l.

--

0.3

0.5

I

OZ

Off State (High Impedance)

V

CC

= Max.

V

O

= 0V

--

≠0.1

≠20.0

µ

A

Output Current

V

O

= V

CC

(Max.)

--

0.1

20.0

I

OS

Output Short Circuit Current

V

CC

= Max., V

OUT

= 0V

(3)

≠30.0

--

--

mA

11.6

17

IDT49C460/A/B/C/D/E

32-BIT CMOS ERROR DETECTION AND CORRECTION UNIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

DC ELECTRICAL CHARACTERISTICS (Cont'd.)

Commercial: T

A

= 0

∞

C to +70

∞

C, V

CC

= 5.0V

±

5%; Military: T

A

= ≠55

∞

C to +125

∞

C, V

CC

= 5.0V

±

10%

V

LC

= 0.2V; V

HC

= V

CC

≠ 0.2V

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

I

CCQ

Quiescent Power Supply Current

V

CC

= Max.; All Inputs

--

3.0

10

mA

(CMOS Inputs)

V

HC

V

IN

, V

IN

V

LC

f

OP

= 0; Outputs Disabled

I

CCT

Quiescent Input Power Supply

V

CC

= Max., V

IN

= 3.4V, f

OP

= 0

--

0.3

0.75

mA/

Current (per Input @ TTL High)

(5)

Input

I

CCD

Dynamic Power Supply Current

V

CC

= Max.

MIL.

--

6

10

mA/

V

HC

V

IN

, V

IN

V

LC

COM'L.

--

6

7

MHz

Outputs Open,

OE

= L

I

CC

Total Power Supply Current

(6)

V

CC

= Max., f

OP

= 10MHz

MIL.

--

60

110

mA

Outputs Open,

OE

= L

COM'L.

--

60

80

50 % Duty cycle

V

HC

V

IN

, V

IN

V

LC

V

CC

= Max., f

OP

= 10MHz

MIL.

--

70

125

Outputs Open,

OE

= L

COM'L.

--

70

95

50 % Duty cycle

V

IH

= 3.4V, V

IL

= 0.4V

NOTES:

2584 tbl 27

5. I

CCT

is derived by measuring the total current with all the inputs tied together at 3.4V, subtracting out I

CCQ

, then dividing by the total number of inputs.

6. Total Supply Current is the sum of the Quiescent current and the Dynamic current (at either CMOS or TTL input levels). For all conditions, the Total Supply

Current can be calculated by using the following equation:

I

CC

= I

CCQ

+ I

CCT

(N

T

x D

H

) + I

CCD

(f

OP

)

D

H

= Data duty cycle TTL high period (V

IN

= 3.4V).

N

T

= Number of dynamic inputs driven at TTL levels.

f

OP

= Operating frequency in Megahertz.

CMOS TESTING CONSIDERATIONS

Special test board considerations must be taken into

account when applying high-speed CMOS products to the

automatic test environment. Large output currents are being

switched in very short periods and proper testing demands

that test set-ups have minimized inductance and guaranteed

zero voltage grounds. The techniques listed below will assist

the user in obtaining accurate testing results:

1) All input pins should be connected to a voltage potential

during testing. If left floating, the device may oscillate,

causing improper device operation and possible latchup.

2) Placement and value of decoupling capacitors is critical.

Each physical set-up has different electrical

characteristics and it is recommended that various

decoupling capacitor sizes be experimented with.

Capacitors should be positioned using the minimum lead

lengths. They should also be distributed to decouple

power supply lines and be placed as close as possible to

the DUT power pins.

3) Device grounding is extremely critical for proper device

testing. The use of multi-layer performance boards with

radial decoupling between power and ground planes is

necessary. The ground plane must be sustained from the

performance board to the DUT interface board and wiring

unused interconnect pins to the ground plane is

recommended. Heavy gauge stranded wire should be

used for power wiring, with twisted pairs being

recommended for minimized inductance.

4) To guarantee data sheet compliance, the input thresholds

should be tested per input pin in a static environment. To

allow for testing and hardware-induced noise, IDT

recommends using V

IL

0V and V

IH

3V for AC tests.

11.6

18

IDT49C460/A/B/C/D/E

32-BIT CMOS ERROR DETECTION AND CORRECTION UNIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

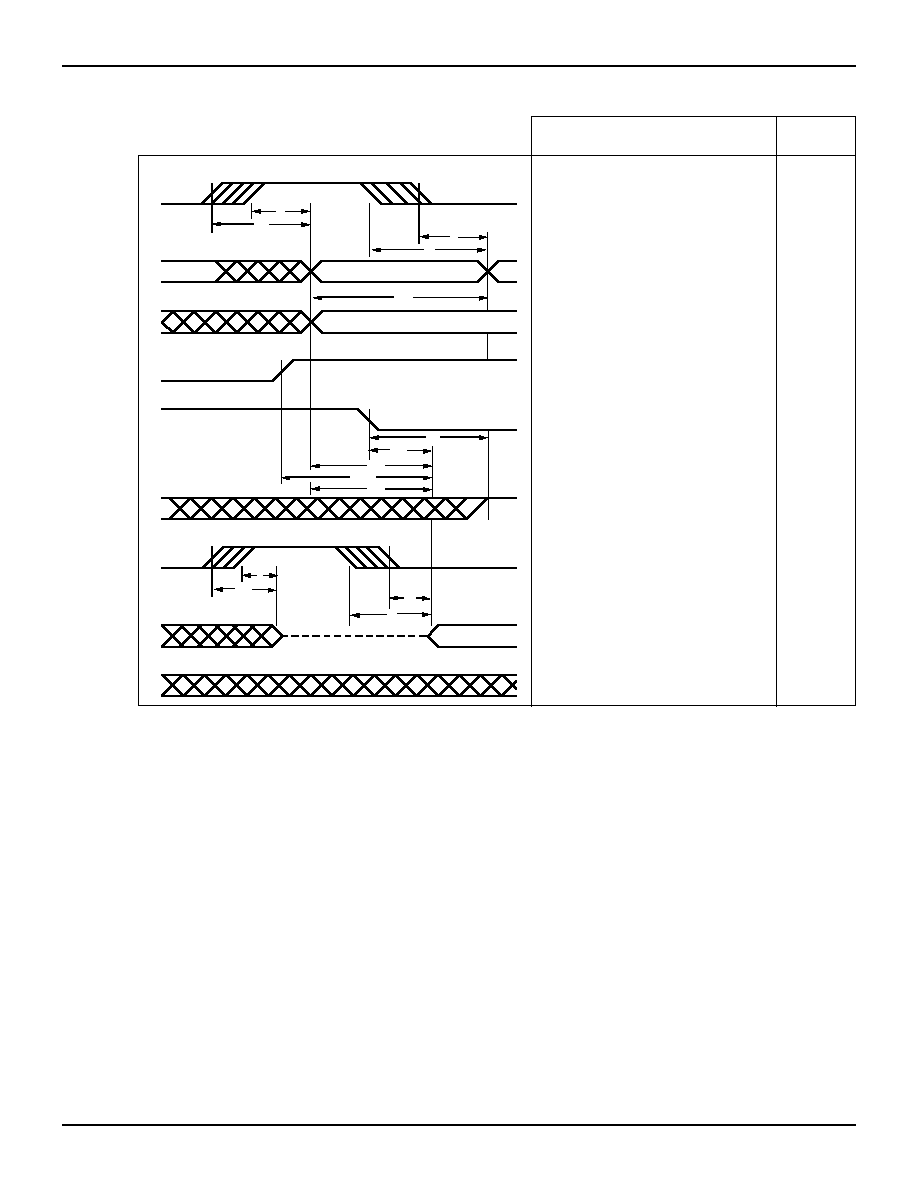

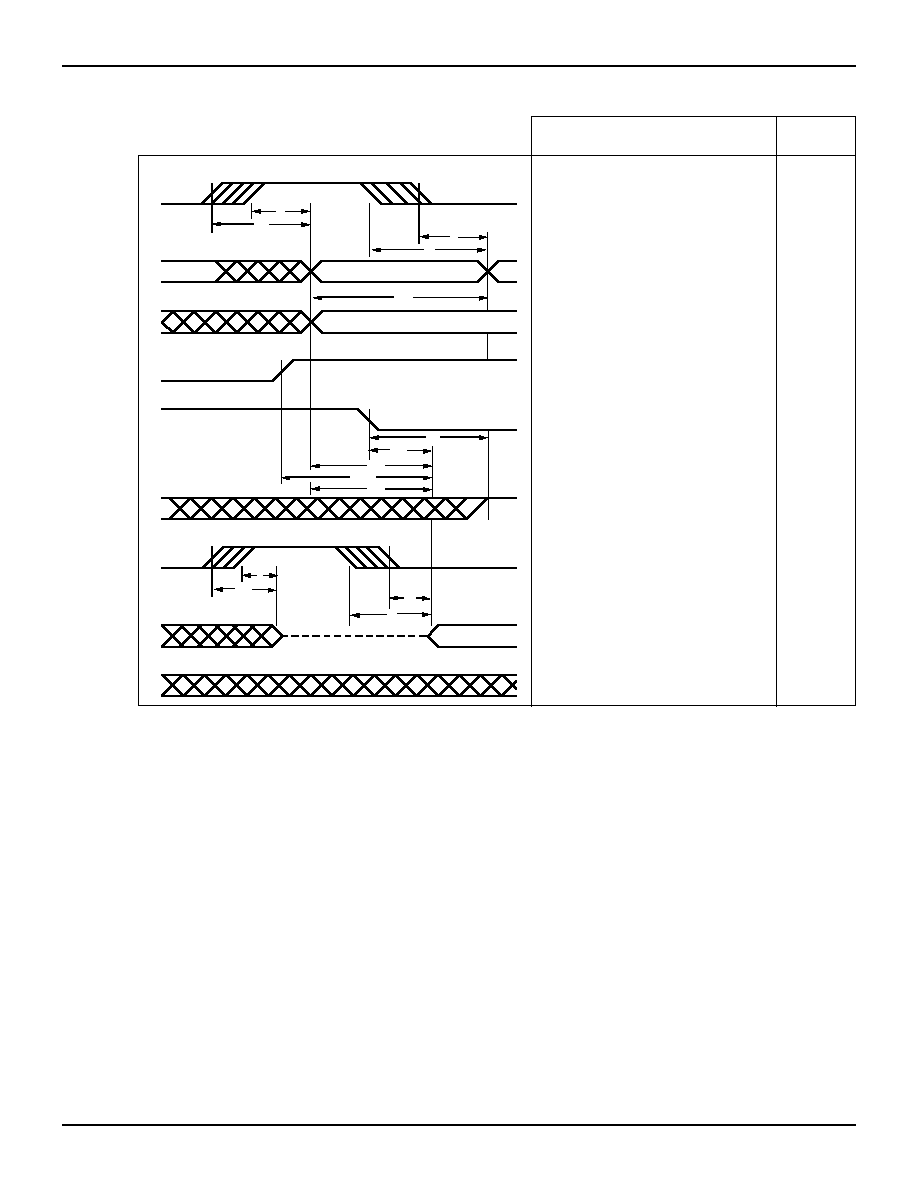

PRELIM

INARY

NOTE: (15) above applies to correction path.

2584 tbl 71

IDT49C460E AC ELECTRICAL CHARACTERISTICS

(Guaranteed Commercial Range Performance) Temperature range: 0

∞

C to +70

∞

C, V

CC

= 5.0V

±

5%

The inputs switch between 0V to 3V with signal measured at the 1.5V level.

PROPAGATION DELAYS

(1)

SET-UP AND HOLD TIMES RELATIVE TO LATCH ENABLES

NOTES:

2584 tbl 73

1. CI = 50pF.

2. These parameters are combinational propagation delay calculations, and are not tested in production.

3. Data In or Correct Data Out measurement requires timing as shown in the Switching Waveforms.

4. Set-up and Hold times relative to Latch Enables (Latching Data).

5. Output tests specified with CI = 5pF and measured to 0.5V change of output level. Testing is performed at CI = 50pF and correlated to CI = 5pF.

6. Not production tested, guaranteed by characterization.

OUTPUT ENABLE/DISABLE TIMES

(5)

MINIMUM PULSE WIDTHS

Min.

LE

IN

, LE

OUT

/

GENERATE

, LE

DIAG

ud

ud

(Positive≠going pulse)

5

ns

Enable

Disable

From Input

Enable

Disable

To Output

Min.

Max.

Min.

Max.

Unit

OE Byte

0≠3

d

d

u

u

DATA

0≠31

0

7

0

6

ns

OE

SC

d

d

u

u

SC

0≠7

0

7

0

6

ns

2584 tbl 70

2584 tbl 72

To Output

From Input

SC

0≠7

DATA

0≠31

ERROR

ERROR

MULT ERROR

MULT ERROR

Unit

DATA

0≠31(3)

11

14

(2)

10

11

ns

CB

0≠7

(CODE ID

1,0

= 00, 11)

9

12

7

9

ns

CB

0≠7

(CODE ID

1,0

= 10)

9

10

--

--

ns

LE

OUT

/

GENERATE

u

u

--

9

d

d

7

d

d

8

ns

d

d

13

--

u

u

7

u

u

8

ns

CORRECT

Not Internal Control Mode

--

11

--

--

ns

DIAG MODE

Not Internal Control Mode

11

18

8

14

ns

CODE ID

1,0

13

(6)

17

12

15

ns

LE

IN

From latched to Transparent

16

19

13

16

ns

LE

DIAG

From latched to Transparent

u

u

11

(6)

17

11

13

ns

Internal

Control

LE

DIAG

(Internal Control Mode) From

latched to Transparent

u

u

11

(6)

16

11

13

ns

Mode

DATA

0≠31

(Internal Control Mode)

Via Diagnostic Latch

u

u

11

17

(2)

9

11

ns

From Input

To Input

(Latching Data)

Set-up Time

Min.

Hold Time

Min.

Unit

DATA

0≠31(4)

d

d

LE

IN

3

3

ns

CB

0≠7

(4)

d

d

LE

IN

2

3

ns

DATA

0≠31(4, 6)

d

d

LE

OUT

/

GENERATE

5

(15)

0

ns

CB

0≠7

(CODE ID 00, 11)

(4, 6)

d

d

LE

OUT

/

GENERATE

11

0

ns

CB

0≠7

(CODE ID 10)

(4, 6)

d

d

LE

OUT

/

GENERATE

6

0

ns

CORRECT

(4, 6)

u

u

d

d

LE

OUT

/

GENERATE

6

0

ns

DIAG MODE

(4, 6)

d

d

LE

OUT

/

GENERATE

13

0

ns

CODE ID

1,0(4, 6)

d

d

LE

OUT

/

GENERATE

8

0

ns

LE

IN(4, 6)

u

u

d

d

LE

OUT

/

GENERATE

14

0

ns

DATA

0≠31(4, 6)

LE

DIAG

3

3

ns

11.6

19

IDT49C460/A/B/C/D/E

32-BIT CMOS ERROR DETECTION AND CORRECTION UNIT

MILITARY AND COMMERCIAL TEMPERATURE RANGES

MINIMUM PULSE WIDTHS

Min.

LE

IN

, LE

OUT

/

GENERATE

, LE

DIAG

ud

ud

(Positive≠going pulse)

5

ns

2584 tbl 30

NOTE: (15) above applies to correction path.

2584 tbl 29

IDT49C460D AC ELECTRICAL CHARACTERISTICS

(Guaranteed Commercial Range Performance) Temperature range: 0

∞

C to +70

∞

C, V

CC

= 5.0V

±

5%

The inputs switch between 0V to 3V with signal measured at the 1.5V level.

PROPAGATION DELAYS

(1)

2584 tbl 28

SET-UP AND HOLD TIMES RELATIVE TO LATCH ENABLES

NOTES:

2584 tbl 31

1. CI = 50pF.

2. These parameters are combinational propagation delay calculations, and are not tested in production.

3. Data In or Correct Data Out measurement requires timing as shown in the Switching Waveforms.

4. Set-up and Hold times relative to Latch Enables (Latching Data).

5. Output tests specified with CI = 5pF and measured to 0.5V change of output level. Testing is performed at CI = 50pF and correlated to CI = 5pF.

6. Not production tested, guaranteed by characterization.

Enable

Disable

From Input

Enable

Disable

To Output

Min.

Max.

Min.

Max.

Unit

OE Byte

0≠3

d

d

u

u

DATA

0≠31

0

8

0

10

ns

OE

SC

d

d

u

u

SC

0≠7

0

8

0

10

ns

OUTPUT ENABLE/DISABLE TIMES

(5)

(6)

To Output

From Input

SC

0≠7

DATA

0≠31

ERROR

ERROR

MULT ERROR

MULT ERROR

Unit

DATA

0≠31(3)

14

18

(2)

12

15

ns

CB

0≠7

(CODE ID

1,0

= 00, 11)

11

16

10

12

ns

CB

0≠7

(CODE ID

1,0

= 10)

12

12

--

--

ns

LE

OUT

/

GENERATE

u

u

--

9

d

d

7

d

d

8

ns

d

d

14

--

u

u

7

u

u

8

ns

CORRECT

Not Internal Control Mode

--

12

--

--

ns

DIAG MODE

Not Internal Control Mode

12

20

10

15

ns

CODE ID

1,0

14

(6)

18

13

16

ns

LE

IN

From latched to Transparent

17

21

14

17

ns

LE

DIAG

From latched to Transparent

u

u

12

(6)

18

12

14

ns

Internal

Control

LE

DIAG

(Internal Control Mode) From

latched to Transparent

u

u

12

(6)

17

12

14

ns

Mode

DATA

0≠31

(Internal Control Mode)

Via Diagnostic Latch

u

u

12

19

(2)

10

12

ns

From Input

To Input

(Latching Data)

Set-up Time

Min.

Hold Time

Min.

Unit

DATA

0≠31(4)

d

d

LE

IN

3

3

ns

CB

0≠7

(4)

d

d

LE

IN

2

3

ns

DATA

0≠31(4, 6)

d

d

LE

OUT

/

GENERATE

5

(15)

0

ns

CB

0≠7

(CODE ID 00, 11)

(4, 6)

d

d

LE

OUT

/

GENERATE

11

0

ns

CB

0≠7

(CODE ID 10)

(4, 6)

d

d

LE

OUT

/

GENERATE

6

0

ns

CORRECT

(4, 6)

u