1

IDT74FCT16925AT/CT/ET

FAST CMOS 16-BIT REGISTERED TRANSCEIVER

INDUSTRIAL TEMPERATURE RANGE

FEATURES:

∑ 0.5 MICRON CMOS Technology

∑ High-speed, low-power CMOS replacement for ABT functions

∑ Typical t

SK(o)

(Output Skew) < 250ps

∑ Low input and output leakage

1µA (max.)

∑ High drive outputs (-32mA I

OH

, 64mA I

OL

)

∑ Power off disable outputs permit "live insertion"

∑ Typical V

OLP

(Output Ground Bounce) < 1.0V at V

CC

= 5V,

T

A

= 25∞C

∑ Available in SSOP and TSSOP packages

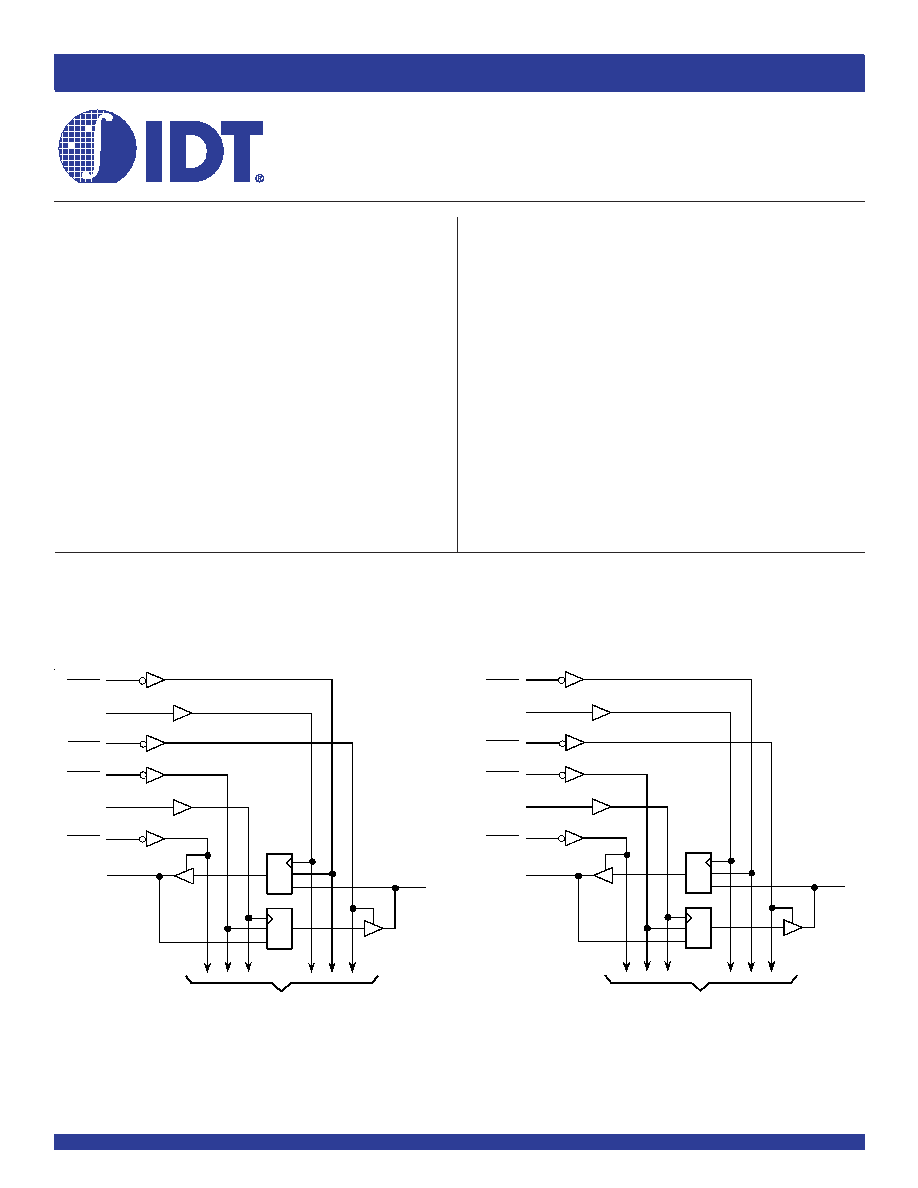

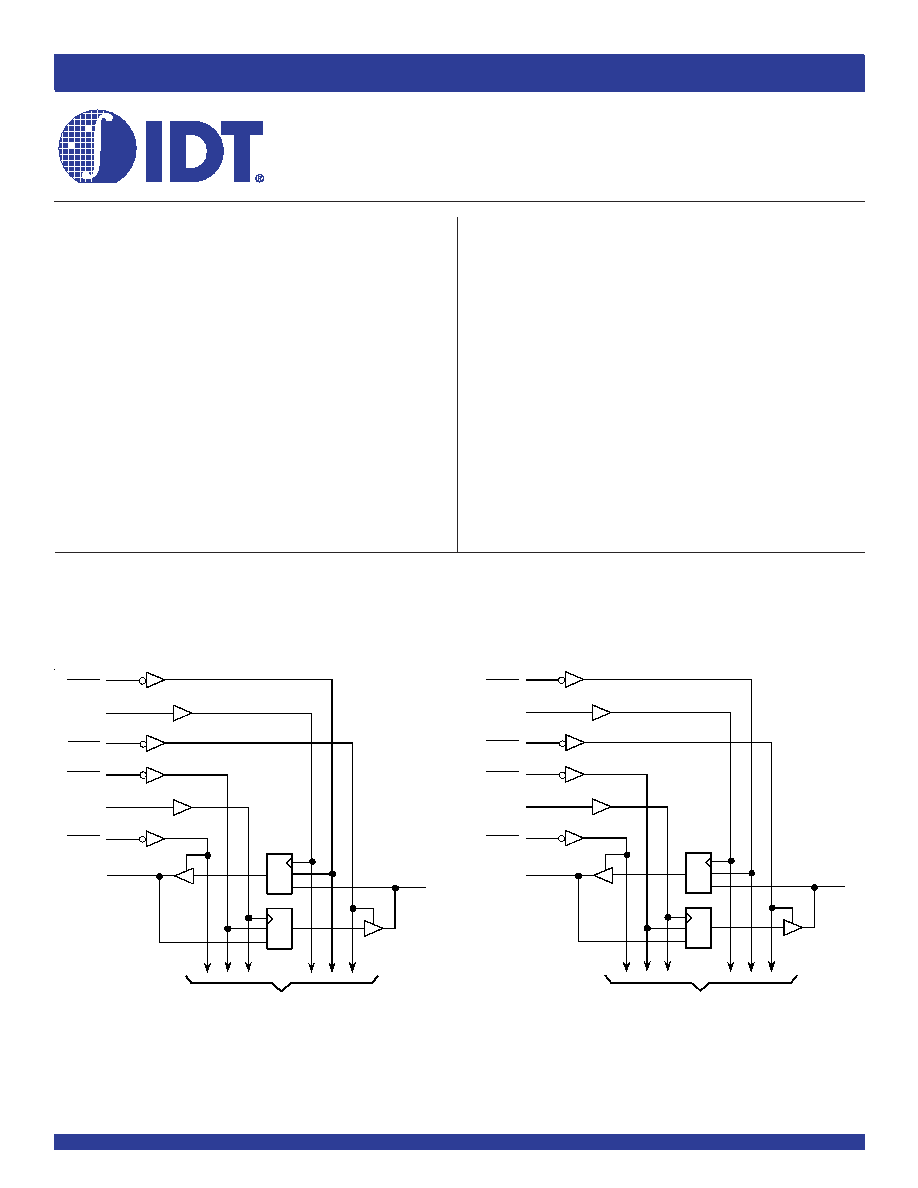

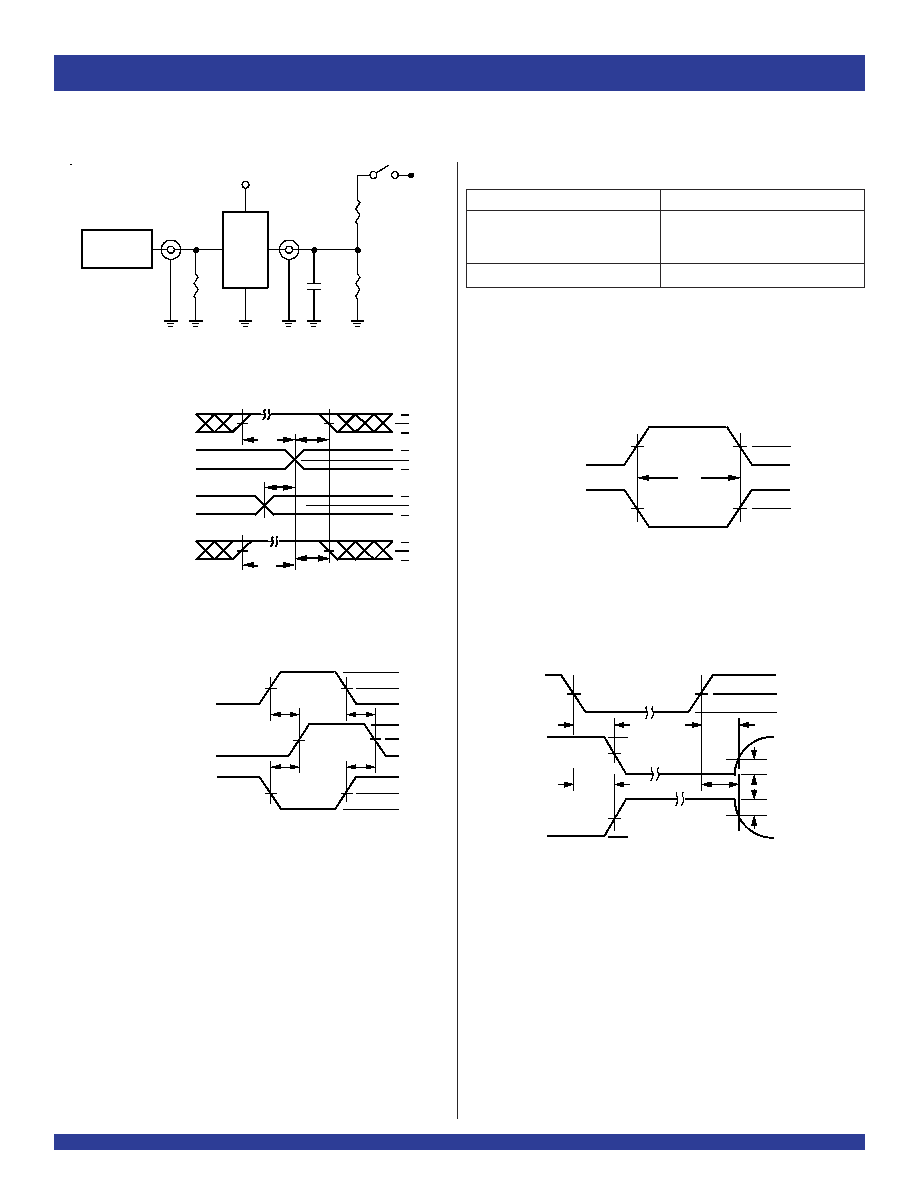

FUNCTIONAL BLOCK DIAGRAM

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

JUNE 2002

INDUSTRIAL TEMPERATURE RANGE

2002 Integrated Device Technology, Inc.

DSC-5442/2

IDT74FCT16952AT/CT/ET

FAST CMOS

16-BIT REGISTERED

TRANSCEIVER

DESCRIPTION:

The FCT16952T 16-bit registered transceiver is built using advanced

dual metal CMOS technology. These high-speed, low-power devices are

organized as two independent 8-bit D-type registered transceivers with

separate input and output control for independent control of data flow in either

direction. For example, the A-to-B Enable (xCEAB) must be low to enter

data from the A port. xCLKAB controls the clocking function. When xCLKAB

toggles from low-to-high, the data present on the A port will be clocked into

the register. xOEAB performs the output enable function on the B port. Data

flow from the B port to A port is similar but requires using xCEBA, xCLKBA,

and xOEBA inputs. Full 16-bit operation is achieved by tying the control pins

of the independent transceivers together.

The FCT16952T is ideally suited for driving high-capacitance loads and

low-impedance backplanes. The output buffers are designed with power off

disable capability allowing "live insertion" of boards when used as backplane

drivers.

2

OE AB

2

CE BA

2

CLKBA

2

OE BA

2

CE AB

2

CLKAB

2

A

1

2

B

1

TO SEVE N OTH ER CHANN ELS

D

C

D

C

CE

C E

1

OE AB

1

CE BA

1

CLKBA

1

OE BA

1

CE AB

1

CLKAB

1

A

1

1

B

1

TO SEVEN OTHE R CHANN ELS

D

C

D

C

C E

C E

54

55

1

3

2

56

5

52

31

30

28

26

27

29

15

42

2

INDUSTRIAL TEMPERATURE RANGE

IDT74FCT16925AT/CT/ET

FAST CMOS 16-BIT REGISTERED TRANSCEIVER

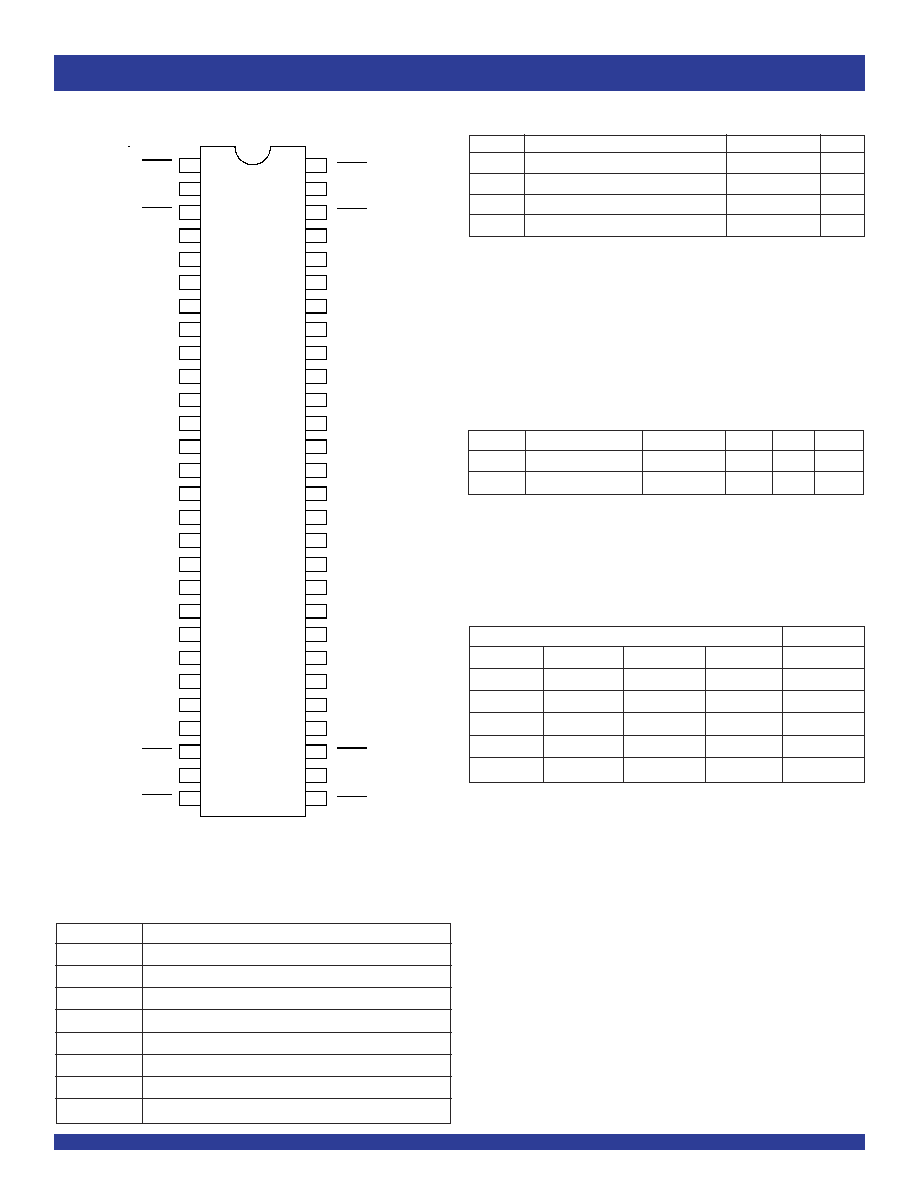

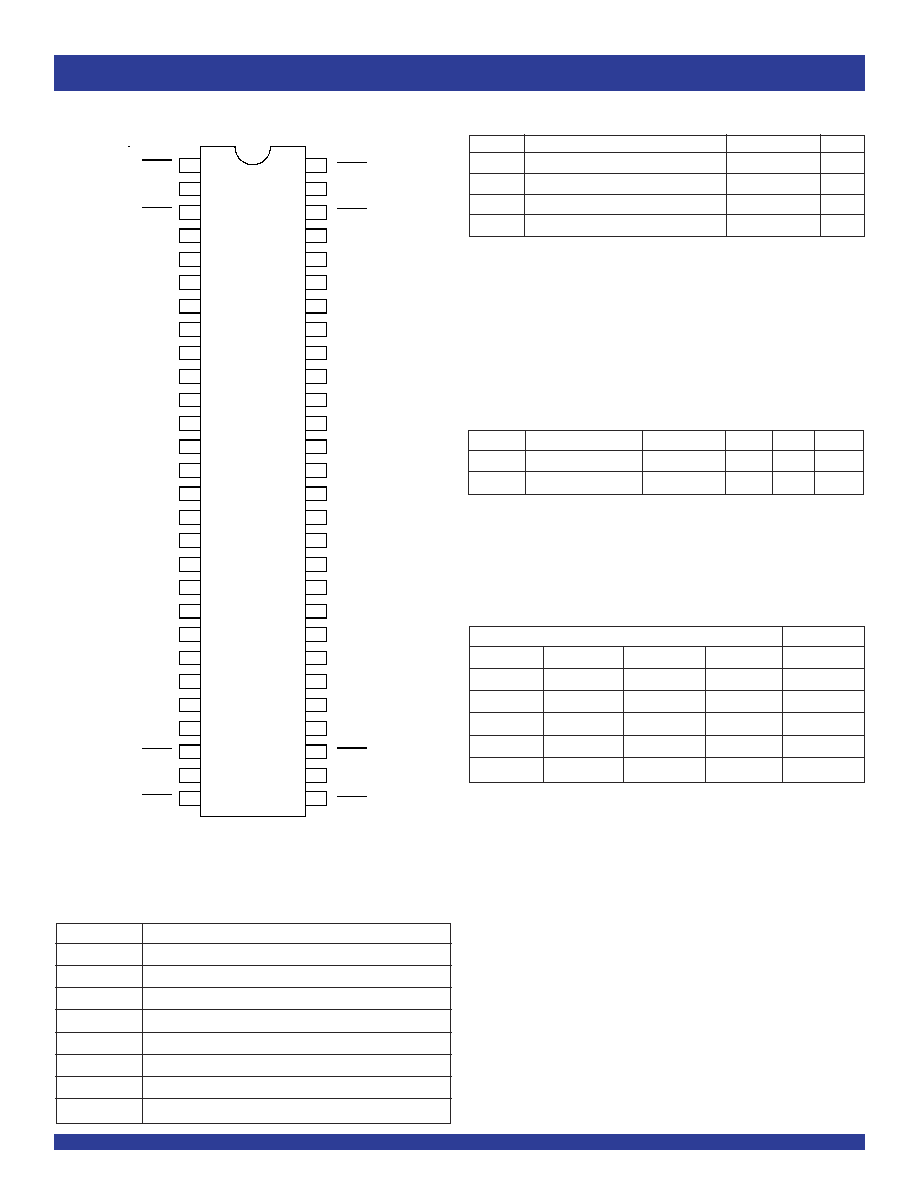

PIN CONFIGURATION

Symbol

Description

Max

Unit

V

TERM(2)

Terminal Voltage with Respect to GND

≠0.5 to +7

V

V

TERM(3)

Terminal Voltage with Respect to GND

≠0.5 to V

CC

+0.5

V

T

STG

Storage Temperature

≠65 to +150

∞C

I

OUT

DC Output Current

≠60 to +120

mA

ABSOLUTE MAXIMUM RATINGS

(1)

NOTES:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause

permanent damage to the device. This is a stress rating only and functional operation

of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability.

2. All device terminals except FCT162XXX Output and I/O terminals.

3. Output and I/O terminals for FCT162XXX.

Symbol

Parameter

(1)

Conditions

Typ.

Max.

Unit

C

IN

Input Capacitance

V

IN

= 0V

3.5

6

pF

C

OUT

Output Capacitance

V

OUT

= 0V

3.5

8

pF

CAPACITANCE

(T

A

= +25∞C, F = 1.0MHz)

NOTE:

1. This parameter is measured at characterization but not tested.

SSOP/ TSSOP

TOP VIEW

1

B

1

1

B

2

GN D

1

B

3

1

B

4

V

CC

1

B

5

1

B

6

1

O EB A

1

B

7

1

B

8

2

B

1

2

B

2

GN D

2

B

3

2

B

4

V

CC

2

B

5

GN D

1

CLKBA

2

B

7

2

B

6

2

B

8

GN D

2

CLKBA

2

O EB A

1

C LK AB

GND

1

A

1

1

A

2

V

C C

1

A

3

1

A

4

GND

1

A

5

1

A

6

1

A

7

1

A

8

GND

2

A

1

2

A

2

V

C C

2

A

3

2

A

5

2

A

4

2

A

7

GND

2

A

8

2

C LK AB

2

A

6

1

OEAB

1

C EAB

2

OEAB

2

C EAB

2

CE BA

1

CE BA

47

37

38

39

40

41

42

43

44

45

46

33

34

35

36

56

55

49

50

51

52

53

54

48

1

2

3

4

5

6

7

8

9

10

12

13

14

15

16

17

18

19

20

11

21

22

23

24

29

30

31

32

25

26

27

28

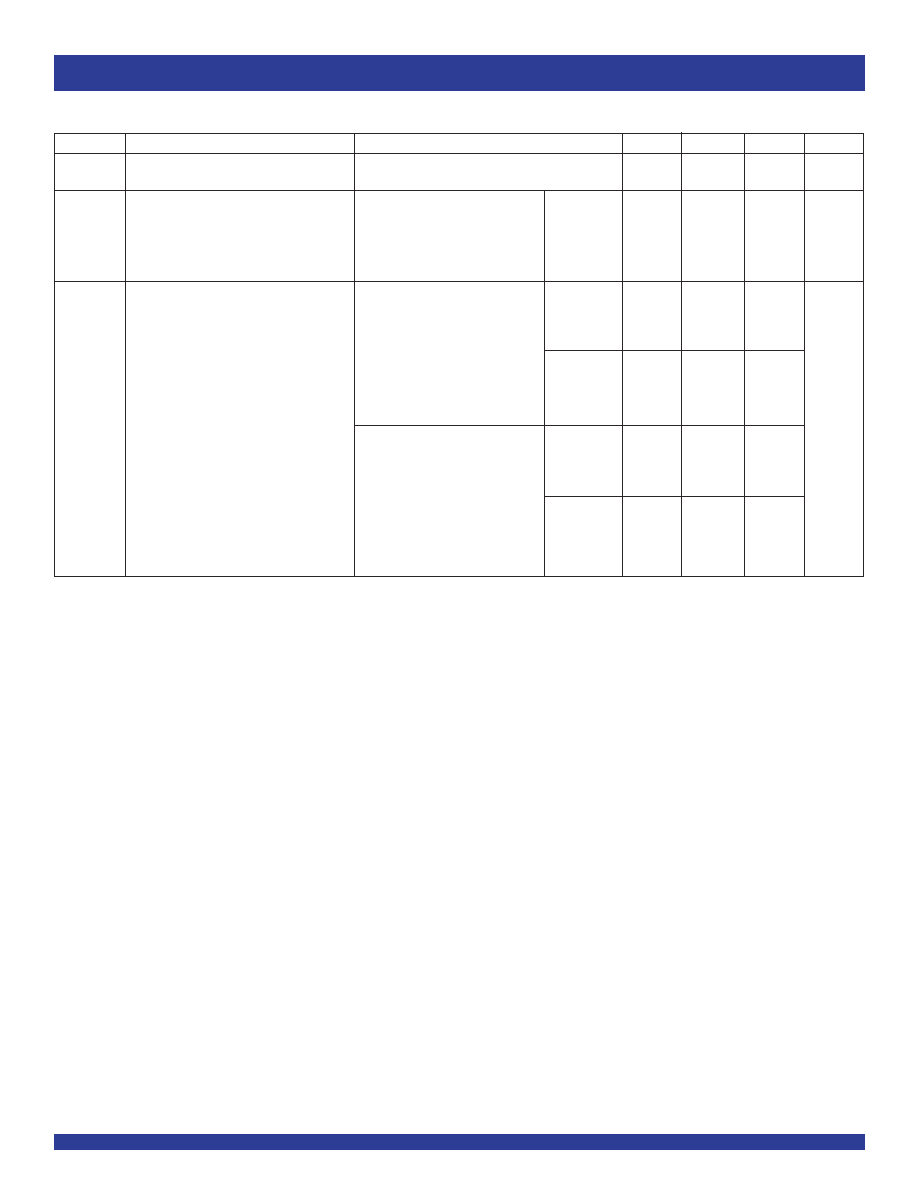

FUNCTION TABLE

(1,3)

Inputs

Outputs

xCEAB

xCLKAB

xOEAB

xAx

xBx

H

X

L

X

B

(2)

X

L

L

X

B

(2)

L

L

L

L

L

L

H

H

X

X

H

X

Z

NOTES:

1. A-to-B data flow is shown: B-to-A data flow is similar but uses xCEBA, xCLKBA, and

xOEBA.

2. Level of B before the indicated steady-state input conditions were established.

3. H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care

= LOW-to-HIGH Transition

Z = High-impedance

PIN DESCRIPTION

Pin Names

Description

xOEAB

A-to-B Output Enable Input (Active LOW)

xOEBA

B-to-A Output Enable Input (Active LOW)

xCEAB

A-to-B Clock Enable Input (Active LOW)

xCEBA

B-to-A Clock Enable Input (Active LOW)

xCLKAB

A-to-B Clock Input

xCLKBA

B-to-A Clock Input

xAx

A-to-B Data Inputs or B-to-A 3-State Outputs

xBx

B-to-A Data Inputs or A-to-B 3-State Outputs

3

IDT74FCT16925AT/CT/ET

FAST CMOS 16-BIT REGISTERED TRANSCEIVER

INDUSTRIAL TEMPERATURE RANGE

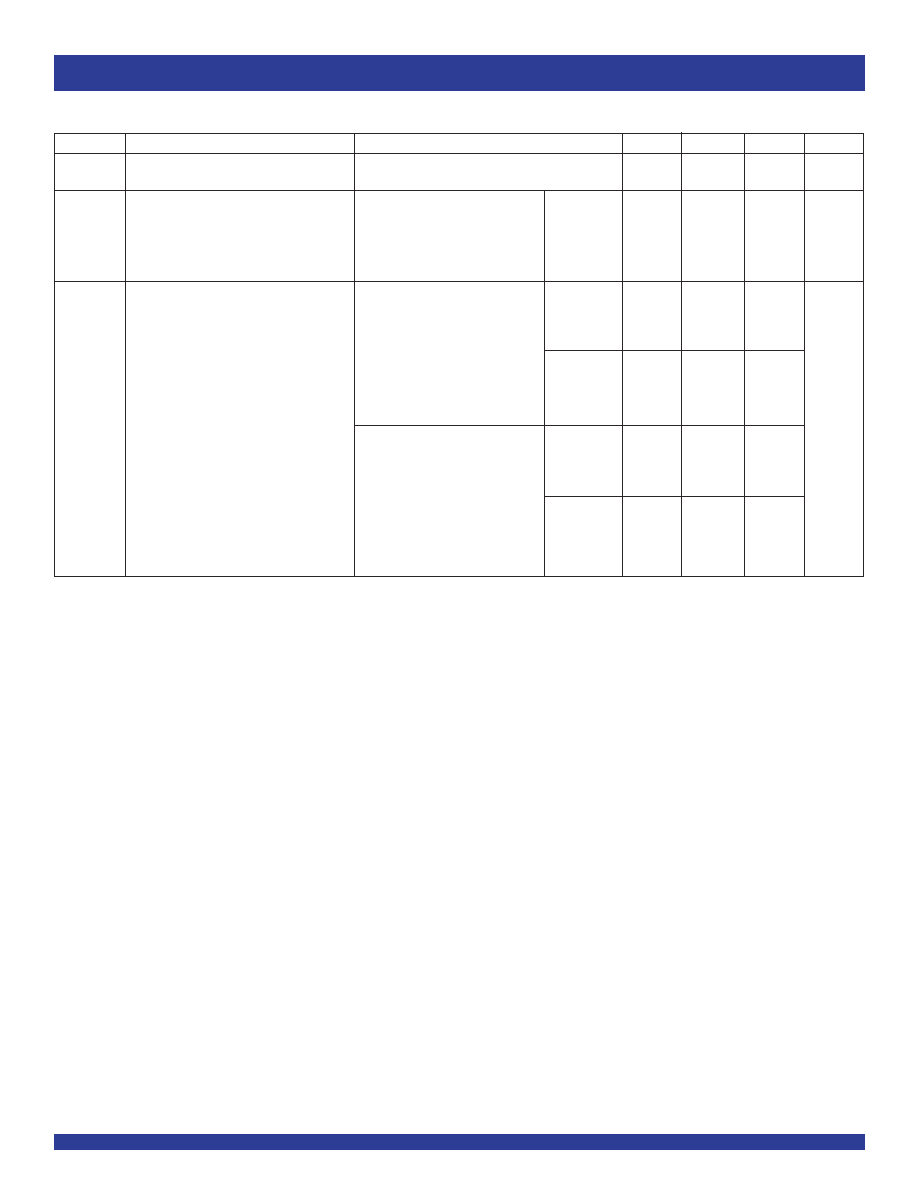

Symbol

Parameter

Test Conditions

(1)

Min.

Typ.

(2)

Max.

Unit

V

IH

Input HIGH Level

Guaranteed Logic HIGH Level

2

--

--

V

V

IL

Input LOW Level

Guaranteed Logic LOW Level

--

--

0.8

V

I

IH

Input HIGH Current (Input pins)

(5)

V

CC

= Max.

V

I

= V

CC

--

--

±1

µA

Input HIGH Current (I/O pins)

(5)

--

--

±1

I

IL

Input LOW Current (Input pins)

(5)

V

I

= GND

--

--

±1

Input LOW Current (I/O pins)

(5)

--

--

±1

I

OZH

High Impedance Output Current

V

CC

= Max.

V

O

= 2.7V

--

--

±1

µA

I

OZL

(3-State Output pins)

(5)

V

O

= 0.5V

--

--

±1

V

IK

Clamp Diode Voltage

V

CC

= Min., I

IN

= ≠18mA

--

≠0.7

≠1.2

V

I

OS

Short Circuit Current

V

CC

= Max., V

O

= GND

(3)

≠80

≠140

≠250

mA

V

H

Input Hysteresis

--

--

100

--

mV

I

CCL

Quiescent Power Supply Current

V

CC

= Max.

--

5

500

µA

I

CCH

V

IN

= GND or V

CC

I

CCZ

DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified:

Industrial: T

A

= ≠40∞C to +85∞C, V

CC

= 5.0V ±10%

NOTES:

1. For conditions shown as Min. or Max., use appropriate value specified under Electrical Characteristics for the applicable device type.

2. Typical values are at V

CC

= 5.0V, +25∞C ambient.

3. Not more than one output should be shorted at one time. Duration of the test should not exceed one second.

4. Duration of the condition can not exceed one second.

5. The test limit for this parameter is ±5

µA at T

A

= -55∞C.

Symbol

Parameter

Test Conditions

(1)

Min.

Typ.

(2)

Max.

Unit

I

O

Output Drive Current

V

CC

= Max., V

O

= 2.5V

(3)

≠50

--

≠180

mA

V

OH

Output HIGH Voltage

V

CC

= Min.

I

OH

= ≠3mA

2.5

3.5

--

V

IN

= V

IH

or V

IL

I

OH

= ≠15mA

2.4

3.5

--

V

I

OH

= ≠32mA

(4)

2

3

--

V

OH

Output LOW Voltage

V

CC

= Min.

I

OL

= 64mA

--

0.2

0.55

V

V

IN

= V

IH

or V

IL

I

OFF

Input/Output Power Off Leakage

(5)

V

CC

= 0V, V

IN

or V

O

4.5V

--

--

±1

µA

OUTPUT DRIVE CHARACTERISTICS

4

INDUSTRIAL TEMPERATURE RANGE

IDT74FCT16925AT/CT/ET

FAST CMOS 16-BIT REGISTERED TRANSCEIVER

Symbol

Parameter

Test Conditions

(1)

Min.

Typ.

(2)

Max.

Unit

I

CC

Quiescent Power Supply

V

CC

= Max.

--

0.5

1.5

mA

Current TTL Inputs HIGH

V

IN

= 3.4V

(3)

I

CCD

Dynamic Power Supply Current

(4)

V

CC

= Max.,

V

IN

= V

CC

--

75

120

µA/

Outputs Open

V

IN

= GND

MHz

xOEAB = xOEBA = GND

One Input Toggling

50% Duty Cycle

I

C

Total Power Supply Current

(6)

V

CC

= Max., Outputs Open

V

IN

= V

CC

--

0.8

1.7

mA

f

CP

= 10MHz (xCLKAB)

V

IN

= GND

50% Duty Cycle

xOEAB = xCEAB = GND

xOEBA = V

CC

V

IN

= 3.4V

--

1.3

3.2

fi = 5MHz

V

IN

= GND

50% Duty Cycle

One Bit Toggling

V

CC

= Max., Outputs Open

V

IN

= V

CC

--

3.8

6.5

(5)

f

CP

= 10MHz (xCLKAB)

V

IN

= GND

50% Duty Cycle

xOEAB = xCEAB = GND

xOEBA = V

CC

V

IN

= 3.4V

--

8.3

20

(5)

fi = 2.5MHz

V

IN

= GND

50% Duty Cycle

Sixteen Bits Toggling

POWER SUPPLY CHARACTERISTICS

NOTES:

1. For conditions shown as Min. or Max., use appropriate value specified under Electrical Characteristics for the applicable device type.

2. Typical values are at V

CC

= 5.0V, +25∞C ambient.

3. Per TTL driven input (V

IN

= 3.4V). All other inputs at V

CC

or GND.

4. This parameter is not directly testable, but is derived for use in Total Power Supply Calculations.

5. Values for these conditions are examples of the I

CC

formula. These limits are guaranteed but not tested.

6. I

C

= I

QUIESCENT

+ I

INPUTS

+ I

DYNAMIC

I

C

= I

CC

+

I

CC

D

H

N

T

+ I

CCD

(f

CP

N

CP

/2 + fiNi)

I

CC

= Quiescent Current (I

CCL

, I

CCH

and I

CCZ

)

I

CC

= Power Supply Current for a TTL High Input (V

IN

= 3.4V)

D

H

= Duty Cycle for TTL Inputs High

N

T

= Number of TTL Inputs at D

H

I

CCD

= Dynamic Current Caused by an Input Transition Pair (HLH or LHL)

f

CP

= Clock Frequency for Register Devices (Zero for Non-Register Devices)

N

CP

= Number of Clock Inputs at f

CP

f

i

= Input Frequency

N

i

= Number of Inputs at f

i

5

IDT74FCT16925AT/CT/ET

FAST CMOS 16-BIT REGISTERED TRANSCEIVER

INDUSTRIAL TEMPERATURE RANGE

NOTES:

1. See test circuit and waveforms.

2. Minimum limits are guaranteed but not tested on Propagation Delays.

3. This limit is guaranteed but not tested.

4. Skew between any two outputs, of the same package, switching in the same direction. This parameter is guaranteed by design.

SWITCHING CHARACTERISTICS OVER OPERATING RANGE - INDUSTRIAL

FCT16952AT FCT16952CT FCT16952ET

Symbol

Parameter

Condition

(1)

Min

.

(2)

Max

.

Min

.

(2)

Max

.

Min

.

(2)

Max

.

Unit

t

PLH

Propagation Delay

C

L

= 50pF

2

10

2

6.3

1.5

3.7

ns

t

PHL

xCLKAB, xCLKBA to xBx, xAx

R

L

= 500

t

PZH

Output EnableTime

1.5

10.5

1.5

7

1.5

4.4

ns

t

PZL

xOEBA, xOEAB to xAx, xBx

t

PHZ

Output Disable Time

1.5

10

1.5

6.5

1.5

3.6

ns

t

PLZ

xOEBA, xOEAB to xAx, xBx

t

SU

Set-up Time, HIGH or LOW

2.5

--

2.5

--

1.5

--

ns

xAx, xBx to xCLKAB, xCLKBA

t

H

Hold Time, HIGH or LOW

2

--

1.5

--

0

--

ns

xAx, xBx to xCLKAB, xCLKBA

t

SU

Set-up Time, HIGH or LOW

3

--

3

--

2

--

ns

xCEBA, xCEAB, to xCLKAB, xCLKBA

t

H

Hold Time, HIGH or LOW

2

--

2

--

0

--

ns

xCEBA, xCEAB, to xCLKAB, xCLKBA

t

W

Pulse Width HIGH or LOW, xCLKAB or xCLKBA

(3)

3

--

3

--

3

--

ns

t

SK

(o)

Output Skew

(4)

--

0.5

--

0.5

--

0.5

ns

6

INDUSTRIAL TEMPERATURE RANGE

IDT74FCT16925AT/CT/ET

FAST CMOS 16-BIT REGISTERED TRANSCEIVER

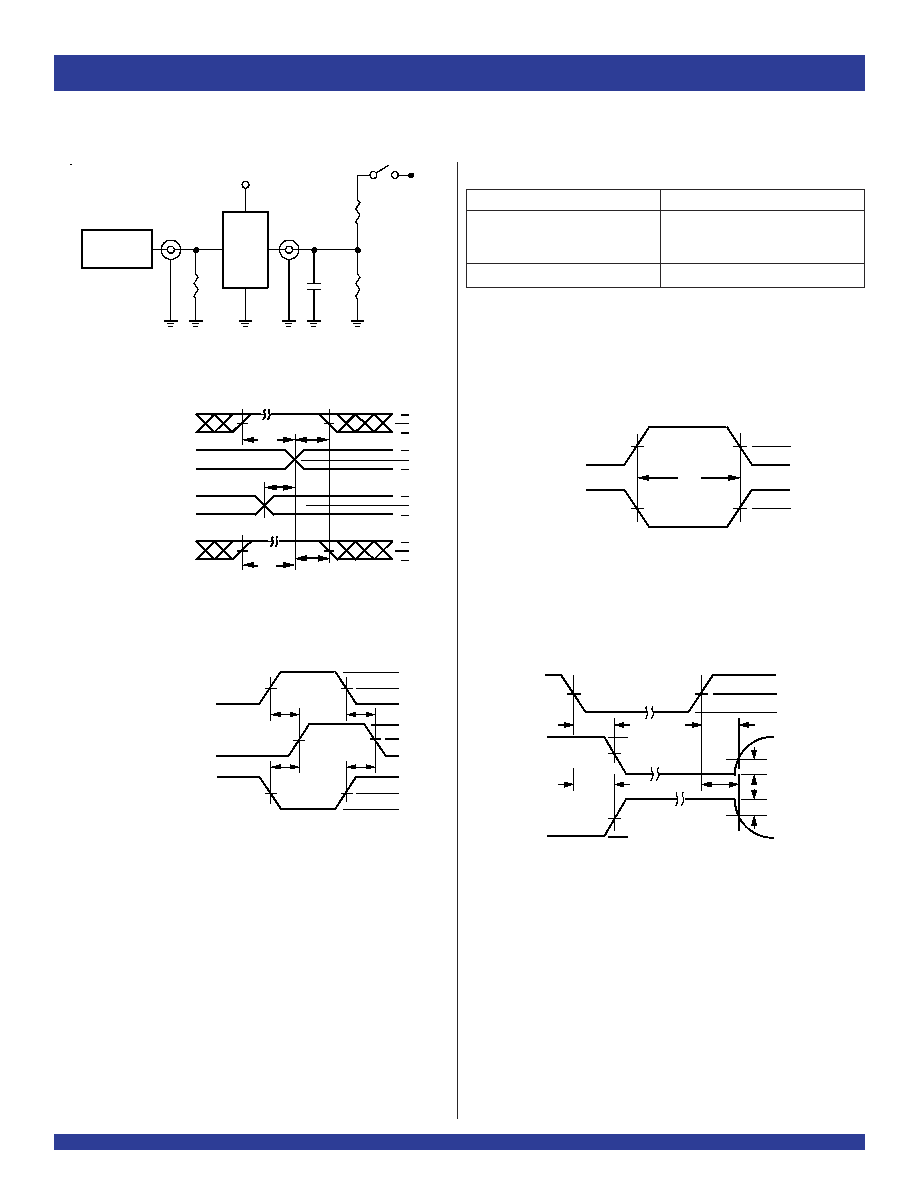

Pulse

Generator

R

T

D.U.T.

V

CC

V

IN

C

L

V

OUT

50pF

500

500

7.0V

3V

1.5V

0V

3V

1.5V

0V

3V

1.5V

0V

3V

1.5V

0V

D ATA

INPUT

TIM IN G

INPUT

ASYNC HR ONOUS C ONTROL

PRES ET

CLEA R

ETC .

SYNCHR ON OUS CONTROL

t

SU

t

H

t

R EM

t

SU

t

H

PRES ET

CLEA R

CLOCK ENABLE

ETC .

HIGH-LOW -H IGH

PU LSE

LOW -HIGH-LOW

PU LSE

t

W

1.5V

1.5V

SAM E PHASE

INPUT TRAN SITION

3V

1.5V

0V

1.5V

V

O H

t

PLH

OU TPU T

OPPOSITE P HASE

INPUT TRAN SITION

3V

1.5V

0V

t

PL H

t

PH L

t

PH L

V

O L

CONTROL

IN PU T

3V

1.5V

0V

3.5V

0V

OUTPU T

NORM ALLY

LOW

OUTPU T

NORM ALLY

H IGH

SW ITCH

C LOSE D

SW ITC H

OPEN

V

OL

0.3V

0.3V

t

PLZ

t

PZL

t

PZH

t

PHZ

3.5V

0V

1.5V

1.5V

ENABLE

D ISABLE

V

OH

TEST CIRCUITS AND WAVEFORMS

Propagation Delay

Test Circuits for All Outputs

Enable and Disable Times

Set-up, Hold, and Release Times

Pulse Width

NOTES:

1. Diagram shown for input Control Enable-LOW and input Control Disable-HIGH.

2. Pulse Generator for All Pulses: Rate

1.0MHz; t

F

2.5ns; t

R

2.5ns.

Test

Switch

Open Drain

Disable Low

Closed

Enable Low

All Other Tests

Open

SWITCH POSITION

DEFINITIONS:

C

L

= Load capacitance: includes jig and probe capacitance.

R

T

= Termination resistance: should be equal to Z

OUT

of the Pulse Generator.

7

IDT74FCT16925AT/CT/ET

FAST CMOS 16-BIT REGISTERED TRANSCEIVER

INDUSTRIAL TEMPERATURE RANGE

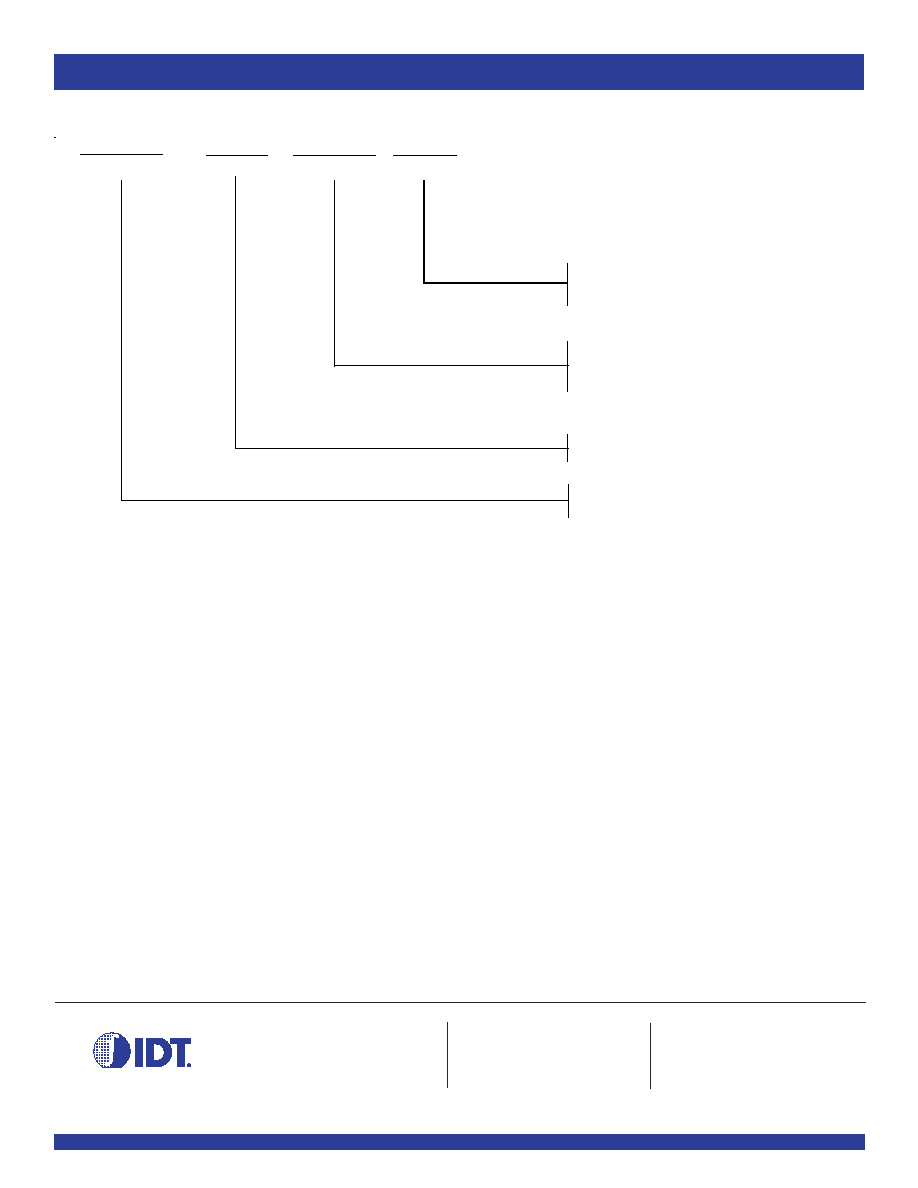

ORDERING INFORMATION

IDT XX

Temp. Range

XXXX

Device Type

XX

Package

PV

PA

Shrink Small Outline Package

Thin Shrink Small Outline Package

74

≠ 40∞C to +85∞C

16

Double-Density, 5 Volt, High Drive

FCT

XXX

Family

952AT

952CT

952ET

16-Bit Registered Transceiver

CORPORATE HEADQUARTERS

for SALES:

for Tech Support:

2975 Stender Way

800-345-7015 or 408-727-6116

logichelp@idt.com

Santa Clara, CA 95054

fax: 408-492-8674

(408) 654-6459

www.idt.com

6/24/2002 Updated as per PDNs Logic-00-07 and Logic-01-04

DATA SHEET DOCUMENT HISTORY