INDUSTRIAL TEMPERATURE RANGE

IDT74FCT2373AT/CT

FAST CMOS OCTAL TRANSPARENT LATCH

1

JUNE 2002

INDUSTRIAL TEMPERATURE RANGE

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

© 2002 Integrated Device Technology, Inc.

DSC-5497/2

FEATURES:

∑ A and C grades

∑ Low input and output leakage

1µA (max.)

∑ CMOS power levels

∑ True TTL input and output compatibility:

≠ V

OH

= 3.3V (typ.)

≠ V

OL

= 0.3V (typ.)

∑ Meets or exceeds JEDEC standard 18 specifications

∑ Resistor outputs -15mA I

OH

, 12mA I

OL

∑ Reduced system switching noise

∑ Available in SOIC, QSOP, and TSSOP packages

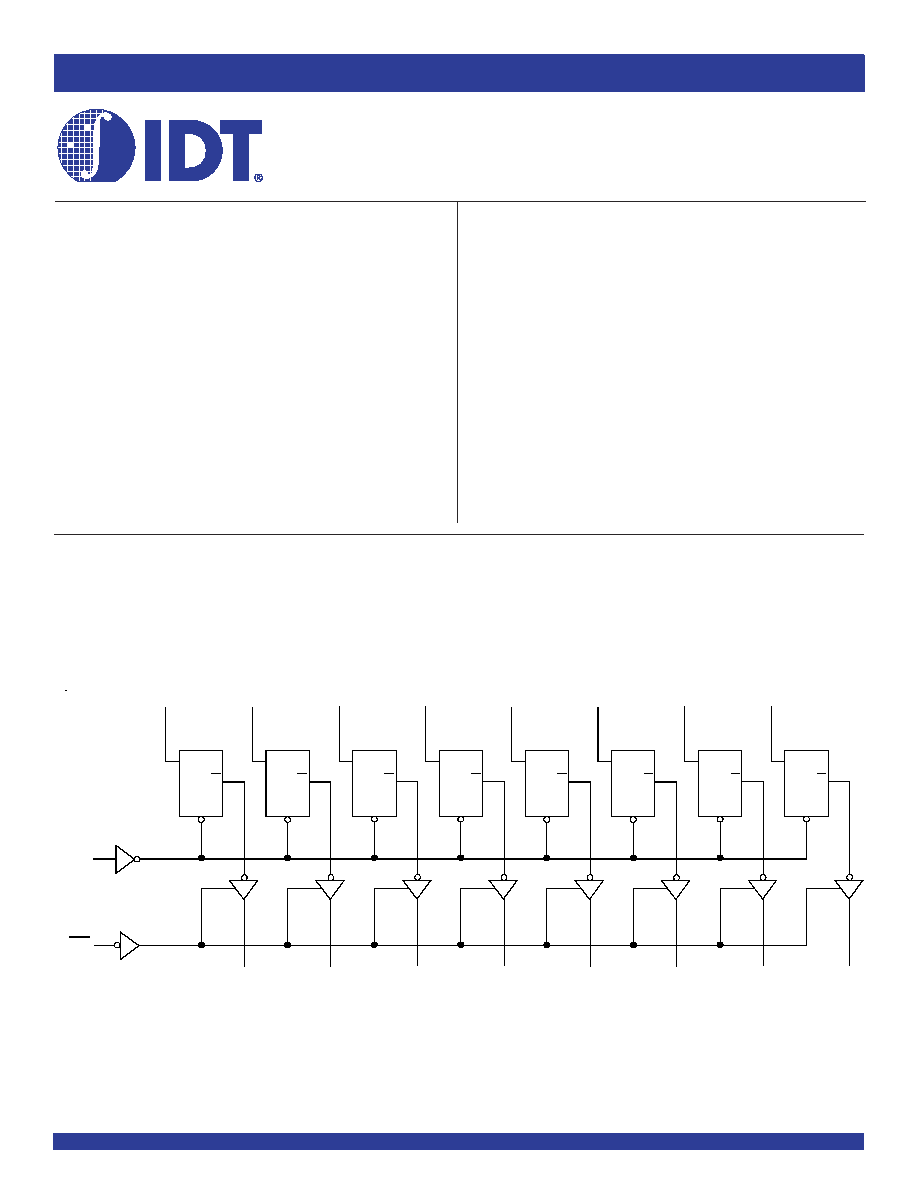

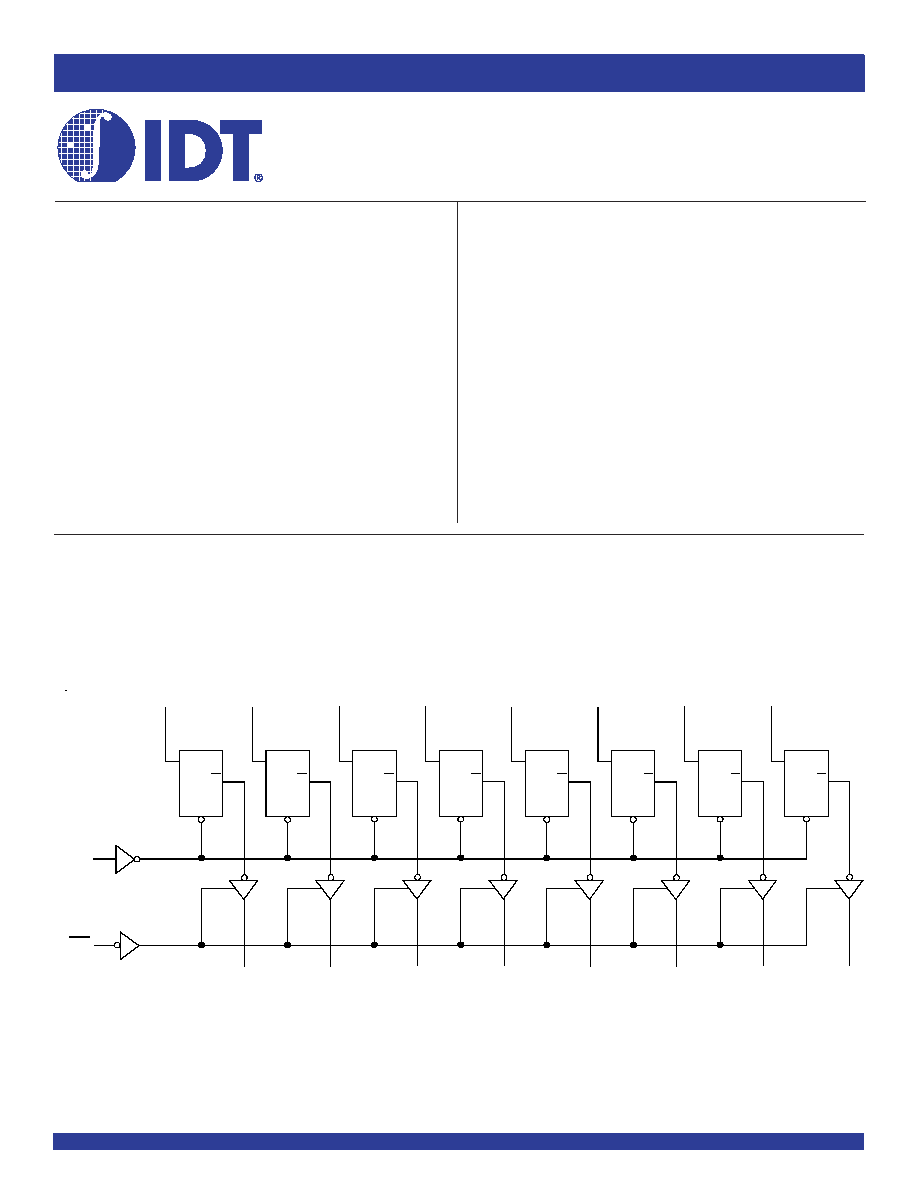

FUNCTIONAL BLOCK DIAGRAM

IDT74FCT2373AT/CT

FAST CMOS OCTAL

TRANSPARENT LATCH

DESCRIPTION:

The FCT2373T is an octal transparent latch built using an advanced dual

metal CMOS technology. These octal latches have 3-state outputs and are

intended for bus oriented applications. The flip-flops appear transparent to

the data when Latch Enable (LE) is high. When LE is low, the data that meets

the set-up time is latched. Data appears on the bus when the Output Enable

(OE) is low. When OE is high, the bus output is in the high-impedance state.

The FCT2373T has balanced drive outputs with current limiting resis-

tors. This offers low ground bounce, minimal undershoot and controlled

output fall times-reducing the need for external series terminating resistors.

The FCT2373T parts are plug-in replacements for FCT373T parts.

LE

D

G

O

O

0

D

0

D

G

O

O

1

D

1

D

G

O

O

2

D

2

D

G

O

O

3

D

3

D

G

O

O

4

D

4

D

G

O

O

5

D

5

D

G

O

O

6

D

6

D

G

O

O

7

D

7

OE

INDUSTRIAL TEMPERATURE RANGE

2

IDT74FCT2373AT/CT

FAST CMOS OCTAL TRANSPARENT LATCH

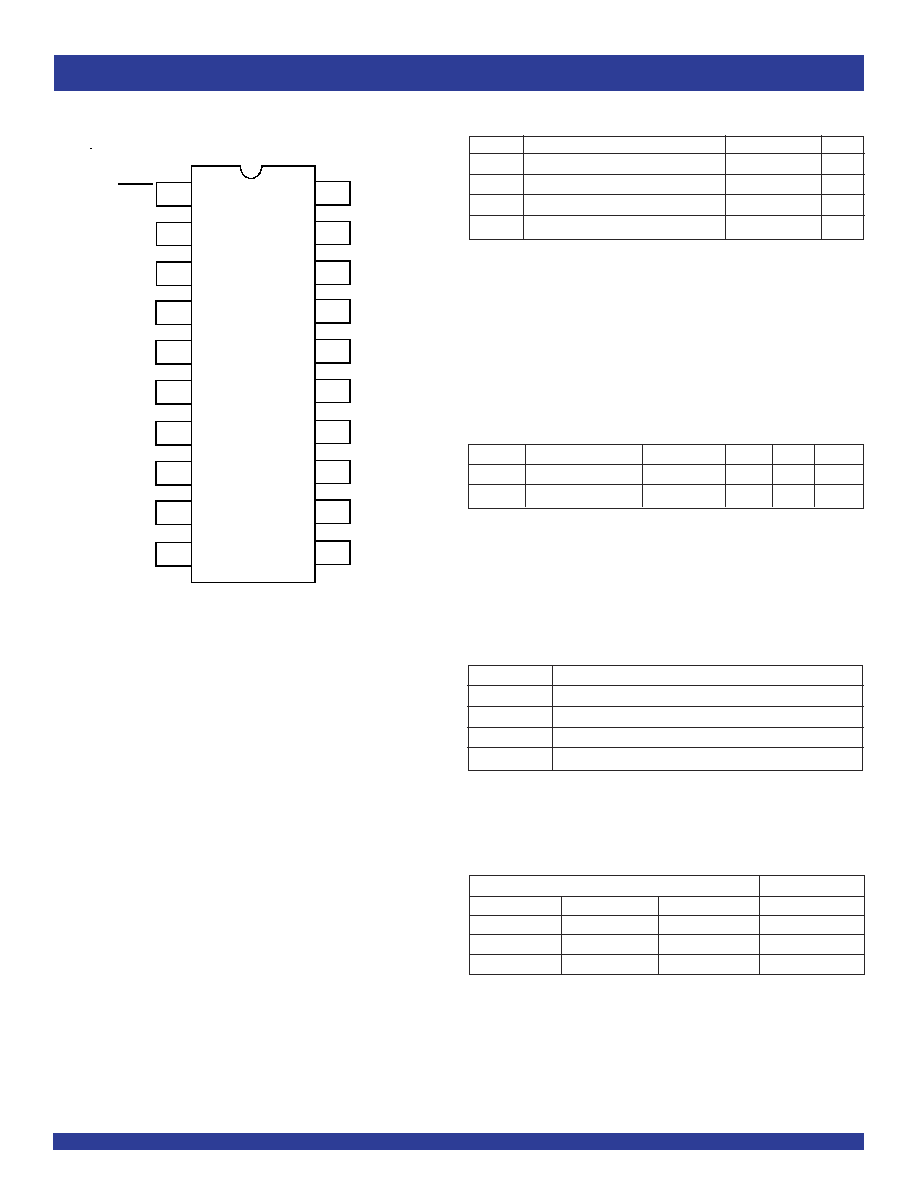

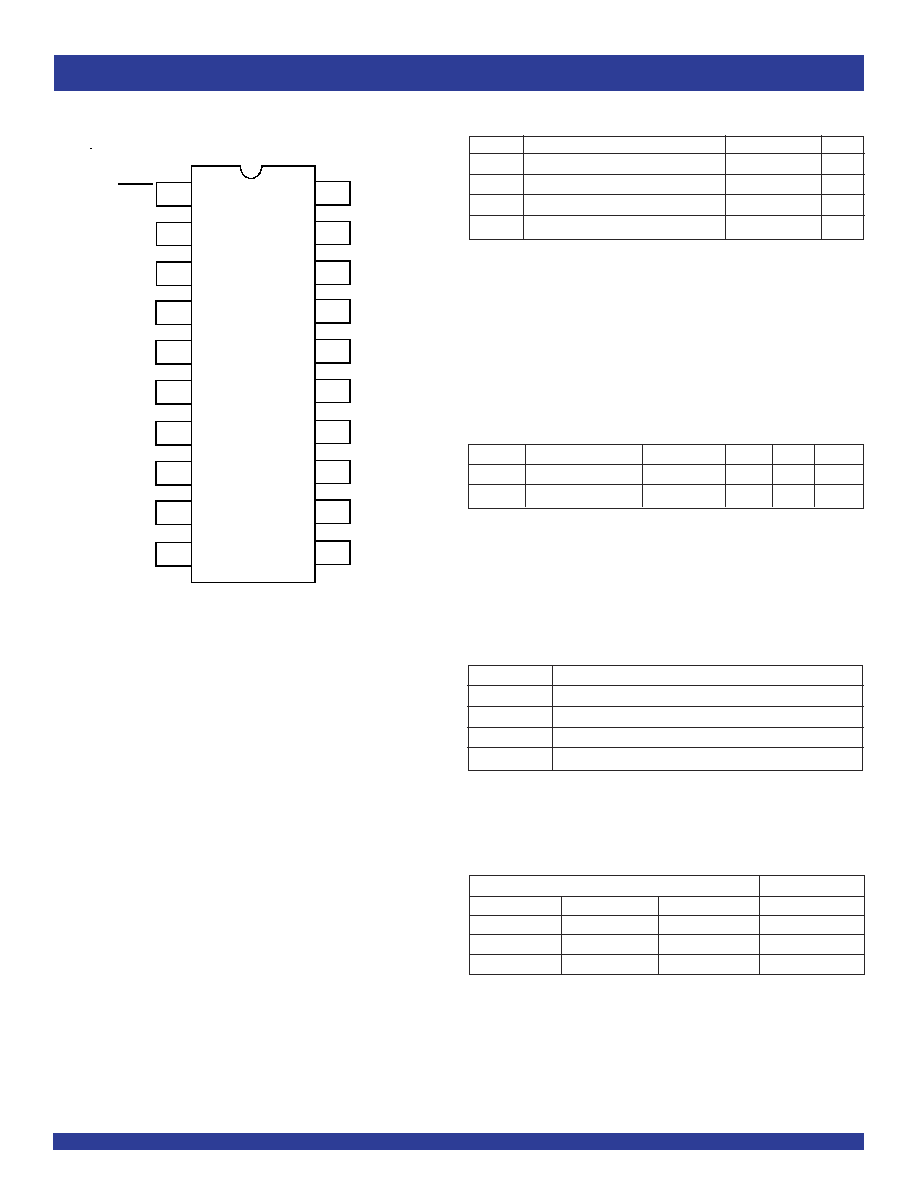

PIN CONFIGURATION

Pin Names

Description

Dx

Data Inputs

LE

Latch Enable Input (Active HIGH)

OE

Output Enable Input (Active LOW)

Ox

3-State Outputs

PIN DESCRIPTION

NOTE:

1. H = HIGH Voltage Level

X = Don't Care

L = LOW Voltage Level

Z = High Impedance

SOIC/ QSOP/ TSSOP

TOP VIEW

FUNCTION TABLE

(1)

Inputs

Outputs

Dx

LE

OE

Ox

L

H

L

L

H

H

L

H

X

X

X

Z

Symbol

Description

Max

Unit

V

TERM

(2)

Terminal Voltage with Respect to GND

≠0.5 to +7

V

V

TERM

(3)

Terminal Voltage with Respect to GND

≠0.5 to V

CC

+0.5

V

T

STG

Storage Temperature

≠65 to +150

∞C

I

OUT

DC Output Current

≠60 to +120

mA

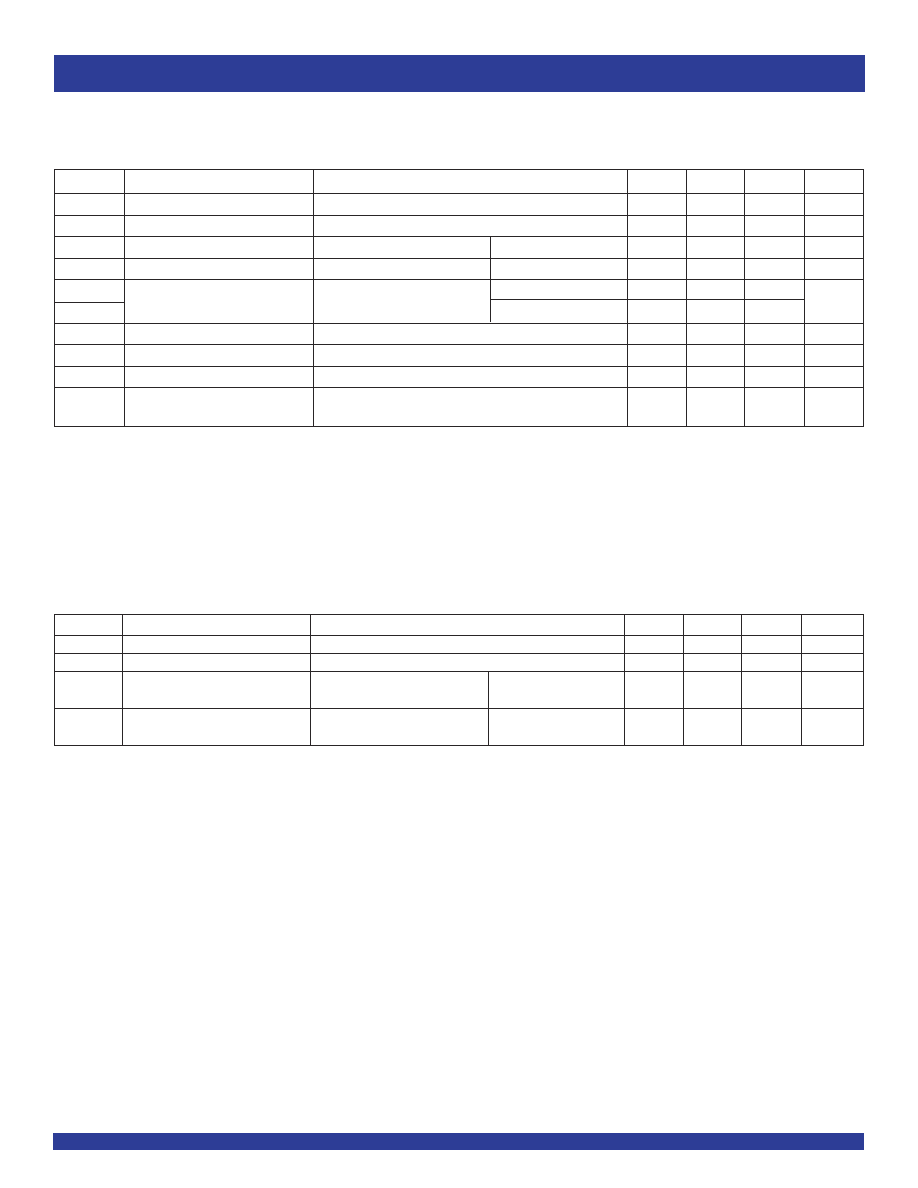

ABSOLUTE MAXIMUM RATINGS

(1)

NOTES:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause

permanent damage to the device. This is a stress rating only and functional operation

of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability. No terminal voltage may exceed

Vcc by +0.5V unless otherwise noted.

2. Inputs and Vcc terminals only.

3. Output and I/O terminals only.

Symbol

Parameter

(1)

Conditions

Typ.

Max.

Unit

C

IN

Input Capacitance

V

IN

= 0V

6

10

pF

C

OUT

Output Capacitance

V

OUT

= 0V

8

12

pF

CAPACITANCE

(T

A

= +25∞C, F = 1.0MHz)

NOTE:

1. This parameter is measured at characterization but not tested.

2

3

1

16

15

14

11

19

18

20

17

13

12

5

6

7

4

8

9

10

D

1

O

0

D

0

V

CC

O

1

D

3

O

2

D

2

O

3

GND

O

7

O

6

D

7

D

6

O

5

O

4

D

5

D

4

LE

OE

INDUSTRIAL TEMPERATURE RANGE

IDT74FCT2373AT/CT

FAST CMOS OCTAL TRANSPARENT LATCH

3

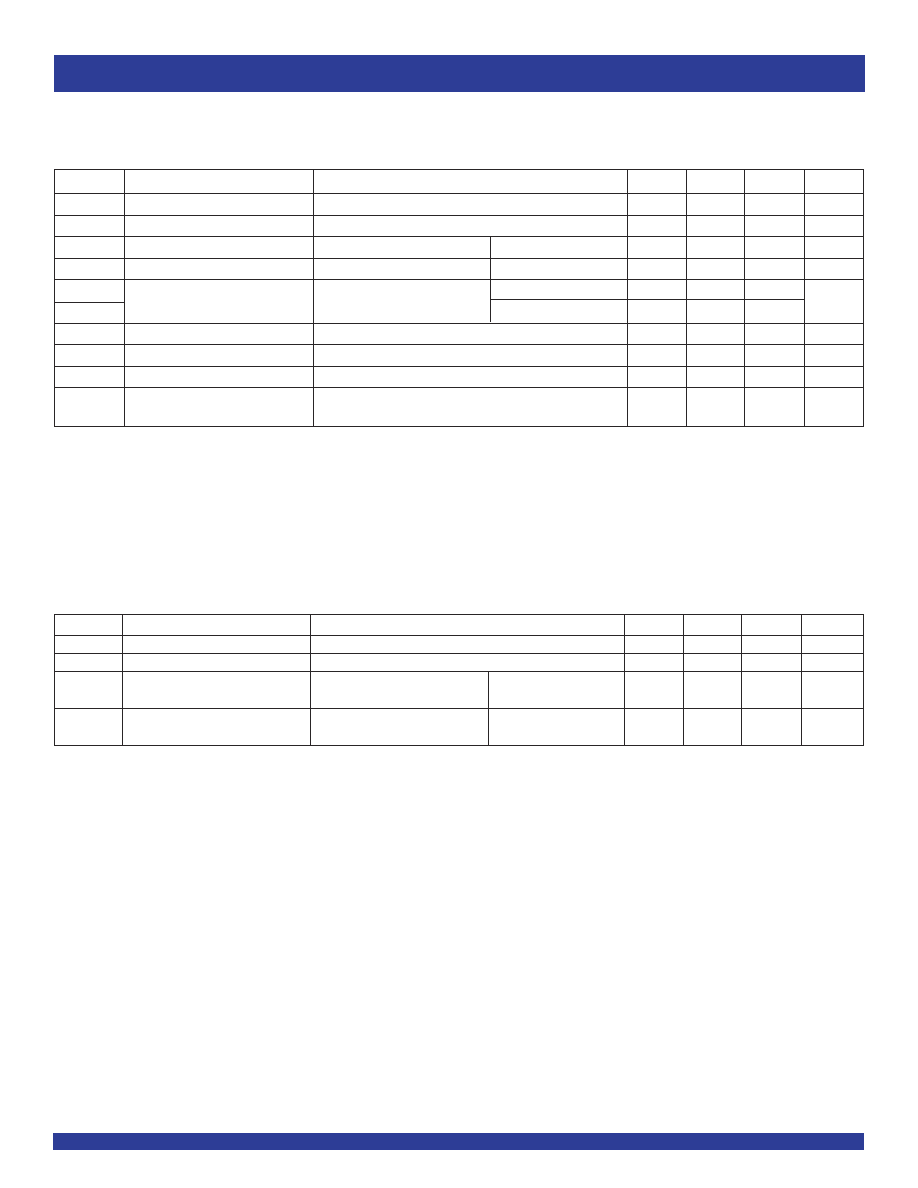

Symbol

Parameter

Test Conditions

(1)

Min.

Typ.

(2)

Max.

Unit

V

IH

Input HIGH Level

Guaranteed Logic HIGH Level

2

--

--

V

V

IL

Input LOW Level

Guaranteed Logic LOW Level

--

--

0.8

V

I

IH

Input HIGH Current

(4)

V

CC

= Max.

V

I

= 2.7V

--

--

±1

µA

I

IL

Input LOW Current

(4)

V

CC

= Max.

V

I

= 0.5V

--

--

±1

µA

I

OZH

High Impedance Output Current

V

CC

= Max.

V

I

= 2.7V

--

--

±1

µA

I

OZL

(3-State Output Pins)

(4)

V

I

= 0.5V

--

--

±1

I

I

Input HIGH Current

(4)

V

CC

= Max., V

I

= V

CC

(Max.)

--

--

±1

µA

V

IK

Clamp Diode Voltage

V

CC

= Min., I

IN

= ≠18mA

--

≠0.7

≠1.2

V

V

H

Input Hysteresis

--

--

200

--

mV

I

CC

Quiescent Power Supply Current

V

CC

= Max.

--

0.01

1

mA

V

IN

= GND or V

CC

DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified:

Industrial: T

A

= ≠40∞C to +85∞C, V

CC

= 5.0V ±5%

NOTES:

1. For conditions shown as Min. or Max., use appropriate value specified under Electrical Characteristics for the applicable device type.

2. Typical values are at V

CC

= 5.0V, +25∞C ambient.

3. Not more than one output should be tested at one time. Duration of the test should not exceed one second.

4. The test limit for this parameter is ±5

µA at TA = -55∞C.

Symbol

Parameter

Test Conditions

(1)

Min.

Typ.

(2)

Max.

Unit

I

ODL

Output LOW Current

V

CC

= 5V, V

IN

= V

IH

or V

IL

, V

OUT

= 1.5V

(3)

16

48

--

mA

I

ODH

Output HIGH Current

V

CC

= 5V, V

IN

= V

IH

or V

IL

, V

OUT

= 1.5V

(3)

-16

-48

--

mA

V

OH

Output HIGH Voltage

V

CC

= Min

I

OH

= ≠15mA

2.4

3.3

--

V

V

IN

= V

IH

or V

IL

V

OL

Output LOW Voltage

V

CC

= Min

I

OL

= 12mA

--

0.3

0.5

V

V

IN

= V

IH

or V

IL

OUTPUT DRIVE CHARACTERISTICS

INDUSTRIAL TEMPERATURE RANGE

4

IDT74FCT2373AT/CT

FAST CMOS OCTAL TRANSPARENT LATCH

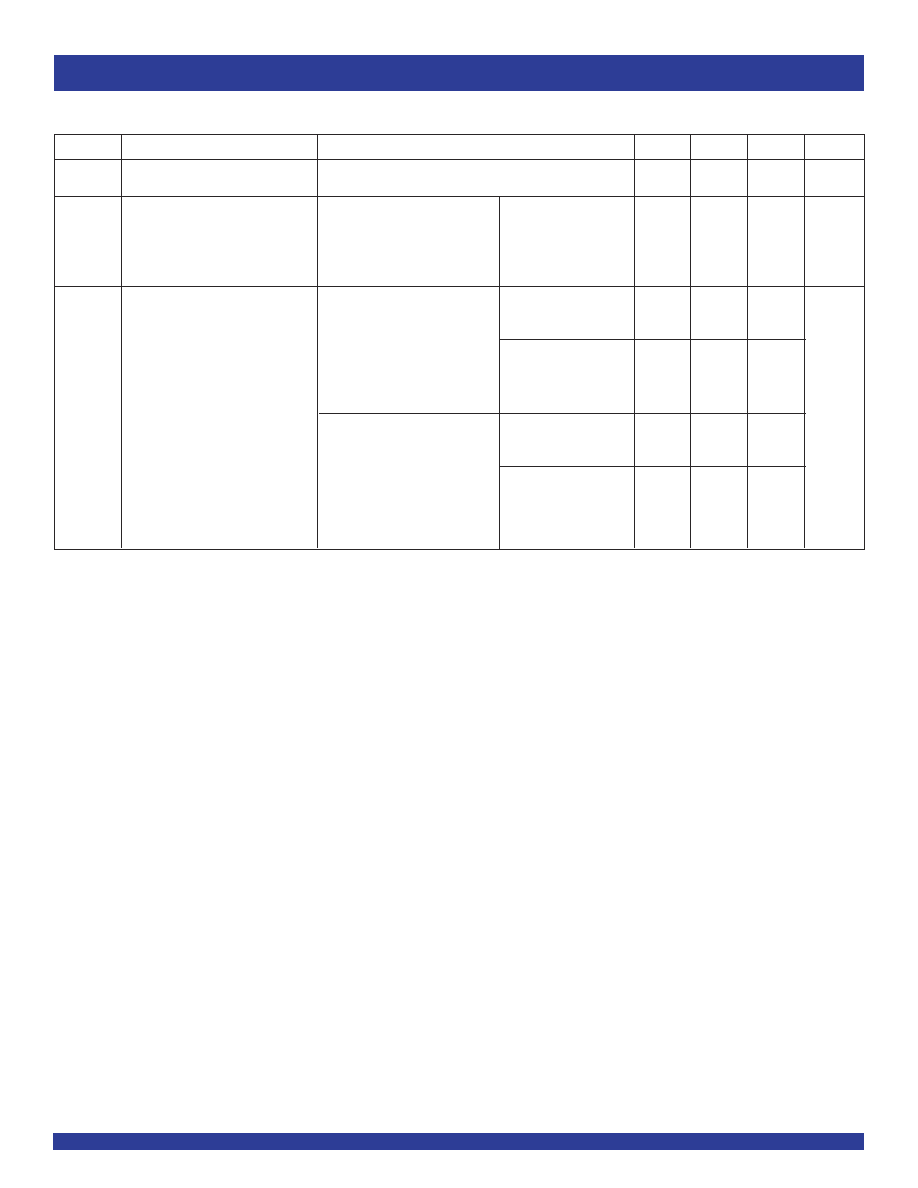

Symbol

Parameter

Test Conditions

(1)

Min.

Typ.

(2)

Max.

Unit

I

CC

Quiescent Power Supply Current

V

CC

= Max.

--

0.5

2

mA

TTL Inputs HIGH

V

IN

= 3.4V

(3)

I

CCD

Dynamic Power Supply

V

CC

= Max.

V

IN

= V

CC

--

0.06

0.12

mA/

Current

(4)

Outputs Open

V

IN

= GND

MHz

OE = GND

One Input Toggling

50% Duty Cycle

I

C

Total Power Supply Current

(6)

V

CC

= Max.

V

IN

= V

CC

--

0.6

2.2

mA

Outputs Open

V

IN

= GND

fi = 10MHz

50% Duty Cycle

V

IN

= 3.4V

--

0.9

3.2

OE = GND

V

IN

= GND

LE = Vcc

One BitToggling

V

CC

= Max.

V

IN

= V

CC

--

1.2

3.4

(5)

Outputs Open

V

IN

= GND

fi = 2.5MHz

50% Duty Cycle

V

IN

= 3.4V

--

3.2

11.4

(5)

OE = GND

V

IN

= GND

LE = Vcc

Eight Bits Toggling

NOTES:

1. For conditions shown as Min. or Max., use appropriate value specified under Electrical Characteristics for the applicable device type.

2. Typical values are at V

CC

= 5.0V, +25∞C ambient.

3. Per TTL driven input; (V

IN

= 3.4V). All other inputs at V

CC

or GND.

4. This parameter is not directly testable, but is derived for use in Total Power Supply Calculations.

5. Values for these conditions are examples of

I

CC

formula. These limits are guaranteed but not tested.

6. I

C

= I

QUIESCENT

+ I

INPUTS

+ I

DYNAMIC

I

C

= I

CC

+

I

CC

D

H

N

T

+ I

CCD

(f

CP

/2+ f

i

N

i

)

I

CC

= Quiescent Current

I

CC

= Power Supply Current for a TTL High Input (V

IN

= 3.4V)

D

H

= Duty Cycle for TTL Inputs High

N

T

= Number of TTL Inputs at D

H

I

CCD

= Dynamic Current caused by an Input Transition Pair (HLH or LHL)

f

CP

= Clock Frequency for Register Devices (Zero for Non-Register Devices)

f

i

= Output Frequency

N

i

= Number of Outputs at f

i

All currents are in milliamps and all frequencies are in megahertz.

POWER SUPPLY CHARACTERISTICS

INDUSTRIAL TEMPERATURE RANGE

IDT74FCT2373AT/CT

FAST CMOS OCTAL TRANSPARENT LATCH

5

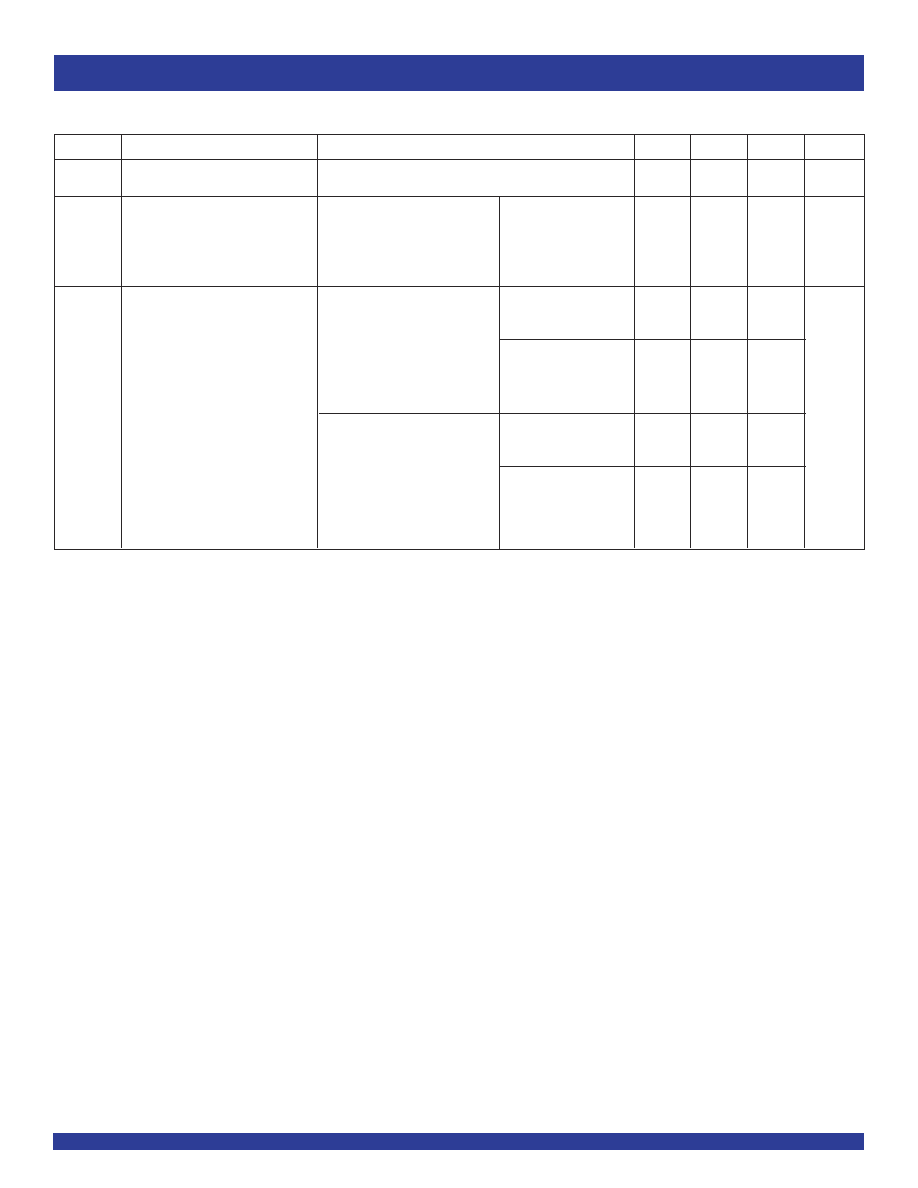

NOTES:

1. See test circuit and waveforms.

2. Minimum limits are guaranteed but not tested on Propagation Delays.

3. This parameter is guaranteed but not tested.

SWITCHING CHARACTERISTICS OVER OPERATING RANGE

(1)

74FCT2373AT

74FCT2373CT

Symbol

Parameter

Condition

(1)

Min

.

(2)

Max.

Min

.

(2)

Max.

Unit

t

PLH

Propagation Delay

C

L

= 50 pF

1.5

5.2

1.5

4.2

ns

t

PHL

Dx to Ox

R

L

= 500

t

PLH

Propagation Delay

2

8.5

2

5.5

ns

t

PHL

LE to Ox

t

PZH

Output Enable Time

1.5

6.5

1.5

5.5

ns

t

PZL

t

PHZ

Output Disable Time

1.5

5.5

1.5

5

ns

t

PLZ

t

SU

Set-up Time HIGH or LOW, Dx to LE

2

--

2

--

ns

t

H

Hold Time HIGH or LOW, Dx to LE

1.5

--

1.5

--

ns

t

W

LE Pulse Width HIGH

(3)

5

--

5

--

ns

INDUSTRIAL TEMPERATURE RANGE

6

IDT74FCT2373AT/CT

FAST CMOS OCTAL TRANSPARENT LATCH

Pulse

Generator

R

T

D.U.T

.

V

CC

V

IN

C

L

V

OUT

50pF

500

500

7.0V

3V

1.5V

0V

3V

1.5V

0V

3V

1.5V

0V

3V

1.5V

0V

DATA

INPUT

TIMING

INPUT

ASYNCHRONOUS CONTROL

PRESET

CLEAR

ETC.

SYNCHRONOUS CONTROL

t

SU

t

H

t

REM

t

SU

t

H

HIGH-LOW-HIGH

PULSE

LOW-HIGH-LOW

PULSE

t

W

1.5V

1.5V

SAME PHASE

INPUT TRANSITION

3V

1.5V

0V

1.5V

V

OH

t

PLH

OUTPUT

OPPOSITE PHASE

INPUT TRANSITION

3V

1.5V

0V

t

PLH

t

PHL

t

PHL

V

OL

CONTROL

INPUT

3V

1.5V

0V

3.5V

0V

OUTPUT

NORMALLY

LOW

OUTPUT

NORMALLY

HIGH

SWITCH

CLOSED

SWITCH

OPEN

V

OL

0.3V

0.3V

t

PLZ

t

PZL

t

PZH

t

PHZ

3.5V

0V

1.5V

1.5V

ENABLE

DISABLE

V

OH

PRESET

CLEAR

CLOCK ENABLE

ETC.

Octal link

Octal link

Octal link

Octal link

Octal link

TEST CIRCUITS AND WAVEFORMS

Propagation Delay

Test Circuits for All Outputs

Enable and Disable Times

Set-Up, Hold, and Release Times

Pulse Width

NOTES:

1. Diagram shown for input Control Enable-LOW and input Control Disable-HIGH.

2. Pulse Generator for All Pulses: Rate

1.0MHz; t

F

2.5ns; t

R

2.5ns.

Test

Switch

Open Drain

Disable Low

Closed

Enable Low

All Other Tests

Open

SWITCH POSITION

DEFINITIONS:

C

L

= Load capacitance: includes jig and probe capacitance.

R

T

= Termination resistance: should be equal to Z

OUT

of the Pulse Generator.

INDUSTRIAL TEMPERATURE RANGE

IDT74FCT2373AT/CT

FAST CMOS OCTAL TRANSPARENT LATCH

7

ORDERING INFORMATION

CORPORATE HEADQUARTERS

for SALES:

for Tech Support:

2975 Stender Way

800-345-7015 or 408-727-6116

logichelp@idt.com

Santa Clara, CA 95054

fax: 408-492-8674

(408) 654-6459

www.idt.com

6/24/2002 Updated as per PDNs Logic-00-07 and Logic-01-04

DATA SHEET DOCUMENT HISTORY

IDT XX

Temp. Range

FCT

XXXX

Device Type

XX

Package

Octal Transparent Latch

2373AT

2373CT

SO

Q

PG

Small Outline IC

Quarter-size Small Outline Package

Thin Shrink Small Outline Package

74

≠ 40∞C to +85∞C