| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: QS33X2253 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

FEATURES/BENEFITS

∑ Enhanced N channel FET with no inherent diode to V

CC

∑ Bidirectional switches connect inputs to outputs

∑ 24:6 Mux/Demux switches

∑ Zero propagation delay, zero ground bounce

∑ Individual controls for each bank

∑ Undershoot clamp diodes on all switch and control pins

∑ TTL-compatible control inputs

∑ Available in 48-pin QVSOP (Q1)

∑ QS33X2253 is 25

version for low noise

APPLICATIONS

∑ Logic replacement

∑ Video, audio, graphics switching, muxing

∑ Hot-swapping, hot-docking

(Application Note AN-13)

∑ Voltage translation

(5V to 3.3V; Application Note AN-11)

DESCRIPTION

The QS33X253 is a high-speed CMOS 24:6 (3, dual 4:1) multi-

plexer/demultiplexer. The QS33X253 is a member of the MultiWidthTM

family and is functionally compatible to three of the QuickSwitch

version of the 74F253, 74FCT253, and the 74ALS/AS/LS253 Dual 4:1

multiplexers. The low ON resistance of the QS33X253 allows inputs to

be connected to outputs without adding propagation delay and without

generating additional ground bounce noise. TTL-compatible control

circuitry with "Break-before-make" feature avoids bus contention on

the demux side. This part is ideal for video switching and four way

memory bank interleaving applications.

The QS33X2253 has 25

series resistors to reduce ground bounce

noise.

Mux/Demux devices provide an order of magnitude faster speed

than equivalent logic devices.

FUNCTIONAL BLOCK DIAGRAM

JULY 1999

1

©

1999 Integrated Device Technology, Inc

DSC-XXXXXX

QS33X253

QS33X2253

QUICKSWITCH

Æ

PRODUCTS

HIGH-SPEED CMOS

QUICKSWITCH MULTIWIDTHTM

24:6 MUX/DEMUX

S0

EF

Y

E

I0

E

I1

E

I2

E

I3

E

I0

F

I1

F

I2

F

I3

F

Y

F

S1

EF

EE

EF

S0

AB

Y

A

I0

A

I1

A

I2

A

I3

A

I0

B

I1

B

I2

B

I3

B

Y

B

S1

AB

EA

EB

S0

CD

Y

C

I0

C

I1

C

I2

C

I3

C

I0

D

I1

D

I2

D

I3

D

Y

D

S1

CD

EC

ED

2

©

1999 Integrated Device Technology, Inc

IDT

QS33X253 AND QS33X2253

DSC-XXXXXX

Name

I/O

Description

IXX

I

Data Inputs

S0XX, S1XX

I

Select Inputs

EX

I

Enable Inputs

Yn, Ym

O

Data Outputs

PIN CONFIGURATION

(ALL PINS TOP VIEW)

QVSOP (Q1)

FUNCTION TABLE

Enable

Select

Outputs

EA

EB

S1

AB

S0

AB

Y

A

Y

B

Function

H

X

X

X

Hi-Z

X

Disable A

X

H

X

X

X

Hi-Z

Disable B

L

L

L

L

I0

A

I0

B

S1-0 = 0

L

L

L

H

I1

A

I1

B

S1-0 = 1

L

L

H

L

I2

A

I2

B

S1-0 = 2

L

L

H

H

I3

A

I3

B

S1-0 = 3

ABSOLUTE MAXIMUM RATINGS

Supply Voltage to Ground .............................................................. ≠0.5V to +7.0V

DC Switch Voltage V

S

.................................................................... ≠0.5V to +7.0V

DC Input Voltage V

IN

...................................................................... ≠0.5V to +7.0V

AC Input Voltage (for a pulse width

20ns) .................................................. ≠3.0V

DC Output Current Max. Sink Current/Pin ................................................... 120mA

Maximum Power Dissipation .................................................................... 0.5 watts

T

STG

Storage Temperature ............................................................ ≠65∞ to +150∞C

Note: ABSOLUTE MAXIMUM CONTINU-

OUS RATINGS are those values beyond

which damage to the device may occur.

Exposure to these conditions or conditions

beyond those indicated may adversely affect

device reliability. Functional operation under

absolute-maximum conditions is not implied.

Note: Capacitance is guaranteed, but not production tested and are typical values. For total

capacitance while the switch is ON, please see Section 1 under "Input and Switch Capacitance".

Note: This function table represents the function for block "AB".

The "CD" block nomenclature substitutes "A" for "C" and "B" for "D".

The "EF" block nomenclature substitutes "A" for "E" and "B" for "F".

CAPACITANCE

T

A

= 25∞C, f = 1MHz, V

IN

= 0V, V

OUT

= 0V

QVSOP

Pins

Typ

Max

Unit

Control Inputs

4

5

pF

QuickSwitch Channels

Demux

5

7

pF

(Switch OFF)

Mux

14

16

pF

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

EA

V

C C

I

3A

I

2A

I

1A

I

0A

YA

G ND

S1

A B

EC

I

3C

I

2C

I

1C

I

0C

YC

G ND

S1

CD

EE

I

3E

I

2E

I

1E

I

0E

YE

G ND

S1

E F

EB

I

3B

I

2B

I

1B

I

0B

YB

V

C C

S0

A B

ED

I

3D

I

2D

I

1D

I

0D

YD

V

C C

S0

CD

EF

I

3F

I

2F

I

1F

I

0F

YF

S0

E F

©

1999 Integrated Device Technology, Inc

IDT

QS33X253 AND QS33X2253

DSC-XXXXXX

3

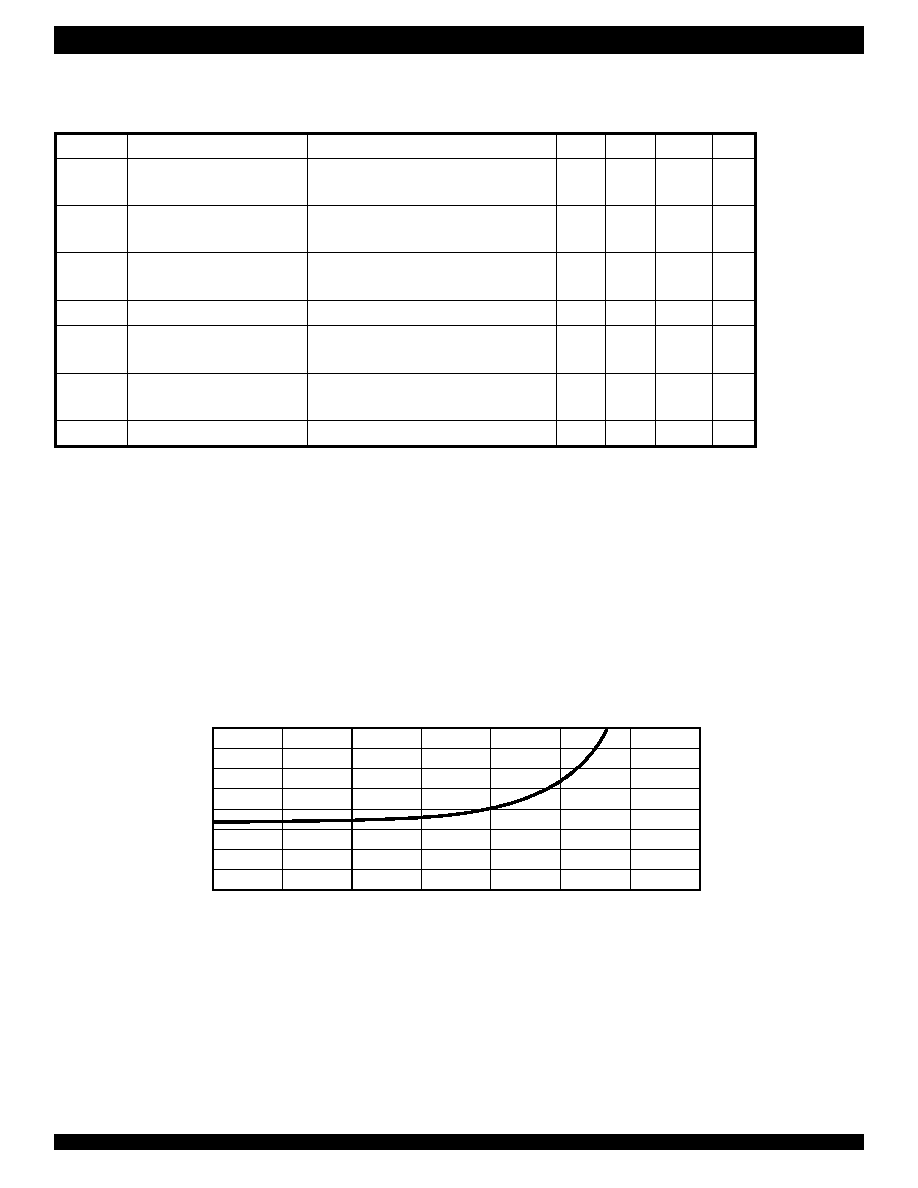

DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

T

A

= ≠40∞C to +85∞C, V

CC

= 5.0V ± 10%

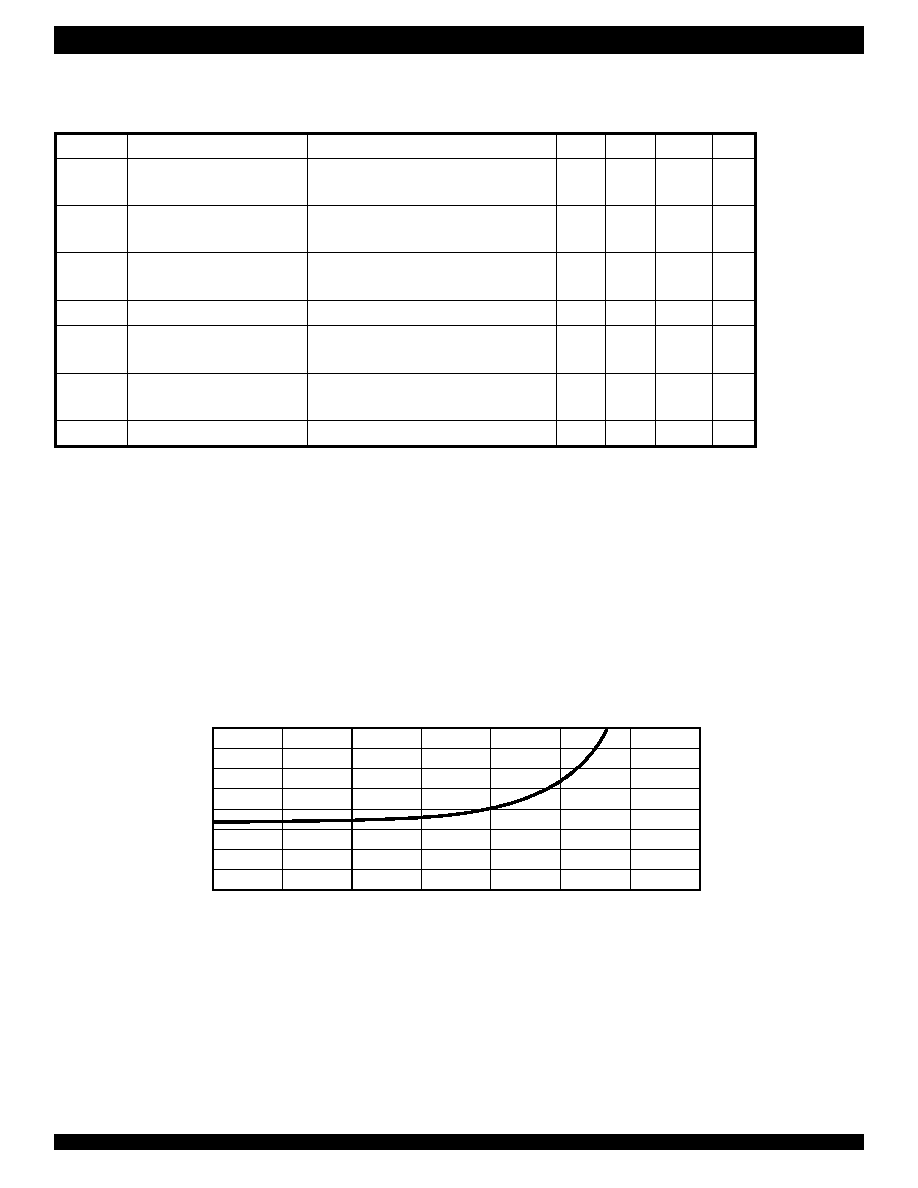

TYPICAL ON RESISTANCE VS. V

IN

AT 5.0 V

CC

(QS33X253)

Notes:

1. Typical values indicate V

CC

= 5.0V and T

A

= 25∞C.

2. For a diagram explaining the procedure for R

ON

measurement, please see Section 1 under "DC Electrical Characteristics". R

ON

guaranteed by characterization, but not

production tested.

3. Pass voltage is guaranteed, but not production tested.

Note: For QS33X2253, add 23

to R

ON

shown.

Symbol

Parameter

Test Conditions

Min

Typ

(1)

Max

Unit

V

IH

Input HIGH Voltage

Guaranteed Logic HIGH

2.0

--

--

V

for Control Pins

V

IL

Input LOW Voltage

Guaranteed Logic LOW

--

--

0.8

V

for Control Pins

| I

IN

|

Input Leakage Current

0V

V

IN

V

CC

--

--

1

µA

(Control Inputs)

| I

OZ

|

Off-State Current (Hi-Z)

0V

V

OUT

V

CC

--

--

1

µA

R

ON

Switch On Resistance

(2)

V

CC

= Min., V

IN

= 0.0V

QS33X253

--

7

10

I

ON

= 30mA

QS33X2253

20

28

40

R

ON

Switch On Resistance

(2)

V

CC

= Min., V

IN

= 2.4V

QS33X253

--

10

15

I

ON

= 15mA

QS33X2253

20

35

48

V

P

Pass Voltage

(3)

V

IN

= V

CC

= 5V, I

OUT

= ≠5µA

3.7

4.0

4.2

V

16

14

12

10

8

6

4

2

0

R

O N

(ohm s)

0.0

0.5

1.0

1.5

2.0

2.5

3.0

3.5

V

IN

(Volts)

4

©

1999 Integrated Device Technology, Inc

IDT

QS33X253 AND QS33X2253

DSC-XXXXXX

POWER SUPPLY CHARACTERISTICS OVER OPERATING RANGE

T

A

= ≠40∞C to +85∞C, V

CC

= 5.0V ± 10%

Symbol

Parameter

Test Conditions

(1)

Max

Unit

I

CCQ

Quiescent Power

V

CC

= Max., V

IN

= GND or V

CC

, f = 0

9

µ A

Supply Current

I

CC

Power Supply Current

(2)

V

CC

= Max., V

IN

= 3.4V, f = 0

1.5

mA

per Input HIGH

per control input

Q

CCD

Dynamic Power Supply

V

CC

= Max., I and Y Pins Open,

0.25

mA/

Current per MHz

(3)

Control Inputs Toggling @ 50% Duty Cycle

MHz

SWITCHING CHARACTERISTICS OVER OPERATING RANGE

T

A

= ≠40∞C to +85∞C, V

CC

= 5.0V ± 5%

C

LOAD

= 50pF, R

LOAD

= 500

unless otherwise noted.

Notes:

1. See Test Circuit and Waveforms. Minimums guaranteed, but not production tested.

2. This parameter is guaranteed, but not production tested.

3. The bus switch contributes no propagation delay other than the RC delay of the ON resistance of the switch and the load capacitance. The time constant for the switch alone is of the

order of 0.25ns for QS33X253 and 1.25ns for QS33X2253 for C

L

= 50pF. Since this time constant is much smaller than the rise/fall times of typical driving signals, it adds very little

propagation delay to the system. Propagation delay of the bus switch when used in a system is determined by the driving circuit on the driving side of the switch and its interaction

with the load on the driven side.

QS33X253

QS33X2253

Symbol

Description

(1)

(

Min

Typ

Max

Min

Typ

Max

Unit

t

PLH

Data Propagation Delay

(2,3)

--

--

0.25

(3)

--

--

1.25

(3)

ns

t

PHL

In to Y

t

PZL

Switch Turn-on Delay

0.5

--

6.6

0.5

--

7.0

ns

t

PZH

Sn to Y

t

PZL

Switch Turn-on Delay

0.5

--

6.0

0.5

--

7.0

ns

t

PZH

En

to Y

t

PLZ

Switch Turn-off Delay

(2)

0.5

--

6.0

0.5

--

6.0

ns

t

PHZ

En

to Y, Sn to Y

CORPORATE HEADQUARTERS

for SALES:

2975 Stender Way

800-345-7015 or 408-727-6116

Santa Clara, CA 95054

fax: 408-492-8674

www.idt.com*

*To search for sales office near you, please click the sales button found on our home page or dial the 800# above and press 2.

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

Notes:

1. For conditions shown as Min. or Max., use the appropriate values specified under DC specifications.

2. Per TTL driven input (V

IN

= 3.4V, control inputs only). I and Y pins do not contribute to I

CC

.

3. This current applies to the control inputs only and represents the current required to switch internal capacitance at the specified frequency. The I and Y inputs generate no significant

AC or DC currents as they transition. This parameter is guaranteed by characterization, but not production tested.