13

Semiconductor, Inc.

7

8

9

10

11

12

13

14

15

16

17

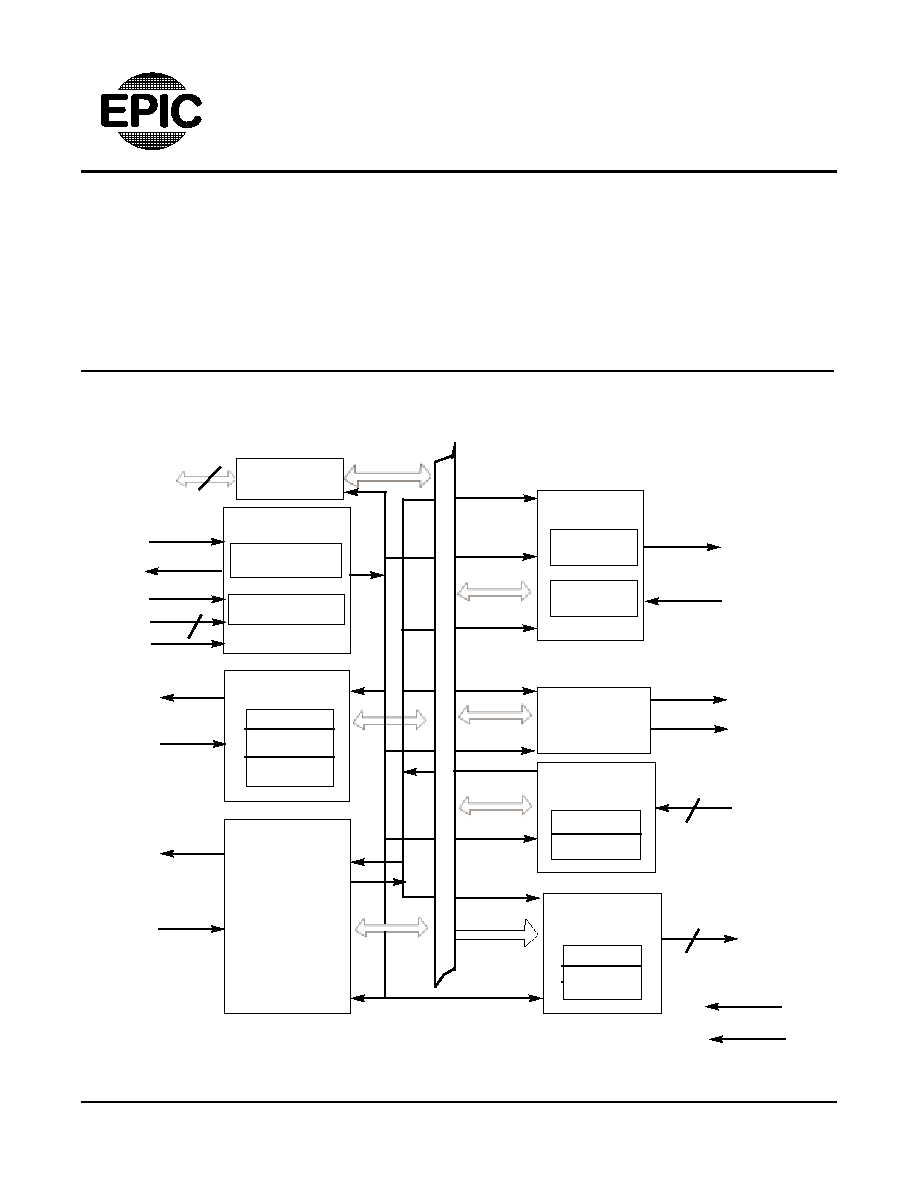

DESCRIPTION

The Epic Ei88C681/Ei68C681 DUART Dual Universal

Asynchronous Receiver and Transmitter is a data com-

munication device that provides two fully independent full

duplex asynchronous communication channels in a

single package. The DUART is designed for use in

microprocessor based systems and may be used in a

polled or interrupt driven environment.

Two basic versions of the DUART are available, each

optimized for use with various microprocessor families:

the 88C81 for 8085/85, 8080/88, Z80, Z8000, 68XX and

65XX family based systems., and the 68C681 for 68000

family based systems. A programmable mode of the

Ei88C681 versions provides an interrupt daisy chain for

use in Z80 and Z8000 based systems. The bus inter-

faces are however general enough to allow interfacing

with other microprocessors and microcontrollers. The

88C681 and 68C681 are enhanced versions of the

Signetics 2681 and the Motorola 68681, and are pin and

function compatible with those devices. Each channel of

the DUART may be independently programmed for

operating mode and data format. The operating speed of

each receiver and transmitter can beselected from baud

rate generator, from the multi-purpose on chip

counter/timer or from an external 1 x or 16 x clock.The bit

rate generator can operate directly from a crystal connect-

ed across two pins or from an external clock. The ability to

independently program the operating speed of the receiv-

er and transmitter of each channel makes the DUART

attractive for split-speed channel application such as clus-

tered terminal systems. Both receive and transmit data is

quadruple-buffered in on-chip FIFO to minimize the risk of

receiver overrun or to reduce overhead in interrupt-drive

applications.

Ei68C681

Ei88C681

DUAL UART

FEATURES

∑

Full duplex, dual channel asynchronous

receiver and transmitter

∑

Quadruple-buffered receiver and transmitter

∑

Stop bits programmable in 1/16-bit increments

∑

Internal bit rate generator with 23 bit rates

∑

Independent bit rate selection for each Rx

and Tx

∑

Maximum bit rate: 1 x clock - 2 Mb/sec., 16

x clock- 250 Kb/sec.

∑

Normal, auto-echo, local loop-back and

remote loop-back modes

∑

Multi-function 16-bit counter/timer

∑

Interrupt output with 8 maskable interrupt

ing conditions

∑

Interrupt vector output on acknowledge

∑

Programmable interrupt daisy chain

∑

Up to 15 I/O pins (depending on package

and version)

∑

Multidrop mode compatible with 8051 nine-

bit mode

∑

On-chip oscillator for crystal

∑

Stand-by mode to reduce operating power

∑

Advanced CMOS low power technology

PIN CONFIGURATION

18

19

20

21

22

23

24

25

26

27

28

6

5

4

3

2

1

44

43

42

41

40 39

38

37

36

35

34

33

32

31

30

29

A3

IP0

WR∑

RD∑

RXDB

NC

TXDB

OP1

OP3

OP5

OP7

CE∑

RESET

X2

X1/CLK∑

RXDA

NC

TXDA

OP0

OP2

OP4

OP6

D1

D3

D5

D7

GND

NC

INTR

D6

D4

D2

D0

A2

IP1

A2

IP3

A1

NC

VCC

IP4/IEI

IP5/IEO

IP6/IACK

IP2

Ei88C681

40

6

5

4

3

2

1 44 43 42 41

28

18 19 20 21 22 23 24 25 26 27

39

29

30

31

32

33

34

35

36

37

38

7

17

16

15

14

13

12

11

10

9

8

CS

∑

RESET

X2

X1/CLK

∑

RXDA

NC

TXDA

OP0

OP2

OP4

OP6

A4

IP0

R/WN

DTACK

∑

RXDB

NC

TXDB

OP1

OP3

OP5

OP7

D1

D3

D5

D7

GND

NC

INTRN

D6

D4

D2

D0

A3

IP1

A2

IP3

A1

NC

VCC

IP4

IP5

IACKN

IP2

Ei68C681

44-PIN PLCC

44-PIN PLCC

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

A1

IP3

A2

IP1

A3

A4

IPO

R/W∑

DTACK∑

RxDB

TxDB

OP1

OP3

OP5

OP7

D1

D3

D5

D7

GND

VCC

IP4

IP5

IACK∑

IP2

CS∑

RESET∑

X2

X1/CLK

RxDA

TxDA

OP0

OP2

OP4

OP6

D0

D2

D4

D6

INTR∑

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

E

i

6

8

C

6

8

1

40-PIN DIP

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

A0

IP3

A1

IP1

A2

A3

IPO

WRN

RDN

RxDB

TxDB

OP1

OP3

OP5

OP7

D1

D3

D5

D7

GND

VCC

IP4/IEI

IP5/IEO

IP6/IACKN

IP2

CEN

RESET

X2

X1/CLK

RxDA

TxDA

OP0

OP2

OP4

OP6

D0

D2

D4

D6

INTRN

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

E

i

8

8

C

6

8

1

40-PIN DIP

Part Numbers May Be Marked With "IMP" or "Ei."

For additional information, contact IMP, Inc. at 408.432.9100 or visit www.impweb.com

IMP, Inc. acquired Epic products on January 26, 2001. (see press release at http://www.impweb.com/PRESS/PR012601.htm)