| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: ICE2BS01 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

PWM-FF IC

I C E 2 A S 0 1 / S 0 1 G

I C E 2 B S 0 1 / S 0 1 G

O f f - L i n e S M P S C u r r e n t M o d e

C o n t r o l l e r

N e v e r s t o p t h i n k i n g .

P o w e r M a n a g em e n t & S u p p l y

D a t a s h e e t , V 2 . 0 , 1 F e b 2 0 0 2

Edition 2002-02-01

Published by Infineon Technologies AG,

St.-Martin-Strasse 53,

D-81541 M¸nchen

©

Infineon Technologies AG 1999.

All Rights Reserved.

Attention please!

The information herein is given to describe certain components and shall not be considered as warranted char-

acteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding

circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infin-

eon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in

question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written

approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure

of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support

devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain

and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may

be endangered.

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or

the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://

www.infineon.com

CoolMOSTM, CoolSETTM are trademarks of Infineon Technologies AG.

ICE2AS01/G

ICE2BS01/G

Revision History: 2002-02-01 Datasheet

Previous Version:

Page

Subjects (major changes since last revision)

Version 2.0 3 1 Feb 2002

Type

Ordering Code

Frequency

Package

ICE2AS01

Q67040-S4472

100kHz

P-DIP-8-4

ICE2AS01G

Q67040-S4473

100kHz

P-DSO-8-3

ICE2BS01

Q67040-S4475

67kHz

P-DIP-8-4

ICE2BS01G

Q67040-S4476

67kHz

P-DSO-8-3

ICE2AS01/G

ICE2BS01/G

P-DIP-8-4

P-DSO-8-3

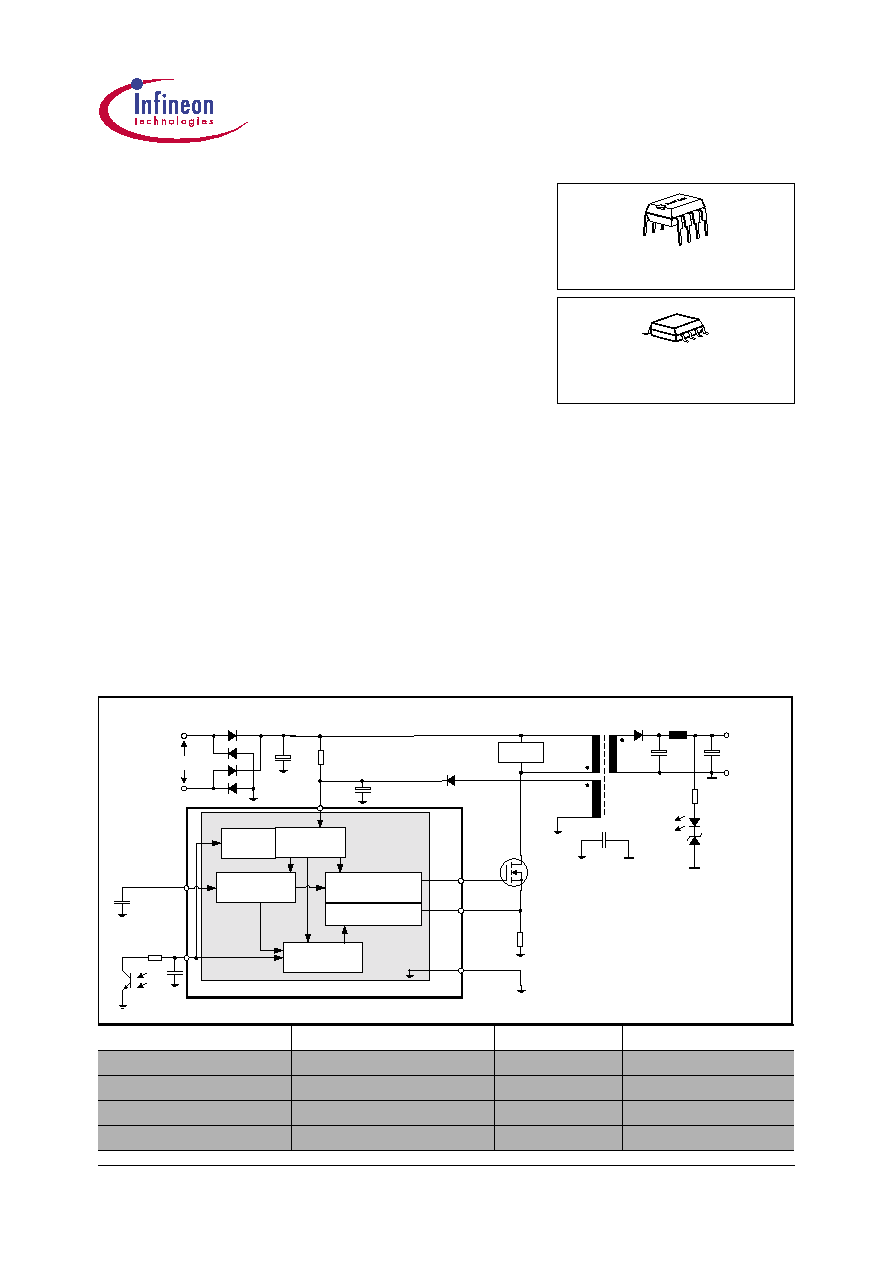

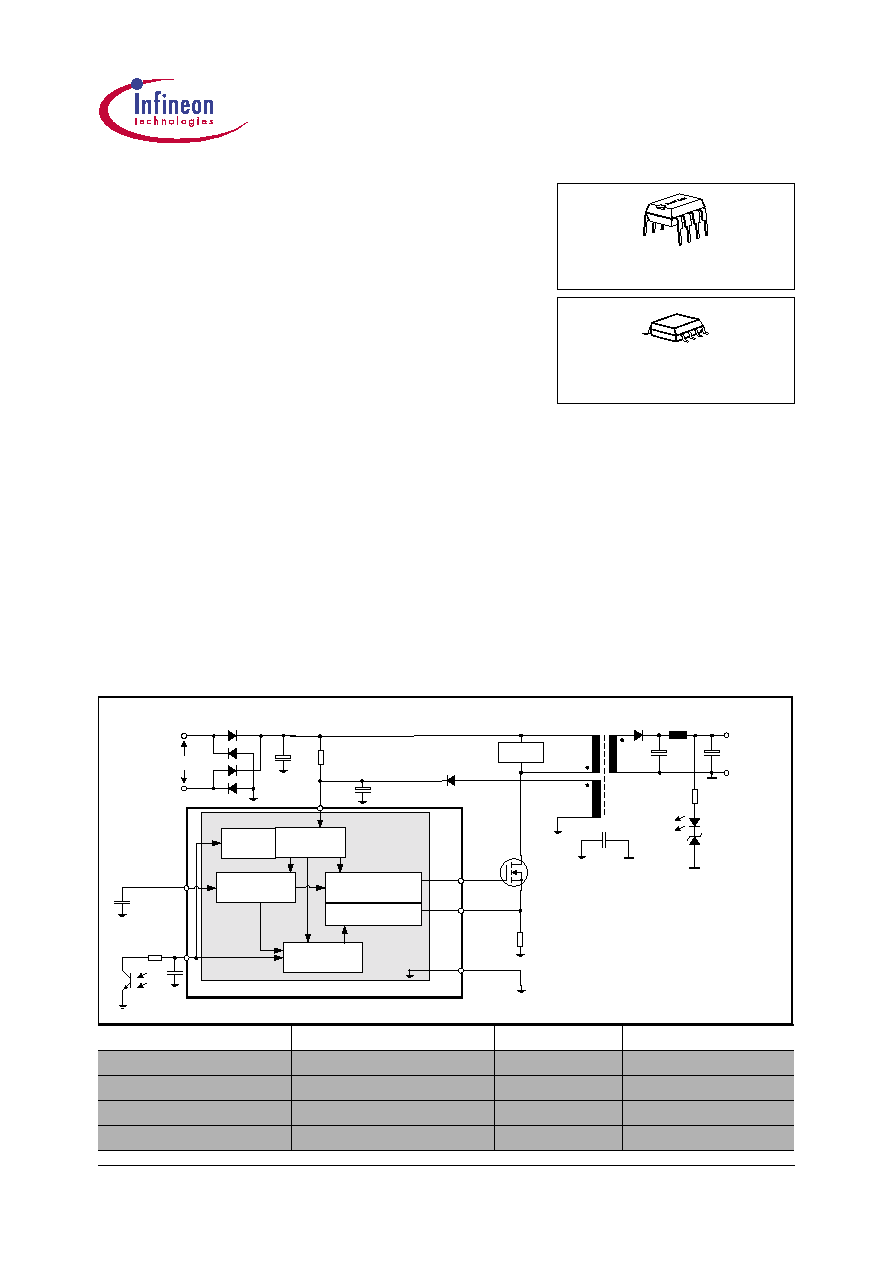

C

Soft Start

C

VCC

R

Start-up

VCC

-

Converter

DC Output

+

ICE2AS01 / ICE2BS01

Snubber

Power

Management

Protection Unit

Soft-Start Control

PWM Controller

Current Mode

FB

85 ... 270 VAC

Feedback

Feedback

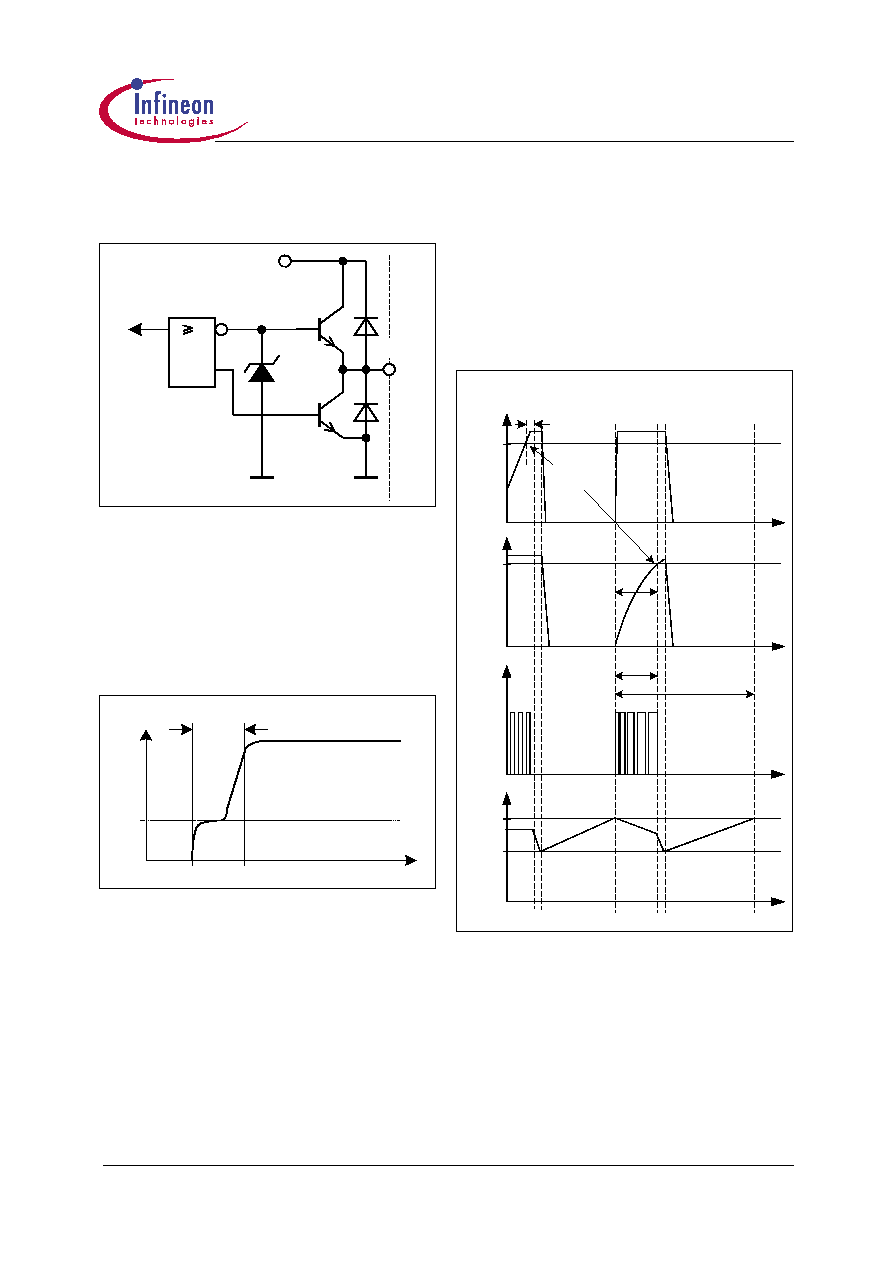

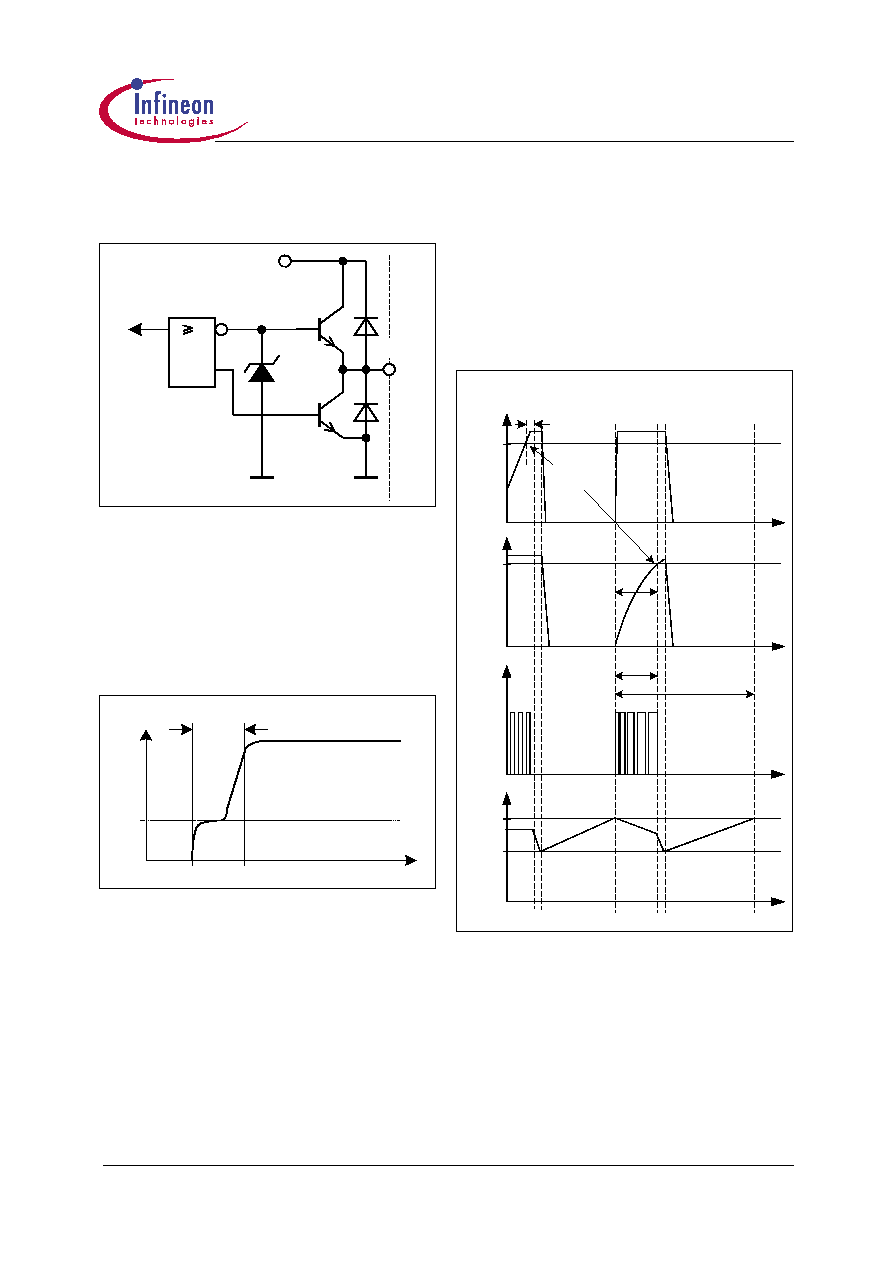

Typical Application

Low Power

StandBy

Precise Low Tolerance

Peak Current Limitation

R

Sense

Isense

GND

SoftS

Gate

Off-Line SMPS Current Mode Controller

Product Highlights

∑ Enhanced Protection Functions all

with Auto Restart

∑ Lowest Standby Power Dissipation

∑ Very Accurate Current Limiting

Features

∑

Only few external Components required

∑

Input Undervoltage Lockout

∑

67kHz/100kHz fixed Switching Frequency

∑

Max Duty Cycle 72%

∑

Low Power Standby Mode to support

"Blue Angle" Norm

∑

Latched Thermal Shut Down

∑

Overload and Open Loop Protection

∑

Overvoltage Protection during Auto Restart

∑

Adjustable Peak Current Limitation via

External Resistor

∑

Overall Tolerance of Current Limiting

<

±5%

∑

Internal Leading Edge Blanking

∑

Soft Start

∑

Soft Switching for Low EMI

Description

This stand alone controller provides several special

enhancements to satisfy the needs for low power standby

and protection features. In standby mode frequency

reduction is used to lower the power consumption and

provide a stable output voltage in this mode. The frequency

reduction is limited to 20kHz / 21.5 kHz (typ.) to avoid

audible noise. In case of failure modes like open loop,

overvoltage or overload due to short circuit the device

switches in Auto Restart Mode which is controlled by the

internal protection unit. By means of the internal precise

peak current limitation the dimension of the transformer and

the secondary diode can be lower which leads to more cost

efficiency.

ICE2AS01/G

ICE2BS01/G

Table of Contents

Page

Version 2.0 4 1 Feb 2002

1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

1.1

Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

1.2

Pin Functionality . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

2

Pin Configuration and Functionality . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

3

Representative Blockdiagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

4

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

4.1

Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

4.2

Improved Current Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

4.2.1

PWM-OP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

4.2.2

PWM-Comparator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

4.3

Soft-Start . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

4.4

Oscillator and Frequency Reduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

4.4.1

Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

4.4.2

Frequency Reduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

4.5

Current Limiting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

4.5.1

Leading Edge Blanking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

4.5.2

Propagation Delay Compensation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

4.6

PWM-Latch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

4.7

Driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

4.8

Protection Unit (Auto Restart Mode) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

4.8.1

Overload & Open loop with normal load . . . . . . . . . . . . . . . . . . . . . . . . .12

4.8.2

Overvoltage due to open loop with no load . . . . . . . . . . . . . . . . . . . . . . .13

4.8.3

Thermal Shut Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

5

Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

5.1

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

5.2

Operating Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

5.3

Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

5.3.1

Supply Section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

5.3.2

Internal Voltage Reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

5.3.3

Control Section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

5.3.4

Protection Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

5.3.5

Current Limiting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

5.3.6

Driver Section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

6

Typical Performance Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . .19

7

Outline Dimension . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

Version 2.0 5 1 Feb 2002

ICE2AS01/G

ICE2BS01/G

1

Figure 1

Pin Configuration (top view)

1.2

Pin Functionality

SoftS (Soft Start & Auto Restart Control)

This pin combines the function of Soft Start in case of

Start Up and Auto Restart Mode and the controlling of

the Auto Restart Mode in case of an error detection.

FB (Feedback)

The information about the regulation is provided by the

FB Pin to the internal Protection Unit and to the internal

PWM-Comparator to control the duty cycle.

Isense (Current Sense)

The Current Sense pin senses the voltage developed

on the series resistor inserted in the source of the

external Power Switch. When Isense reaches the

internal threshold of the Current Limit Comparator, the

Driver output is disabled. By this mean the Over

Current Detection is realized.

Furthermore the current information is provided for the

PWM-Comparator to realize the Current Mode.

Gate (Driver Output)

The current and slew rate capability of this pin are

suited to drive Power MOSFETs.

VCC (Power supply)

This pin is the positiv supply of the IC. The operating

range is between 8.5V and 21V.

To provide overvoltage protection the driver gets

disabled when the voltage becomes higher than 16.5V

during Start up Phase.

GND (Ground)

This pin is the ground of the primary side of the SMPS.

1.1

Pin Configuration

Pin

Symbol

Function

1

N.C.

Not connected

2

SoftS

Soft Start & Auto Restart Control

3

FB

Regulation Fedback

4

Isense

Controller Current Sense Input

5

Gate

Driver Output

6

VCC

Controller Supply Voltage

7

GND

Controller Ground

8

N.C.

Not connected

1

6

7

8

4

3

2

5

GND

SoftS

FB

Isense

N.C.

VCC

N.C.

Gate

Package P-DIP-8-4

G-Package P-DSO-8-3

1

Pin Configuration and Functionality

ICE2AS01/G

ICE2BS01/G

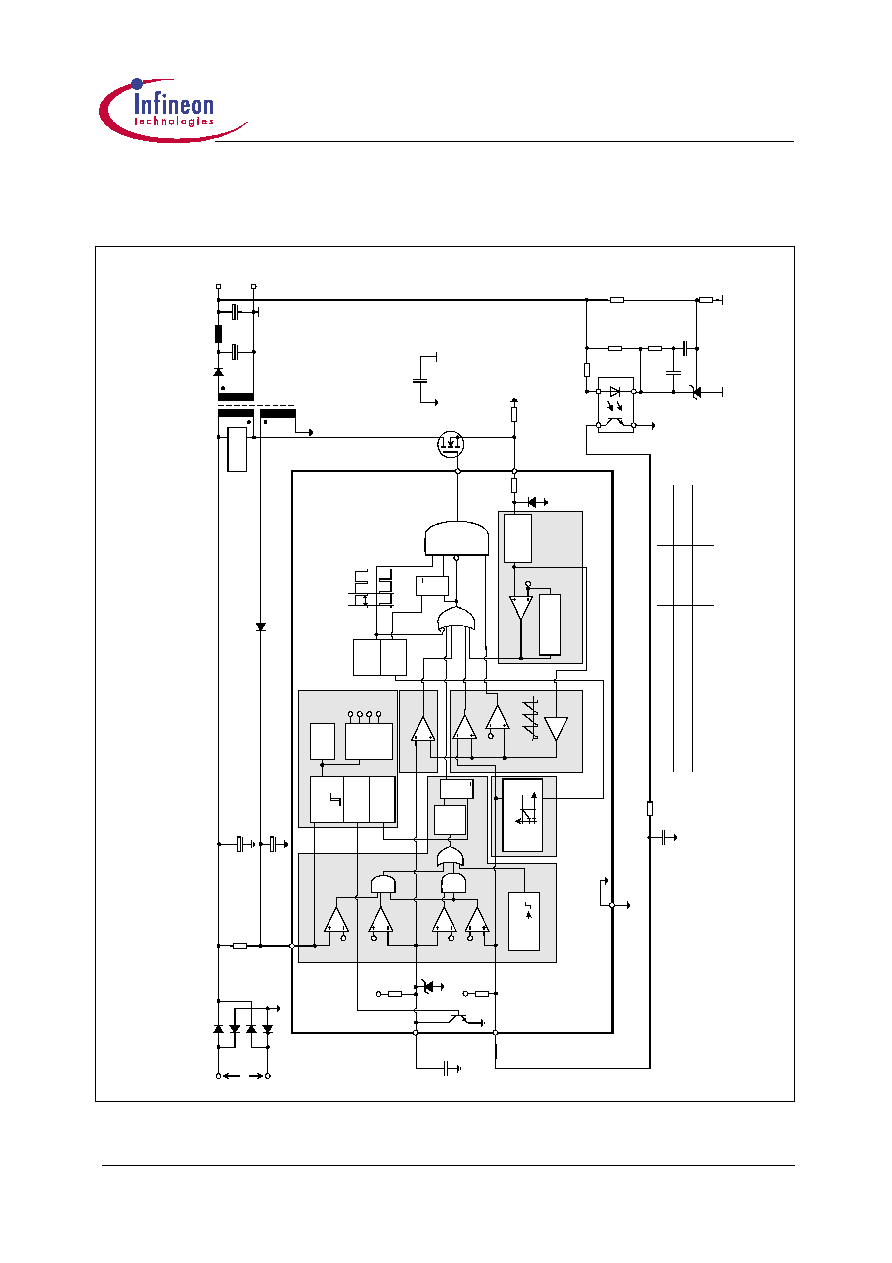

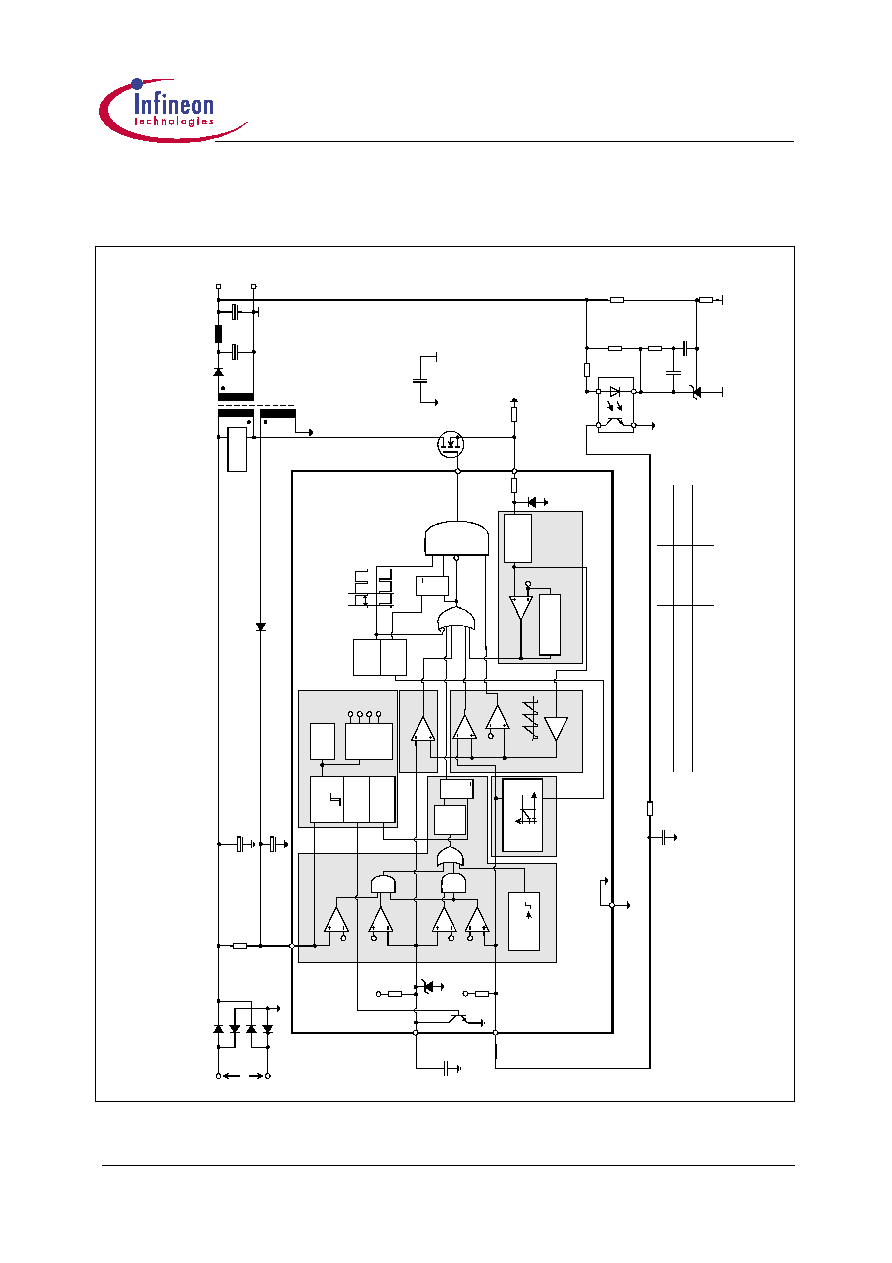

Representative Blockdiagram

Version 2.0 6 1 Feb 2002

2

Representative Blockdiagram

Figure 2

Ther

m

a

l

S

hut

dow

n

T

j

>1

4

0

∞

C

In

te

r

n

a

l

Bi

a

s

V

ol

t

age

R

e

f

e

r

ence

6.

5V

4.

8V

Leadi

ng E

dge

B

l

anki

n

g

200

ns

U

nder

v

ol

t

age

Lockout

O

s

c

i

l

l

at

or

Du

t

y

Cy

c

l

e

ma

x

C

ur

r

ent

-

Li

m

i

t

C

om

par

at

or

x3

.

6

5

S

o

ft-

S

t

a

r

t

C

om

par

at

or

C

ur

r

e

nt

Li

m

i

t

i

ng

PW

M

O

P

I

m

pr

oved C

u

r

r

e

nt

M

o

d

e

So

f

t

S

t

a

r

t

13.5V

8.5V

6.

5V

C2

C1

16.

5V

4.

0V

R

FB

6.

5V

Pr

ot

ect

i

on U

ni

t

P

o

we

r

-

Do

wn

Re

s

e

t

P

o

w

e

r-U

p

Re

s

e

t

P

o

w

e

r

M

a

nagem

e

nt

C

S

o

ft-

S

t

ar

t

C

VC

C

R

S

t

ar

t

-

up

8

5

...

270 V

A

C

C

Li

ne

VCC

GN

D

+

-

C

onver

t

e

r

DC O

u

tp

u

t

V

OU

T

IC

E

2

A

S

0

1

/

IC

E

2

B

S

0

1

Op

t

o

co

u

p

le

r

S

nubber

Sp

i

k

e

B

l

anki

n

g

5

µ

s

PW

M

C

om

par

at

or

R

SQ

Q

Er

r

o

r

-

L

a

t

c

h

C4

5.

3V

C3

4.

8V

R

S

o

ft

-

S

ta

r

t

Ga

t

e

Dr

iv

e

r

G3

G2

G1

G4

SoftS

5.

3V

T1

V

cst

h

P

r

opagat

i

on-

D

el

ay

C

o

m

pensat

i

o

n

R

S

Q

Q

P

W

M

-

Lat

ch

0.7

2

Cl

o

c

k

U

FB

f

os

c

f

nor

m

f

s

t

an

dby

S

t

an

dby U

n

i

t

FB

4.

0V

R

S

ens

e

Ga

t

e

Isens

e

0.8V

C5

0.

3V

5.

6V

10k

D1

Frequ

ency i

n N

orma

l

M

ode

f

nor

m

:

I

C

E

2B

S

01/

S

O

1G

I

C

E

2A

S

01/

S

O

1G

67kH

z

100

kH

z

Frequ

ency i

n S

t

andb

y Mod

e f

st

andby

:

20kH

z

21.

5kH

z

Version 2.0 7 1 Feb 2002

ICE2AS01/G

ICE2BS01/G

Functional Description

3

Functional Description

3.1

Power Management

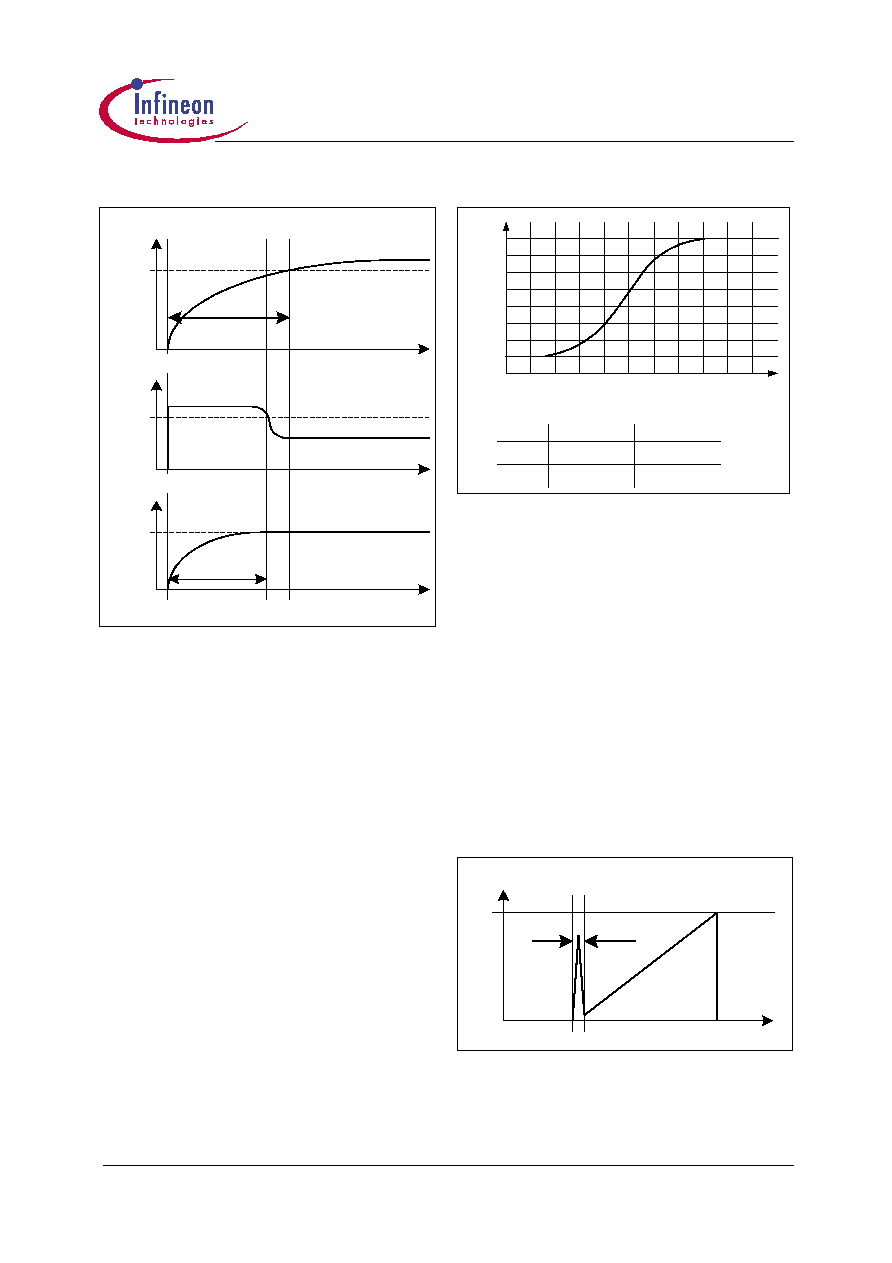

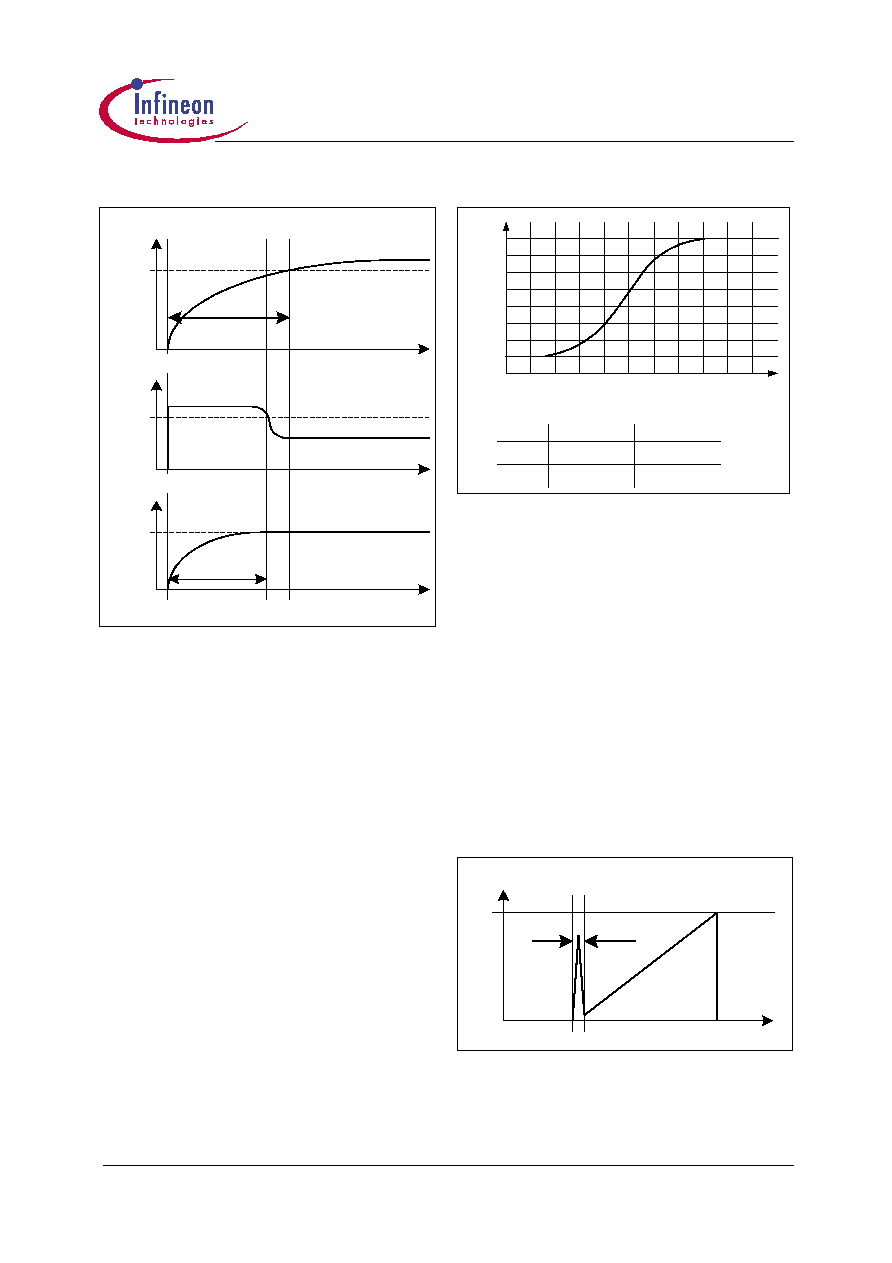

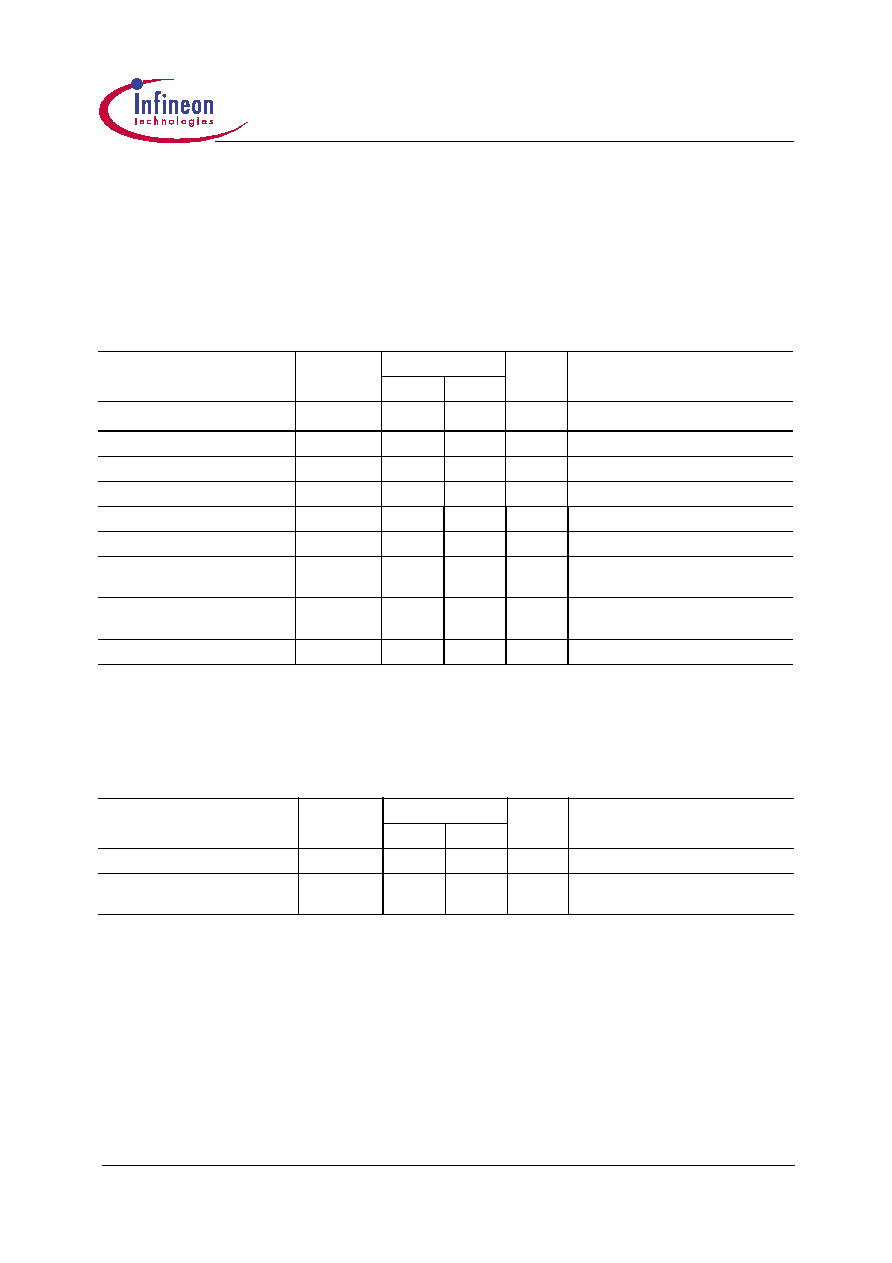

Figure 3

Power Management

The Undervoltage Lockout monitors the external

supply voltage V

VCC

. In case the IC is inactive the

current consumption is max. 55µA. When the SMPS is

plugged to the main line the current through R

Start-up

charges the external Capacitor C

VCC

. When V

VCC

exceeds the on-threshold V

CCon

=13.5V the internal bias

circuit and the voltage reference are switched on. After

it the internal bandgap generates a reference voltage

V

REF

=6.5V to supply the internal circuits. To avoid

uncontrolled ringing at switch-on a hysteresis is

implemented which means that switch-off is only after

active mode when Vcc falls below 8.5V.

In case of switch-on a Power Up Reset is done by

reseting the internal error-latch in the protection unit.

When V

VCC

falls below the off-threshold V

CCoff

=8.5V the

internal reference is switched off and the Power Down

reset let T1 discharging the soft-start capacitor C

Soft-Start

at pin SoftS. Thus it is ensured that at every switch-on

the voltage ramp at pin SoftS starts at zero.

3.2

Improved Current Mode

Figure 4

Current Mode

Current Mode means that the duty cycle is controlled

by the slope of the primary current. This is done by

comparison the FB signal with the amplified current

sense signal.

Figure 5

Pulse Width Modulation

In case the amplified current sense signal exceeds the

FB signal the on-time T

on

of the driver is finished by

reseting the PWM-Latch (see Figure 5).

In te rn a l

B ias

V o lta g e

R efe ren ce

6.5 V

4.8 V

U n de rvolta g e

L o ckou t

1 3 .5V

8 .5 V

P o w er-D ow n

R e set

P o w er-U p

R e se t

Pow er M anagem ent

5.3 V

4.0 V

T 1

P W M -L atch

R

S

Q

Q

E rro r-L a tch

S o ftS

6 .5 V

E rror-D ete ctio n

V C C

M ain L in e (1 00 V -3 80 V )

P rim ary W in ding

S o ft-S ta rt C om p ara tor

C

V C C

R

S oft-S ta rt

R

S tart-U p

C

S oft-S tart

x 3 .6 5

P W M O P

Im proved

C urrent M ode

0 .8 V

P W M C o m p a ra to r

P W M -L a tc h

Is e n se

F B

R

S

Q

Q

D rive r

S o ft-S ta rt C o m p a ra to r

t

F B

A m p lifie d C u rre n t S ig n a l

T

o n

t

0 .8 V

D rive r

Version 2.0 8 1 Feb 2002

ICE2AS01/G

ICE2BS01/G

Functional Description

The primary current is sensed by the series resistor

R

Sense

inserted in the source of the external Power

Switch. By means of Current Mode the regulation of the

secondary voltage is insensitive on line variations. Line

variation causes varition of the increasing current slope

which controls the duty cycle.

The external R

Sense

allows an individual adjustment of

the maximum source current of the external Power

Switch.

Figure 6

Improved Current Mode

To improve the Current Mode during light load

conditions the amplified current ramp of the PWM-OP

is superimposed on a voltage ramp, which is built by

the switch T

2

, the voltage source V

1

and the 1st order

low pass filter composed of R

1

and C

1

(see Figure 6,

Figure 7). Every time the oscillator shuts down for max.

duty cycle limitation the switch T2 is closed by V

OSC

.

When the oscillator triggers the Gate Driver T2 is

opened so that the voltage ramp can start (see Figure

7).

In case of light load the amplified current ramp is to

small to ensure a stable regulation. In that case the

Voltage Ramp is a well defined signal for the

comparison with the FB-signal. The duty cycle is then

controlled by the slope of the Voltage Ramp.

By means of the C5 Comparator the Gate Driver is

switched-off until the voltage ramp exceeds 0.3V. It

allows the duty cycle to be reduced continously till 0%

by decreasing V

FB

below that threshold.

Figure 7

Light Load Conditions

3.2.1

PWM-OP

The input of the PWM-OP is applied over the internal

leading edge blanking to the external sense resistor

R

Sense

connected to pin ISense. R

Sense

converts the

source current into a sense voltage. The sense voltage

is amplified with a gain of 3.65 by PWM OP. The output

of the PWM-OP is connected to the voltage source V1.

The voltage ramp with the superimposed amplified

current singal is fed into the positive inputs of the PWM-

Comparator, C5 and the Soft-Start-Comparator.

3.2.2

PWM-Comparator

The PWM-Comparator compares the sensed current

signal of the external Power Switch with the feedback

signal V

FB

(see Figure 8). V

FB

is created by an external

optocoupler or external transistor in combination with

the internal pullup resistor R

FB

and provides the load

information of the feedback circuitry. When the

amplified current signal of the external Power Switch

exceeds the signal V

FB

the PWM-Comparator switches

off the Gate Driver.

x3 .6 5

P W M O P

0.8V

1 0 k

O s cilla to r

P W M C o m p a ra to r

2 0 p F

T

2

R

1

C

1

F B

P W M -L a tch

V

1

C 5

0 .3 V

G a te D rive r

V oltage Ram p

V

O S C

S o ft-S ta rt C o m p a ra to r

t

t

V

O S C

0 .8 V

F B

G a te D rive r

V o lta g e R a m p

t

m a x.

D u ty C yc le

0 .3 V

Version 2.0 9 1 Feb 2002

ICE2AS01/G

ICE2BS01/G

Functional Description

Figure 8

PWM Controlling

3.3

Soft-Start

Figure 9

Soft-Start Phase

The Soft-Start is realized by the internal pullup resistor

R

Soft-Start

and the external Capacitor C

Soft-Start

(see

Figure 2). The Soft-Start voltage V

SoftS

is generated by

charging the external capacitor C

Soft-Start

by the internal

pullup resistor R

Soft-Start

. The Soft-Start-Comparator

compares the voltage at pin SoftS at the negative input

with the ramp signal of the PWM-OP at the positive

input. When Soft-Start voltage V

SoftS

is less than

Feedback voltage V

FB

the Soft-Start-Comparator limits

the pulse width by reseting the PWM-Latch (see Figure

9). In addition to Start-Up, Soft-Start is also activated at

each restart attempt during Auto Restart. By means of

the above mentioned C

Soft-Start

the Soft-Start can be

defined by the user. The Soft-Start is finished when

V

SoftS

exceeds 5.3V. At that time the Protection Unit is

activated by Comparator C4 and senses the FB by

Comparator C3 wether the voltage is below 4.8V which

means that the voltage on the secondary side of the

SMPS is settled. The internal Zener Diode at SoftS with

breaktrough voltage of 5.6V is to prevent the internal

circuit from saturation (see Figure 10).

Figure 10

Activation of Protection Unit

The Start-Up time T

Start-Up

within the converter output

voltage V

OUT

is settled must be shorter than the Soft-

Start Phase T

Soft-Start

(see Figure 11).

By means of Soft-Start there is an effective

minimization of current and voltage stresses on the

external Power Switch, the clamp circuit and the output

overshoot and prevents saturation of the transformer

during Start-Up.

x3 .6 5

P W M O P

Im proved

Current M ode

P W M C o m p a ra to r

Is e n se

S o ft-S ta rt C o m p ara to r

6 .5 V

P W M -L atch

0 .8 V

F B

O p to co u p le r

R

F B

t

5 .3 V

V

S oftS

G a te D rive r

t

T

S oft-S tart

5 .6 V

6 .5 V

R

F B

6 .5 V

P o w e r-U p R e s e t

C 4

5 .3 V

C 3

4 .8 V

R

S o ft-S ta rt

F B

R

S

Q

Q

E rro r-L a tc h

R

S

Q

Q

P W M -L a tc h

G 2

C lo c k

G a te

D riv e r

5 .6 V

S o ftS

69

,

1

◊

=

-

-

-

Start

Soft

Start

Soft

Start

Soft

R

T

C

Version 2.0 10 1 Feb 2002

ICE2AS01/G

ICE2BS01/G

Functional Description

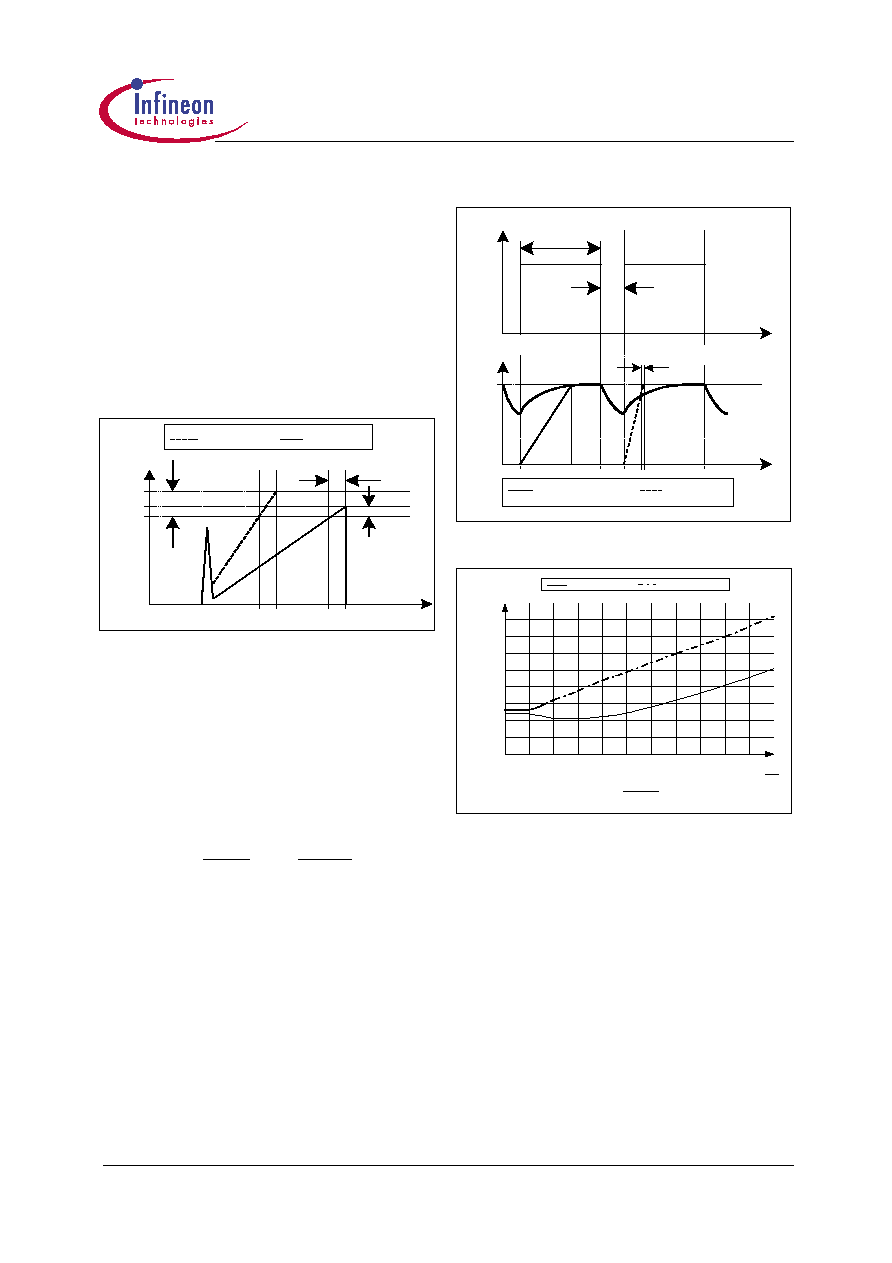

Figure 11

Start Up Phase

3.4

Oscillator and Frequency

Reduction

3.4.1

Oscillator

The oscillator generates a frequency f

switch

= 100kHz. A

resistor, a capacitor and a current source and current

sink which determine the frequency are integrated. The

charging and discharging current of the implemented

oscillator capacitor are internally trimmed, in order to

achieve a very accurate switching frequency. The ratio

of controlled charge to discharge current is adjusted to

reach a max. duty cycle limitation of D

max

=0.72.

3.4.2

Frequency Reduction

The frequency of the oscillator is depending on the

voltage at pin FB. The dependence is shown in Figure

12. This feature allows a power supply to operate at

lower frequency at light loads thus lowering the

switching losses while maintaining good cross

regulation performance and low output ripple. In case

of low power the power consumption of the whole

SMPS can now be reduced very effective. The minimal

reachable frequency is limited to 20kHz / 21.5 kHz to

avoid audible noise in any case.

Figure 12

Frequency Dependence

3.5

Current Limiting

There is a cycle by cycle current limiting realised by the

Current-Limit Comparator to provide an overcurrent

detection. The source current of the external Power

Switch is sensed via an external sense resistor R

Sense

.

By means of R

Sense

the source current is transformed to

a sense voltage V

Sense

. When the voltage V

Sense

exceeds the internal threshold voltage V

csth

the

Current-Limit-Comparator immediately turns off the

gate drive. To prevent the Current Limiting from

distortions caused by leading edge spikes a Leading

Edge Blanking is integrated at the Current Sense.

Furthermore a Propagation Delay Compensation is

added to support the immedeate shut down of the

Power Switch in case of overcurrent.

3.5.1

Leading Edge Blanking

Figure 13

Leading Edge Blanking

Each time when the external Power Switch is switched

on a leading spike is generated due to the primary-side

capacitances and secondary-side rectifier reverse

t

t

V

S o ftS

t

5 .3 V

4 .8 V

T

S o ft-S ta rt

V

O U T

V

F B

V

O U T

T

S ta rt-U p

f

standby

f

norm

1,0

1,1

1,2

1,3

1,4

1,5

1,6

1,7

1,8

1,9

2

FB

V

V

kHz

OS

C

f

f

norm

:

ICE2BS01

ICE2AS01

67kHz

100kHz

f

standby

:

20kHz

21.5kHz

t

V

S en s e

V

c s th

t

L E B

= 2 2 0 n s

Version 2.0 11 1 Feb 2002

ICE2AS01/G

ICE2BS01/G

Functional Description

recovery time. To avoid a premature termination of the

switching pulse this spike is blanked out with a time

constant of t

LEB

= 220ns. During that time the output of

the Current-Limit Comparator cannot switch off the

gate drive.

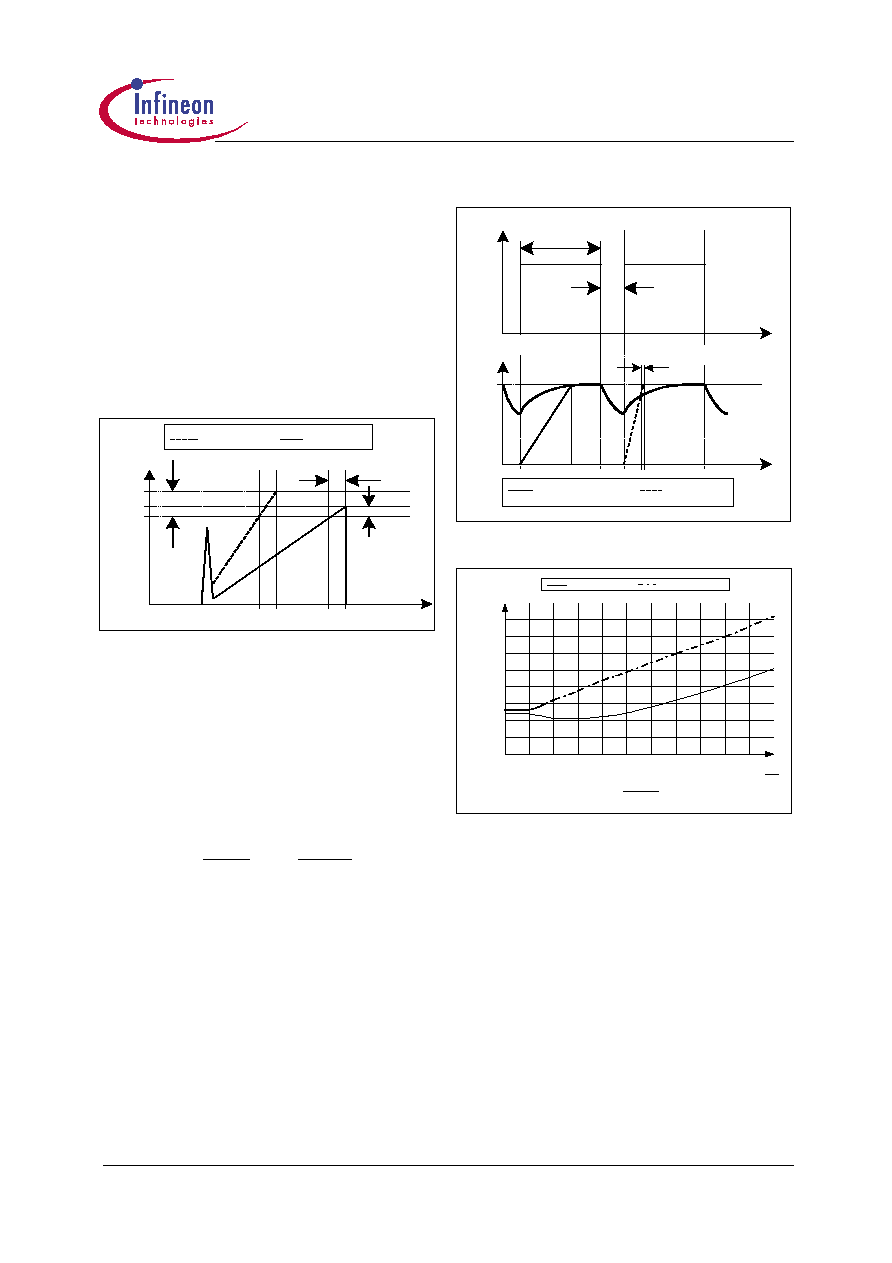

3.5.2

Propagation Delay Compensation

In case of overcurrent detection the shut down of the

external Power Switch is delayed due to the

propagation delay of the circuit. This delay causes an

overshoot of the peak current I

peak

which depends on

the ratio of dI/dt of the peak current (see Figure 14).

.

Figure 14

Current Limiting

The overshoot of Signal2 is bigger than of Signal1 due

to the steeper rising waveform.

A propagation delay compensation is integrated to

bound the overshoot dependent on dI/dt of the rising

primary current. That means the propagation delay

time between exceeding the current sense threshold

V

csth

and the switch off of the external Power Switch is

compensated over temperature within a range of at

least

.

So current limiting is now capable in a very accurate

way (see Figure 16).

E.g. I

peak

= 0.5A with R

Sense

= 2 . Without propagation

delay compensation the current sense threshold is set

to a static voltage level V

csth

=1V. A current ramp of

dI/dt = 0.4A/µs, that means dV

Sense

/dt = 0.8V/µs, and a

propagation delay time of i.e. t

Propagation Delay

=180ns

leads then to an I

peak

overshoot of 12%. By means of

propagation delay compensation the overshoot is only

about 2% (see Figure 15).

The propagation delay compensation is done by

means of a dynamic threshold voltage V

csth

(see Figure

15). In case of a steeper slope the switch off of the

driver is earlier to compensate the delay.

Figure 15

Dynamic Voltage Threshold V

csth

Figure 16

Overcurrent Shutdown

3.6

PWM-Latch

The oscillator clock output applies a set pulse to the

PWM-Latch when initiating the external Power Switch

conduction. After setting the PWM-Latch can be reset

by the PWM-OP, the Soft-Start-Comparator, the

Current-Limit-Comparator, Comparator C3 or the

Error-Latch of the Protection Unit. In case of reseting

the driver is shut down immediately.

3.7

Driver

The driver is a fast totem pole gate drive, which is

designed to avoid cross conduction currents and which

is equipped with a Zener diode Z1 (see Figure 17) in

order to improve the control of the gate attached power

t

I

S e n s e

I

L im it

t

P ro p a g a tio n D e la y

I

O v e rs h o o t1

I

p e a k 1

S ig n a l1

S ig n a l2

I

O v e rs h o o t2

I

p e a k 2

dt

dV

dt

dI

R

Sense

peak

Sense

1

0

◊

t

V

csth

V

OSC

Signal1

Signal2

V

Sense

Propagation Delay

max. Duty Cycle

off time

t

0,9

0,95

1

1,05

1,1

1,15

1,2

1,25

1,3

0

0,2

0,4

0,6

0,8

1

1,2

1,4

1,6

1,8

2

with compensation

without compensation

dt

dV

Sense

s

V

µ

Se

n

s

e

V

V

Version 2.0 12 1 Feb 2002

ICE2AS01/G

ICE2BS01/G

Functional Description

transistors as well as to protect them against

undesirable gate overvoltages.

Figure 17

Gate Driver

At voltages below the undervoltage lockout threshold

V

VCCoff

the gate drive is active low.

The driver-stage is optimized to minimize EMI and to

provide high circuit efficiency. This is done by reducing

the switch on slope when reaching the external Power

Switch threshold. This is achieved by a slope control of

the rising edge at the driver's output (see Figure 18).

Figure 18

Gate Rising Slope

Thus the leading switch on spike is minimized. When

the external Power Switch is switched off, the falling

shape of the driver is slowed down when reaching 2V

to prevent an overshoot below ground. Furthermore the

driver circuit is designed to eliminate cross conduction

of the output stage.

3.8

Protection Unit (Auto Restart Mode)

An overload, open loop and overvoltage detection is

integrated within the Protection Unit. These three

failure modes are latched by an Error-Latch. Additional

thermal shutdown is latched by the Error-Latch. In case

of those failure modes the Error-Latch is set after a

blanking time of 5µs and the external Power Switch is

shut down. That blanking prevents the Error-Latch from

distortions caused by spikes during operation mode.

3.8.1

Overload & Open loop with normal

load

Figure 19

Auto Restart Mode

Figure 19 shows the Auto Restart Mode in case of

overload or open loop with normal load. The detection

of open loop or overload is provided by the Comparator

C3, C4 and the AND-gate G2 (see Figure20).

Z 1

V C C

1

P W M -L a tch

G a te

t

V

G a te

5 V

C

L o ad

= 1 n F

ca . t = 1 3 0 n s

O ve rloa d & O p en lo op/no rm a l lo ad

F B

t

4 .8 V

5 .3 V

S o ftS

5 µ s B la n k in g

F a ilu re

D e te c tio n

S o ft-S ta rt P h a s e

V C C

1 3 .5 V

8 .5 V

t

D riv e r

t

T

R e s tart

T

B u rs t1

t

Version 2.0 13 1 Feb 2002

ICE2AS01/G

ICE2BS01/G

Functional Description

Figure 20

FB-Detection

The detection is activated by C4 when the voltage at

pin SoftS exceeds 5.3V. Till this time the IC operates in

the Soft-Start Phase. After this phase the comparator

C3 can set the Error-Latch in case of open loop or

overload which leads the feedback voltage V

FB

to

exceed the threshold of 4.8V. After latching VCC

decreases till 8.5V and inactivates the IC. At this time

the external Soft-Start capacitor is discharged by the

internal transistor T1 due to Power Down Reset. When

the IC is inactive VCC increases till V

CCon

= 13.5V by

charging the Capacitor C

VCC

by means of the Start-Up

Resistor R

Start-Up

. Then the Error-Latch is reset by

Power Up Reset and the external Soft-Start capacitor

C

Soft-Start

is charged by the internal pullup resistor R

Soft-

Start

. During the Soft-Start Phase which ends when the

voltage at pin SoftS exceeds 5.3V the detection of

overload and open loop by C3 and G2 is inactive. In this

way the Start Up Phase is not detected as an overload.

But the Soft-Start Phase must be finished within the

Start Up Phase to force the voltage at pin FB below the

failure detection threshold of 4.8V.

3.8.2

Overvoltage due to open loop with

no load

Figure 21

Auto Restart Mode

Figure 21 shows the Auto Restart Mode for open loop

and no load condition. In case of this failure mode the

converter output voltage increases and also VCC. An

additional protection by the comparators C1, C2 and

the AND-gate G1 is implemented to consider this

failure mode (see Figure 22).

R

S o ft-S ta rt

6 .5 V

C

S o ft-S ta rt

C 4

5 .3 V

C 3

4 .8 V

G 2

T 1

E rro r-L a tch

P o w e r U p R e se t

R

F B

6 .5 V

F B

S o ftS

O pe n loop & no loa d c onditio n

t

D riv e r

1 3 .5 V

1 6 .5 V

F B

4 .8 V

5 µ s B la n k in g

F a ilu re

D e te c tio n

5 .3 V

S o ftS

4 .0 V

O v e rv o lta g e

D e te c tio n P h a s e

S o ft-S ta rt P h a s e

t

t

T

R e s ta rt

T

B u rs t2

V C C

8 .5 V

O v e rv o lta g e D e te c tio n

t

Version 2.0 14 1 Feb 2002

ICE2AS01/G

ICE2BS01/G

Functional Description

Figure 22

Overvoltage Detection

The overvoltage detection is provided by Comparator

C1 only in the first time during the Auto Restart Mode

till the Soft-Start voltage exceeds the threshold of the

Comparator C2 at 4.0V and the voltage at pin FB is

above 4.8V. When VCC exceeds 16.5V during the

overvoltage detection phase C1 can set the Error-Latch

and the Burst Phase during Auto Restart Mode is

finished earlier. In that case T

Burst2

is shorter than T

Soft-

Start

. By means of C2 the normal operation mode is

prevented from overvoltage detection due to varying of

VCC concerning the regulation of the converter output.

When the voltage V

SoftS

is above 4.0V the overvoltage

detection by C1 is deactivated.

3.8.3

Thermal Shut Down

Thermal Shut Down is latched by the Error-Latch when

junction temperature T

j

of the pwm controller is

exceeding an internal threshold of 140∞C. In that case

the IC switches in Auto Restart Mode.

Note:

All the values which are mentioned in the

functional description are typical. Please refer

to Electrical Characteristics for min/max limit

values.

6 .5 V

C

S o ft-S ta rt

V C C

R

S o ft-S ta rt

C 1

1 6 .5 V

C 2

4 .0 V

T 1

S o ftS

G 1

E rro r L a tch

P o w e r U p R e se t

ICE2AS01/G

ICE2BS01/G

Electrical Characteristics

Version 2.0 15 1 Feb 2002

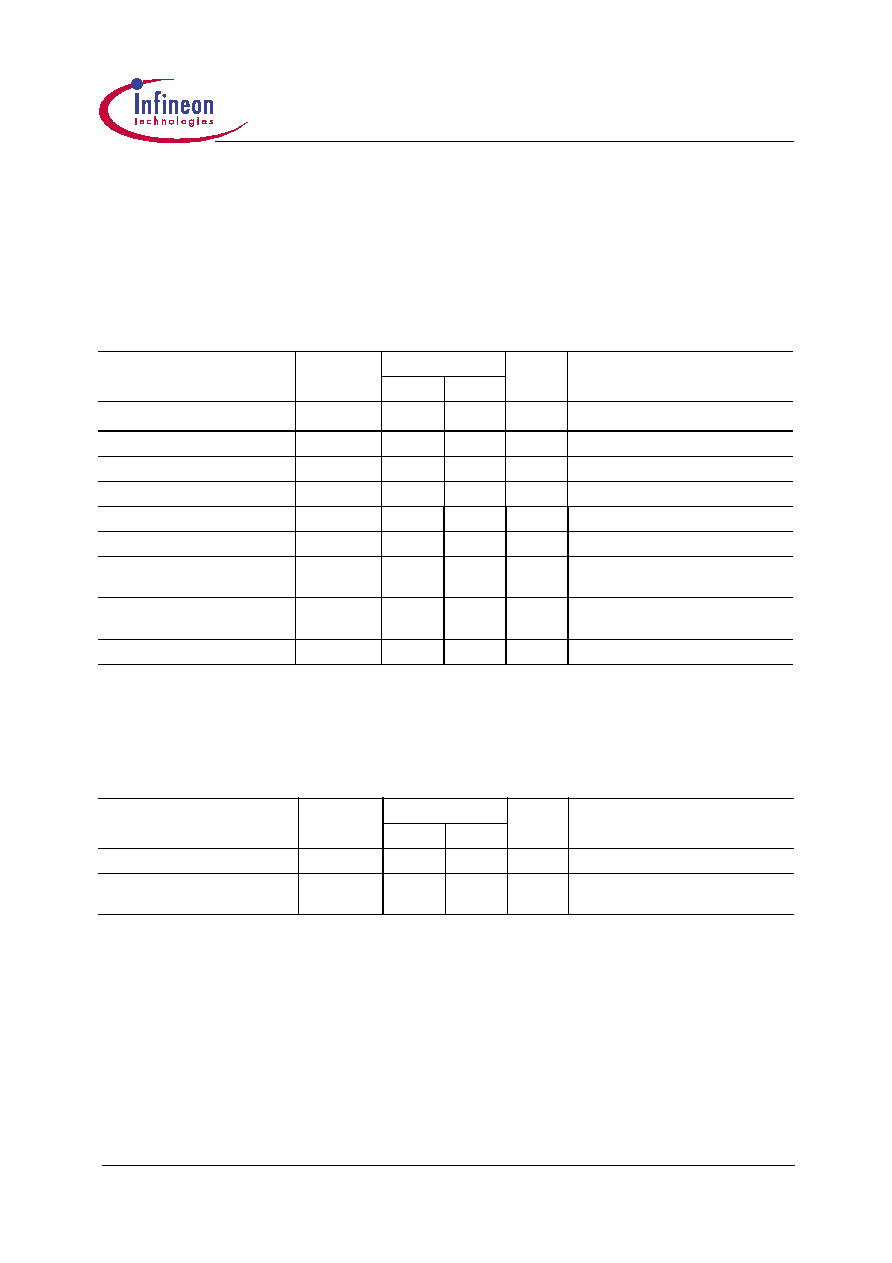

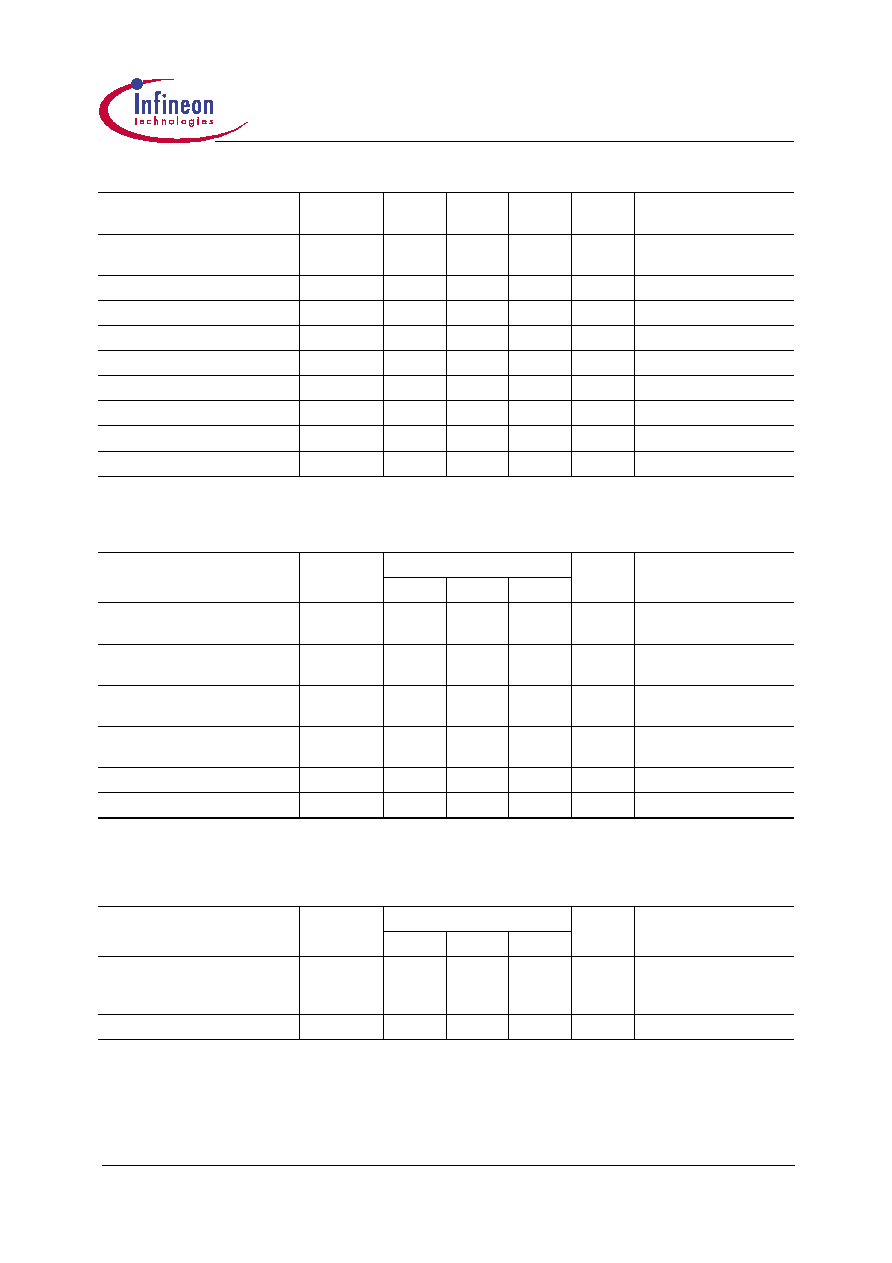

4

Electrical Characteristics

4.1

Absolute Maximum Ratings

Note:

Absolute maximum ratings are defined as ratings, which when being exceeded may lead to destruction

of the integrated circuit. For the same reason make sure, that any capacitor that will be connected to pin 6

(

V

CC) is discharged before assembling the application circuit.

4.2

Operating Range

Note:

Within the operating range the IC operates as described in the functional description.

Parameter

Symbol

Limit Values

Unit

Remarks

min.

max.

V

CC

Supply Voltage

V

CC

-0.3

22

V

FB Voltage

V

FB

-0.3

6.5

V

SoftS Voltage

V

SoftS

-0.3

6.5

V

ISense

I

Sense

-0.3

3

V

Junction Temperature

T

j

-40

150

∞

C

Controller & CoolMOS

Storage Temperature

T

S

-50

150

∞

C

Thermal Resistance

Junction-Ambient

R

thJA

-

90

K/W

P-DIP-8-4

Thermal Resistance

Junction-Ambient

R

thJA

-

185

K/W

P-DSO-8-3

ESD Capability

1)

1)

Equivalent to discharging a 100pF capacitor through a 1.5 k

series resistor

V

ESD

-

2

kV

Human Body Model

Parameter

Symbol

Limit Values

Unit

Remarks

min.

max.

V

CC

Supply Voltage

V

CC

V

CCoff

21

V

Junction Temperature of

Controller

T

JCon

-25

130

∞

C

limited due to thermal shut down of

controller

ICE2AS01/G

ICE2BS01/G

Electrical Characteristics

Version 2.0 16 1 Feb 2002

4.3

Characteristics

Note:

The electrical characteristics involve the spread of values guaranteed within the specified supply voltage

and junction temperature range

T

J

from ≠ 25

∞

C to 125

∞

C.Typical values represent the median values,

which are related to 25∞C. If not otherwise stated, a supply voltage of

V

CC

= 15 V is assumed.

4.3.1

Supply Section

4.3.2

Internal Voltage Reference

4.3.3

Control Section

Parameter

Symbol

Limit Values

Unit

Test Condition

min.

typ.

max.

Start Up Current

I

VCC1

-

27

55

µA

V

CC

=V

CCon

-0.1V

Supply Current with Inactiv

Gate

I

VCC2

-

5.3

7

mA

V

SoftS

= 0

I

FB

= 0

Supply Current with Activ Gate

ICE2AS01/G

I

VCC3

-

6.5

8

mA

V

SoftS

= 5V

I

FB

= 0

C

Gate

= 1nF

Supply Current with Activ Gate

ICE2BS01/G

I

VCC3

-

6

7.5

mA

V

SoftS

= 5V

I

FB

= 0

C

Gate

= 1nF

VCC Turn-On Threshold

VCC Turn-Off Threshold

VCC Turn-On/Off Hysteresis

V

CCon

V

CCoff

V

CCHY

13

-

4.5

13.5

8.5

5

14

-

5.5

V

V

V

Parameter

Symbol

Limit Values

Unit

Test Condition

min.

typ.

max.

Trimmed Reference Voltage

V

REF

6.37

6.50

6.63

V

measured at pin FB

Parameter

Symbol

Limit Values

Unit

Test Condition

min.

typ.

max.

Oscillator Frequency

ICE2AS01/G

f

OSC1

93

100

107

kHz

V

FB

= 4V

Oscillator Frequency

ICE2BS01/G

f

OSC3

62

67

72

kHz

V

FB

= 4V

Reduced Osc. Frequency

ICE2AS01/G

f

OSC2

-

21.5

-

kHz

V

FB

= 1V

Reduced Osc. Frequency

ICE2AS01/G

f

OSC4

-

20

-

kHz

V

FB

= 1V

ICE2AS01/G

ICE2BS01/G

Electrical Characteristics

Version 2.0 17 1 Feb 2002

4.3.4

Protection Unit

4.3.5

Current Limiting

Frequency Ratio f

osc1

/f

osc2

ICE2AS01/G

4.5

4.65

4.9

Frequency Ratio f

osc3

/f

osc4

ICE2BS01/G

3.18

3.35

3.53

Max Duty Cycle

D

max

0.67

0.72

0.77

Min Duty Cycle

D

min

0

-

-

V

FB

< 0V

PWM-OP Gain

A

V

3.45

3.65

3.85

Max. Level of Voltage Ramp

V

Max-Ramp

-

0.85

-

V

V

FB

Operating Range Min Level V

FBmin

0.3

-

-

V

V

FB

Operating Range Max level V

FBmax

-

-

4.6

V

Feedback Resistance

R

FB

3.0

3.7

4.9

k

Soft-Start Resistance

R

Soft-Start

42

50

62

k

Parameter

Symbol

Limit Values

Unit

Test Condition

min.

typ.

max.

Over Load & Open Loop

Detection Limit

V

FB2

4.65

4.8

4.95

V

V

SoftS

> 5.5V

Activation Limit of Overload &

Open Loop Detection

V

SoftS1

5.15

5.3

5.46

V

V

FB

> 5V

Deactivation Limit of

Overvoltage Detection

V

SoftS2

3.88

4.0

4.12

V

V

FB

> 5V

V

CC

> 17.5V

Overvoltage Detection Limit

V

VCC1

16

16.5

17.2

V

V

SoftS

< 3.8V

V

FB

> 5V

Latched Thermal Shutdown

T

jSD

130

140

150

∞C

guaranteed by design

Spike Blanking

t

Spike

-

5

-

µs

Parameter

Symbol

Limit Values

Unit

Test Condition

min.

typ.

max.

Peak Current Limitation (incl.

Propagation Delay Time)

(see Figure 7)

V

csth

0.95

1.00

1.05

V

dV

sense

/ dt = 0.6V/

µ

s

Leading Edge Blanking

t

LEB

-

220

-

ns

ICE2AS01/G

ICE2BS01/G

Electrical Characteristics

Version 2.0 18 1 Feb 2002

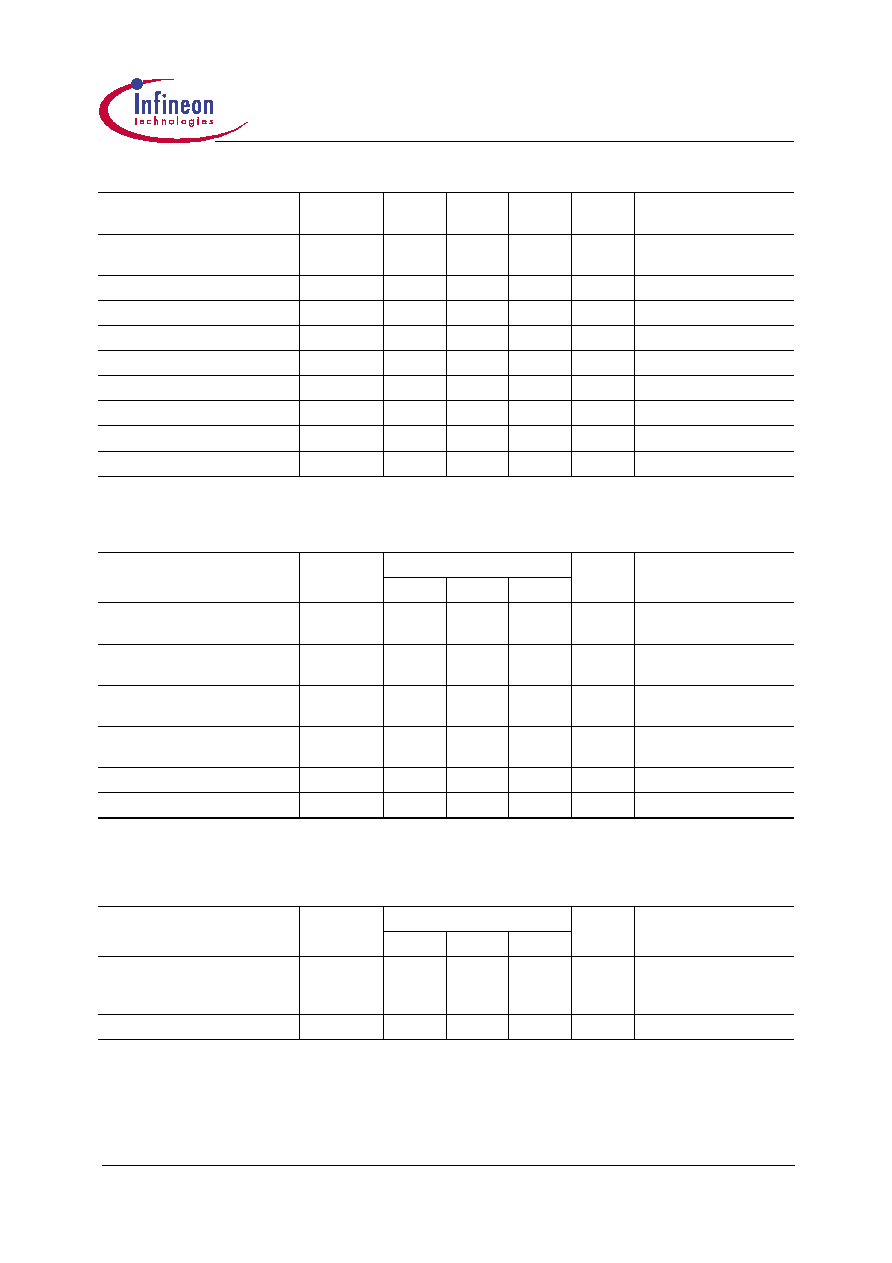

4.3.6

Driver Section

Parameter

Symbol

Limit Values

Unit

Test Condition

min.

typ.

max.

GATE Low Voltage

V

GATE

-

0.95

1.2

V

V

VCC

= 5 V

I

Gate

= 5 mA

-

1.0

1.5

V

V

VCC

= 5 V

I

Gate

= 20 mA

-

0.88

-

V

I

Gate

= 0 A

-

1.6

2.2

V

I

Gate

= 50 mA

-0.2

0.2

-

V

I

Gate

= -50 mA

GATE High Voltage

V

GATE

-

11.5

-

V

V

VCC

= 20V

C

L

= 4.7nF

-

10

-

V

V

VCC

= 11V

C

L

= 4.7nF

-

7.5

-

V

V

VCC

= V

VCCoff

+ 0.2V

C

L

= 4.7nF

GATE Rise Time

t

r

-

160

-

ns

V

Gate

= 2V ...9V

1)

C

L

= 4.7nF

1)

Transient reference value

GATE Fall Time

t

f

-

65

-

ns

V

Gate

= 9V ...2V

1)

C

L

= 4.7nF

GATE Current, Peak,

Rising Edge

I

GATE

-0.5

-

-

A

C

L

= 4.7nF

2)

2)

Design characteristics (not meant for production testing)

GATE Current, Peak,

Falling Edge

I

GATE

-

-

0.7

A

C

L

= 4.7nF

2)

Version 2.0 19 1 Feb 2002

ICE2AS01/G

ICE2BS01/G

Typical Performance Characteristics

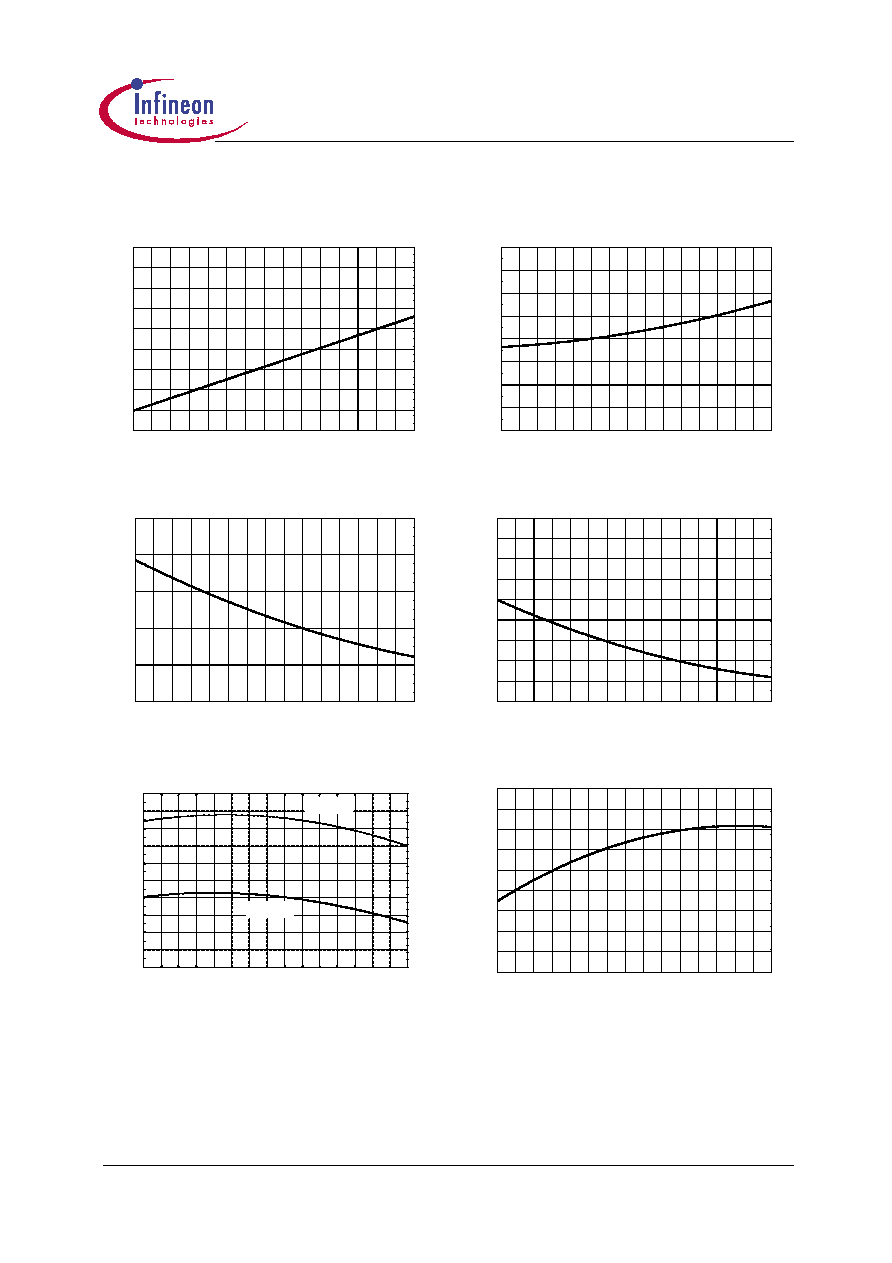

5

Typical Performance Characteristics

Figure 23

Start Up Current I

VCC1

vs. T

j

Figure 24

Supply Current I

VCC2

vs. T

j

Figure 25

Supply Current I

VCC3

vs. T

j

Figure 26

VCC Turn-On Threshold V

VCCon

vs. T

j

Figure 27

VCC Turn-Off Threshold V

VCCoff

vs. T

j

Figure 28

VCC Turn-On/Off HysteresisV

VCCHY

vs. T

j

Junction Temperature [∞C]

St

a

r

t

Up

Cu

r

r

e

n

t

I

V

CC1

[µA

]

P

I

-

001-

190101

22

24

26

28

30

32

34

36

38

40

-25 -15

-5

5

15

25

35

45

55

65

75

85

95 105 115 125

Junction Temperature [∞C]

S

uppl

y C

u

r

r

e

nt I

V

CC2

[m

A

]

P

I

-

003-

190101

4,5

4,8

5,1

5,4

5,7

6,0

-25 -15

-5

5

15

25

35

45

55

65

75

85

95 105 115 125

Junction Temperature [∞C]

S

upply C

u

r

r

e

nt I

V

CC3

[m

A

]

P

I

-

002-

190101

5,0

5,2

5,4

5,6

5,8

6,0

6,2

6,4

6,6

6,8

7,0

-25 -15 -5

5

15 25 35 45 55 65 75 85 95 105 115 125

ICE2ASO1

ICE2ASO1G

ICE2BSO1

ICE2BSO1G

Junction Temperature [∞C]

V

C

C

Tur

n-O

n

Thr

eshol

d V

CCo

n

[V

]

P

I

-

004-

190101

13,42

13,44

13,46

13,48

13,50

13,52

13,54

13,56

13,58

-25 -15

-5

5

15

25

35

45

55

65

75

85

95 105 115 125

Junction Temperature [∞C]

V

C

C

Tur

n-O

ff Thr

eshol

d V

V

CCo

f

f

[V

]

P

I

-

005-

190101

8,40

8,43

8,46

8,49

8,52

8,55

8,58

8,61

8,64

8,67

-25 -15

-5

5

15

25

35

45

55

65

75

85

95 105 115 125

Junction Temperature [∞C]

V

C

C

Tur

n-On/Off H

yster

esis V

CCHY

[V

]

P

I

-

006-

190101

4,83

4,86

4,89

4,92

4,95

4,98

5,01

5,04

5,07

5,10

-25 -15

-5

5

15

25

35

45

55

65

75

85

95 105 115 125

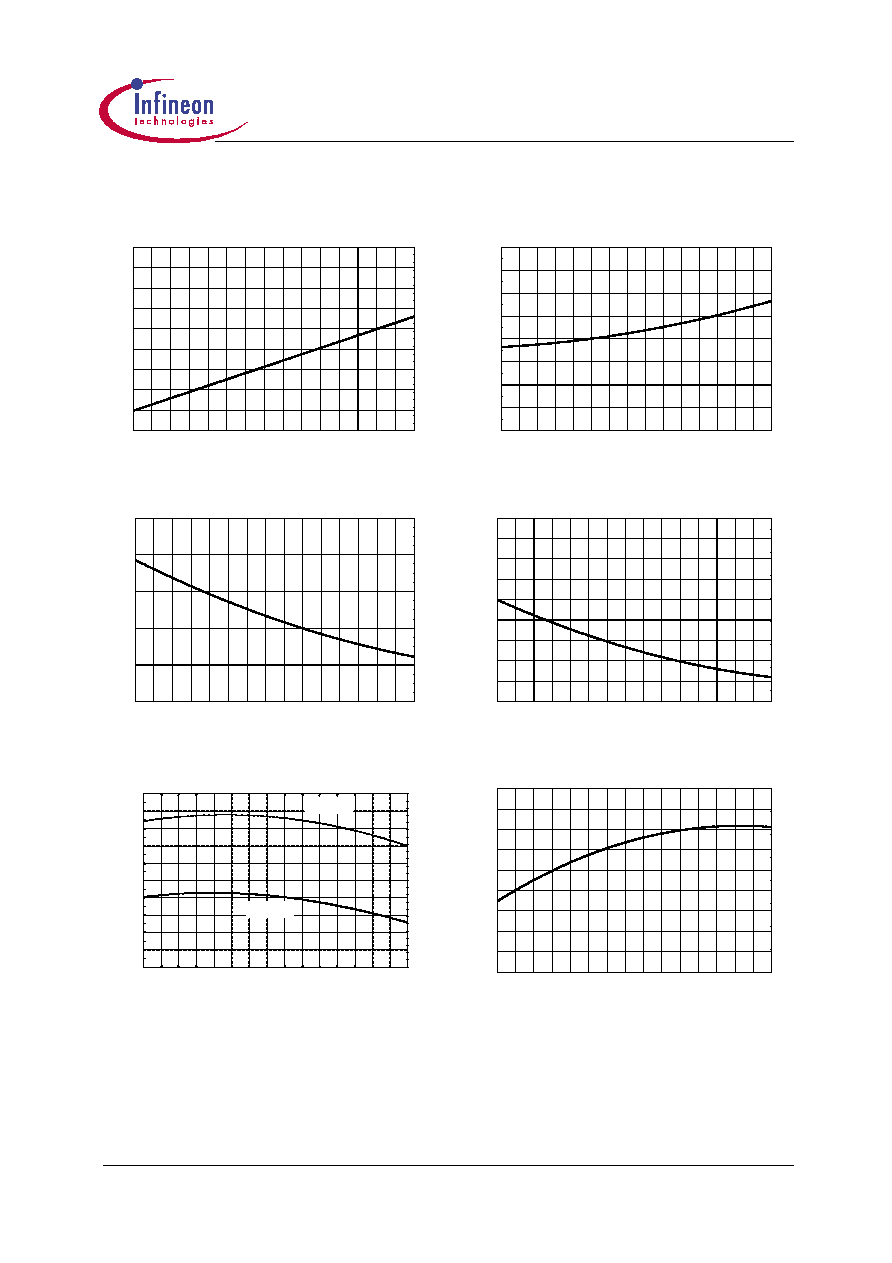

Version 2.0 20 1 Feb 2002

ICE2AS01/G

ICE2BS01/G

Typical Performance Characteristics

Figure 29

Trimmed Reference V

REF

vs. T

j

Figure 30

Oscillator Frequency f

OSC1

vs. T

j

Figure 31

Oscillator Frequency f

OSC3

vs. T

j

Figure 32

Reduced Osc. Frequency f

OSC2

vs. T

j

Figure 33

Reduced Osc. Frequency f

OSC4

vs. T

j

Figure 34

Frequency Ratio f

OSC1

/ f

OSC2

vs. T

j

Junction Temperature [∞C]

Tr

i

m

m

e

d R

e

fer

e

nce V

o

l

tage V

RE

F

[V

]

P

I

-

007-

190101

6,45

6,46

6,47

6,48

6,49

6,50

6,51

6,52

6,53

6,54

6,55

-25 -15

-5

5

15

25

35

45

55

65

75

85

95 105 115 125

Junction Temperature [∞C]

Oscillato

r

F

r

eq

u

e

n

cy f

OS

C

1

[kH

z

]

P

I

-

008-

190101

97,0

97,5

98,0

98,5

99,0

99,5

100,0

100,5

101,0

101,5

102,0

-25 -15 -5

5

15 25 35 45 55 65 75 85 95 105 115 125

ICE2ASO1

ICE2ASO1G

Junction Temperature [∞C]

Oscillato

r

F

r

eq

u

e

n

cy f

OS

C

3

[kH

z

]

P

I

-

008a-

190101

64,0

64,5

65,0

65,5

66,0

66,5

67,0

67,5

68,0

68,5

69,0

69,5

70,0

-25 -15 -5

5

15 25 35 45 55 65 75 85 95 105 115 125

ICE2BSO1

ICE2BSO1G

Junction Temperature [∞C]

R

e

duced Osc. Fr

equency f

OS

C

2

[kH

z

]

P

I

-

009-

190101

20,8

20,9

21,0

21,1

21,2

21,3

21,4

21,5

21,6

21,7

21,8

-25 -15 -5

5

15 25 35 45 55 65 75 85 95 105 115 125

ICE2ASO1

ICE2ASO1G

Junction Temperature [∞C]

R

e

duced Osc. Fr

equency f

OS

C

4

[kH

z

]

P

I

-

009a-

190101

19,0

19,2

19,4

19,6

19,8

20,0

20,2

20,4

20,6

20,8

21,0

-25 -15 -5

5

15 25 35 45 55 65 75 85 95 105 115 125

ICE2BSO1

ICE2BSO1G

Junction Temperature [∞C]

Fr

equency R

a

ti

o f

OS

C

1

/f

OS

C

2

P

I

-

010-

190101

4,50

4,52

4,54

4,56

4,58

4,60

4,62

4,64

4,66

4,68

4,70

-25 -15 -5

5

15 25 35 45 55 65 75 85 95 105 115 125

ICE2ASO1

ICE2ASO1G

Version 2.0 21 1 Feb 2002

ICE2AS01/G

ICE2BS01/G

Typical Performance Characteristics

Figure 35

Frequency Ratio f

OSC3

/ f

OSC4

vs. T

j

Figure 36

Max. Duty Cycle vs. T

j

Figure 37

PWM-OP Gain A

V

vs. T

j

Figure 38

Feedback Resistance R

FB

vs. T

j

Figure 39

Soft-Start Resistance R

Soft-Start

vs. T

j

Figure 40

Detection Limit V

FB2

vs. T

j

Junction Temperature [∞C]

Fr

equency R

a

ti

o f

OS

C

3

/f

OS

C

4

P

I

-

010a-

190101

3,25

3,27

3,29

3,31

3,33

3,35

3,37

3,39

3,41

3,43

3,45

-25 -15 -5

5

15 25 35 45 55 65 75 85 95 105 115 125

ICE2BSO1

ICE2BSO1G

Junction Temperature [∞C]

Max. D

u

ty C

ycle

P

I

-

011-

190101

0,710

0,712

0,714

0,716

0,718

0,720

0,722

0,724

0,726

0,728

0,730

-25 -15

-5

5

15

25

35

45

55

65

75

85

95 105 115 125

Junction Temperature [∞C]

P

W

M-OP

Gain

A

V

P

I

-

012-

190101

3,60

3,61

3,62

3,63

3,64

3,65

3,66

3,67

3,68

3,69

3,70

-25 -15

-5

5

15

25

35

45

55

65

75

85

95 105 115 125

Junction Temperature [∞C]

Feedback R

esistance R

FB

[kOhm

]

P

I

-

013-

190101

3,50

3,55

3,60

3,65

3,70

3,75

3,80

3,85

3,90

3,95

4,00

-25 -15

-5

5

15

25

35

45

55

65

75

85

95 105 115 125

Junction Temperature [∞C]

S

o

ft-S

tar

t

R

esistance R

S

o

ft-S

tar

t

[kOhm

]

P

I

-

014-

190101

40

42

44

46

48

50

52

54

56

58

-25 -15

-5

5

15

25

35

45

55

65

75

85

95 105 115 125

Junction Temperature [∞C]

D

e

tection Lim

i

t V

FB

2

[V

]

P

I

-

015-

190101

4,75

4,76

4,77

4,78

4,79

4,80

4,81

4,82

4,83

4,84

4,85

-25 -15

-5

5

15

25

35

45

55

65

75

85

95 105 115 125

Version 2.0 22 1 Feb 2002

ICE2AS01/G

ICE2BS01/G

Typical Performance Characteristics

Figure 41

Detection Limit V

Soft-Start1

vs. T

j

Figure 42

Detection Limit V

Soft-Start2

vs. T

j

Figure 43

Overvoltage Detection Limit V

VCC1

vs. T

j

Figure 44

Peak Current Limitation V

csth

vs. T

j

Figure 45

Leading Edge Blanking V

VCC1

vs. T

j

Junction Temperature [∞C]

D

e

tecti

on Li

m

i

t V

S

o

ft-S

tar

t1

[V

]

P

I

-

016-

190101

5,25

5,26

5,27

5,28

5,29

5,30

5,31

5,32

5,33

5,34

5,35

-25 -15

-5

5

15

25

35

45

55

65

75

85

95 105 115 125

Junction Temperature [∞C]

D

e

tecti

on Li

m

i

t V

S

o

ft-S

tar

t2

[V

]

P

I

-

017-

190101

3,95

3,96

3,97

3,98

3,99

4,00

4,01

4,02

4,03

4,04

4,05

-25 -15

-5

5

15

25

35

45

55

65

75

85

95 105 115 125

Junction Temperature [∞C]

Over

voltage D

e

tection Lim

i

t V

V

CC1

[V

]

P

I

-

018-

190101

16,20

16,25

16,30

16,35

16,40

16,45

16,50

16,55

16,60

16,65

16,70

16,75

16,80

-25 -15

-5

5

15

25

35

45

55

65

75

85

95 105 115 125

Junction Temperature [∞C]

P

eak C

u

r

r

e

nt Lim

i

tation V

csth

[V

]

P

I

-

019-

190101

0,990

0,992

0,994

0,996

0,998

1,000

1,002

1,004

1,006

1,008

1,010

-25 -15

-5

5

15

25

35

45

55

65

75

85

95 105 115 125

Junction Temperature [∞C]

Leadi

ng E

dge B

l

anki

ng t

LE

B

[ns]

P

I

-

020-

190101

180

190

200

210

220

230

240

250

260

270

280

-25 -15

-5

5

15

25

35

45

55

65

75

85

95 105 115 125

ICE2AS01/G

ICE2BS01/G

Outline Dimension

Version 2.0 23 1 Feb 2002

Preliminary Specification

6

Outline Dimension

Figure 46

Figure 47

Dimensions in mm

P-DSO-8-3

(Plastic Dual Small

Outline)

P-DIP-8-4

(Plastic Dual In-line

Package)

Qualit‰t hat f¸r uns eine umfassende

Bedeutung. Wir wollen allen Ihren

Anspr¸chen in der bestmˆglichen

Weise gerecht werden. Es geht uns also

nicht nur um die Produktqualit‰t ≠

unsere Anstrengungen gelten

gleichermaþen der Lieferqualit‰t und

Logistik, dem Service und Support

sowie allen sonstigen Beratungs- und

Betreuungsleistungen.

Dazu gehˆrt eine bestimmte

Geisteshaltung unserer Mitarbeiter.

Total Quality im Denken und Handeln

gegen¸ber Kollegen, Lieferanten und

Ihnen, unserem Kunden. Unsere

Leitlinie ist jede Aufgabe mit ,,Null

Fehlern" zu lˆsen ≠ in offener

Sichtweise auch ¸ber den eigenen

Arbeitsplatz hinaus ≠ und uns st‰ndig

zu verbessern.

Unternehmensweit orientieren wir uns

dabei auch an ,,top" (Time Optimized

Processes), um Ihnen durch grˆþere

Schnelligkeit den entscheidenden

Wettbewerbsvorsprung zu verschaffen.

Geben Sie uns die Chance, hohe

Leistung durch umfassende Qualit‰t zu

beweisen.

Wir werden Sie ¸berzeugen.

Quality takes on an allencompassing

significance at Semiconductor Group.

For us it means living up to each and

every one of your demands in the best

possible way. So we are not only

concerned with product quality. We

direct our efforts equally at quality of

supply and logistics, service and

support, as well as all the other ways in

which we advise and attend to you.

Part of this is the very special attitude of

our staff. Total Quality in thought and

deed, towards co-workers, suppliers

and you, our customer. Our guideline is

"do everything with zero defects", in an

open manner that is demonstrated

beyond your immediate workplace, and

to constantly improve.

Throughout the corporation we also

think in terms of Time Optimized

Processes (top), greater speed on our

part to give you that decisive

competitive edge.

Give us the chance to prove the best of

performance through the best of quality

≠ you will be convinced.

h t t p : / / w w w . i n f i n e o n . c o m

Total Quality Management

Published by Infineon Technologies AG