PRELIMINARY

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is

granted by this document or by the sale of Intel products. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability

whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a

particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life

saving, or life sustaining applications. Intel retains the right to make changes to specifications and product descriptions at any time, without notice. The Intel 430TX

PCIset may contain design defects or errors known as errata. Current characterized errata are available on request. Third-party brands and names are the property of

their respective owners.

© INTEL CORPORATION 1997

February 1997

Order Number: 290559-001

Supports Mobile and Desktop

Supports the Pentium

Æ

Processor

Family Host Bus at 66 MHz and 60 MHz

at 3.3V and 2.5V

PCI 2.1 Compliant

Integrated Data Path

Integrated DRAM Controller

4 Mbytes to 256 MBytes main

memory

64-Mbit DRAM/SDRAM Technology

Support

FPM (Fast Page Mode), EDO and

SDRAM DRAM Support

6 RAS Lines Available

Integrated Programmable Strength

for DRAM Interface

CAS-Before-RAS Refresh, Extended

Refresh and Self Refresh for EDO

CAS-Before-RAS and Self Refresh

for SDRAM

Integrated L2 Cache Controller

64-MB DRAM Cacheability

Direct Mapped Organization--Write

Back Only

Supports 256K and 512K Pipelined

Burst SRAM and DRAM Cache

SRAM

Cache Hit Read/Write Cycle

Timings at 3-1-1-1

Back-to-Back Read/Write Cycles at

3-1-1-1-1-1-1-1

64K x 32 SRAM also supported

Fully Synchronous, Minimum Latency

30/33-MHz PCI Bus Interface

Five PCI Bus Masters (including

PIIX4)

10 DWord PCI-to-DRAM Read

Prefetch Buffer

18 DWord PCI-DRAM Post Buffer

Multi-Transaction Timer to Support

Multiple Short PCI Transactions

Power Management Features

PCI CLKRUN# Support

Dynamic Stop Clock Support

Suspend to RAM (STR)

Suspend to Disk (STD)

Power On Suspend (POS)

Internal Clock Control

SDRAM and EDO Self Refresh

During Suspend

ACPI Support

Compatible SMRAM (C_SMRAM)

and Extended SMRAM (E_SMRAM)

SMM Writeback Cacheable in

E_SMRAM Mode up to 1 MB

3.3/5V DRAM, 3.3/5V PCI 3.3/5V Tag

and 3.3/2.5 SRAM Support

Test Features

NAND Tree Support for all Pins

Supports the Universal Serial Bus

(USB)

324-Pin MBGA 430TX PCIset

Xcelerated Controller (MTXC) with

integrated Data Paths

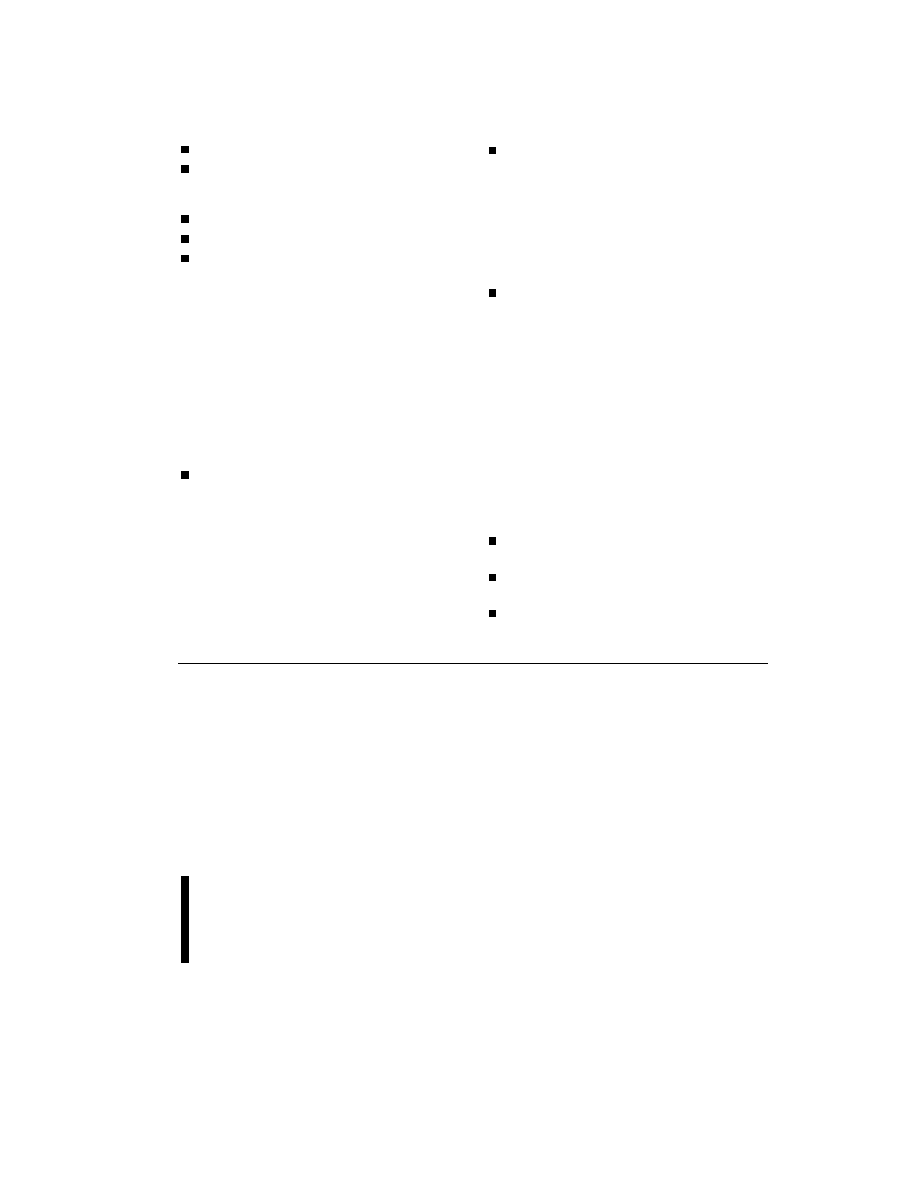

The Intel 430TX PCIset (430TX) consists of the 82439TX System Controller (MTXC) and the 82371AB PCI ISA

IDE Xcelerator (PIIX4). The 430TX supports both mobile and desktop architectures. The 430TX forms a Host-to-

PCI bridge and provides the second level cache control and a full function 64-bit data path to main memory. The

MTXC integrates the cache and main memory DRAM control functions and provides bus control to transfers

between the CPU, cache, main memory, and the PCI Bus. The second level (L2) cache controller supports a

writeback cache policy for cache sizes of 256 Kbytes and 512 Kbytes. Cacheless designs are also supported.

The cache memory can be implemented with pipelined burst SRAMs or DRAM cache SRAMs. An external Tag

RAM is used for the address tag and an internal Tag RAM for the cache line status bits. For the MTXC DRAM

controller, six rows are supported for up to 256 Mbytes of main memory. The MTXC is highly integrated by

including the Data Path into the same BGA chip. Using the snoop ahead feature, the MTXC allows PCI masters

to achieve full PCI bandwidth. For increased system performance, the MTXC integrates posted write and read

prefetch buffers. The 430TX integrates many Power Management features that enable the system to save power

when the system resources become idle.

INTEL 430TX PCISET: 82439TX SYSTEM

CONTROLLER (MTXC)

82439TX (MTXC)

2

PRELIMINARY

A [ 3 1 : 0 ]

D E V S E L #

P A R

R E Q [ 3 : 0 ] #

P H L D #

P L O C K #

I R D Y #

T R D Y #

F R A M E #

C / B E [ 3 : 0 ] #

C A S [ 7 : 0 ] # / D Q M [ 7 : 0 ] #

S C A S [ A , B ] #

M W E B #

C K E / M A A 0 , C K E B / M A A 1

C A C H E #

B R D Y #

W / R #

H I T M #

B O F F #

N A #

K E N # / I N V

B E [ 7 : 0 ] #

M / I O #

D /C #

C O E #

C A D V #

C a c h e

I n t e r f a c e

H D [ 6 3 : 0 ]

A D [ 3 1 : 0 ]

C C S #

H C L K I N

H L O C K #

S M I A C T #

T I O [ 7 : 0 ]

K R Q A K / C S 4 _ 6 4 #

B W E #

R A S [ 5 : 0 ] # / C S [ 5 : 0 ] #

S R A S [ A , B ] #

M D [ 6 3 : 0 ]

C l o c k s ,

R e s e t ,

T e s t ,

a n d

P o w e r

M g n t

P C L K I N

T E S T #

S U S C L K

S U S S T A T 1 #

C L K R U N #

D R A M

I n t e r f a c e

P C I

I n t e r f a c e

H o s t

I n t e r f a c e

A D S #

E A D S #

A H O L D

T W E #

G W E #

C A D S #

R S T #

M W E #

M A [ 1 1 : 0 ]

P H L D A #

G N T [ 3 : 0 ] #

S T O P #

mtx_blk

MTXC Simplified Block Diagram

82439TX (MTXC)

3

PRELIMINARY

CONTENTS

PAGE

1.0. ARCHITECTURE OVERVIEW ........................................................................................................................6

2.0. SIGNAL DESCRIPTION ..................................................................................................................................8

2.1. MTXC Signals ...............................................................................................................................................8

2.1.1. Host Interface.........................................................................................................................................8

2.1.2. DRAM Interface ...................................................................................................................................10

2.1.3. Secondary Cache Interface .................................................................................................................12

2.1.4. PCI Interface ........................................................................................................................................13

2.1.5. Test and Clock .....................................................................................................................................14

2.1.6. Power Management .............................................................................................................................14

2.1.7. Power and Ground Pins.......................................................................................................................14

2.2. MTXC Strapping Options ............................................................................................................................15

2.3. Power Planes..............................................................................................................................................15

2.4. Power Sequencing Requirements ..............................................................................................................16

2.5. Signal States During and After a Hard Reset .............................................................................................17

3.0. REGISTER DESCRIPTION ...........................................................................................................................18

3.1. I/O Mapped Registers .................................................................................................................................18

3.1.1. PM2_CNTRL

PM2 Register Block ....................................................................................................19

3.1.2. CONFADD

Configuration Address Register .....................................................................................19

3.1.3. CONFDATA

Configuration Data Register.........................................................................................20

PCI Configuration Space Mapped Registers .....................................................................................................20

3.1.4. VID

Vendor Identification Register ....................................................................................................23

3.1.5. DID

Device Identification Register ....................................................................................................23

3.1.6. PCICMD

PCI Command Register.....................................................................................................23

3.1.7. PCISTS

PCI Status Register ............................................................................................................24

3.1.8. RID

Revision Identification Register..................................................................................................25

3.1.9. CLASSC

Class Code Register..........................................................................................................25

3.1.10. MLT

Master Latency Timer Register...............................................................................................25

3.1.11. HEDT

Header Type Register ..........................................................................................................26

3.1.12. BIST

BIST Register.........................................................................................................................26

3.1.13. ACON

Arbitration Control Register .................................................................................................26

3.1.14. PCON

PCI Control Register............................................................................................................27

3.1.15. CC

Cache Control Register.............................................................................................................27

3.1.16. CEC

Extended Cache Control Register..........................................................................................29

3.1.17. SDRAMC

SDRAM Control Register ...............................................................................................29

3.1.18. DRAMEC

DRAM Extended Control Register .................................................................................31

3.1.19. DRAMC

DRAM Control Register ....................................................................................................32

3.1.20. DRAMT

DRAM Timing Register......................................................................................................33

82439TX (MTXC)

4

PRELIMINARY

3.1.21. PAM

Programmable Attribute Map Registers (PAM[6:0])...............................................................34

3.1.22. DRB

DRAM Row Boundary Registers............................................................................................38

3.1.23. DRTH

DRAM Row Type Register High ..........................................................................................40

3.1.24. DRTL--DRAM Row Type Register Low............................................................................................41

3.1.25. MTT

Multi-Transaction Timer Register (Reserved Test Mode Register)........................................41

3.1.26. ESMRAMC

Extended System Management RAM Control Register ..............................................42

3.1.27. SMRAMC

System Management RAM Control Register................................................................43

3.1.28. MCTL

Miscellaneous Control Register............................................................................................45

4.0. FUNCTIONAL DESCRIPTION ......................................................................................................................46

4.1. Host Interface..............................................................................................................................................46

4.2. Secondary Cache Interface ........................................................................................................................46

4.2.1. Clock Latencies....................................................................................................................................49

4.2.2. Snoop Cycles.......................................................................................................................................49

4.2.3. DRAM Cache Second Level Cache Mode ..........................................................................................50

4.3. DRAM Interface ..........................................................................................................................................50

4.3.1. DRAM Organization .............................................................................................................................51

4.3.2. Configuration Requirements ................................................................................................................53

4.3.3. DRAM Address Translation .................................................................................................................57

4.3.4. DRAM Paging ......................................................................................................................................57

4.3.5. DRAM Types........................................................................................................................................57

4.3.5.1. FPM Mode.....................................................................................................................................57

4.3.5.2. EDO Mode ....................................................................................................................................57

4.3.5.3. SDRAM Mode ...............................................................................................................................57

4.3.6. Auto Detection......................................................................................................................................59

4.3.7. DRAM Performance.............................................................................................................................59

4.3.8. DRAM Refresh.....................................................................................................................................62

4.4. PCI CLK Control (CLKRUN#).....................................................................................................................62

4.4.1. Clocking States ....................................................................................................................................62

4.4.2. Operation .............................................................................................................................................62

4.5. SMRAM Memory Space .............................................................................................................................62

4.5.1. Compatible SMRAM (C_SMRAM).......................................................................................................62

4.5.2. Extended SMRAM (E_SMRAM) ..........................................................................................................62

4.5.3. SMRAM Programming Considerations................................................................................................64

4.6. Low Power States .......................................................................................................................................64

4.6.1. Chip Standby........................................................................................................................................65

4.6.2. Suspend/Resume ................................................................................................................................65

4.6.2.1. Power Transition Changes............................................................................................................66

4.7. PCI Interface ...............................................................................................................................................67

4.8. System Arbitration.......................................................................................................................................68

4.8.1. Priority Scheme and Bus Grant ...........................................................................................................68

4.8.2. CPU Policies ........................................................................................................................................70

82439TX (MTXC)

5

PRELIMINARY

5.0. CLOCKS AND RESET ..................................................................................................................................70

5.1. Clock Generation and distribution...............................................................................................................70

5.2. RESET Sequencing ....................................................................................................................................70

6.0. PINOUT INFORMATION ...............................................................................................................................71

7.0. MTXC PACKAGE INFORMATION................................................................................................................76

8.0. TESTABILITY.................................................................................................................................................79

8.1. NAND Tree Mode .......................................................................................................................................79

8.2. NAND Chain Mode .....................................................................................................................................79