| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 440GXAGP | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Document Outline

- Intel Æ 440GX AGPset Datasheet:

- Intel 82443GX Features

- Contents

- Architectural Overview

- Signal Description

- 2.1 Host Interface Signals

- 2.2 DRAM Interface

- 2.3 PCI Interface (Primary)

- 2.4 Primary PCI Sideband Interface

- 2.5 AGP Interface Signals

- 2.6 Clocks, Reset, and Miscellaneous

- 2.7 Power-Up/Reset Strap Options

- Register Description 3

- 3.1 I/O Mapped Registers

- 3.2 PCI Configuration Space Access

- 3.3 Host-to-PCI Bridge Registers (Device 0)

- 3.4 PCI-to-PCI Bridge Registers (Device 1)

- Functional Description 4

- 4.1 System Address Map

- 4.2 Host Interface

- 4.3 DRAM Interface

- 4.4 PCI Interface

- 4.5 AGP Interface

- 4.6 Data Integrity Support

- 4.7 System Clocking

- 4.8 Power Management

- Pinout and Package Information 5

- 5.1 82443GX Pinout

- 5.2 Package Dimensions

- Testability 6

- 6.1 Test Mode Activation

- 6.2 Tester Powerup Sequence

- 6.3 Test Mode Details

- Intel around the world locations

Intel

Æ

440GX AGPset:

82443GX Host Bridge/Controller

Datasheet

June 1998

Order Number: 290638-001

82443GX Host Bridge

Datasheet

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual

property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability

whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to

fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not

intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

The 82443GX chipset may contain design defects or errors known as errata which may cause the product to deviate from published specifications.

Current characterized errata are available upon request.

I

2

C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I

2

C bus/protocol and was developed by Intel.

Implementations of the I

2

C bus/protocol or the SMBus bus/protocol may require licenses from various entities, including Philips Electronics N.V. and

North American Philips Corporation.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by:

calling 1-800-548-4725 or

by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1997-1998

*Third-party brands and names are the property of their respective owners.

82443GX Host Bridge

Datasheet

iii

Intel 82443GX Features

The Intel

Æ

440GX AGPset is intended for the Pentium

Æ

II processor and Pentium

Æ

II XeonTM

processor platforms. The 82443GX Host Bridge provides a Host-to-PCI bridge, optimized

DRAM controller and data path, and an Accelerated Graphic Port (AGP) interface. AGP is a

high performance, component level interconnect targeted at 3D graphics applications and is

based on a set of performance enhancements to PCI.

The I/O subsystem portion of the Intel

Æ

440GX AGPset platform is based on the 82371EB

(PIIX4E), a highly integrated version of the Intel's PCI-ISA bridge family.

∑

Processor/System bus support

-- Optimized for Pentium

Æ

II and

Pentium

Æ

II XeonTM processors at

100 MHz system bus frequency

-- Supports full symmetric

Multiprocessor (SMP) Protocol for

up to two processors; I/O APIC

related buffer management support

(WSC# signal)

-- In-order transaction and dynamic

deferred transaction support

-- Supports GTL+ and AGTL+ bus

driver technology (gated GTL+

receivers for reduced power)

∑

Integrated DRAM controller

-- 16 MB to 2 GB

-- Supports up to 4 double-sided

DIMMs (8 rows memory)

-- 64-bit data interface with ECC

support (SDRAM only)

-- Unbuffered and Registered

SDRAM (Synchronous) Support

(x-1-1-1 access @ 100 MHz)

-- Enhanced SDRAM Open Page

Architecture Support for 16-, 64-,

128-, and 256-Mbit* DRAM devices

with 2k, 4k and 8k page sizes

∑

PCI bus interface

-- PCI Rev. 2.1, 3.3V and 5V, 33MHz

interface compliant

-- PCI Parity Generation Support

-- Data streaming support from PCI to

DRAM

-- Delayed Transaction support for

PCI-DRAM Reads

-- Supports concurrent CPU, AGP and

PCI transactions to main memory

∑

AGP interface

-- Supports single AGP compliant

device (AGP-66/133 3.3V device)

-- AGP Specification Rev 1.0 compliant

-- AGP-data/transaction flow optimized

arbitration mechanism

-- AGP side-band interface for efficient

request pipelining without

interfering with the data streams

-- AGP-specific data buffering

-- Supports concurrent CPU, AGP and

PCI transactions to main memory

-- AGP high-priority transactions

("expedite") support

∑

Power management functions

-- Stop Clock Grant and Halt special

cycle translation (host to PCI Bus)

-- "Deep Green" Desktop support for

system suspend/resume (i.e., DRAM

and power-on suspend)

-- SDRAM self-refresh power down

support in suspend mode

-- Independent, internal dynamic clock

gating reduces average power

dissipation

-- Static STOP CLOCK support

-- Power-on Suspend mode

-- Suspend to DRAM

-- ACPI compliant power management

∑

Packaging/Voltage

-- 492 Pin BGA

-- 3.3V core & mixed 3.3V & GTL I/O

∑

Supporting I/O Bridge

-- System Management Bus (SMB)

with support for DIMM Serial

Presence Detect (SPD)

-- PCI-ISA Bridge (PIIX4E)

-- Power Management Support

-- 3.3V core and mixed 5V, 3.3V I/O

and interface to the 2.5V CPU signals

via open-drain output buffers

The Intel 82443GX may contain design defects or errors known as errata which may cause the products to deviate from

published specifications. Current characterized errata are available on request.

* Proper operation of the 82443GX AGPset with 256-Mbit SDRAM devices has not yet been verified. Intel's current plans are

to validate this feature in the second half of 1998 when 256-Mbit SDRAM devices are available.

iv

82443GX Host Bridge

Datasheet

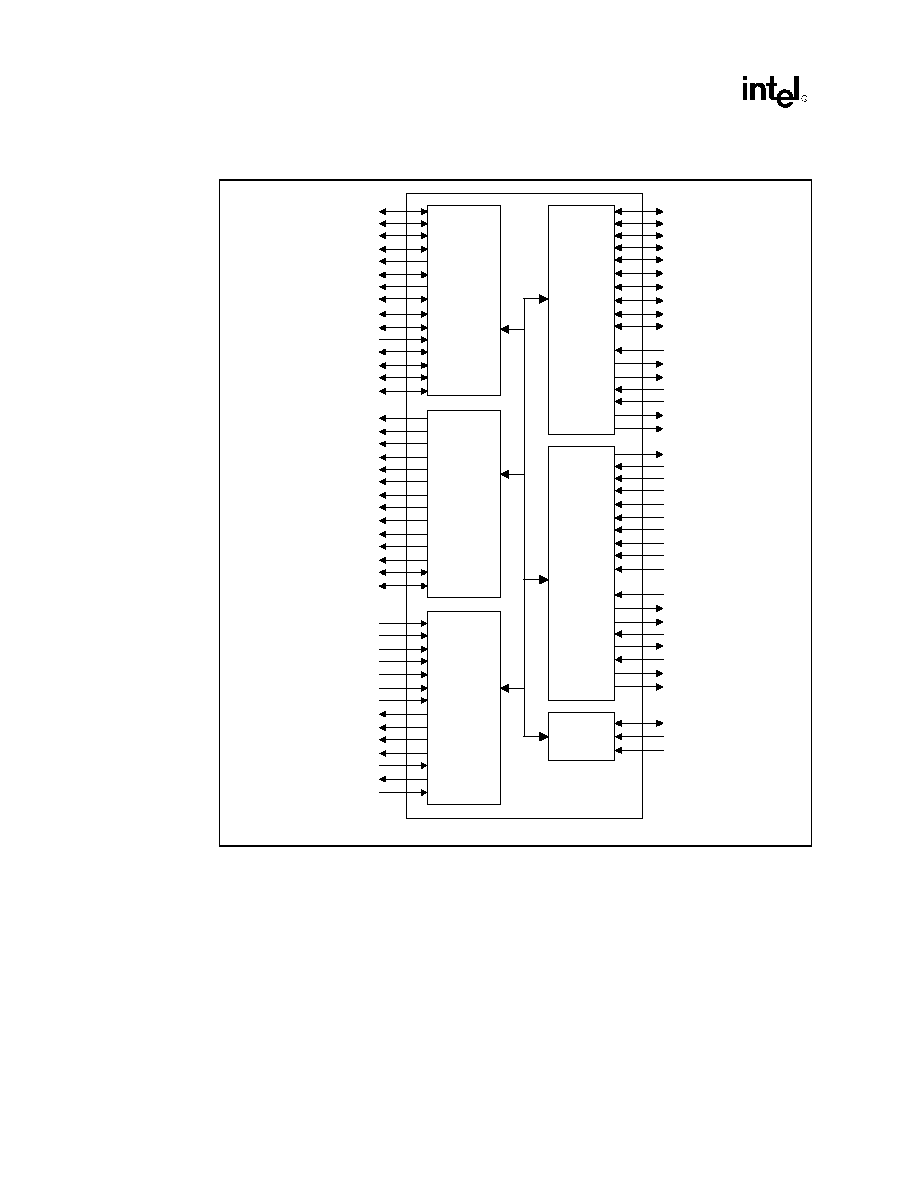

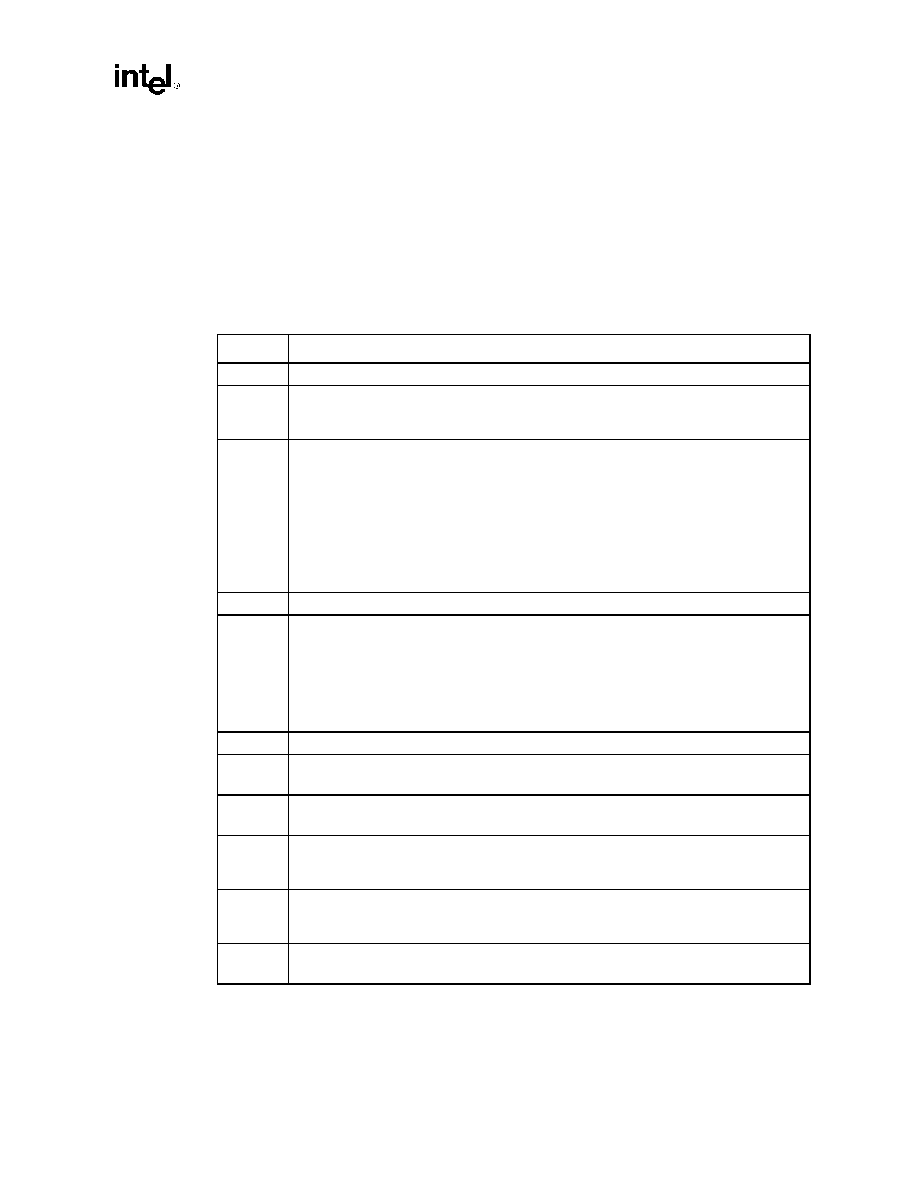

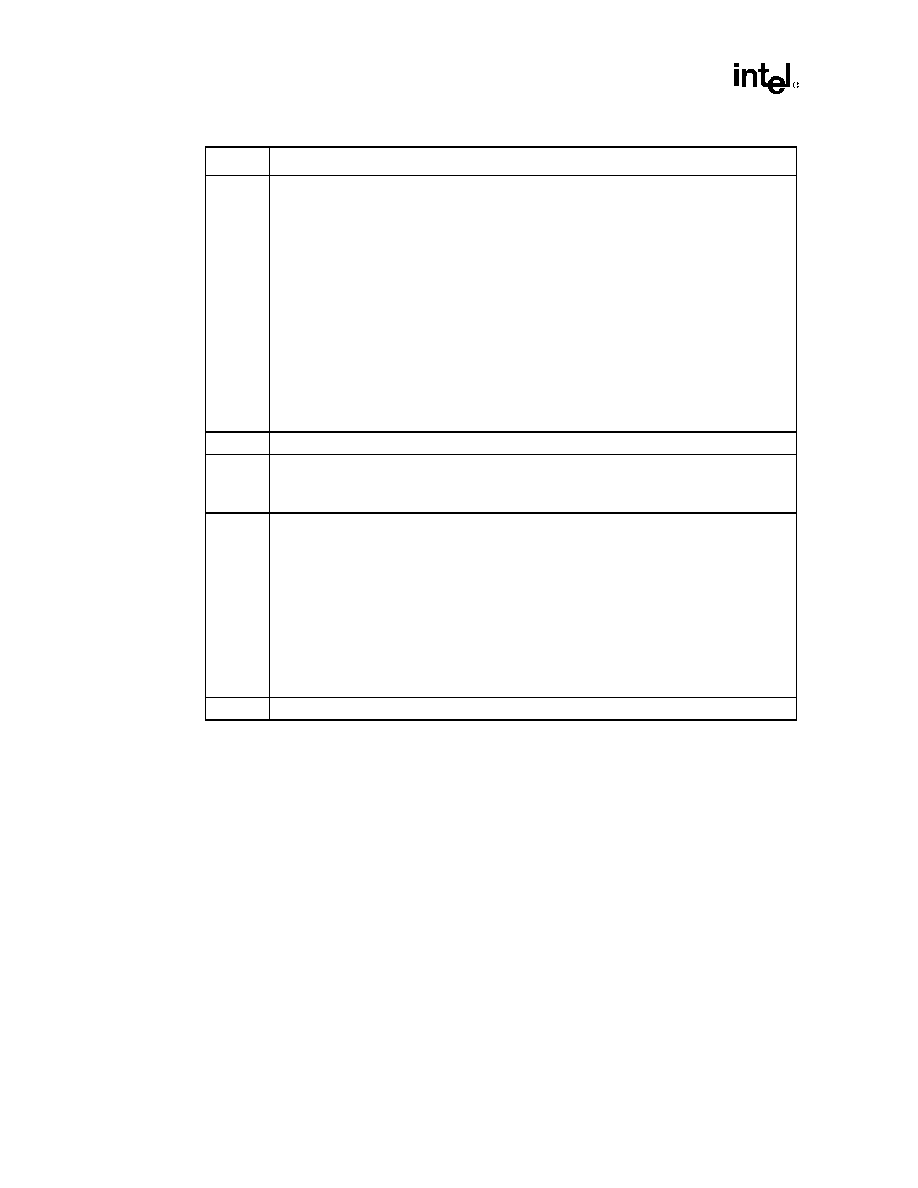

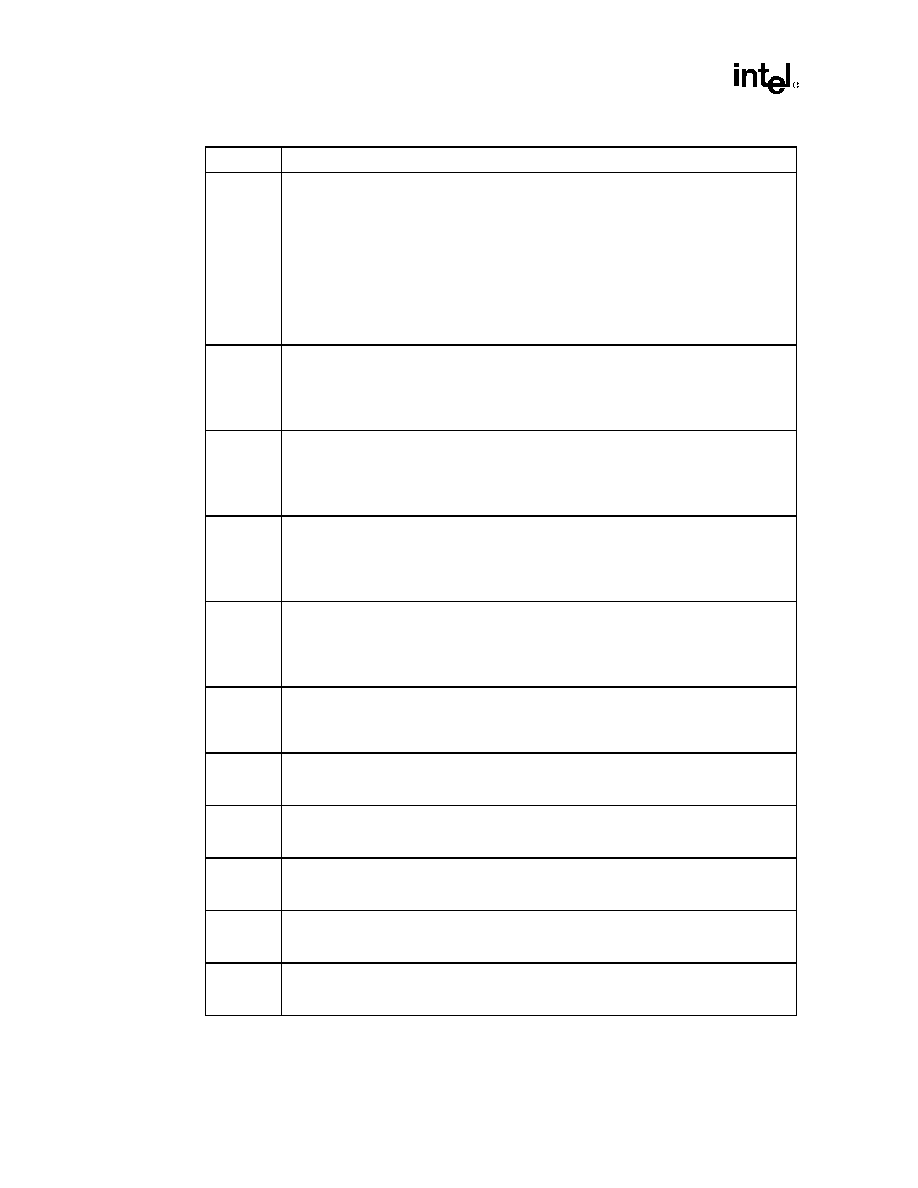

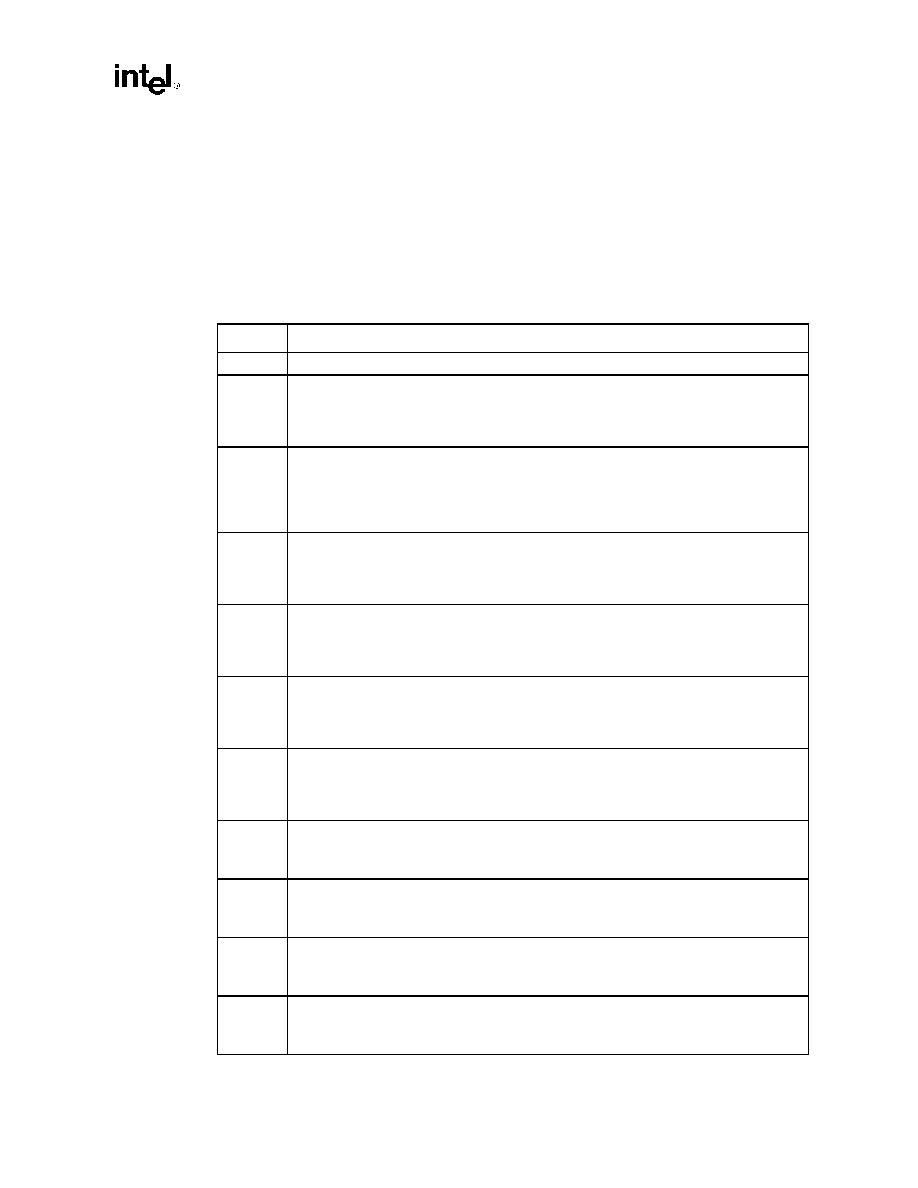

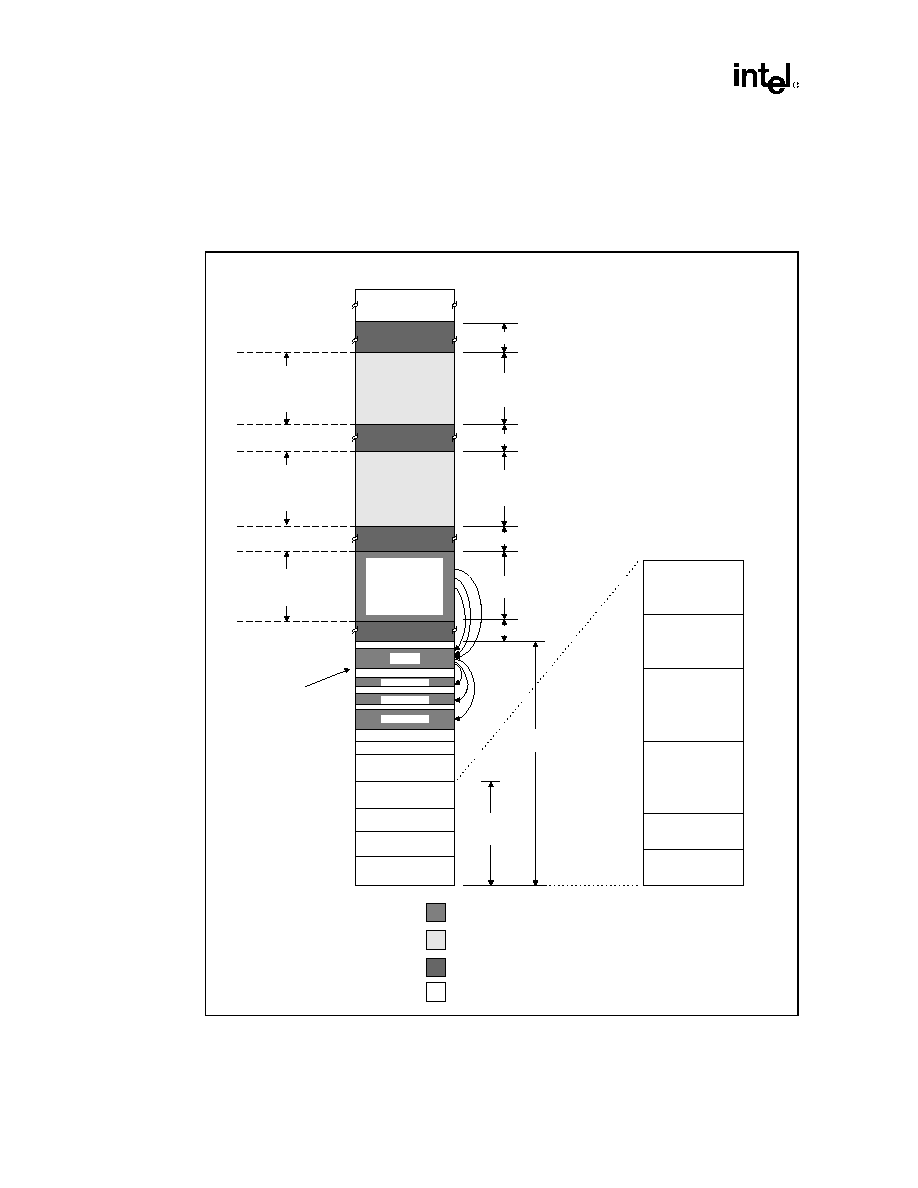

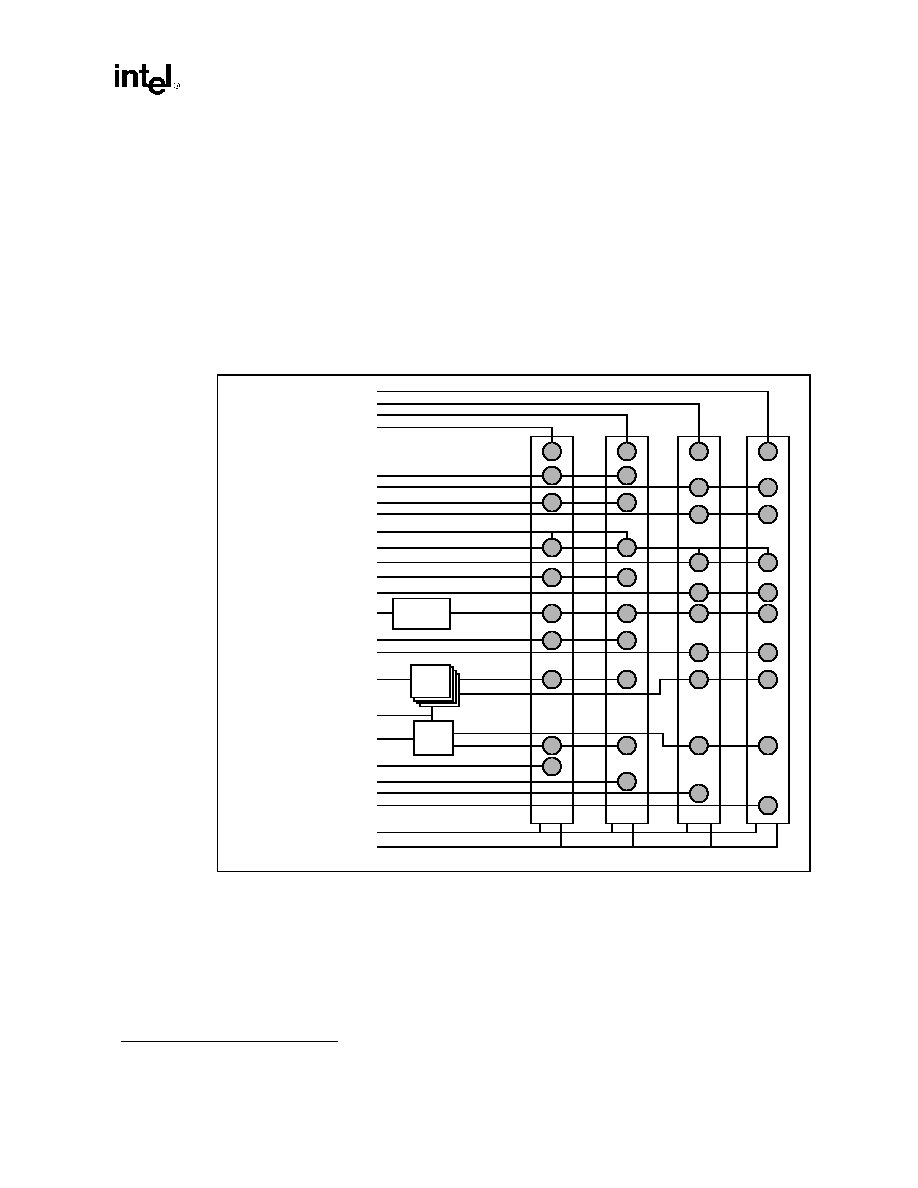

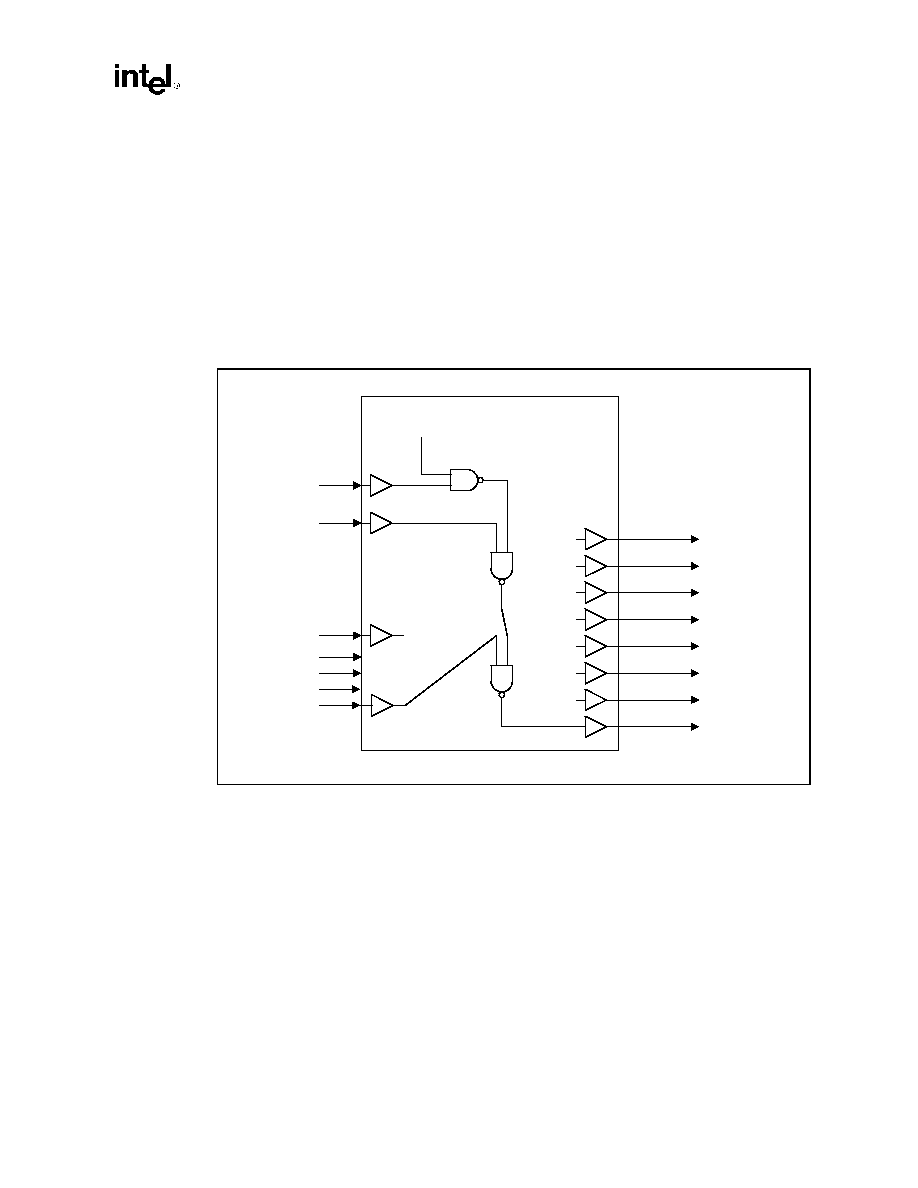

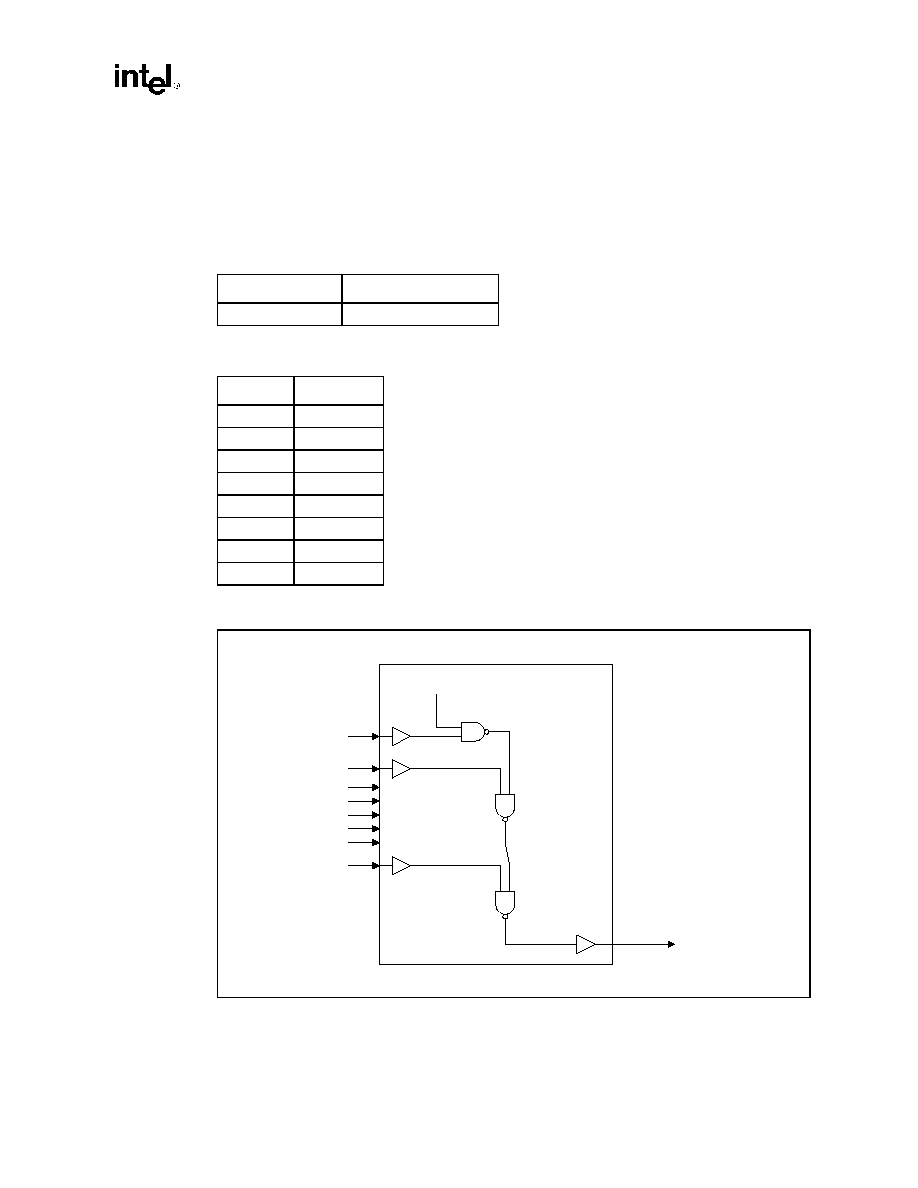

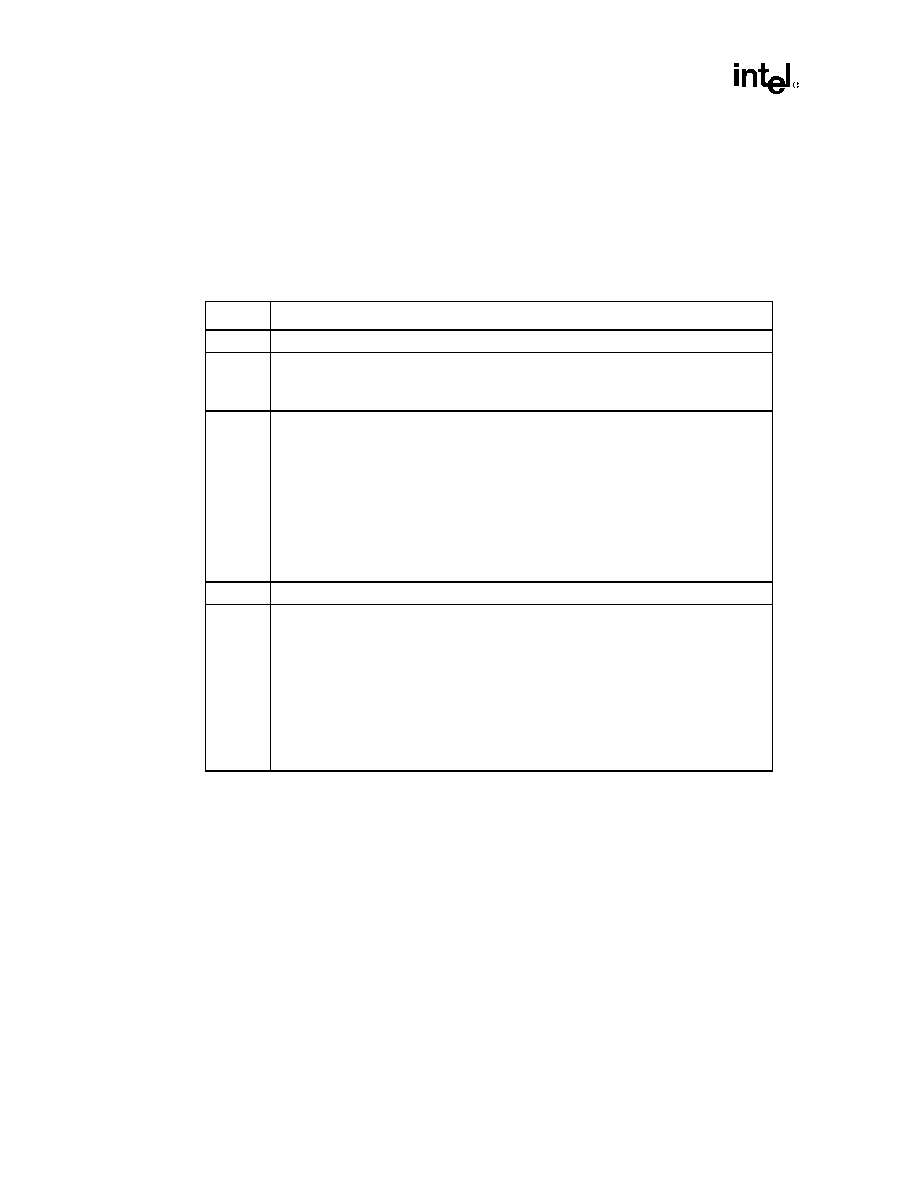

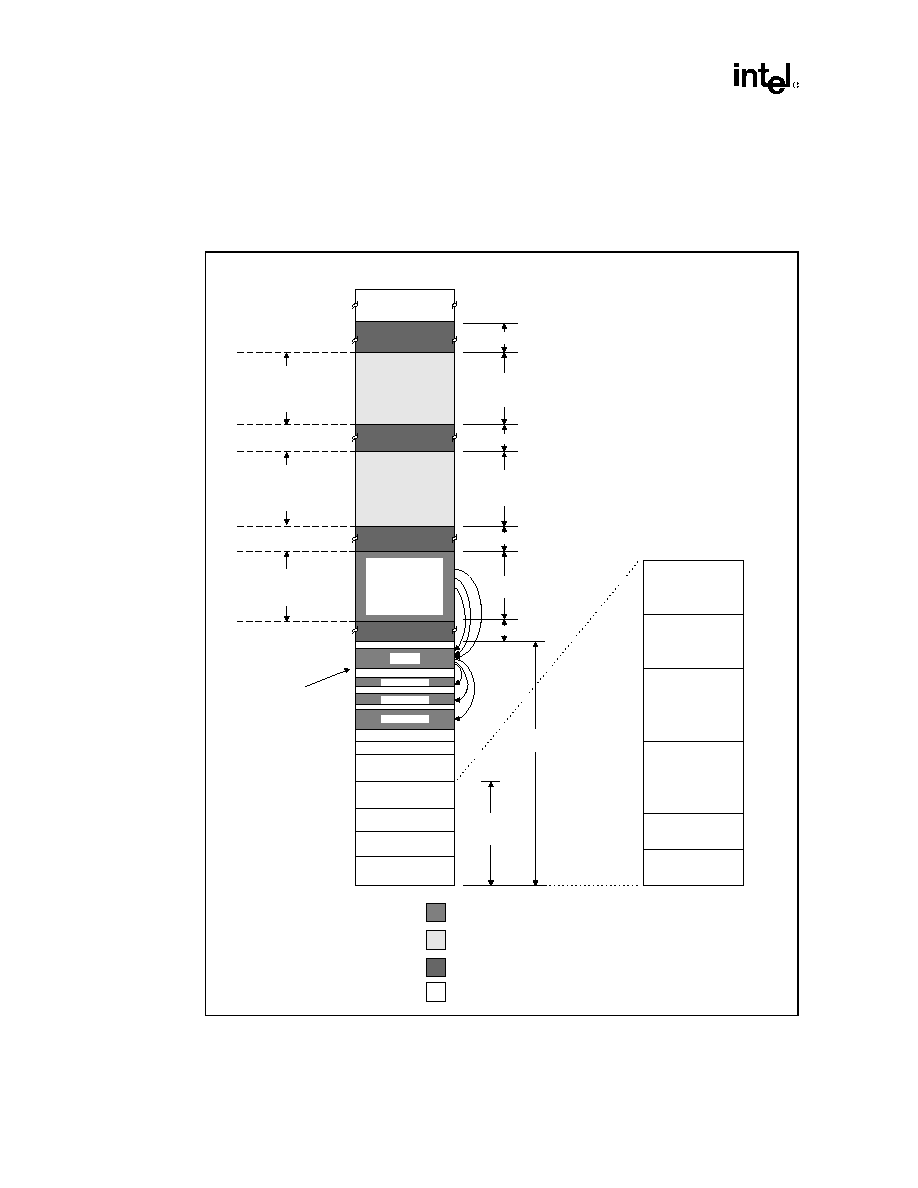

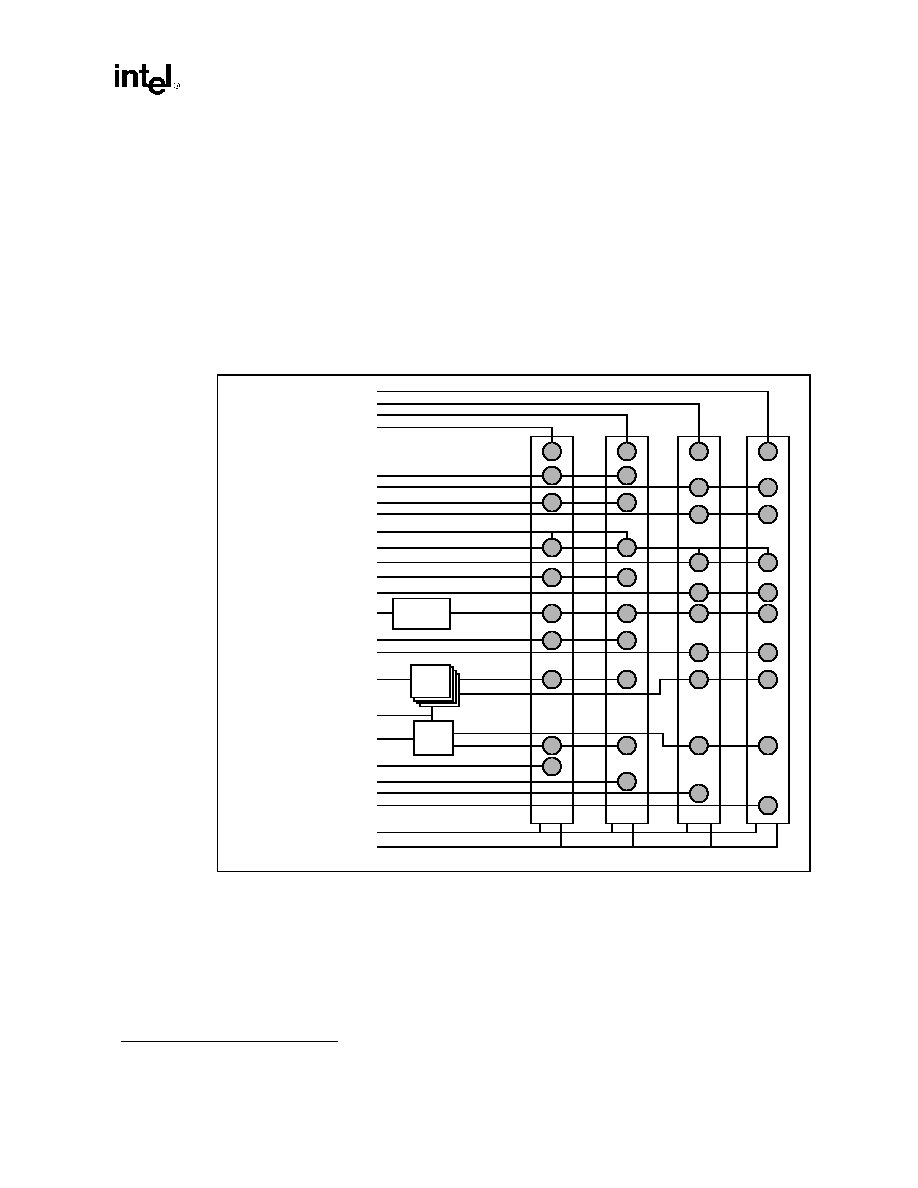

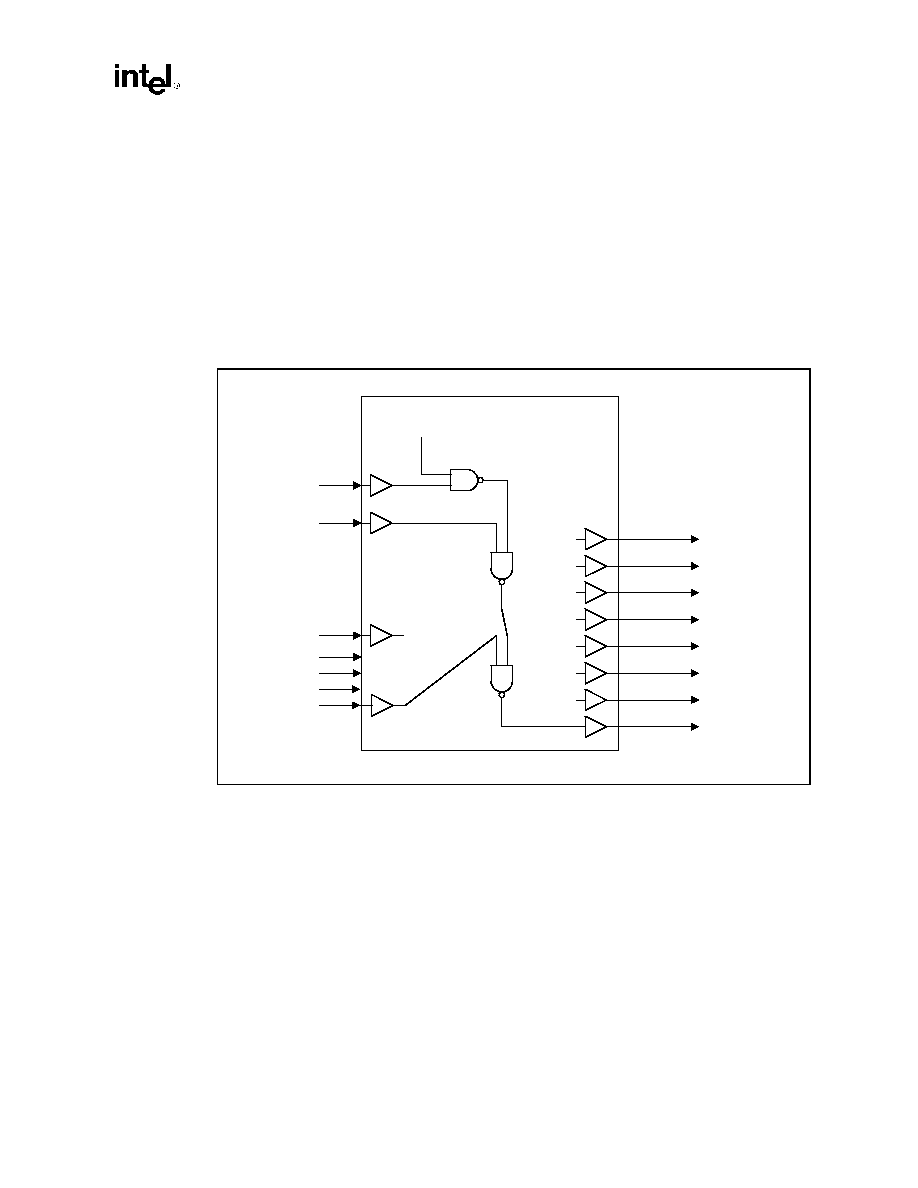

Intel 82443GX Simplified Block Diagram

GX_BLK.VSD

Host

Interface

A[31:3]#

ADS#

BPRI#

BNR#

CPURST#

DBSY#

DEFER#

HD[63:0]#

HIT#

HITM#

HLOCK#

HREQ[4:0]#

HTRDY#

DRDY#

RS[2:0]#

DRAM

Interface

CSA[7:0]#

CSB[7:0]#

DQMA[7:0]

DQMB[5,1]

GCKE

SRAS[B,A]#

FENA

SCAS[B,A]#

MAA[14:0]

MAB[14,13,12#,11#,10,9#:0

#]

WEA#

WEB#

MD[63:0]

MECC[7:0]

HCLKIN

PCLKIN

GTLREF[B:A]

AGPREF

VTT[B:A]

REF5V

PCIRST#

CRESET#

BREQ0#

TESTIN#

GCLKO

GCLKIN

DCLKO

DCLKWR

AD[31:0]

C/BE[3:0]#

FRAME#

TRDY#

IRDY#

DEVSEL#

PAR

SERR#

PLOCK#

STOP#

PHOLD#

PHLDA#

WSC#

PREQ0#

PREQ[4:1]#

PGNT0#

PGNT[4:1]#

GAD[31:0]

GC/BE[3:0]#

GFRAME#

GIRDY#

GTRDY#

GSTOP#

GDEVSEL#

GREQ#

GGNT#

GPAR

PIPE#

SBA[7:0]

RBF#

STOP#

ST[2:0]

ADSTB_A

ADSTB_B

SBSTB

CLKRUN#

SUSTAT#

GXPWROK

PCI Bus

Interface

(PCI #0)

AGP

Interface

Power

Mgnt

Clocks,

Reset,

Test,

and

Misc.

82443GX Host Bridge

Datasheet

v

Contents

1

Architectural Overview ...............................................................................................1-1

2

Signal Description ......................................................................................................2-1

2.1

Host Interface Signals...................................................................................2-1

2.2

DRAM Interface ............................................................................................2-3

2.3

PCI Interface (Primary) .................................................................................2-4

2.4

Primary PCI Sideband Interface ...................................................................2-6

2.5

AGP Interface Signals...................................................................................2-6

2.6

Clocks, Reset, and Miscellaneous ................................................................2-8

2.7

Power-Up/Reset Strap Options.....................................................................2-9

3

Register Description...................................................................................................3-1

3.1

I/O Mapped Registers ...................................................................................3-2

3.1.1

CONFADD--Configuration Address Register..................................3-2

3.1.2

CONFDATA--Configuration Data Register .....................................3-3

3.1.3

PM2_CTL--ACPI Power Control 2 Control Register .......................3-4

3.2

PCI Configuration Space Access..................................................................3-4

3.2.1

Configuration Space Mechanism Overview .....................................3-5

3.2.2

Routing the Configuration Accesses to PCI or AGP ........................3-5

3.2.3

PCI Bus Configuration Mechanism Overview ..................................3-6

3.2.3.1 Type 0 Access ....................................................................3-6

3.2.3.2 Type 1 Access ....................................................................3-6

3.2.4

AGP Bus Configuration Mechanism Overview ................................3-6

3.2.5

Mapping of Configuration Cycles on AGP .......................................3-7

3.3

Host-to-PCI Bridge Registers (Device 0) ......................................................3-8

3.3.1

VID--Vendor Identification Register (Device 0).............................3-10

3.3.2

DID--Device Identification Register (Device 0) .............................3-10

3.3.3

PCICMD--PCI Command Register (Device 0) ..............................3-11

3.3.4

PCISTS--PCI Status Register (Device 0) .....................................3-12

3.3.5

RID--Revision Identification Register (Device 0) ..........................3-13

3.3.6

SUBC--Sub-Class Code Register (Device 0) ...............................3-13

3.3.7

BCC--Base Class Code Register (Device 0) ................................3-13

3.3.8

MLT--Master Latency Timer Register (Device 0)..........................3-14

3.3.9

HDR--Header Type Register (Device 0) .......................................3-14

3.3.10 APBASE--Aperture Base Configuration Register (Device 0)........3-14

3.3.11 SVID--Subsystem Vendor Identification Register (Device 0)........3-15

3.3.12 SID--Subsystem Identification Register (Device 0).......................3-16

3.3.13 CAPPTR--Capabilities Pointer Register (Device 0) ......................3-16

3.3.14 NBXCFG--NBX Configuration Register (Device 0) .......................3-16

3.3.15 DRAMC--DRAM Control Register (Device 0) ...............................3-19

3.3.16 PAM[6:0]--Programmable Attribute Map Registers

(Device 0).......................................................................................3-20

3.3.17 DRB[0:7]--DRAM Row Boundary Registers (Device 0) ................3-22

3.3.18 FDHC--Fixed DRAM Hole Control Register (Device 0) ................3-24

3.3.19 MBSC--Memory Buffer Strength Control Register

(Device 0).......................................................................................3-24

3.3.20 SMRAM--System Management RAM Control Register

(Device 0).......................................................................................3-28

vi

82443GX Host Bridge

Datasheet

3.3.21 ESMRAMC--Extended System Management RAM Control Register

(Device 0) ......................................................................................3-29

3.3.22 RPS--SDRAM Row Page Size Register (Device 0)......................3-30

3.3.23 SDRAMC--SDRAM Control Register (Device 0) ..........................3-30

3.3.24 PGPOL--Paging Policy Register (Device 0) .................................3-32

3.3.25 PMCR--Power Management Control Register (Device 0) ............3-33

3.3.26 SCRR--Suspend CBR Refresh Rate Register (Device 0) ............3-34

3.3.27 EAP--Error Address Pointer Register (Device 0)..........................3-34

3.3.28 ERRCMD--Error Command Register (Device 0) ..........................3-35

3.3.29 ERRSTS--Error Status Register (Device 0)..................................3-36

3.3.30 ACAPID--AGP Capability Identifier Register (Device 0) ...............3-37

3.3.31 AGPSTAT--AGP Status Register (Device 0) ................................3-37

3.3.32 AGPCMD--AGP Command Register (Device 0)...........................3-38

3.3.33 AGPCTRL--AGP Control Register (Device 0) ..............................3-39

3.3.34 APSIZE--Aperture Size Register (Device 0) .................................3-40

3.3.35 ATTBASE--Aperture Translation Table Base Register

(Device 0) ......................................................................................3-40

3.3.36 MBFS--Memory Buffer Frequency Select Register

(Device 0) ......................................................................................3-41

3.3.37 BSPAD--BIOS Scratch Pad Register (Device 0) ..........................3-43

3.3.38 DWTC--DRAM Write Thermal Throttling Control Register

(Device 0) ......................................................................................3-43

3.3.39 DRTC--DRAM Read Thermal Throttling Control Register

(Device 0) ......................................................................................3-44

3.3.40 BUFFC--Buffer Control Register (Device 0) .................................3-45

3.4

PCI-to-PCI Bridge Registers (Device 1) .....................................................3-46

3.4.1

VID1--Vendor Identification Register (Device 1)...........................3-47

3.4.2

DID1--Device Identification Register (Device 1) ...........................3-47

3.4.3

PCICMD1--PCI-to-PCI Command Register (Device 1) ................3-48

3.4.4

PCISTS1--PCI-to-PCI Status Register (Device 1) ........................3-49

3.4.5

RID1--Revision Identification Register (Device 1) ........................3-49

3.4.6

SUBC1--Sub-Class Code Register (Device 1) .............................3-50

3.4.7

BCC1--Base Class Code Register (Device 1) ..............................3-50

3.4.8

MLT1--Master Latency Timer Register (Device 1)........................3-50

3.4.9

HDR1--Header Type Register (Device 1) .....................................3-51

3.4.10 PBUSN--Primary Bus Number Register (Device 1)......................3-51

3.4.11 SBUSN--Secondary Bus Number Register (Device 1) .................3-51

3.4.12 SUBUSN--Subordinate Bus Number Register (Device 1) ............3-52

3.4.13 SMLT--Secondary Master Latency Timer Register

(Device 1) ......................................................................................3-52

3.4.14 IOBASE--I/O Base Address Register (Device 1) ..........................3-52

3.4.15 IOLIMIT--I/O Limit Address Register (Device 1) ...........................3-52

3.4.16 SSTS--Secondary PCI-to-PCI Status Register (Device 1) ...........3-53

3.4.17 MBASE--Memory Base Address Register (Device 1)...................3-54

3.4.18 MLIMIT--Memory Limit Address Register (Device 1)....................3-54

3.4.19 PMBASE--Prefetchable Memory Base Address Register

(Device 1) ......................................................................................3-55

3.4.20 PMLIMIT--Prefetchable Memory Limit Address Register

(Device 1) ......................................................................................3-55

3.4.21 BCTRL--PCI-to-PCI Bridge Control Register (Device 1) ..............3-56

82443GX Host Bridge

Datasheet

vii

4

Functional Description ...............................................................................................4-1

4.1

System Address Map....................................................................................4-1

4.1.1

Memory Address Ranges ................................................................4-2

4.1.1.1 Compatibility Area ...............................................................4-3

4.1.1.2 Extended Memory Area ......................................................4-4

4.1.1.3 AGP Memory Address Range.............................................4-6

4.1.1.4 AGP DRAM Graphics Aperture...........................................4-6

4.1.1.5 System Management Mode (SMM) Memory Range...........4-6

4.1.2

Memory Shadowing .........................................................................4-8

4.1.3

I/O Address Space...........................................................................4-8

4.1.4

AGP I/O Address Mapping...............................................................4-8

4.1.5

Decode Rules and Cross-Bridge Address Mapping ........................4-9

4.1.5.1 PCI Interface Decode Rules ...............................................4-9

4.1.5.2 AGP Interface Decode Rules ..............................................4-9

4.1.5.3 Legacy VGA Ranges ........................................................4-10

4.2

Host Interface..............................................................................................4-10

4.2.1

Host Bus Device Support ...............................................................4-10

4.2.2

Symmetric Multiprocessor (SMP) Protocol Support.......................4-13

4.2.3

In-Order Queue Pipelining .............................................................4-13

4.2.4

Frame Buffer Memory Support (USWC) ........................................4-13

4.3

DRAM Interface ..........................................................................................4-14

4.3.1

DRAM Organization and Configuration..........................................4-14

4.3.1.1 Configuration Mechanism For DIMMS ..............................4-16

4.3.2

DRAM Address Translation and Decoding ....................................4-17

4.3.3

SDRAMC Register Programming ..................................................4-19

4.3.4

SDRAM Paging Policy ...................................................................4-19

4.4

PCI Interface ...............................................................................................4-19

4.5

AGP Interface .............................................................................................4-20

4.6

Data Integrity Support .................................................................................4-20

4.6.1

Data Integrity Mode Selection ........................................................4-20

4.6.1.1 Non-ECC (Default Mode of Operation) .............................4-20

4.6.1.2 EC Mode ...........................................................................4-20

4.6.1.3 ECC Mode ........................................................................4-21

4.6.1.4 ECC Generation and Error Detection/Correction and

Reporting ..........................................................................4-21

4.6.1.5 Optimum ECC Coverage ..................................................4-22

4.6.2

DRAM ECC Error Signaling Mechanism........................................4-22

4.6.3

CPU Bus Integrity ..........................................................................4-22

4.6.4

PCI Bus Integrity ............................................................................4-22

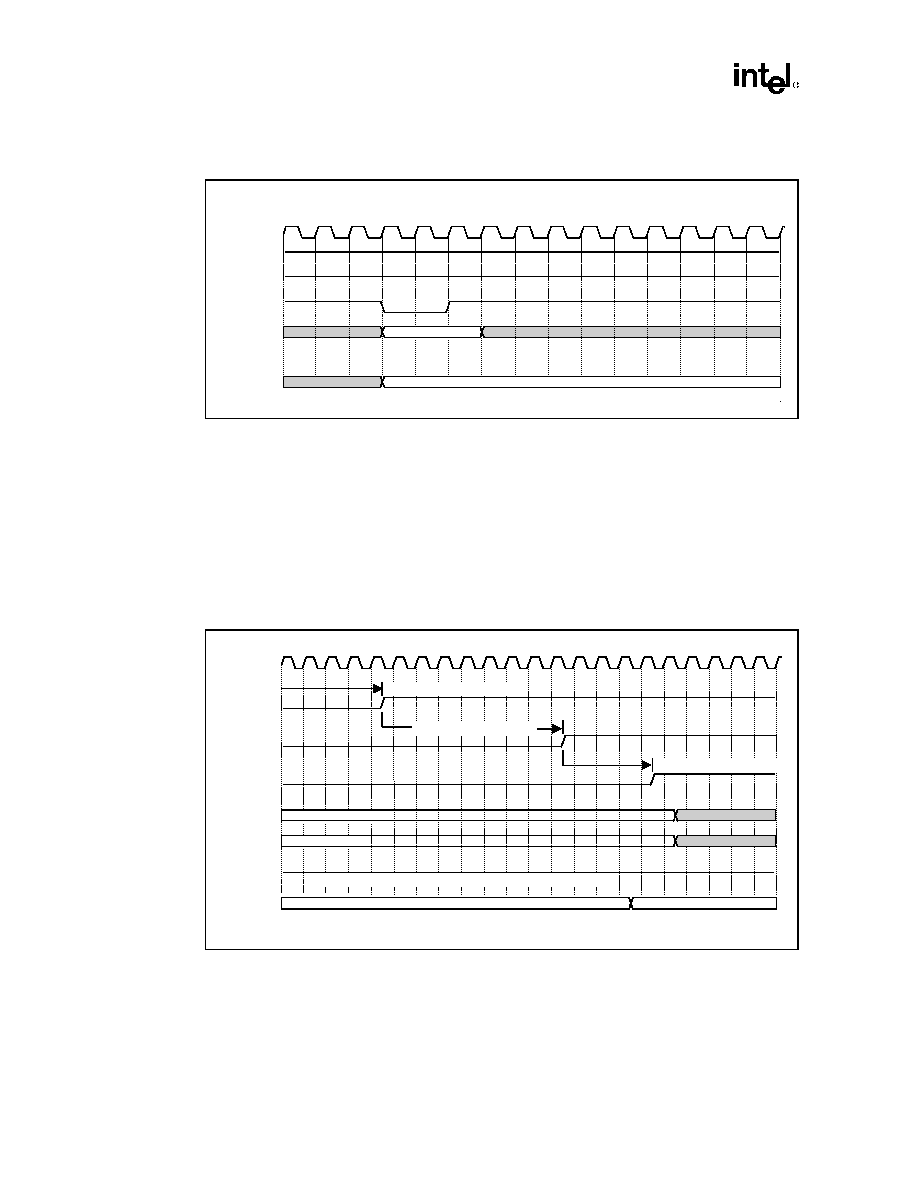

4.7

System Clocking .........................................................................................4-23

4.8

Power Management....................................................................................4-23

4.8.1

Overview ........................................................................................4-23

4.8.2

82443GX Reset .............................................................................4-26

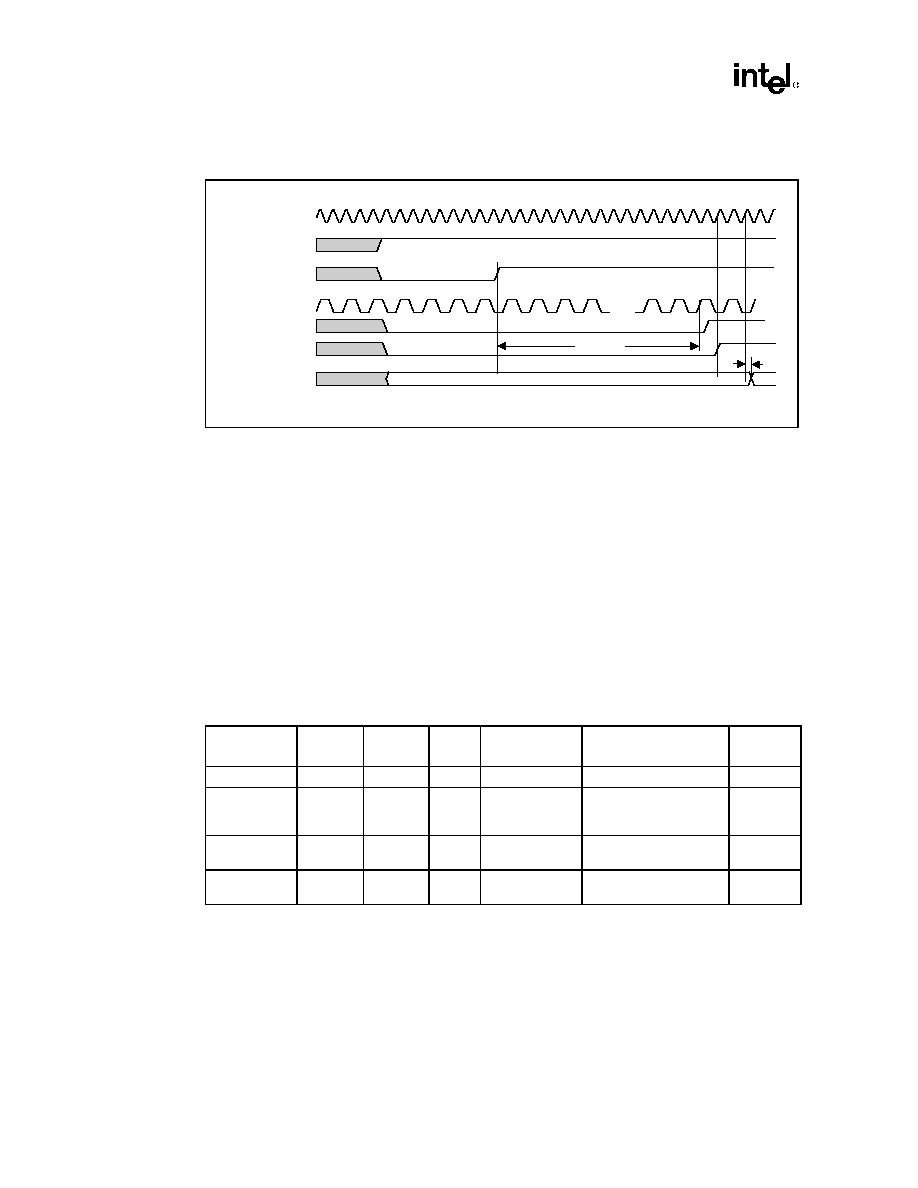

4.8.2.1 CPU Reset ........................................................................4-27

4.8.2.2 CPU Clock Ratio Straps....................................................4-27

4.8.2.3 82443GX Straps ...............................................................4-28

4.8.3

Suspend Resume ..........................................................................4-28

4.8.3.1 Suspend Resume protocols ..............................................4-28

4.8.3.2 Suspend Refresh ..............................................................4-29

4.8.4

Clock Control Functions .................................................................4-29

4.8.5

SMRAM..........................................................................................4-30

viii

82443GX Host Bridge

Datasheet

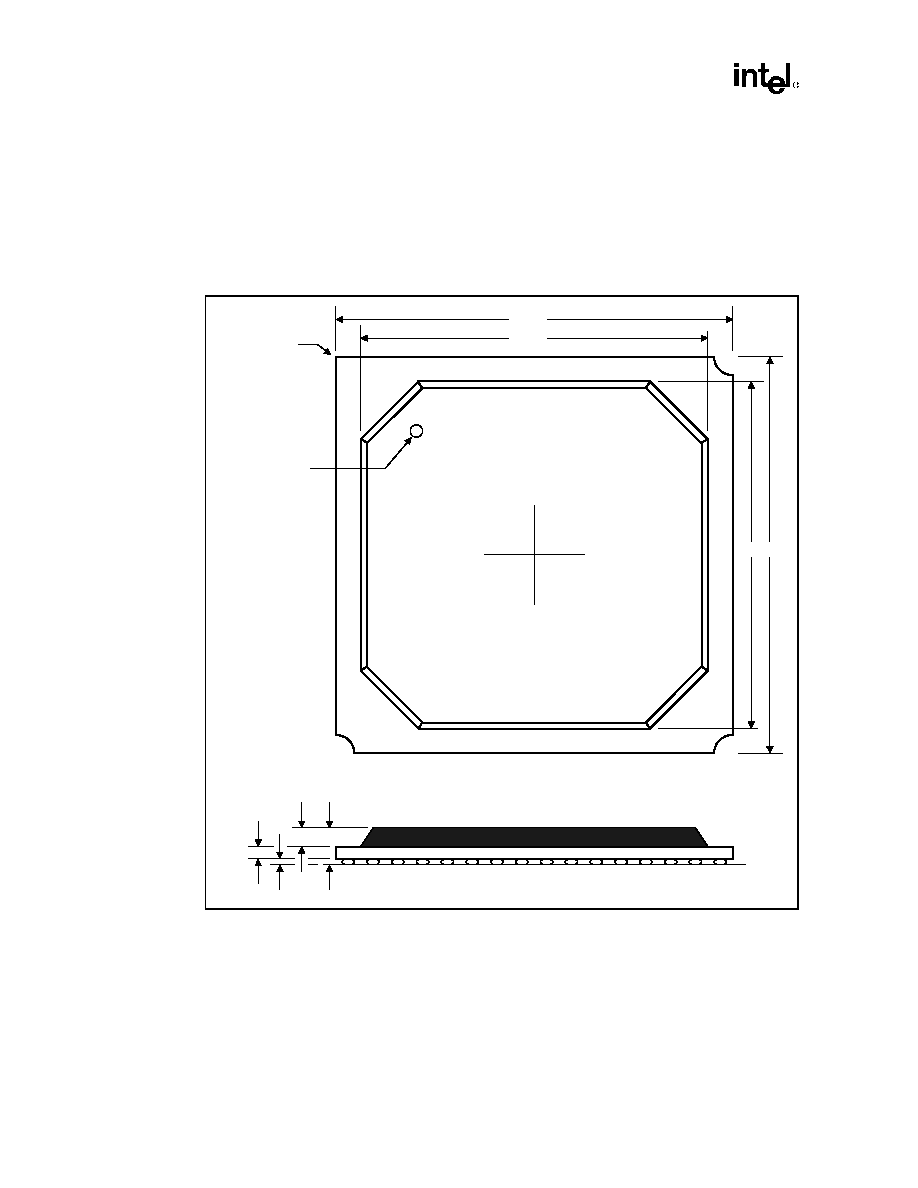

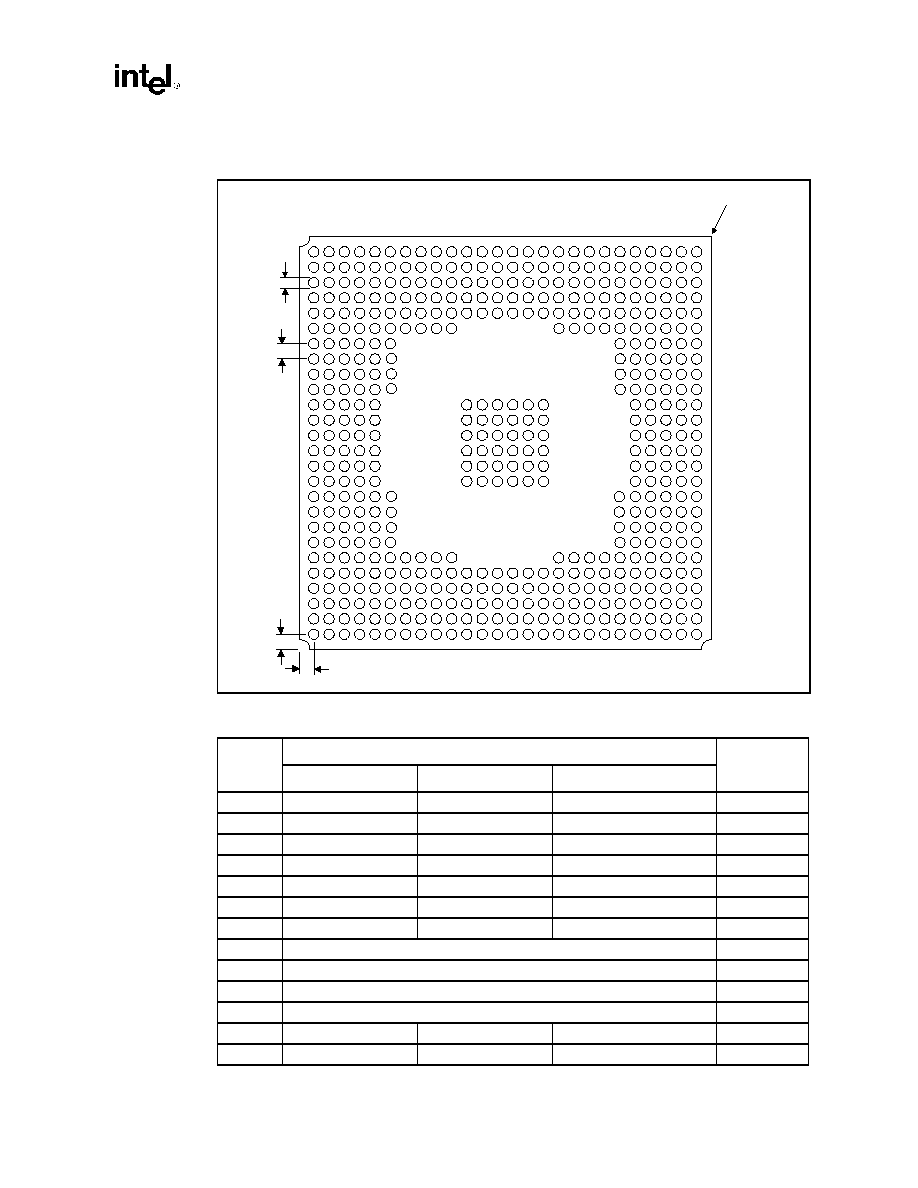

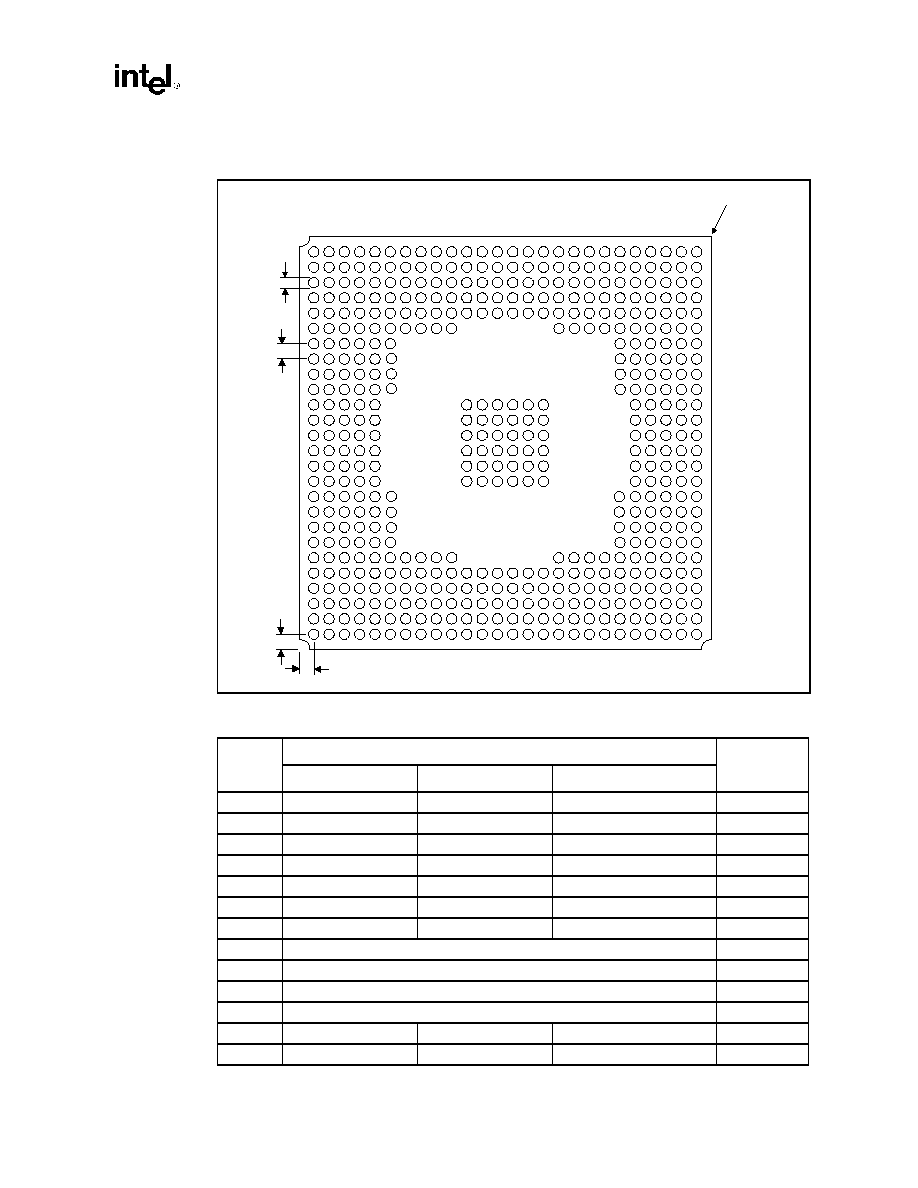

5

Pinout and Package Information................................................................................5-1

5.1

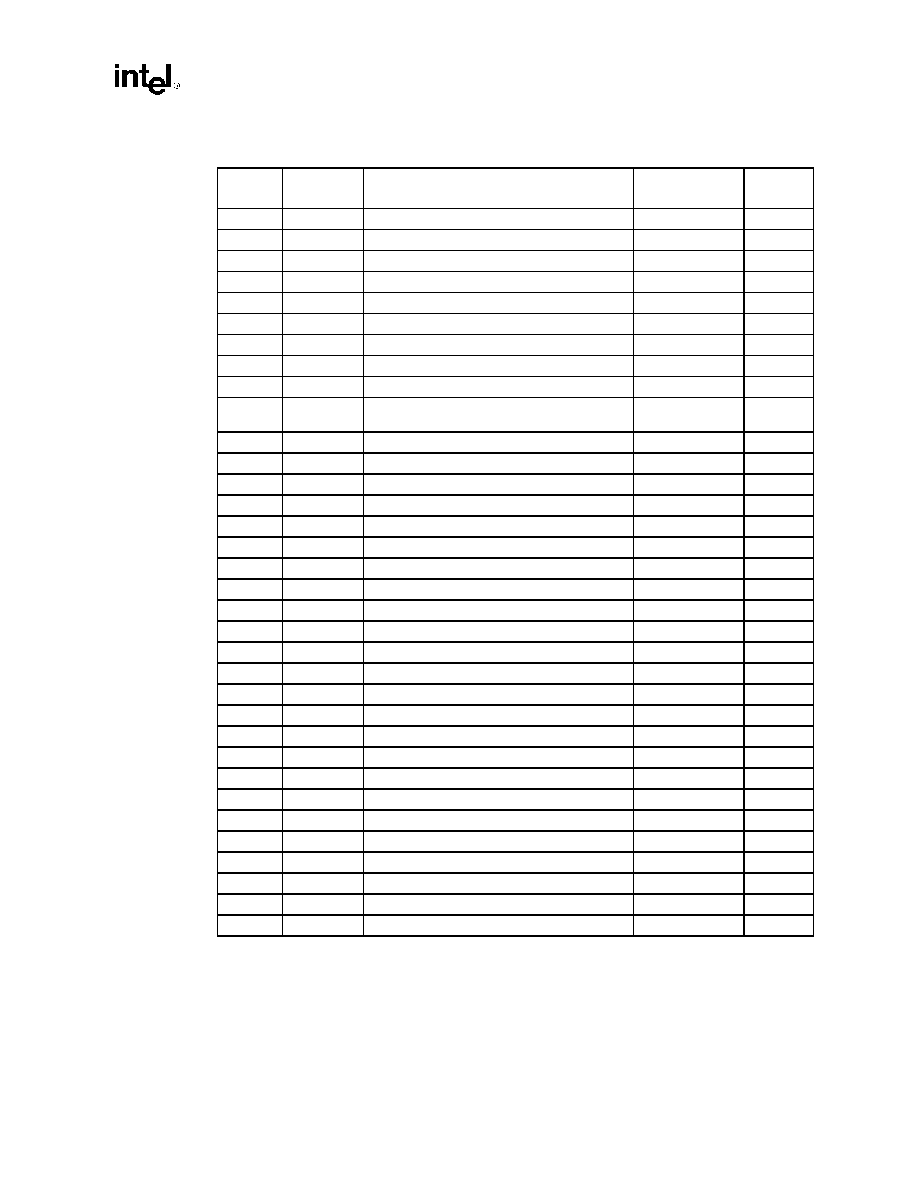

82443GX Pinout ...........................................................................................5-1

5.2

Package Dimensions ....................................................................................5-8

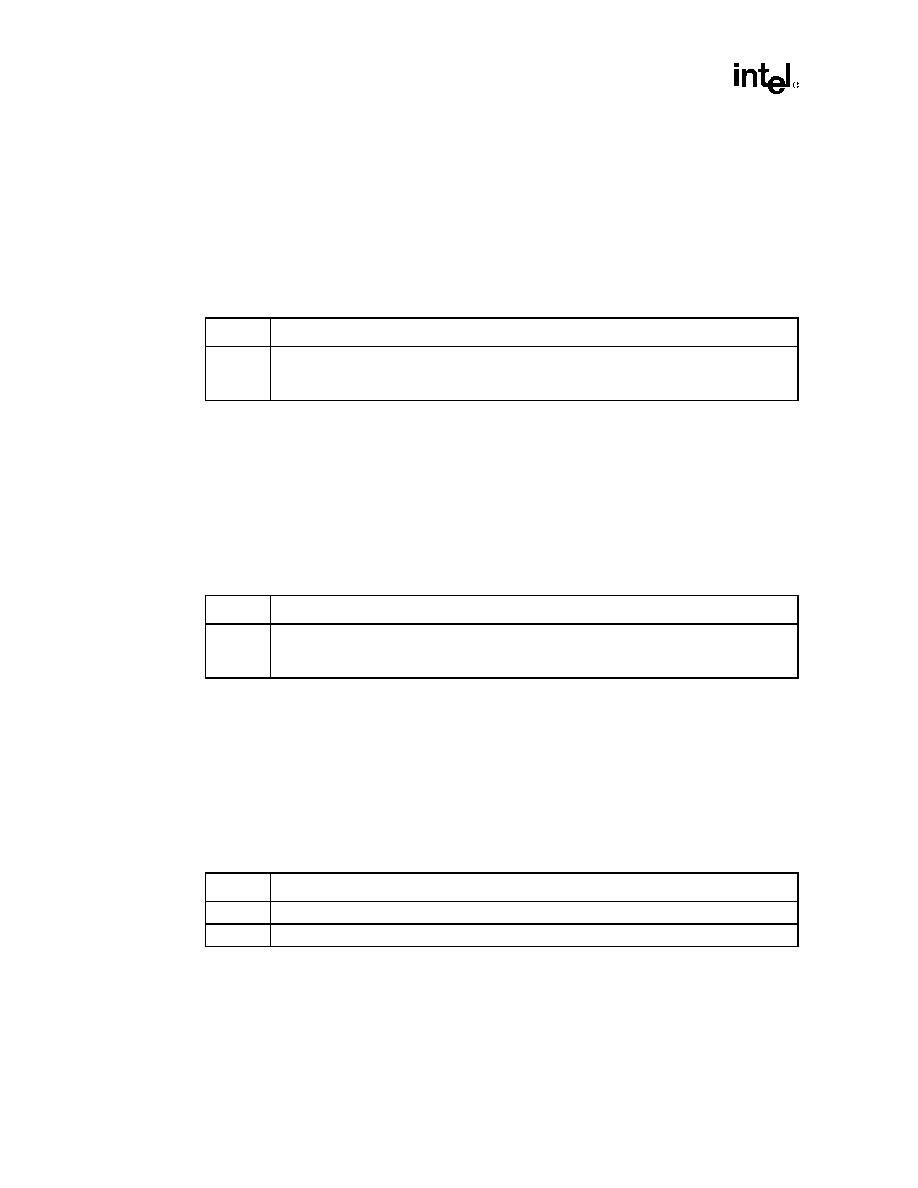

Figures

1-1

Intel

Æ

440GX AGPset System Block Diagram .............................................1-2

3-1

82443GX PCI Bus Hierarchy ........................................................................3-5

3-2

SDRAM DIMMs and Corresponding DRB Registers ..................................3-23

4-1

Memory System Address Space ..................................................................4-2

4-2

Four-DIMM Configuration with FET switches .............................................4-15

4-3

Typical Intel

Æ

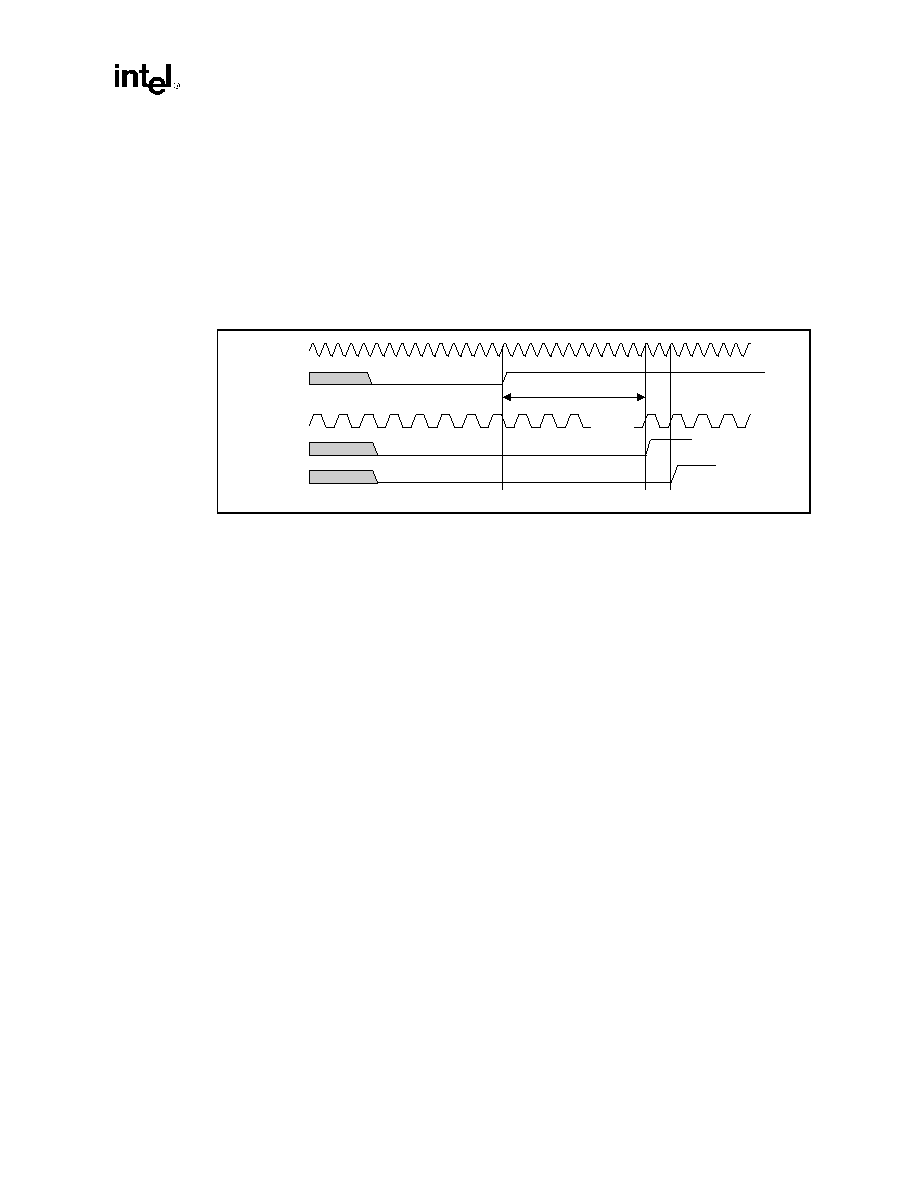

440GX AGPset System Clocking .........................................4-23

4-4

Reset CPURST# in a Desktop System When PCIRST# Asserted .............4-27

4-5

External Glue Logic Drives CPU Clock Ratio Straps ..................................4-28

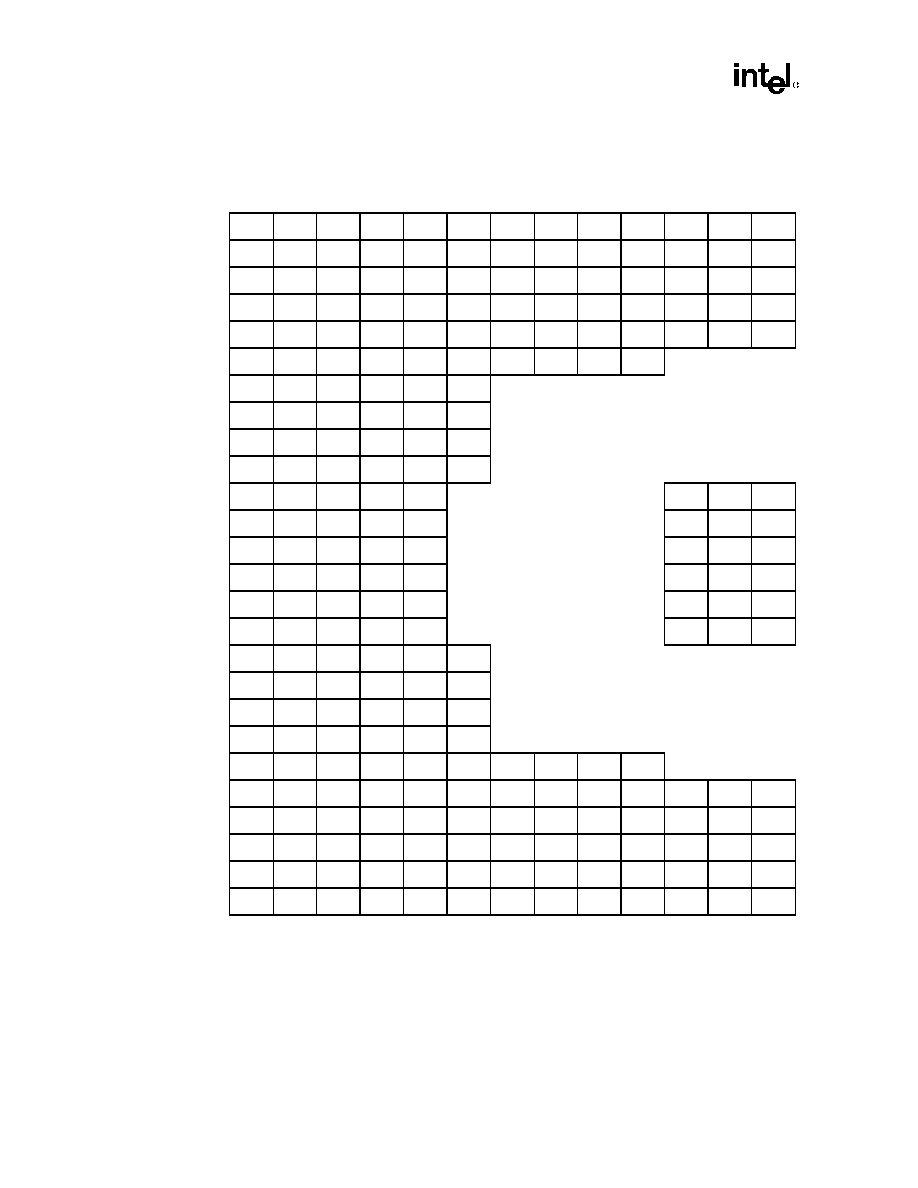

5-1

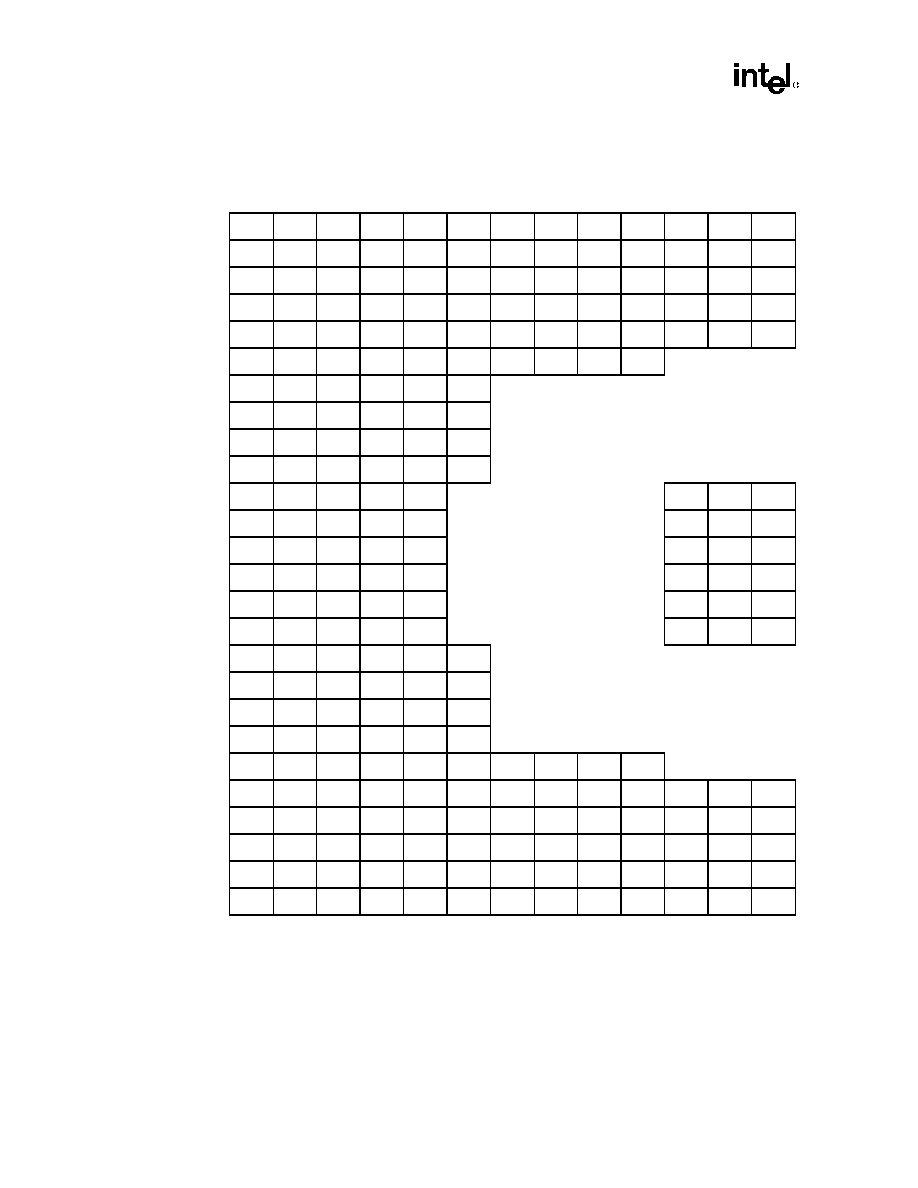

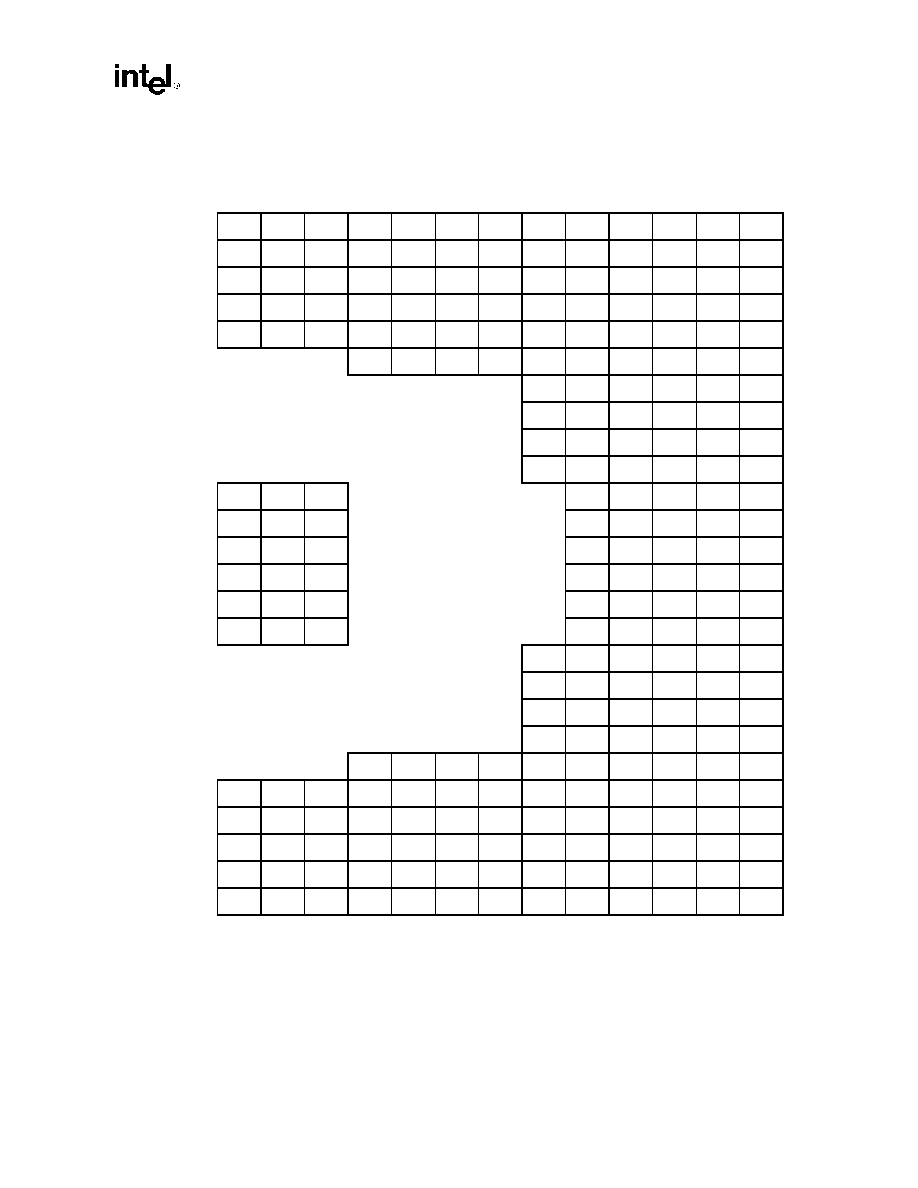

82443GX Pinout (Top View≠left side)...........................................................5-2

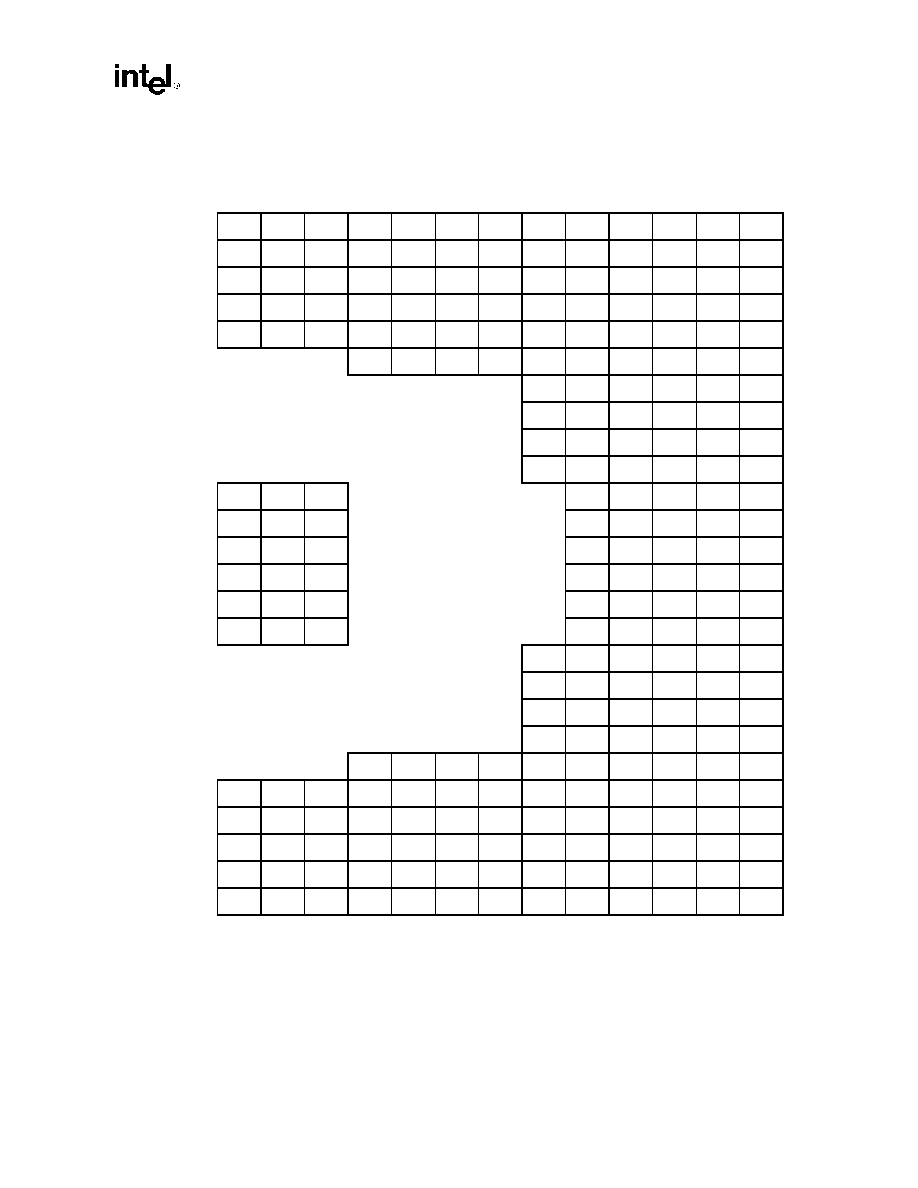

5-2

82443GX Pinout (Top View≠right side) ........................................................5-3

5-3

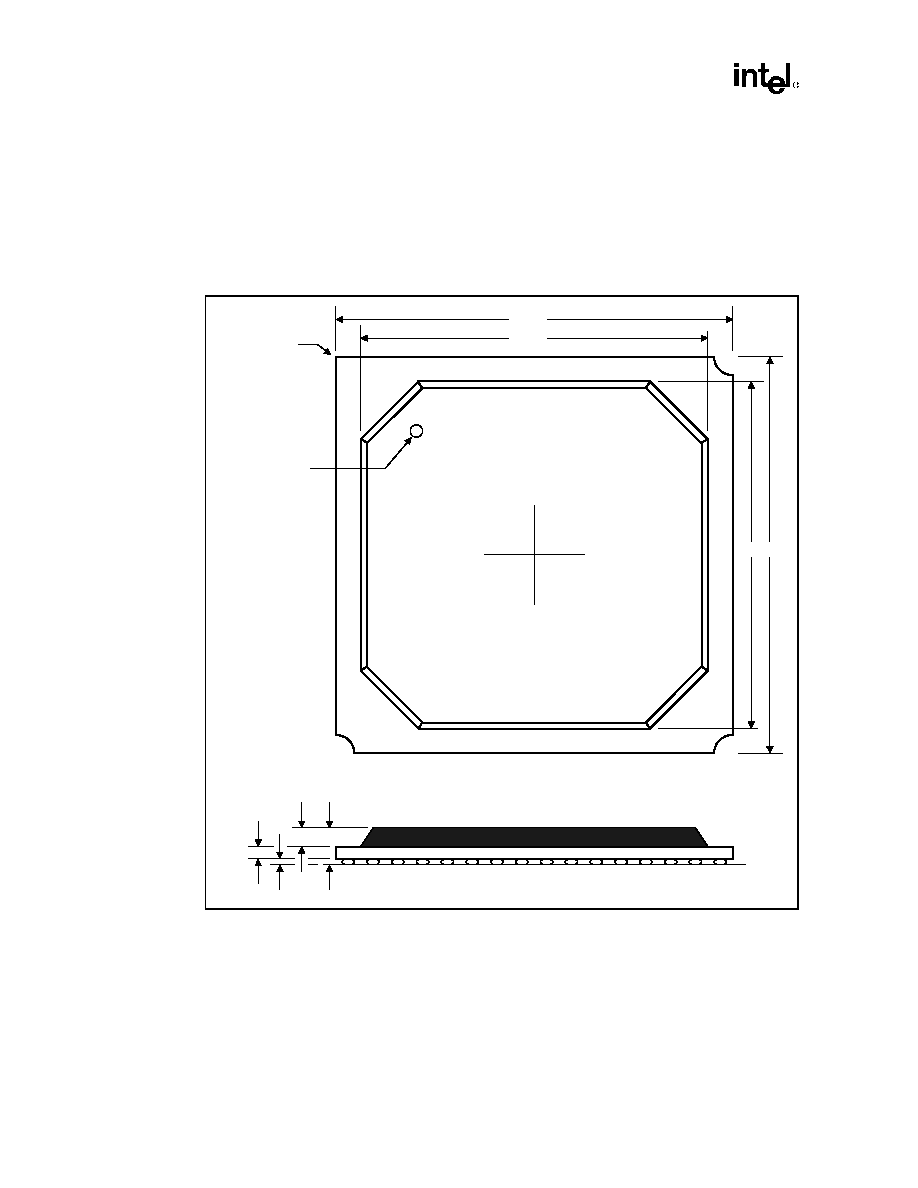

82443GX BGA Package Dimensions--Top and Side Views........................5-8

5-4

82443GX BGA Package Dimensions--Bottom Views..................................5-9

82443GX Host Bridge

Datasheet

ix

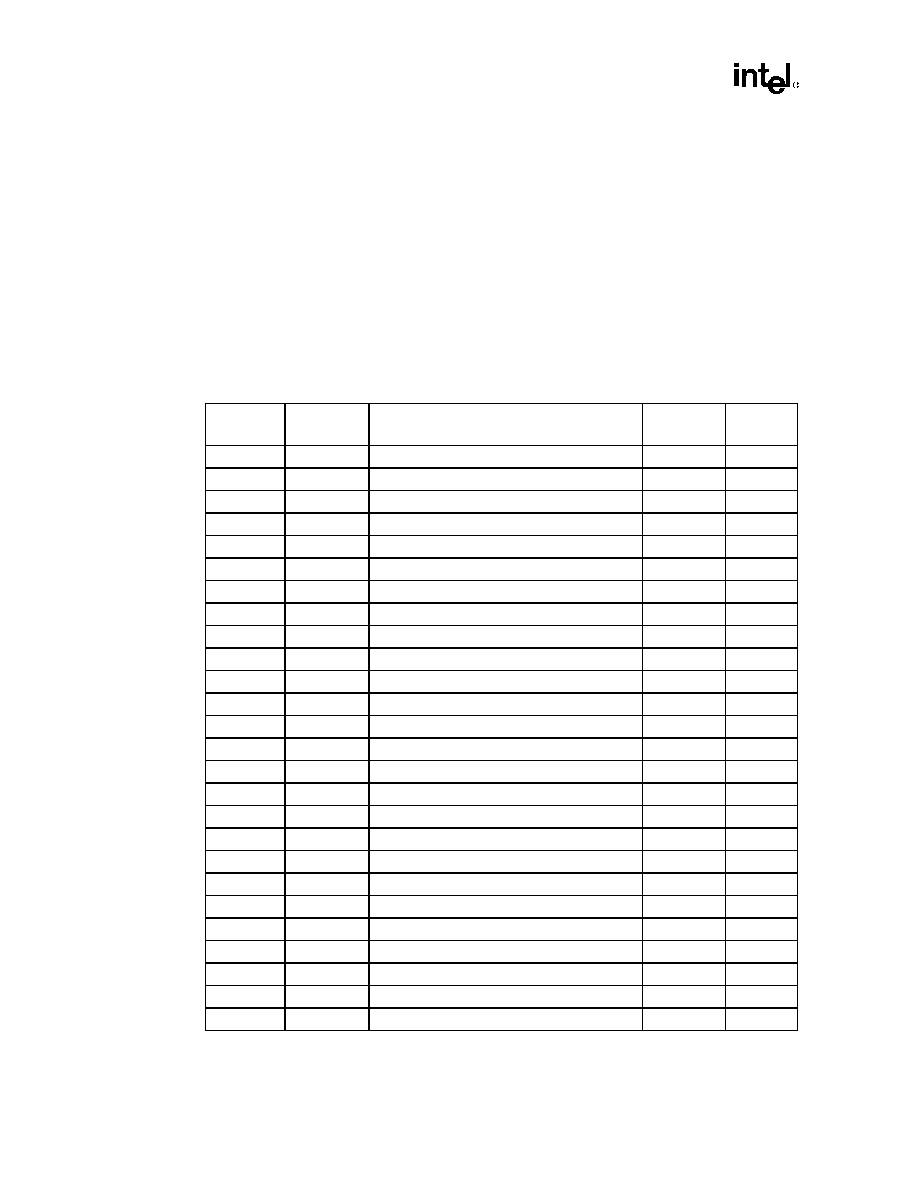

Tables

2-1

Host Interface Signals...................................................................................2-1

2-2

Host Signals Not supported by the 82443GX ...............................................2-3

2-3

DRAM Interface Signals................................................................................2-3

2-4

Primary PCI Interface Signals.......................................................................2-4

2-5

Primary PCI Sideband Interface Signals.......................................................2-6

2-6

AGP Interface Signals...................................................................................2-6

2-7

Clocks, Reset, and Miscellaneous ................................................................2-8

2-8

Power Management Interface.......................................................................2-9

2-9

Reference Pins .............................................................................................2-9

2-10

Strapping Options .......................................................................................2-10

3-1

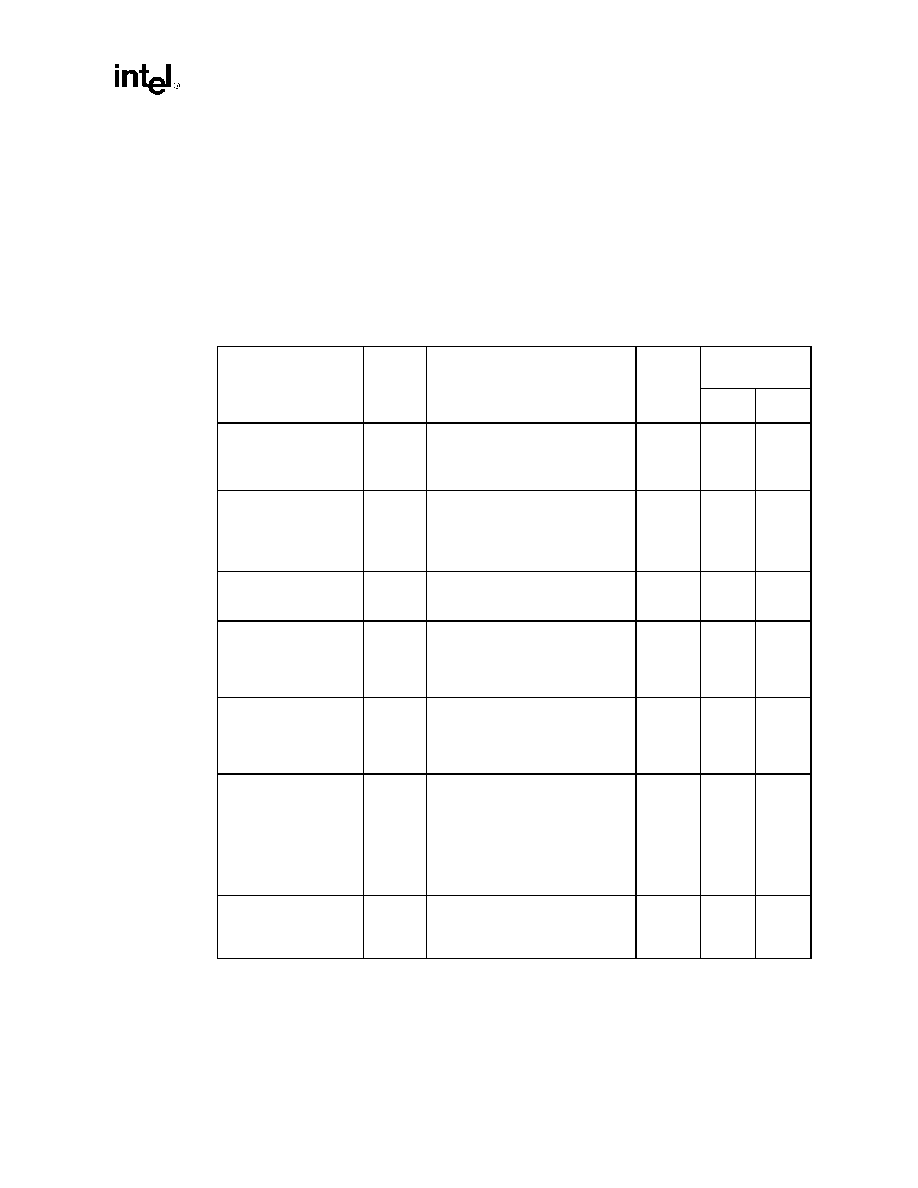

82443GX Register Map -- Device 0.............................................................3-8

3-2

Attribute Bit Assignment..............................................................................3-20

3-3

PAM Registers and Associated Memory Segments ...................................3-21

3-4

82443GX Configuration Space--Device 1..................................................3-46

4-1

Memory Segments and their Attributes.........................................................4-3

4-2

SMRAM Decoding ........................................................................................4-7

4-3

SMRAM Range Decode................................................................................4-7

4-4

SMRAM Decode Control...............................................................................4-7

4-5

Host Bus Transactions Supported By 82443GX.........................................4-11

4-6

Host Responses supported by the 82443GX..............................................4-12

4-7

Host Special Cycles with 82443GX ............................................................4-12

4-8

Data Bytes on DIMM Used for Programming DRAM Registers ..................4-16

4-9

Supported Memory Configurations .............................................................4-18

4-10

MA Muxing vs. DRAM Address Split...........................................................4-18

4-11

Programmable SDRAM Timing Parameters ...............................................4-19

4-12

Low Power Mode ........................................................................................4-25

4-13

AGPset Reset .............................................................................................4-26

4-14

Reset Signals..............................................................................................4-26

4-15

Suspend / Resume Events and Activities ...................................................4-28

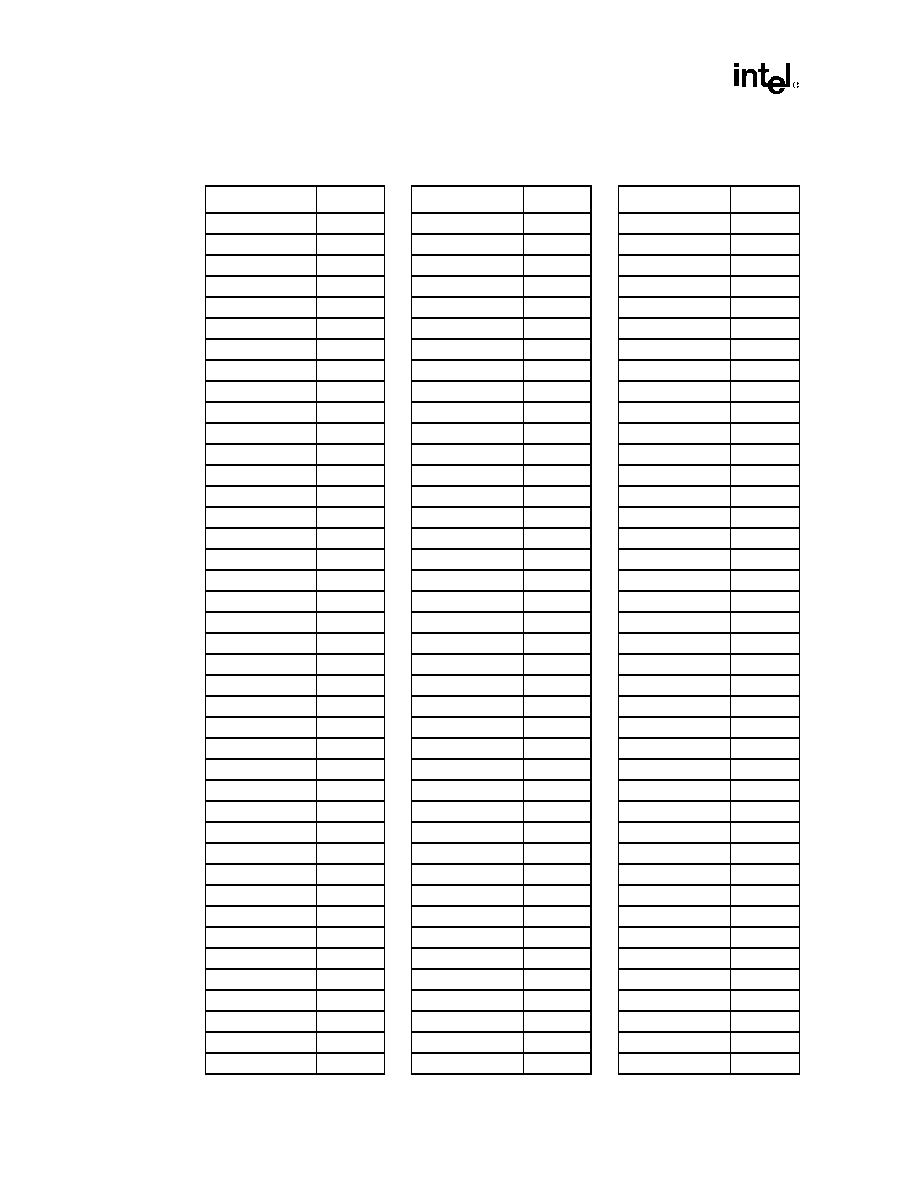

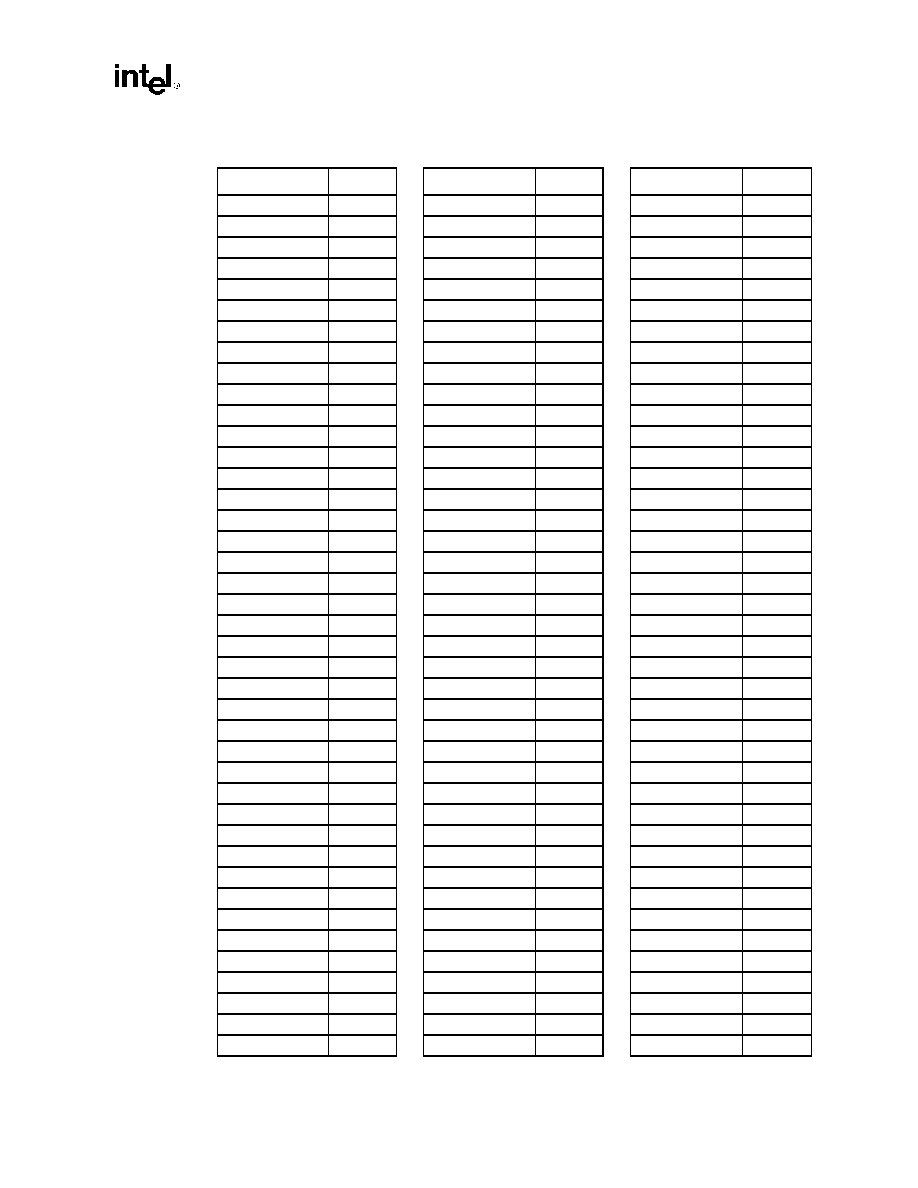

5-1

82443GX Alphabetical BGA Pin List.............................................................5-4

5-2

82443GX Package Dimensions (492 BGA) ..................................................5-9

82443GX Host Bridge Datasheet

1-1

Architectural Overview

1

The Intel

Æ

440GX AGPset includes the 82443GX Host Bridge and the 82371EB PIIX4E for the

I/O subsystem. The 82443GX functions and capabilities include:

∑

Support for single and dual Pentium

Æ

II processor and Pentium

Æ

II XeonTM processor

configurations

∑

64-bit GTL+ and AGTL+ based System (Host) Bus Interface

∑

32-bit Host address Support

∑

64-bit Main Memory Interface with optimized support for SDRAM at 100 MHz

∑

32-bit Primary PCI Bus Interface (PCI) with integrated PCI arbiter

∑

AGP Interface (AGP) with 133 MHz data transfer capability configurable as a Secondary PCI

Bus

∑

Extensive Data Buffering between all interfaces for high throughput and concurrent operations

∑

"Deep Green" Desktop power management support

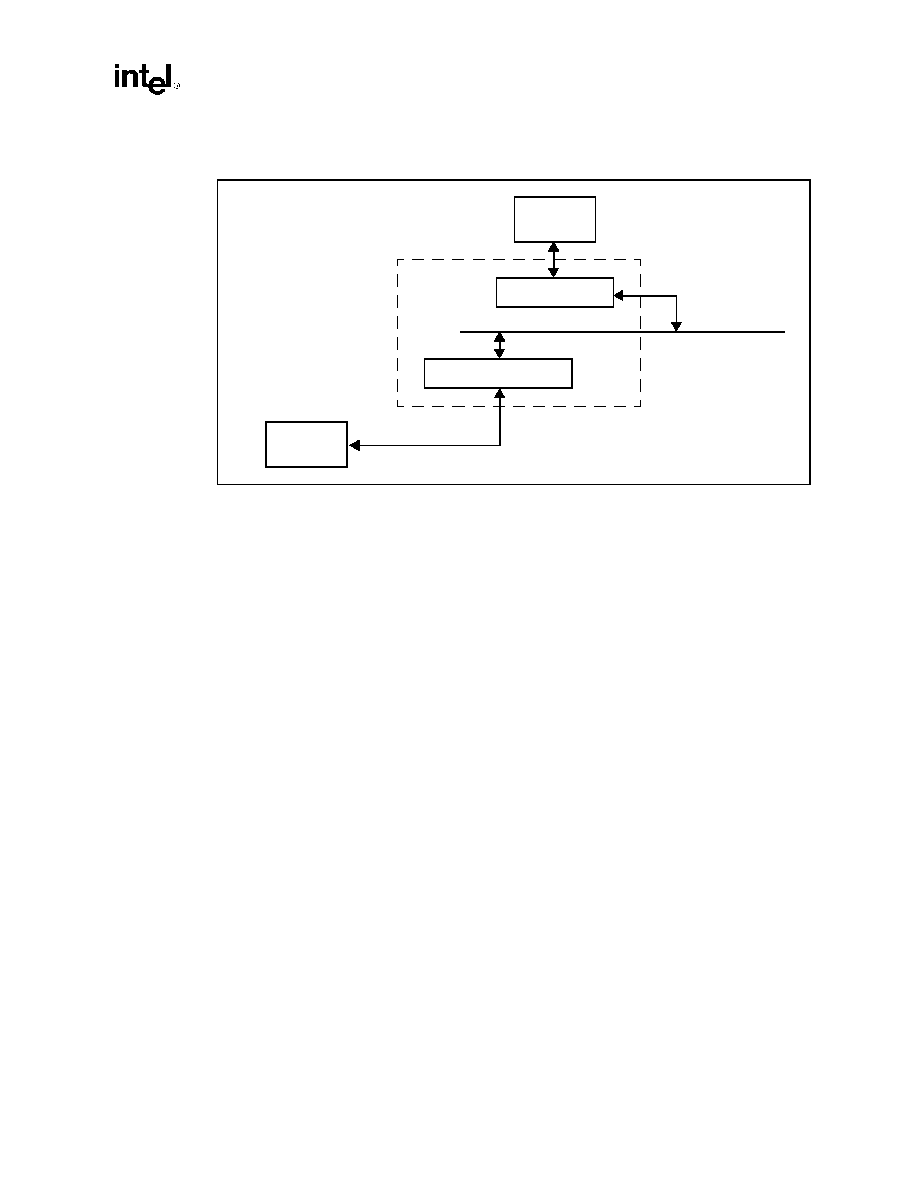

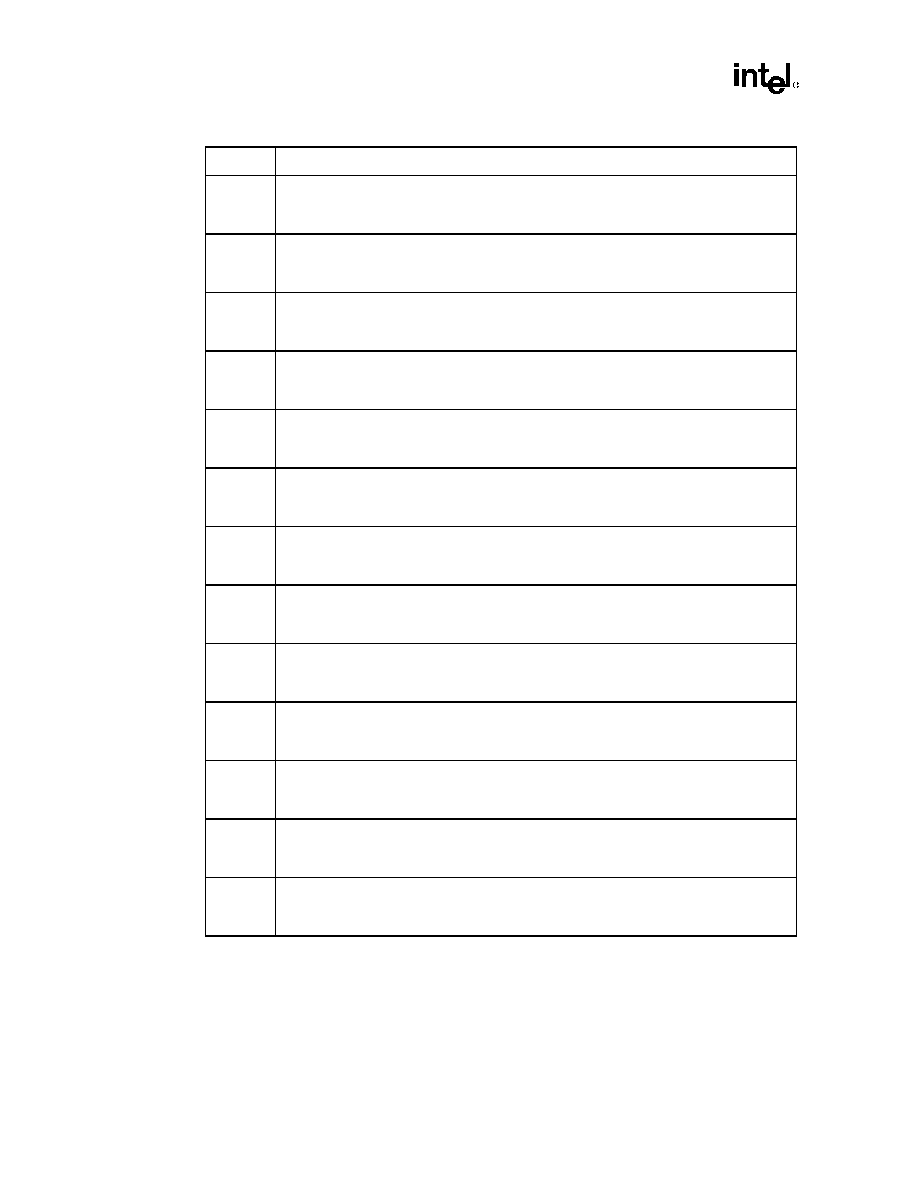

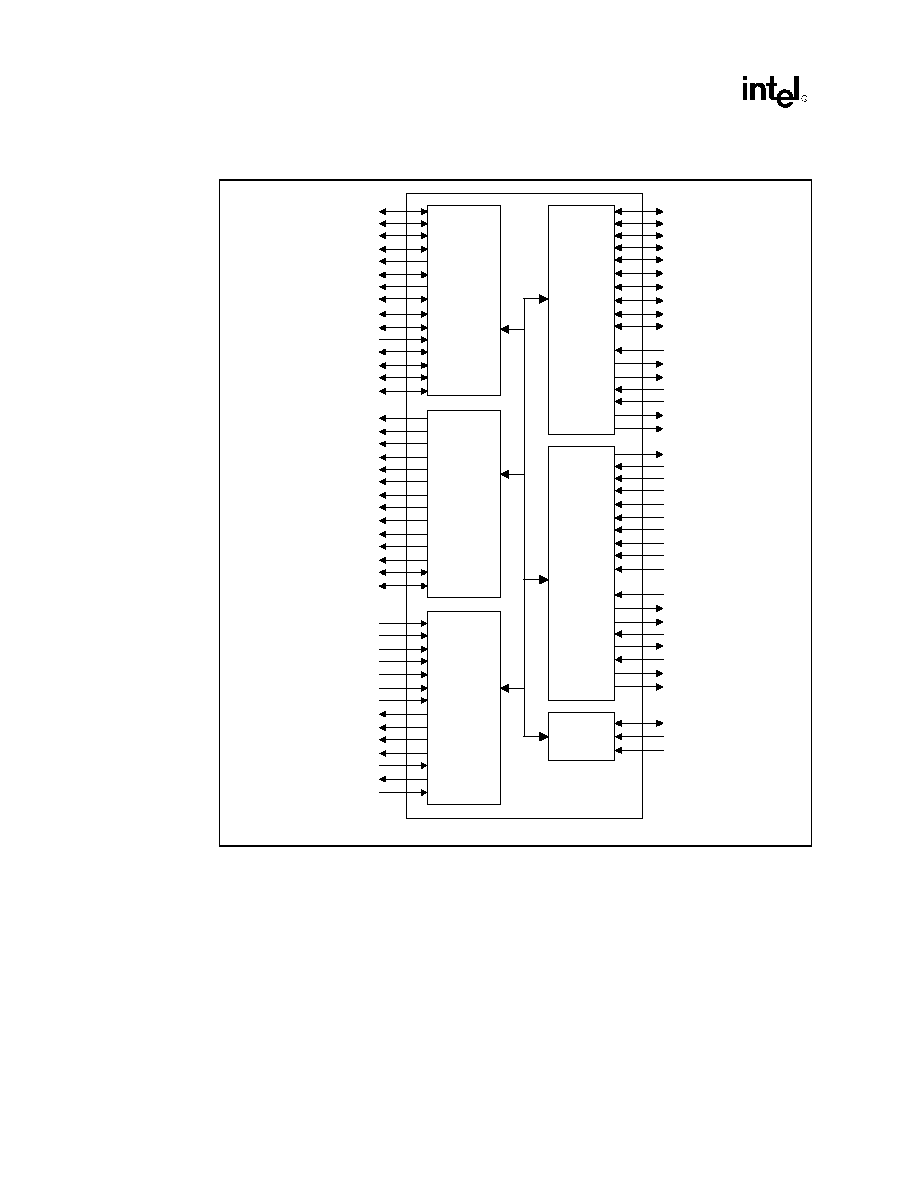

Figure 1-1 shows a block diagram of a typical platform based on the Intel

Æ

440GX AGPset. The

82443GX host bus interface supports up to two Pentium II processors or two Pentium II XeonTM

processors at 100 MHz bus frequency. The physical interface design is based on the GTL+

specification optimized for the desktop. The 82443GX provides an optimized 64-bit DRAM

interface. This interface is implemented as a 3.3V-only interface that supports only 3V DRAM

technology. Two copies of the MA, and CS# signals drive a maximum of two DIMMs each;

providing unbuffered high performance at 100 MHz. The 82443GX provides interface to PCI

operating at 33 MHz. This interface implementation is compliant with PCI Rev 2.1 Specification.

The 82443GX AGP interface implementation is based on Rev 1.0 of the AGP Specification. The

AGP interface supports 133 MHz data transfer rates.

The 82443GX is designed to support the PIIX4E I/O bridge. PIIX4E is a highly integrated

multifunctional component supporting the following functions and capabilities:

∑

PCI Rev 2.1 compliant PCI-ISA Bridge with support for both 3.3V and 5V 33 MHz PCI

operations

∑

Deep Green Desktop Power Management Support

∑

Enhanced DMA controller and Interrupt Controller and Timer functions

∑

Integrated IDE controller with Ultra DMA/33 support

∑

USB host interface with support for 2 USB ports

∑

System Management Bus (SMB) with support for DIMM Serial PD

∑

Support for an external I/O APIC component

Architectural Overview

1-2

82443GX Host Bridge Datasheet

Host Interface

The Pentium

Æ

II processor and Pentium

Æ

II XeonTM processor support a second level cache via a

cache bus interface. All control for the L2 cache is handled by the processor. The 82443GX

provides bus control signals and address paths for transfers between the processors system bus

(host bus), PCI bus, AGP and main memory. The 82443GX supports a 4-deep in-order queue (i.e.,

supports pipelining of up to 4 outstanding transaction requests on the host bus). Due to the system

concurrency requirements, along with support for pipelining of address requests from the host bus,

the 82443GX supports request queuing for all three interfaces (Host, AGP and PCI).

Host-initiated I/O cycles are decoded to PCI, AGP or PCI configuration space. Host-initiated

memory cycles are decoded to PCI, AGP (prefetchable or non-prefetchable memory space) or

DRAM (including AGP aperture memory). For memory cycles (host, PCI or AGP initiated) that

target the AGP aperture space in DRAM, the 82443GX translates the address using the AGP

address translation table. Other host cycles forwarded to AGP are defined by the AGP address map.

PCI and AGP initiated cycles that target the AGP graphics aperture are also translated using the

AGP aperture translation table. AGP-initiated cycles that target the AGP graphics aperture mapped

in main memory do not require a snoop cycle on the host bus, since the coherency of data for that

particular memory range will be maintained by the software.

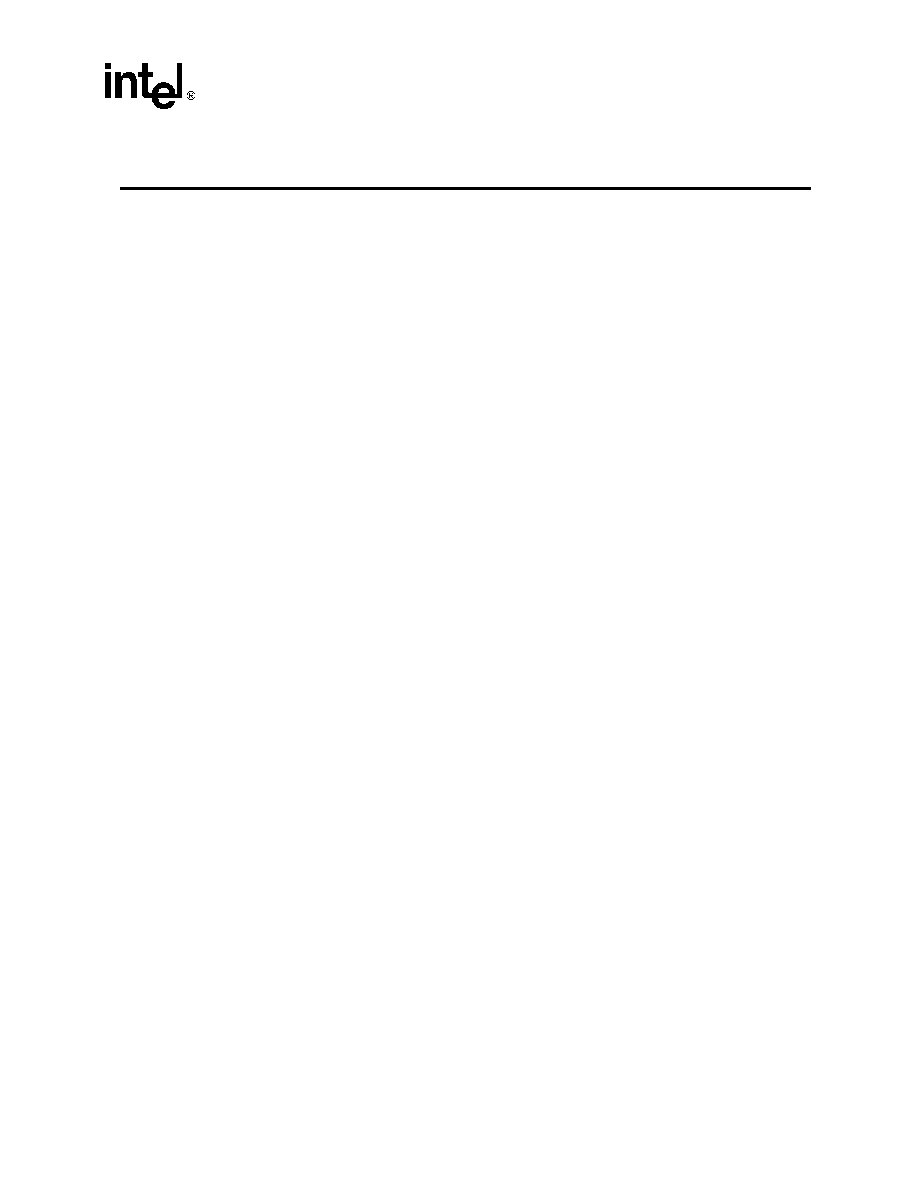

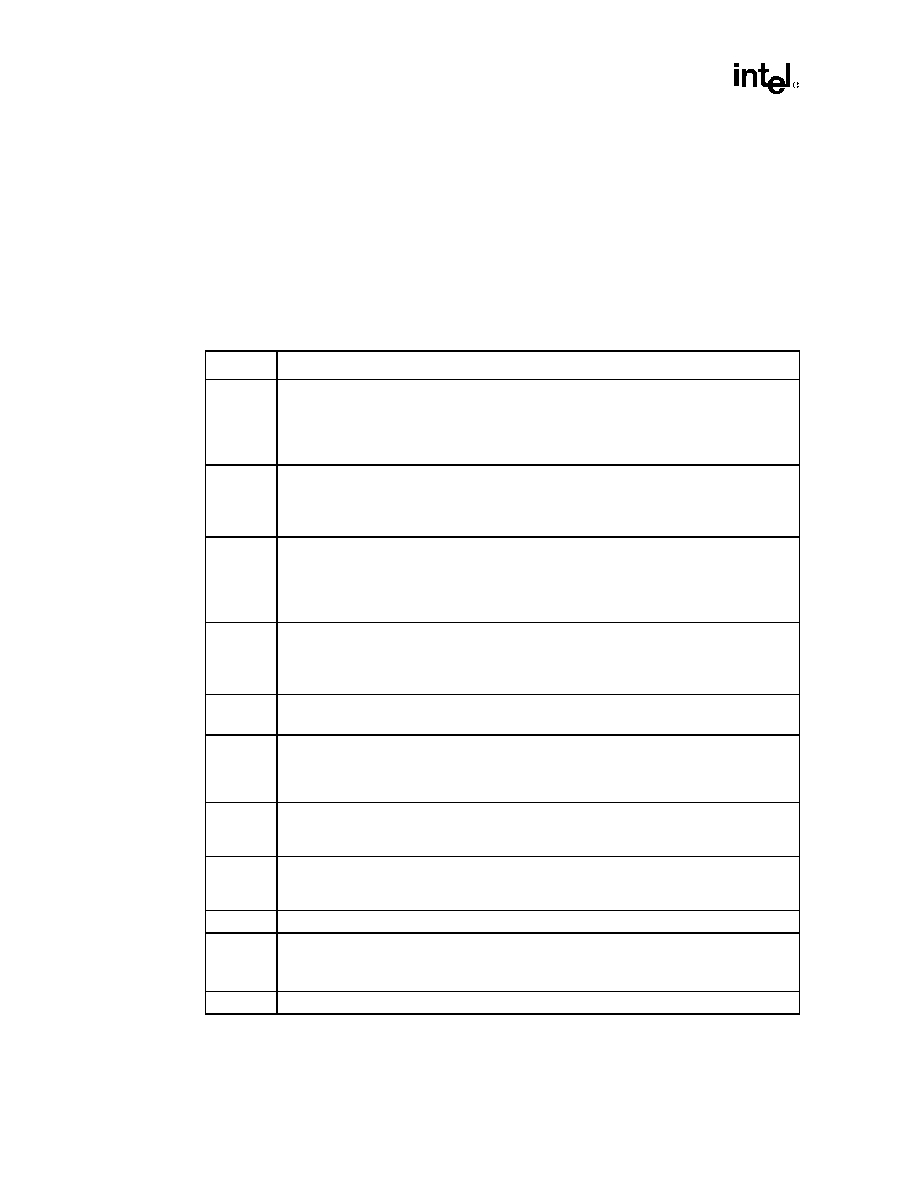

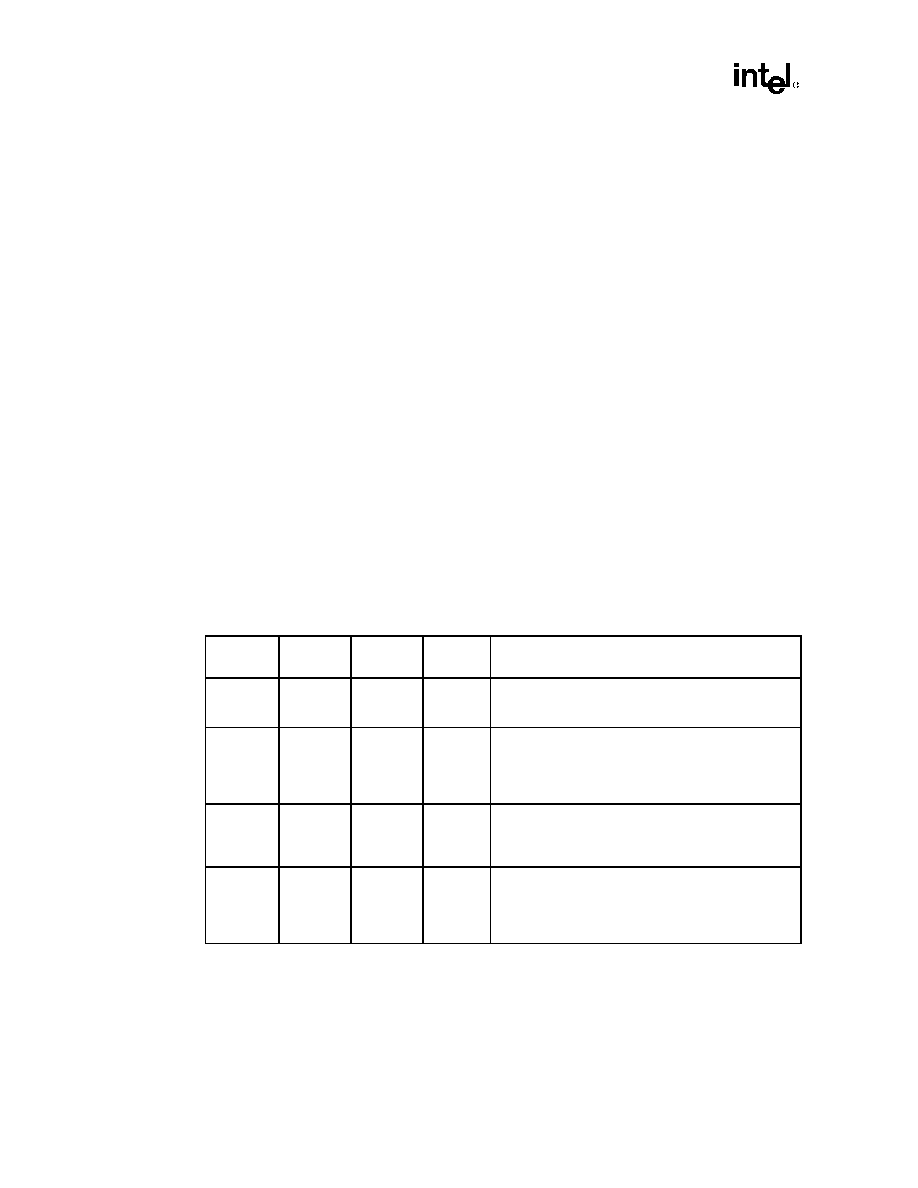

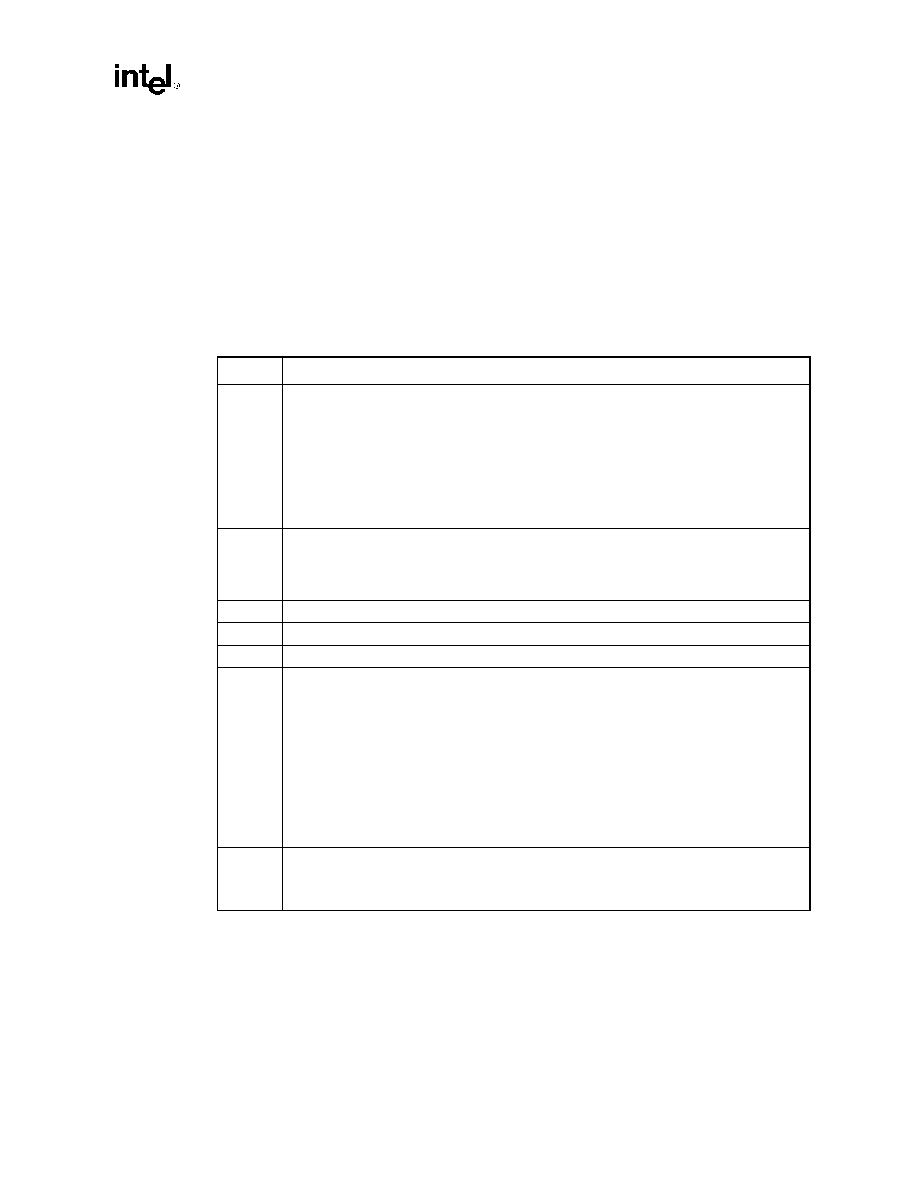

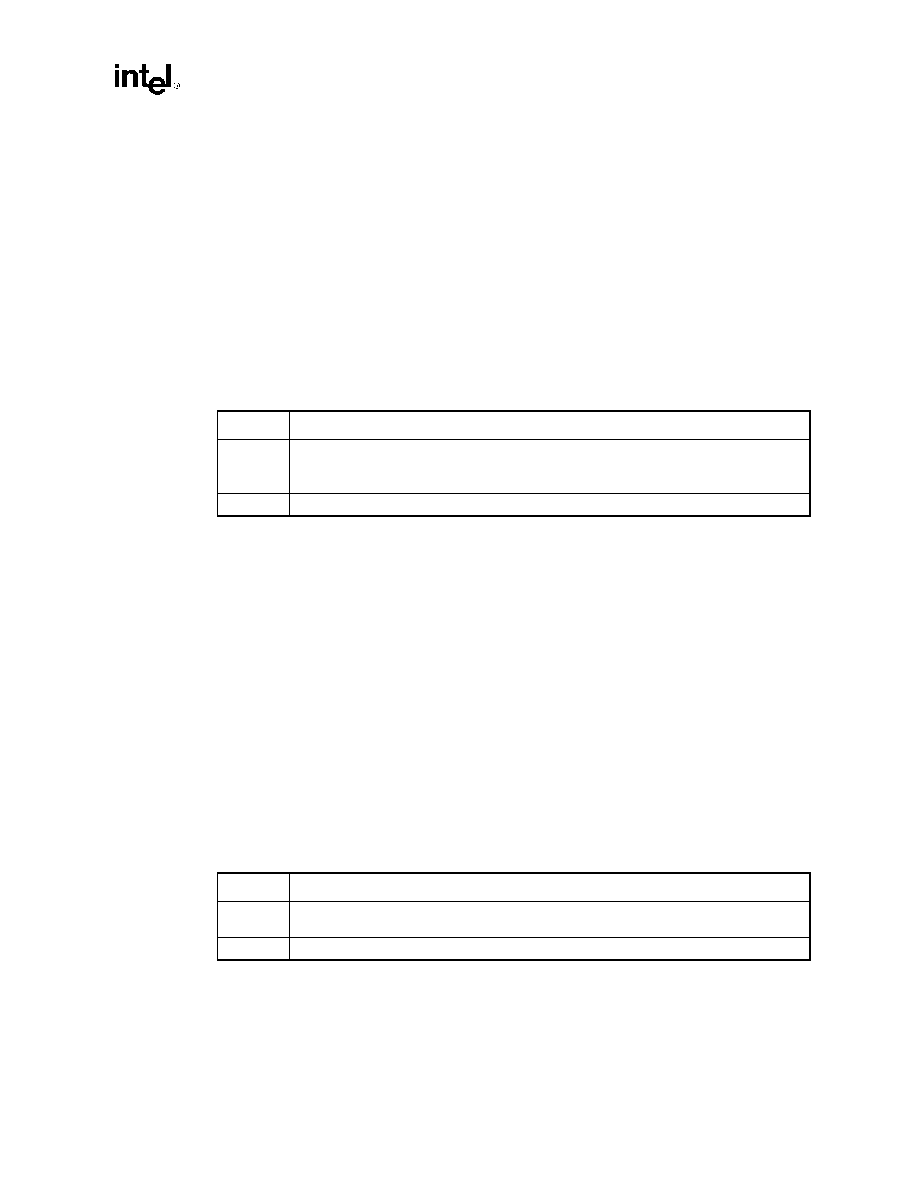

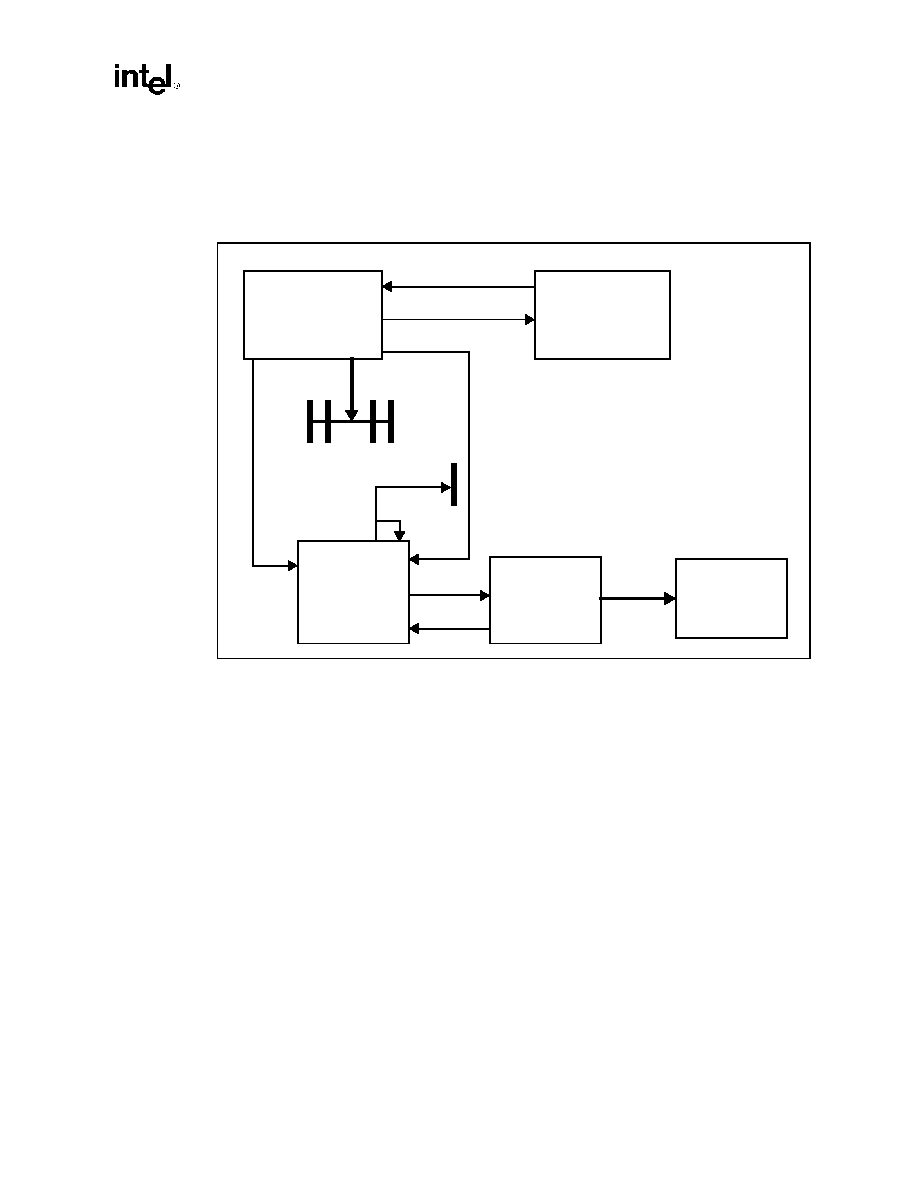

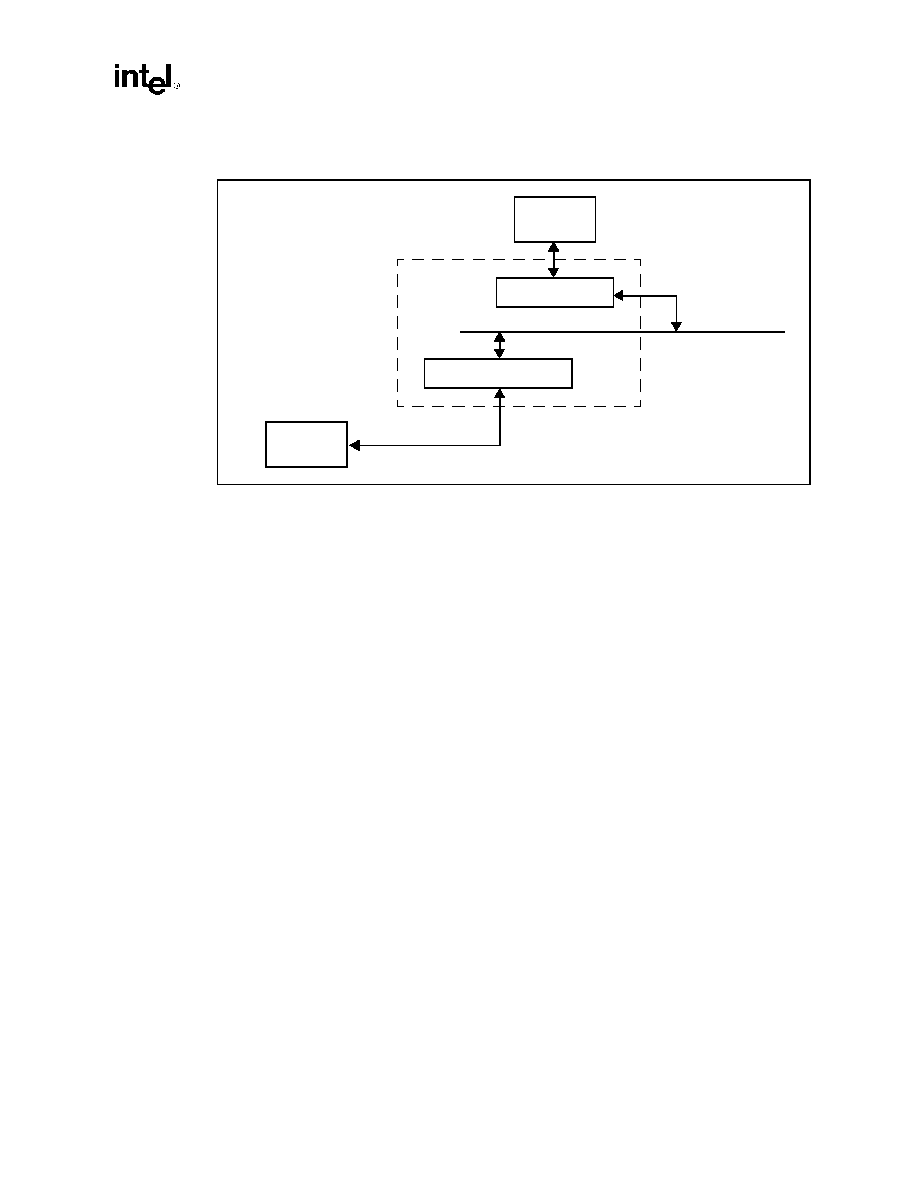

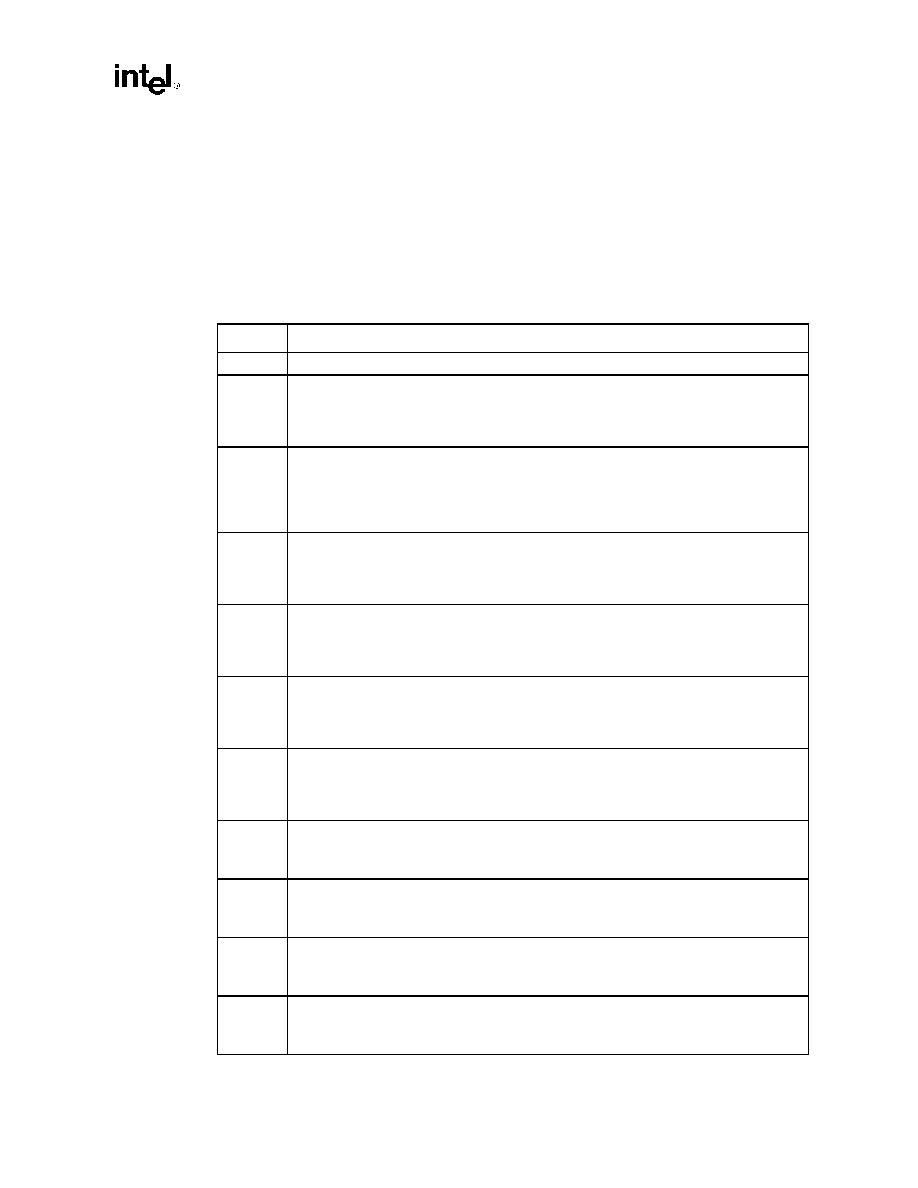

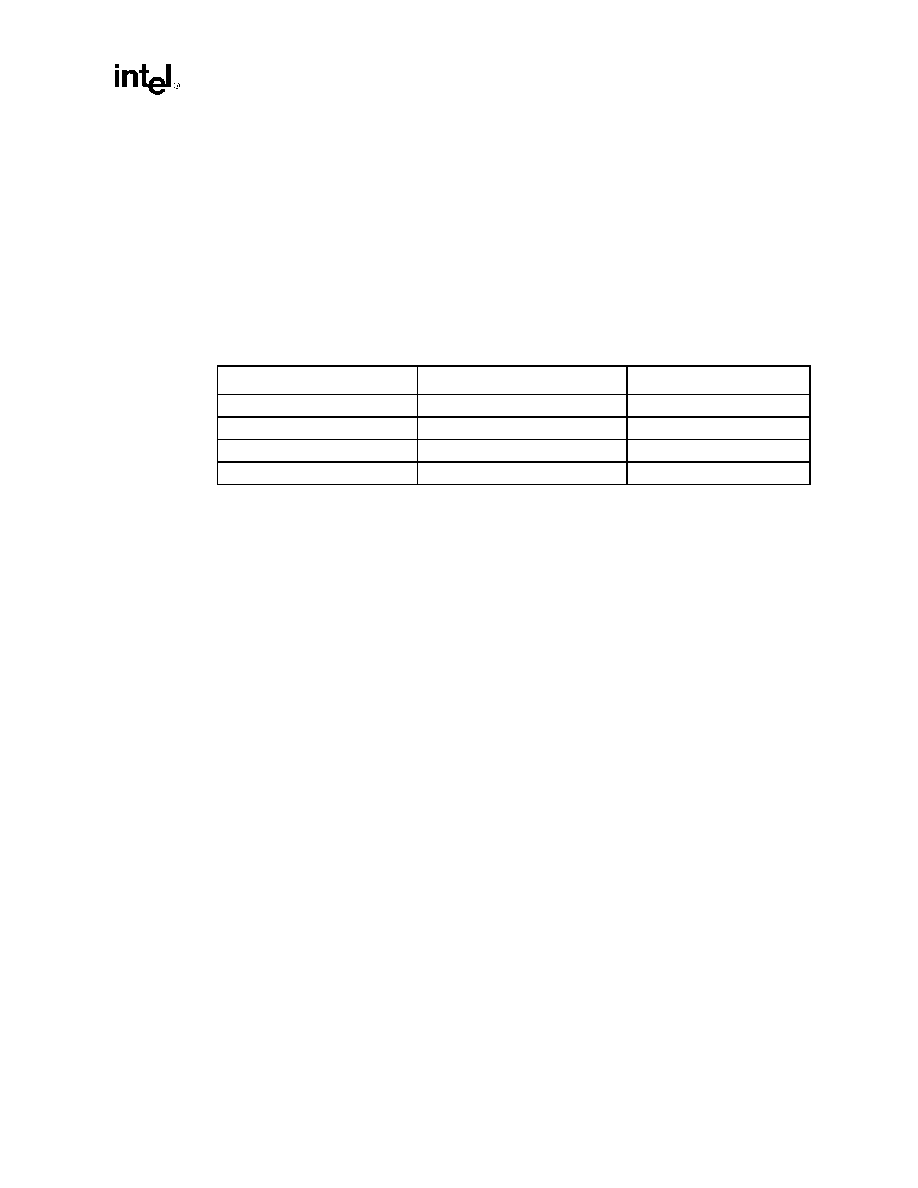

Figure 1-1. Intel

Æ

440GX AGPset System Block Diagram

sys_blk.vsd

TV

Video BIOS

System Bus

82443GX

Host Bridge

Main

Memory

Pentium

Æ

II or

Pentium

Æ

II

XeonTM Processor

3.3V SDRAM

Support

2X AGP Bus

Graphics

Device

Display

ISA Bus

ISA Slots

System BIOS

System MGMT (SM) Bus

2 IDE Ports

(Ultra DMA/33)

2 USB

Ports

USB

USB

IO

APIC

82371EB

(PIIX4E)

(PCI-to-ISA

Bridge)

Primary PCI Bus

(PCI Bus #0)

PCI Slots

Encoder

Graphics

Local Memory

Video

- DVD

- Camera

- VCR

- VMI

- Video Capture

100 MHz

Pentium

Æ

II or

Pentium

Æ

II

XeonTM Processor

82443GX Host Bridge Datasheet

1-3

Architectural Overview

DRAM Interface

The 82443GX integrates a DRAM controller that supports a 64-bit main memory interface. The

DRAM controller supports the following features:

∑

DRAM type: Synchronous DRAM (SDRAM) controller optimized for dual/quad-bank

SDRAM organization on a row by row basis

∑

Memory Size: 16 MB to 2 GB with eight memory rows

∑

Addressing Type: Asymmetrical addressing

∑

Memory Modules supported: Single and double-sided 3.3V DIMMs

∑

DRAM device technology: 16 Mbit, 64 Mbit, 128 Mbit, and 256 Mbit

1

∑

DRAM Speed: 100 MHz synchronous memory (SDRAM).

The Intel

Æ

440GX AGPset also provides DIMM plug-and-play support via Serial Presence Detect

(SPD) mechanism using the SMBus interface. The 82443GX provides optional data integrity

features including ECC in the memory array. During reads from DRAM, the 82443GX provides

error checking and correction of the data. The 82443GX supports multiple-bit error detection and

single-bit error correction when ECC mode is enabled and single/multi-bit error detection when

correction is disabled. During writes to the DRAM, the 82443GX generates ECC for the data on a

QWord basis. Partial QWord writes require a read-modify-write cycle when ECC is enabled.

AGP Interface

The 82443GX AGP implementation is compatible with the following:

∑

The Accelerated Graphics Port Specification, Rev 1.0

∑

Accelerated Graphics Port Memory Performance Specification, Rev 1.0 (4/12/96)

The 82443GX supports only a synchronous AGP interface coupling to the 82443GX core

frequency. The AGP interface can reach a theoretical ~500 MByte/sec transfer rate (i.e., using

133 MHz AGP compliant devices).

PCI Interface

The 82443GX PCI interface is 3.3V (5V tolerant), 33 MHz Rev. 2.1 compliant and supports up to

five external PCI bus masters in addition to the I/O bridge (PIIX4/PIIX4E). The PCI-to-DRAM

interface can reach over 100 MByte/sec transfer rate for streaming reads and over 120 MBytes/sec

for streaming writes.

System Clocking

The 82443GX operates the host interface, SDRAM, and core at 100 MHz only; PCI at

33 MHz; and AGP at 66/133 MHz.

I/O APIC

I/O APIC is used to support dual processors as well as enhanced interrupt processing in the single

processor environment. The 82443GX supports an external status output signal that can be used to

control synchronization of interrupts in configurations that use PIIX4E with stand-alone I/O APIC

component.

1.

Proper operation of the 82443GX AGPset with 256-Mbit SDRAM devices has not yet been verified. Intel's current plans are to validate this feature

in the second half of 1998 when 256-Mbit SDRAM devices are available.

82443GX Host Bridge Datasheet

2-1

Signal Description

S i g n a l D e s c r i p t i o n

2

This chapter provides a detailed description of 82443GX signals. The signals are arranged in

functional groups according to their associated interface.

The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when

the signal is at a low voltage level. When "#" is not present after the signal name the signal is

asserted when at the high voltage level.

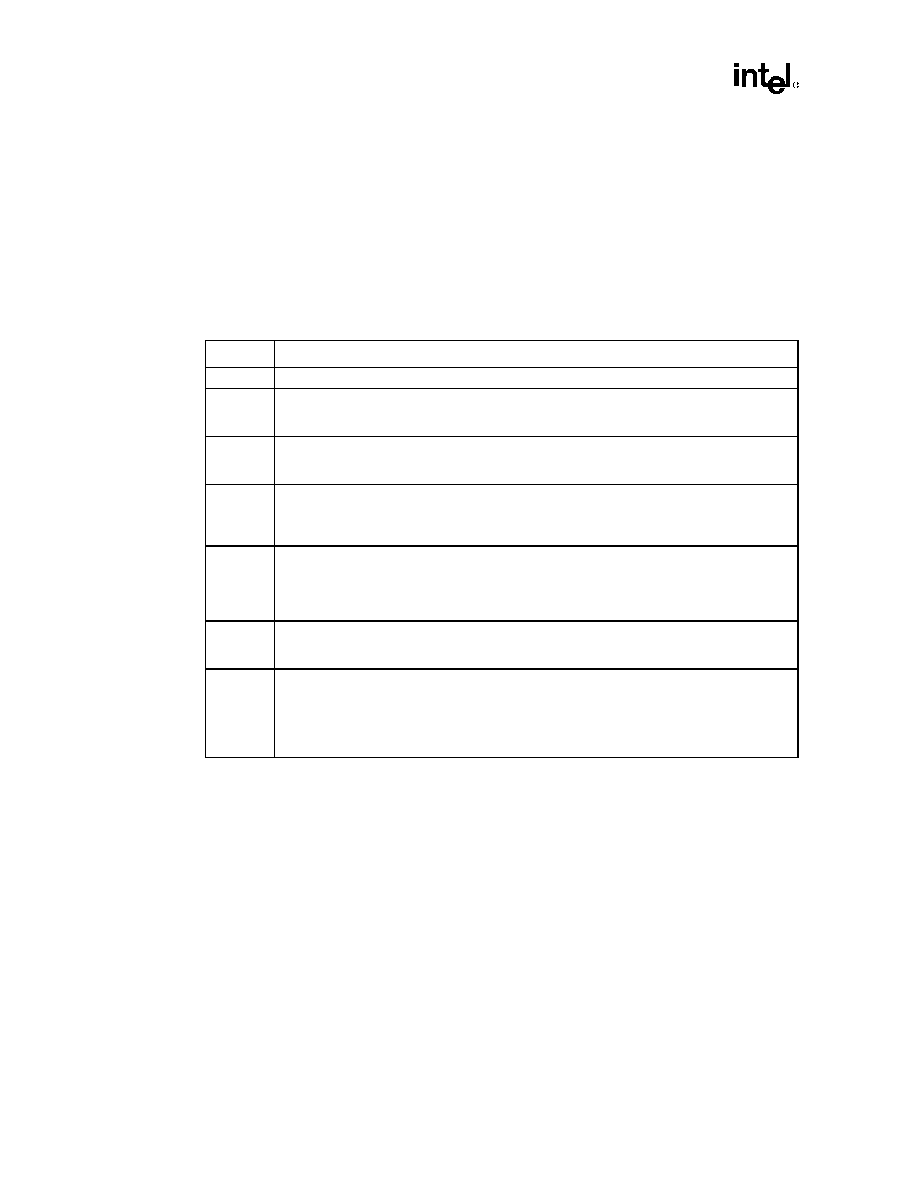

The following notations are used to describe the signal type:

I

Input pin

O

Output pin

OD

Open Drain Output pin. This pin requires a pullup to the VCC of the processor core

I/OD

Input / Open Drain Output pin. This pin requires a pullup to the VCC of the processor

core

I/O

Bi-directional Input/Output pin

The signal description also includes the type of buffer used for the particular signal:

GTL+ Open Drain GTL+ interface signal. Refer to the GTL+ I/O Specification for complete

details

PCI

PCI bus interface signals. These signals are compliant with the PCI 3.3V and 5.0V

Signaling Environment DC and AC Specifications

AGP

AGP interface signals. These signals are compatible with AGP 3.3V Signaling

Environment DC and AC Specifications

CMOS The CMOS buffers are Low Voltage TTL compatible signals. These are 3.3V only.

2.1

Host Interface Signals

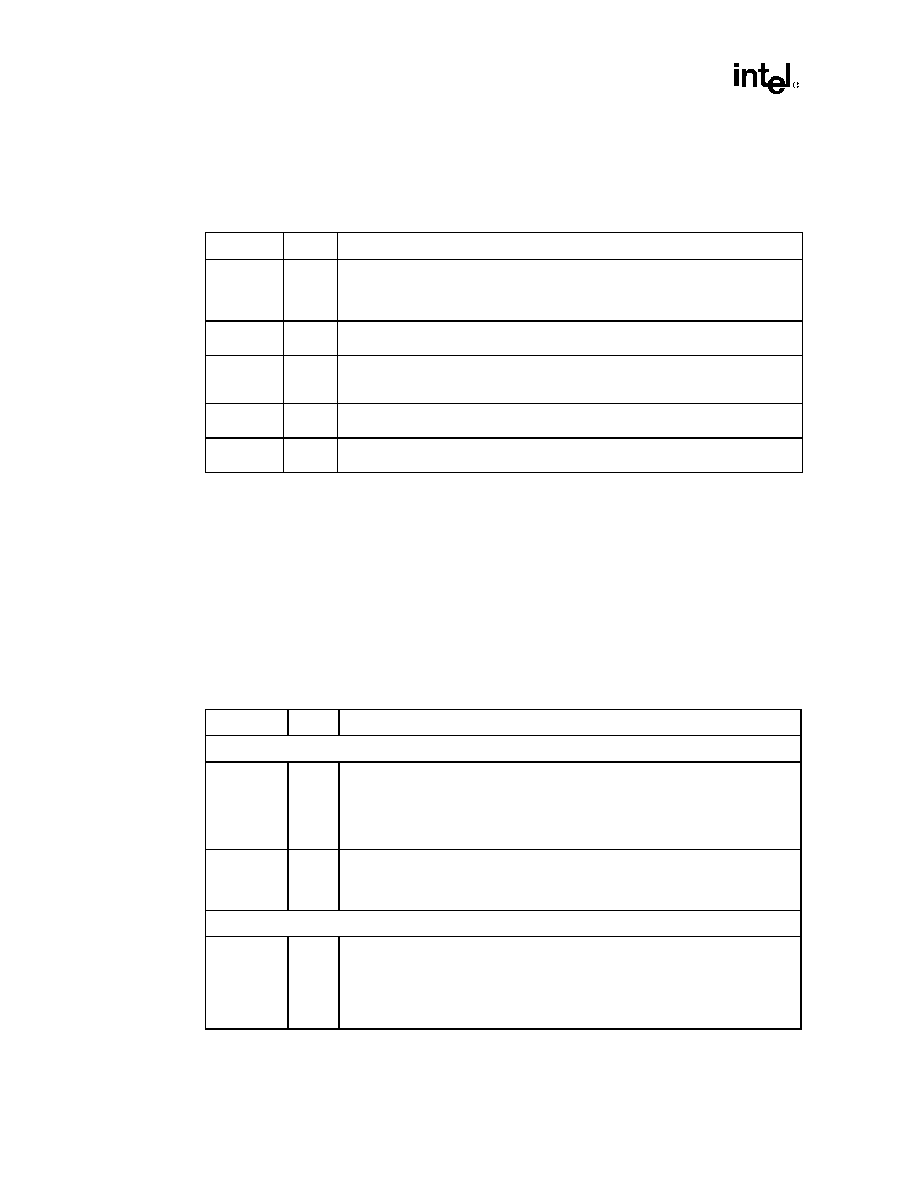

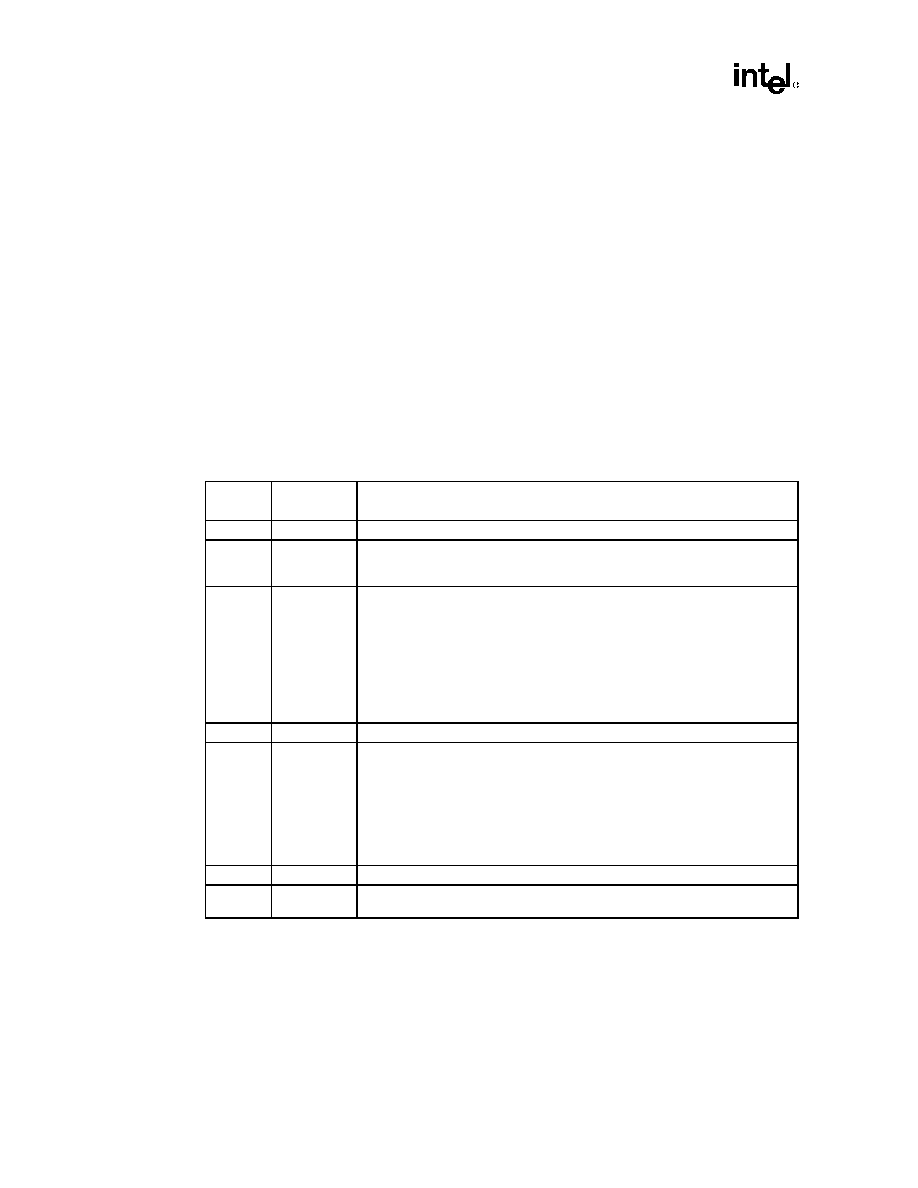

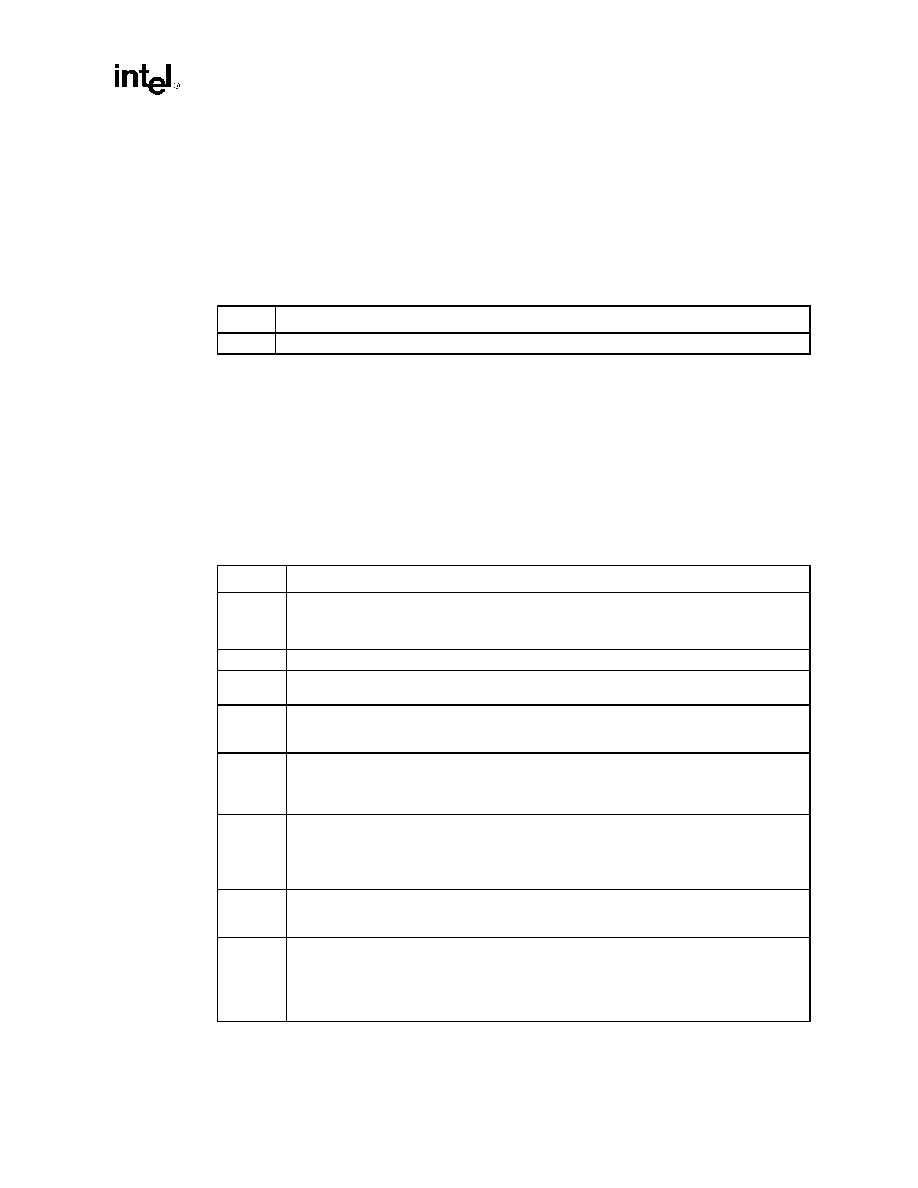

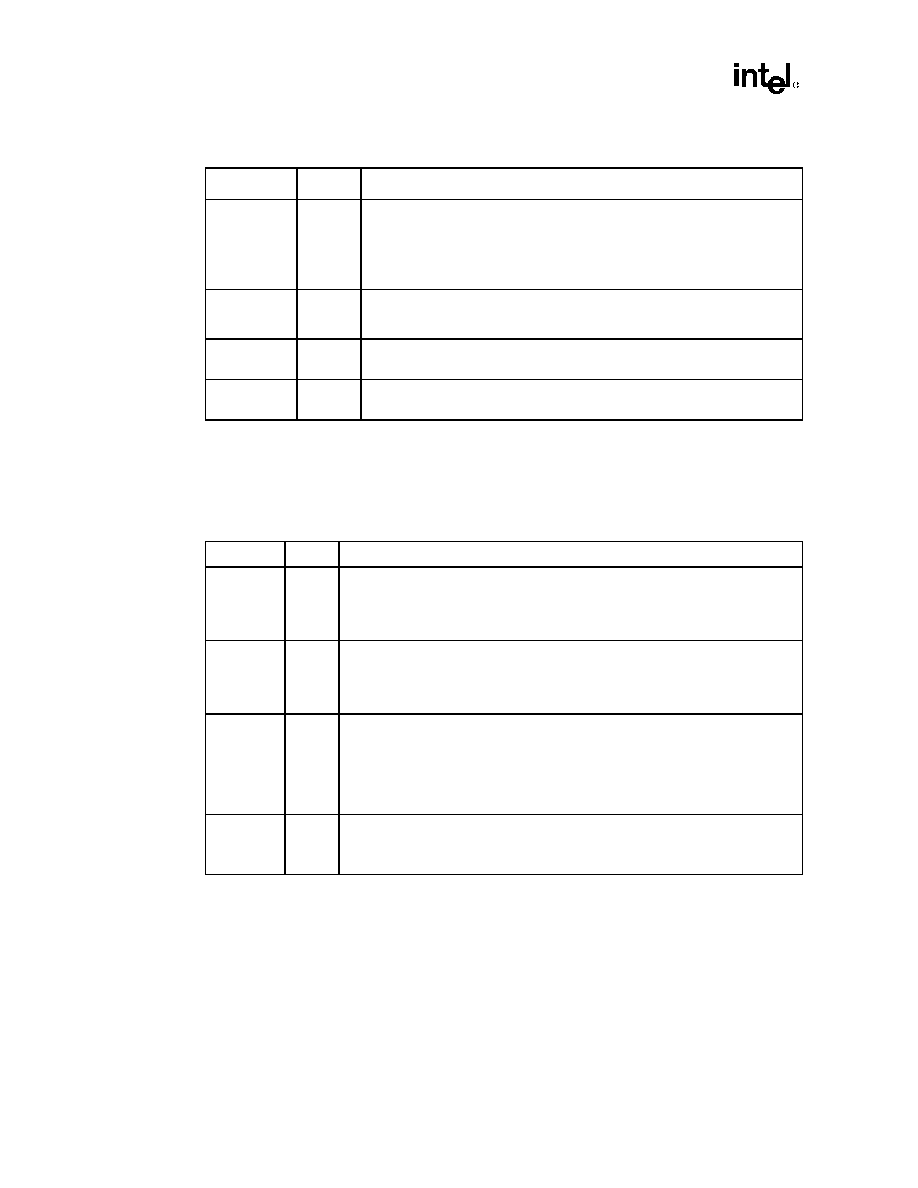

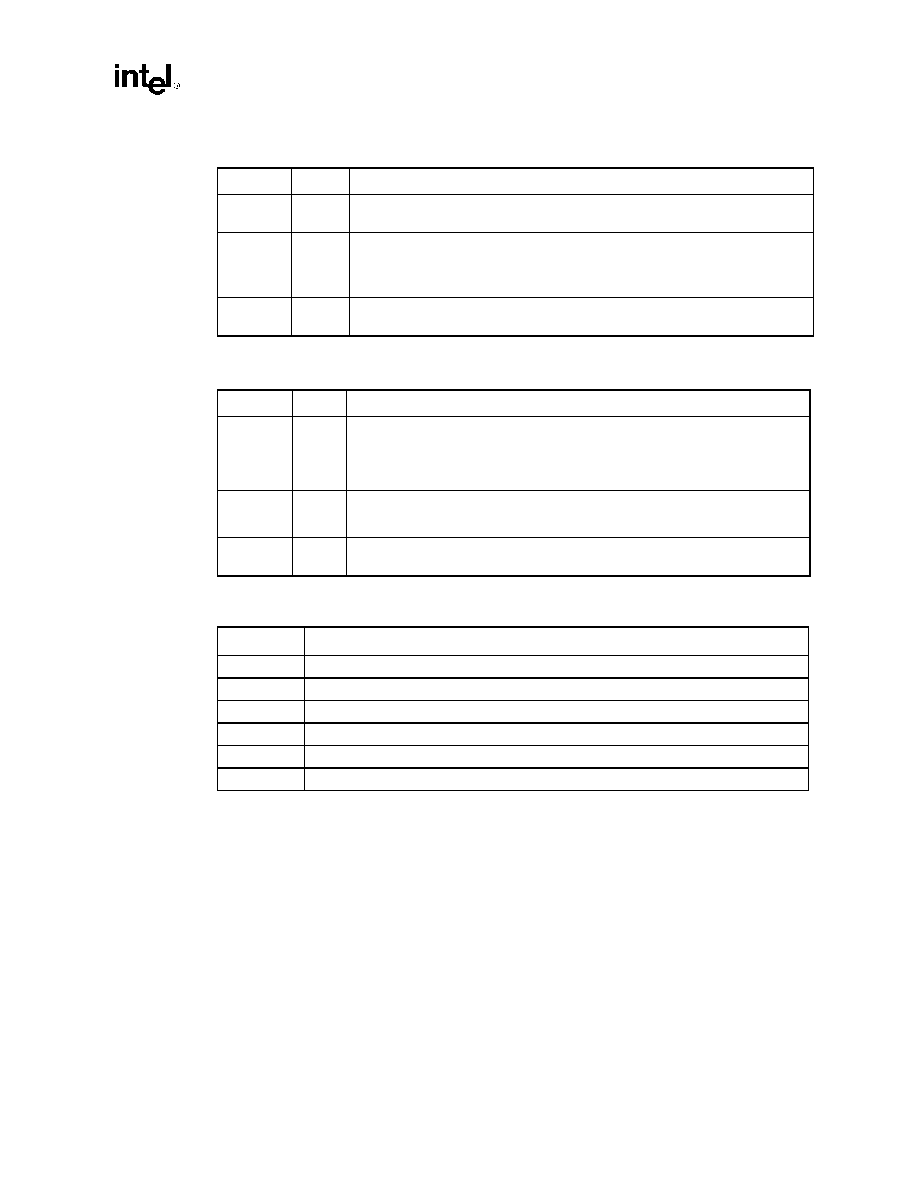

Table 2-1. Host Interface Signals (Sheet 1 of 2)

Name

Type

Description

CPURST#

O

GTL+

CPU Reset. The CPURST# pin is an output from the 82443GX. The 82443GX

generates this signal based on the PCIRST# input (from PIIX4E) and also the

SUSTAT# pin in mobile mode. The CPURST# allows the CPUs to begin execution in

a known state.

A[31:3]#

I/O

GTL+

Address Bus: A[31:3]# connect to the CPU address bus. During CPU cycles, the

A[31:3]# are inputs.

HD[63:0]#

I/O

GTL+

Host Data: These signals are connected to the CPU data bus. Note that the data

signals are inverted on the CPU bus.

Signal Description

2-2

82443GX Host Bridge Datasheet

NOTE:

1. All of the signals in the host interface are described in the CPU External Bus Specification. The preceding

table highlights 82443GX specific uses of these signals.

ADS#

I/O

GTL+

Address Strobe: The CPU bus owner asserts ADS# to indicate the first of two

cycles of a request phase.

BNR#

I/O

GTL+

Block Next Request: Used to block the current request bus owner from issuing a

new request. This signal is used to dynamically control the CPU bus pipeline depth.

BPRI#

O

GTL+

Priority Agent Bus Request: The 82443GX is the only Priority Agent on the CPU

bus. It asserts this signal to obtain the ownership of the address bus. This signal has

priority over symmetric bus requests and will cause the current symmetric owner to

stop issuing new transactions unless the HLOCK# signal was asserted.

BREQ0#

O

GTL+

Symmetric Agent Bus Request: Asserted by the 82443GX when CPURST# is

asserted to configure the symmetric bus agents. BREQ0# is negated 2 host clocks

after CPURST# is negated.

DBSY#

I/O

GTL+

Data Bus Busy: Used by the data bus owner to hold the data bus for transfers

requiring more than one cycle.

DEFER#

O

GTL+

Defer: The 82443GX generates a deferred response as defined by the rules of the

82443GX's dynamic defer policy. The 82443GX also uses the DEFER# signal to

indicate a CPU retry response.

DRDY#

I/O

GTL+

Data Ready: Asserted for each cycle that data is transferred.

HIT#

I/O

GTL+

Hit: Indicates that a caching agent holds an unmodified version of the requested line.

Also driven in conjunction with HITM# by the target to extend the snoop window.

HITM#

I/O

GTL+

Hit Modified: Indicates that a caching agent holds a modified version of the

requested line and that this agent assumes responsibility for providing the line. Also

driven in conjunction with HIT# to extend the snoop window.

HLOCK#

I

GTL+

Host Lock: All CPU bus cycles sampled with the assertion of HLOCK# and ADS#,

until the negation of HLOCK# must be atomic, i.e. no PCI or AGP snoopable access

to DRAM is allowed when HLOCK# is asserted by the CPU.

HREQ[4:0]#

I/O

GTL+

Request Command: Asserted during both clocks of request phase. In the first clock,

the signals define the transaction type to a level of detail that is sufficient to begin a

snoop request. In the second clock, the signals carry additional information to define

the complete transaction type. The transactions supported by the 82443GX Host

Bridge are defined in the Host Interface section of this document.

HTRDY#

I/O

GTL+

Host Target Ready: Indicates that the target of the CPU transaction is able to enter

the data transfer phase.

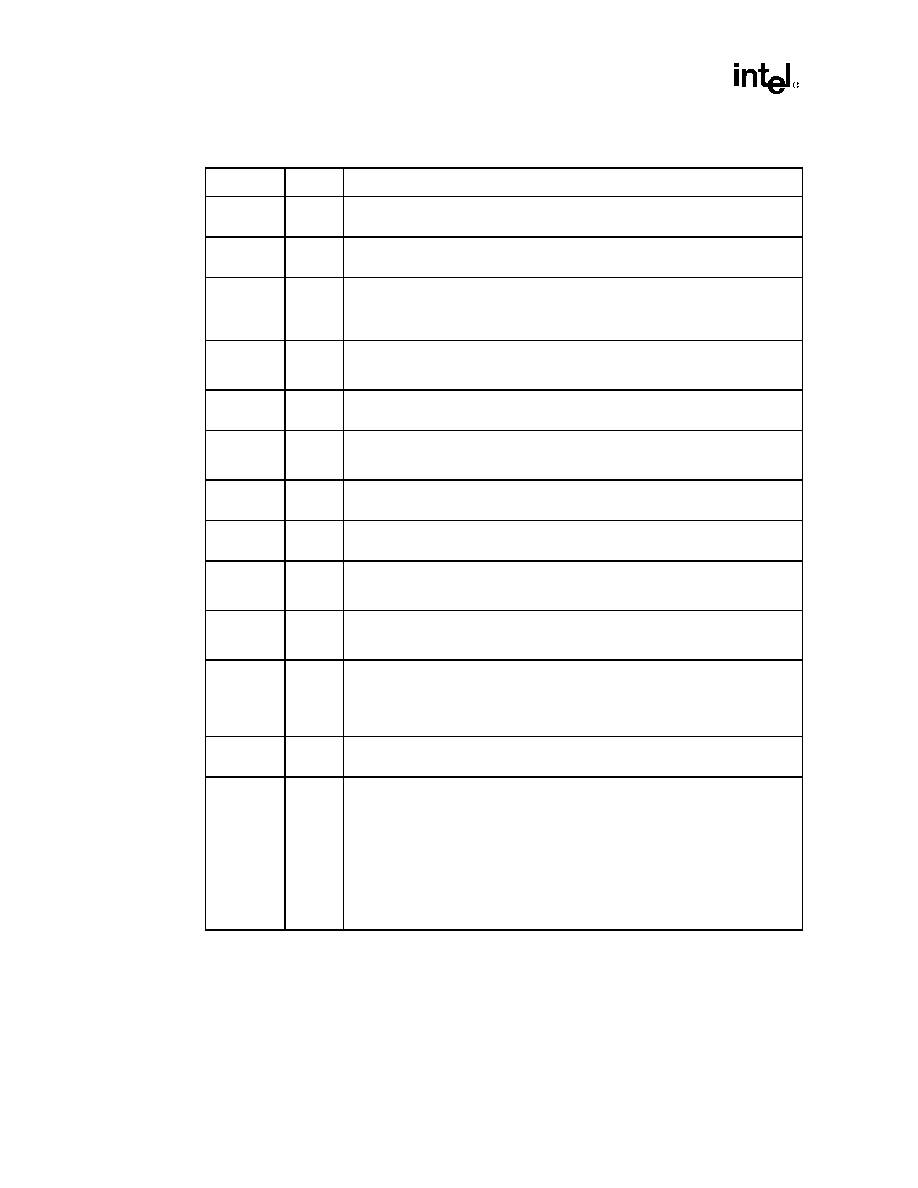

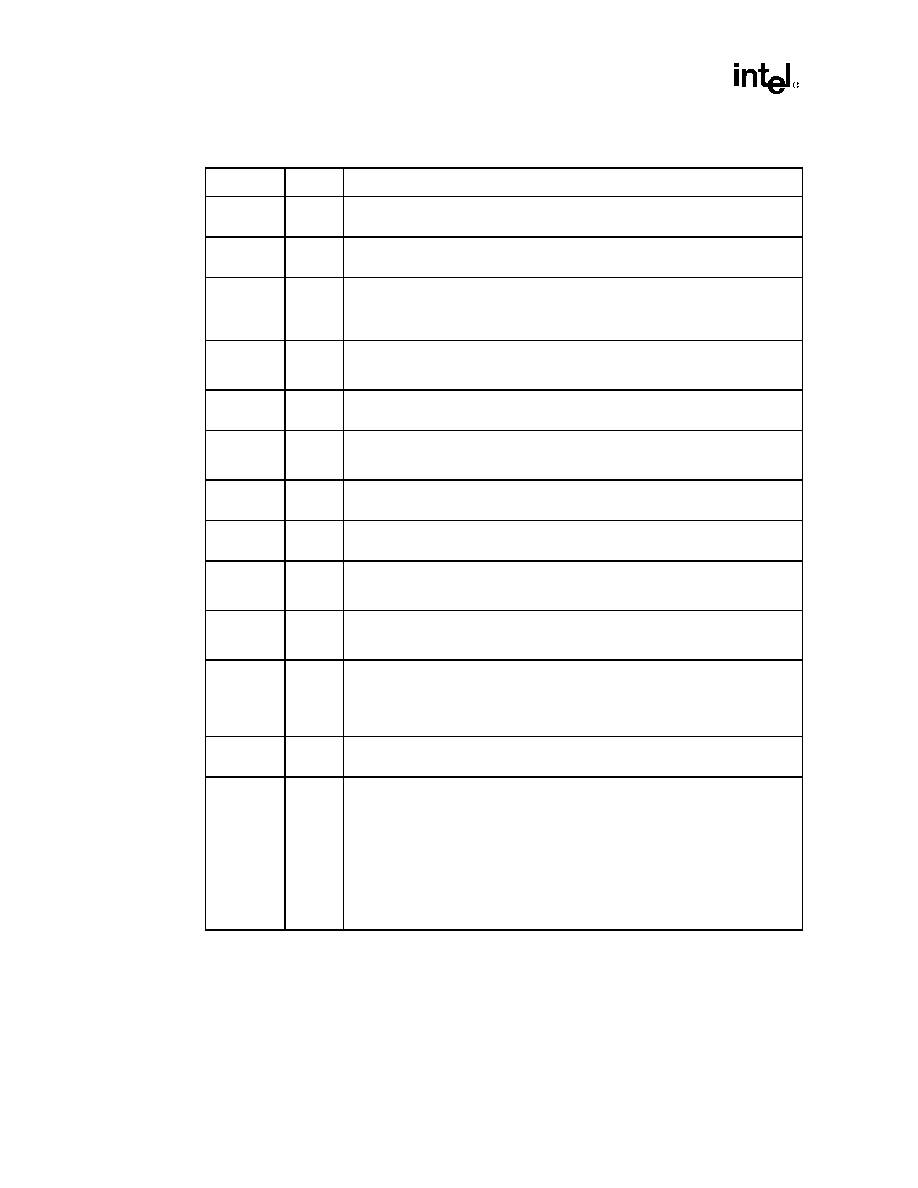

RS[2:0]#

I/O

GTL+

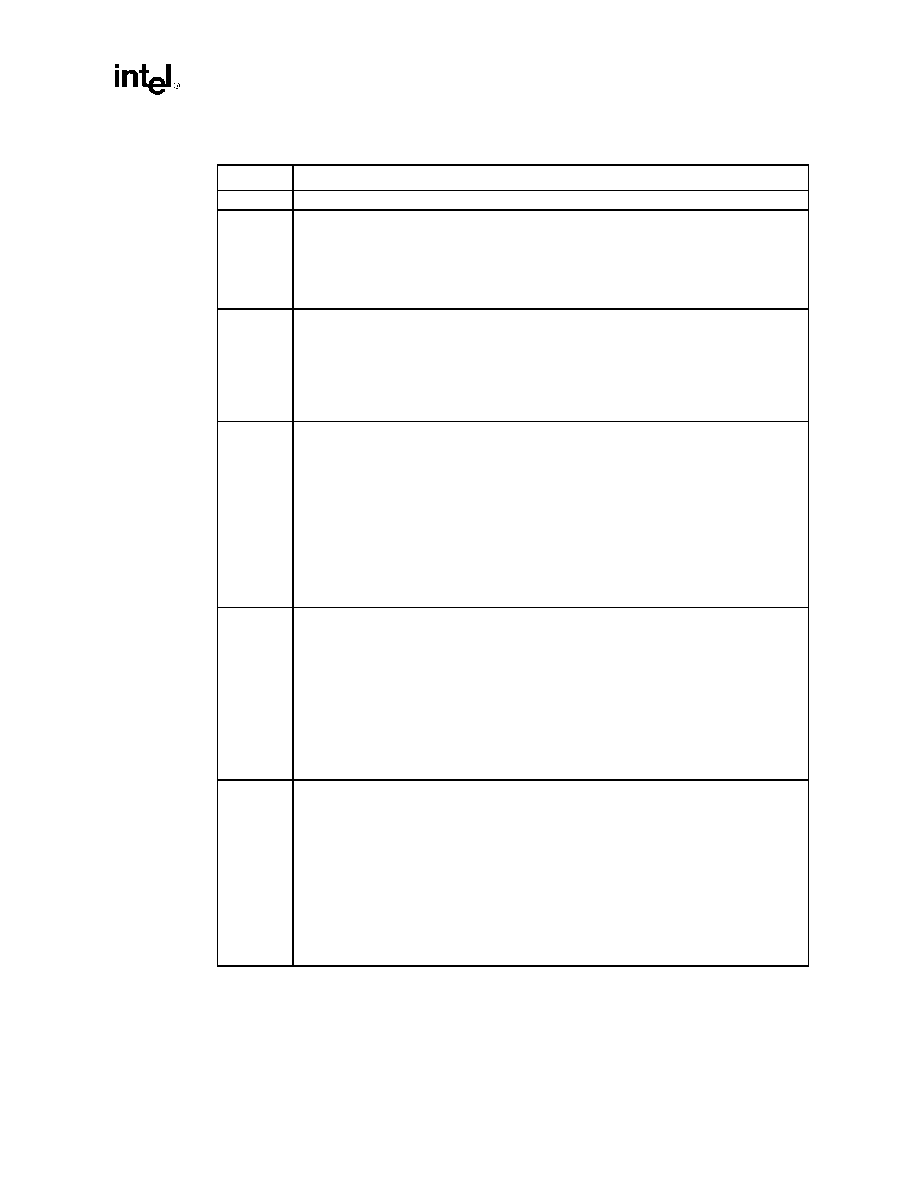

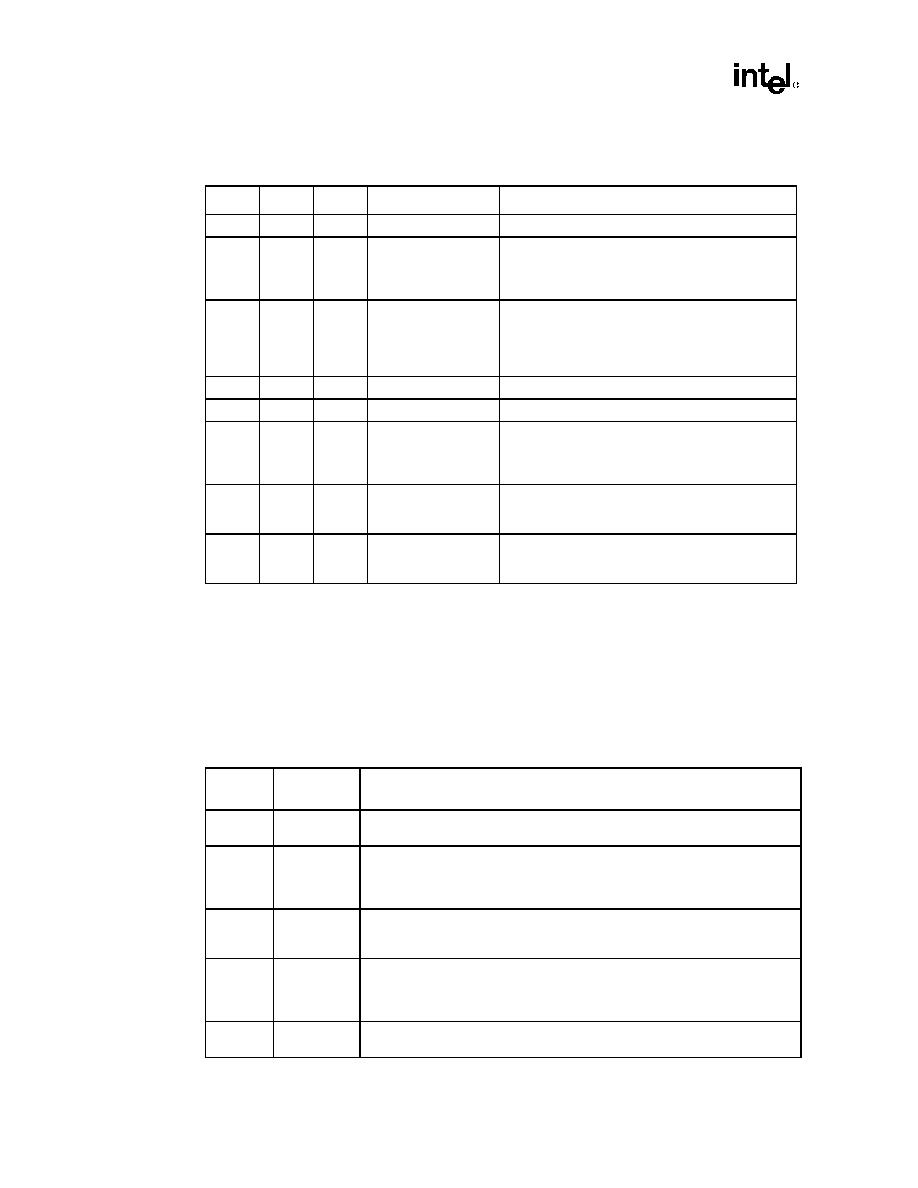

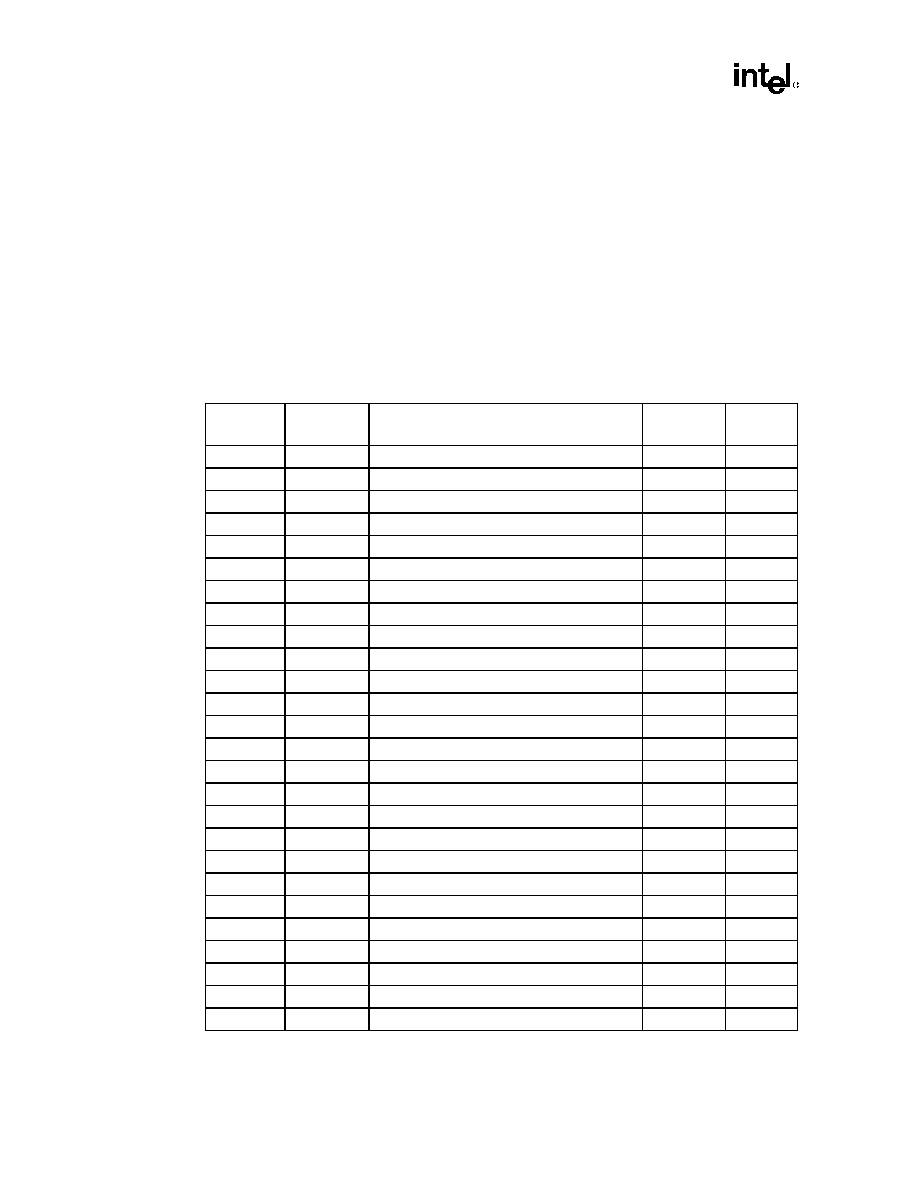

Response Signals: Indicates type of response according to the following the table:

RS[2:0]

Response type

000

Idle state

001

Retry response

010 Deferred

response

011

Reserved (not driven by 82443GX)

100

Hard Failure (not driven by 82443GX)

101

No data response

110

Implicit Writeback

111

Normal data response

Table 2-1. Host Interface Signals (Sheet 2 of 2)

Name

Type

Description

82443GX Host Bridge Datasheet

2-3

Signal Description

Table 2-2 lists the CPU bus interface signals which are NOT supported by the Intel

Æ

440GX

AGPset.

2.2

DRAM Interface

Table 2-2. Host Signals Not supported by the 82443GX

Signal

Function

Not Supported By 82443GX

A[35:32]#

Address

Extended addressing (over 4 GB)

AERR#

Address Parity Error

Parity protection on address bus

AP[1:0]#

Address Parity

Parity protection on address bus

BINIT#

Bus Initialization

Checking for bus protocol violation and protocol recovery mechanism

DEP[7:0]#

Data Bus ECC/Parity

Enhanced data bus integrity

IERR#

Internal Error

Direct internal error observation via IERR# pin

INIT#

Soft Reset

Implemented by PIIX4E, BIST supported by external logic.

BERR#

Bus Error

Unrecoverable error without a bus protocol violation

RP#

Request Parity

Parity protection on ADS# and PREQ[4:0]#

RSP#

Response Parity

Signal

Parity protection on RS[2:0]#

BP[3:2]#

BreakPoint

Breakpoint status

BPM[1:0]#

BreakPoint Monitor

Breakpoint and performance monitor

Table 2-3. DRAM Interface Signals (Sheet 1 of 2)

Name

Type

Description

CSA[7:0]#

/CSB[7:0]#

O

CMOS

Chip Select (SDRAM): These pins perform the function of selecting the

particular SDRAM components during the active state.

Note that there are 2 copies of CS# per physical memory row to improve the

loading.

DQMA[7:0]

O

CMOS

Input/Output Data Mask A-side: These pins control A half of the memory array

and act as synchronized output enables during read cycles and as a byte enables

during write cycles.

DQMB[1,5]

O

CMOS

Input/Output Data Mask B-side (SDRAM): The same function as the

corresponding signals for the A side (DQMAx). These signals are used to reduce

the loading in an ECC configuration.

GCKE

O

CMOS

Global CKE: Global CKE is used in a 4 DIMM configuration requiring power

down mode for the SDRAM. External logic must be used to implement this

function.

SRAS[B,A]#

O

CMOS

SDRAM Row Address Strobe: The SRAS[B,A]# signals are multiple copies of

the same logical SRASx signal (for loading purposes) used to generate SDRAM

command encoded on SRASx/SCASx/WE signals.

FENA

O

CMOS

FET Enable (FENA): FENA is used to select the proper MD path through the

FET switches in a 4 DIMM configuration.

SCAS[B,A]#

O

CMOS

SDRAM Column Address Strobe: The SCAS[B,A]# signals are multiple copies

of the same logical SCASx signal (for loading purposes) used to generate

SDRAM command encoded on SRASx/SCASx/WE signals.

Signal Description

2-4

82443GX Host Bridge Datasheet

2.3

PCI Interface (Primary)

MAA[14:0]

MAB[12:11]#

MAB[14,13,10]

MAB[9:0]#

O

CMOS

Memory Address(SDRAM): MAA[14:0] and MAB[14,13,12#,11#,10,9#:0#] are

used to provide the multiplexed row and column address to DRAM. There are two

sets of MA signals which drive a max. of 2 DIMMs each. MAB[12:11,9:0]# are

inverted copies of MAA[12:11,9:0]. MAA[14,13,10] and MAB[14,13,10] are

identical copies. Each MAA/MAB[14:0] line has a programmable buffer strength to

optimize for different signal loading conditions.

WEA#

WEB#

O

CMOS

Write Enable Signa: WE# is asserted during writes to DRAM. The WE# lines

have a programmable buffer strength to optimize for different signal loading

conditions.

MD[63:0]

I/O

CMOS

Memory Data: These signals are used to interface to the DRAM data bus.

MECC[7:0]

I/O

CMOS

Memory ECC Data: These signals carry Memory ECC data during access to

DRAM.

Table 2-4. Primary PCI Interface Signals (Sheet 1 of 2)

Name

Type

Description

AD[31:0]

I/O

PCI

PCI Address/Data: These signals are connected to the PCI address/data bus.

Address is driven by the 82443GX with FRAME# assertion, data is driven or received

in the following clocks. When the 82443GX acts as a target on the PCI Bus, the

AD[31:0] signals are inputs and contain the address during the first clock of FRAME#

assertion and input data (writes) or output data (reads) on subsequent clocks.

DEVSEL#

I/O

PCI

Device Select: Device select, when asserted, indicates that a PCI target device has

decoded its address as the target of the current access. The 82443GX asserts

DEVSEL# based on the DRAM address range or

AGP address range

being accessed

by a PCI initiator. As an input it indicates whether any device on the bus has been

selected.

FRAME#

I/O

PCI

Frame: FRAME# is an output when the 82443GX acts as an initiator on the PCI Bus.

FRAME# is asserted by the 82443GX to indicate the beginning and duration of an

access. The 82443GX asserts FRAME# to indicate a bus transaction is beginning.

While FRAME# is asserted, data transfers continue. When FRAME# is negated, the

transaction is in the final data phase. FRAME# is an input when the 82443GX acts as

a PCI target. As a PCI target, the 82443GX latches the C/BE[3:0]# and the AD[31:0]

signals on the first clock edge on which it samples FRAME# active.

IRDY#

I/O

PCI

Initiator Ready: IRDY# is an output when 82443GX acts as a PCI initiator and an

input when the 82443GX acts as a PCI target. The assertion of IRDY# indicates the

current PCI Bus initiator's ability to complete the current data phase of the

transaction.

Table 2-3. DRAM Interface Signals (Sheet 2 of 2)

Name

Type

Description

82443GX Host Bridge Datasheet

2-5

Signal Description

NOTE:

1. All PCI interface signals conform to the PCI Rev 2.1 specification.

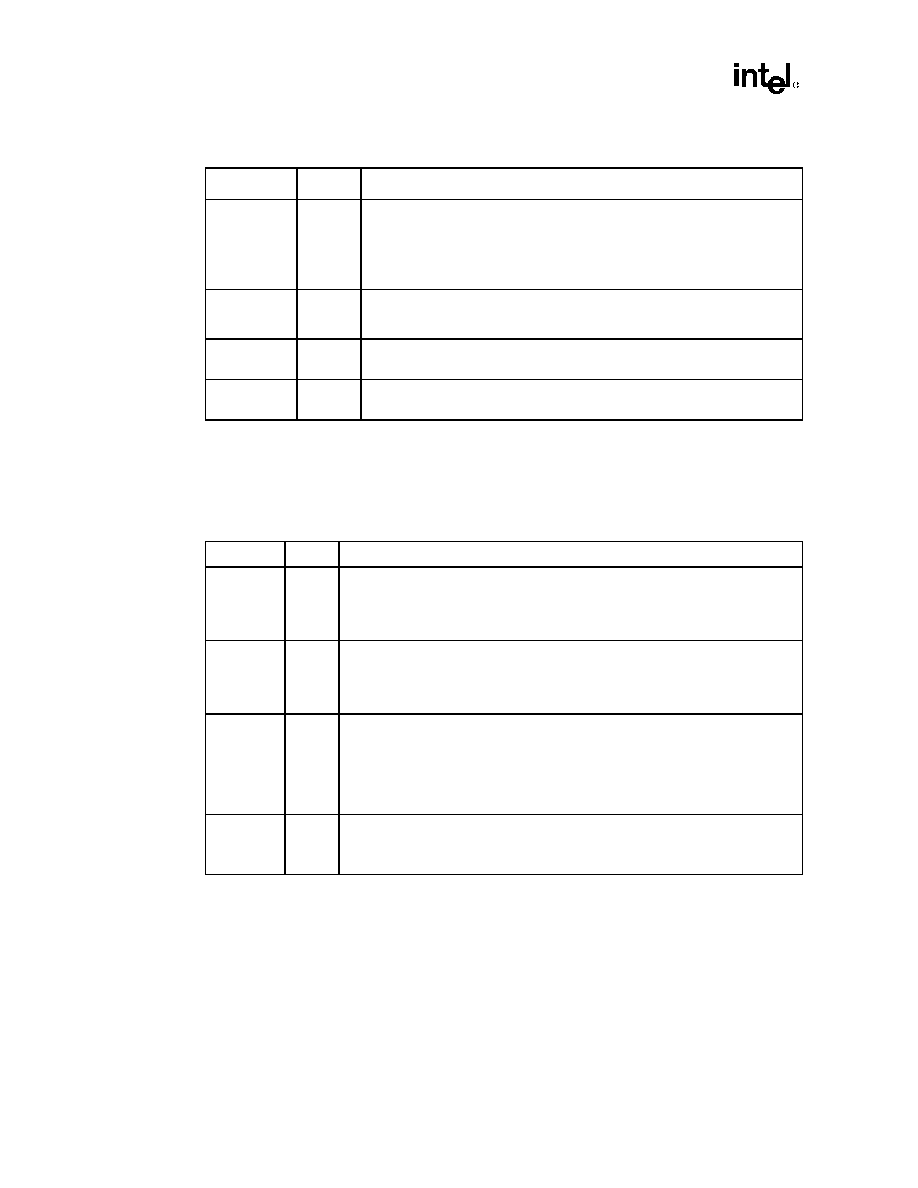

C/BE[3:0]#

I/O

PCI

Command/Byte Enable: PCI Bus Command and Byte Enable signals are

multiplexed on the same pins. During the address phase of a transaction, C/BE[3:0]#

define the bus command. During the data phase C/BE[3:0]# are used as byte

enables. The byte enables determine which byte lanes carry meaningful data. PCI

Bus command encoding and types are listed below.

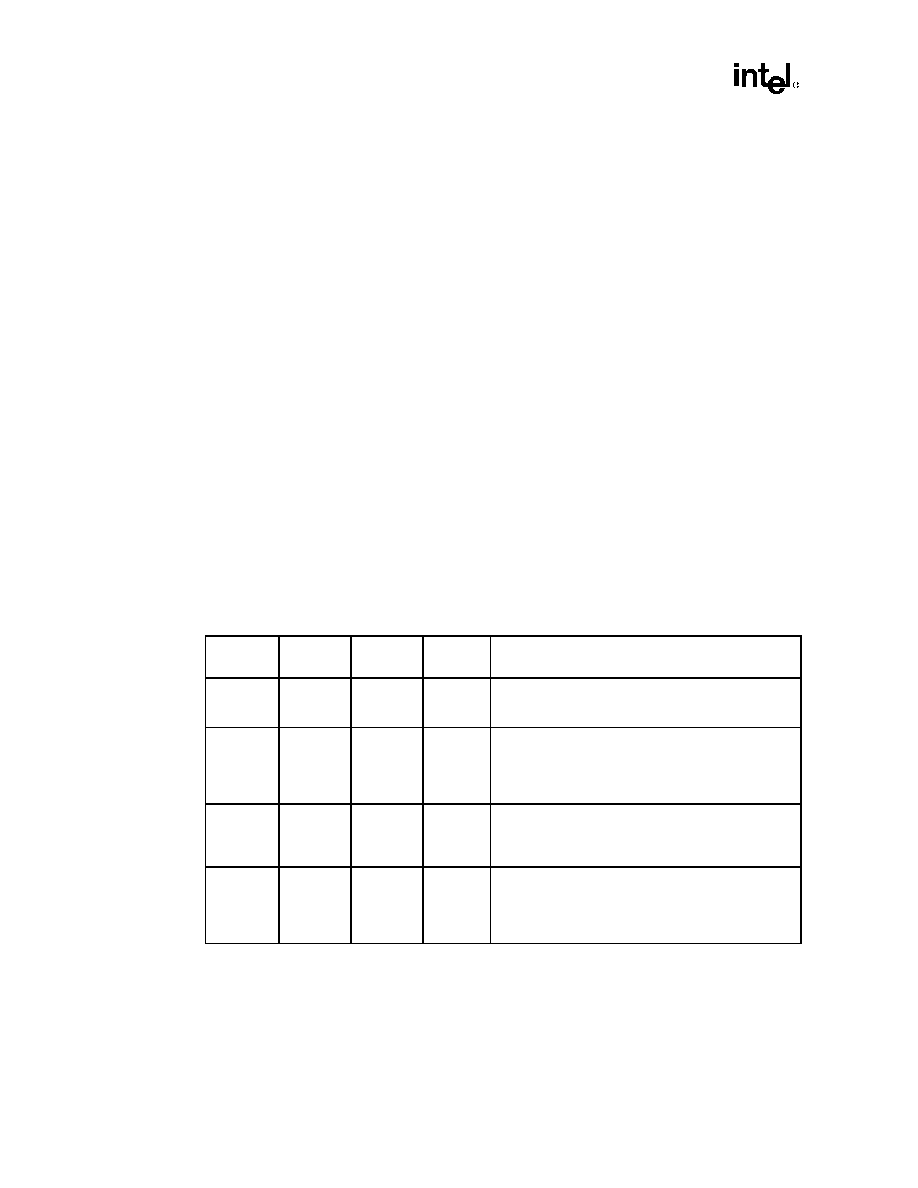

C/BE[3:0]#

Command Type

0000

Interrupt Acknowledge

0001

Special Cycle

0010

I/O Read

0011

I/O Write

0100

Reserved

0101

Reserved

0110

Memory Read

0111

Memory Write

1000

Reserved

1001

Reserved

1010

Configuration Read

1011

Configuration Write

1100

Memory Read Multiple

1101

Reserved (Dual Address Cycle)

1110

Memory Read Line

1111

Memory Write and Invalidate

PAR

I/O

PCI

Parity: PAR is driven by the 82443GX when it acts as a PCI initiator during address

and data phases for a write cycle, and during the address phase for a read cycle. PAR

is driven by the 82443GX when it acts as a PCI target during each data phase of a

PCI memory read cycle. Even parity is generated across AD[31:0] and C/BE[3:0]#.

PLOCK#

I/O

PCI

Lock: PLOCK# indicates an exclusive bus operation and may require multiple

transactions to complete. When PLOCK# is asserted, non-exclusive transactions may

proceed. The 82443GX supports lock for CPU initiated cycles only. PCI initiated

locked cycles are not supported.

TRDY#

I/O

PCI

Target Ready: TRDY# is an input when the 82443GX acts as a PCI initiator and an

output when the 82443GX acts as a PCI target. The assertion of TRDY# indicates the

target agent's ability to complete the current data phase of the transaction.

SERR#

I/O

PCI

System Error: The 82443GX asserts this signal to indicate an error condition. The

SERR# assertion by the 82443GX is enabled globally via SERRE bit of the PCICMD

register. SERR# is asserted under the following conditions:

In an ECC configuration, the 82443GX asserts SERR#, for single bit (correctable)

ECC errors or multiple bit (non-correctable) ECC errors if SERR# signaling is enabled

via the ERRCMD control register. Any ECC errors received during initialization should

be ignored.

∑

The 82443GX asserts SERR# for one clock when it detects a target abort during

82443GX initiated PCI cycle.

∑

The 82443GX can also assert SERR# when a PCI parity error occurs during the

address or data phase.

∑

The 82443GX can assert SERR# when it detects a PCI address or data parity

error on AGP.

∑

The 82443GX can assert SERR# upon detection of access to an invalid entry in

the Graphics Aperture Translation Table.

∑

The 82443GX can assert SERR# upon detecting an invalid AGP master access

outside of AGP aperture and outside of main DRAM range (i.e. in the 640k - 1M

range or above TOM).

∑

The 82443GX can assert SERR# upon detecting an invalid AGP master access

outside of AGP aperture.

∑

The 82443GX asserts SERR# for one clock when it detects a target abort during

82443GX initiated AGP cycle.

STOP#

I/O

PCI

Stop: STOP# is an input when the 82443GX acts as a PCI initiator and an output

when the 82443GX acts as a PCI target. STOP# is used for disconnect, retry, and

abort sequences on the PCI Bus.

Table 2-4. Primary PCI Interface Signals (Sheet 2 of 2)

Name

Type

Description

Signal Description

2-6

82443GX Host Bridge Datasheet

2.4

Primary PCI Sideband Interface

2.5

AGP Interface Signals

There are 17 new signals added to the normal PCI group of signals that together constitute the AGP

interface. The sections below describe their operation and use, and are organized in five groups:

∑

AGP Addressing Signals

∑

AGP Flow Control Signals

∑

AGP Status Signals

∑

AGP Clocking Signals - Strobes

∑

PCI Signals

Table 2-5. Primary PCI Sideband Interface Signals

Name

Type

Description

PHOLD#

I

PCI

PCI Hold: This signal comes from the PIIX4E. It is the PIIX4E request for PCI bus

ownership. The 82443GX will flush and disable the CPU-to-PCI write buffers before

granting the PIIX4E the PCI bus via PHLDA#. This prevents bus deadlock between

PCI and ISA.

PHLDA#

O

PCI

PCI Hold Acknowledge: This signal is driven by the 82443GX to grant PCI bus

ownership to the PIIX4E after CPU-PCI post buffers have been flushed and disabled.

WSC#

O

CMOS

Write Snoop Complete. This signal is asserted active to indicate that all that the

snoop activity on the CPU bus on the behalf of the last PCI-DRAM write transaction is

complete and that is safe to send the APIC interrupt message.

PREQ[4:0]#

I

PCI

PCI Bus Request: PREQ[4:0]# are the PCI bus request signals used as inputs by the

internal PCI arbiter.

PGNT[4:0]#

O

PCI

PCI Grant: PGNT[4:0]# are the PCI bus grant output signals generated by the internal

PCI arbiter.

Table 2-6. AGP Interface Signals (Sheet 1 of 3)

Name

Type

Description

AGP Sideband Addressing Signals

1

PIPE#

I

AGP

Pipelined Read:

This signal is asserted by the current master to indicate a full width

address is to be queued by the target. The master queues one request each rising

clock edge while PIPE# is asserted. When PIPE# is deasserted no new requests are

queued across the AD bus. PIPE# is a sustained tri-state signal from

masters

(graphics controller)

and is an input to the 82443GX. Note that initial AGP designs

may not use PIPE#.

SBA[7:0]

I

AGP

Sideband Address: This bus

provides an additional bus to pass address and

command to the 82443GX from the AGP master. Note that, when sideband

addressing is disabled, these signals are isolated (no external/internal pull-ups are

required).

AGP Flow Control Signals

RBF#

I

AGP

Read Buffer Full.

This signal indicates if the master is ready to accept previously

requested low priority read data. When RBF# is asserted the 82443GX is not allowed

to return low priority read data to the AGP master on the first block. RBF# is only

sampled at the beginning of a cycle.

If the AGP master is always ready to accept return read data then it is not required to

implement this signal.

82443GX Host Bridge Datasheet

2-7

Signal Description

AGP Status Signals

ST[2:0]

O

AGP

Status

Bus: This bus provides information from the arbiter to a AGP Master on what

it may do. ST[2:0] only have meaning to the master when its GGNT# is asserted.

When GGNT# is deasserted these signals have no meaning and must be ignored.

000 Indicates that previously requested low priority read data is being returned to

the master.

001 Indicates that previously requested high priority read data is being returned to

the master.

010 Indicates that the master is to provide low priority write data for a previously

queued write command.

011 Indicates that the master is to provide high priority write data for a previously

queued write command.

100 Reserved

101 Reserved

110 Reserved

111 Indicates that the master has been given permission to start a bus transaction.

The master may queue AGP requests by asserting PIPE# or start a PCI

transaction by asserting FRAME#. ST[2:0] are always an output from the

82443GX and an input to the master.

AGP Clocking Signals - Strobes

ADSTB_A

I/O

AGP

AD Bus Strobe A: This signal provides timing for double clocked data on the AD bus.

The agent that is providing data drives this signal. This signal requires an 8.2K ohm

external pull-up resistor.

ADSTB_B

I/O

AGP

AD Bus Strobe B: This signal is an additional copy of the AD_STBA signal. This

signal requires an 8.2K ohm external pull-up resistor.

SBSTB

I

AGP

Sideband Strobe: THis signal provides timing for a side-band bus. This signal

requires an 8.2K ohm external pull-up resistor.

AGP FRAME# Protocol SIgnals (similar to PCI)

2

GFRAME#

I/O

AGP

Graphics Frame: Same as PCI. Not used by AGP. GFRAME# remains deasserted

by its own pull up resistor.

GIRDY#

I/O

AGP

Graphics Initiator Ready: New meaning. GIRDY# indicates the AGP compliant

master is ready to provide

all

write data for the current transaction. Once IRDY# is

asserted for a write operation, the master is not allowed to insert wait states. The

assertion of IRDY# for reads indicates that the master is ready to transfer to a

subsequent block (32 bytes) of read data. The master is

never

allowed to insert wait

states during the initial data transfer (32 bytes) of a read transaction. However, it may

insert wait states after each 32 byte block is transferred.

(There is no GFRAME# -- GIRDY# relationship for AGP transactions.)

GTRDY#

I/O

AGP

Graphics Target Ready: New meaning. GTRDY# indicates the AGP compliant

target is ready to provide read data for the entire transaction (when the transfer size is

less than or equal to 32 bytes) or is ready to transfer the initial or subsequent block

(32 bytes) of data when the transfer size is greater than 32 bytes. The target is

allowed to insert wait states after each block (32 bytes) is transferred on both read

and write transactions.

GSTOP#

I/O

AGP

Graphics Stop: Same as PCI. Not used by AGP.

GDEVSEL#

I/O

AGP

Graphics Device Select: Same as PCI. Not used by AGP.

GREQ#

I

AGP

Graphics Request: Same as PCI. (Used to request access to the bus to initiate a

PCI or AGP request.)

Table 2-6. AGP Interface Signals (Sheet 2 of 3)

Name

Type

Description

Signal Description

2-8

82443GX Host Bridge Datasheet

NOTE:

1.

AGP Sideband Addressing Signals.

The above table contains two mechanisms to queue requests by

the AGP master. Note that the master can only use one mechanism. When PIPE# is used to queue

addresses the master is not allowed to queue addresses using the SBA bus. For example, during

configuration time, if the master indicates that it can use either mechanism, the configuration software will

indicate which mechanism the master will use. Once this choice has been made, the master will continue to

use the mechanism selected until the master is reset (and reprogrammed) to use the other mode. This

change of modes is not a dynamic mechanism but rather a static decision when the device is first being

configured after reset.

2. PCI signals are redefined when used in AGP transactions carried using AGP protocol extension. For

transactions on the AGP interface carried using PCI protocol these signals completely preserve PCI

semantics. The exact role of all PCI signals during AGP transactions is in Table 2-6.

3. The LOCK# signal is not supported on the AGP interface (even for PCI operations).

4. PCI signals described in Table 2-4 behave according to PCI 2.1 specifications when used to perform PCI

transactions on the AGP Interface.

2.6

Clocks, Reset, and Miscellaneous

GGNT#

O

AGP

Graphics Grant: Same meaning as PCI but additional information is provided on

ST[2:0]. The additional information indicates that the selected master is the recipient

of previously requested read data (high or normal priority), it is to provide write data

(high or normal priority), for a previously queued write command or has been given

permission to start a bus transaction (AGP or PCI).

GAD[31:0]

I/O

AGP

Graphics Address/Data: Same as PCI.

GC/BE[3:0]#

I/O

AGP

Graphics Command/Byte Enables: Slightly different meaning. Provides command

information (different commands than PCI) when requests are being queued when

using PIPE#. Provide valid byte information during AGP write transactions and are

not used during the return of read data.

GPAR

I/O

AGP

Graphics Parity: Same as PCI. Not used on AGP transactions, but used during PCI

transactions as defined by the PCI specification.

Table 2-6. AGP Interface Signals (Sheet 3 of 3)

Name

Type

Description

Table 2-7. Clocks, Reset, and Miscellaneous (Sheet 1 of 2)

Name

Type

Description

HCLKIN

I

CMOS

Host Clock In: This pin receives a buffered host clock. This clock is used by all of the

82443GX logic that is in the Host clock domain.

When SUSTAT# is active, there is an internal 100K ohm pull down on this signal.

PCLKIN

I

CMOS

PCI Clock In: This is a buffered PCI clock reference that is synchronously derived by

an external clock synthesizer component from the host clock. This clock is used by all

of the 82443GX logic that is in the PCI clock domain.

When SUSTAT# is active, there is an internal 100K ohm pull down on this signal.

DCLKO

O

CMOS

SDRAM Clock Out: 100 MHz SDRAM clock reference. It feeds an external buffer

clock device that produces multiple copies for the DIMMs.

DCLKWR

I

CMOS

SDRAM Write Clock: Feedback reference from the external SDRAM clock buffer.

PCIRST#

I

CMOS

PCI Reset: When asserted, this signal will reset the 82443GX logic. All PCI output

and bi-directional signals will also tri-state compliant to PCI Rev 2.0 and 2.1

specifications.

When SUSTAT# is active, there is an internal 100K ohm pull down on this signal.

GCLKIN

I

CMOS

AGP Clock In: The GCLKIN input is a feedback reference from the GCLKOUT signal.

82443GX Host Bridge Datasheet

2-9

Signal Description

2.7

Power-Up/Reset Strap Options

Table 2-10 is the list of all power-up options that are loaded into the 82443GX during cold reset.

The 82443GX is required to float all the signals connected to straps during cold reset and keep

them floated for a minimum of 4 host clocks after the end of cold reset sequence. Cold reset

sequence is performed when the 82443GX power is applied.

Note:

All signals used to select power-up strap options are connected to either internal pull-down or pull-

up resistors of minimum 50K ohms (maximum is 150K). That selects a default mode on the signal

during reset. To enable different modes, external pull ups or pull downs (the opposite of the internal

GCLKO

O

CMOS

AGP Clock Out: The frequency is 66 MHz. The GCLKOUT output is used to feed

both the reference input pin on the 82443GX and the AGP compliant device.

CRESET#

O

CMOS

Delayed CPU Reset: CRESET# is a delayed copy of CPURST#. This signal is used

to control the multiplexer for the CPU strap signals. CRESET# is delayed from

CPURST# by two host clocks.

Note: This pin requires an external pull-up resistor. If not used, no pull up is required.

TESTIN#

I

CMOS

Test Input: This pin is used for manufacturing, and board level test purposes.

Note: This pin has an internal 50K ohm pull-up.

Table 2-8. Power Management Interface

Name

Type

Description

CLKRUN#

I/OD

CMOS

Primary PCI Clock Run: The 82443GX requests the central resource (PIIX4E) to

start or maintain the PCI clock by the assertion of CLKRUN#. The 82443GX tristates

CLKRUN# upon deassertion of PCIRST# (since CLK is running upon deassertion of

reset). If connected to PIIX4E an external 2.7K Ohm pull-up is required for Desktop,

Mobile requires (8.2k≠10K) pull-up. Otherwise, a 100 Ohm pull down is required.

SUSTAT#

I

CMOS

Suspend Status (from PIIX): SUSTAT# signals the system suspend state transition

from the PIIX4E. It is used to isolate the suspend voltage well and enter/exit DRAM

self-refresh mode. During POS/STR SUSTAT# is active.

GXPWROK

I

CMOS

GX Power OK: GXPWROK input must be connected to the PWROK signal that

indicates valid power is applied to the 82443GX.

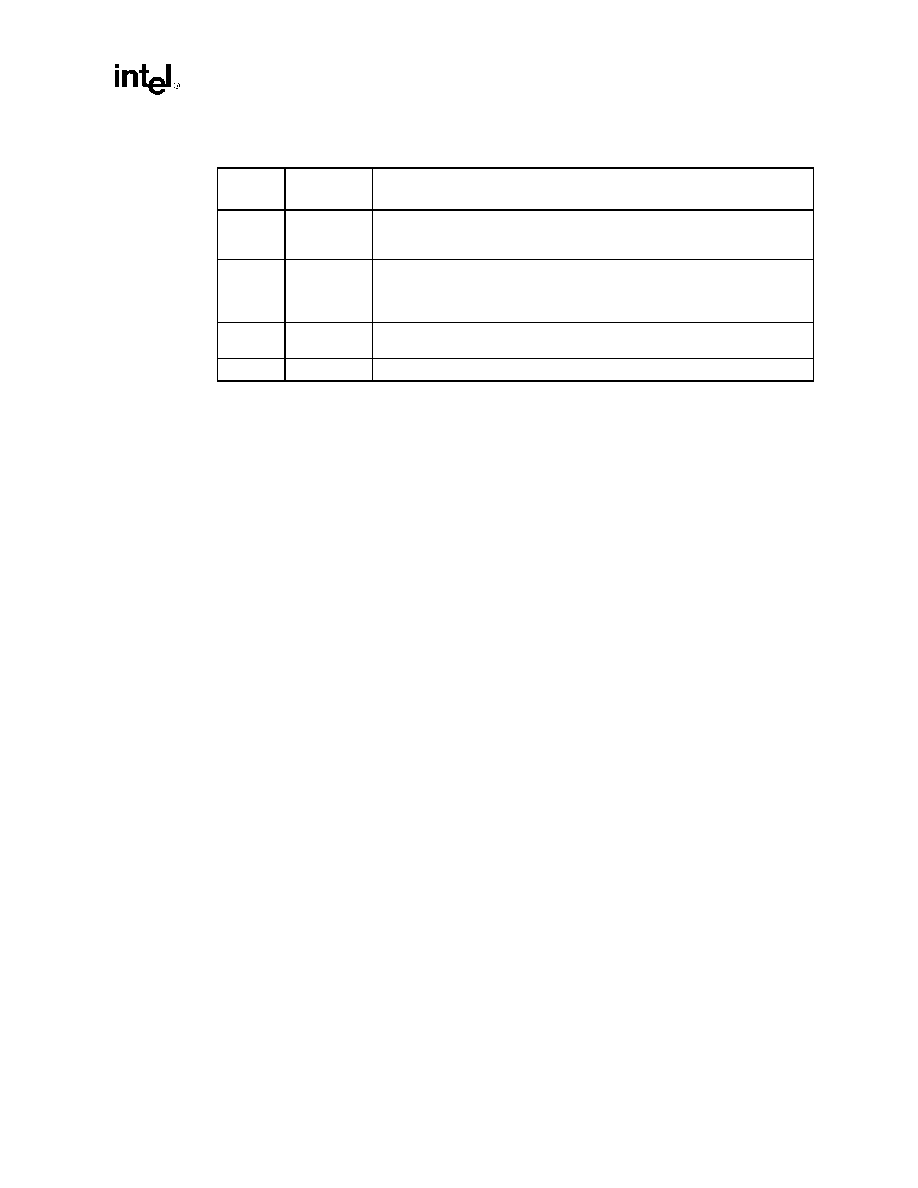

Table 2-9. Reference Pins

Name

Description

GTLREF[B:A]

GTL Buffer voltage reference input

VTT[B:A]

GTL Threshold voltage for early clamps

VCC

Power pin @ 3.3V

VSS

Ground

REF5V

PCI 5V reference voltage (for 5V tolerant buffers)

AGPREF

External Input Reference

Table 2-7. Clocks, Reset, and Miscellaneous (Sheet 2 of 2)

Name

Type

Description

Signal Description

2-10

82443GX Host Bridge Datasheet

resistor) of approximately 10K ohm can be connected to particular signals. These pull up or pull

down resistors should be connected to the 3.3V power supply.

During normal operation of the 82443GX, including while it is in suspend mode, the paths from

GND or Vcc to internal strapping resistors are disabled to effectively disable the resistors. In these

cases, the MAB# lines are driven by the 82443GX to a valid voltage levels.

Note:

Note that when resuming from suspend, even while PCIRST# is active, the MAB# lines remain

driven by the 82443GX and the strapping latches maintain the value stored during the cold reset.

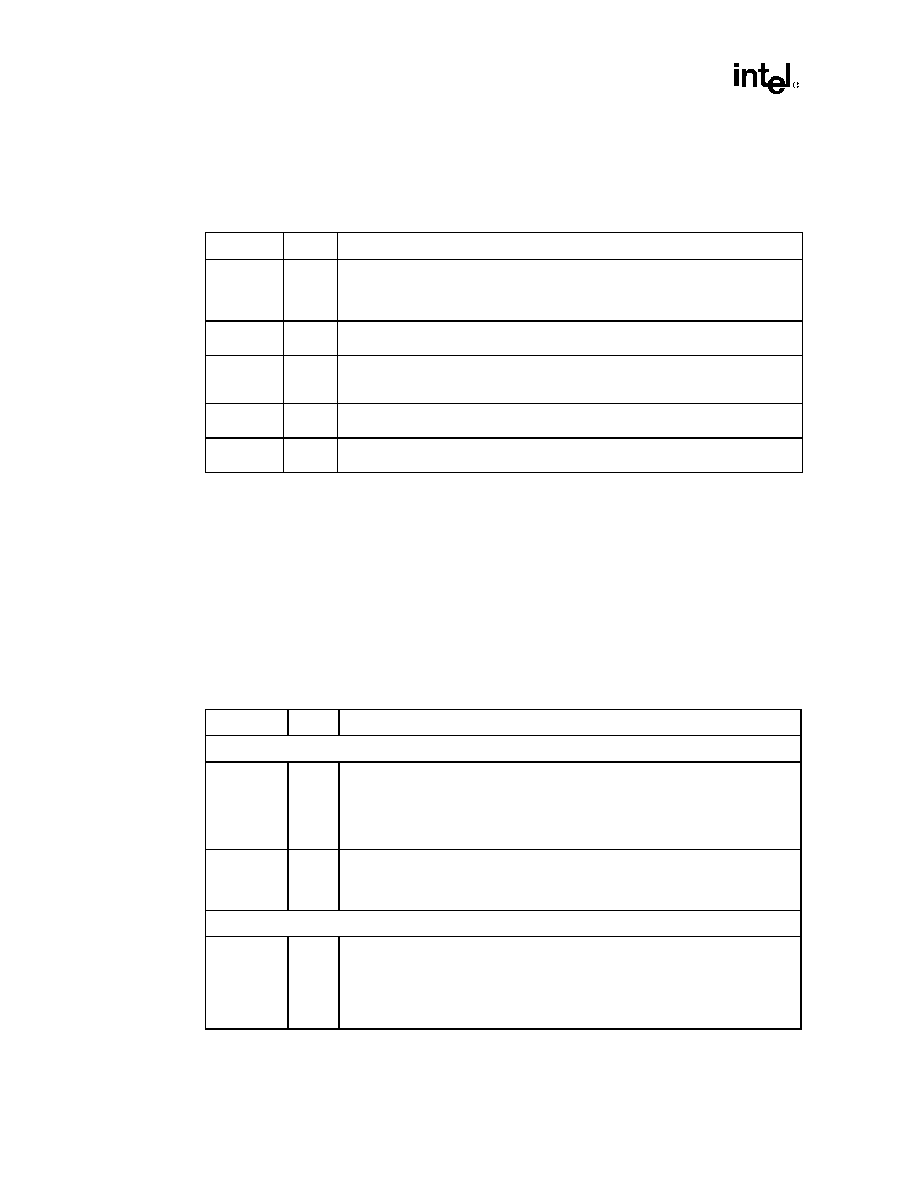

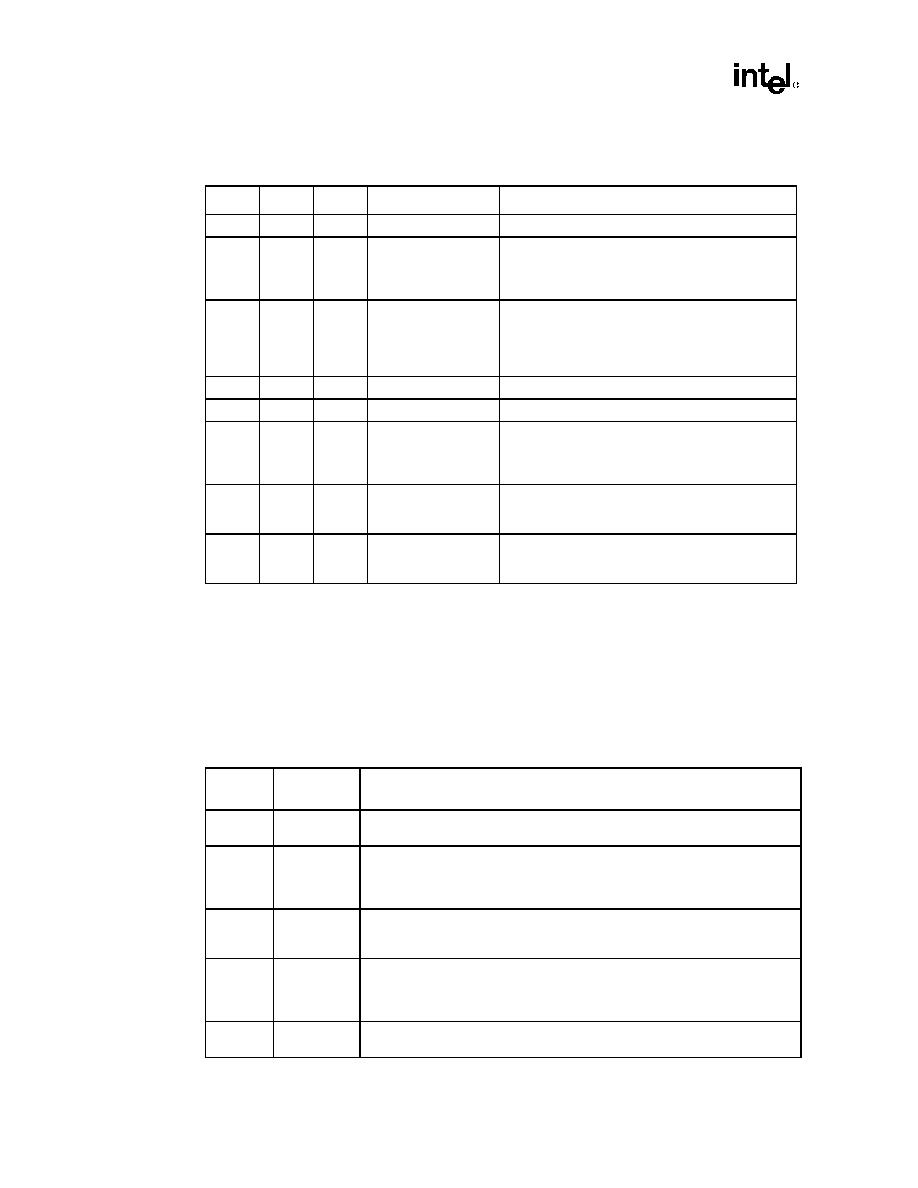

This first column in Table 2-10 lists the signal that is sampled to obtain the strapping option. The

second column shows which register the strapping option is loaded into. The third column is a

description of what functionality the strapping selects.

The GTL+ signals are connected to the VTT through the normal pull-ups. CPU bus straps

controlled by the 82443GX (e.g. A7# and A15#), are driven active at least six clocks prior to the

active-to-inactive edge of CPURST# and driven inactive four clocks after the active-to-inactive

edge of the CPURST#.

NOTE:

1. Proper strapping must be used to define logical values for these signals. Default value "0", or "1" provided by

the internal pull-up or pull-down resistor can be overridden by the external pull-up, or pull-down resistor.

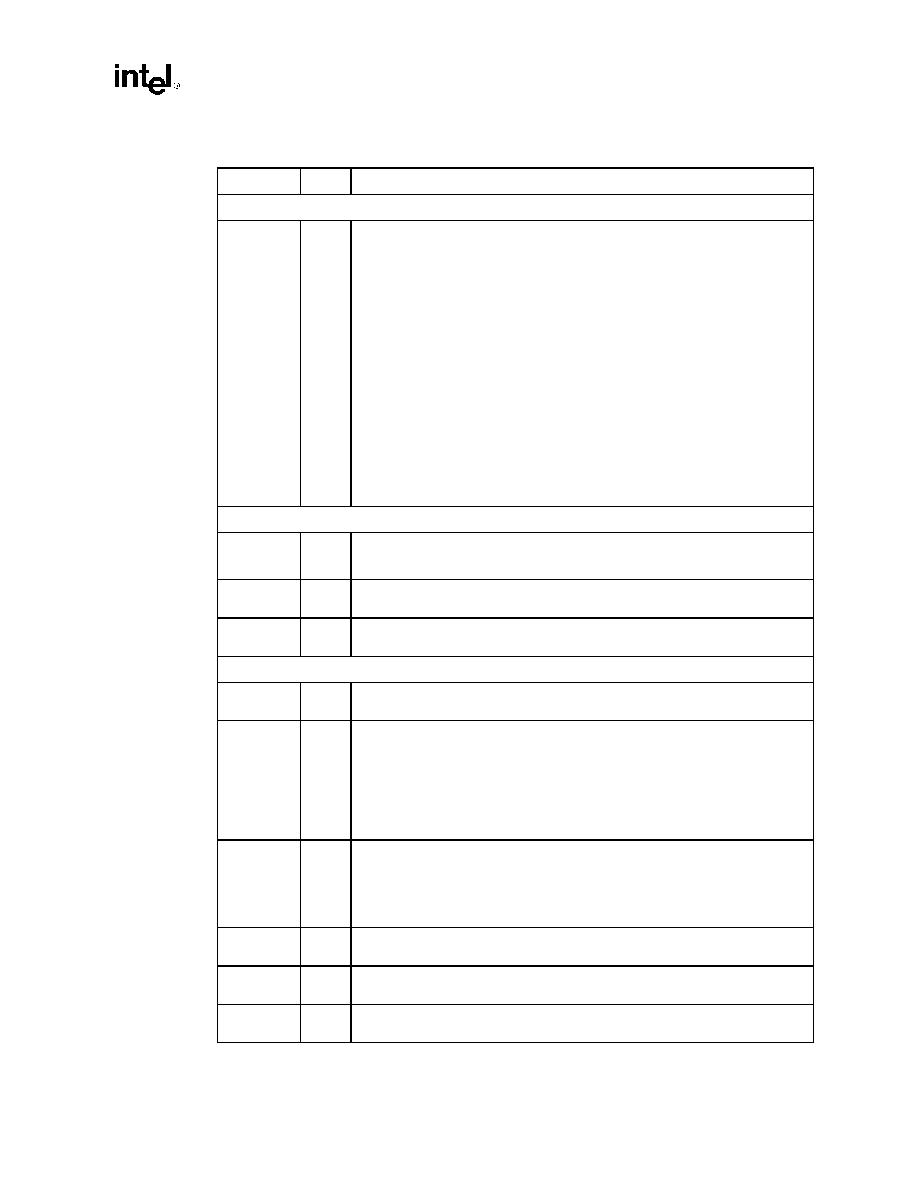

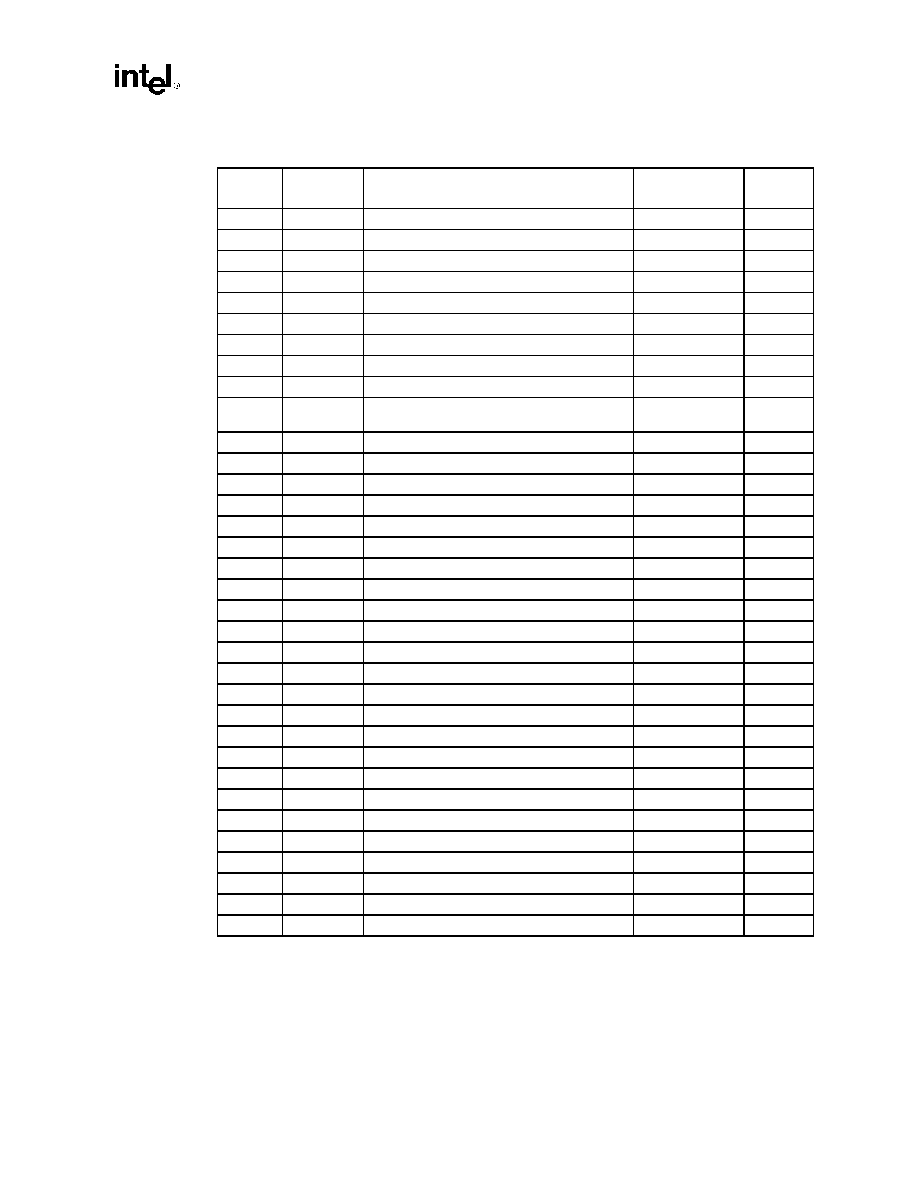

Table 2-10. Strapping Options

Signal

Register

Name[bit]

Description

MAB13#

Reserved.

MAB12#

NBXCFG[13]

MAB12# is strapped to 1 for a host bus frequency of 100 MHz. Strapping

MAB12# to 0 is a reserved condition. An internal pull-down provides a default

setting of 0.

MAB11#

NBXCFG[2]

In-Order Queue Depth Enable: If MAB11# is strapped to 0 during the rising

edge of PCIRST#, then the 82442GX will drive A7# low during the CPURST#

deassertion. This forces the CPU bus to be configured for non-pipelined

operation.

If MAB11 is strapped to 1 (default), then the 82443GX does not drive the A7# low

during reset, and A7# is sampled in default non-driven state (i.e. pulled-up as far

as GTL+ termination is concerned) then the maximum allowable queue depth by

the CPU bus protocol is selected (i.e., 8).

Note that internal pull-up is used to provide pipelined bus mode as a default.

MAB10

--

Reserved.

MAB9#

PMCR[1]

AGP Disable: When strapped to a 1, the AGP interface is disabled, all AGP

signals are tri-stated and isolated. When strapped to a 0 (default), the AGP

interface is enabled.

When MMCONFIG is strapped active, we require that AGP_DISABLE is also

strapped active. When MMCONFIG is strapped inactive, AGP_DISABLE can be

strapped active or inactive but IDSEL_REDIRECT (bit 16 in NBXCFG register)

must never be activated.

This signal has an internal pull-down resistor.

MAB[8:6]

--

Reserved.

A[7]#

none

In-order Queue Depth Status: The value on A[7]# sampled at the rising edge of

CPURST# reflects if the IOQD is set to 1 or maximum allowable by the CPU bus.

82443GX Host Bridge Datasheet

3-1

Register Description

R e g i s t e r D e s c r i p t i o n

3

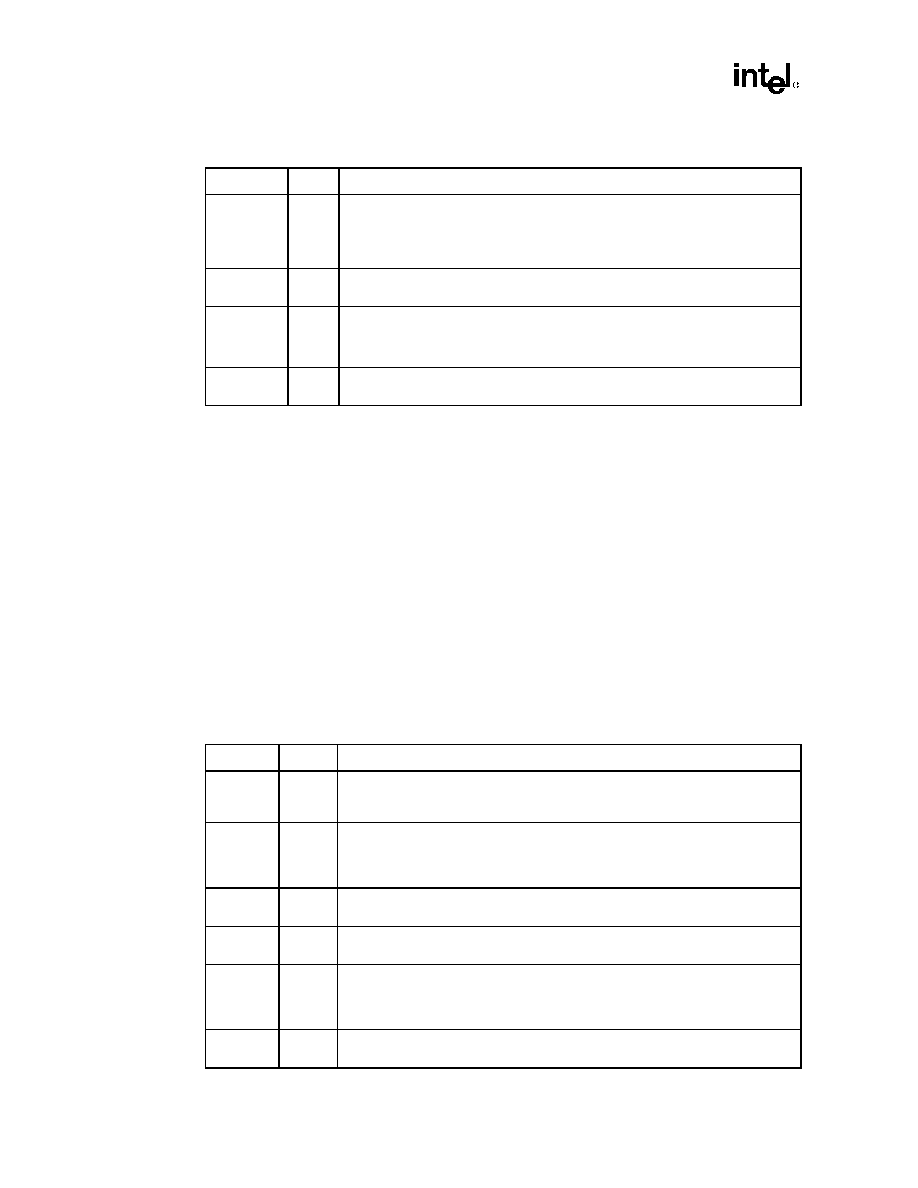

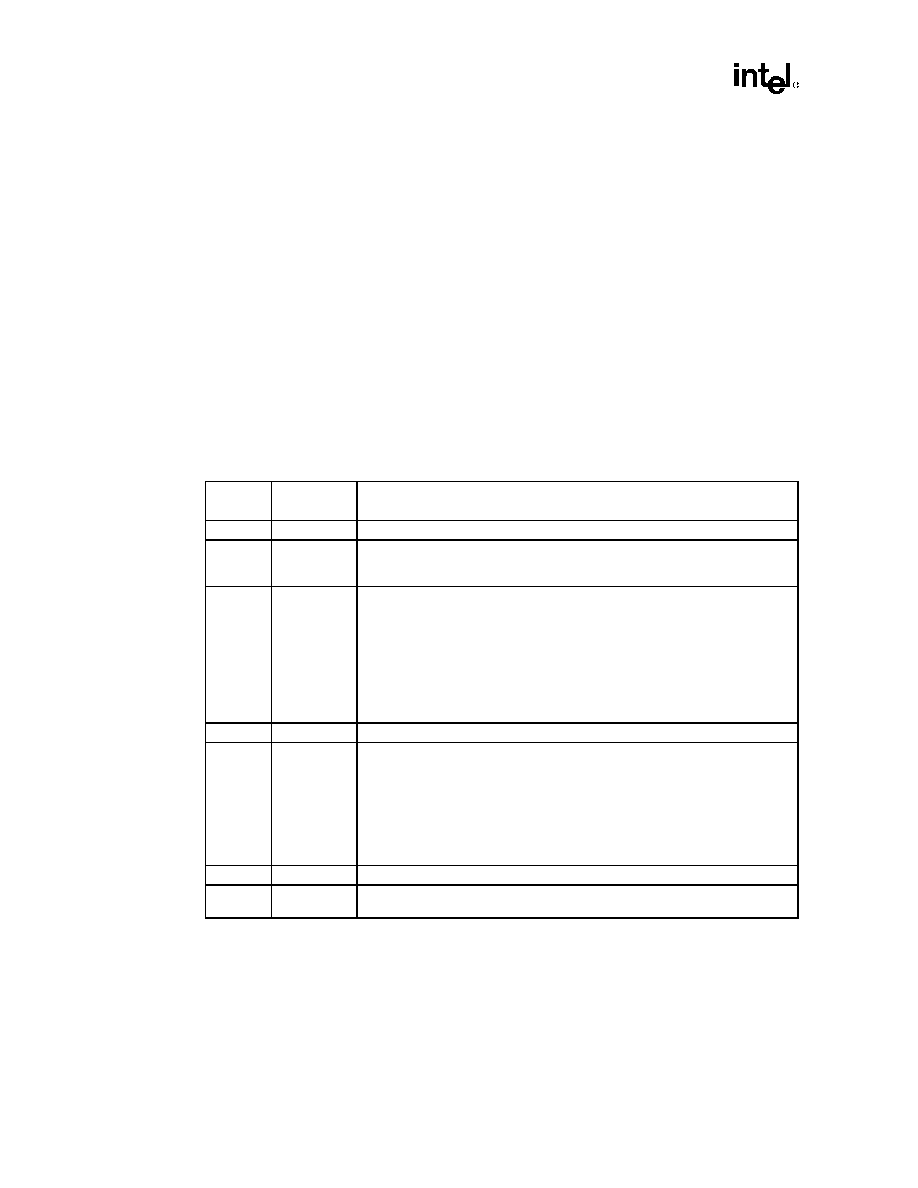

The 82443GX contains two sets of software accessible registers, accessed via the Host CPU I/O

address space:

1. Control registers that are I/O mapped into the CPU I/O space. These registers control access to

PCI and AGP configuration space.

2. Internal configuration registers residing within the 82443GX, partitioned into two logical

device register sets ("logical" since they reside within a single physical device). The first

register set is dedicated to Host-to-PCI Bridge functionality. This set (device 0) controls PCI

interface operations, DRAM configuration, and other chip-set operating parameters and

optional features. The second register set (device 1) is dedicated to Host-to-AGP Bridge

functions (controls AGP interface configurations and operating parameters).

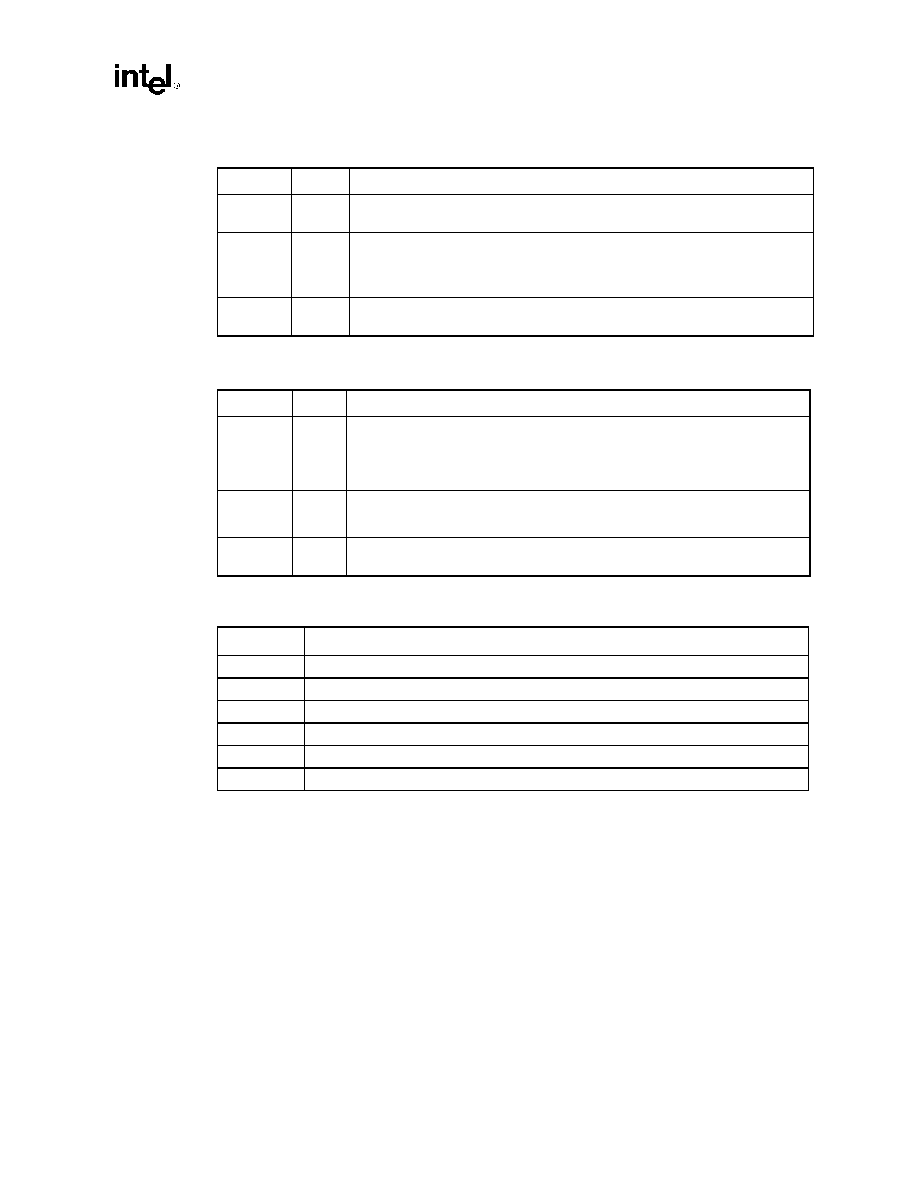

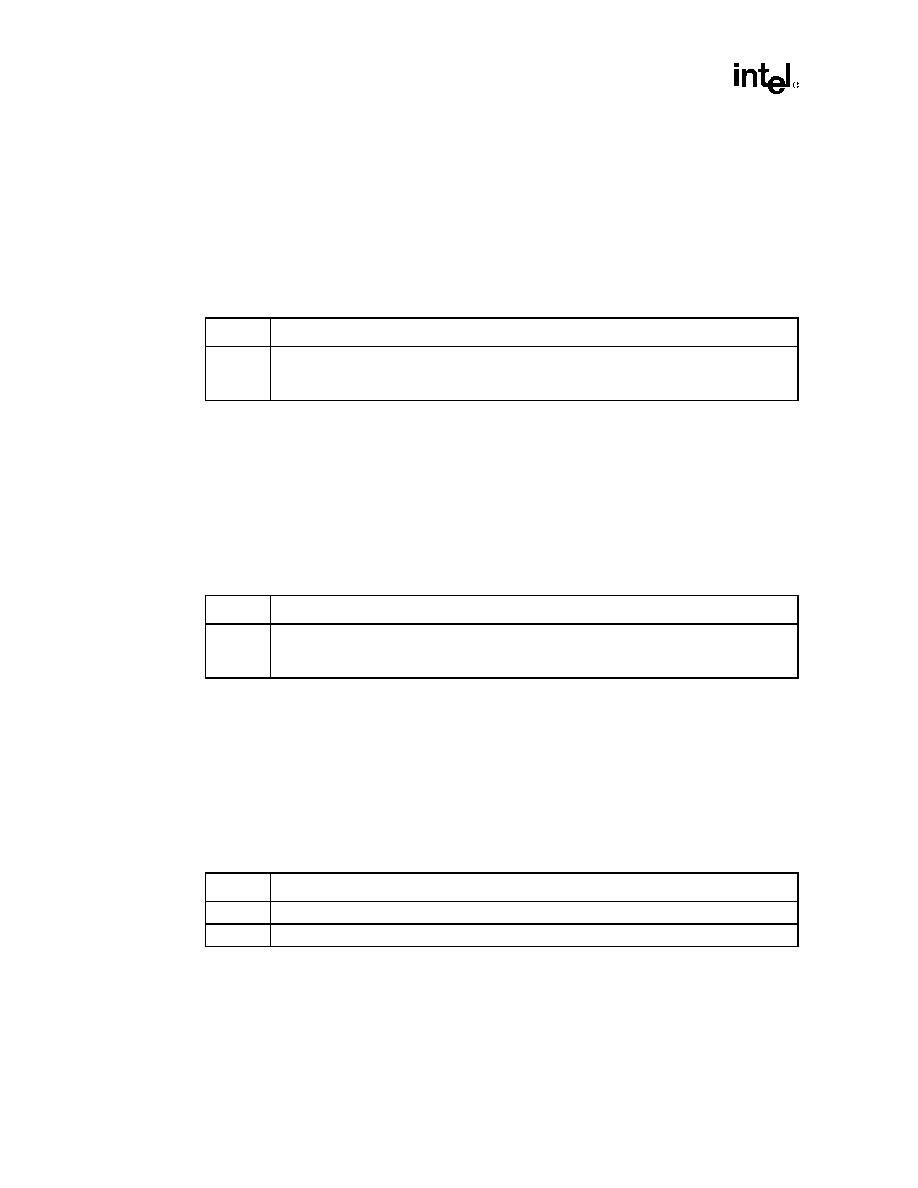

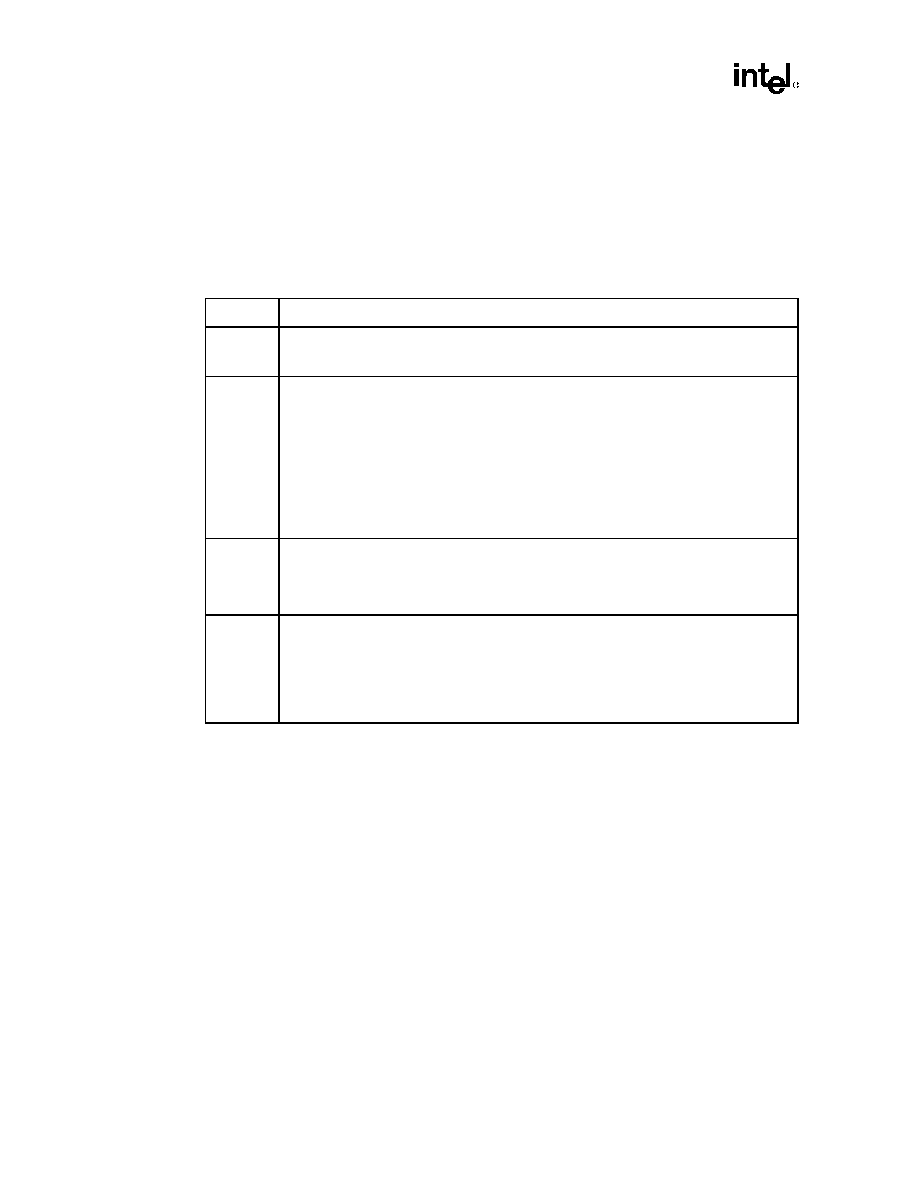

The following nomenclature is used for register access attributes.

The 82443GX supports PCI configuration space access using the mechanism denoted as

Configuration Mechanism #1 in the PCI specification.

The 82443GX internal registers (both I/O Mapped and Configuration registers) are accessible by

the Host CPU. The registers can be accessed as Byte, Word (16-bit), or DWord (32-bit) quantities,

with the exception of CONFADD which can only be accessed as a Dword. All multi-byte numeric

fields use "little-endian" ordering (i.e., lower addresses contain the least significant parts of the

field).

Some of the 82443GX registers described in this section contain reserved bits. These bits are

labeled "Reserved". Software must deal correctly with fields that are reserved. On reads, software

must use appropriate masks to extract the defined bits and not rely on reserved bits being any

particular value. On writes, software must ensure that the values of reserved bit positions are

preserved. That is, the values of reserved bit positions must first be read, merged with the new

values for other bit positions and then written back.

Note:

Software does not need to perform read, merge, write operation for the configuration address

register.

In addition to reserved bits within a register, the 82443GX contains address locations in the

configuration space of the Host-to-PCI Bridge entity that are marked either "Reserved" or "Intel

Reserved". The 82443GX responds to accesses to "Reserved" address locations by completing the

host cycle. When a "Reserved" register location is read, a zero value is returned. ("Reserved"

registers can be 8-, 16-, or 32-bit in size). Writes to "Reserved" registers have no effect on the

RO

Read Only. If a register is read only, writes to this register have no effect.

R/W

Read/Write. A register with this attribute can be read and written

R/WC

Read/Write Clear. A register bit with this attribute can be read and written.

However, a write of a 1 clears (sets to 0) the corresponding bit and a write of a 0 has

no effect.

R/WO

Read/Write Once. A register bit with this attribute can be written to only once after

power up. After the first write, the bit becomes read only.

R/WL

Read/Write/Lock. This register includes a lock bit. Once the lock bit has been set to

1, the register becomes read only.

Register Description

3-2

82443GX Host Bridge Datasheet

82443GX. Registers that are marked as "Intel Reserved" must not be modified by system software.

Writes to "Intel Reserved" registers may cause system failure. Reads to "Intel Reserved" registers

may return a non-zero value. Software should not write to reserved configuration locations in the

device-specific region (above address offset 3Fh)

Upon reset, the 82443GX sets its internal configuration registers to predetermined default states.

However, there are a few exceptions to this rule.

1. When a reset occurs during the POS/STR state, several configuration bits are not reset to their

default state. These bits are noted in the following register description.

2. Some register values at reset are determined by external strapping options.

The default state represents the minimum functionality feature set required to successfully bring up

the system. Hence, it does not represent the optimal system configuration. It is the responsibility of

the system initialization software (usually BIOS) to properly determine the DRAM configurations,

operating parameters and optional system features that are applicable, and to program the

82443GX registers accordingly.

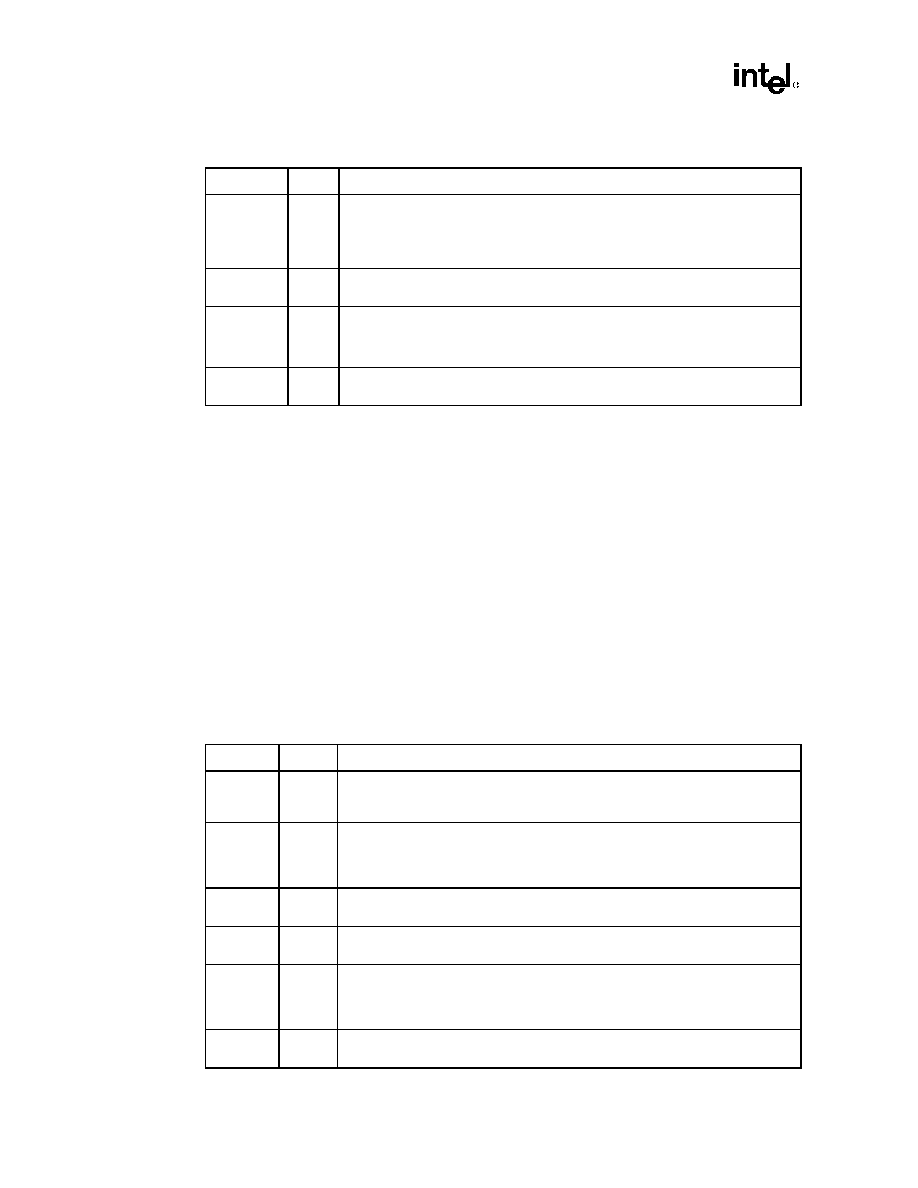

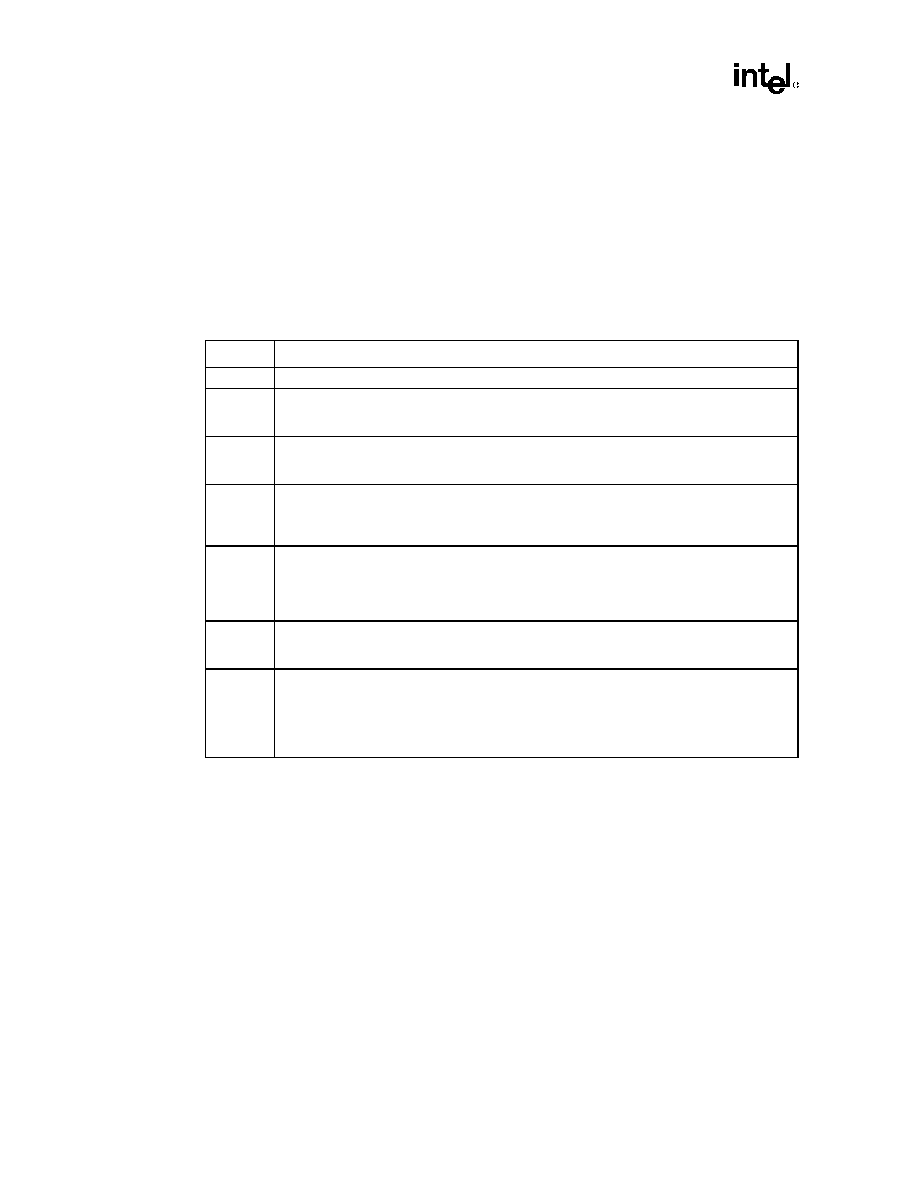

3.1

I/O Mapped Registers

The 82443GX contains three registers that reside in the CPU I/O address space - the Configuration

Address (CONFADD) Register, the Configuration Data (CONFDATA) Register, and the Power

Management Control Register. The Configuration Address Register enables/disables the

configuration space and determines what portion of configuration space is visible through the

Configuration Data window.

3.1.1

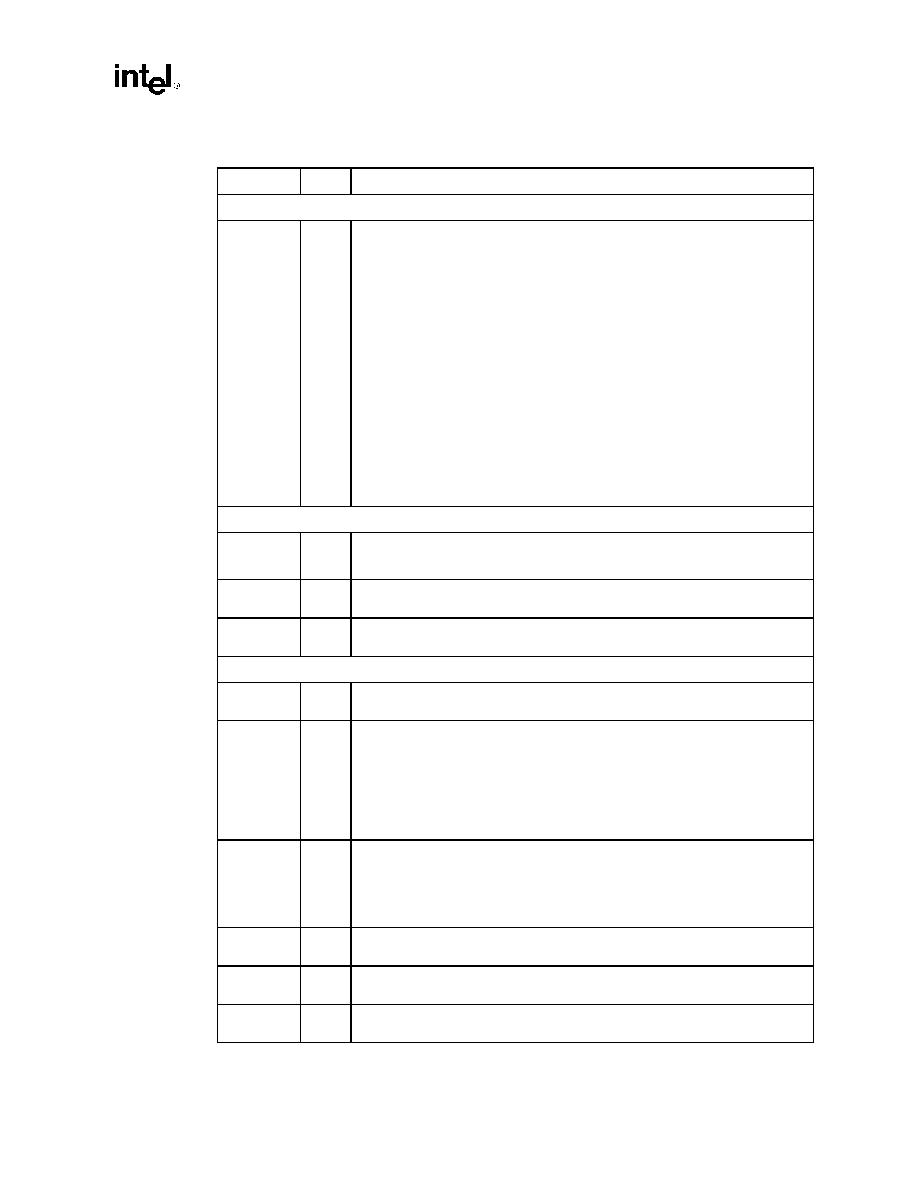

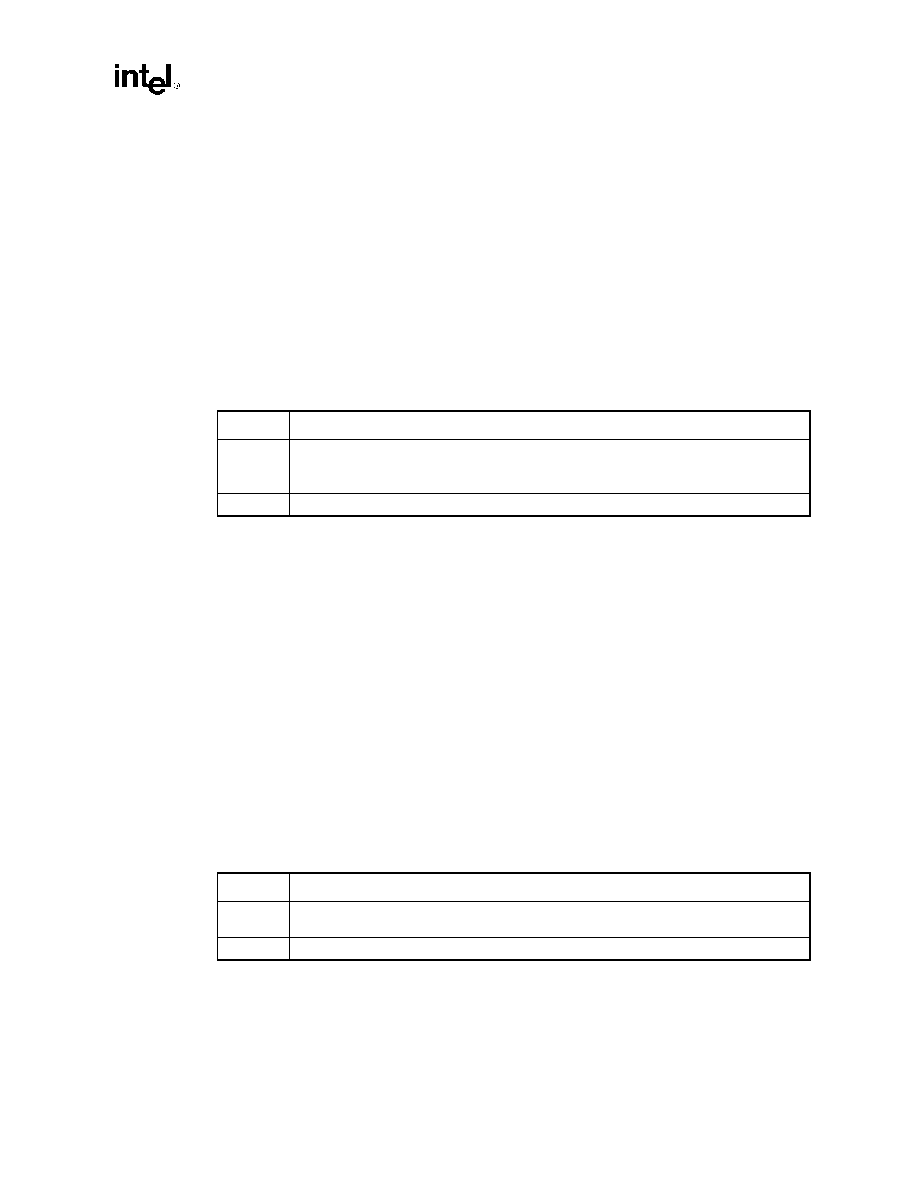

CONFADD--Configuration Address Register

I/O Address:

0CF8h Accessed as a Dword

Default Value:

00000000h

Access:

Read/Write

Size:

32 bits

CONFADD is a 32 bit register accessed only when referenced as a Dword. A Byte or Word

reference will "pass through" the Configuration Address Register onto the PCI bus as an I/O cycle.

The CONFADD register contains the Bus Number, Device Number, Function Number, and

Register Number for which a subsequent configuration access is intended.

82443GX Host Bridge Datasheet

3-3

Register Description

3.1.2

CONFDATA--Configuration Data Register

I/O Address:

0CFCh

Default Value:

00000000h

Access:

Read/Write

Size:

32 bits

CONFDATA is a 32 bit read/write window into configuration space. The portion of configuration

space that is referenced by CONFDATA is determined by the contents of CONFADD.

Bit

Descriptions

31

Configuration Enable (CFGE). When this bit is set to 1 accesses to PCI configuration space are

enabled. If this bit is reset to 0 accesses to PCI configuration space are disabled.

30:24

Reserved.

23:16

Bus Number. When the Bus Number is programmed to 00h the target of the Configuration Cycle

is either the 82443GX or the PCI Bus that is directly connected to the 82443GX, depending on the

Device Number field. A type 0 Configuration Cycle is generated on PCI if the Bus Number is

programmed to 00h and the 82443GX is not the target. If the Bus Number is non-zero a type 1

configuration cycle is generated on PCI or AGP with the Bus Number mapped to AD[23:16] during

the address phase.

15:11

Device Number. This field selects one agent on the PCI bus selected by the Bus Number. During

a Type 1 Configuration cycle this field is mapped to AD[15:11]. During a Type 0 Configuration

Cycle this field is decoded and one bit among AD[31:11] is driven to a 1. The 82443GX is always

Device Number 0 for the Host-to-PCI bridge entity and Device Number 1 for the Host- AGP entity.

Therefore, the 82443GX internally references the AD11 and AD12 pins as corresponding IDSELs

for the respective devices during PCI configuration cycles. NOTE: The AD11 and AD12 must not

be connected to any other PCI bus device as IDSEL signals.

10:8

Function Number. This field is mapped to AD[10:8] during PCIx configuration cycles. This allows

the configuration registers of a particular function in a multi-function device to be accessed. The

82443GX only responds to configuration cycles with a function number of 000b; all other function

number values attempting access to the 82443GX (Device Number = 0 and 1, Bus Number = 0)

will generate a master abort.

7:2

Register Number. This field selects one register within a particular Bus, Device, and Function as

specified by the other fields in the Configuration Address Register. This field is mapped to AD[7:2]

during PCI configuration cycles.

1:0

Reserved.

Bit

Descriptions

31:0

Configuration Data Window (CDW). If bit 31 of CONFADD is 1 any I/O reference that falls in the

CONFDATA I/O space will be mapped to configuration space using the contents of CONFADD.

Register Description

3-4

82443GX Host Bridge Datasheet

3.1.3

PM2_CTL--ACPI Power Control 2 Control Register

I/O Address:

0022h

Default Value:

00h

Access:

Read/Write

Size:

8 bits

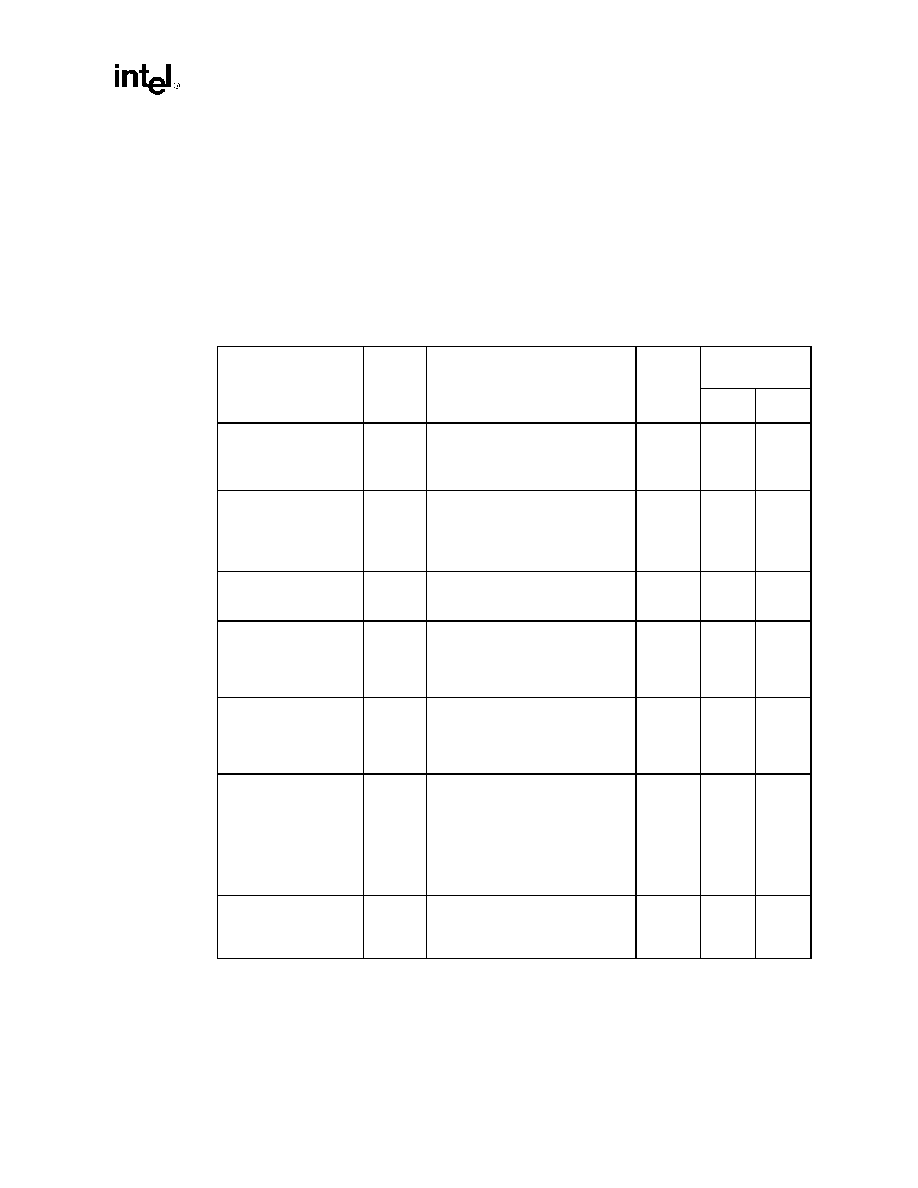

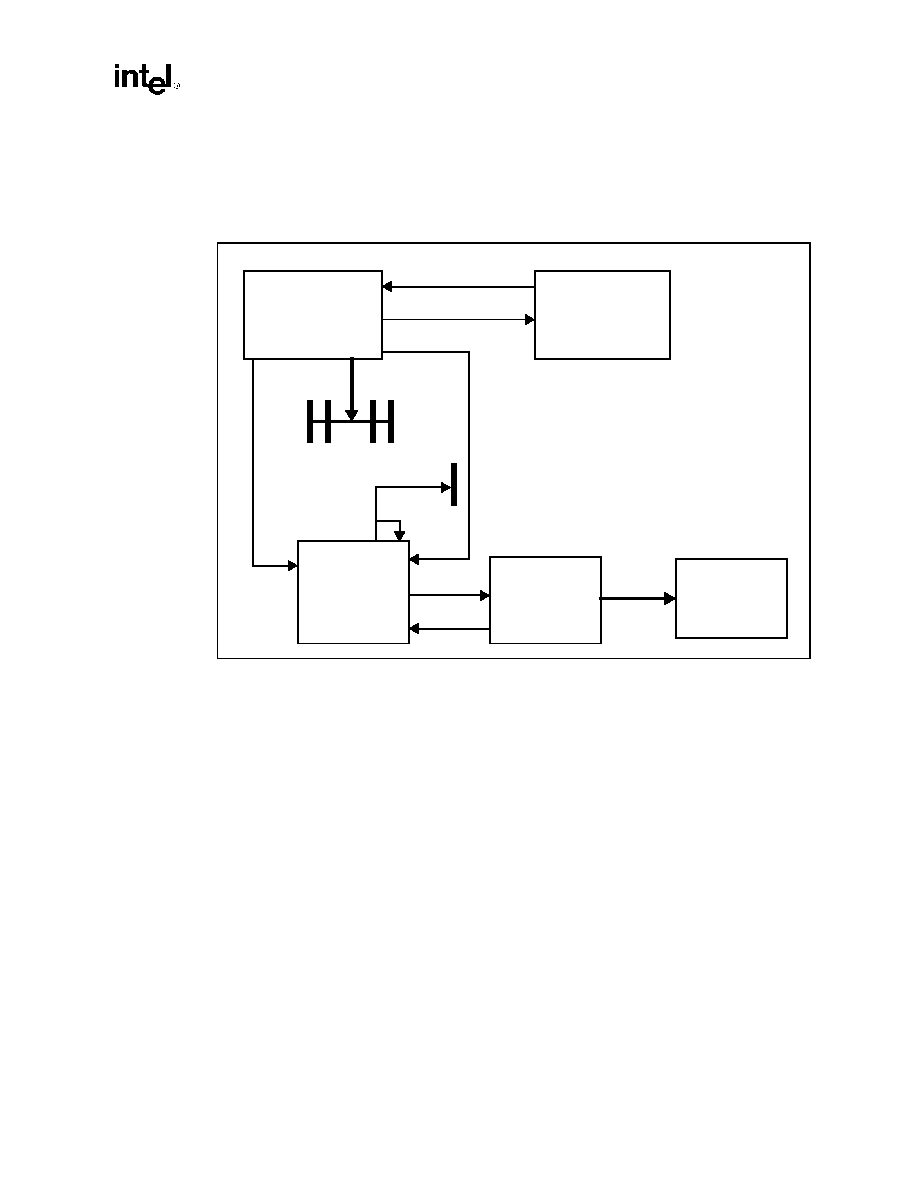

This register is used to disable both the PCI and AGP arbiters in the 82443GX to prevent any