© Intel Corporation

el

Æ

int

IntelÆ 450NX PCIset

Revision 1.3

March 1999

82454NX PCI Expander Bridge (PXB)

82453NX Data Path Multiplexor (MUX)

82452NX RAS/CAS Generator (RCG)

82451NX Memory & I/O Controller (MIOC)

1998, 1999

Information in this document is provided in connection with Intel products. No license, express or

implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except

as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatso-

ever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products

including liability or warranties relating to fitness for a particular purpose, merchantability, or infringe-

ment of any patent, copyright or other intellectual property right. Intel products are not intended for use

in medical, life saving, or life sustaining applications. Intel retains the right to make changes to specifica-

tions and product descriptions at any time, without notice.

The IntelÆ 450NX PCIset may contain design defects or errors known as errata which may cause the prod-

uct to deviate from the published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing

your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel

literature, may be obtained from:

Intel Corporation

P.O. Box 7641

Mt. Prospect IL 60056-7641

or call 1-800-879-4683

Copyright © Intel Corporation 1998, 1999

. Third-party brands and names are the property of their

respective owners.

Intel 450NX PCIset

-i-

CONTENTS

Chapter 1

Introduction ......................................................................................................................................... 1-1

1.1

Overview ..................................................................................................................................................... 1-1

1.2

IntelÆ 450NX PCIset Components .............................................................................................................. 1-2

1.3

IntelÆ 450NX PCIset Feature Summary ..................................................................................................... 1-3

1.4

Packaging & Power ..................................................................................................................................... 1-4

Chapter 2

Signal Descriptions ............................................................................................................................ 2-1

2.1

Conventions ................................................................................................................................................ 2-1

2.2

Summary ..................................................................................................................................................... 2-2

2.2.1

Signal Summary, By Component .................................................................................................. 2-2

2.2.1.1

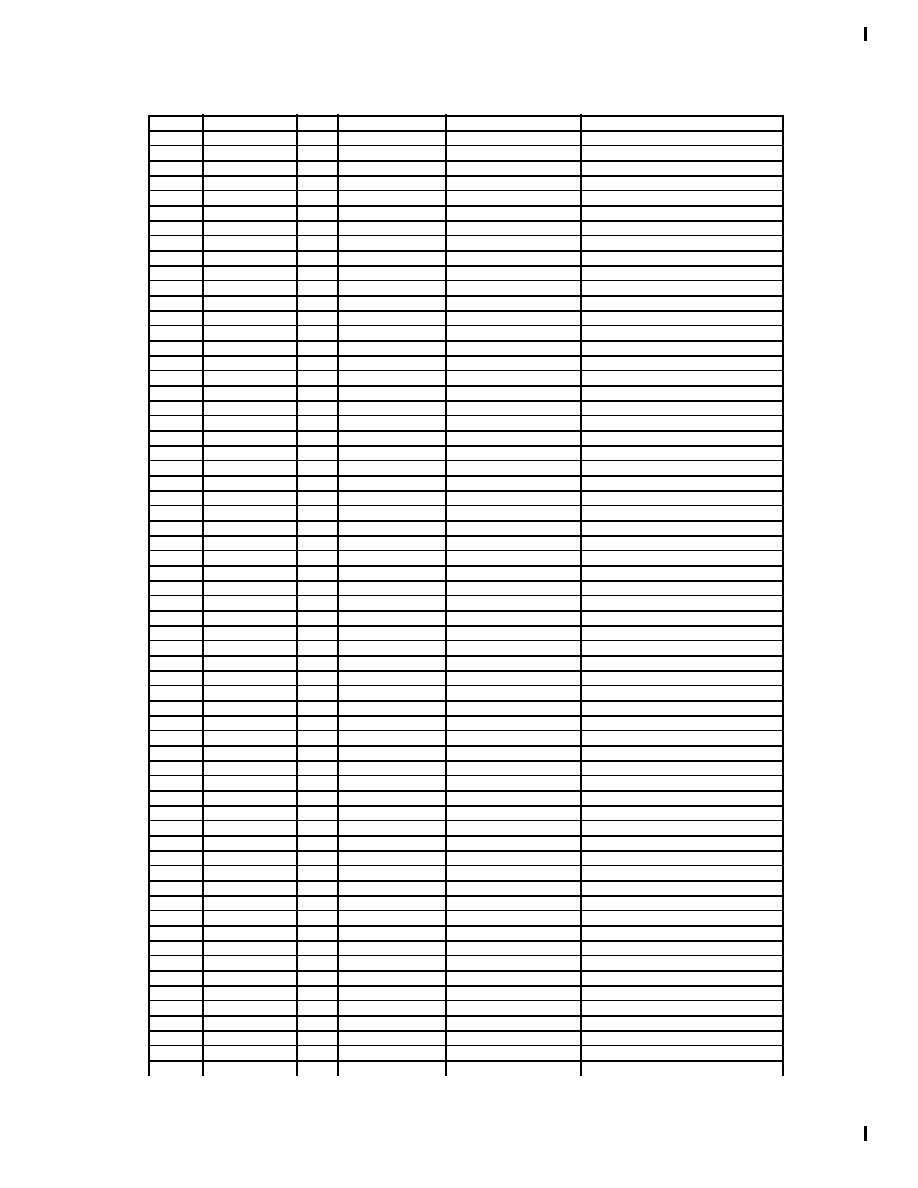

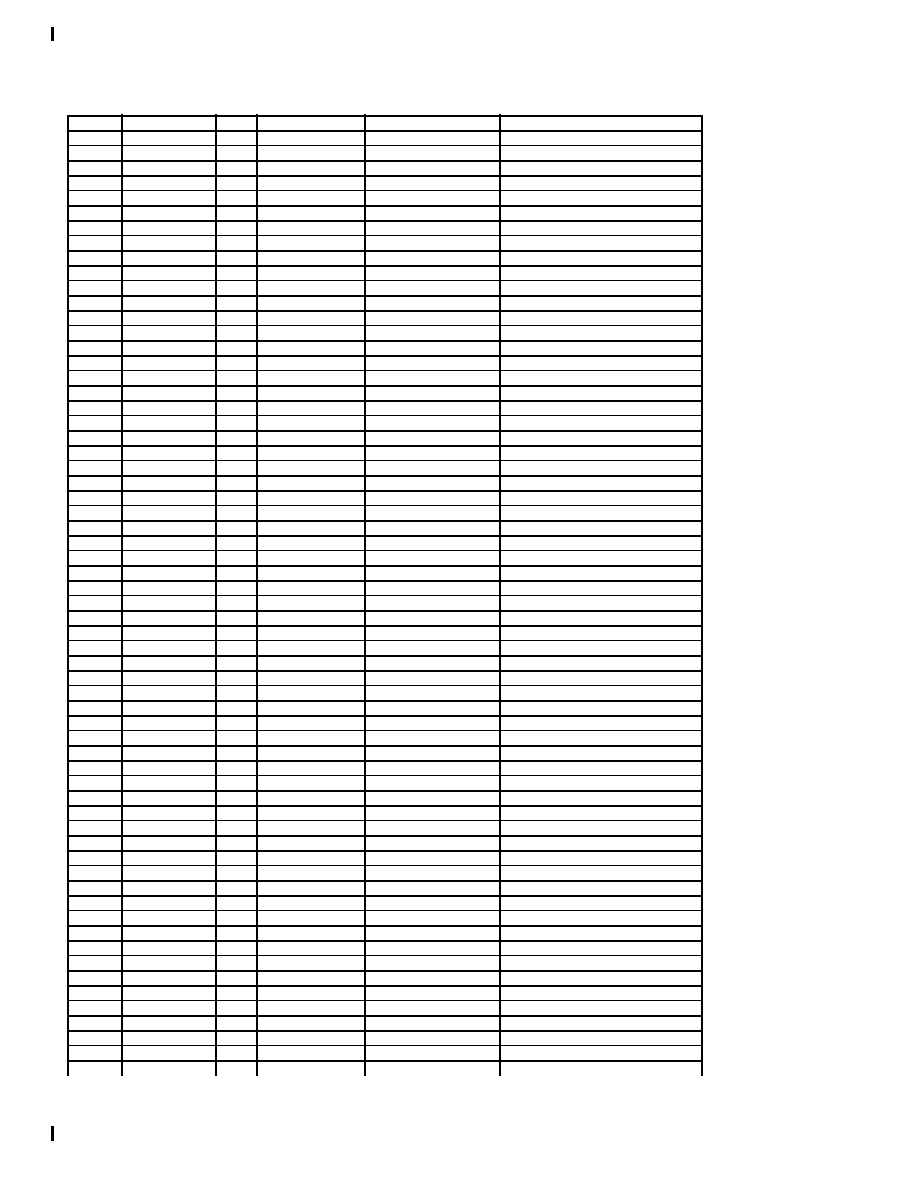

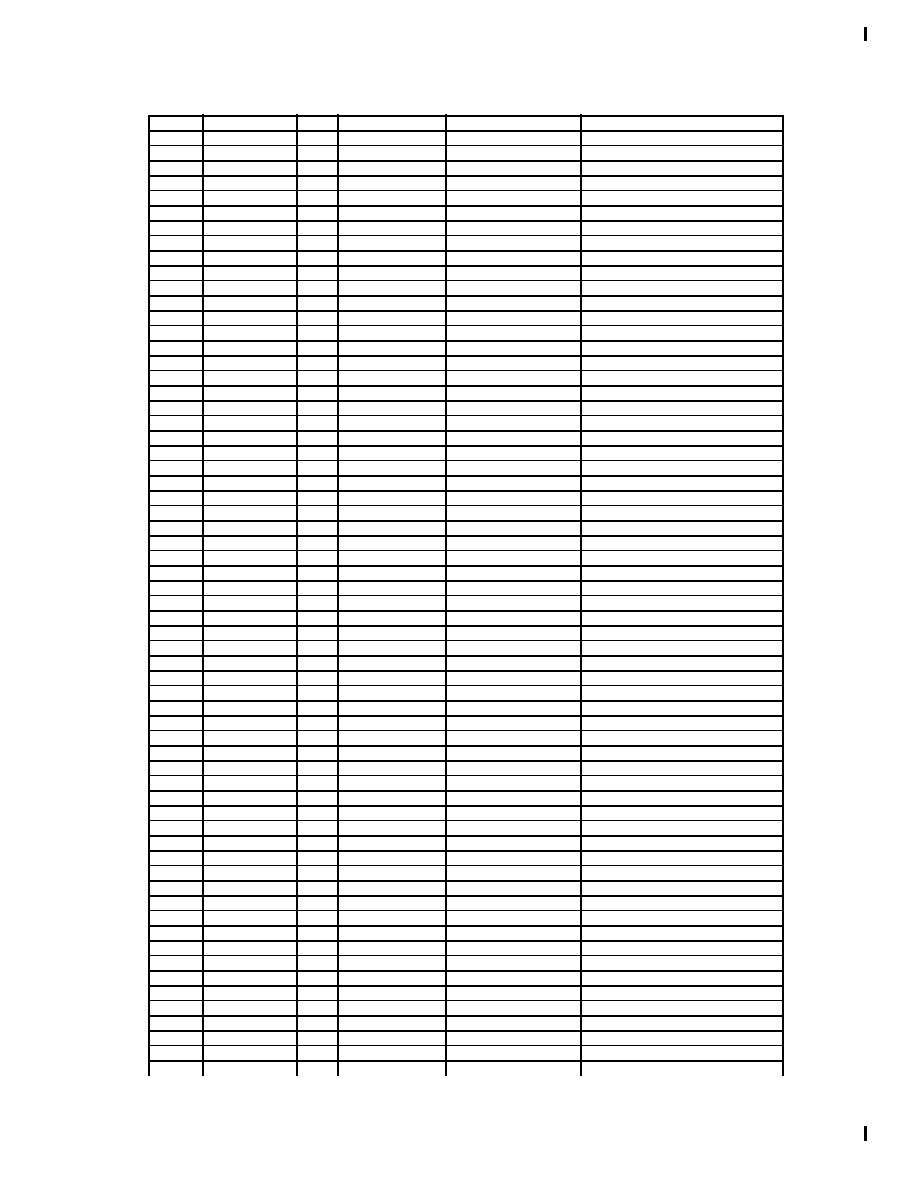

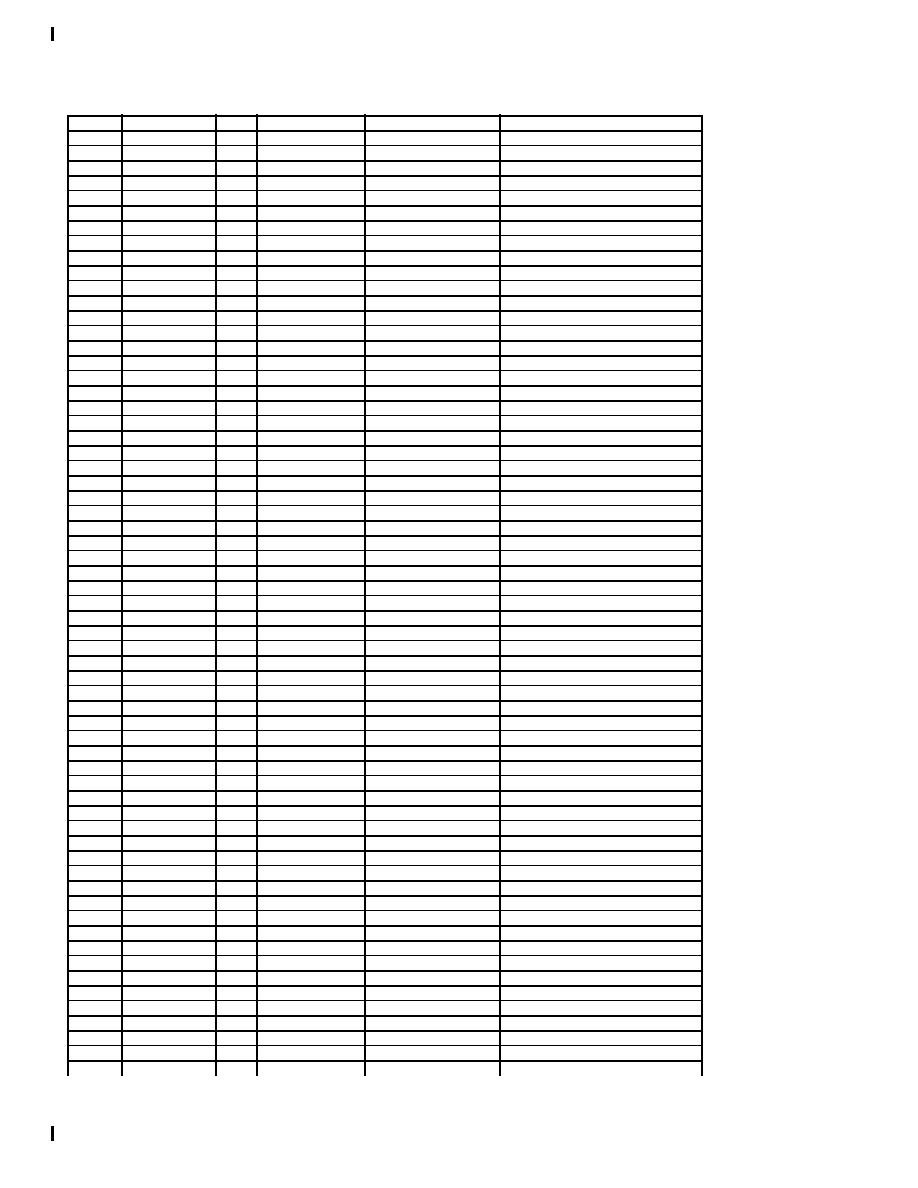

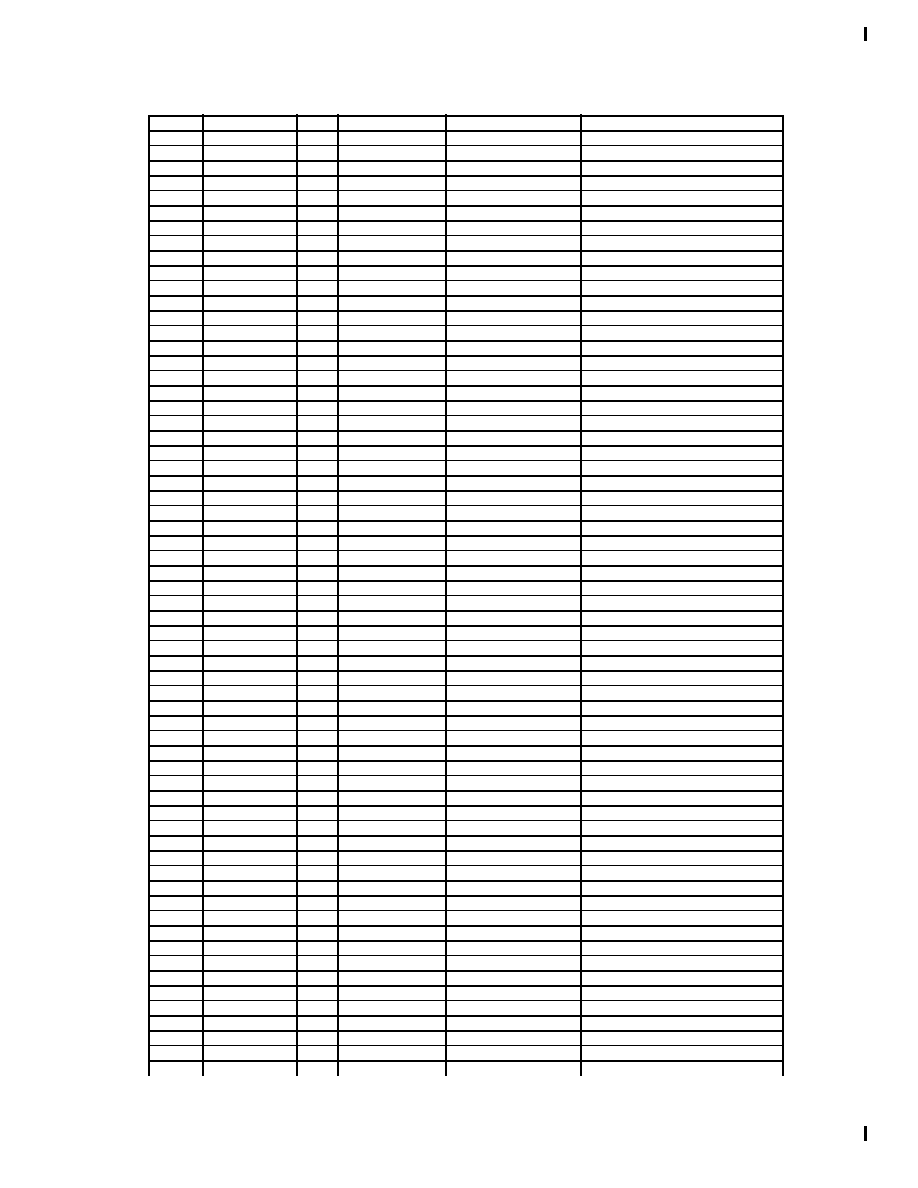

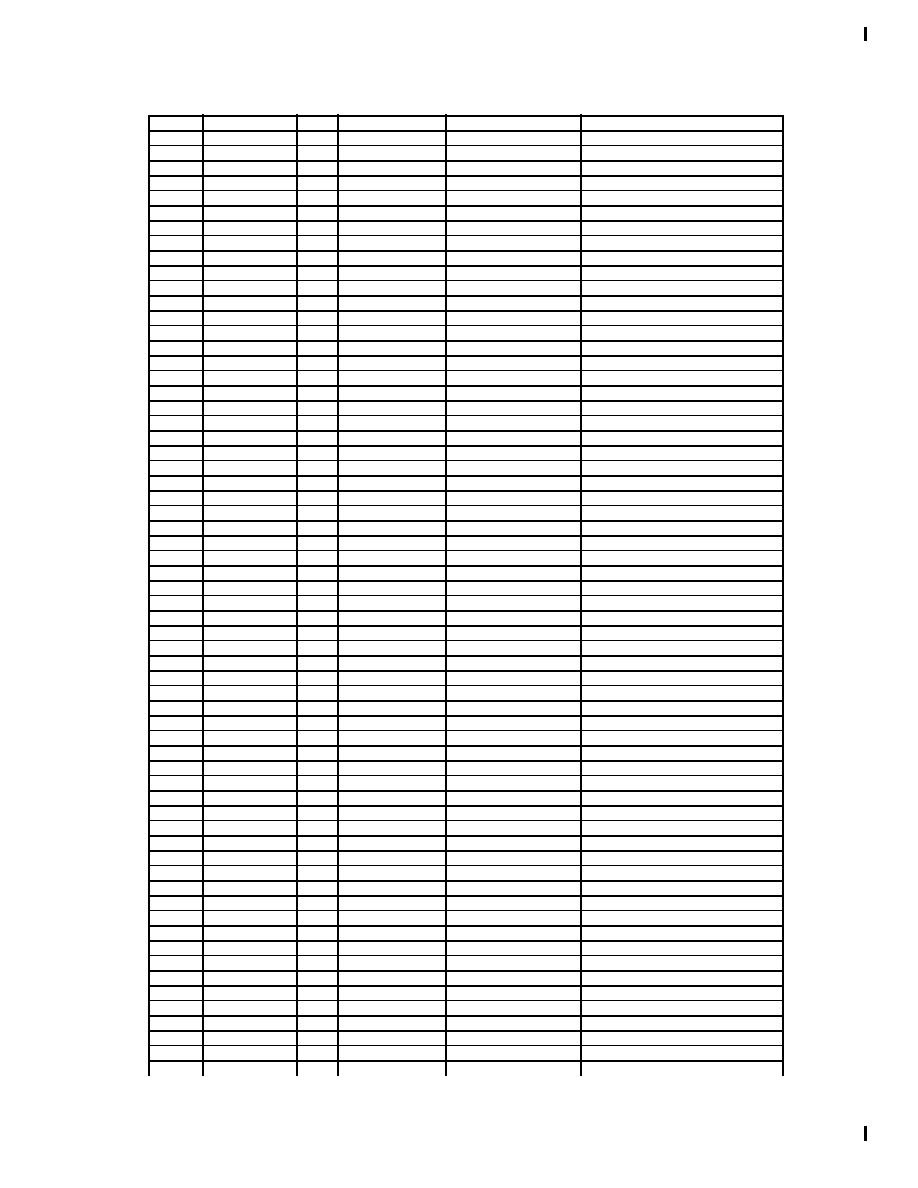

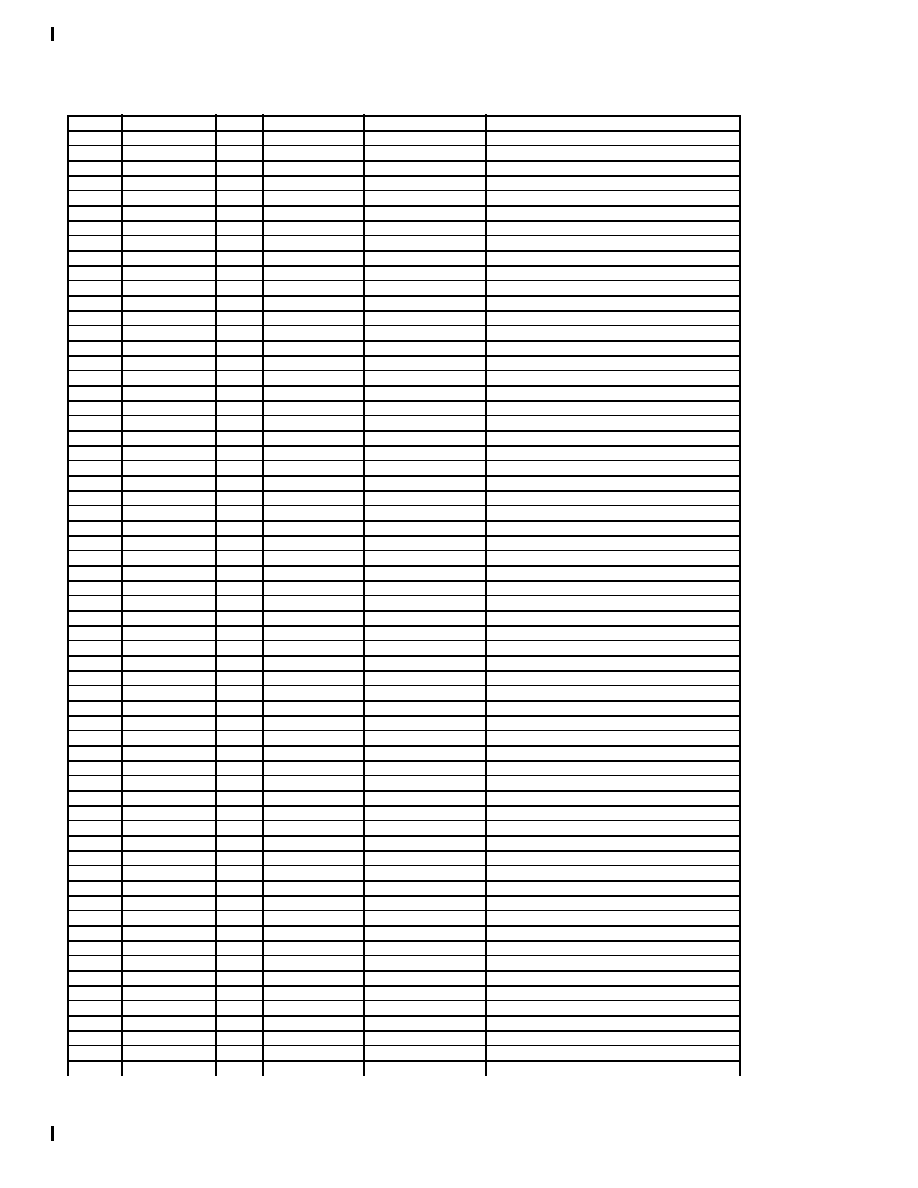

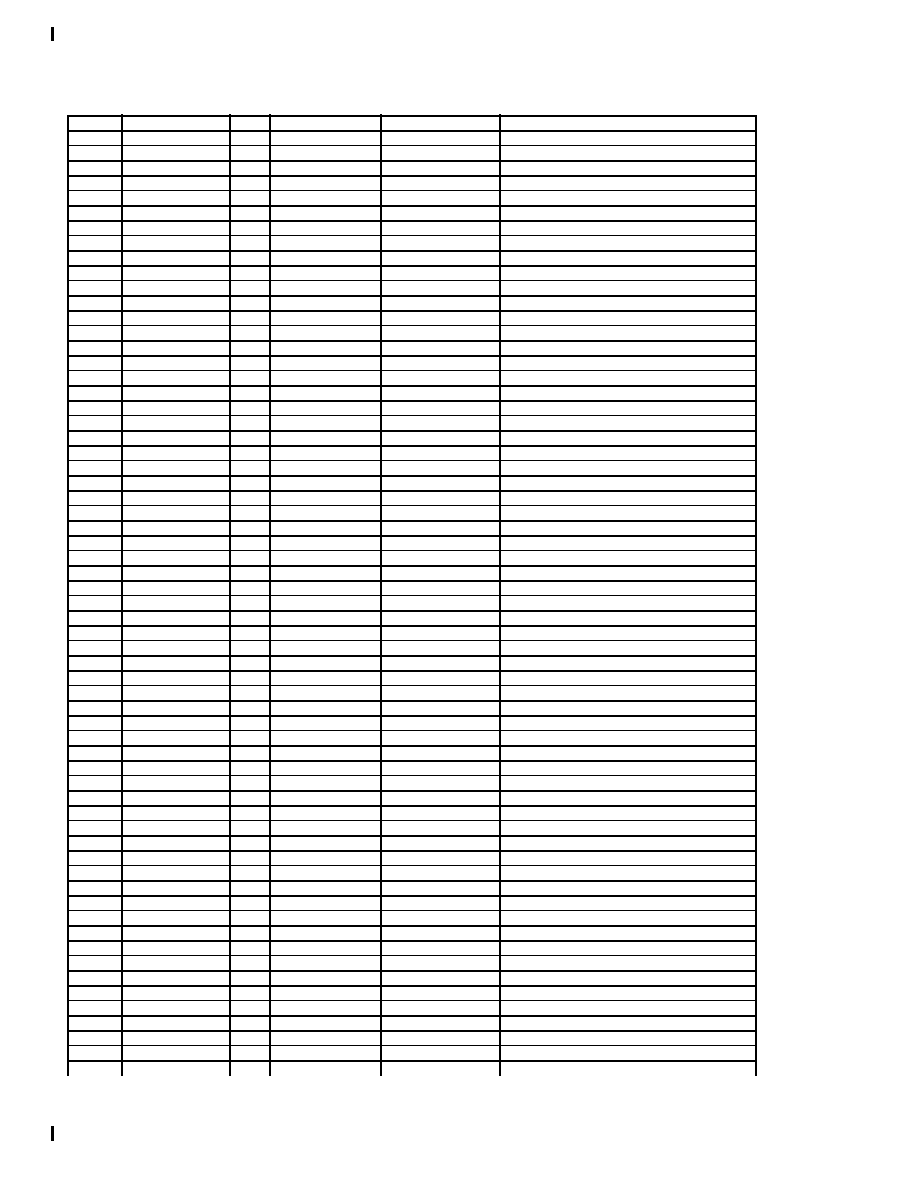

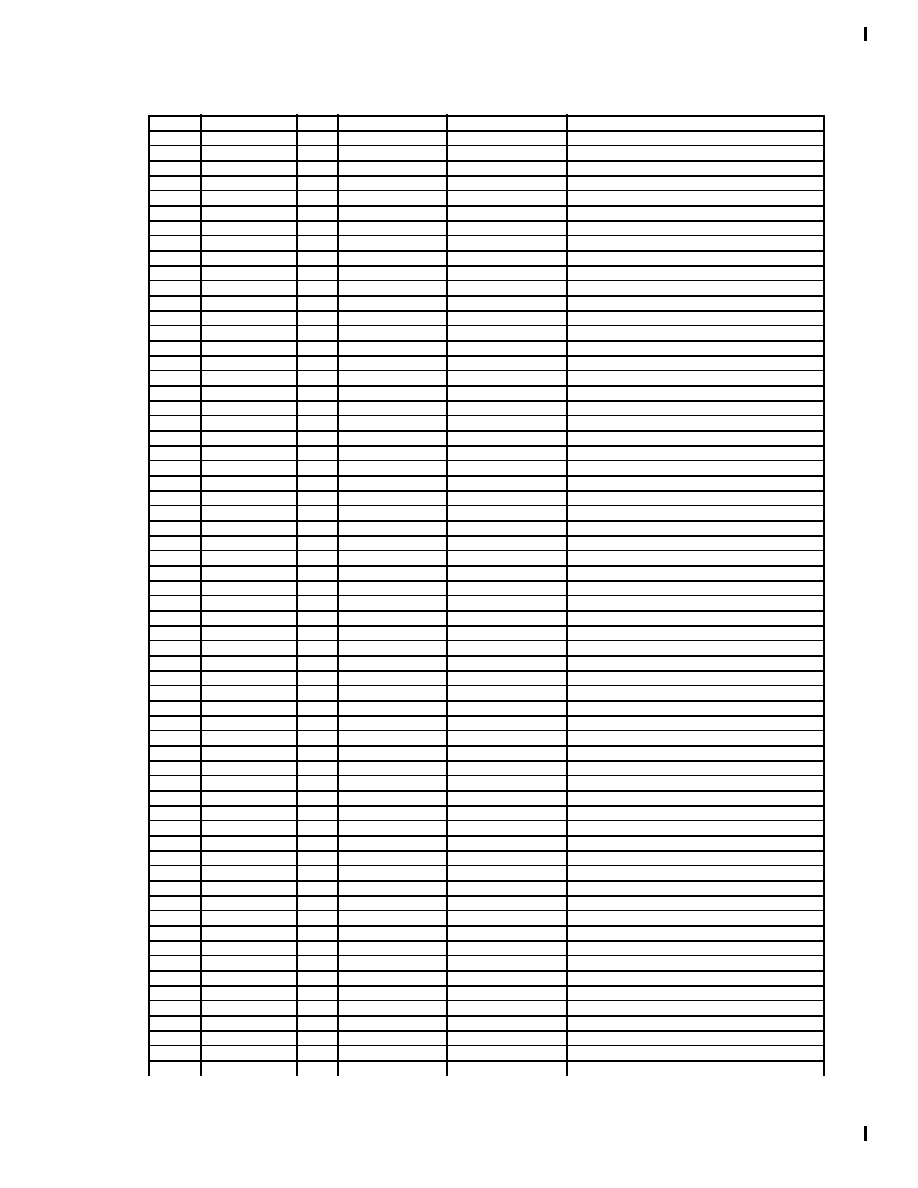

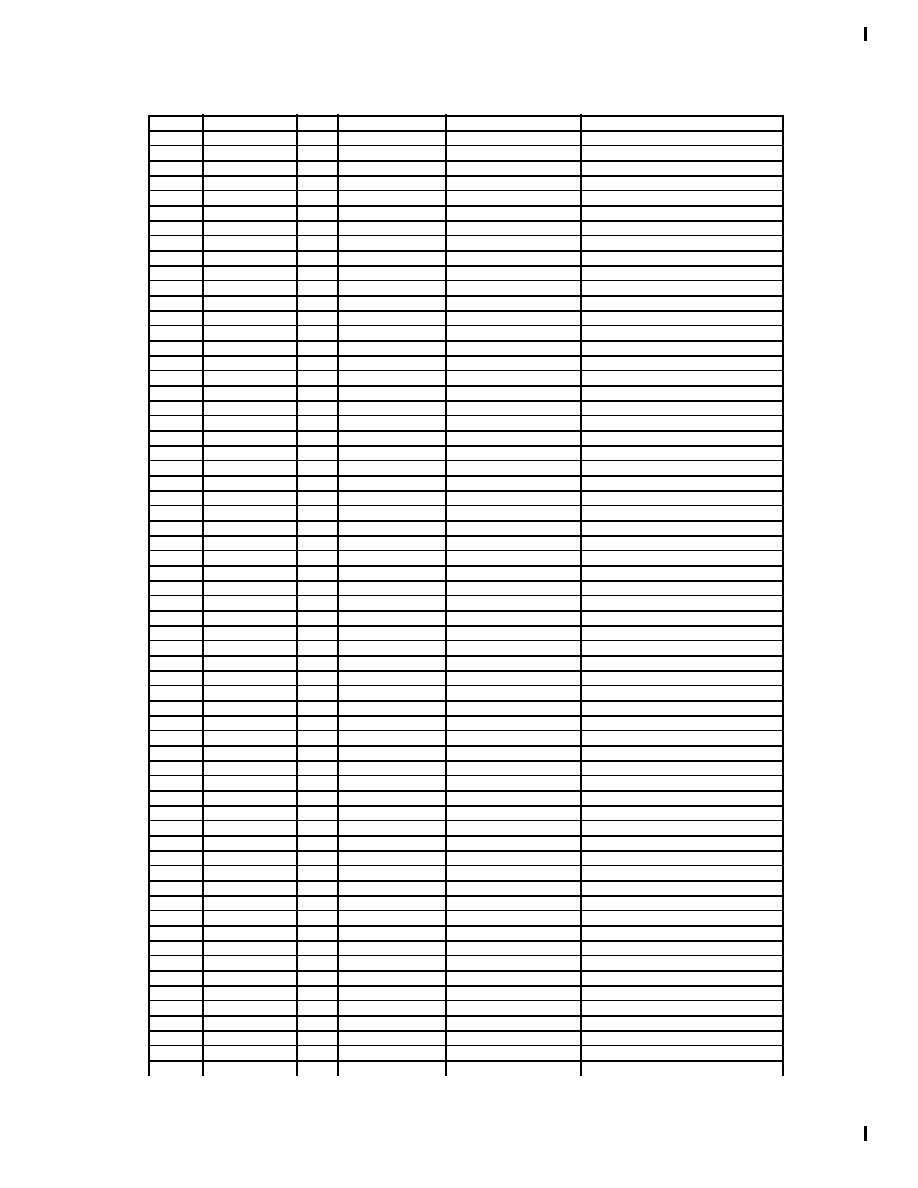

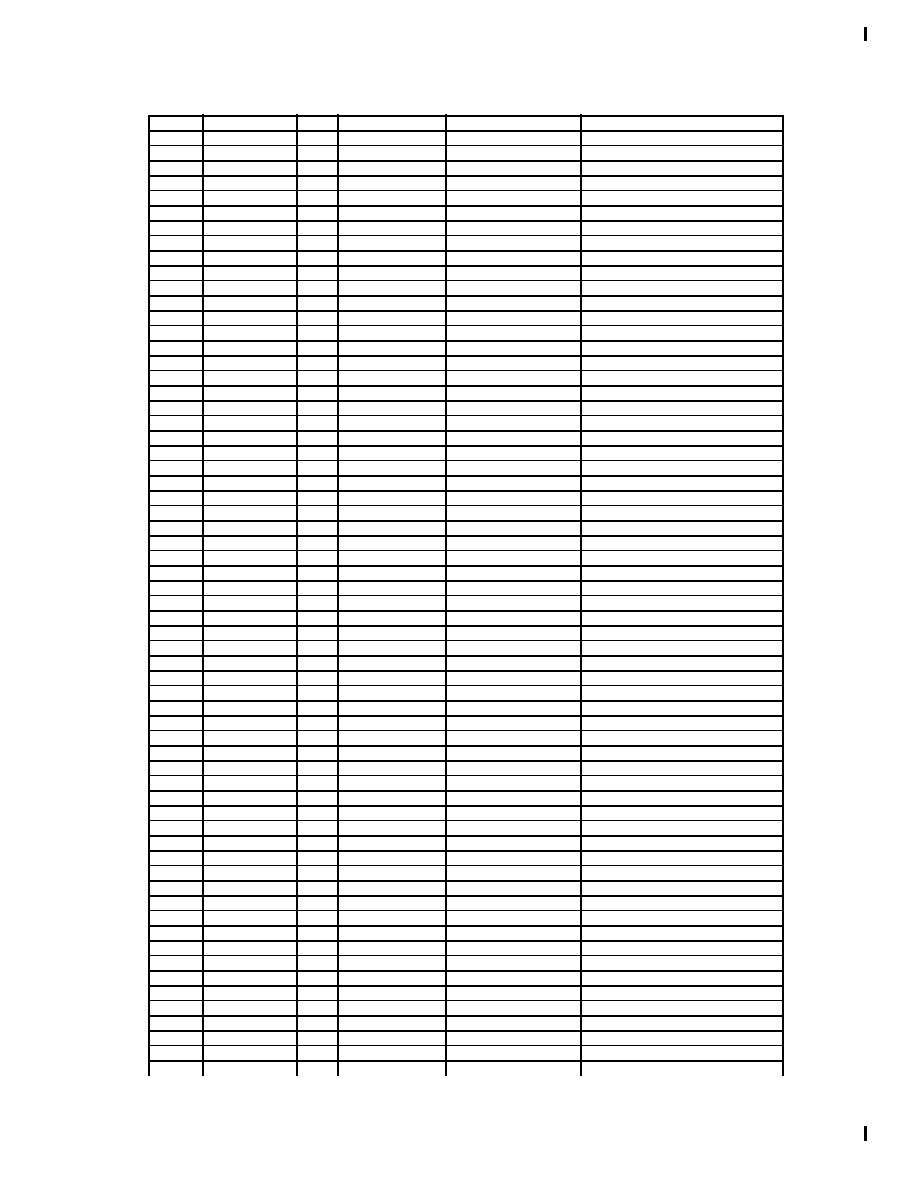

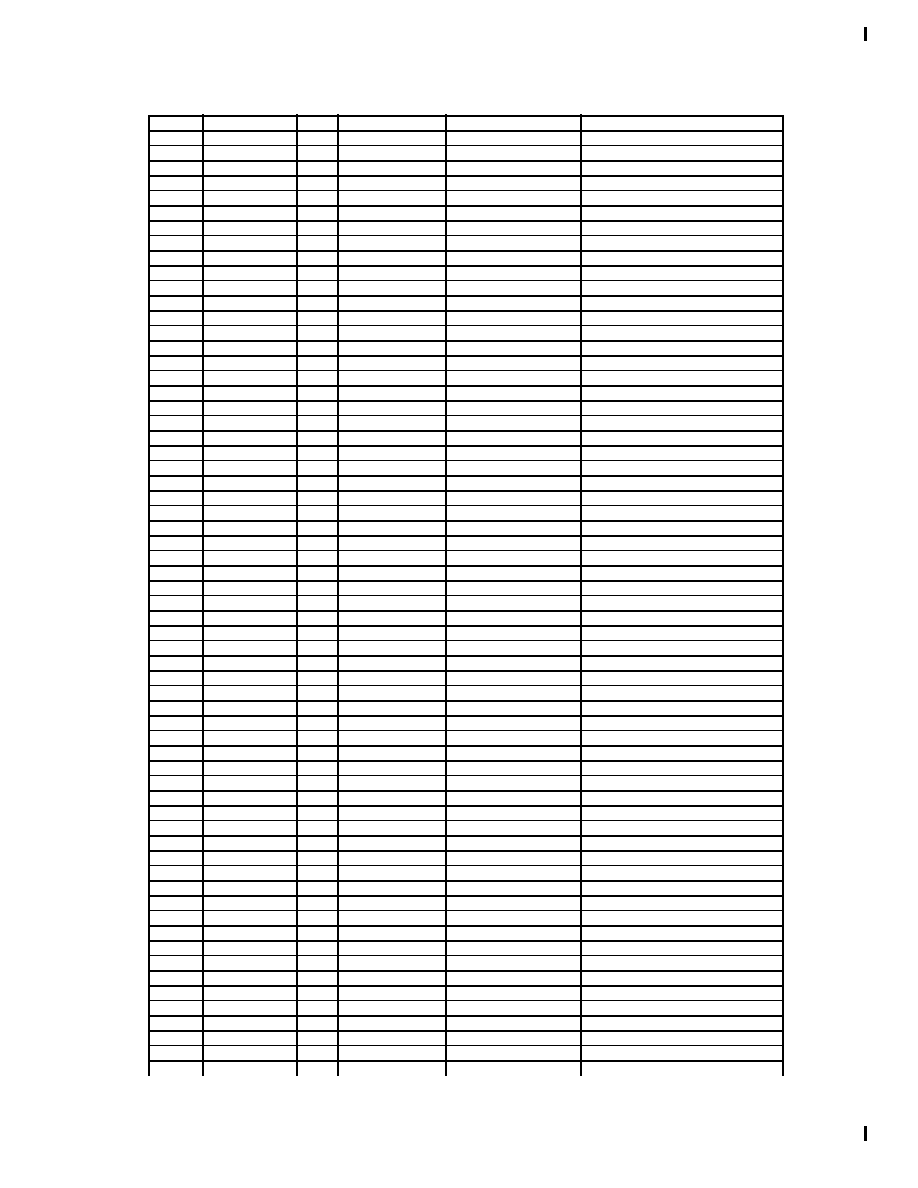

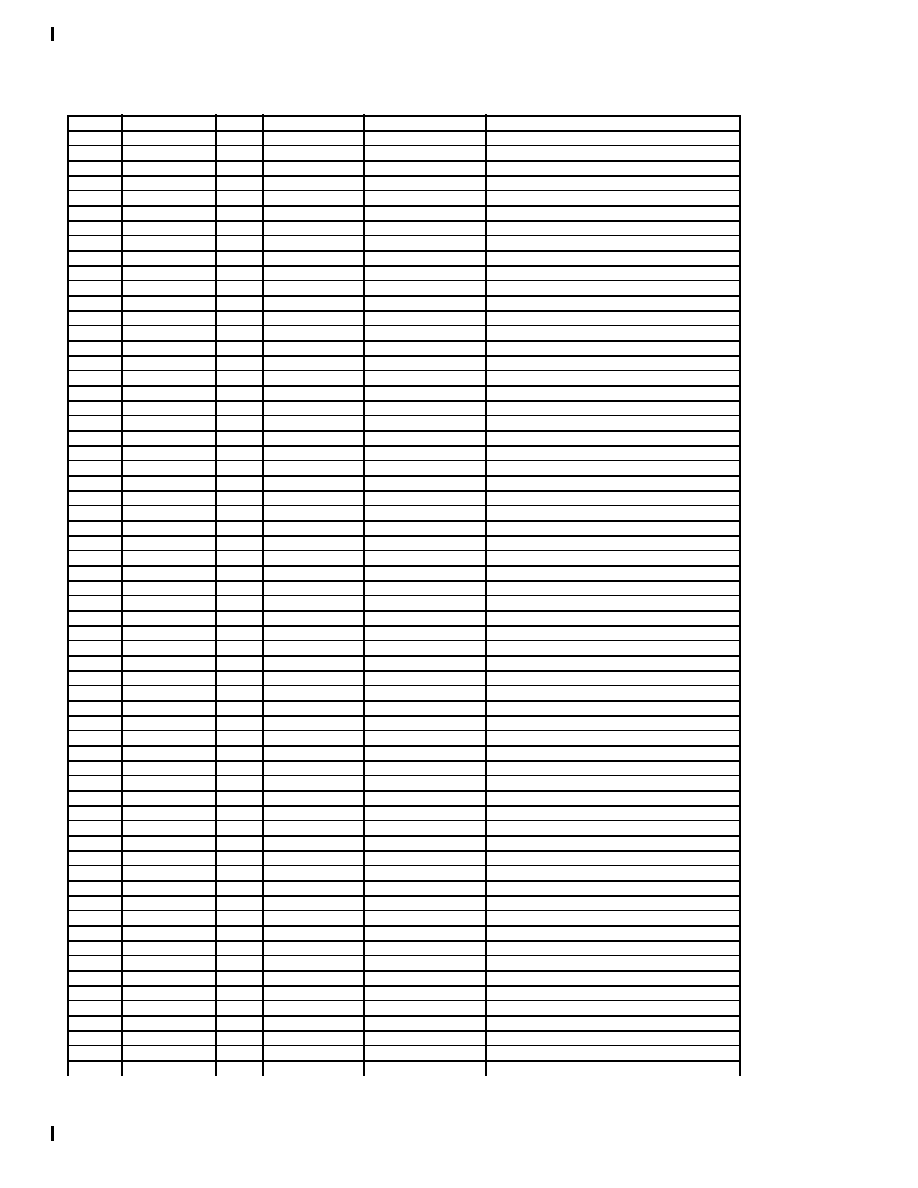

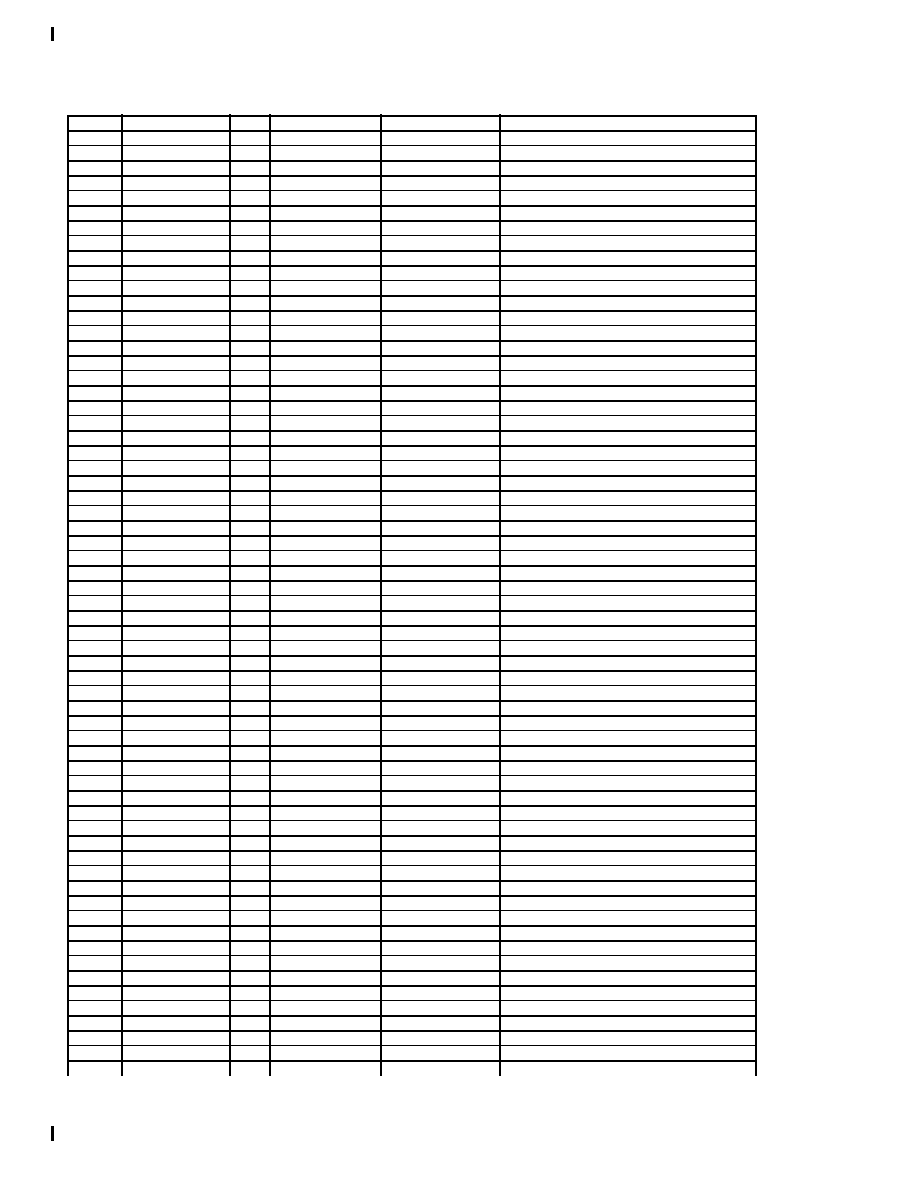

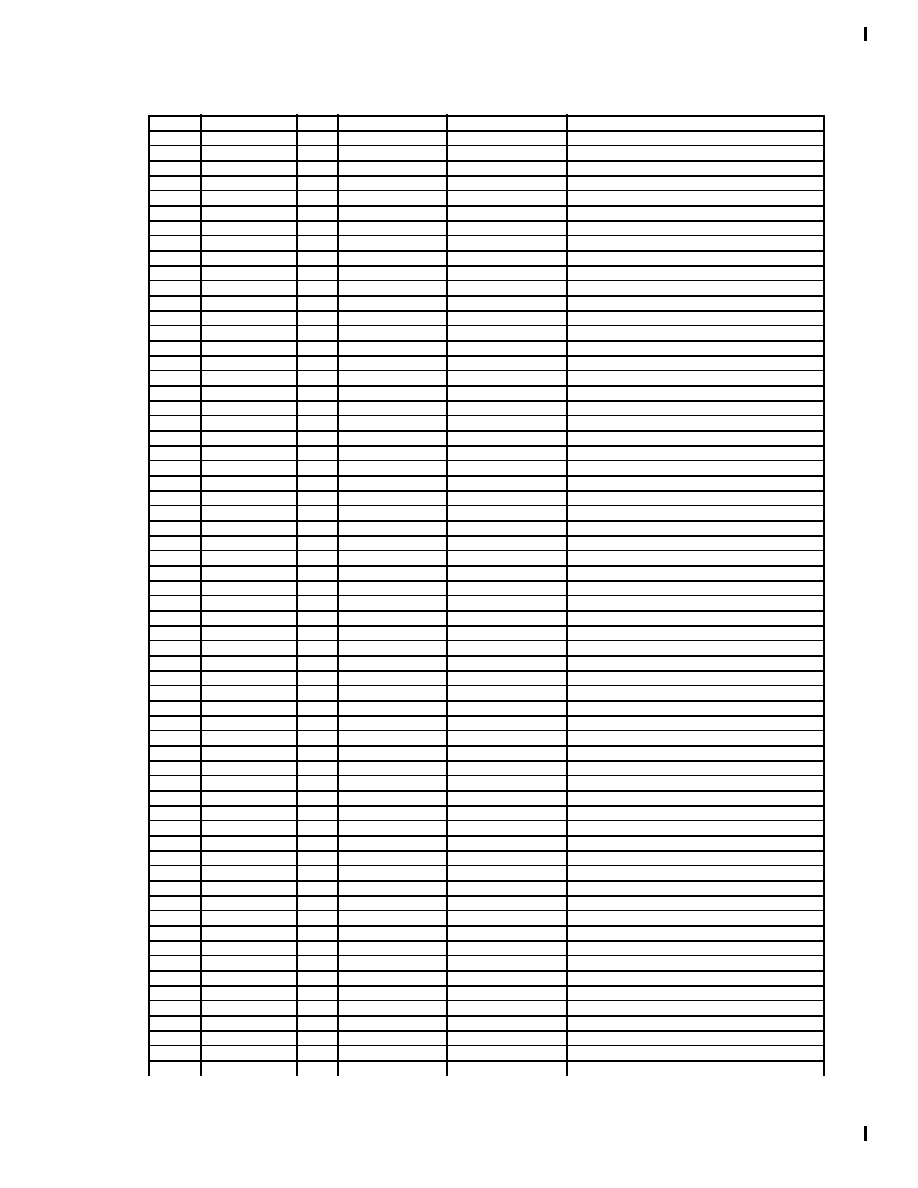

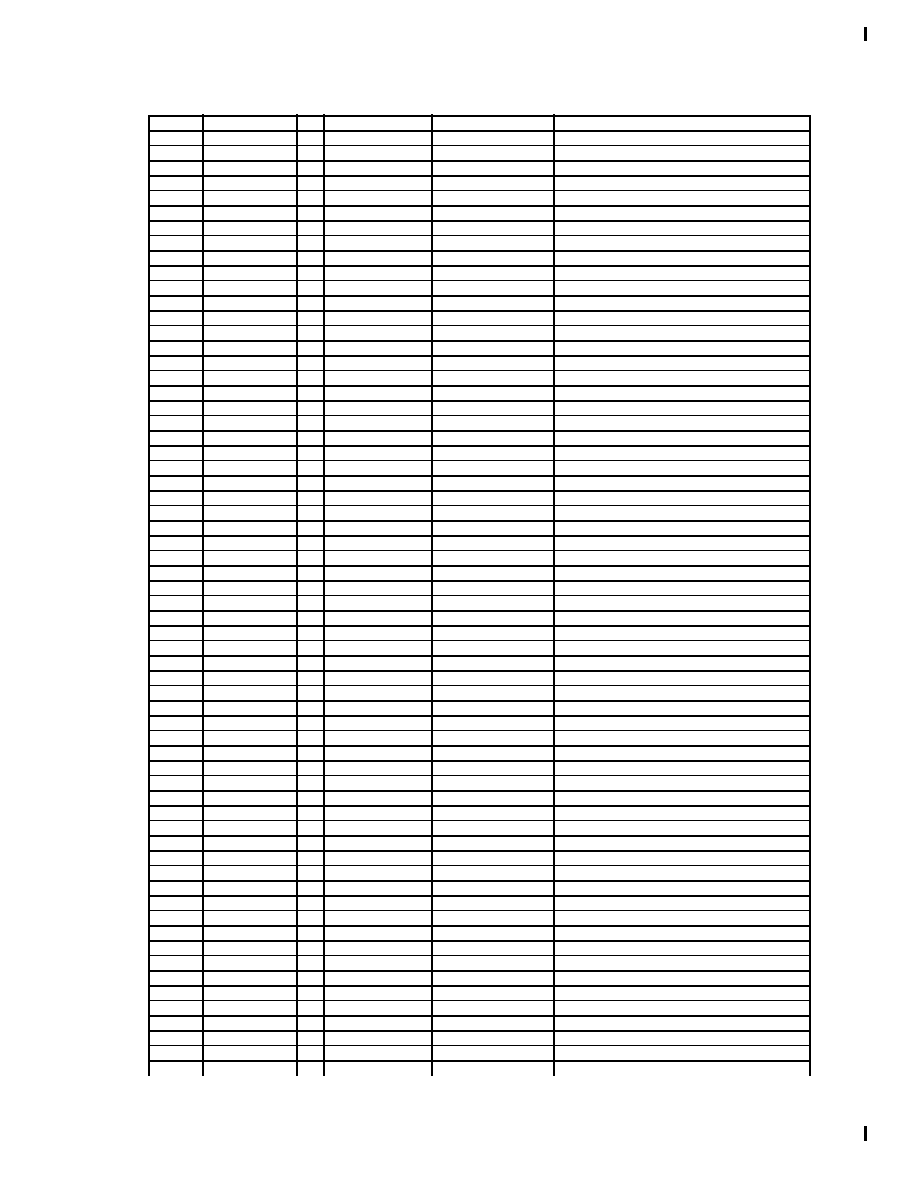

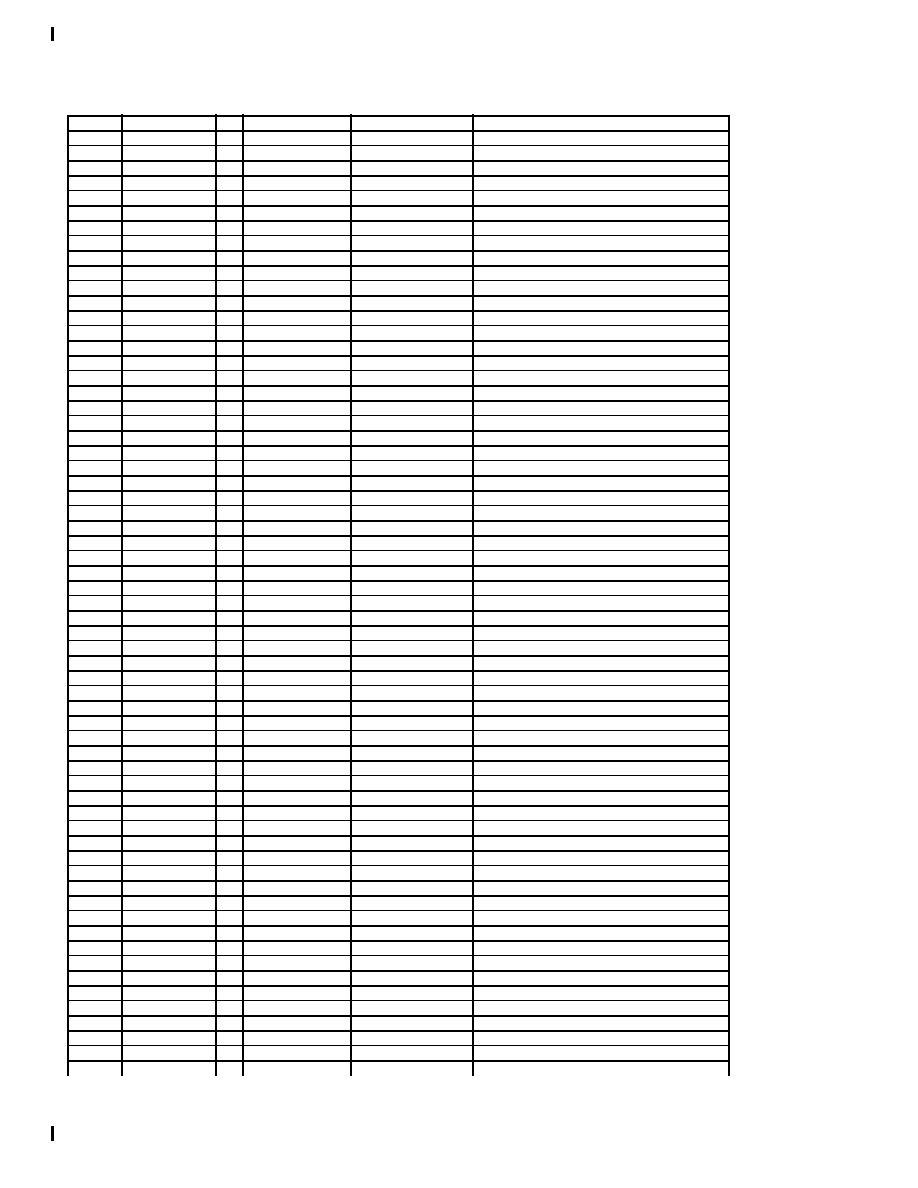

MIOC Signal List .......................................................................................................... 2-3

2.2.1.2

PXB Signal List ............................................................................................................ 2-4

2.2.1.3

RCG Signal List ........................................................................................................... 2-5

2.2.1.4

MUX Signal List ........................................................................................................... 2-5

2.3

System Interface ......................................................................................................................................... 2-6

2.3.1

System / MIOC Interface ............................................................................................................... 2-6

2.3.2

Third-Party Agent / MIOC Interface .............................................................................................. 2-8

2.4

PCI Interface ............................................................................................................................................... 2-8

2.4.1

Primary Bus .................................................................................................................................. 2-8

2.4.2

64-bit Access Support ................................................................................................................. 2-10

2.4.3

Internal vs. External Arbitration ................................................................................................... 2-10

2.4.4

PIIX4E Interface .......................................................................................................................... 2-11

2.5

Memory Subsystem Interface .................................................................................................................... 2-12

2.5.1

External Interface ........................................................................................................................ 2-12

2.5.2

Internal Interface ......................................................................................................................... 2-14

2.5.2.1

RCG / DRAM Interface .............................................................................................. 2-14

2.5.2.2

DRAM / MUX Interface .............................................................................................. 2-15

2.5.2.3

RCG / MUX Interface ................................................................................................. 2-15

2.6

Expander Interface .................................................................................................................................... 2-15

2.7

Common Support Signals ......................................................................................................................... 2-17

2.7.1

JTAG Interface ............................................................................................................................ 2-17

2.7.2

Reference Signals ....................................................................................................................... 2-17

2.8

Component-Specific Support Signals ........................................................................................................ 2-18

2.8.1

MIOC ........................................................................................................................................... 2-18

2.8.2

PXB ............................................................................................................................................ 2-19

2.8.3

RCG ............................................................................................................................................ 2-19

2.8.4

MUX ............................................................................................................................................ 2-19

Chapter 3

Register Descriptions ......................................................................................................................... 3-1

3.1

Access Restrictions ..................................................................................................................................... 3-1

3.2

I/O Mapped Registers ................................................................................................................................. 3-1

3.2.1

CONFIG_ADDRESS: Configuration Address Register ............................................................... 3-1

-ii-

Intel 450NX PCIset

CONTENTS

3.2.2

CONFIG_DATA: Configuration Data Register .............................................................................. 3-2

3.3

MIOC Configuration Space ..................................................................................................................... 3-3

3.3.1

BUFSIZ: Buffer Sizes ................................................................................................................... 3-4

3.3.2

BUSNO[1:0]: Lowest PCI Bus Number, per PXB ......................................................................... 3-5

3.3.3

CHKCON: Check Connection ....................................................................................................... 3-5

3.3.4

CLASS: Class Code Register ....................................................................................................... 3-6

3.3.5

CONFIG: Software-Defined Configuration Register ..................................................................... 3-6

3.3.6

CVCR: Configuration Values Captured on Reset ......................................................................... 3-8

3.3.7

CVDR: Configuration Values Driven On Reset ............................................................................ 3-9

3.3.8

DBC[15:0]: DRAM Bank Configuration Registers ......................................................................... 3-9

3.3.9

DEVMAP: System Bus PCI Device Map .................................................................................... 3-10

3.3.10

DID: Device Identification Register ............................................................................................. 3-11

3.3.11

ECCCMD: ECC Command Register .......................................................................................... 3-11

3.3.12

ECCMSK: ECC Mask Register ................................................................................................... 3-12

3.3.13

ERRCMD: Error Command Register .......................................................................................... 3-12

3.3.14

ERRSTS: Error Status Register ................................................................................................. 3-13

3.3.15

GAPEN: Gap Enables ................................................................................................................ 3-14

3.3.16

HDR: Header Type Register ....................................................................................................... 3-15

3.3.17

HEL[1:0] Host Bus Error Log ...................................................................................................... 3-15

3.3.18

HXGB: High Expansion Gap Base ............................................................................................. 3-16

3.3.19

HXGT: High Expansion Gap Top ............................................................................................... 3-16

3.3.20

IOABASE: I/O APIC Base Address ............................................................................................ 3-16

3.3.21

IOAR: I/O APIC Ranges ............................................................................................................. 3-17

3.3.22

IOR: I/O Ranges ......................................................................................................................... 3-17

3.3.23

ISA: ISA Space ........................................................................................................................... 3-18

3.3.24

LXGB: Low Expansion Gap Base ............................................................................................... 3-18

3.3.25

LXGT: Low Expansion Gap Top ................................................................................................. 3-18

3.3.26

MAR[6:0]: Memory Attribute Region Registers ........................................................................... 3-19

3.3.27

MEA[1:0] Memory Error Effective Address ................................................................................. 3-20

3.3.28

MEL[1:0] Memory Error Log ....................................................................................................... 3-20

3.3.29

MMBASE: Memory-Mapped PCI Base ...................................................................................... 3-21

3.3.30

MMR[3:0]: Memory-Mapped PCI Ranges .................................................................................. 3-21

3.3.31

PMD[1:0]: Performance Monitoring Data Register ..................................................................... 3-21

3.3.32

PME[1:0]: Performance Monitoring Event Selection .................................................................. 3-22

3.3.33

PMR[1:0]: Performance Monitoring Response ........................................................................... 3-23

3.3.34

RC: Reset Control Register ........................................................................................................ 3-24

3.3.35

RCGP: RCGs Present ................................................................................................................ 3-25

3.3.36

REFRESH: DRAM Refresh Control Register ............................................................................. 3-25

3.3.37

RID: Revision Identification Register .......................................................................................... 3-26

3.3.38

ROUTE[1:0]: Route Field Seed ................................................................................................. 3-26

3.3.39

SMRAM: SMM RAM Control Register ........................................................................................ 3-26

3.3.40

SUBA[1:0]: Bus A Subordinate Bus Number, per PXB .............................................................. 3-28

3.3.41

SUBB[1:0]: Bus B Subordinate Bus Number, per PXB .............................................................. 3-28

3.3.42

TCAP[0:3]: Target Capacity, per PXB/PCI Port .......................................................................... 3-28

3.3.43

TOM: Top of Memory ................................................................................................................. 3-29

3.3.44

VID: Vendor Identification Register ............................................................................................ 3-29

3.4

PXB Configuration Space .......................................................................................................................... 3-29

3.4.1

BUFSIZ: Buffer Sizes ................................................................................................................. 3-31

3.4.2

CLASS: Class Code Register ..................................................................................................... 3-31

3.4.3

CLS: Cache Line Size ................................................................................................................ 3-32

3.4.4

CONFIG: Configuration Register ................................................................................................ 3-32

3.4.5

DID: Device Identification Register ............................................................................................. 3-34

3.4.6

ERRCMD: Error Command Register .......................................................................................... 3-34

3.4.7

ERRSTS: Error Status Register ................................................................................................. 3-35

Intel 450NX PCIset

-iii-

CONTENTS

3.4.8

GAPEN: Gap Enables ................................................................................................................ 3-36

3.4.9

HDR: Header Type Register ...................................................................................................... 3-36

3.4.10

HXGB: High Expansion Gap Base ............................................................................................. 3-36

3.4.11

HXGT: High Expansion Gap Top ............................................................................................... 3-37

3.4.12

IOABASE: I/O APIC Base Address ............................................................................................ 3-37

3.4.13

ISA: ISA Space .......................................................................................................................... 3-37

3.4.14

LXGB: Low Expansion Gap Base .............................................................................................. 3-37

3.4.15

LXGT: Low Expansion Gap Top ................................................................................................ 3-38

3.4.16

MAR[6:0]: Memory Attribute Region Registers .......................................................................... 3-38

3.4.17

MLT: Master Latency Timer Register ......................................................................................... 3-38

3.4.18

MMBASE: Memory-Mapped PCI Base ..................................................................................... 3-39

3.4.19

MMT: Memory-Mapped PCI Top ............................................................................................... 3-39

3.4.20

MODES: Modes Register ........................................................................................................... 3-39

3.4.21

MTT: Multi-Transaction Timer Register ..................................................................................... 3-39

3.4.22

PCICMD: PCI Command Register ............................................................................................. 3-40

3.4.23

PCISTS: PCI Status Register .................................................................................................... 3-41

3.4.24

PMD[1:0]: Performance Monitoring Data Register ..................................................................... 3-42

3.4.25

PME[1:0]: Performance Monitoring Event Selection .................................................................. 3-42

3.4.26

PMR[1:0]: Performance Monitoring Response .......................................................................... 3-44

3.4.27

RID: Revision Identification Register ......................................................................................... 3-44

3.4.28

RC: Reset Control Register ....................................................................................................... 3-45

3.4.29

ROUTE: Route Field Seed ......................................................................................................... 3-45

3.4.30

SMRAM: SMM RAM Control Register ....................................................................................... 3-46

3.4.31

TCAP: Target Capacity .............................................................................................................. 3-46

3.4.32

TMODE: Timer Mode ................................................................................................................. 3-47

3.4.33

TOM: Top of Memory ................................................................................................................. 3-47

3.4.34

VID: Vendor Identification Register ............................................................................................ 3-48

Chapter 4

System Address Maps ....................................................................................................................... 4-1

4.1

Memory Address Map ................................................................................................................................. 4-1

4.1.1

Memory-Mapped I/O Spaces ........................................................................................................ 4-4

4.1.2

SMM RAM Support ....................................................................................................................... 4-4

4.2

I/O Space .................................................................................................................................................... 4-5

4.3

PCI Configuration Space ............................................................................................................................. 4-6

Chapter 5

Interfaces ............................................................................................................................................. 5-1

5.1

System Bus ................................................................................................................................................. 5-1

5.2

PCI Bus ....................................................................................................................................................... 5-1

5.3

Expander Bus .............................................................................................................................................. 5-1

5.3.1

Expander Electrical Signal and Clock Distribution ........................................................................ 5-2

5.4

Third-Party Agents ...................................................................................................................................... 5-2

5.5

Connectors ............................................................................................................................................... 5-3

Chapter 6

Memory Subsystem ............................................................................................................................ 6-1

6.1

Overview ..................................................................................................................................................... 6-1

6.1.1

Physical Organization ................................................................................................................... 6-1

6.1.2

Configuration Rules and Limitations ............................................................................................. 6-3

6.1.2.1

Interleaving .................................................................................................................. 6-3

6.1.2.2

Address Bit Permuting Rules and Limitations ............................................................. 6-4

6.1.2.3

Card to Card (C2C) Interleaving rules and limitations ................................................. 6-4

-iv-

Intel 450NX PCIset

CONTENTS

6.1.3

Address Bit Permuting ................................................................................................................... 6-5

6.1.4

Card to Card (C2C) Interleaving .................................................................................................... 6-5

6.1.5

Memory Initialization ...................................................................................................................... 6-6

Chapter 7

Transaction Summary ......................................................................................................................... 7-1

7.1

Host To/From Memory Transactions ........................................................................................................... 7-1

7.1.1

Reads and Writes .......................................................................................................................... 7-1

7.1.2

Cache Coherency Cycles .............................................................................................................. 7-1

7.1.3

Interrupt Acknowledge Cycles ....................................................................................................... 7-1

7.1.4

Locked Cycles ............................................................................................................................... 7-1

7.1.5

Branch Trace Cycles ..................................................................................................................... 7-2

7.1.6

Special Cycles ............................................................................................................................... 7-2

7.1.7

System Management Mode Accesses .......................................................................................... 7-3

7.1.8

Third-Party Intervention ................................................................................................................. 7-3

7.2

Outbound Transactions ................................................................................................................................ 7-4

7.2.1

Supported Outbound Accesses ..................................................................................................... 7-4

7.2.2

Outbound Locked Transactions ..................................................................................................... 7-4

7.2.3

Outbound Write Combining ........................................................................................................... 7-4

7.2.4

Third-Party Intervention on Outbounds ......................................................................................... 7-4

7.3

Inbound Transactions .................................................................................................................................. 7-5

7.3.1

Inbound LOCKs ............................................................................................................................. 7-5

7.3.2

South Bridge Accesses ................................................................................................................. 7-5

7.4

Configuration Accesses ............................................................................................................................... 7-6

Chapter 8

Arbitration, Buffers & Concurrency ................................................................................................... 8-1

8.1

PCI Arbitration Scheme ............................................................................................................................... 8-1

8.2

Host Arbitration Scheme .............................................................................................................................. 8-1

8.2.1

Third Party Arbitration .................................................................................................................... 8-2

8.3

South Bridge Support ................................................................................................................................... 8-2

8.3.1

I/O Bridge Configuration Example. ................................................................................................ 8-2

8.3.2

PHOLD#/PHLDA# Protocol ........................................................................................................... 8-3

8.3.3

WSC# Protocol .............................................................................................................................. 8-3

Chapter 9

Data Integrity & Error Handling .......................................................................................................... 9-1

9.1

DRAM Integrity ............................................................................................................................................. 9-1

9.1.1

ECC Generation ............................................................................................................................ 9-1

9.1.2

ECC Checking and Correction ...................................................................................................... 9-1

9.1.3

ECC Error Reporting ..................................................................................................................... 9-1

9.1.4

Memory Scrubbing ........................................................................................................................ 9-2

9.1.5

Debug/Diagnostic Support ............................................................................................................. 9-2

9.2

System Bus Integrity .................................................................................................................................... 9-2

9.2.1

System Bus Control & Data Integrity ............................................................................................. 9-3

9.3

PCI Integrity ................................................................................................................................................. 9-3

9.4

Expander Bus .............................................................................................................................................. 9-3

Chapter 10

System Initialization .......................................................................................................................... 10-1

10.1

Post Reset Initialization .............................................................................................................................. 10-1

10.1.1

Reset Configuration using CVDR/CVCR ..................................................................................... 10-1

10.1.1.1

Configuration Protocol ................................................................................................ 10-1

Intel 450NX PCIset

-v-

CONTENTS

10.1.1.2

Special Considerations for Third-Party Agents .......................................................... 10-2

Chapter 11

Clocking and Reset .......................................................................................................................... 11-1

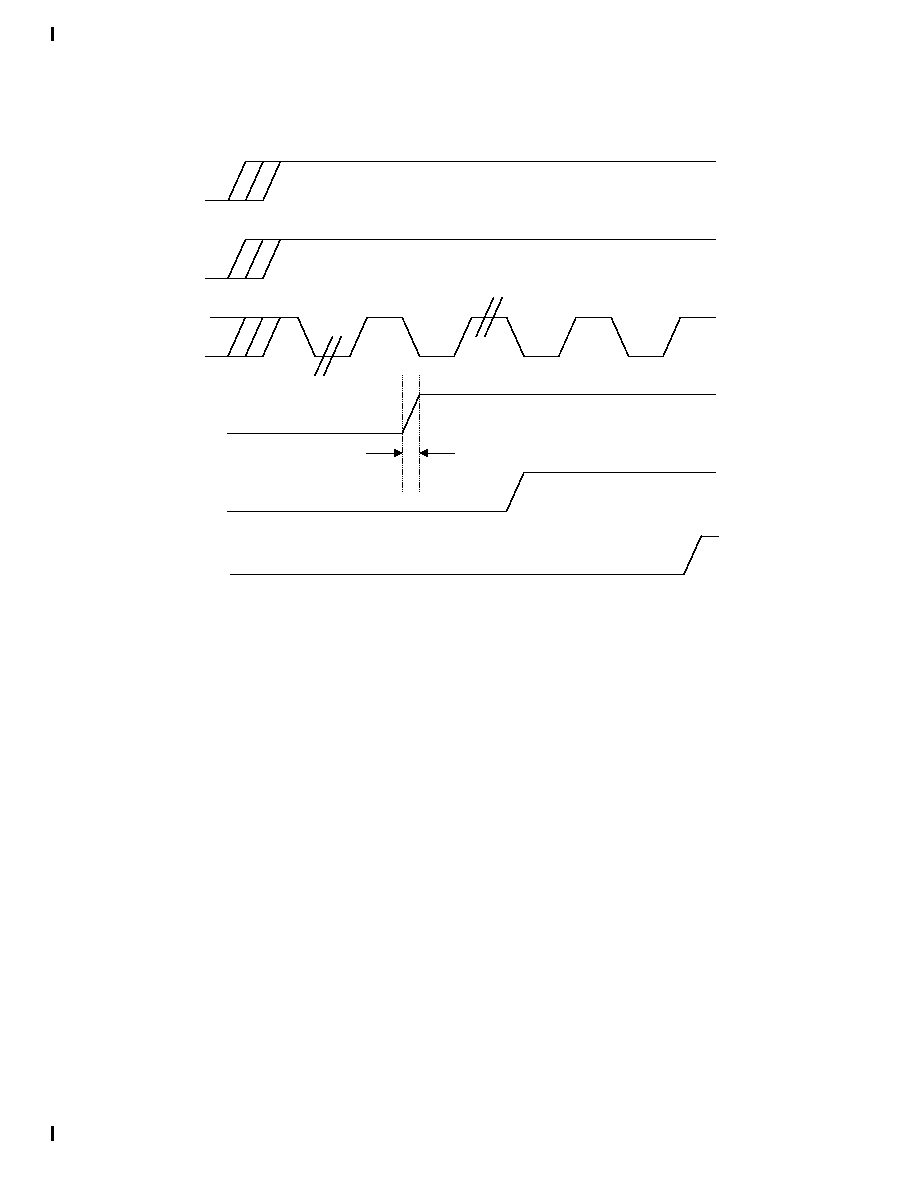

11.1

Clocking ..................................................................................................................................................... 11-1

11.2

System Reset ............................................................................................................................................ 11-2

11.2.1

IntelÆ 450NX PCIset Reset Structure ......................................................................................... 11-2

11.2.2

Output States During Reset ........................................................................................................ 11-5

11.2.2.1

MIOC Reset State ..................................................................................................... 11-6

11.2.2.2

PXB Reset State ........................................................................................................ 11-8

11.2.2.3

RCG Reset State ....................................................................................................... 11-9

11.2.2.4

MUX Reset State ....................................................................................................... 11-9

Chapter 12

Electrical Characteristics ................................................................................................................. 12-1

12.1

Signal Specifications ................................................................................................................................. 12-1

12.1.1

Unused Pins ................................................................................................................................ 12-1

12.1.2

Signal Groups ............................................................................................................................. 12-1

12.1.3

The Power Good Signal: PWRGD .............................................................................................. 12-3

12.1.4

LDSTB# Usage ........................................................................................................................... 12-5

12.1.5

VCCA Pins .................................................................................................................................. 12-5

12.2

Maximum Ratings ...................................................................................................................................... 12-6

12.3

DC Specifications ...................................................................................................................................... 12-7

12.4

AC Specifications .................................................................................................................................... 12-11

12.5

Source Synchronous Data Transfers ...................................................................................................... 12-22

12.6

I/O Signal Simulations: Ensuring I/O Timings ......................................................................................... 12-22

12.7

Signal Quality Specifications ................................................................................................................... 12-23

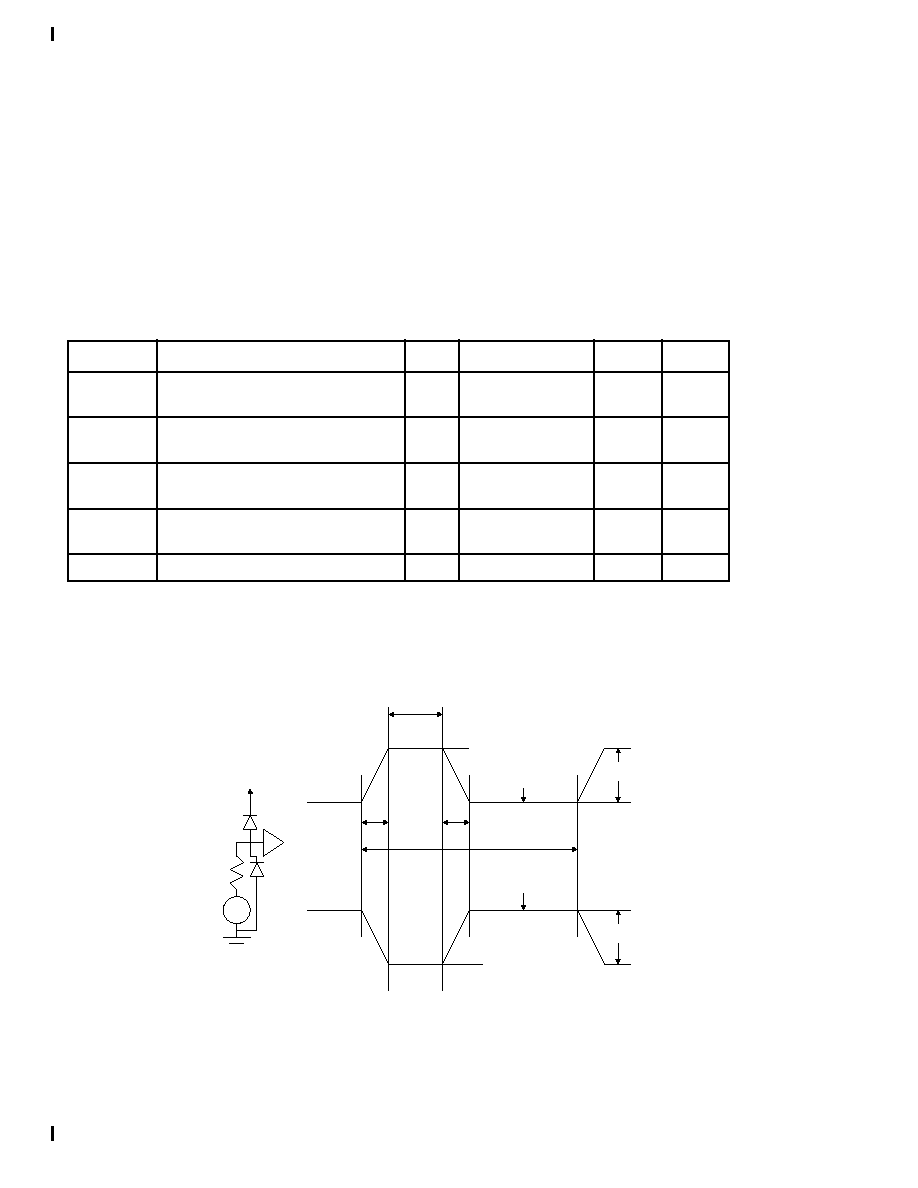

12.7.1

IntelÆ 450NX PCIset Ringback Specification ........................................................................... 12-23

12.7.2

IntelÆ 450NX PCIset Undershoot Specification ........................................................................ 12-25

12.7.3

Skew Requirements .................................................................................................................. 12-25

12.8

IntelÆ 450NX PCIset Thermal Specifications .......................................................................................... 12-26

12.8.1

Thermal Solution Performance ................................................................................................. 12-26

12.9

Mechanical Specifications ....................................................................................................................... 12-27

12.9.1

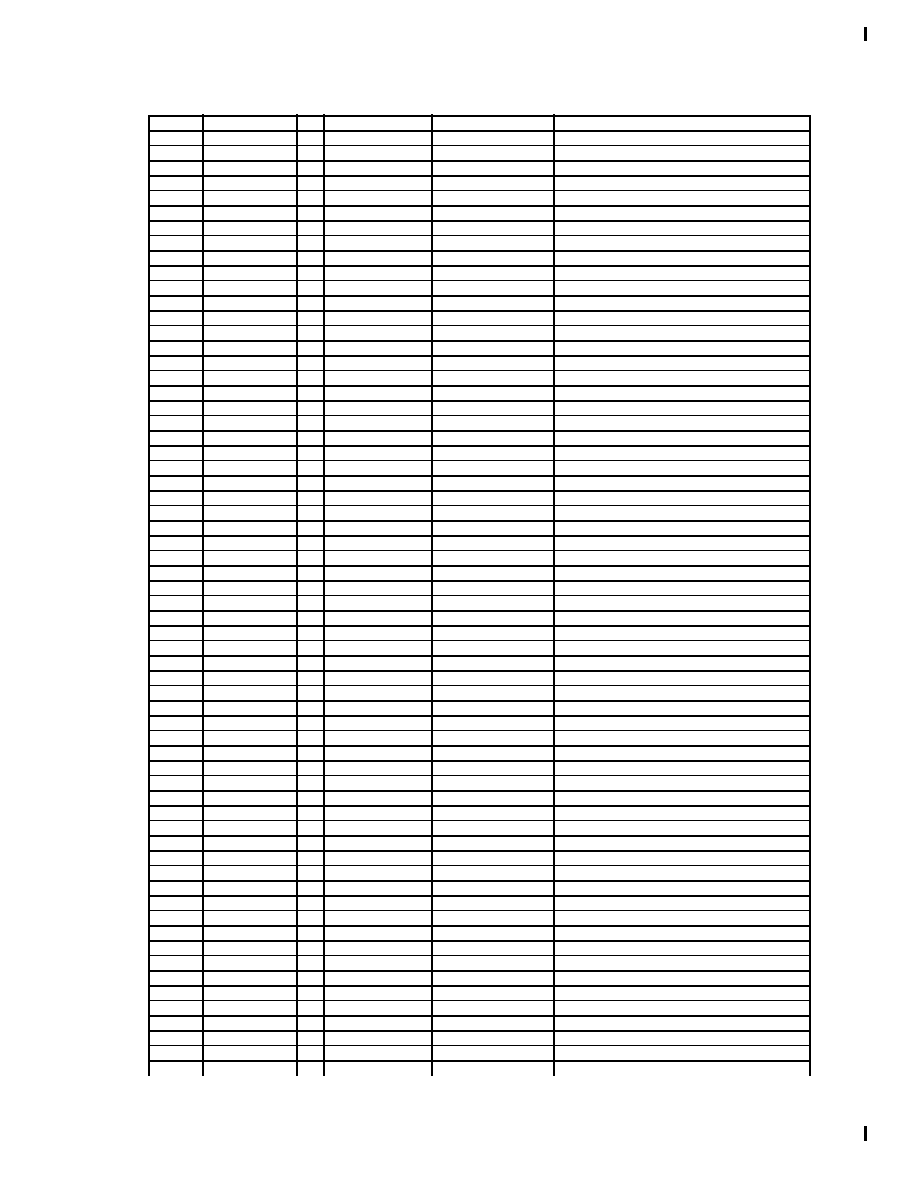

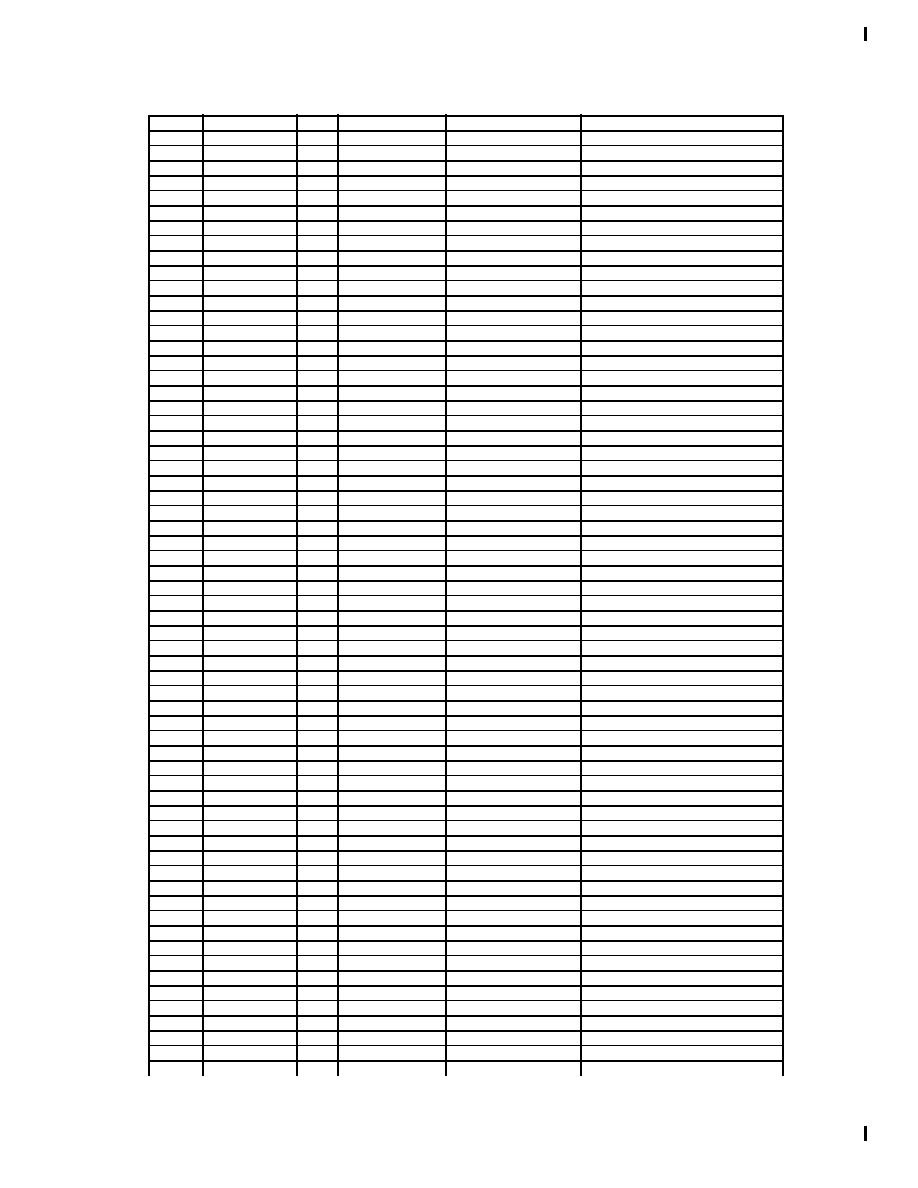

Pin Lists Sorted by Pin Number: ............................................................................................... 12-27

12.9.2

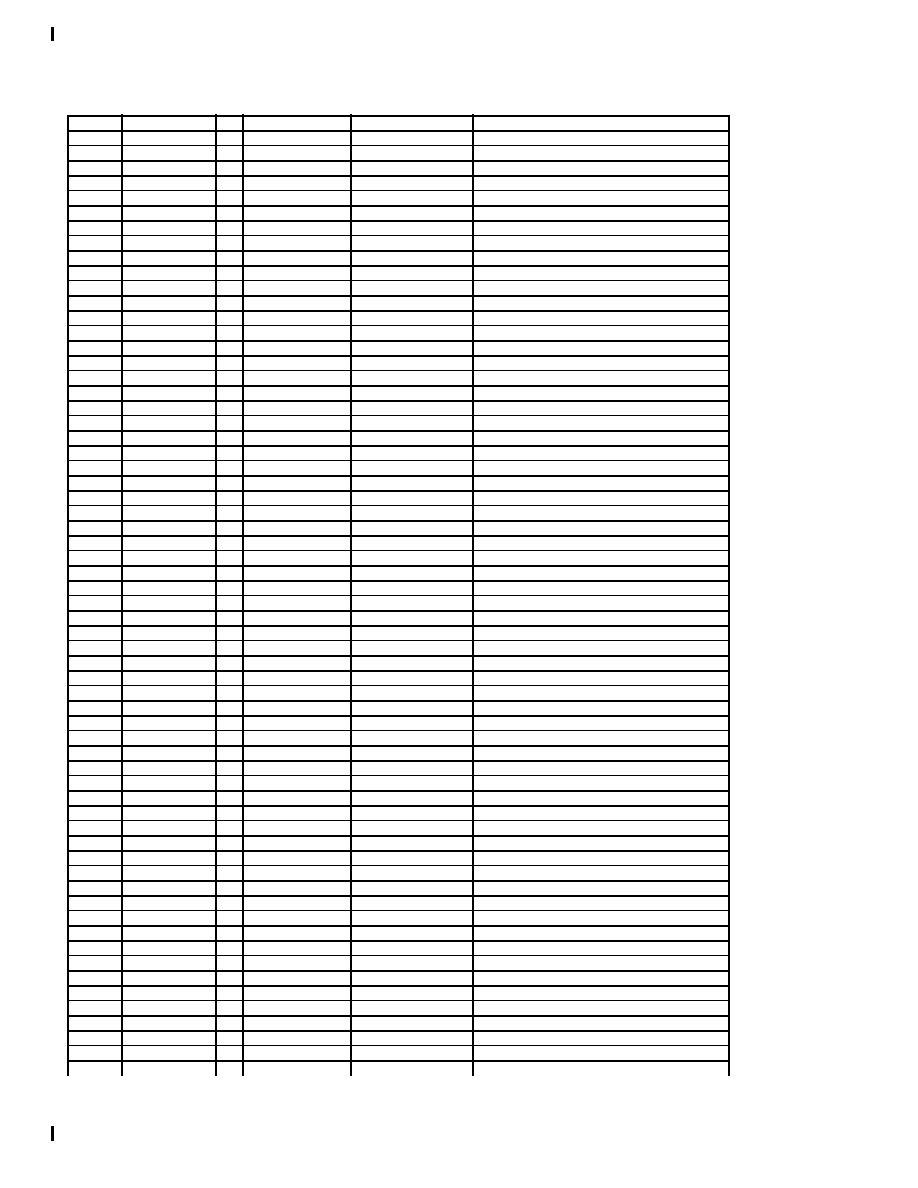

Pin Lists Sorted by Signal ......................................................................................................... 12-54

12.9.3

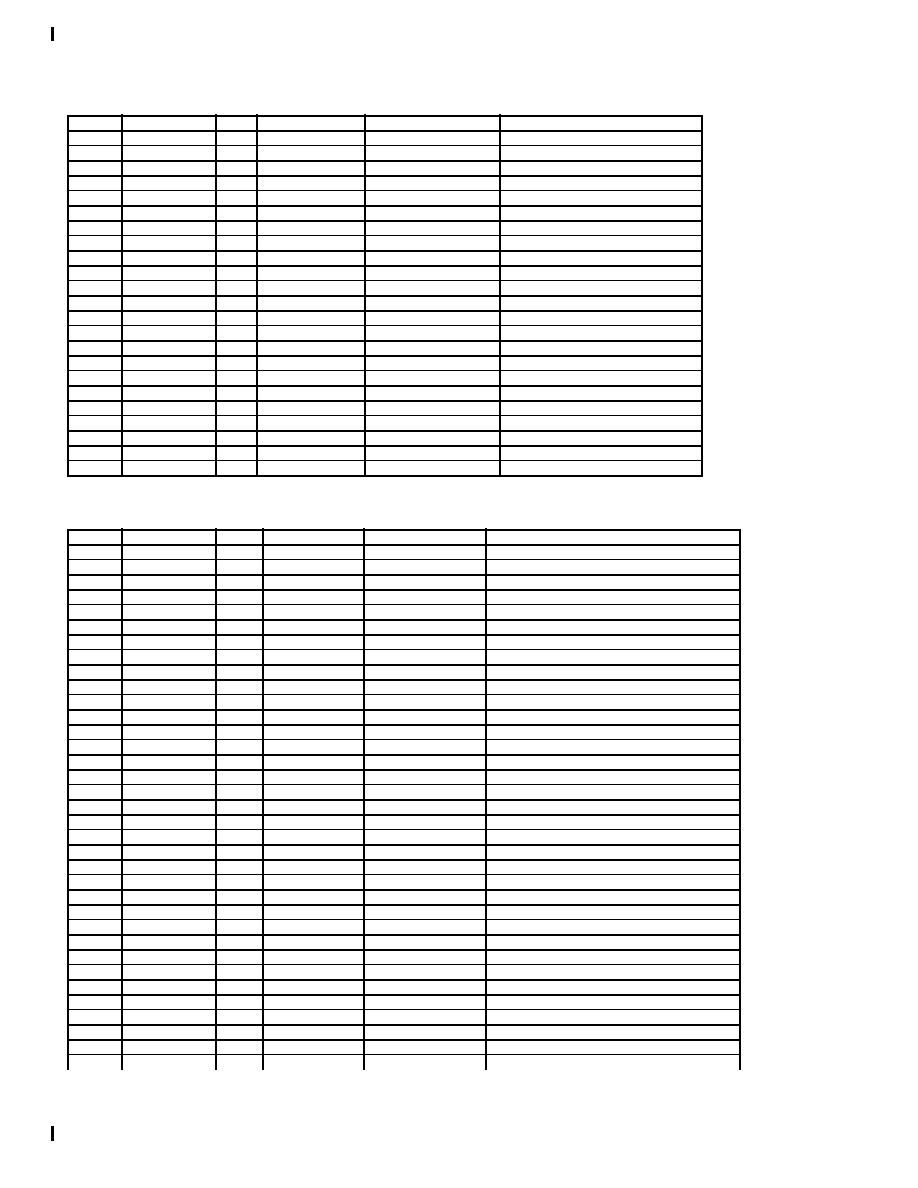

Package information ................................................................................................................. 12-83

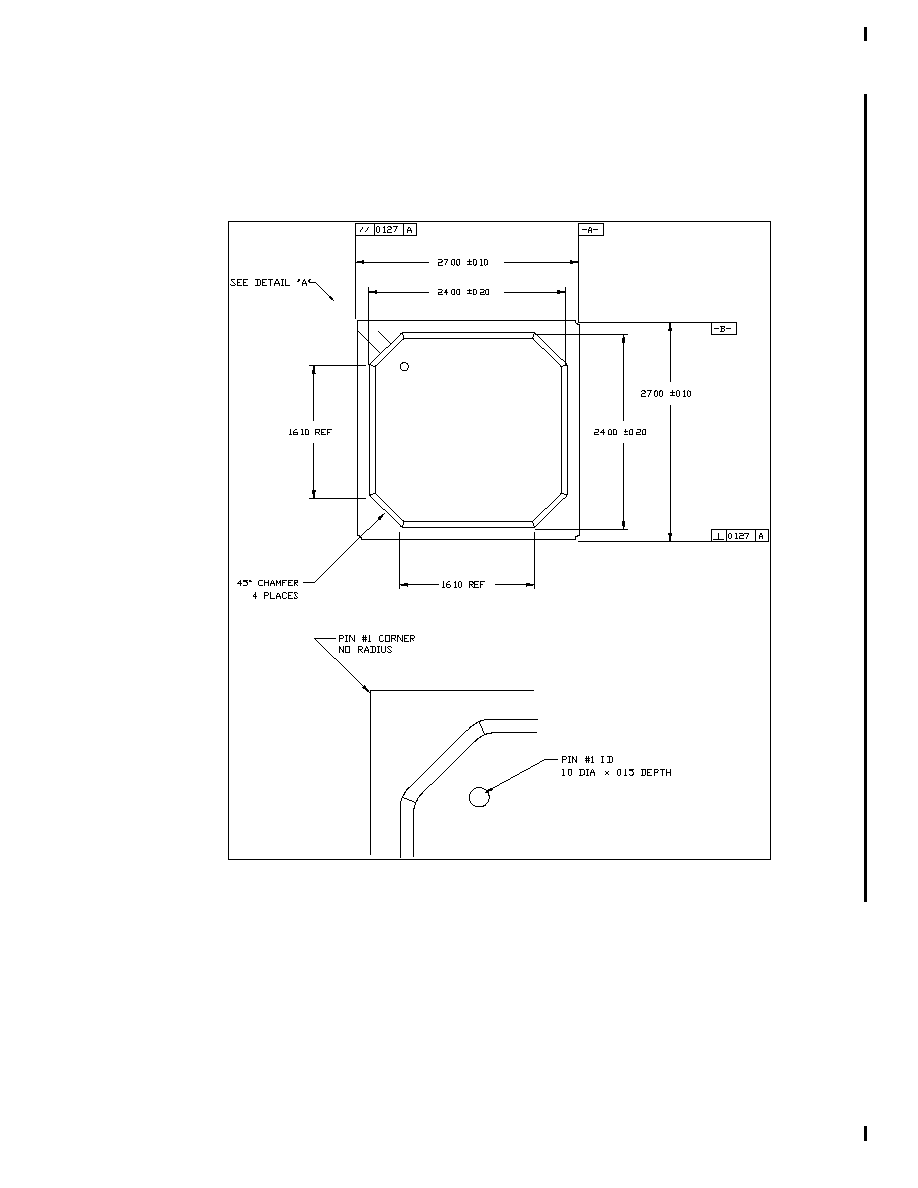

12.9.3.1

324 BGA Package Information ................................................................................ 12-83

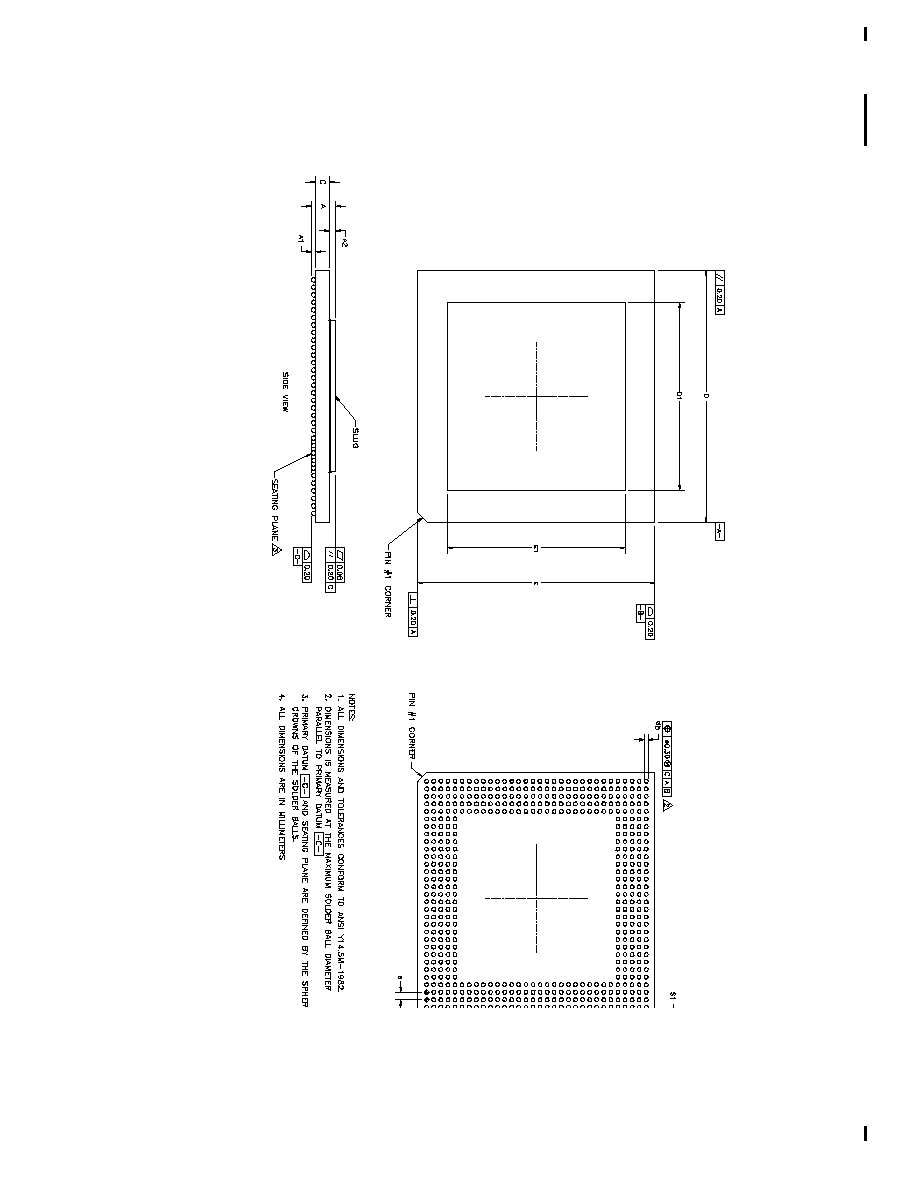

12.9.3.2

540 PBGA Package Information .............................................................................. 12-85

-vi-

Intel 450NX PCIset

CONTENTS

Intel

Æ

450NX PCIset

1-1

1

Introduction

1.1

Overview

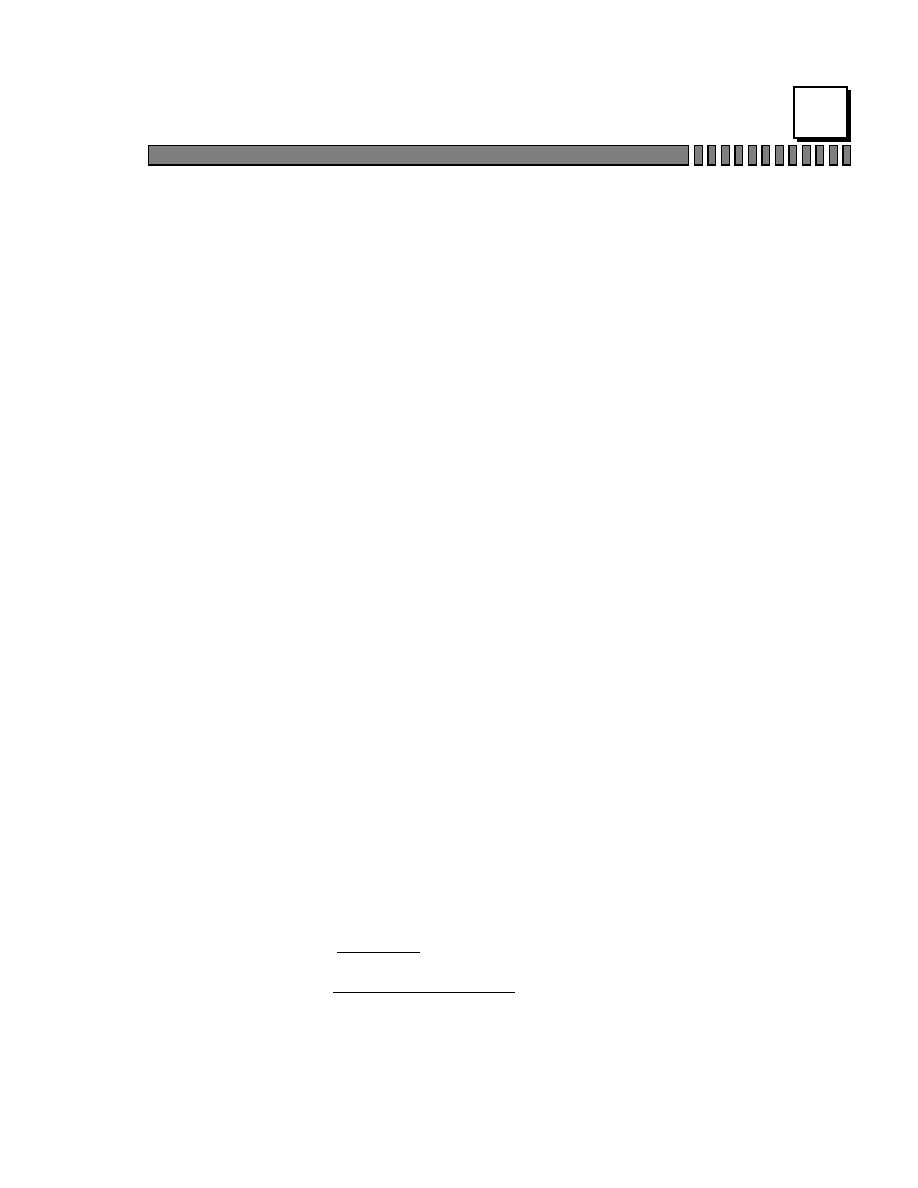

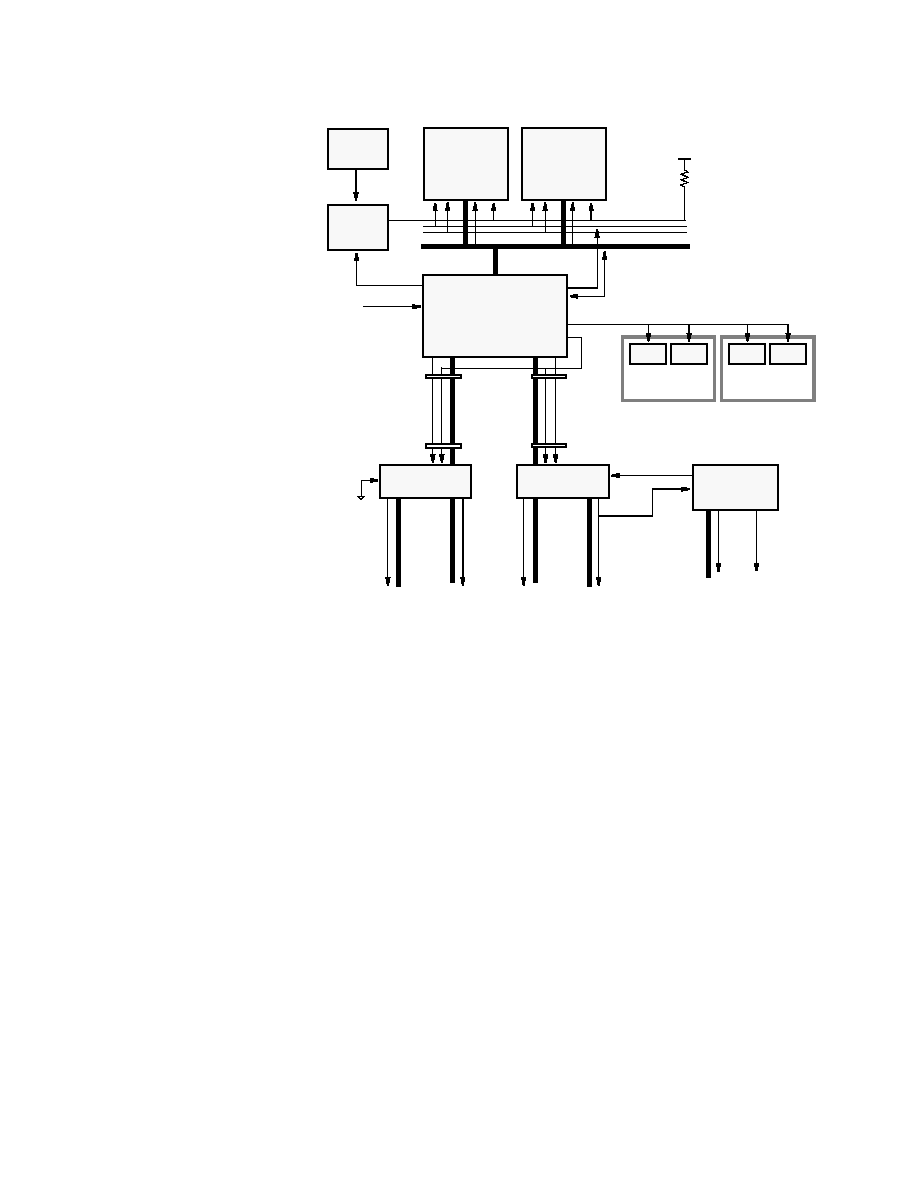

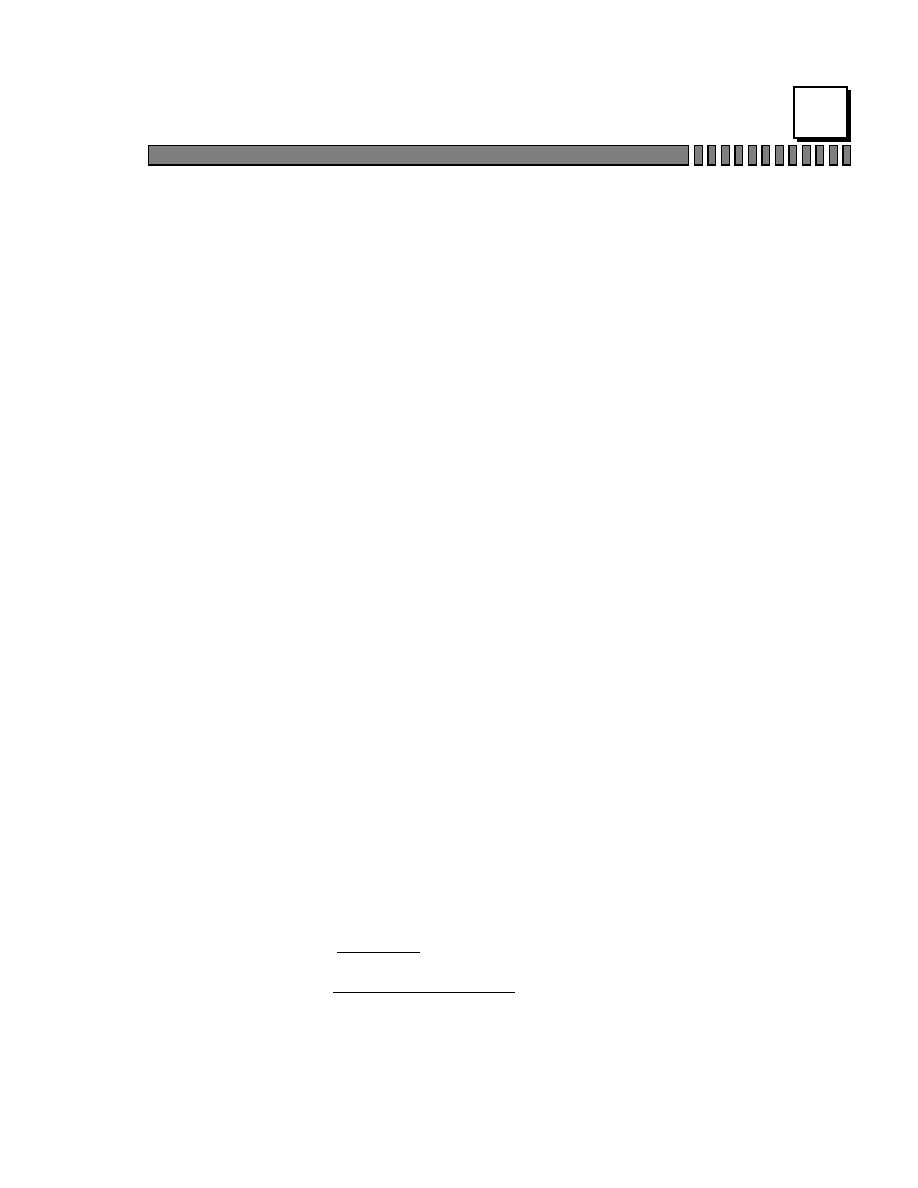

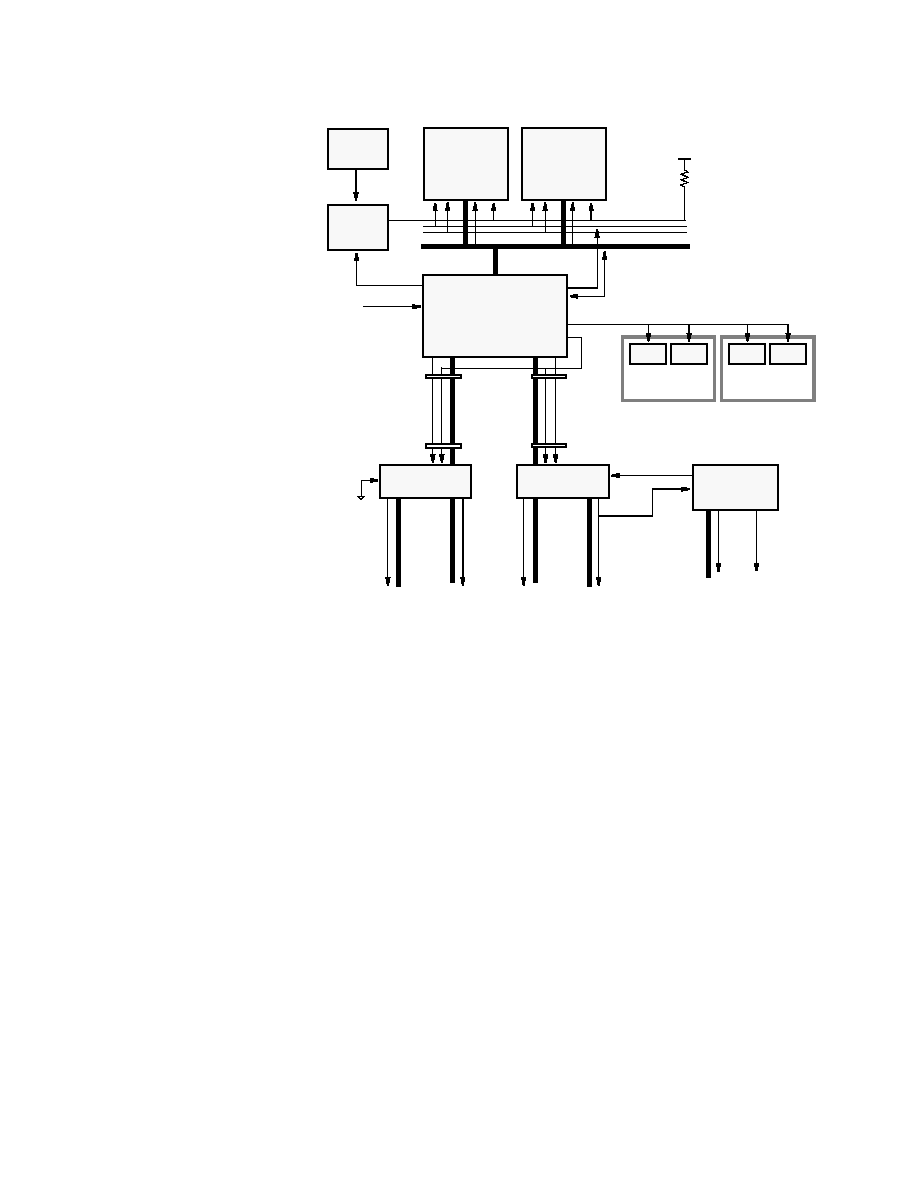

The IntelÆ 450NX PCIset provides an integrated Host-to-PCI bridge and memory controller

optimized for multiprocessor systems and standard high-volume (SHV) servers based on the

PentiumÆ II XeonTM processor variant of the P6 family. The Intel 450NX PCIset consists of

four components: 82454NX PCI Expander Bridge (PXB), 82451NX Memory and I/O Bridge

Controller (MIOC), 82452NX RAS/CAS Generator (RCG), and 82453NX Data Path

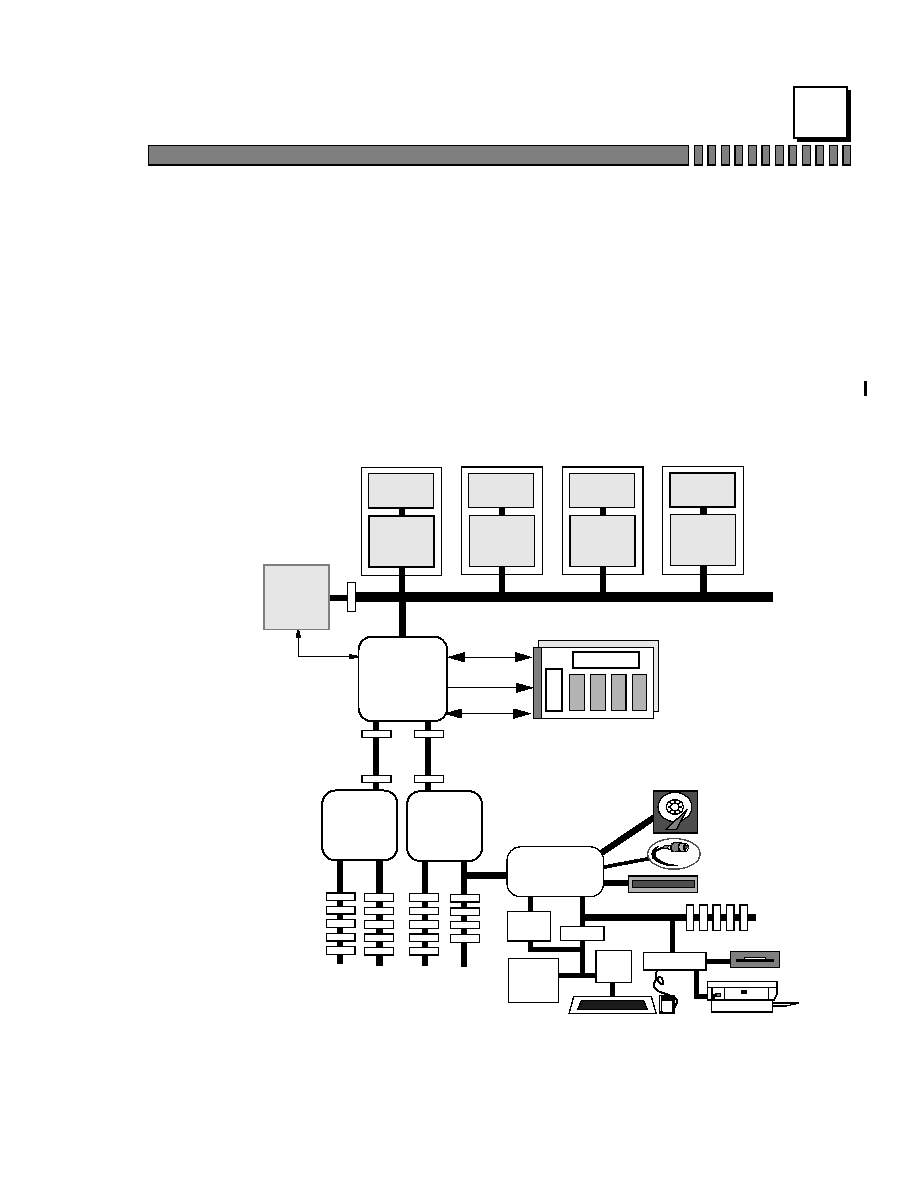

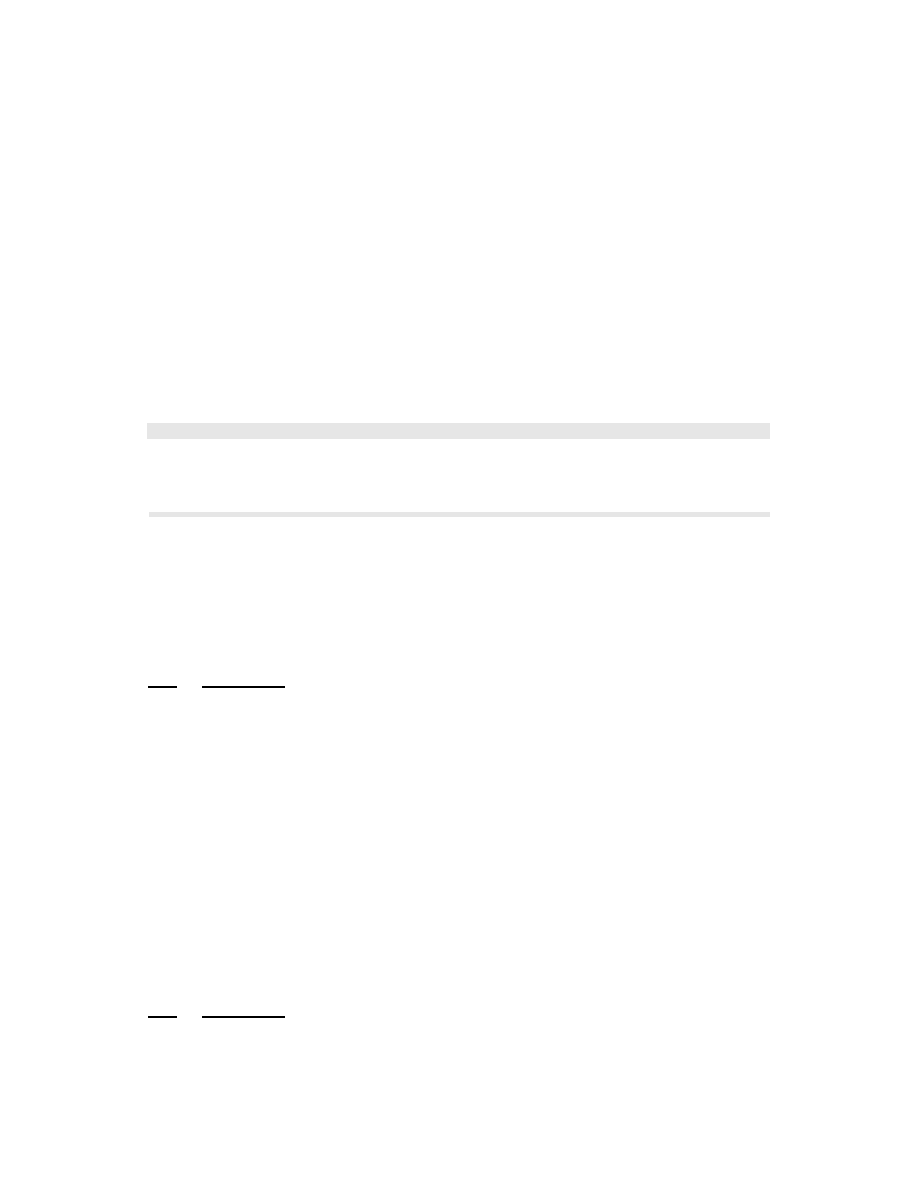

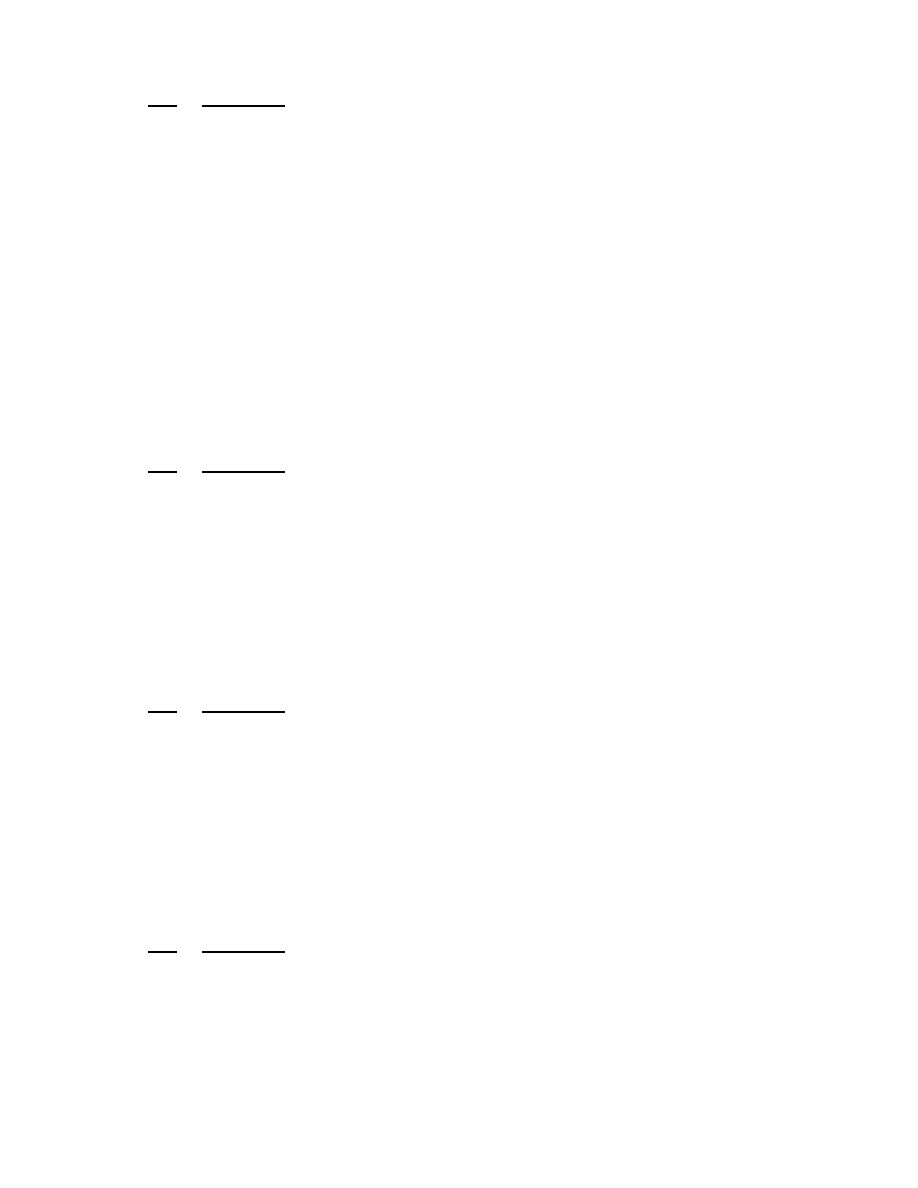

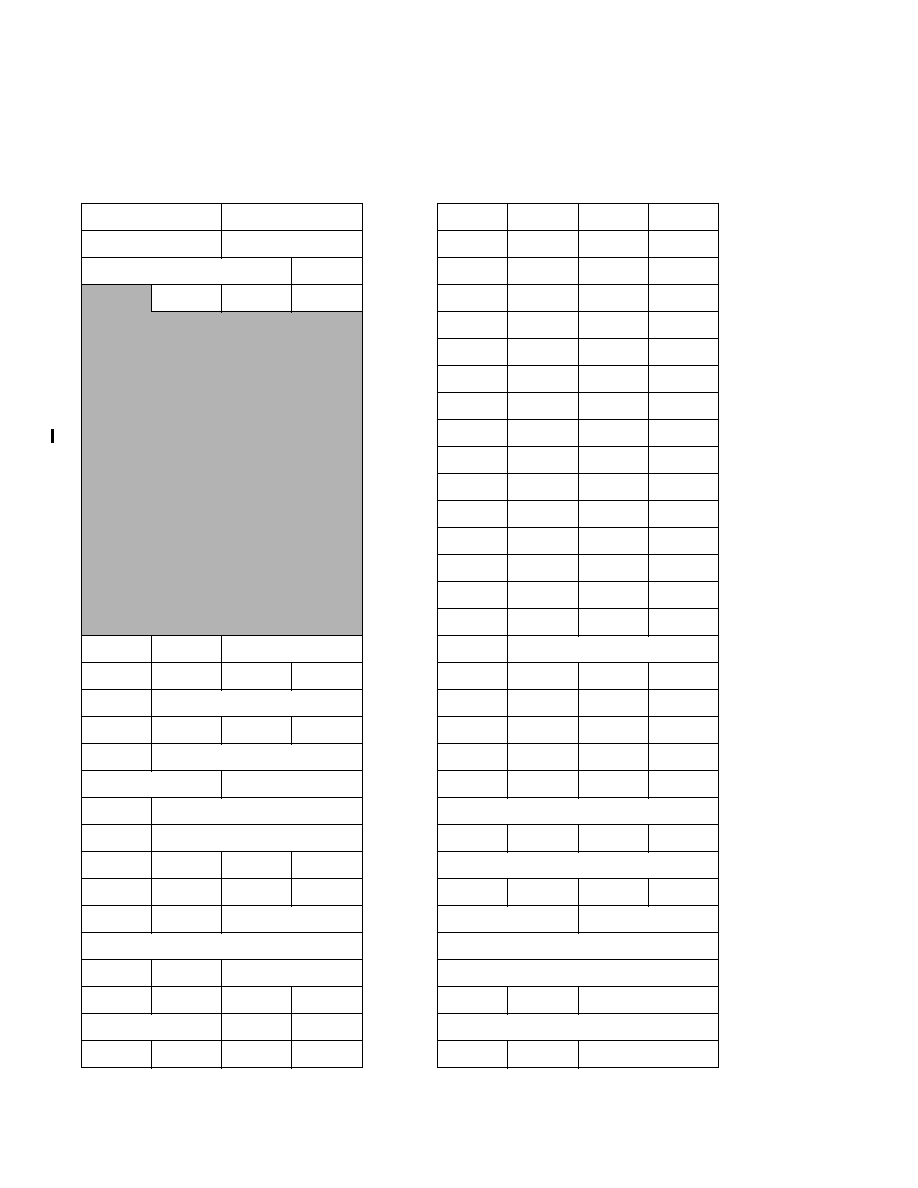

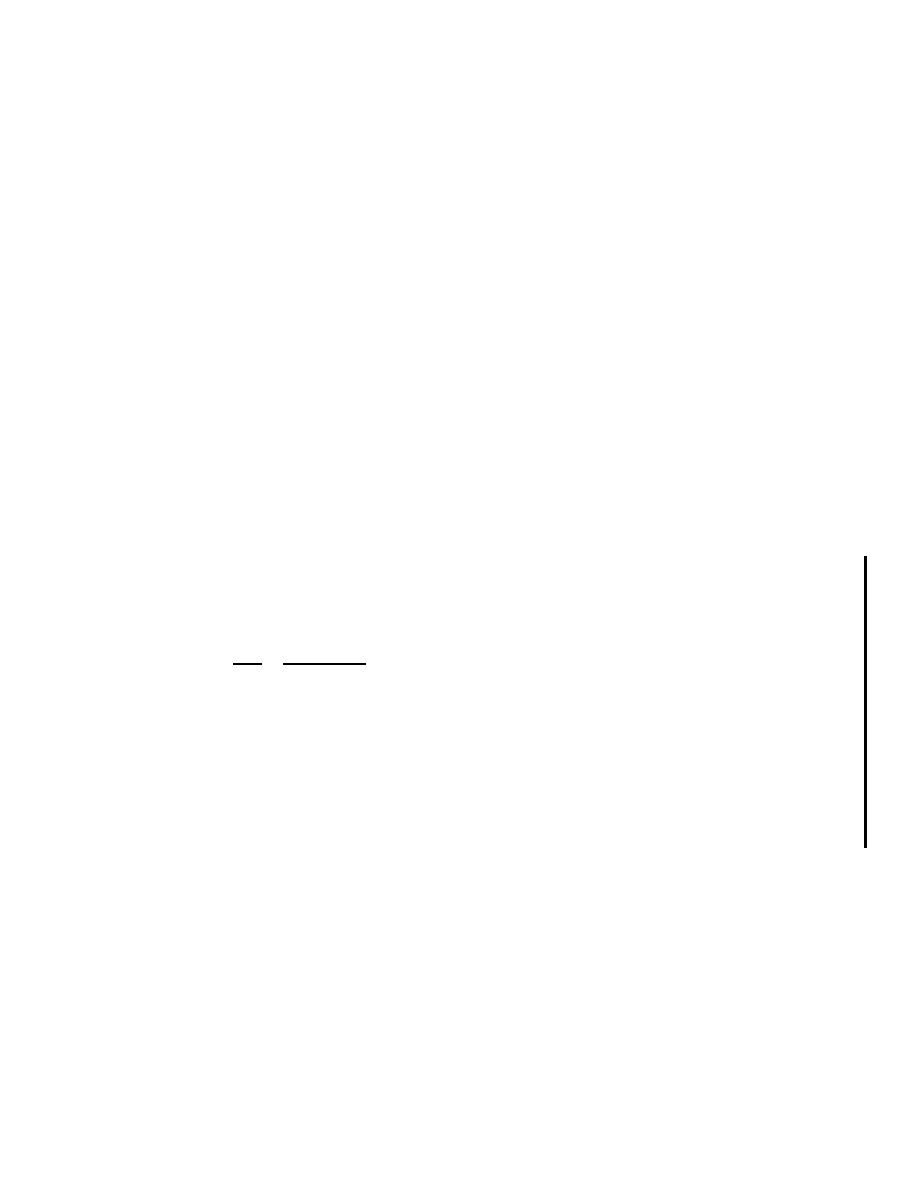

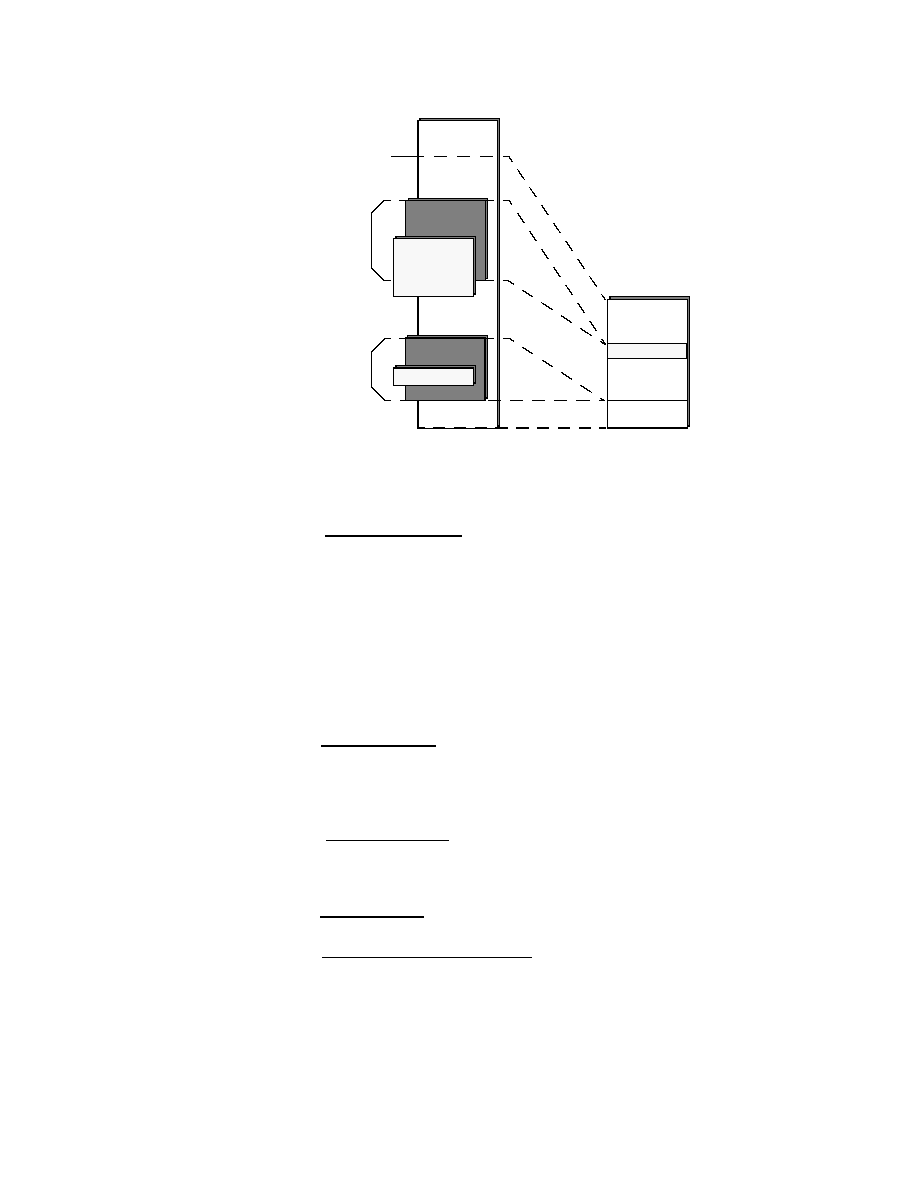

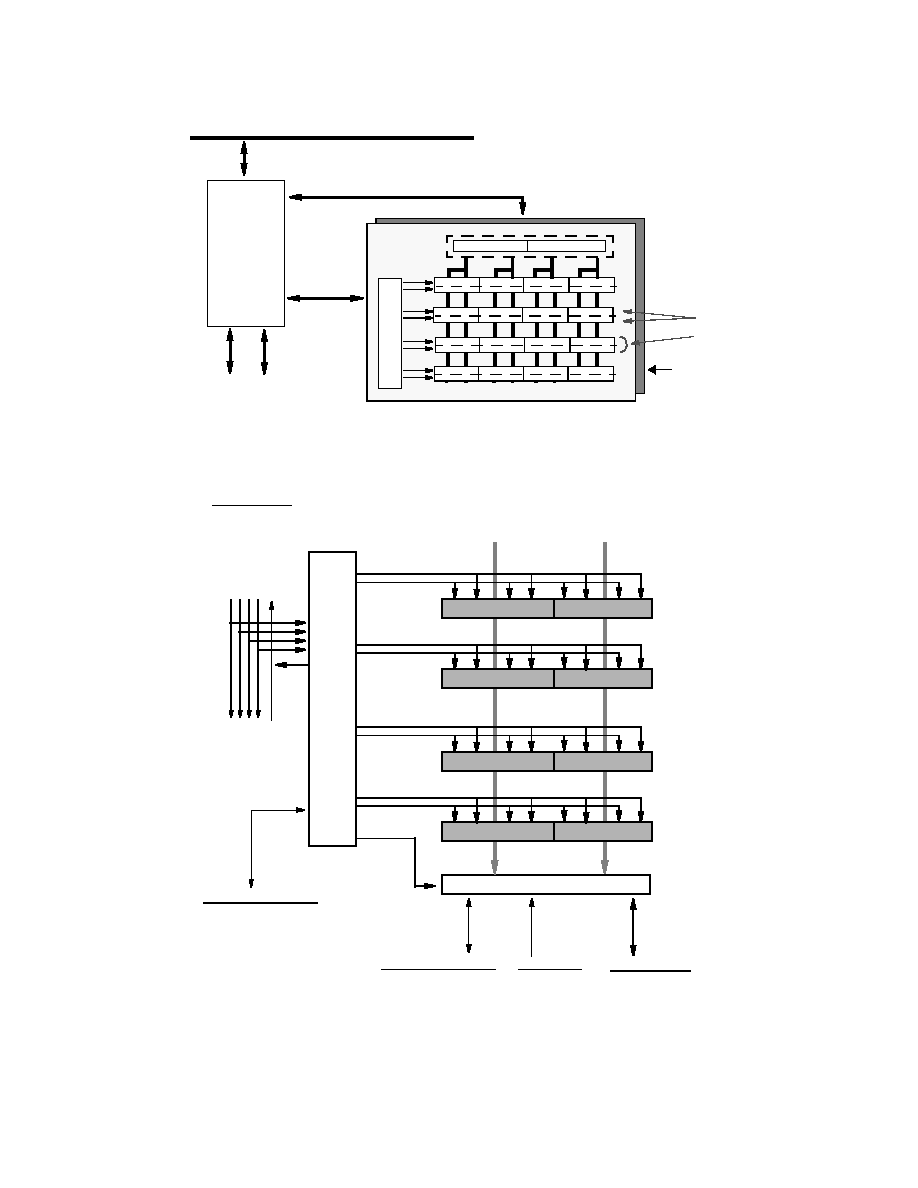

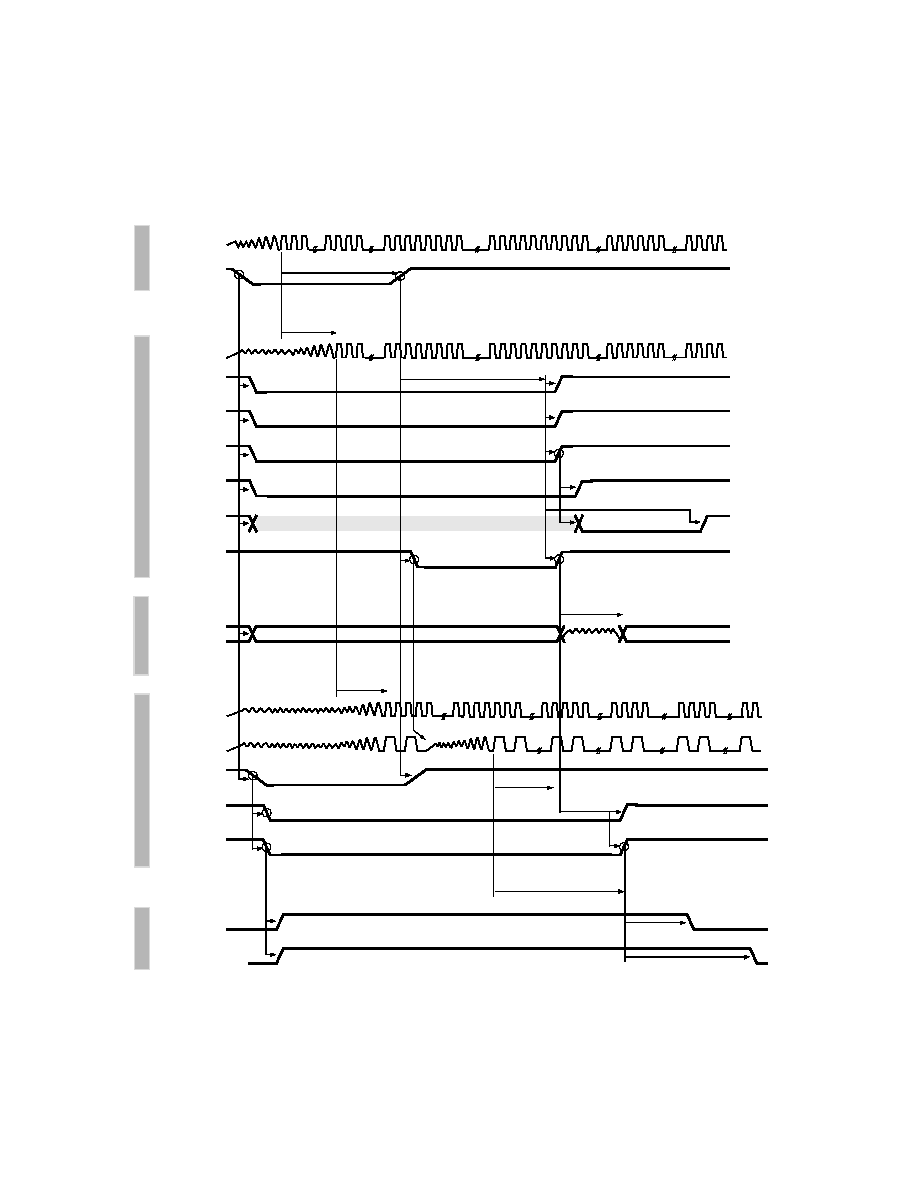

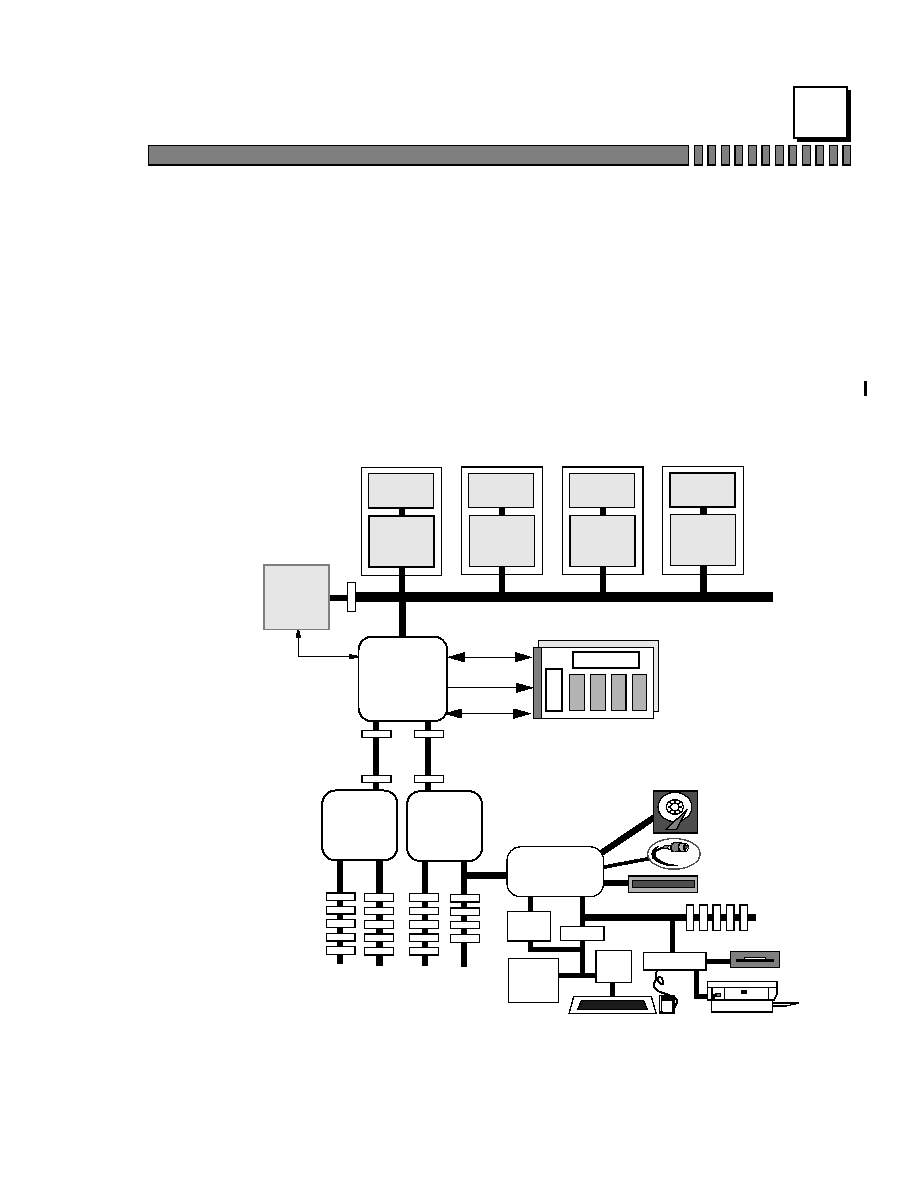

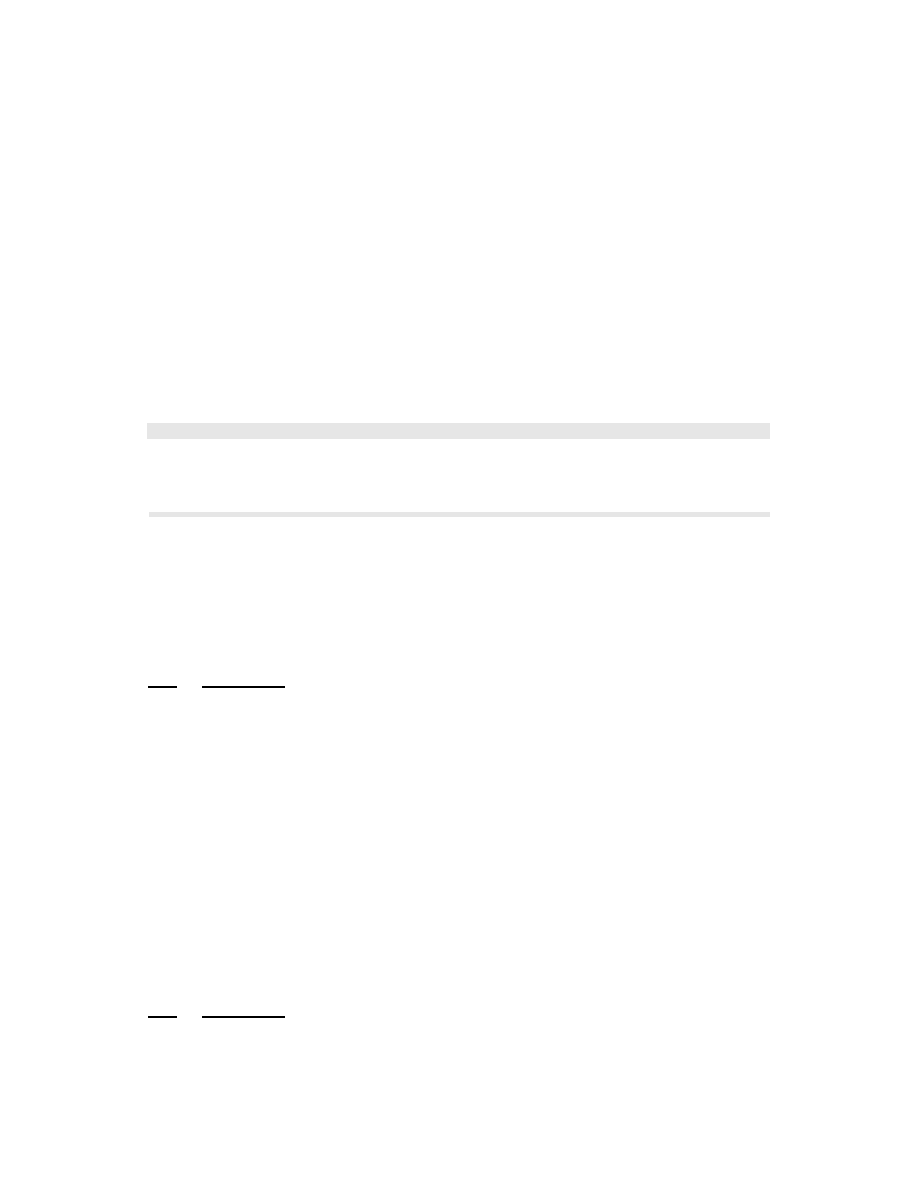

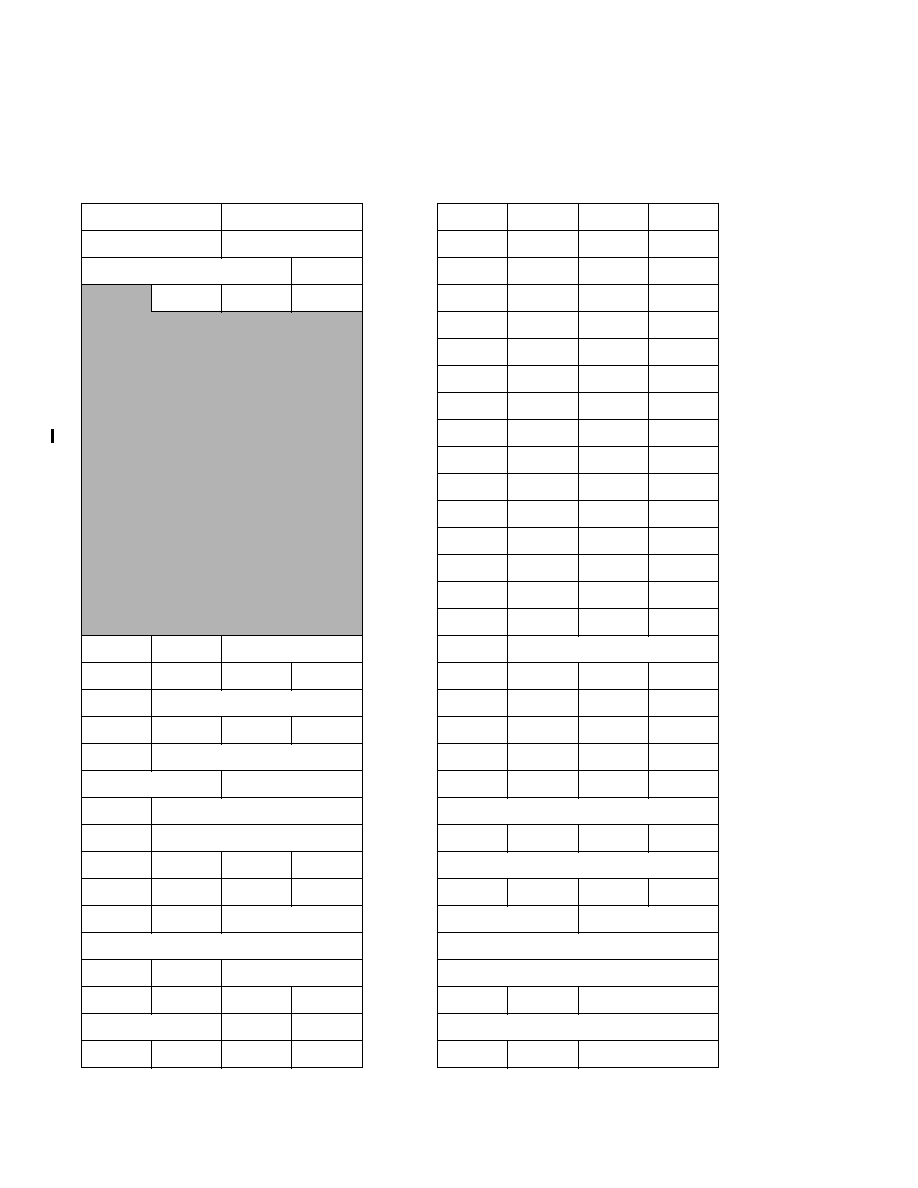

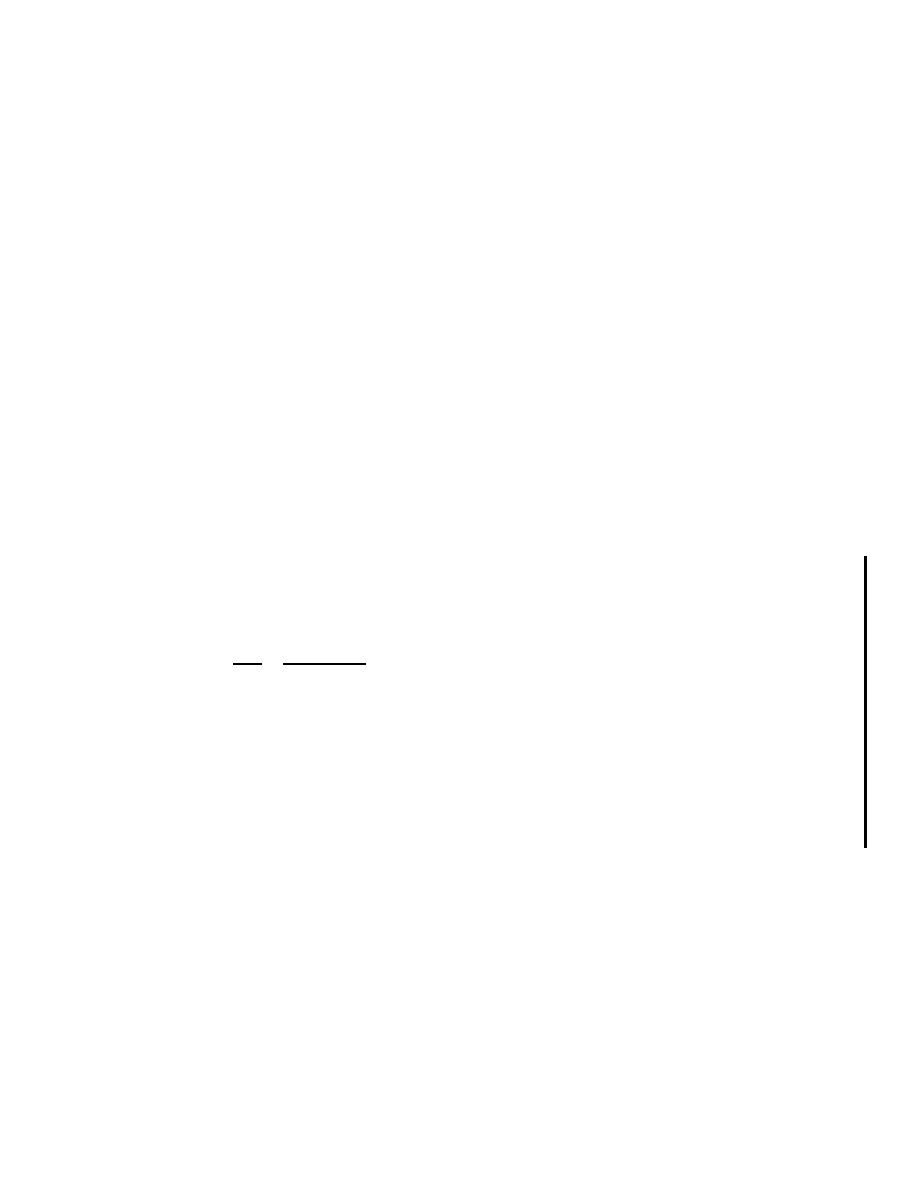

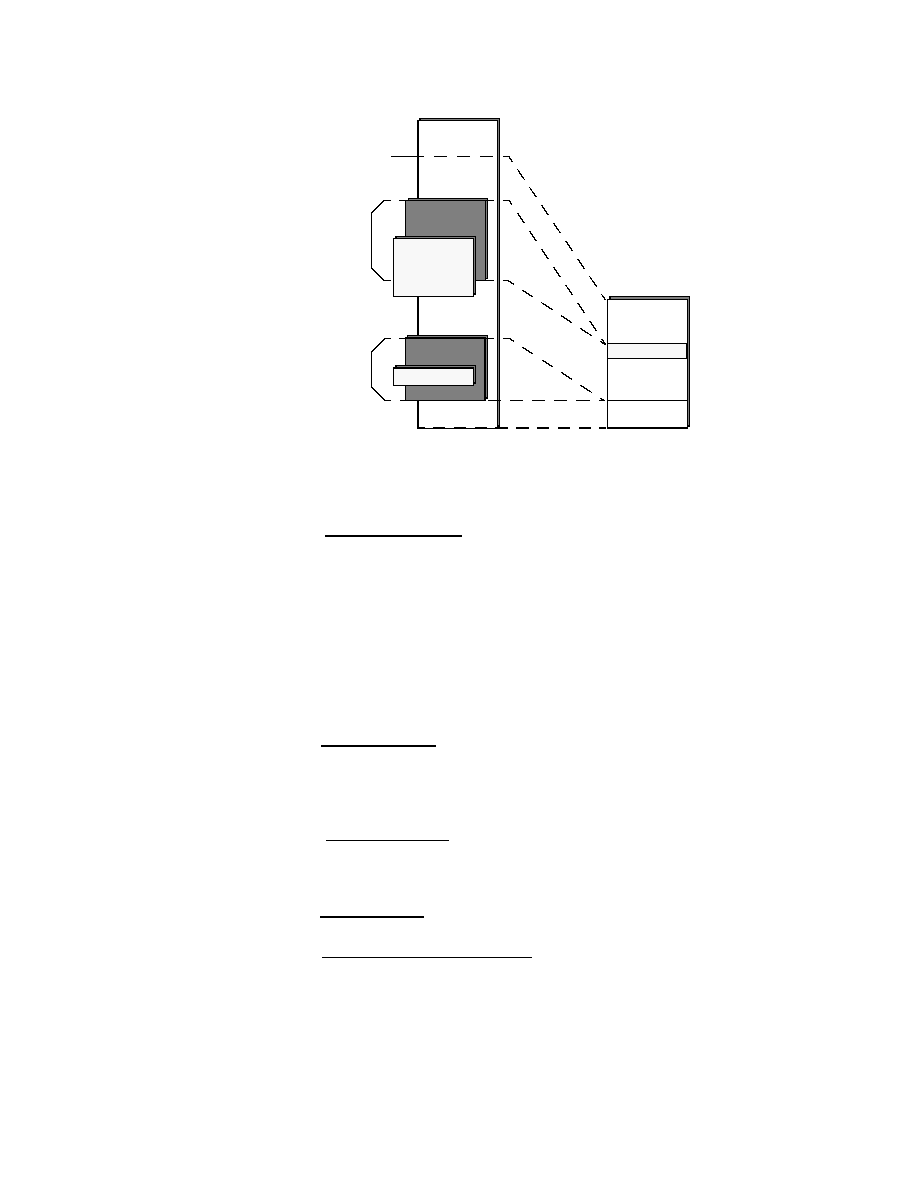

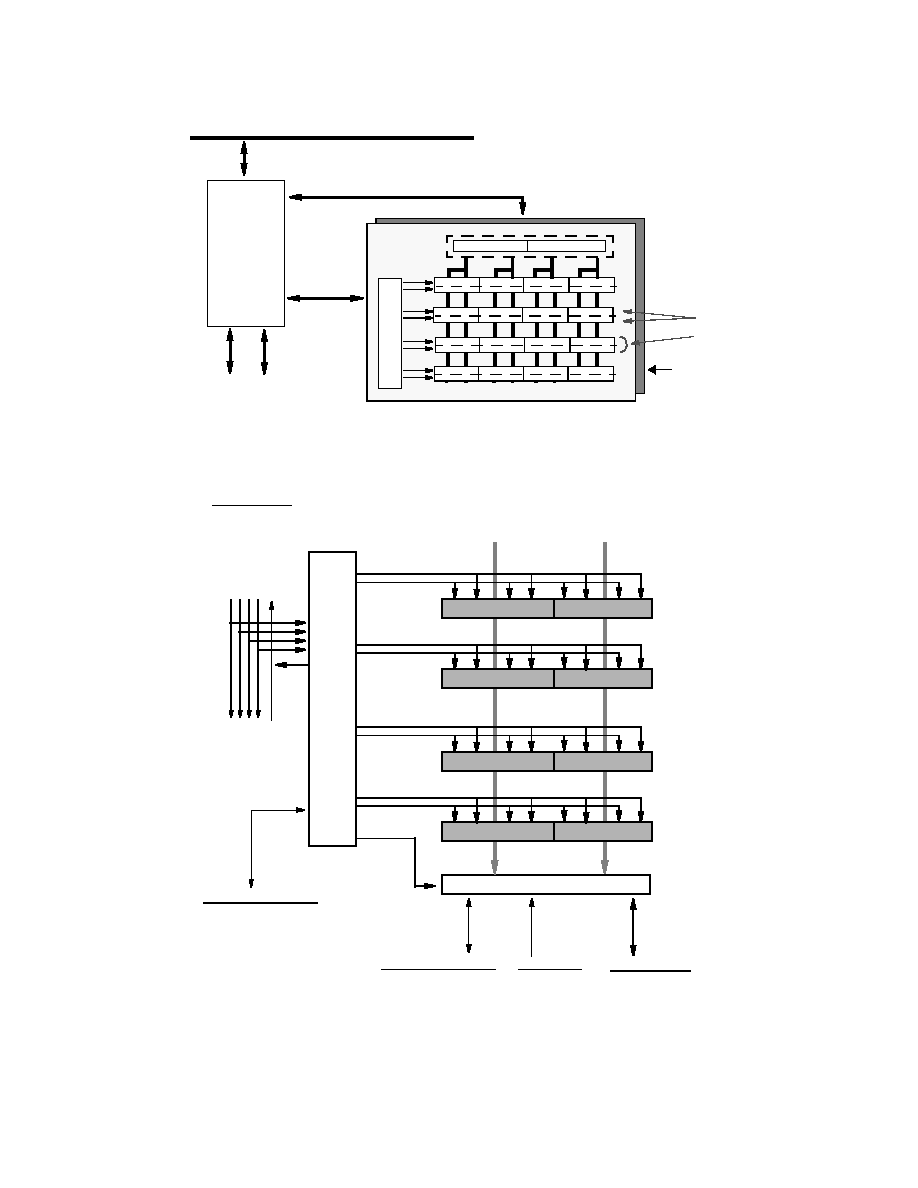

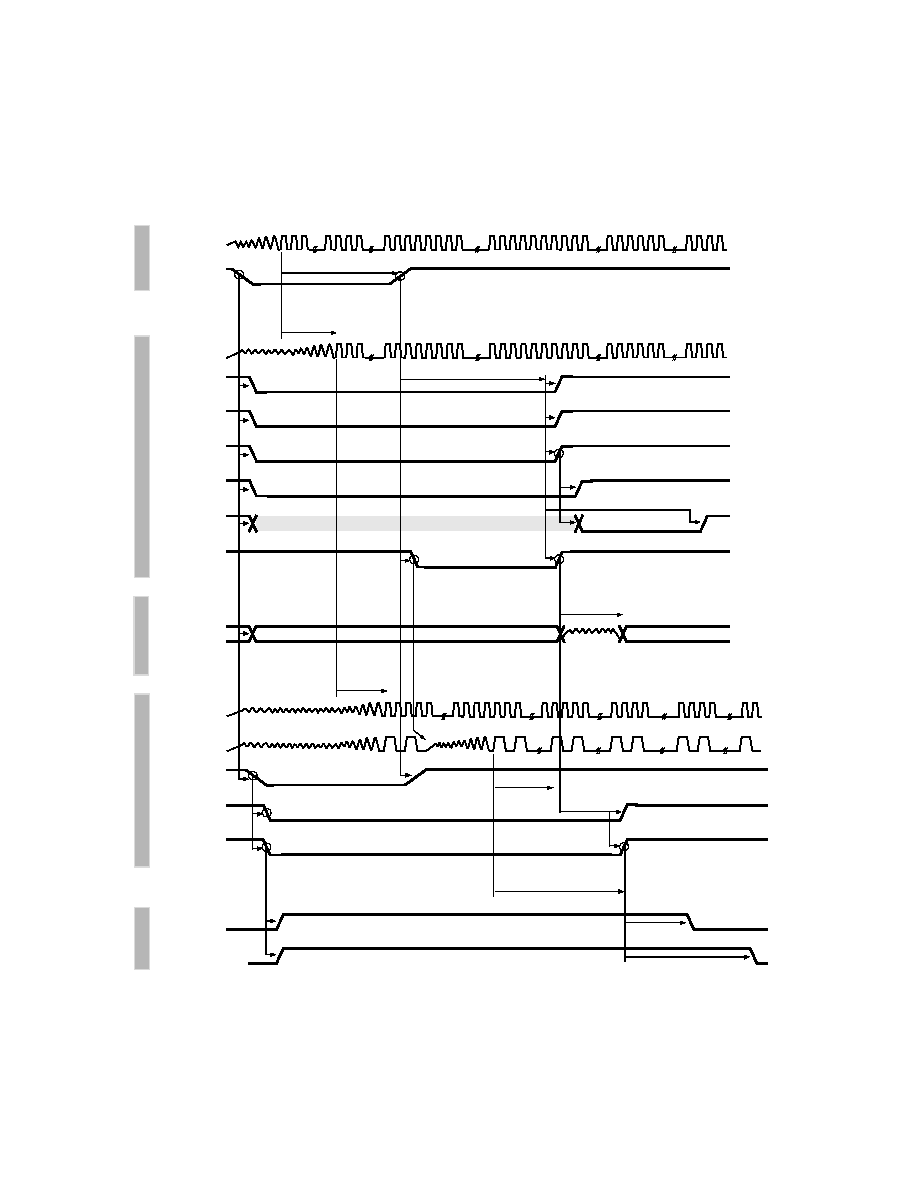

Multiplexor (MUX). Figure 1-1 illustrates a typical SHV server system based on the Intel

450NX PCIset. The system bus interface supports up to 4 Pentium II Xeon processors at 100

MHz. An additional bus mastering agent such as a cluster bridge can be supported at reduced

frequencies. Two dedicated PCI Expander Bridges (PXBs) can be connected via the Expander

Figure 1-1:

Simplified Intel

Æ

450NX PCIset System Block Diagram

RCGs

MUXs

MA[13:0]

Control

BMIDE HDDs

IDE CD-ROM

SIO

XCVR

BIOS

I/O

KBC

8042

Flash

ISA slots

4 PCI Buses

32-bit, 33 MHz, 3.3v or 5v

PCI

Slots

MIOC

Memory

and I/O

MD[71:0]

System Bus

AGTL+ 100 MHz

Memory

EPROM

PIIX4E

South Bridge

Pentium II

processor

Pentium II

processor

Pentium II

processor

Pentium II

processor

APIC

Controller

PXB #1

PCI

Expander

Bridge

Optional

Cluster

Bridge

PXB #0

PCI

Expander

Bridge

USB

Xeon

Xeon

Xeon

Xeon

L2

Cache

L2

Cache

L2

Cache

L2

Cache

1 or 2 cards

Can link pairs into 64-bit bus

0A

0B

1A

1B

USB

Subsystem

X0

X1

Expander

Buses

third-party

controls

1-2

Intel

Æ

450NX PCIset

1. Introduction

Bus. Each PXB provides two independent 32-bit, 33 MHz PCI buses, with an option to link the

two buses into a single 64-bit, 33 MHz bus. The Intel 450NX PCIset memory subsystem

supports one or two memory cards. Each card is comprised of an RCG, a DRAM array, and

two MUXs. The MIOC issues requests to the RCG components on each card to generate RAS#,

CAS#, and WE# outputs to the DRAMs. The MUX components provide the datapath for the

DRAM arrays. Up to 8 GB of memory in various configurations are supported.

Other capabilities of the Intel 450NX PCIset include:

∑

Full Pentium II Xeon processor bus interface (36-bit address, 64-bit data) at 100 MHz.

∑

Support for two dedicated PCI expander bridges (PXBs) attached behind the system bus so

as not to add additional electrical load to the system bus.

∑

Support for both internal and external system bus and I/O bus arbitration.

Supporting Devices

The Intel 450NX PCIset is designed to support the PIIX4E south bridge. The PIIX4E is a highly

integrated multi-functional component that supports the following capabilities:

∑

PCI Rev 2.1-compliant PCI-to-ISA Bridge with support for 33-MHz PCI operations

∑

Enhanced DMA controller

∑

8259 Compatible Programmable Interrupt Controller

∑

System Timer functions

∑

Integrated IDE controller with Ultra DMA/33 support

1.2

IntelÆ 450NX PCIset Components

MIOC

Memory and I/O Bridge Controller

The MIOC accepts access requests from the system bus and directs those accesses to

memory or one of the PCI buses. The MIOC also accepts inbound requests from the

PCI buses. The MIOC provides the data port and buffering for data transferred

between the system bus, PXBs and memory. In addition, the MIOC generates the

appropriate controls to the RCG and MUX components to control data transfer to and

from the memory.

PXB

PCI Expander Bridge

The PXB provides the interface to two independent 32-bit, 33 MHz Rev 2.1-compliant

PCI buses. The PXB is both a master and target on each PCI bus.

RCG

RAS/CAS Generator

The RCG is responsible for accepting memory requests from the MIOC and

converting these into the specific signals and timings required by the DRAM. Each

RCG controls up to four banks of memory.

MUX

Data Path Multiplexor.

The MUX provides the multiplexing and staging required to support memory

interleaving between the DRAMs and the MIOC. Each MUX provides the data path

for one-half of a Qword for each of four interleaves.

Intel

Æ

450NX PCIset

1-3

1.3 IntelÆ 450NX PCIset Feature Summary

1.3

IntelÆ 450NX PCIset Feature Summary

System Bus Support

∑

Fully supports the PentiumÆ II XeonTM processor bus protocol at bus frequencies up to

100 MHz.

∑

Functionally and electrically compatible with the original and PentiumÆ II P6 family

processor buses.

∑

Fully supports 4-way multiprocessing, with performance scaling to 3.5x that of a uni-

processor system.

∑

Full 36-bit address decode and drive capability.

∑

Full 64-bit data bus (32-bit data bus mode is not supported).

∑

Parity protection on address and control signals, ECC protection on data signals.

∑

8-deep in-order queue; 24-deep memory request queue; 2-deep outbound read-request

queue per PCI bus; 6-deep outbound write-posting queue per PCI bus.

∑

AGTL+ bus driver technology.

∑

Intel 450NX PCIset adds only one load to the system bus.

∑

Intel 450GX PCIset-compatible third-party request/grant and control signals, allowing

cluster bridges to be placed on the system bus.

DRAM Interface Support

∑

Memory technologies supported are 16- and 64-Mbit, 60nsec and 50nsec 3.3v EDO DRAM

devices.

∑

Supports from 32 MB to 8 GB of memory, in 64 MB increments after the initial 32 MB.

∑

Supports 4-way interleaved operation, with 2-way interleave supported in the first bank

of card 0 to permit entry-level systems with minimal memory.

∑

Supports memory address bit permuting (ABP) to obtain alternate row selection bits.

∑

Supports card-to-card interleaving to further distribute memory accesses across multiple

banks of memory.

∑

Staggered CAS-before-RAS refresh.

∑

ECC with single-bit error correction and scrub-on-error in the memory.

∑

Extensive Host-to-Memory and PCI-to-Memory write data buffering.

I/O Bridge Support

∑

Up to four independent 32-bit PCI ports (using two PXBs)

≠

each supports up to 10 electrical loads (connectors count as loads).

≠

each provides internal arbitration for up to 6 masters plus a south bridge on the

compatibility PCI bus, or external arbitration.

∑

Synchronous operation to the system bus clock using a 3:1 system bus/PCI bus gearing

ratio.

≠

3:1 ratio supports a 100 MHz system bus and 33.33 MHz PCI bus.

≠

3:1 ratio supports a 90 MHz system bus and 30 MHz PCI bus (or lower, depending on

effect of 6th load).

∑

Parity protection on all PCI signals.

∑

Inbound read prefetches of up to 4 cache lines.

∑

Outbound write assembly of full/partial line writes.

∑

Data streaming support from PCI to DRAM.

1-4

Intel

Æ

450NX PCIset

1. Introduction

System Management Features

∑

Provides controlled access to the Intel Architecture System Management Mode (SMM)

memory space (SM RAM).

Test & Tuning Features

∑

Signal interconnectivity testing via boundary scan.

∑

Access to internal control and status registers via JTAG TAP port.

I2C access is not provided in the PCIset; however, error indicators are reported to pins

which can be monitored and sampled using I2C capabilities if provided elsewhere in the

system.

∑

System bus, memory and I/O performance counters with programmable events.

Reliability/Availability/Serviceability (RAS) Features

∑

ECC coverage of system data bus and memory; parity coverage of system bus controls,

PCI bus, and Expander bus.

∑

ECC bits can be corrupted via selective masking for diagnostics.

∑

Fault recording of the first two ECC errors. Each includes error type and syndrome.

Memory ECC error logs include the effective address, allowing identification of the failing

location. Error logs are not affected by reset, allowing recovery software to examine the

logs.

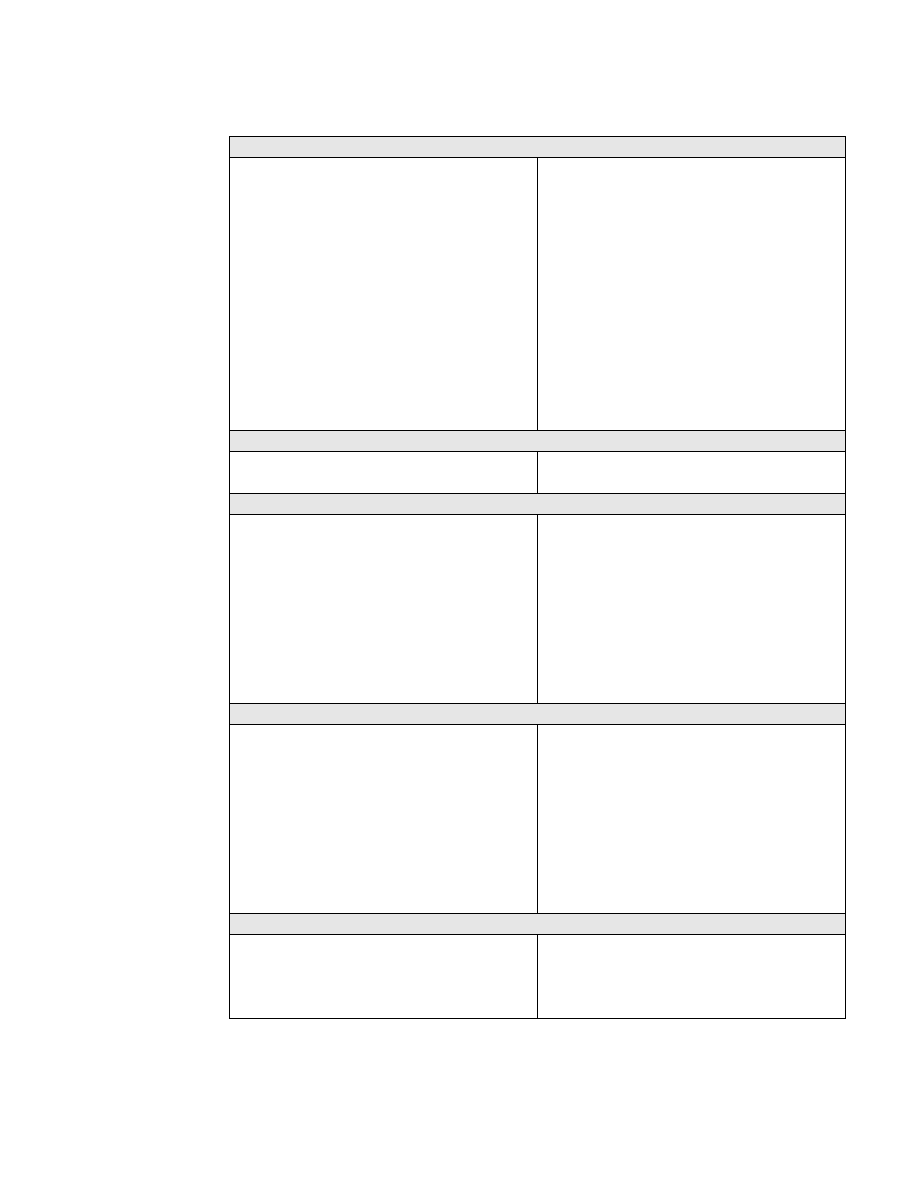

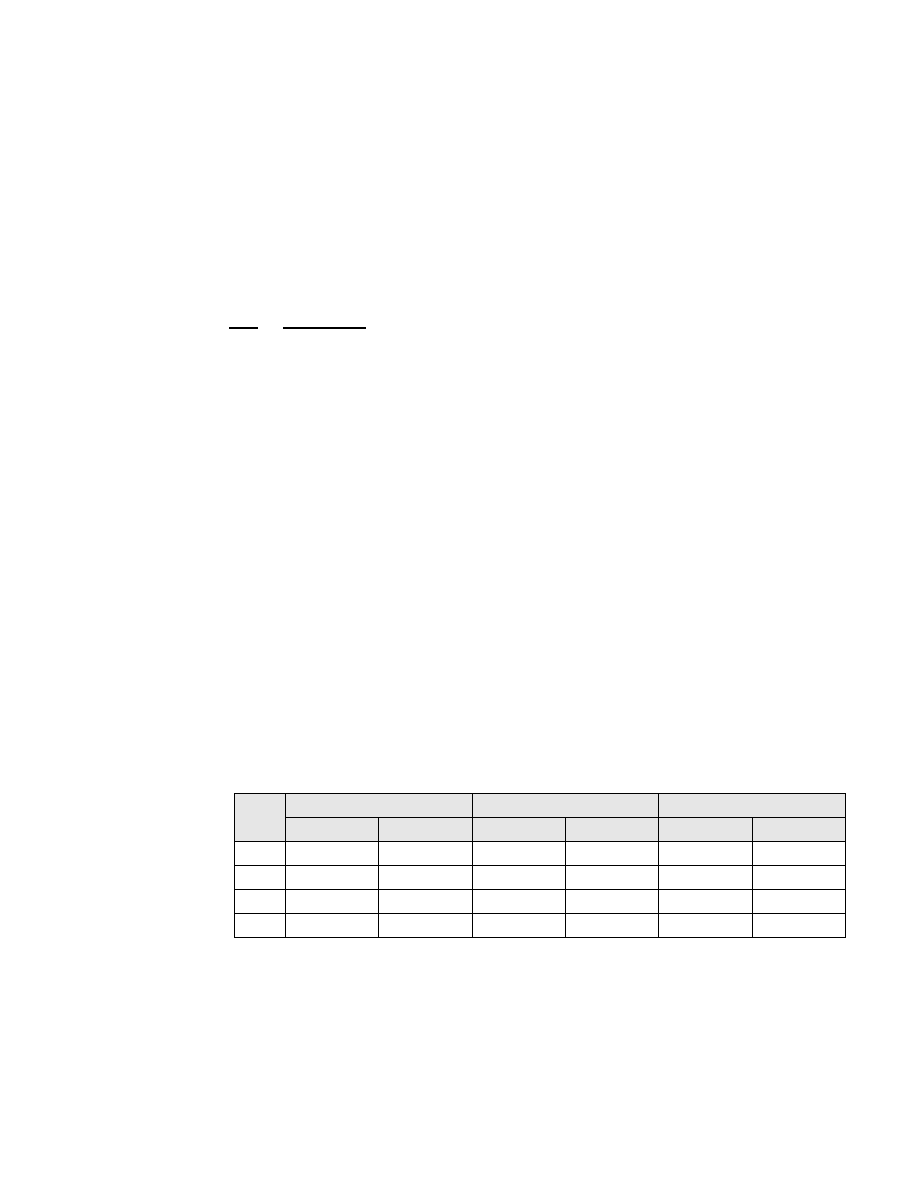

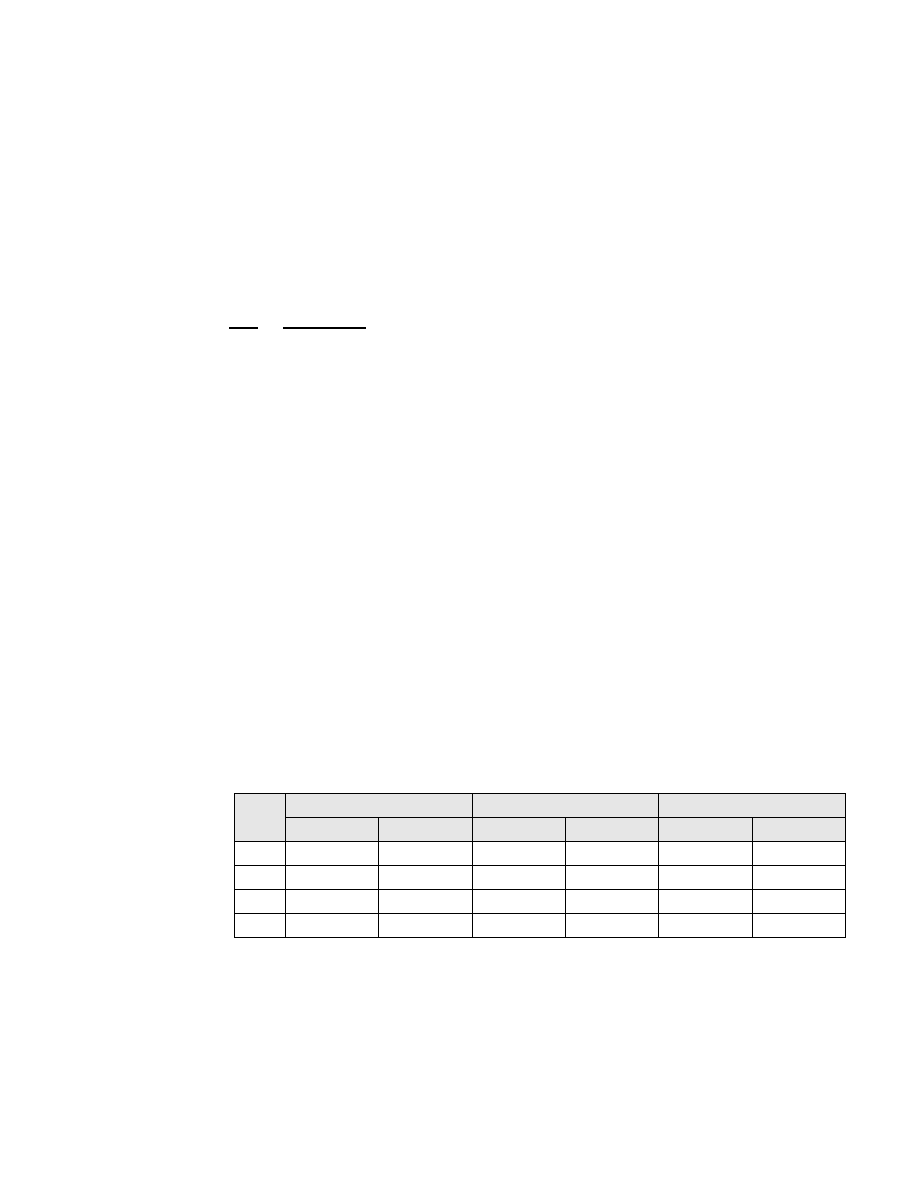

1.4

Packaging & Power

∑

Table 1-1 indicates the signal count, package and power for each component in the Intel

450NX PCIset. In a common high-end configuration, using two memory cards (each with

one RCG and two MUX components), two PXBs and 3.3V supplies, the Intel 450NX PCIset

would contribute approximately 47 watts.

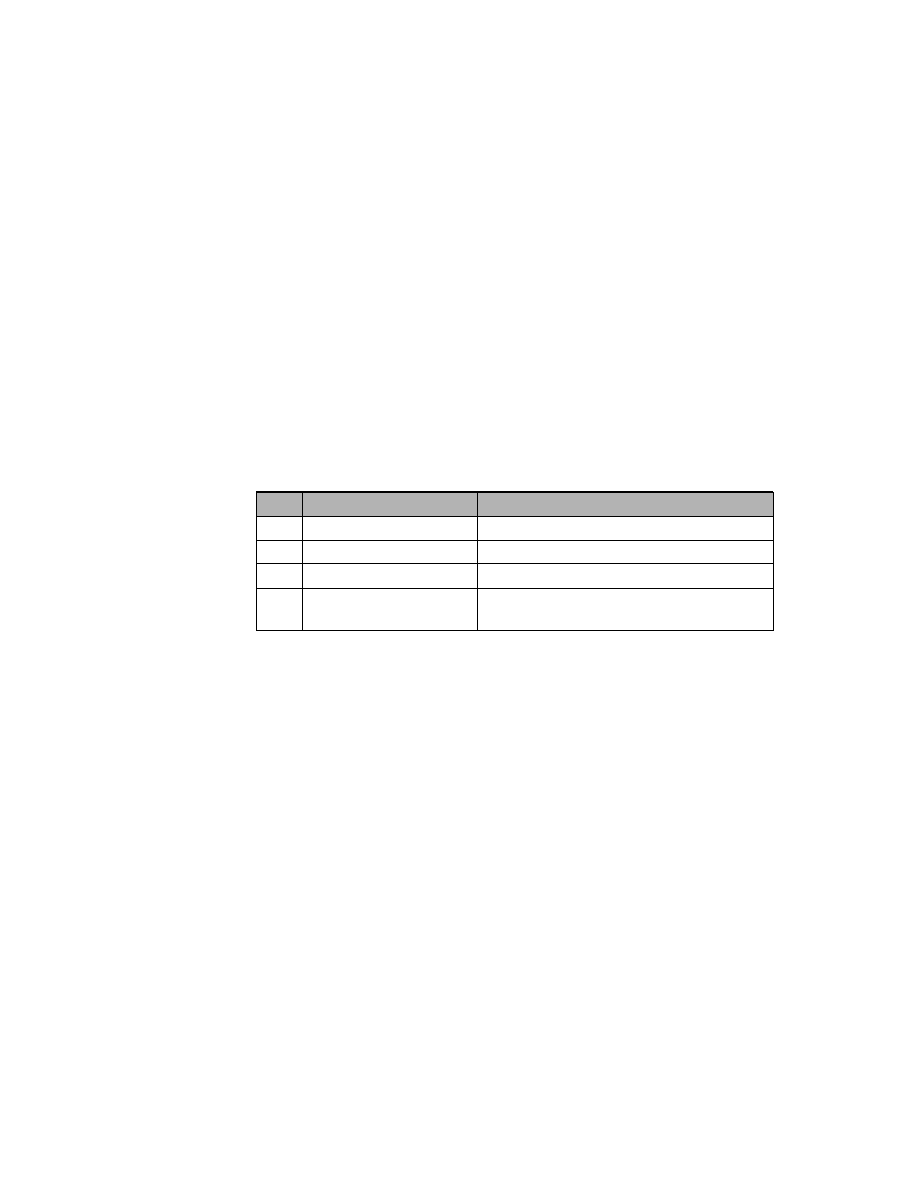

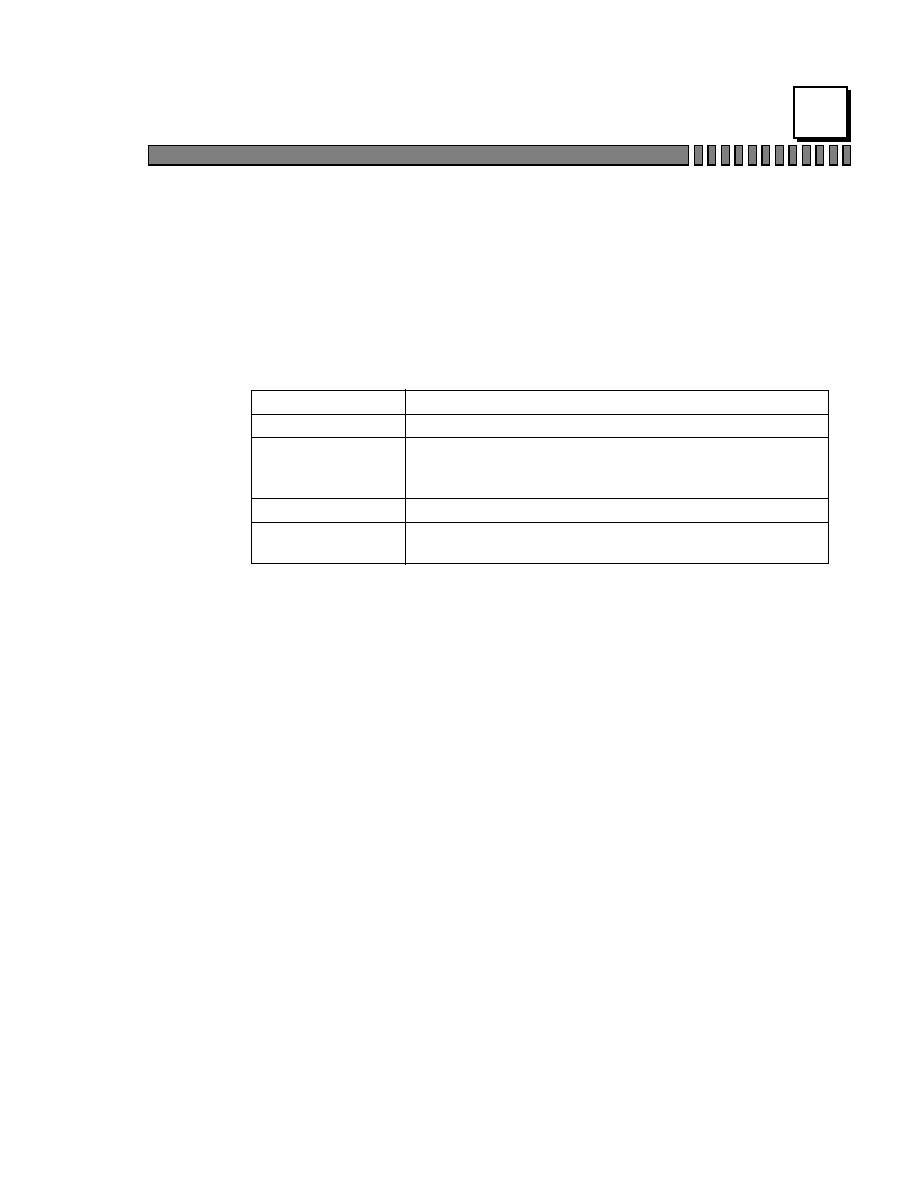

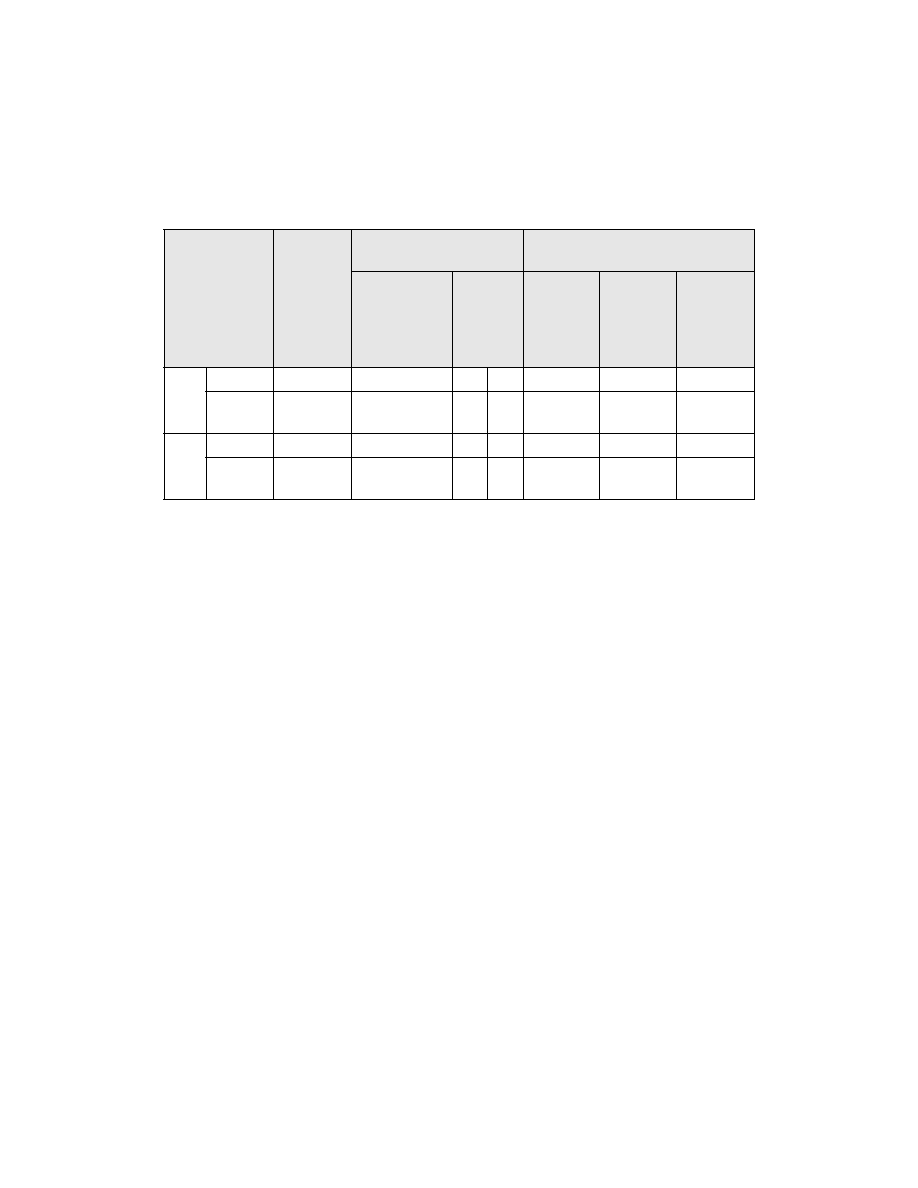

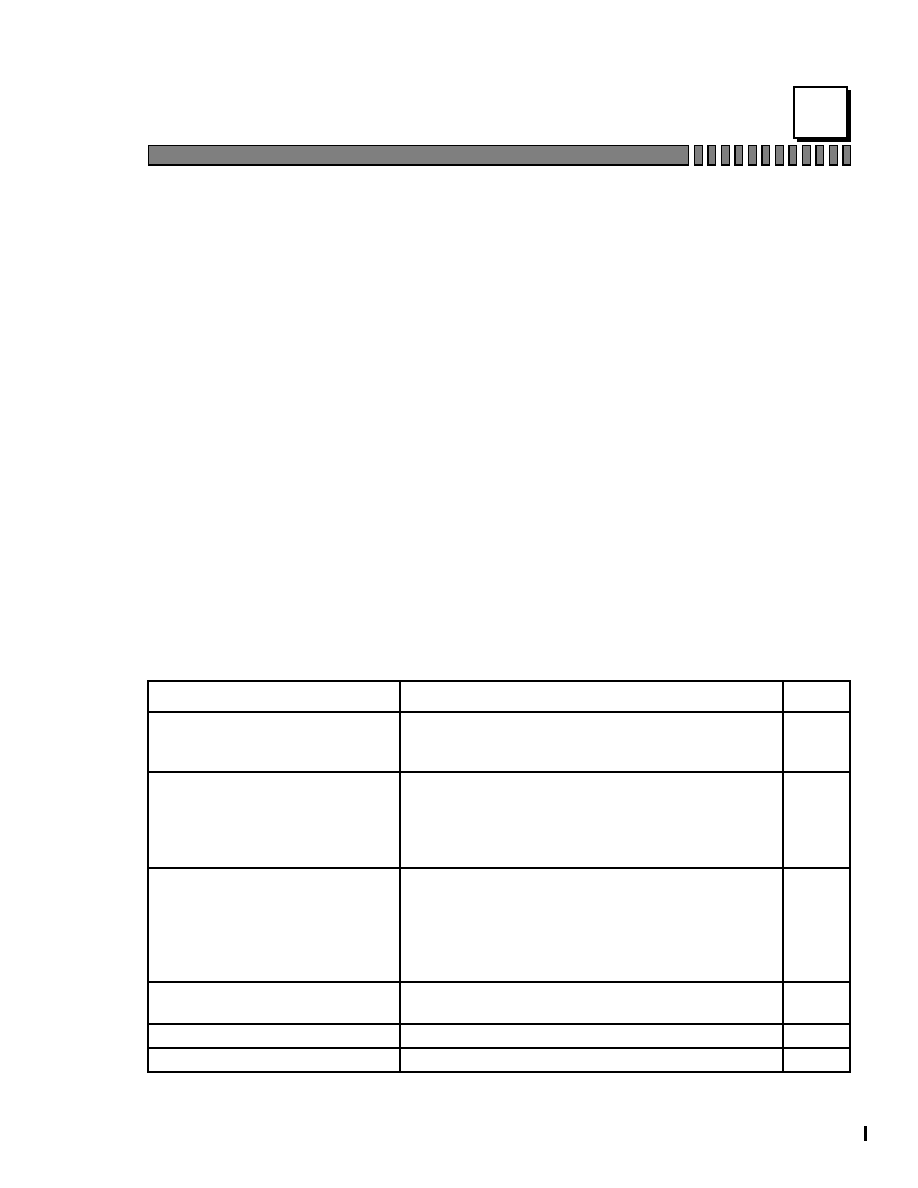

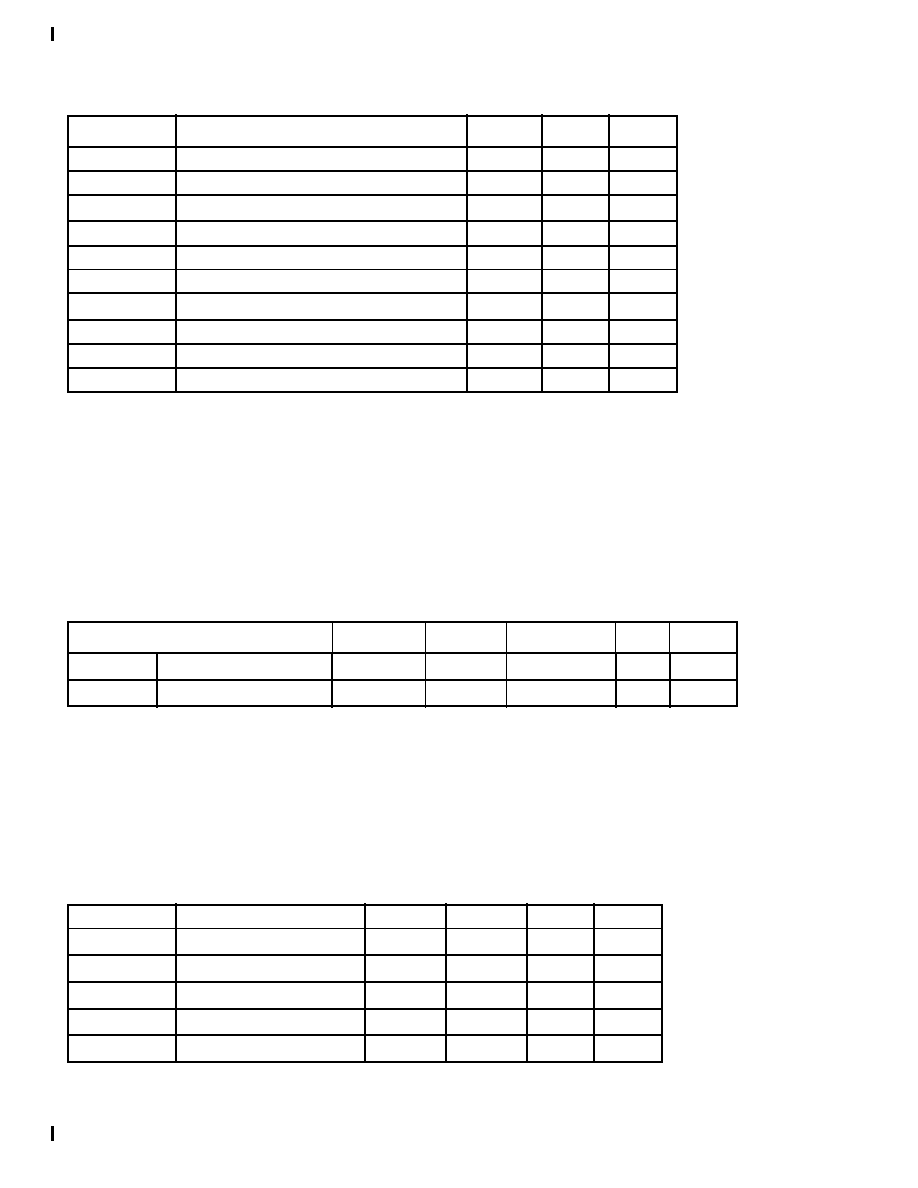

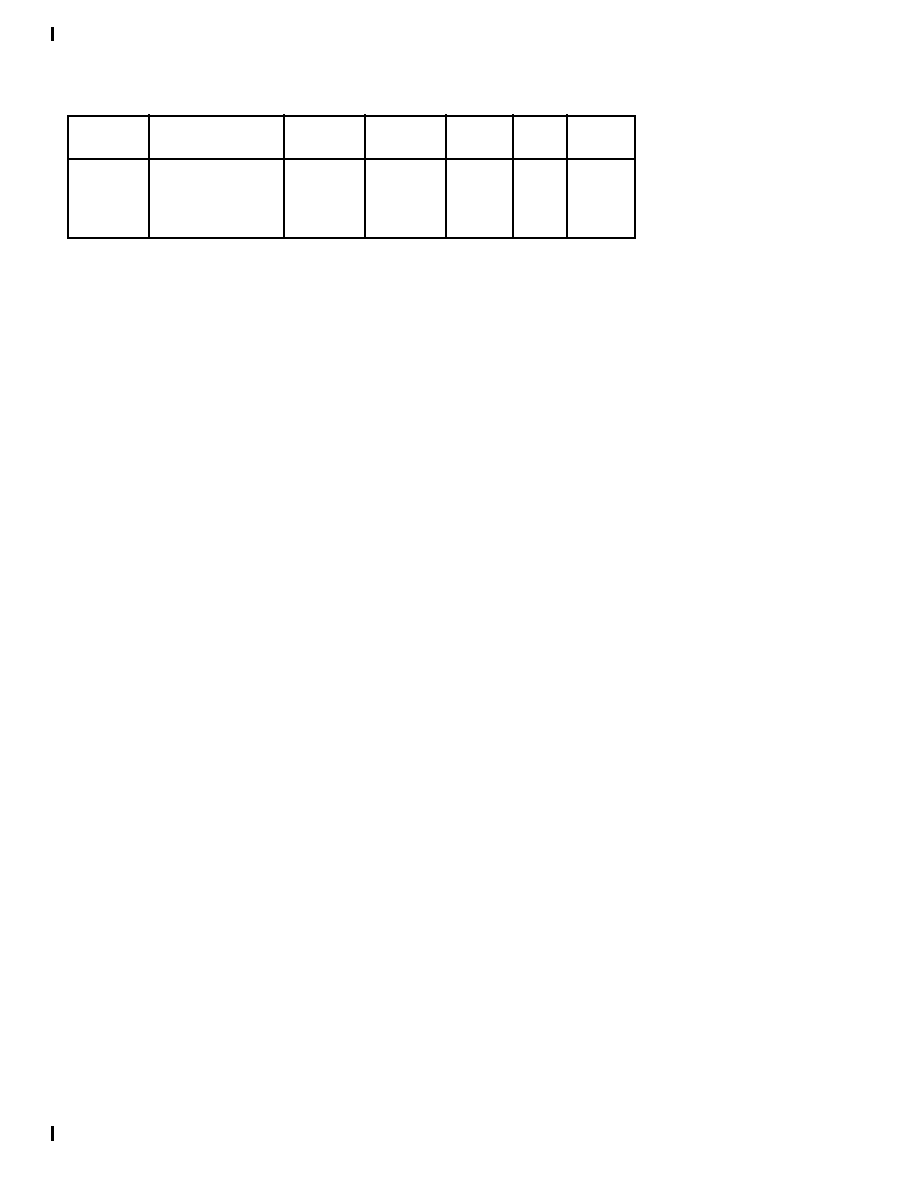

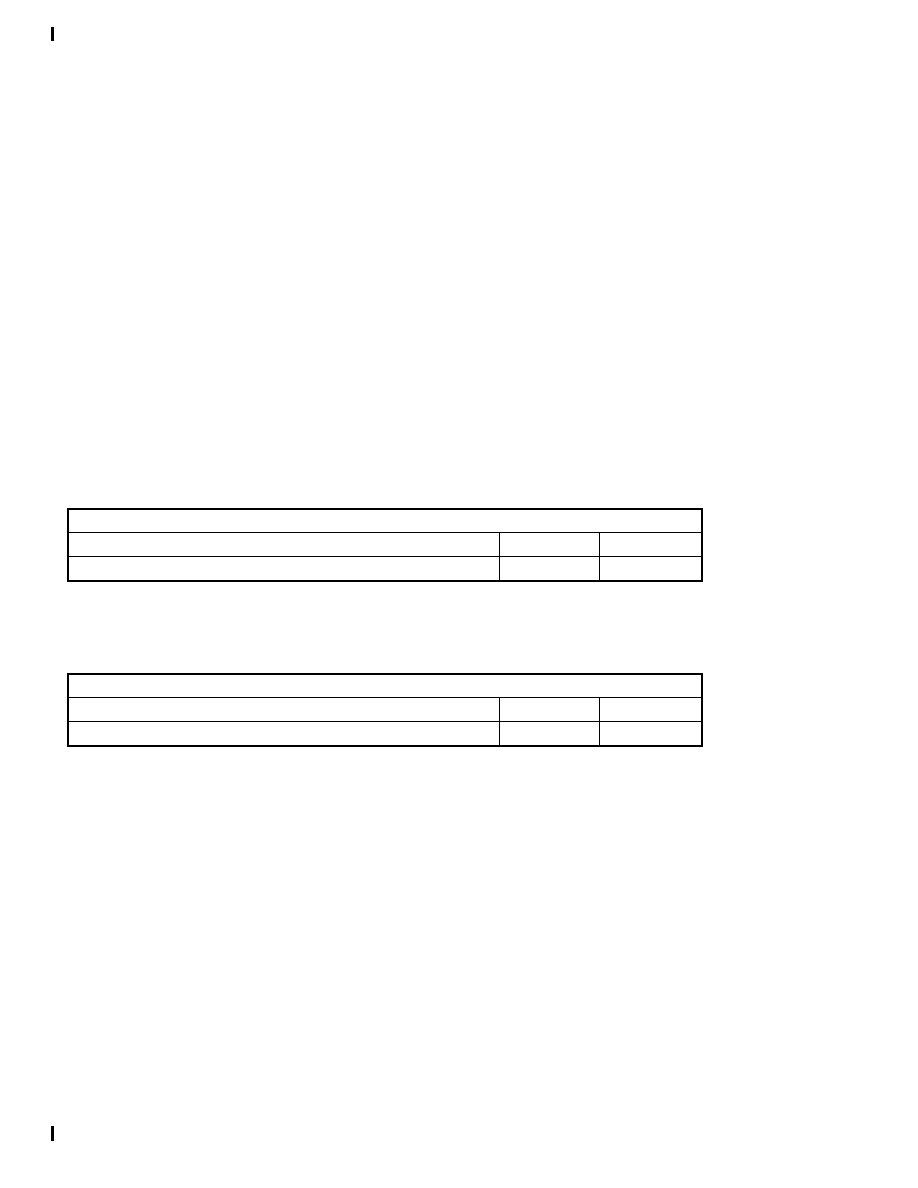

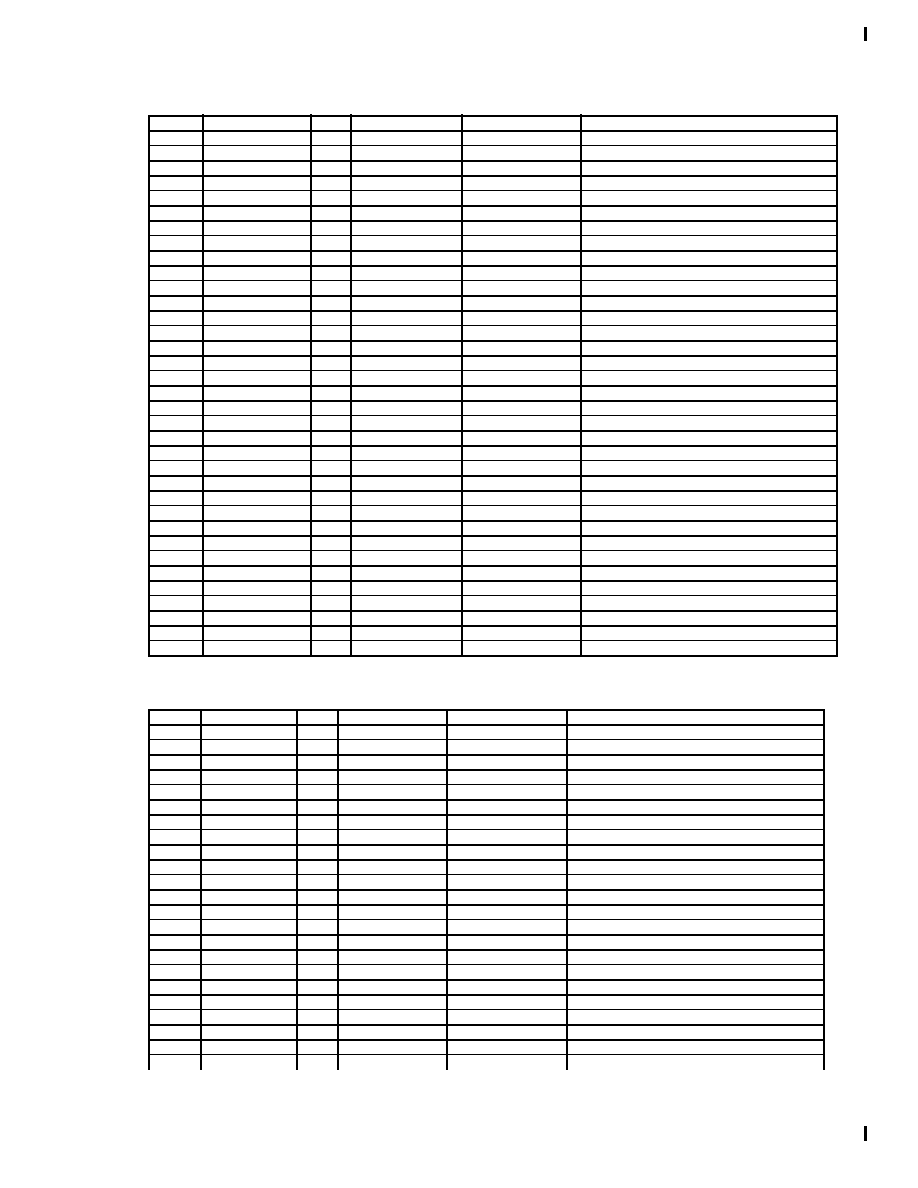

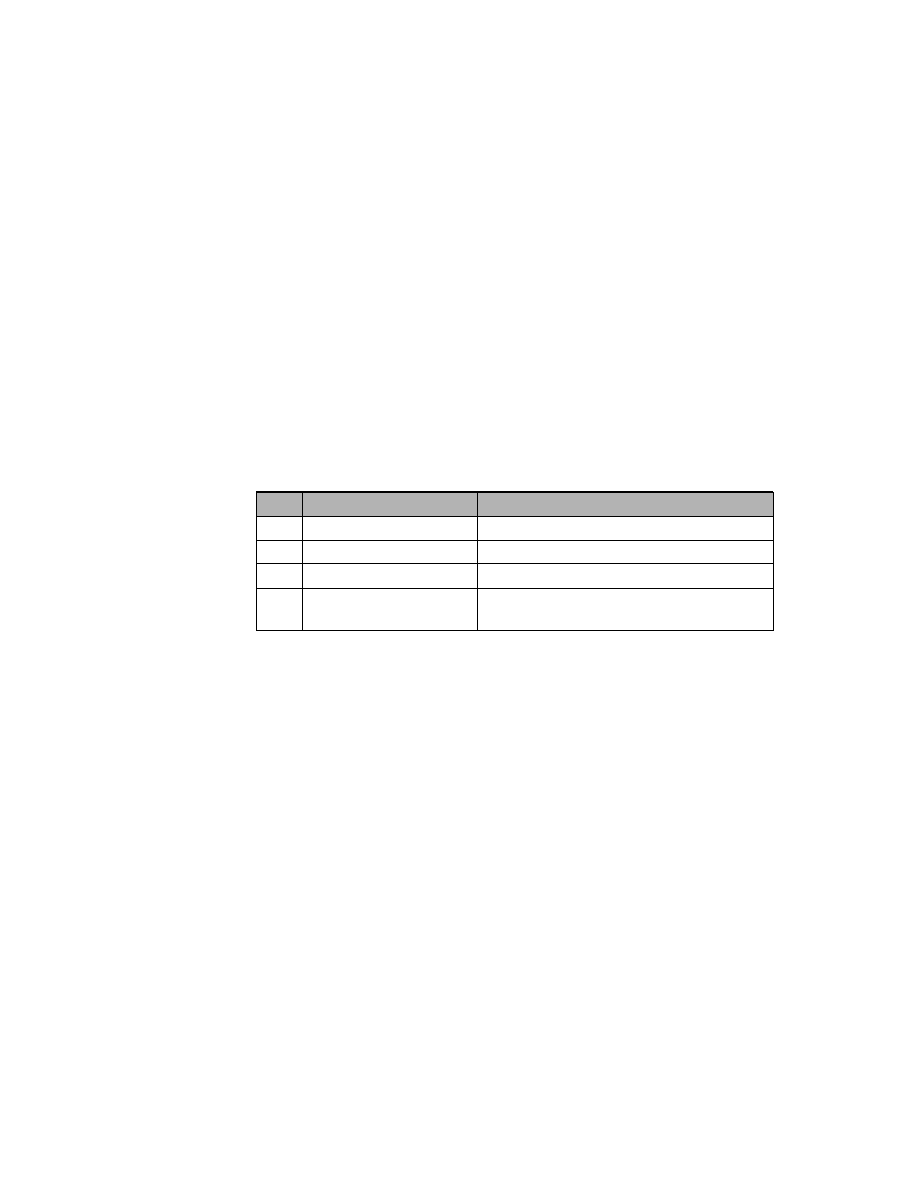

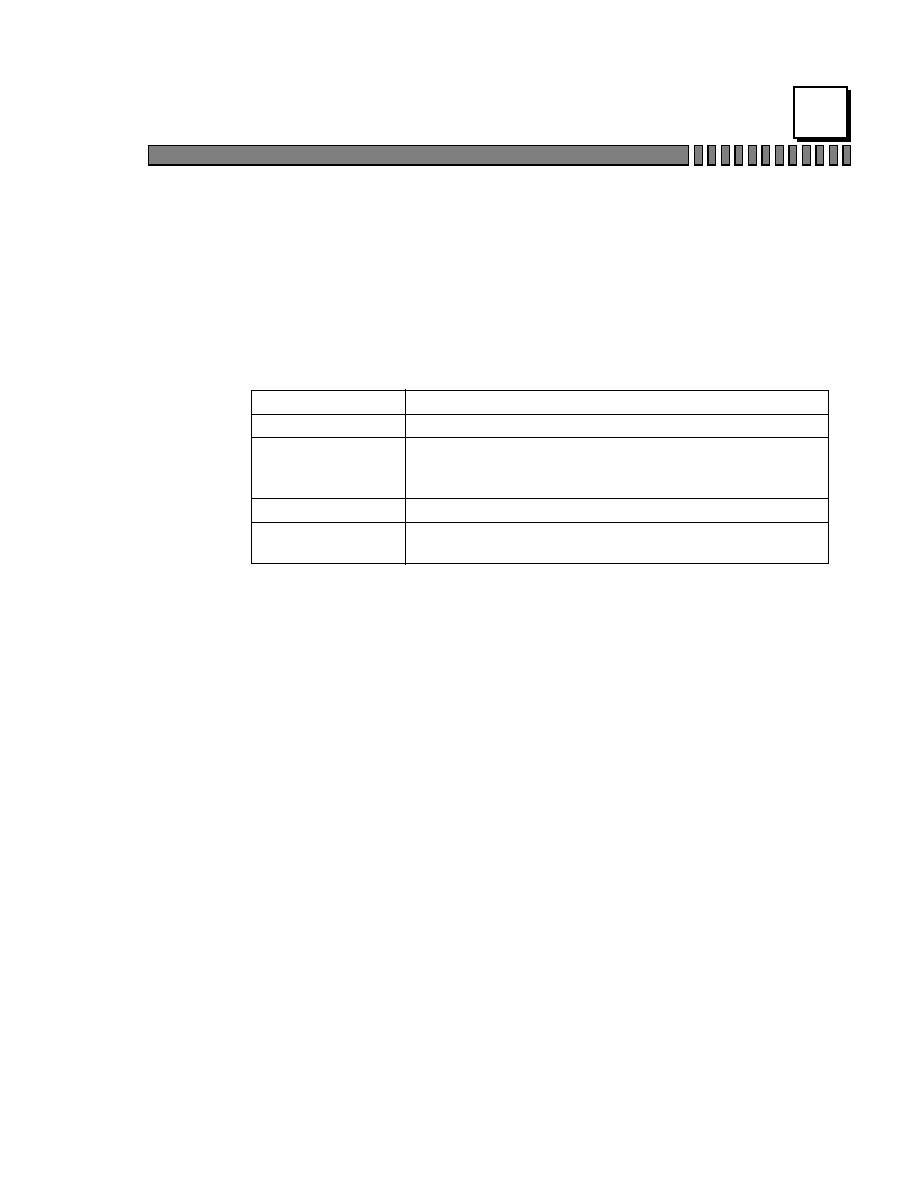

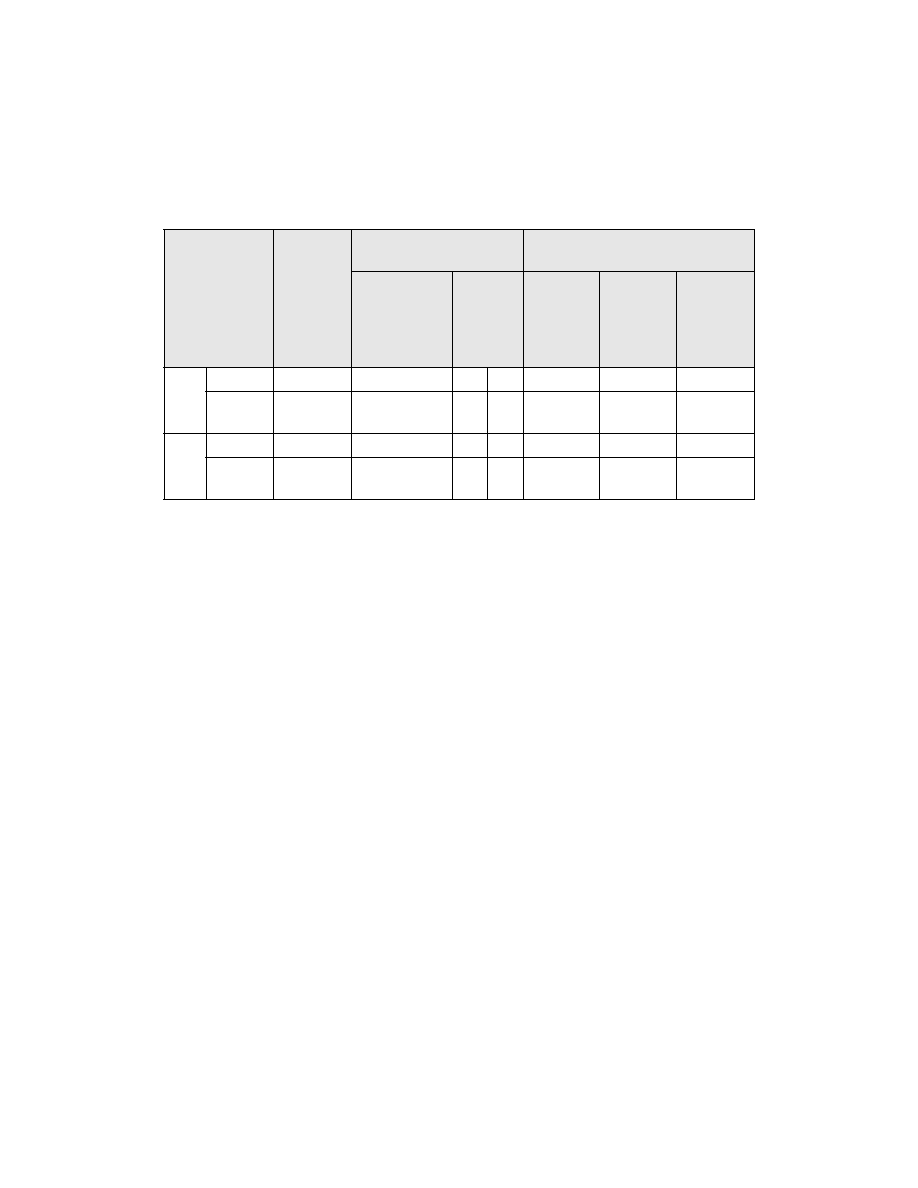

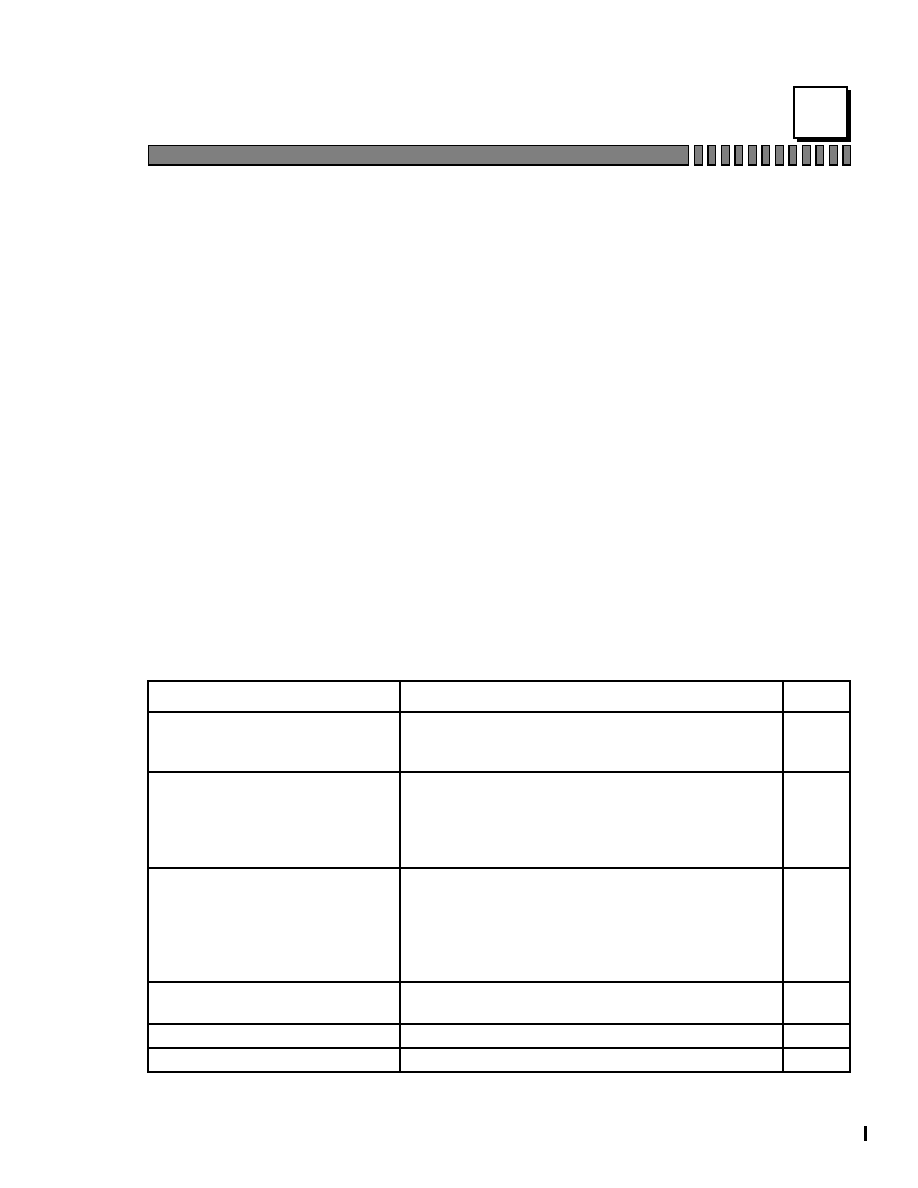

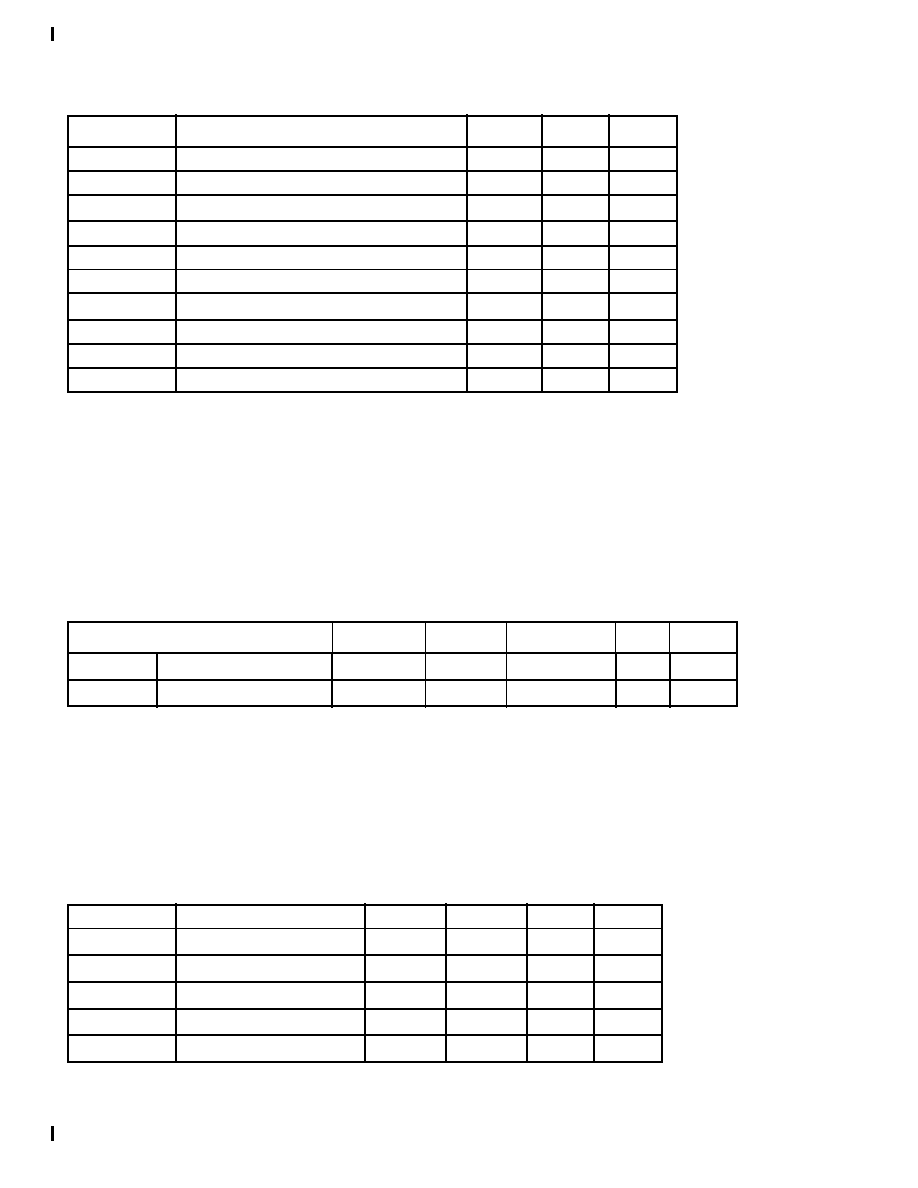

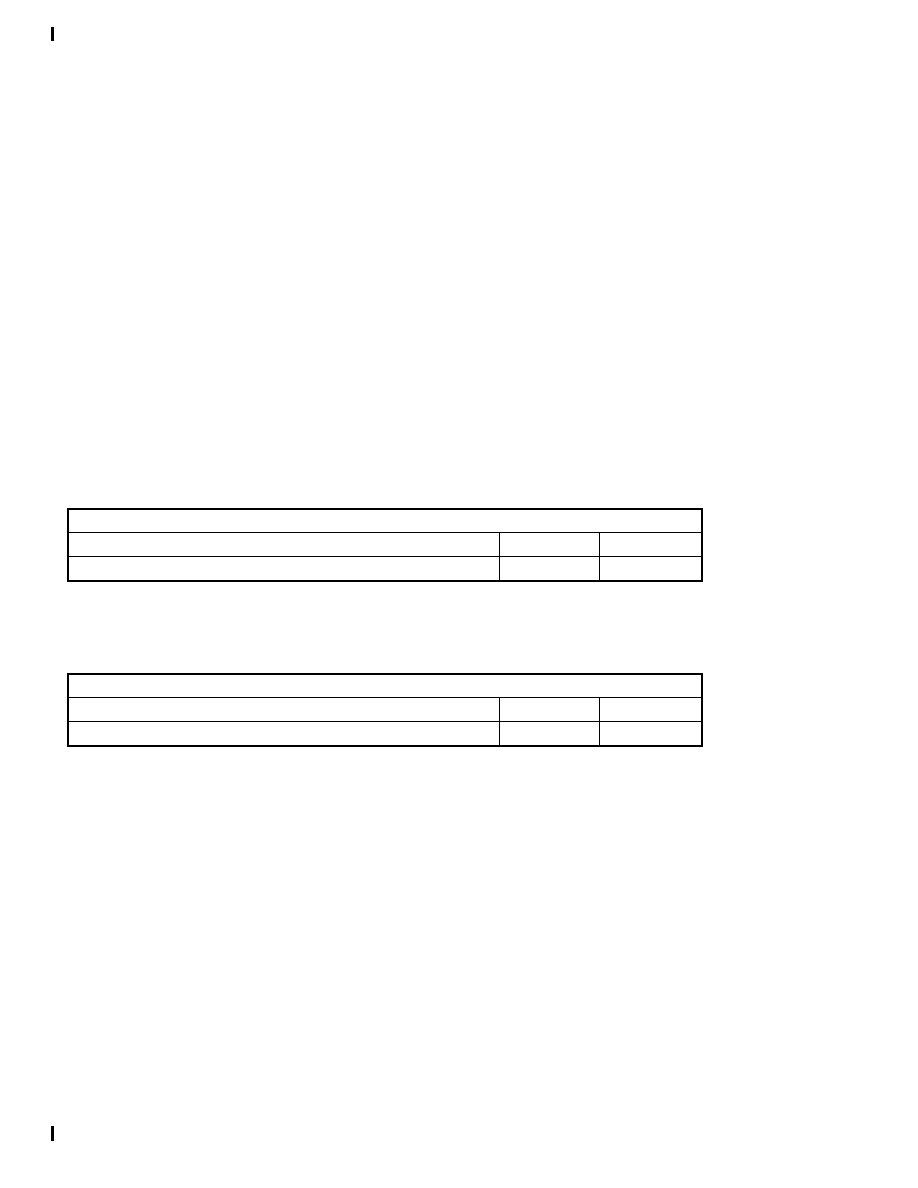

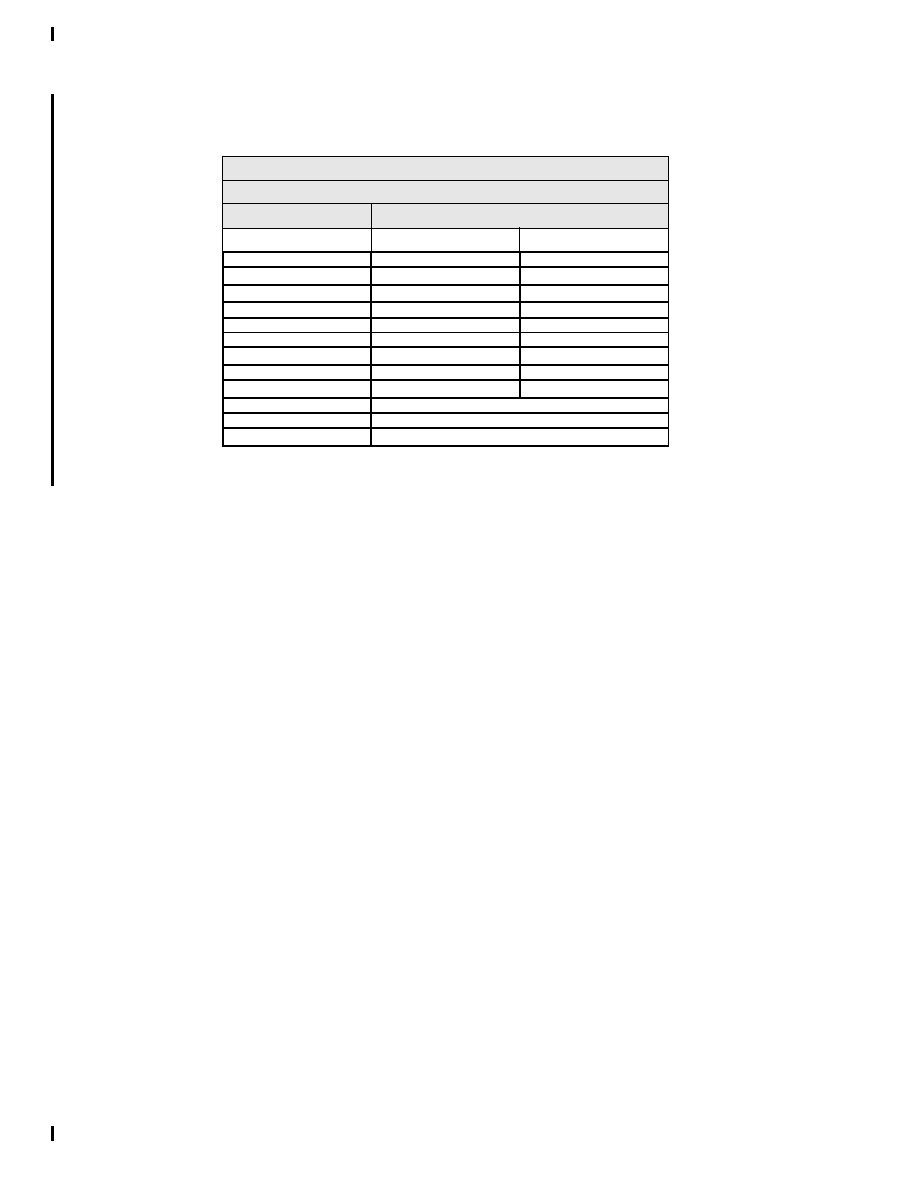

Table 1-1: Signals, Pins, Packaging and Power

Chip

Signals

Package

Footprint

Power

1

MIOC

348

PLGA-540

2

42.5 mm

13.2 W

PXB

177

PLGA-540

2

42.5 mm

7.8 W

RCG

173

BGA-324

27.0 mm

2.5 W

MUX

207

BGA-324

27.0 mm

3.3 W

1. Assumes 3.3v supplies.

2. Requires heat sink.

Intel

Æ

450NX PCIset

2-1

2

Signal Descriptions

This chapter provides a detailed description of all signals used in any component in the IntelÆ

450NX PCIset.

2.1

Conventions

The terms assertion and deassertion are used extensively when describing signals, to avoid

confusion when working with a mix of active-high and active-low signals. The term assert, or

assertion, indicates that the signal is active, independent of whether the active level is

represented by a high or low voltage. The term deassert, or deassertion, indicates that the signal

is inactive.

The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs

when the signal is at a low voltage level. When "#" is not present after the signal name the

signal is asserted when at the high voltage level.

When discussing data values used inside the chip set, the logical value is used; i.e., a data

value described as "

1101b

" would appear as "

1101b

" on an active-high bus, and as "

0010b

" on

an active-low bus. When discussing the assertion of a value on the actual pin, the physical

value is used; i.e., asserting an active-low signal produces a "0" value on the pin.

The following notations are used to describe the signal type:

The signal description also includes the type of buffer used for the particular signal:

I

Input pin

O

Output pin

I/O

Bidirectional (input/output) pin

OD

Open drain output pin (other than AGTL+ signals)

AGTL+

Open drain AGTL+ interface.

PCI

PCI-compliant 3.3v/5v-tolerant interface

LVTTL

Low-voltage (3.3v) TTL-compatible signals.

2.5V

2.5v CMOS signals.

Analog

Typically a voltage reference or specialty power supply.

2-2

Intel

Æ

450NX PCIset

2. Signal Descriptions

Some signals or groups of signals have multiple versions. These signal groups may represent

distinct but similar ports or interfaces, or may represent identical copies of the signal used to

reduce loading effects. The following conventions are used:

Typically, upper case groups (e.g., "

(A,B,C)

") represent functionally similar but logically

distinct signals; each signal provides an independent control, and may or may not be asserted

at the same time as the other signals in the grouping. In contrast, lower case groups (e.g.,

"

(a,b,c)

") typically represent identical duplicates of a common signal provided to reduce

loading.

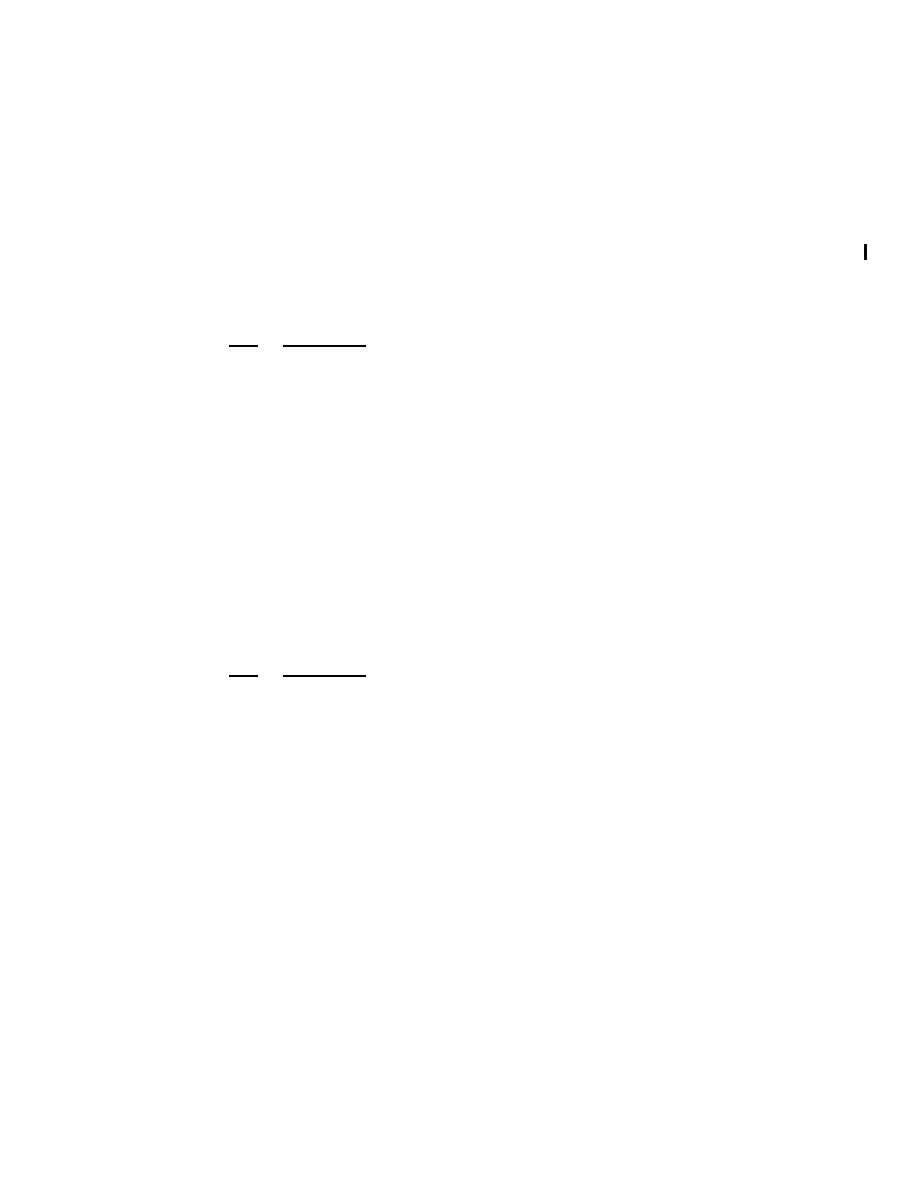

2.2

Summary

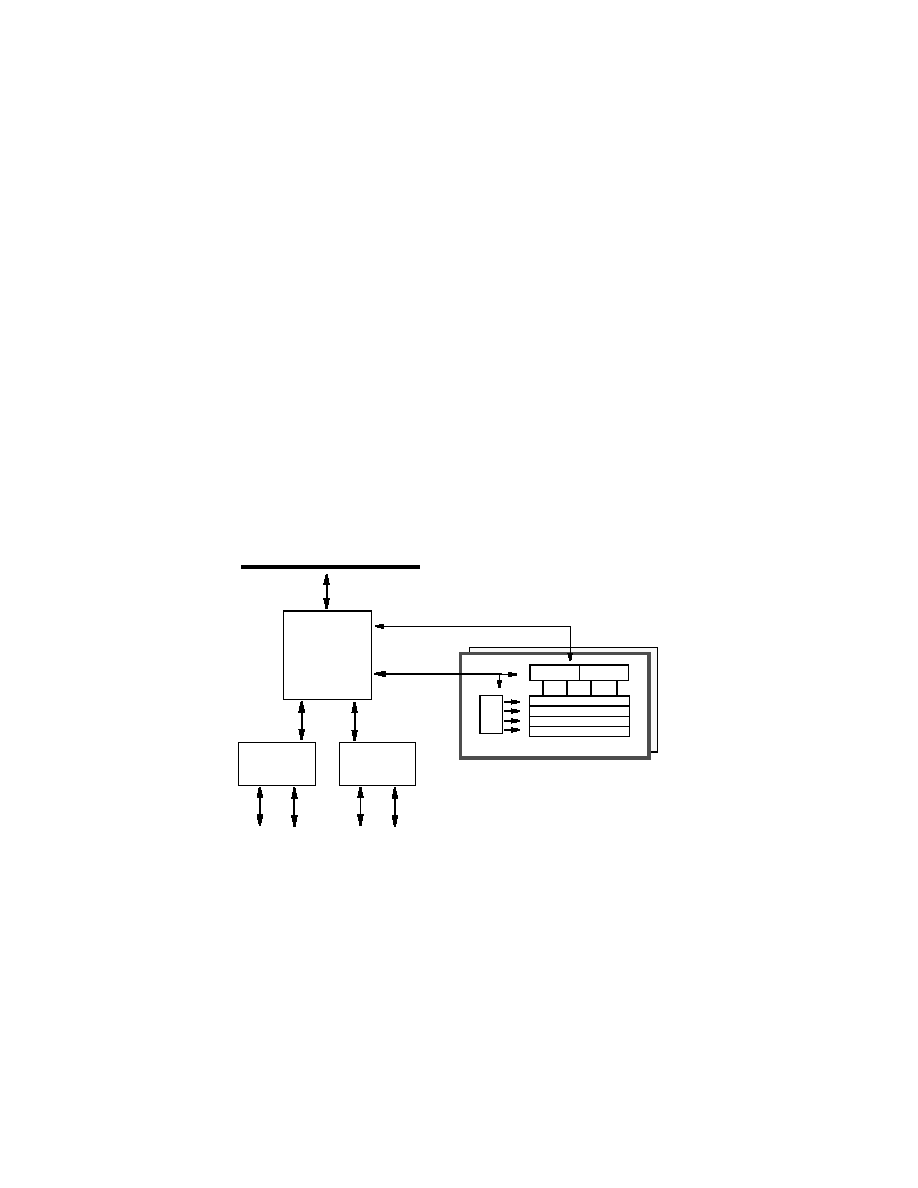

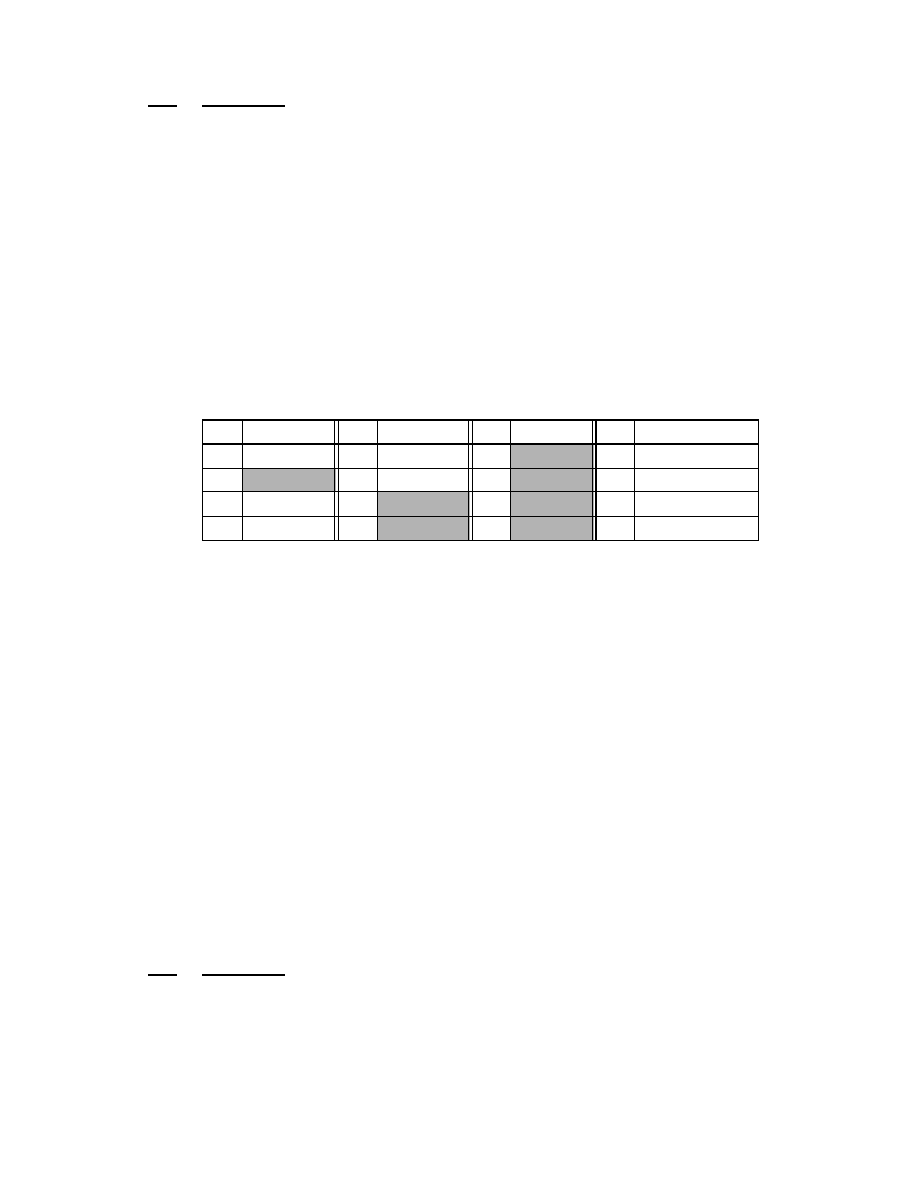

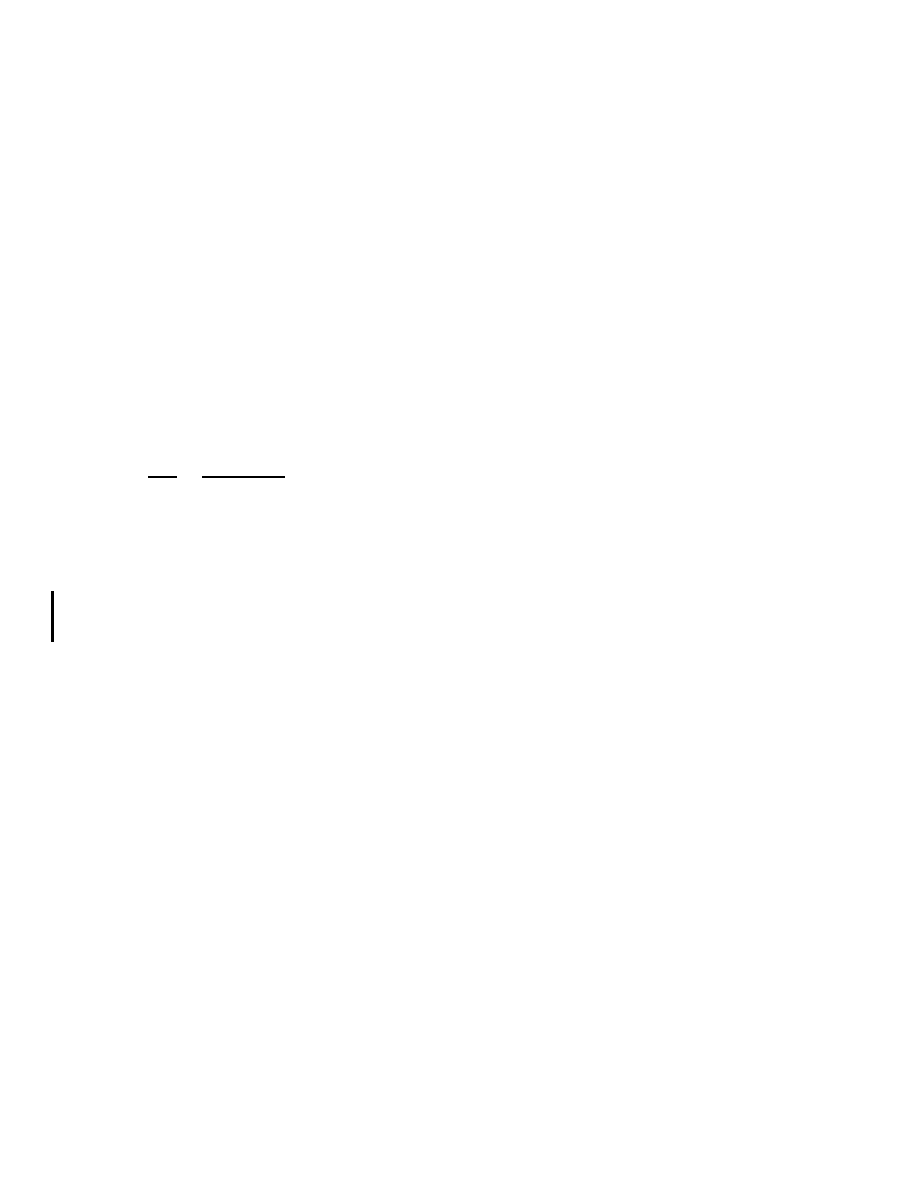

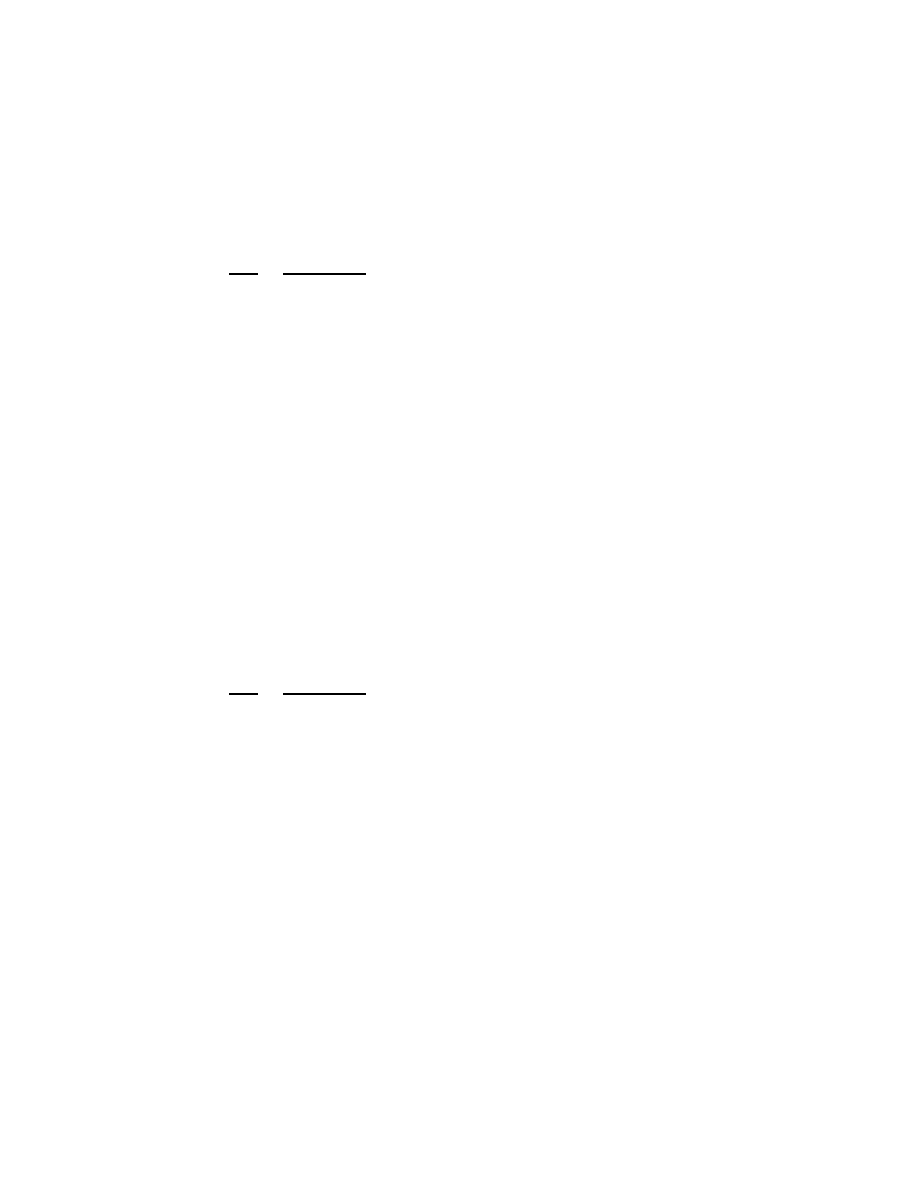

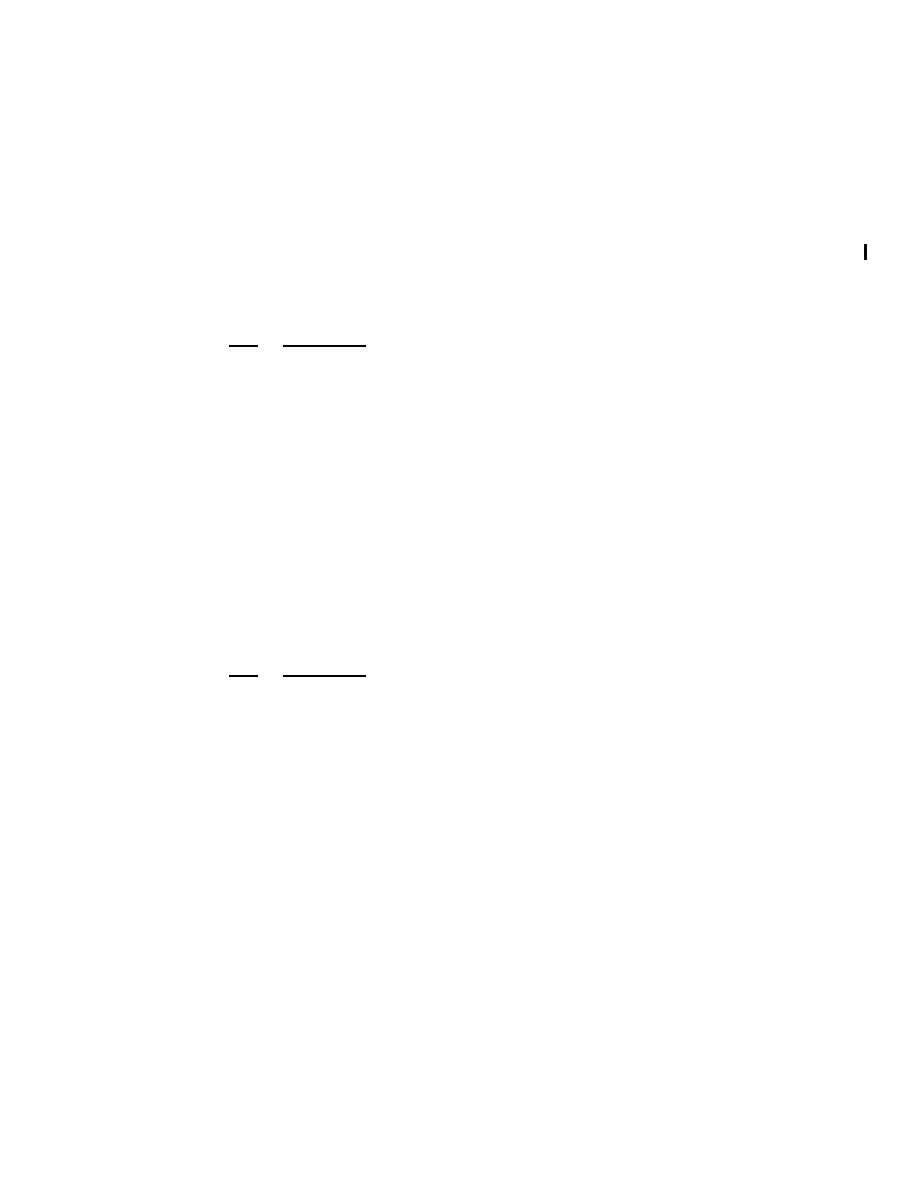

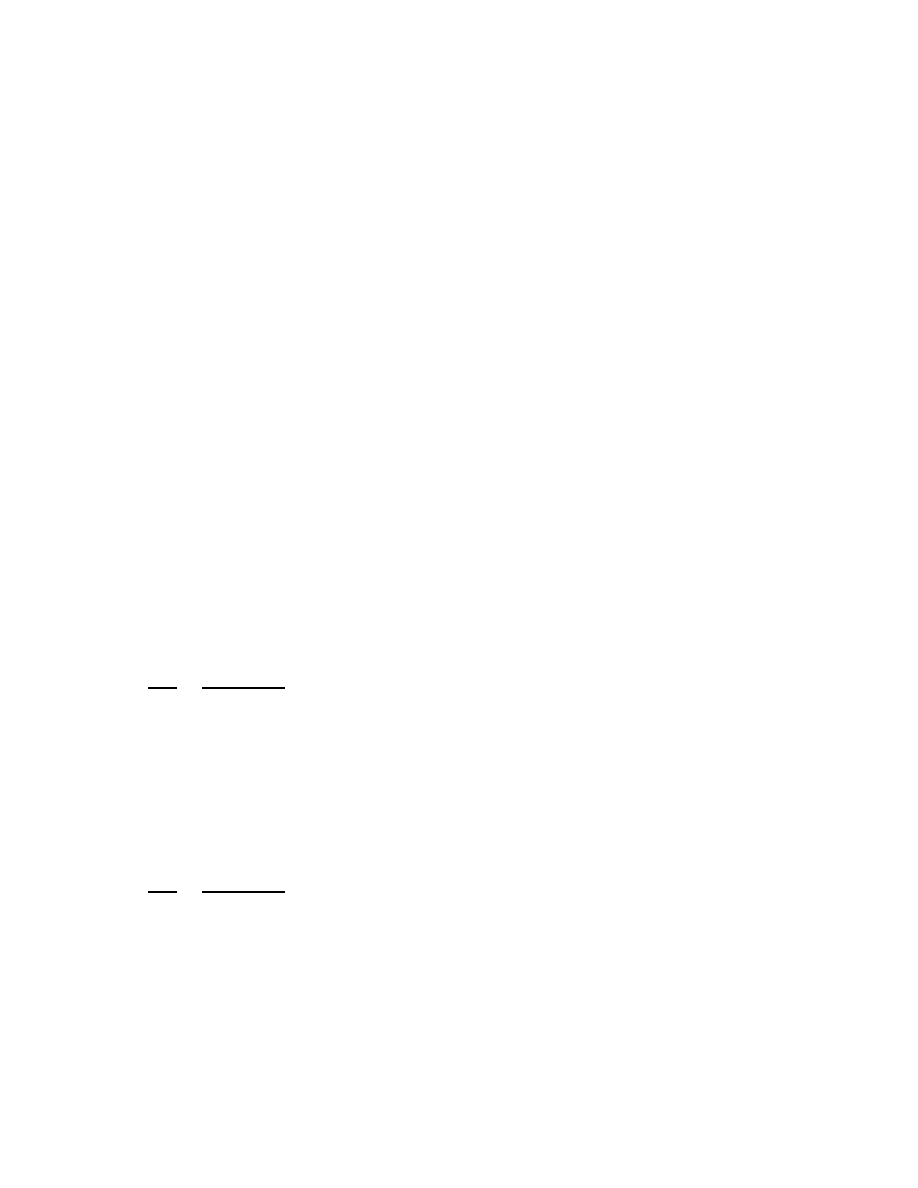

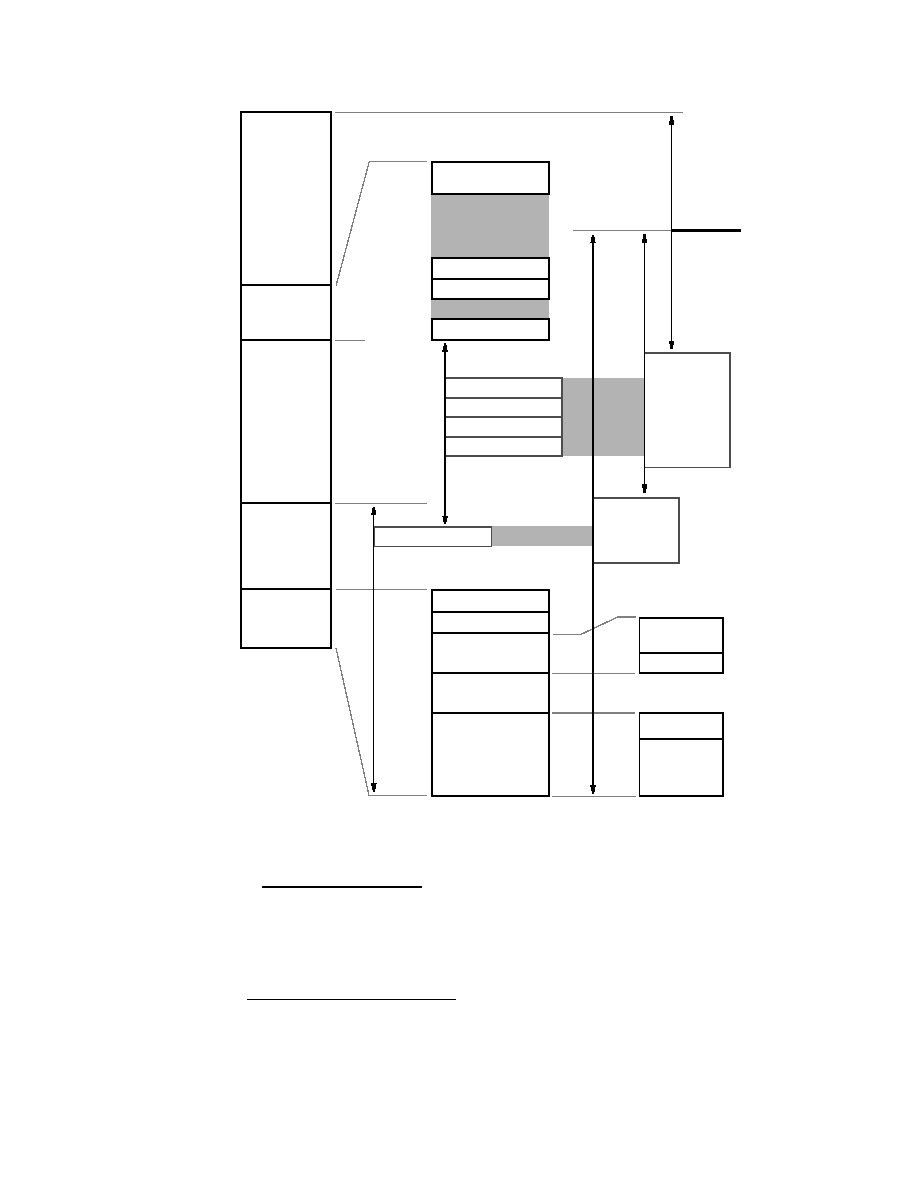

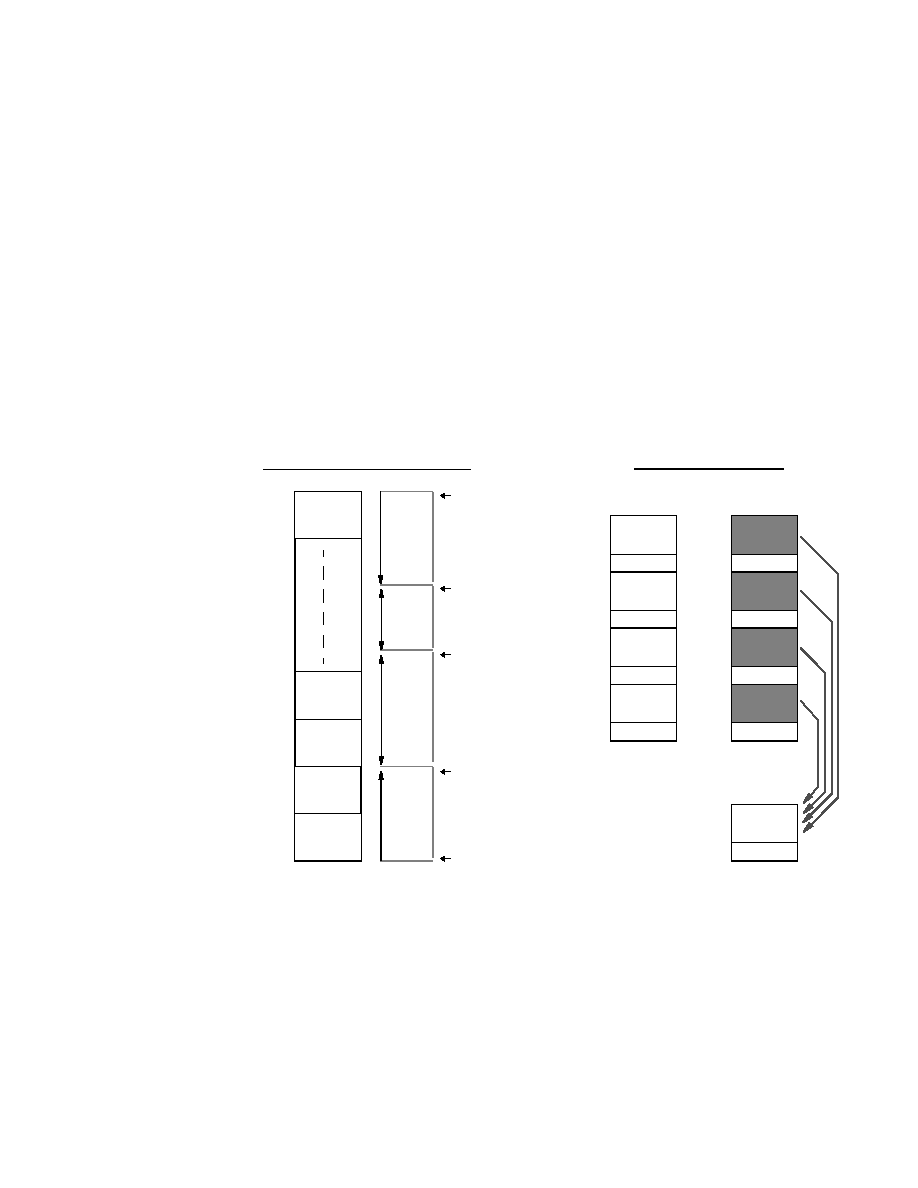

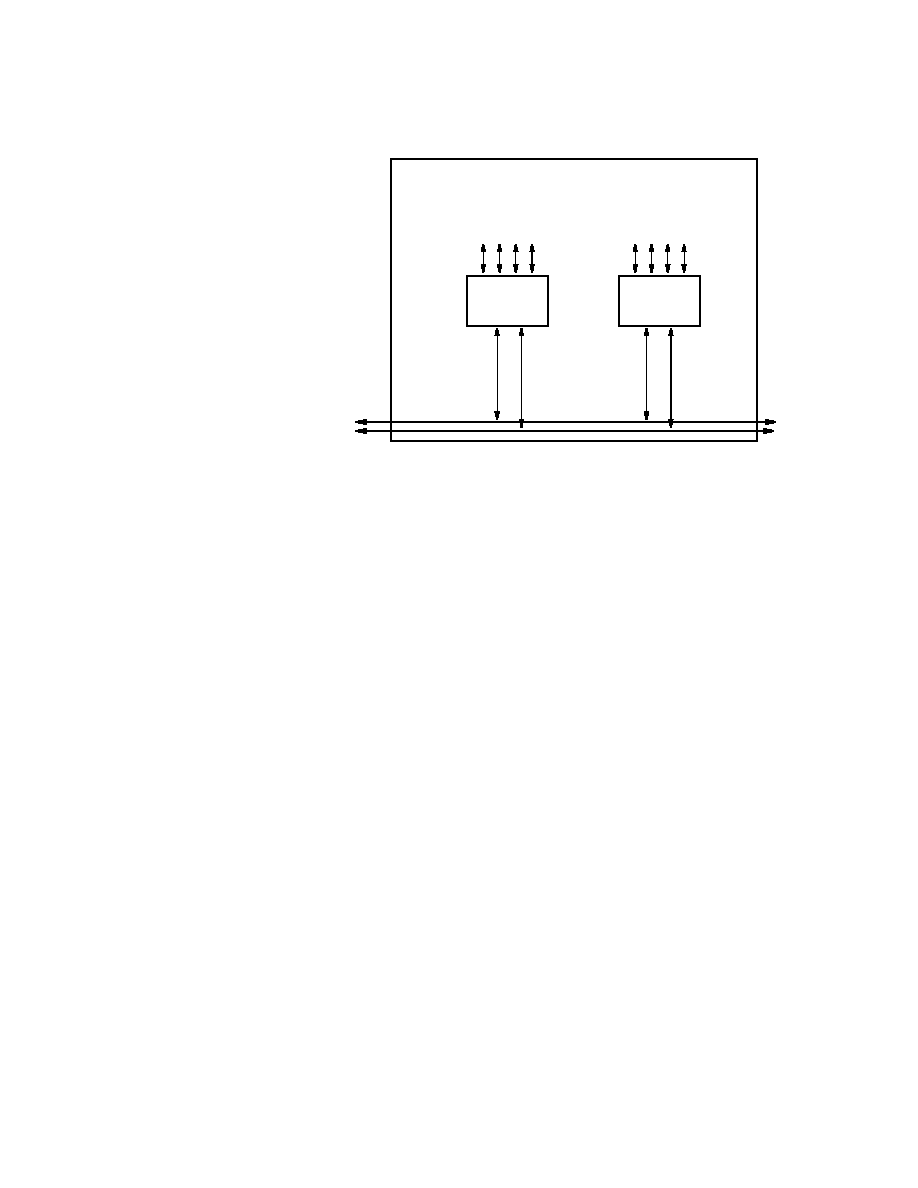

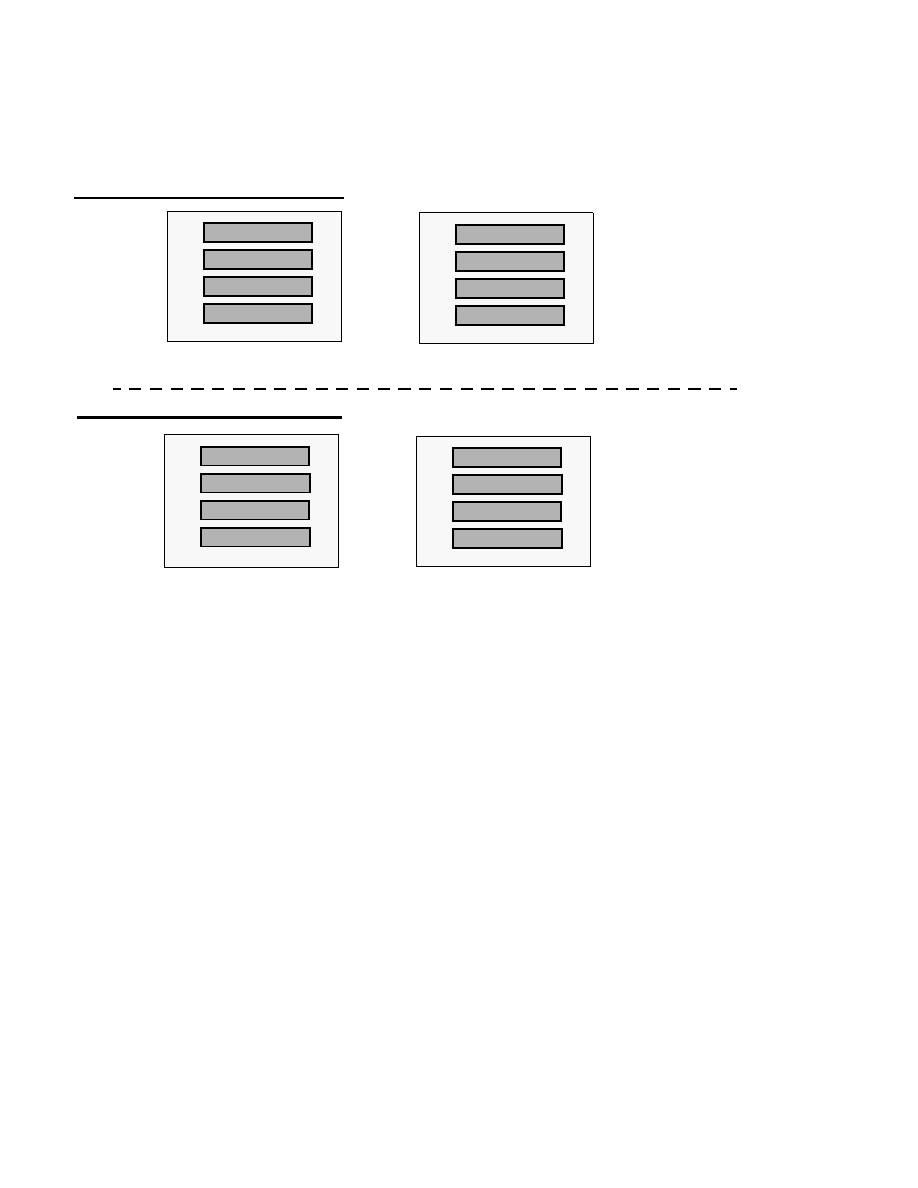

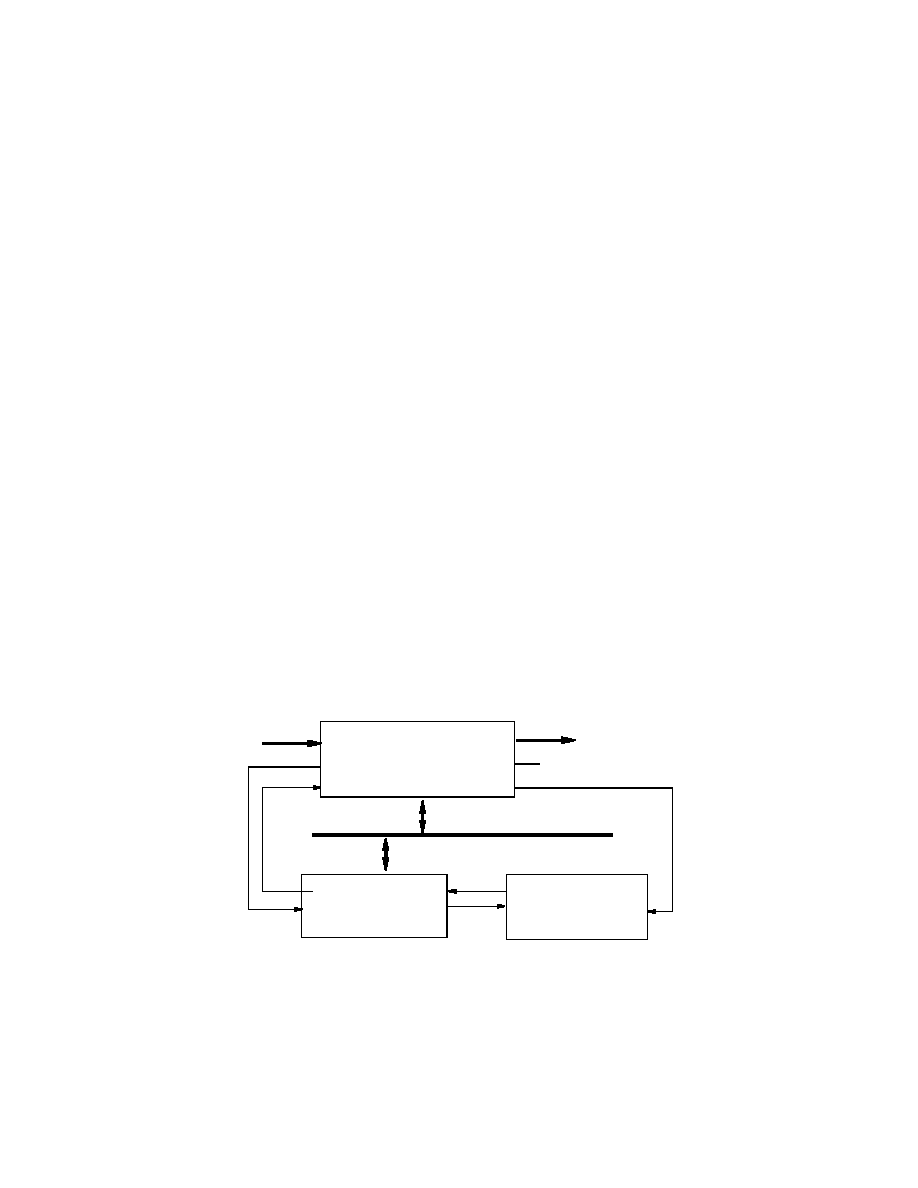

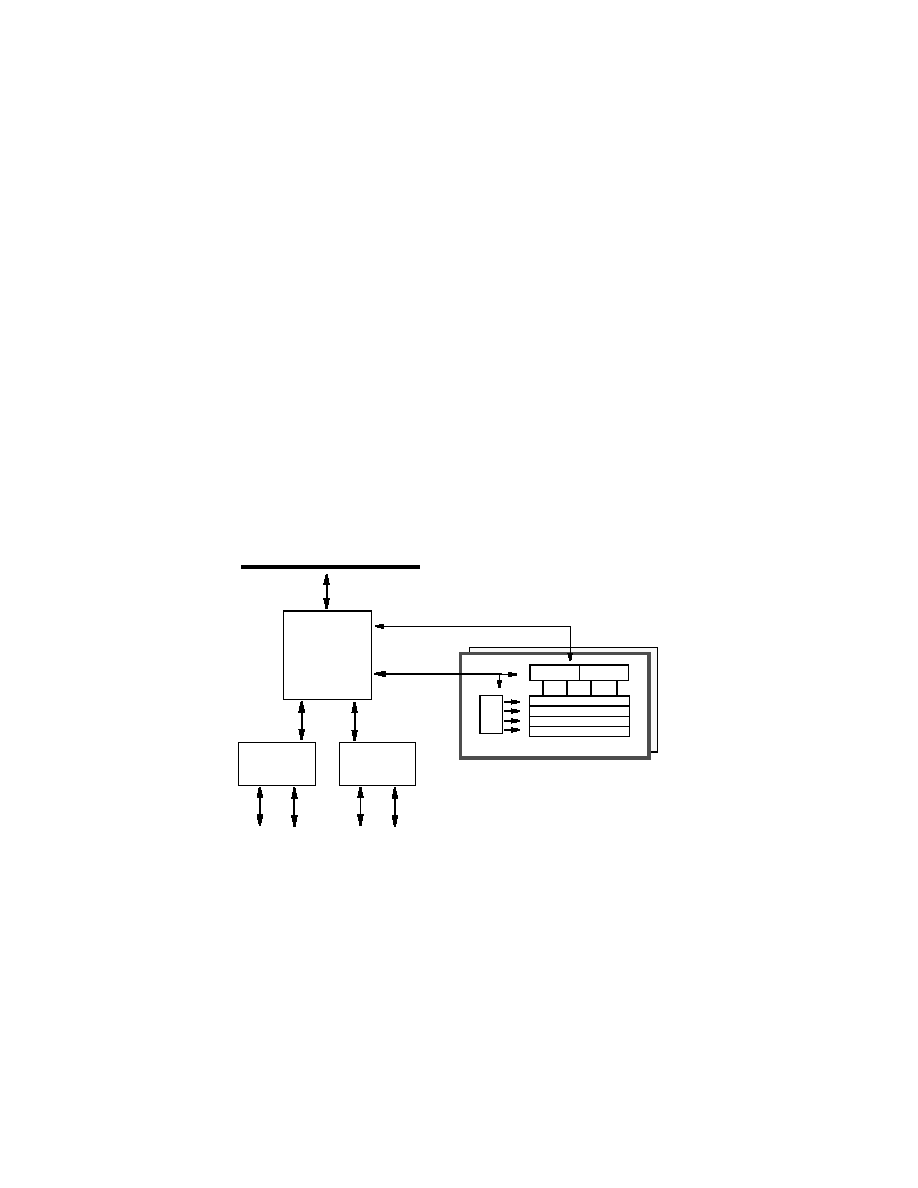

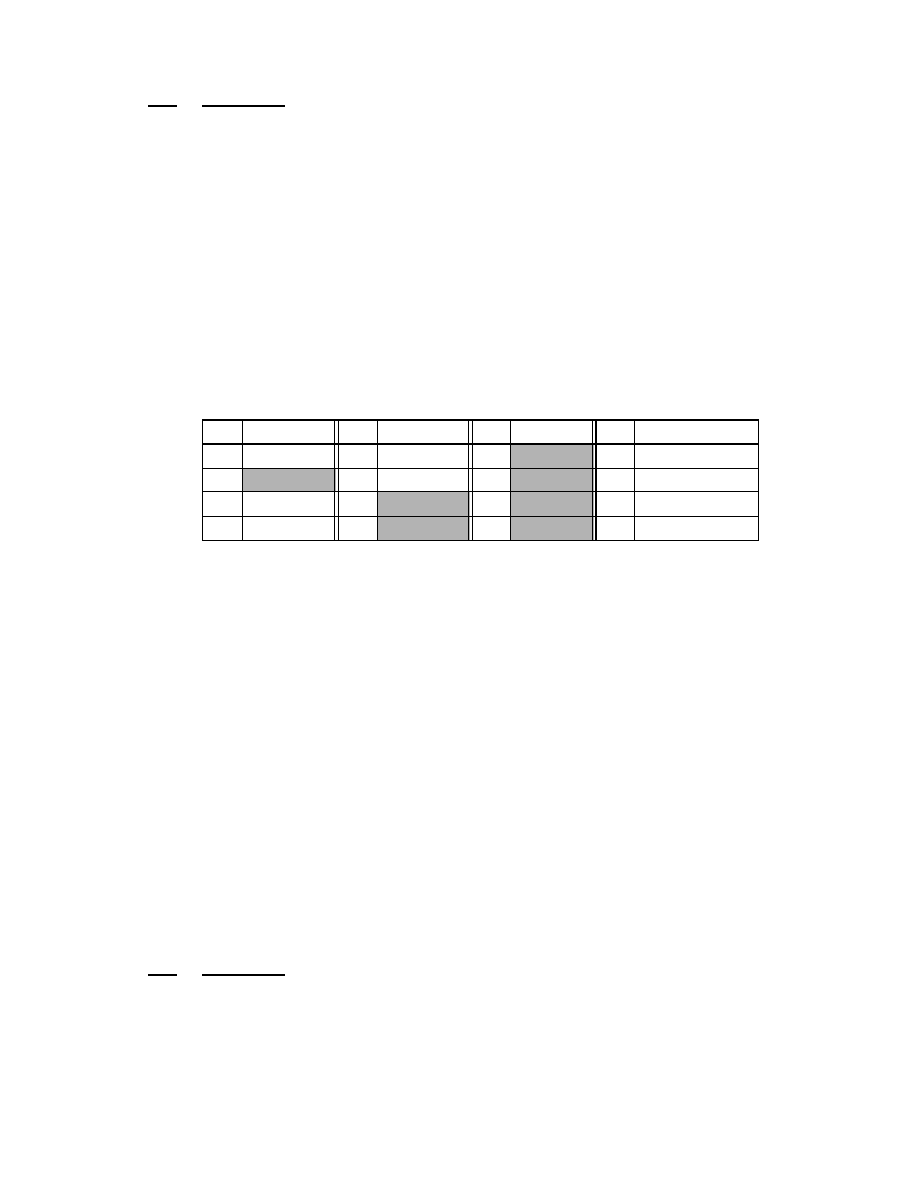

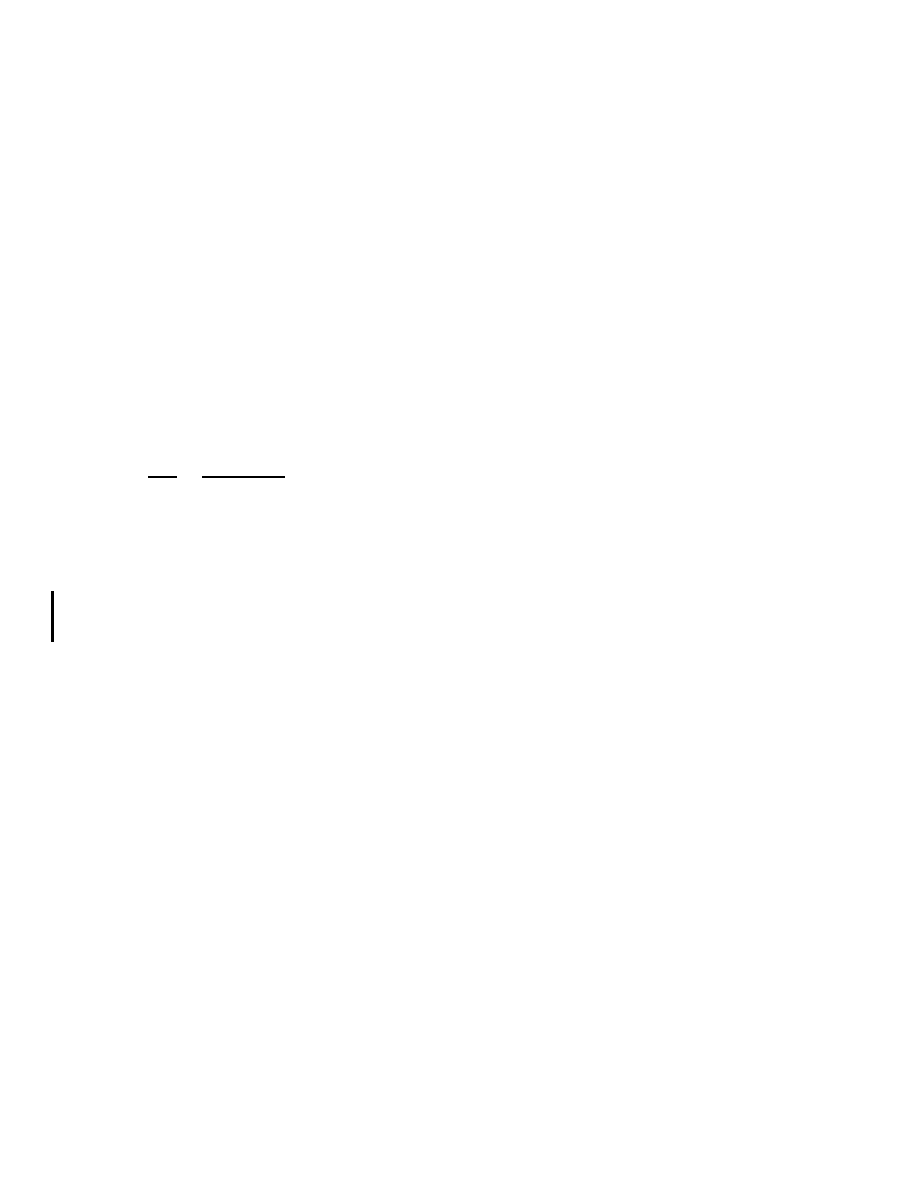

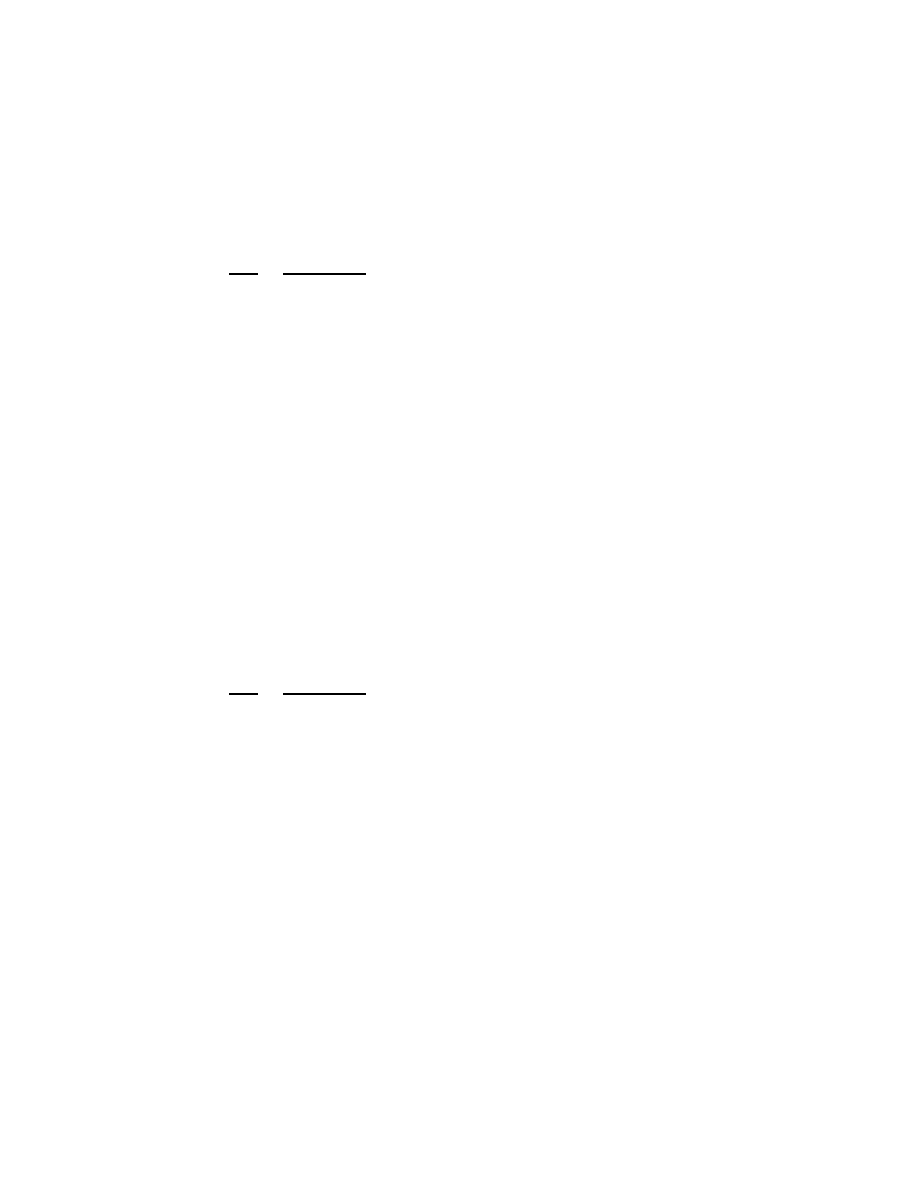

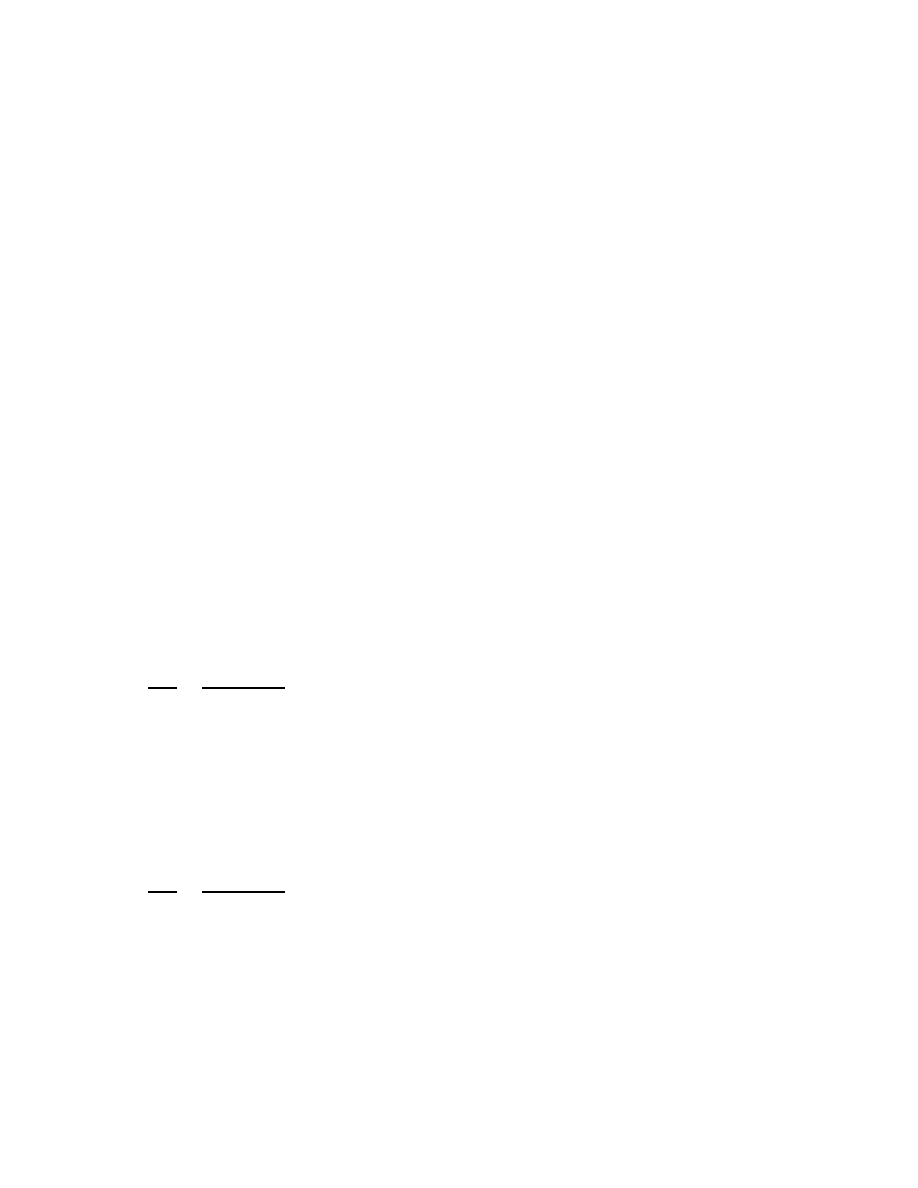

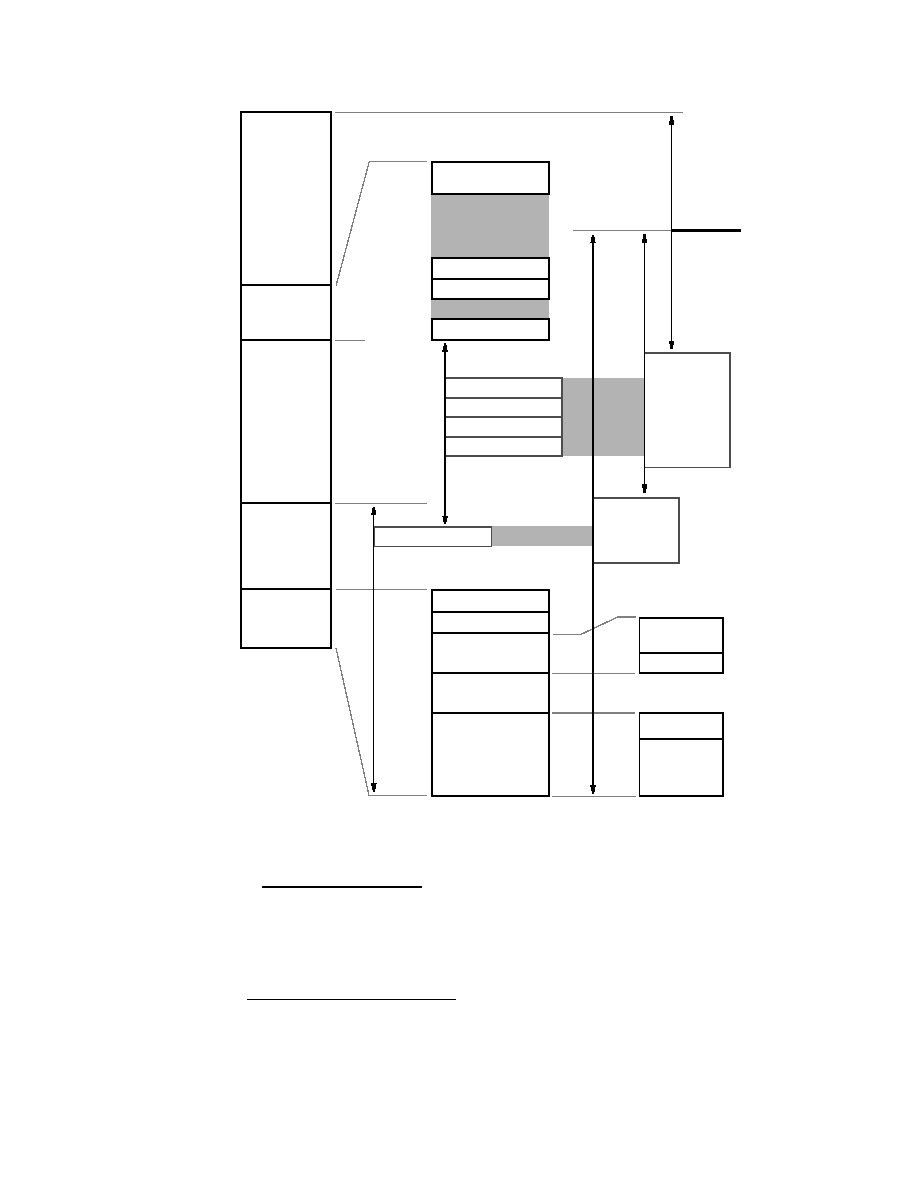

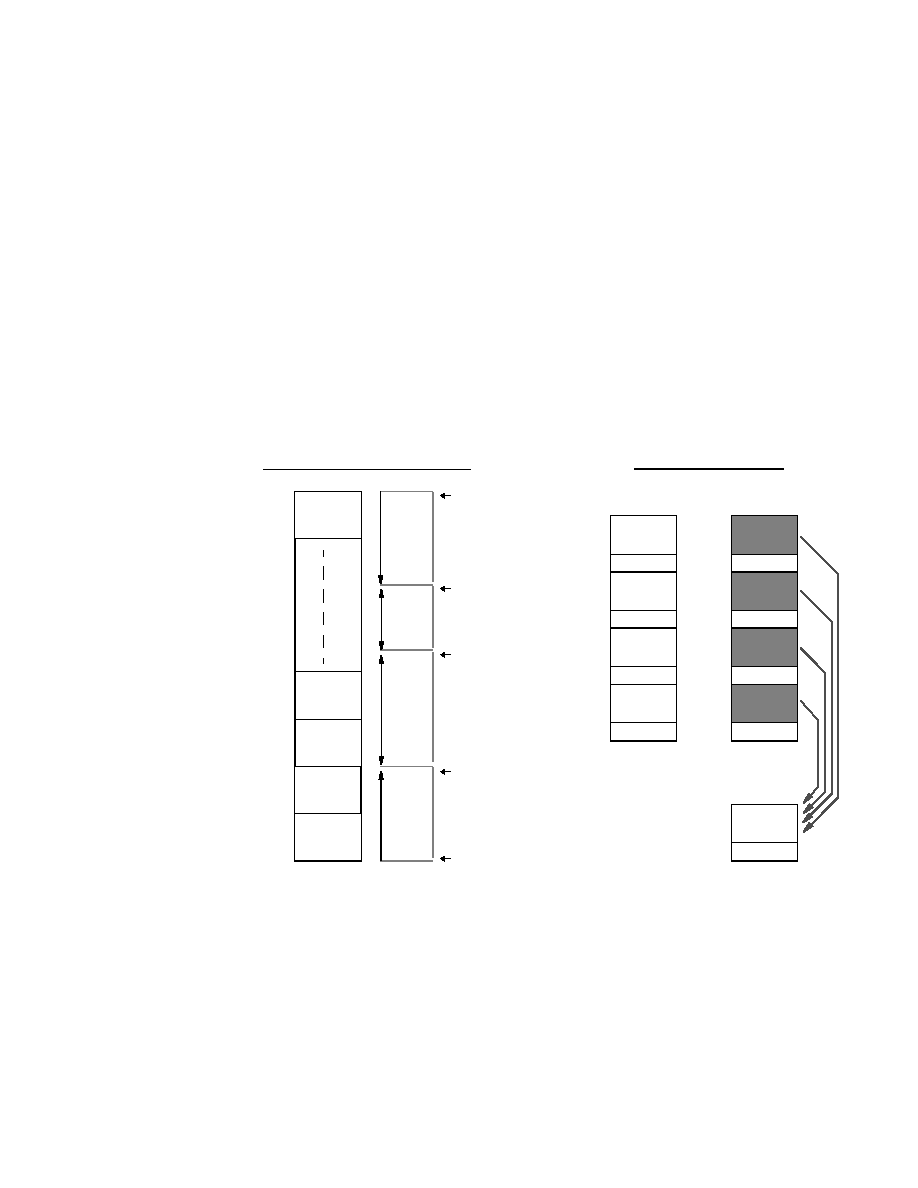

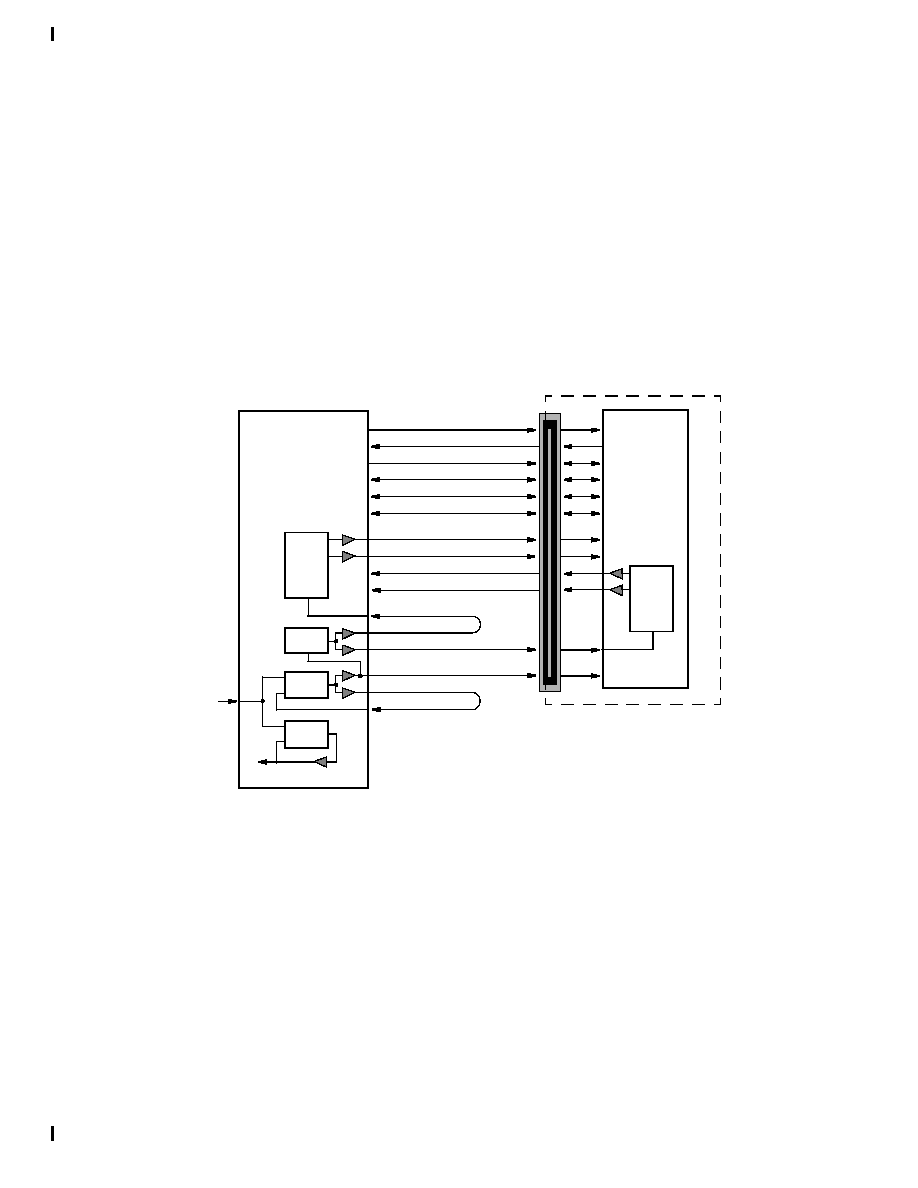

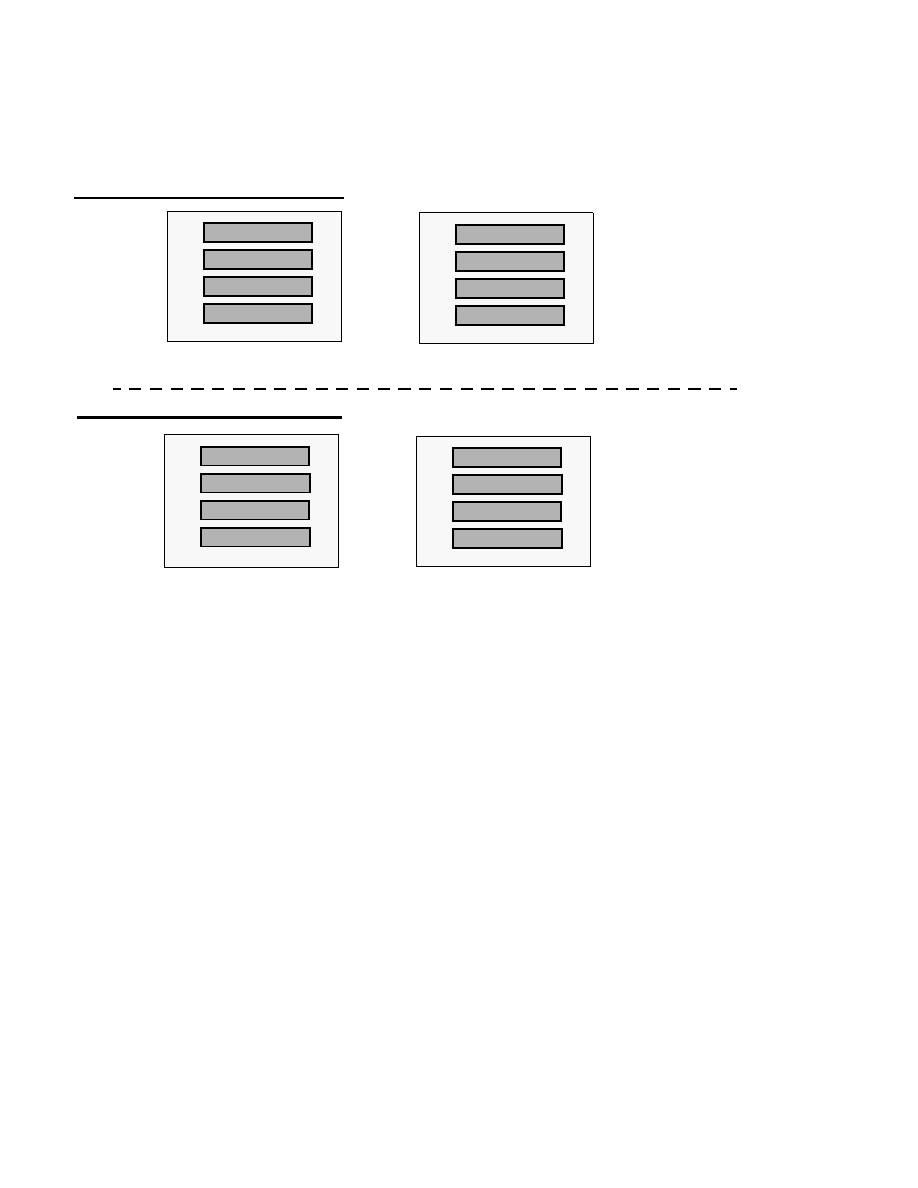

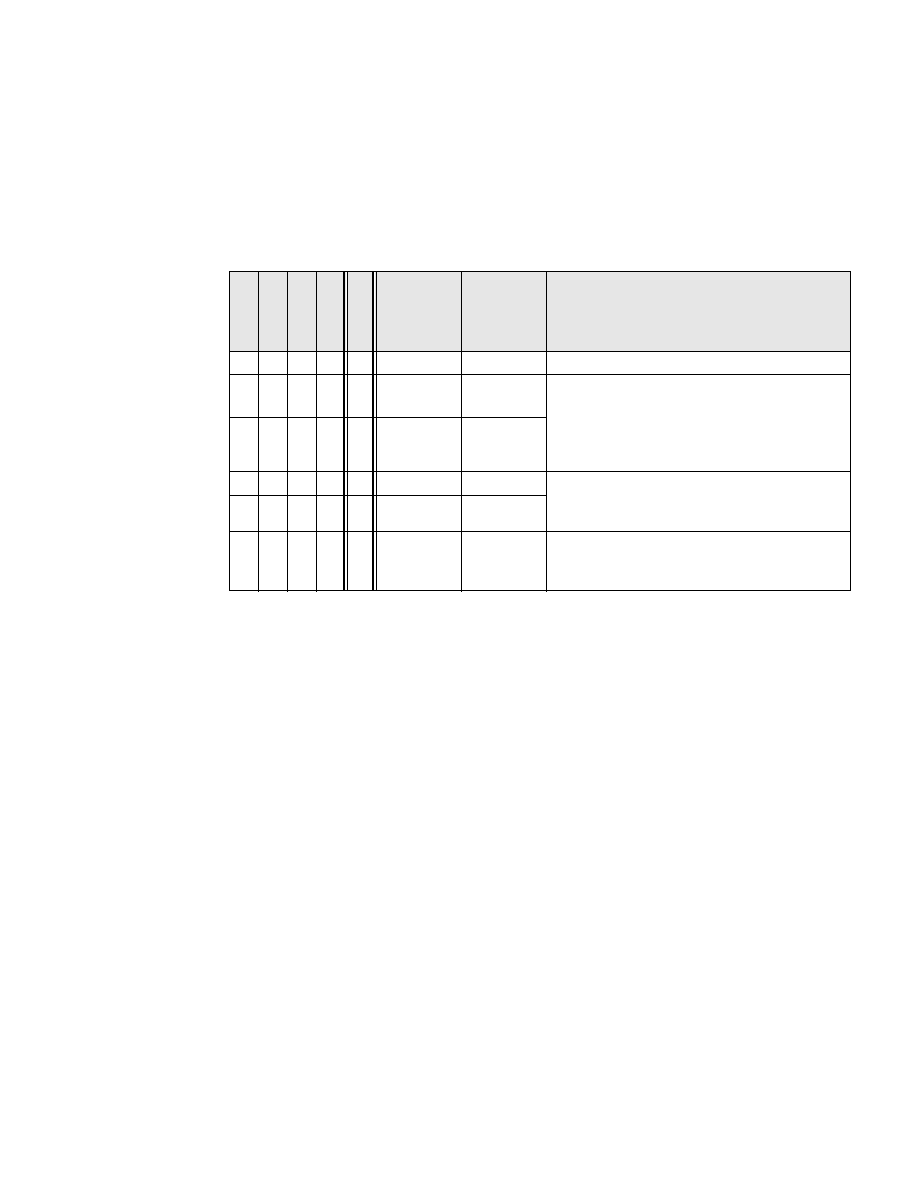

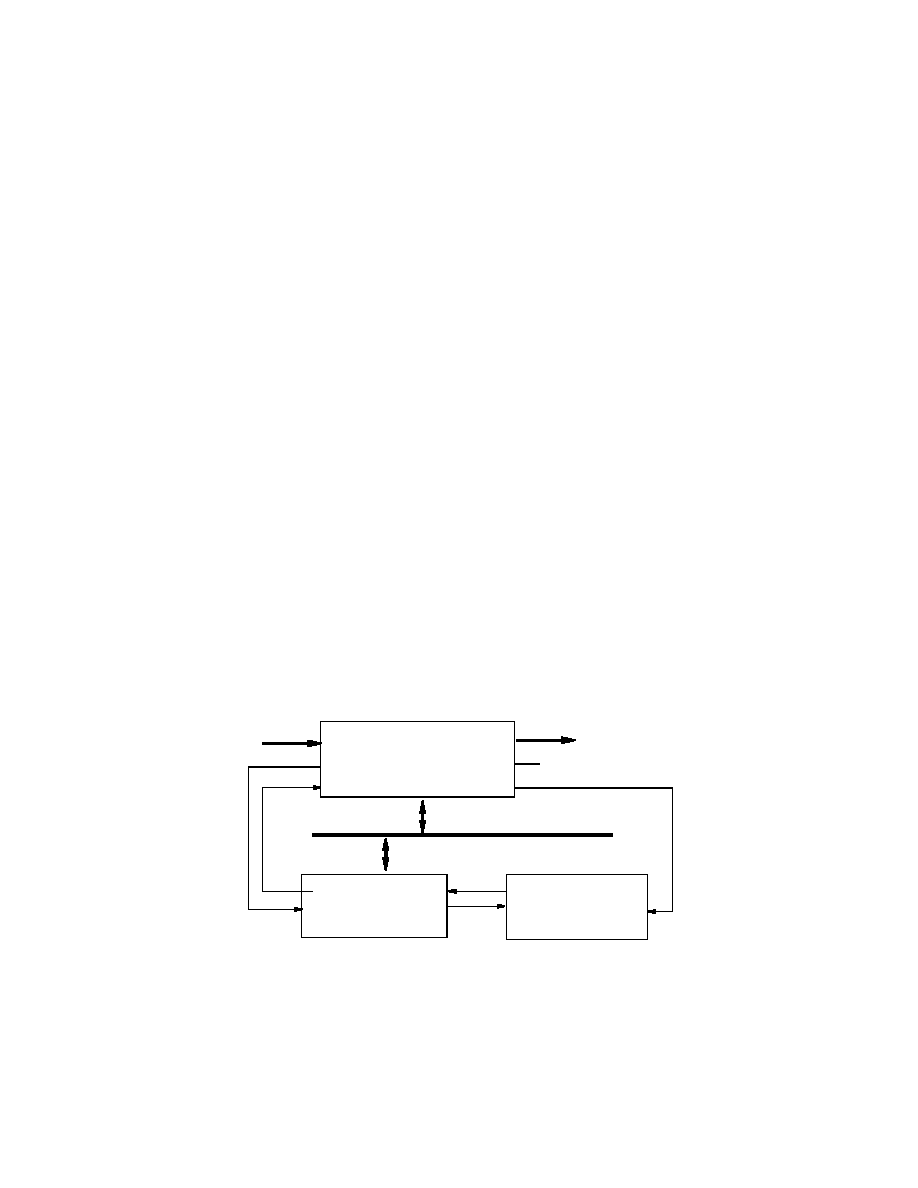

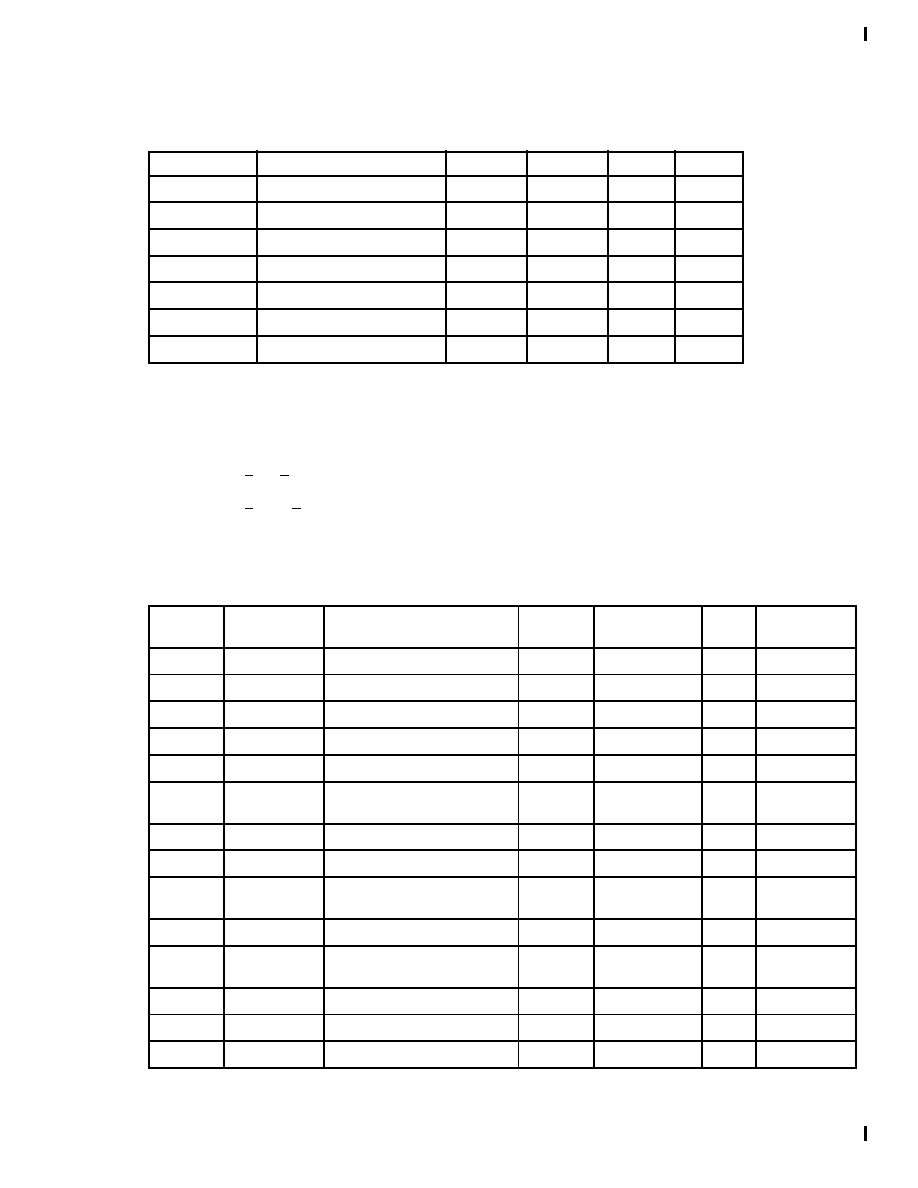

Figure 2-1 illustrates the partitioning of interfaces across the components in the Intel 450NX

PCIset. The remainder of this section lists the signals and signal counts in each interface by

component. The signal functions are described in subsequent sections.

2.2.1

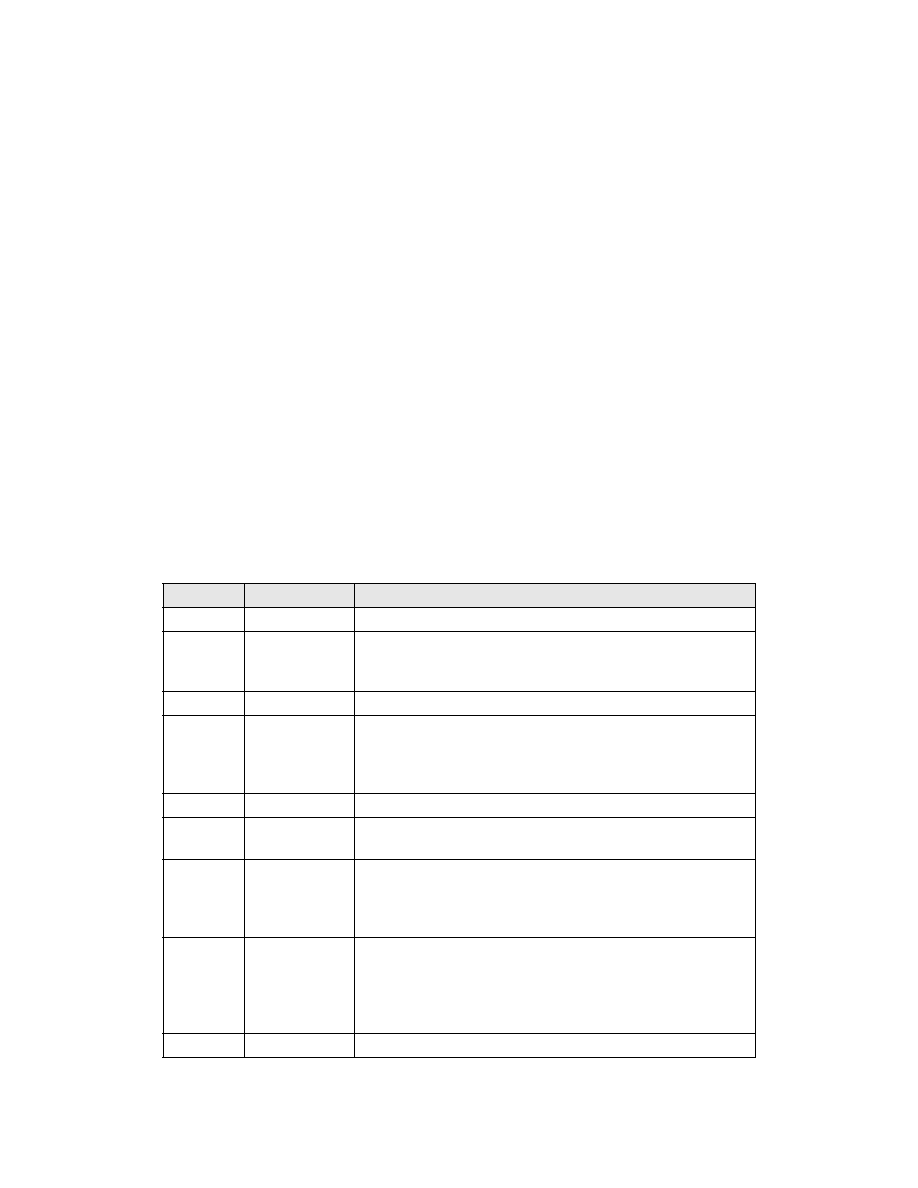

Signal Summary, By Component

The following tables provide summary lists of all signals in each component, sorted

alphabetically within interface type. The signals are described in a later section.

RR(A,B,C)XX

expands to:

RRAXX

,

RRBXX

, and

RRCXX

RR(A,...,D)XX

expands to:

RRAXX

,

RRBXX

,

RRCXX

, and

RRDXX

RRpXX

, where

p

=

A

,

B

,

C

expands to:

RRAXX

,

RRBXX

, and

RRCXX

Figure 2-1:

Interface Summary: Partitioning

MIOC

Memory

memory

Pentium

Æ

II Xeon

TM

processor bus

Interface

System Interface

Expander

DRAM

Array

MUXs

RCG

Memory Interface (Internal)

(External)

PXB #1

PCI Interfaces (2)

cards

Interface (2)

PXB #0

PCI Interfaces (2)

0A

0B

1A

1B

0

1

PCI Bus #0A is the Compatibility Bus

Intel

Æ

450NX PCIset

2-3

2.2 Summary

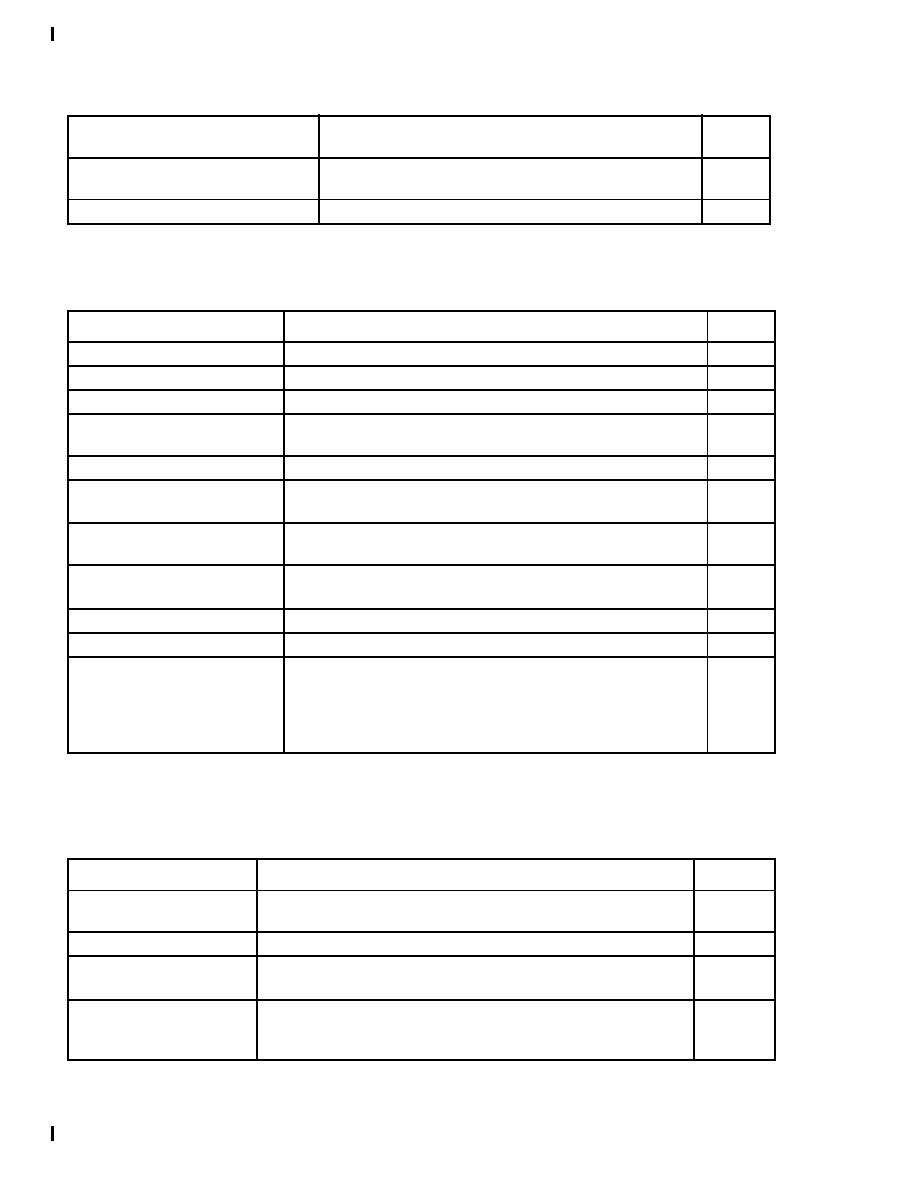

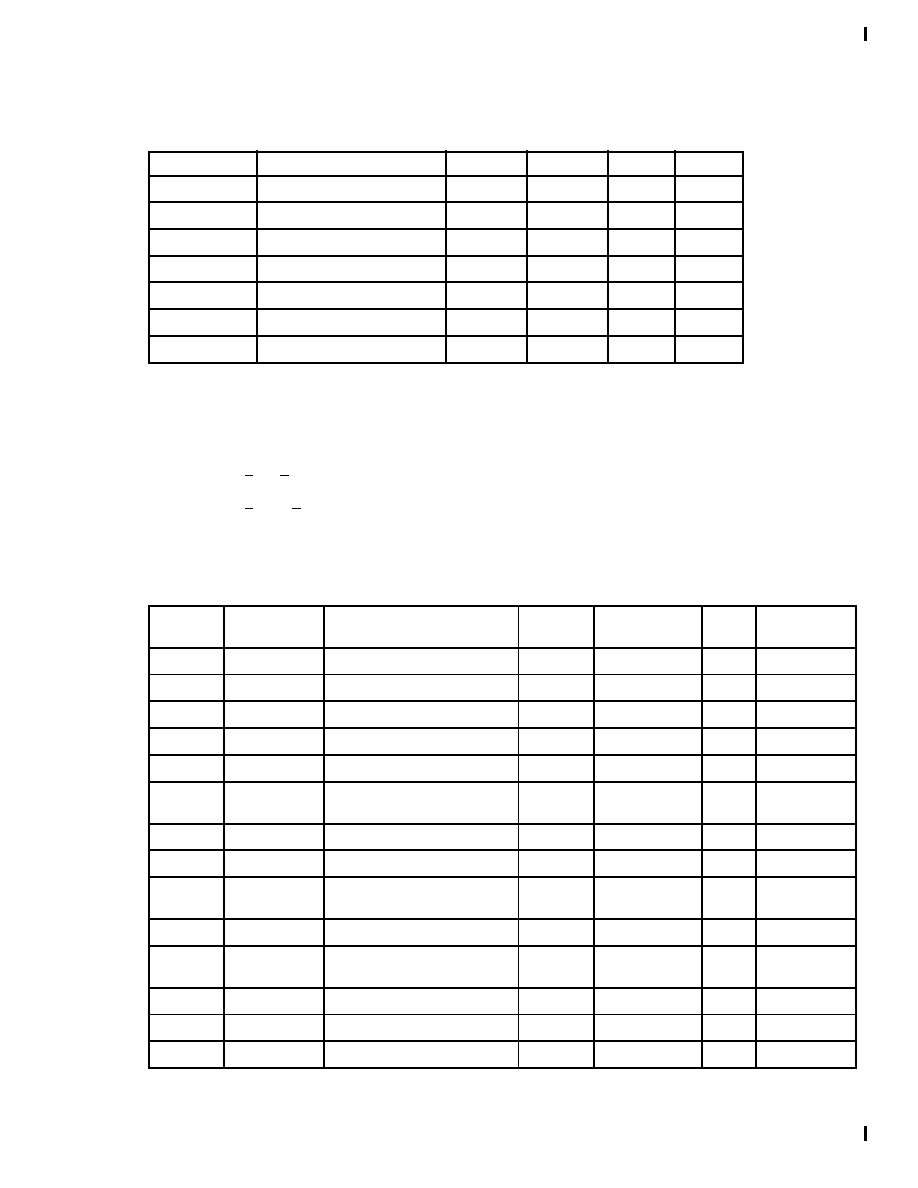

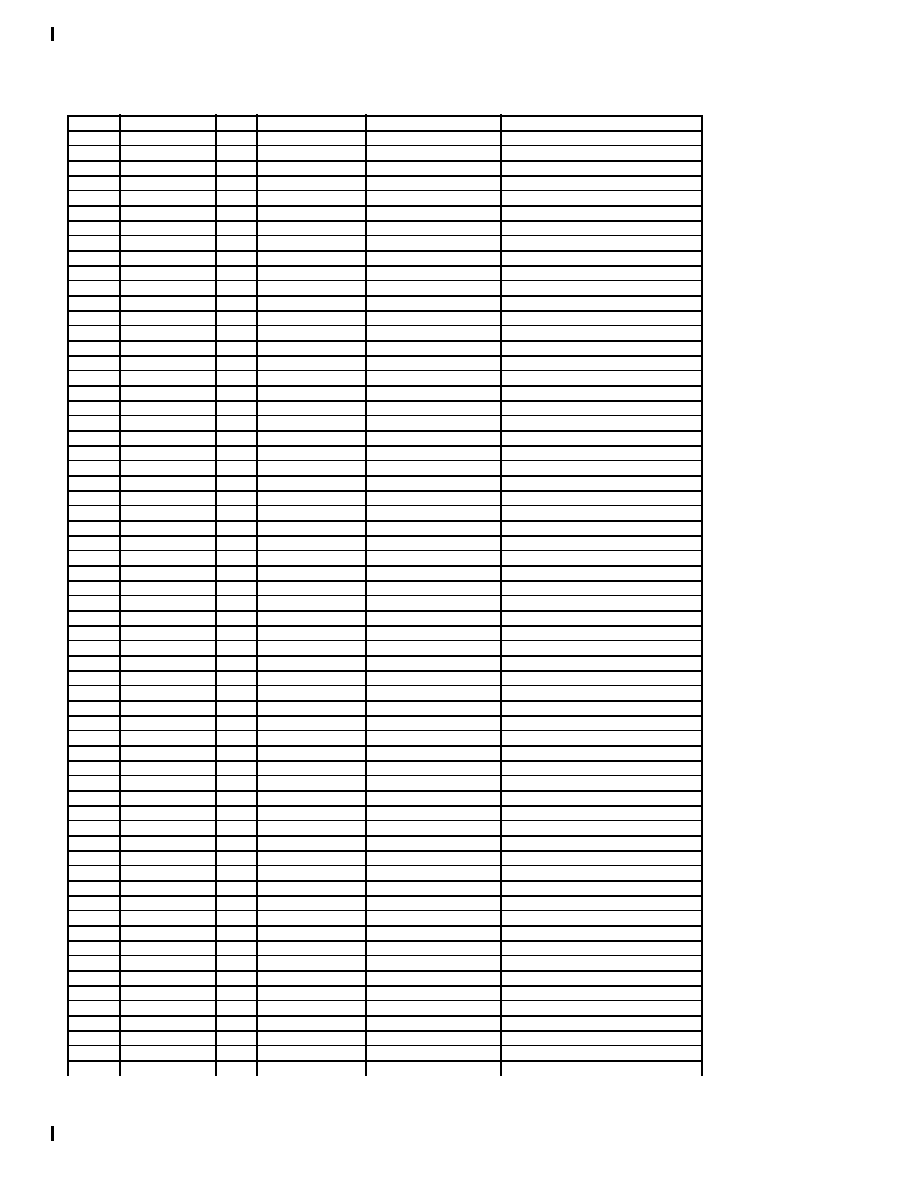

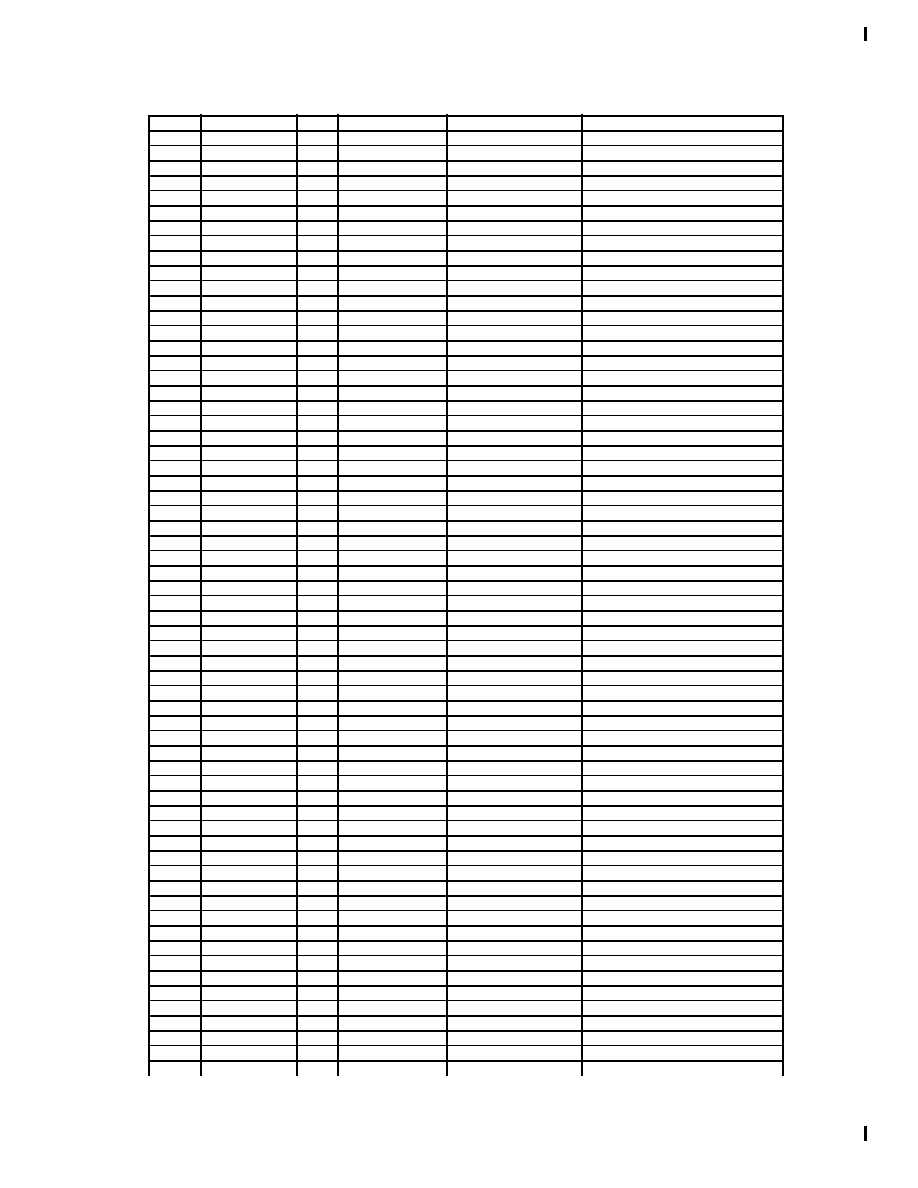

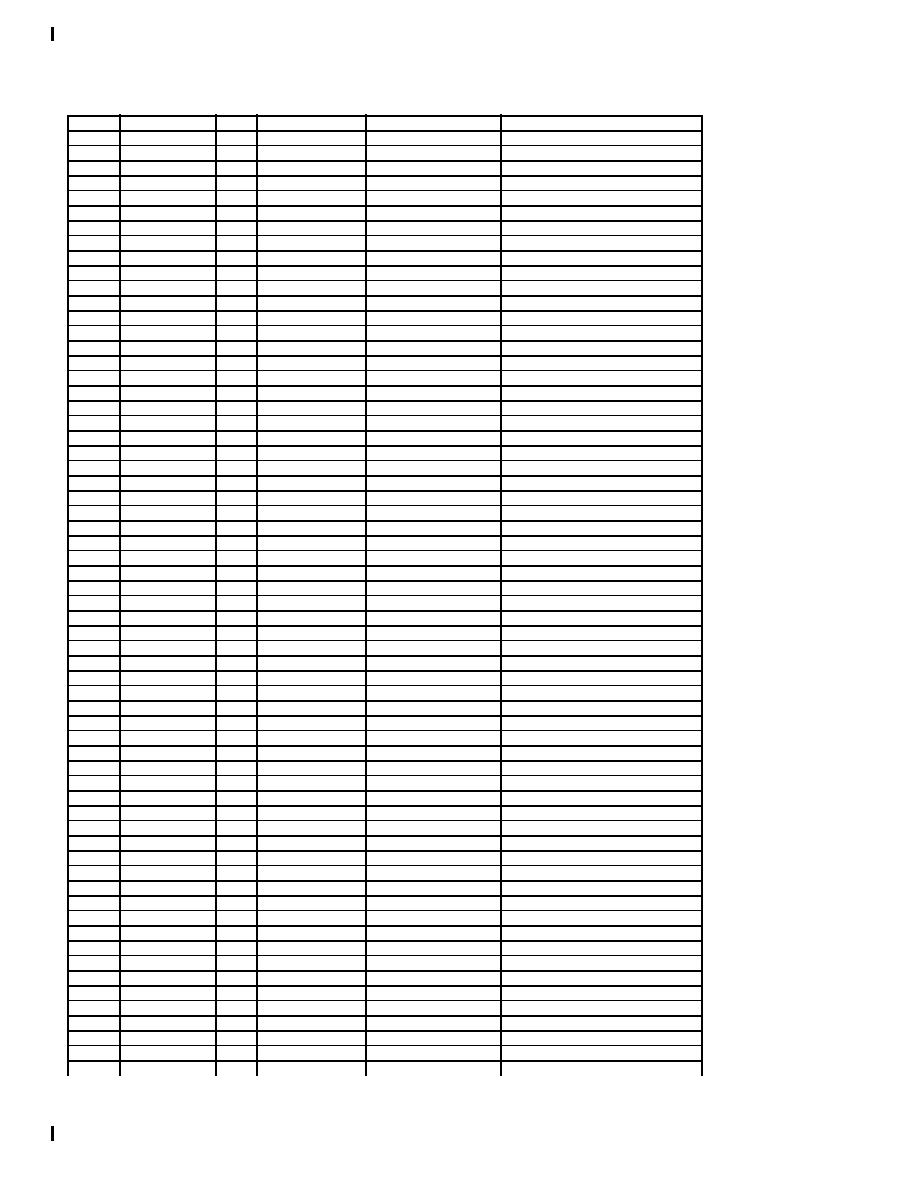

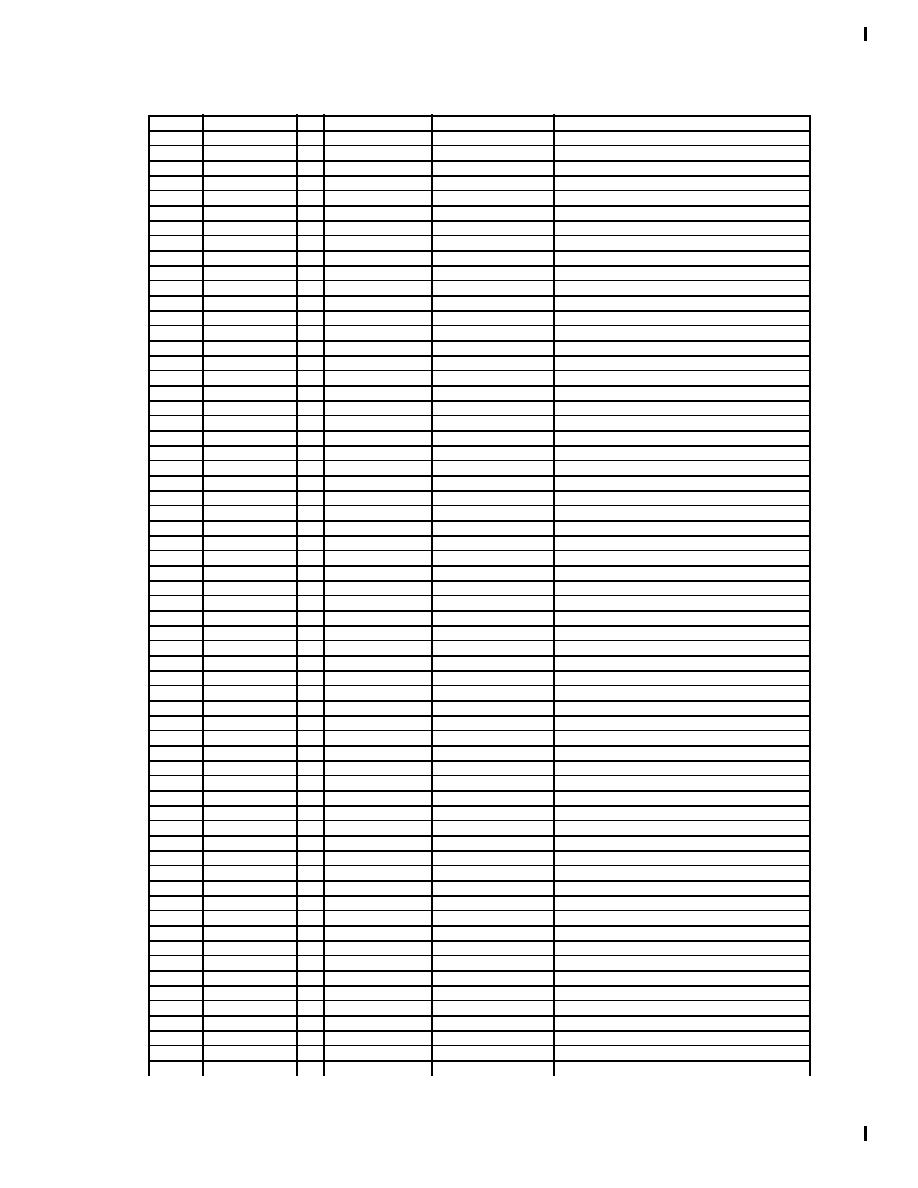

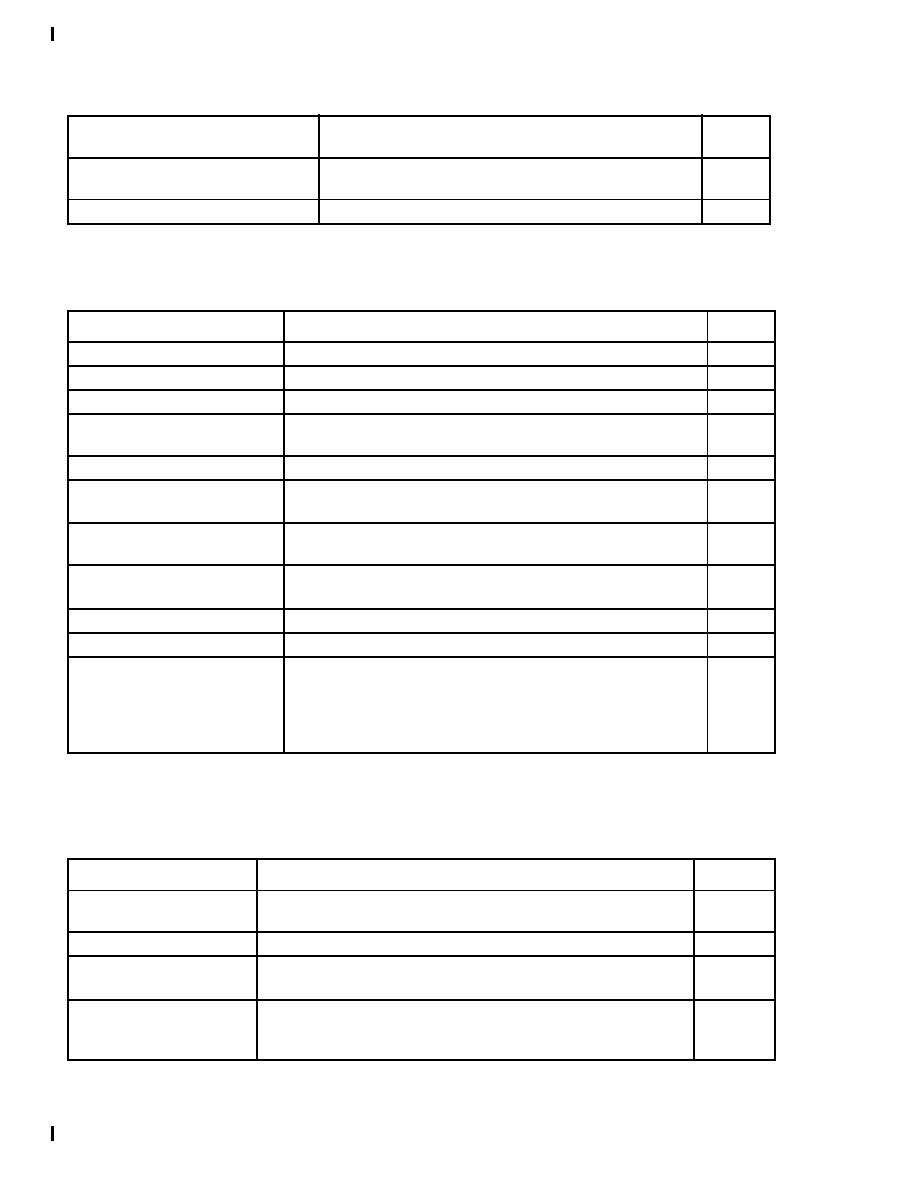

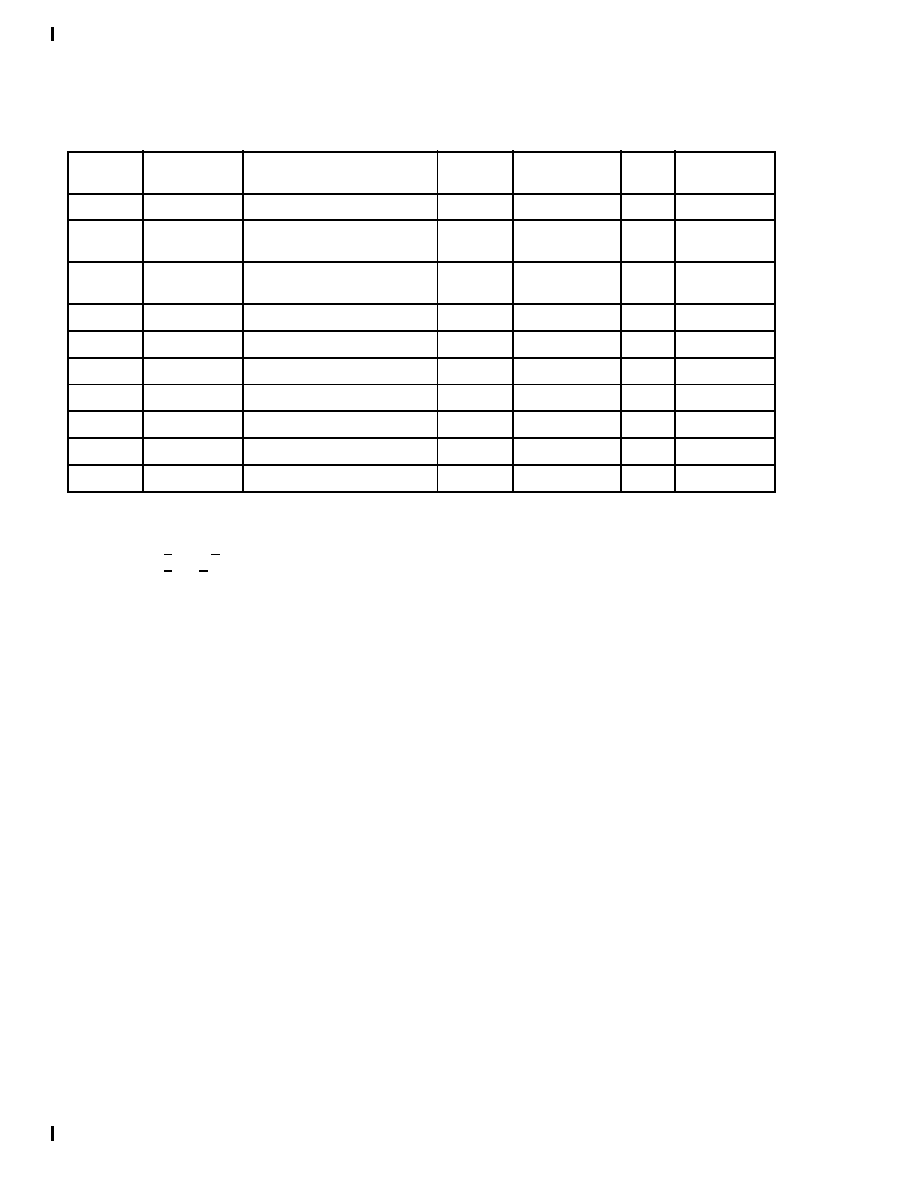

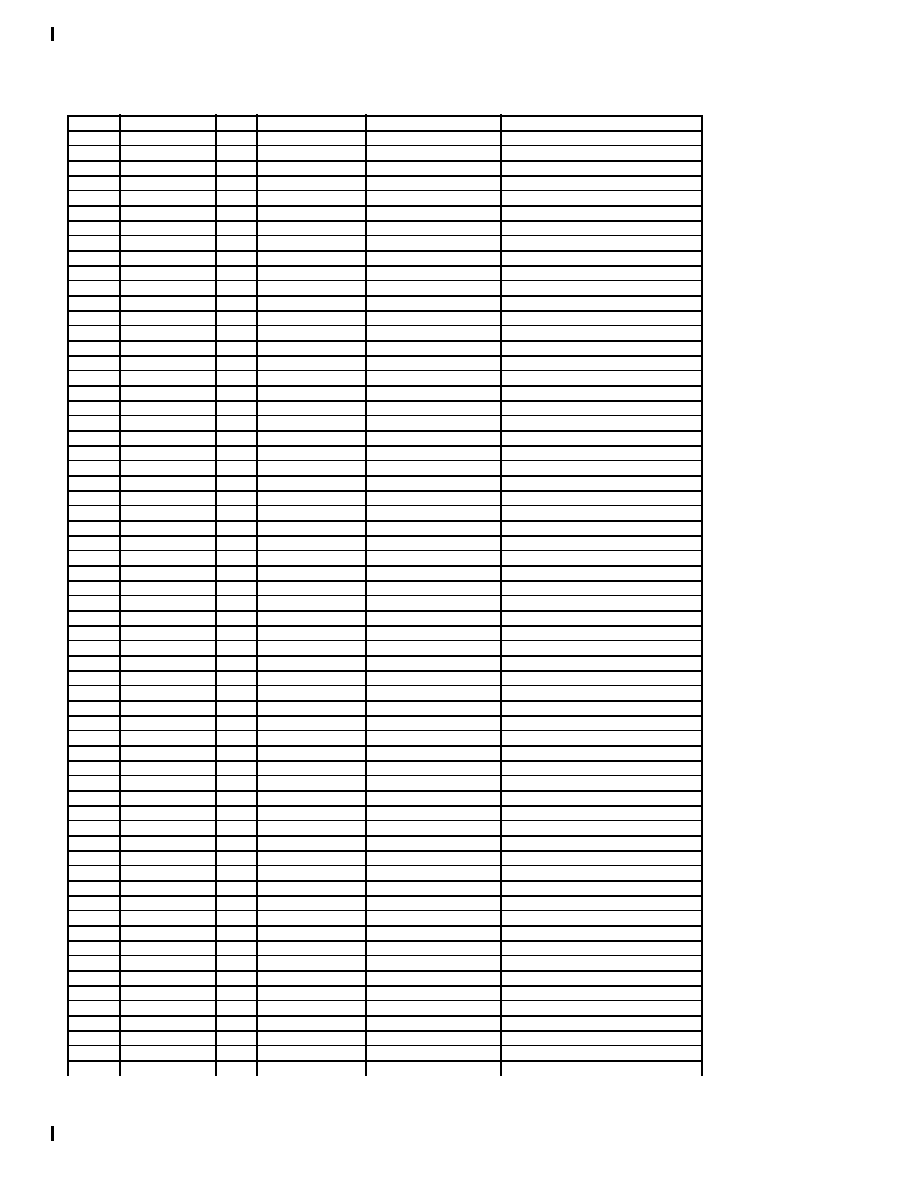

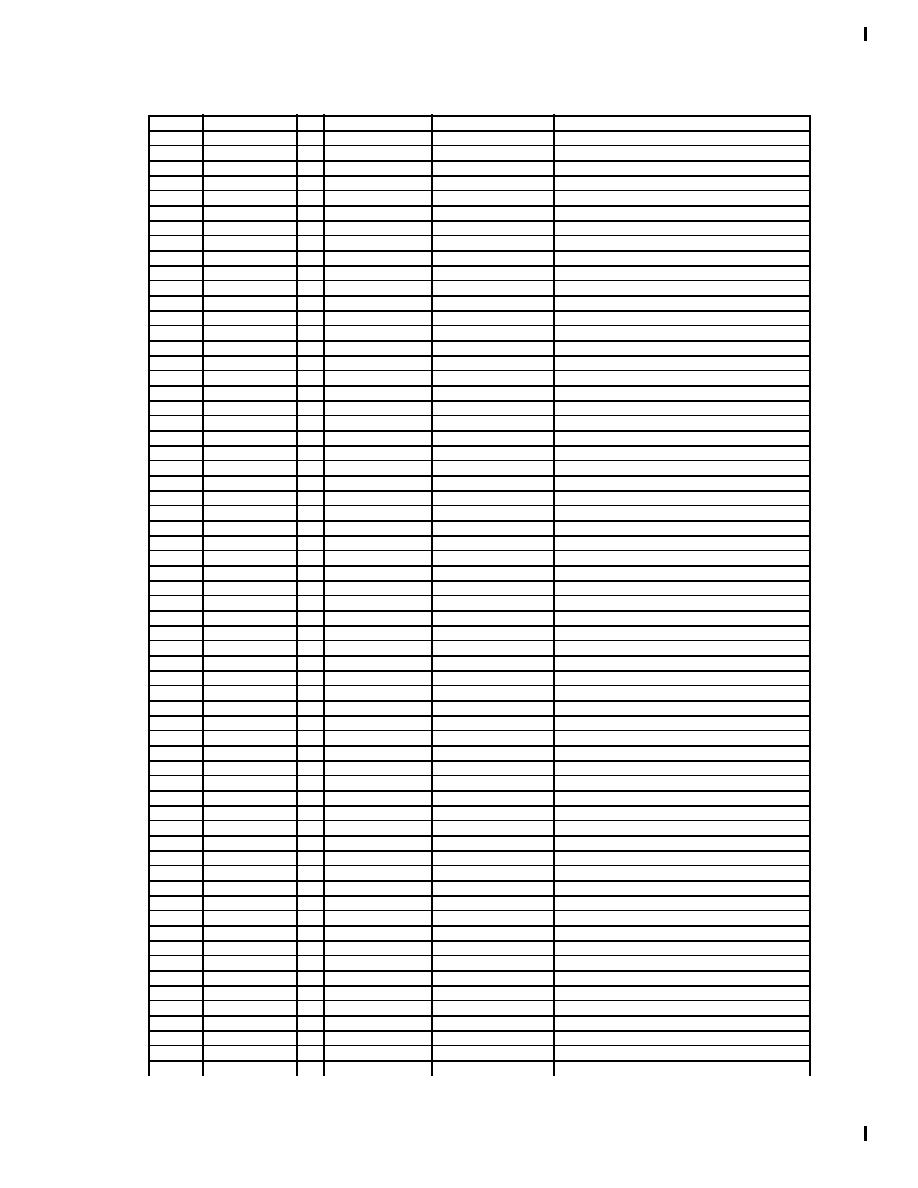

2.2.1.1

MIOC Signal List

System Interface

134

A[35:3]#

AGTL+ I/O

DEP[7:0]#

AGTL+ I/O

ADS#

AGTL+ I/O

DRDY#

AGTL+ I/O

AERR#

AGTL+ I/O

HIT#

AGTL+ I

AP[1:0]#

AGTL+ I/O

HITM#

AGTL+ I

BERR#

AGTL+ I/O

INIT#

2.5V

OD

BINIT#

AGTL+ I/O

LOCK#

AGTL+ I

BNR#

AGTL+ I/O

REQ[4:0]#

AGTL+ I/O

BP[1:0]#

LVTTL I/OD

RP#

AGTL+ I/O

BPRI#

AGTL+ I/O

RS[2:0]#

AGTL+ I/O

BREQ[0]#

AGTL+ O

RSP#

AGTL+ I/O

D[63:0]#

AGTL+ I/O

TRDY#

AGTL+ I/O

DBSY#

AGTL+ I/O

DEFER#

AGTL+ I/O

Third-Party Agent Interface

4

IOGNT#

LVTTL I

TPCTL[1:0]

LVTTL I

IOREQ#

LVTTL O

Memory Subsystem / External Interface

119

BANK[2:0]#

AGTL+ O

DVALID(a,b)#

AGTL+ O

CARD[1:0]#

AGTL+ O

MA[13:0]#

AGTL+ O

CMND[1:0]#

AGTL+ O

MD[71:0]#

AGTL+ I/O

CSTB#

AGTL+ O

MRESET#

AGTL+ O

DCMPLT(a,b)#

AGTL+ I/O

PHIT(a,b)#

AGTL+ I

DOFF[1:0]#

AGTL+ O

ROW#

AGTL+ O

DSEL[1:0]#

AGTL+ O

RCMPLT(a,b)#

AGTL+ I

DSTBN[3:0]#

AGTL+ I/O

RHIT(a,b)#

AGTL+ I

DSTBP[3:0]#

AGTL+ I/O

WDEVT#

AGTL+ O

Expander Interface (two per MIOC: 0,1)

2 x 33

X(0,1)ADS#

AGTL+ I/O

X(0,1)HSTBP#

AGTL+ O

X(0,1)BE[1:0]#

AGTL+ I/O

X(0,1)PAR#

AGTL+ I/O

X(0,1)BLK#

AGTL+ O

X(0,1)RST#

AGTL+ O

X(0,1)CLK

CMOS O

X(0,1)RSTB#

AGTL+ O

X(0,1)CLKB

CMOS O

X(0,1)RSTFB#

AGTL+ I

X(0,1)CLKFB

CMOS I

X(0,1)XRTS#

AGTL+ I

X(0,1)D[15:0]#

AGTL+ I/O

X(0,1)XSTBN#

AGTL+ I

X(0,1)HRTS#

AGTL+ O

X(0,1)XSTBP#

AGTL+ I

X(0,1)HSTBN#

AGTL+ O

Common Support Signals

16

CRES[1:0]

Analog

I

TMS

2.5V

I

TCK

2.5V

I

TRST#

2.5V

I

TDI

2.5V

I

VCCA (3)

Analog

I

TDO

2.5V

OD

VREF (6)

Analog

I

2-4

Intel

Æ

450NX PCIset

2. Signal Descriptions

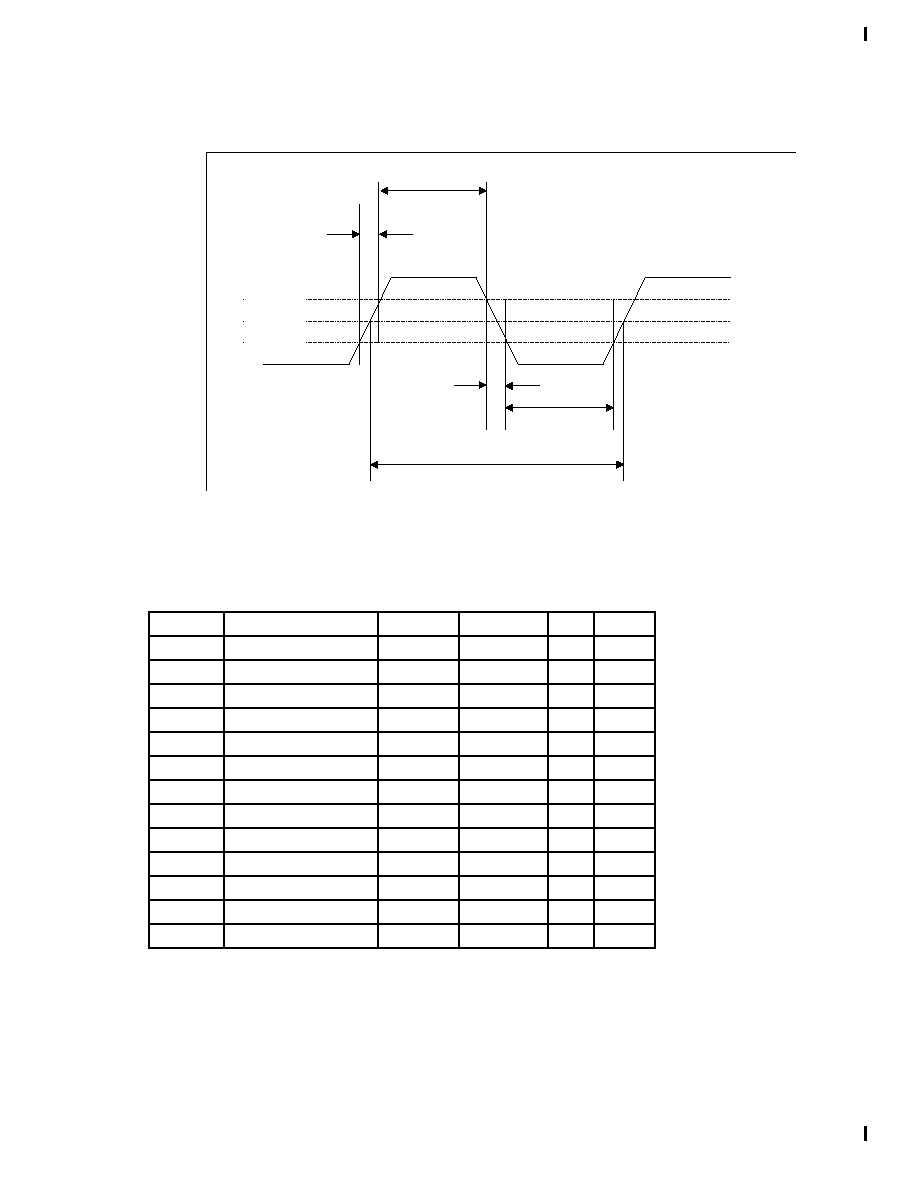

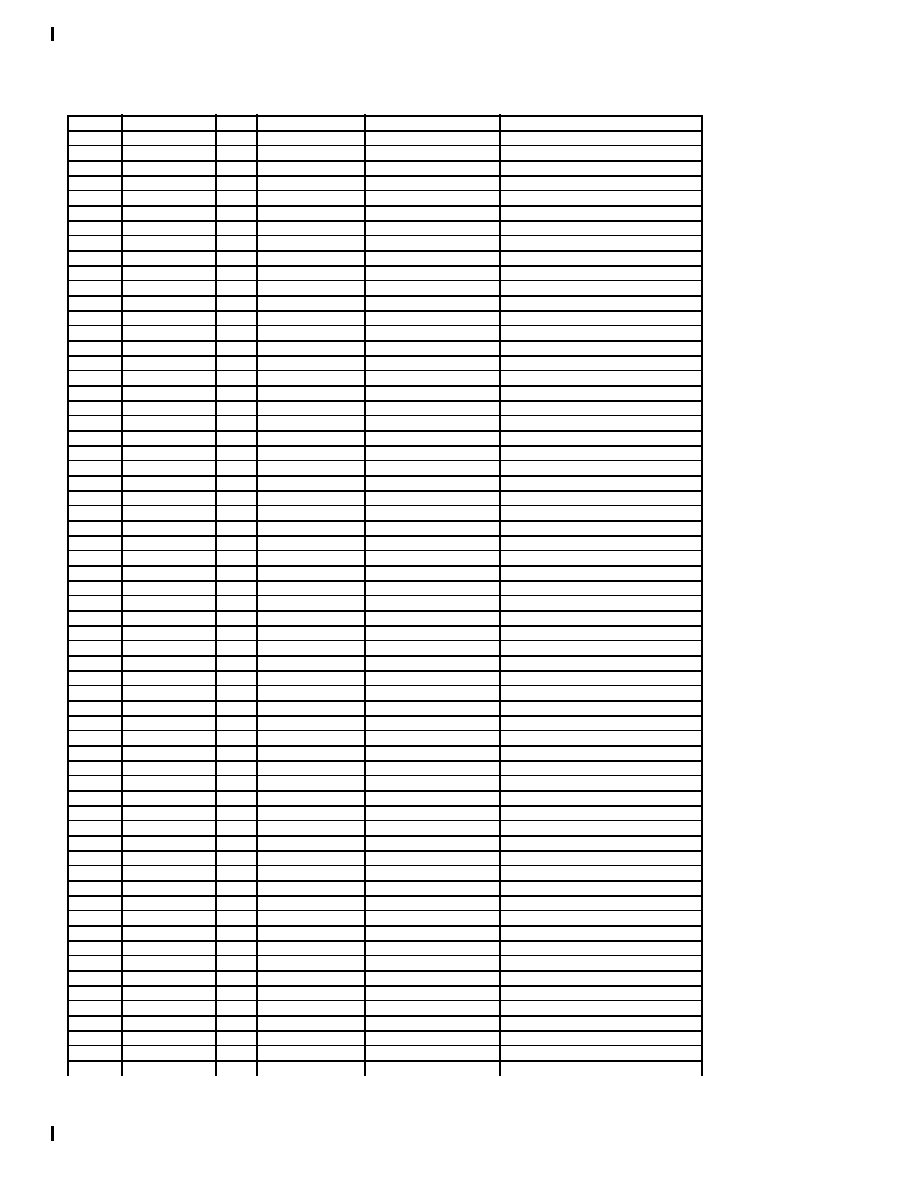

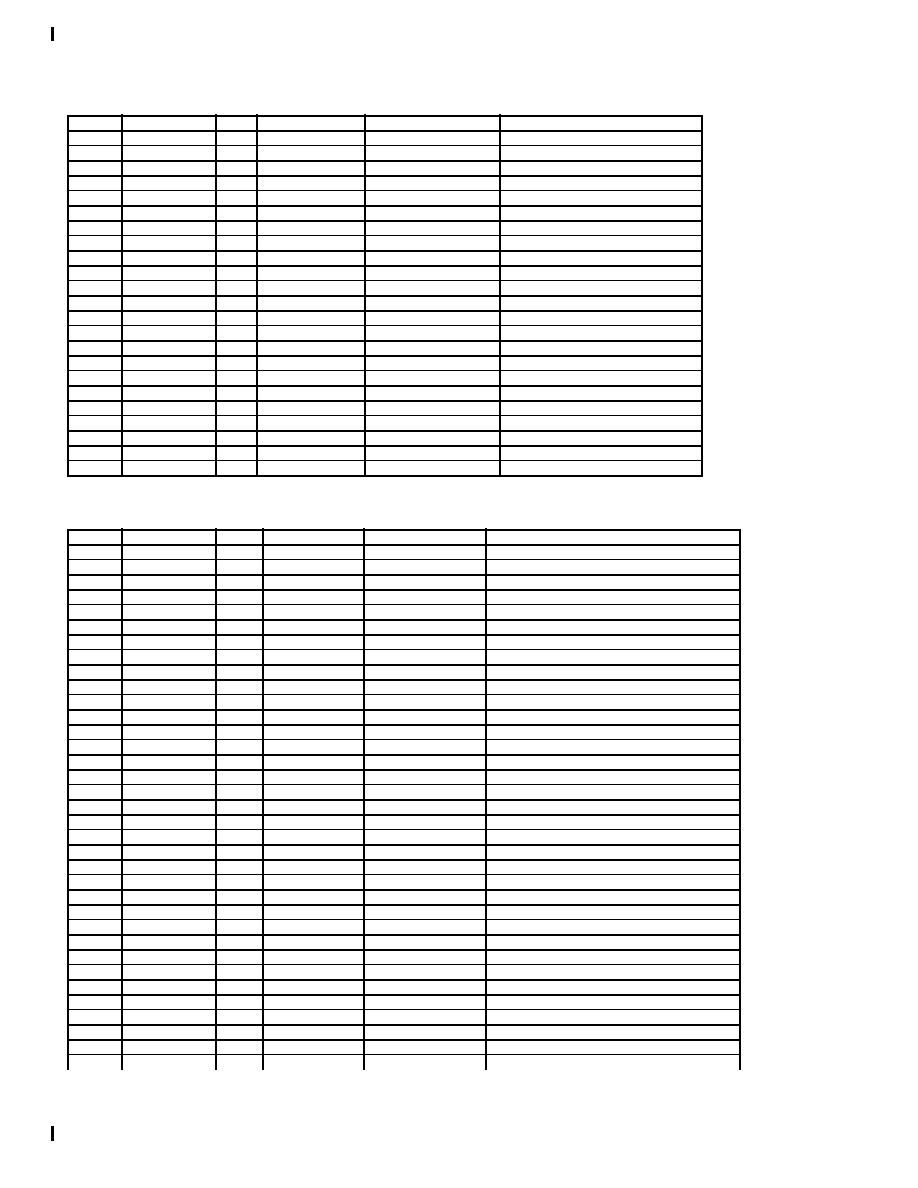

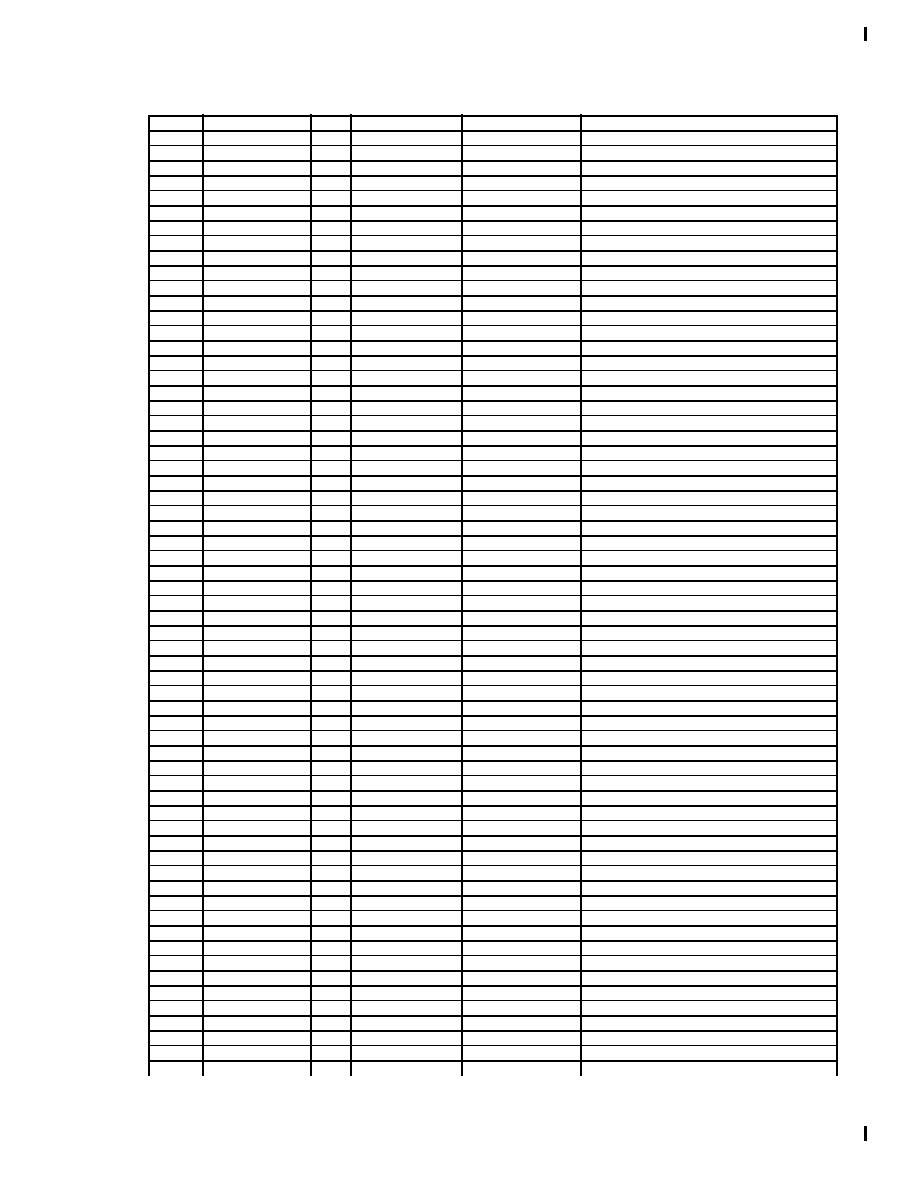

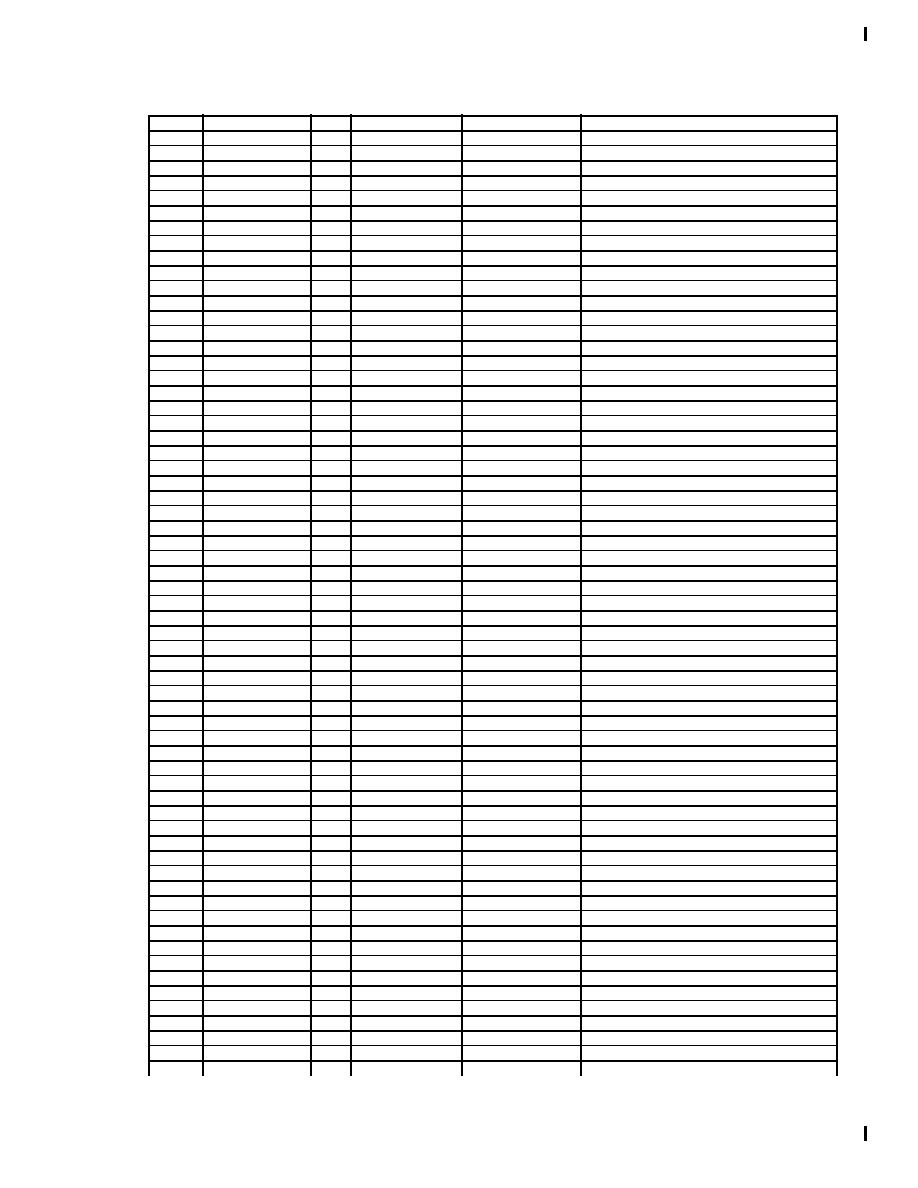

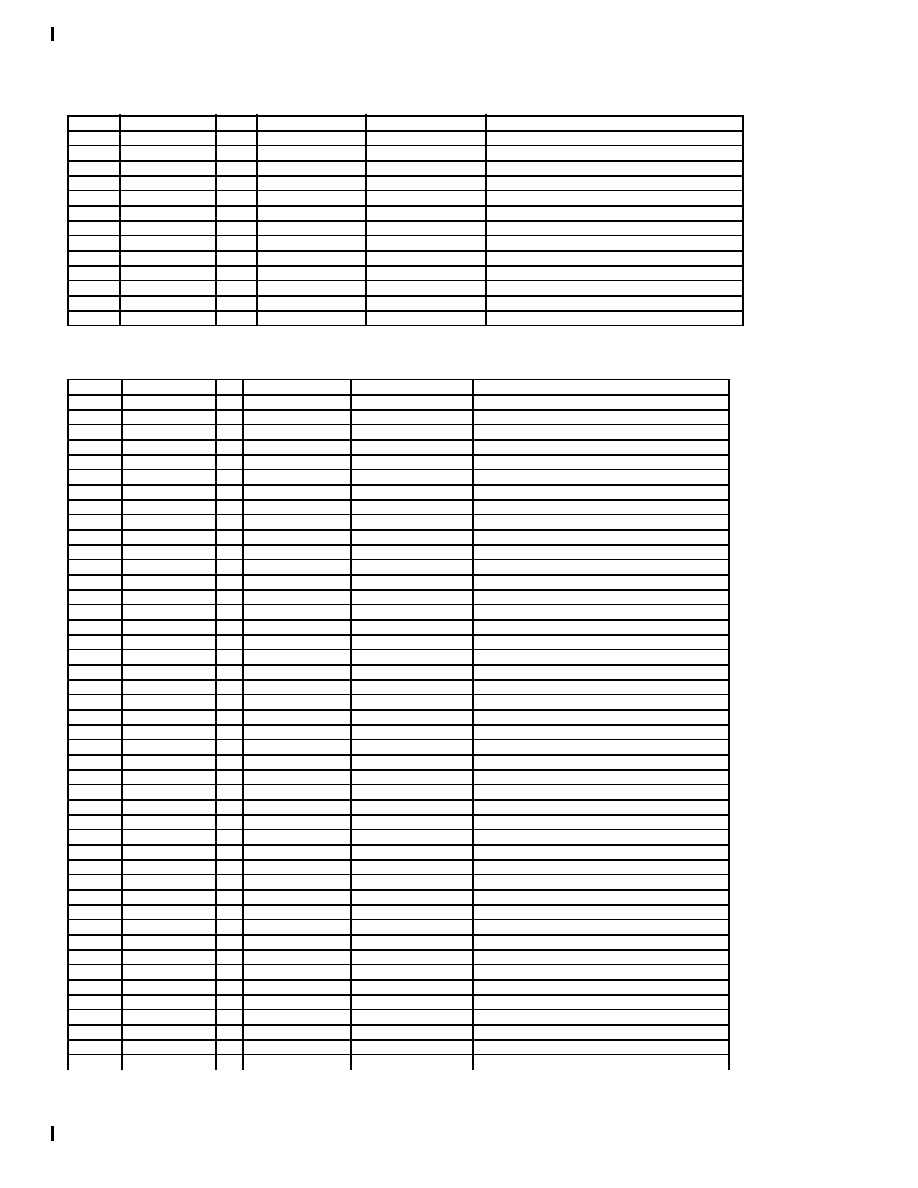

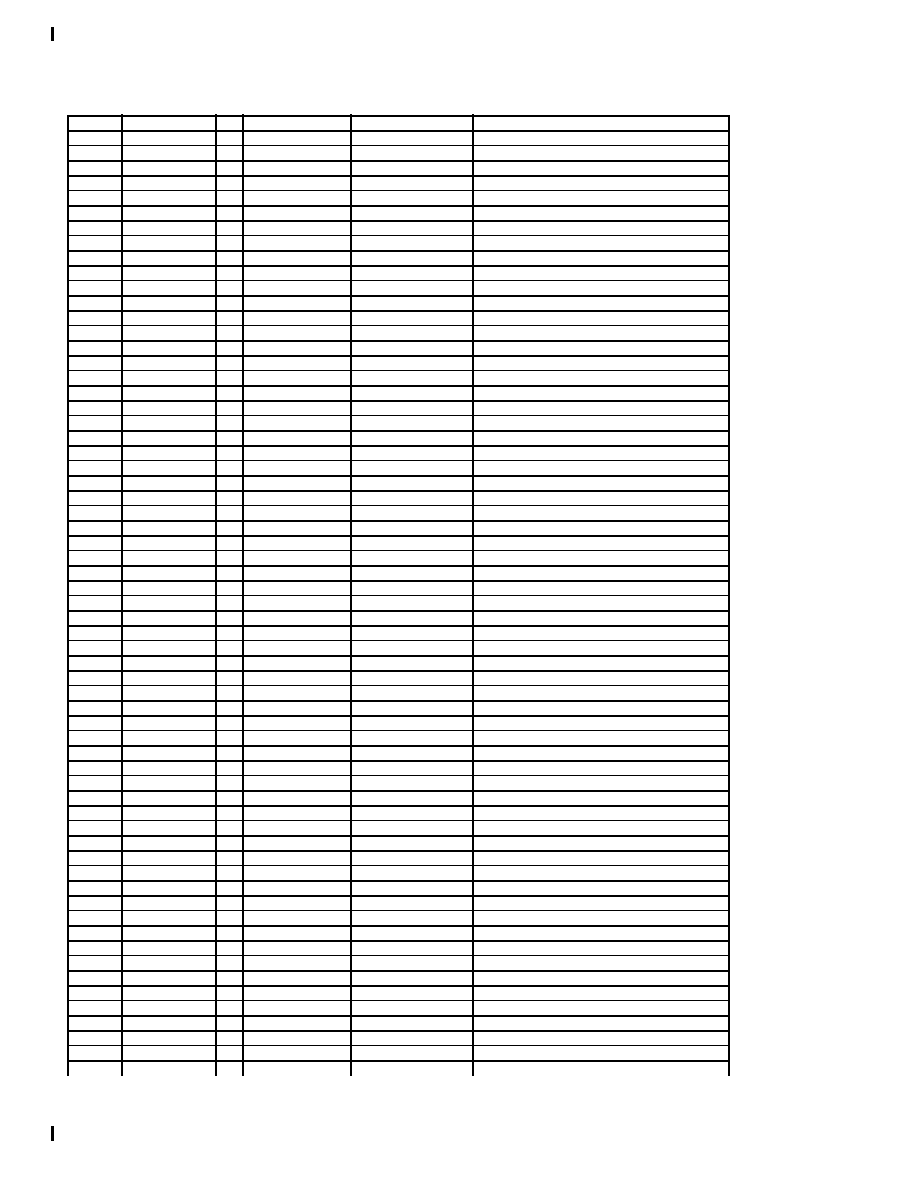

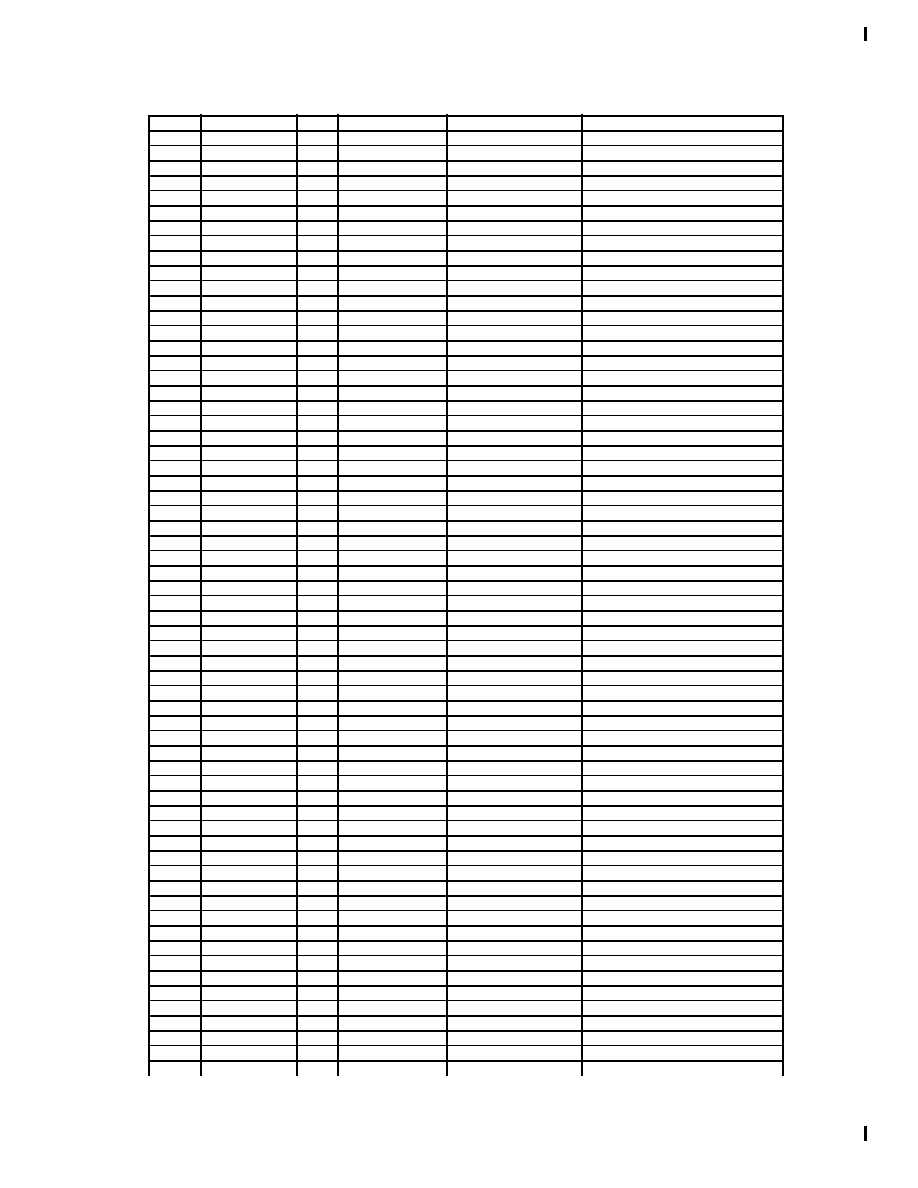

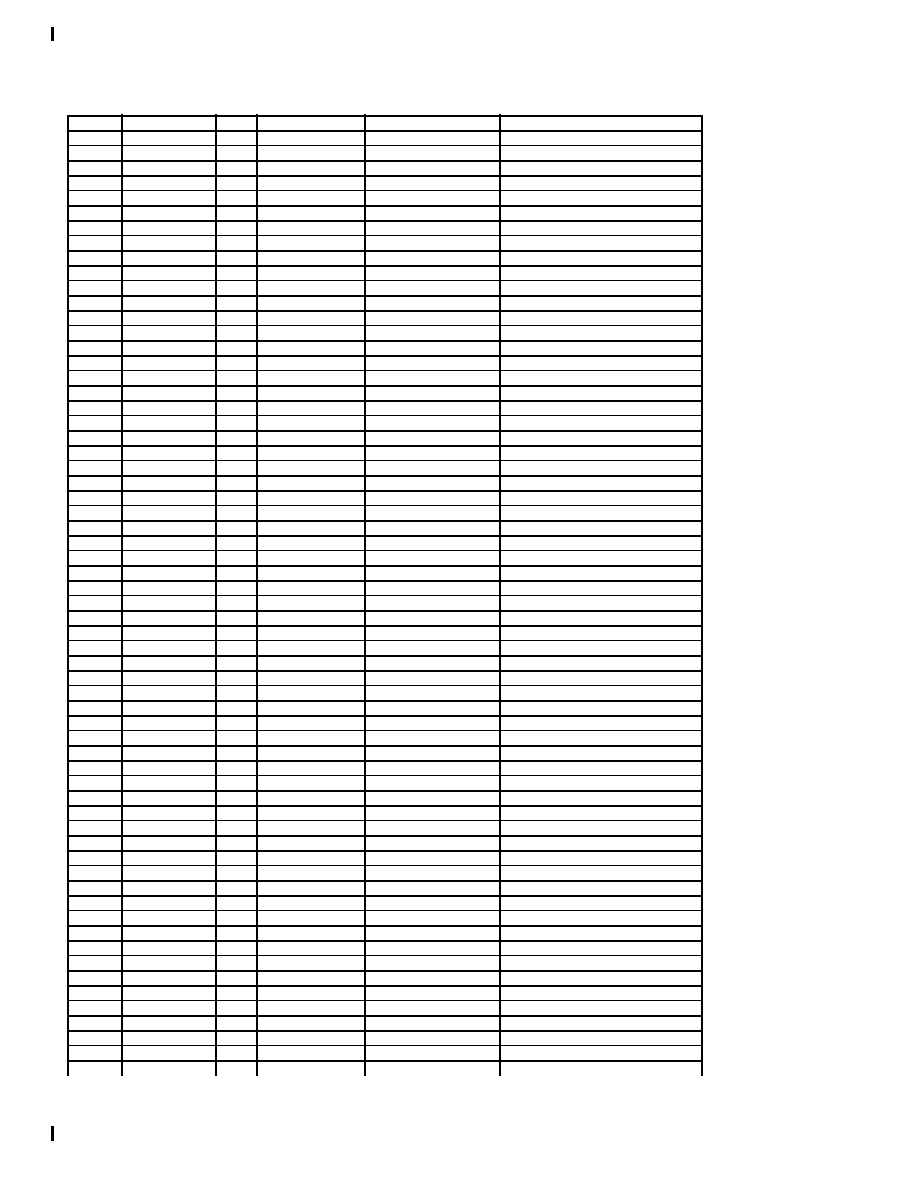

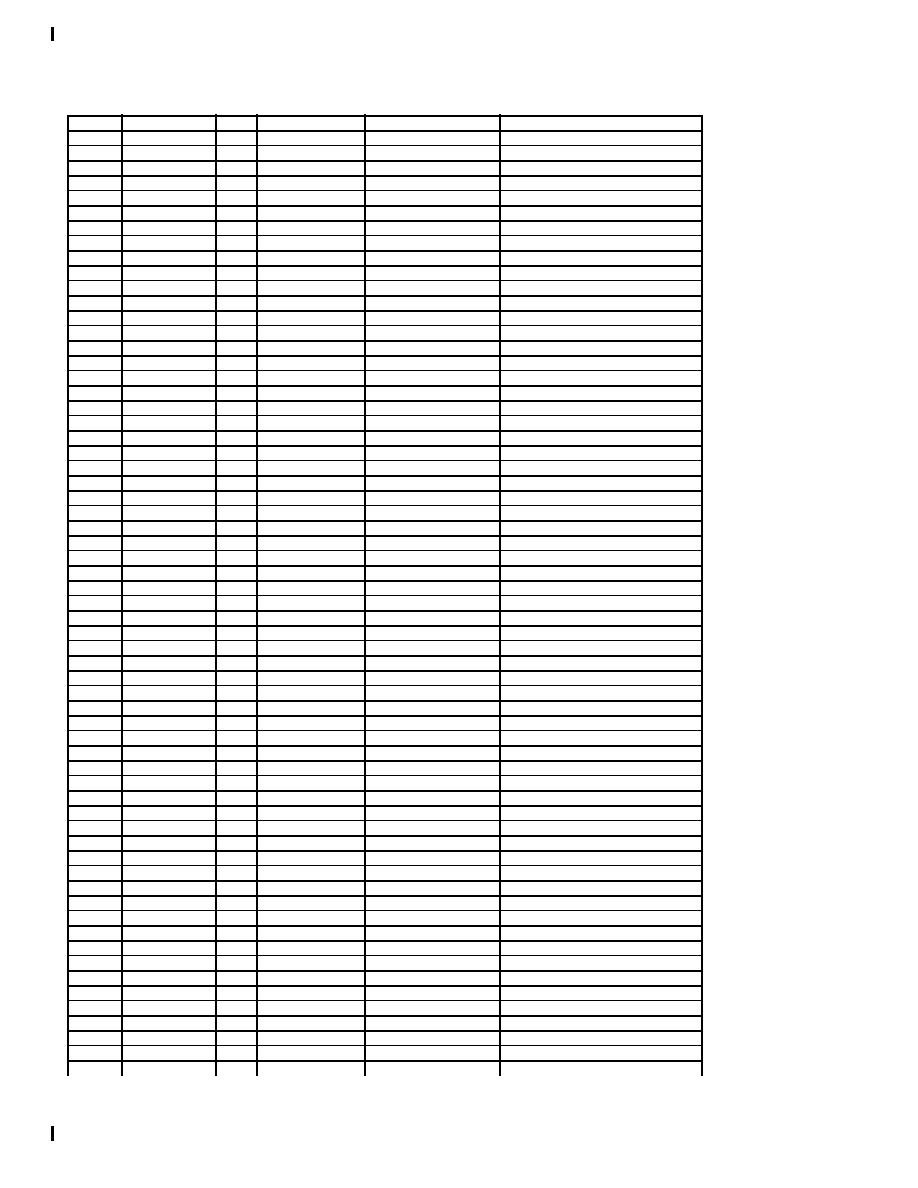

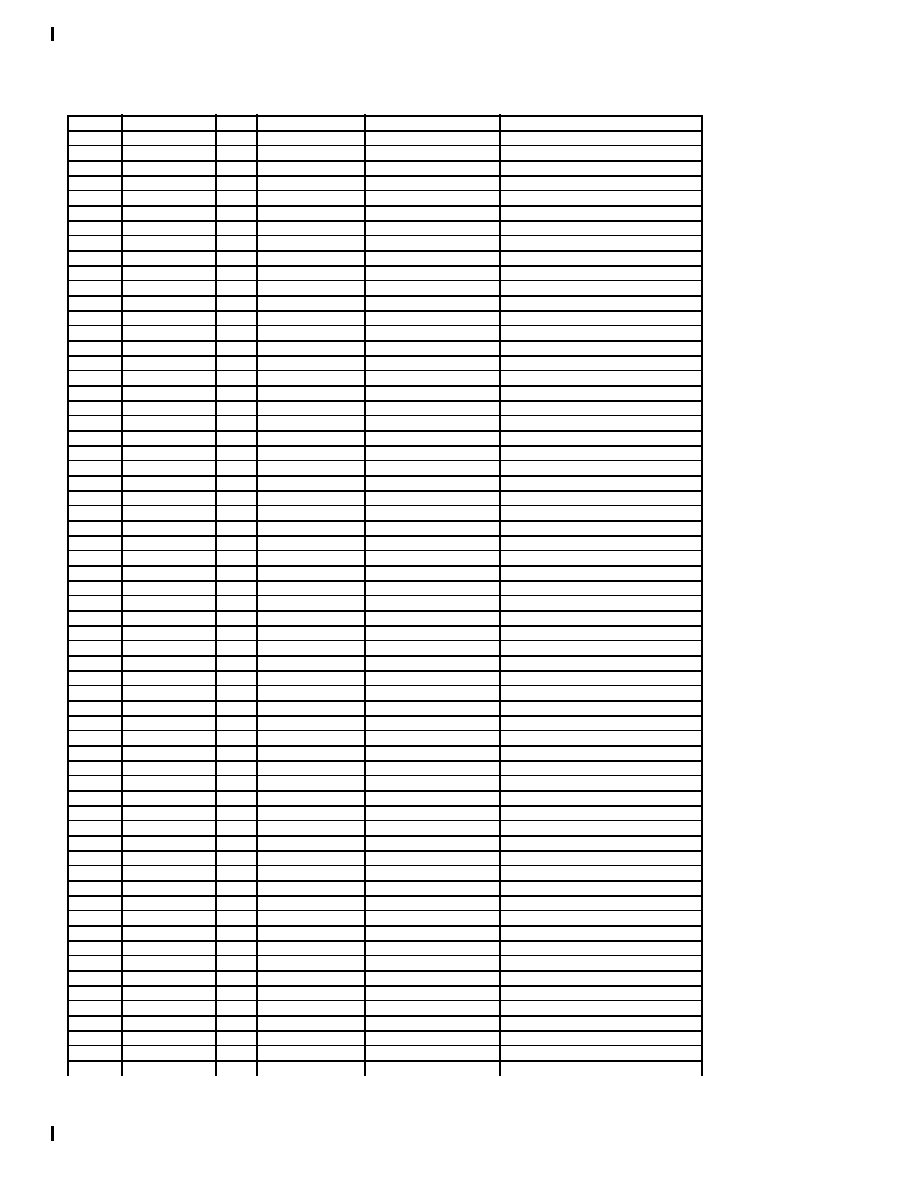

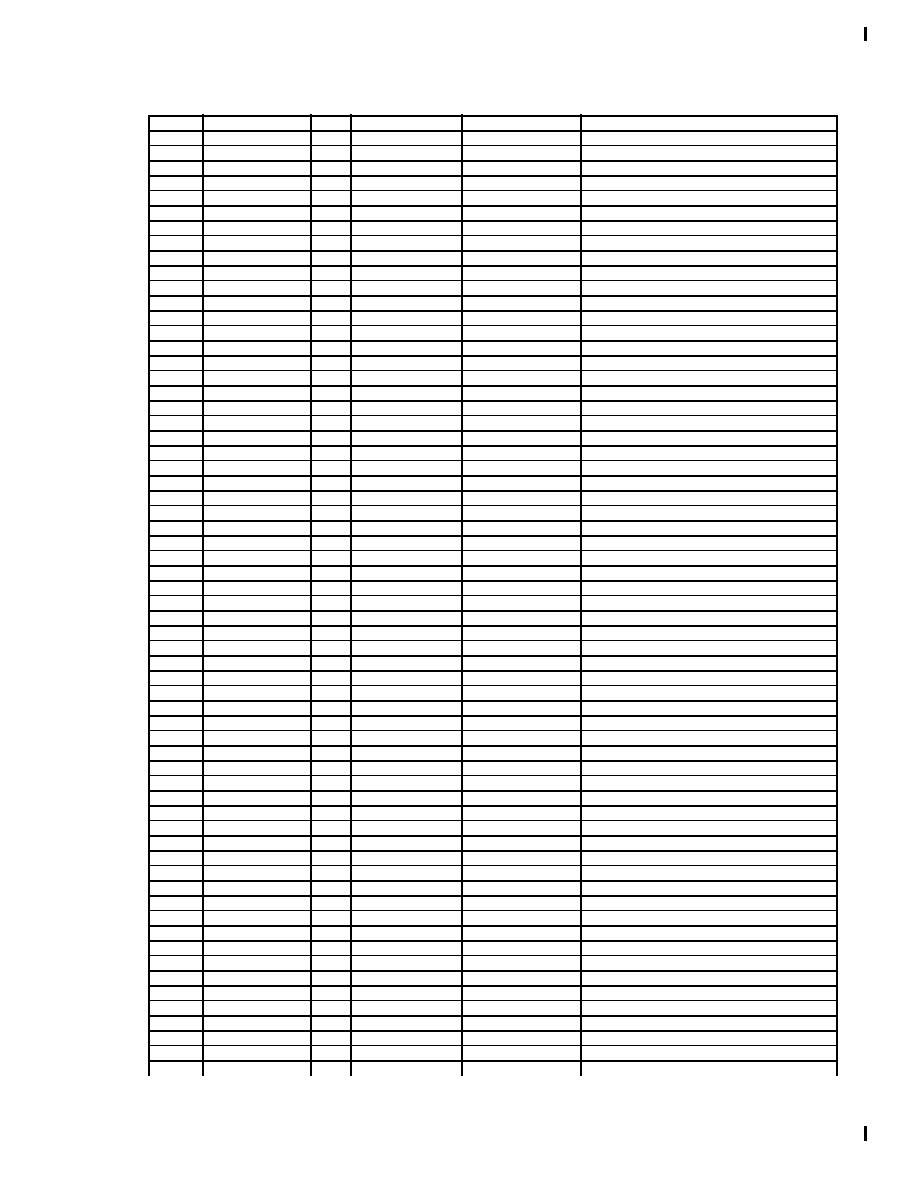

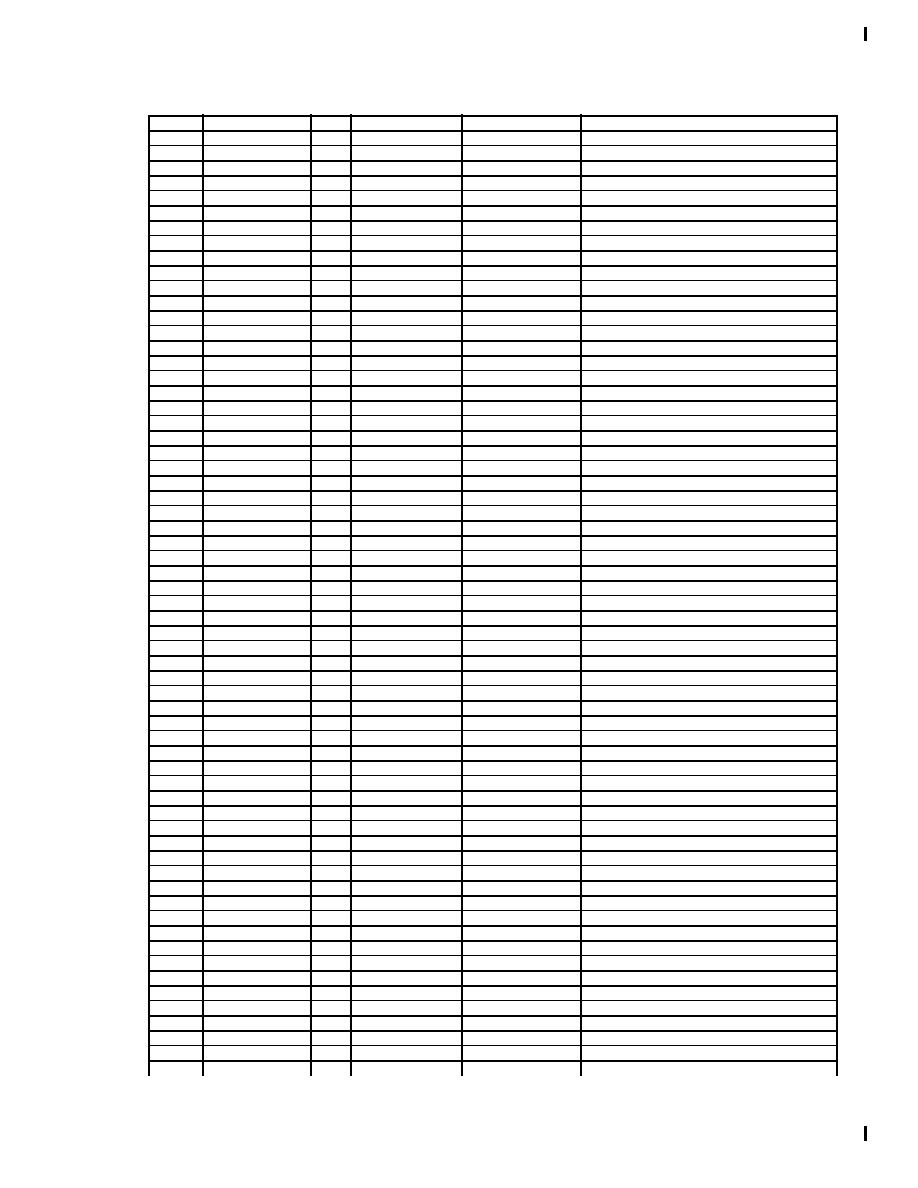

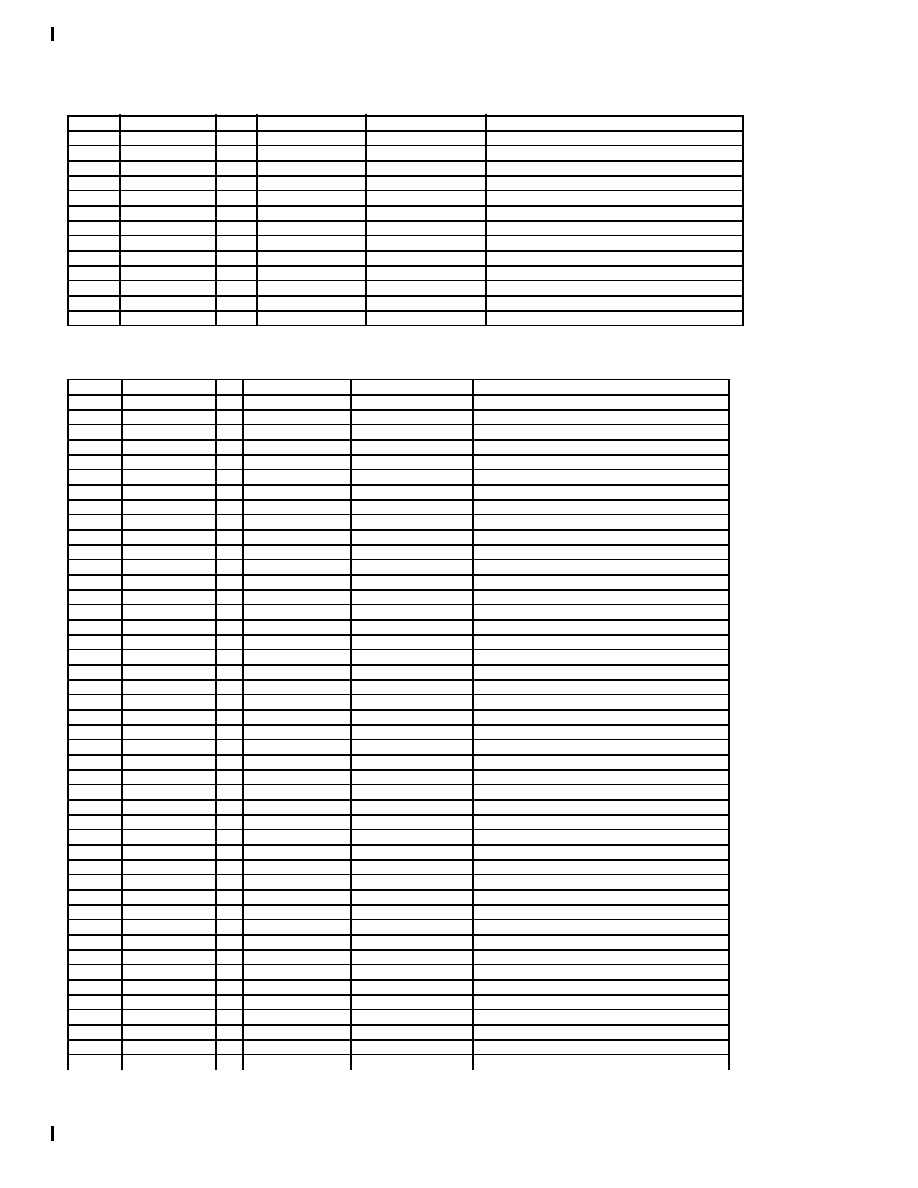

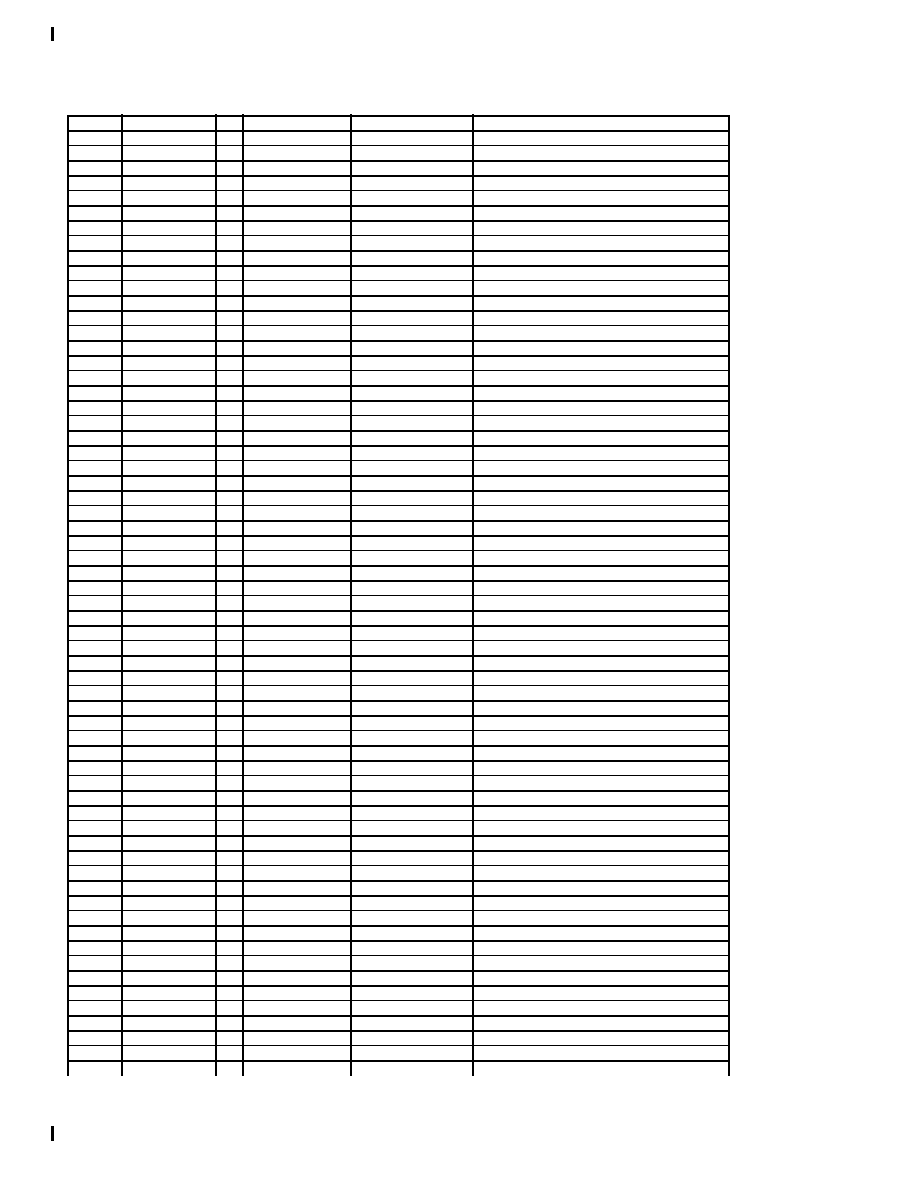

2.2.1.2

PXB Signal List

Component-Specific Support Signals

9

CRESET#

LVTTL O

PWRGD

LVTTL I

ERR[1:0]#

LVTTL I/OD

PWRGDB

LVTTL O

HCLKIN

2.5V

I

RESET#

AGTL+ I/O

INTREQ#

LVTTL O

SMIACT#

LVTTL O

TOTAL SIGNALS

348

PCI Bus Interface (2 per PXB: A,B)

2 x 61

P(A,B)AD[31:0]

PCI

I/O

P(A,B)PAR

PCI

I/O

P(A,B)C/BE[3:0]#

PCI

I/O

P(A,B)PERR#

PCI

I/O

P(A,B)CLKFB

LVTTL I

P(A,B)REQ[5:0]#

PCI

I

P(A,B)CLK

LVTTL O

P(A,B)RST#

PCI

O

P(A,B)DEVSEL#

PCI

I/O

P(A,B)SERR#

PCI

OD

P(A,B)FRAME#

PCI

I/O

P(A,B)STOP#

PCI

I/O

P(A,B)GNT[5:0]#

PCI

O

P(A,B)TRDY#

PCI

I/O

P(A,B)IRDY#

PCI

I/O

P(A,B)XARB#

PCI

I

P(A,B)LOCK#

PCI

I/O

PCI Bus Interface / Non-Duplicated (one set per PXB)

6

ACK64#

PCI

I/O

PHLDA#

PCI

O

MODE64#

PCI

I

REQ64#

PCI

I/O

PHOLD#

PCI

I

WSC#

PCI

O

Expander Interface (one per PXB)

30

XADS#

AGTL+ I/O

XHSTBP#

AGTL+ I

XBE[1:0]#

AGTL+ I/O

XIB

AGTL+ O

XBLK#

AGTL+ I

XPAR#

AGTL+ I/O

XCLK

CMOS I

XRST#

AGTL+ I

XD[15:0]#

AGTL+ I/O

XXRTS#

AGTL+ O

XHRTS#

AGTL+ I

XXSTBN#

AGTL+ O

XHSTBN#

AGTL+ I

XXSTBP#

AGTL+ O

Common Support Signals

12

CRES[1:0]

Analog

I

TMS

2.5V

I

TCK

2.5V

I

TRST#

2.5V

I

TDI

2.5V

I

VCCA (3)

Analog

I

TDO

2.5V

OD

VREF (2)

Analog

I

Component-Specific Support Signals

8

INTRQ(A,B)#

PCI

OD

PIIXOK#

LVTTL I

P(A,B)MON[1:0]#

LVTTL I/OD

PWRGD

LVTTL I

TOTAL SIGNALS

177

Intel

Æ

450NX PCIset

2-5

2.2 Summary

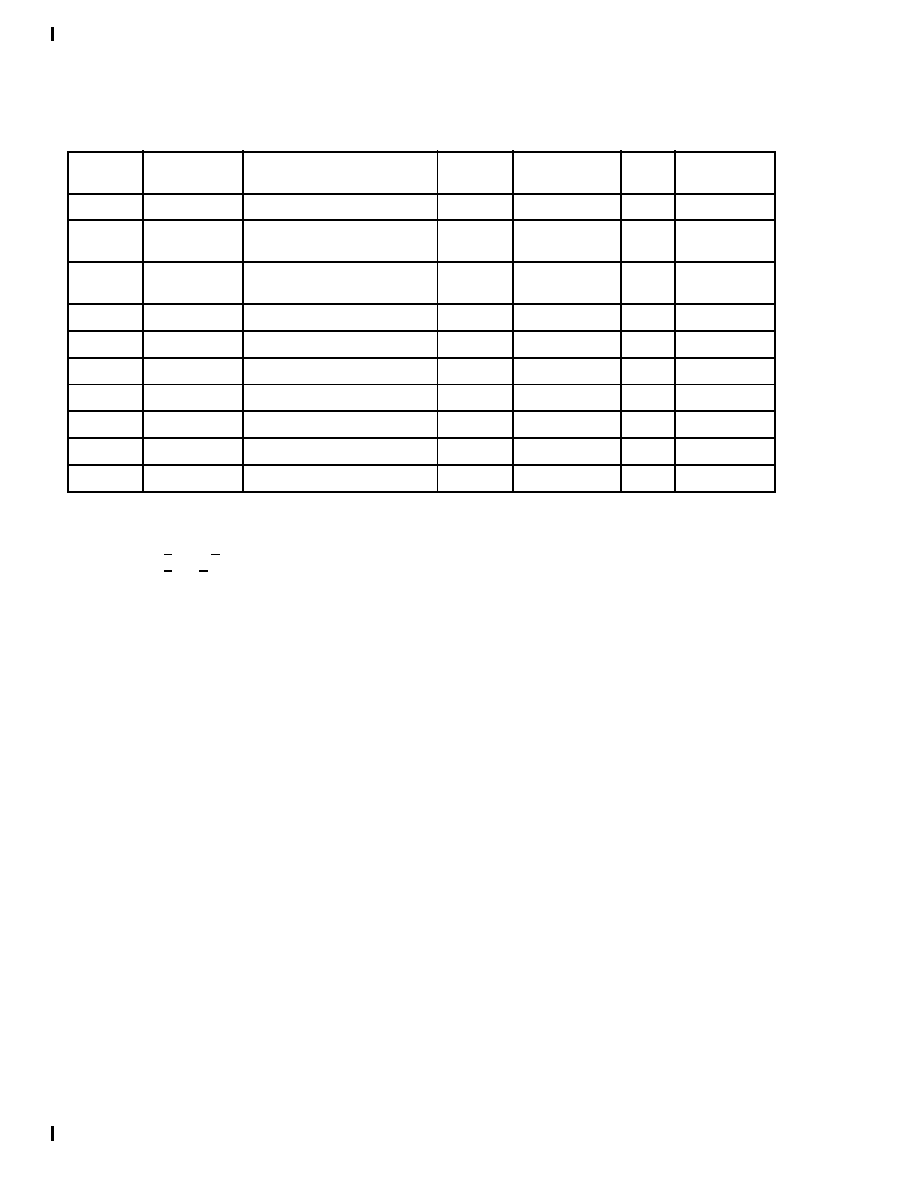

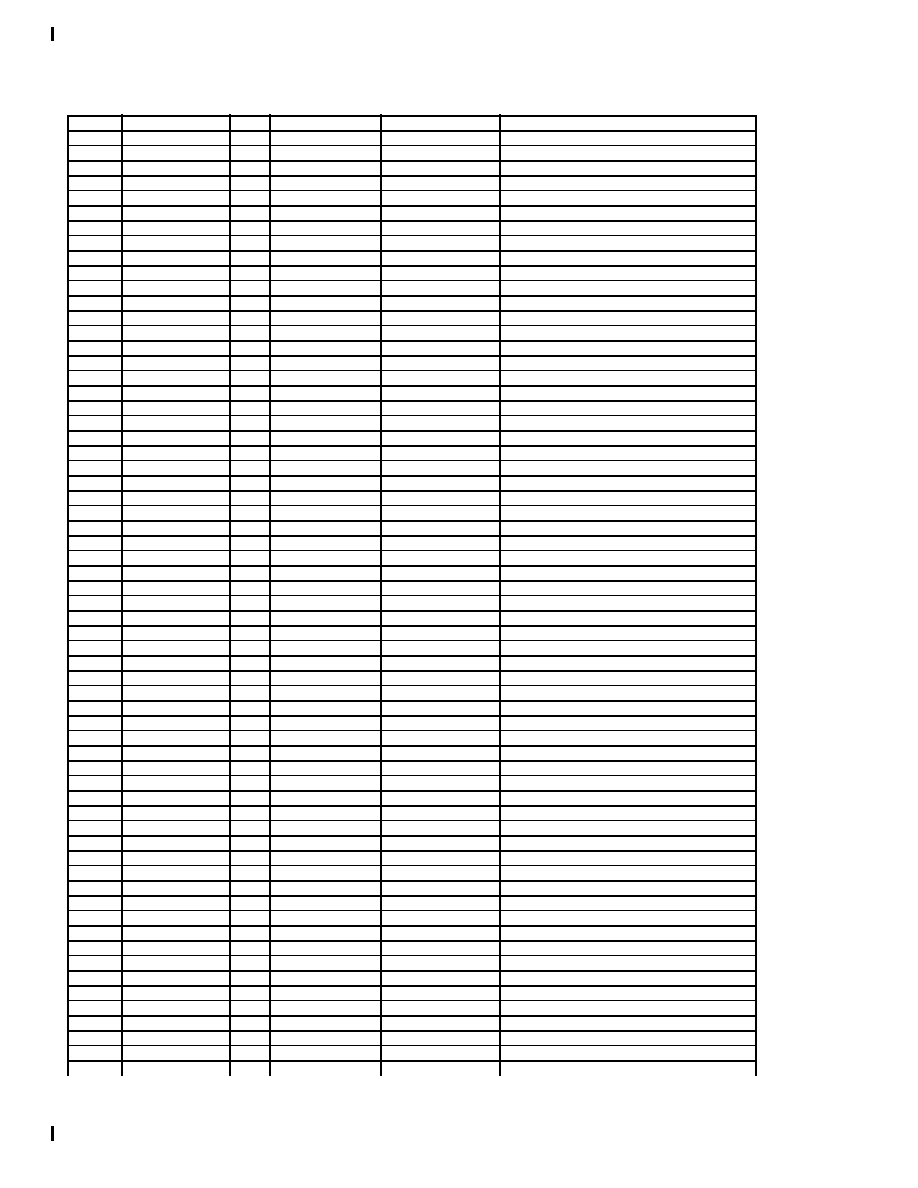

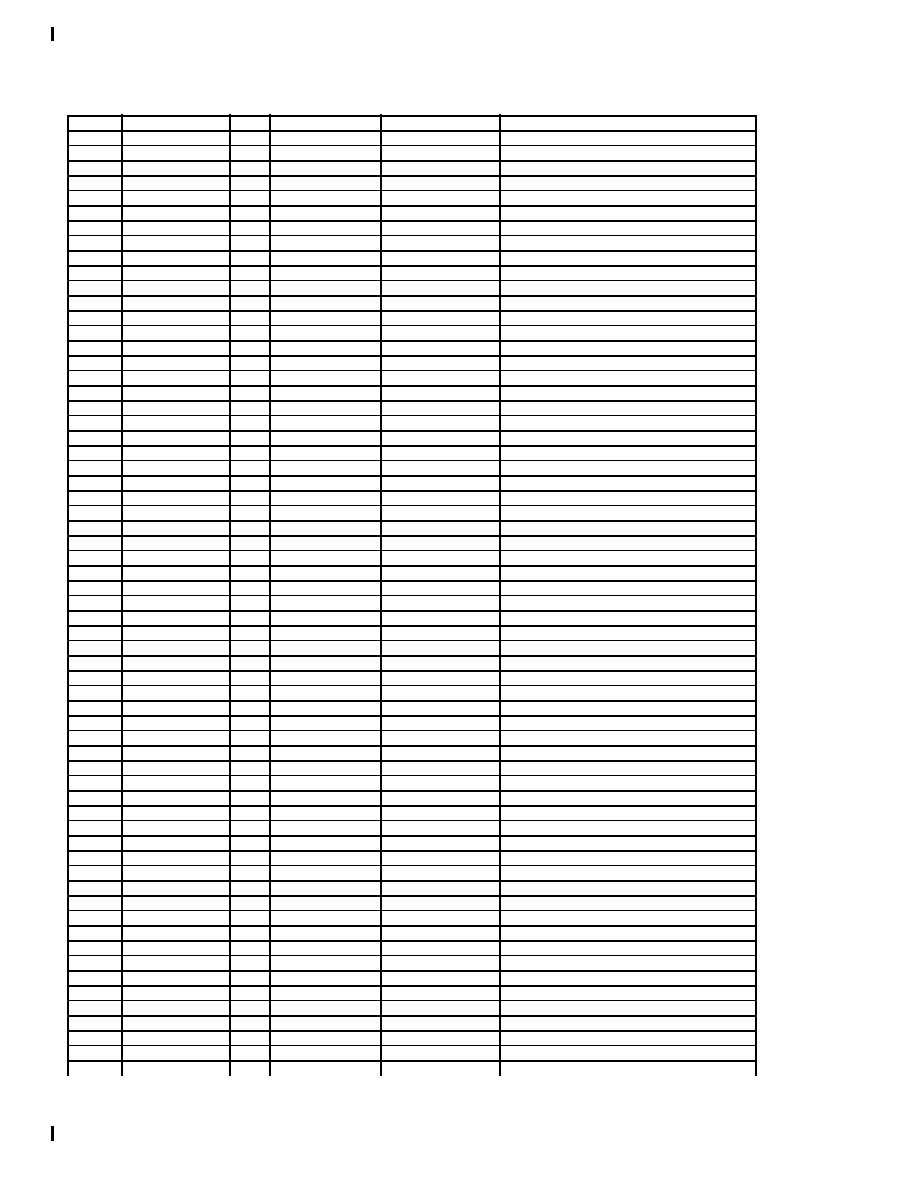

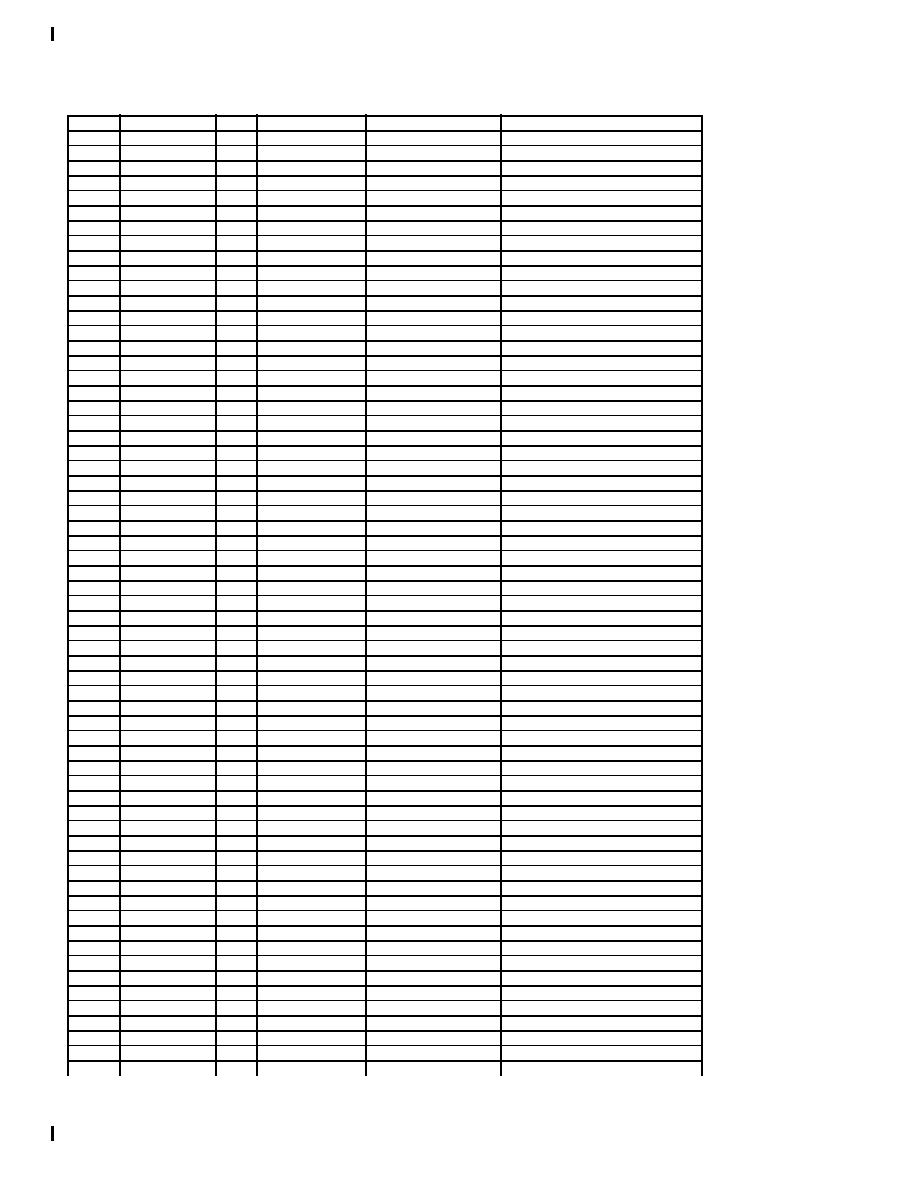

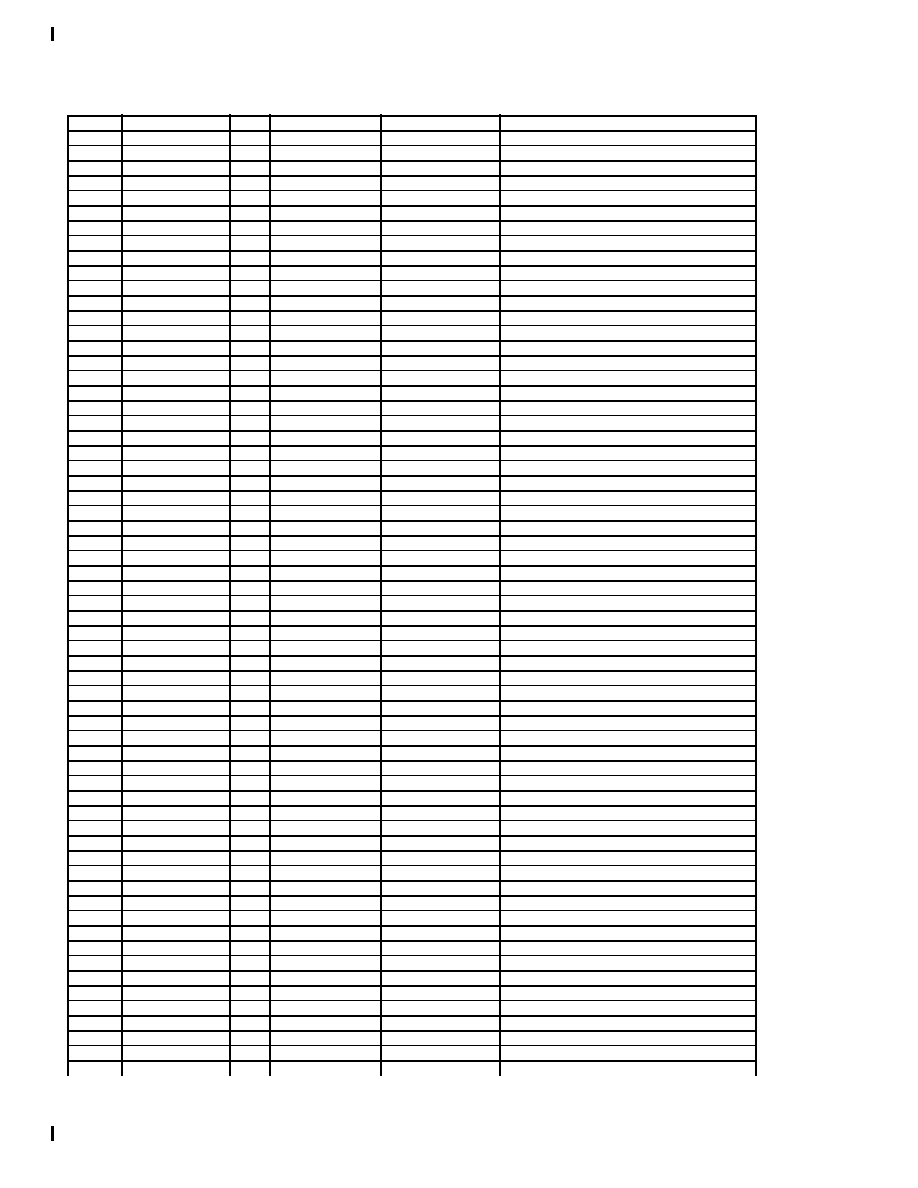

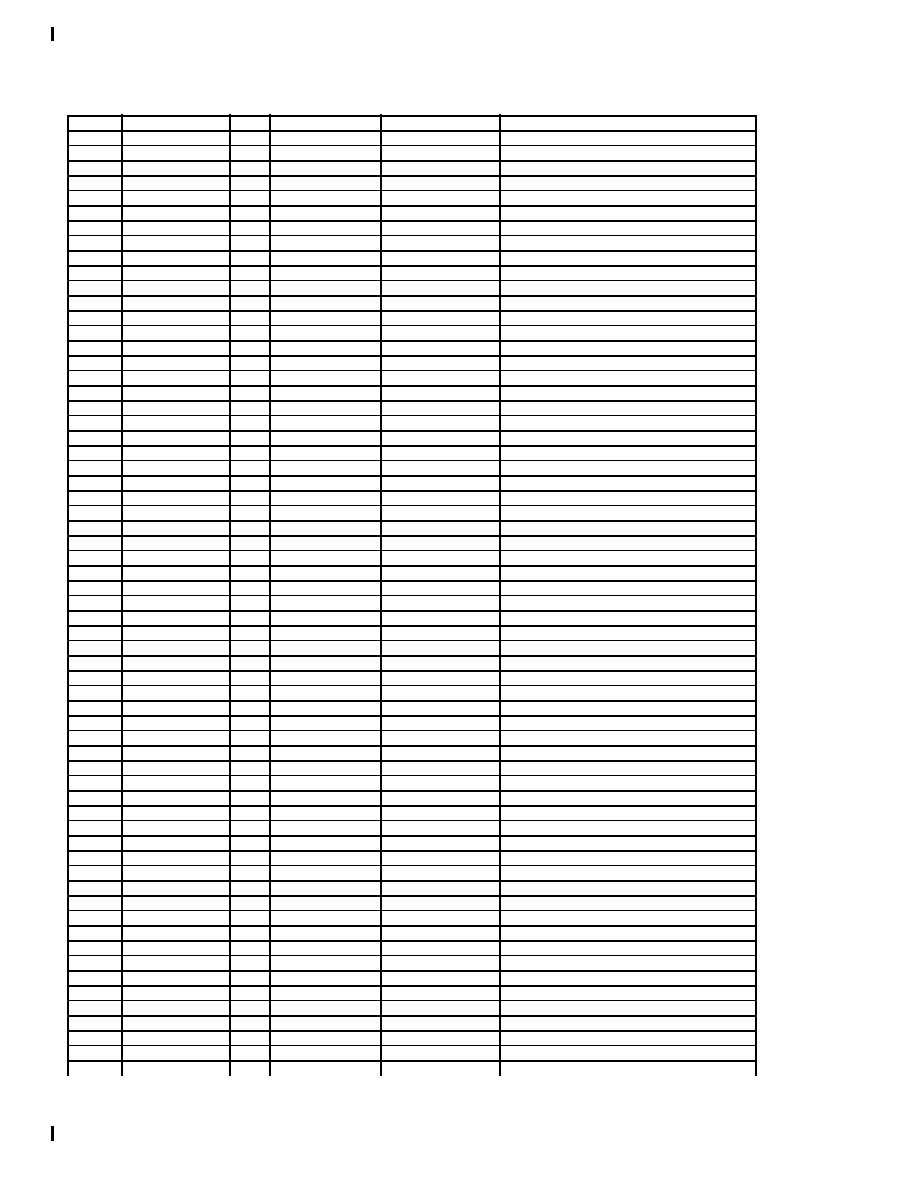

2.2.1.3

RCG Signal List

2.2.1.4

MUX Signal List

Memory Subsystem / External Interface

27

BANK[2:0]#

AGTL+ I

MRESET#

AGTL+ I

CARD#

AGTL+ I

PHIT#

AGTL+ O

CMND[1:0]#

AGTL+ I

RCMPLT#

AGTL+ O

CSTB#

AGTL+ I

RHIT#

AGTL+ O

GRCMPLT#

AGTL+ I/O

ROW#

AGTL+ I

MA[13:0]#

AGTL+ I

Memory Subsystem / Internal Interface

123

ADDR(A,B,C,D)[13:0]

LVTTL O

LRD#

AGTL+ O

AVWP#

AGTL+ O

RAS(A,B,C,D)(a,b,c,d)[1:0]#

LVTTL O

CAS(A,B,C,D)(a,b,c,d)[1:0]#

LVTTL O

WDME#

AGTL+ O

LDSTB#

AGTL+ O

WE(A,B,C,D)(a,b)#

LVTTL O

Common Support Signals

10

CRES[1:0]

Analog

I

TMS

2.5V

I

TCK

2.5V

I

TRST#

2.5V

I

TDI

2.5V

I

VCCA

Analog

I

TDO

2.5V

OD

VREF (2)

Analog

I

Component-Specific Support Signals

4

BANKID#

LVTTL I

DR50T#

LVTTL I

DR50H#

LVTTL I

HCLKIN

2.5V

I

TOTAL SIGNALS

173

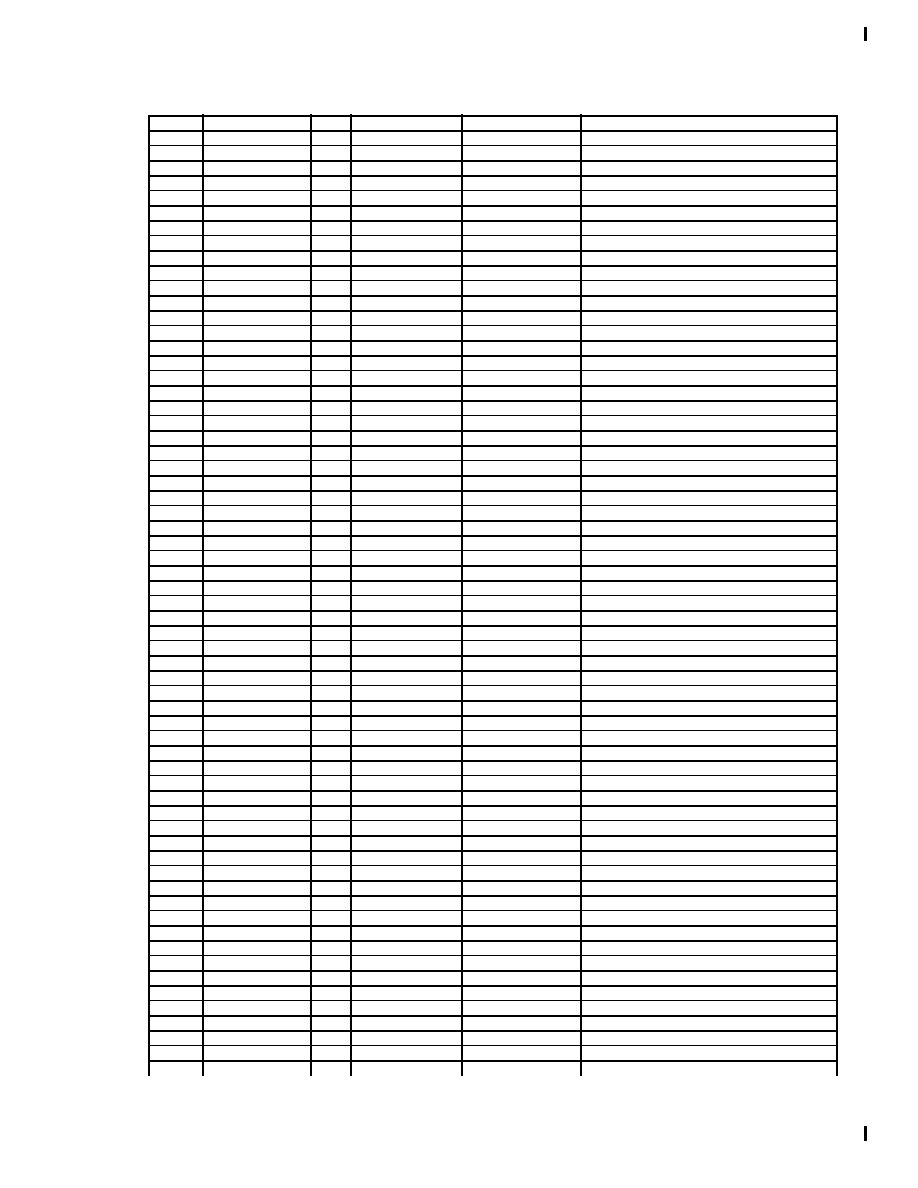

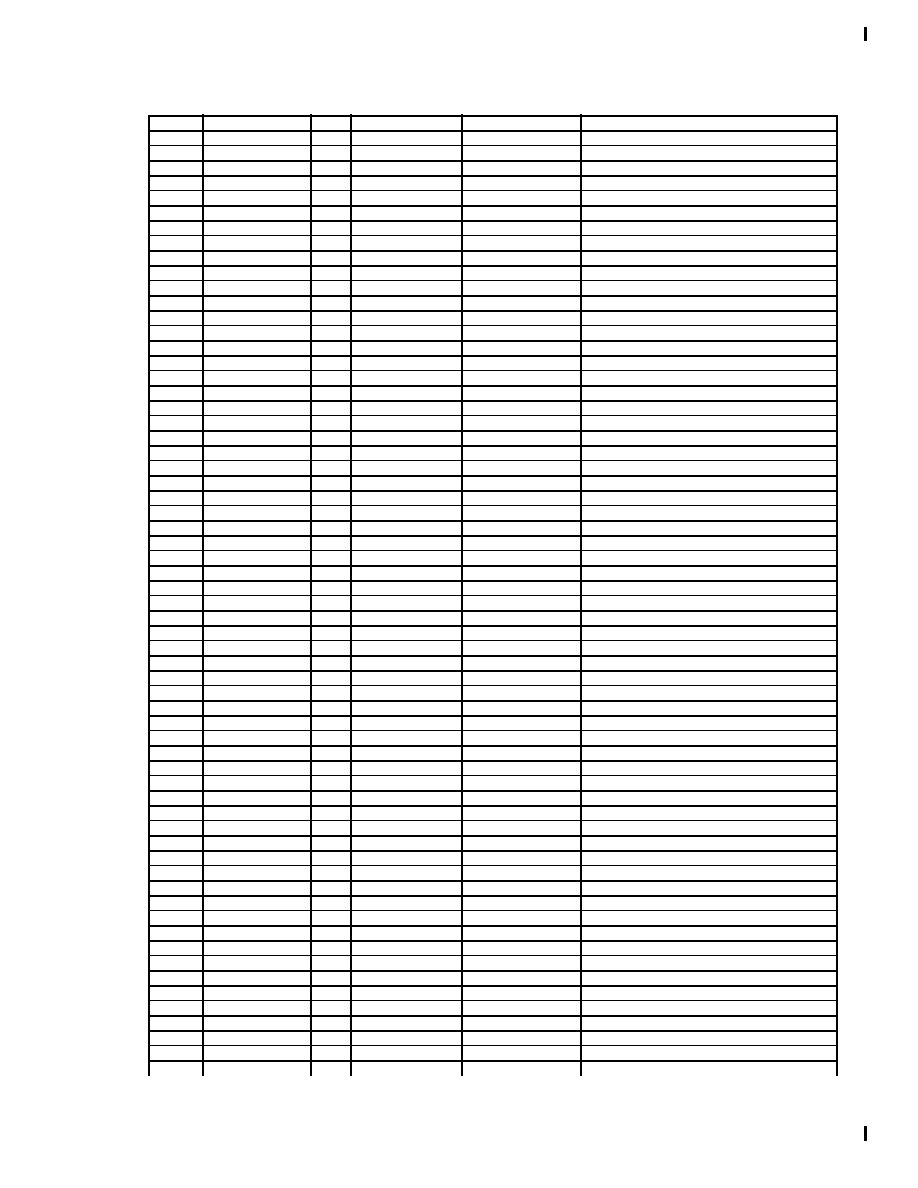

Memory Subsystem / External Interface

48

DCMPLT#

AGTL+ I/O

DVALID#

AGTL+ I

DOFF[1:0]#

AGTL+ I

GDCMPLT#

AGTL+ I/O

DSEL#

AGTL+ I

MD[35:0]#

AGTL+ I/O

DSTBP[1:0]#

AGTL+ I/O

MRESET#

AGTL+ I

DSTBN[1:0]#

AGTL+ I/O

WDEVT#

AGTL+ I

Memory Subsystem / Internal Interface

148

AVWP#

AGTL+ I

Q1D[35:0]

LVTTL I/O

LDSTB#

AGTL+ I

Q2D[35:0]

LVTTL I/O

LRD#

AGTL+ I

Q3D[35:0]

LVTTL I/O

Q0D[35:0]

LVTTL I/O

WDME#

AGTL+ I

Common Support Signals

10

CRES[1:0]

Analog

I

TMS

2.5V

I

TCK

2.5V

I

TRST#

2.5V

I

TDI

2.5V

I

VCCA

Analog

I

TDO

2.5V

OD

VREF (2)

Analog

I

Component-Specific Support Signals

1

HCLKIN

2.5V

I

TOTAL SIGNALS

207

2-6

Intel

Æ

450NX PCIset

2. Signal Descriptions

2.3

System Interface

The MIOC provides the Intel 450NX PCIset's sole connection to the system bus. This section

describes the Intel 450NX PCIset-specific uses of these signals.

2.3.1

System / MIOC Interface

A[35:3]#

Address Bus

AGTL+ I/O

A[35:3]#

connect to the system address bus. During processor cycles the

A[35:3]

# are inputs. The MIOC drives

A[35:3]#

during snoop cycles on behalf

of PCI initiators. The address bus is inverted on the system bus.

ADS#

Address Strobe

AGTL+ I/O

The system bus owner asserts

ADS#

to indicate the first of two cycles of a

request phase.

AERR#

Address Parity Error

AGTL+ I/O

AERR# is asserted by any agent that detects an address parity error.

AP[1:0]#

Address Parity

AGTL+ I/O

Parity protection on the address bus.

AP#[1]

covers

A#[35:24

], and

AP#[0]

covers

A#[23:3]

. They are valid on both cycles of the request.

BERR#

Bus Error

AGTL+ I/O

This signal is asserted by any agent that observes an unrecoverable bus

protocol violation.

BINIT#

Bus Initialization

AGTL+ I/O

BINIT#

is asserted to re-initialize the bus state machines. The MIOC will

terminate any ongoing PCI transaction and reset its inbound and outbound

queues. No configuration registers or error logging registers are affected.

BNR#

Block Next Request

AGTL+ I/O

Used to block the current request bus owner from issuing a new request.

BP[1:0]#

Performance Monitoring

LVTTL I/OD

In normal operation, the MIOC can be configured to drive performance

monitoring data out of either of these pins, similar in function to the

BP

pins

provided on the processors.

BPRI#

Priority Agent Bus Request

AGTL+ O

The MIOC is the only Priority Agent on the system bus. It asserts this signal

to obtain ownership of the address bus. BPRI# has priority over symmetric

bus requests.

BREQ[0]#

Symmetric Agent Bus Request

AGTL+ O

This signal is asserted by the MIOC when

RESET#

is asserted, to select the

boot processor. It is deasserted 2 host clocks after

RESET

# is deasserted.

Intel

Æ

450NX PCIset

2-7

2.3 System Interface

D[63:0]#

Data

AGTL+ I/O

These signals are connected to the system data bus. The data signals are

inverted on the system bus.

DBSY#

Data Bus Busy

AGTL+ I/O

Used by the data bus owner to hold the data bus for transfers requiring more

than one cycle.

DEP[7:0]#

Data Bus ECC/Parity

AGTL+ I/O

These signals provide parity or ECC for the

D#[63:0]

signals. The MIOC only

provides ECC.

DEFER#

Defer

AGTL+ I/O

DEFER#

is driven by the addressed agent to indicate that the transaction

cannot be guaranteed to be globally observed.

DRDY#

Data Ready

AGTL+ I/O

Asserted for each cycle that valid data is transferred.

HIT#

Hit

AGTL+ I

The MIOC never asserts

HIT#;

it has no cache, and never snoop stalls.

HITM#

Hit Modified

AGTL+ I

The MIOC never asserts

HITM#

; it has no cache, and never snoop stalls.

INIT#

Soft Reset

2.5V OD

INIT#

may be asserted to request a soft reset of the processors. During a

system hard reset, the

INIT#

signal may be optionally asserted to cause the

processors to initiate their BIST. The

INIT#

signal is not asserted during

power-good reset.

LOCK#

Lock

AGTL+ I

All system bus cycles sampled with the assertion of

LOCK#

and

ADS#

, until

the negation of

LOCK#,

must be atomic; i.e., no PCI activity to DRAM is

allowed and the locked cycle must be translated to PCI if targeted for the PCI

bus.

REQ[4:0]#

Request Command

AGTL+ I/O

Asserted during both clocks of a request phase. In the first clock, the signals

define the transaction type to a level which is sufficient to begin a snoop

request. In the second clock, the signals carry additional information to define

the complete transaction type.

RP#

Request Parity

AGTL+ I/O

Even parity protection on

ADS#

and

REQ[4:0]#.

It is valid on both cycles of

the request.

RS[2:0]#

Response Signals

AGTL+ I/O

Indicate response type as shown below:

000

Idle state

100

Hard failure

001

Retry

101

No Data

010

Deferred

110

Implicit writeback

011

reserved

111

Normal Data

2-8

Intel

Æ

450NX PCIset

2. Signal Descriptions

RSP#

Response Parity Signal

AGTL+ I/O

Parity protection on

RS[2:0]#

.

TRDY#

Target Ready

AGTL+ I/O

Indicates that the target of the system transaction is able to enter the data

transfer phase.

2.3.2

Third-Party Agent / MIOC Interface

The following signals provide support for an additional non-processor, third-party agent

(TPA) on the system bus. Such agents may need priority access to the system bus itself, or may

need to intervene in transactions between the processors and the Intel 450NX PCIset.

IOGNT#

I/O Grant

LVTTL I

The

IOGNT#

signal has two modes: Internal Arbitration Mode and External

Arbitration Mode, selected by a bit in the MIOC's

CONFIG

register. In

Internal Arbitration Mode

IOGNT#

is an input from another bridge device

which is requesting ownership of the

BPRI#

signal. In external arbitration

mode, this bridge requests

BPRI#

ownership from an external bridge arbiter.

IOGNT#

should be asserted by the external arbiter when this MIOC has been

granted ownership of the

BPRI#

signal.

IOREQ#

I/O Request

LVTTL O

The

IOREQ#

signal has two modes: Internal Arbitration Mode and External

Arbitration Mode, selected by a bit in the MIOC's

CONFIG

register. In

Internal Arbitration Mode

IOREQ#

is the grant to another bridge device that

is making a request for ownership of the

BPRI#

signal. In external arbitration

mode this signal is asserted to request ownership of the

BPRI#

signal.

TPCTL[1:0]

Third Party Control

LVTTL I

These signals allow an agent participating in transactions between the Intel

450NX PCIset and another bus agent as a "third-party" to control the

responses generated by the Intel 450NX PCIset.

2.4

PCI Interface

2.4.1

Primary Bus

There are two primary PCI buses per PXB, identified as the "

a

" bus and the "

b

" bus groups.

Each signal name includes a "

p

", indicating the PCI bus port;

p

=

A

or

B

.

00

Accept

The MIOC will accept the request and provide the

normal response.

01

reserved

≠

10

Retry

The MIOC will generate a RETRY response.

11

Defer

The MIOC will generate a DEFERRED response.

Intel

Æ

450NX PCIset

2-9

2.4 PCI Interface

PpAD[31:0]

PCI Address/Data

PCI I/O

PCI Address and Data signals are multiplexed on this bus. The physical byte

address is output during the address phase and the data follows in the

subsequent data phase(s).

PpC/BE[3:0]#

C

ommand/Byte Enable

PCI I/O

PCI Bus Command and Byte Enable signals are multiplexed on the same pins.

During the address phase of a transaction,

C/BE[3:0]#

define the bus

command. During the data phase C/

BE[3:0]#

are used as byte enables.

PpCLK

PCI Clock

LVTTL O

This signal is an output with a derived frequency equal to 1/3 of the system

bus frequency.

PpCLKFB

PCI Clock Feedback

LVTTL I

This signal is connected to the output of a low skew PCI clock buffer tree. It is

used to synchronize the PCI clock driven from

PpCLK

to the clock used for

the internal PCI logic.

PpDEVSEL#

Device Select

PCI I/ O

DEVSEL# is driven by the device that has decoded its address as the target of

the current access.

PpFRAME#

Frame

PCI I/O

The PXB asserts

FRAME#

to indicate the start of a bus transaction. While

FRAME#

is asserted, data transfers continue. When

FRAME#

is negated, the

transaction is in the final data phase.

FRAME#

is an input when the PXB acts

as a PCI target.

PpIRDY#

Initiator Ready

PCI I/O

This signal is asserted by a master to indicate its ability to complete the

current data transfer.

IRDY#

is an output when the PXB acts as a PCI initiator

and an input when the PXB acts as a PCI target.

PpPAR

Parity

PCI I/O

PAR

is driven by the PXB when it acts as a PCI initiator during address and

data phases for a write cycle, and during the address phase for a read cycle.

PAR

is driven by the PXB when it acts as a PCI target during each data phase

of a PCI memory read cycle. Even parity is generated across

AD[31:0

] and

C/BE[3:0]#

.

PpRST#

PCI Reset

PCI O

PCI Bus Reset forces the PCI interfaces of each device to a known state. The

PXB generates a minimum 1 ms pulse on

RST#

.

PpPERR#

PCI Parity Error

PCI I/O

Pulsed by an agent receiving data with bad parity one clock after

PAR

is

asserted. The PXB will generate

PERR#

active if it detects a parity error on

the PCI bus and the

PERR#

Enable bit in the

PCICMD

register is set.

PpLOCK#

Lock

PCI I/O

LOCK#

indicates an exclusive bus operation and may require multiple

transactions to complete. It is possible for different agents to use the PCI Bus

while a single initiator retains ownership of the

LOCK#

signal.

2-10

Intel

Æ

450NX PCIset

2. Signal Descriptions

PpTRDY#

Target Ready

PCI I/O

The assertion of

TRDY#

indicates the target agent's ability to complete the

current data phase of the transaction.

TRDY#

is an input when the PXB acts as

a PCI master and an output when the PXB acts as a PCI target.

PpSERR#

System Error

PCI OD

The PXB asserts this signal to indicate an error condition.

PpSTOP#

Stop

PCI I/O

STOP#

is used for disconnect, retry, and abort sequences on the PCI Bus. It is

an input when the PXB acts as a PCI initiator and an output when the PXB

acts as a PCI target.

2.4.2

64-bit Access Support

These signals are used only in 64-bit bus mode. There is one set per PXB.

ACK64#

64-bit Access Acknowledge

PCI I/O

This signal is driven by the accessed target to indicate it's willingness to

transfer 64-bit data. When the PXB is the bus target, this signal is an output.

If asserted, the PXB will transfer 64-bit data; otherwise, the PXB will transfer

32-bit data. When the PXB is the bus master, this signal is an input.

MODE64#

64-bit Bus Mode

PCI I

A strapping pin that selects whether the pair of 32-bit PCI buses are used as

two independent 32-bit buses, or linked together as a single 64-bit bus. If

asserted, the buses are used as a single 64-bit bus: the 32-bit data bus of the

PCI "B" port becomes the high Dword of the 64-bit bus. An internal pull-up

insures that the pin appears deasserted if left unconnected.

REQ64#

64-bit Access Request

PCI I/O

This signal is driven by the bus master to indicate it's desire to transfer 64-bit

data. When the PXB is the bus master, this signal is an output. The PXB will

assert this signal if it can transfer 64-bit data. When the PXB is the bus target,

this signal is an input.

The following 64-bit extension signals are mapped from the existing "B" port signals:

AD[63:32]

from

PBAD[31:0]

C/BE[7:4]

from

PBC/BE[3:0]

PAR64

from

PBPAR

All other controls and status signals in 64-bit operation are taken from the Bus "A" signal set.

Unused pins on the "B" side should be tied inactive.

2.4.3

Internal vs. External Arbitration

Each PXB supports both internal arbitration and external arbitration, independently for each

PCI bus. While in internal arbitration mode, six pairs of request/grant signals are used to

support up to six PCI masters on the bus (plus the PXB itself, and the PIIX4E south bridge on

Intel

Æ

450NX PCIset

2-11

2.4 PCI Interface

the compatibility PCI bus). While in external arbitration mode, only one pair (#0) are used,

and have different meanings.

Each signal name includes a "

p

", indicating the PCI bus port;

p

=

A

or

B

.

PpXARB#

External Arbitration Mode

PCI I

A strapping pin, sampled at the trailing edge of reset. If asserted, the PCI bus

is controlled using an external arbiter. If deasserted, the PCI bus is controlled

using the PXB's internal arbiter. An internal pull-up insures that the pin

appears deasserted if left unconnected.

Internal Arbitration Mode (per PCI bus, p=A,B)

PpREQ[5:0]#

PCI Bus Request

PCI I

Six independent PCI bus request signals used by the internal PCI arbiter for

PCI initiator arbitration. Unused signals should be strapped inactive.

PpGNT[5:0]#

PCI Grant

PCI O

Six independent PCI bus grant signals used by the internal PCI arbiter for PCI

initiator arbitration.

External Arbitration Mode (per PCI bus, p=A,B)

When operating in external arbitration mode,

REQ[5:1]#

and

GNT[5:1]#

signals are not used.

The

REQ[0]#

signal is redefined as

HGNT#

, and the

GNT[0]#

signal is redefined as

HREQ#

.

PpHREQ#

Host Request

PCI O

Generated by the PXB to the external PCI arbiter to request control of the PCI

bus to perform a Host-PCI access.

PpHGNT#

Host Grant

PCI I

Generated by the external PCI arbiter to grant the PCI bus to the PXB to

perform a Host-PCI transfer.

2.4.4

PIIX4E Interface

The compatibility PCI bus (PCI Bus 0A) supports a PIIX4E south bridge, and requires several

additional handshake signals, provided by the PXB. They are active only for Bus 0A.

NOTE

These signals, and the associated PHOLDA# and WSC# protocols, cannot be used with the PXB in

external arbiter mode.

PHOLD#

PCI Hold

PCI I

This signal is the PIIX4E's request for the PCI bus.

PHLDA#

PCI Hold Acknowledge

PCI O

This signal is driven by the PXB to grant PCI bus ownership to the PIIX4E.

2-12

Intel

Æ

450NX PCIset

2. Signal Descriptions

WSC#

Write Snoop Complete

PCI O

This signal is asserted active to indicate completion of snoop activity on the

system bus on the behalf of the last PCI-DRAM write transaction, and that it

is safe to send the APIC interrupt message.

2.5

Memory Subsystem Interface

The memory subsystem is comprised of the DRAM arrays and the associated RCGs and

MUXs. There is the external interface (between the MIOC and the memory subsystem), and

the internal interface (between the various parts of the memory subsystem.)

2.5.1

External Interface

BANK[2:0]#

Bank Selects

AGTL+ MIOC

RCG

These signals indicate which memory bank will service this access.

BANK[2:0]# are connected to all RCGs on both memory cards.

CARD[1:0]#

Card Selects

AGTL+ MIOC

RCG

These signals indicate which memory card will service this access. Valid

patterns in the Intel 450NX PCIset are

01b

=card0 and

10b

=card1, allowing

CARD[0]#

to be connected only to card 0 and

CARD[1]#

to be connected only

to card 1. Each

CARD

signal is connected to all RCGs on the given memory

card.

CMND[1:0]#

Access Command

AGTL+ MIOC

RCG

These signals encode the command of the current operation. CMND[1:0]# are

connected to all RCGs on both memory cards.

CSTB#

Command Strobe

AGTL+ MIOC

RCG

This strobe, when activated, indicates the initiation of an access. This signal is

connected to all RCGs on both memory cards.

MA[13:0]#

Memory Address bus

AGTL+ MIOC

RCG

These signals define the address of the location to be accessed in the DRAM.,

and are driven on two successive clock cycles to provide up to 28 bits of

effective memory address. The signals are connected to all RCGs on both

memory cards.

ROW#

Row Selects

AGTL+ MIOC

RCG

These signals indicate which row in the selected memory bank will service

this access. These signals are connected to all RCGs on both memory cards.

GRCMPLT#

Global

RCMPLT#

AGTL+, I/O, all RCGs

A "global" version of the

RCMPLT(a,b)#

signals, asserted coincident with

RCMPLT#

, and by the same agent. Whereas each

RCMPLT#

signal connects

the RCGs on one card with the MIOC, the

GRCMPLT#

signal connects the

Intel

Æ

450NX PCIset

2-13

2.5 Memory Subsystem Interface

RCGs across both cards while excluding the MIOC. This allows all RCGs to

monitor each request completion without placing undue loading on the

RCMPLT#

signals.

MRESET#

Memory Subsystem Reset

AGTL+ MIOC

RCG/MUX

This signal represents a hard reset of the memory subsystem. It is asserted

following

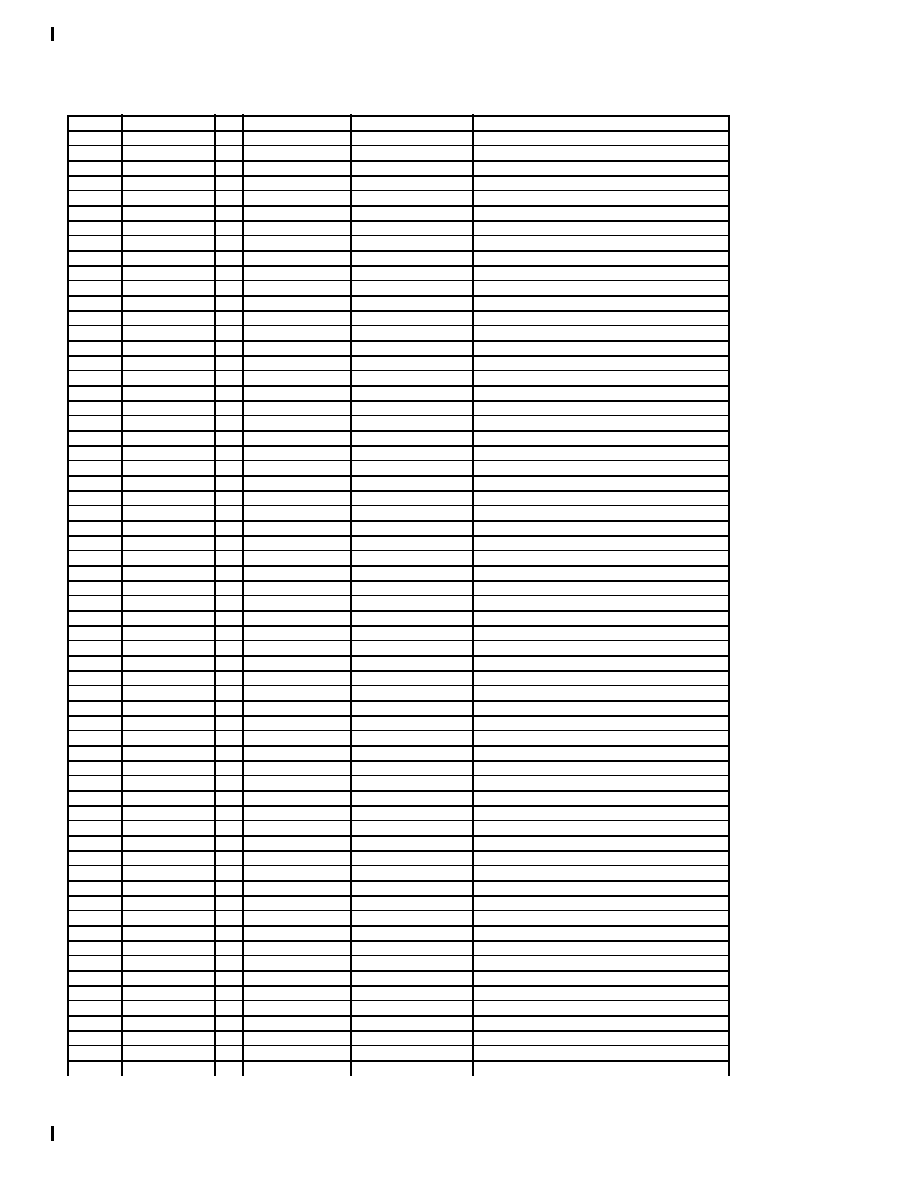

PWRGD

or upon the MIOC issuing a processor RESET due to

software invocation.

RCMPLTa#

RCMPLTb#

Request Complete

AGTL+ RCG

MIOC

This signal, which is driven by the currently active RCG, indicates the

completion of a request into the memory array. Typically the "

a

" signal

connects the MIOC and all RCGs on Card #0, while the "

b

" signal connects

the MIOC and all RCGs on Card #1.

PHIT(a,b)#

RHIT(a,b)#

Page and Row Hit Status

AGTL+ RCG

MIOC

These signals indicate what resource, if any, delayed the initiation of a read.

Typically the "

a

" signal connects the MIOC and all RCGs on Card #0, while

the "

b

" signal connects the MIOC and all RCGs on Card #1.

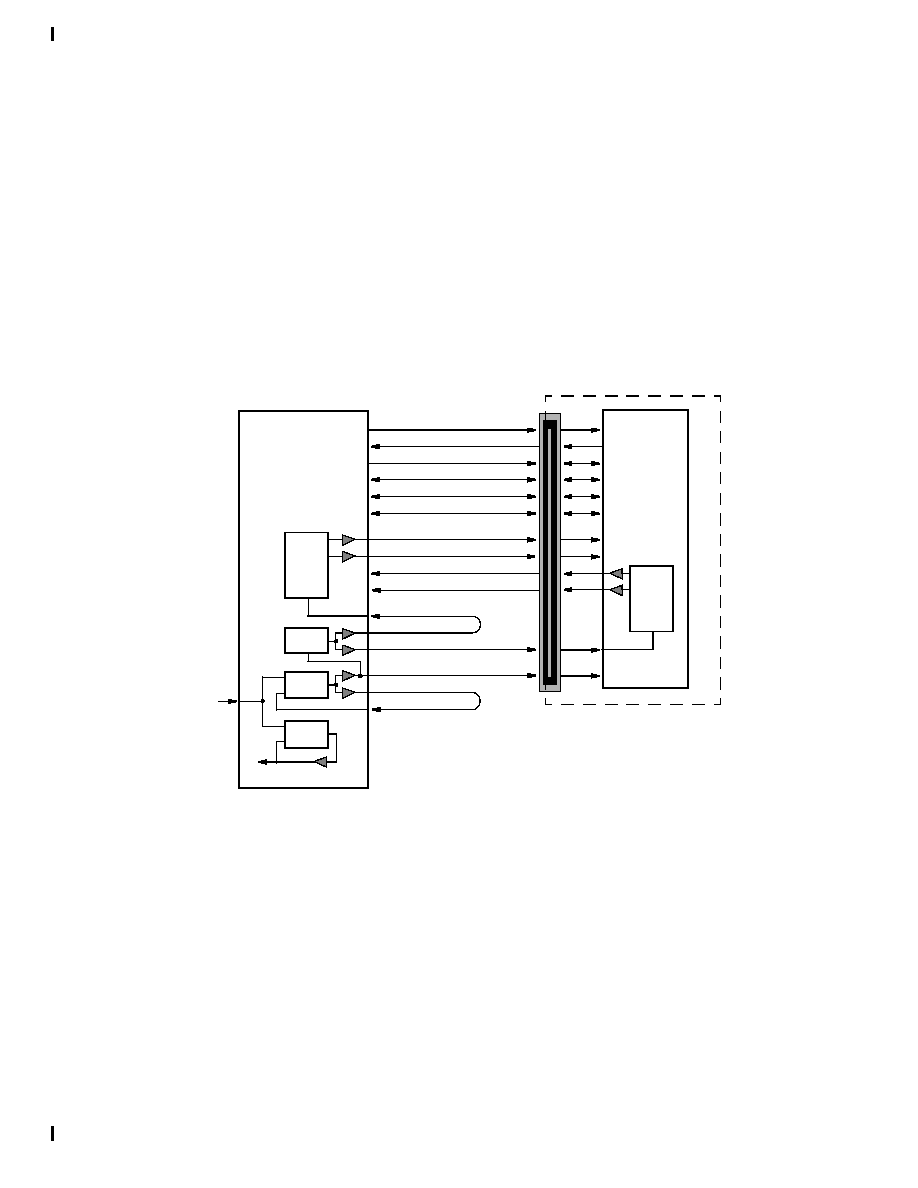

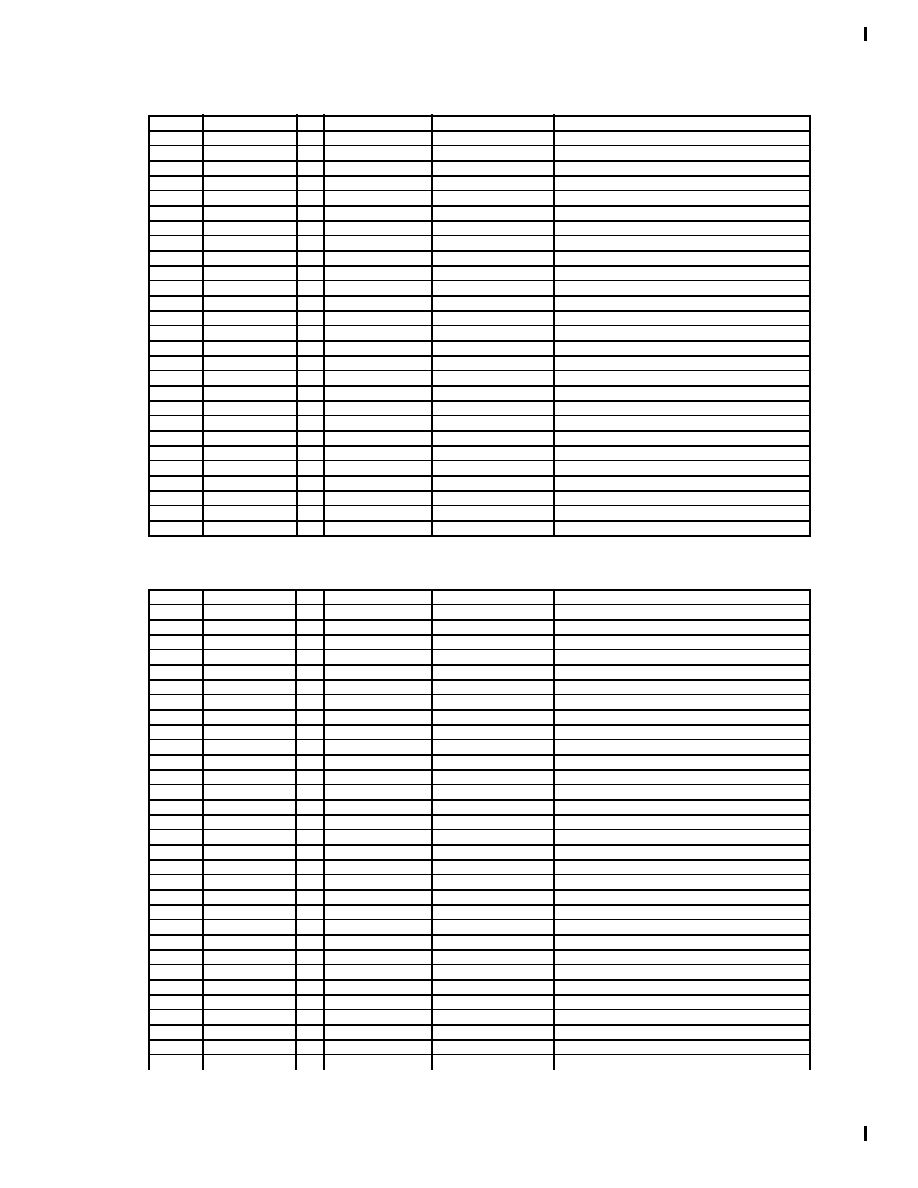

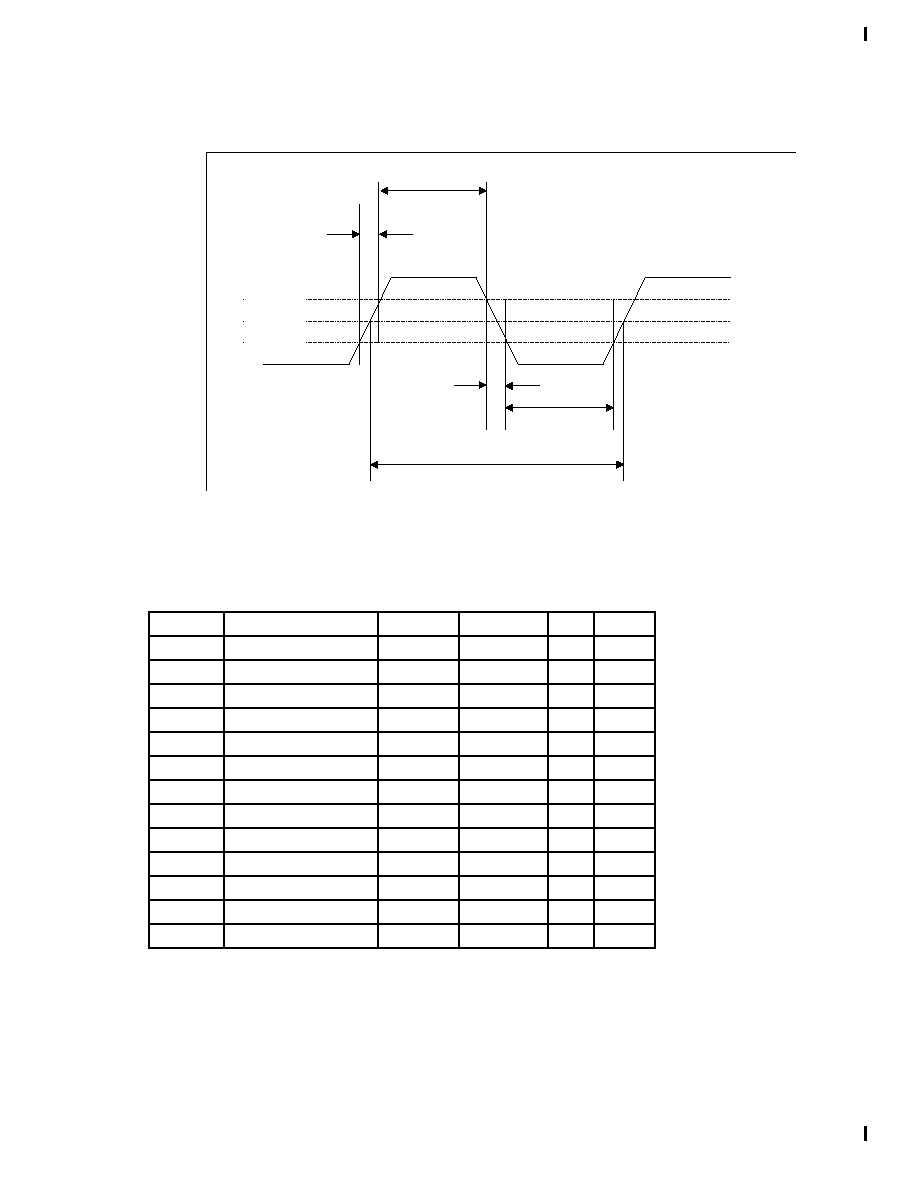

DSTBP[3:0]#

DSTBN[3:0]#

Data Strobes

AGTL+ MUX

MIOC

This set of four signal-pairs are strobes which qualify the data transferred

between the MUX and MIOC. Each strobe pair qualifies 18 bits (two bytes

and two check bits), as follows:

In a 4:1 interleaved system, with 2 MUXs per card,

DSTB[1:0]#

strobes the

low MUX and

DSTB[3:2]#

strobes the high MUX. In a 2:1 interleaved system,

with only a single MUX per card,

DSTB[1:0]#

strobes the MUX, and

DSTB[3:2]#

is not used.

MD[71:36]#

MD[35:00]#

Memory Data

AGTL+ MUX

MIOC

These signals are connected to the external datapath of the MUXs. Each MUX

provides 36 bits of the 72-bit datapath to the MIOC.

DCMPLTa#

AGTL+ MUX

MIOC/MUX

DCMPLTb#

Data Transfer Complete

MIOC

MUXs

This signal is driven by the source of the data transfer: the MIOC for writes,

and the MUX for reads.

DCMPLT#

active indicates that the data transfer is

complete. Typically the "

a

" signal connects the MIOC and all MUXs on Card

#0, while the "

b

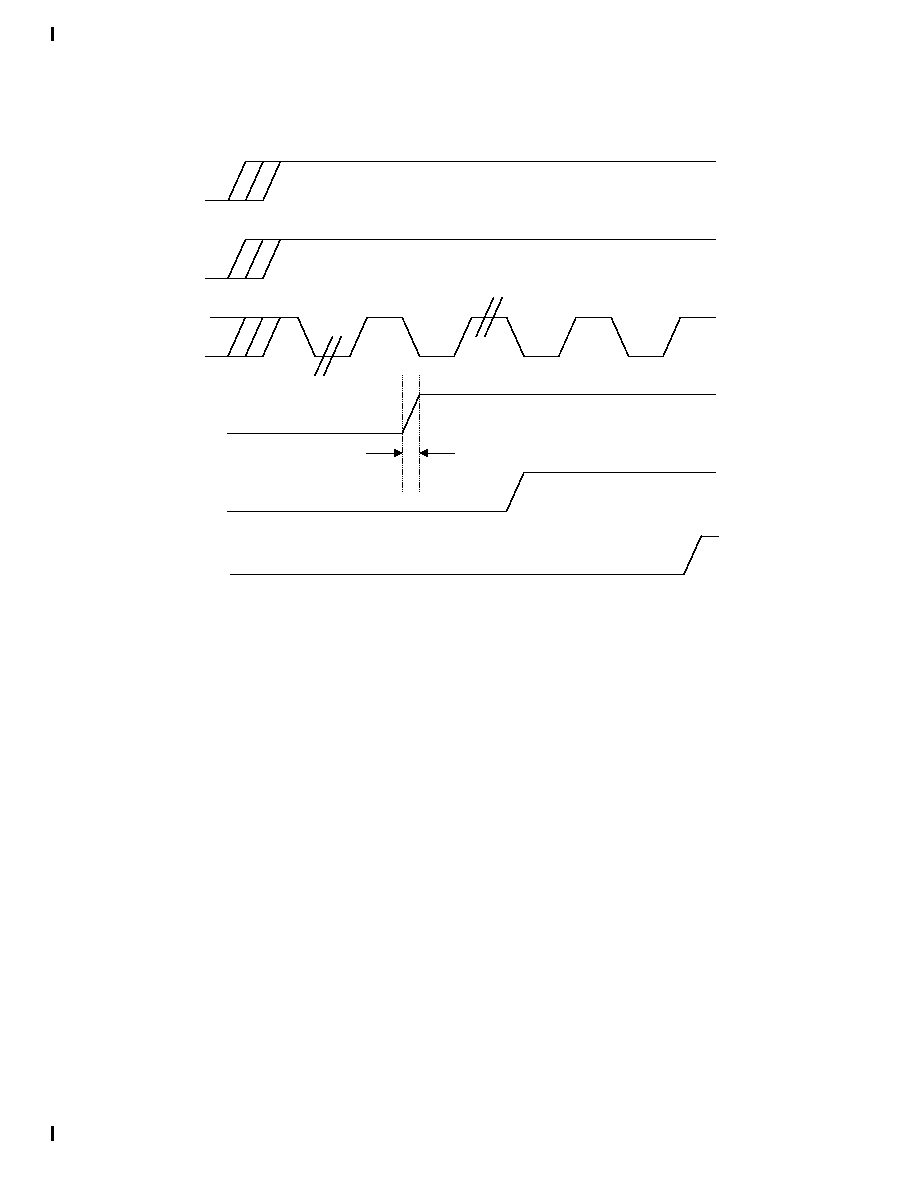

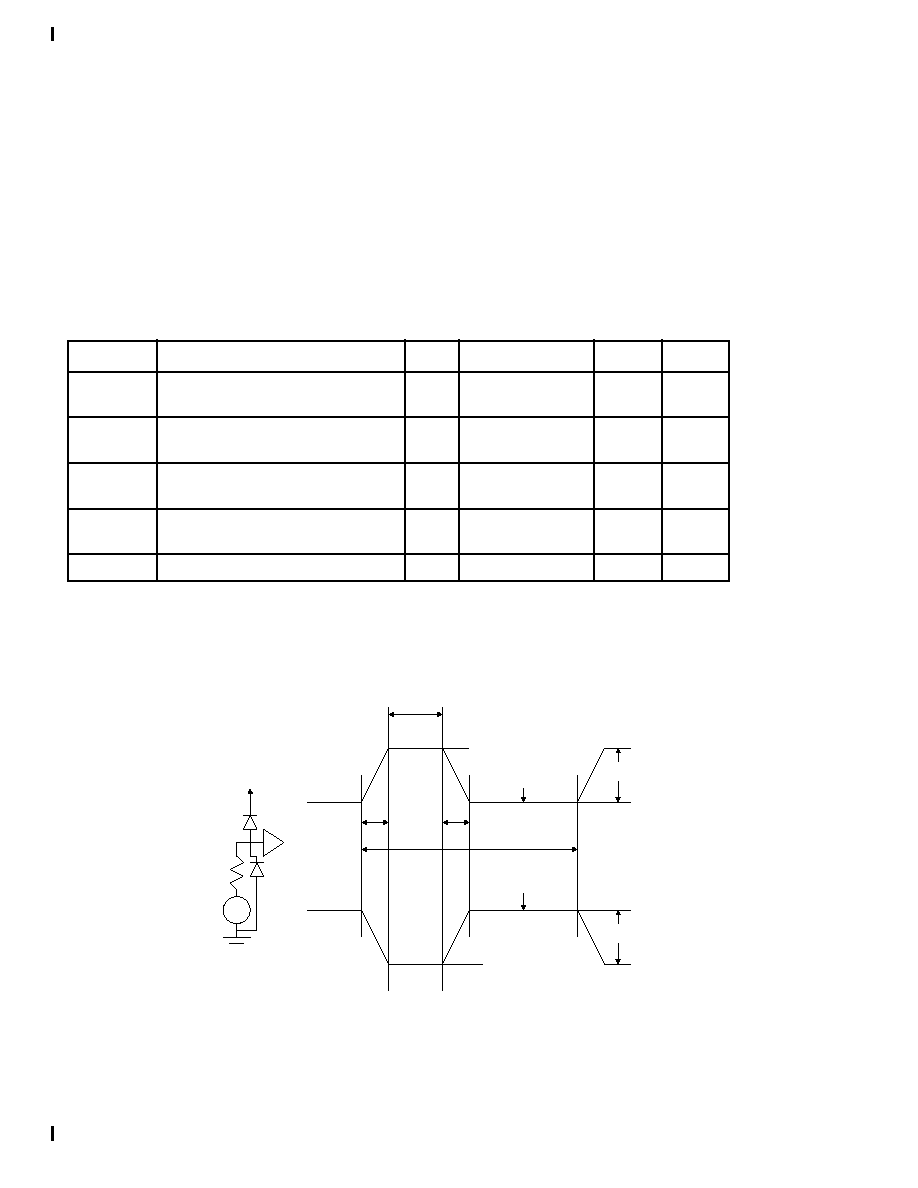

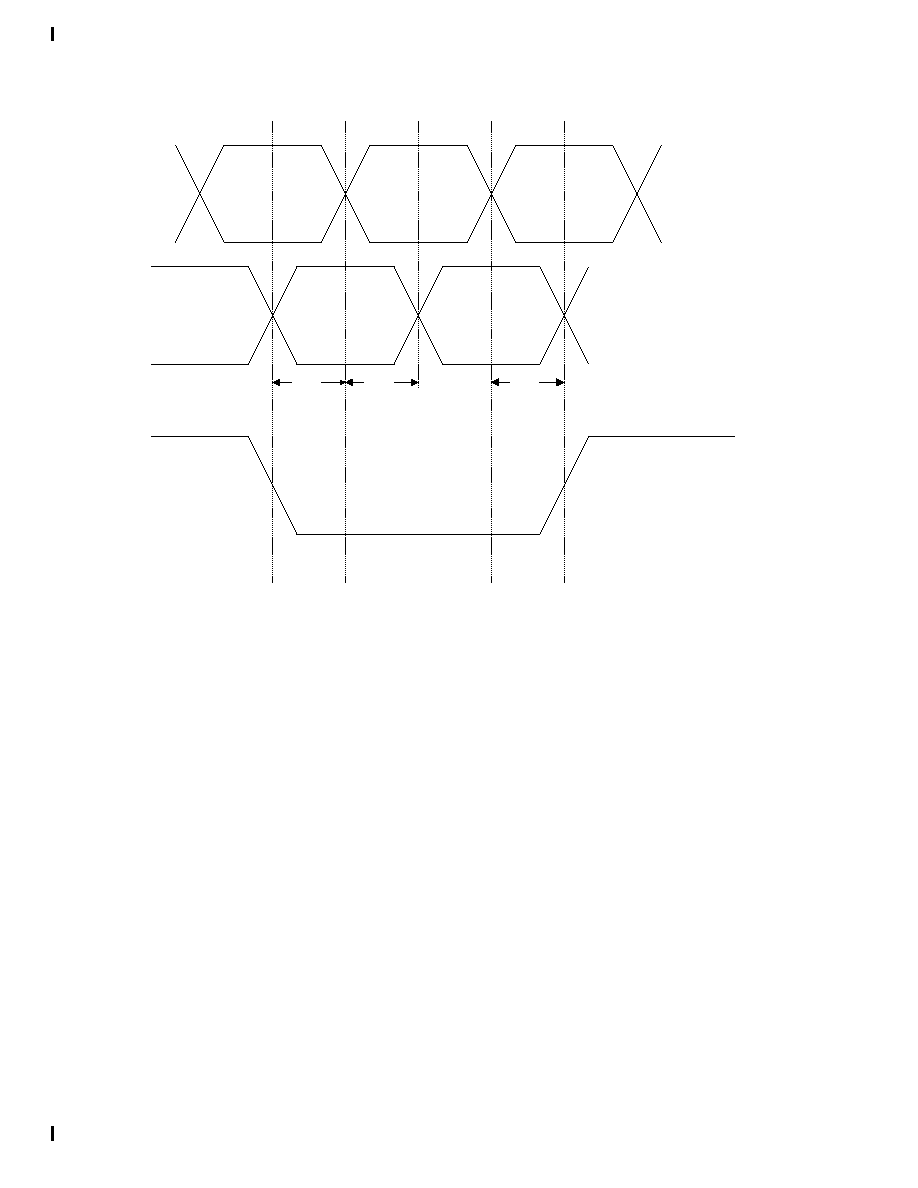

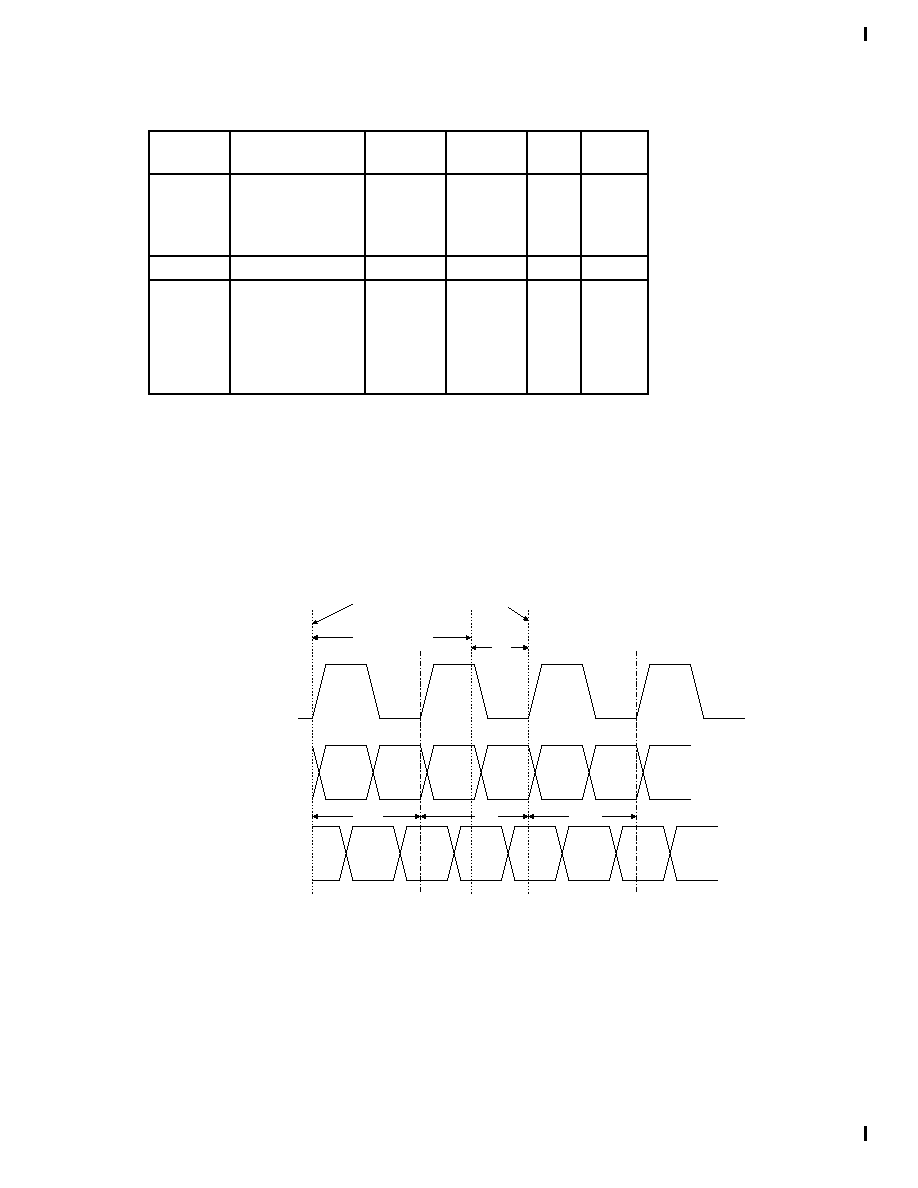

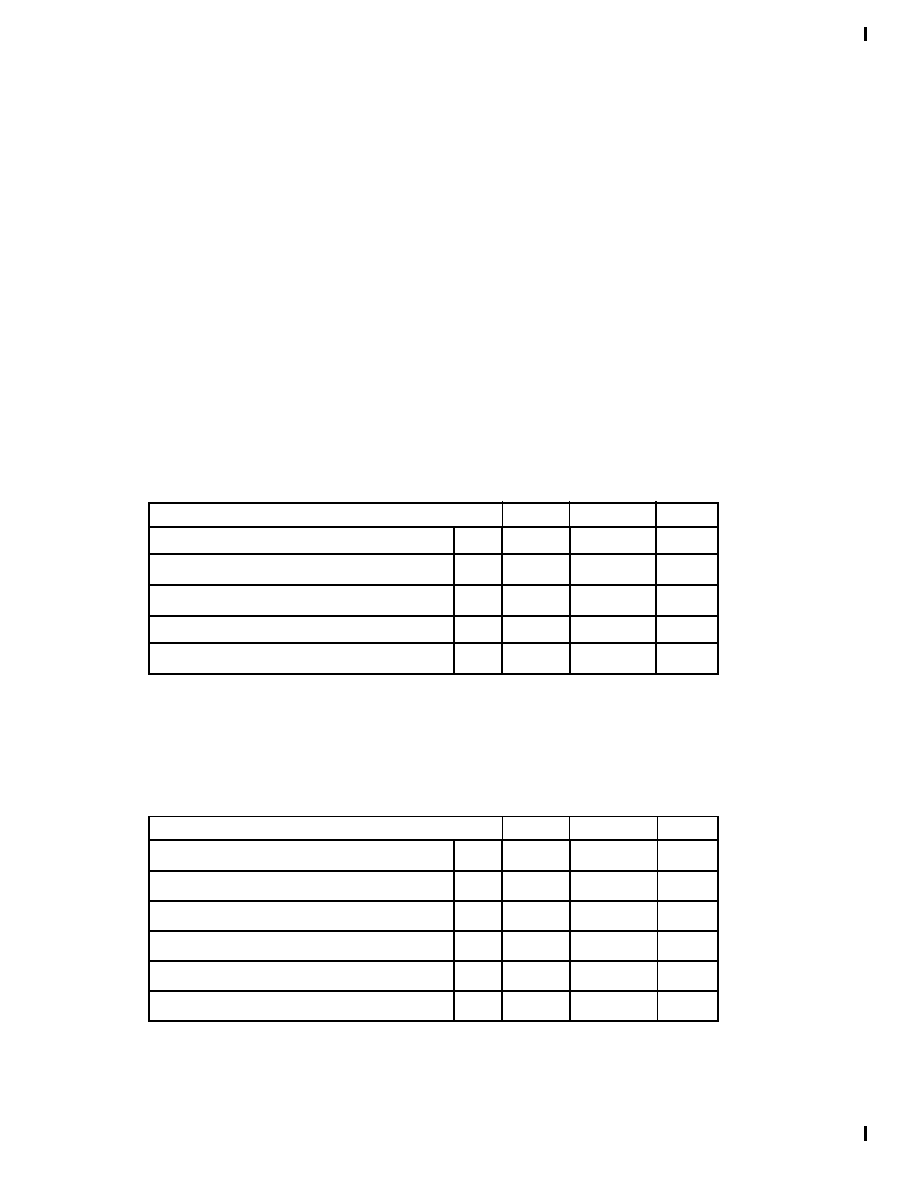

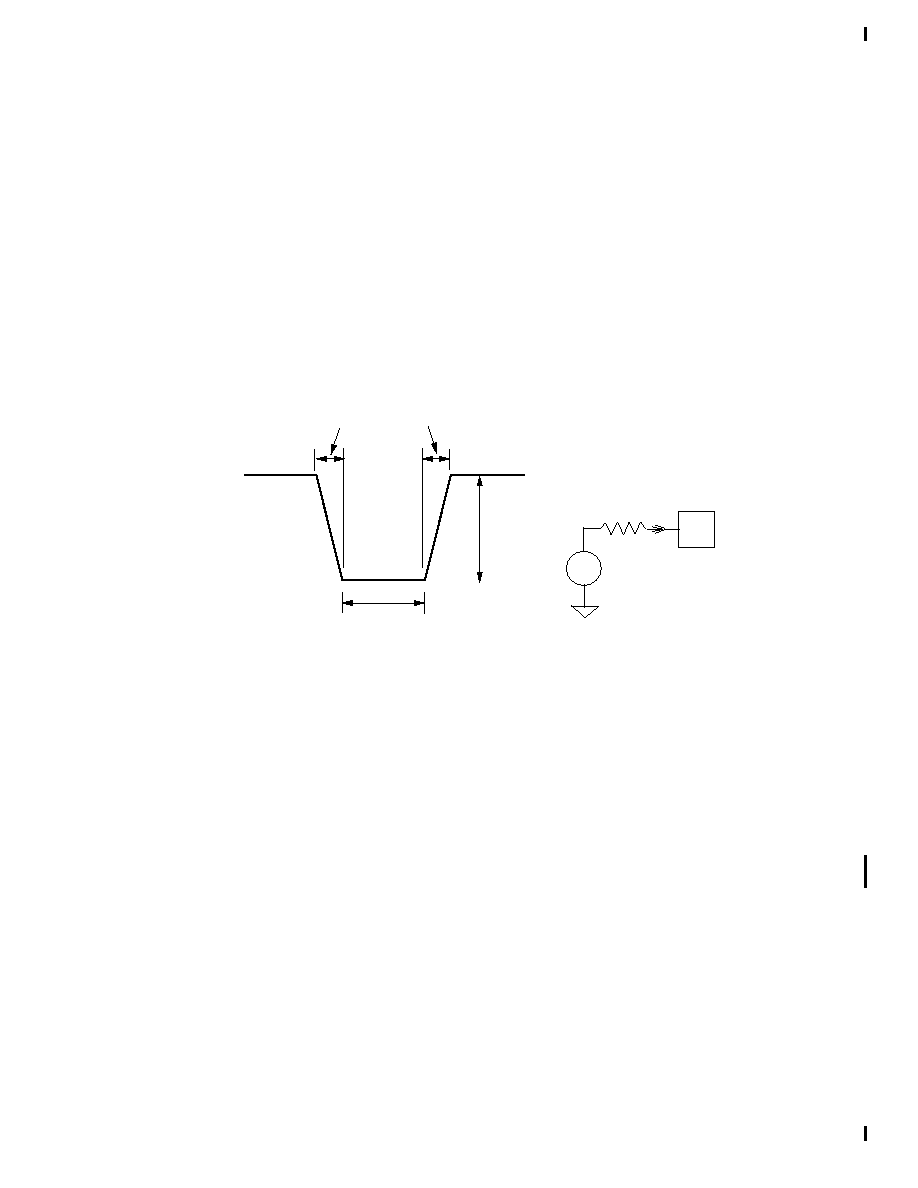

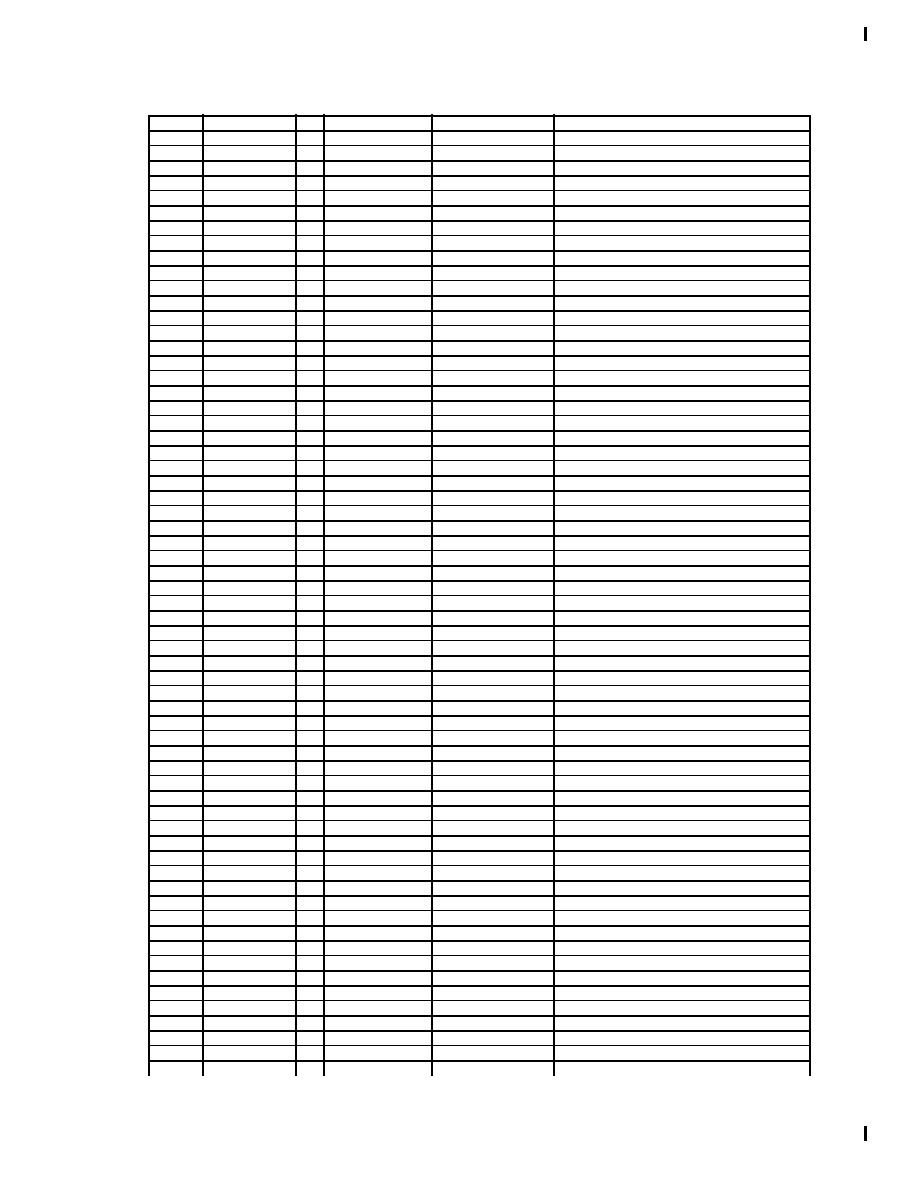

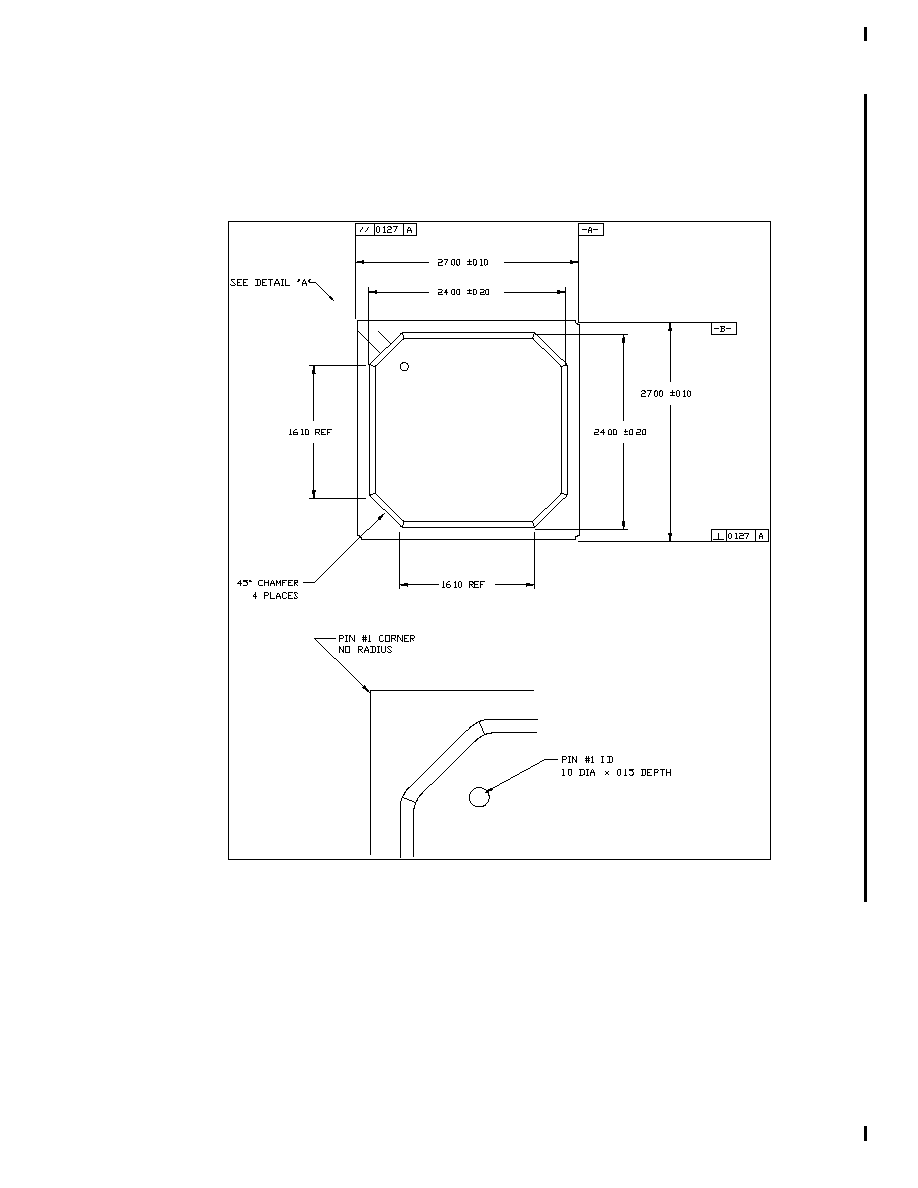

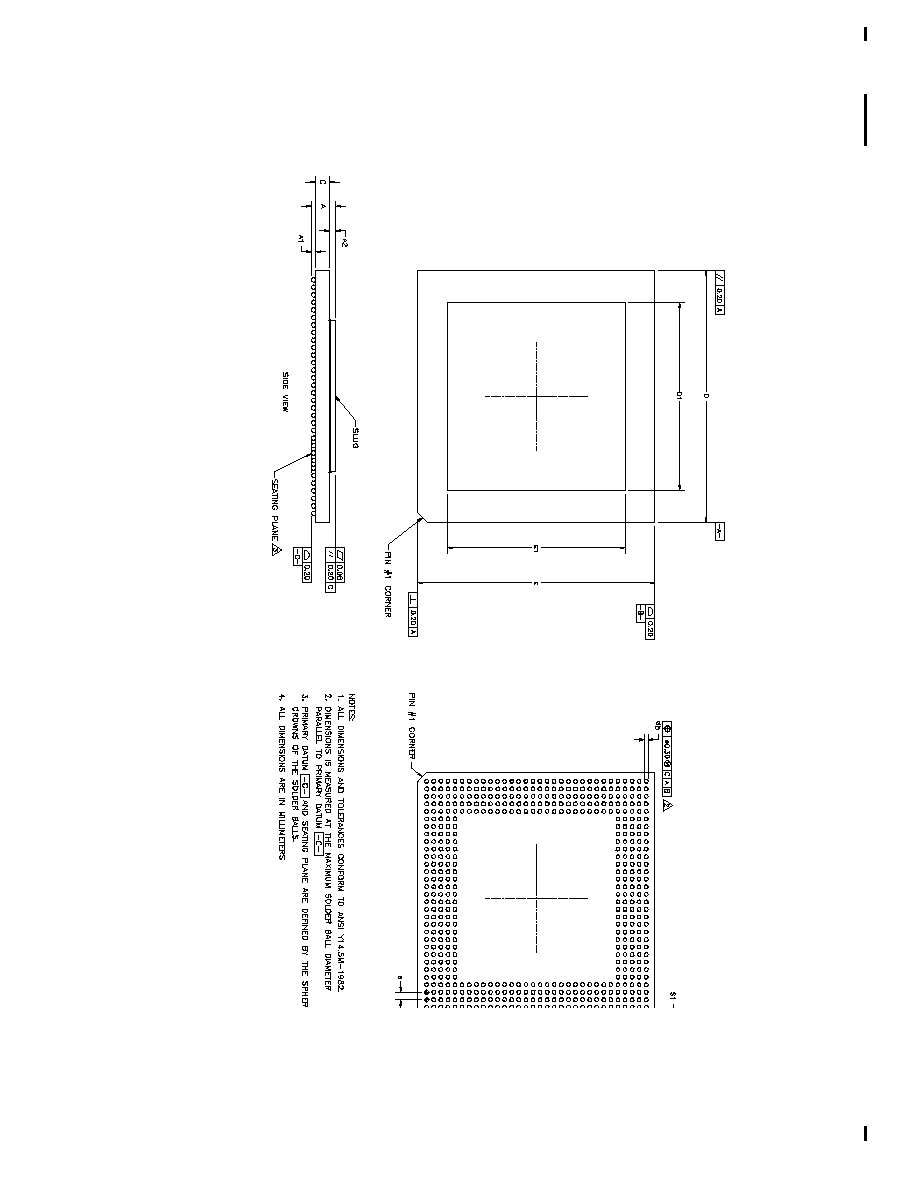

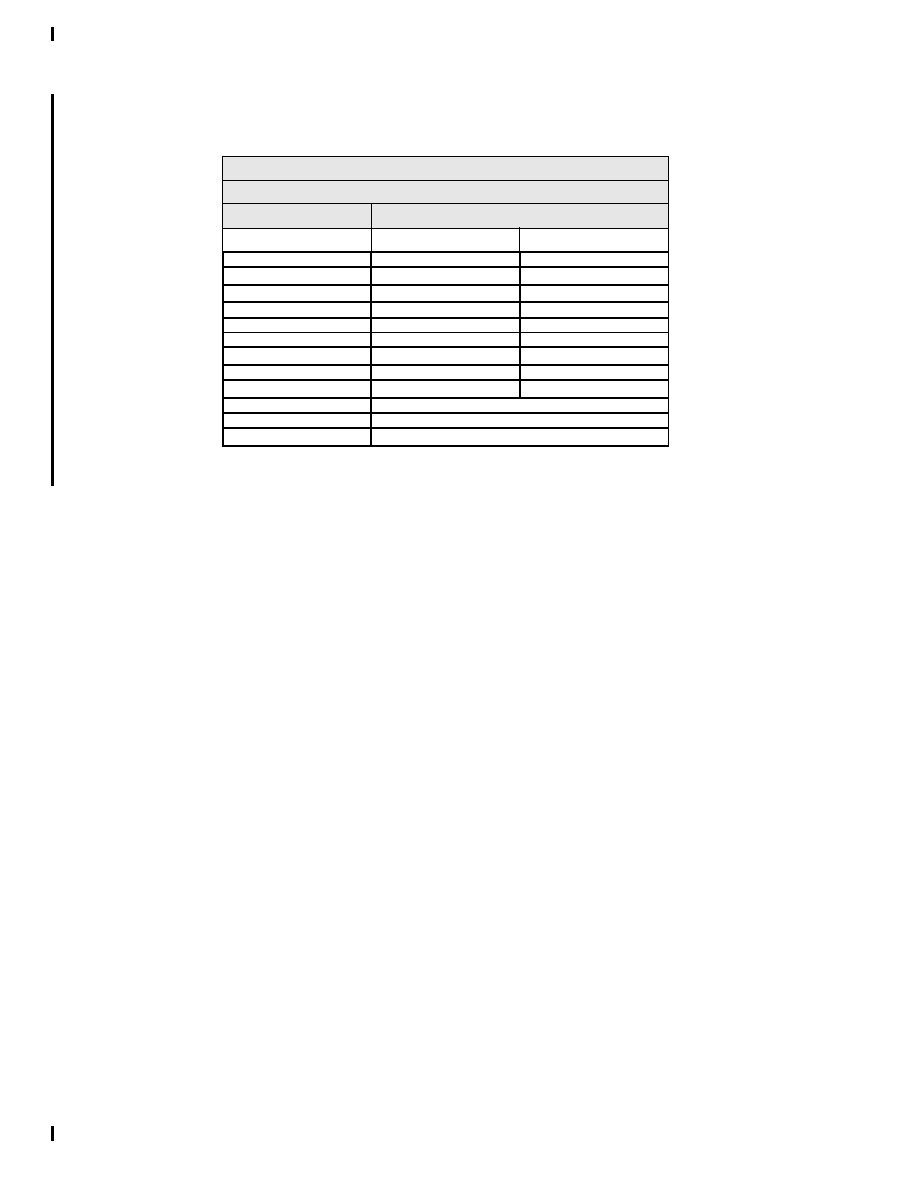

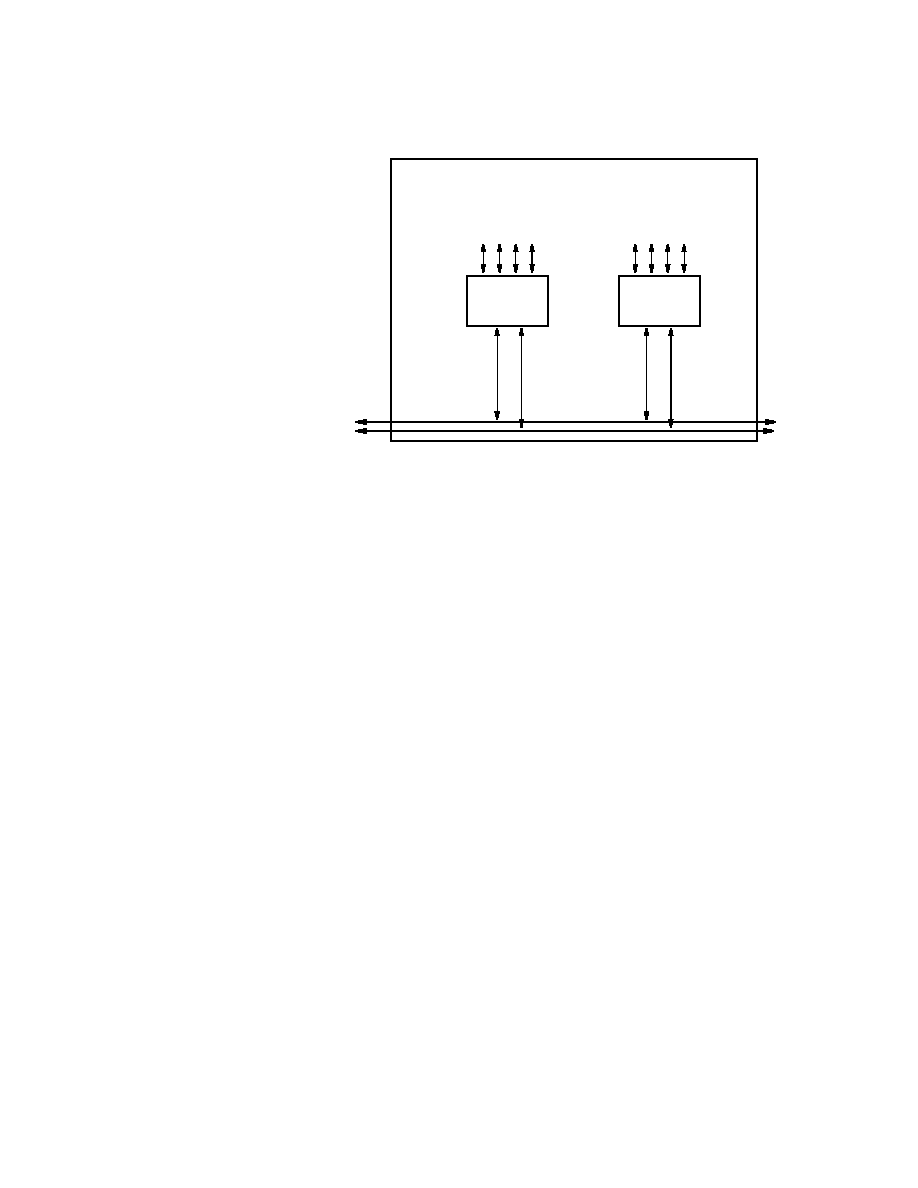

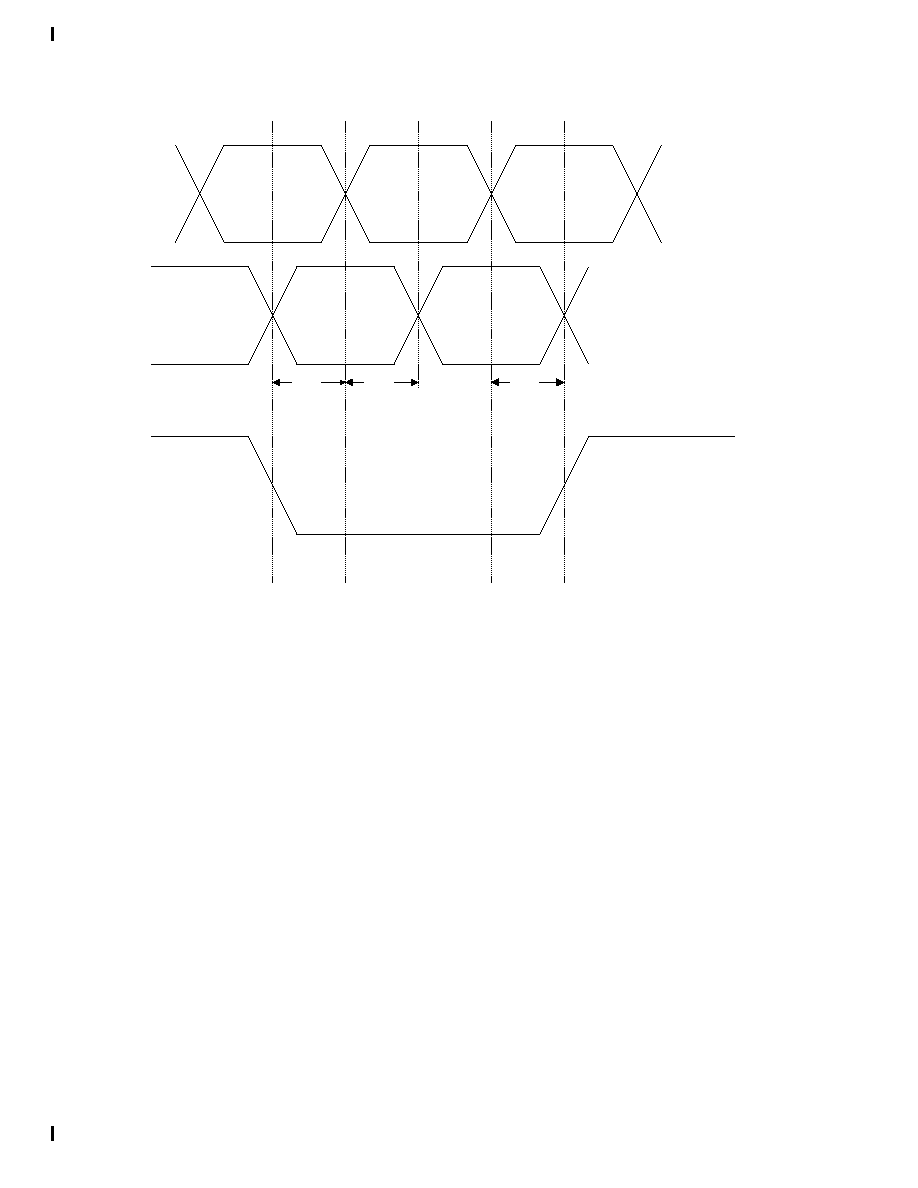

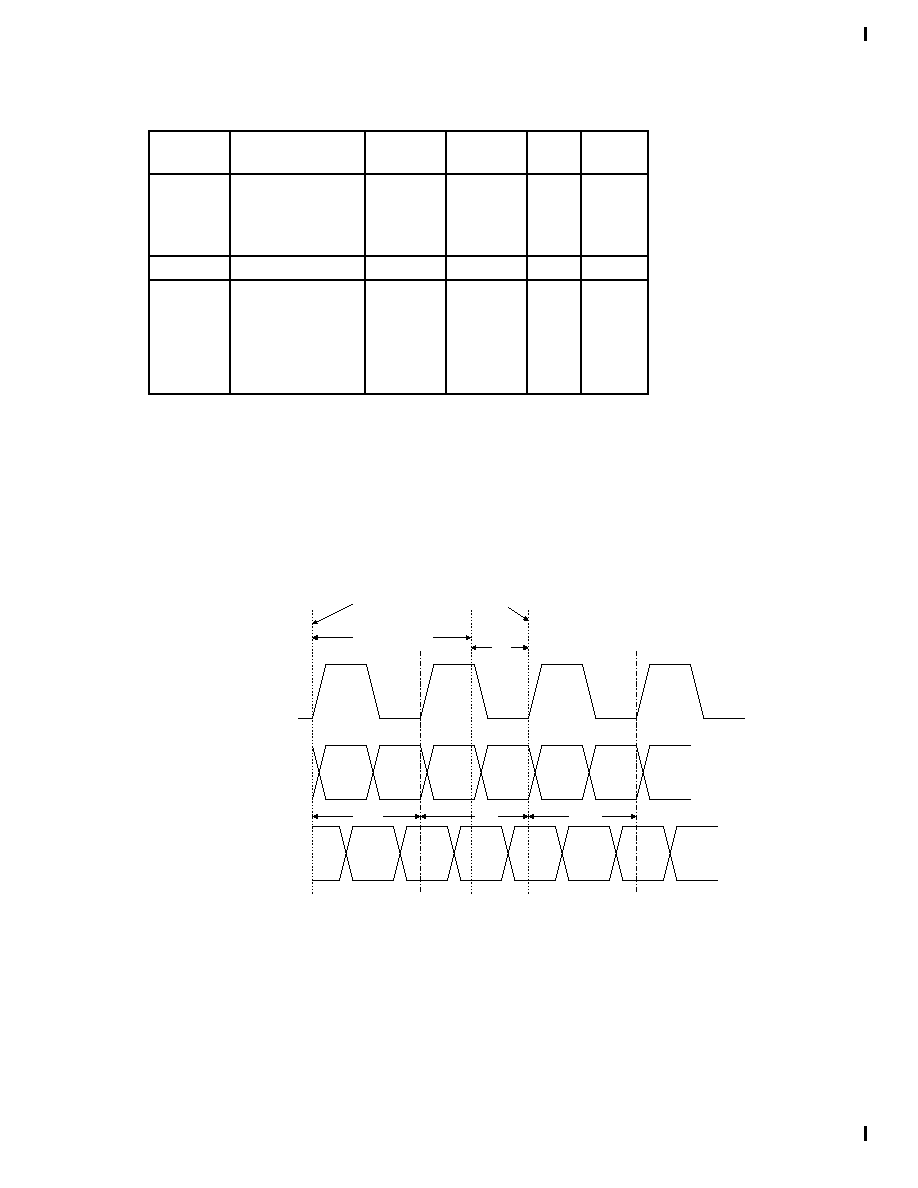

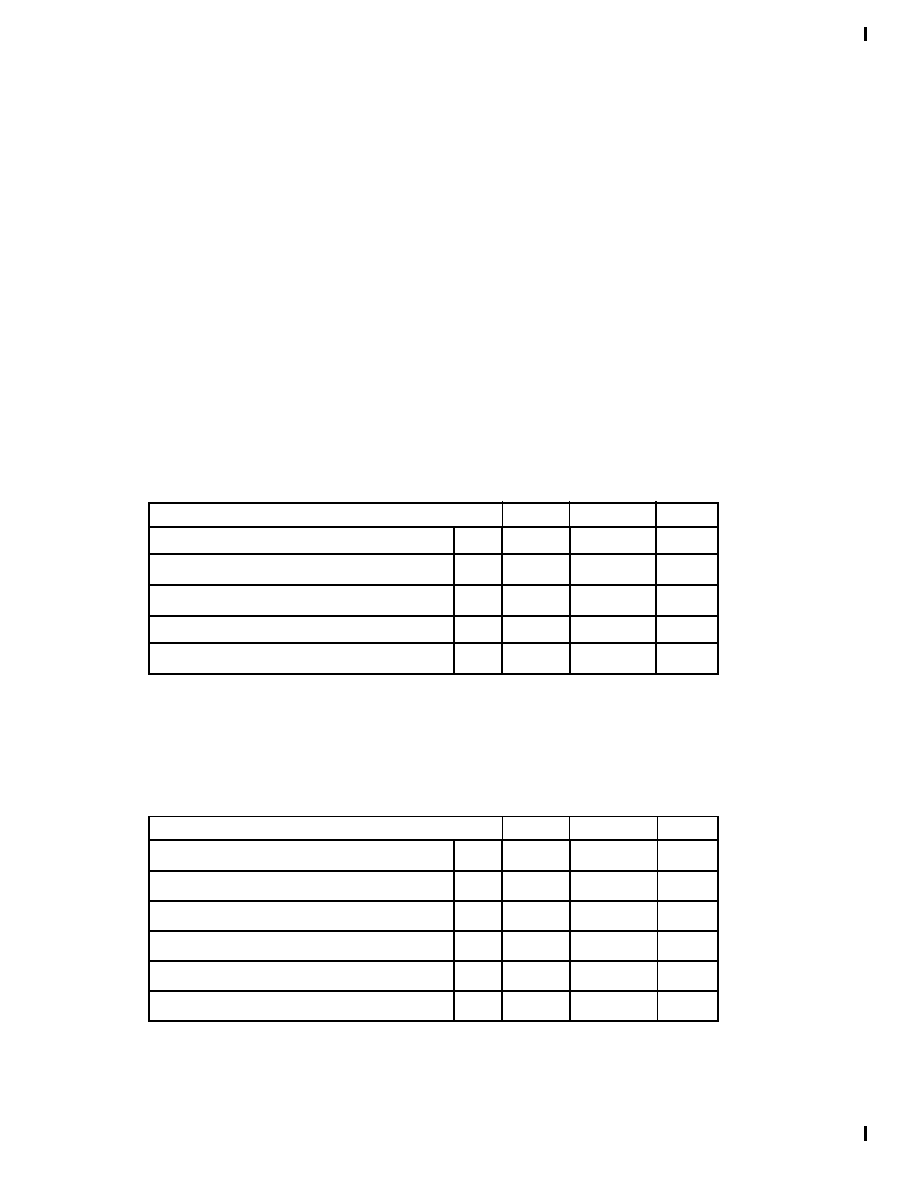

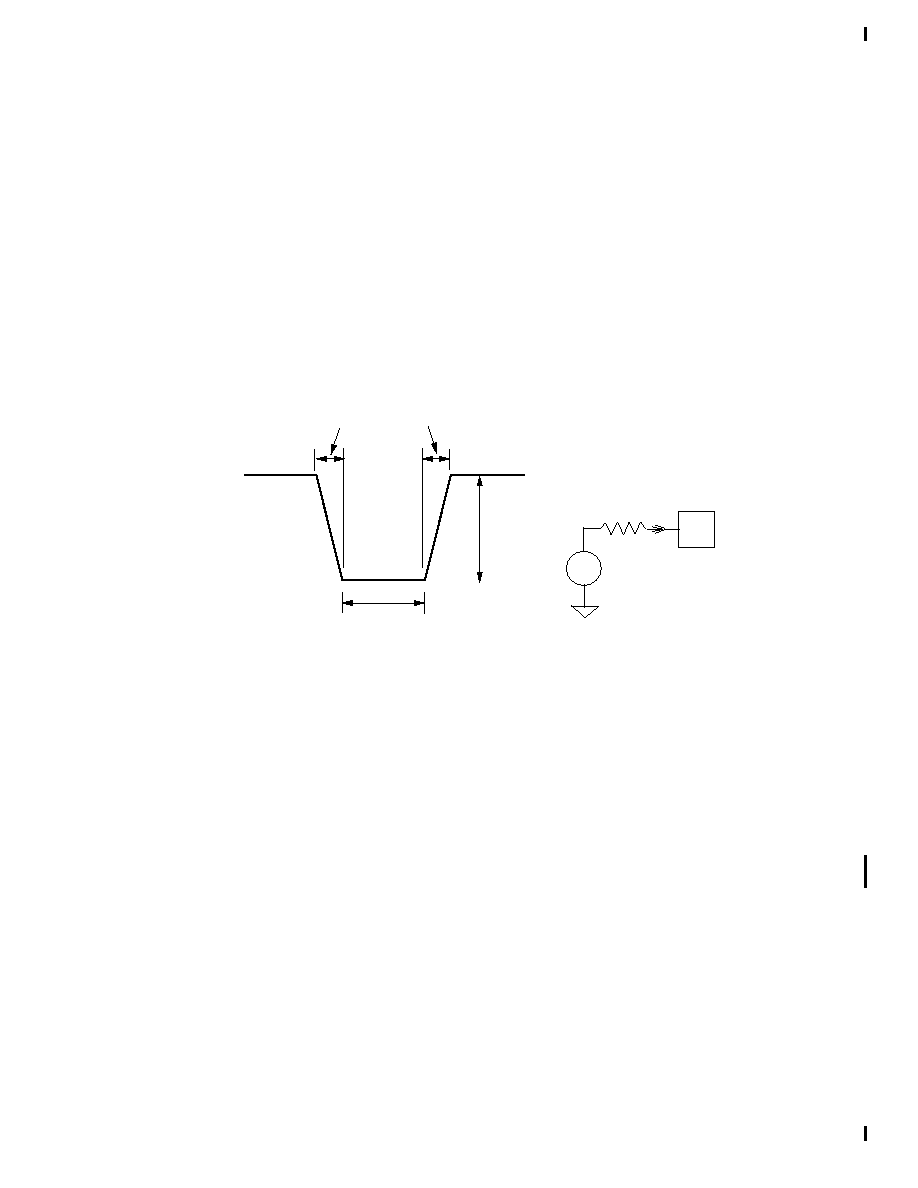

" signal connects the MIOC and all MUXs on Card #1.