Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of

any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products.

Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor

variations to this specification known as errata. Other brands and names are the property of their respective owners.

� INTEL CORPORATION 1996

March 1996

Order Number: 290571-001

Provides the Bridge Between the PCI

Bus and ISA Bus

100% PCI and ISA Compatible

PCI and ISA Master/Slave Interface

Directly Drives 10 PCI Loads and 6

ISA Slots

PCI at 25 MHz and 33 MHz

ISA from 6 MHz to 8.33 MHz

Enhanced DMA Functions

Scatter/Gather (S/G) (82378ZB)

Fast DMA Type A, B and F (82378ZB)

Compatible DMA Transfers

32-bit Addressability(82378ZB)

27-bit Addressability(82379AB)

Seven Independently Programmable

Channels

Functionality of Two 82C37A DMA

Controllers

Data Buffers to Improve Performance

8-Byte DMA/ISA Master Line Buffer

32-bit Posted Memory Write Buffer to

ISA

Integrated 16-bit BIOS Timer

Non-Maskable Interrupts (NMI)

PCI System Errors

ISA Parity Errors

Arbitration for ISA Devices

ISA Masters

DMA and Refresh

Four Dedicated PCI Interrupts

Level Sensitive

Mapped to Any Unused Interrupt

Arbitration for PCI Devices

Six PCI Masters Supported

Fixed, Rotating, or a Combination

Utility Bus (X-Bus) Peripheral Support

Provides Chip Select Decode

Controls Lower X-Bus Data Byte

Transceiver

Functionality of One 82C54 Timer

System Timer

Refresh Request

Speaker Tone Output

Functionality of Two 82C59 Interrupt

Controllers

14 Interrupts Supported

Edge/Level Selectable Interrupts

I/O APIC (Advanced Programmable

Interrupt Controller (82379AB)

Support for Multi-Processor Systems

System Power Management (Intel SMM

Support)

Programmable System Management

Interrupt (SMI)

Hardware Events,

Software Events, EXTSMI#

Programmable CPU Clock Control

(STPCLK#)

Fast-On/Off Mode

208-Pin QFP Package

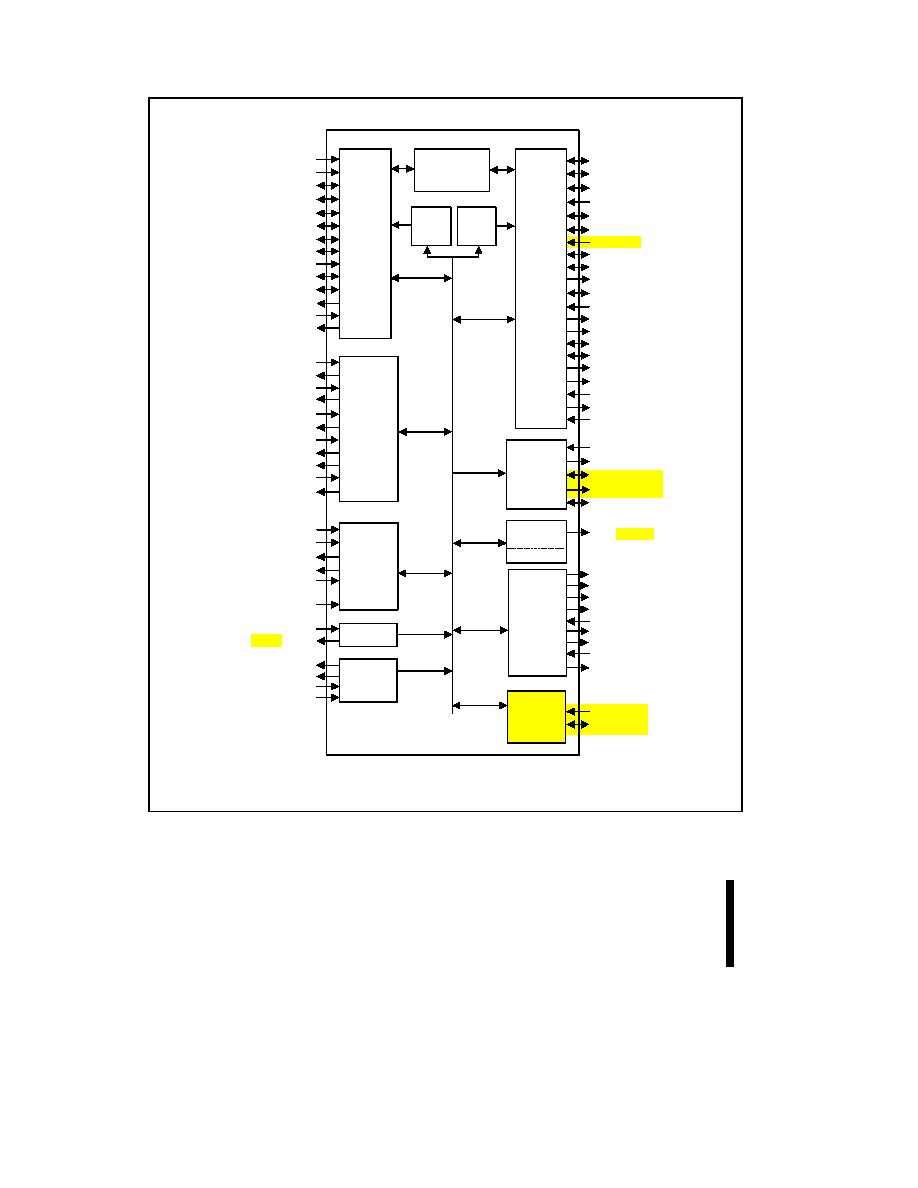

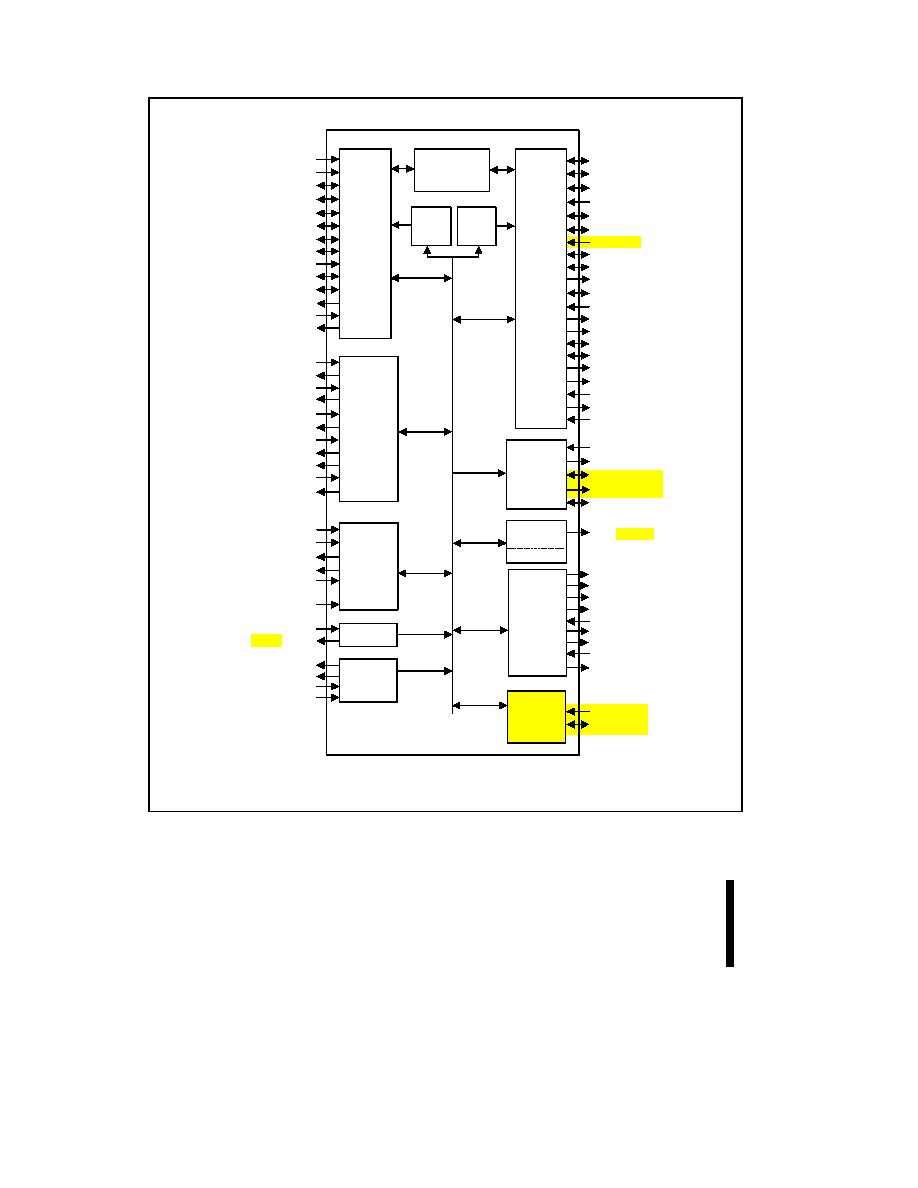

The 82378ZB System I/O (SIO) and 82379AB System I/O APIC (SIO.A) components are PCI-to-ISA Bus Bridge

devices. These devices integrate many of the common I/O functions found in today's ISA-based PC systems

a

seven channel DMA controller, two 82C59 interrupt controllers, an 8254 timer/counter, a BIOS timer, Intel SMM

power management support, and logic for NMI generation. In addition, the SIO and SIO.A each support a total of

six PCI Masters, and four PCI Interrupts. Decode is provided for peripheral devices such as the flash BIOS, real

time clock, keyboard/mouse controller, floppy controller, two serial ports, one parallel port, and IDE hard disk

drive.

For both the SIO and SIO.A, each DMA channel supports compatibility transfers. The SIO also supports types

A, B, and F transfers and scatter/gather. In addtion to the standard ISA-compatible interrupt controller that is in

both the SIO and SIO.A, the SIO.A contains an Advance Programmable Interrupt Controller (IO APIC) for use in

multi-processing systems.

This document describes both the 82378ZB (SIO) and 82379AB (SIO.A) components. Unshaded areas describe

the 82378ZB. Shaded areas, like this one, describe differences between the 82379AB and 82378ZB.

82378ZB SYSTEM I/O (SIO) AND

82379AB SYSTEM I/O APIC (SIO.A)

82378ZB (SIO) AND 82379AB (SIO.A)

2

REQ0#/SIOGNT#

DREQ[7:5,3:0]

Data Buffers

PCI

Decode

ISA

Decode

PCI

Bus

Interface

ISA

Bus

Interface

PCI

Arbiter

Interrupt

Timers/

Counters

D M A

PCICLK

PCIRST#

AD[31:0]

C/BE#[3:0]

FRAME#

IRDY#

TRDY#

STOP#

LOCK#

DEVSEL#

SERR#

PAR

IDSEL

MEMCS#

REQ1#

CPUREQ#

GNT0#/SIOREQ#

GNT1#/RESUME#

CPUGNT#

MEMREQ#

MEMACK#

INT

NMI

IRQ[15,14,

11:9,7:3,1]

DA CK[7:5,3:0]#

TC (82379AB)

REFRESH#

SD[15:0]

SA[19:0]

LA[23:17]

IOCS16#

MEMCS16#

SBHE#

MASTER#

MEMR#

MEMW#

AEN

IOCHRDY

IOCHK#

SYSCLK

BALE

IOR#

IOW#

SMEMR#

SMEMW#

ZEROWS#

RSTDRV

SPKR/TESTO

UBUSTR

UBUSOE#

EC SAD D R[2:0]

ECSEN#

DSKCHG

ALT_RST#

ALT_A20

FERR#/IRQ13

IGNNE#

Utility

Bus

Support

Logic

OSC

FLSHREQ#

IRQ12/M

IRQ8#

Test

TEST

BIOS Timer

SPKR/TESTO

REQ[3:2]#

GNT[3:2]#

PIRQ[3:0]#

SMI#

STPCLK#

EXTSMI#

INIT

CPU

Interface

I/O

A P IC

(8 2 37 9 AB

O n ly)

APICCLK

APIC D[1:0]

EOP(82378Z B)

SIO_A_BK.DRW

Note: I/O APIC signals are only on the 82379AB. Also, SPKR/TESTO are only multiplexed on the 82379AB and are separate

signals on the 82378ZB. The MASTER# signal is only on the 82378ZB.

82378ZB SIO and 82379AB SIO.A Component Block Diagram

82378ZB (SIO) AND 82379 (SIO.A)

3

CONTENTS

PAGE

1.0. ARCHITECTURAL OVERVIEW.................................................................................................................... 9

2.0. SIGNAL DESCRIPTION...............................................................................................................................12

2.1. PCI BUS INTERFACE SIGNALS ................................ ................................ ................................ ............. 13

2.2. PCI ARBITER SIGNALS ................................ ................................ ................................ ........................... 14

2.3. ADDRESS DECODER SIGNAL ................................ ................................ ................................ ............... 16

2.4. POWER MANAGEMENT SIGNALS ................................ ................................ ................................ ........ 17

2.5. ISA INTERFACE SIGNALS ................................ ................................ ................................ ...................... 17

2.6. DMA SIGNALS ................................ ................................ ................................ ................................ .......... 19

2.7. TIMER SIGNAL ................................ ................................ ................................ ................................ ......... 20

2.8. INTERRUPT CONTROLLER SIGNALS ................................ ................................ ................................ .. 21

2.9. APIC BUS SIGNALS (82379AB ONLY) ................................ ................................ ................................ .. 22

2.10. UTILITY BUS SIGNALS ................................ ................................ ................................ .......................... 22

2.11. TEST SIGNALS ................................ ................................ ................................ ................................ ....... 24

3.0. REGISTER DESCRIPTION..........................................................................................................................25

3.1. SIO CONFIGURATION REGISTER DESCRIPTION ................................ ................................ ............. 32

3.1.1. VID--VENDOR IDENTIFICATION REGISTER ................................ ................................ ............... 32

3.1.2. DID--DEVICE IDENTIFICATION REGISTER ................................ ................................ ................. 33

3.1.3. COM--COMMAND REGISTER ................................ ................................ ................................ ........ 33

3.1.4. DS--DEVICE STATUS REGISTER ................................ ................................ ................................ . 34

3.1.5. RID--REVISION IDENTIFICATION REGISTER ................................ ................................ ............. 34

3.1.6. PCICON--PCI CONTROL REGISTER ................................ ................................ ............................ 35

3.1.7. PAC--PCI ARBITER CONTROL REGISTER ................................ ................................ ................. 36

3.1.8. PAPC--PCI ARBITER PRIORITY CONTROL REGISTER ................................ ............................ 37

3.1.9. ARBPRIX--PCI ARBITER PRIORITY CONTROL EXTENSION REGISTER ............................... 39

3.1.10. MCSCON-MEMCS# CONTROL REGISTER ................................ ................................ ................. 39

3.1.11. MCSBOH--MEMCS# BOTTOM OF HOLE REGISTER ................................ ............................... 40

3.1.12. MCSTOH--MEMCS# TOP OF HOLE REGISTER ................................ ................................ ........ 40

3.1.13. MCSTOM--MEMCS# TOP OF MEMORY REGISTER ................................ ................................ . 41

3.1.14. IADCON--ISA ADDRESS DECODER CONTROL REGISTER ................................ ................... 41

3.1.15. IADRBE--ISA ADDRESS DECODER ROM BLOCK ENABLE REGISTER ............................... 42

3.1.16. IADBOH--ISA ADDRESS DECODER BOTTOM OF HOLE REGISTER ................................ .... 42

3.1.17. IADTOH--ISA ADDRESS DECODER TOP OF HOLE REGISTER ................................ ............ 42

3.1.18. ICRT--ISA CONTROLLER RECOVERY TIMER REGISTER ................................ ..................... 43

3.1.19. ICD--ISA CLOCK DIVISOR REGISTER ................................ ................................ ....................... 44

3.1.20. UBCSA--UTILITY BUS CHIP SELECT A REGISTER ................................ ................................ . 45

3.1.21. UBCSB--UTILITY BUS CHIP SELECT B REGISTER ................................ ................................ . 46

3.1.22. MAR1--MEMCS# ATTRIBUTE REGISTER #1 ................................ ................................ ............ 47

82378ZB (SIO) AND 82379AB (SIO.A)

4

3.1.23. MAR2--MEMCS# ATTRIBUTE REGISTER #2 ................................ ................................ ............. 47

3.1.24. MAR3--MEMCS# ATTRIBUTE REGISTER #3 ................................ ................................ ............. 48

3.1.25. PIRQ[3:0]#--PIRQ ROUTE CONTROL REGISTERS ................................ ................................ ...48

3.1.26. PACC--PIC/APIC CONFIGURATION CONTROL REGISTER (82379AB Only)

........................ 49

3.1.27. APICBASE--APIC BASE ADDRESS RELOCATION (82379AB Only) ................................ .......49

3.1.28. BIOS TIMER BASE ADDRESS REGISTER ................................ ................................ .................. 50

3.1.29. SMICNTL--SMI CONTROL REGISTER ................................ ................................ ........................ 50

3.1.30. SMIEN--SMI ENABLE REGISTER ................................ ................................ ................................ 51

3.1.31. SEE--SYSTEM EVENT ENABLE REGISTER ................................ ................................ .............. 51

3.1.32. FTMR--FAST OFF TIMER REGISTER ................................ ................................ ......................... 52

3.1.33. SMIREQ--SMI REQUEST REGISTER ................................ ................................ .......................... 53

3.1.34. CTLTMR--CLOCK SCALE STPCLK# LOW TIMER ................................ ................................ .....54

3.1.35. CTLTMRH--CLOCK SCALE STPCLK# HIGH TIMER ................................ ................................ .54

3.2. DMA REGISTER DESCRIPTION ................................ ................................ ................................ ............. 55

3.2.1. DCOM--DMA COMMAND REGISTER ................................ ................................ ............................ 55

3.2.2. DCM--DMA CHANNEL MODE REGISTER ................................ ................................ .................... 55

3.2.3. DCEM--DMA CHANNEL EXTENDED MODE REGISTER (82378ZB Only)

................................ 56

3.2.4. DR--DMA REQUEST REGISTER ................................ ................................ ................................ ....59

3.2.5. MASK REGISTER--WRITE SINGLE MASK BIT ................................ ................................ ............. 59

3.2.6. MASK REGISTER--WRITE ALL MASK BITS ................................ ................................ ................. 60

3.2.7. DS--DMA STATUS REGISTER ................................ ................................ ................................ .......60

3.2.8. DMA BASE AND CURRENT ADDRESS REGISTERS (8237 COMPATIBLE SEGMENT)

......... 61

3.2.9. DMA BASE AND CURRENT BYTE/WORD COUNT REGISTERS (8237 COMPATIBLE

SEGMENT) ................................ ................................ ................................ ................................ ................ 61

3.2.10. DMA MEMORY BASE LOW PAGE AND CURRENT LOW PAGE REGISTERS

....................... 62

3.2.11. DMA MEMORY BASE HIGH PAGE AND CURRENT HIGH PAGE REGISTERS ...................... 62

3.2.12. DMA CLEAR BYTE POINTER REGISTER ................................ ................................ .................... 63

3.2.13. DMC--DMA MASTER CLEAR REGISTER ................................ ................................ ................... 64

3.2.14. DCM--DMA CLEAR MASK REGISTER ................................ ................................ ........................ 64

3.2.15. SCATTER/GATHER (S/G) COMMAND REGISTER (82378ZB Only)

................................ ......... 64

3.2.16. SCATTER/GATHER (S/G) STATUS REGISTER (82378ZB Only) ................................ .............. 65

3.2.17. SCATTER/GATHER (S/G) DESCRIPTOR TABLE POINTER REGISTER (82378ZB Only)

.....67

3.2.18. SCATTER/GATHER (S/G) INTERRUPT STATUS REGISTER (82378ZB Only)

....................... 67

3.3. TIMER REGISTER DESCRIPTION ................................ ................................ ................................ ......... 68

3.3.1. TCW--TIMER CONTROL WORD REGISTER ................................ ................................ ................ 68

3.3.2. INTERVAL TIMER STATUS BYTE FORMAT REGISTER ................................ ............................. 70

3.3.3. COUNTER ACCESS PORTS REGISTER ................................ ................................ ....................... 71

3.3.4. BIOS TIMER REGISTER ................................ ................................ ................................ ................... 71

3.4. INTERRUPT CONTROLLER REGISTER DESCRIPTION ................................ ................................ ....72

3.4.1. ICW1--INITIALIZATION COMMAND WORD 1 REGISTER ................................ ........................... 72

3.4.2. ICW2--INITIALIZATION COMMAND WORD 2 REGISTER ................................ ........................... 73

3.4.3. ICW3--INITIALIZATION COMMAND WORD 3 REGISTER ................................ ........................... 73

82378ZB (SIO) AND 82379 (SIO.A)

5

3.4.4. ICW3--INITIALIZATION COMMAND WORD 3 REGISTER ................................ ........................... 73

3.4.5. ICW4--INITIALIZATION COMMAND WORD 4 REGISTER ................................ ........................... 74

3.4.6. OCW1--OPERATIONAL CONTROL WORD 1 REGISTER ................................ ........................... 74

3.4.7. OCW2--OPERATIONAL CONTROL WORD 2 REGISTER ................................ ........................... 75

3.4.8. OCW3--OPERATIONAL CONTROL WORD 3 REGISTER ................................ ........................... 76

3.5. CONTROL REGISTERS ................................ ................................ ................................ ........................... 77

3.5.1. NMISC--NMI STATUS AND CONTROL REGISTER ................................ ................................ ..... 77

3.5.2. NMI ENABLE AND REAL-TIME CLOCK ADDRESS REGISTER ................................ .................. 78

3.5.3. PORT 92 REGISTER ................................ ................................ ................................ ......................... 78

3.5.4. DIGITAL OUTPUT REGISTER ................................ ................................ ................................ ......... 79

3.5.5. RESET UBUS IRQ1/IRQ12 REGISTER ................................ ................................ .......................... 79

3.5.6. COPROCESSOR ERROR REGISTER ................................ ................................ ............................ 80

3.5.7. ELCR--EDGE/LEVEL CONTROL REGISTER ................................ ................................ ............... 80

3.6. POWER MANAGEMENT REGISTERS ................................ ................................ ................................ ... 80

3.6.1. APMC--ADVANCED POWER MANAGEMENT CONTROL PORT ................................ .............. 81

3.6.2. APMS--ADVANCED POWER MANAGEMENT STATUS PORT ................................ .................. 81

3.7. APIC REGISTERS (82379AB ONLY) ................................ ................................ ................................ ...... 81

3.7.1. IOREGSEL--I/O REGISTER SELECT REGISTER (82379AB Only)

................................ ............ 82

3.7.2. IOWIN--I/O WINDOW REGISTER (82379AB Only) ................................ ................................ ....... 82

3.7.3. APICID--I/O APIC IDENTIFICATION REGISTER (82379AB Only) ................................ .............. 82

3.7.4. APICID--I/O APIC VERSION REGISTER (82379AB Only) ................................ ........................... 83

3.7.5. APICARB--I/O APIC ARBITRATION REGISTER (82379AB Only) ................................ ............... 83

3.7.6. IOREDTBL[15:0]--I/O REDIRECTION TABLE REGISTERS (82379AB Only) ............................. 83

4.0. FUNCTIONAL DESCRIPTION .................................................................................................................... 86

4.1. MEMORY AND I/O ADDRESS MAP ................................ ................................ ................................ ....... 86

4.1.1. MEMORY ADDRESS MAP (GENERATING MEMCS#) ................................ ................................ . 86

4.1.2. BIOS MEMORY SPACE ................................ ................................ ................................ .................... 87

4.1.3. I/O ACCESSES ................................ ................................ ................................ ................................ .. 87

4.1.4. SUBTRACTIVELY DECODED CYCLES TO ISA ................................ ................................ ............ 88

4.1.5. UTILITY BUS ENCODED CHIP SELECTS ................................ ................................ ..................... 88

4.2. PCI INTERFACE ................................ ................................ ................................ ................................ ....... 88

4.2.1. PCI COMMAND SET ................................ ................................ ................................ ......................... 88

4.2.2. TRANSACTION TERMINATION ................................ ................................ ................................ ....... 89

4.3. PCI ARBITRATION CONTROLLER ................................ ................................ ................................ ........ 90

4.3.1. ARBITRATION SIGNAL PROTOCOL ................................ ................................ .............................. 90

4.3.2. INTERNAL/EXTERNAL ARBITER CONFIGURATION ................................ ................................ ... 91

4.3.3. Guaranteed Access Time Mode ................................ ................................ ................................ ........ 92

4.3.3.1. DMA LATENCIES IN GAT MODE ONLY (82378ZB ONLY) ................................ .................... 92

4.4. ISA INTERFACE ................................ ................................ ................................ ................................ ....... 92

4.4.1. ISA CLOCK GENERATION ................................ ................................ ................................ ............... 93

4.5. DMA CONTROLLER ................................ ................................ ................................ ................................ . 93