ii

82801AA and 82801AB

Datasheet

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual

property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability

whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to

fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not

intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

The Intel

Æ

82801AA (ICH) and Intel

Æ

82801AB (ICH0) may contain design defects or errors known as errata which may cause the product to deviate

from published specifications. Current characterized errata are available upon request.

I

2

C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I

2

C bus/protocol and was developed by Intel.

Implementations of the I

2

C bus/protocol or the SMBus bus/protocol may require licenses from various entities, including Philips Electronics N.V. and

North American Philips Corporation.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by:

calling 1-800-548-4725 or

by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1999

*Third-party brands and names are the property of their respective owners.

82801AA and 82801AB

Datasheet

iii

Intel

Æ

82801AA (I CH) and Intel

Æ

82801AB (ICH0)

Features

s

PCI Bus Interface

-- Supports PCI at 33 MHz

-- Supports PCI Rev 2.2 Specification

-- 133 MByte/sec Maximum Throughput

s

Integrated IDE Controller

-- Independent Timing of Up to 4 Drives

-- Supports Ultra ATA/33 Mode

(33 Mbytes/sec)

-- PIO Mode 4 Transfers up to 14 Mbytes/s

-- Separate IDE Connections for Primary and

Secondary Cables

-- Implements Write Ping-Pong Buffer for

faster write performance

s

USB

-- UHCI Implementation With 2 Ports

-- Supports Wake-up From Sleeping States

S1-S4

-- Supports Legacy Keyboard/Mouse Software

-- USB Revision 1.1 Compliant

s

AC'97 Link for Audio and Telephony CODECs

-- AC'97 2.1 Compliant

-- 5 Independent Bus Master Logic for PCM In,

PCM Out, Mic Input, Modem In, Modem

Out

-- Separate Independent PCI Functions for

Audio and Modem

-- Supports wake-up events

s

Interrupt Controller

-- Two Cascaded 82C59

-- Integrated I/O APIC Capability

-- 15 Interrupts Support in 8259 Mode, 24

Supported in I/O APIC Mode.

-- Supports Serial Interrupt Protocol

s

Timers Based on 82C54

s

System Timer, Refresh Request, Speaker Tone

Output

s

3.3 V Operation With 5 V Tolerant Buffers for

IDE and PCI signals.

s

241 BGA package

s

GPIO

-- TTL, Open-Drain, Inversion

s

Power Management Logic

-- ACPI 1.0 Compliant

-- Support for APM-Based Legacy Power

Management for Non-ACPI Implementations

-- ACPI Defined Power States (S1, S3, S4, S5)

-- ACPI Power Management Timer

-- SMI# Generation

-- All Registers Readable/Restorable for Proper

Resume from 0 V Suspend States

-- PCI PME#

s

Low Pin count (LPC) Interface

-- Allows Connection of Legacy ISA and

X-Bus Devices such as Super I/O

-- Supports Two Master/DMA Devices.

s

Enhanced DMA Controller

-- Two Cascaded 8237 DMA Controllers

-- PCI DMA: Supports PC/PCI -- Includes

Two PC/PCI REQ#/GNT# Pairs

-- Supports LPC DMA

-- Supports DMA Collection Buffer to Provide

Type-F DMA Performance for All DMA

Channels

s

Real - Time Clock

-- 256-byte Battery-Backed CMOS RAM

-- Hardware implementation to indicate

Century Rollover

s

System TCO Reduction Circuits

-- Timers to Generate SMI# and Reset Upon

Detection of locked system

-- Timers to Detect Improper Processor Reset

-- Integrated Processor Frequency Strap Logic

s

SM Bus

-- Host Interface Allows Processor to

Communicate via SM Bus

-- Compatible With Most 2-Wire Components

that are Also I

2

C compatible

s

Supports ISA Bus via External PCI-ISA Bridge

s

Firmware Hub (FWH) Interface

-- Master PCI Device Support: up to 6 for the

ICH and up to 4 for the ICH0

-- The ICH Supports Ultra ATA/66 Mode (66

Mbytes/sec)

s

The 82801AA provides Alert On LAN*

Support

The Intel

Æ

82801AA and Intel

Æ

82801AB may contain design defects or errors known as errata which may cause the

products to deviate from published specifications. Current characterized errata are available on request.

This datasheet describes the Intel

Æ

82801AA and Intel

Æ

82801AB components. Non-shaded areas

describe the functionality of both components.

Shading,as is shown here, indicates differences between the two components.

iv

82801AA and 82801AB

Datasheet

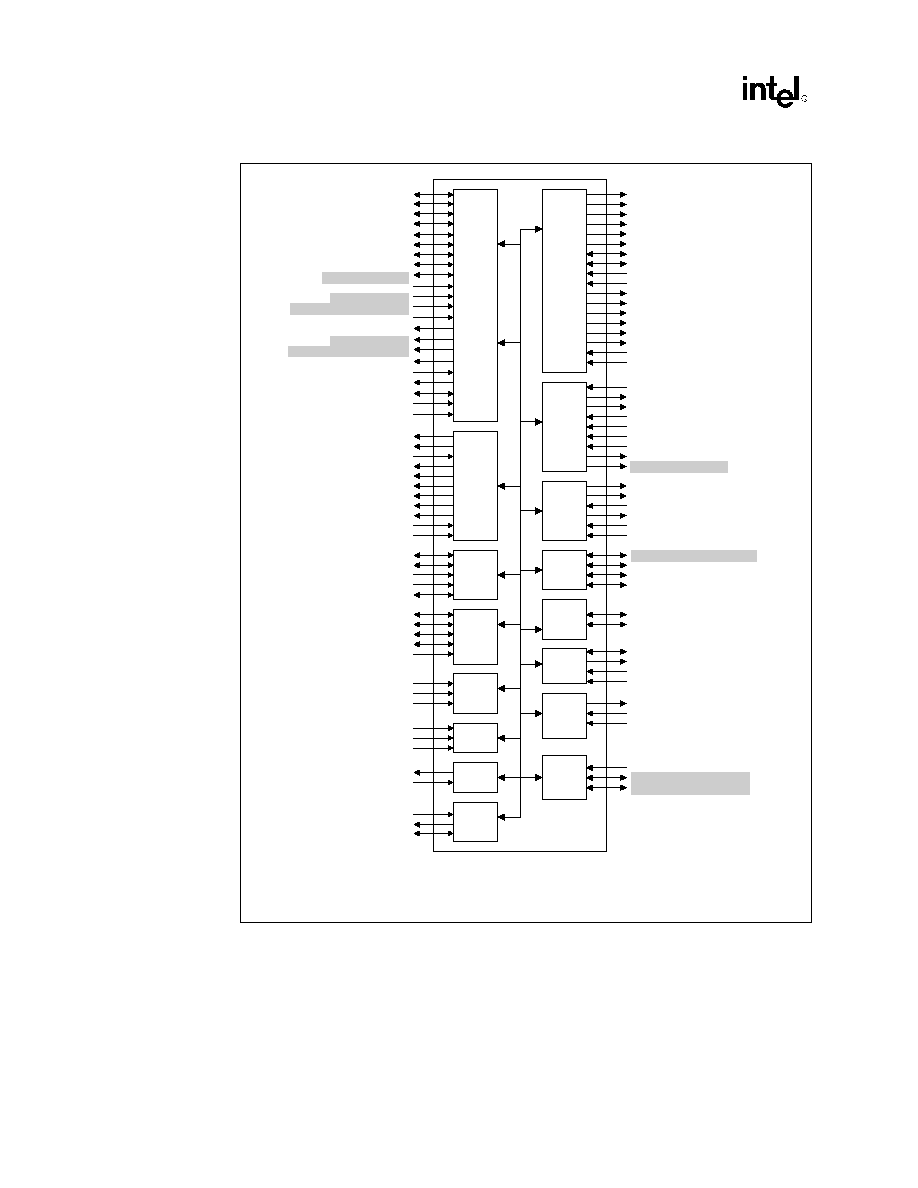

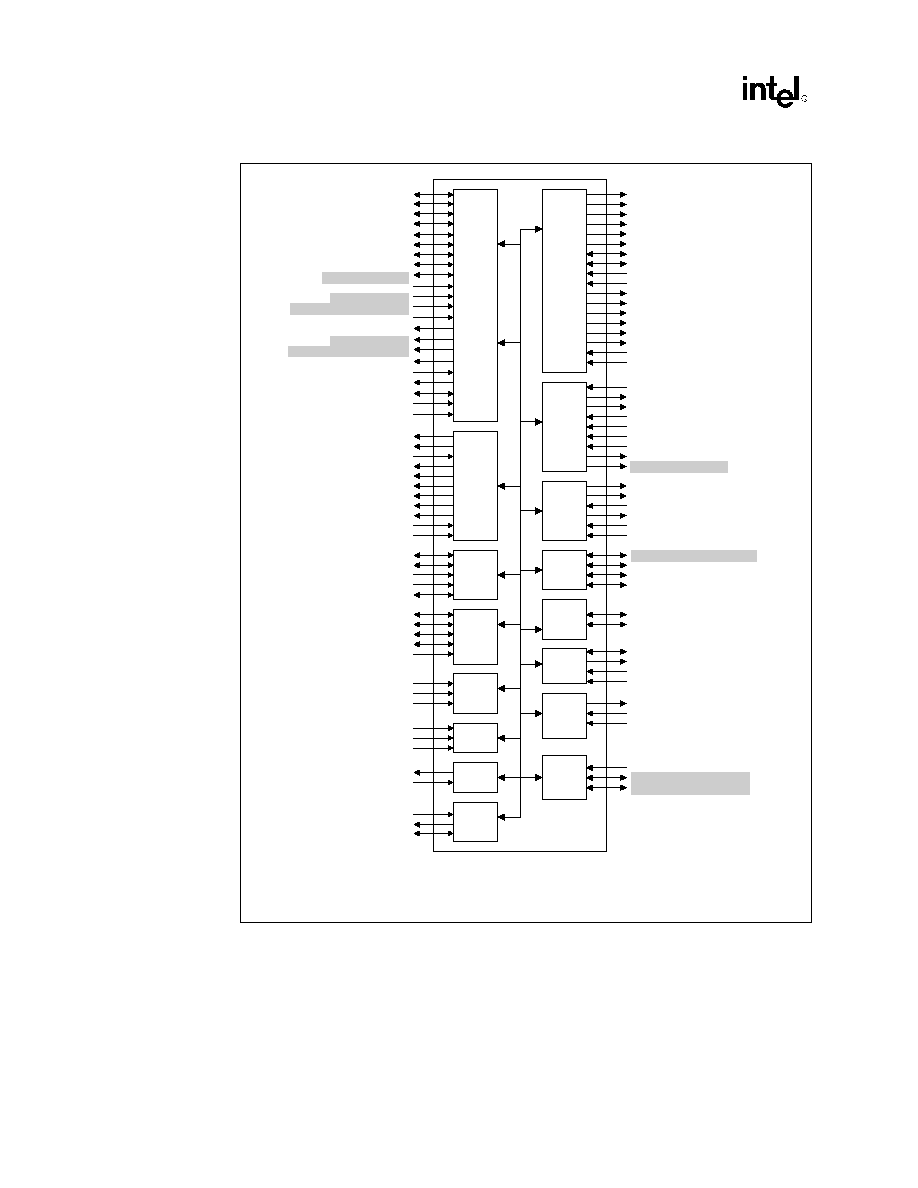

Intel

Æ

82801AA (ICH) and Intel

Æ

82801AB (ICH0) Simplified Block Diagram

Interrupt

AD[31:0]

C/BE[3:0]#

DEVSEL#

FRAME#

IRDY#

TRDY#

STOP#

PAR

(ICH) PERR#/GPIO7

REQ[0:3]#

(ICH) REQ[4]#

(ICH) REQ5#/REQB#/GPIO1

REQA#

GNT[0:3]#

(ICH) GNT[4]#

(ICH) GNT5#/GNTB#/GPIO17

GNTA#

PCICLK

PCIRST#

PLOCK#

SERR#

PME#

A20M#

CPUSLP#

FERR#

IGNNE#

INIT#

INTR

NMI

SMI#

STPCLK#

RCIN#

A20GATE

CPU

Interface

PCI

Interface

USB

SERIRQ

PIRQ[A:D]#

IRQ[14:15]

APICCLK

APICD[1:0]

USBP1P

USBP1N

USBP0P

USBP0N

OC[1:0]#

RTCX1

RTCX2

VBIAS

CLK14

CLK48

CLK66

RTC

Clocks

Misc.

Signals

SPKR

RTCRST#

PDCS1#

SDCS1#

PDCS3#

SDCS3#

PDA[2:0]

SDA[2:0]

PDD[15:0]

SDD[15:0]

PDDREQ

SDDREQ

PDDACK#

SDDACK#

PDIOR#

SDIOR#

PDIOW#

SDIOW#

PIORDY

SIORDY

IDE

Interface

HL[10:0] (ICH0); HL11:0] (ICH)

HL_STB

HL_STB#

HLCOMP

Hub

Interface

LPC

Interface

SMBus

Interface

THRM#

SLP_S3/GPIO24

SLP_S5#

PWROK

PWRBTN#

RI#

RSMRST#

SUS_STAT#/GPIO25

SUSCLK/GPIO26 (ICH)

Power

Mgnt

AC_RST#

AC_SYNC

AC_BIT_CLK

AC_SDOUT

AC_SDIN0

AC_SDIN1/GPIO9

AC'97

Link

Firmware

Hub

System

Mgnt

General

Purpose

I/O

FWH[3:0]/LAD[3:0]

FWH[4]/LFRAME#

LAD[3:0]/FWH[4]

LFRAME#/FWH[4]

LDRQ[0]#

LDRQ[1]#/GPIO[8]

SMBDATA

SMBCLK

SMBALERT#/GPIO[11]

INTRUDER#

ALERTCLK/GPIO[27] (ICH)

ALERTDATA/GPIO[28] (ICH)

GPIO[0,1,5:13]

GPIO[16,17, 21:26]

GPIO[27:28]

Note

1. Shaded areas: PERR#, REQ[4,5]#, GNT[4,5]#, HL[11], SUSCLK, ALERTCLK, and ALERTDATA are ICH

(82801AA) Signals only. The associated GPIOx signals are multiplexed on the ICH and are

non-multiplexed on ICH0.

2. General Purpose I/O Unit. Some GPIO signals are multiplexed with signals in other functional units.