| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 82801E | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Intel

Æ

82801E Communications I/O

Controller Hub (C-ICH)

for Applied Computing

Advance Information Datasheet

Product Features

s

Supports Intel processors, the

82815E GMCH and the 82810E GMCH

s

8-Bit Hub Interface

-- 266 Mbyte/s maximum throughput

s

Two integrated LAN controllers

s

USB

-- Includes one UHCI Host Controller

with a total of two ports

-- USB 1.1 compliant

s

PCI Bus interface

-- Supports PCI Rev 2.2 specification at

33 MHz

-- 133 Mbyte/s maximum throughput

s

Low-Pincount (LPC) interface

s

Firmware Hub (FWH) interface

-- Supports 8-Mbyte memory size

s

Integrated IDE controller supports

Ultra100 DMA, Ultra66 and Ultra33

DMA mode transfers

s

Interrupt Controller

-- Two cascaded 82C59 interrupt

controllers

-- Integrated I/O (x) APIC supporting 24

interrupts

-- 15 interrupts supported in 8259 mode

s

Two cascaded 8237 DMA controllers

s

Integrated 82C54-compatible timers

s

Real-time clock with 256-byte battery-

backed CMOS RAM

s

System Management Bus (SMBus)

-- Compatible with most two-wire

components that are also I

2

C compatible

-- Slave interface allows external

microcontroller to access system

resources

s

GPIO

-- Exact number varies by configuration.

Maximum: 12 inputs, eight outputs, four

I/O

s

Integrated 16550 compatible UARTs

-- Two UARTs

-- Serial Interrupts

s

Supports IRQ1/IRQ12 emulation to avoid

external keyboard controller

s

1.8 V operation with 3.3 V I/O. 5 V

tolerance on many buffers, including PCI

and IDE

s

Package: 421 BGA

Order Number: 273598-003

January 2002

Notice: This document contains information on products in the sampling and initial production

phases of development. The specifications are subject to change without notice. Verify with your

local Intel sales office that you have the latest datasheet before finalizing a design.

2

Advance Information Datasheet

Information in this document is provided in connection with Intel

Æ

products. No license, express or implied, by estoppel or otherwise, to any intellectual

property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability

whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to

fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not

intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel

Æ

82801E Communications I/O Controller Hub may contain design defects or errors known as errata which may cause the product to deviate

from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling

1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2002

AlertVIEW, i960, AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, Commerce Cart, CT Connect, CT Media, Dialogic,

DM3, EtherExpress, ETOX, FlashFile, GatherRound, i386, i486, iCat, iCOMP, Insight960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740,

IntelDX2, IntelDX4, IntelSX2, Intel ChatPad, Intel Create&Share, Intel Dot.Station, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel

NetBurst, Intel NetStructure, Intel Play, Intel Play logo, Intel Pocket Concert, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation,

Intel WebOutfitter, Intel Xeon, Intel XScale, Itanium, JobAnalyst, LANDesk, LanRover, MCS, MMX, MMX logo, NetPort, NetportExpress, Optimizer

logo, OverDrive, Paragon, PC Dads, PC Parents, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, ProShare,

RemoteExpress, Screamline, Shiva, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside, The Journey Inside, This Way In,

TokenExpress, Trillium, Vivonic, and VTune are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and

other countries.

*Other names and brands may be claimed as the property of others.

Advance Information Datasheet

3

Contents

Contents

1.0

Introduction....................................................................................................................................7

1.1

Overview ............................................................................................................................... 9

1.2

About this Document .......................................................................................................... 10

2.0

Package Information ................................................................................................................... 11

2.1

Ball Location ....................................................................................................................... 11

2.2

Mechanical Specifications .................................................................................................. 23

3.0

Signal Descriptions ..................................................................................................................... 25

3.1

Alphabetical Signal Reference............................................................................................25

3.2

Signals Grouped By Type ................................................................................................... 36

3.2.1

Hub Interface to Host Controller ............................................................................ 36

3.2.2

Link to LAN Connect .............................................................................................. 36

3.2.3

EEPROM Interface ................................................................................................ 36

3.2.4

Firmware Hub Interface ......................................................................................... 37

3.2.5

PCI Interface .......................................................................................................... 37

3.2.6

IDE Interface .......................................................................................................... 40

3.2.7

LPC Interface ......................................................................................................... 41

3.2.8

Interrupt Interface .................................................................................................. 41

3.2.9

USB Interface ........................................................................................................42

3.2.10 Power Signals ........................................................................................................42

3.2.11 Processor Interface................................................................................................ 43

3.2.12 SMBus Interface .................................................................................................... 44

3.2.13 System Management Interface ..............................................................................44

3.2.14 Real Time Clock Interface .....................................................................................44

3.2.15 Other Clocks .......................................................................................................... 45

3.2.16 Universal Asynchronous Receive and Transmit (UART 0,1) .................................45

3.2.17 SIU LPC Interface .................................................................................................. 46

3.2.18 Miscellaneous Signals ........................................................................................... 47

3.2.19 General Purpose I/O .............................................................................................. 47

3.2.20 Power and Ground.................................................................................................48

3.3

Pin Straps ...........................................................................................................................49

3.3.1

Functional Straps ................................................................................................... 49

3.3.2

Test Signals ........................................................................................................... 49

3.3.2.1

Test Mode Selection ..............................................................................49

3.3.2.2

Test Straps............................................................................................. 50

3.3.3

External RTC Circuitry ........................................................................................... 50

3.3.4

V5REF/Vcc3_3 Sequencing Requirements ...........................................................51

3.4

Power Planes and Pin States ............................................................................................. 51

3.4.1

Power Planes......................................................................................................... 51

3.4.2

Integrated Pull-Ups and Pull-Downs ...................................................................... 52

3.4.3

IDE Integrated Series Termination Resistors......................................................... 52

3.4.4

Output and I/O Signals Planes and States ............................................................ 53

3.4.5

Power Planes for Input Signals..............................................................................55

4.0

Electrical Characteristics............................................................................................................ 57

4.1

Absolute Maximum Ratings ................................................................................................ 57

Contents

4

Advance Information Datasheet

4.2

Functional Operating Range............................................................................................... 57

4.3

DC Characteristics.............................................................................................................. 58

4.4

AC Characteristics .............................................................................................................. 62

4.5

Timing Diagrams................................................................................................................. 70

5.0

Testability..................................................................................................................................... 77

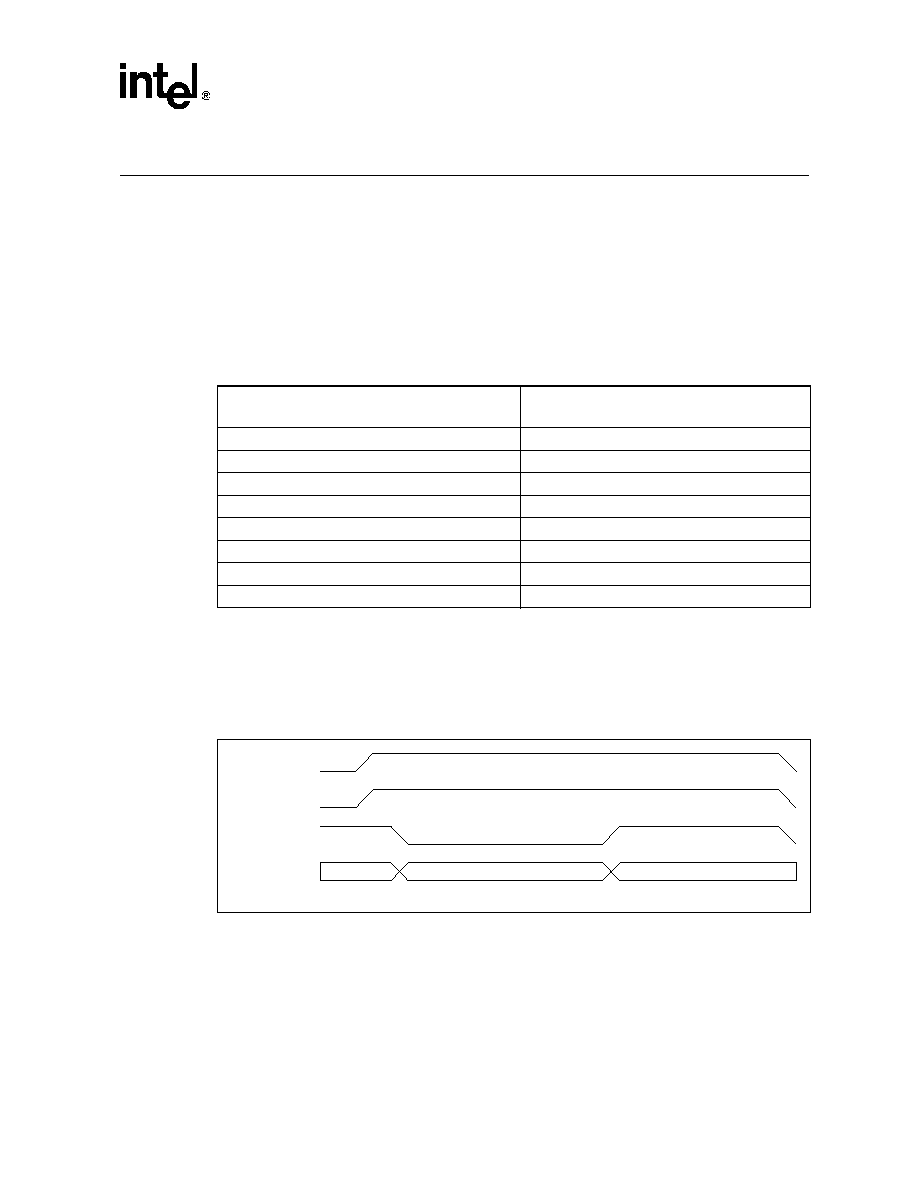

5.1

Test Mode Description........................................................................................................ 77

5.2

Tri-state Mode..................................................................................................................... 78

5.3

XOR Chain Mode................................................................................................................ 78

5.3.1

XOR Chain Testability Algorithm Example ............................................................ 84

5.3.1.1

Test Pattern Consideration for XOR Chain 4......................................... 84

Figures

1

System Configuration ................................................................................................................... 7

2

Intel

Æ

82801E C-ICH Simplified Block Diagram ........................................................................... 8

3

Ball Diagram (Top View)............................................................................................................. 11

4

Intel

Æ

82801E C-ICH Package (Top View) ................................................................................. 23

5

Intel

Æ

82801E C-ICH Package (Side View) ................................................................................ 24

6

Intel

Æ

82801E C-ICH Package (Bottom View)............................................................................ 24

7

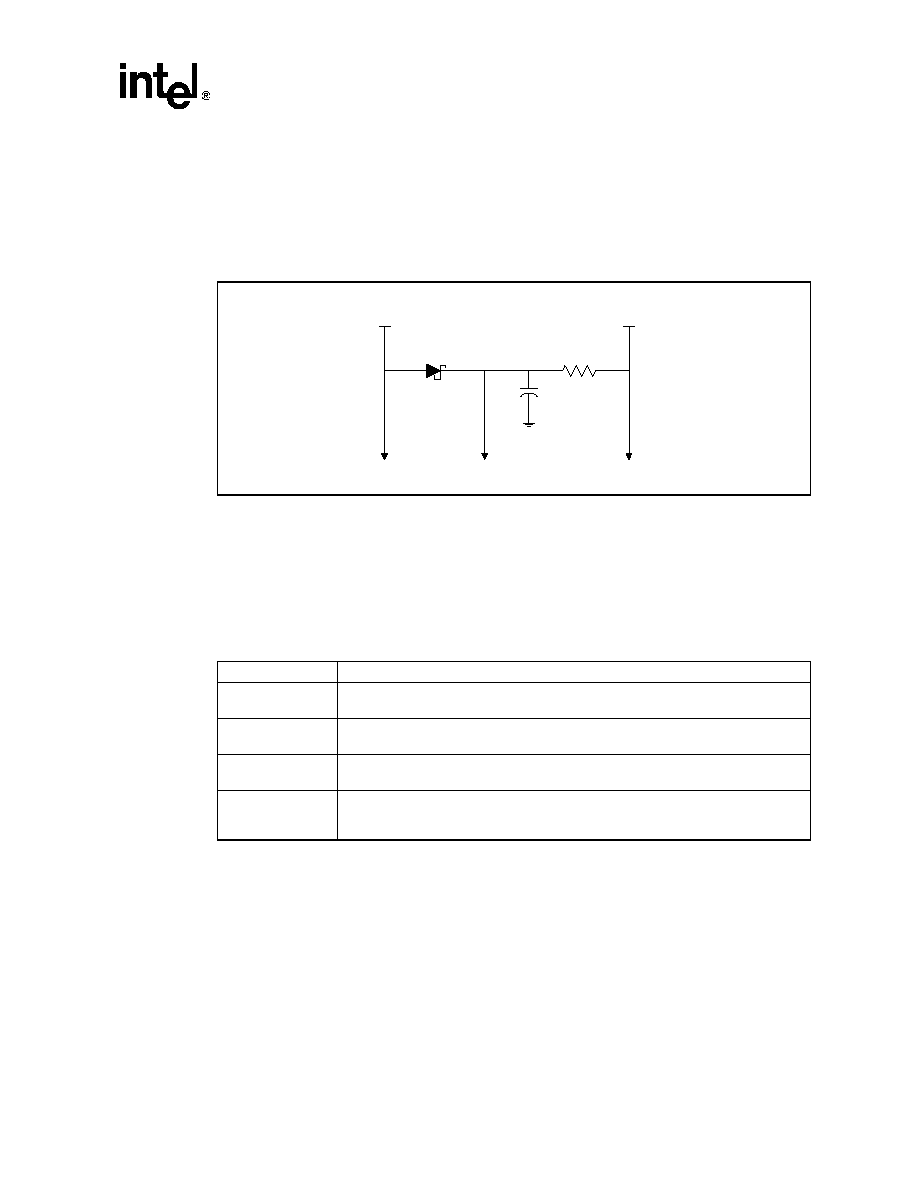

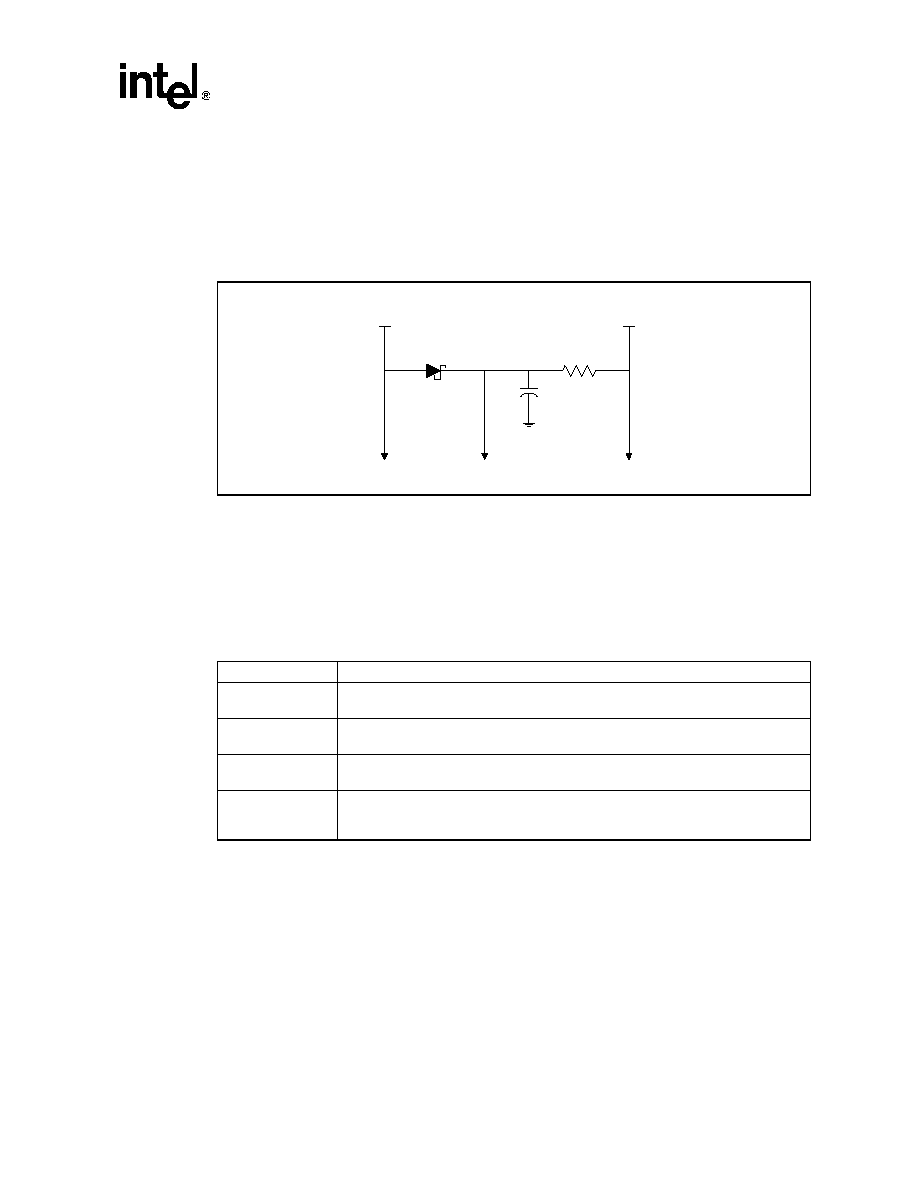

Required External RTC Circuit ................................................................................................... 50

8

Example V5REF Sequencing Circuit .......................................................................................... 51

9

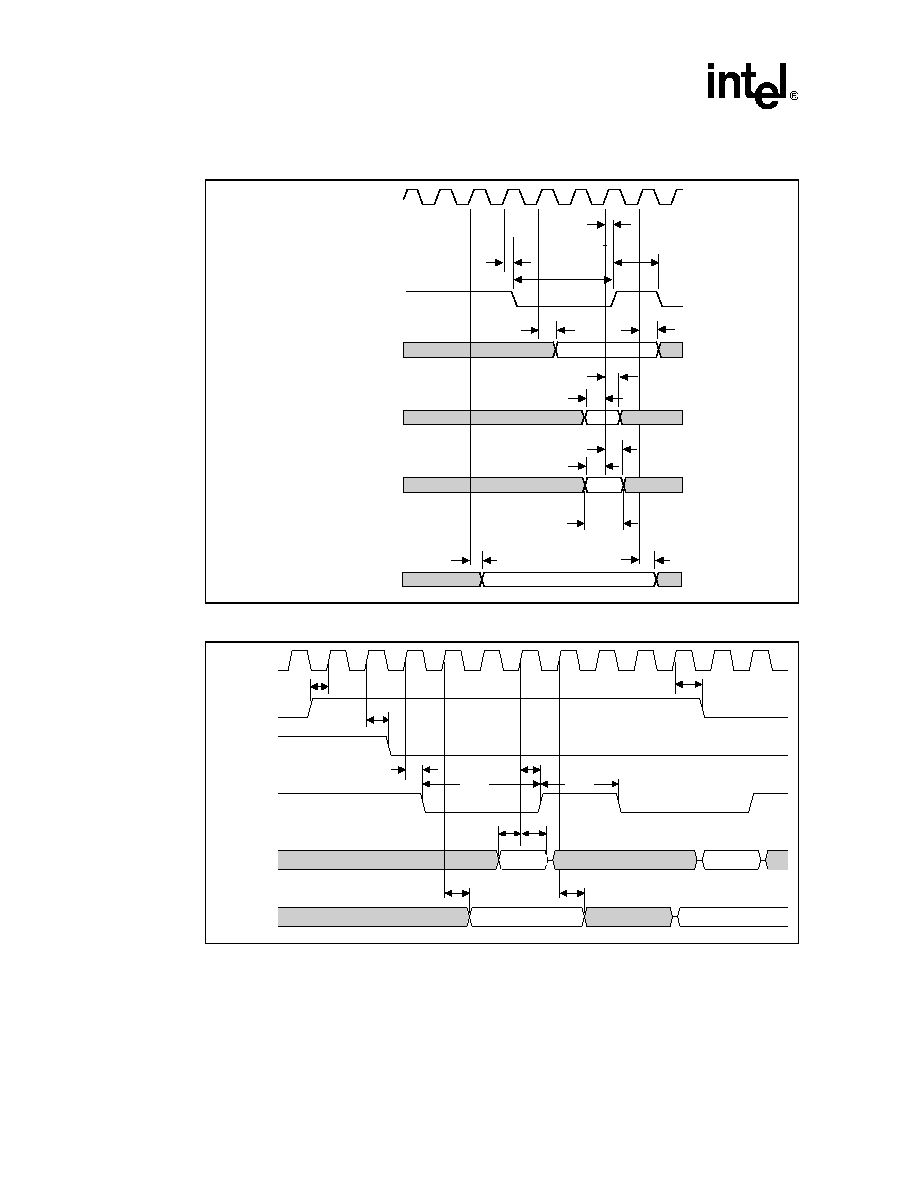

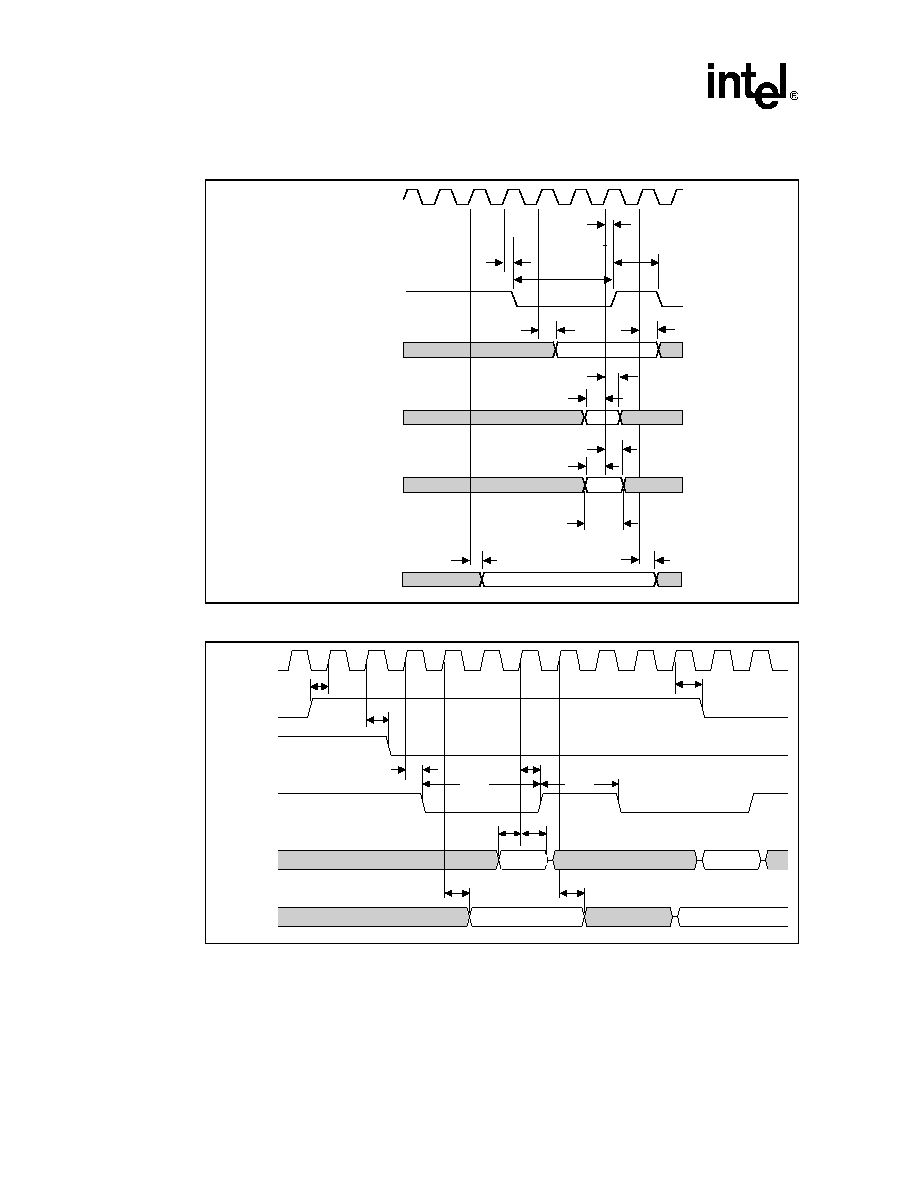

Clock Timing ............................................................................................................................... 70

10

Valid Delay From Rising Clock Edge.......................................................................................... 70

11

Setup And Hold Times................................................................................................................ 71

12

Float Delay ................................................................................................................................. 71

13

Pulse Width ................................................................................................................................ 71

14

Output Enable Delay .................................................................................................................. 71

15

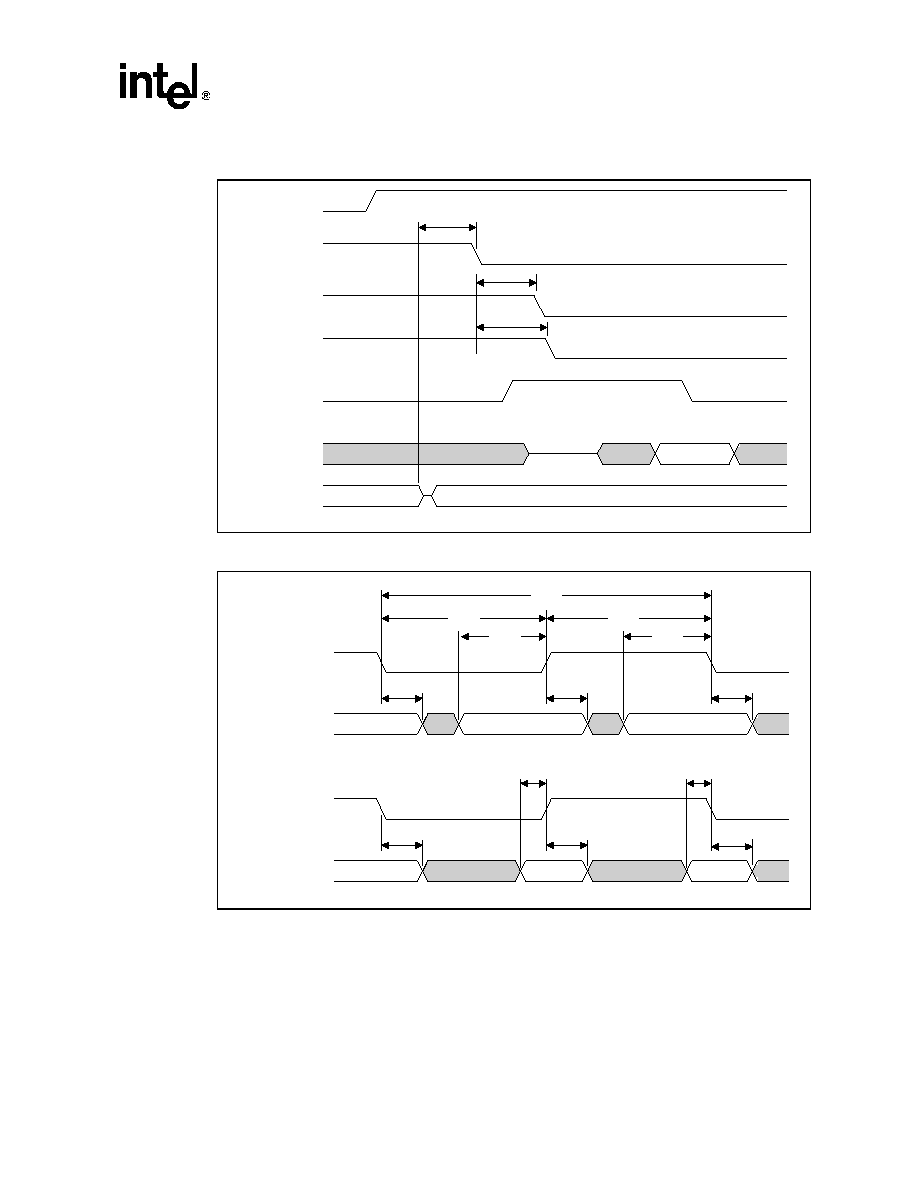

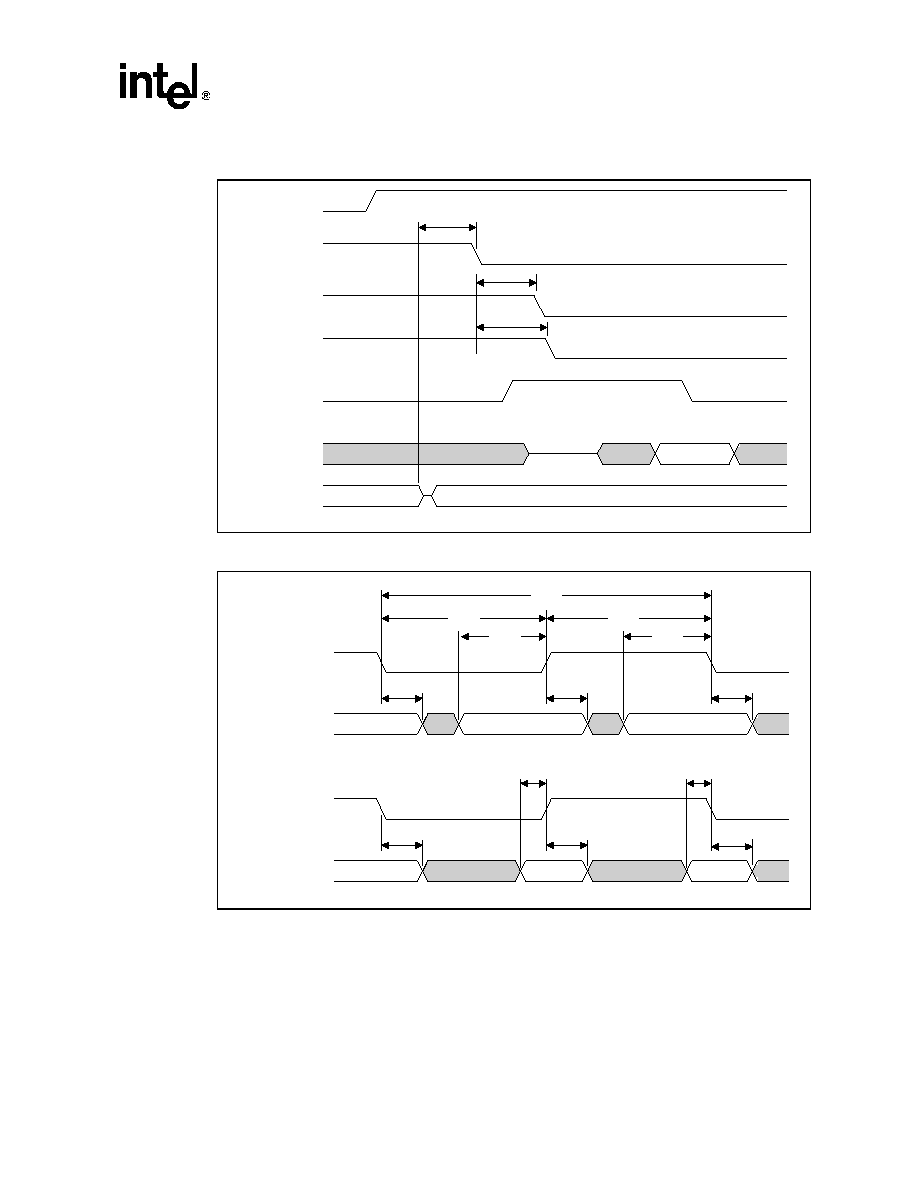

IDE PIO Mode ............................................................................................................................ 72

16

IDE Multiword DMA .................................................................................................................... 72

17

Ultra ATA Mode (Drive Initiating a Burst Read) .......................................................................... 73

18

Ultra ATA Mode (Sustained Burst) ............................................................................................. 73

19

Ultra ATA Mode (Pausing a DMA Burst) .................................................................................... 74

20

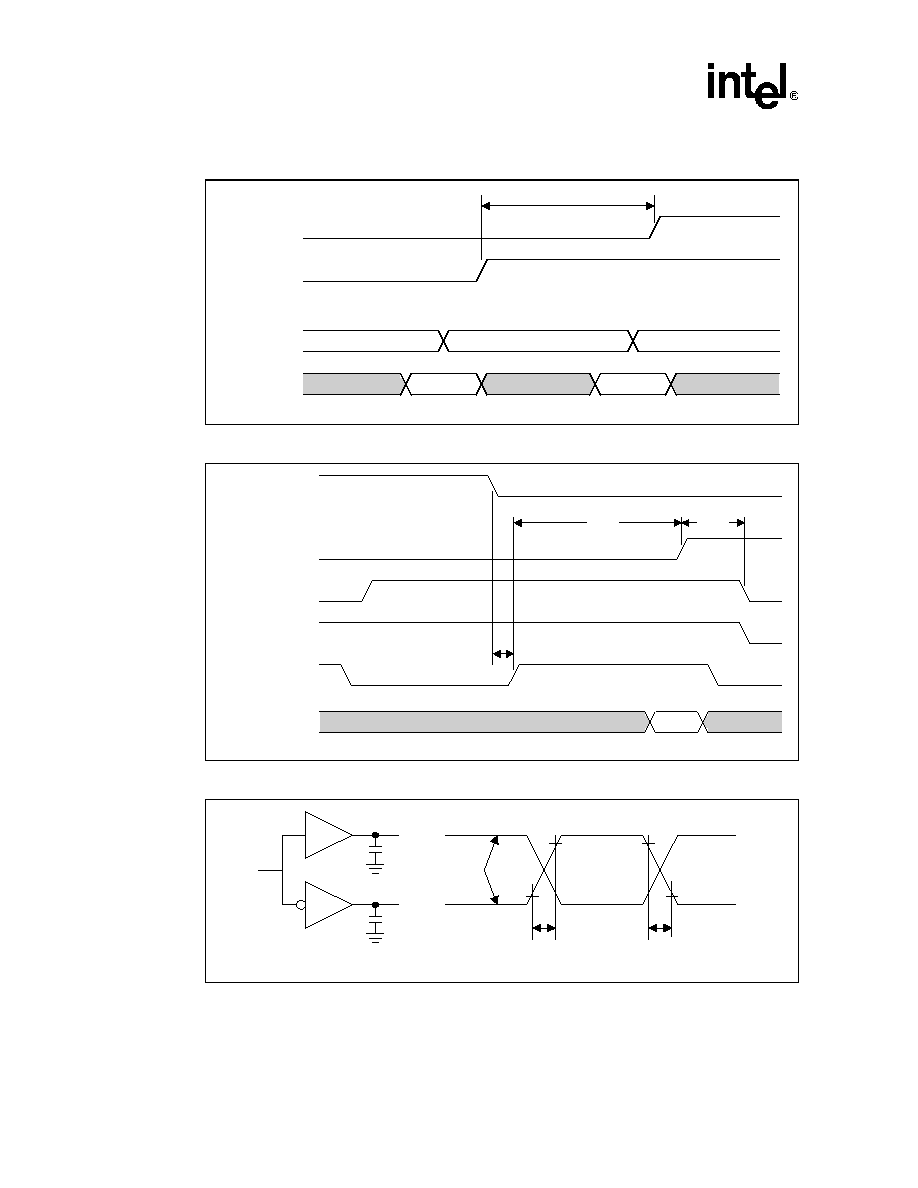

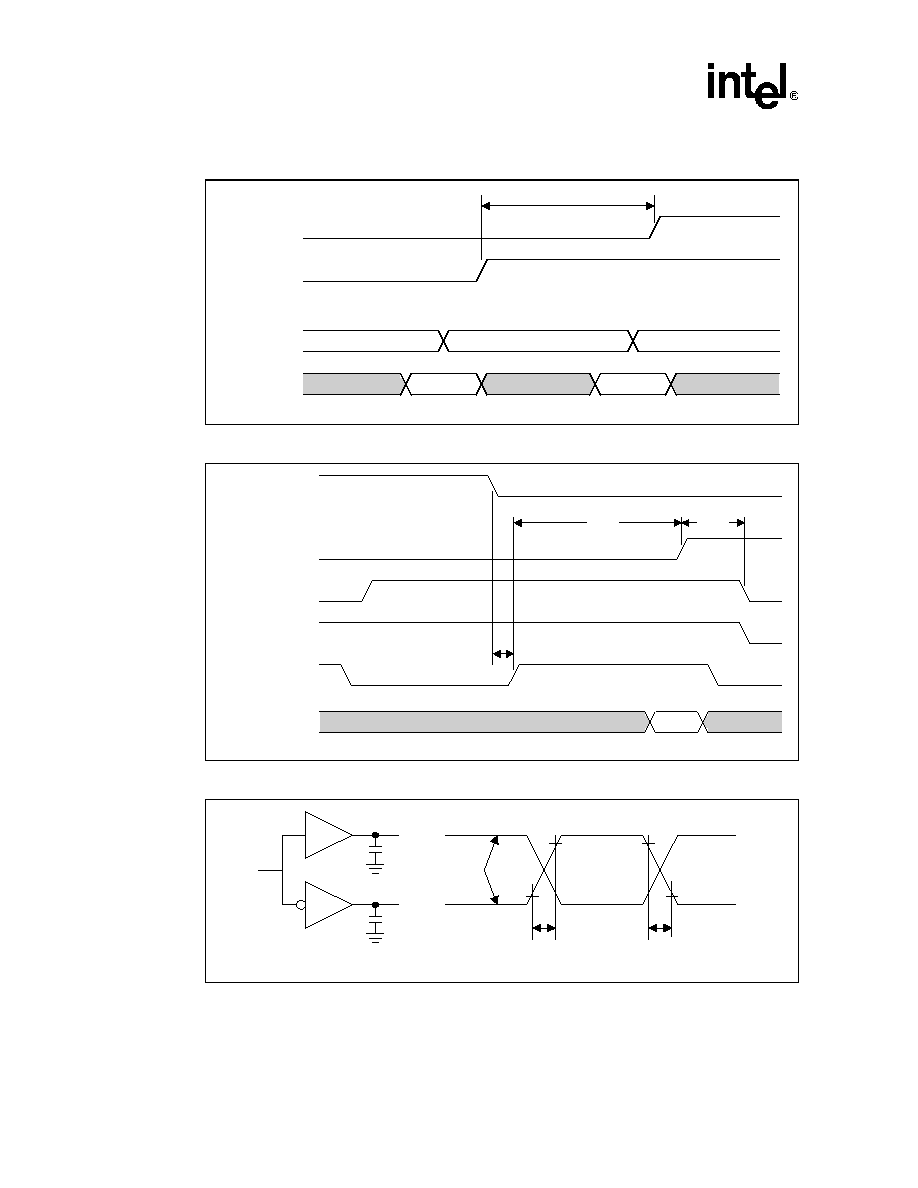

Ultra ATA Mode (Terminating a DMA Burst) .............................................................................. 74

21

USB Rise and Fall Times ........................................................................................................... 74

22

USB Jitter ................................................................................................................................... 75

23

USB EOP Width ......................................................................................................................... 75

24

SMBus Transaction .................................................................................................................... 75

25

SMBus Time-out ......................................................................................................................... 75

26

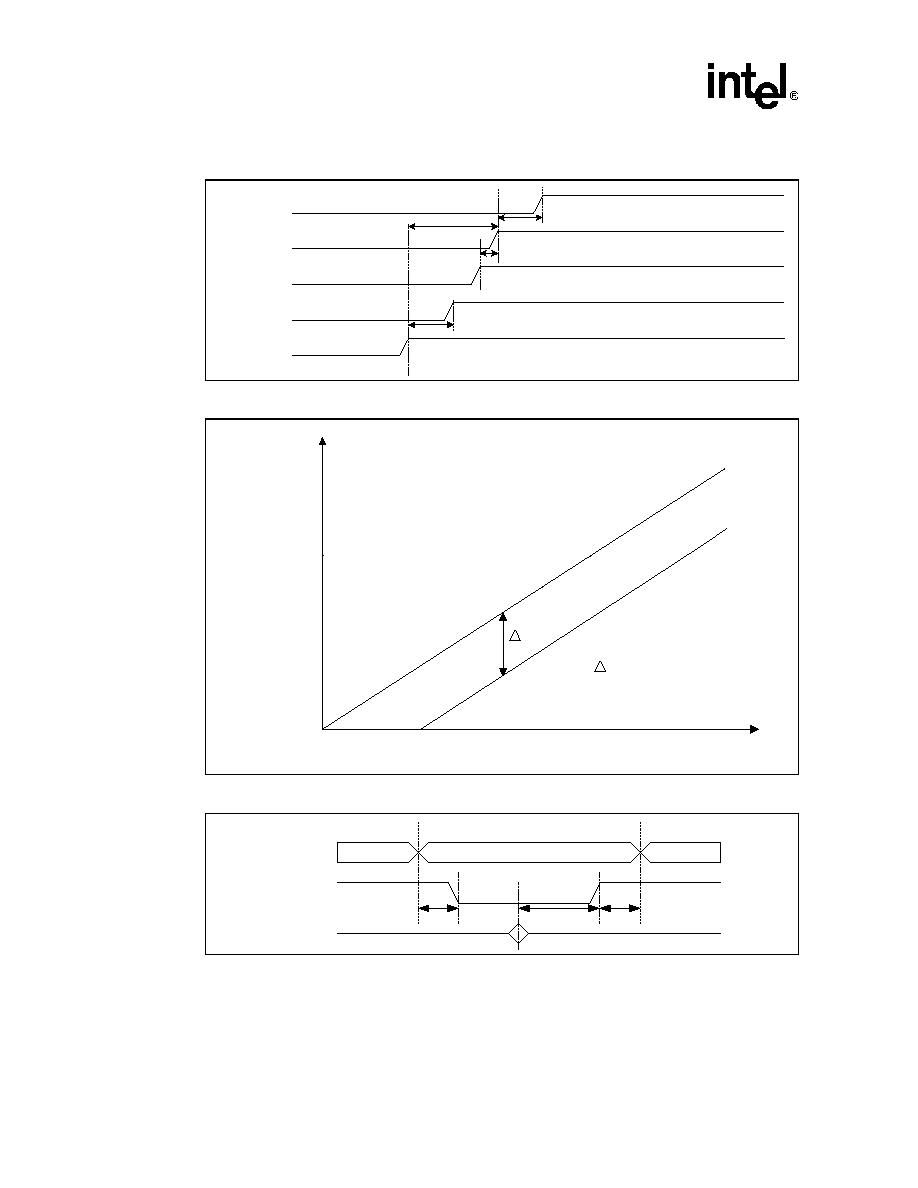

Power Sequencing and Reset Signal Timings ........................................................................... 76

27

1.8 V/3.3 V Power Sequencing................................................................................................... 76

28

C0 to C2 to C0 Timings .............................................................................................................. 76

29

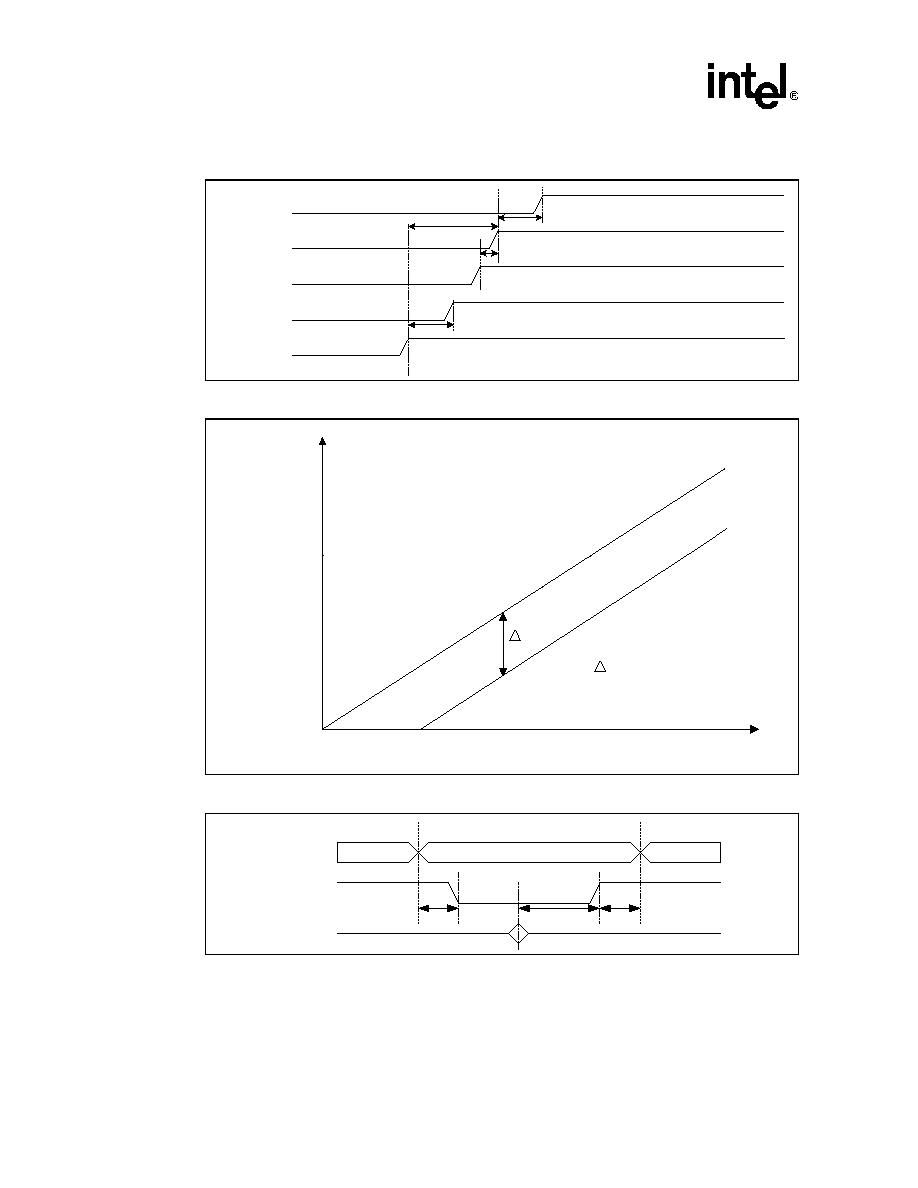

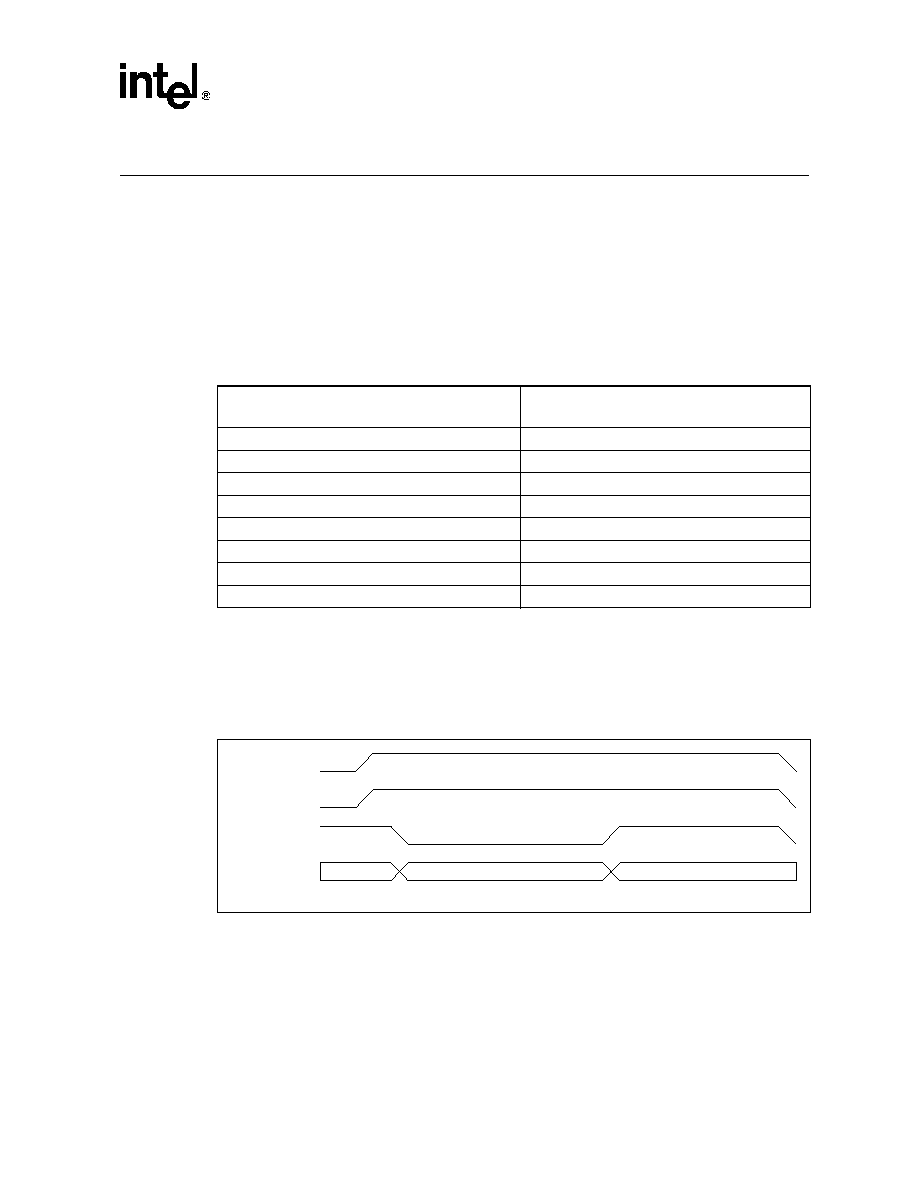

Test Mode Entry (XOR Chain Example)..................................................................................... 77

30

Example XOR Chain Circuitry .................................................................................................... 78

Advance Information Datasheet

5

Contents

Tables

1

PCI Devices and Functions ..........................................................................................................9

2

Related Documents ....................................................................................................................10

3

Industry Specifications................................................................................................................ 10

4

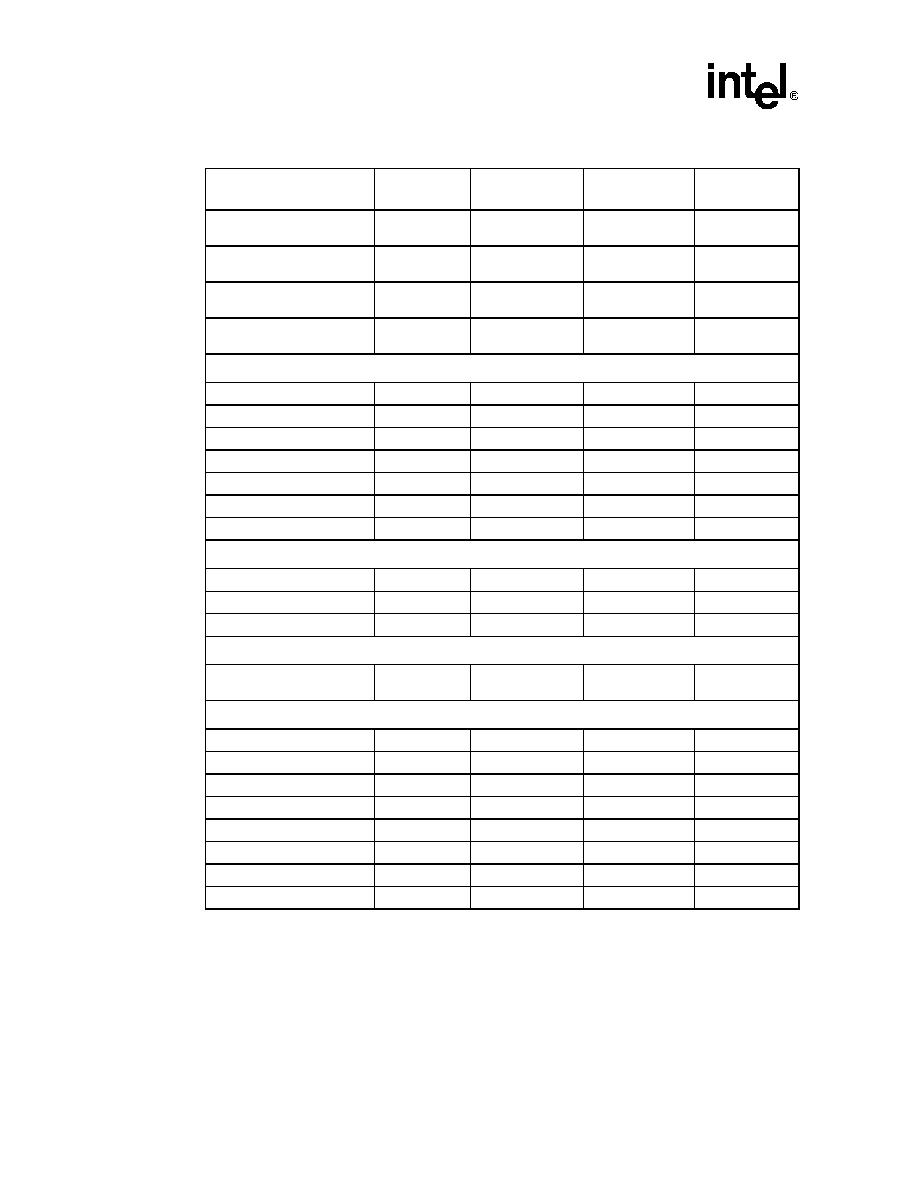

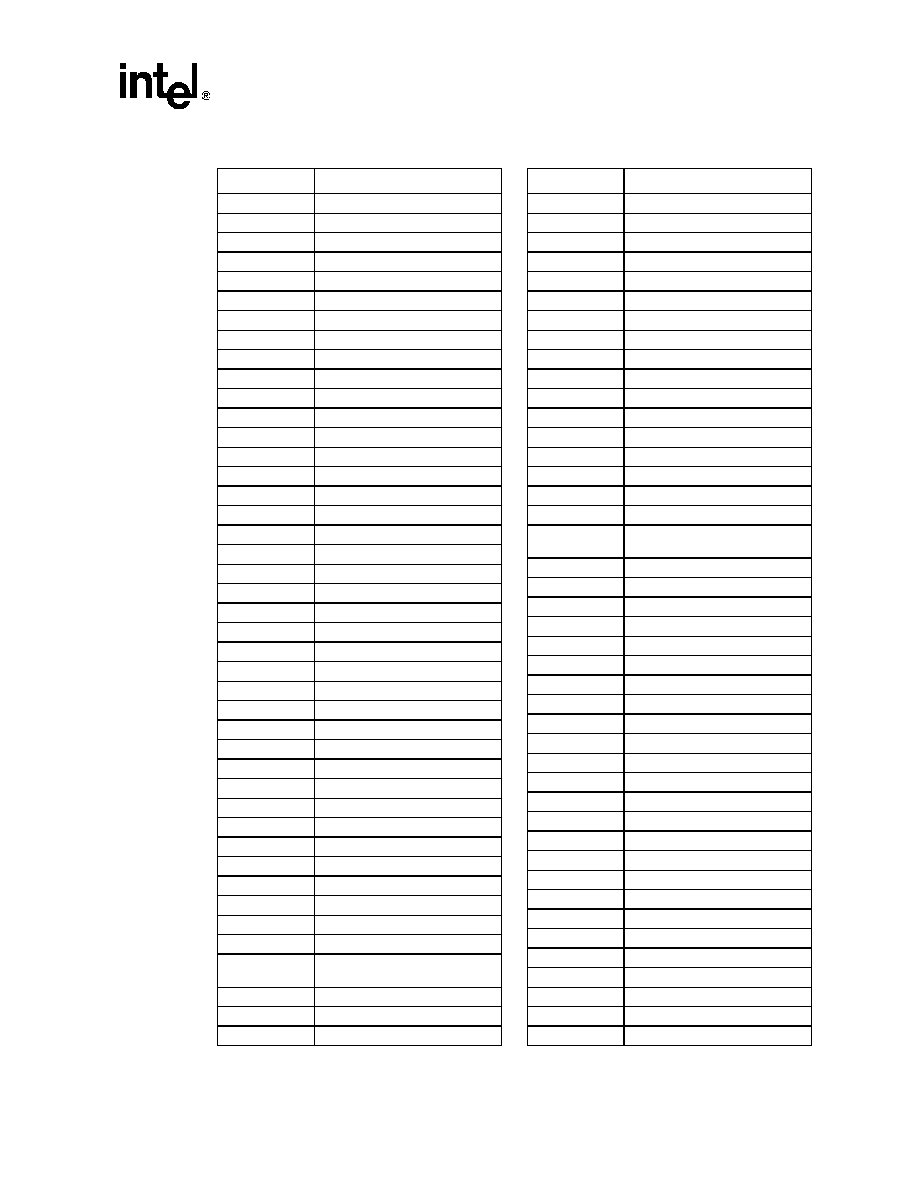

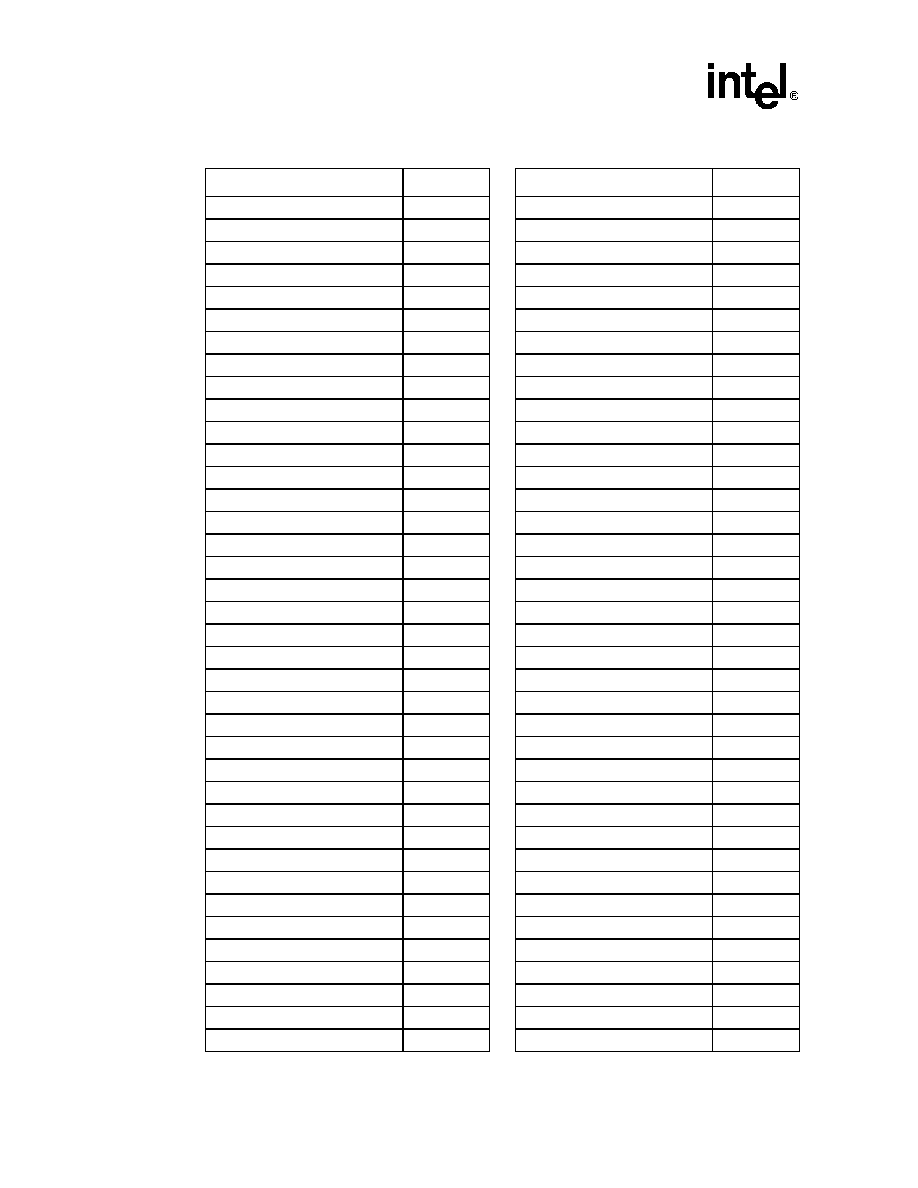

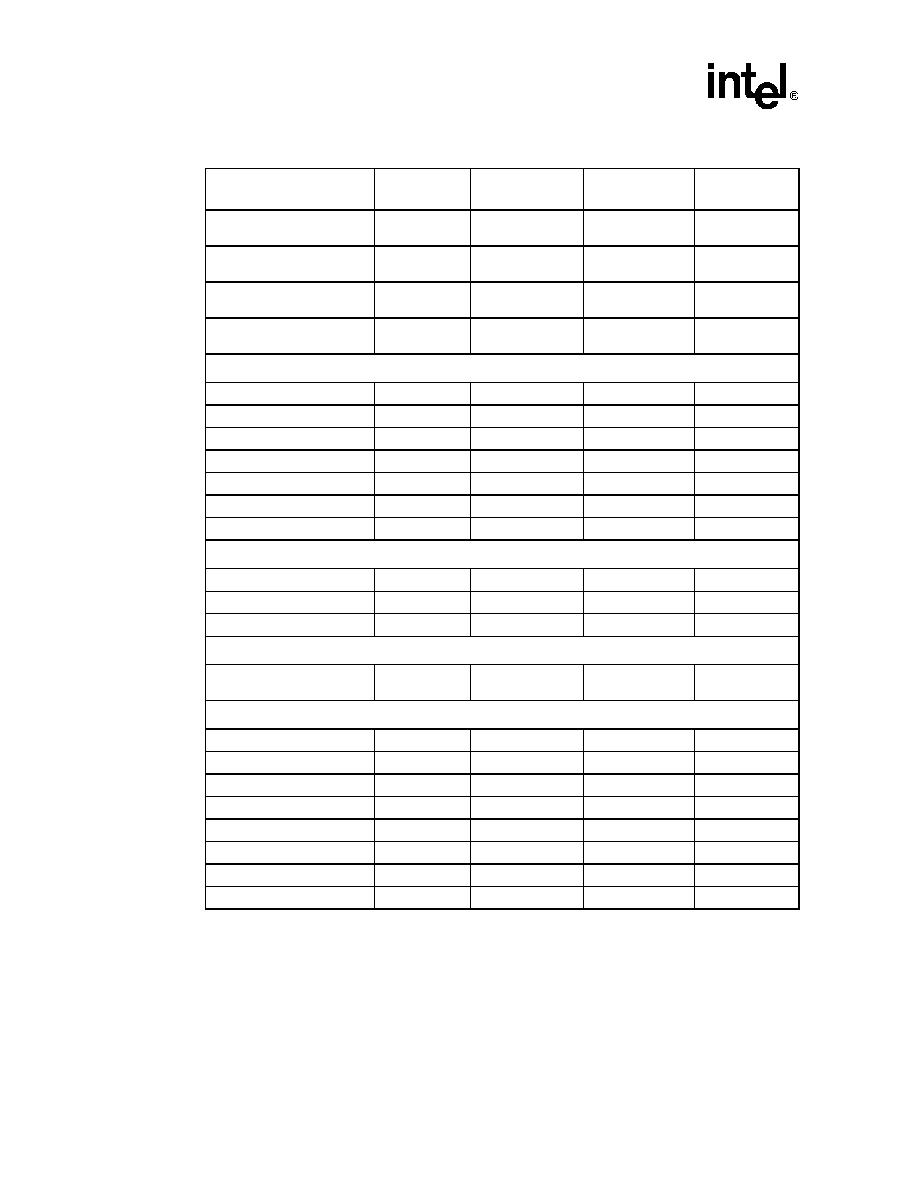

Ball List By Number ....................................................................................................................12

5

Ball List By Signal Name ............................................................................................................ 17

6

82801E C-ICH Signal Description .............................................................................................. 25

7

Hub Interface Signals ................................................................................................................. 36

8

LAN Interface.............................................................................................................................. 36

9

EEPROM Interface ..................................................................................................................... 36

10

Firmware Hub Interface Signals .................................................................................................37

11

PCI Interface Signals .................................................................................................................. 37

12

IDE Interface Signals .................................................................................................................. 40

13

LPC Interface Signals ................................................................................................................. 41

14

Interrupt Signals.......................................................................................................................... 41

15

USB Interface Signals................................................................................................................. 42

16

Power Signals............................................................................................................................. 42

17

Processor Interface Signals ........................................................................................................43

18

SMBus Interface Signals ............................................................................................................ 44

19

System Management Interface Signals ...................................................................................... 44

20

Real Time Clock Interface .......................................................................................................... 44

21

Other Clocks ............................................................................................................................... 45

22

Universal Asynchronous Receive And Transmit (UART 0, 1) ....................................................45

23

SIU Interface............................................................................................................................... 46

24

Miscellaneous Signals ................................................................................................................ 47

25

General Purpose I/O Signals ...................................................................................................... 47

26

Power and Ground Signals......................................................................................................... 48

27

Functional Strap Definitions ........................................................................................................49

28

Test Mode Selection ................................................................................................................... 49

29

82801E C-ICH Power Planes ..................................................................................................... 51

30

Integrated Pull-Up and Pull-Down Resistors ..............................................................................52

31

IDE Series Termination Resistors............................................................................................... 52

32

Power Plane and States for Output and I/O Signals................................................................... 53

33

Power Plane for Input Signals ................................................................................................ .... 56

34

Absolute Maximum Ratings ........................................................................................................57

35

Functional Operating Range....................................................................................................... 57

36

82801E C-ICH Power Consumption Measurements ..................................................................58

37

DC Characteristic Input Signal Association ................................................................................ 58

38

DC Input Characteristics............................................................................................................. 59

39

DC Characteristic Output Signal Association ............................................................................. 59

40

DC Output Characteristics .......................................................................................................... 60

41

Other DC Characteristics............................................................................................................ 61

42

Clock Timings ............................................................................................................................. 62

43

Clock Timings - UART_CLK ....................................................................................................... 63

44

PCI Interface Timing ................................................................................................................... 63

45

IDE PIO & Multiword DMA Mode Timing .................................................................................... 64

46

Ultra ATA Timing (Mode 0, Mode 1, Mode 2) ............................................................................. 65

47

Ultra ATA Timing (Mode 3, Mode 4, Mode 5) ............................................................................. 66

48

Universal Serial Bus Timing........................................................................................................67

49

IOAPIC Bus Timing..................................................................................................................... 68

Contents

6

Advance Information Datasheet

50

SMBus Timing ............................................................................................................................ 68

51

SIU LPC and Serial IRQ Timings ............................................................................................... 68

52

UART Timings ............................................................................................................................ 69

53

LPC Timing ................................................................................................................................. 69

54

Miscellaneous Timings ............................................................................................................... 69

55

Power Sequencing and Reset Signal Timings ........................................................................... 70

56

Test Mode Selection ................................................................................................................... 77

57

XOR Chain #1 ............................................................................................................................ 79

58

XOR Chain #2; Chain 2-1 and Chain 2-2 ................................................................................... 80

59

XOR Chain #3; Chain 3-1 and Chain 3-2 ................................................................................... 81

60

XOR Chain #4; Chain 4-1 and Chain 4-2 ................................................................................... 82

61

Signals Not in XOR Chain .......................................................................................................... 83

62

XOR Test Pattern Example ........................................................................................................ 84

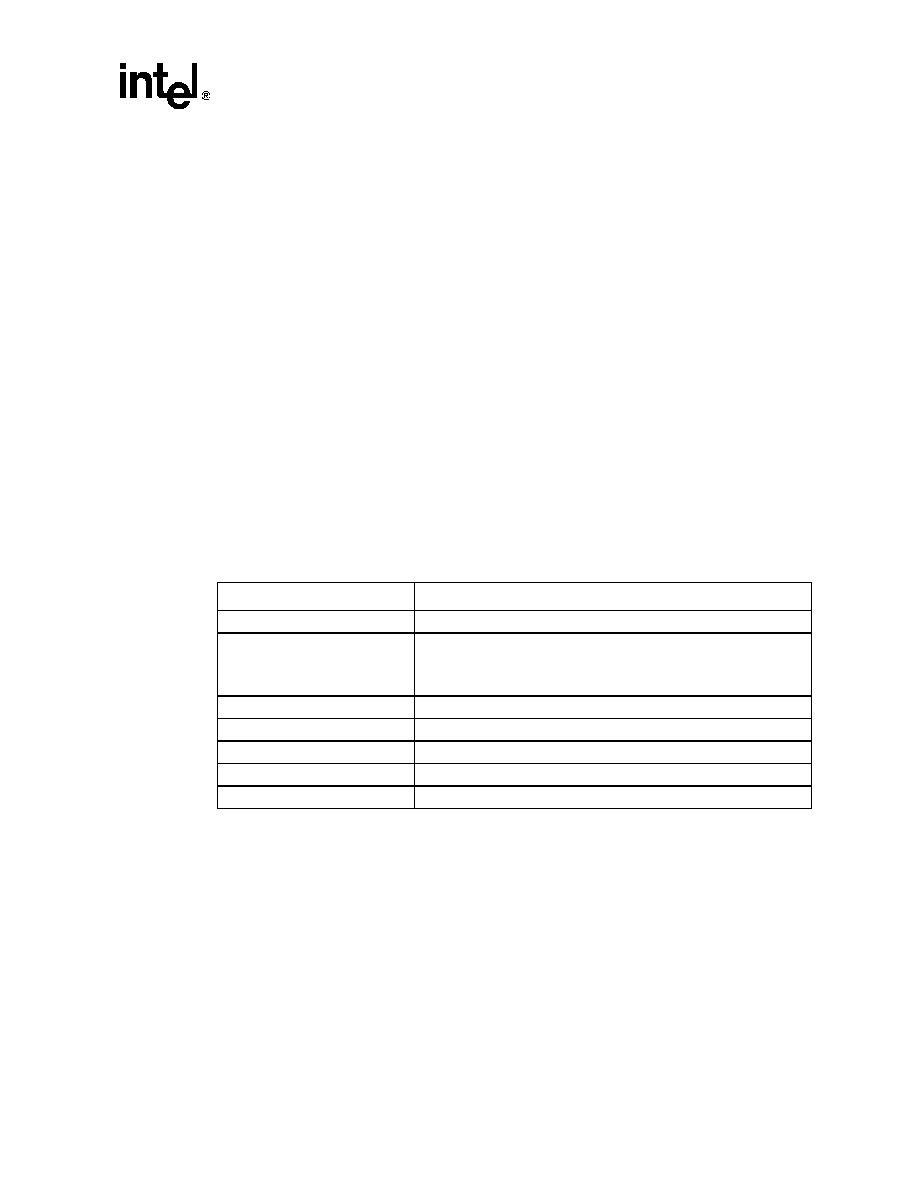

Revision History

Date

Revision

Description

January 2001

003

Corrected XOR Chain 2. Added note to CPUSLP# signal

description.

December 2001

002

Corrected pinouts and pin list.

December 2001

001

First release of this datasheet.

Intel

Æ

82801E C-ICH

Advance Information Datasheet

7

1.0

Introduction

The Intel

Æ

82801E Communications I/O Controller Hub (82801E C-ICH) is a highly integrated

multifunctional communications I/O controller hub that provides the interface to the PCI bus and

integrates many of the functions needed in today's communications applications. This document

provides a detailed description of the 82801E C-ICH thermal, electrical and mechanical

specifications, including signals, pinout, packaging, electrical characteristics, and testability.

Figure 1 illustrates the typical system configuration using the 82801E C-ICH. Figure 2 is a

simplified block diagram of the functional units of the 82801E C-ICH.

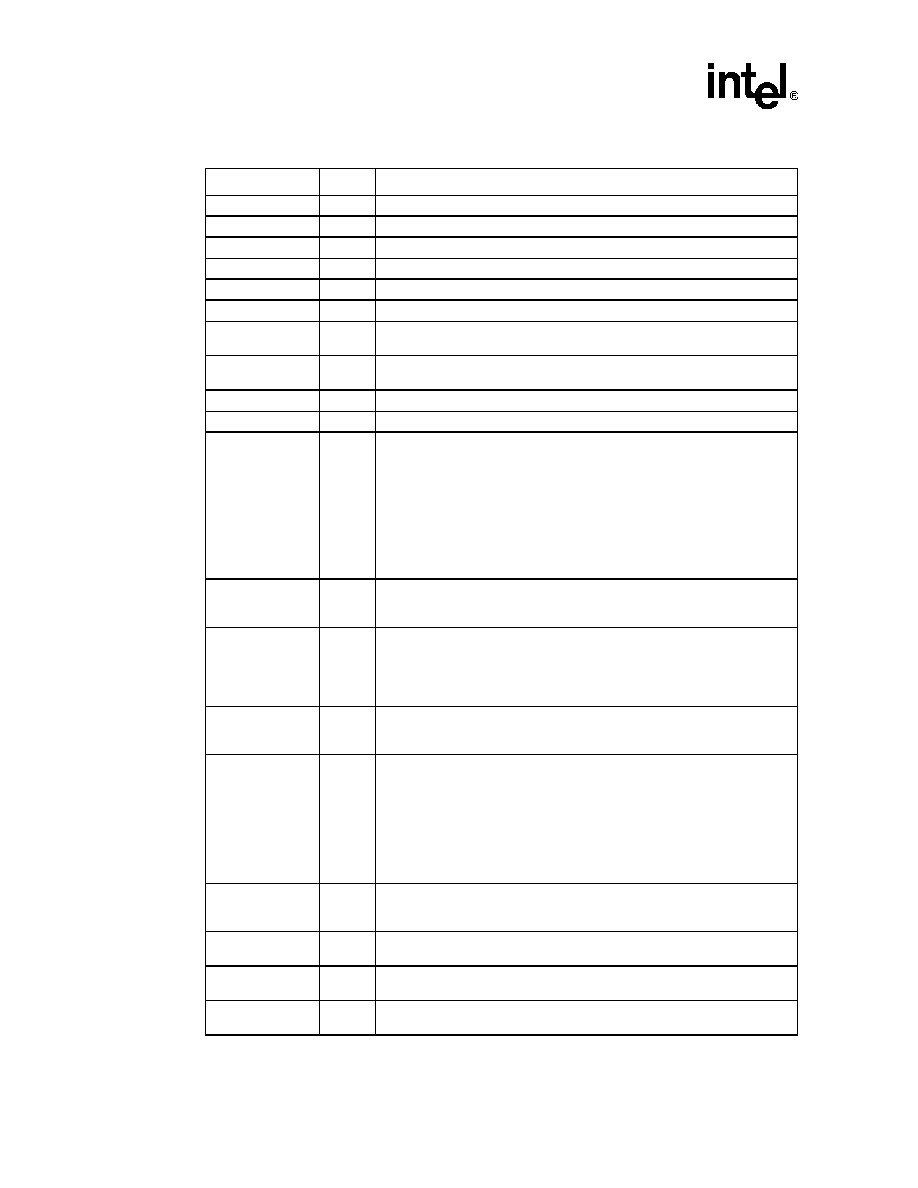

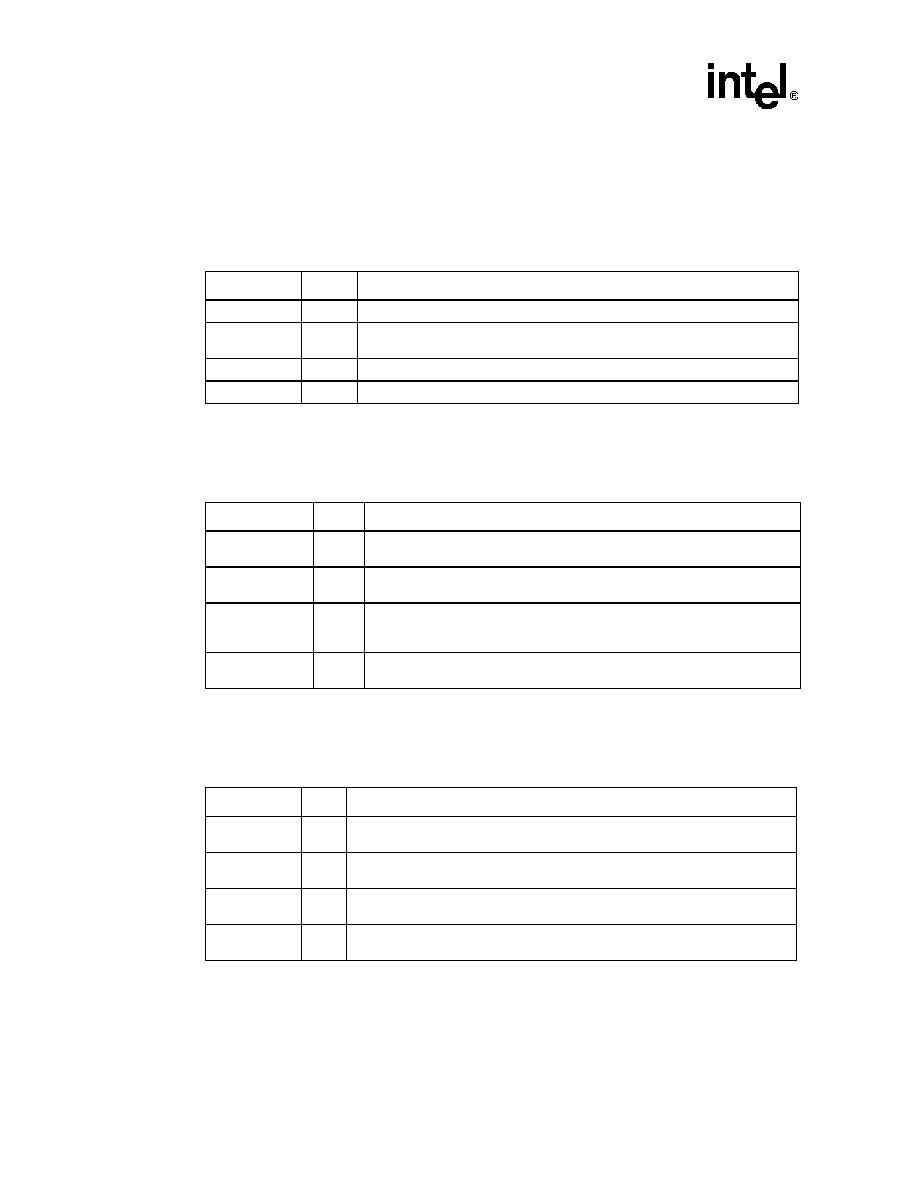

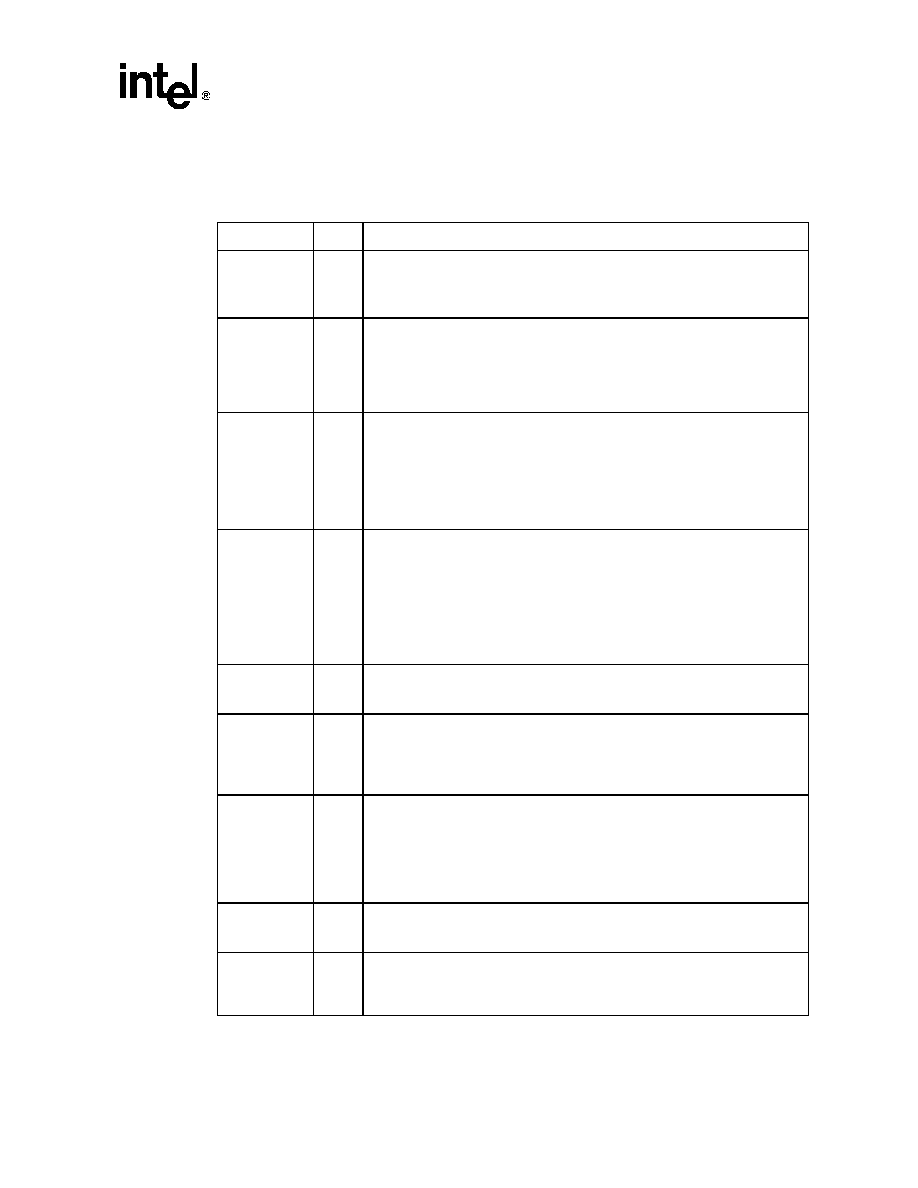

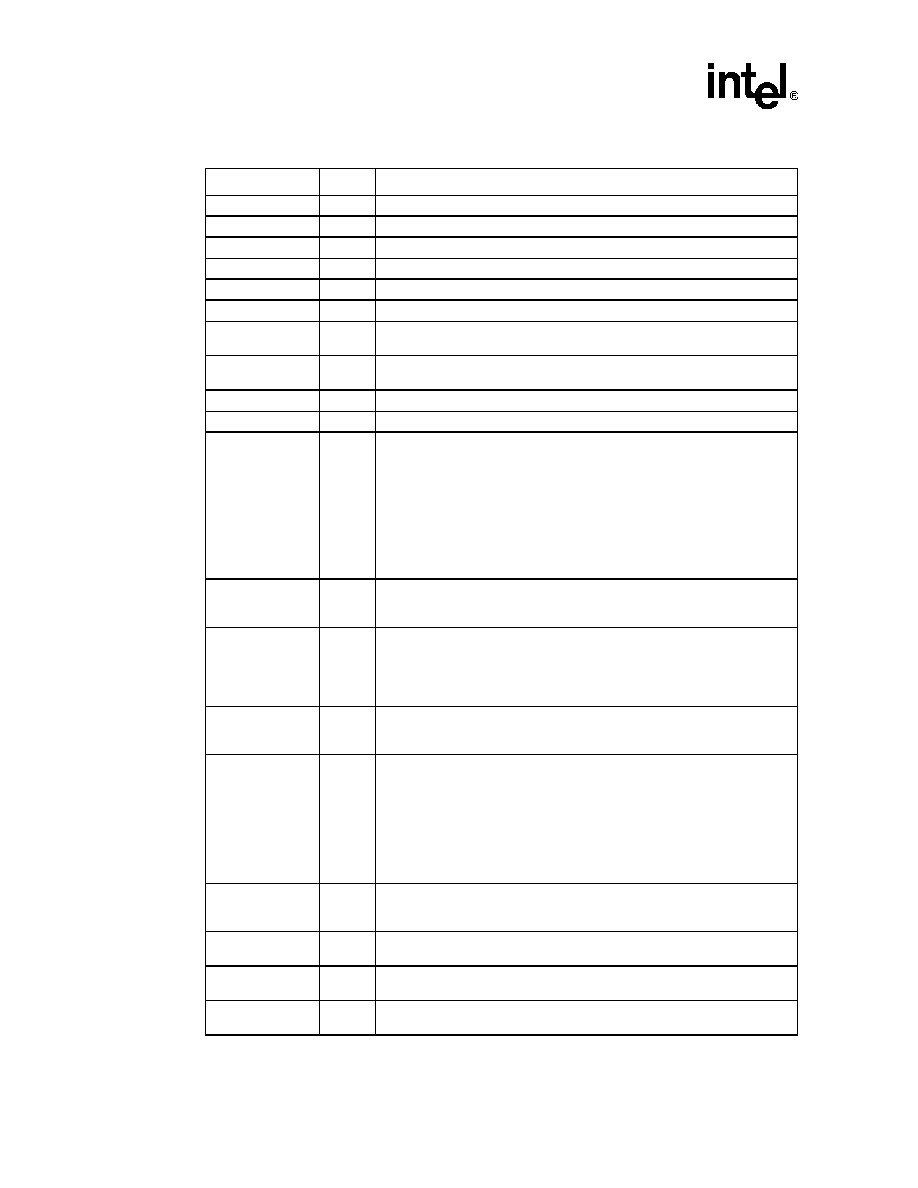

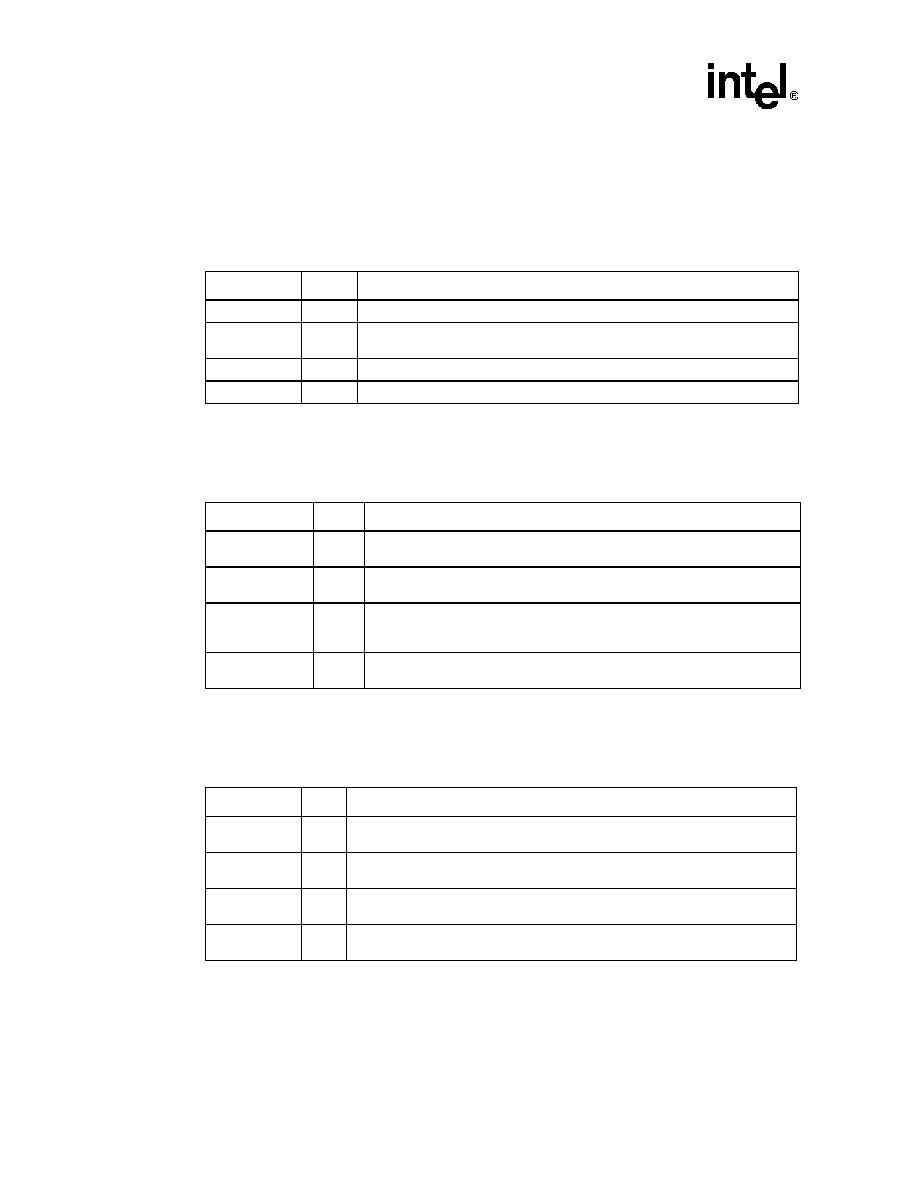

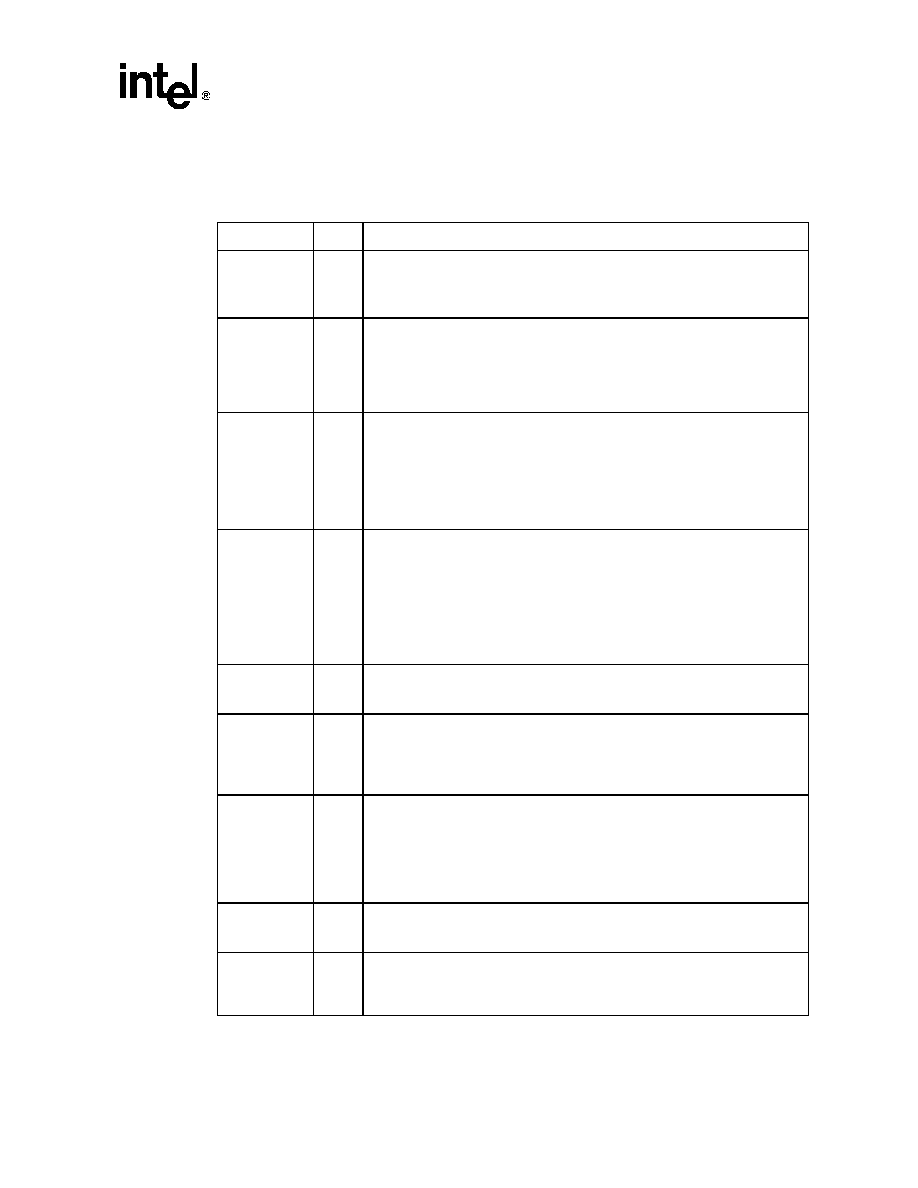

Figure 1. System Configuration

Main

Memory

Processor

sys_blk_CICH.vsd

PCI Bus

Up to Four

PCI Slots

Host

Controller

Communications

I/O Controller Hub

(C-ICH)

FWH

Two USB Ports

GPIO

LPC I/F

Graphics

Controller

SMBus

Device(s)

SMBus

ATA/100/66/33

4 IDE Drives

Hub Interface

Two LAN Controllers

Two UARTs

Intel

Æ

82801E C-ICH

8

Advance Information Datasheet

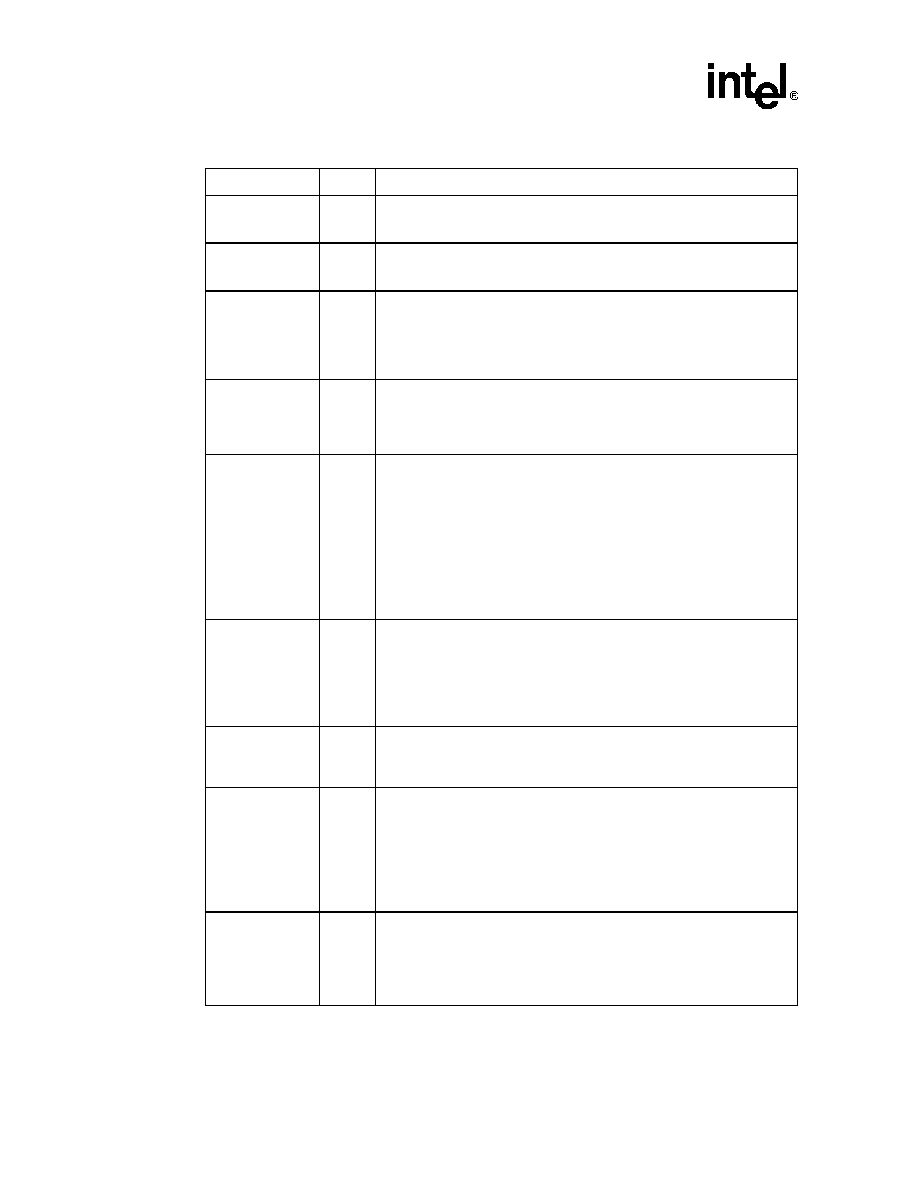

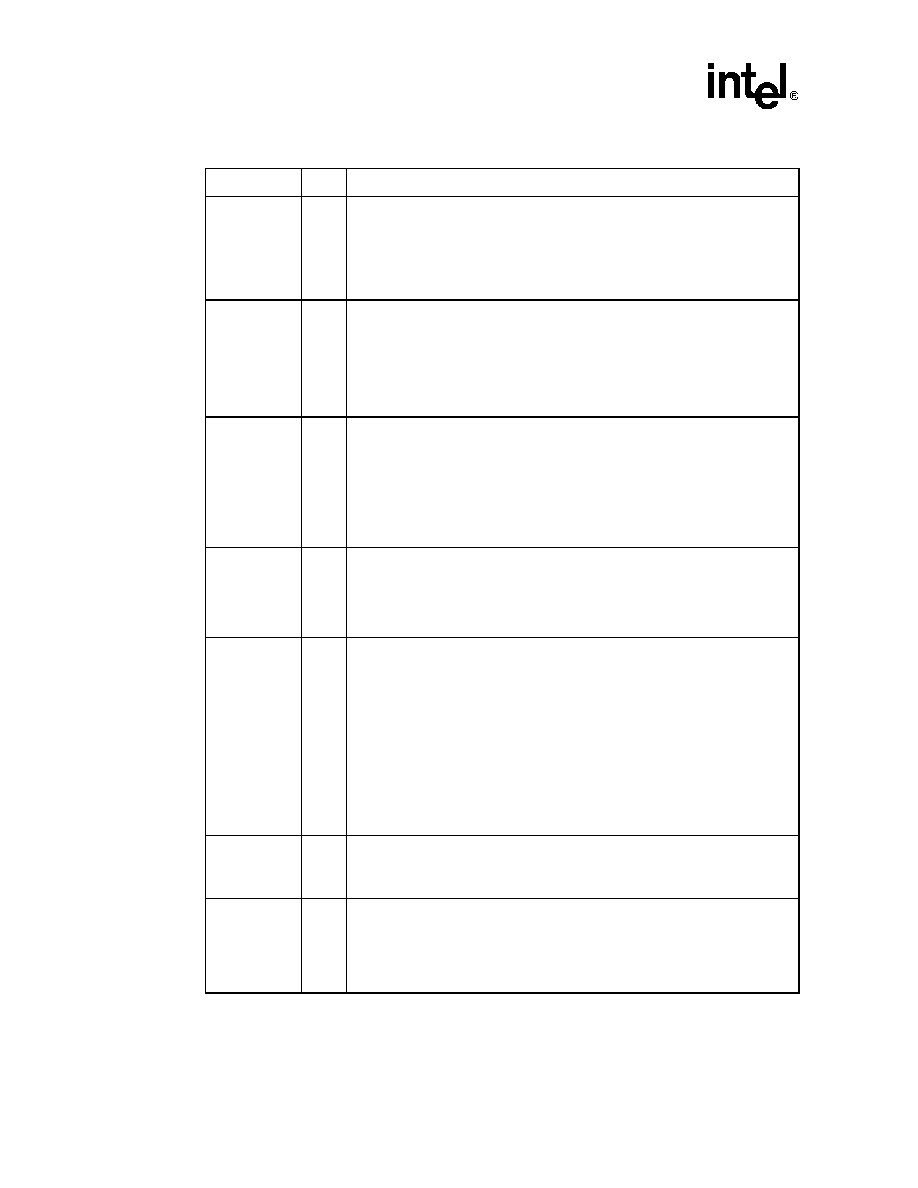

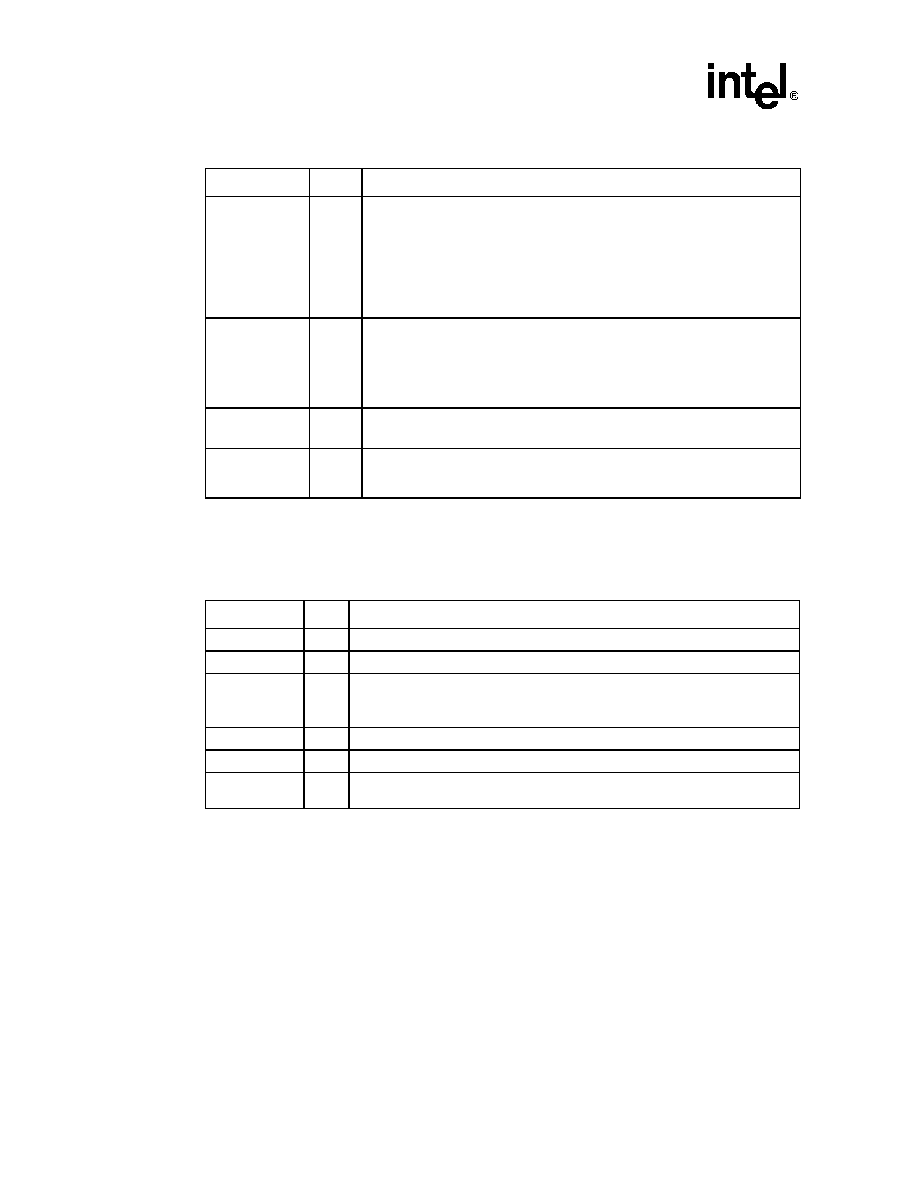

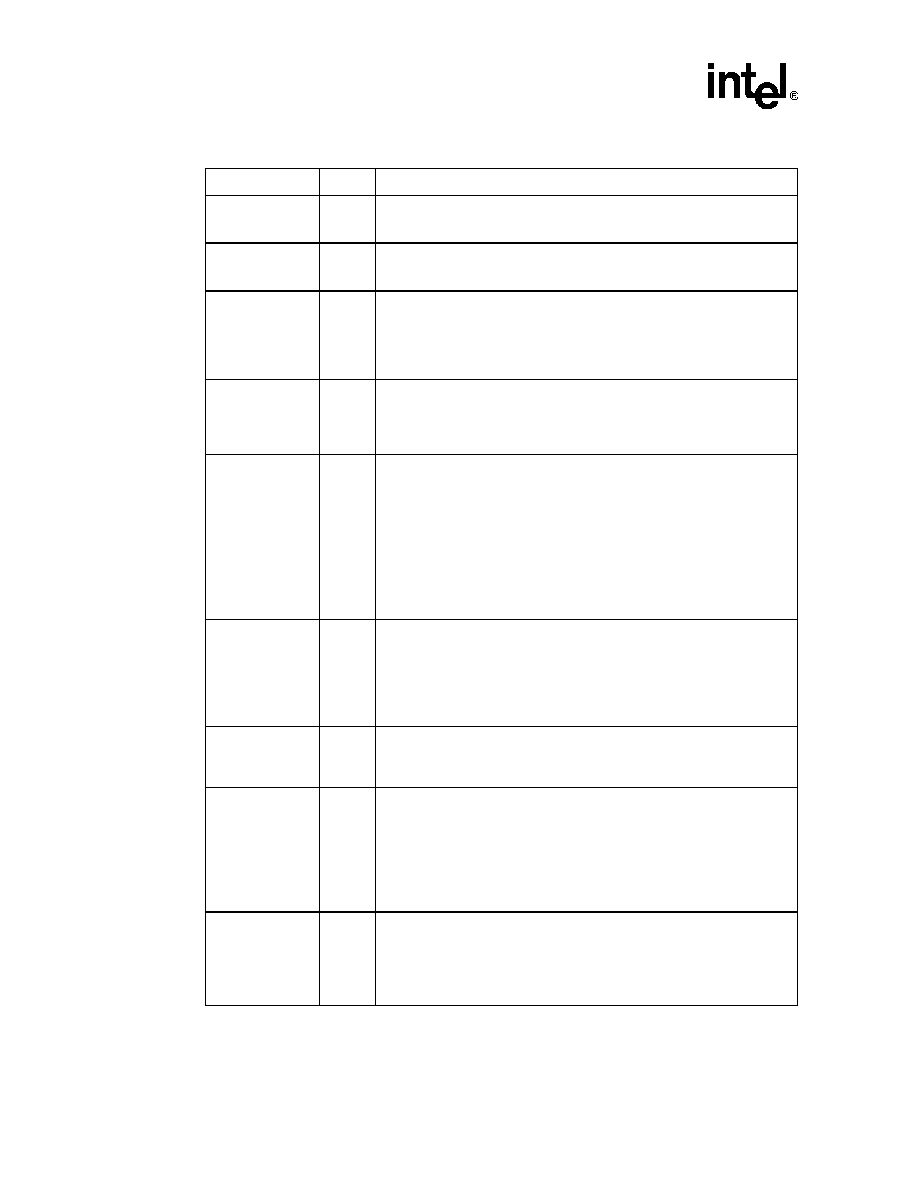

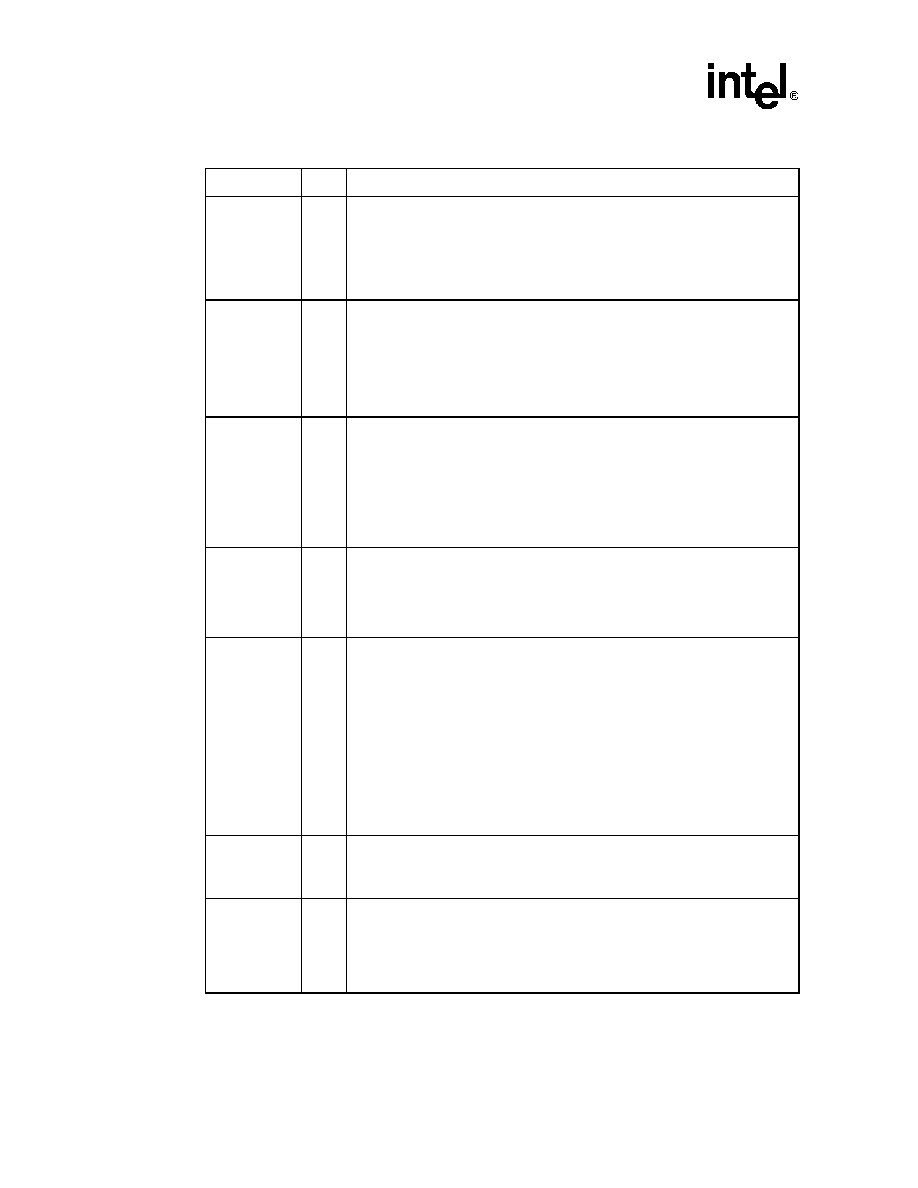

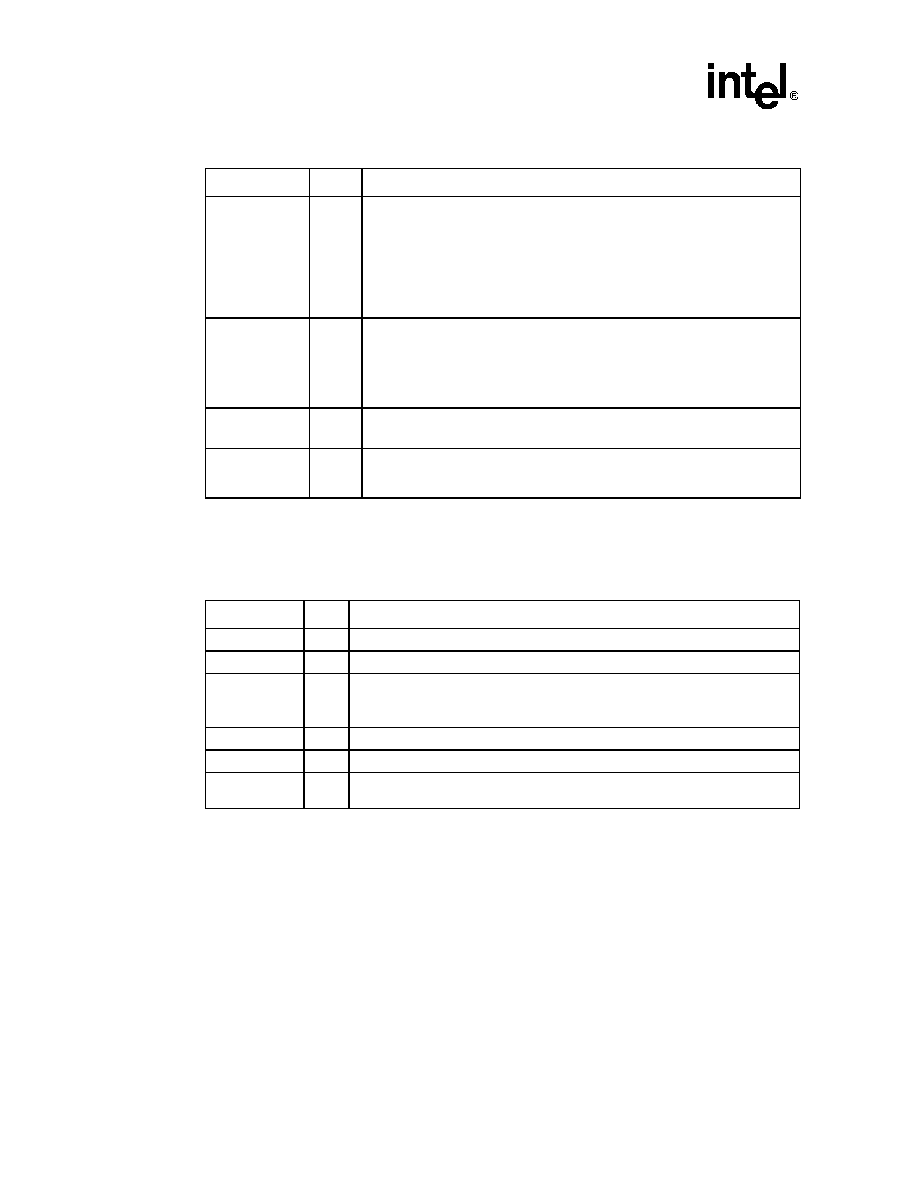

Figure 2. Intel

Æ

82801E C-ICH Simplified Block Diagram

INTRUDER#

SMLINK[1:0]

HL[11:0]

HL_STB

HL_STB#

HLCOMP

PWROK

RSMRST#

RSM_PWROK

VRMPWRGD

AD[31:0]

C/BE[3:0]#

DEVSEL#

FRAME#

IRDY#

TRDY#

STOP#

PAR

PERR#

REQ[3:0]#

REQ[5]#/REQ[B]#/GPIO[1]

REQ[A]#/GPIO[0]

GNT[3:0]#

GNT[5]#/GNT[B]#/GPIO[17]

GNT[A]#/GPIO[16]

PCICLK

PCIRST#

PLOCK#

SERR#

Interrupt

A20M#

CPUSLP#

FERR#

IGNNE#

INIT#

INTR

NMI

SMI#

STPCLK#

RCIN#

A20GATE

CPUPWRGD

Processor

Interface

PCI

Interface

USB

SERIRQ

PIRQ[A:F]#

PIRQ[G:H]/GPIO[5:4]

IRQ[15:14]

APICCLK

APICD[1:0]

USBP1P

USBP1N

USBP0P

USBP0N

OC[1:0]#

RTCX1

RTCX2

CLK14

CLK48

CLK66

RTC

Clocks

Miscellaneous

Signals

SPKR

RTCRST#

TP[3:0]

PDCS1#

SDCS1#

PDCS3#

SDCS3#

PDA[2:0]

SDA[2:0]

PDD[15:0]

SDD[15:0]

PDDREQ

SDDREQ

PDDACK#

SDDACK#

PDIOR#

SDIOR#

PDIOW#

SDIOW#

PIORDY

SIORDY

IDE

Interface

Hub

Interface

LPC

Interface

SMBus

Interface

Power

Signals

Firmware

Hub

System

Manage-

ment

General

Purpose

I/O

FWH[3:0]/LAD[3:0]

FWH[4]/LFRAME#

LAD[3:0]/FWH[3:0]

LFRAME#/FWH[4]

LDRQ[1:0]#

SMBDATA

SMBCLK

SMBALERT#/GPIO[11]

GPIO[13:11,8:4,1:0]

GPIO[23:16]

GPIO[28:27,25:24]

LAN1_CLK

LAN1_RXD[2:0]

LAN1_TXD[2:0]

LAN1_RSTSYNC

LAN1

EEPROM1

EE1_SHCLK

EE1_DIN

EE1_DOUT

EE1_CS

LAN0_CLK

LAN0_RXD[2:0]

LAN0_TXD[2:0]

LAN0_RSTSYNC

LAN0

Serial I/O

Unit

SIU_LCLK

SIU0_RXD

SIU0_TXD

SIU0_CTS#

SIU0_DSR#

SIU0_DCD#

SIU0_RI#

SIU0_DTR#

SIU0_RTS#

SIU_RESET#

SIU_LAD[3:0]

EE0_SHCLK

EE0_DIN

EE0_DOUT

EE0_CS

EEPROM0

UART_CLK

SIU1_RXD

SIU1_TXD

SIU1_CTS#

SIU1_DSR#

SIU1_DCD#

SIU1_RI#

SIU1_DTR#

SIU1_RTS#

SIU_LFRAME#

SIU_LDRQ#

SIU_SERIRQ

Blk_CICH.vsd

THRM#

RI#

SUSCLK

Intel

Æ

82801E C-ICH

Advance Information Datasheet

9

1.1

Overview

The 82801E C-ICH provides extensive I/O support. Functions and capabilities include:

∑

PCI Rev 2.2 compliant with support for 33 MHz PCI operations

∑

PCI slots support up to four Req/Gnt pairs

∑

Enhanced DMA Controller, Interrupt Controller, and Timer Functions

∑

Integrated IDE controller supports Ultra ATA100/66/33

∑

USB host interface with support for two USB ports; one host controller

∑

Two integrated LAN controllers

∑

System Management Bus (SMBus) with additional support for I

2

C devices

∑

Low Pin Count (LPC) interface

∑

Firmware Hub (FWH) interface support

∑

Serial I/O unit containing two UARTs

The 82801E C-ICH incorporates a variety of PCI functions that are divided into two logical

devices (30 and 31) on PCI Bus 0 and one device on Bus 1. Device 30 is the Hub Interface-to-PCI

bridge. Device 31 contains all the other PCI functions, except the LAN controller as shown in

Table 1. The LAN controllers are located on Bus 1.

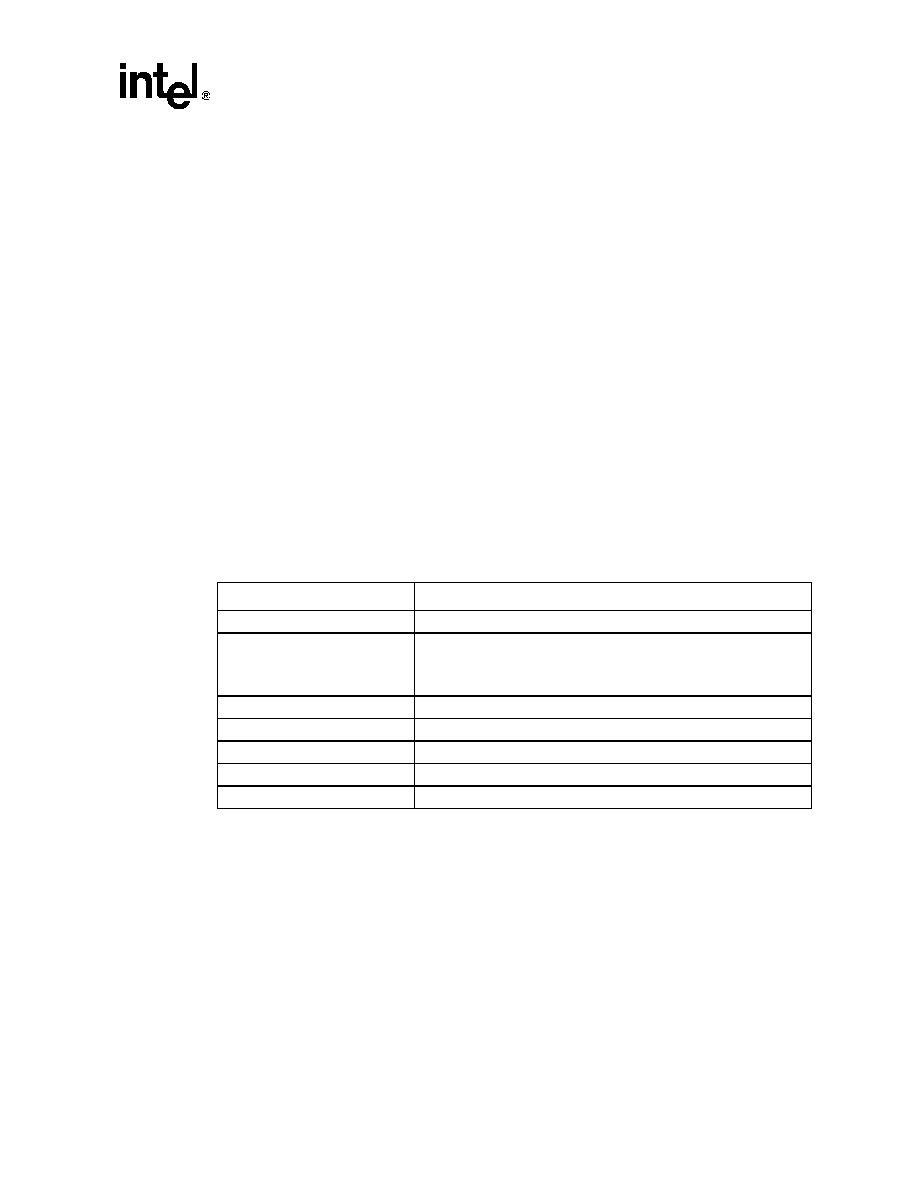

Table 1. PCI Devices and Functions

Bus:Device:Function

Function Description

Bus 0:Device 30:Function 0

Hub Interface to PCI Bridge

Bus 0:Device 31:Function 0

PCI to LPC Bridge

(includes: DMA, Timers, compatible interrupt controller, APIC, RTC, SIU,

processor interface control, power management control, system

management control, and GPIO control)

Bus 0:Device 31:Function 1

IDE Controller

Bus 0:Device 31:Function 2

USB Controller

Bus 0:Device 31:Function 3

SMBus Controller

Bus 1:Device 8:Function 0

LAN0 Controller

Bus 1:Device 9:Function 0

LAN1 Controller

Intel

Æ

82801E C-ICH

10

Advance Information Datasheet

1.2

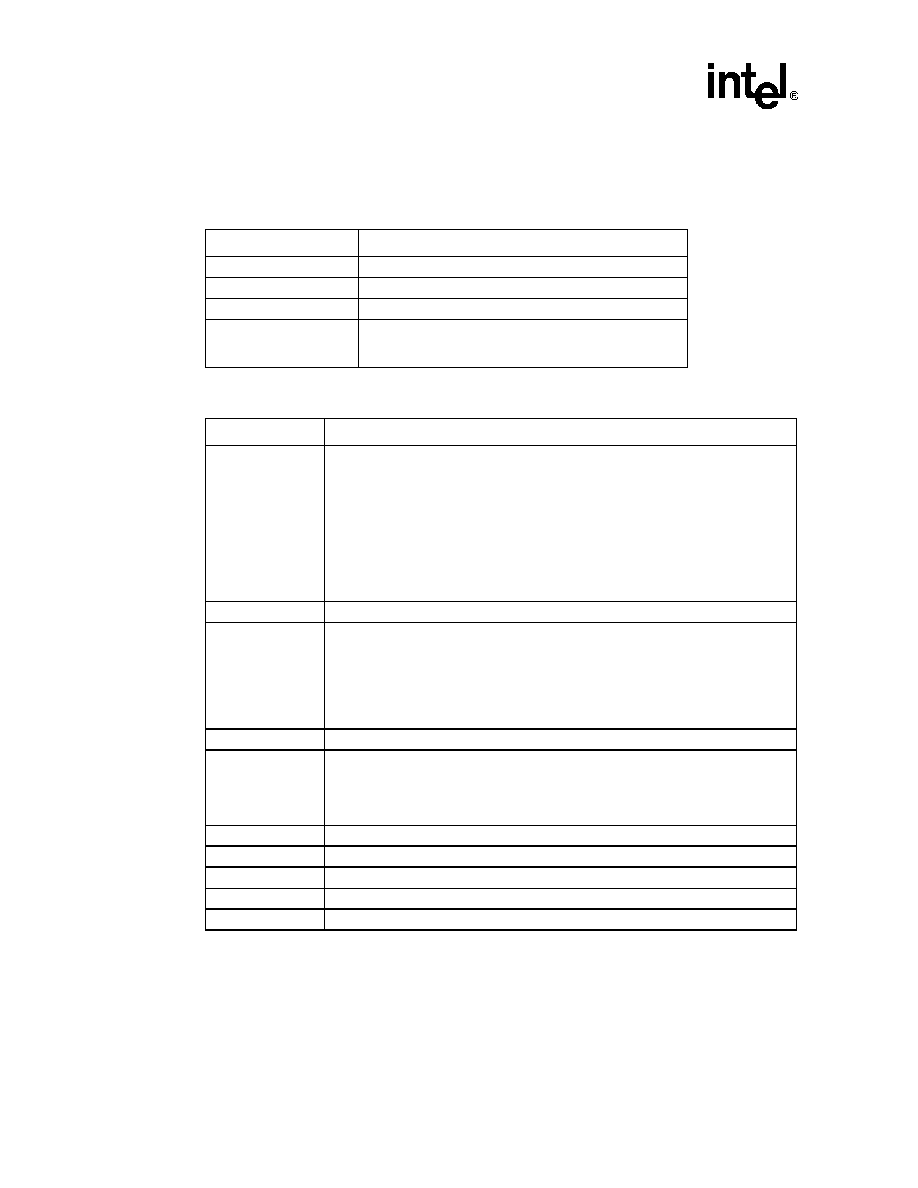

About this Document

This document is intended for original equipment manufacturers (OEMs) and BIOS vendors

creating 82801E C-ICH-based products. This document contains electrical thermal and mechanical

specifications for the 82801E C-ICH, including complete signal descriptions, pin maps, and

testability information. For additional information, refer to the documents listed in Table 2.

This document assumes a working knowledge of the vocabulary and principles of USB, IDE,

SMBus, PCI, LAN, LPC, and serial I/O. Details of these features are described in the Intel

Æ

82801E Communications I/O Controller Hub (C-ICH) Developer's Manual (order number 273599)

and in the industry specifications listed in Table 3.

Table

2. Related

Documents

Document

Order Number

Intel

Æ

82801E Communications I/O Controller Hub (C-ICH) Developer's Manual

273599

Intel

Æ

82801E Communications I/O Controller Hub (C-ICH) Specification Update

273645

Intel

Æ

82801E Communications I/O Controller Hub (C-ICH) Platform Design Guide

273671

Intel

Æ

810E Chipset: 82810E Graphics and Memory Controller Hub (GMCH)

Datasheet

290676

82802AB/82802AC Firmware Hub (FWH)

Datasheet

290658

Table 3. Industry Specifications

Specification

Location

LPC

http://developer.intel.com/design/chipsets/industry/lpc.htm

WfM

http://developer.intel.com/ial/WfM/usesite.htm

SMBus

http://www.sbs-forum.org/specs/

PCI

http://pcisig.com/

USB

http://www.usb.org

Intel

Æ

82801E C-ICH

Advance Information Datasheet

11

2.0

Package Information

2.1

Ball Location

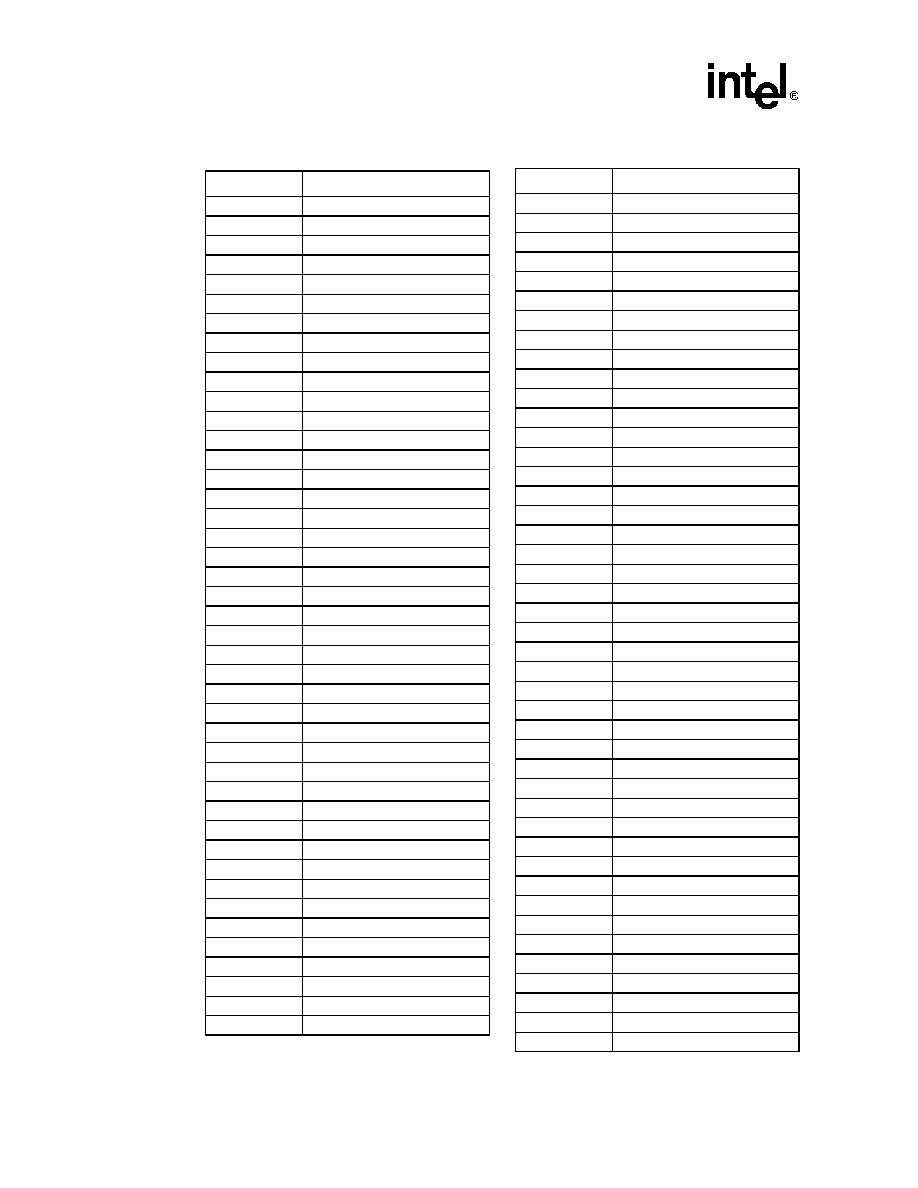

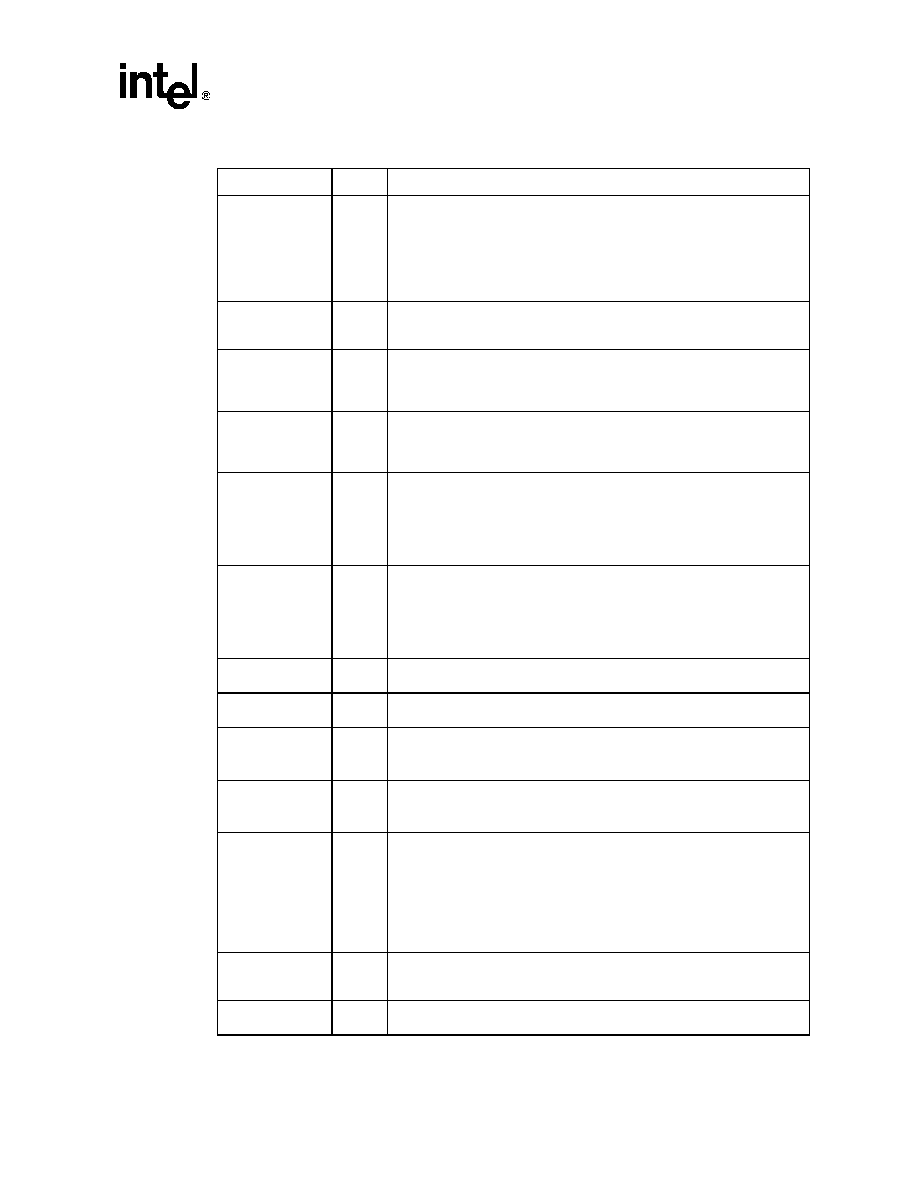

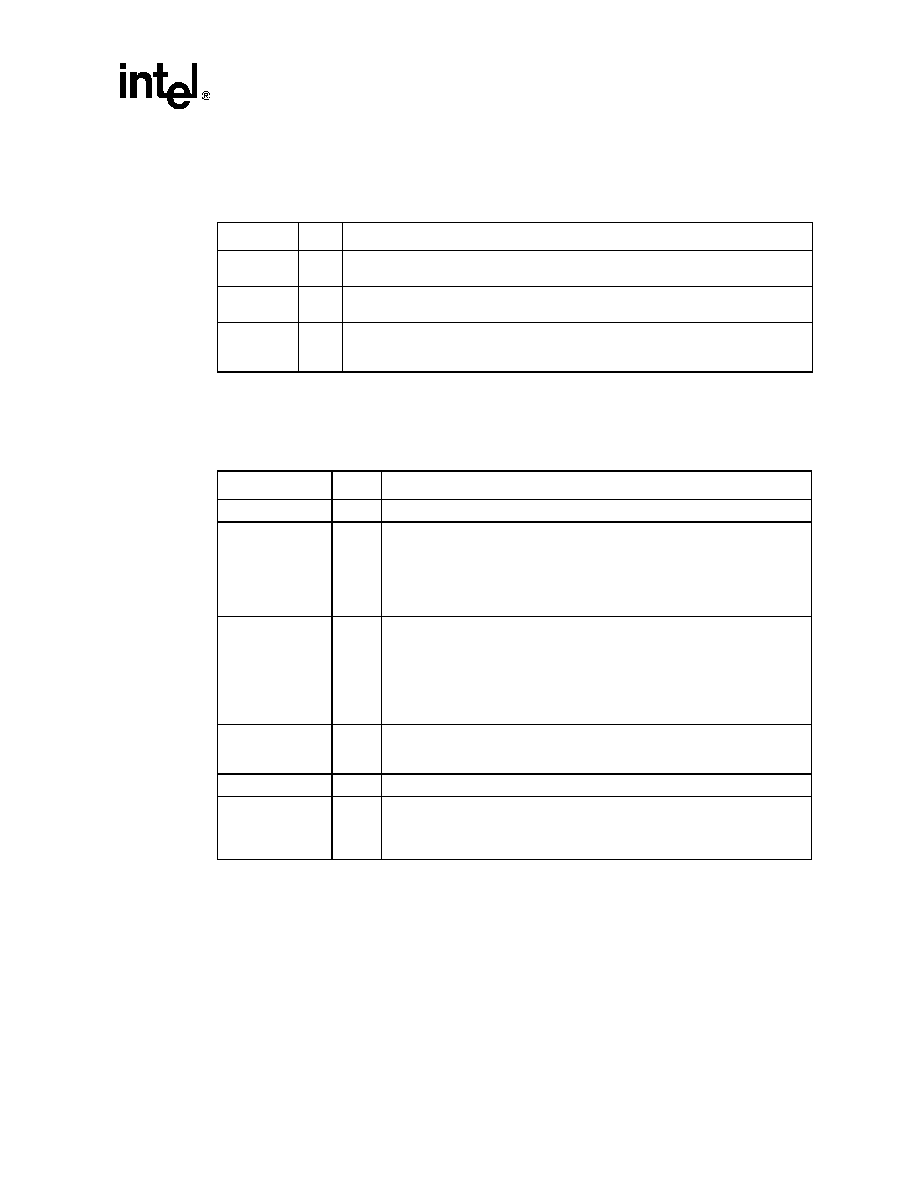

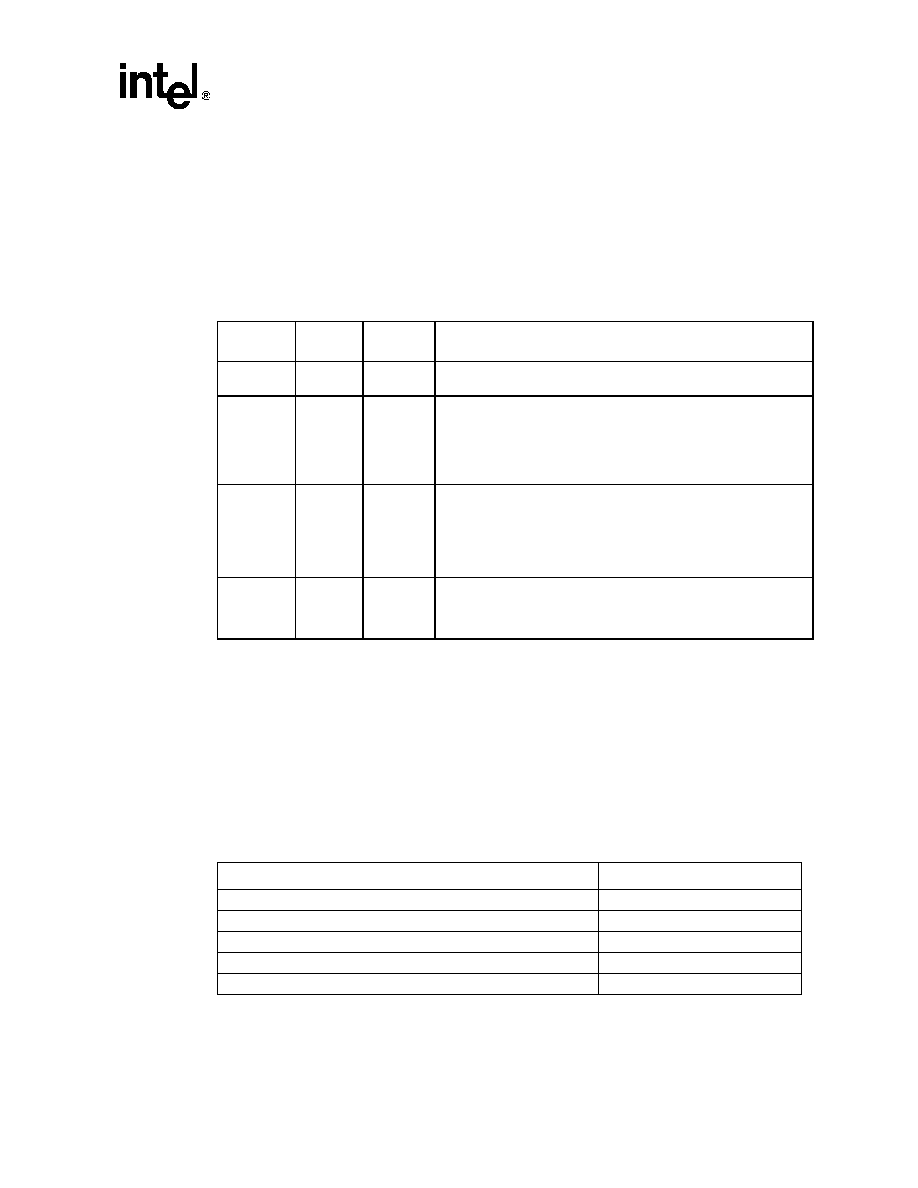

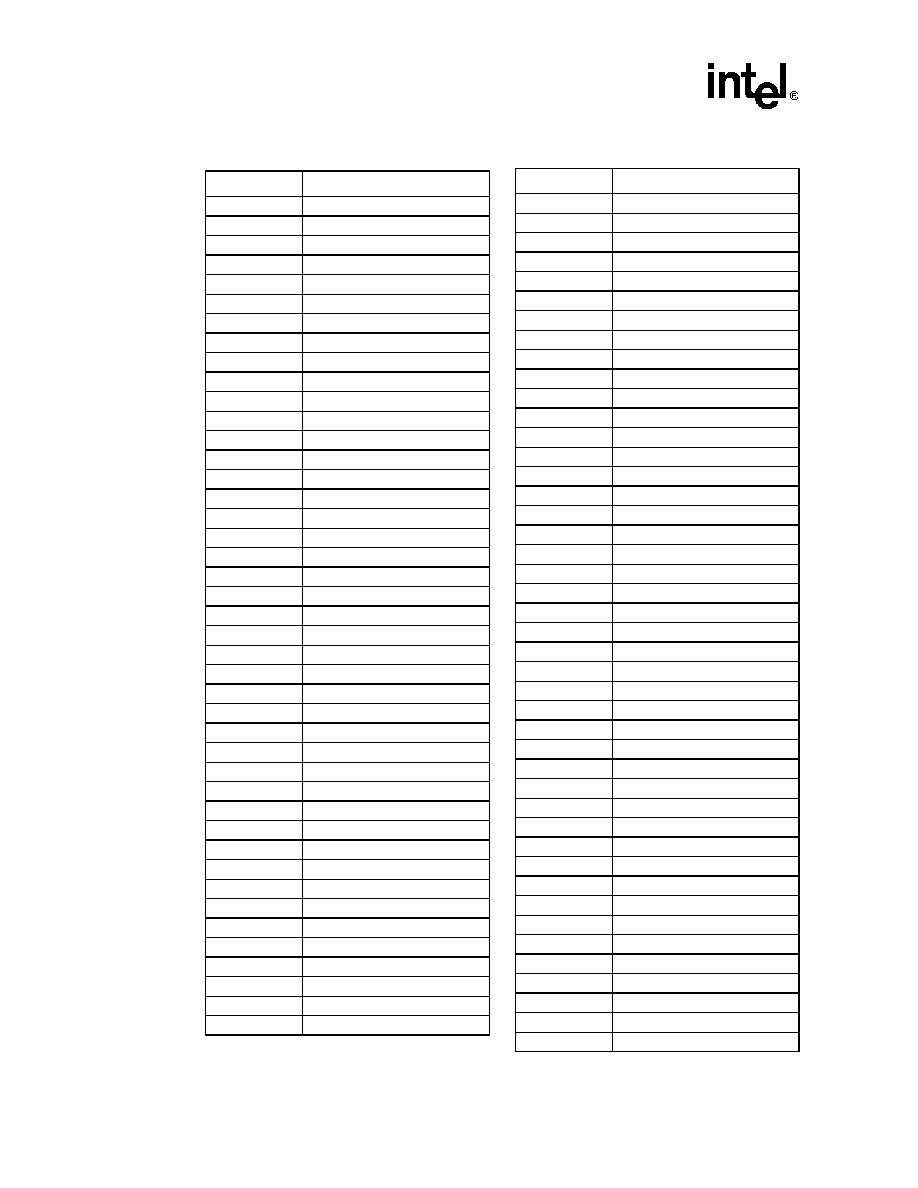

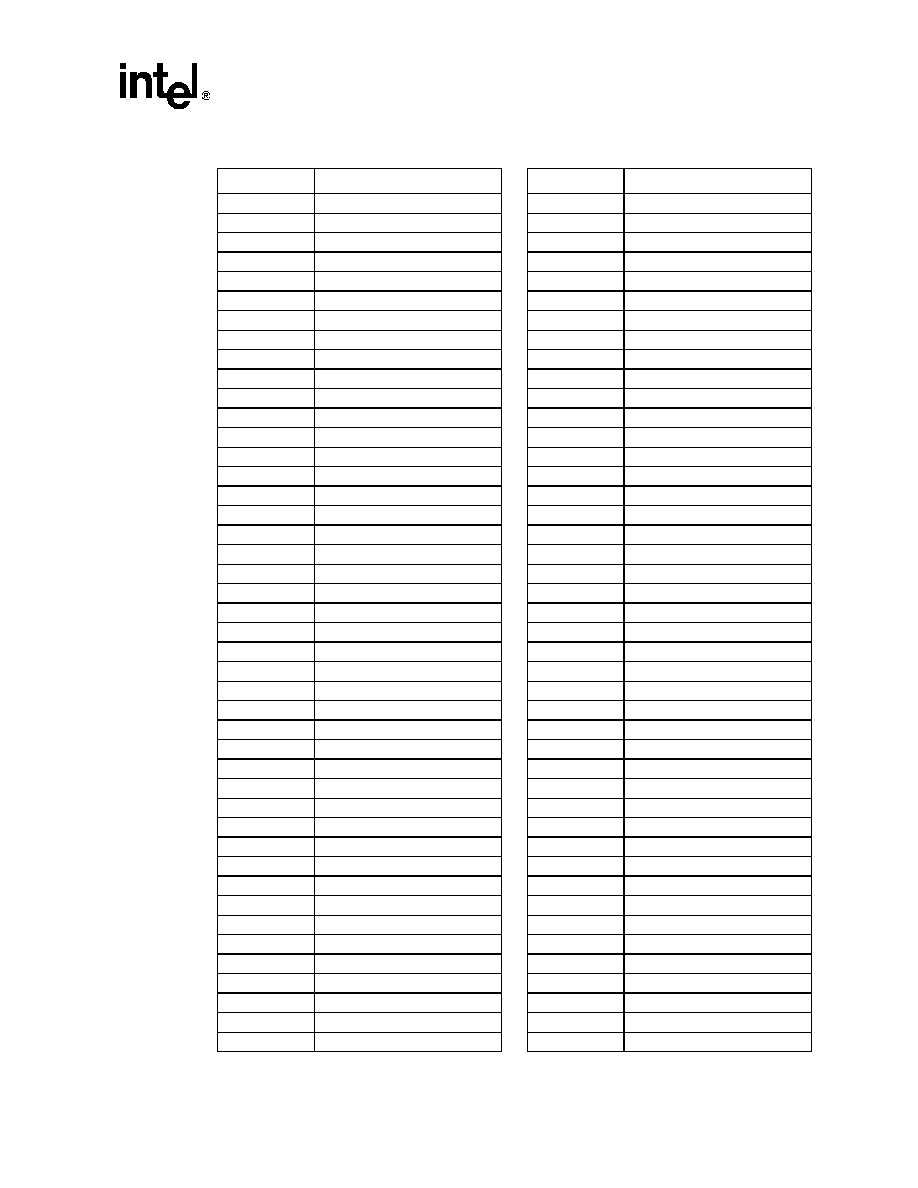

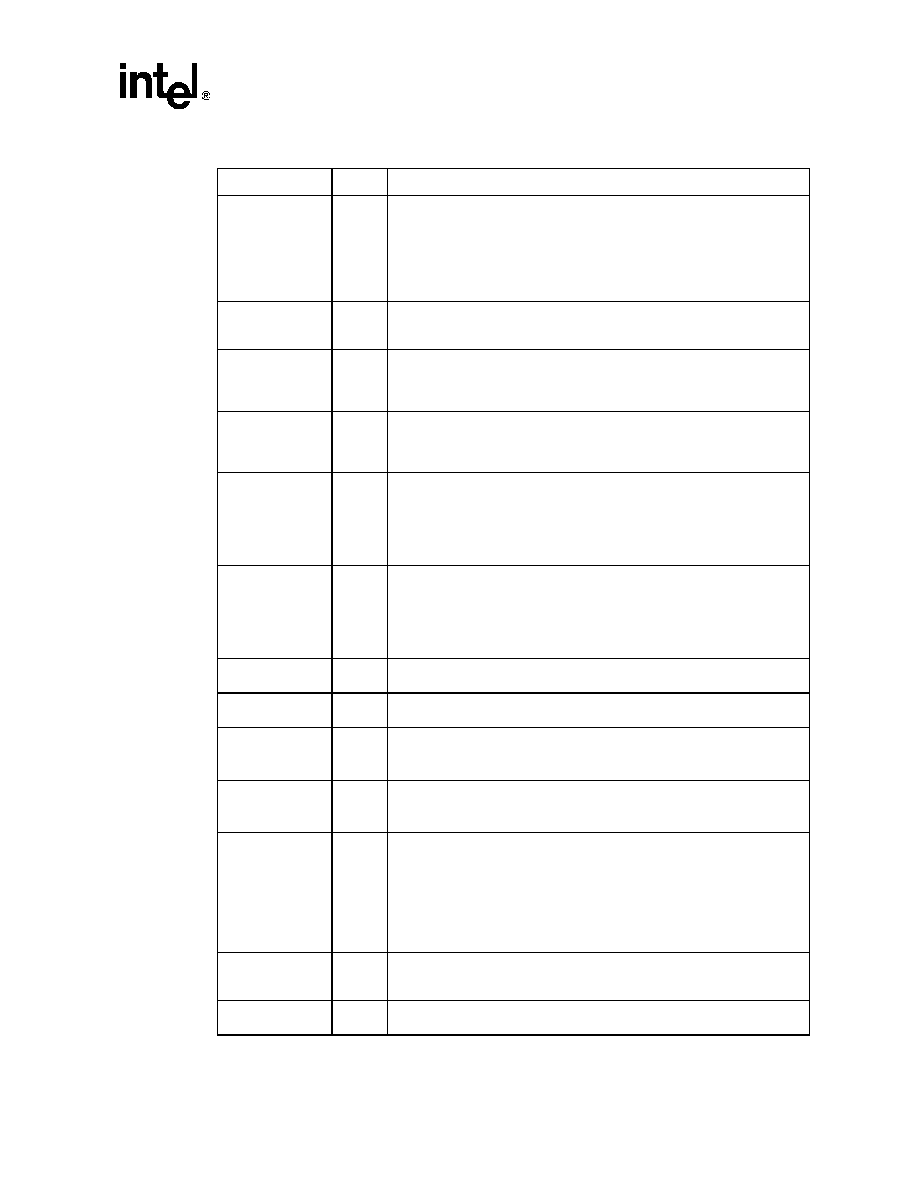

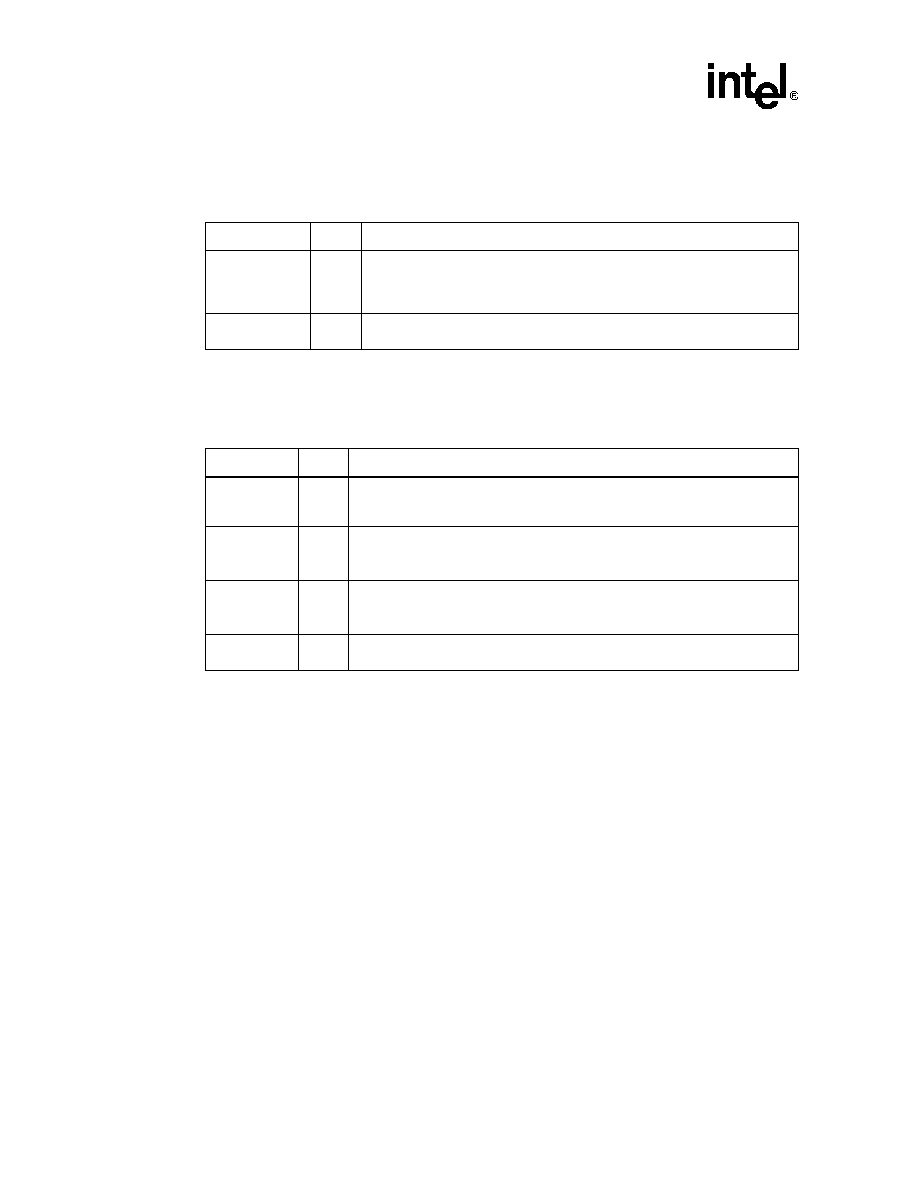

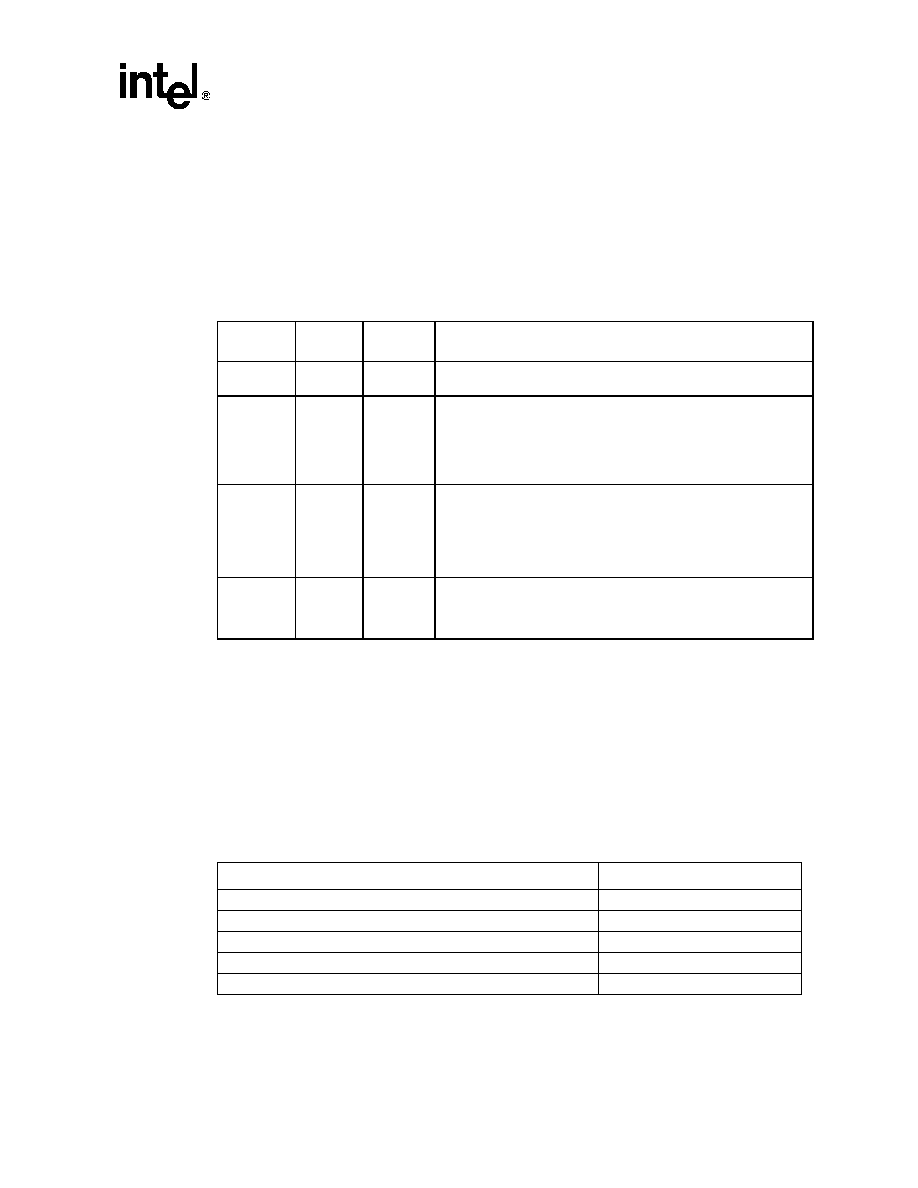

This section describes the 82801E C-ICH ball assignment. Figure 3 provides a 421-ball location

diagram. The diagram also indicates general signal groupings. Table 4 lists the 82801E C-ICH

signal assignments by ball number. Table 5 lists the assignments alphabetically by signal name.

Figure 3. Ball Diagram (Top View)

A8684-02

IDE

SMLINK

POWER

MANAGEMENT

SIU

LPC

PCI

LAN

PCI

SMBUS

USB

HUB INTERFACE

PROCESSOR

IDE

A

C

B

E

D

G

F

J

H

L

K

N

M

R

P

U

T

W

V

AA

Y

AC

AB

A

C

B

E

D

G

F

J

H

L

K

N

M

R

P

U

T

W

V

AA

Y

AC

AB

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

PIRQ[A]# VSS

NC[4]

GNT[3]#

VSS

AD[28]

VSS

SIU0_

RI#

UART_

CLK

VSS

SIU_

LAD[1]

LAN1_

TXD[1]

VSS

SIU1_

DSR#

SIU1_

RTS#

SIU_

SERIRQ

TP[0]

VSS

THRM#

GPIO[21]

VSS

GNT[0]#

PIRQ[H]#/

GPIO[5]

REQ[0]# NC[5]

AD[26]

AD[22]

FRAME# AD[16]

LAN1_

RXD[2]

LAN1_

CLK

SIU0_

DTR#

VCC3_3

SIU_

LFRAME#

Vcc1_8

SIU0_

DCD#

SIU1_

RXD

SIU1_

DTR#

Vcc1_8

LAD[0]/

FWH[0]

LAD[3]/

FWH[3]

LDRQ[0]#

GNT[A]#/

GPIO[16]

GNT[B]#/

GNT[5]#/

GPIO[17]

VCC1_8

PIRQ[D]#

AD[30]

VSS

VSS

PAR

AD[13]

AD[20]

EE0_

SHCLK

LAN1_

RXD[0]

VSS

SIU1_

TXD

SIU_

LDRQ#

LAN1_

RSTSYNC

LAN1_

TXD[0]

Vcc3_3

SIU1_

DCD#

SIU_

LAD[2]

VSS LFRAME#/

FWH[4]

LDRQ[1]#

REQ[B]#/

REQ[5]#/

GPIO[1]

REQ[A]#/

GPIO[0]

PIRQ[E]#

PIRQ[C]#

AD[18] AD[24]

STOP#

AD[15]

VSS

AD[4]

LAN0_

RSTSYNC

EE1_

DOUT

SIU0_

TXD

SIU0_

CTS#

SIU1_

RI#

VSS

LAN1_

TXD[2]

SIU0_

DSR#

SIU1_

CTS#

SIU_

LAD[0]

LAD[1]/

FWH[1]

SIU_

RESET#

V5REF

GNT[1]#

VSS

PIRQ[B]#

REQ[1]#

VSS

Vcc3_3

TRDY#

AD[9]

AD[0]

Vcc1_8

LAN0_

TXD[2]

EE0_

DIN

VSS

SIU0_

RXD

VSS

LAN0_

RXD[2]

EE1_

SHCLK

Vcc3_3

SIU0_

RTS#

SIU_

LAD[3]

LAD[2]/

FWH[2]

SIU_

LCLK

PIRQ[G]#/

GPIO[4]

PIRQ[F]#

REQ[2]#

GNT[2]#

VSS

V5REF Vcc3_3

NC[6]

Vcc3_3

NC[10]

USBP1N

IGNNE#

V_CPU_IO

SDDACK#

Vcc3_3

Vcc3_3

CPUPWRGD

SIORDY

Vcc3_3

Vcc3_3

Vcc3_3

Vcc3_3

Vcc3_3

Vcc3_3

Vcc3_3

VSS

VSS

OC[1]#

NC[7]

USBP1P

NC[9]

RCIN#

VRMPWRGD

SDIOW#

SDD[14]

PDA[1]

V_CPU_IO

SDA[2]

SDIOR#

SDD[5]

PDD[1]

CLK14

PDD[5]

PDCS1#

Vcc3_3

PWROK

VccRTC

NC[1]

SMLINK[0] VSS

RESERVED2

V5REF

VSS

NC[8]

A20GATE

SDCS3#

SDD[0]

SDD[10]

SDD[6]

GPIO[18]

SDD[15]

SDD[12]

PDA[0]

PDD[12]

PDD[6]

PDD[10]

PDIOW#

APICD[1]

NC[2]

RSMRST#

RTCX1

TP[1]

RTCRST#

SMLINK[1]

VSS

OC0#

VSS

GPIO[19]

SDA[1]

SDD[3]

SDD[8]

PDDACK#

VSS

VSS

SDD[4]

VSS

PDD[3]

PDD[7]

VSS

PDD[0]

SERIRQ

FERR#

VccRTC

RTCX2

INTRUDER#

VBIAS

GPIO[24]

Vcc3_3

V5REF

TP[3]

SDA[0]

Vcc3_3

SDD[11]

PDIOR#

PDD[15]

IRQ[15]

SDD[13]

SDD[9]

IRQ[14]

PDD[13]

PDD[8]

PDD[4]

PDD[14]

SPKR

APICD[0]

CLK48

VSS

VSS

VSS

VSS

VSS

VSS

TP[2]

VSS

SDD[1]

PDCS3#

PIORDY

PDDREQ

SDDREQ

SDD[2]

SDD[7]

PDA[2]

VSS

PDD[9]

PDD[11]

PDD[2]

V5REF

APICCLK

VSS

NC[3]

Vcc3_3

C/BE[2]#

VSS

VSS

Vcc1_8

PLOCK# Vcc3_3

Vcc3_3

IRDY#

AD[17]

AD[19]

AD[23]

VSS

VSS

HLCOMP

HL[11]

HUBREF

Vcc1_8

Vcc1_8

Vcc1_8

Vcc1_8

VSS

VSS

VSS

Vcc1_8

AD[21]

C/BE[3]#

VSS

AD[27]

AD[25]

HL[2]

HL[1]

HL[0]

VSS

VSS

Vcc1_8

VSS

VSS

VSS

VSS

Vcc1_8

GPIO[28]

GPIO[27]

VSS

GPIO[7]

HL_STB#

HL[10]

HL[4]

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

RESERVED1

GPIO[13]

GPIO[8]

GPIO[12]

VSS

VSS

HL[7]

HL[8]

HL[5]

Vcc1_8

Vcc1_8

VSS

Vcc1_8

Vcc3_3

Vcc1_8

RI#

SMBDATA

Vcc3_3

PCIRST#

GPIO[25]

HL[6]

VSS

CPUSLP#

VSS

VSS

Vcc3_3

Vcc1_8

USBP0N

NC[12]

RSM_PWROK

VSS

SMBCLK

A20M#

SMI#

GPIO[20]

STPCLK#

GPIO[23]

Vcc3_3

Vcc3_3

VSS

USBP0P

SUSCLK

SMBALERT#/

GPIO[11]

NC[11]

INTR

INIT#

SDCS1#

NMI

GPIO[22]

VSS

PCICLK

REQ[3]#

GPIO[6]

AD[29]

AD[31]

VSS

VSS

HL[9]

HL_STB

HL[3]

Vcc1_8

VSS

VSS

Vcc1_8

AD[11] Vcc3_3

C/BE[0]#

AD[6]

AD[7]

AD[10]

Vcc1_8

Vcc1_8

EE1_CS

Vcc3_3

Vcc3_3

LAN0_CLK

EE0_CS

Vcc3_3

AD[2]

Vcc3_3

AD[3]

VSS

SERR#

AD[12]

LAN0_

RXD[1]

LAN0_

TXD[1]

EE1_

DIN

VSS

EE0_

DOUT

Vcc3_3

AD[5]

Vcc3_3

AD[1]

AD[8]

C/BE[1]# AD[14]

VSS

LAN0_

TXD[0]

LAN1_

RXD[1]

Vcc1_8

LAN0_

RXD[0]

Vcc3_3

VSS

PERR#

DEVSEL#

VSS

CLK66

(HLCLK)

VSS

VSS

VSS

Vcc3_3

Vcc1_8

Vcc1_8

Vcc1_8

Vcc1_8

Vcc3_3

Intel

Æ

82801E C-ICH

12

Advance Information Datasheet

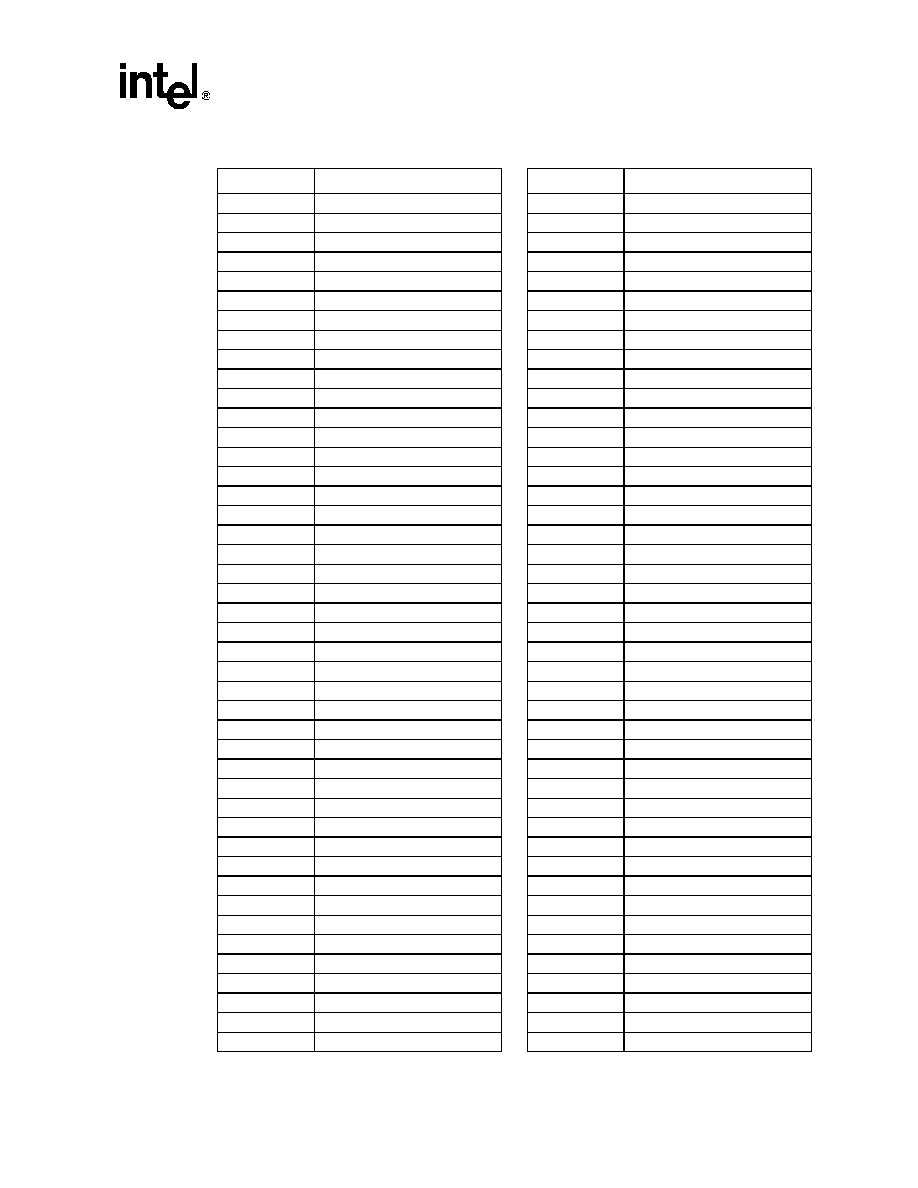

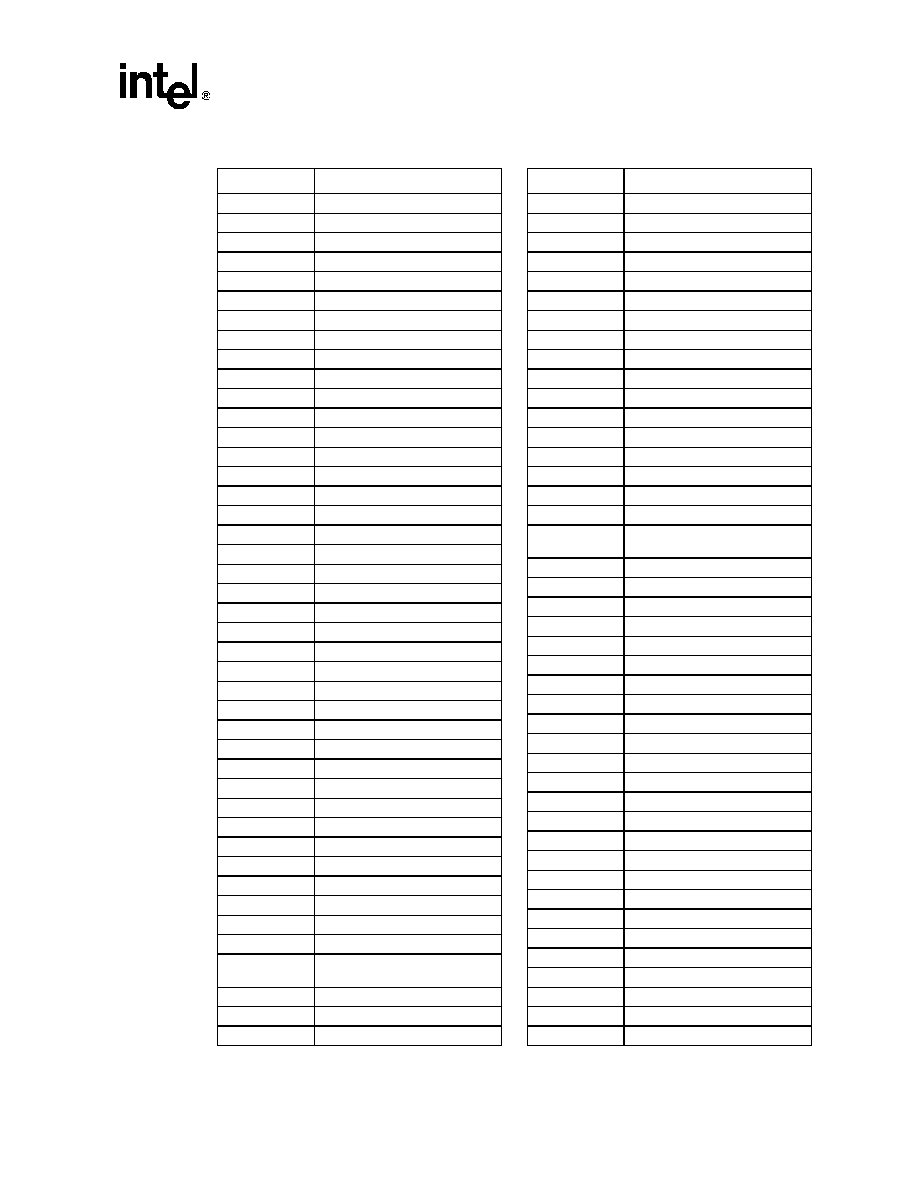

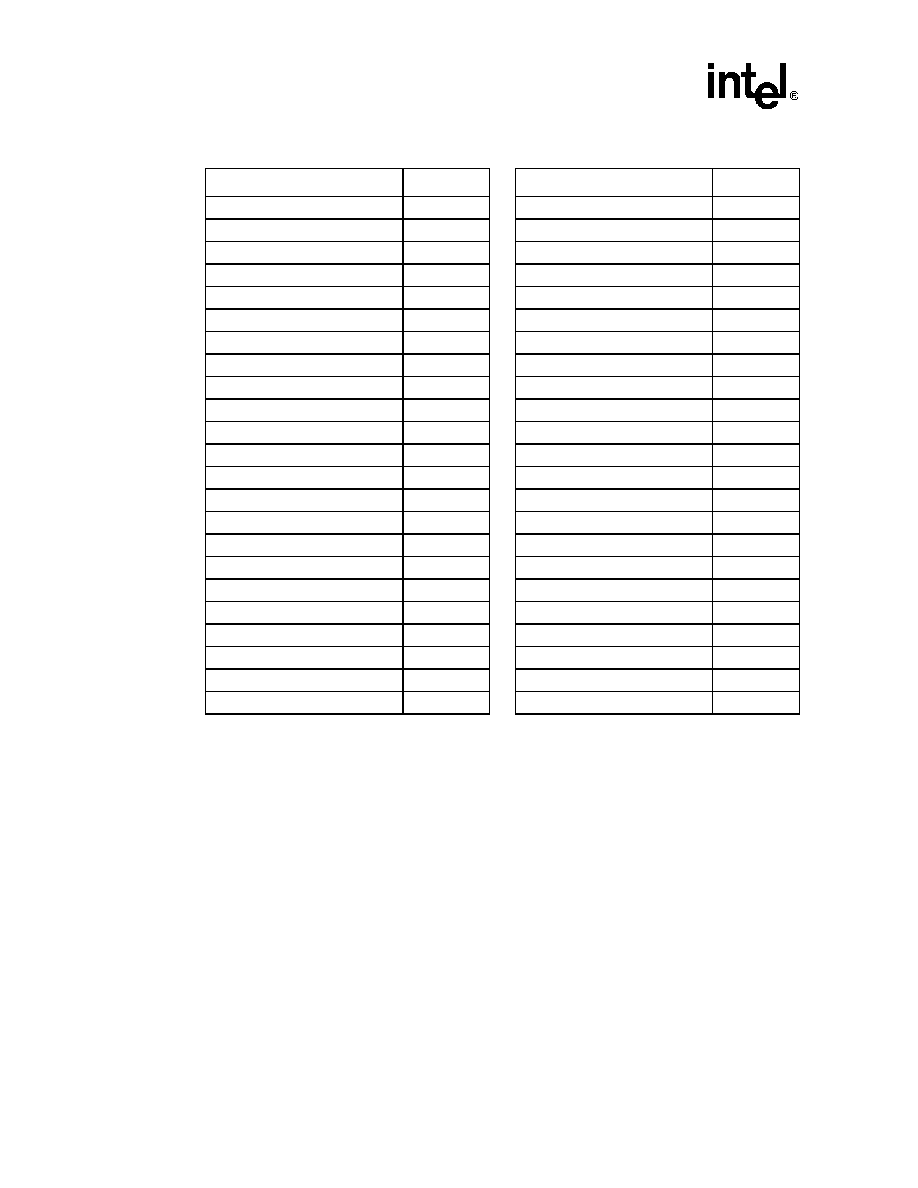

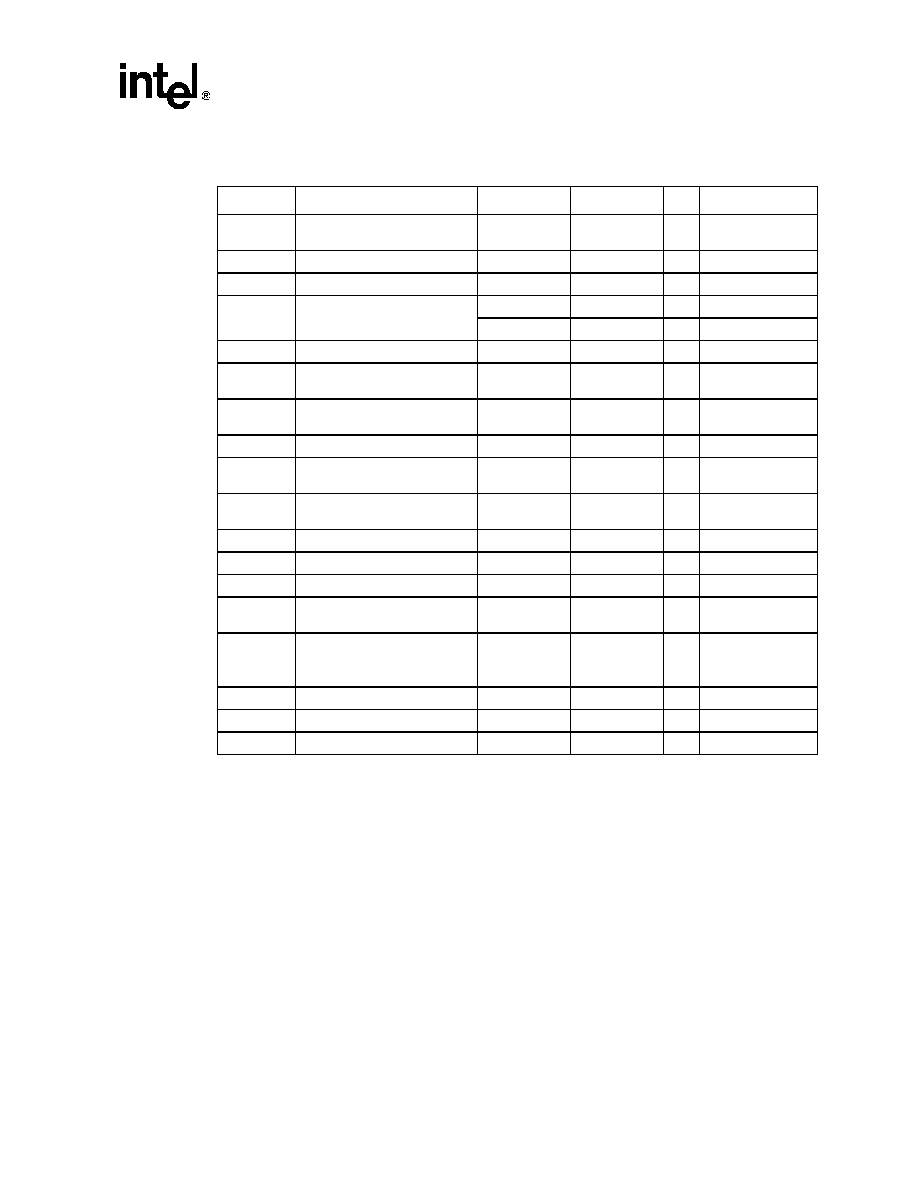

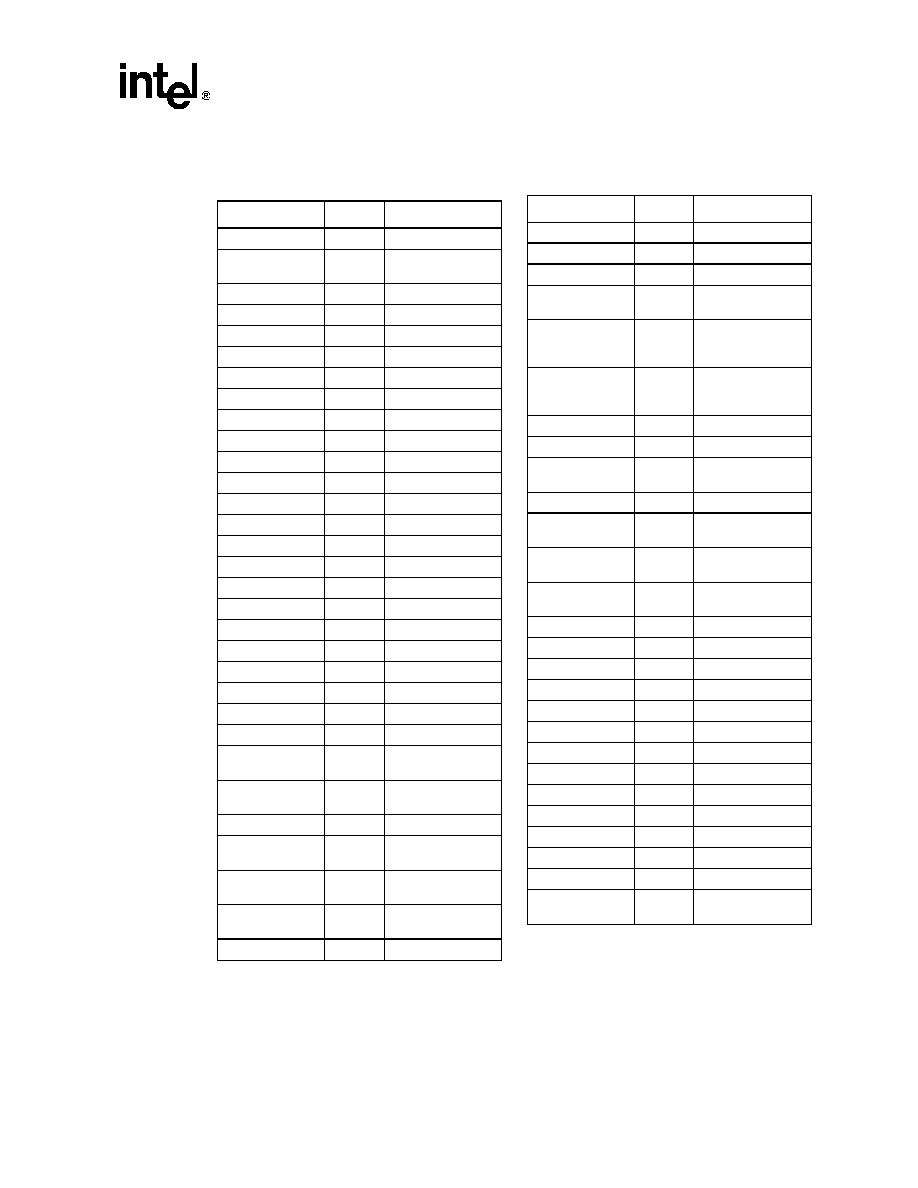

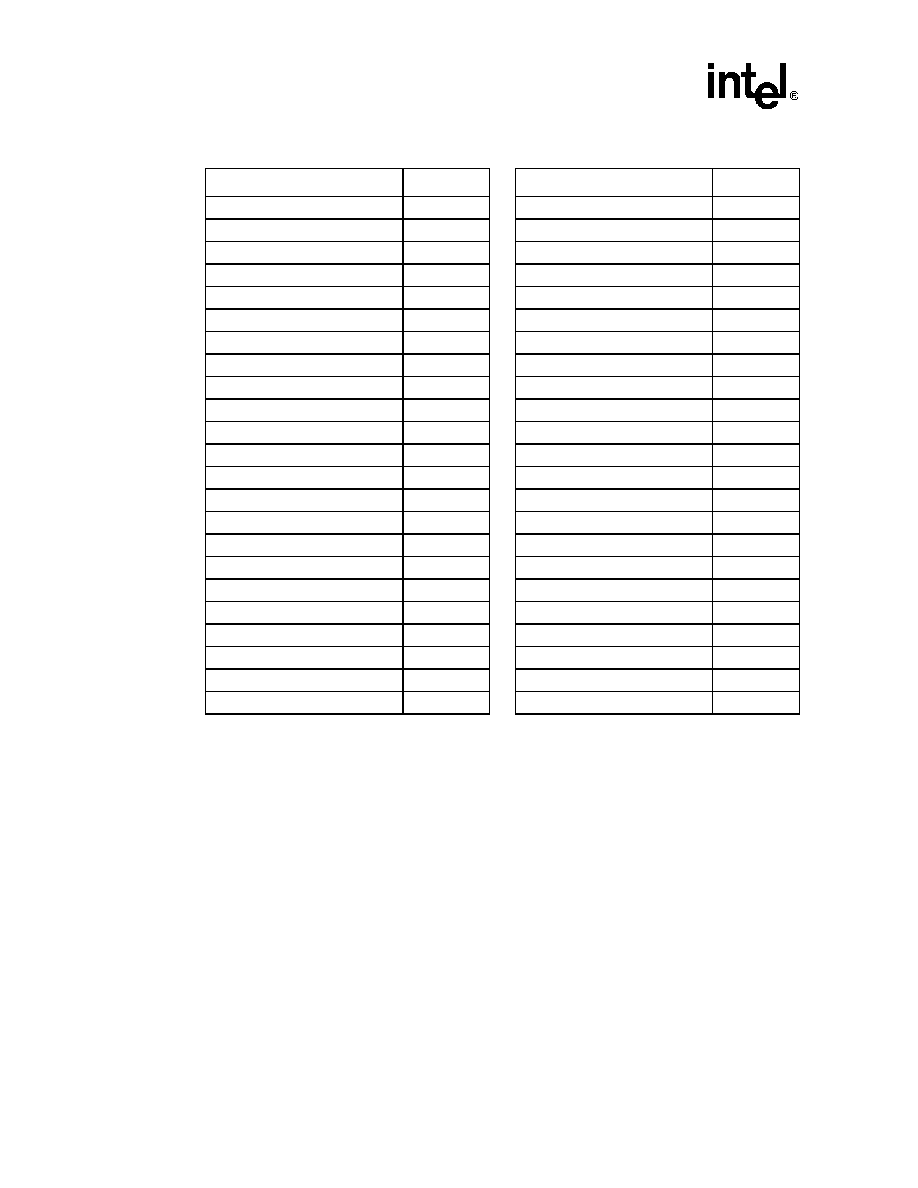

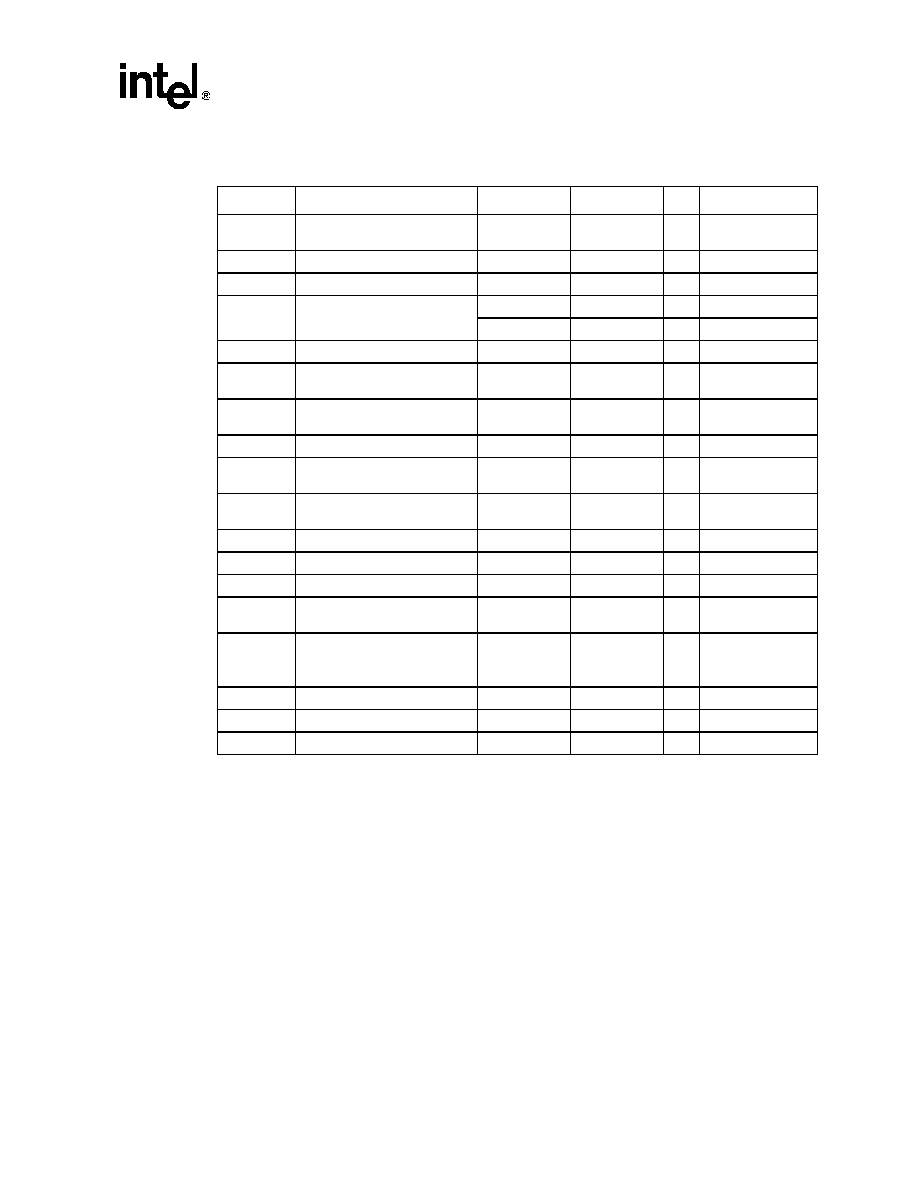

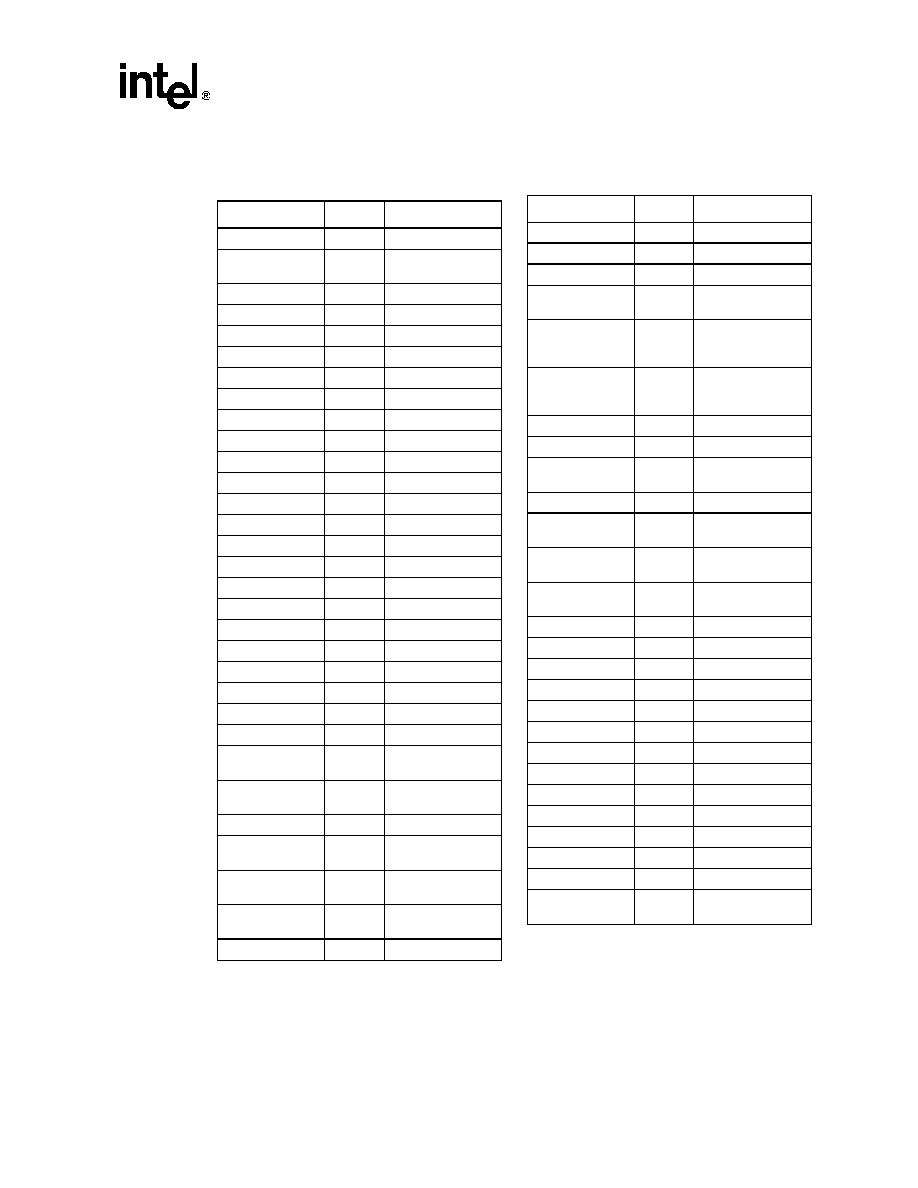

Table 4. Ball List By Number

Ball Number

Signal Name

A1

VSS

A2

AD[28]

A3

GNT[3]#

A4

NC[4]

A5

PIRQ[A]#

A6

VSS

A7

PIRQ[H]#/GPIO[5]

A8

GNT[0]#

A9

VSS

A10

GPIO[21]

A11

THRM#

A12

TP[0]

A13

VSS

A14

SIU_SERIRQ

A15

SIU_LAD[1]

A16

SIU1_RTS#

A17

VSS

A18

SIU1_DSR#

A19

UART_CLK

A20

VSS

A21

SIU0_RI#

A22

LAN1_TXD[1]

A23

VSS

B1

FRAME#

B2

AD[16]

B3

AD[22]

B4

AD[26]

B5

REQ[0]#

B6

NC[5]

B7

PIRQ[D]#

B8

Vcc1_8

B9

GNT[B]#/GNT[5]#/GPIO[17]

B10

GNT[A]#/GPIO[16]

B11

LDRQ[0]#

B12

LAD[0]/FWH[0]

B13

LAD[3]/FWH[3]

B14

Vcc1_8

B15

SIU_LFRAME#

B16

SIU1_DTR#

B17

Vcc3_3

B18

SIU1_RXD

B19

SIU0_DTR#

B20

SIU0_DCD#

B21

LAN1_CLK

B22

Vcc1_8

B23

LAN1_RXD[2]

C1

AD[13]

C2

AD[20]

C3

PAR

C4

VSS

C5

AD[30]

C6

VSS

C7

PIRQ[C]#

C8

PIRQ[E]#

C9

REQ[A]#/GPIO[0]

C10

REQ[B]#/REQ[5]#/GPIO[1]

C11

LDRQ[1]#

C12

VSS

C13

LFRAME#/FWH[4]

C14

SIU_LAD[2]

C15

SIU_LDRQ#

C16

SIU1_DCD#

C17

SIU1_TXD

C18

Vcc3_3

C19

VSS

C20

LAN1_TXD[0]

C21

LAN1_RXD[0]

C22

LAN1_RSTSYNC

C23

EE0_SHCLK

D1

VSS

D2

AD[4]

D3

AD[15]

D4

STOP#

D5

AD[18]

D6

AD[24]

D7

REQ[1]#

D8

PIRQ[B]#

D9

VSS

D10

GNT[1]#

D11

V5REF

D12

LAD[1]/FWH[1]

D13

SIU_RESET#

D14

SIU_LAD[0]

D15

SIU1_RI#

D16

SIU1_CTS#

D17

SIU0_CTS#

D18

SIU0_DSR#

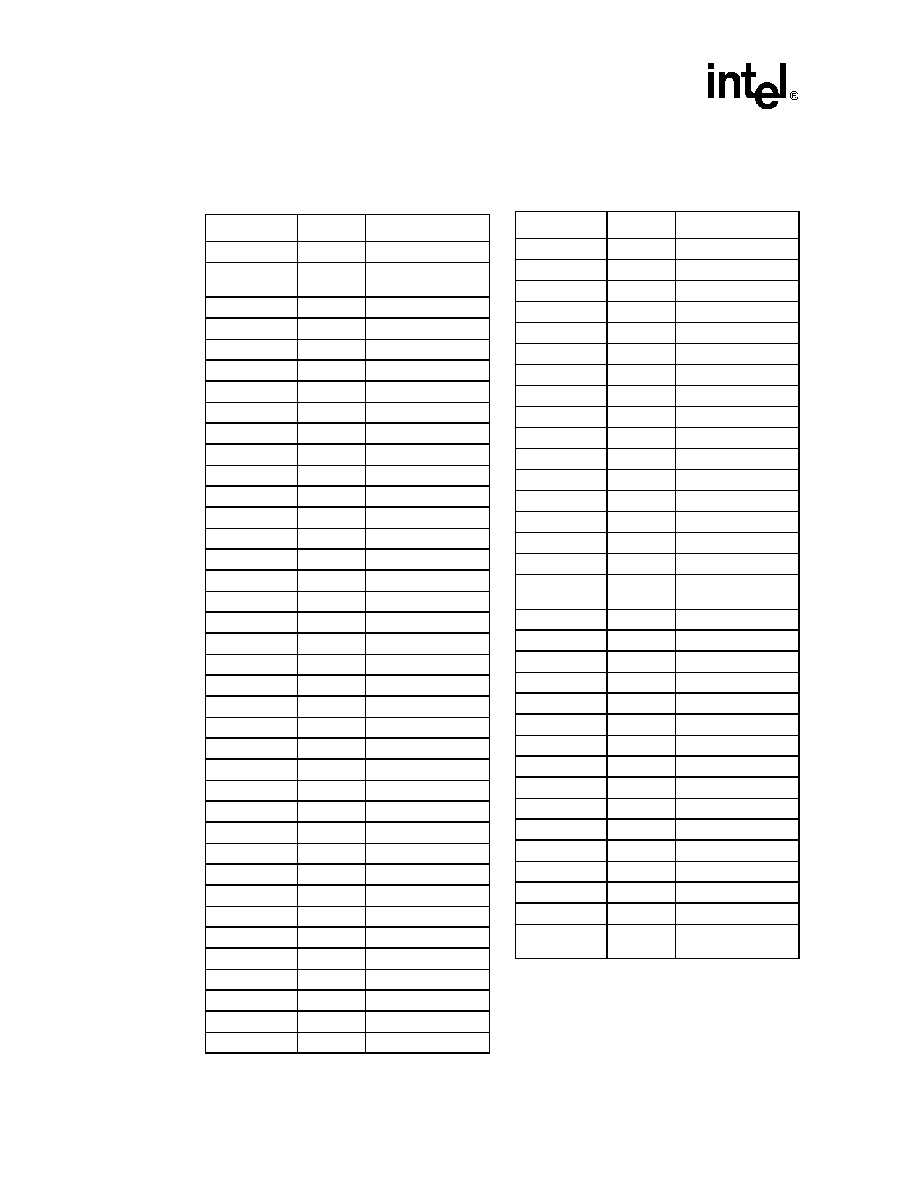

Table 4. Ball List By Number

Ball Number

Signal Name

Intel

Æ

82801E C-ICH

Advance Information Datasheet

13

D19

SIU0_TXD

D20

LAN1_TXD[2]

D21

EE1_DOUT

D22

VSS

D23

LAN0_RSTSYNC

E1

AD[0]

E2

Vcc1_8

E3

AD[9]

E4

TRDY#

E5

VSS

E6

Vcc3_3

E7

VSS

E8

GNT[2]#

E9

REQ[2]#

E10

PIRQ[F]#

E11

PIRQ[G]#/GPIO[4]

E12

LAD[2]/FWH[2]

E13

SIU_LCLK

E14

SIU_LAD[3]

E15

VSS

E16

SIU0_RTS#

E17

SIU0_RXD

E18

Vcc3_3

E19

VSS

E20

EE1_SHCLK

E21

EE0_DIN

E22

LAN0_RXD[2]

E23

LAN0_TXD[2]

F1

AD[7]

F2

AD[10]

F3

AD[6]

F4

C/BE[0]#

F5

AD[11]

F6

Vcc3_3

F7

Vcc3_3

F8

Vcc1_8

F9

Vcc1_8

F10

Vcc1_8

F14

Vcc1_8

F15

Vcc3_3

F16

Vcc3_3

F17

Vcc3_3

F18

Vcc3_3

F19

EE1_CS

Table 4. Ball List By Number

Ball Number

Signal Name

F20

EE0_CS

F21

Vcc1_8

F22

LAN0_CLK

F23

Vcc1_8

G1

SERR#

G2

AD[12]

G3

VSS

G4

AD[3]

G5

AD[2]

G6

Vcc3_3

G18

Vcc3_3

G19

EE1_DIN

G20

EE0_DOUT

G21

LAN0_TXD[1]

G22

VSS

G23

LAN0_RXD[1]

H1

C/BE[1]#

H2

AD[14]

H3

AD[8]

H4

AD[1]

H5

AD[5]

H6

Vcc3_3

H18

Vcc3_3

H19

LAN1_RXD[1]

H20

LAN0_RXD[0]

H21

LAN0_TXD[0]

H22

Vcc1_8

H23

VSS

J1

VSS

J2

C/BE[2]#

J3

DEVSEL#

J4

PERR#

J5

VSS

J6

Vcc3_3

J18

Vcc1_8

J19

VSS

J20

VSS

J21

VSS

J22

VSS

J23

CLK66 (HLCLK)

K1

AD[23]

K2

AD[19]

K3

AD[17]

K4

IRDY#

Table 4. Ball List By Number

Ball Number

Signal Name

Intel

Æ

82801E C-ICH

14

Advance Information Datasheet

K5

PLOCK#

K6

Vcc3_3

K10

Vcc1_8

K11

VSS

K12

Vcc1_8

K13

VSS

K14

Vcc1_8

K18

Vcc1_8

K19

HLCOMP

K20

HUBREF

K21

VSS

K22

HL[11]

K23

VSS

L1

AD[27]

L2

AD[25]

L3

VSS

L4

C/BE[3]#

L5

AD[21]

L10

VSS

L11

VSS

L12

VSS

L13

VSS

L14

Vcc1_8

L19

HL[0]

L20

VSS

L21

HL[1]

L22

VSS

L23

HL[2]

M1

AD[29]

M2

AD[31]

M3

GPIO[6]

M4

REQ[3]#

M5

PCICLK

M10

Vcc1_8

M11

VSS

M12

VSS

M13

VSS

M14

Vcc1_8

M19

HL[9]

M20

HL[3]

M21

VSS

M22

HL_STB

M23

VSS

N1

VSS

Table 4. Ball List By Number

Ball Number

Signal Name

N2

GPIO[7]

N3

GPIO[27]

N4

GPIO[28]

N5

Vcc1_8

N10

VSS

N11

VSS

N12

VSS

N13

VSS

N14

VSS

N19

HL[4]

N20

VSS

N21

HL[10]

N22

VSS

N23

HL_STB#

P1

GPIO[8]

P2

GPIO[12]

P3

GPIO[13]

P4

RESERVED1

P5

VSS

P6

Vcc3_3

P10

Vcc1_8

P11

VSS

P12

Vcc1_8

P13

VSS

P14

Vcc1_8

P18

Vcc1_8

P19

HL[7]

P20

HL[5]

P21

VSS

P22

HL[8]

P23

VSS

R1

PCIRST#

R2

GPIO[25]

R3

Vcc3_3

R4

SMBDATA

R5

RI#

R6

Vcc3_3

R18

Vcc1_8

R19

CPUSLP#

R20

VSS

R21

VSS

R22

VSS

R23

HL[6]

T1

VSS

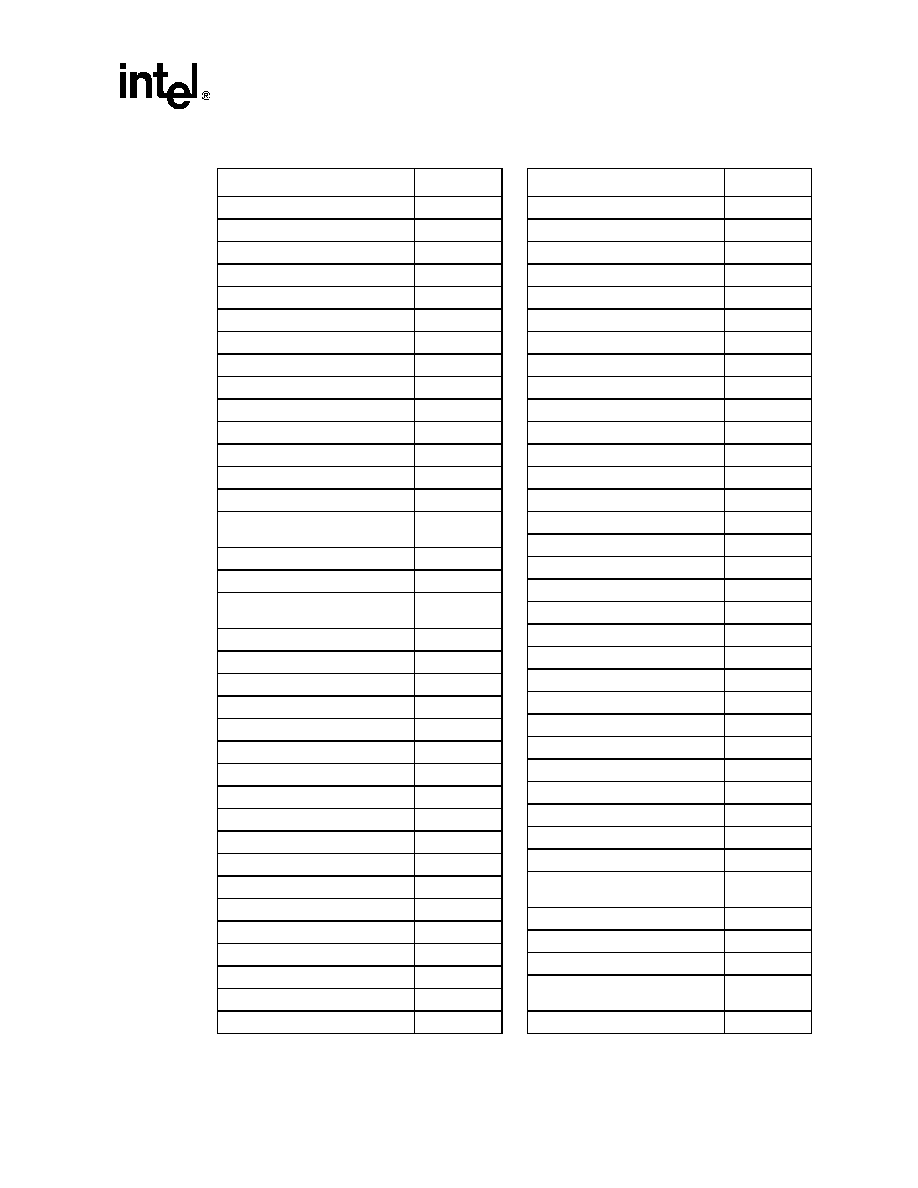

Table 4. Ball List By Number

Ball Number

Signal Name

Intel

Æ

82801E C-ICH

Advance Information Datasheet

15

T2

SMBCLK

T3

RSM_PWROK

T4

NC[12]

T5

USBP0N

T6

Vcc3_3

T18

Vcc1_8

T19

GPIO[20]

T20

GPIO[23]

T21

SMI#

T22

STPCLK#

T23

A20M#

U1

SMBALERT#/GPIO[11]

U2

NC[11]

U3

SUSCLK

U4

USBP0P

U5

VSS

U6

Vcc3_3

U18

Vcc3_3

U19

SDCS1#

U20

GPIO[22]

U21

INIT#

U22

NMI

U23

INTR

V1

NC[10]

V2

USBP1N

V3

Vcc3_3

V4

NC[6]

V5

V5REF

V6

Vcc3_3

V7

Vcc3_3

V8

Vcc3_3

V9

Vcc3_3

V10

Vcc3_3

V14

Vcc3_3

V15

Vcc3_3

V16

Vcc3_3

V17

Vcc3_3

V18

Vcc3_3

V19

SDDACK#

V20

SIORDY (/SDRSTB/

SWDMARDY#)

V21

V_CPU_IO

V22

CPUPWRGD

V23

IGNNE#

Table 4. Ball List By Number

Ball Number

Signal Name

W1

USBP1P

W2

NC[9]

W3

NC[7]

W4

OC[1]#

W5

VSS

W6

VSS

W7

NC[1]

W8

VccRTC

W9

PWROK

W10

Vcc3_3

W11

CLK14

W12

PDD[5]

W13

PDD[1]

W14

PDCS1#

W15

PDA[1]

W16

SDD[5]

W17

SDD[14]

W18

SDIOR# (/SDWSTB/

SRDMARDY#)

W19

SDIOW# (/SDSTOP)

W20

SDA[2]

W21

VRMPWRGD

W22

V_CPU_IO

W23

RCIN#

Y1

VSS

Y2

NC[8]

Y3

V5REF

Y4

RESERVED2

Y5

SMLINK[0]

Y6

VSS

Y7

RTCX1

Y8

RSMRST#

Y9

NC[2]

Y10

APICD[1]

Y11

PDD[6]

Y12

PDD[10]

Y13

PDD[12]

Y14

PDIOW# (/PDSTOP)

Y15

SDD[6]

Y16

PDA[0]

Y17

SDD[10]

Y18

SDD[12]

Y19

SDD[0]

Y20

SDD[15]

Table 4. Ball List By Number

Ball Number

Signal Name

Intel

Æ

82801E C-ICH

16

Advance Information Datasheet

Y21

SDCS3#

Y22

GPIO[18]

Y23

A20GATE

AA1

OC[0]#

AA2

VSS

AA3

VSS

AA4

SMLINK[1]

AA5

TP[1]

AA6

RTCRST#

AA7

RTCX2

AA8

VccRTC

AA9

FERR#

AA10

SERIRQ

AA11

PDD[7]

AA12

VSS

AA13

PDD[3]

AA14

PDD[0]

AA15

PDDACK#

AA16

VSS

AA17

SDD[8]

AA18

SDD[4]

AA19

SDD[3]

AA20

VSS

AA21

SDA[1]

AA22

VSS

AA23

GPIO[19]

AB1

V5REF

AB2

TP[3]

AB3

Vcc3_3

AB4

GPIO[24]

AB5

INTRUDER#

AB6

VBIAS

AB7

VSS

AB8

CLK48

AB9

APICD[0]

AB10

SPKR

AB11

PDD[8]

Table 4. Ball List By Number

Ball Number

Signal Name

AB12

PDD[4]

AB13

PDD[13]

AB14

PDD[14]

AB15

PDD[15]

AB16

IRQ[14]

AB17

PDIOR# (/PDWSTB/

PRDMARDY#)

AB18

SDD[9]

AB19

SDD[11]

AB20

SDD[13]

AB21

Vcc3_3

AB22

IRQ[15]

AB23

SDA[0]

AC1

VSS

AC2

TP[2]

AC3

VSS

AC4

VSS

AC5

VSS

AC6

VSS

AC7

NC[3]

AC8

VSS

AC9

APICCLK

AC10

V5REF

AC11

PDD[9]

AC12

PDD[11]

AC13

VSS

AC14

PDD[2]

AC15

PDDREQ

AC16

PDA[2]

AC17

PIORDY (/PDRSTB/

PWDMARDY#)

AC18

SDD[7]

AC19

PDCS3#

AC20

SDD[2]

AC21

SDD[1]

AC22

SDDREQ

AC23

VSS

Table 4. Ball List By Number

Ball Number

Signal Name

Intel

Æ

82801E C-ICH

Advance Information Datasheet

17

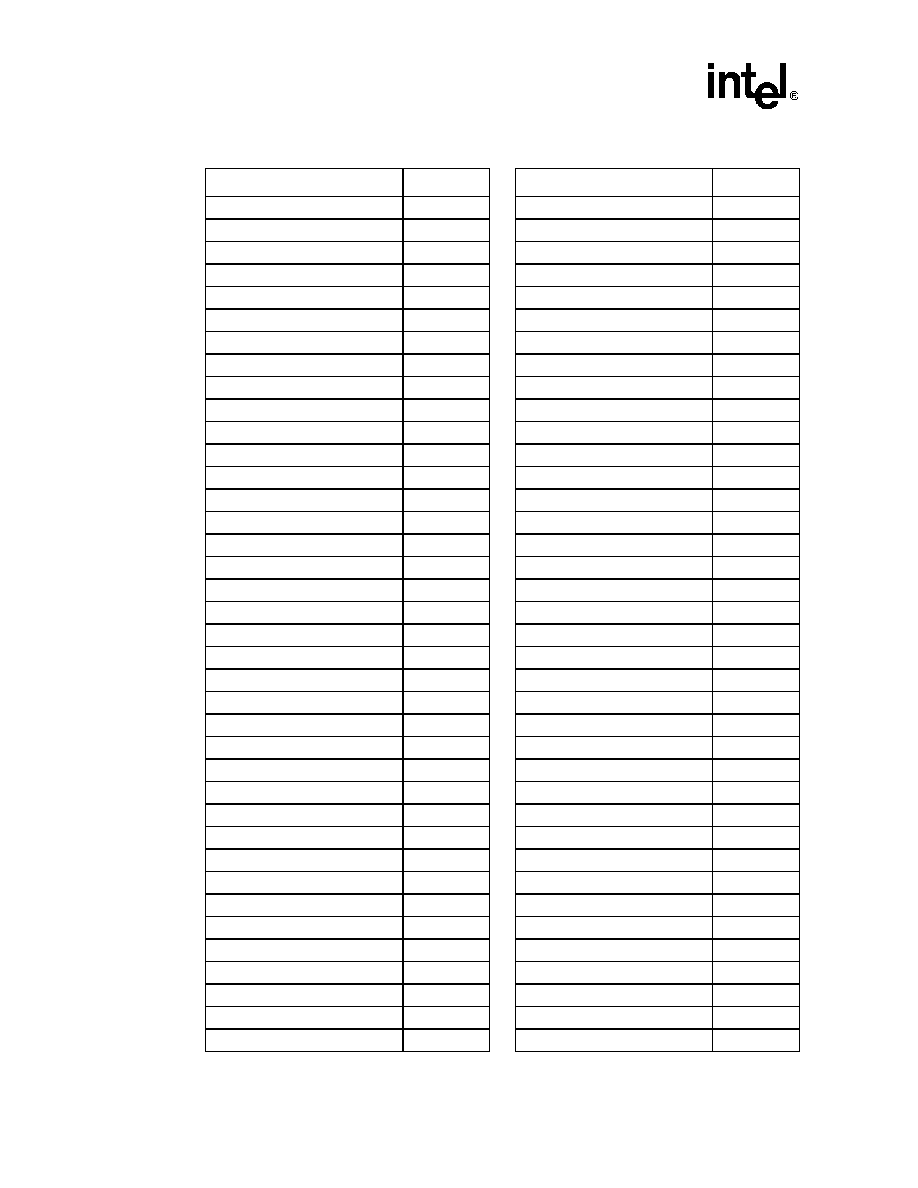

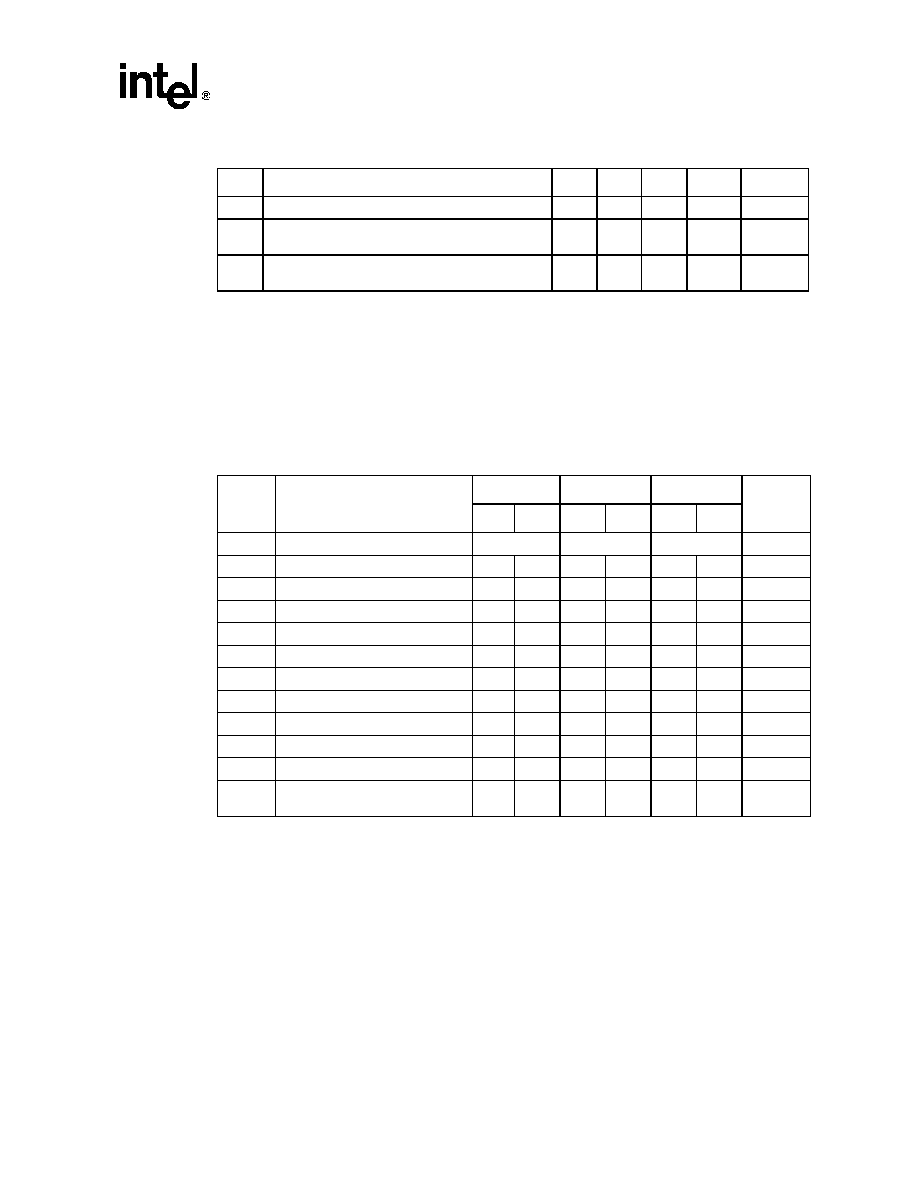

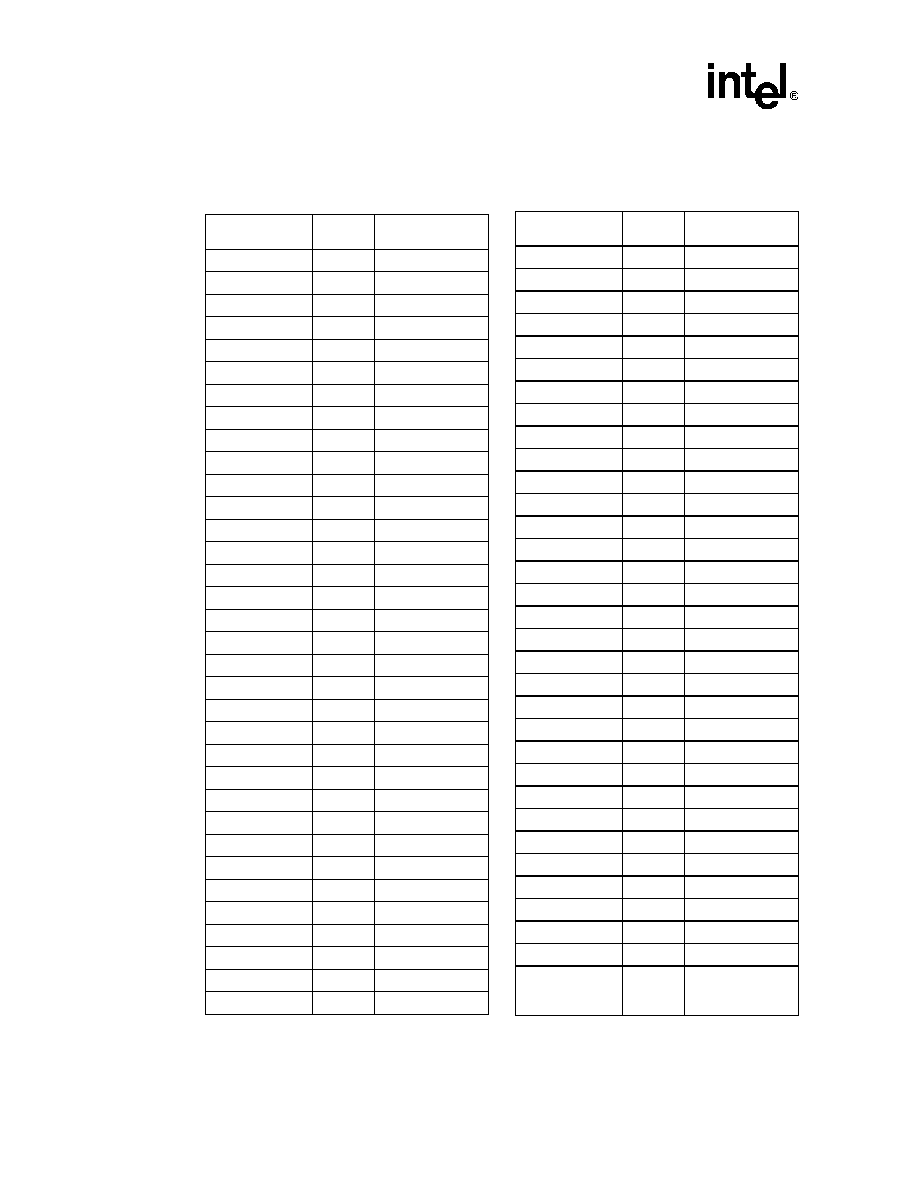

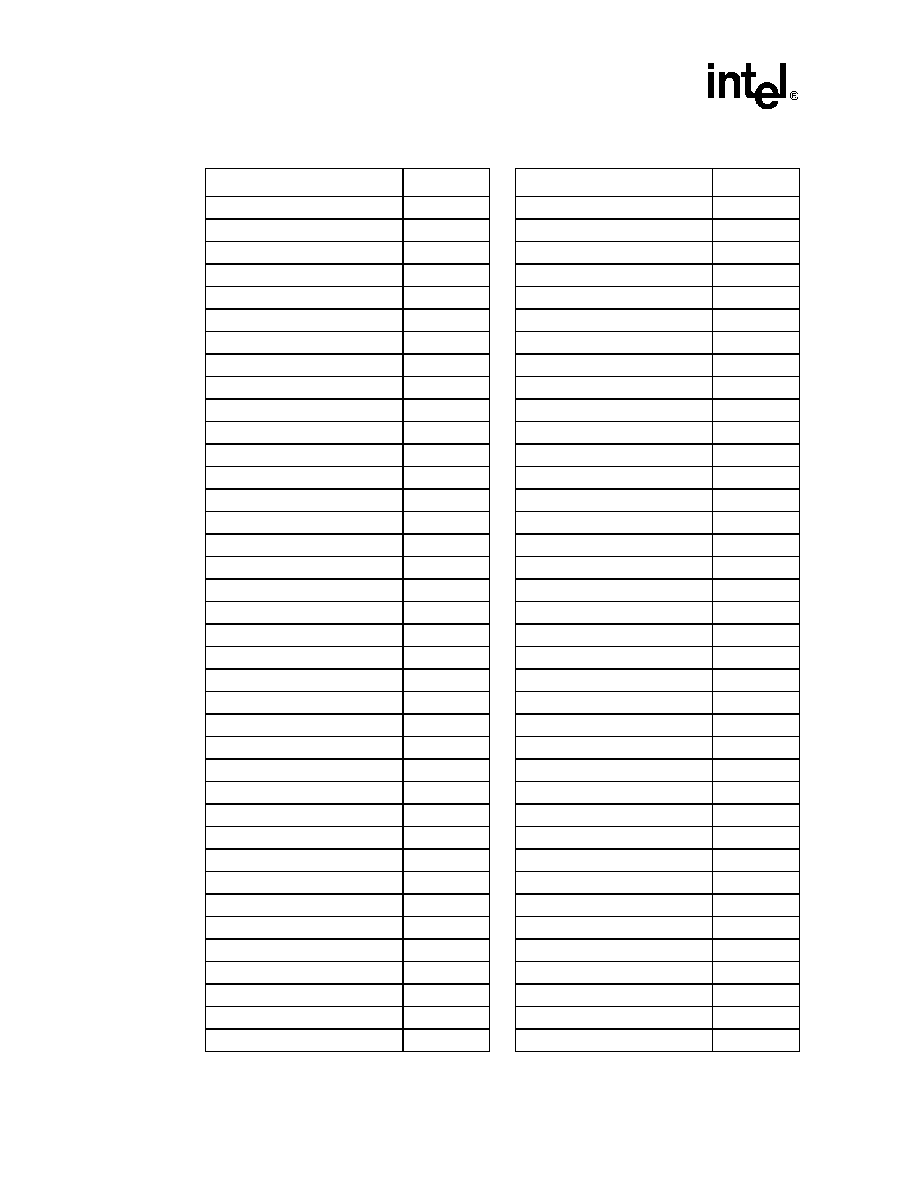

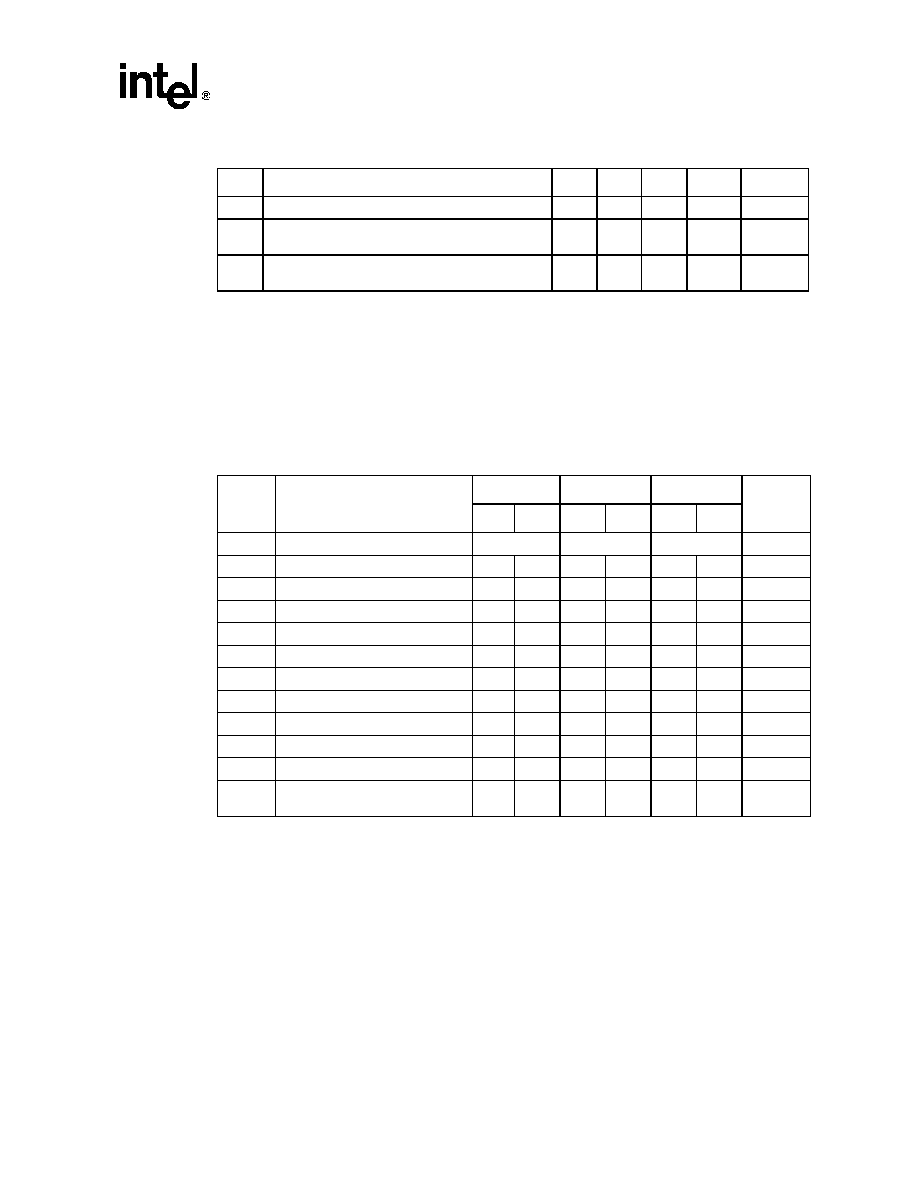

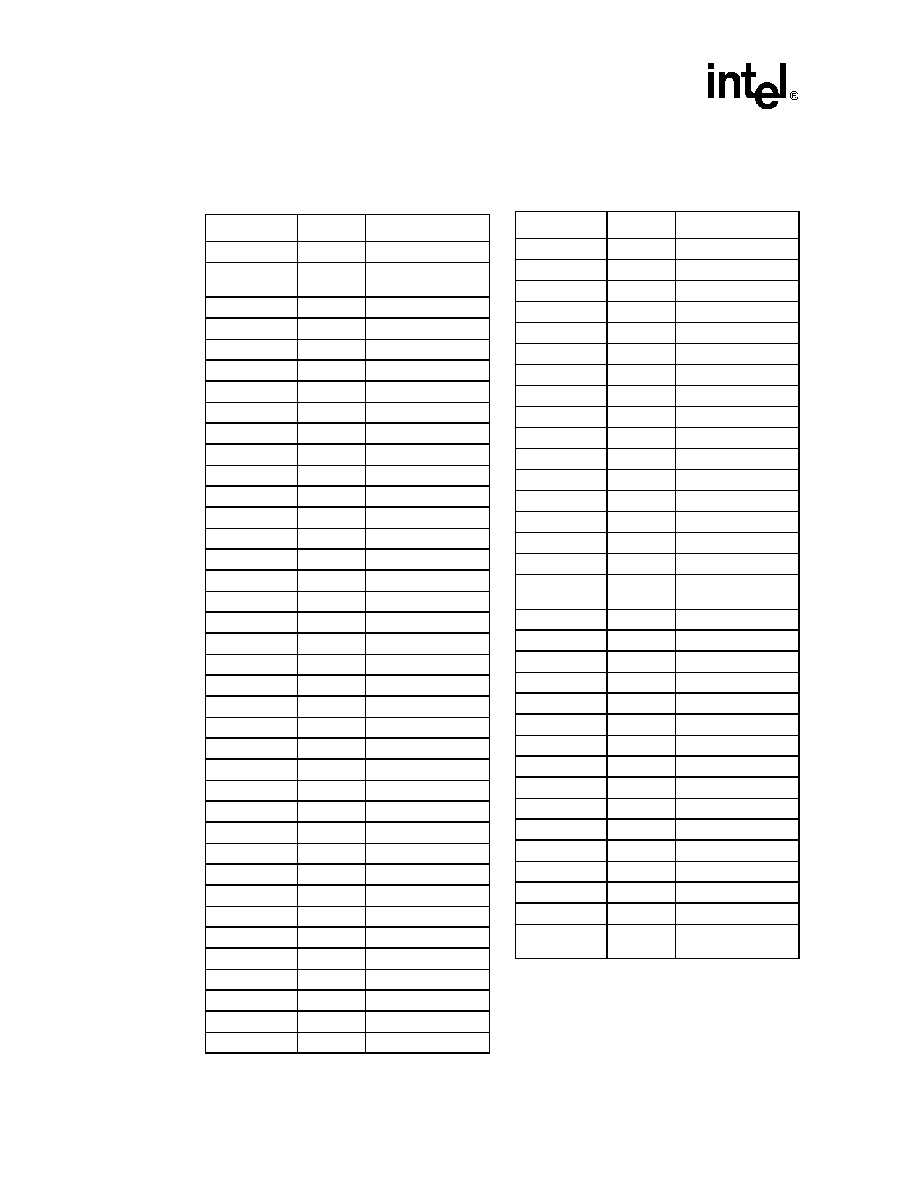

Table 5. Ball List By Signal Name

Signal Name

Ball Number

A20GATE

Y23

A20M#

T23

AD[0]

E1

AD[1]

H4

AD[2]

G5

AD[3]

G4

AD[4]

D2

AD[5]

H5

AD[6]

F3

AD[7]

F1

AD[8]

H3

AD[9]

E3

AD[10]

F2

AD[11]

F5

AD[12]

G2

AD[13]

C1

AD[14]

H2

AD[15]

D3

AD[16]

B2

AD[17]

K3

AD[18]

D5

AD[19]

K2

AD[20]

C2

AD[21]

L5

AD[22]

B3

AD[23]

K1

AD[24]

D6

AD[25]

L2

AD[26]

B4

AD[27]

L1

AD[28]

A2

AD[29]

M1

AD[30]

C5

AD[31]

M2

APICCLK

AC9

APICD[0]

AB9

APICD[1]

Y10

C/BE[0]#

F4

C/BE[1]#

H1

C/BE[2]#

J2

C/BE[3]#

L4

CLK14

W11

CLK48

AB8

CLK66 (HLCLK)

J23

CPUPWRGD

V22

CPUSLP#

R19

DEVSEL#

J3

EE0_CS

F20

EE0_DIN

E21

EE0_DOUT

G20

EE0_SHCLK

C23

EE1_CS

F19

EE1_DIN

G19

EE1_DOUT

D21

EE1_SHCLK

E20

FERR#

AA9

FRAME#

B1

GNT[0]#

A8

GNT[1]#

D10

GNT[2]#

E8

GNT[3]#

A3

GNT[A]#/GPIO[16]

B10

GNT[B]#/GNT[5]#/GPIO[17]

B9

GPIO[6]

M3

GPIO[7]

N2

GPIO[8]

P1

GPIO[12]

P2

GPIO[13]

P3

GPIO[18]

Y22

GPIO[19]

AA23

GPIO[20]

T19

GPIO[21]

A10

GPIO[22]

U20

GPIO[23]

T20

GPIO[24]

AB4

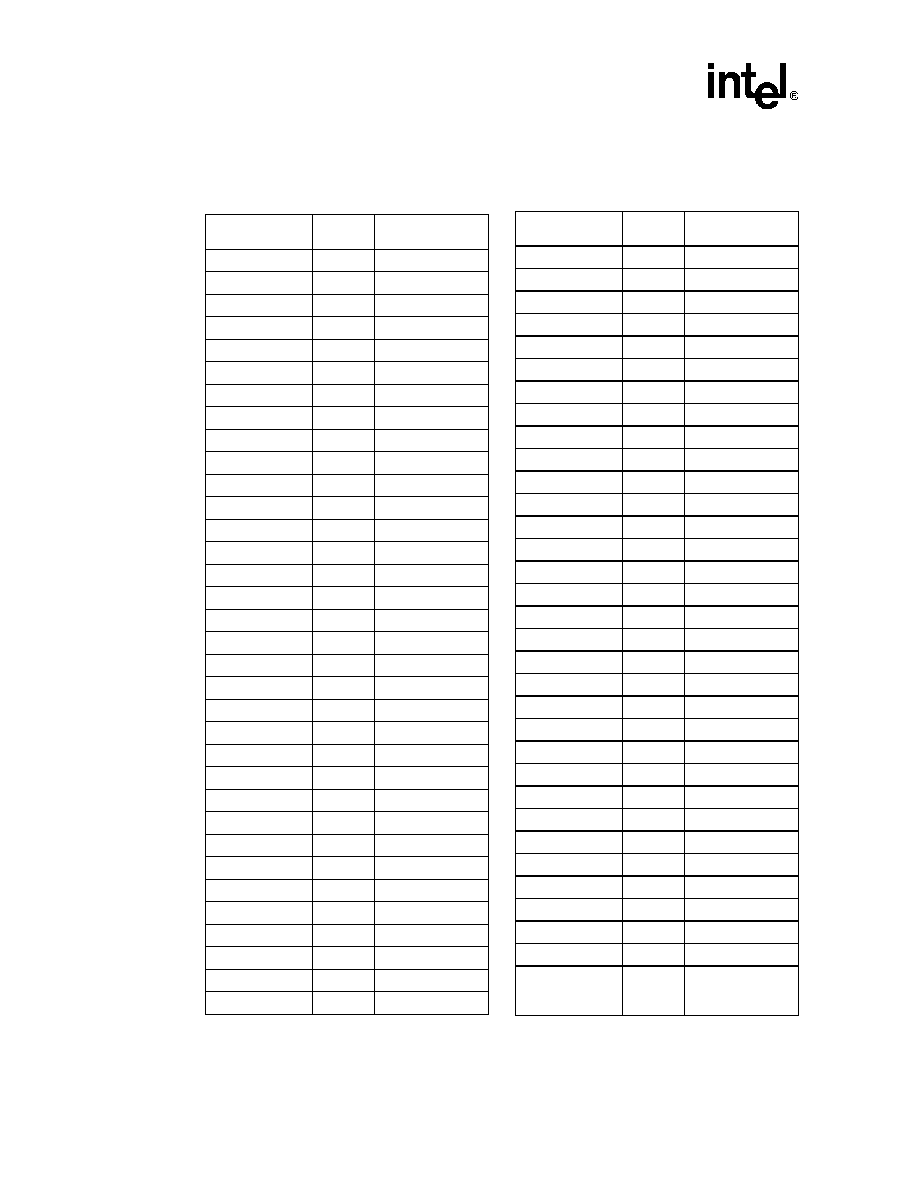

Table 5. Ball List By Signal Name

Signal Name

Ball Number

Intel

Æ

82801E C-ICH

18

Advance Information Datasheet

GPIO[25]

R2

GPIO[27]

N3

GPIO[28]

N4

HL[0]

L19

HL[1]

L21

HL[2]

L23

HL[3]

M20

HL[4]

N19

HL[5]

P20

HL[6]

R23

HL[7]

P19

HL[8]

P22

HL[9]

M19

HL[10]

N21

HL[11]

K22

HL_STB

M22

HL_STB#

N23

HLCOMP

K19

HUBREF

K20

IGNNE#

V23

INIT#

U21

INTR

U23

INTRUDER#

AB5

IRDY#

K4

IRQ[14]

AB16

IRQ[15]

AB22

LAD[0]/FWH[0]

B12

LAD[1]/FWH[1]

D12

LAD[2]/FWH[2]

E12

LAD[3]/FWH[3]

B13

LAN0_CLK

F22

LAN0_RSTSYNC

D23

LAN0_RXD[0]

H20

LAN0_RXD[1]

G23

LAN0_RXD[2]

E22

LAN0_TXD[0]

H21

LAN0_TXD[1]

G21

LAN0_TXD[2]

E23

Table 5. Ball List By Signal Name

Signal Name

Ball Number

LAN1_CLK

B21

LAN1_RSTSYNC

C22

LAN1_RXD[0]

C21

LAN1_RXD[1]

H19

LAN1_RXD[2]

B23

LAN1_TXD[0]

C20

LAN1_TXD[1]

A22

LAN1_TXD[2]

D20

LDRQ[0]#

B11

LDRQ[1]#

C11

LFRAME#/FWH[4]

C13

NC[1]

W7

NC[2]

Y9

NC[3]

AC7

NC[4]

A4

NC[5]

B6

NC[6]

V4

NC[7]

W3

NC[8]

Y2

NC[9]

W2

NC[10]

V1

NC[11]

U2

NC[12]

T4

NMI

U22

OC[0]#

AA1

OC[1]#

W4

PAR

C3

PCICLK

M5

PCIRST#

R1

PDA[0]

Y16

PDA[1]

W15

PDA[2]

AC16

PDCS1#

W14

PDCS3#

AC19

PDD[0]

AA14

PDD[1]

W13

PDD[2]

AC14

PDD[3]

AA13

Table 5. Ball List By Signal Name

Signal Name

Ball Number

Intel

Æ

82801E C-ICH

Advance Information Datasheet

19

PDD[4]

AB12

PDD[5]

W12

PDD[6]

Y11

PDD[7]

AA11

PDD[8]

AB11

PDD[9]

AC11

PDD[10]

Y12

PDD[11]

AC12

PDD[12]

Y13

PDD[13]

AB13

PDD[14]

AB14

PDD[15]

AB15

PDDACK#

AA15

PDDREQ

AC15

PDIOR# (/PDWSTB/

PRDMARDY#)

AB17

PDIOW# (/PDSTOP)

Y14

PERR#

J4

PIORDY (/PDRSTB/

PWDMARDY#)

AC17

PIRQ[A]#

A5

PIRQ[B]#

D8

PIRQ[C]#

C7

PIRQ[D]#

B7

PIRQ[E]# C8

PIRQ[F]#

E10

PIRQ[G]#/GPIO[4]

E11

PIRQ[H]#/GPIO[5]

A7

PLOCK#

K5

PWROK

W9

RCIN#

W23

REQ[0]#

B5

REQ[1]#

D7

REQ[2]#

E9

REQ[3]#

M4

REQ[A]#/GPIO[0]

C9

REQ[B]#/REQ[5]#/GPIO[1]

C10

RESERVED1

P4

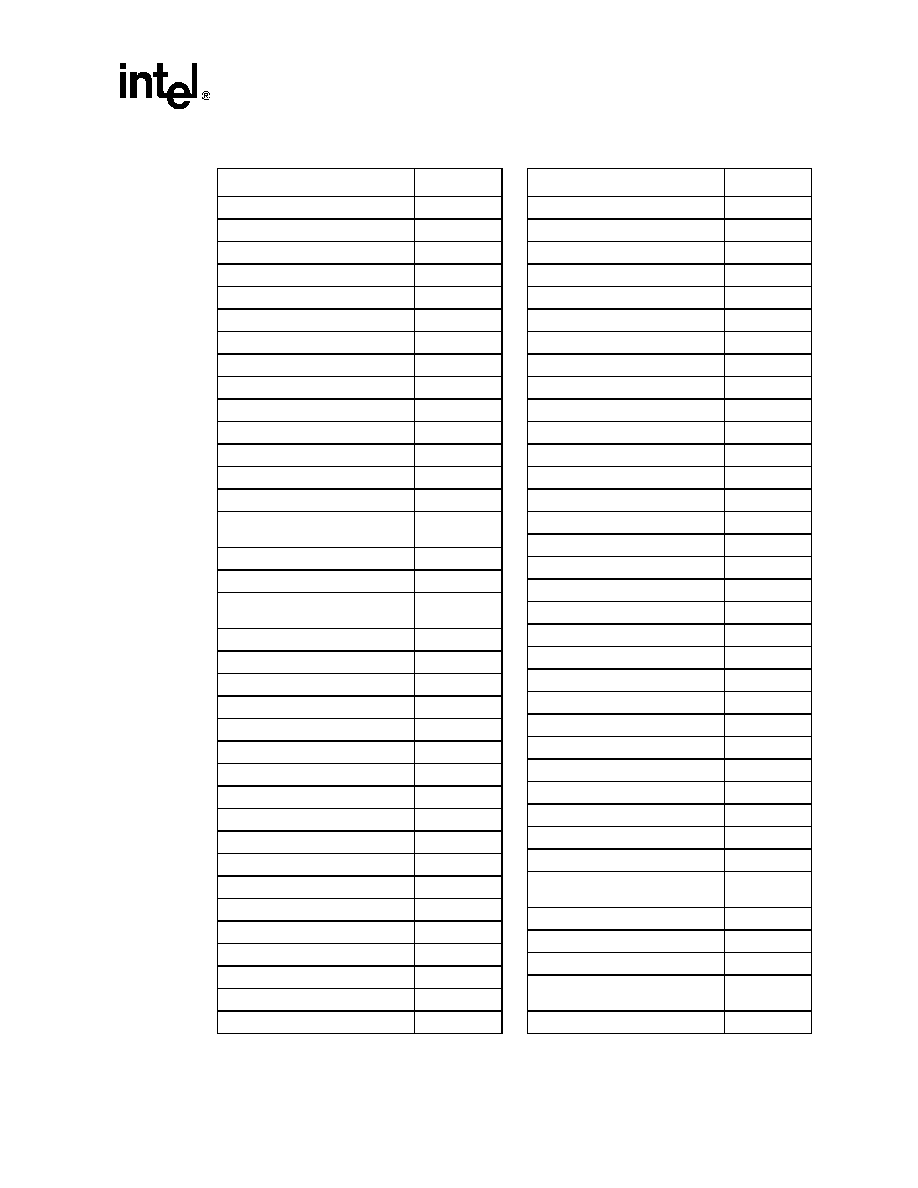

Table 5. Ball List By Signal Name

Signal Name

Ball Number

RESERVED2

Y4

RI#

R5

RSM_PWROK

T3

RSMRST#

Y8

RTCRST#

AA6

RTCX1

Y7

RTCX2

AA7

SDA[0]

AB23

SDA[1]

AA21

SDA[2]

W20

SDCS1#

U19

SDCS3#

Y21

SDD[0]

Y19

SDD[1]

AC21

SDD[2]

AC20

SDD[3]

AA19

SDD[4]

AA18

SDD[5]

W16

SDD[6]

Y15

SDD[7]

AC18

SDD[8]

AA17

SDD[9]

AB18

SDD[10]

Y17

SDD[11]

AB19

SDD[12]

Y18

SDD[13]

AB20

SDD[14]

W17

SDD[15]

Y20

SDDACK#

V19

SDDREQ

AC22

SDIOR# (/SDWSTB/

SRDMARDY#)

W18

SDIOW# (/SDSTOP)

W19

SERIRQ

AA10

SERR#

G1

SIORDY (/SDRSTB/

SWDMARDY#)

V20

SIU_LAD[0]

D14

Table 5. Ball List By Signal Name

Signal Name

Ball Number

Intel

Æ

82801E C-ICH

20

Advance Information Datasheet

SIU_LAD[1]

A15

SIU_LAD[2]

C14

SIU_LAD[3]

E14

SIU_LCLK

E13

SIU_LDRQ#

C15

SIU_LFRAME#

B15

SIU_RESET#

D13

SIU_SERIRQ

A14

SIU0_CTS#

D17

SIU0_DCD#

B20

SIU0_DSR#

D18

SIU0_DTR#

B19

SIU0_RI#

A21

SIU0_RTS#

E16

SIU0_RXD

E17

SIU0_TXD

D19

SIU1_CTS#

D16

SIU1_DCD#

C16

SIU1_DSR#

A18

SIU1_DTR#

B16

SIU1_RI#

D15

SIU1_RTS#

A16

SIU1_RXD

B18

SIU1_TXD

C17

SMBALERT#/GPIO[11]

U1

SMBCLK

T2

SMBDATA

R4

SMI#

T21

SMLINK[0]

Y5

SMLINK[1]

AA4

SPKR

AB10

STOP#

D4

STPCLK#

T22

SUSCLK

U3

THRM#

A11

TP[0]

A12

TP[1]

AA5

TP[2]

AC2

Table 5. Ball List By Signal Name

Signal Name

Ball Number

TP[3]

AB2

TRDY#

E4

UART_CLK

A19

USBP0N

T5

USBP0P

U4

USBP1N

V2

USBP1P

W1

V_CPU_IO

V21

V_CPU_IO

W22

V5REF

AB1

V5REF

AC10

V5REF

D11

V5REF

V5

V5REF

Y3

VBIAS

AB6

Vcc1_8

B8

Vcc1_8

B14

Vcc1_8

B22

Vcc1_8

E2

Vcc1_8

F8

Vcc1_8

F9

Vcc1_8

F10

Vcc1_8

F14

Vcc1_8

F21

Vcc1_8

F23

Vcc1_8

H22

Vcc1_8

J18

Vcc1_8

K10

Vcc1_8

K12

Vcc1_8

K14

Vcc1_8

K18

Vcc1_8

L14

Vcc1_8

M10

Vcc1_8

M14

Vcc1_8

N5

Vcc1_8

P10

Vcc1_8

P12

Vcc1_8

P14

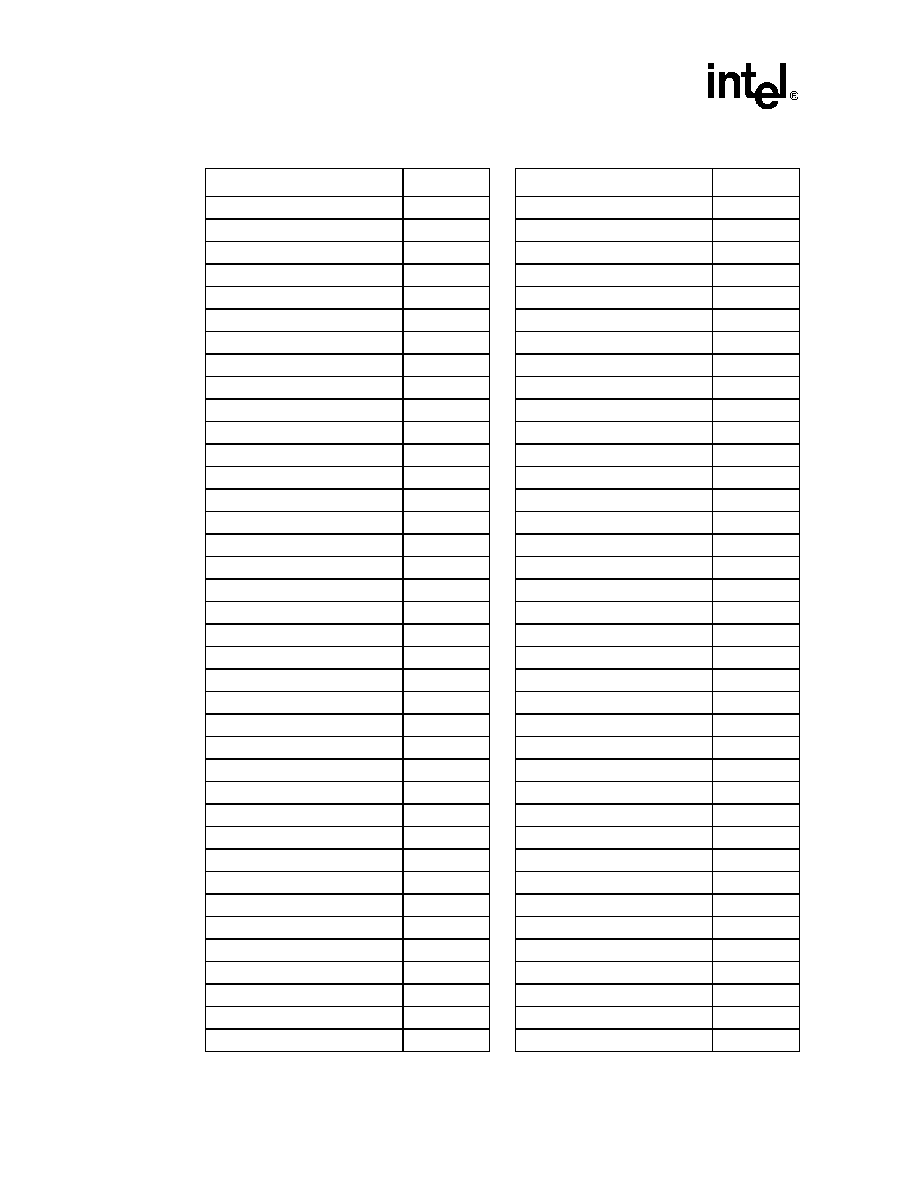

Table 5. Ball List By Signal Name

Signal Name

Ball Number

Intel

Æ

82801E C-ICH

Advance Information Datasheet

21

Vcc1_8

P18

Vcc1_8

R18

Vcc1_8

T18

Vcc3_3

AB3

Vcc3_3

AB21

Vcc3_3

B17

Vcc3_3

C18

Vcc3_3

E6

Vcc3_3

E18

Vcc3_3

F6

Vcc3_3

F7

Vcc3_3

F15

Vcc3_3

F16

Vcc3_3

F17

Vcc3_3

F18

Vcc3_3

G6

Vcc3_3

G18

Vcc3_3

H6

Vcc3_3

H18

Vcc3_3

J6

Vcc3_3

K6

Vcc3_3

P6

Vcc3_3

R3

Vcc3_3

R6

Vcc3_3

T6

Vcc3_3

U6

Vcc3_3

U18

Vcc3_3

V3

Vcc3_3

V6

Vcc3_3

V7

Vcc3_3

V8

Vcc3_3

V9

Vcc3_3

V10

Vcc3_3

V14

Vcc3_3

V15

Vcc3_3

V16

Vcc3_3

V17

Vcc3_3

V18

Table 5. Ball List By Signal Name

Signal Name

Ball Number

Vcc3_3

W10

VccRTC

W8

VccRTC

AA8

VRMPWRGD

W21

VSS

A1

VSS

A6

VSS

A9

VSS

A13

VSS

A17

VSS

A20

VSS

A23

VSS

C4

VSS

C6

VSS

C12

VSS

C19

VSS

D1

VSS

D9

VSS

D22

VSS

E5

VSS

E7

VSS

E15

VSS

E19

VSS

G3

VSS

G22

VSS

H23

VSS

J1

VSS

J5

VSS

J19

VSS

J20

VSS

J21

VSS

J22

VSS

K11

VSS

K13

VSS

K21

VSS

K23

VSS

L3

VSS

L10

VSS

L11

Table 5. Ball List By Signal Name

Signal Name

Ball Number

Intel

Æ

82801E C-ICH

22

Advance Information Datasheet

VSS

L12

VSS

L13

VSS

L20

VSS

L22

VSS

M11

VSS

M12

VSS

M13

VSS

M21

VSS

M23

VSS

N1

VSS

N10

VSS

N11

VSS

N12

VSS

N13

VSS

N14

VSS

N20

VSS

N22

VSS

P5

VSS

P11

VSS

P13

VSS

P21

VSS

P23

VSS

R20

Table 5. Ball List By Signal Name

Signal Name

Ball Number

VSS

R21

VSS

R22

VSS

T1

VSS

U5

VSS

W5

VSS

W6

VSS

Y1

VSS

Y6

VSS

AA2

VSS

AA3

VSS

AA12

VSS

AA16

VSS

AA20

VSS

AA22

VSS

AB7

VSS

AC1

VSS

AC3

VSS

AC4

VSS

AC5

VSS

AC6

VSS

AC8

VSS

AC13

VSS

AC23

Table 5. Ball List By Signal Name

Signal Name

Ball Number

Intel

Æ

82801E C-ICH

Advance Information Datasheet

23

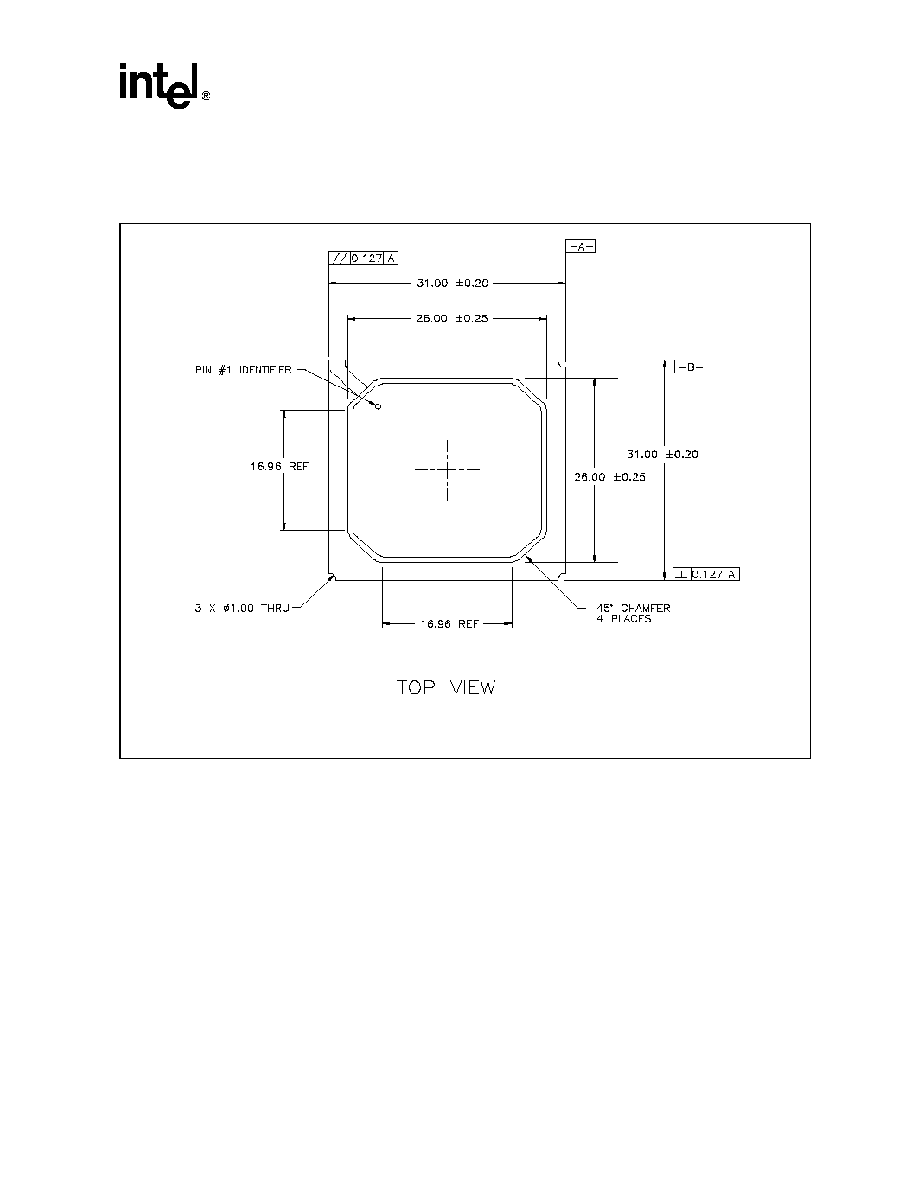

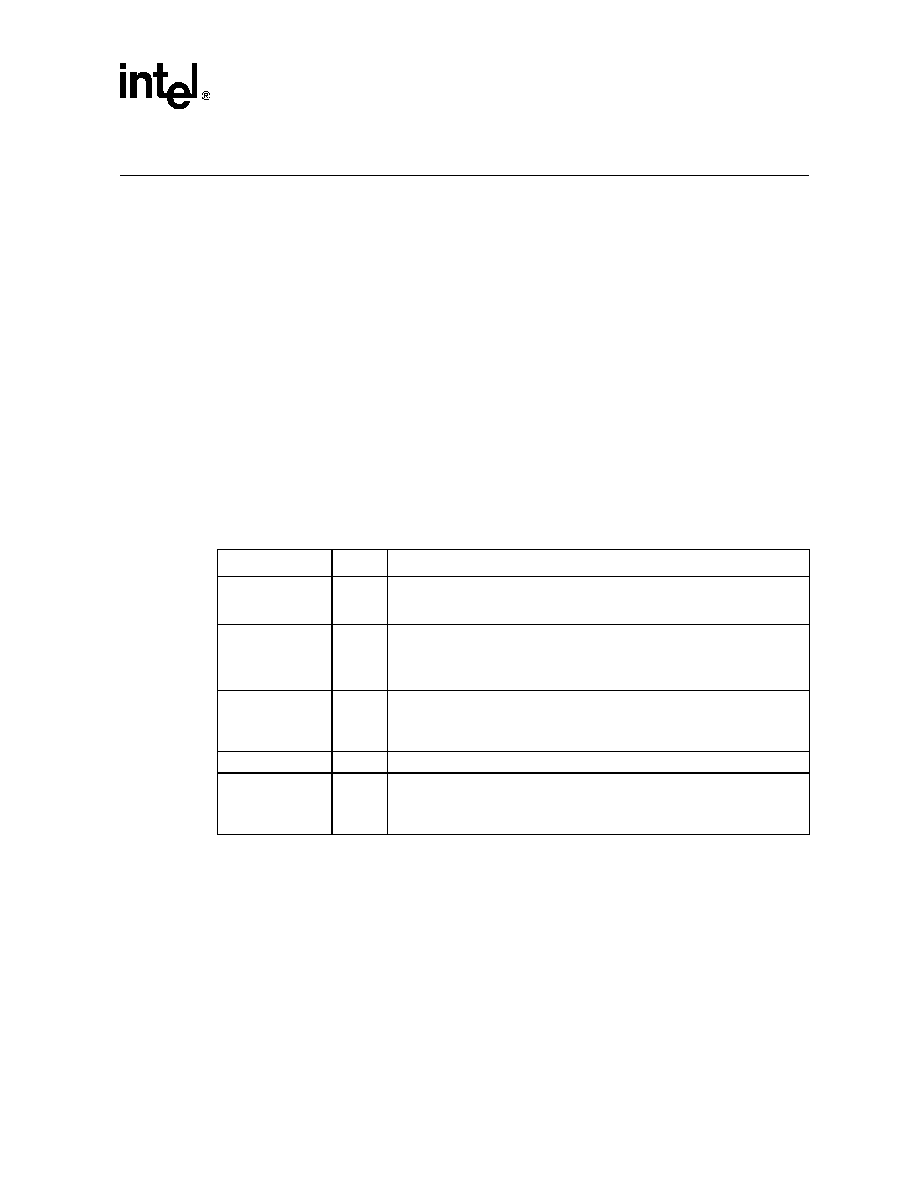

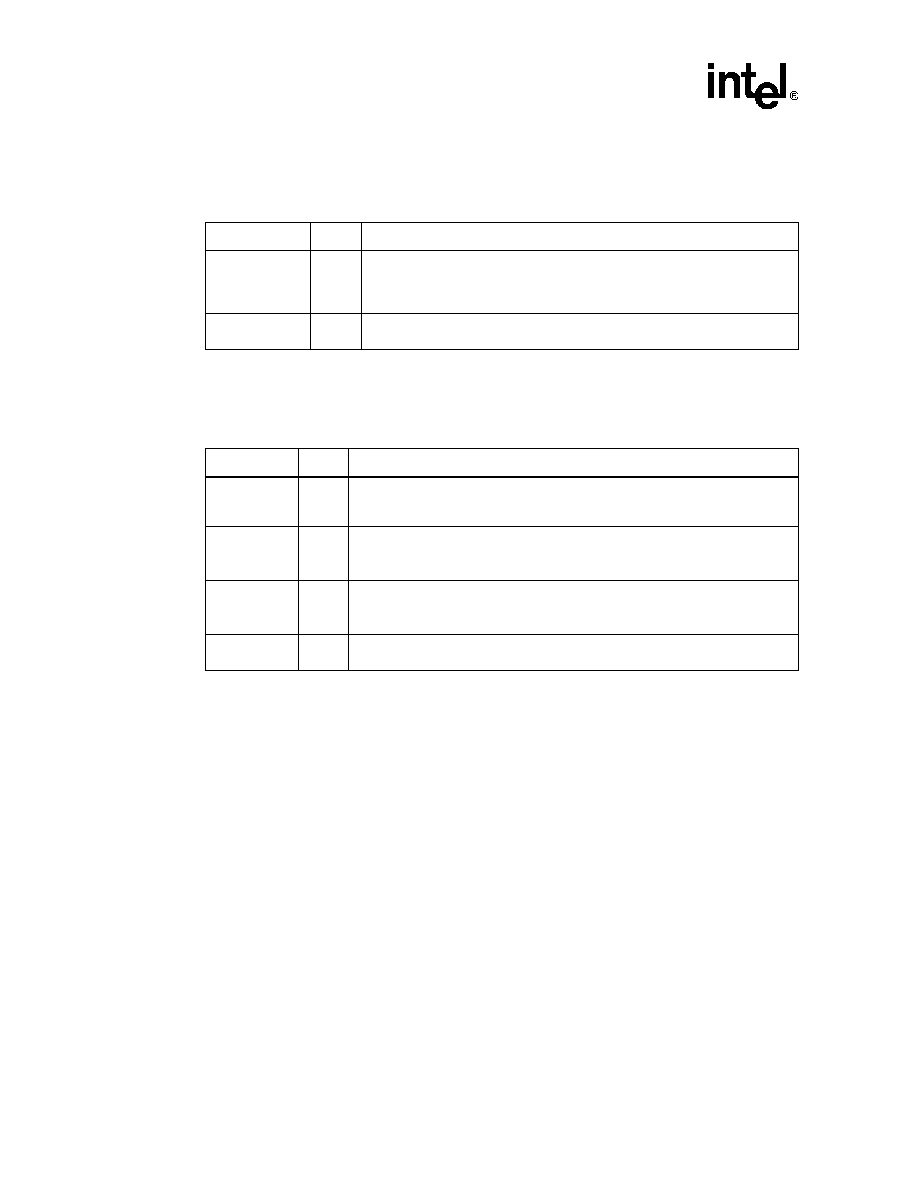

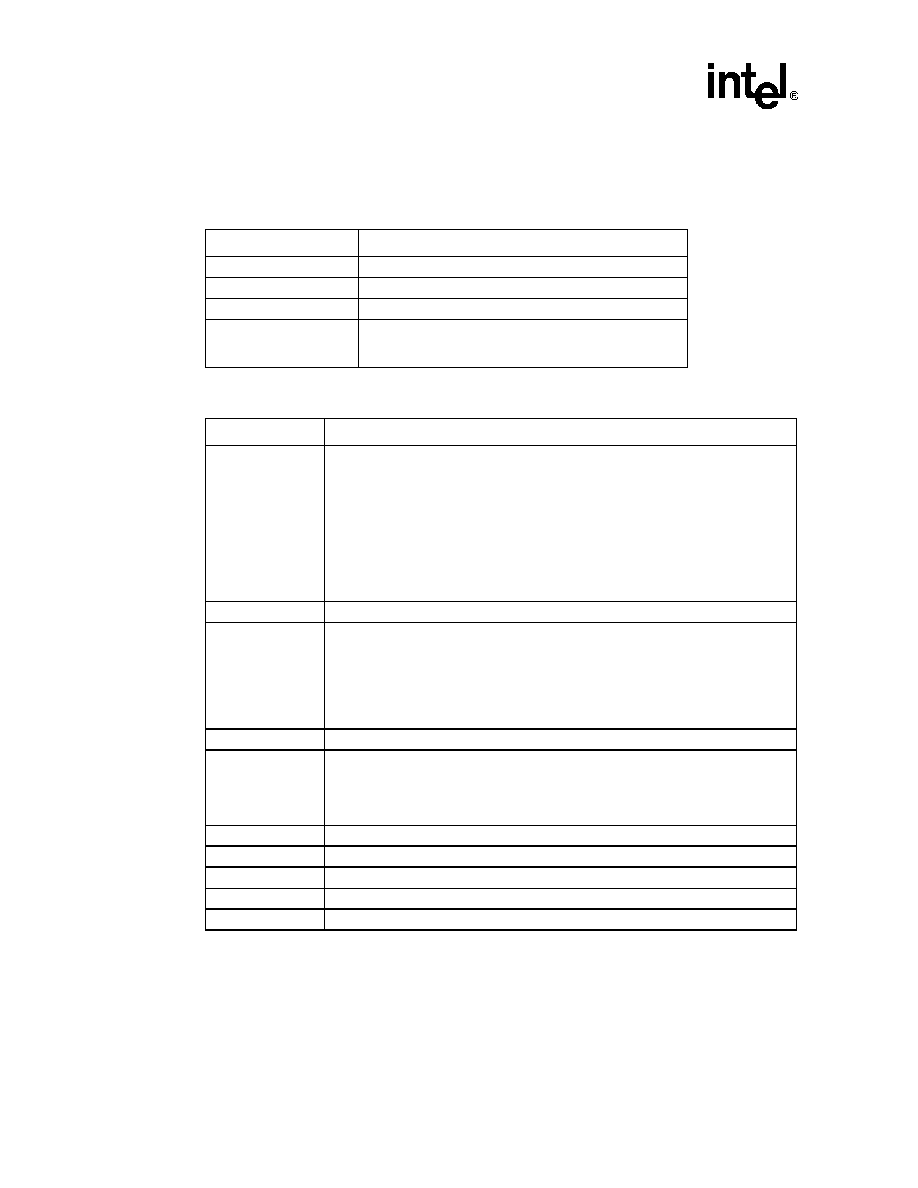

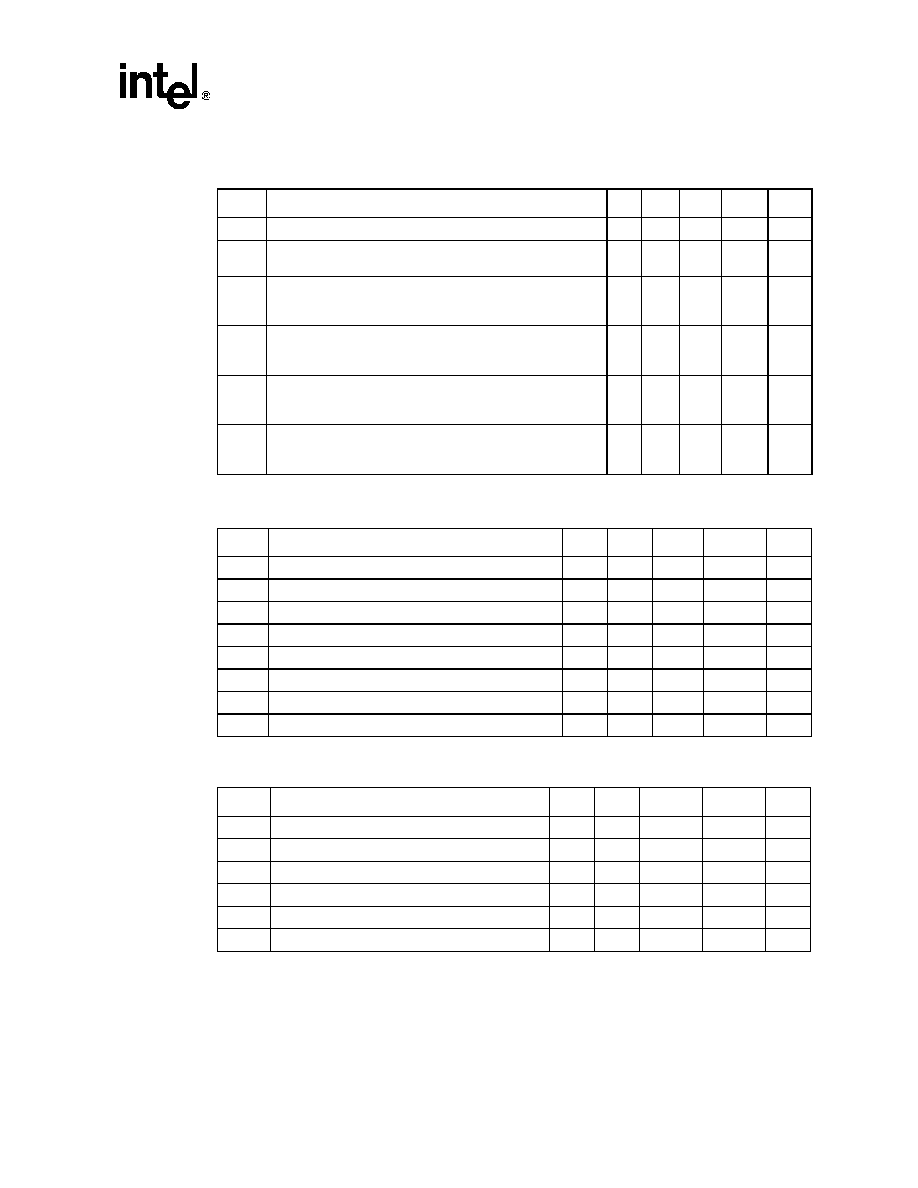

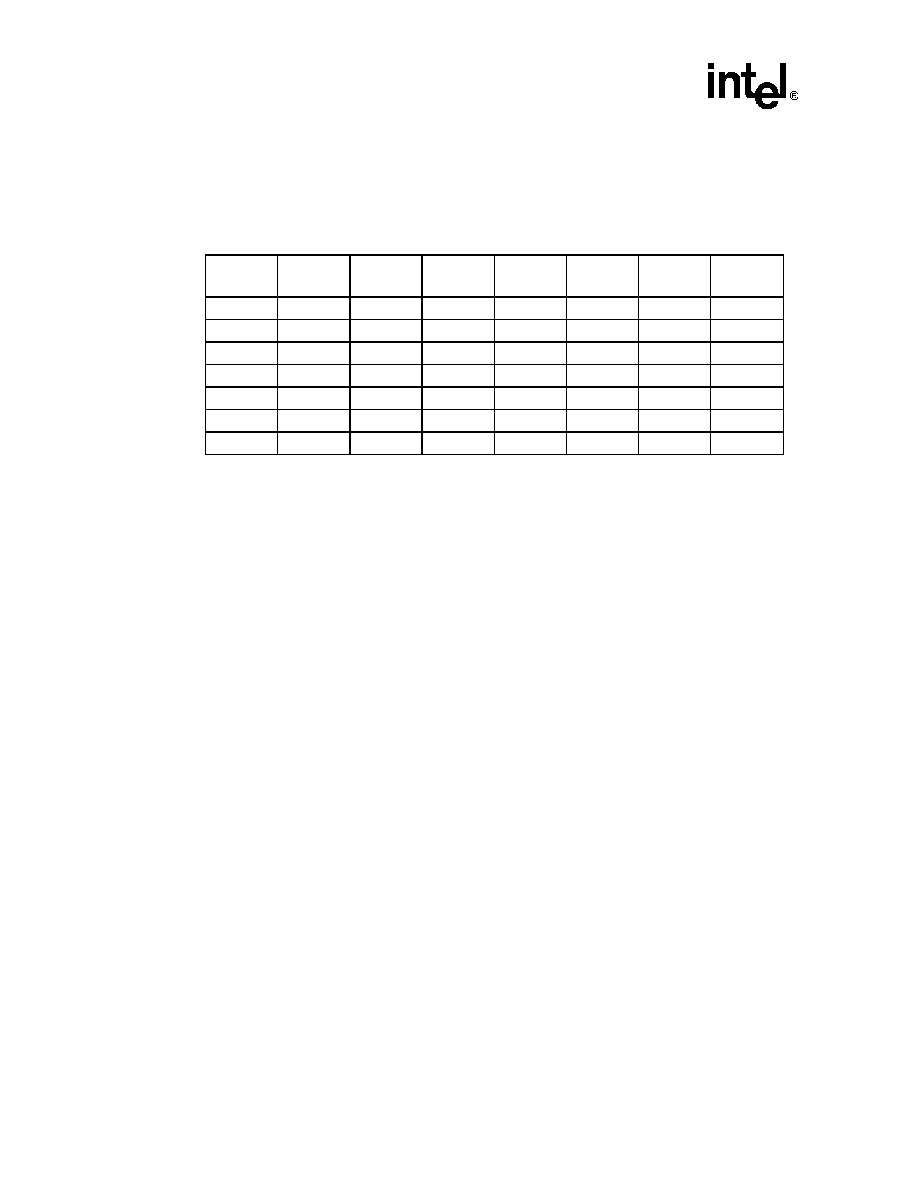

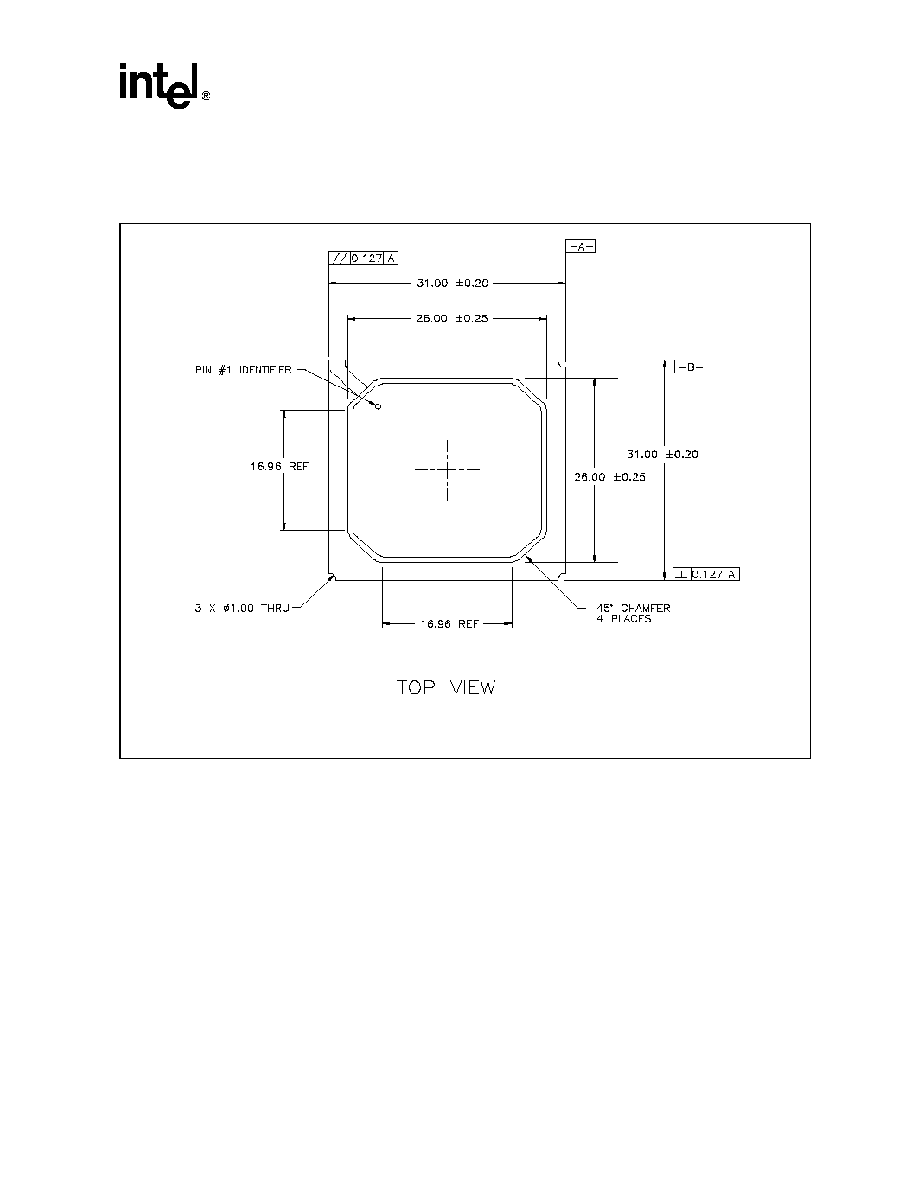

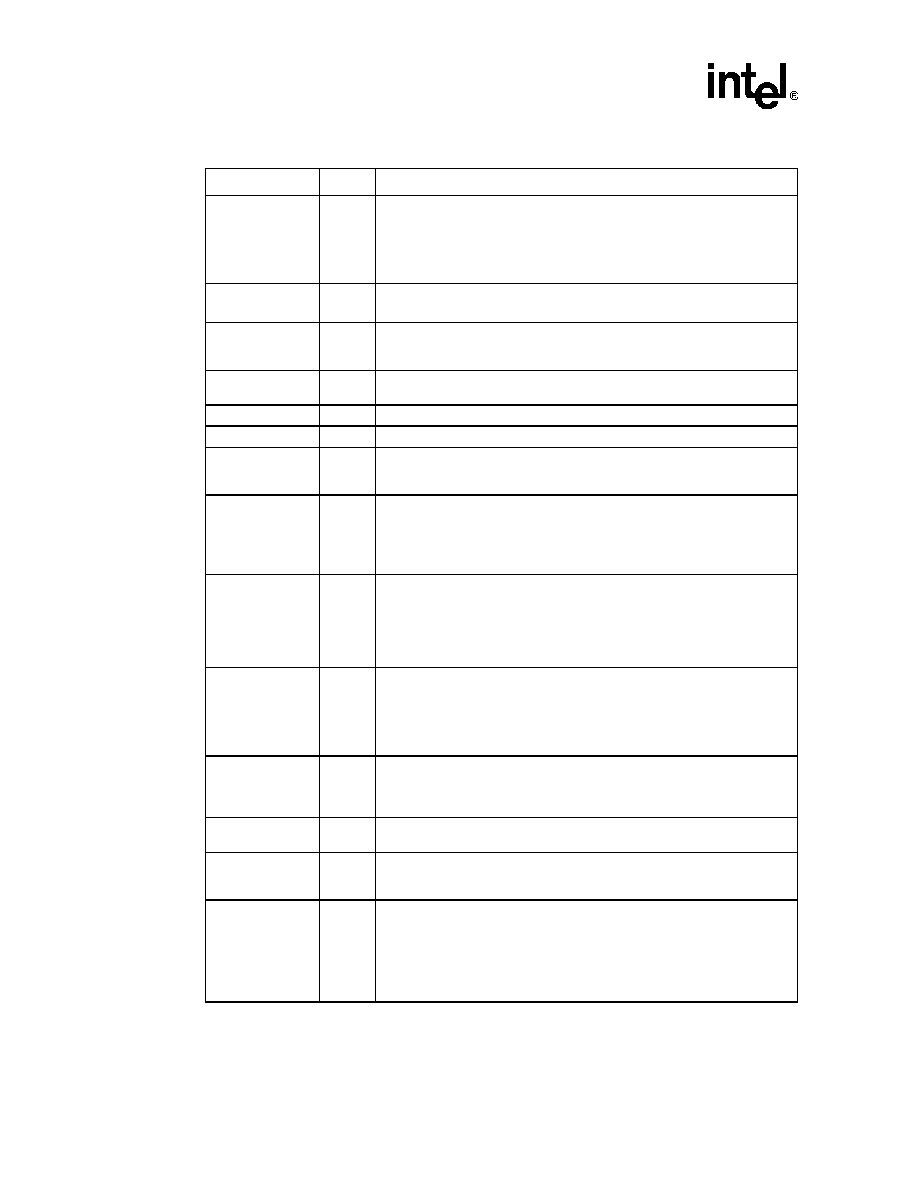

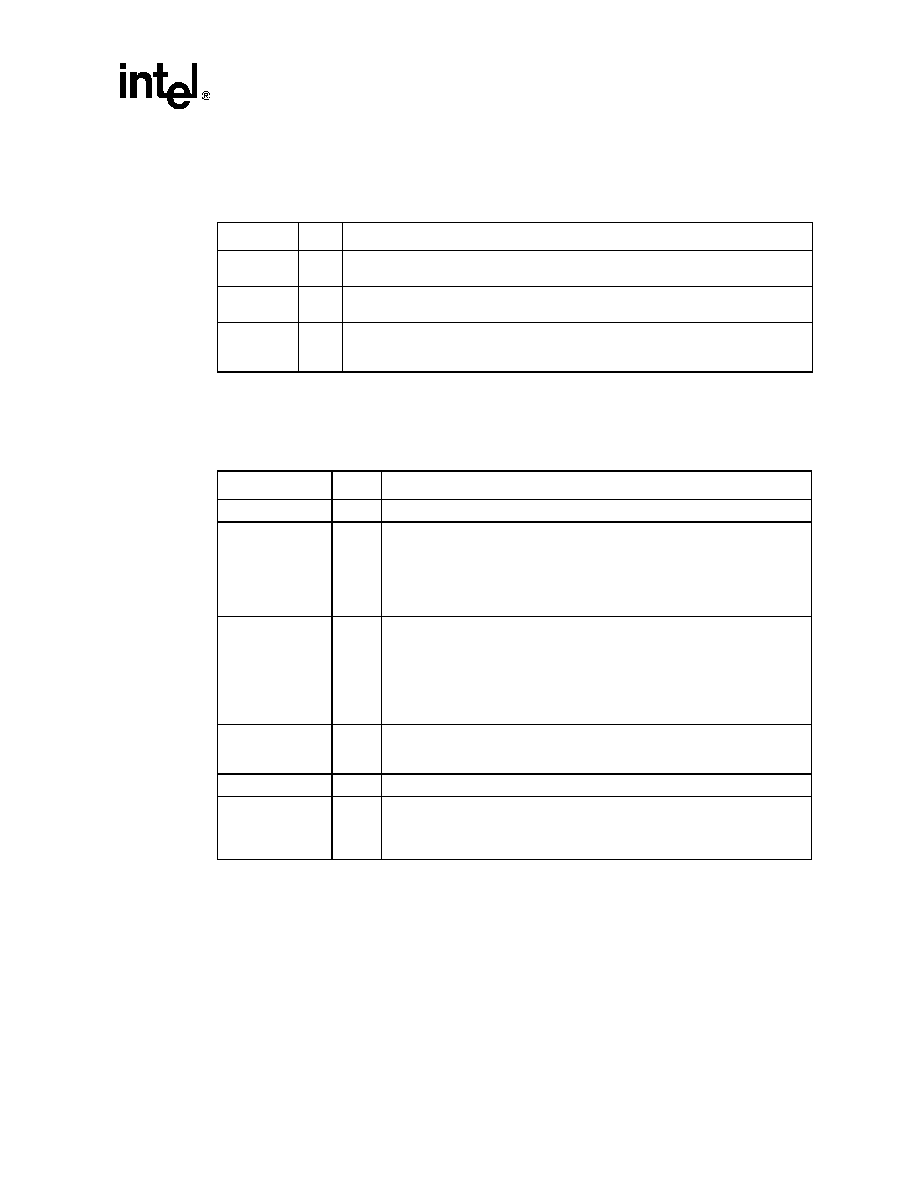

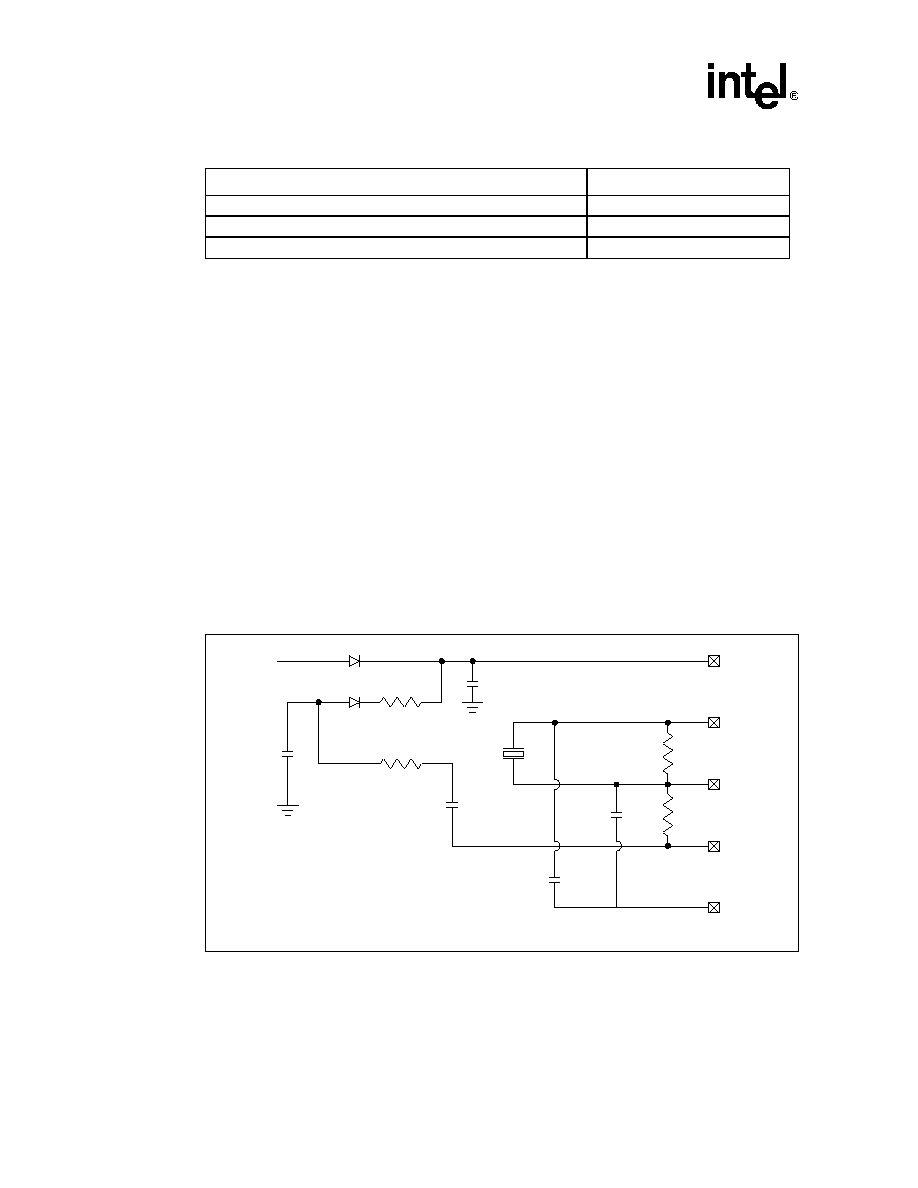

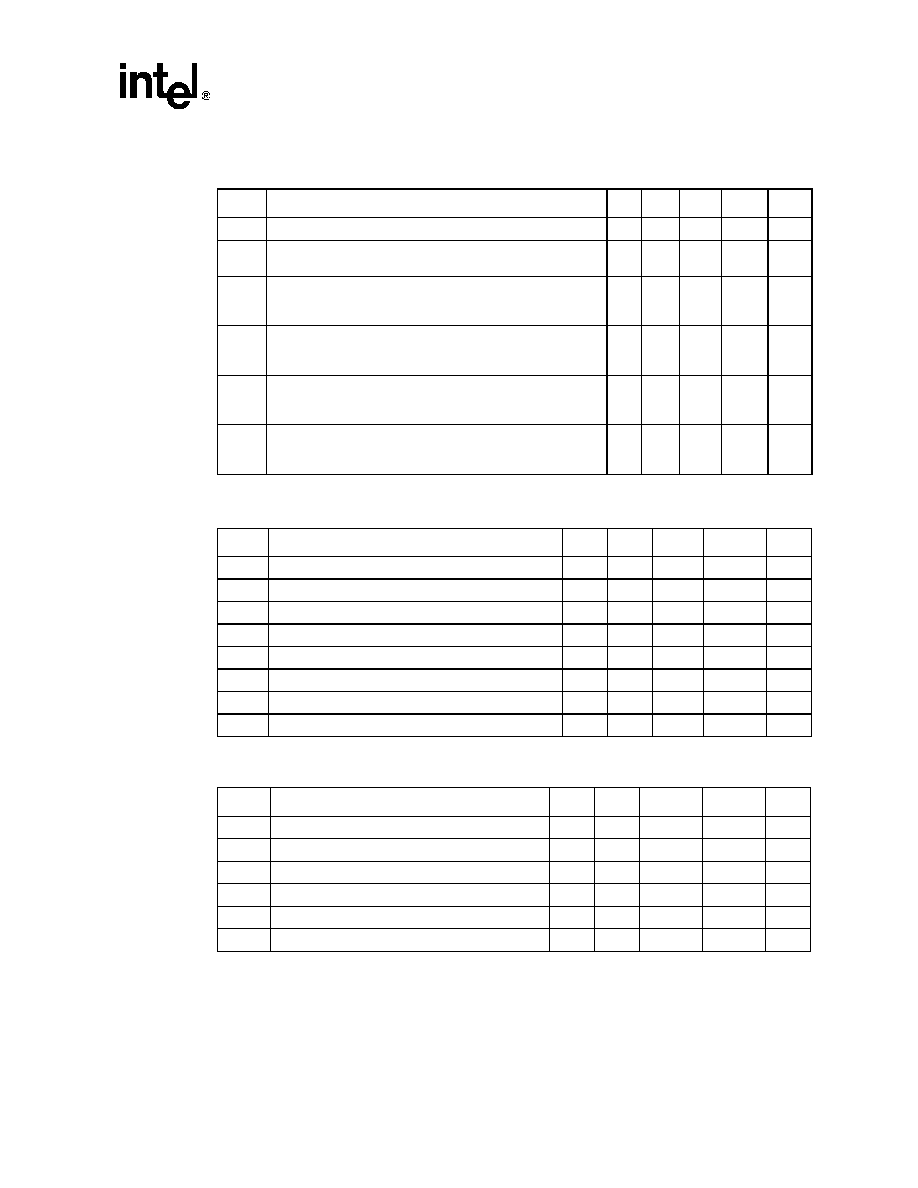

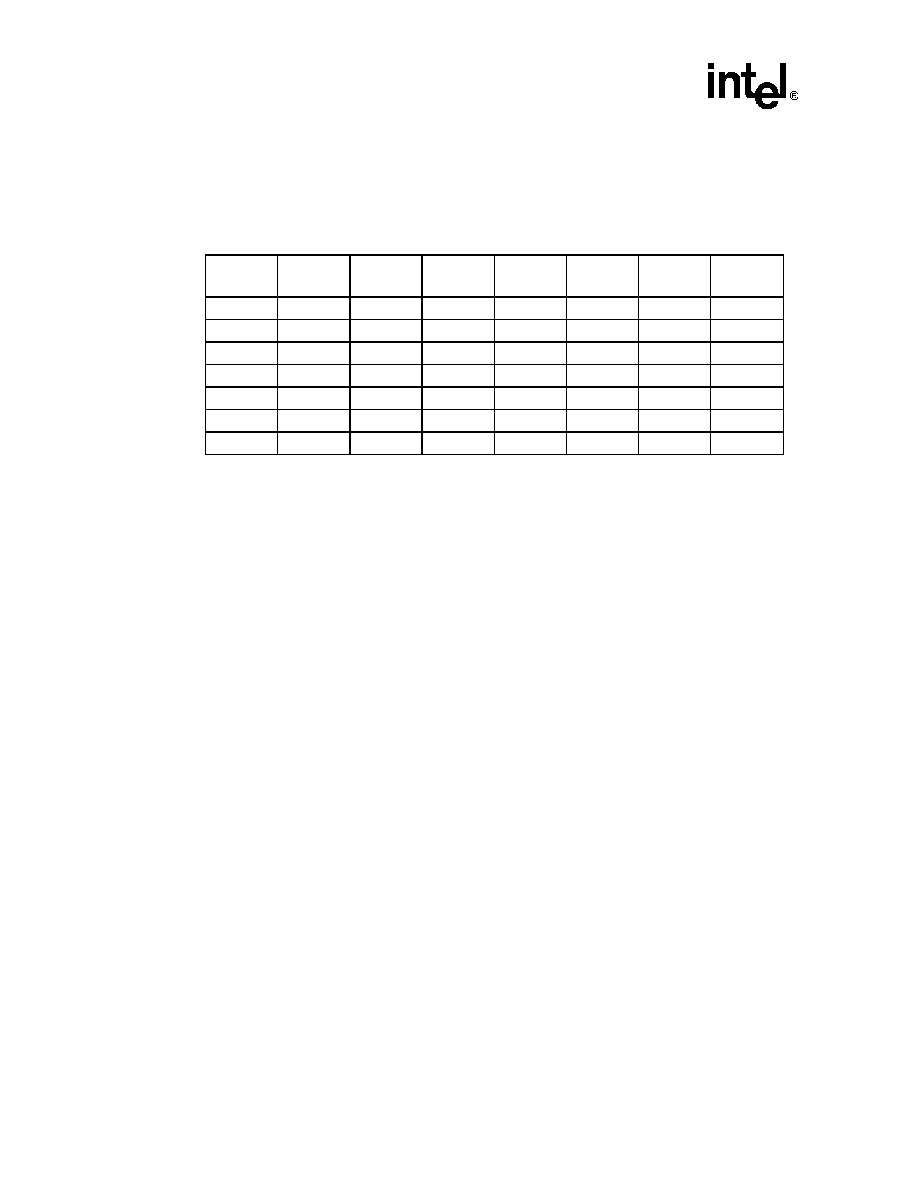

2.2

Mechanical Specifications

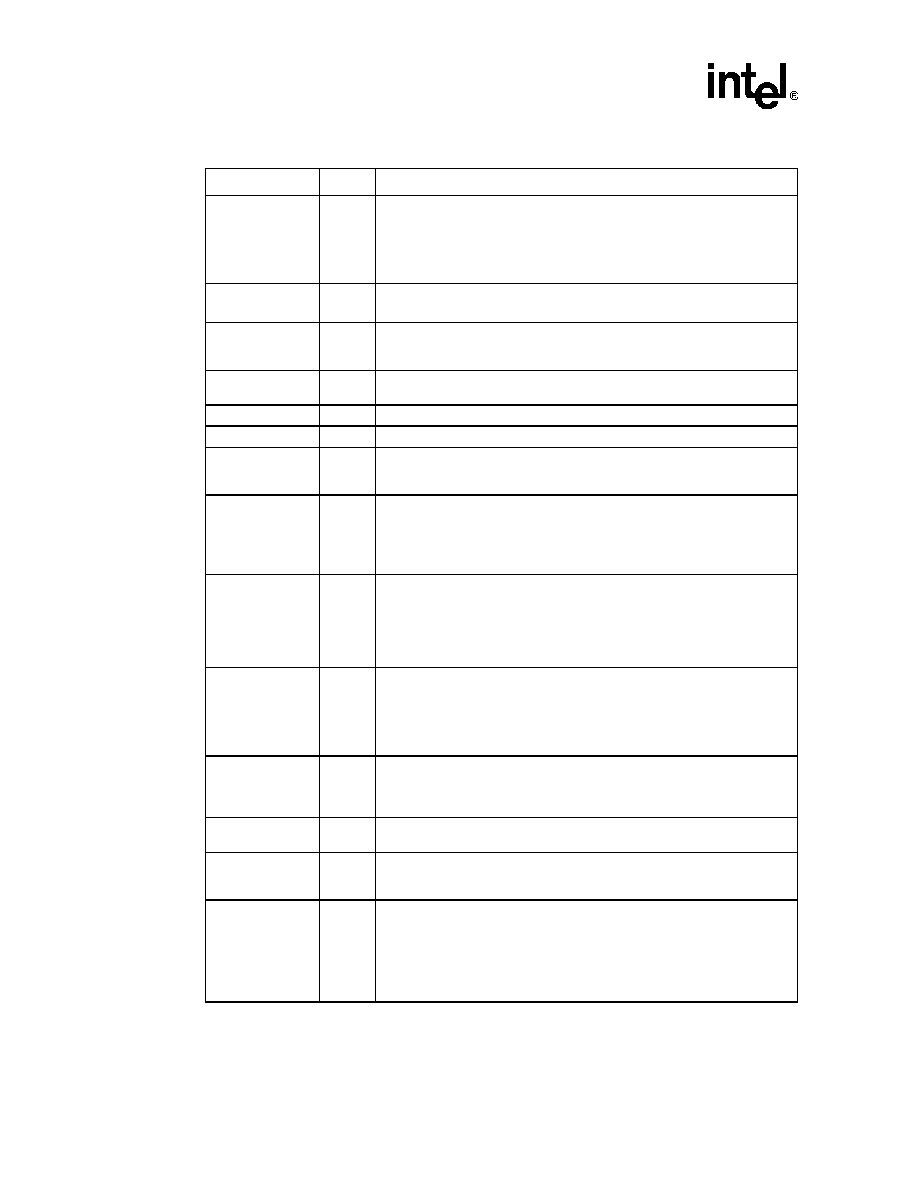

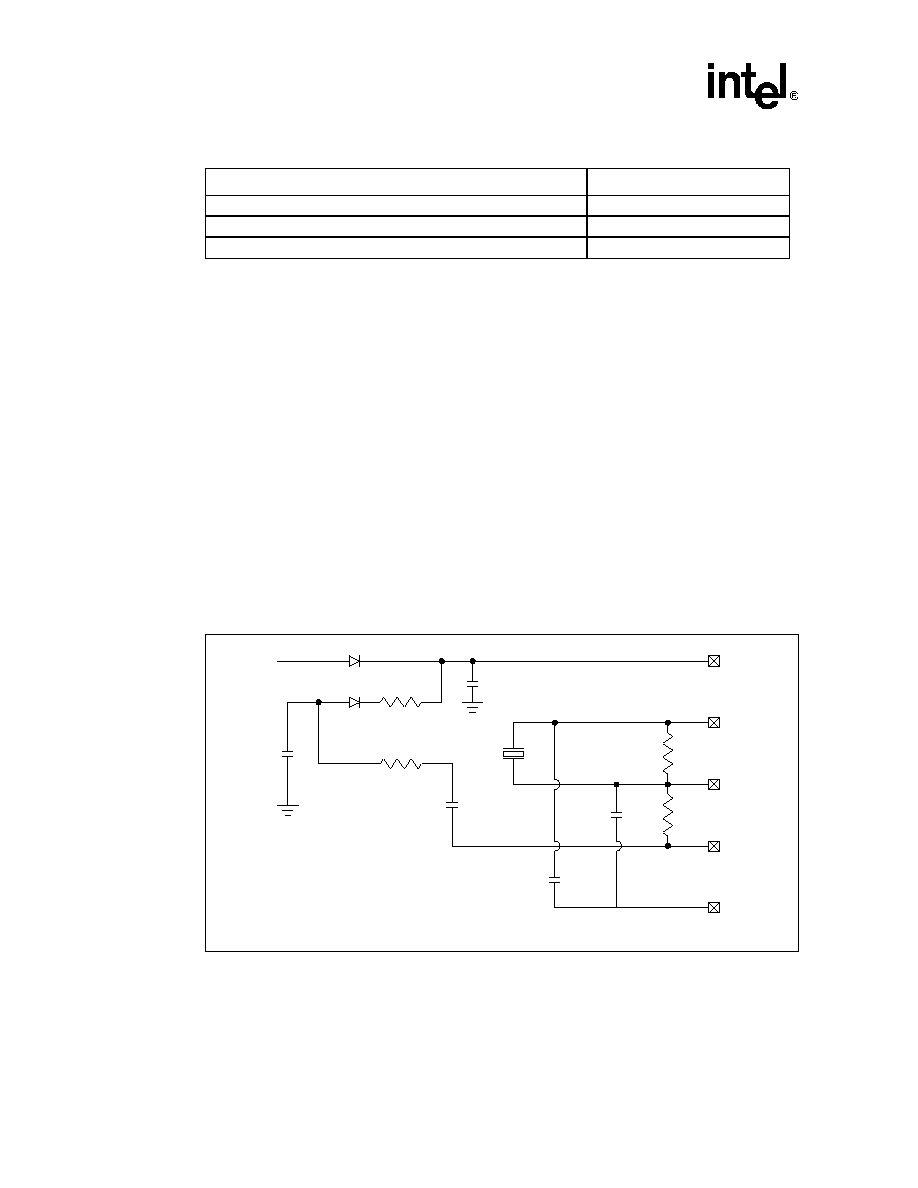

Figure 4. Intel

Æ

82801E C-ICH Package (Top View)

Notes:

1. All Dimensions and tolerances conform to ANSI Y14.5M - 1982

2. All Dimensions are in millimeters.

Intel

Æ

82801E C-ICH

24

Advance Information Datasheet

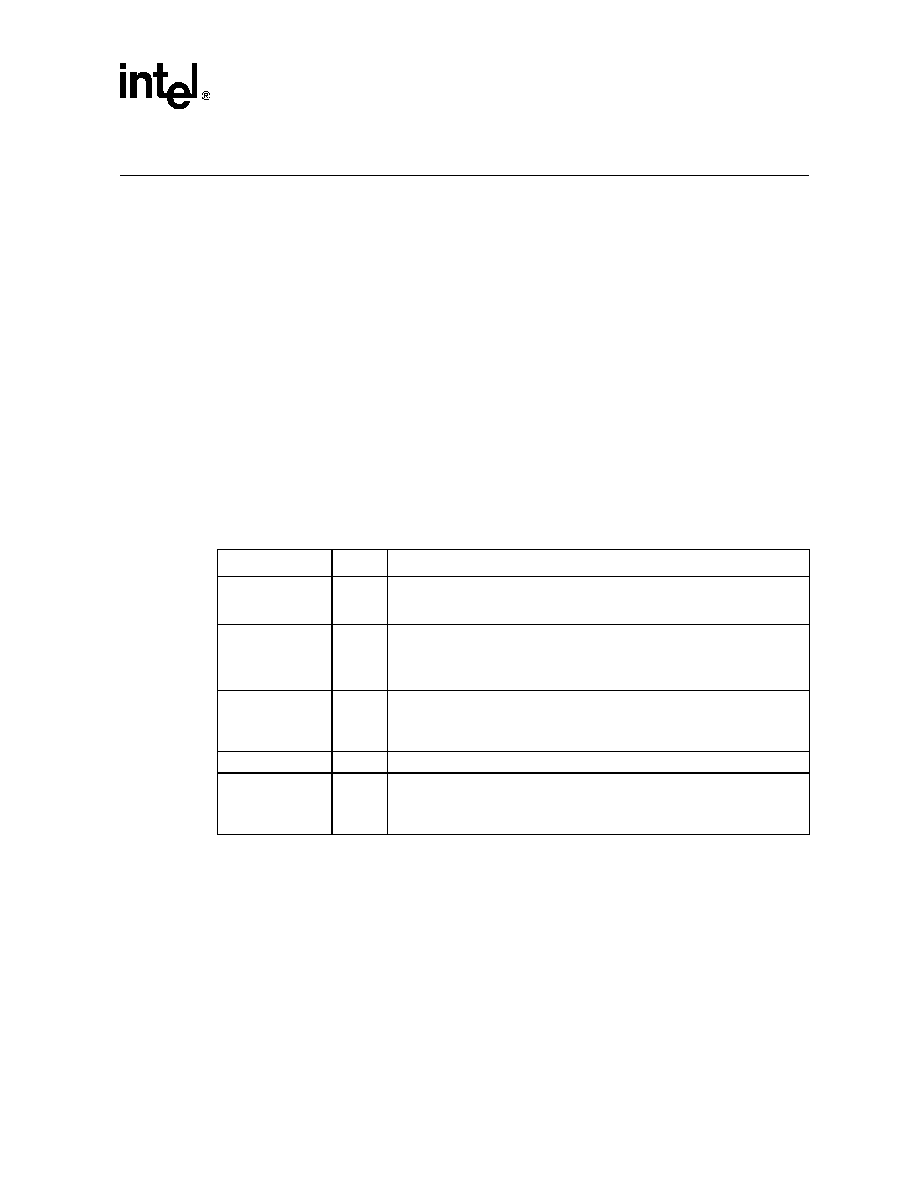

Figure 5. Intel

Æ

82801E C-ICH Package (Side View)

Figure 6. Intel

Æ

82801E C-ICH Package (Bottom View)

Notes:

1. All Dimensions and tolerances conform to ANSI Y14.5M - 1982

3. Primary datum -C- and seating plane are defined

2. All Dimensions are in millimeters.

by the spherical crowns of the solder balls.

Notes:

1. All Dimensions and tolerances conform to ANSI Y14.5M - 1982

3. All Dimensions are in millimeters.

2. Dimension is measured at the maximum solder ball diameter.

Parallel to Datum -C- on side view illustration.

Intel

Æ

82801E C-ICH

Advance Information Datasheet

25

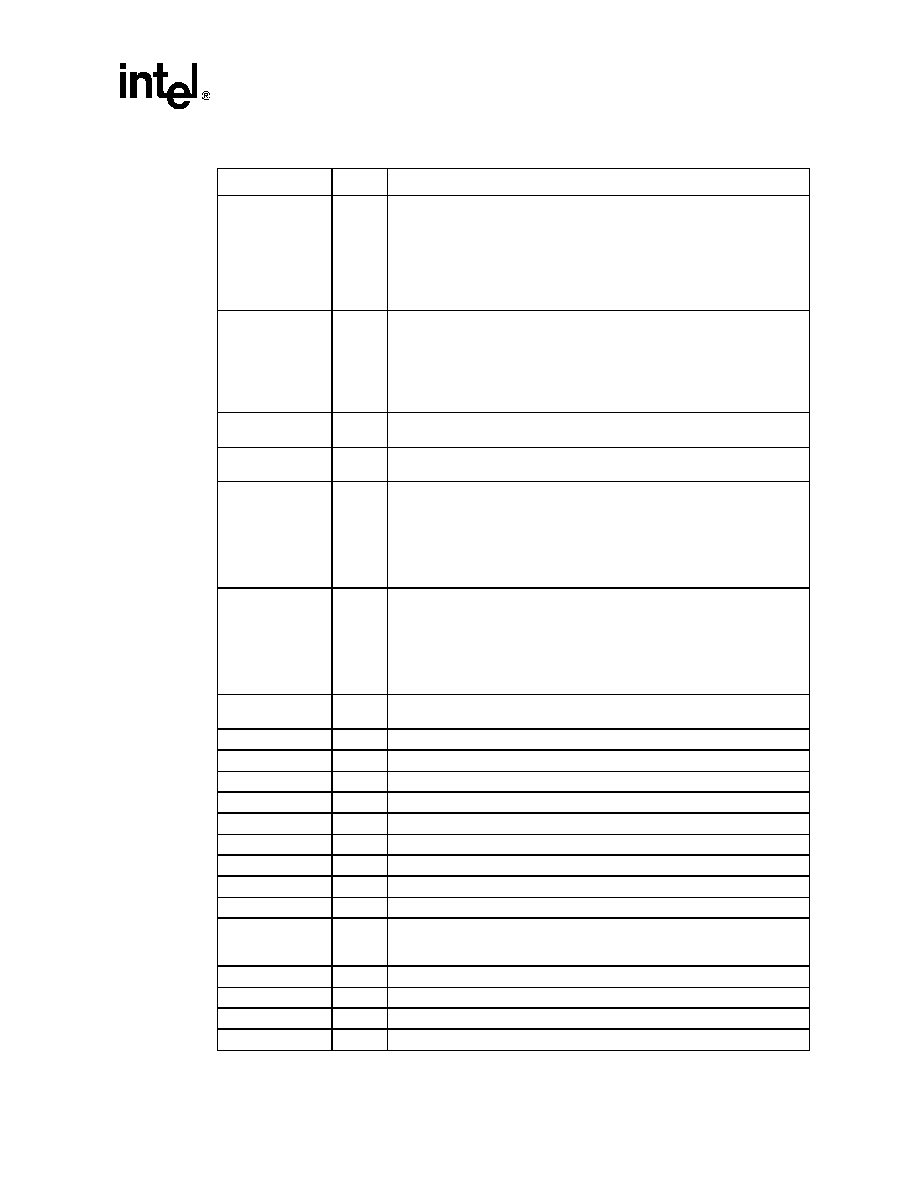

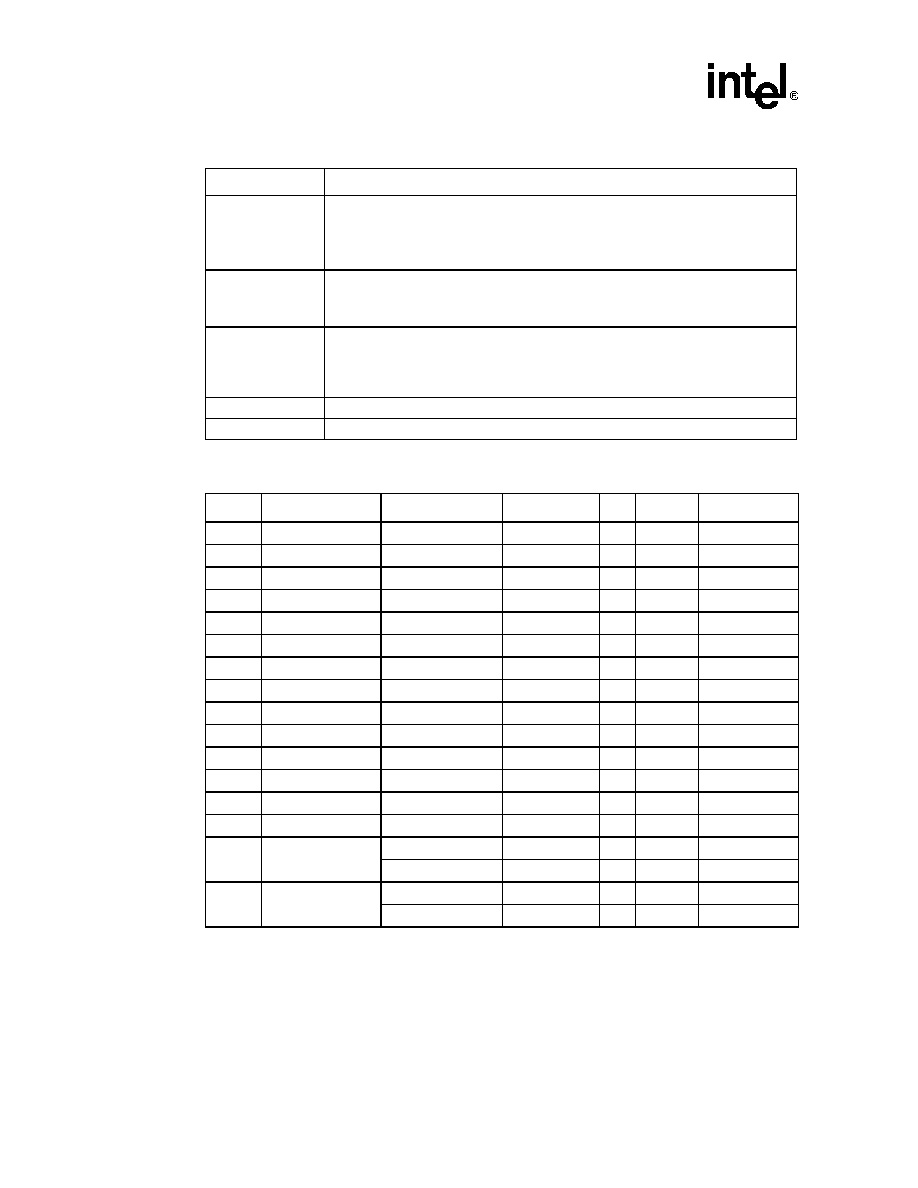

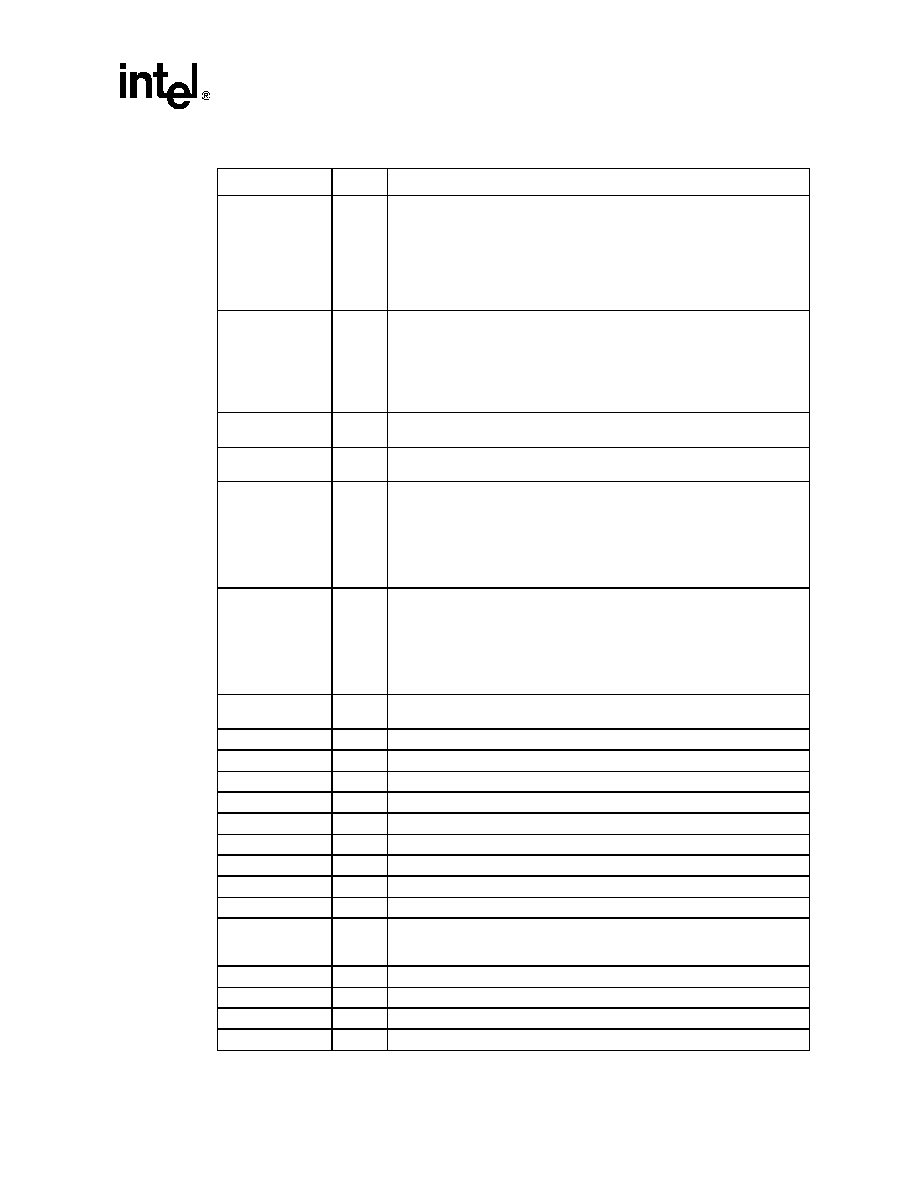

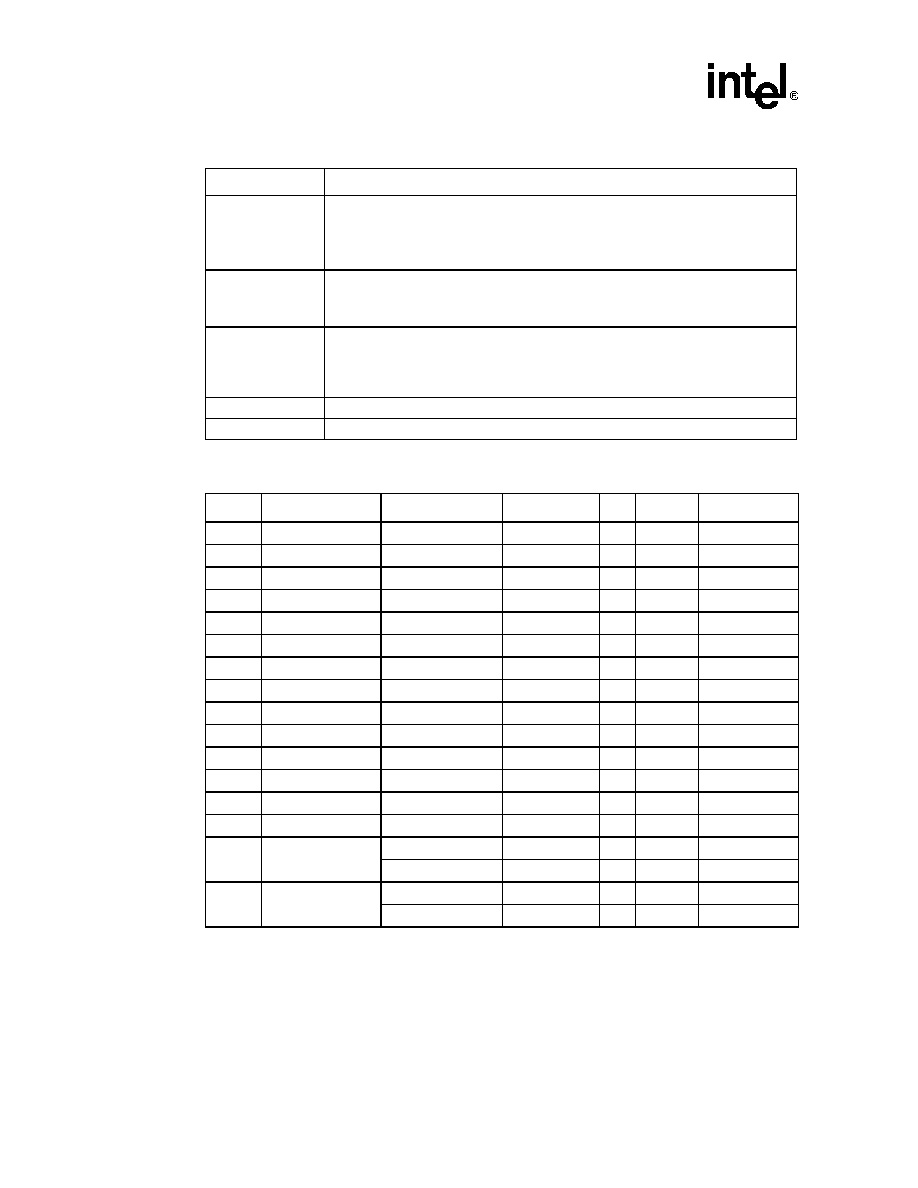

3.0

Signal Descriptions

This section provides a detailed description of each signal. The signals are arranged in functional

groups according to their associated interface.

The "#" symbol at the end of the signal name indicates that the active, or asserted state occurs when

the signal is at a low voltage level. When "#" is not present, the signal is asserted when at the high

voltage level.

The following notations are used to describe the signal type:

I

Input pin

O Output

pin

OD

Open drain output pin.

I/O

Bidirectional input/output pin.

3.1

Alphabetical Signal Reference

Table 6. 82801E C-ICH Signal Description (Sheet 1 of 11)

Signal

Type

Description

A20GATE

I

A20 Gate: This signal is from the keyboard controller. It acts as an alternative

method to force the A20M# signal active. A20GATE eliminates the need for

the external OR gate needed with various other PCIsets.

A20M#

O

Mask A20: A20M# goes active based on setting the appropriate bit in the

Port 92h register, or based on the A20GATE signal.

Speed Strap: During the reset sequence, 82801E C-ICH drives A20M# high

if the corresponding bit is set in the FREQ_STRP register.

AD[31:0]

I/O

PCI Address/Data: AD[31:0] is a multiplexed address and data bus. During

the first clock of a transaction, AD[31:0] contain a physical address (32 bits).

During subsequent clocks, AD[31:0] contain data. The 82801E C-ICH drives

all 0s on AD[31:0] during the address phase of all PCI Special Cycles.

APICCLK

I

APIC Clock: The APIC clock runs at 33.333 MHz.

APICD[1:0]

I/OD

APIC Data: These bidirectional open drain signals are used to send and

receive data over the APIC bus. As inputs, the data is valid on the rising edge

of APICCLK. As outputs, new data is driven from the rising edge of the

APICCLK.

Intel

Æ

82801E C-ICH

26

Advance Information Datasheet

C/BE[3:0]#

I/O

Bus Command and Byte Enables: The command and byte enable signals

are multiplexed on the same PCI pins. During the address phase of a

transaction, C/BE[3:0]# define the bus command. During the data phase,

C/BE[3:0]# define the Byte Enables.

C/BE[3:0]#

Command Type

0000

Interrupt Acknowledge

0001

Special Cycle

0010

I/O Read

0011

I/O Write

0110

Memory Read

0111

Memory Write

1010

Configuration Read

1011

Configuration Write

1100

Memory Read Multiple

1101

DAC Mode Address to be latched (target only)

1110

Memory Read Line

1111

Memory Write and Invalidate

All command encodings not shown are reserved. The 82801E C-ICH does

not decode reserved values, and therefore will not respond when a PCI

master generates a cycle using one of the reserved values.

As a target, the 82801E C-ICH can support DAC mode addressing for 44 bits.

CLK14

I

Oscillator Clock: CLK14 is used for 8254 timers and runs at 14.31818 MHz.

CLK48

I

48 MHz Clock: CLK48 is used to for the USB controller and runs at 48 MHz.

CLK66

(HLCLK)

I

66 MHz Clock (HLCLK): CLK66 is used for the hub interface and runs at

66 MHz.

CPUPWRGD

OD

Processor Power Good: This signal should be connected to the processor's

PWRGOOD input. This is an open-drain output signal (external pull-up

resistor required) that represents a logical AND of the 82801E C-ICH's

PWROK and VRMPWRGD signals.

CPUSLP#

O

Processor Sleep: This signal puts the processor into a state that saves

substantial power compared to Stop-Grant state. However, during that time,

no snoops occur.

NOTE: The 82801E C-ICH does not support Sleep states. This signal must

be pulled up through an 8.2 K

resistor to 3.3 V.

DEVSEL#

I/O

Device Select: The 82801E C-ICH asserts DEVSEL# to claim a PCI

transaction. As an output, the 82801E C-ICH asserts DEVSEL# when a PCI

master peripheral attempts an access to an internal 82801E C-ICH address

or an address destined for the hub interface (main memory or AGP). As an

input, DEVSEL# indicates the response to an 82801E C-ICH-initiated

transaction on the PCI bus. DEVSEL# is tri-stated from the leading edge of

PCIRST#. DEVSEL# remains tri-stated by the 82801E C-ICH until driven by a

target device.

EE0_CS

EE1_CS

O

EEPROM Chip Select: These signals are chip-select signals to the

EEPROMs.

EE0_DIN

EE1_DIN

I

EEPROM Data In: These signals transfer data from the EEPROMs to the

82801E C-ICH. These signals have an integrated pull-up resistor.

EE0_DOUT

EE1_DOUT

O

EEPROM Data Out: These signals transfer data from the 82801E C-ICH to

the EEPROMs.

EE0_SHCLK

EE1_SHCLK

O

EEPROM Shift Clock: These signals are the serial shift clock output to the

EEPROMs.

Table 6. 82801E C-ICH Signal Description (Sheet 2 of 11)

Signal

Type

Description

Intel

Æ

82801E C-ICH

Advance Information Datasheet

27

FERR#

I

Numeric Coprocessor Error: This signal is tied to the coprocessor error

signal on the processor. FERR# is only used if the 82801E C-ICH

coprocessor error reporting function is enabled in the General Control

Register (Device 31:Function 0, Offset D0, bit 13). If FERR# is asserted, the

82801E C-ICH generates an internal IRQ13 to its interrupt controller unit. It is

also used to gate the IGNNE# signal to ensure that IGNNE# is not asserted to

the processor unless FERR# is active. FERR# requires an external weak

pull-up to ensure a high level when the coprocessor error function is disabled.

FRAME#

I/O

Cycle Frame: The current Initiator asserts FRAME# to indicate the beginning

and duration of a PCI transaction. While the initiator asserts FRAME#, data

transfers continue. When the initiator deasserts FRAME#, the transaction is in

the final data phase. FRAME# is an input to the 82801E C-ICH when the

82801E C-ICH is the target, and FRAME# is an output from the 82801E

C-ICH when the 82801E C-ICH is the Initiator. FRAME# remains tri-stated by

the 82801E C-ICH until driven by an Initiator.

FWH[3:0]

/LAD[3:0]

I/O

Firmware Hub Signals: These signals are muxed with LPC address signals.

FWH[4]

/LFRAME#

I/O

Firmware Hub Signals: This signal is muxed with the LPC LFRAME# signal.

GNT[3:0]#

GNT[5]#

/GNT[B]#

/GPIO[17]#

O

PCI Grants: The 82801E C-ICH supports up to four masters on the PCI bus.

GNT[5]# is muxed with PC/PCI GNT[B]# (must choose one or the other, but

not both). If not needed for PCI or PC/PCI, GNT[5]# can instead be used as a

GPIO.

Pull-up resistors are not required on these signals. If pullups are used, they

should be tied to the Vcc3_3 power rail. GNT[B]#/GNT[5]#/GPIO[17] has an

internal pull-up.

GNT[A]#

/GPIO[16]

/GNT[B]#

/GNT[5]#

/GPIO[17]

O

PC/PCI DMA Acknowledges [A:B]: This grant serializes an ISA-like DACK#

for the purpose of running DMA/ISA master cycles over the PCI bus. This is

used by devices such as PCI-based Super I/O or audio codecs which need to

perform legacy 8237 DMA but have no ISA bus.

When not used for PC/PCI, these signals can be used as General Purpose

Outputs. GNTB# can also be used as the fourth PCI bus master grant output.

These signal have internal pull-up resistors.

GPIO[1:0]

I

Fixed as Input only. Main Power Well. Can instead be used for PC/PCI

REQ[A:B]#. GPIO[1] can also alternatively be used for PCI REQ[5]#.

GPIO[3:2]

Not implemented.

GPIO[5:4]

I

Fixed as Input only. Main power well. Can be used instead as PIRQ[G:H]#.

GPIO[6]

I

Fixed as Input only. Main power well.

GPIO[7]

I

Fixed as Input only. Main power well. Not muxed.

GPIO[8]

I

Fixed as Input only. Main power well. Not muxed.

GPIO[10:9]

I

Not implemented.

GPIO[11]

I

Fixed as Input only. Main power well. Can instead be used for SMBALERT#.

GPIO[13:12]

I

Fixed as Input only. Main power well. Not muxed.

GPIO[15:14]

I

Not implemented.

GPIO[17:16]

O

Fixed as Output only. Main Power Well. Can instead be used for PC/PCI

GNT[A:B]#. GPIO[17] can also alternatively be used for PCI GNT[5]#.

Integrated pull-up resistor.

GPIO[20:18]

O

Fixed as Output only. Main power well.

GPIO[21]

O

Fixed as Output only. Main power well.

GPIO[22]

OD

Fixed as Output only. Main power well. Open-drain output.

GPIO[23]

O

Fixed as Output only. Main power well.

Table 6. 82801E C-ICH Signal Description (Sheet 3 of 11)

Signal

Type

Description

Intel

Æ

82801E C-ICH

28

Advance Information Datasheet

GPIO[24]

I/O

Can be input or output. Main power well.

GPIO[25]

I/O

Can be input or output. Main power well. Not Muxed.

GPIO[26]

I/O

Not implemented.

GPIO[28:27]

I/O

Can be input or output. Main power well. Unmuxed.

GPIO[31:29]

O

Not implemented.

HL[11:0]

I/O

Hub Interface Signals

HL_STB

I/O

Hub Interface Strobe: One of two differential strobe signals used to transmit

and receive data through the hub interface.

HL_STB#

I/O

Hub Interface Strobe Complement: Second of the two differential strobe

signals.

HLCOMP

I/O

Hub Interface Compensation: Used for hub interface buffer compensation.

HUBREF

0.9 V reference for the hub interface.

IGNNE#

O

Ignore Numeric Error: This signal is connected to the ignore error pin on the

processor. IGNNE# is only used if the 82801E C-ICH coprocessor error

reporting function is enabled in the General Control Register (Device

31:Function 0, Offset D0, bit 13). When FERR# is active, indicating a

coprocessor error, a write to the Coprocessor Error Register (F0h) causes the

IGNNE# to be asserted. IGNNE# remains asserted until FERR# is negated. If

FERR# is not asserted when the Coprocessor Error Register is written, the

IGNNE# signal is not asserted.

Speed Strap: During the reset sequence, 82801E C-ICH drives IGNNE# high

if the corresponding bit is set in the FREQ_STRP register.

INIT#

O

Initialization: INIT# is asserted by the 82801E C-ICH for 16 PCI clocks to

reset the processor. 82801E C-ICH can be configured to support processor

BIST. In that case, INIT# will be active when PCIRST# is active.

INTR

O

Processor Interrupt: INTR is asserted by the 82801E C-ICH to signal the

processor that an interrupt request is pending and needs to be serviced. It is

an asynchronous output and normally driven low.

Speed Strap: During the reset sequence, 82801E C-ICH drives INTR high if

the corresponding bit is set in the FREQ_STRP register.

INTRUDER#

I

Intruder Detect: This signal can be set to disable system if box detected

open. This signal's status is readable, so it can be used like a GPI if the

Intruder Detection is not needed.

IRDY#

I/O

Initiator Ready: IRDY# indicates the 82801E C-ICH's ability, as an Initiator,