| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: E8870SP | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Intel

Æ

E8870SP Scalability Port Switch

(SPS) Datasheet

Product Features

s

Scalability Port (SP):

-- Six SPs with 3.2 GB/s peak bandwidth

per direction per SP.

-- Bi-directional SPs for a total bandwidth

of 38.4 GB/s.

s

Integrated Snoop Filter:

-- 1 MB 12-way set associative tag array

capable of maintaining state of 200K

cache lines.

-- Partitioned into four interleaves, each

interleave can be accessed in parallel.

-- Supports up to 266M look-up and

update (LUU) operations per second.

-- Pseudo Least Recently Used (PLRU)

replacement algorithm, with updates on

look-ups and invalidates.

-- ECC coverage, with correction of

single bit errors, detection of double bit

errors.

-- Fast array initialization and/or self test

through configuration register access.

s

Multiple Processor Node Support:

-- Conflict detection logic to maintain

memory consistency for coherent

memory across multiple processor

nodes.

-- Advanced address mapping and decode

capabilities enable flexible routing of

transactions based on address and/or

transaction type.

s

Internal Interconnect:

-- A six-ported dual lane crossbar network

routes transaction packets from one SP

port to another.

-- Separate bypass buses for low latency

snoop look-up and response connection

between ports and interleaves.

s

System Management Bus (SMBus) 2.0

slave interface for server management with

packet error checking.

s

Reliability, Availability, and Serviceability

(RAS):

-- Sideband access to configuration

registers via SMBus or JTAG.

-- End-to-end ECC for all interfaces.

-- Fault detection and logging.

-- Signal connectivity testing via

boundary scan.

s

Packaging:

-- 42.5 mm x 42.5 mm.

-- 1012-pin organic LAN grid array

(OLGA) package-2B.

Document Number: 252034-001

November 2002

ii

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL

Æ

PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY

ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN

INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS

ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES

RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER

INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Itanium 2 processor, E8870 chipset, and E8870SP scalability port switch (SPS) may contain design defects or errors known as errata which may

cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling1-800-548-

4725, or by visiting Intel's website at http://www.intel.com.

Intel and Itanium are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Copyright © 2002, Intel Corporation. All rights reserved.

*Other names and brands may be claimed as the property of others.

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

iii

Contents

1

Introduction......................................................................................................................1-1

1.1

Overview ............................................................................................................1-1

1.2

Feature Summary...............................................................................................1-1

1.2.1

Interfaces...............................................................................................1-1

1.2.2

Multinode Routing, Cache Coherency, and Memory Consistency ........1-1

1.2.3

Reliability and Serviceability..................................................................1-1

1.3

SPS Blocks.........................................................................................................1-2

1.3.1

Interleaves.............................................................................................1-2

1.3.2

Ports ......................................................................................................1-3

1.3.3

Interconnect...........................................................................................1-3

1.4

Reference Documents........................................................................................1-3

1.5

Revision History .................................................................................................1-4

2

Signal Descriptions..........................................................................................................2-1

2.1

Conventions .......................................................................................................2-1

2.2

SPS Pin List .......................................................................................................2-2

3

Configuration Registers...................................................................................................3-1

3.1

Access Mechanism ............................................................................................3-1

3.1.1

Conflict Resolution ................................................................................3-1

3.2

Device Mapping..................................................................................................3-1

3.2.1

Assignment of Device Number ..............................................................3-1

3.2.2

Device Mapping Table...........................................................................3-2

3.3

Register Attributes..............................................................................................3-2

3.3.1

SMBus-Initiated Register Access ..........................................................3-3

3.4

SPS Configuration Register Definitions..............................................................3-3

3.5

SPS PCI Standard Configuration Registers ≠ All Functions ..............................3-3

3.5.1

VID: Vendor Identification Register .......................................................3-3

3.5.2

DID: Device Identification Register........................................................3-3

3.5.3

RID: Revision ID Register .....................................................................3-4

3.5.4

CCR: Class Code Register....................................................................3-4

3.5.5

HDR: Header Type Register .................................................................3-5

3.5.6

SVID: Subsystem Vendor Identification Register ..................................3-5

3.5.7

SDID: Subsystem Device Identification Register ..................................3-5

3.6

SP Port Configuration Register ≠ Functions 0:5.................................................3-5

3.6.1

CBC: Chip Boot Configuration...............................................................3-5

3.6.2

SPINCO: SP Interface Control ..............................................................3-7

3.6.3

RECSPPD: Recoverable Error Control Information of SPPD ...............3-9

3.6.4

RECSPL: Recoverable Error Control Information of SPL .....................3-9

3.6.5

REDSPL: Recoverable Error Data Log SPL .........................................3-9

3.6.6

MIR[5:0]: Memory Interleave Range Registers ...................................3-10

3.6.7

SIOH_MAP: SIOH Mapping Register ..................................................3-11

3.6.8

MMIOLS: Memory-Mapped I/O Low Segment Register ......................3-11

3.6.9

MMIOHS: Memory-Mapped I/O High Segment Register ....................3-11

3.6.10 SARS: SAPIC Range Segment Register ............................................3-12

3.6.11 IOPORTS: I/O Space Segment Address.............................................3-12

3.6.12 PSEG: PCI Configuration Bus Segment Address ...............................3-12

3.6.13 CB_PORT: Compatibility Bus Port Number ........................................3-13

iv

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

3.6.14 VGA_PORT: VGA Port Number..........................................................3-13

3.6.15 PMISC: Port Miscellaneous.................................................................3-13

3.7

SPS Global Registers ≠ Function 6 Only .........................................................3-14

3.7.1

FERRST[1:0]: First Error Status..........................................................3-14

3.7.2

SERRST[1:0]: Two or More Error Status ............................................3-16

3.7.3

ERRMASK[1:0]: ERRST MASK ..........................................................3-16

3.7.4

SPSGLB: SPS Global Register ...........................................................3-16

3.7.5

PERFCON: Performance Monitor Master Control...............................3-17

3.7.6

PMD[1:0]: Performance Monitor Data .................................................3-18

3.7.7

PCMP[1:0]: Performance Monitor Compare........................................3-18

3.7.8

PMR[1:0]: Performance Monitor Response.........................................3-18

3.8

Interleave Configuration Registers ≠ Functions 6 and 7 ..................................3-20

3.8.1

NRESPPC[1:0]: Non-recoverable Error Control Information

of SPPC ..............................................................................................3-21

3.8.2

RECSPPC[1:0]: Recoverable Error Control Information

of SPPC ..............................................................................................3-21

3.8.3

SYS_CFG[1:0]: System Configuration ................................................3-22

3.8.4

ERRCOM[1:0]: Error Command..........................................................3-22

3.8.5

NID_DEF[1:0]: Node ID Definition.......................................................3-23

3.8.6

REM_CDEF[1:0] Remote Component Definition ................................3-23

3.8.7

SFCMD: Snoop Filter Tag/LRU Array Command................................3-24

3.8.8

SFDATA: Snoop Filter Tag/LRU Array Data .......................................3-24

3.8.9

PME[1:0]: Performance Monitor Events ..............................................3-25

4

Address Mapping ............................................................................................................4-1

4.1

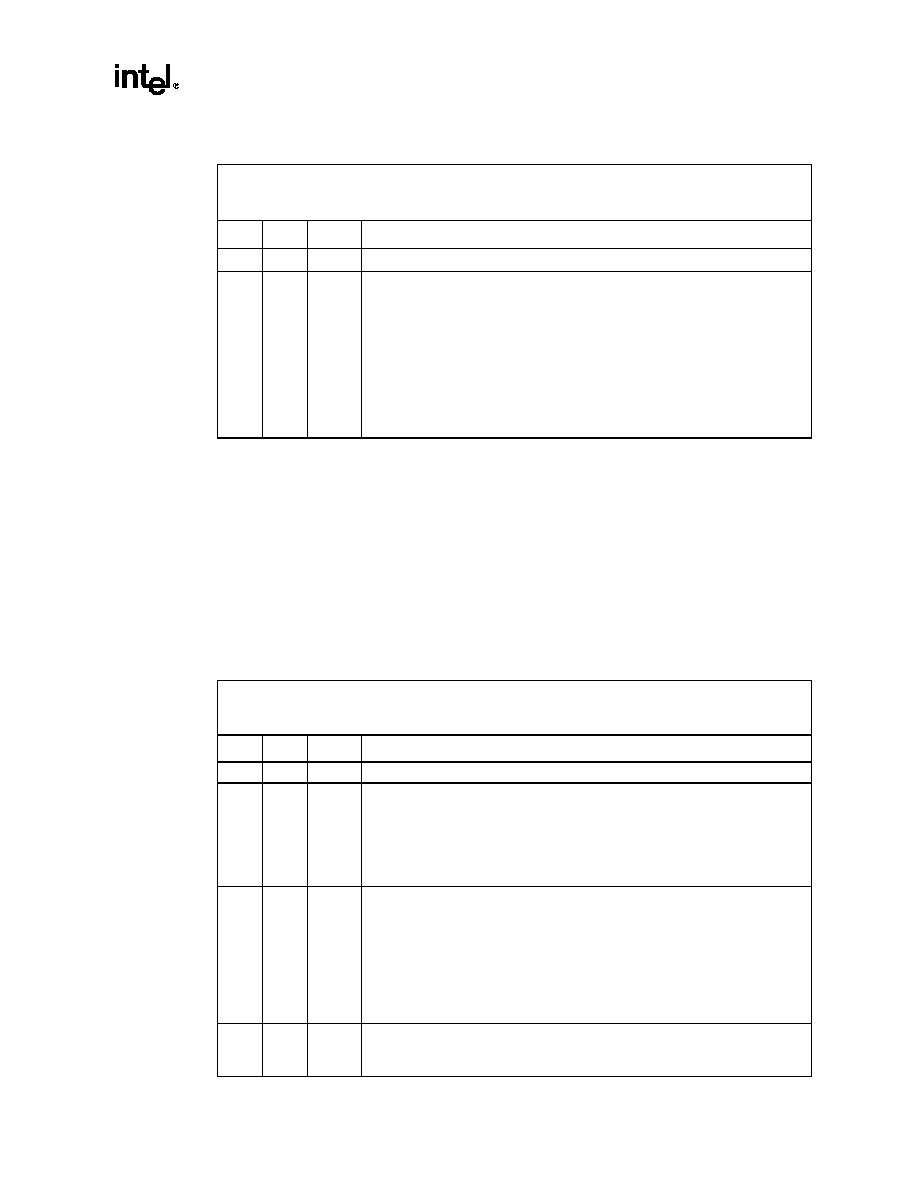

Memory Map ...................................................................................................... 4-1

4.1.1

SPS Memory Address Space Regions..................................................4-1

4.1.2

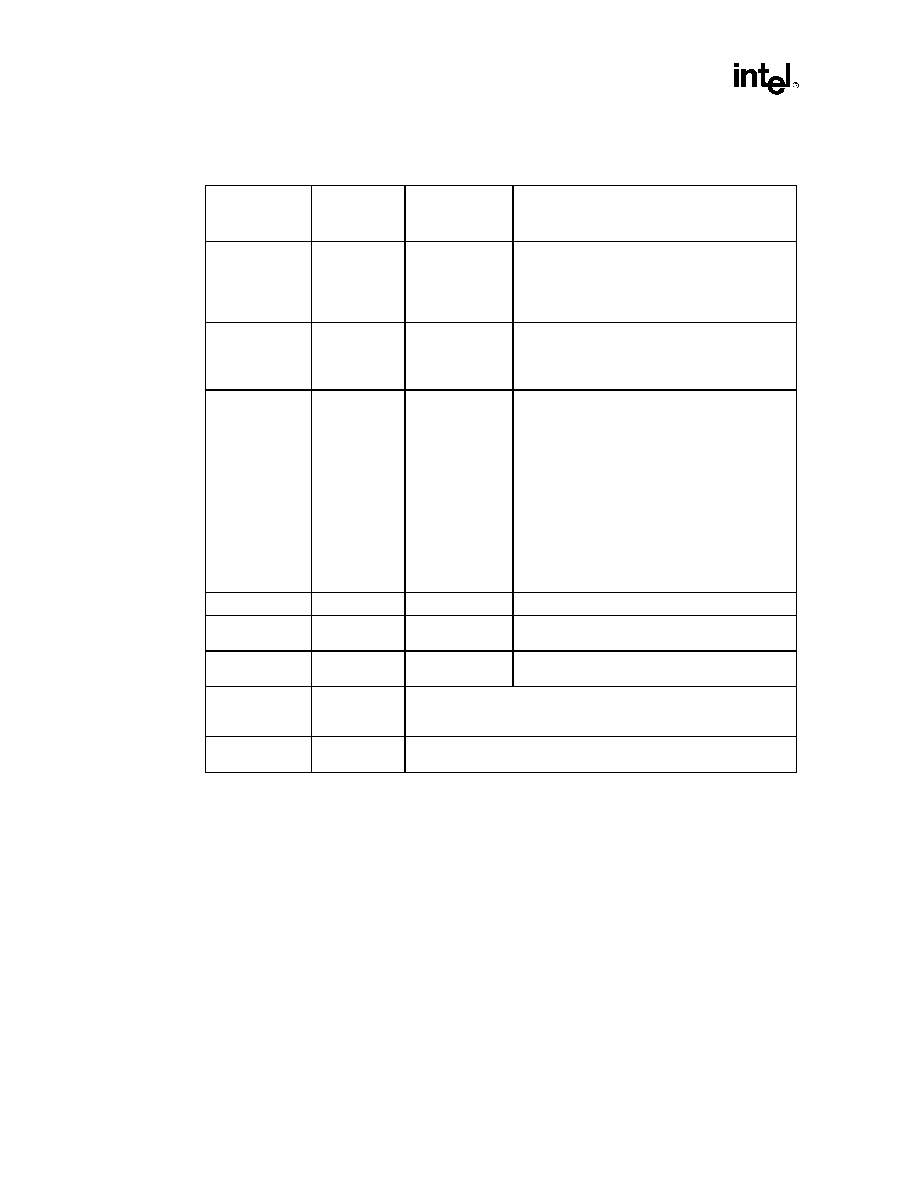

Memory-Mapped I/O Regions ...............................................................4-2

4.1.3

Routing Interrupts.................................................................................. 4-3

4.2

Address Mapping in I/O Space ..........................................................................4-3

4.3

Address Mapping to Access Snoop Filter ..........................................................4-4

4.4

Illegal Addresses ................................................................................................4-4

5

Functional Description.....................................................................................................5-1

5.1

Interfaces ...........................................................................................................5-1

5.1.1

Scalability Port ......................................................................................5-1

5.1.2

JTAG .....................................................................................................5-1

5.1.3

SMBus Interface....................................................................................5-1

5.1.4

GPIO .....................................................................................................5-1

5.2

Snoop Filter ........................................................................................................5-2

5.2.1

Coverage and Addressing.....................................................................5-2

5.2.2

Replacement Algorithm .........................................................................5-3

5.2.3

Snoop Filter Operations and Interfaces ................................................5-3

5.2.4

Error Correction and Logging ................................................................5-4

5.2.5

Snoop Filter Performance .....................................................................5-4

5.3

Interconnect .......................................................................................................5-4

5.3.1

Bypass Buses .......................................................................................5-4

5.3.2

Crossbar Switch ....................................................................................5-5

6

Clocking .......................................................................................................................... 6-1

6.1

SPS Reference Clock (SYSCLK) .......................................................................6-1

6.2

Other Functional and Electrical Requirements...................................................6-1

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

v

6.2.1

Spread Spectrum Support.....................................................................6-1

6.2.2

No Stop Clock or Thermal Shutdown ....................................................6-1

6.2.3

SMBus Clocking ....................................................................................6-1

6.2.4

JTAG Test Access Port .........................................................................6-1

7

Reliability, Availability and Serviceability.........................................................................7-1

7.1

Data Integrity ......................................................................................................7-1

7.1.1

End-to-End Error Detection ...................................................................7-1

7.1.2

Error Reporting ......................................................................................7-2

7.1.3

Interface Details ....................................................................................7-3

7.1.4

Time-out ................................................................................................7-3

8

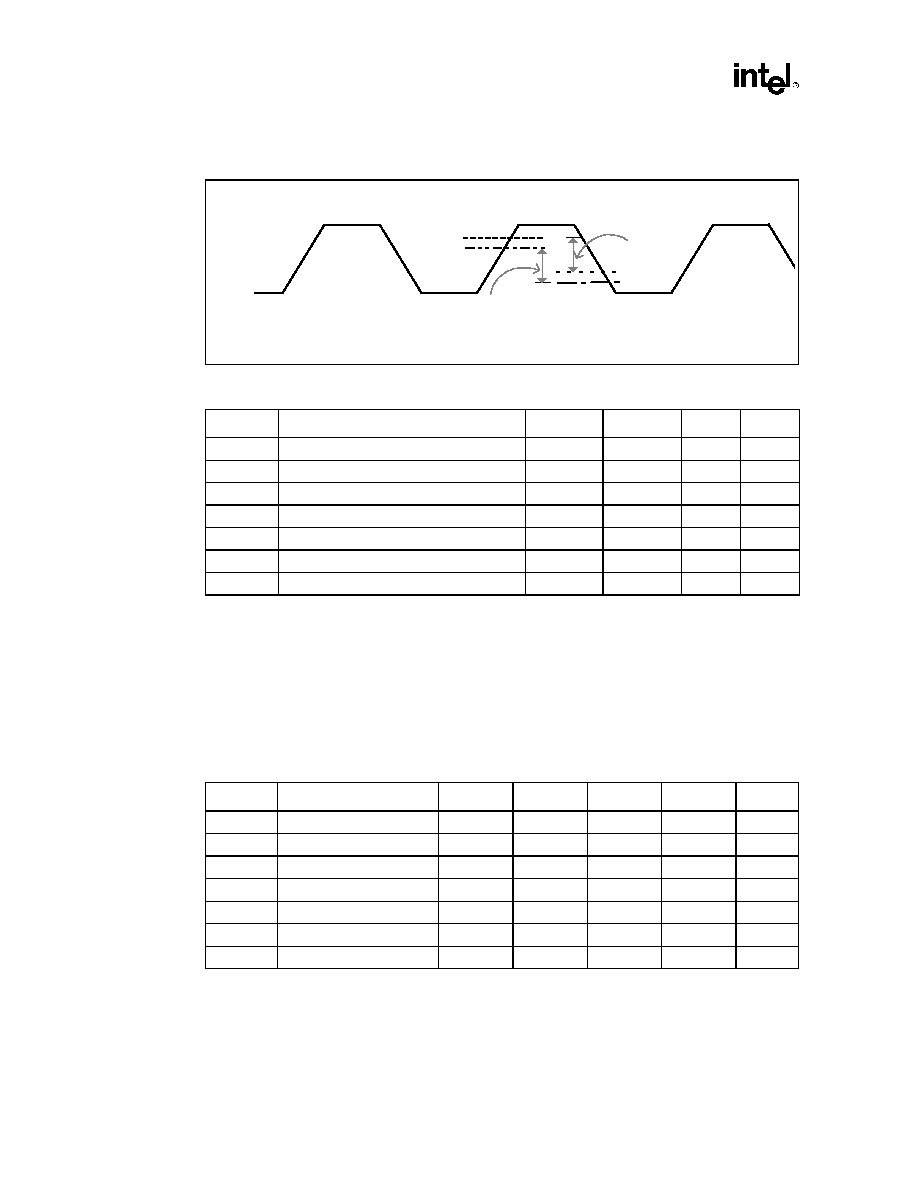

Electrical Specification ....................................................................................................8-1

8.1

Non-operational Maximum Rating......................................................................8-1

8.2

Operational Power Delivery Specification ..........................................................8-1

8.3

Scalability Port Signal Group..............................................................................8-2

8.4

SMBus and TAP Electrical Specifications ..........................................................8-2

8.5

DC Specifications ...............................................................................................8-3

8.6

AC Specifications ...............................................................................................8-4

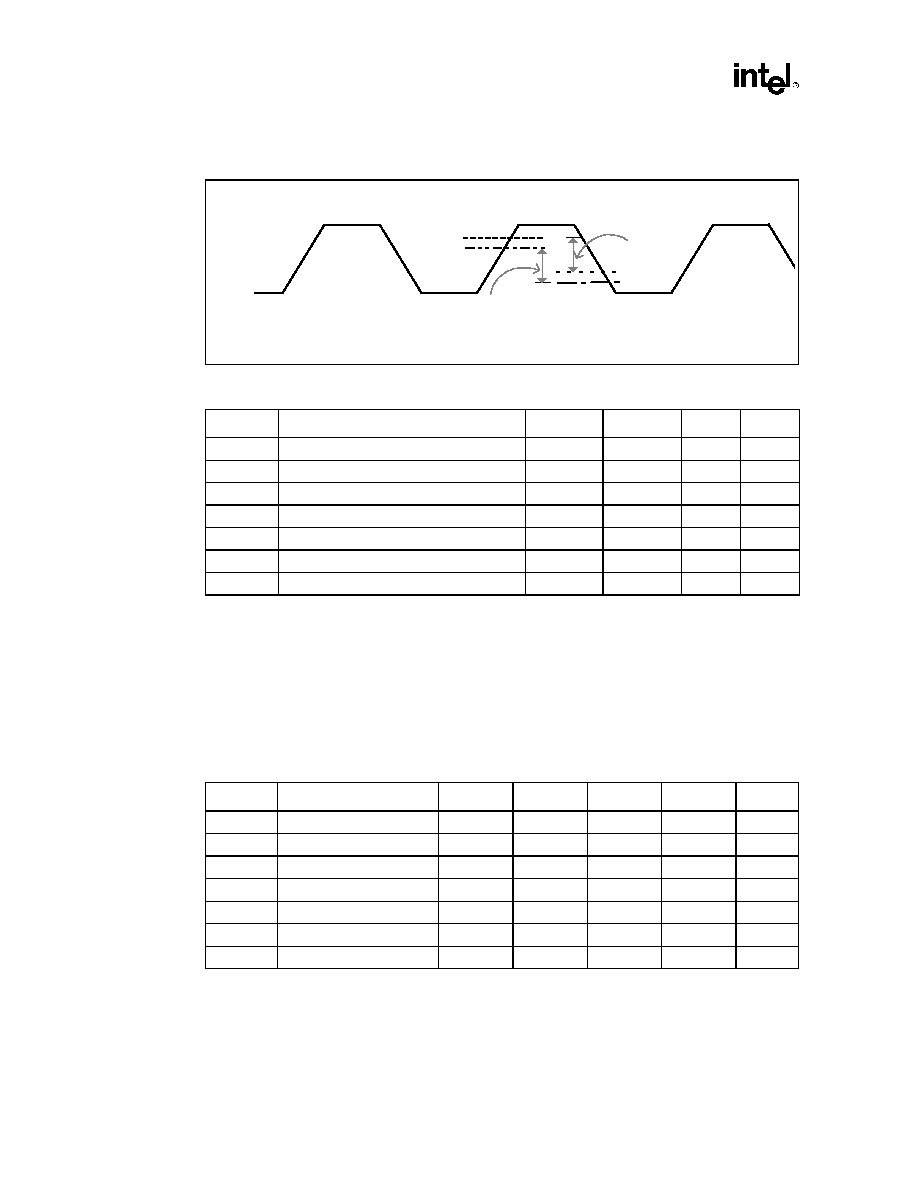

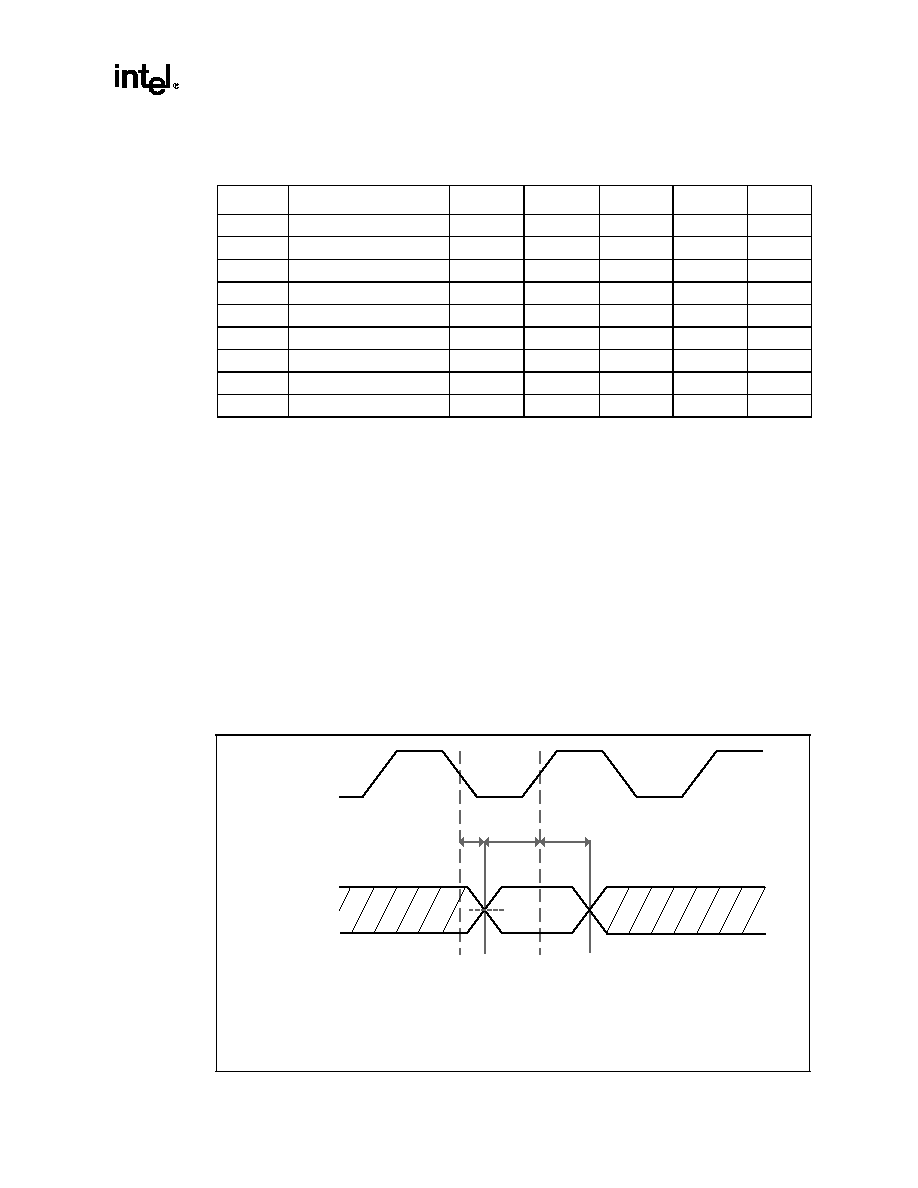

8.6.1

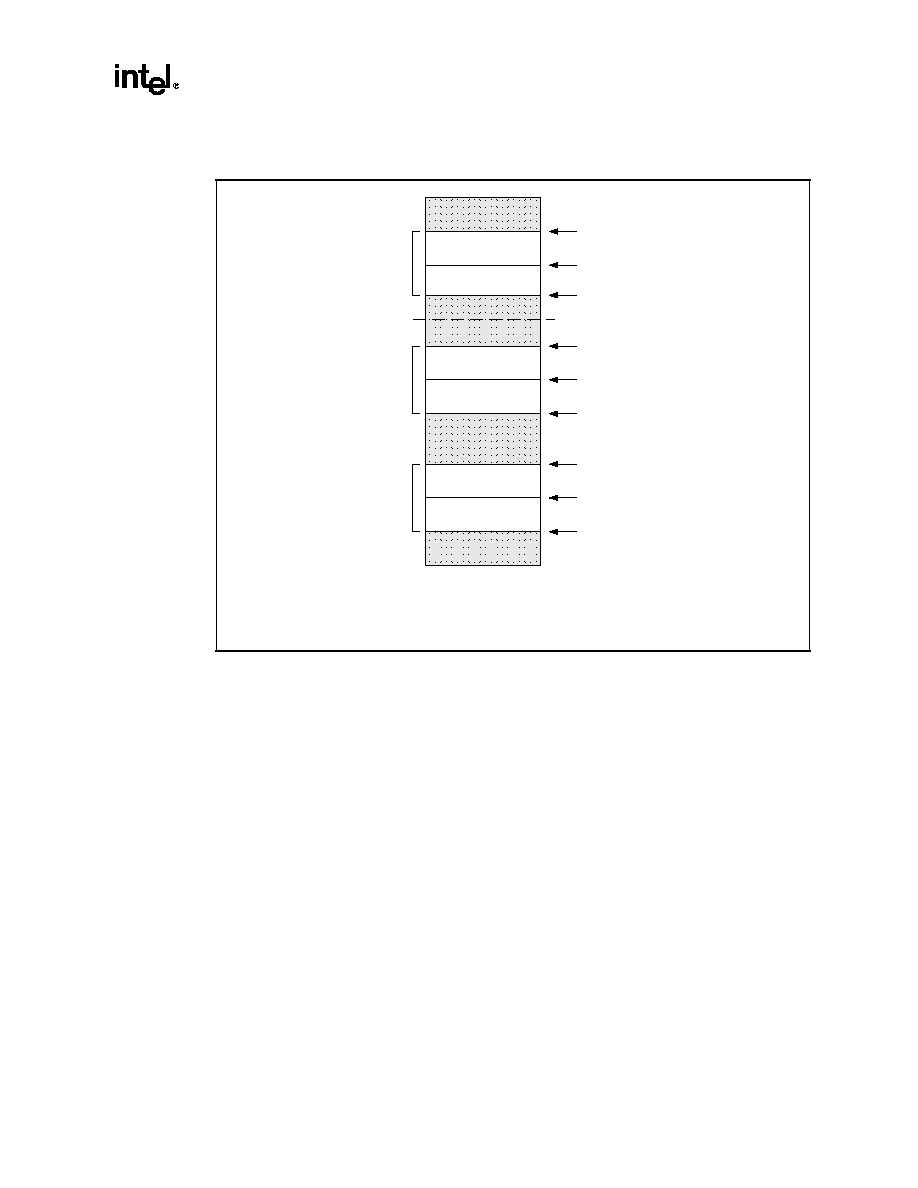

AC Timing Waveforms ..........................................................................8-5

8.7

Miscellaneous Signal Pins..................................................................................8-6

8.7.1

Signal Groups........................................................................................8-6

8.7.2

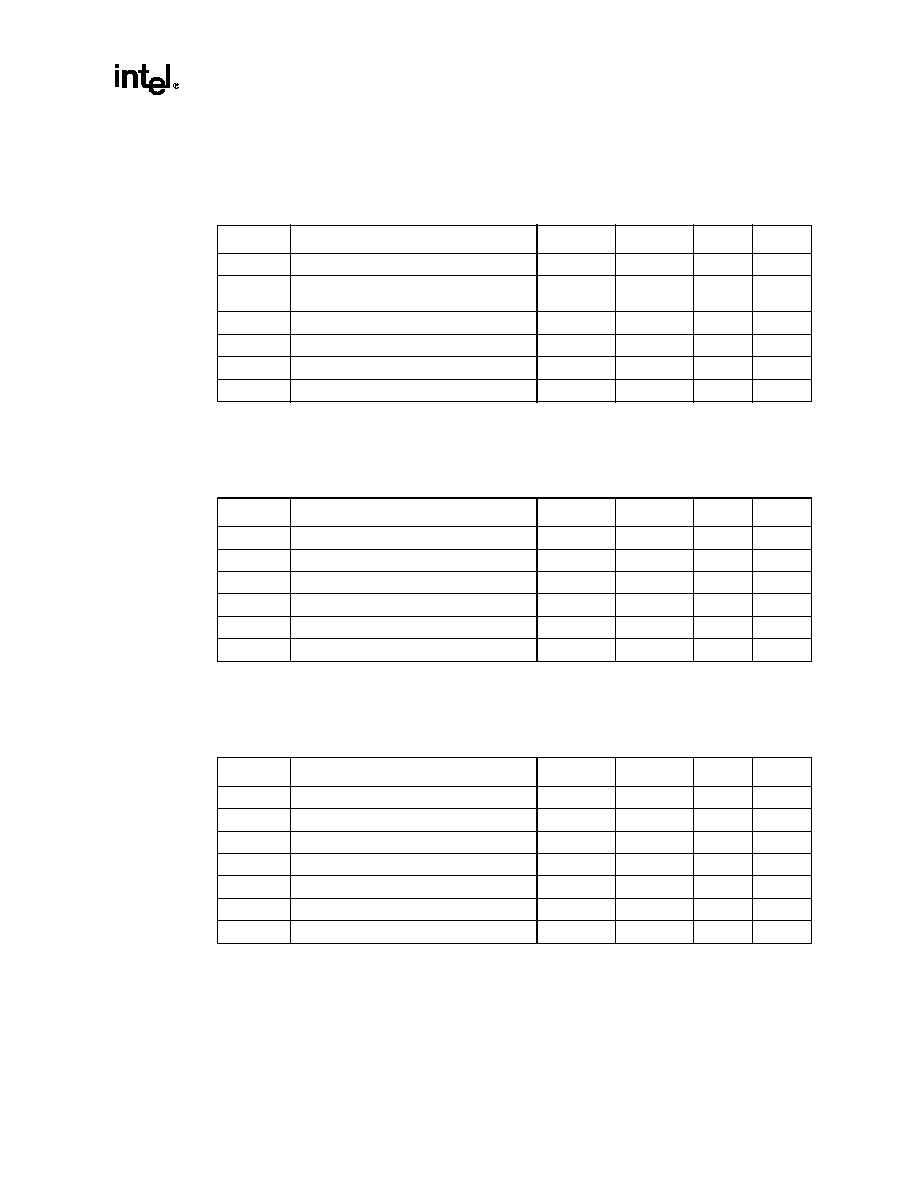

DC Characteristics ................................................................................8-7

8.8

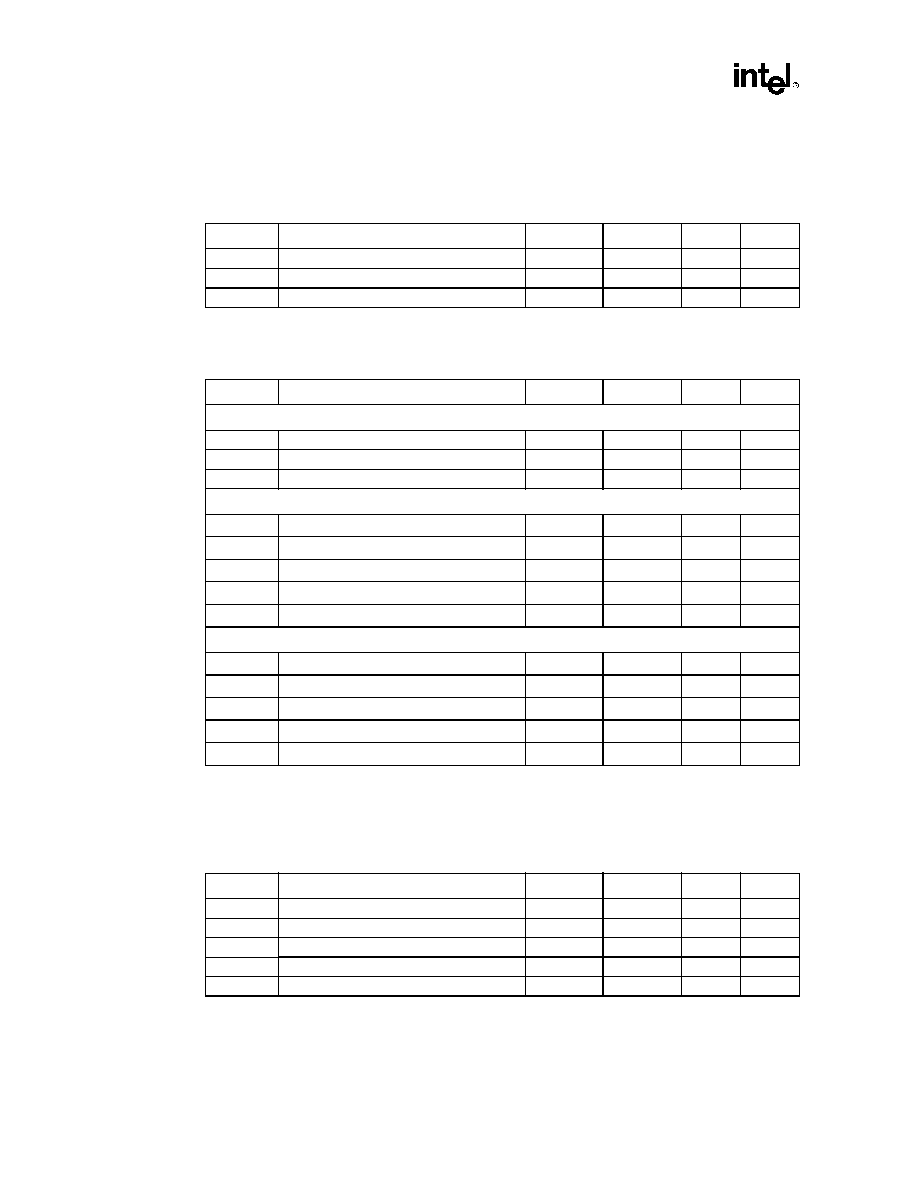

AC Specification .................................................................................................8-8

8.9

Intel

Æ

E8870 Chipset Clock Signal Groups ........................................................8-9

9

Ballout and Package Information ....................................................................................9-1

9.1

1012-Ball OLGA2b Package Information ...........................................................9-1

10

Testability ......................................................................................................................10-1

10.1

Test Access Port ..............................................................................................10-1

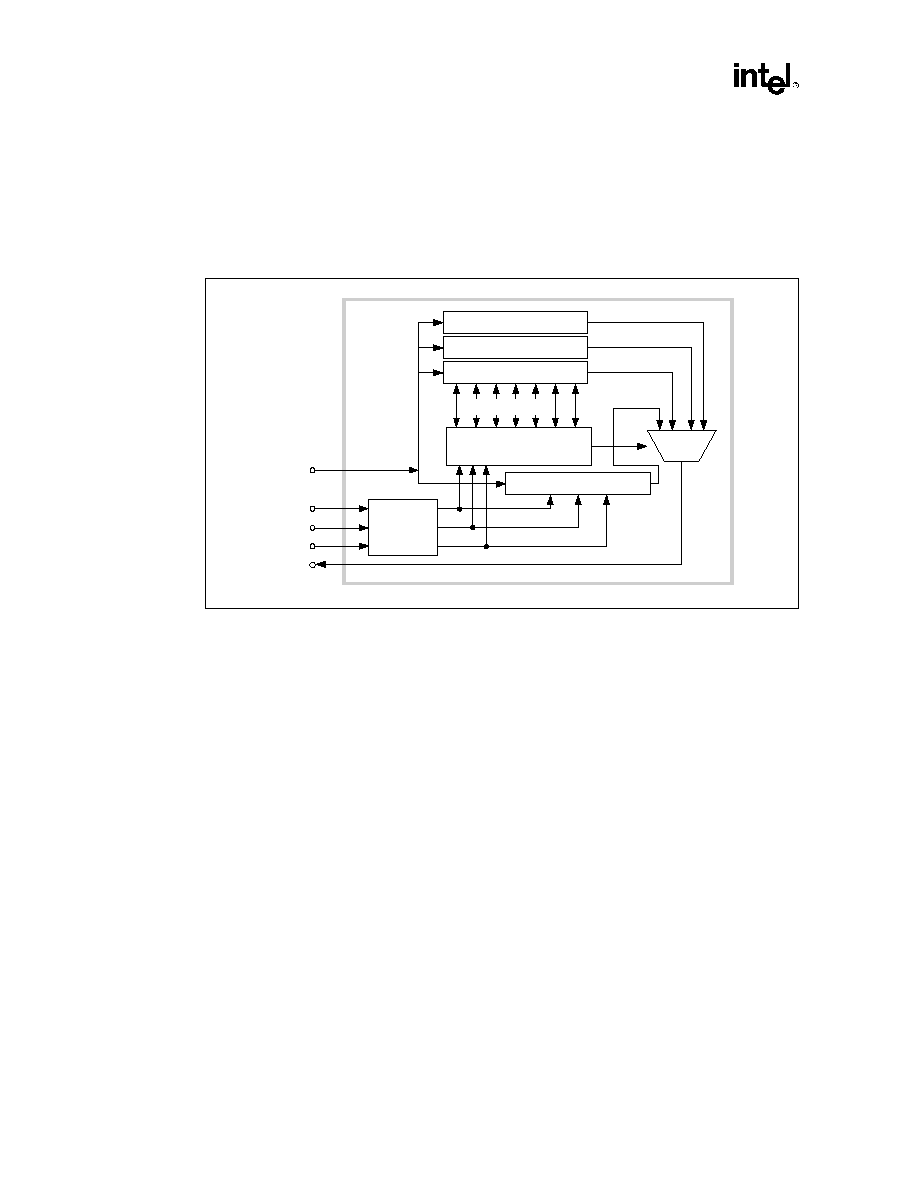

10.1.1 The TAP Logic.....................................................................................10-1

10.1.2 Accessing the TAP Logic ....................................................................10-2

10.2

Public TAP Instructions ....................................................................................10-4

10.3

TAP Registers ..................................................................................................10-5

Figures

1-1

SPS Block Diagram............................................................................................1-2

4-1

System Memory Address Space ........................................................................4-1

4-2

Example of Mapping MMIO Regions..................................................................4-3

8-1

TAP DC Thresholds ...........................................................................................8-4

8-2

TAP and SMBus Valid Delay Timing Waveform ................................................8-5

8-3

TCK and SM_CLK Clock Waveform ..................................................................8-6

9-1

1012-Ball OLGA2b Package Dimensions ≠ Top View .......................................9-1

9-2

1012-Ball OLGA2b Package Dimensions ≠ Bottom View ..................................9-2

9-3

1012-Ball OLGA2b Solder Ball Detail.................................................................9-3

10-1

TAP Controller Signals .....................................................................................10-1

10-2

Simplified Block Diagram of TAP Controller.....................................................10-2

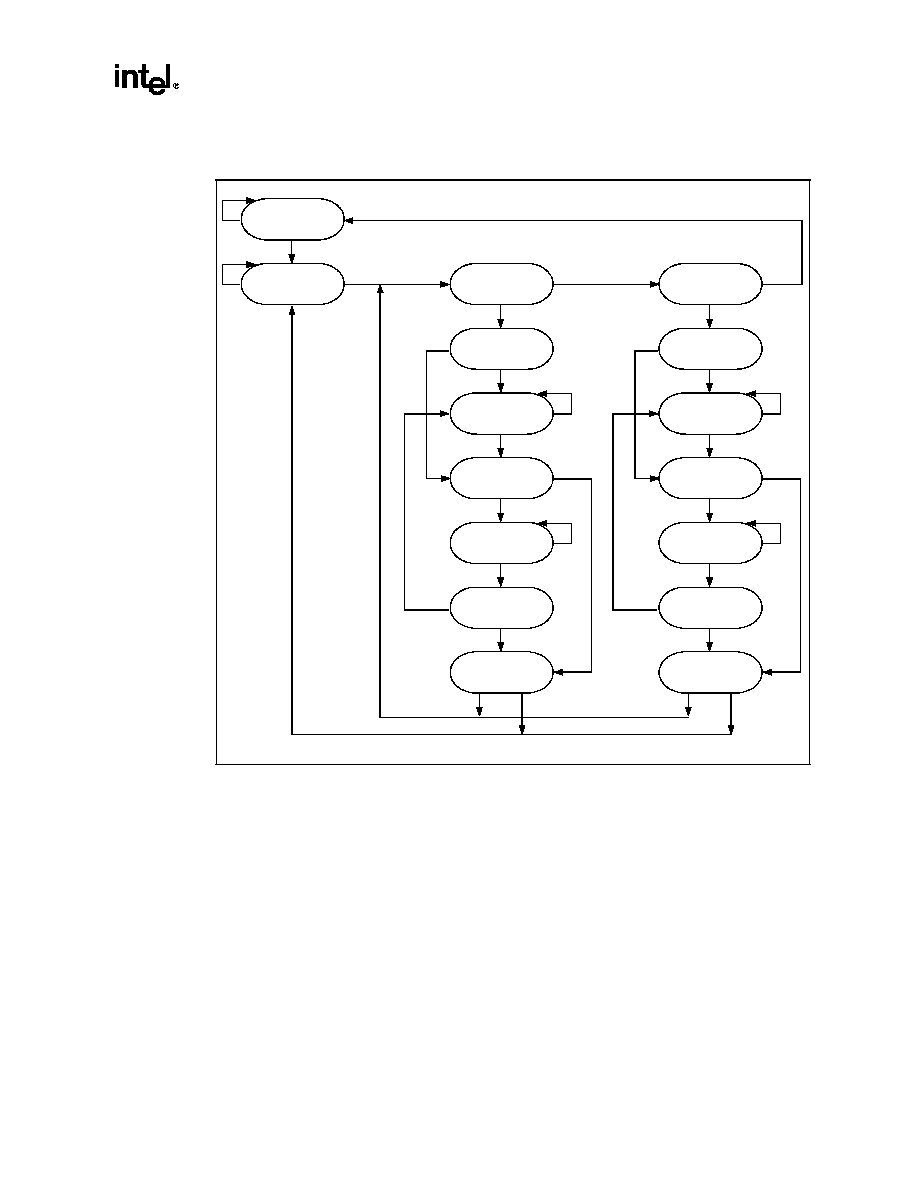

10-3

TAP Controller State Diagram..........................................................................10-3

10-4

TAP Instruction Register ..................................................................................10-6

vi

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

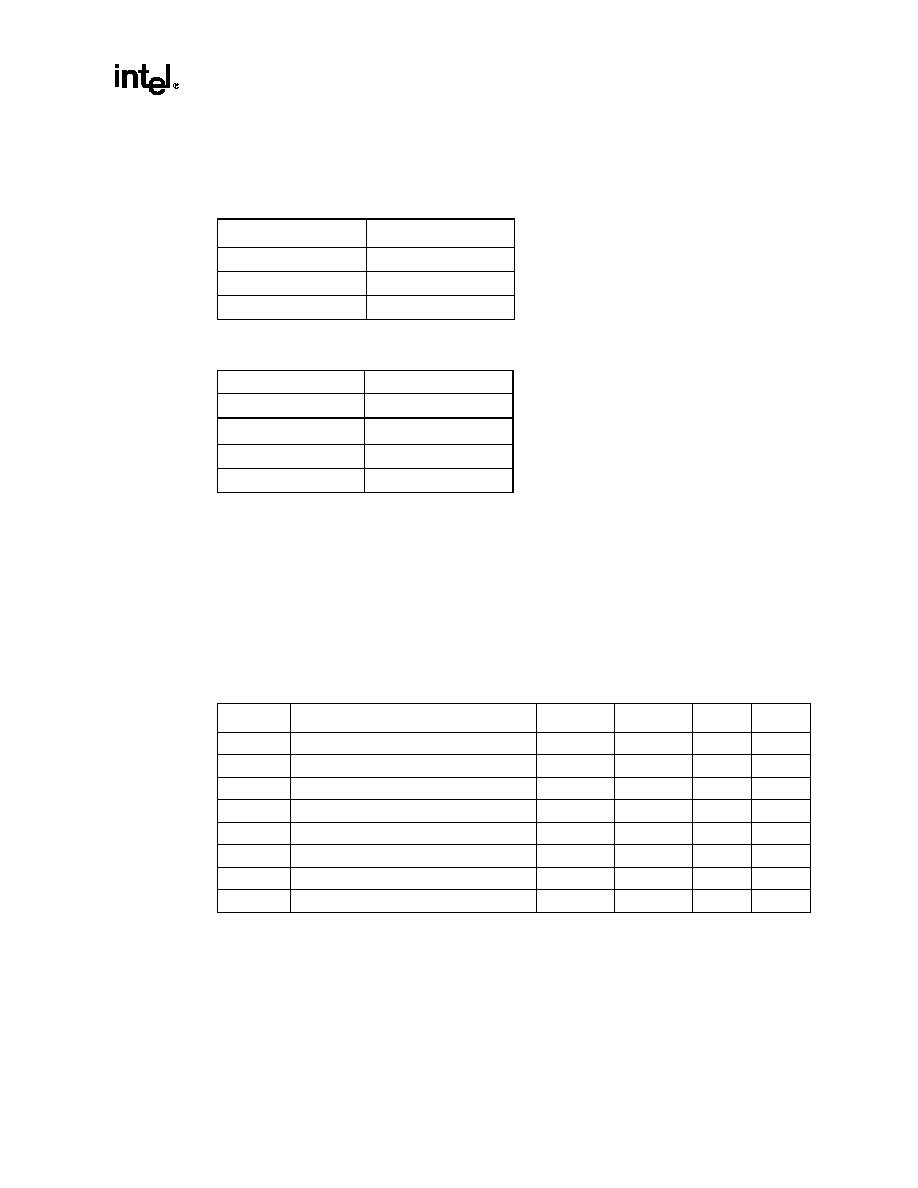

Tables

2-1

Buffer Technology Types ...................................................................................2-1

2-2

Buffer Signal Directions......................................................................................2-1

2-3

Signal Naming Conventions ...............................................................................2-2

2-4

SPS Pin List .......................................................................................................2-2

3-1

Configuration Address Bit Mapping....................................................................3-1

3-2

Function Maps....................................................................................................3-2

3-3

Register Attributes Definitions ............................................................................3-2

3-4

Register Range for Functions 6 and 7 .............................................................3-20

3-5

Control: Snoop Filter ECC Error Fields ............................................................3-21

4-1

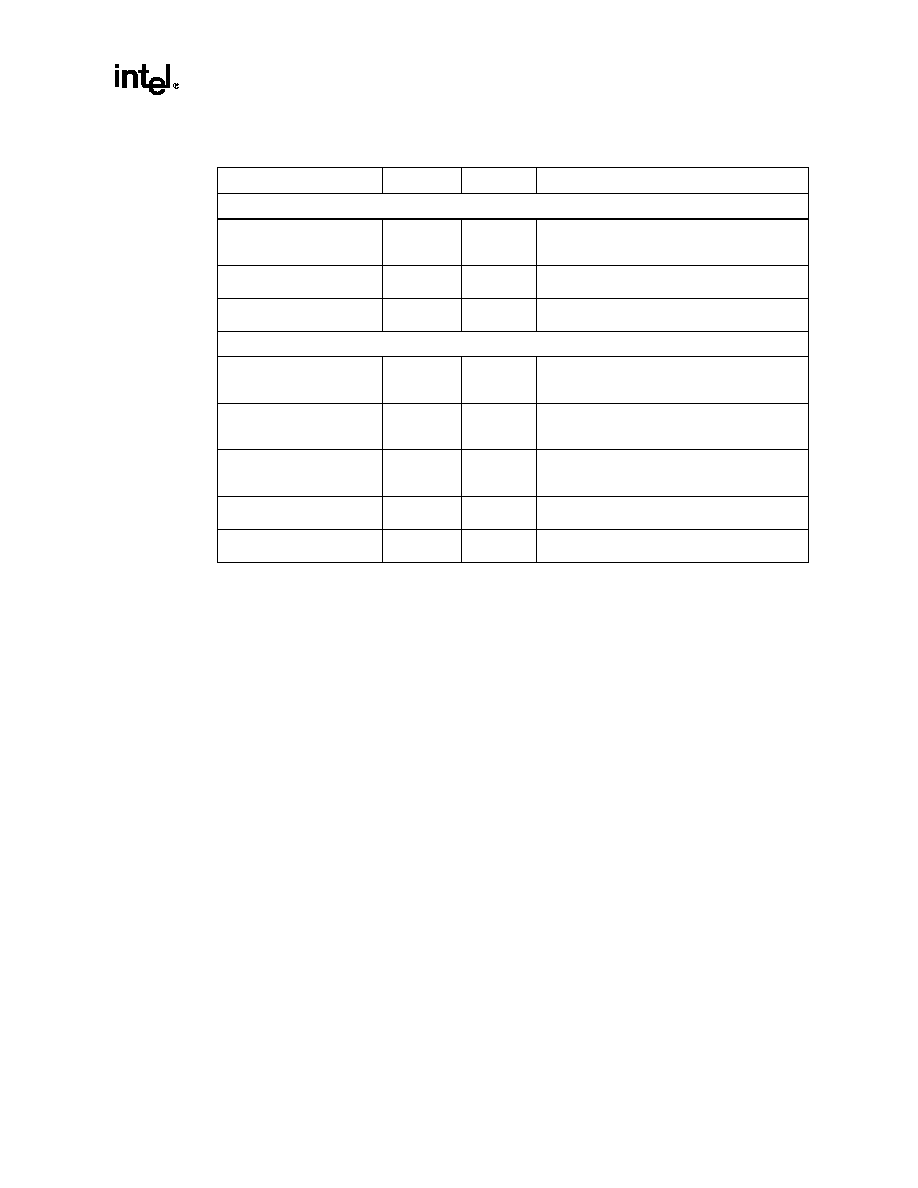

Regions of Transactions to Decode ...................................................................4-2

4-2

I/O Space Mappings...........................................................................................4-4

4-3

SPS Transactions to Illegal Addresses .............................................................. 4-4

5-1

Example SF Coverage for Different Node/L3 Configurations ............................5-2

5-2

Physical Address Partitioning.............................................................................5-3

5-3

Snoop Filter Entry ..............................................................................................5-3

8-1

Absolute Maximum Non-operational DC Ratings at the Package Pin ...............8-1

8-2

Voltage and Current Specifications....................................................................8-1

8-3

Scalability Port Interface Signal Group .............................................................. 8-2

8-4

SMBus and TAP Interface Signal Group............................................................8-3

8-5

TAP Signal Terminations ...................................................................................8-3

8-6

TAP DC Parameters .........................................................................................8-3

8-7

SMBus DC Parameters ......................................................................................8-4

8-8

SMBus Signal Group AC Specifications ...........................................................8-4

8-9

TAP Signal Group AC Specifications ................................................................8-5

8-10

Signal Groups ....................................................................................................8-6

8-11

CMOS 1.3V DC Parameters ..............................................................................8-7

8-12

CMOS 1.5V OD DC Parameters .......................................................................8-7

8-13

CMOS 1.5V DC Parameters ..............................................................................8-7

8-14

CMOS 1.3V AC Parameters .............................................................................8-8

8-15

CMOS 1.5V Open-Drain AC Parameters ...........................................................8-8

8-16

CMOS 1.5V AC Parameters ..............................................................................8-8

8-17

Clock Signal Groups ..........................................................................................8-9

8-18

LVHSTL Clock DC Parameters..........................................................................8-9

9-1

SPS Ball List ...................................................................................................... 9-4

9-2

SPS Signal List ................................................................................................9-17

10-1

TAP Signal Definitions .....................................................................................10-1

10-2

Public TAP Instructions ....................................................................................10-4

10-3

Example of Configuration Access Data Register Format.................................10-6

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

1-1

Introduction

1

1.1

Overview

The Scalability Port Switch (SPS) component provides the interconnect and coherency support for

building multinode, multiprocessor systems with the Intel

Æ

E8870 chipset. It has six Scalability

Port (SP) interfaces that provide physical and logical connections to the Scalable Node Controller

(SNC) and Server Input/Output Hub (SIOH) components.

The SPS has an integrated snoop filter (SF) that is used to track the state of cached lines in the

system. The SP coherency protocol and the SF are used by the SPS to maintain cache coherency

and memory consistency in multinode systems.

1.2

Feature Summary

1.2.1

Interfaces

∑

Six simultaneous bi-directional (SBD) SP interfaces (each port supporting up to 3.2 GB/s peak

bandwidth in each direction).

∑

Access to internal control and status registers via TAP port (i.e. JTAG) and System

Management Bus (i.e. SMBus).

1.2.2

Multinode Routing, Cache Coherency, and Memory

Consistency

∑

An integrated SF tag array capable of maintaining state of 200K cache lines. In a system with

two SPS components, this is equivalent to 2X coverage for a system with eight Intel

Æ

Itanium

Æ

2 processors with 3 MB of L3 cache per processor.

∑

A single SPS can support up to 266 SF mega look-up and update (MLUU) operations per

second.

∑

Includes support for 128 byte cache lines, and different L3 cache state transitions.

∑

Conflict detection to maintain memory consistency for coherent memory across multiple

nodes.

∑

Address mapping and decode capabilities that enable flexible routing of transactions based on

address and/or transaction type.

1.2.3

Reliability and Serviceability

∑

ECC generation/detection/correction on accesses to and from configuration space, and ECC

coverage on the SF tag array.

∑

Link-level retry support on all SP interfaces.

∑

Signal connectivity testing via boundary scan.

Introduction

1-2

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

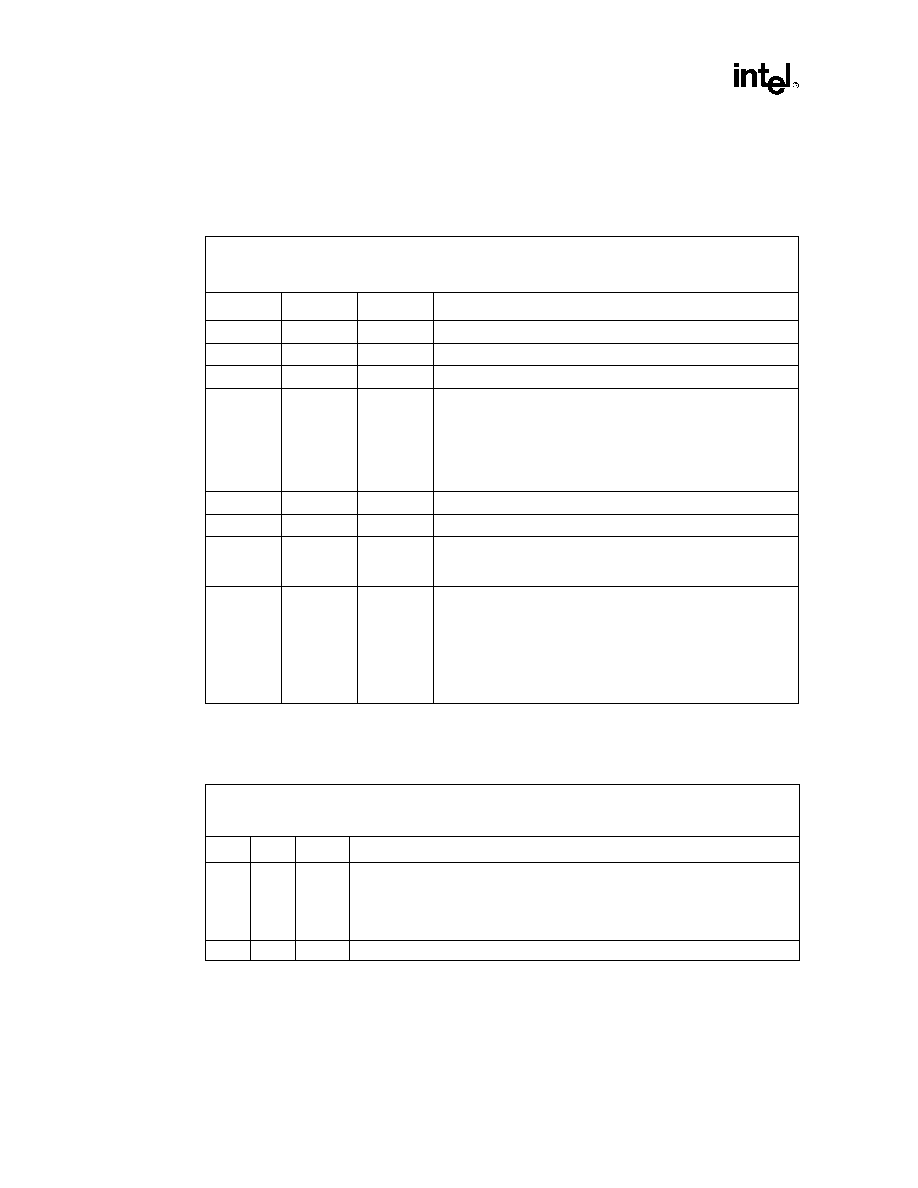

1.3

SPS Blocks

1.3.1

Interleaves

The SPS coherency protocol logic is divided into four interleaves. Each interleave consists of a

portion of the SF tag array and a Scalability Port Protocol Central (SPPC) block. Transactions are

directed to an interleave based on address and transaction type. Each interleave can operate in

parallel.

The SF is a 12-way set associative array, with each interleave containing 4K sets, for a total of 16K

sets per SPS. Each SF entry contains an address tag, the state of the cache line, and a presence

vector identifying the nodes that have the line cached. The replacement algorithm for the SF is

Pseudo Least Recently Used (PLRU), with modifications to support updates based on replacement

information received from the processors. Each SF interleave can support 66 MLUU/s, for a total

SPS throughput of 266 MLUU/s. Each system bus request results in one LUU operation in the SF.

A SPPC block is associated with each SF partition. As the name implies, the SPPC generates a

sequence of operations or transactions based on the type of request as defined by the SP Protocol.

For coherent transactions, the SF is accessed, and address conflicts are checked and handled.

The SPPC may retry transactions or assert back pressure to the SP due to conflicts or resource

limitations. The SPPC may generate snoop requests to remote nodes, invalidation requests or read

requests in response to coherent memory requests. The SPPC also handles transactions that require

special handling such as broadcast or sequencing.

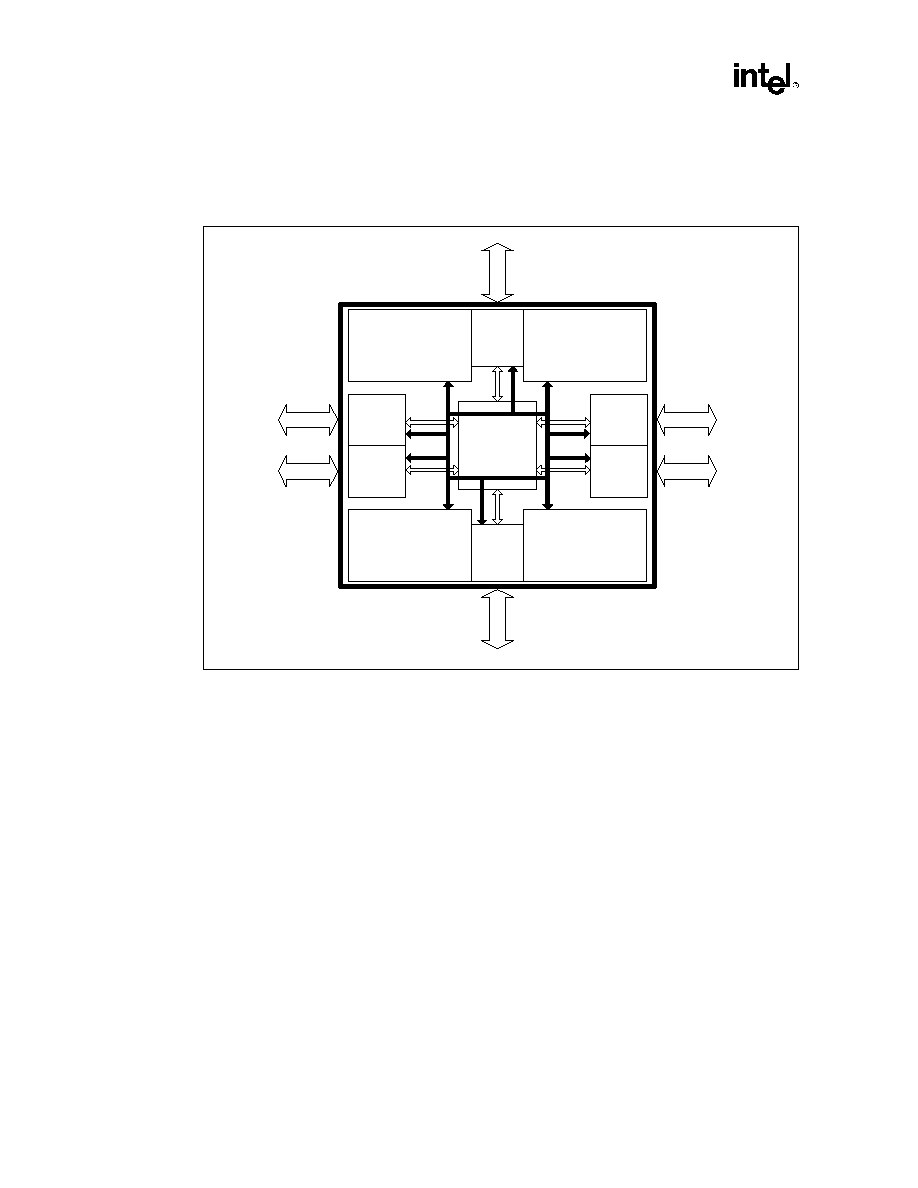

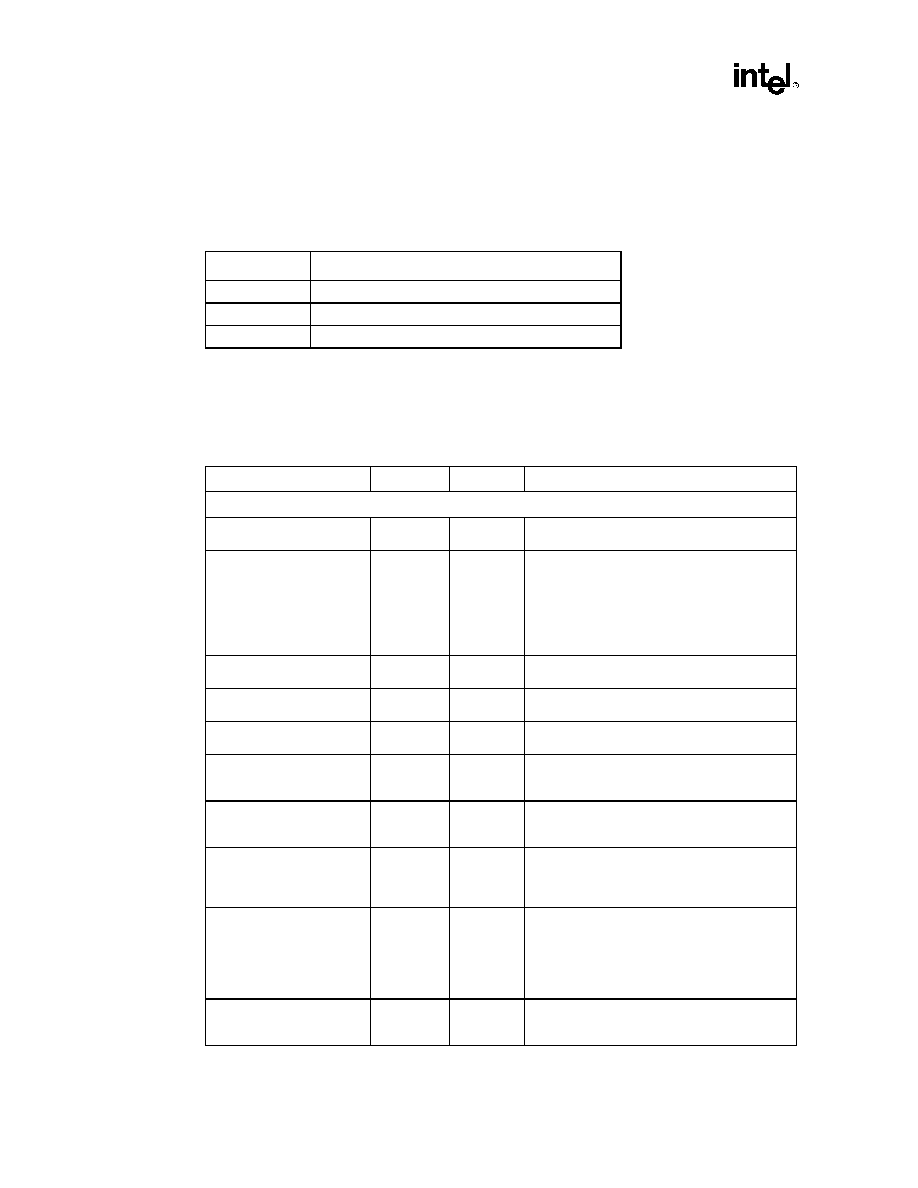

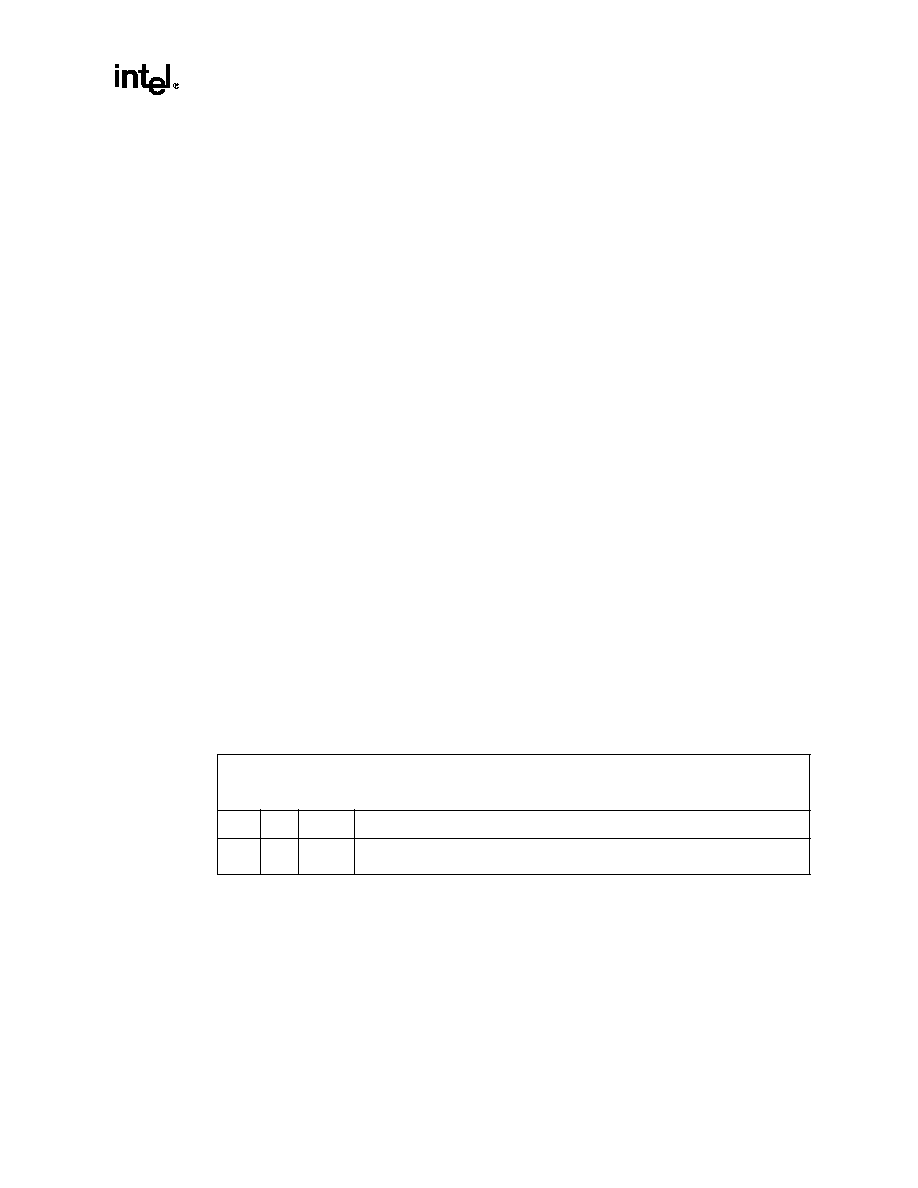

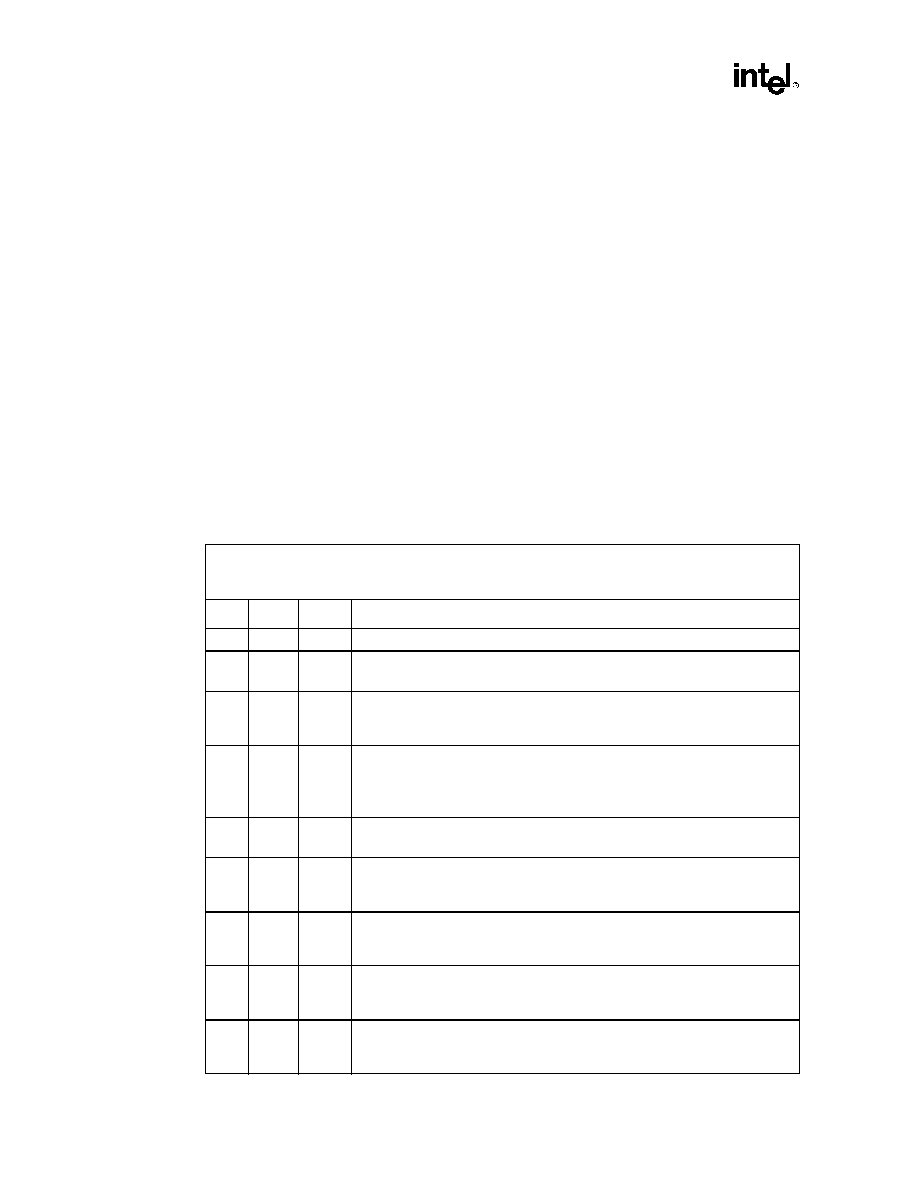

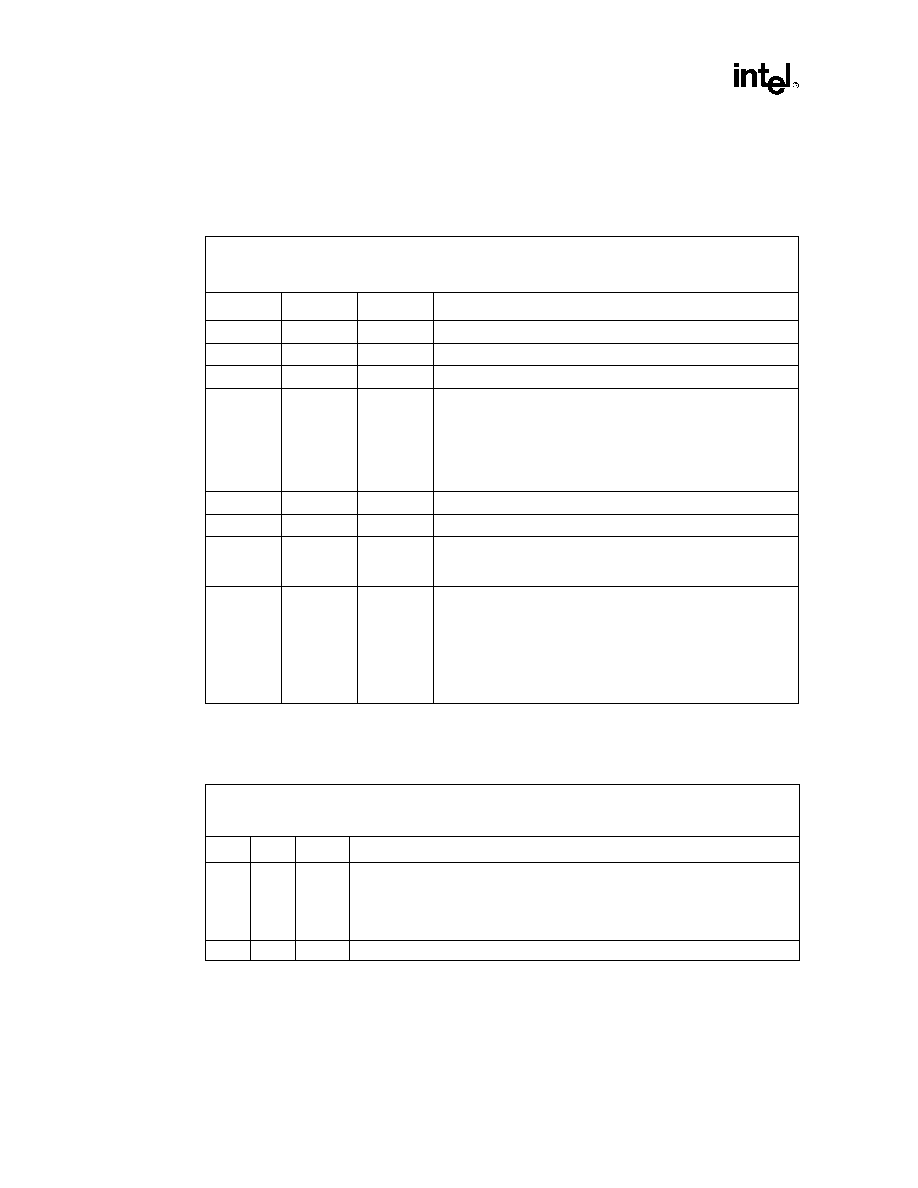

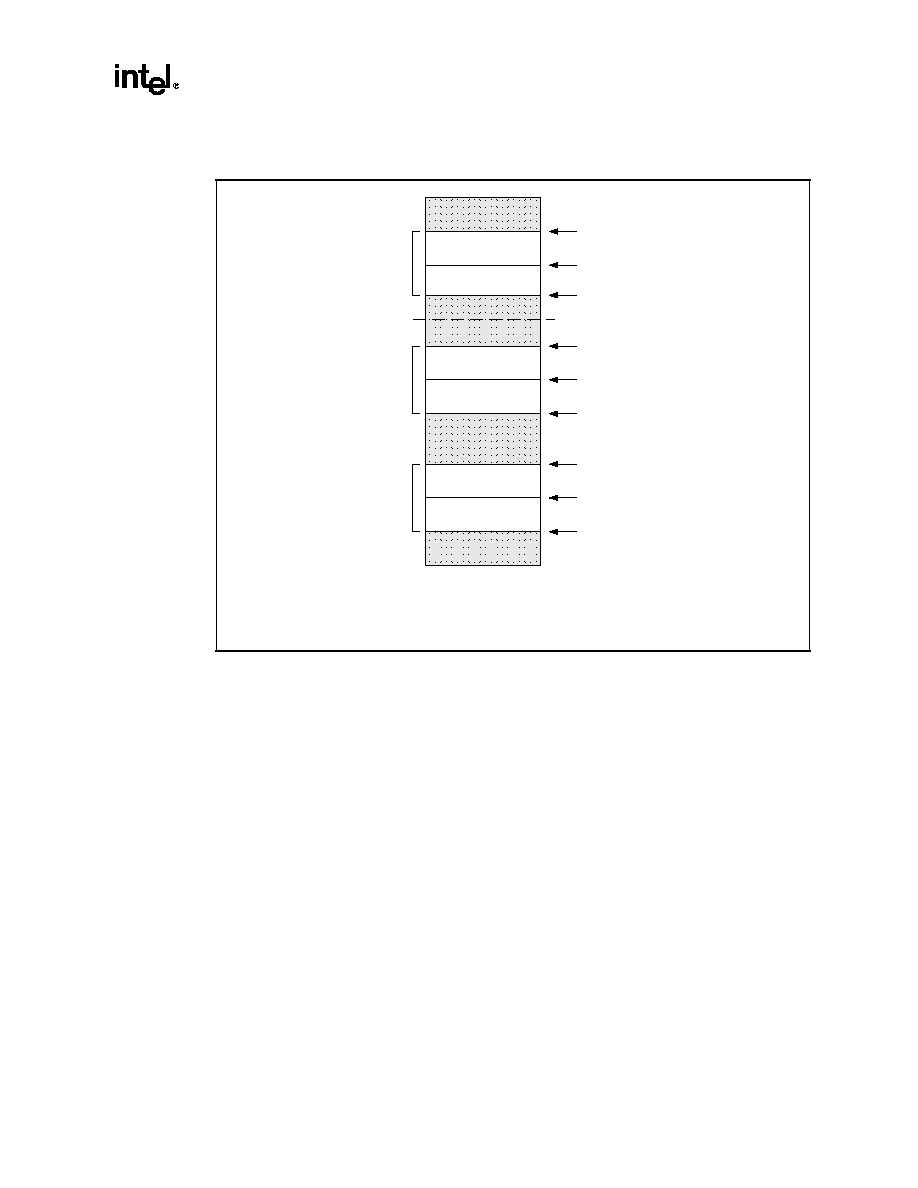

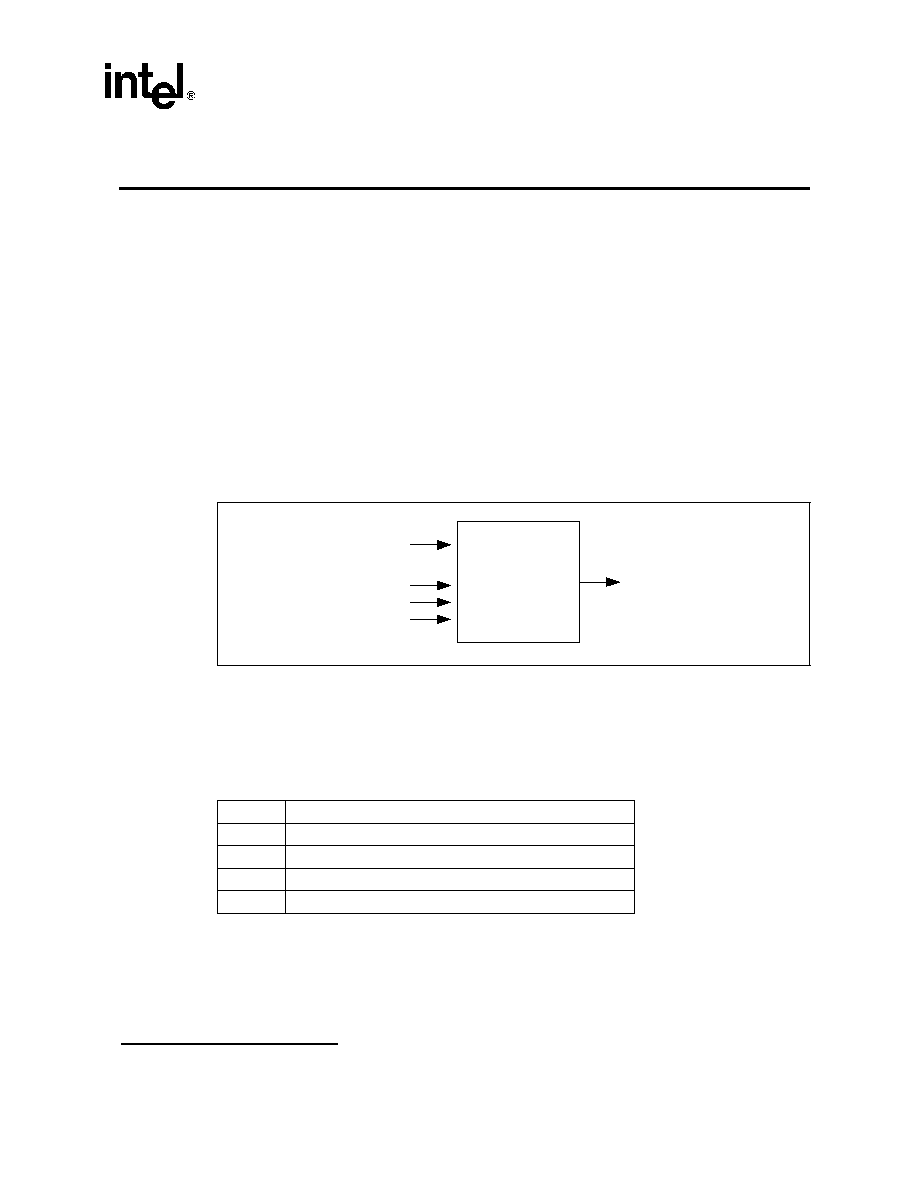

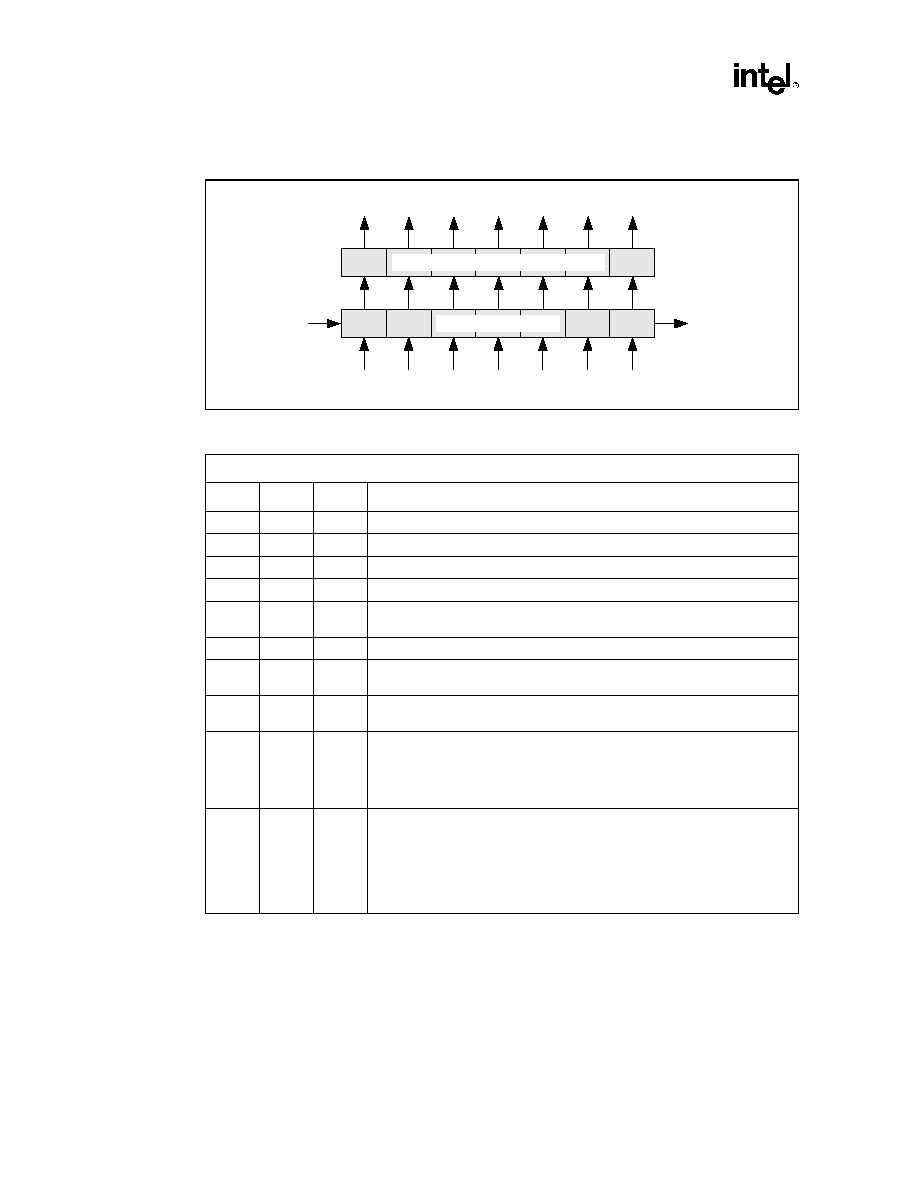

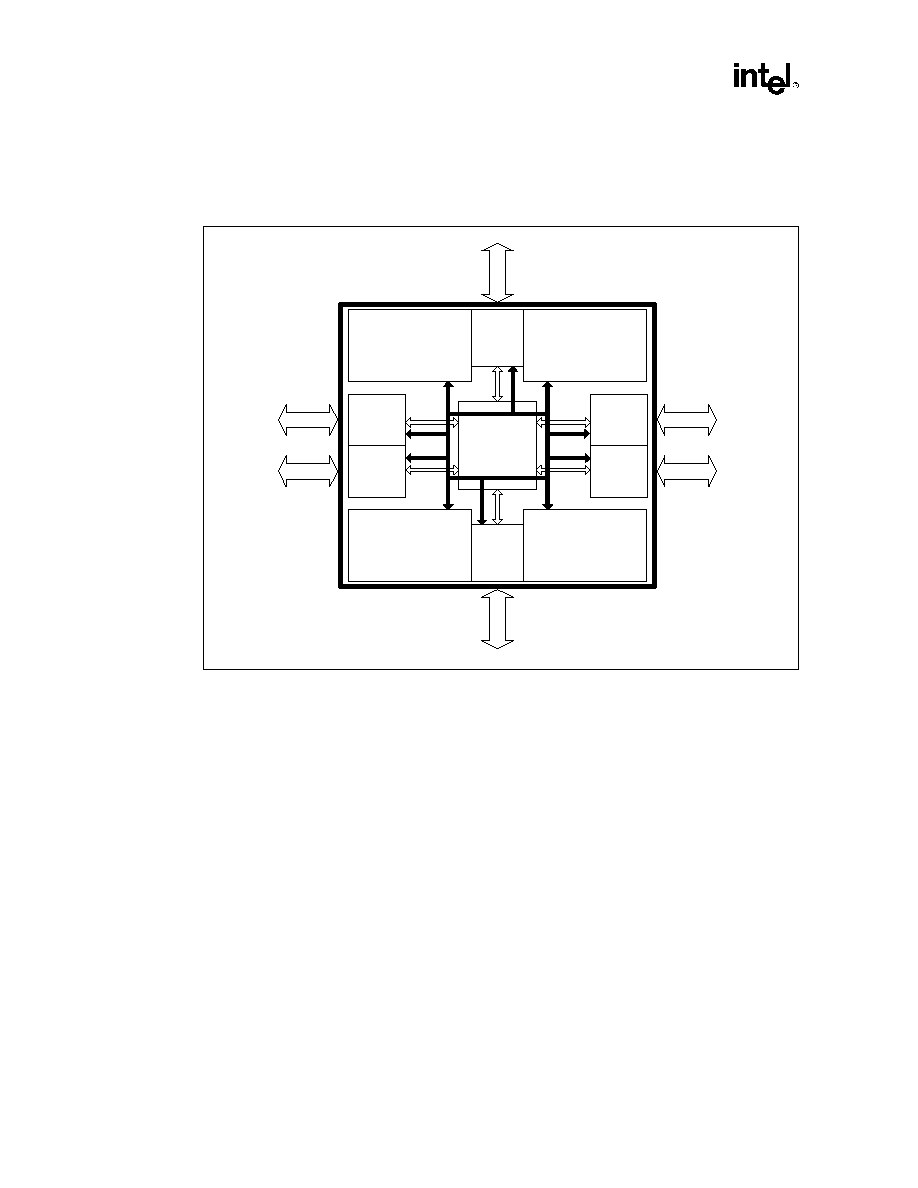

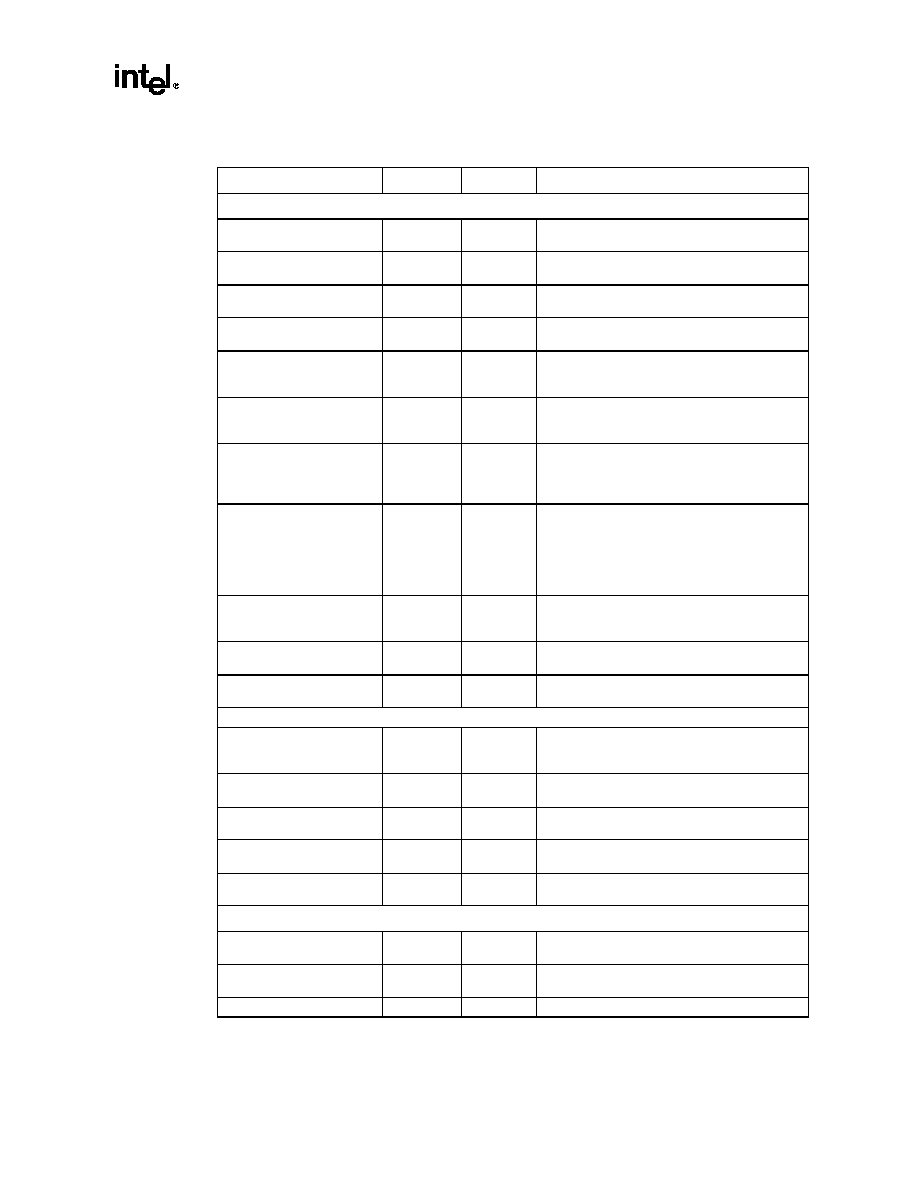

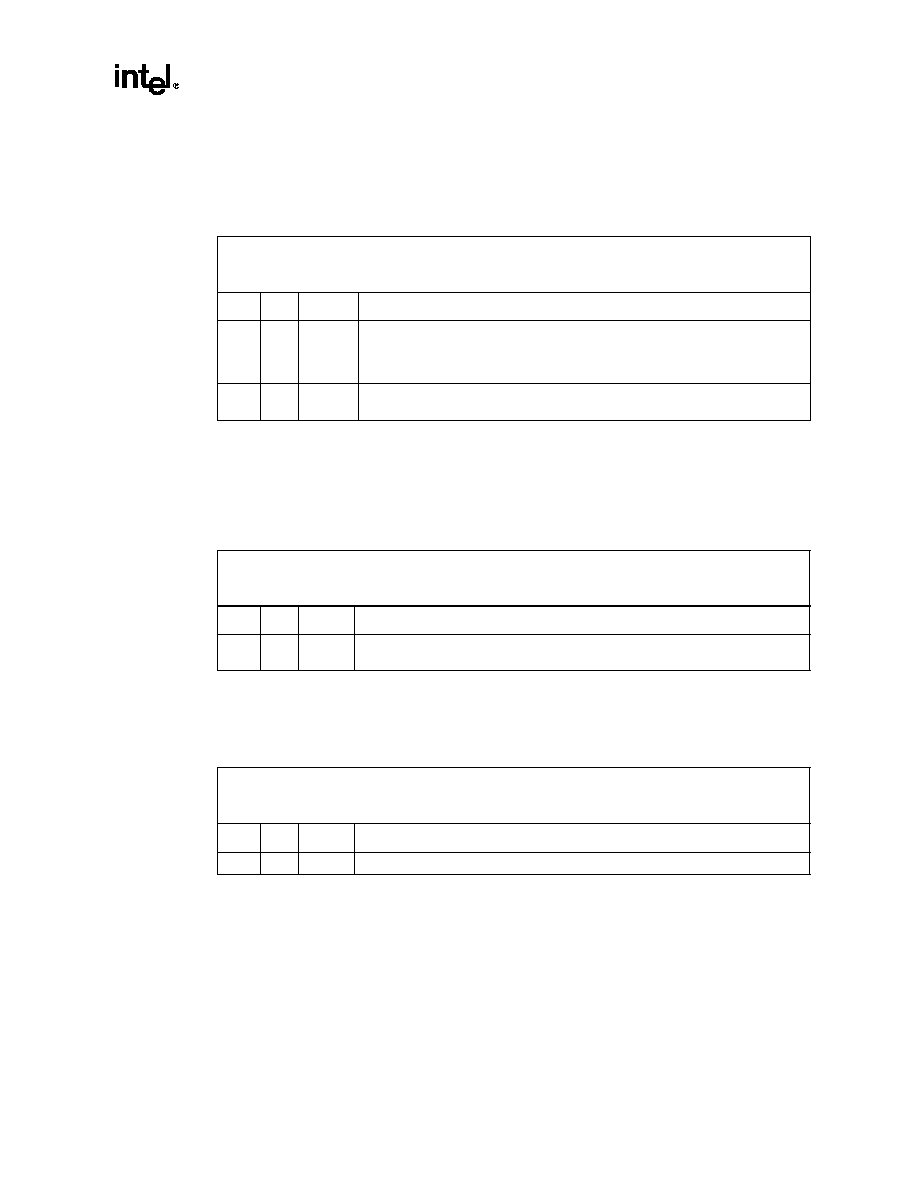

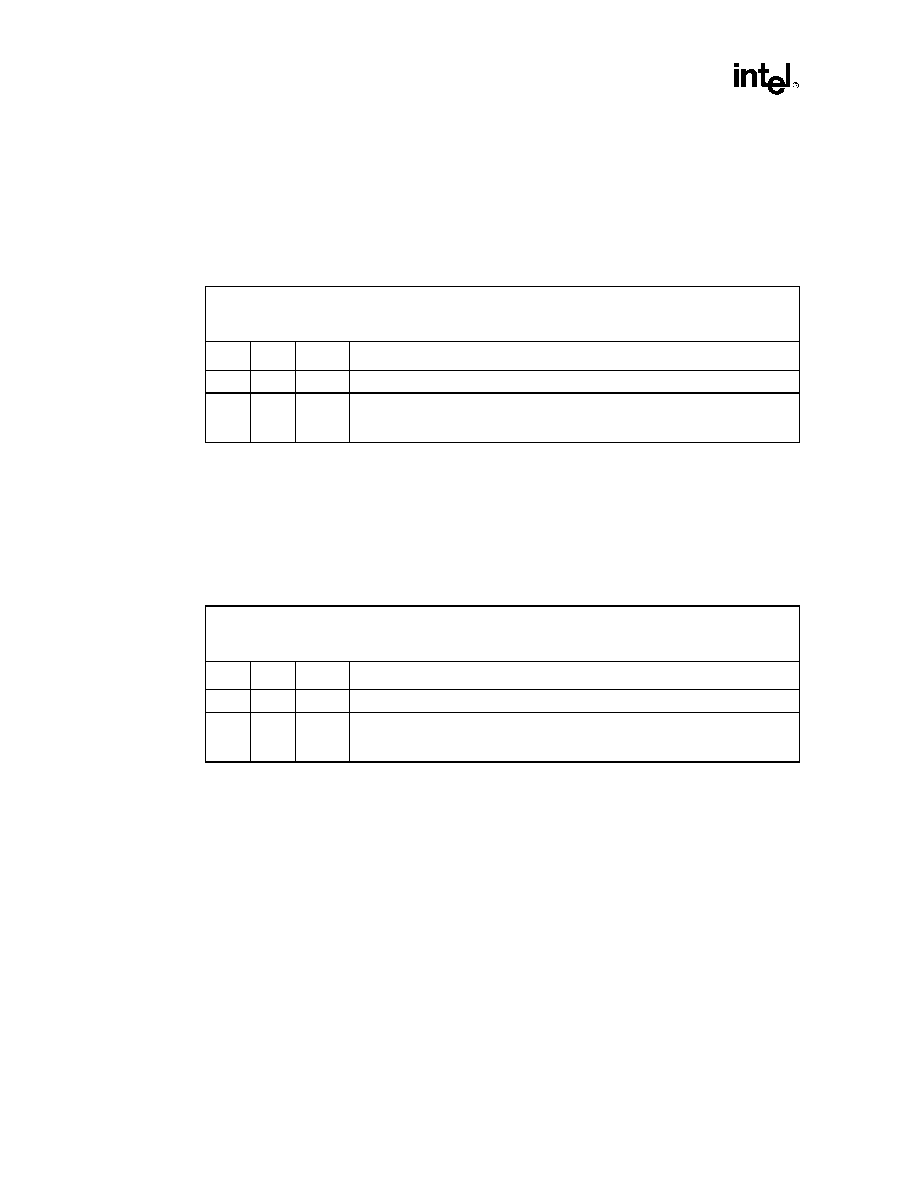

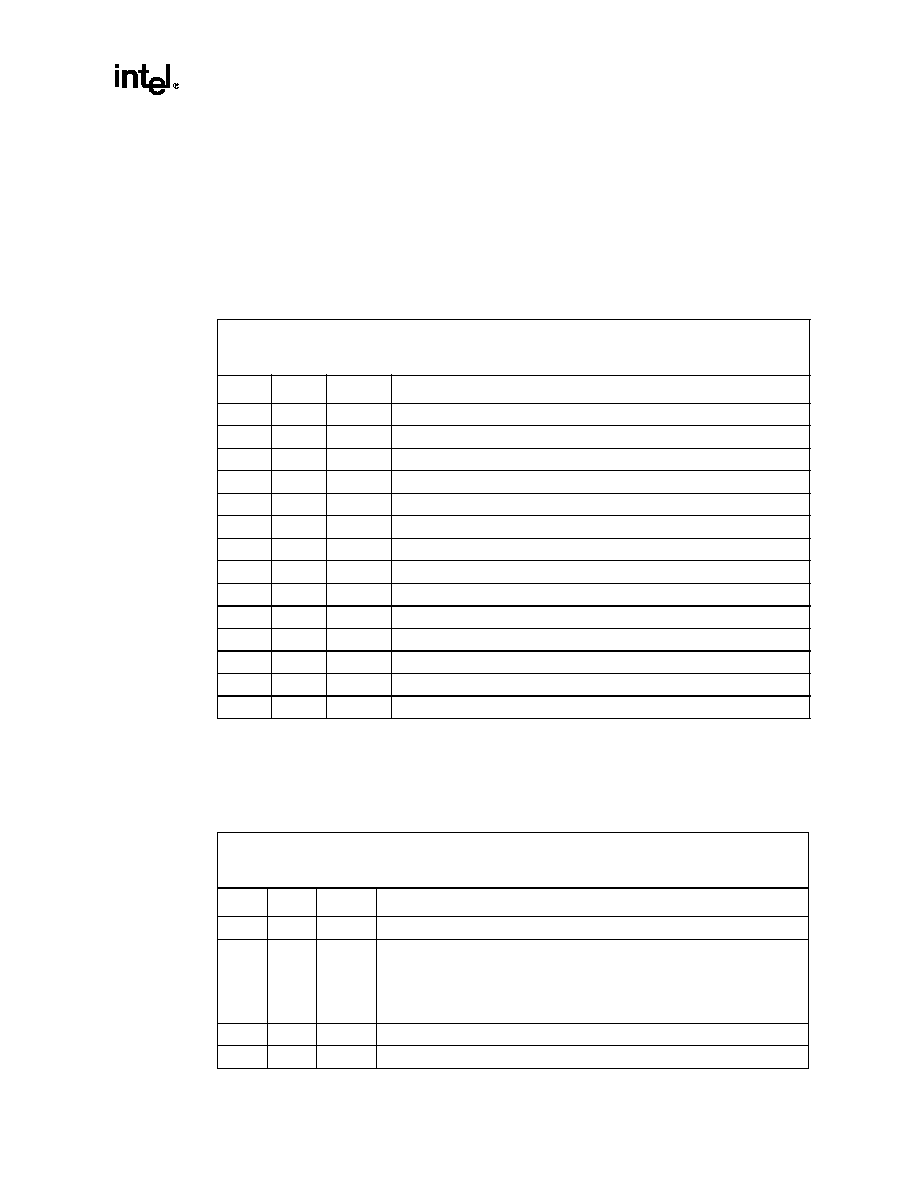

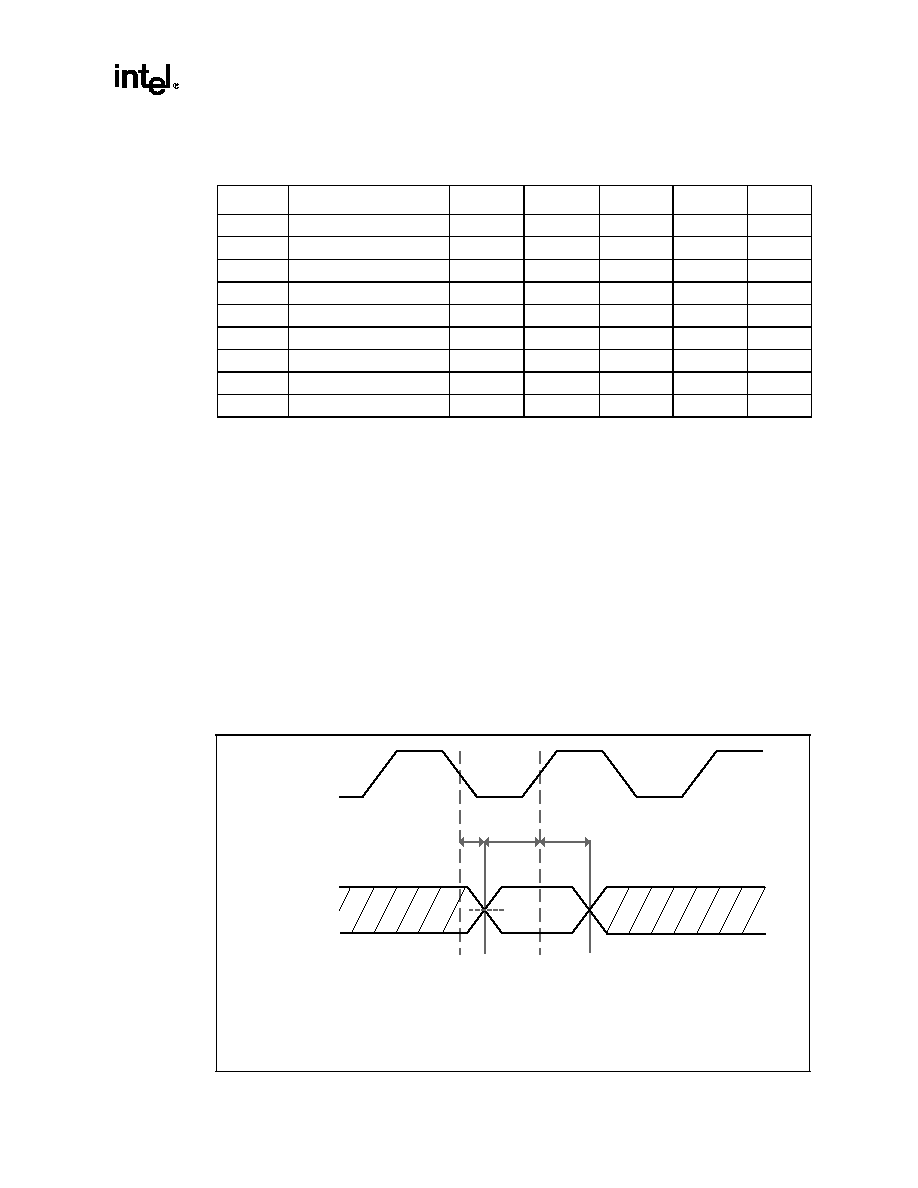

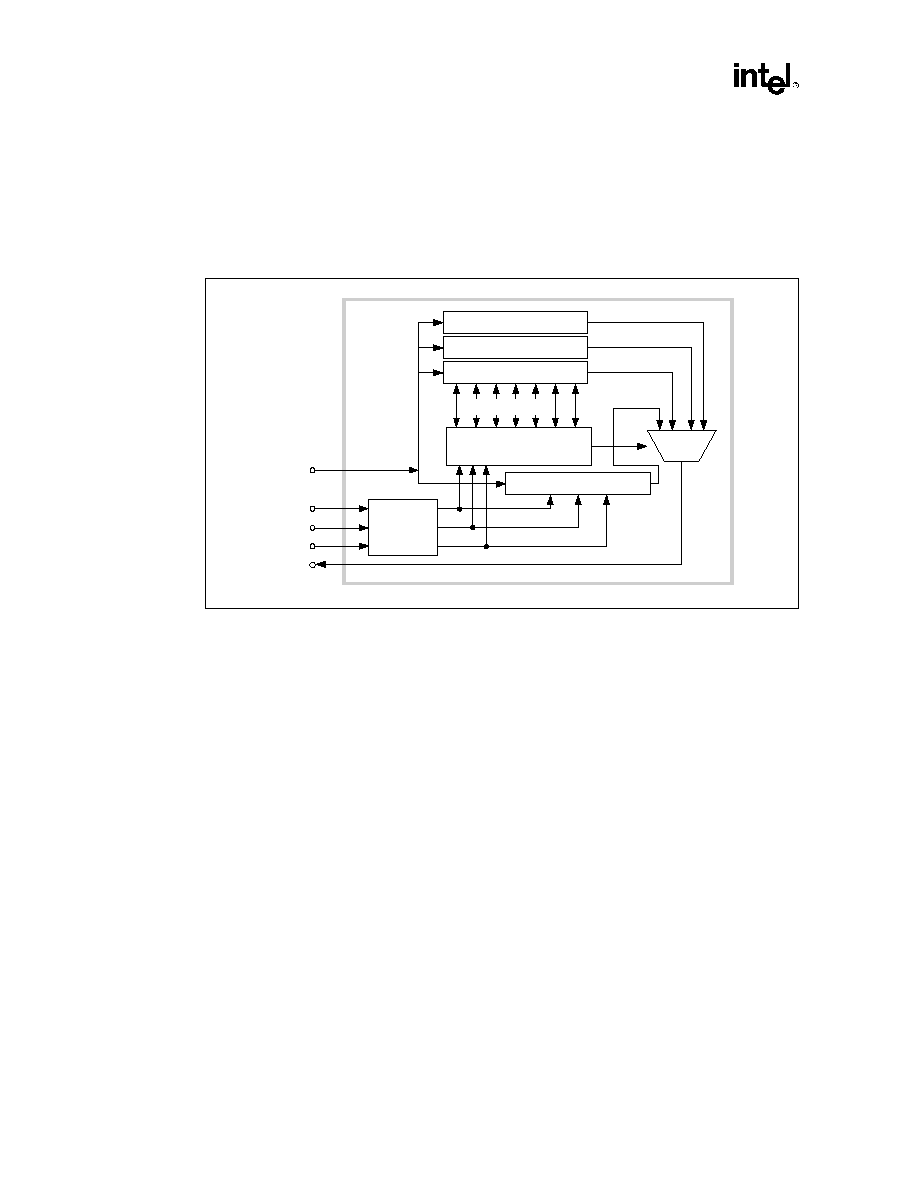

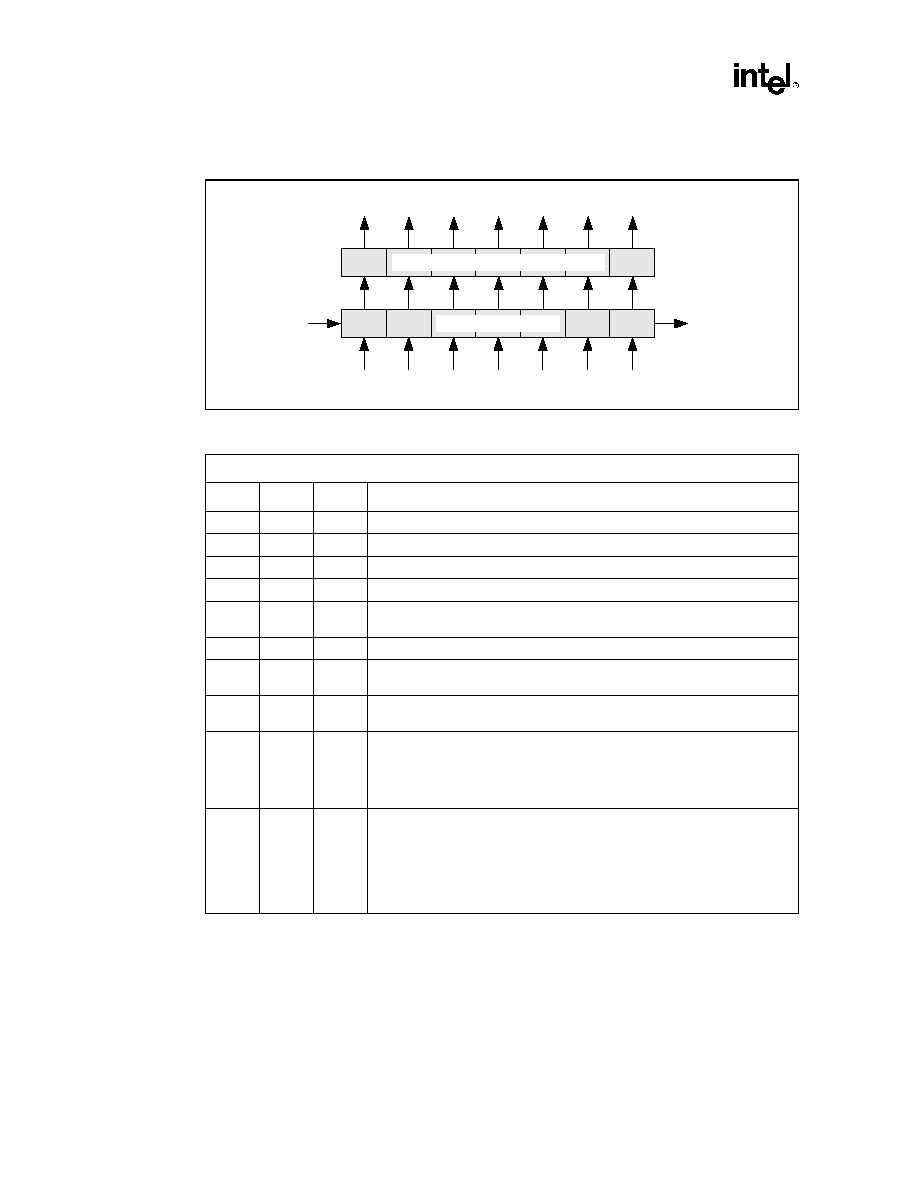

Figure 1-1. SPS Block Diagram

001333

SPPC/SF Interleave 0

SPPC/SF Interleave 2

SP Port 1

SP Port 0

SP Port 3

SP Port 2

SPPC/SF Interleave 3

SP/

SPP

D

SP

/

S

PPD

SPPC/SF Interleave 1

Port 4

Port 5

Port 0

Port 1

Port 2

Port 3

X-Bar

Bypass

Bypass

SP Po

rt

5

SP

Po

r

t

4

SP/SPPD

SP/SPPD

SP/SPPD

SP/SPPD

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

1-3

Introduction

1.3.2

Ports

The SPS has six SPs. Each port consists of a SP block and a Scalability Port Protocol Distributed

(SPPD) block.

The SP block implements the physical layer and link layer of the SP protocol. This interface is

common between all components of the E8870 chipset.

Upon receiving a packet from the SP, the SPPD decodes the header to determine how the packet

should be routed in the SPS. The SPPD routes coherent requests to the appropriate SF interleave

based on address. For some coherent requests, requests may be spawned directly by the SPPD and

sent to the home node. For non-coherent and special transactions, attribute encodings and address

decode are used to determine the packet destination. For responses, packets may be routed to either

the SPPC, or to another port based on information in the packet header. The SPPD also provides

the data path for requests and responses that have data. The SPPD only asserts back pressure to the

SP due to resource limitations.

The six SPs are logically identical. However, the pinout of two of the ports are oriented differently.

This is to enable at least one system configuration where the SPs can be connected without doing

any swizzling of wires on the board.

1.3.3

Interconnect

The SPS uses bypass buses to route request and response packets between the SPPD and SPPC

blocks. This improves performance by "bypassing" the crossbar and decreasing latency. The

bypass buses carry packets from the SPPDs to the SPPCs and from the SPPCs to the SPPDs. Each

pair of SPPD_to_C and SPPC_to_D bypass buses is shared by three ports and two SPPCs. Each

bus can support up to 200 MT/s. The bypass buses can support a maximum of 800 MT/s from all

the ports to the SPPCs, assuming evenly distributed traffic.

A six-ported crossbar switch is also used to route packets from one SP port to another across the

SPS. The crossbar switch has two lanes per port; one allocated to requests, and the other to

responses. Each crossbar port can send and receive data at the full SP port bandwidth.

1.4

Reference Documents

∑

Intel

Æ

E8870 Scalable Node Controller (SNC) Datasheet

∑

Intel

Æ

E8870DH DDR Memory Hub (DMH) Datasheet

∑

Intel

Æ

E8870IO Server I/O Hub (SIOH) Datasheet

∑

Intel

Æ

82870P2 64-bit Hub 2 (P64H2) Datasheet

∑

Intel

Æ

82801DB I/O Controller Hub4 (ICH4) Datasheet

∑

SMBus Specification, Revision 2.0

∑

PCI Local Bus Specification, Revision 2.2

∑

PCI-X Local Bus Specification, Revision 1.0

Introduction

1-4

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

1.5

Revision History

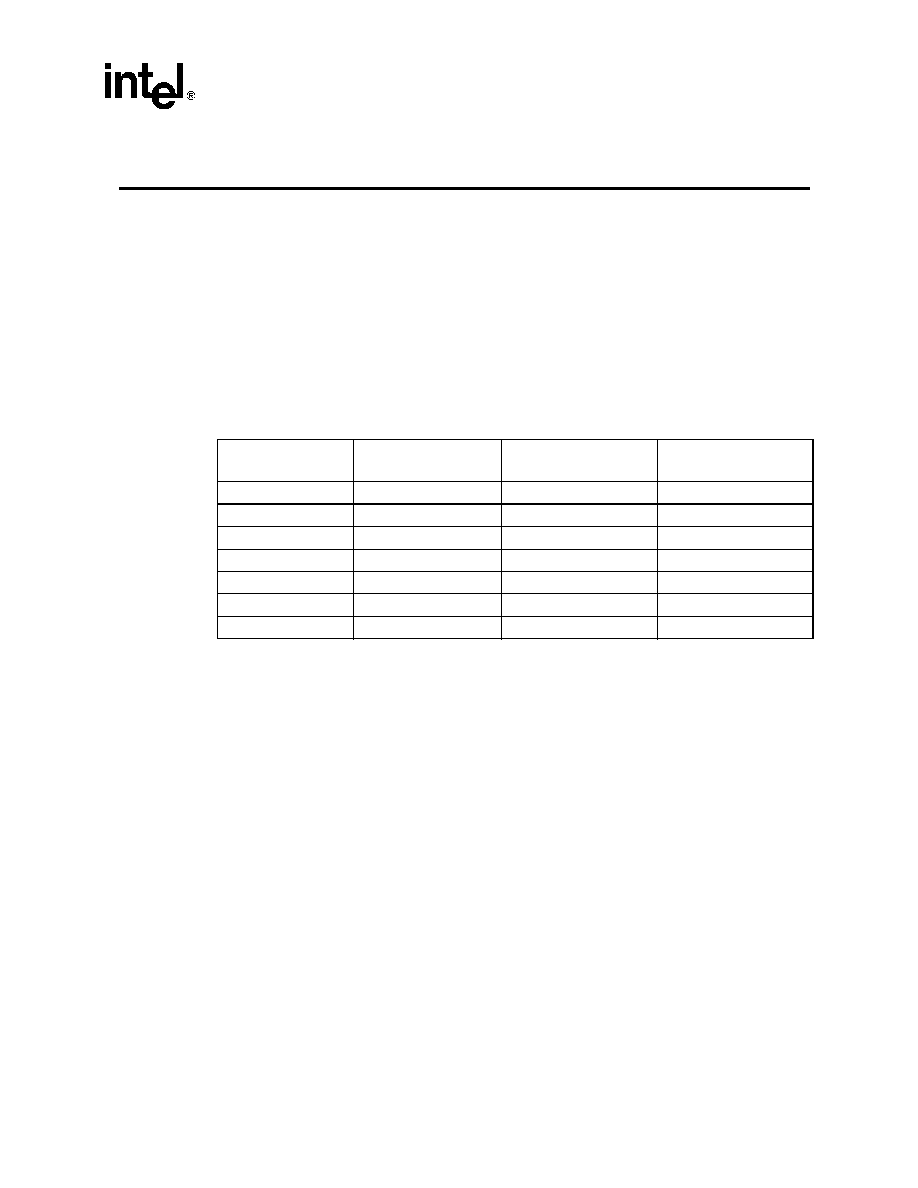

Revision

Number

Description

Date

-001

Initial release of the document.

November 2002

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

2-1

Signal Descriptions

2

2.1

Conventions

The terms assertion and deassertion are used extensively when describing signals, to avoid

confusion when working with a mix of active-high and active-low signals. The term assert, or

assertion, indicates that the signal is active, independent of whether the active level is represented

by a high or low voltage. The term deassert, or deassertion, indicates that the signal is inactive.

Signal names may or may not have a "#" appended to them. The "#" symbol at the end of a signal

name indicates that the active, or asserted state occurs when the signal is at a low voltage level.

When "#" is not present after the signal name the signal is asserted when at the high voltage level.

When discussing data values used inside the component, the logical value is used. For instance.,a

data value described as "1101b" would appear as "1101b" on an active-high bus, and as "0010b"

on an active-low bus. When discussing the assertion of a value on the actual signal, the physical

value is used; i.e. asserting an active-low signal produces a "0" value on the signal.

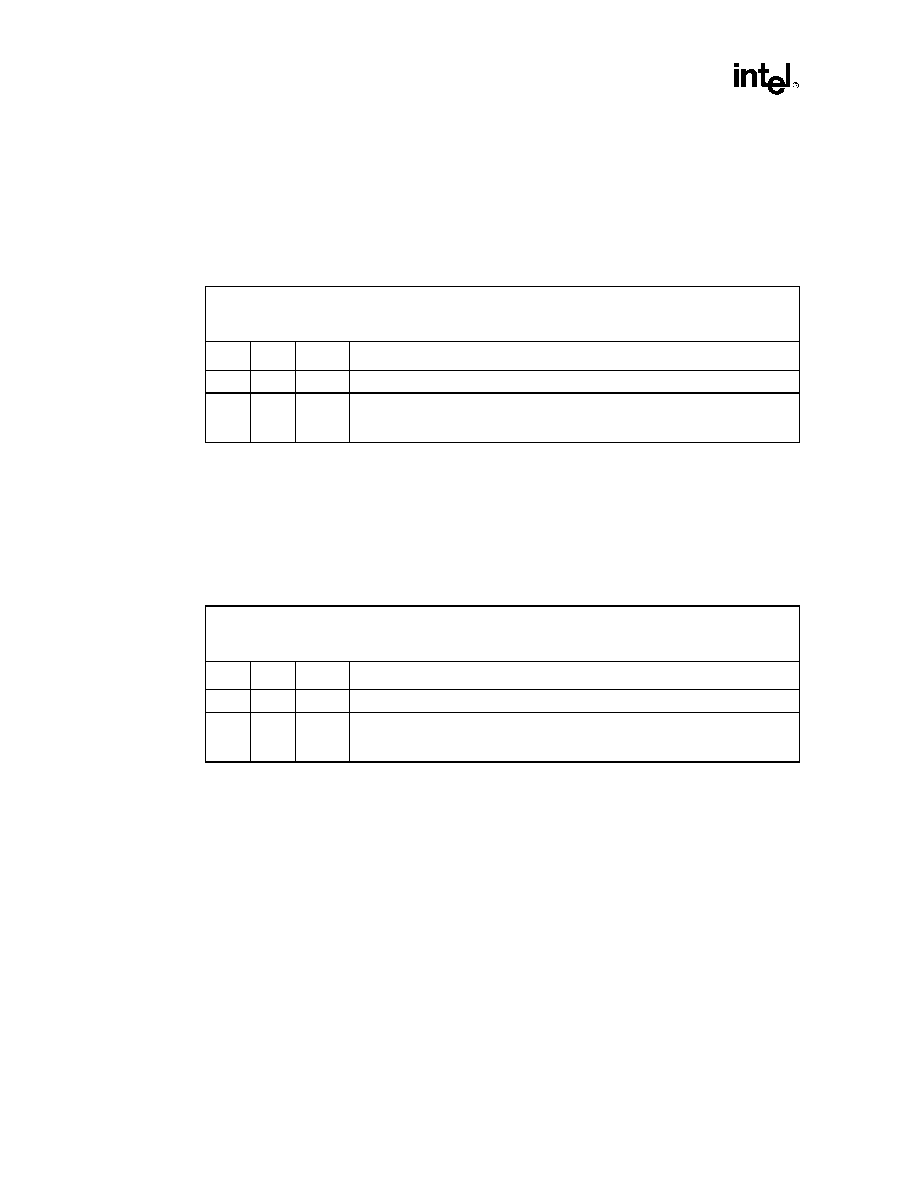

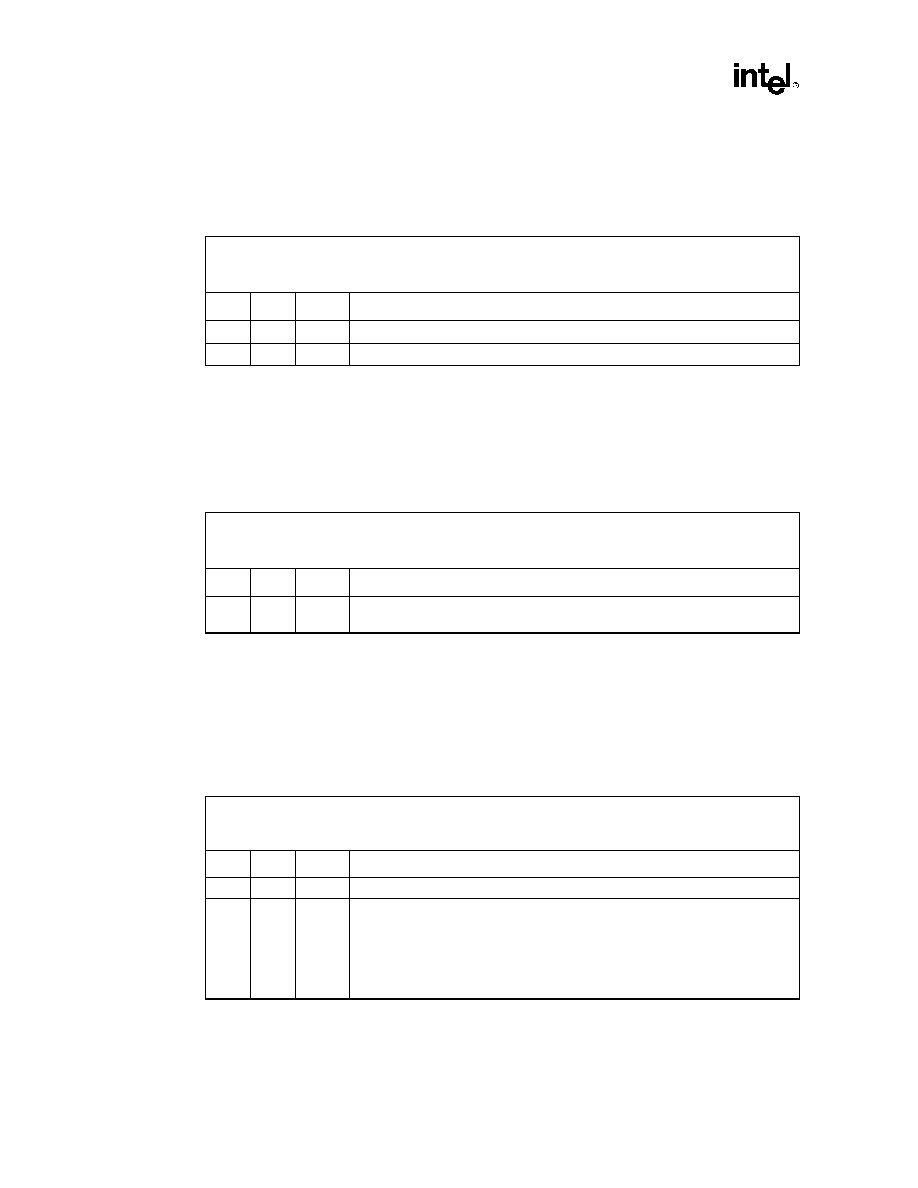

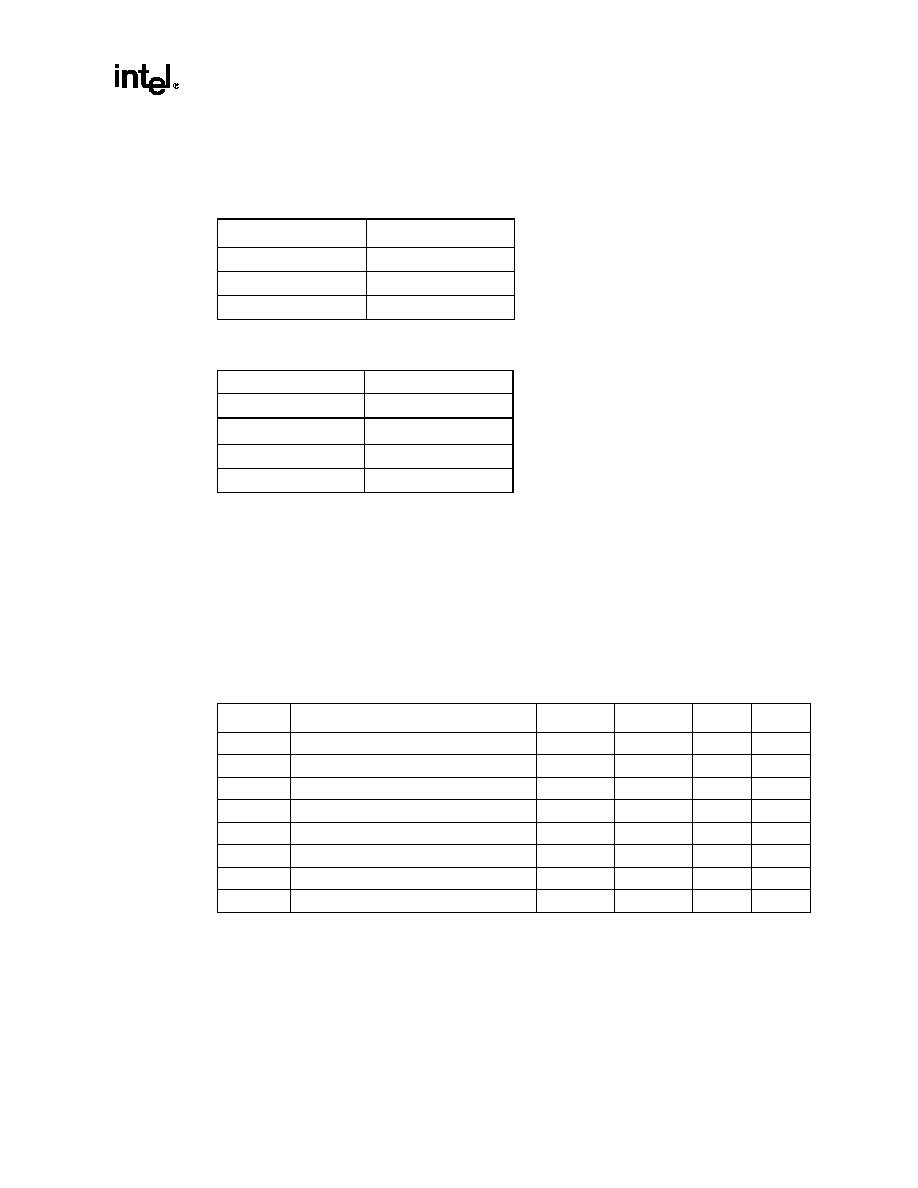

Table 2-1

and

Table 2-2

list the reference terminology used later for buffer technology types (e.g.

SBD, etc.) and buffering signal types (e.g. input, output, etc.).

Some signals or groups of signals have multiple versions. These signal groups may represent

distinct, but similar, ports or interfaces or they may represent identical copies of the signal used to

reduce loading effects.

Table 2-3

shows the conventions the SPS uses

.

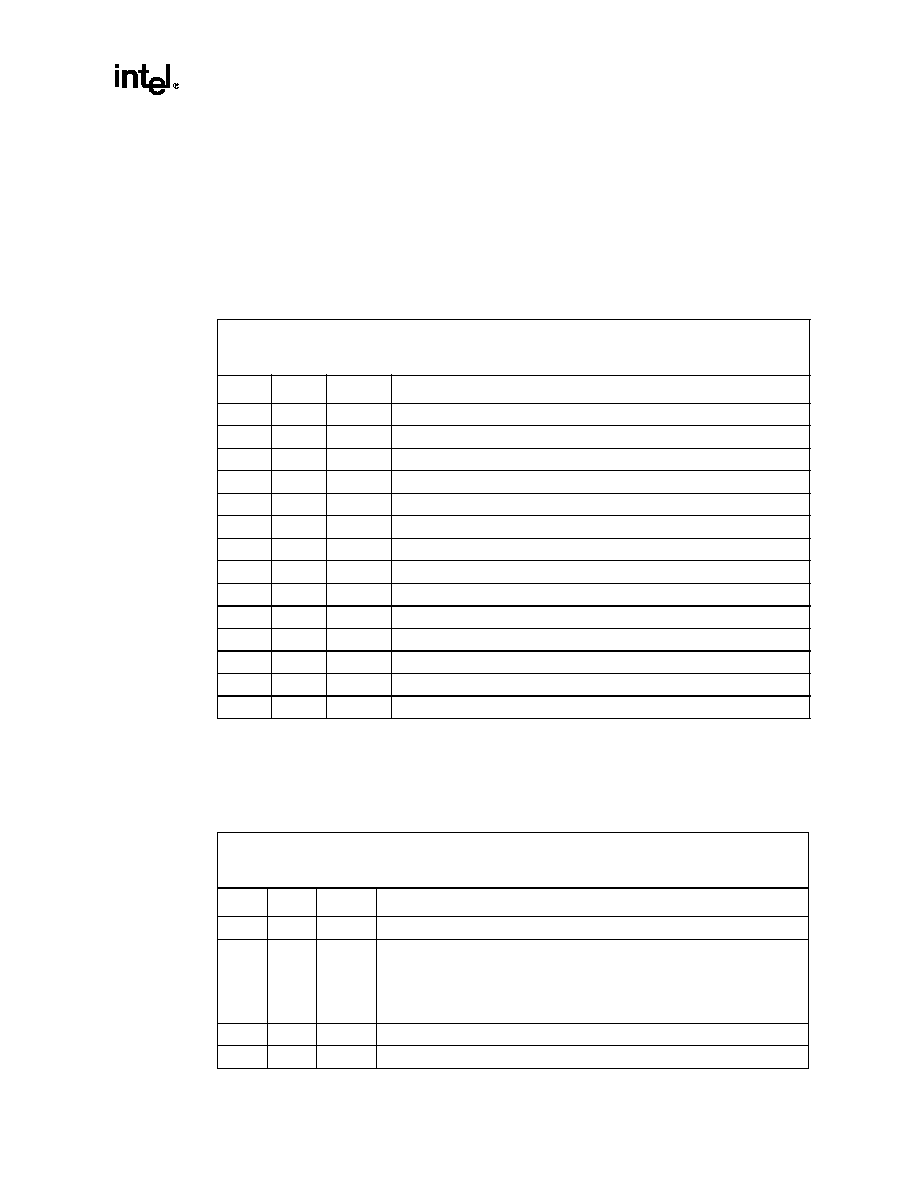

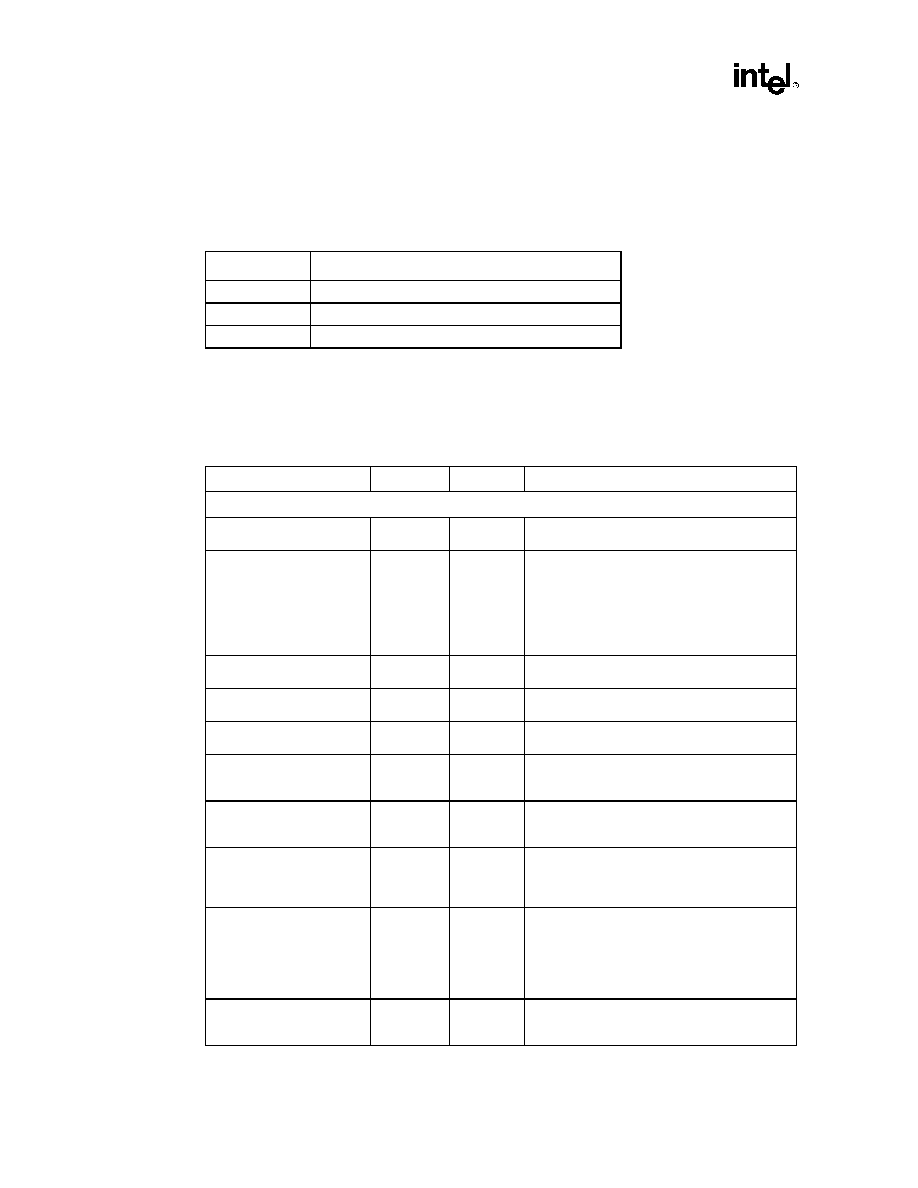

Table 2-1. Buffer Technology Types

Buffer Type

Description

SBD

Simultaneous bi-directional.

Differential

A differential input that requires a voltage reference or

the signal compliment.

SPCMOS

CMOS type I/O with Schmidt trigger input.

CMOS OD

CMOS open drain I/O.

SMBus OD

SMBus open drain I/O with Schmidt trigger input with a

voltage level of 3.3V and max. frequency of 100 KHz.

JTAG

1.5V JTAG I/O.

Analog

Typically a voltage reference or specialty power supply.

Table 2-2. Buffer Signal Directions

Buffer Direction

Description

I

Input pin.

O

Output pin.

I/O

Bi-directional (input/output) pin.

Signal Descriptions

2-2

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

Typically, upper case groups (e.g. "A, B, C") represent functionally similar, but logically distinct,

signals. Each signal provides an independent control, and may or may not be asserted at the same

time as the other signals in the grouping. In contrast, lower case groups, (e.g. "a, b, c") typically

represent identical duplicates of a common signal. Such duplicates are provided to reduce loading.

2.2

SPS Pin List

Table 2-3. Signal Naming Conventions

Convention

Expands to

RR{0/1/2}XX

Expands to: RR0XX, RR1XX, and RR2XX.

RR[2:0]

Denotes a bus and expands to: RR2, RR1, and RR0.

RR# or RR[2:0]#

Denotes an active low signal or bus.

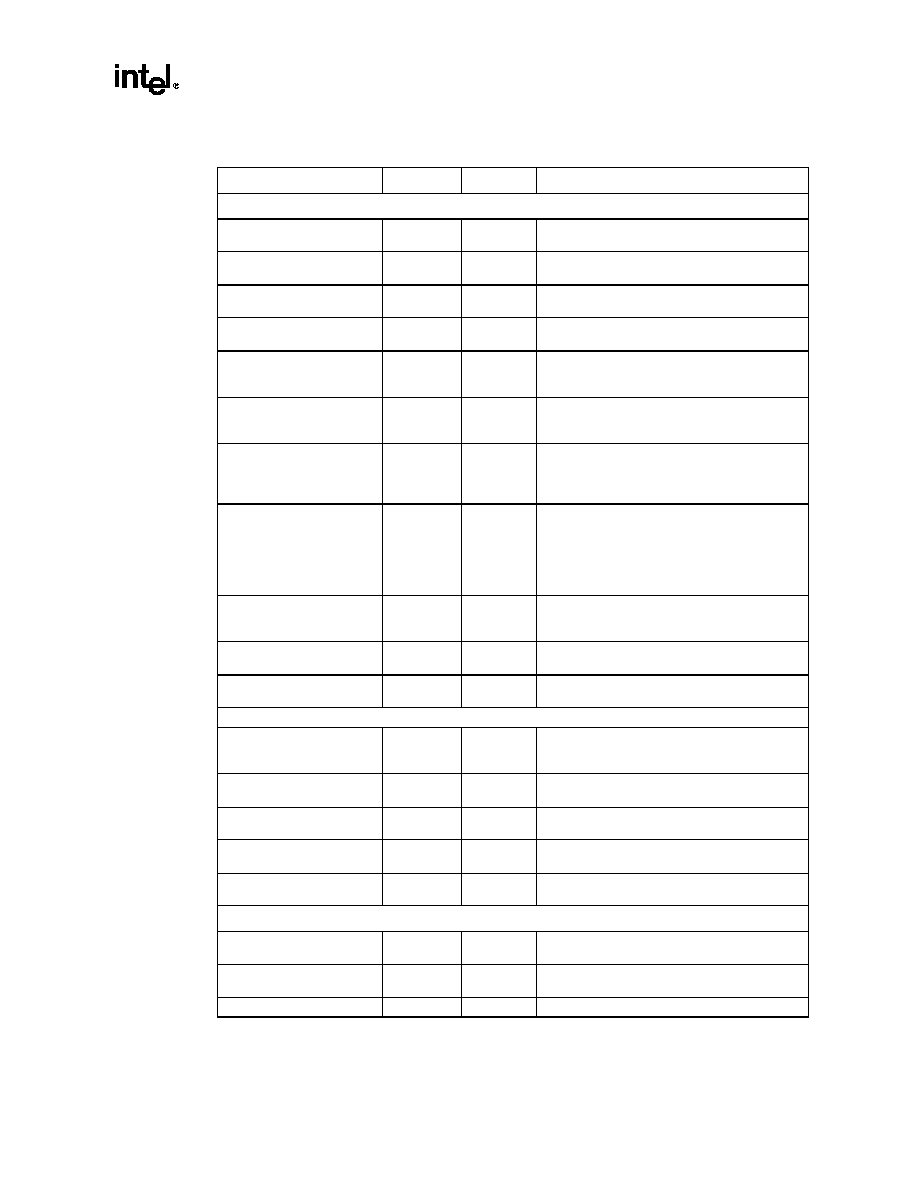

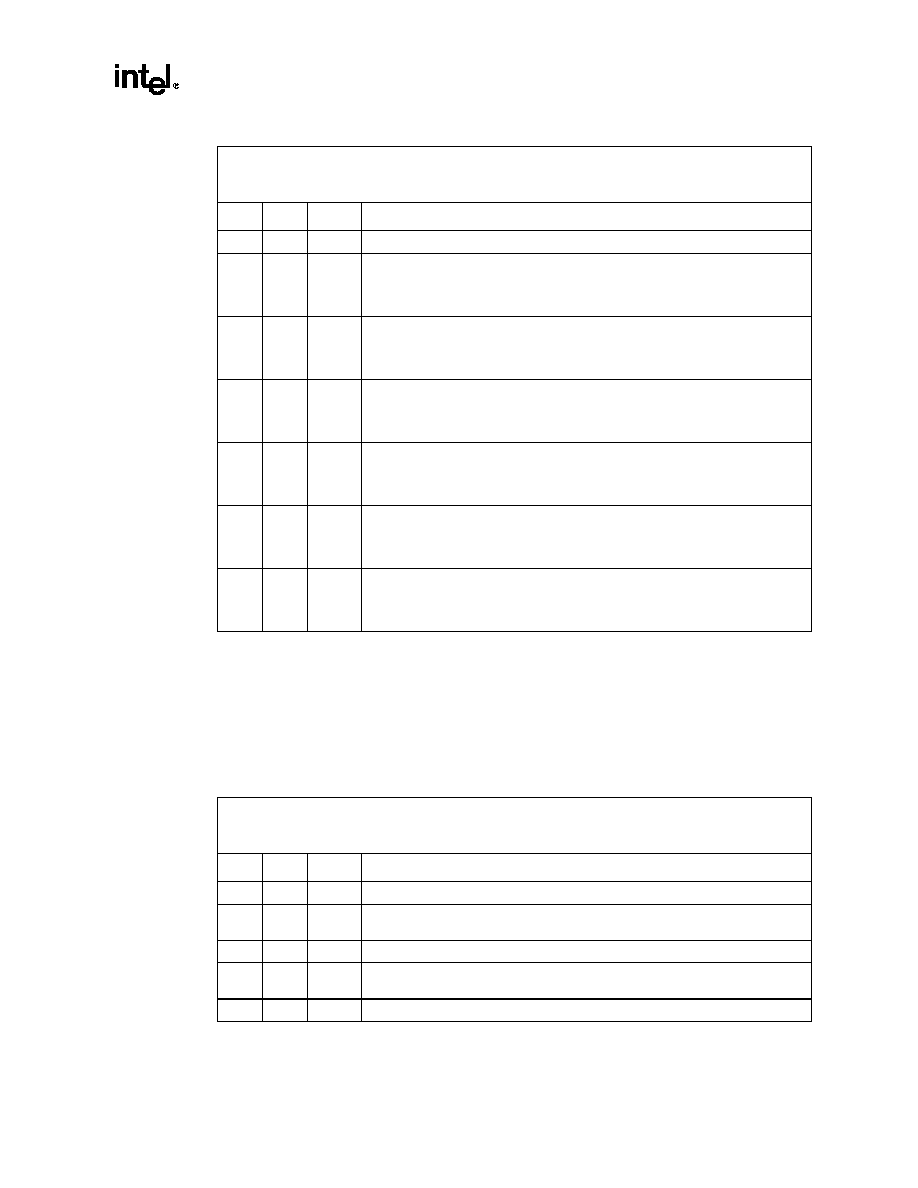

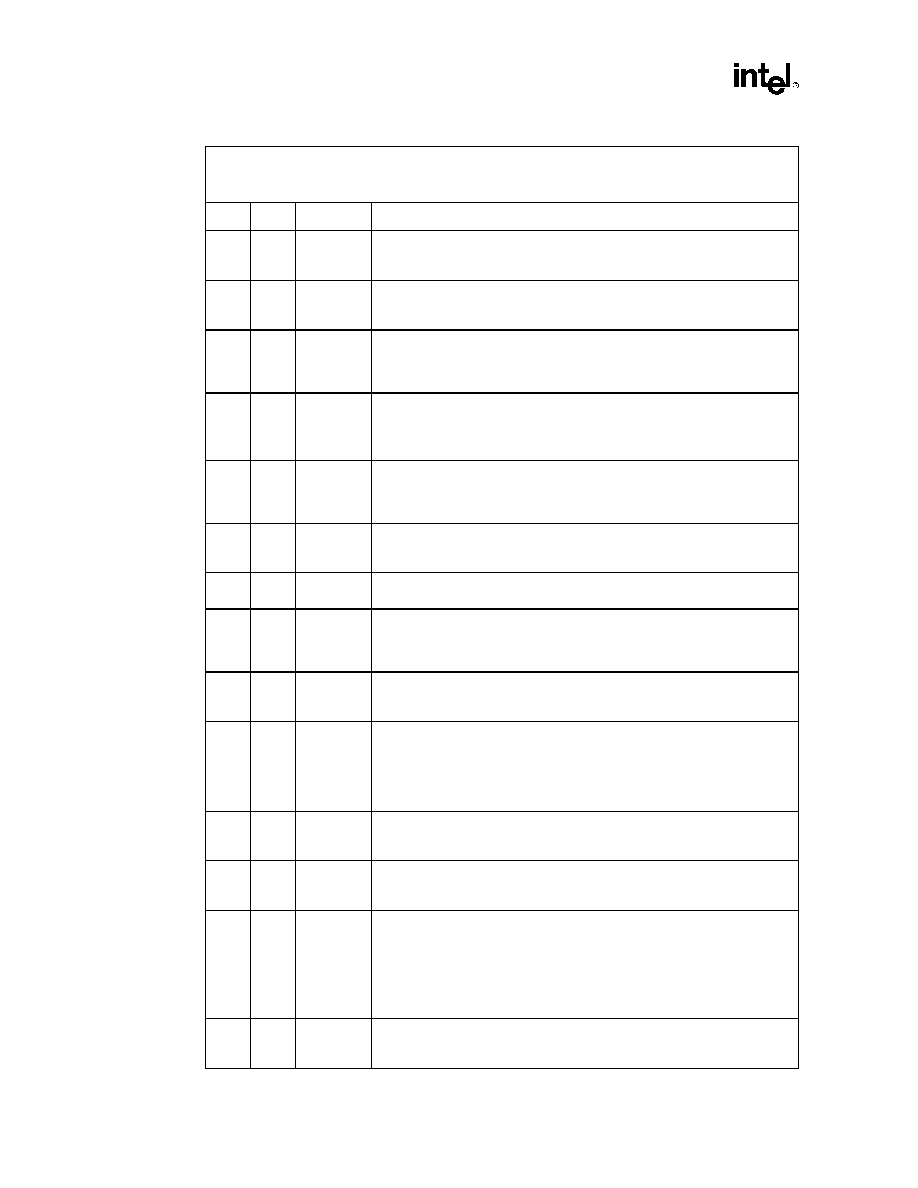

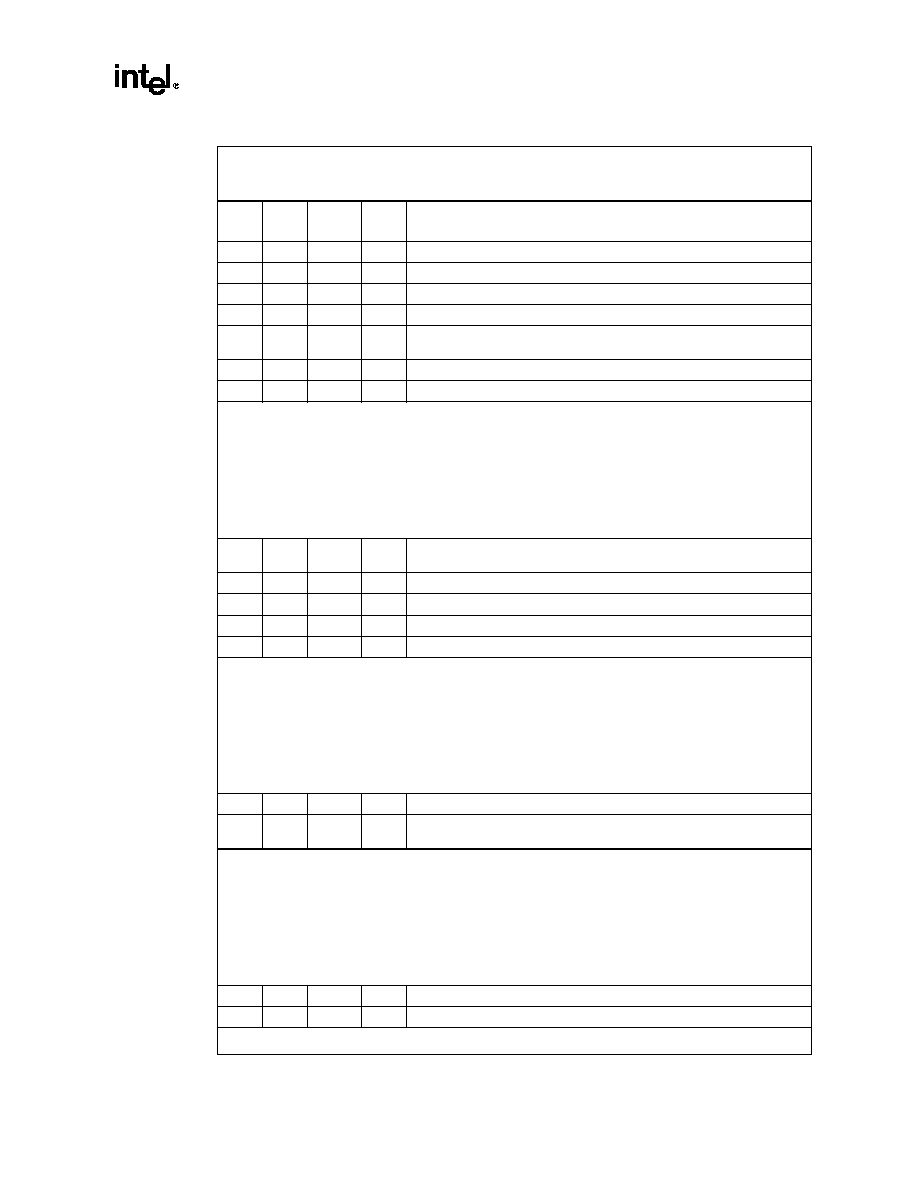

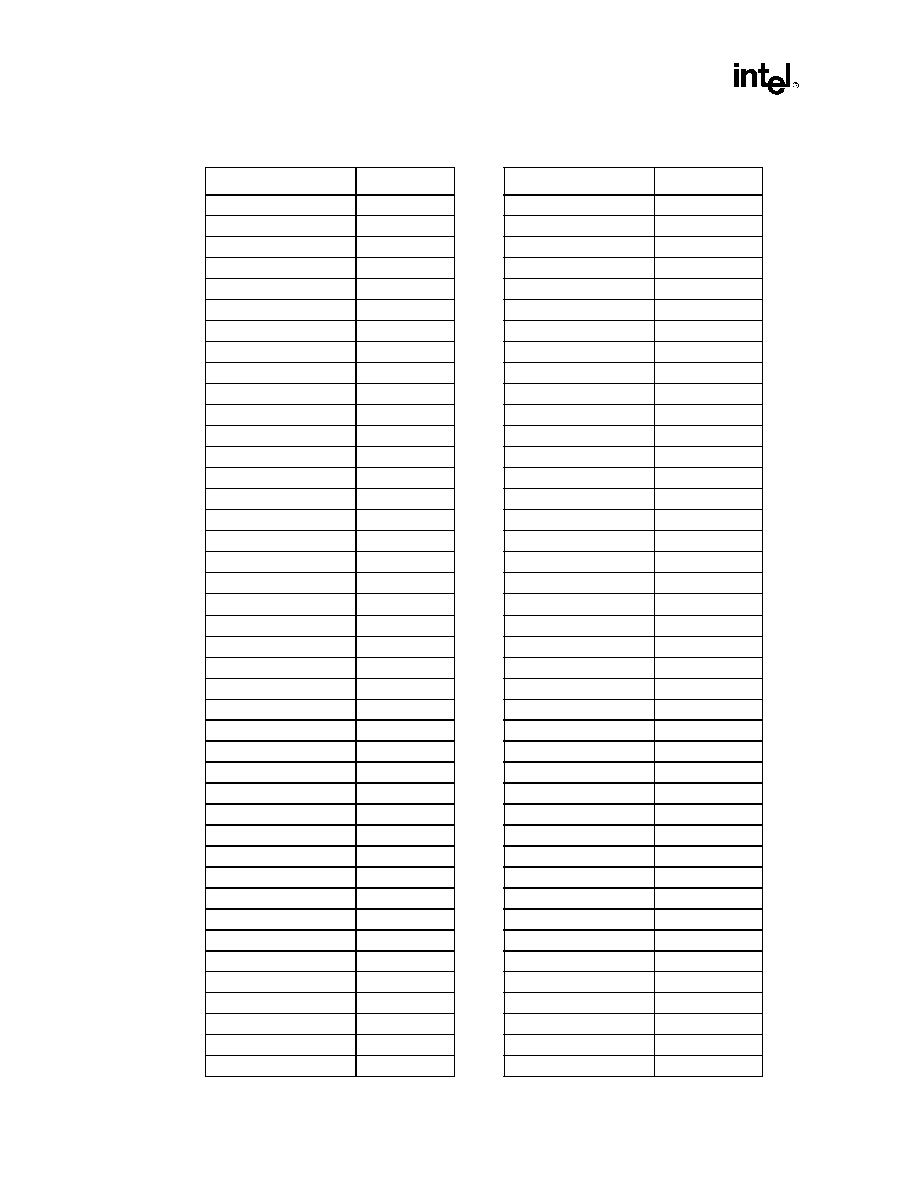

Table 2-4. SPS Pin List

Signal

Type

Frequency

Description

Scalability Ports ≠ 72 Pins Total each Port

SP{0/1/2/3/4/5}ZUPD[1:0]

I

Analog

N/A

Impedance Update: Used to adjust the

impedance of I/O drivers.

SP{0/1/2/3/4/5}SYNC

I/O

SPCMOS

N/A

Reset Synchronization: Provides

synchronization between ports for impedance

control and reference voltage adjustment. This

signal is also used by the SP reset logic to

determine when SP comes out of reset.

SP{0/1/2/3/4/5}SYNC is released when ports at

both ends of the link are ready.

SP{0/1/2/3/4/5}PRES

I

SPCMOS

N/A

Scalability Port Present: Signals the Scalability

Port of an impending hot plug event.

SP{0/1/2/3/4/5}AVREFH[3:0]

I

Analog

N/A

Strand A Voltage Reference: 3/4 VCC

Reference.

SP{0/1/2/3/4/5}AVREFL[3:0]

I

Analog

N/A

Strand A Voltage Reference: 1/4 VCC

Reference.

SP{0/1/2/3/4/5}ASTBP[1:0]

I/O

SBD

400 MHz

P Strobes: Positive phase data strobes for

strand A to transfer data at the 2x rate

(800 MHz).

SP{0/1/2/3/4/5}ASTBN[1:0]

I/O

SBD

400 MHz

N Strobes: Negative phase data strobes for

strand A to transfer data at the 2x rate

(800 MHz).

SP{0/1/2/3/4/5}AD[15:0]

I/O

SBD

800 MHz

Data Bus: 16 bits of the data portion of a PHIT

on strand A (D[15:0]). These bits are SSO

encoded. SP{0/1/2/3/4/5}ASSO determines if

these are out of an inverter or not.

SP{0/1/2/3/4/5}AEP[2:0]

I/O

SBD

800 MHz

Parity/ECC: Two of these signals carry the ECC

information for the data flits. There are four bits of

ECC for each data PHIT. The header flits are not

ECC protected. The third signal is for parity. Each

PHIT is always protected by two bits of parity.

AEP[1:0] is GEP[1:0] and AEP[2] is TEP[0].

SP{0/1/2/3/4/5}ALLC

I/O

SBD

800 MHz

Link Layer Control: For each PHIT these

signals carry two of the four bits of link layer

control information.

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

2-3

Signal Descriptions

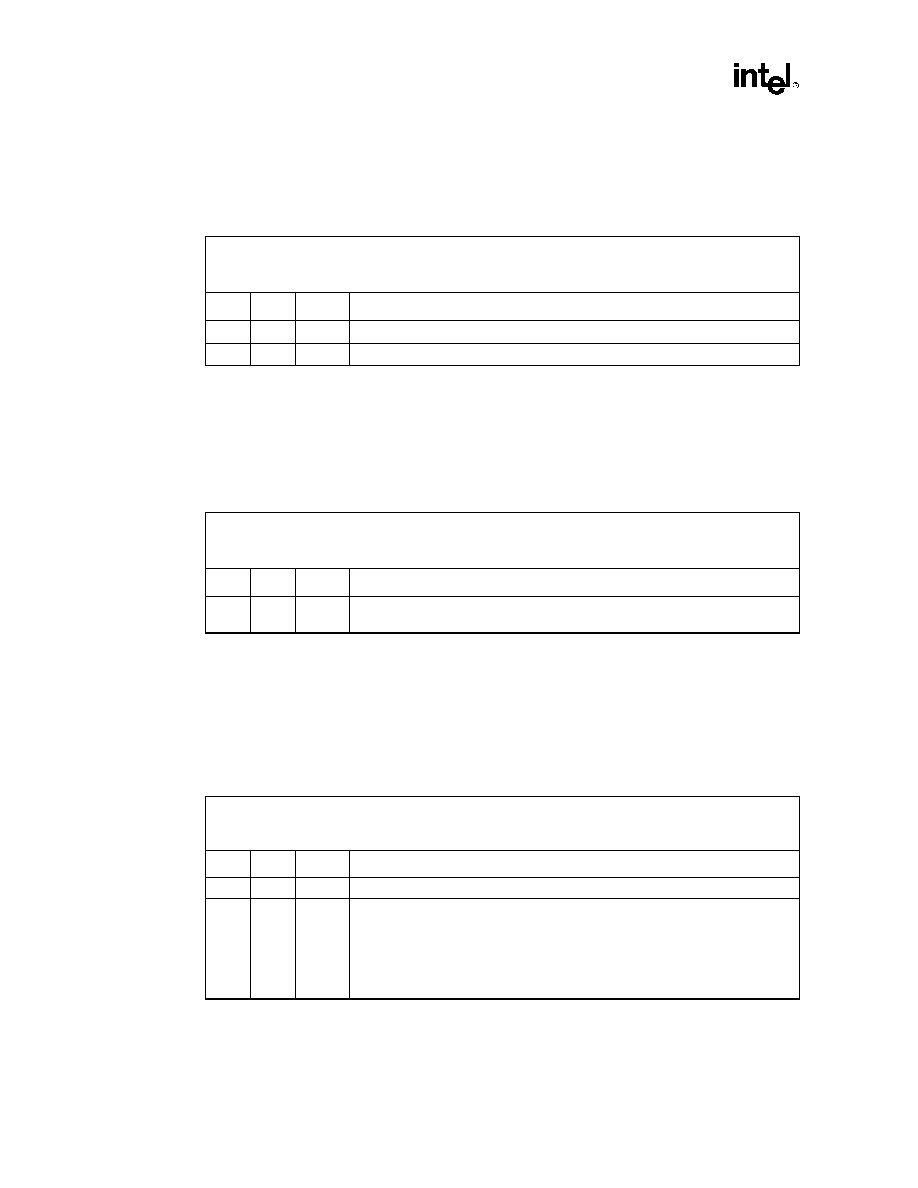

Scalability Ports ≠ 72 Pins Total each Port (Continued)

SP{0/1/2/3/4/5}ASSO

I/O

SBD

800 MHz

SSO Encode: This signal is asserted to indicate

that the data bits over Strand A are inverted.

SP{0/1/2/3/4/5}ARSVD

I/O

SBD

N/A

Reserved

SP{0/1/2/3/4/5}BVREFH[3:0]

I

Analog

N/A

Strand B Voltage Reference:

3/4 VCC Reference.

SP{0/1/2/3/4/5}BVREFL[3:0]

I

Analog

N/A

Strand B Voltage Reference:

1/4 VCC Reference.

SP{0/1/2/3/4/5}BSTBP[1:0]

I/O

SBD

400 MHz

P Strobes: Positive phase data strobes for

strand B to transfer data at the 2x rate

(800 MHz).

SP{0/1/2/3/4/5}BSTBN[1:0]

I/O

SBD

400 MHz

N Strobes: Negative phase data strobes for

strand B to transfer data at the 2x rate

(800 MHz).

SP{0/1/2/3/4/5}BD[15:0]

I/O

SBD

800 MHz

Data Bus: 16 bits of the data portion of a PHIT

on strand B (D[31:16]). These bits are SSO

encoded. SP{0/1/2/3/4/5}BSSO determines if

these are out of an inverter or not.

SP{0/1/2/3/4/5}BEP[2:0]

I/O

SBD

800 MHz

Parity/ECC: Two of these signals carry the ECC

information for the data flits. There are four bits of

ECC for each data PHIT. The header flits are not

ECC protected. The third signal is for parity. Each

PHIT is always protected by two bits of parity.

BEP[1:0] is GEP[3:2] and BEP[2] is TEP[1].

SP{0/1/2/3/4/5}BLLC

I/O

SBD

800 MHz

Link Layer Control: For each PHIT these

signals carry two of the four bits of link layer

control information.

SP{0/1/2/3/4/5}BSSO

I/O

SBD

800 MHz

SSO Encode: This signal is asserted to indicate

that the data bits over Strand B are inverted.

SP{0/1/2/3/4/5}BRSVD

I/O

SBD

N/A

Reserved

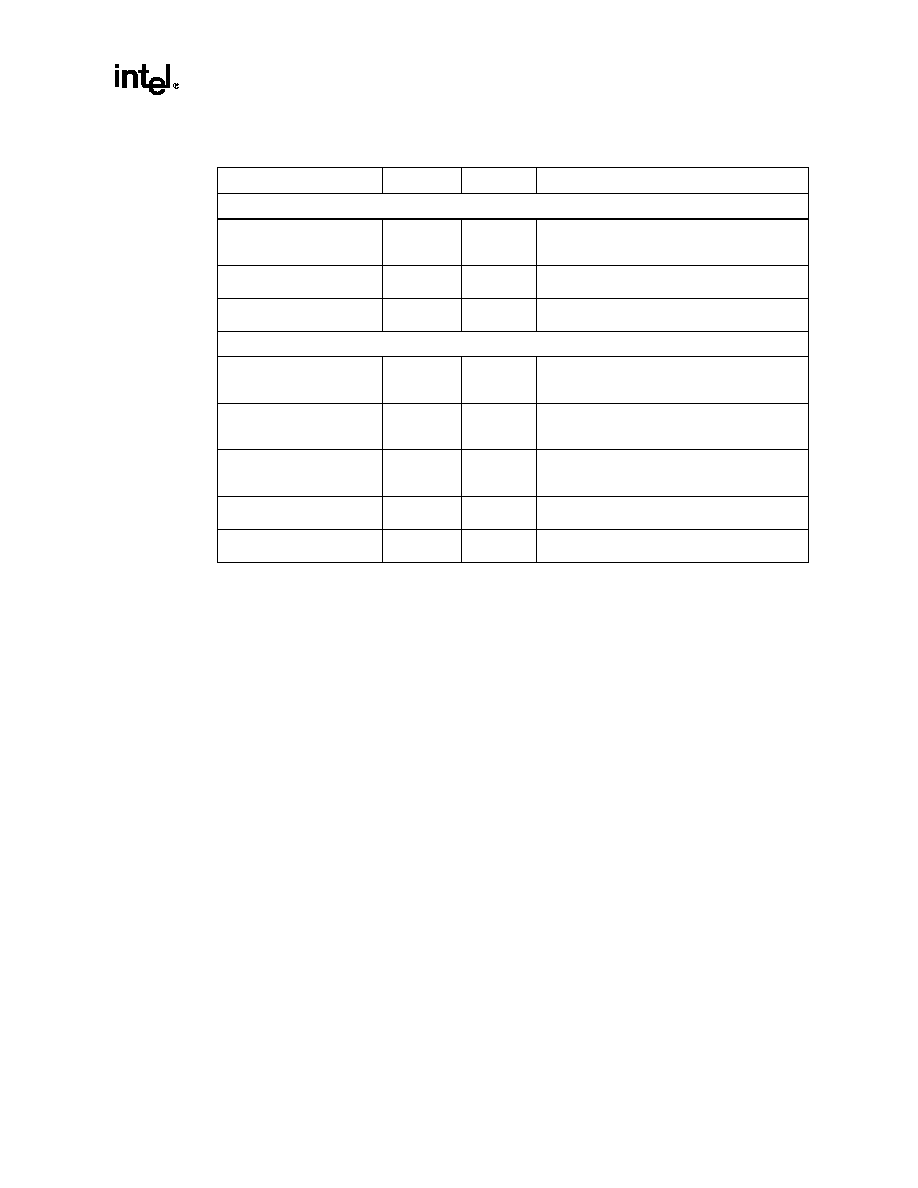

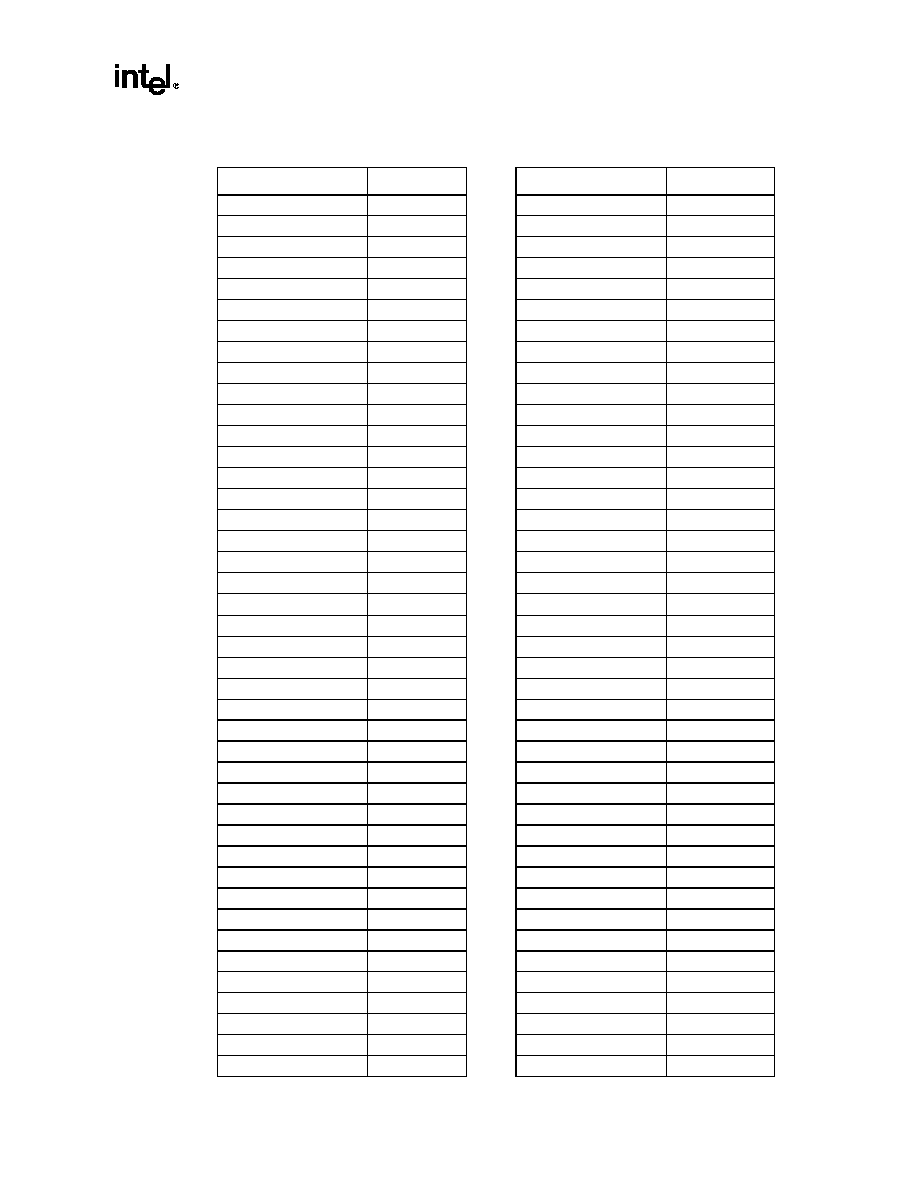

Clocking ≠ 5 Pins Total

SYSCLK

I

Differential

200 MHz

SYS Clock: This is the 200 MHz differential clock

reference input to the SPS core. The system

board logic generates this signal.

SYSCLK#

I

Differential

200 MHz

SYS Clock Complement: 200 MHz Clock

Complement.

LVHSTLODTEN

I

CMOS

N/A

On-die Termination: SYSCLK and SYSCLK#

on-die termination enable.

VCCA

I

Analog

N/A

Analog VCC Voltage.

VSSA

I

Analog

N/A

Analog VSS Voltage.

System Management ≠ 3 Pins Total

SCL

I/O

SMBus OD

SCL

SMBus Clock: Provides synchronous operation

of the SMBus bus.

SDA

I/O

SMBus OD

SCL

SMBus Addr/Data: Used for data transfer and

arbitration on the SMBus bus.

VCC33

Analog

N/A

Vcc3.3: Voltage reference for 3.3v I/Os.

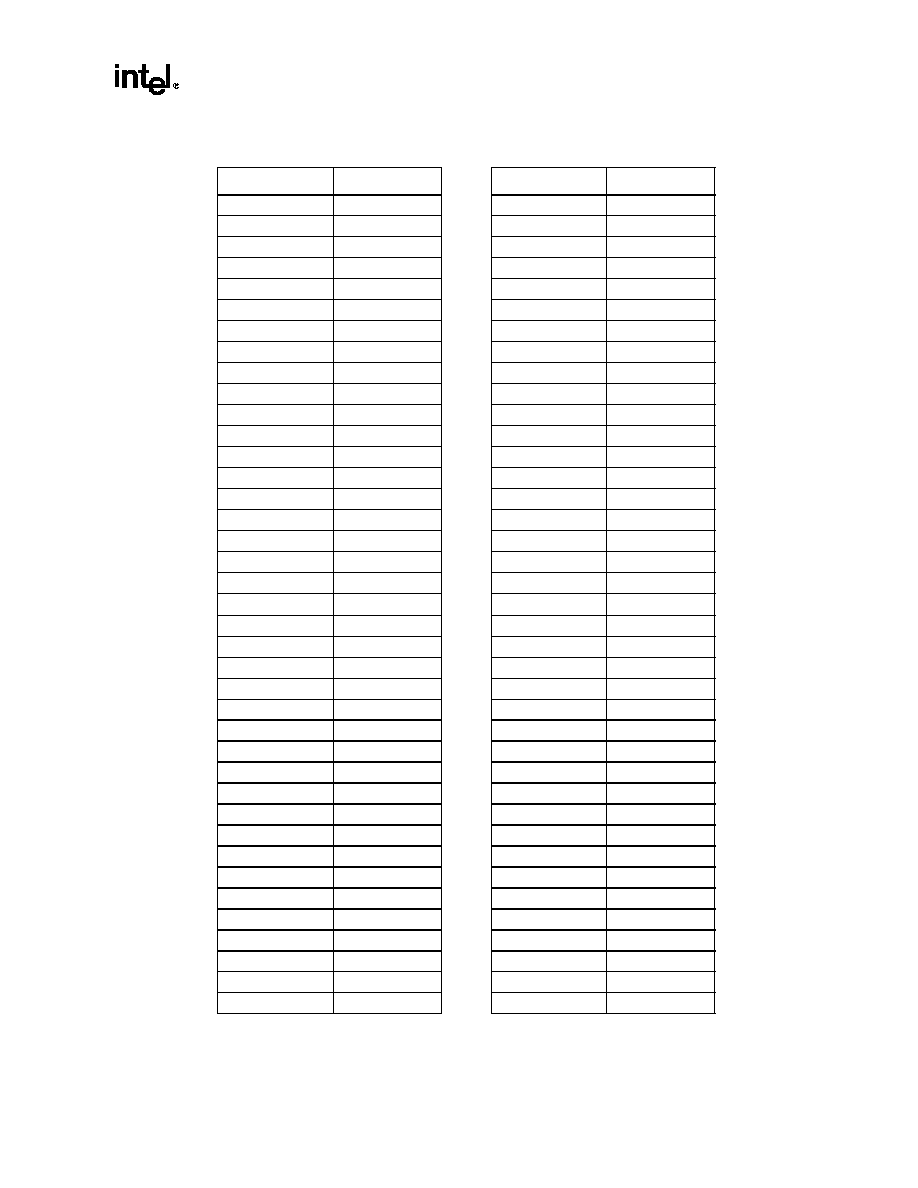

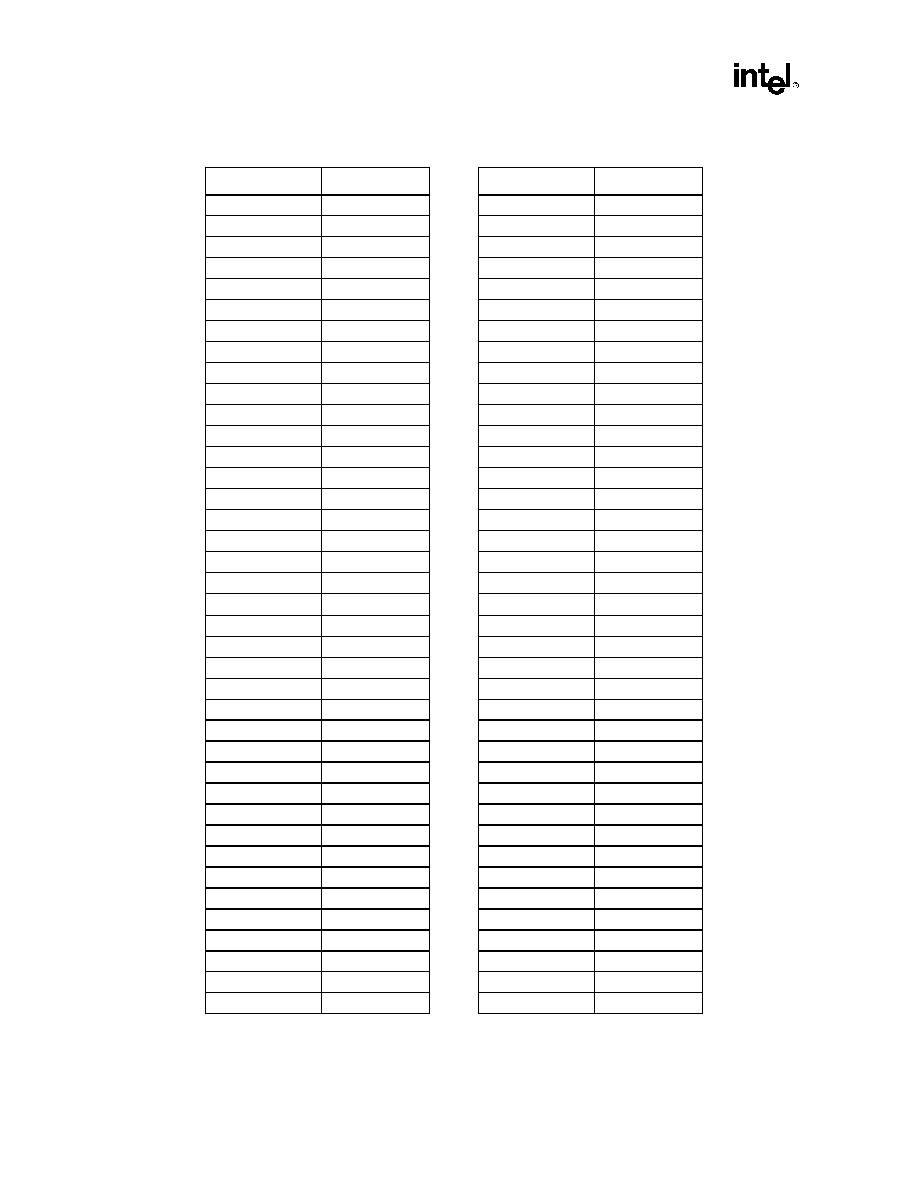

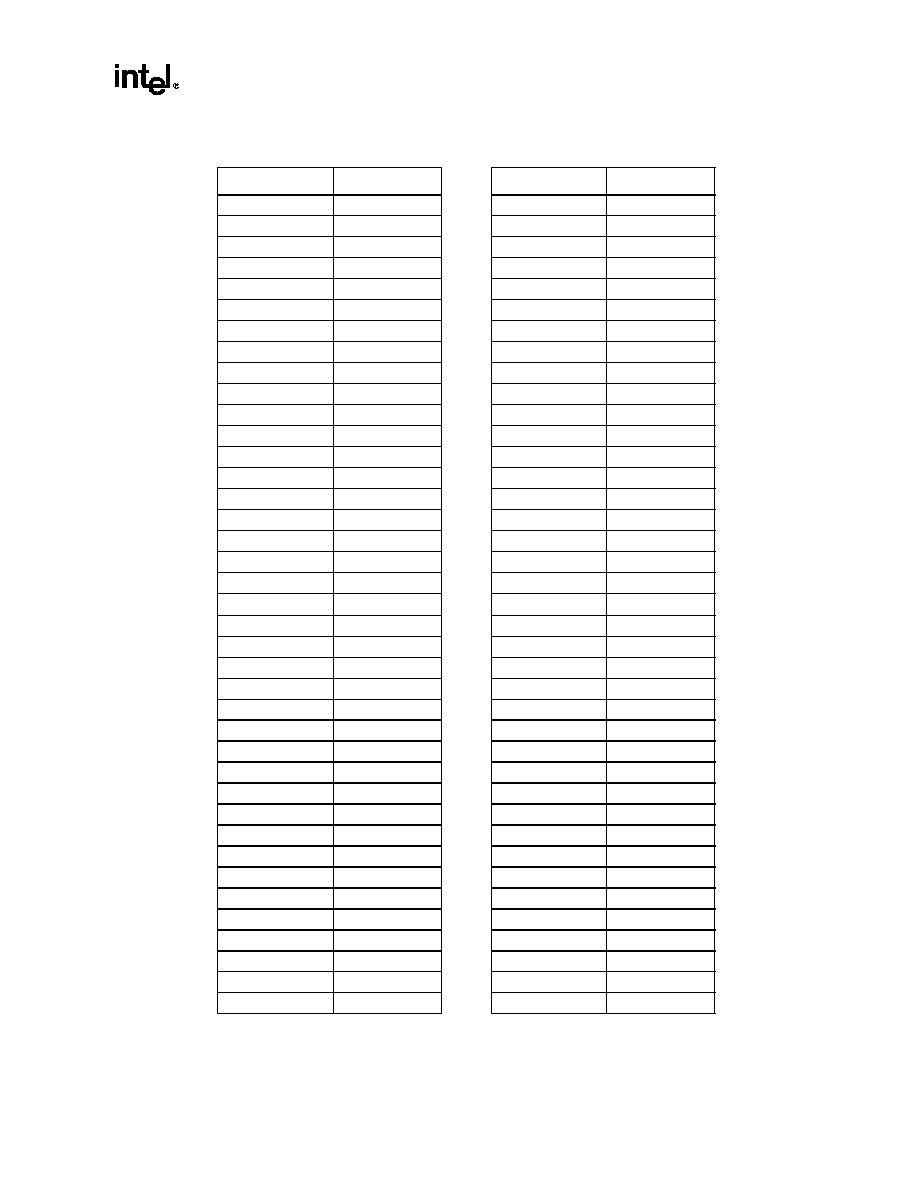

Table 2-4. SPS Pin List (Continued)

Signal

Type

Frequency

Description

Signal Descriptions

2-4

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

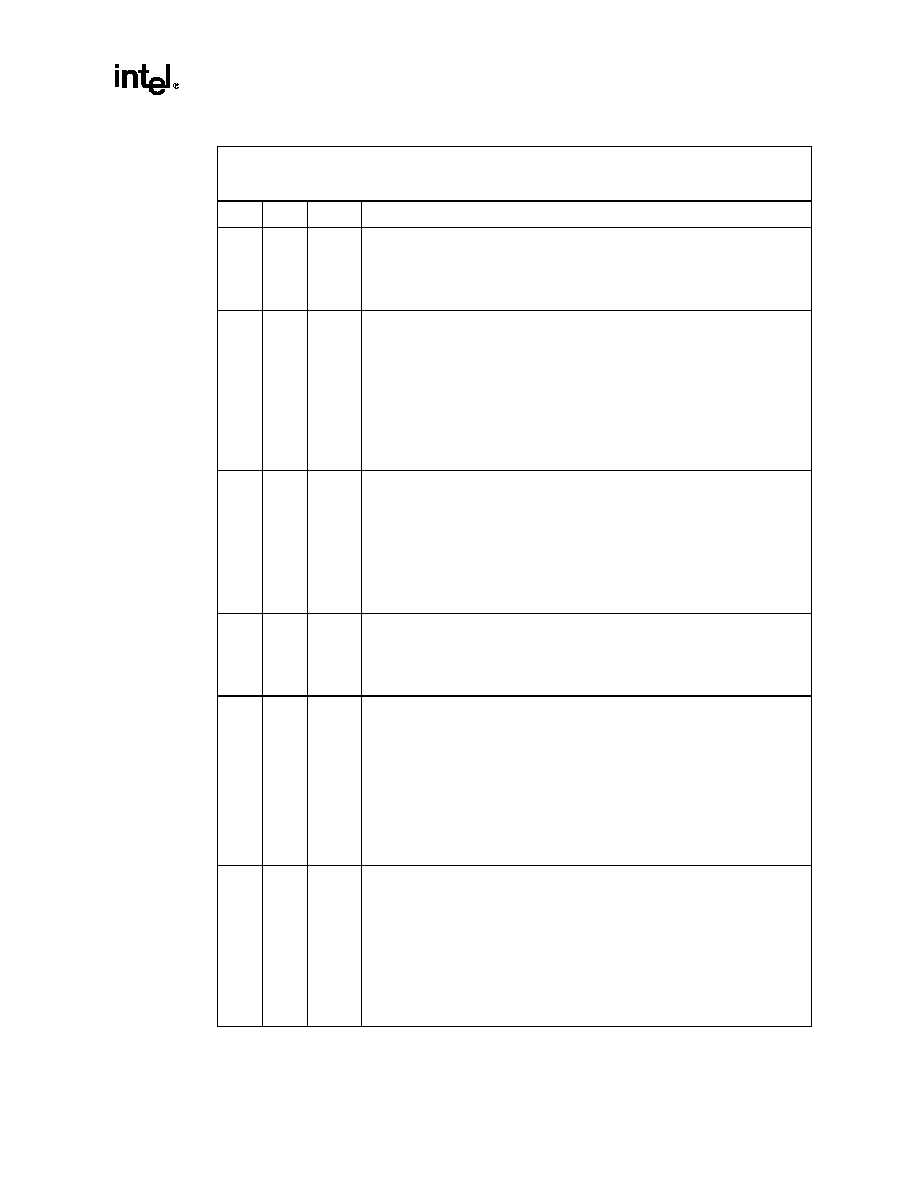

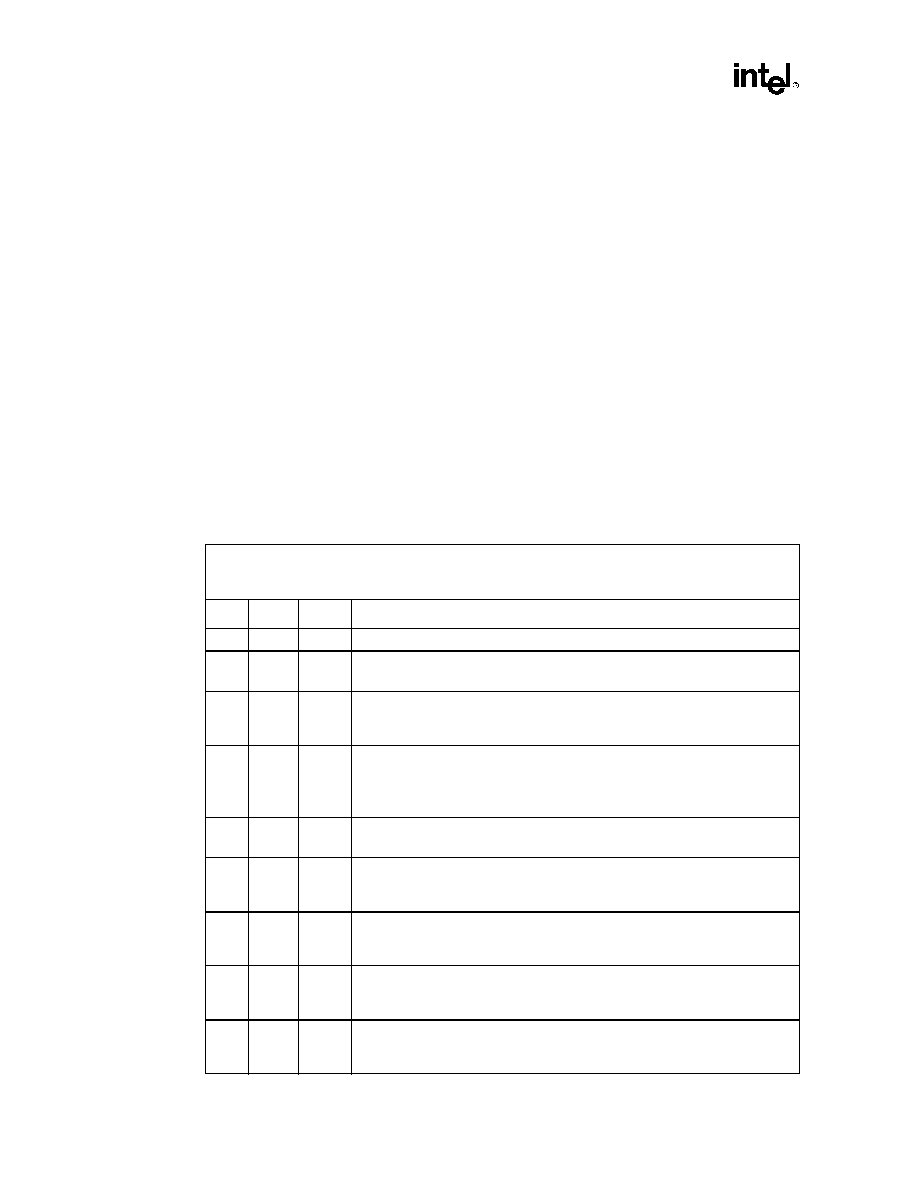

Performance, Debug, and Error Signals ≠ 33 Pins Total

SP{0/1/2/3/4/5}GPIO[1:0]

I/O

CMOS OD

N/A

Scalability Port General Purpose I/O:

These signals could be used to route sideband

signals for domains in multinode systems.

NODEID[2:0]

I

CMOS

N/A

Node ID: Strap bits that indicate the Node ID of

this SPS. The NODEID is captured on the rising

edge of hard reset. The captured value is sent on

the IDLE flits. NODEID[4:3] should always be set

to "11".

BPOUT

O

CMOS

200 MHz

Breakpoint Input: Breakpoint and Performance

Monitoring Output signal.

BPIN

I

CMOS

200 MHz

Breakpoint Output: Breakpoint and

Performance Monitoring Input signal.

DBG[3:0]#

O

CMOS

200 MHz

Event Output Signals.

ERRD0[2:0]#

I/O

CMOS OD

50 MHz

Error Code Signals Domain 0: These signals

carry encoded error information from SPS.

These reflect recoverable and non-recoverable

errors detected by SPS. The system

management logic can examine these

independent of the operating system.

The output value will be asserted until the

software clears the error in the error register.

ERRD1[2:0]#

I/O

CMOS OD

50 MHz

Error Code Signals Domain 1: These signals

carry encoded error information from SPS.

These reflect recoverable and non-recoverable

errors detected by SPS. The system

management logic can examine these

independent of the operating system.

The output value will be asserted until the

software clears the error in the error register.

EV[3:0]#

I/O

CMOS OD

50 MHz

Event External Inputs: These signals are driven

and sampled by the performance monitor unit in

SPS and are used by the system debug logic. As

inputs these signals are driven by the debug logic

to the performance monitor unit.

INT_OUT[1:0]#

O

CMOS OD

50 MHz

Interrupt Request: This signal is asserted by

SPS.

TDIOAnode

I/O

Analog

N/A

Thermal Diode Anode: This is the anode of the

thermal diode.

TDIOCathode

I/O

Analog

N/A

Thermal Diode Cathode: This is the cathode of

the thermal diode.

Table 2-4. SPS Pin List (Continued)

Signal

Type

Frequency

Description

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

2-5

Signal Descriptions

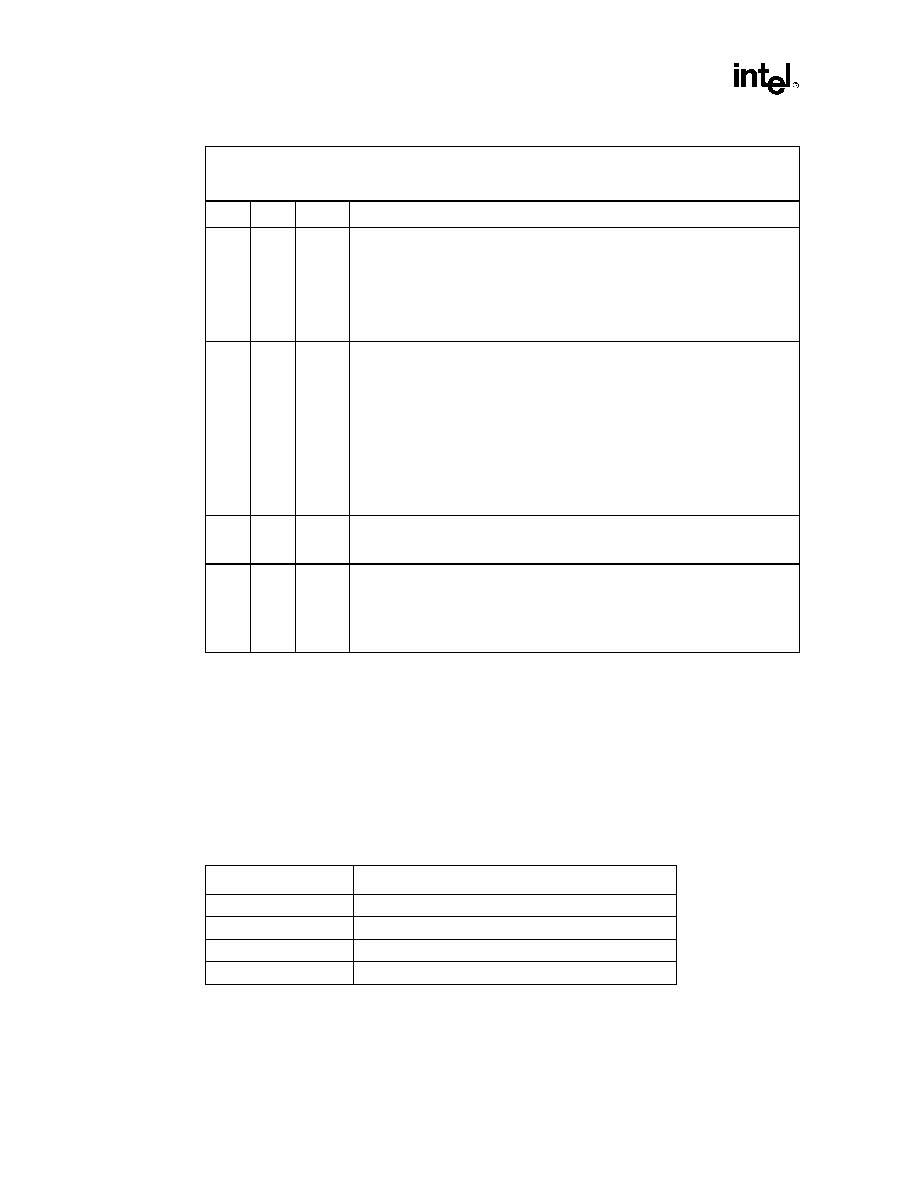

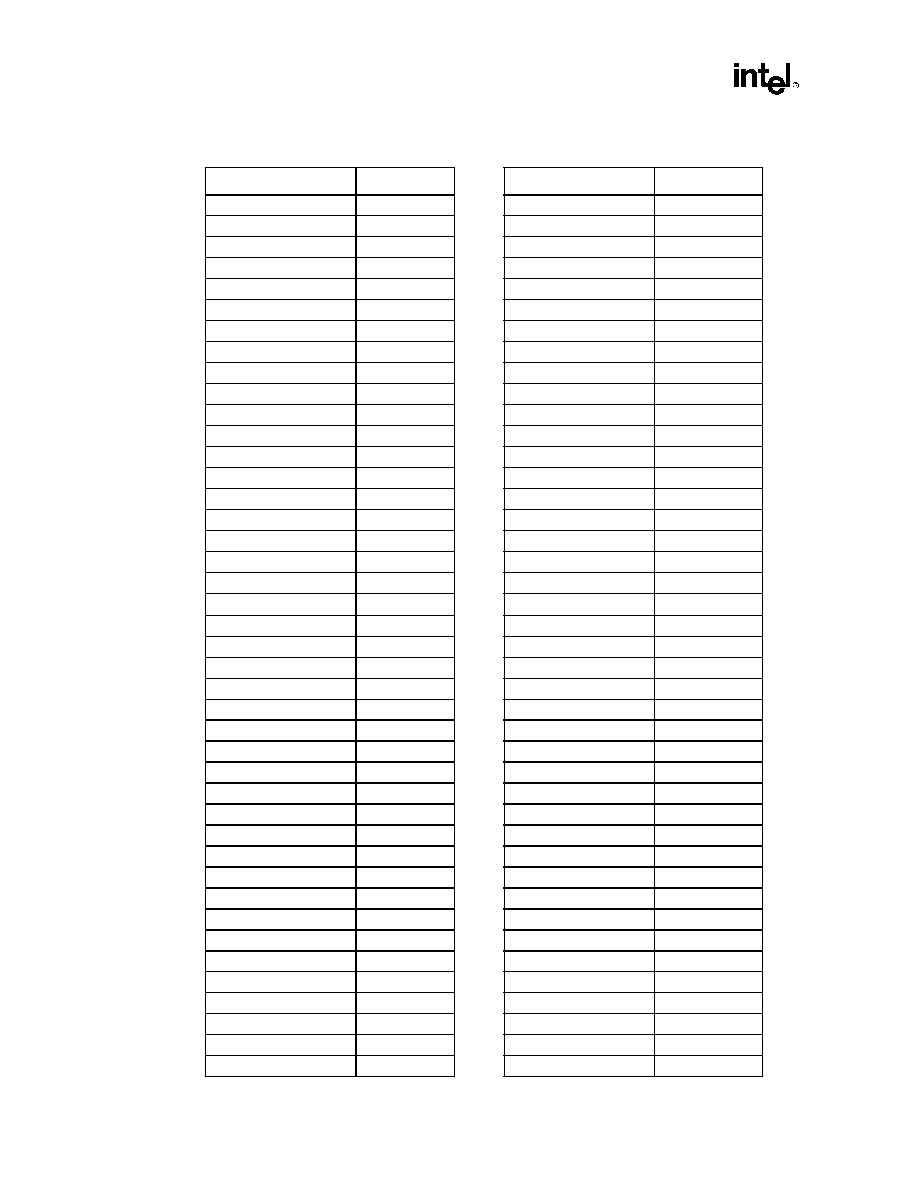

Reset ≠ 4 Pins Total

PWRGOOD

I

CMOS

N/A

Power Good: This signal is held low until all

power supplies are in specification. This signal is

followed by RESETI# deassertion.

RESETI#

I

CMOS

N/A

Reset Input: This is the hard reset input to the

SPS.

RESETID#[1:0]

I

CMOS

N/A

Reserved

Test Access Port (JTAG) ≠ 5 Pins Total

TCK

I

JTAG

TCK

JTAG Test Clock: Clock input used to drive Test

Access Port (TAP) state machine during test and

debugging.

TDI

I

JTAG

TCK

JTAG Test Data In: Data input for test mode.

Used to serially shift data and instructions into

TAP.

TDO

O

JTAG

TCK

JTAG Test Data Out: Data: Data output for test

mode. Used to serially shift data out of the

device.

TMS

I

JTAG

TCK

JTAG Test Mode Select: This signal is used to

control the state of the TAP controller.

TRST#

I

JTAG

N/A

JTAG Test Reset: This signal resets the TAP

controller logic.

Table 2-4. SPS Pin List (Continued)

Signal

Type

Frequency

Description

Signal Descriptions

2-6

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

3-1

Configuration Registers

3

3.1

Access Mechanism

The E8870 chipset supports PCI configuration space access as defined in the PCI Local Bus

Specification, Revision 2.2. The internal registers of this chipset can be accessed in Byte, Word

(16-bit), or Dword (32-bit) quantities, with the exception of CONFIG_ADDRESS, which can only

be accessed as a Dword. All mult-byte numeric fields use "little-endian" ordering (i.e. lower

addresses contain the least significant parts of the field).

Address mapping from the SP, SMBus port, and JTAG interface are defined in

Table 3-1

.

3.1.1

Conflict Resolution

The SPS accepts configuration register reads and writes through three mechanisms. There are two

serial mechanisms: SMBus and JTAG. Accesses initiated by other SNCs or SIOHs appear as

Configurations reads and writes on the SPs.

Multiple configuration accesses arriving on a SP are handled one at a time, and back pressure may

be asserted on the SP. Accesses arriving on different SPs, the SMBus port, and the JTAG interface

are handled one at a time, in any order. Requests are serviced in a round-robin manner.

3.2

Device Mapping

3.2.1

Assignment of Device Number

BUS[7:0] are set to 0xFFh and NodeID[4:3] are hardwired to 0x3 on the SPS. NodeID[2:0] are

captured from external pins on the SPS. Information captured from the idle flits is valid only when

the idle detection bit in the SP Interface Control Register (SPINCO) register is set. As a

convention, an invalid port will have the same NodeID as the SPS.

BUS[7:0] and NodeID[4:0] (only NodeID[2:0] for SPS) are captured and saved in the Chip Boot

Configuration (CBC) register. The power-up strappings are included in the SP idle packet.

Information captured in the CBC register is valid only when the idle detection bit in register

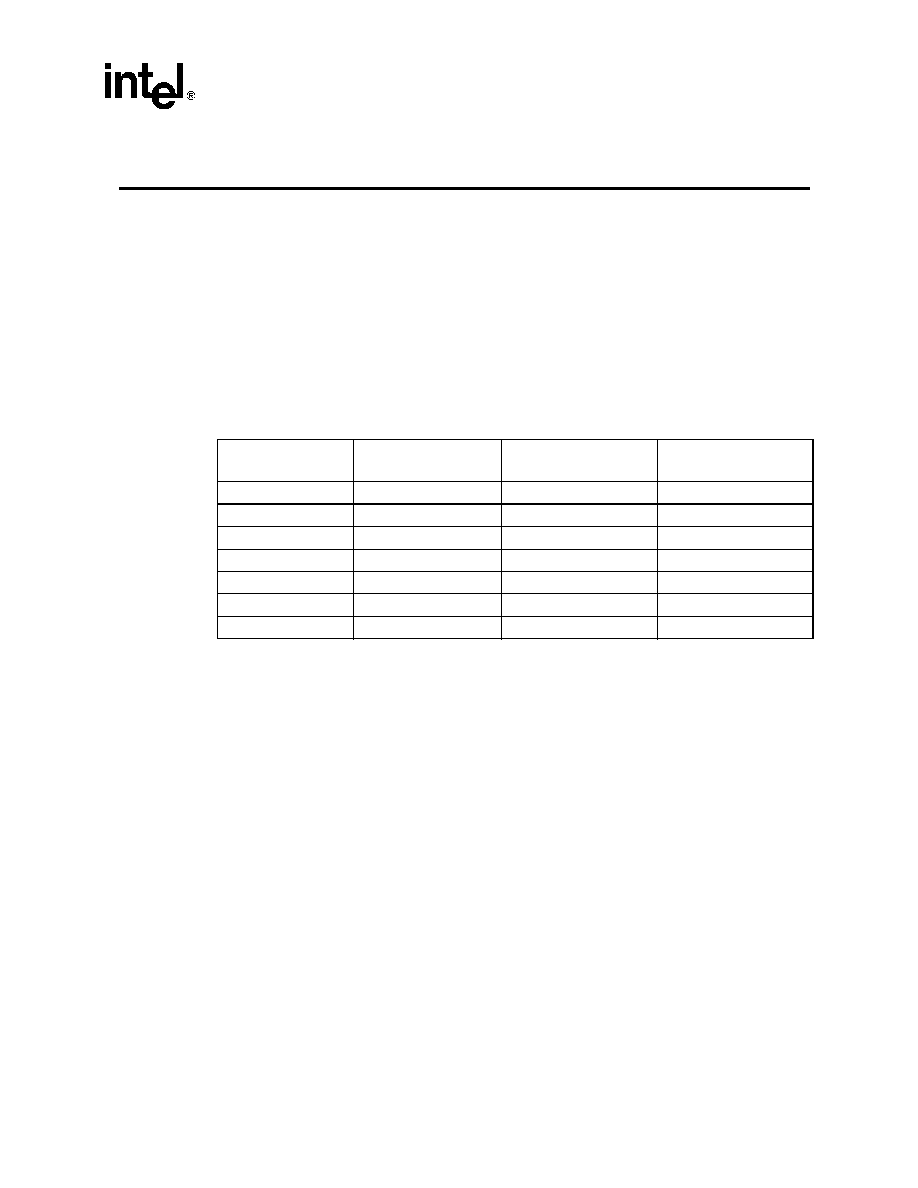

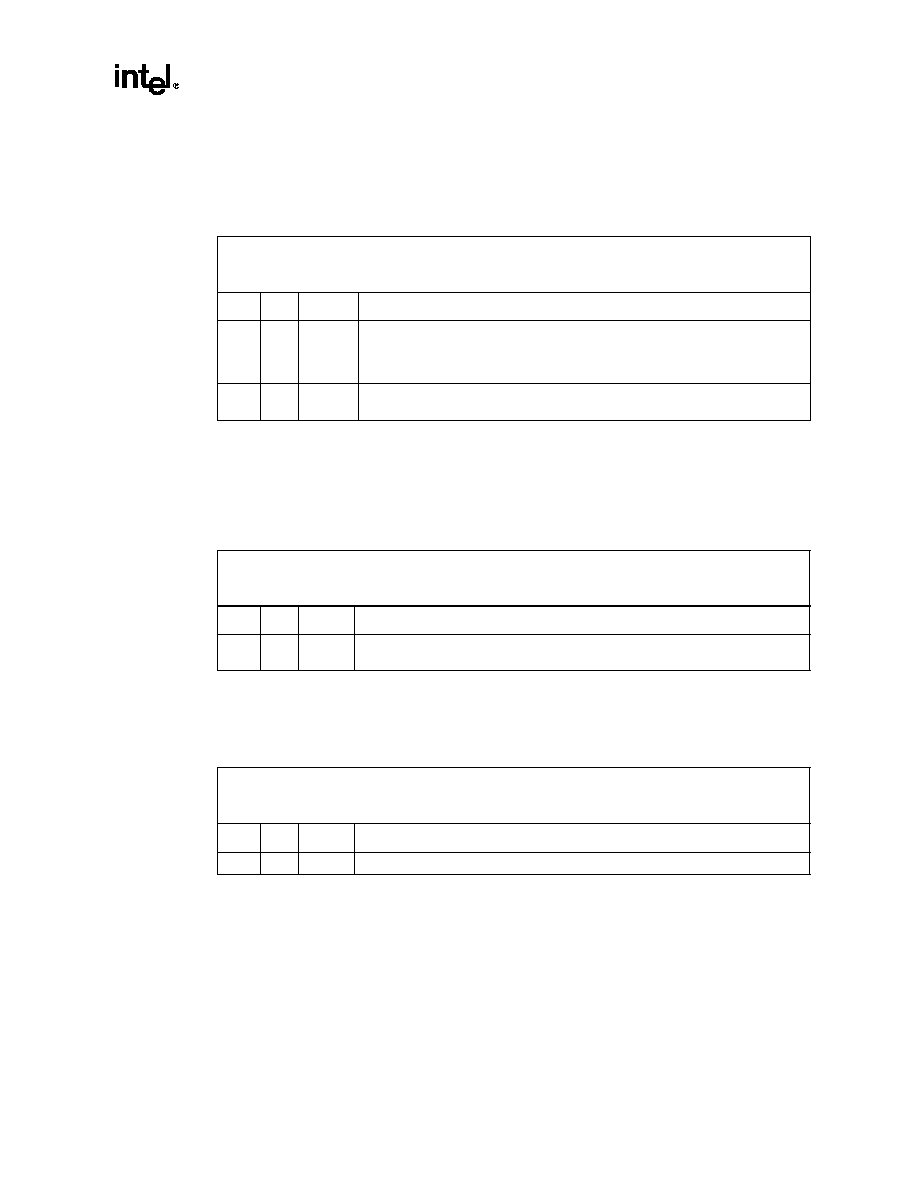

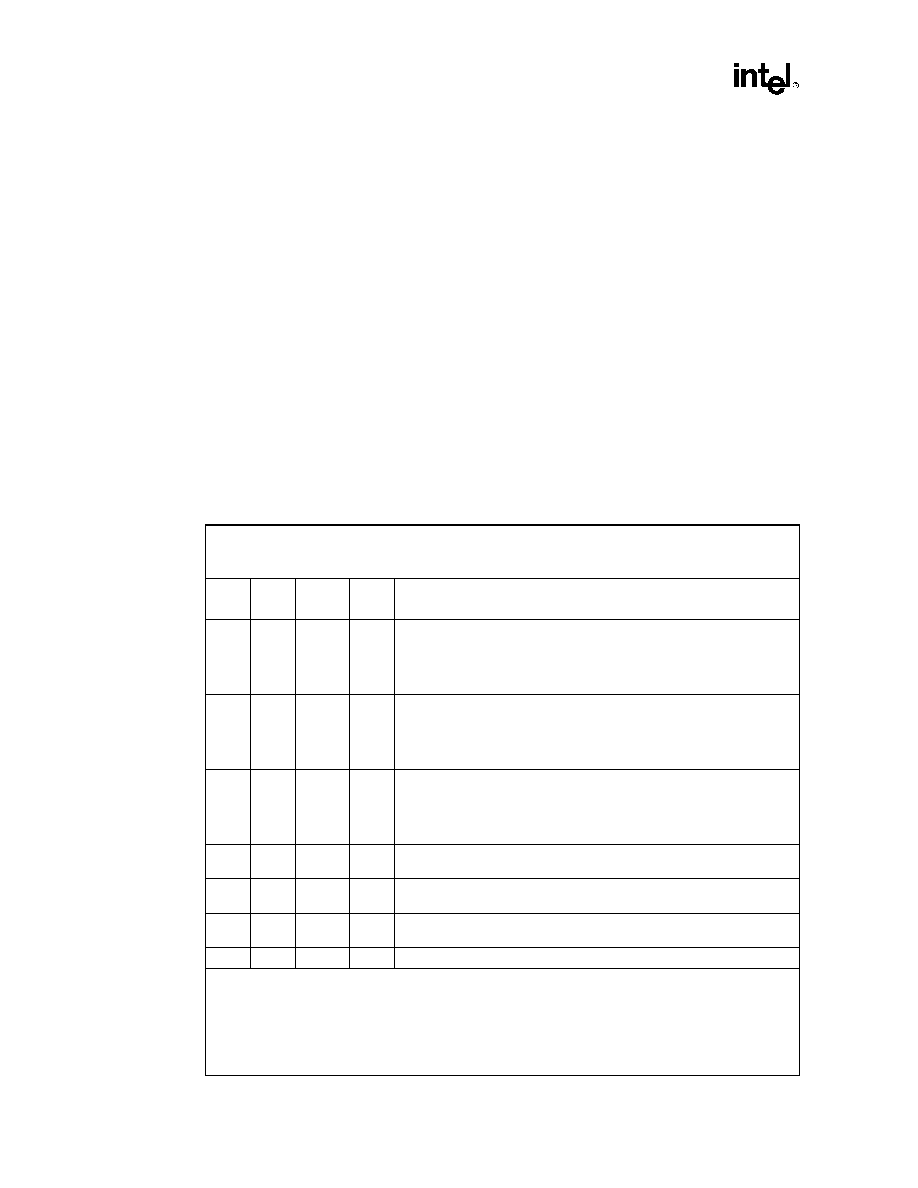

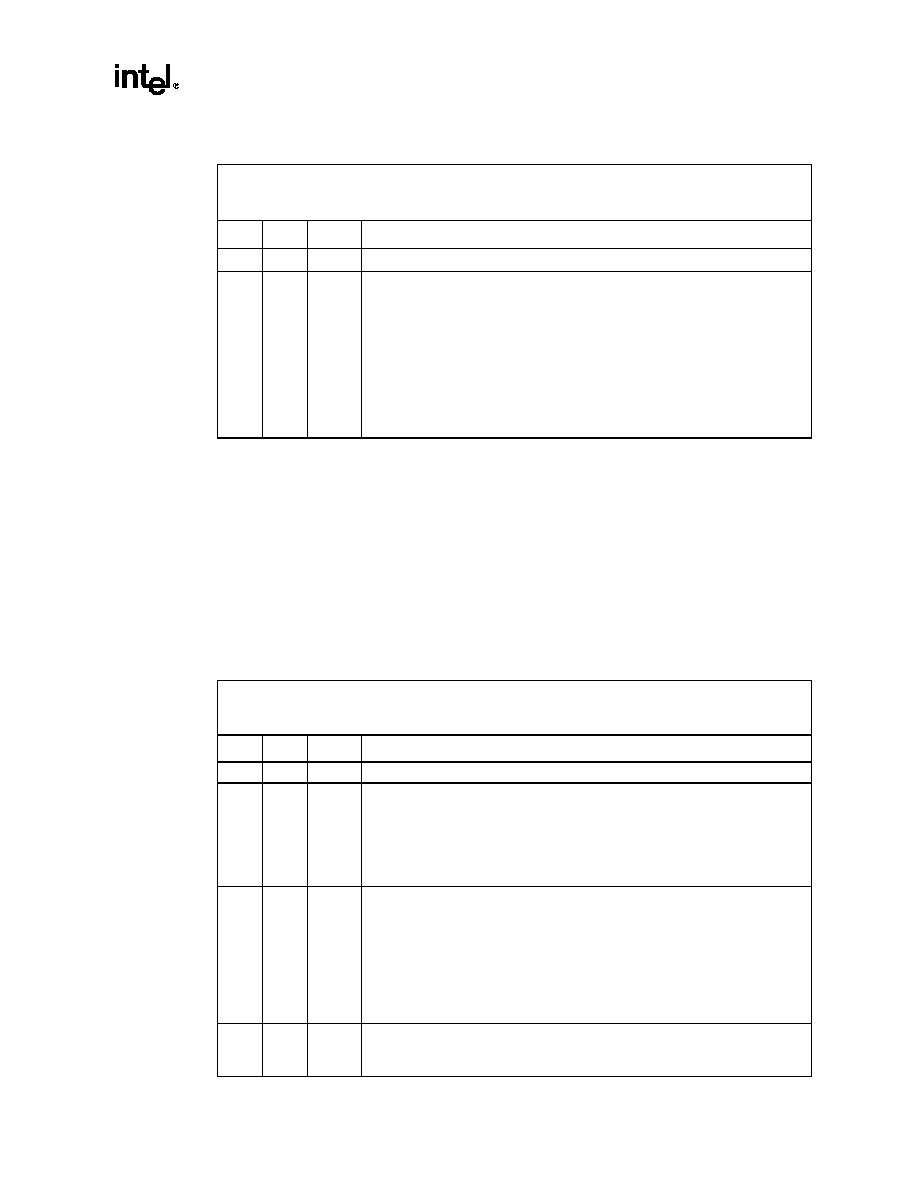

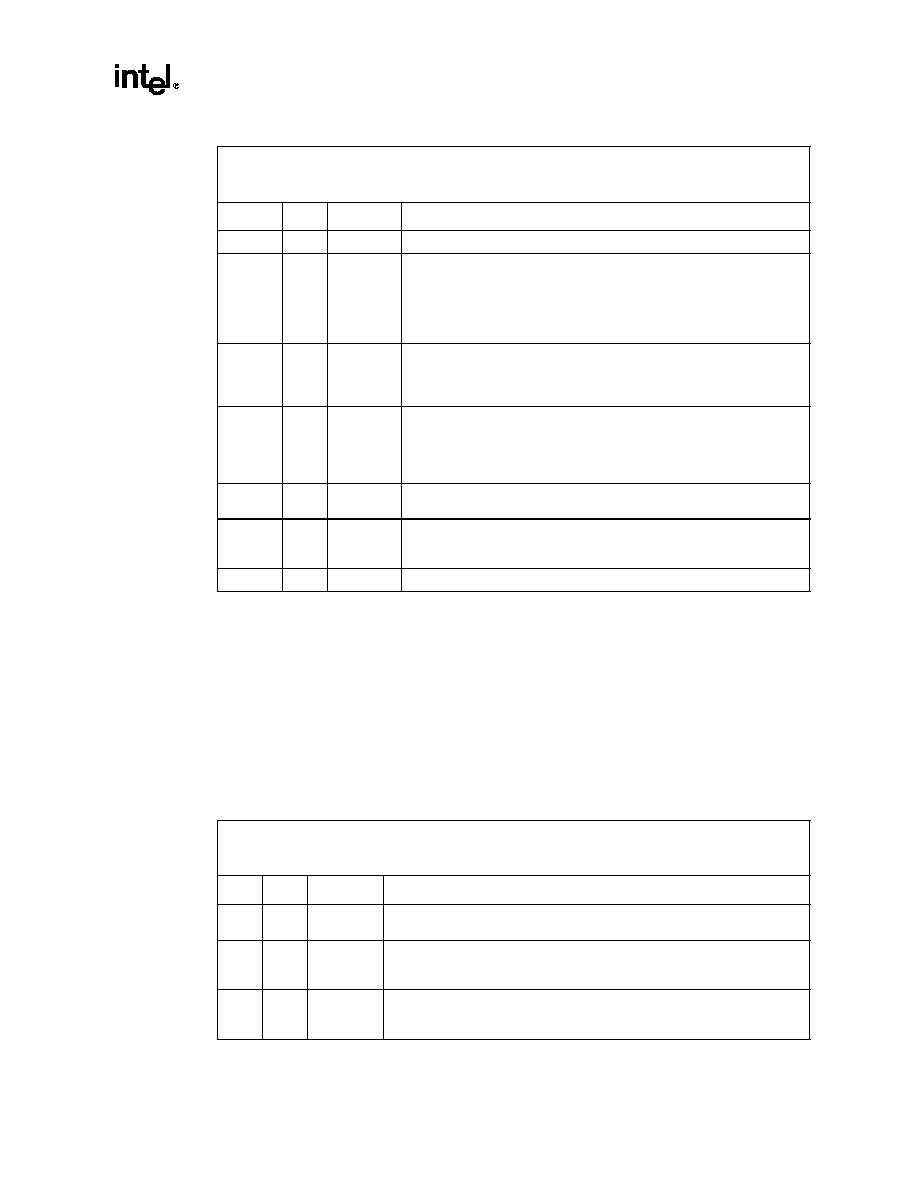

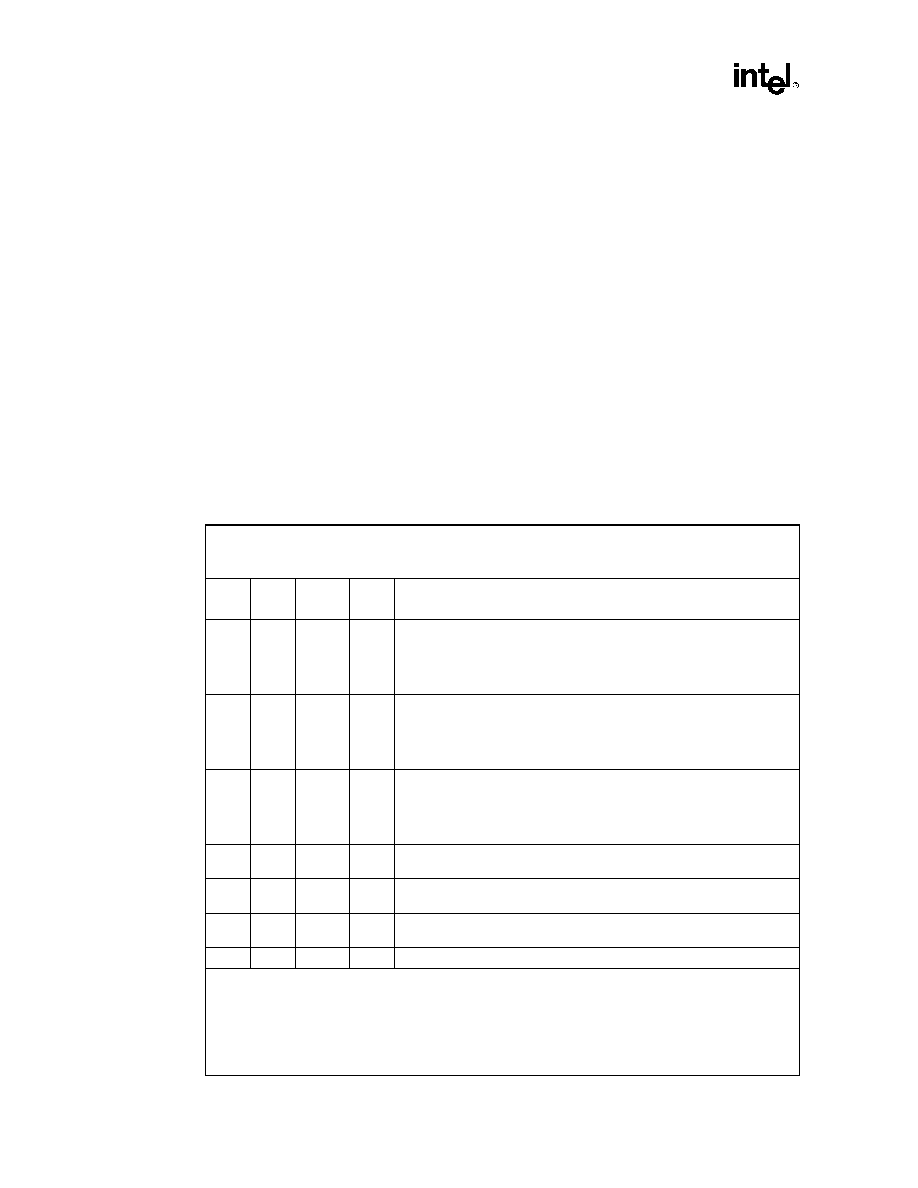

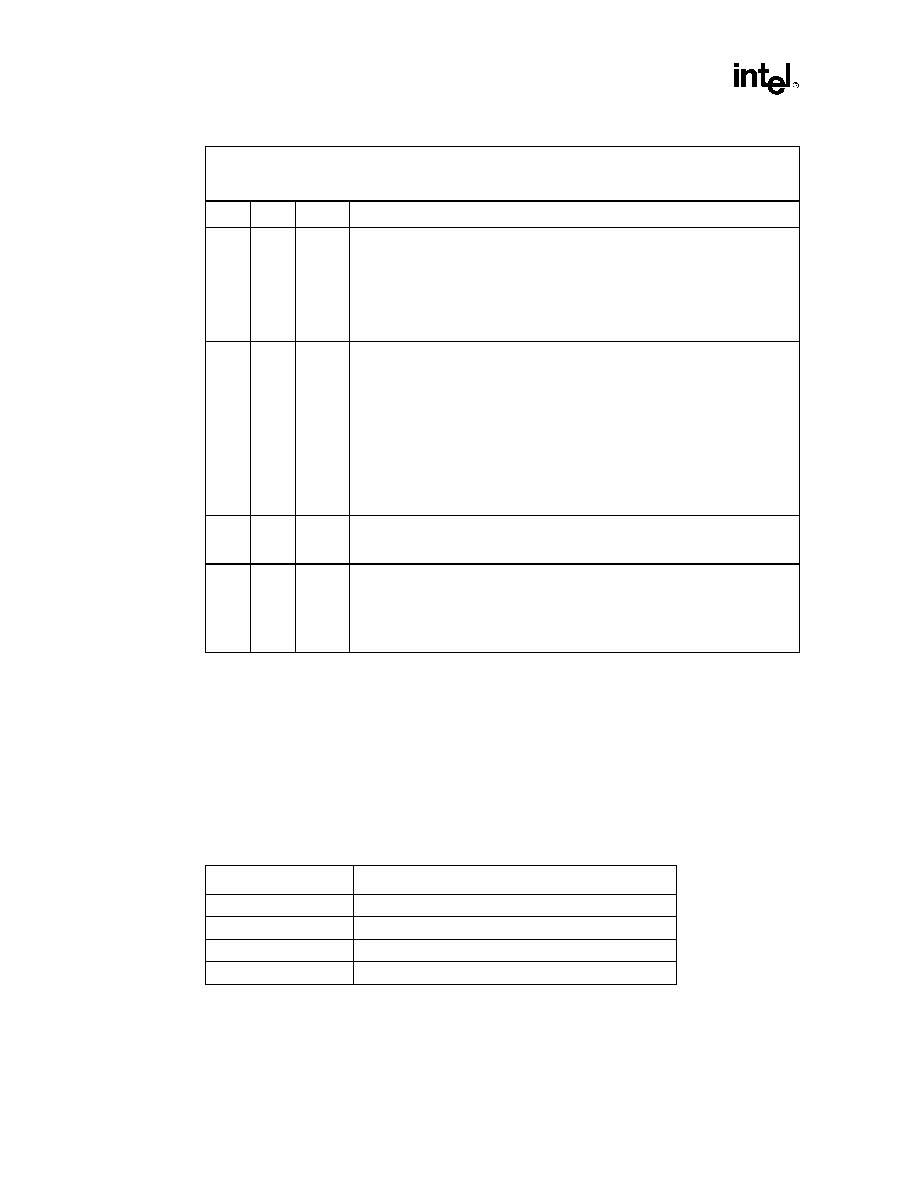

Table 3-1. Configuration Address Bit Mapping

PCI Configuration

Space

SP Configuration

Read/write

JTAG Configuration

Register

SMBus Configuration

Registers

Bus[7:0]

A[23:16]

BusNumber[7:0]

BusNumber[7:0]

Device[4:0]

A[15:11]

DeviceID[4:0]

Dev[4:0]

Function[2:0]

A[10:8]

FunctionNumber[2:0]

Func[2:0]

Register[5:1]

A[7:3]

RegisterAddress[5:1]

Reg[5:1]

Register[0]

ReqType[0]

RegisterAddress[0]

Reg[0]

ByteEn[3:0]

BE[7:4]

Command (Decoded)

Command (Decoded)

Reserved

A[43:24]=0, SPS ignores

N/A

N/A

Configuration Registers

3-2

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

SPINCO is set. Any transactions routed to a SP whose idle flit detection bit is not set is master-

aborted. Each chip uses the contents of register CBC to decide whether a configuration access is

targeted to it or not. The two SPS's can be assigned the same device number upon reset. The

configuration spaces of the SPS's are accessed by setting the "Default SP" bit in the SPINCO

register or the CBC registers of SIOH and SNC. The initialization software assigns different device

numbers to the two SPSs.

SPS routes configuration accesses based upon the PSEG (PCI bus segment register) and the per-

port CBC register. After reset, only one entry in each port's CBC register is valid. The valid entry is

selected by the function number. For example, SP3 NodeID and BUS is valid upon reset only in

function 3. BIOS/SAL/PAL must copy those valid entries into all ports so that configuration writes

and reads can be routed to other components.

3.2.2

Device Mapping Table

The device number for each component of this chipset can be anywhere between 0 and 31 (refer to

Table 3-2

). PAL/SAL must probe the system to find where each component is located.

3.3

Register Attributes

The Default column in the following register definitions (refer to

Table 3-3

) indicates that the

register will be set to this value after a hard reset. Start-up BIOS software is responsible for setting

all register values that are dependent on the particular platform. Each of the following registers

uses the following conventions for the bit attribute column.

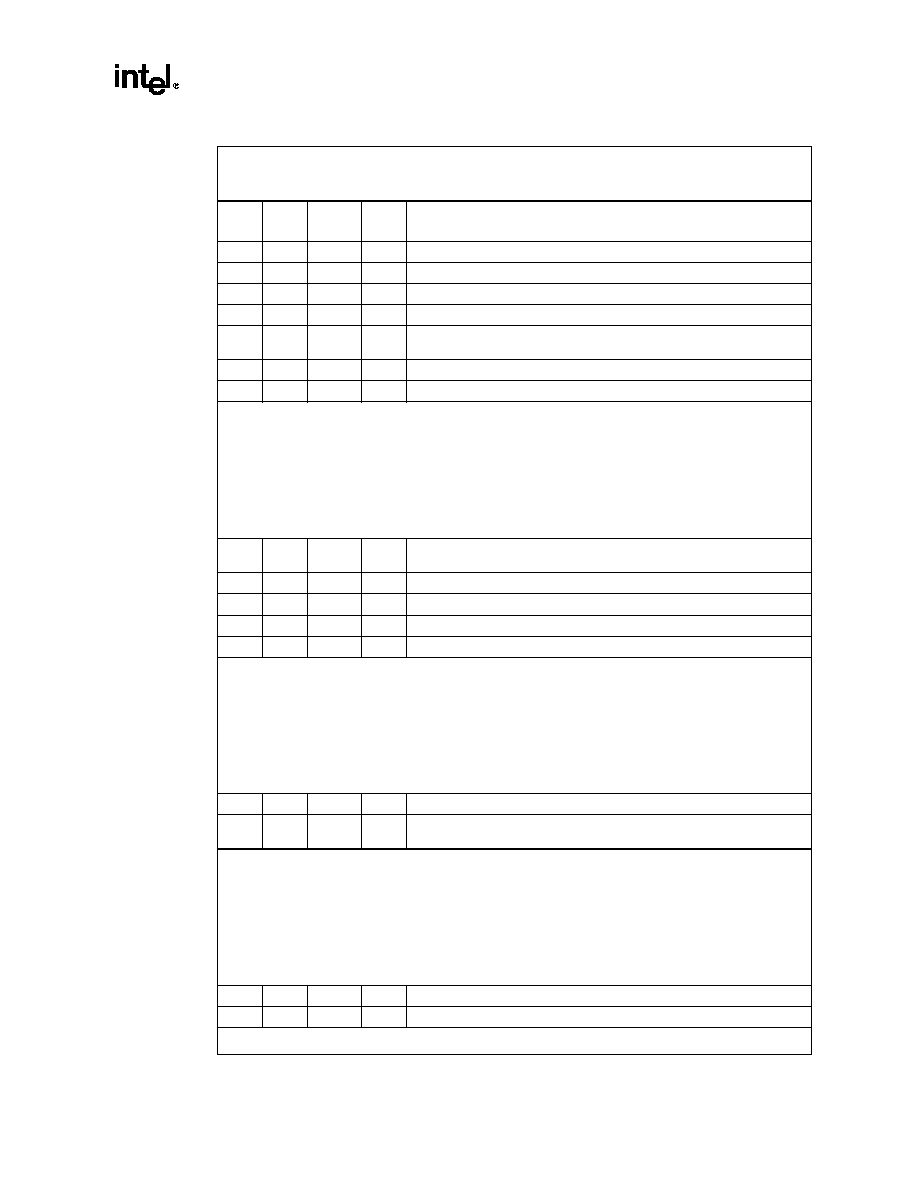

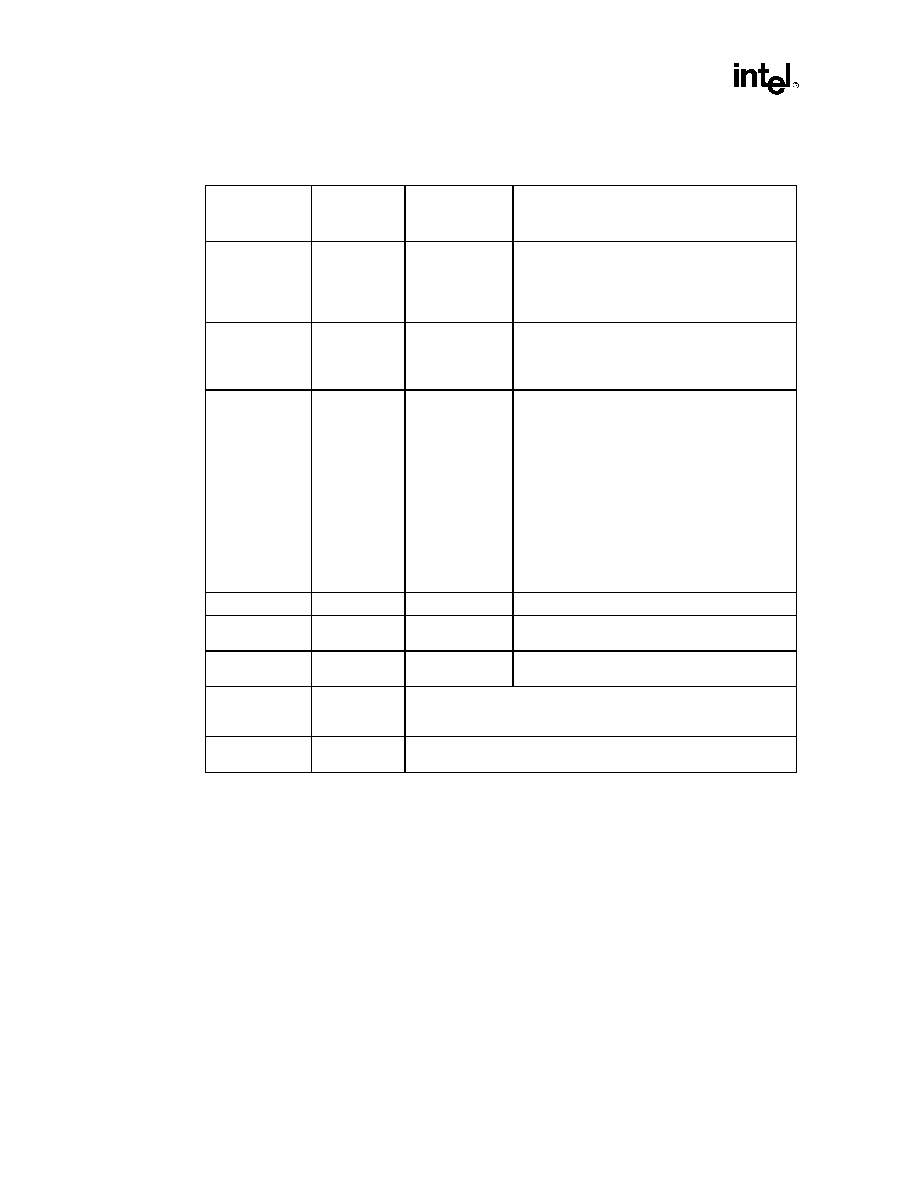

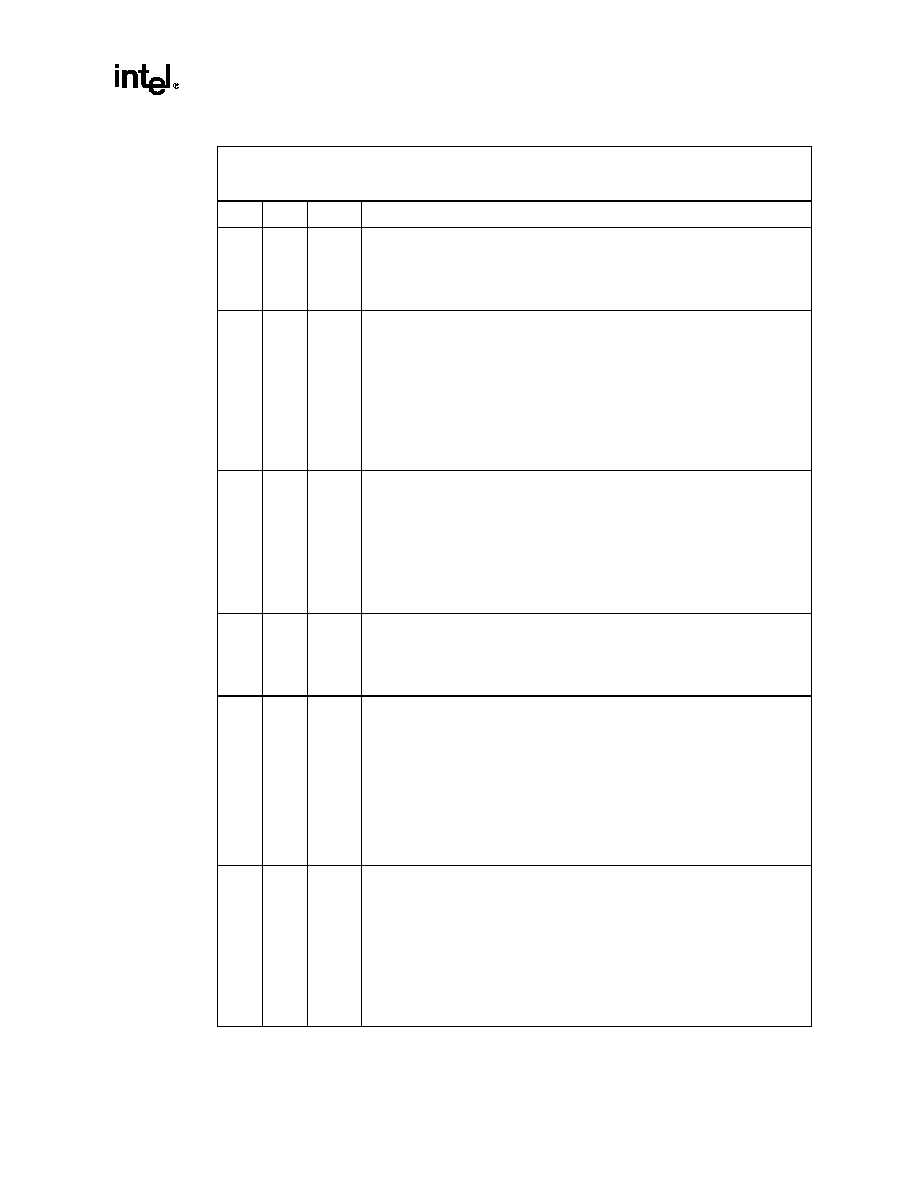

Table 3-2. Function Maps

Device/Function

Description

SPS Function 0:5

Registers for port 0, 1, 2, 3, 4, 5.

SPS Function 6

Registers for interleaves 0 and 1 (bi-interleave 0) and global registers that are

neither per-port nor per-interleave.

SPS Function 7

Registers for interleaves 2 and 3 (bi-interleave 1).

Table 3-3. Register Attributes Definitions

Attribute

Abbreviation

Description

Read Only

RO

The bit is set by the hardware only; software can only read the bit. Writes to the

register have no effect. A hard reset sets the bit to its default value.

Read/Write

RW

The bit can be read or written by software. A hard reset sets the bit to its default

value.

Read/Clear

RC

The bit can be either read or cleared by software. In order to clear a RC bit, the

software must write a one to it. Writing a zero to an RC bit will have no effect. A

hard reset sets the bit to its default value.

Sticky

RWS, RCS,

ROS

The bit is "sticky" or unchanged by a hard reset. Read/Write, Read/Clear and

Read Only bits may be sticky. These bits can only be cleared by a PWRGOOD

reset.

Write Once

W1

Only the first write has an effect. Cleared by reset.

Reserved

RV

This bit is reserved for future expansion and must not be written. The PCI Local

Bus Specification, Revision 2.2 requires that reserved bits must be preserved.

Any software that modifies a register containing a reserved bit is responsible for

reading the register, modifying the desired bits, and writing back the result.

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

3-3

Configuration Registers

3.3.1

SMBus-Initiated Register Access

The SPS claims addresses 1110_XXX, where XXX specifies NODEID[2:0] pin strappings

(sampled upon the deassertion of RESETI#).

3.4

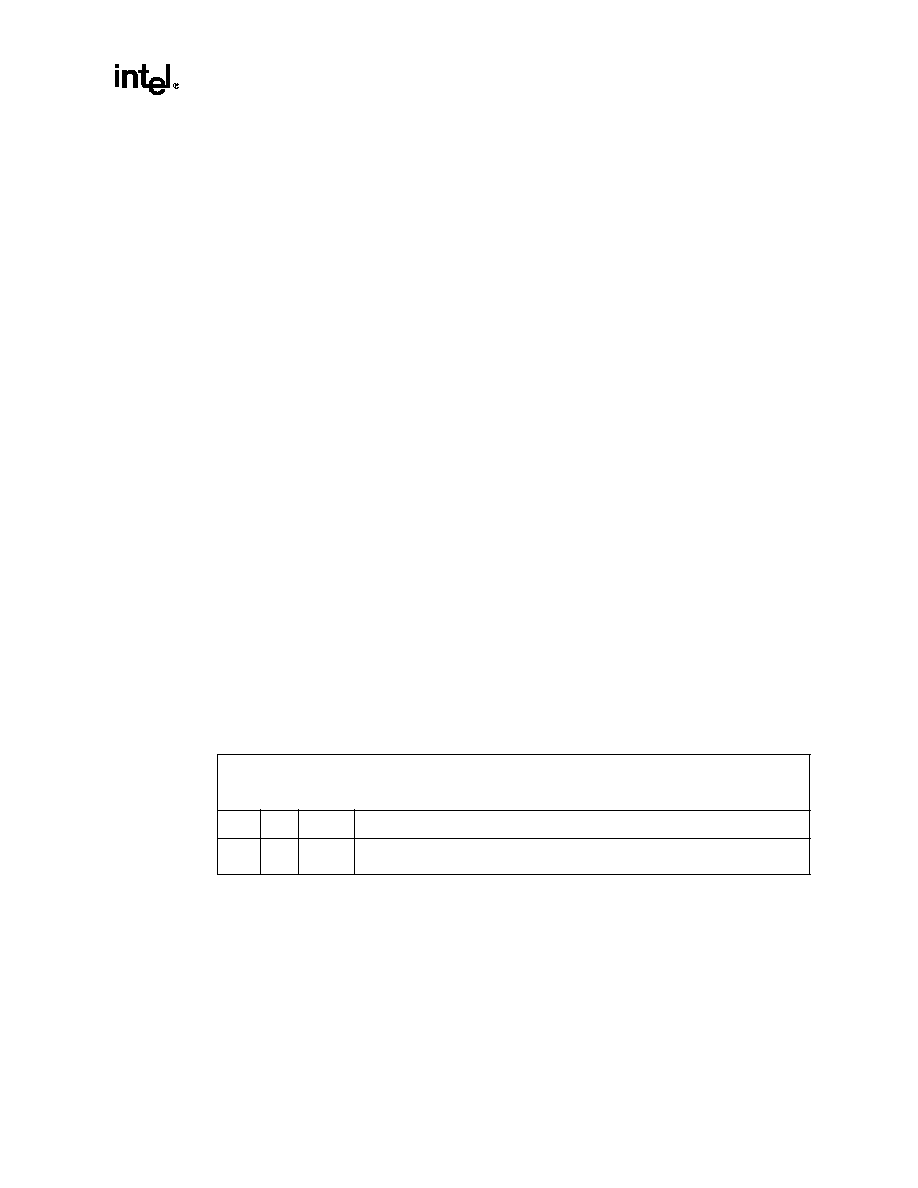

SPS Configuration Register Definitions

The following register definitions are accessed through the standard PCI mechanism (See

Section 3.1, "Access Mechanism."

) The SPS is not a fully PCI compliant device, but the register

map is defined with the intent to be as similar to PCI devices as possible. This is to help software

stay as consistent as possible. Some PCI header registers are defined and the remaining

configuration registers reside above 40h.

Unimplemented registers return all zeros when read. Writes to unimplemented registers are

ignored, and return with a normal completion status.

3.5

SPS PCI Standard Configuration Registers ≠ All

Functions

Writes to unimplemented and reserved registers will have no effect. Reads to unimplemented and

reserved registers will return a data value of 0. These accesses will complete normally (no master

abort).

The first group of registers in this section define the necessary standard PCI registers.

3.5.1

VID: Vendor Identification Register

The VID Register contains the vendor identification number, which identifies the manufacturer of

the device. This 16-bit register, combined with the Device Identification Register, uniquely

identifies any PCI device. Writes to this register have no effect.

3.5.2

DID: Device Identification Register

This 16-bit register, combined with the Vendor Identification register, uniquely identifies the SPS.

Writes to this register have no effect.

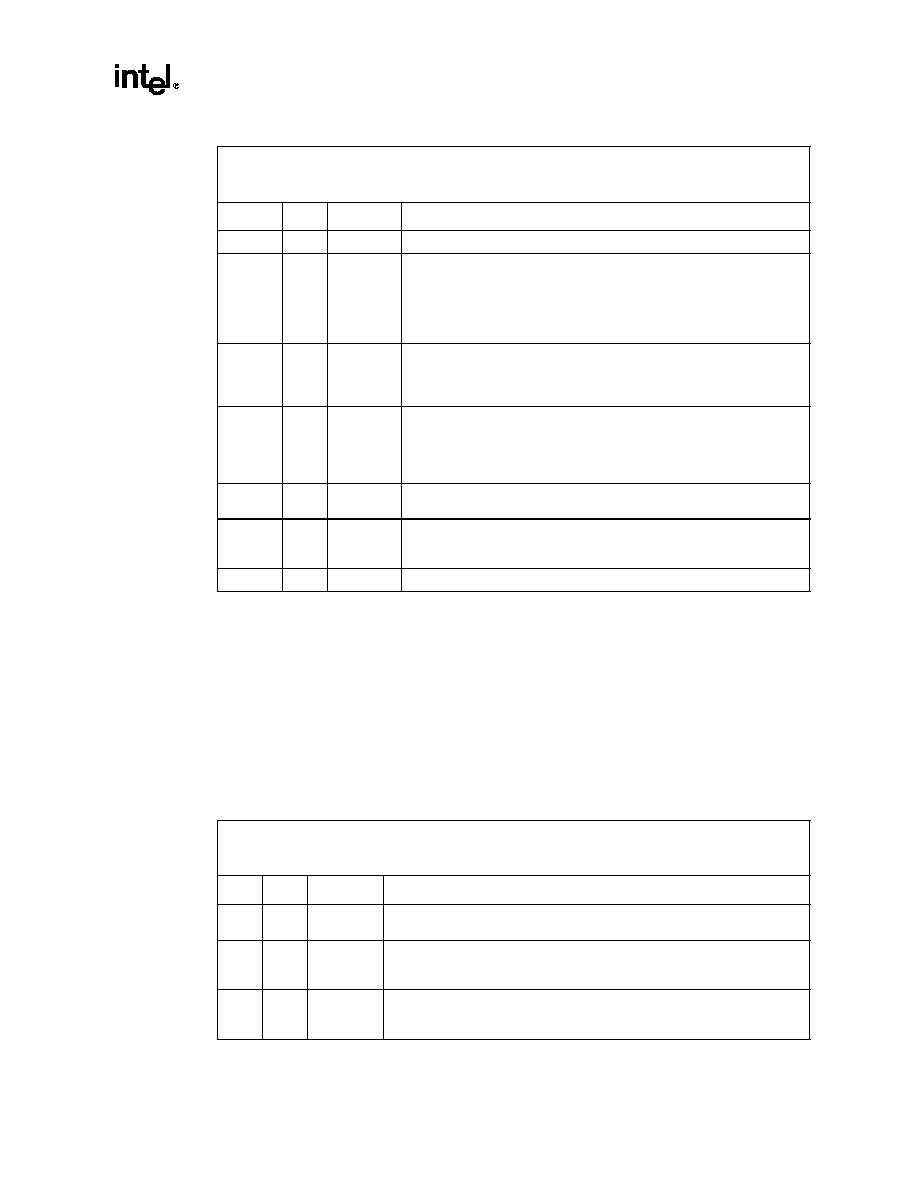

Device:

Node_ID

Function: 0-7

Offset:

00h

Bit

Attr

Default

Description

15:0

RO

8086h

Vendor Identification Number: This is a 16-bit value assigned to Intel. Intel VID =

8086h.

Configuration Registers

3-4

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

3.5.3

RID: Revision ID Register

The Revision ID register tracks the specific revision of this component. Since this register is part of

the standard PCI header, there is a RID register per PCI function.

3.5.4

CCR: Class Code Register

The Class Code register identifies the SPS component as a host bridge. This register adheres to the

PCI Local Bus Specification, Revision 2.2. Since this register is part of the standard PCI header,

there is a CCR register per PCI function.

Device:

Node_ID

Function: 0-7

Offset:

02h

Bit

Attr

Default

Description

15:0

RO

F0:0x0530

F1:0x0531

F2:0x0532

F3:0x0533

F4:0x0534

F5:0x0535

F6:0x0536

F7:0x0537

Device Identification Number: This value is the device ID for the SPS

component. In order for proper driver functionality, each SPS function has a

different value for the DID register.

Device:

Node_ID

Function: 0-7

Offset:

08h

Bit

Attr

Default

Description

7:0

RO

10h

Revision Identification Number: For the B-0 stepping of the SPS, this value is

10H.

Device:

Node_ID

Function: 0-7

Offset:

09h

Bit

Attr

Default

Description

23:16

RO

06h

Base Class Code: This code indicates that the SPS is a bridge device.

15:8

RO

00h

Sub-Class Code: This code indicates that the SPS bridge is part of a host bridge.

7:0

RO

00h

Register-Level Programming Interface: This field identifies a specific

programming interface that device independent software can use to interact with

the device. There are no such interfaces defined for host bridges.

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

3-5

Configuration Registers

3.5.5

HDR: Header Type Register

This register identifies the header layout of the configuration space. Writes to this register have no

effect.

3.5.6

SVID: Subsystem Vendor Identification Register

This register contains the subsystem vendor identification number. It is programmed by software

and assists in software in future activities such as driver selection. Only the first write to this

register has any affect.

3.5.7

SDID: Subsystem Device Identification Register

This register contains the subsystem device ID. Only the first write to this register has any affect.

3.6

SP Port Configuration Register ≠ Functions 0:5

3.6.1

CBC: Chip Boot Configuration

SPS routes configuration accesses based upon the per-port PCI bus range (bus_start:bus_end) and

the per-port CBC register. After reset, only one entry in each port's CBC register is valid. The valid

entry is selected by the function number. For example, SP3 NodeID and BUS is valid upon reset

only in function 3. BIOS/SAL/PAL must copy those valid entries into all ports so that

configuration reads and writes can be routed.

Device:

NodeID

Function: 0-7

Offset:

0Eh

Bit

Attr

Default

Description

7

RO

1

Multi-function Device: Selects whether this is a multi-function device, that may

have alternative configuration layouts. The SPS has more than the 256 bytes of

configuration registers allotted to a single function. Therefore, the SPS is defined to

be a multifunction device, and this bit is hardwired to 1.

6:0

RO

00h

Configuration Layout: This field identifies the format of the 10h through 3Fh space.

The SPS uses header type "00".

Device:

NodeID

Function: 0-7

Offset:

2Ch

Bit

Attr

Default

Description

15:0

W1

8086

Subsystem Vendor Identification Number: This value is the subsystem vendor ID

for the SIOH component. The value can only be assigned once after reset.

Device:

NodeID

Function: 0-7

Offset:

2Eh

Bit

Attr

Default

Description

15:0

W1

0h

Subsystem Device Identification Number.

Configuration Registers

3-6

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

To save register bits, BUS[7:0] are hardwired to FFh and NodeID[4:3] are hardwired to 11b on the

SPS. NodeID[2:0] are captured from external pins on the SPS. Information captured from the idle

flits is valid only when the idle detection bit in the SPINCO register is set. As a convention,

software can program the invalid ports to have the same NodeID as the SPS (except for the RO

bits).

Device:

Node_ID

Function: 0-5

Offset:

E8h

Bit

Attr

Default

Description

111:109

RV

0

Reserved

108:107

RO

11

SP5 Node ID[4:3]

106:104

RW/R

O

111

SP5 Node ID[2:0]: Device# received from the corresponding SP

∑

RO for function 5

∑

RW for functions 0-4

103:96

RO

FFh

SP5 Bus[7:0].

95:93

RO

0

Reserved

92:91

RO

11

SP4 Node ID[4:3]

90:88

RW/R

O

111

SP4 Node ID[2:0]: Device# received from the corresponding SP

∑

RO for function 4

∑

RW for functions 0-3,5

87:80

RO

FFh

SP4 Bus[7:0]

79:77

RV

0

Reserved

76:75

RO

11

SP3 Node ID[4:3]

74:72

RW/R

O

111

SP3 Node ID[2:0]: Device# received from the corresponding SP

∑

RO for function 3

∑

RW for functions 0-2, 4-5

71:64

RO

FFh

SP3 Bus[7:0]

63:61

RV

0

Reserved

60:59

RO

11

SP2 Node ID[4:3]

58:56

RW/R

O

111

SP2 Node ID[2:0]: Device# received from the corresponding SP

∑

RO for function 2

∑

RW for functions 0-1, 3-5

55:48

RO

FFh

SP2 Bus[7:0].

47:45

RV

0

Reserved

44:43

RO

11

SP1 Node ID[4:3]

42:40

RW/R

O

111

SP1 Node ID[2:0]: Device# received from the corresponding SP

∑

RO for function 1

∑

RW for functions 0, 2-5

39:32

RO

FFh

SP1 Bus[7:0]

31:29

RV

0

Reserved

28:27

RO

11

SP0 Node ID[4:3]

26:24

RW/R

O

111

SP0 Node ID[2:0]: Device# received from the corresponding SP

∑

RO for function 0

∑

RW for function 1-5

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

3-7

Configuration Registers

3.6.2

SPINCO: SP Interface Control

This register is common across all E8870 chipset components. It provides the control and status for

each SP. Two GPIO pins (GPIO[1:0]) are associated with each SP. These pins are open drain, and

are observable and controllable from this register.

The SPS has two INT_OUT# pins: INT_OUT[1:0]#. In a system operation, INT_OUT0# is

asserted. Use of INT_OUT1# is not supported.

Disabling a SP should not be done with a configuration write transaction from the same SP as the

one being disabled. Otherwise, the configuration write will not complete.

23:16

RO

FFh

SP0 Bus[7:0]

15

RWS

0

StopOnEr:

0 = An agent will send idle or info flits when in RETRY_LOCAL_IDLE

state.

1 = If an agent has detected an error and has sent an LLRReq and its

local retry state machine is in RETRY_LOCAL_IDLE state, then it

should not send any info or idle flits and sends a Ctrl flit with LLRIdle.

14

RWS

0

SndMultAck:

0 = 0 or 1 ACK is sent in LCC[7] of idle flits. Byte D = 0.

1 = LCC[7] = 0. Up to 25 ACKs will be sent in Byte D[4:0] of idle flits. Idle

flits are forced whenever there are multiple acks to send.

13

RWS

0

RcvMultAck:

0 = 0 or 1 ACK is extracted from LCC[7] of idle flits.

1 = Up to 25 ACKs may be extracted from idle flits. Ack[4:0] = LCC[7] ||

Byte D[4:0]. Any particular idle flit will use either LCC[7] or Byte D, but

not both.

12:11

RO

11

Node ID[4:3]: Bit [4:3] of this chip's device #. These bits are sent in idle

flits.

10:8

RW

See

Description

Node ID[2:0]: Those bits define the device # of this chip. The default value

is captured from the NODEID[2:0] pins on the rising edge of RESETI#. See

device mapping for details. These bits are sent in the idle flits.

7:0

RO

FFh

Bus[7:0]: This chip's bus #. These bits are sent in idle flits.

Device:

Node_ID

Function: 0-5

Offset:

E8h (Continued)

Bit

Attr

Default

Description

Device:

Node_ID

Function: 0-5

Offset:

40h

Bit

Attr

Default

Description

31:26

RWS

0

Scratch Bits: These bits may be used by software to record information

specific to this SP. For example, hot plug sequencing history

25

RO

X

GPIO1 STATE:

0 = GPIO1 pin is high (inactive)

1 = GPIO1 pin is low (active)

24

RO

X

GPIO0 STATE:

0 = GPIO0 pin is high (inactive)

1 = GPIO0 pin is low (active)

Configuration Registers

3-8

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

23

RWS

0

GPIO1 EN:

0 = Do not drive the GPIO1 pin (input only)

1 = Drive the GPIO1 pin low (open drain output)

22

RWS

0

GPIO0 EN:

0 = Do not drive the GPIO0 pin (input only)

1 = Drive the GPIO0 pin low (open drain output)

21

RW

0

INT_OUT:

0 = Do not explicitly drive the INT_OUT# pin low. Note that the INT_OUT pin

can still be driven due to other SPINCO interrupt conditions.

1 = Explicitly drive the INT_OUT# pin low (open drain output)

20:19

RO

0

SPAlign: The value of this field reflects the staging delays through the SP input

mux to frame the transfer of data from the SP source synchronous data

transfer to the core clock of the component.

This field valid only when "idle flit detected" is set.

18:16

RWS

101

Response Credits: Credits supported by this SP port on the response VC.

Credit = 2

size

except that when size >= 101, credit = 25 instead of 32. These

bits are sent in the idle flits. Must be set to a value <= to 25 for reliable SP

operation.

15:13

RWS

101

Request Credits: Credit supported by this SP port on request VC. Credit =

2

size

except that when size >= 101, credit = 25 instead of 32. These bits are

sent in the idle flits. Must be set to a value <= 25 for reliable SP operation.

12

RW

0

Disable SP Link Level Retry (LLR): When set, this bit will disable link level

retry on SP. Note: SP LLR is always disabled during framing/initialization.

11:9

RO

0

Connecting SP Response Credits: Credits supported by the response VC of

the device connected to this SP port. Credit = 2

size

except that when size=

101, credit = 25 instead of 32. This field is captured and updated from the idle

flits.

8:6

RO

0

Connecting SP Request Credits: Credits supported by the request VC of the

device connected to this SP port. Credit = 2

size

except that when size = 101,

credit = 25 instead of 32. This field is captured and updated from the idle flits.

5

RWS:

SPS/

SIOH

RW:

SNC

SPS:1

SIOH:1

SNC: 0

Enable SP:

0 = The port is disabled. The outputs of the SP excluding SPSync are tri-

stated. Deassertion will cause the port to de-assert SPSync and enter

initialization sequence.

1 = Enable SP output drivers. The port must complete initialization and

framing before data can be transferred.

4

RO

0

Idle Flit Acknowledgment Detected: Detected acknowledgement in a idle flit

received by this SP. This bit is cleared at the beginning of the initialization

sequence.

3

RO

0

Idle Flit Detected: Set during framing when 256 valid idle flits in a row are

detected by the SP receiver. This bit is cleared at the beginning of the

initialization sequence.

2

RW

0

Interrupt on SP Idle Flit State Change:

1 = A 0 to 1 transition of the Idle Flit Detected bit in the above field will trigger

an interrupt from this chip via INT_OUT# assertion by this port.

0 = De-assert the interrupt request controlled by this bit. The open drain

interrupt pin (INT_OUT#) may remain asserted if other interrupt

conditions exist.

Note that the detection mechanism is initialized at the start of port framing only.

1

RO

See

Description

SP Present State: This bit follows the SPPRES pin associated with this SP.

When deasserted, the output of the SP are tri-stated (including SPSync), and

transactions targeting the SP are master-aborted.

Device:

Node_ID

Function: 0-5

Offset:

40h (Continued)

Bit

Attr

Default

Description

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

3-9

Configuration Registers

3.6.3

RECSPPD: Recoverable Error Control Information of SPPD

This register latches control information for the first non-fatal error detected inside the SPPD

cluster. Not all errors have logs. See Table 9-1 in the RS - Intel

Æ

82870 Chipset System Architecture

Specification for a listing of the errors that use this log.

3.6.4

RECSPL: Recoverable Error Control Information of SPL

This register latches control information for the first non-fatal error detected inside the SPL cluster.

Not all errors have logs.

3.6.5

REDSPL: Recoverable Error Data Log SPL

This register latches ECC information for the first SP link layer ECC error detected in the SPL.

0

RW

0

Interrupt on Pin SP Present State Change:

1 = A 0->1 or 1->0 transition in the above field will trigger an interrupt from

this chip (via INT_OUT# assertion by this port).

0 = Deassert the interrupt request controlled by this bit. The open drain

interrupt pin (INT_OUT#) may remain asserted if other interrupt

conditions exist.

Device:

Node_ID

Function: 0-5

Offset:

40h (Continued)

Bit

Attr

Default

Description

Device:

Node_ID

Function: 0-5

Offset:

64h

Bit

Attr

Default

Description

63:0

ROS

0

SP request header or SP response header or internal request/response header.

Device:

Node_ID

Function: 0-5

Offset:

44h

Bit

Attr

Default

Description

63:0

ROS

0

SP request header or SP response header or internal request/response header for

errors that log control. Phit and LLR information for parity or LLR errors.

Device:

Node_ID

Function: 0-5

Offset:

4Ch

Bit

Attr

Default

Description

15:0

ROS

0

Syndrome and ECC Checkbits.

Configuration Registers

3-10

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

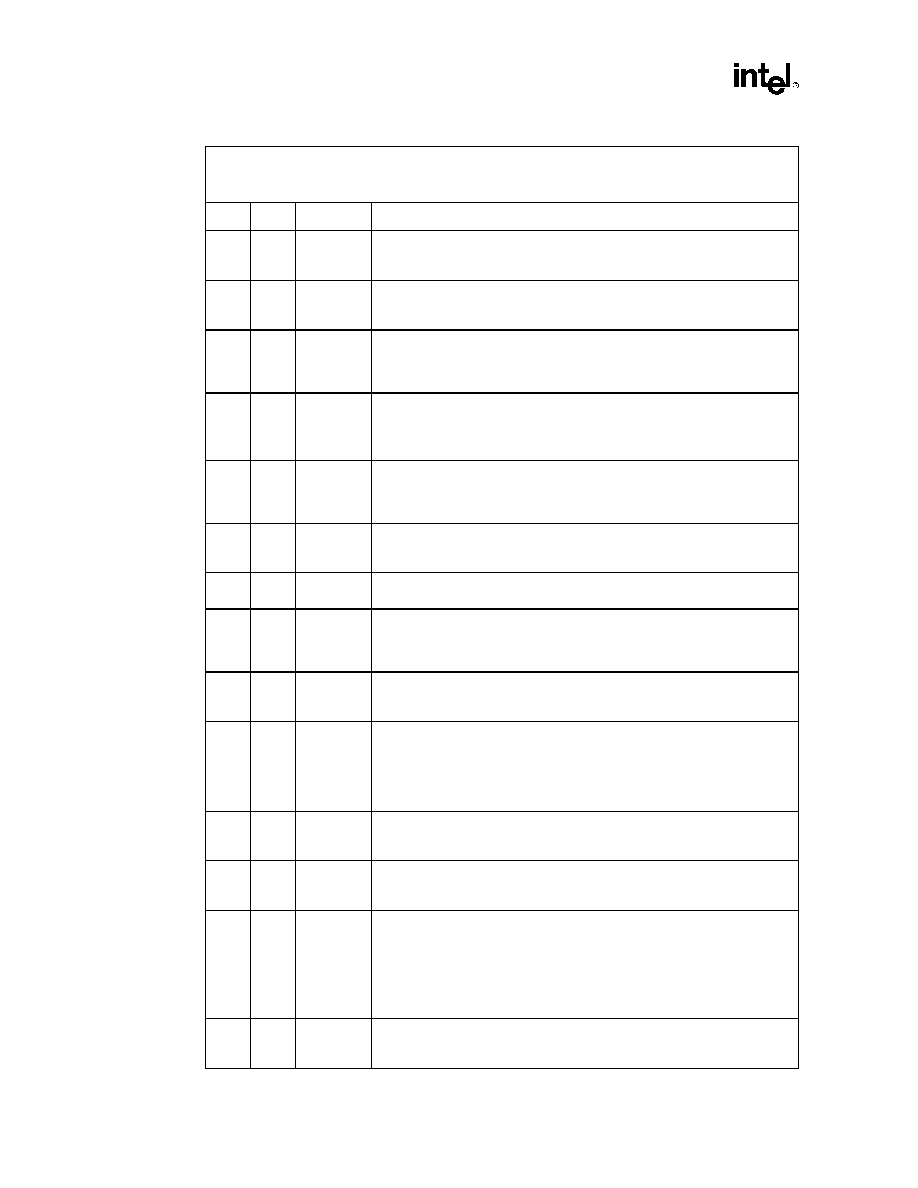

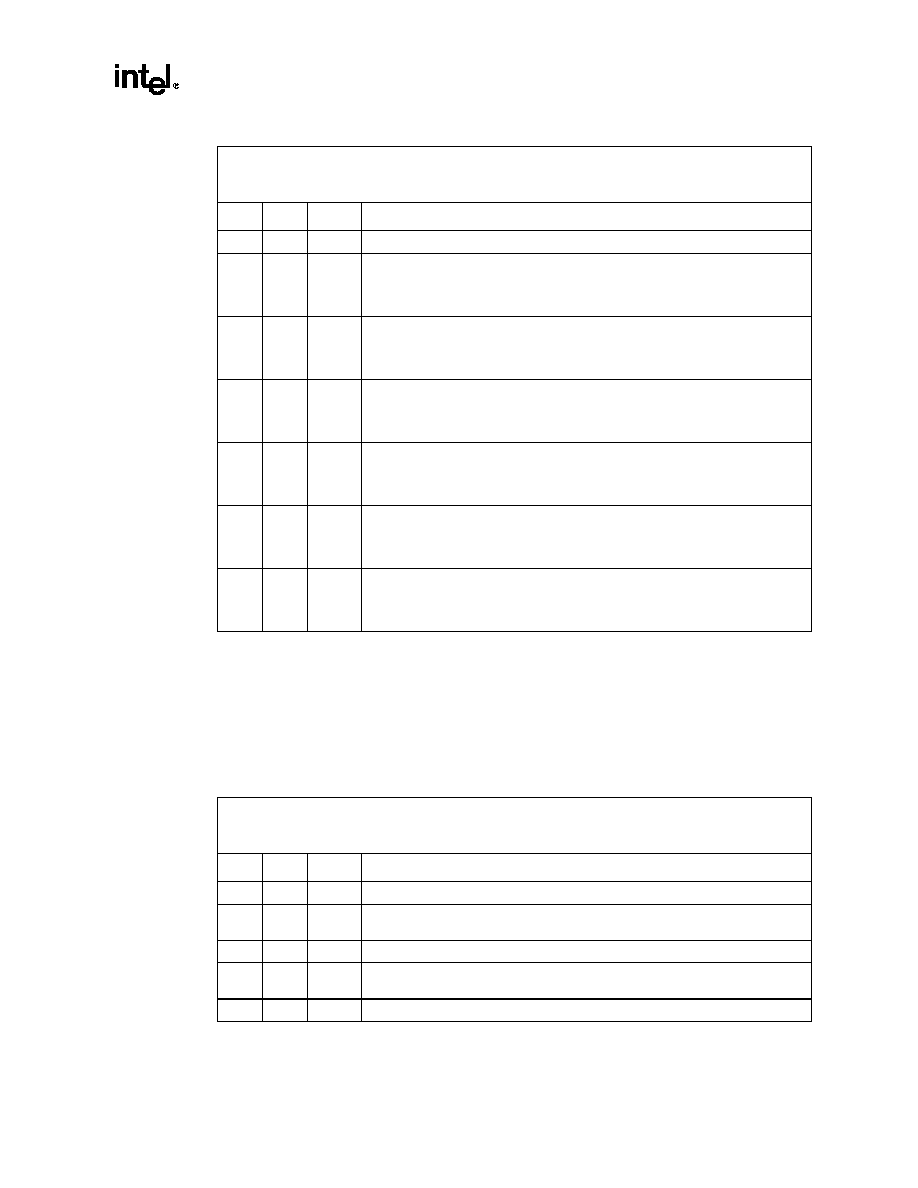

3.6.6

MIR[5:0]: Memory Interleave Range Registers

These registers define the home node of every main memory address. The six MIRs divide main

memory into six interleave ranges. Each range is of variable size and can have a different address

interleaves. The EN, BASE and SIZE fields define the existence and extent of this interleave. An

address falls in this interleave if:

EN && [BASE <= Address[43:27] < BASE + 2

SIZE

]

The SPS uses these registers to route requests to SP ports.

The four WAY fields in each MIR define the four nodes that own the memory in this interleave

range. The GRAN bit defines whether the SPS interleaves at the 128-byte level, or if the range is

divided into four equal-sized blocks. Any node can be assigned to any of the four ways, but these

ways must match the ways in the SNC MIRs.

If an address does not fall in any of the interleaves, the home node of packet is set to the same node

as Way[0] in MIR[0]. Note that MIR[0] must be enabled and WAY[0] must specify an SNC. If one

of the "WAY" fields is programmed to a non-existent port (6 or 7), the home node is also set as

WAY[0] in MIR[0]. MIR Blocks that are not used to map physical memory should be programmed

to point to port 7. There should be a one-to-one correspondence between MIR registers in the two

SPS's. Each Way field for the corresponding MIR in the other SPS must point to the same logical

node.

Device:

Node_ID

Function: 0-5

Offset:

84h, 8Ch, 94h, 9C, A4, AC

Bit

Attr

Default

Description

39:36

RV

0

Reserved

35

RW

0

EN: Range Enable

If set, route requests according to this register.

34:18

RW

00000h

BASE

This defines the lowest address in the interleave. These bits are compared against

A[43:27]. This field must be set to a multiple of the Interleave size defined below.

17

RW

0

GRAN: Interleave Granularity

This bit modifies how the WAY fields are interpreted.

If 1, the range is interleaved at the cache line granularity.

If 0, the range is divided into 4 equal-sized blocks.

16:12

RW

00000

SIZE

2

SIZE

is the number of 128 MB blocks in the interleave range.

11:9

RW

000

WAY3

If GRAN=0, route requests to this physical port for addresses in the highest block.

If GRAN =1, route requests to this physical port if A[8:7] = 11.

8:6

RW

000

WAY2

If GRAN=0, route requests to this physical port for addresses in the third block.

If GRAN =1, route requests to this physical port if A[8:7] = 10.

5:3

RW

000

WAY1

If GRAN=0, route requests to this physical port for addresses in the second block.

If GRAN =1, route requests to this physical port if A[8:7] = 01.

2:0

RW

000

WAY0

If GRAN=0, route requests to this physical port for addresses in the lowest block.

If GRAN =1, route requests to this physical port if A[8:7] = 00.

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

3-11

Configuration Registers

3.6.7

SIOH_MAP: SIOH Mapping Register

This register maps the SIOH0 and SIOH1 to particular physical ports. It can be used to route

transactions that are decoded to I/O range 0 or I/O range 1 of various registers such as MMIOLS,

MMIOHS, SARS. If only one SIOH is present, both fields should be set to that physical port.

3.6.8

MMIOLS: Memory-Mapped I/O Low Segment Register

This register divides the Low MMIO range between the two possible SIOHs connected to this SPS.

SP requests to the Low MMIO range have (Attr = MMIO) and (A[43:32] = 0) and

(A[31:20] != FEC). The boundary can be defined at 16 MB increments. The mapping of each

MMIOL range to SPS ports is defined in

Section 3.6.7, "SIOH_MAP: SIOH Mapping Register."

This register should be set to the same value as SIOH0.MMIOSL[5] + 1.

3.6.9

MMIOHS: Memory-Mapped I/O High Segment Register

This register divides the High MMIO range between the two possible SIOHs connected to this

SPS. SP requests to the High MMIO range have Attr = MMIO and A[43:40] = `0000 and A[39:32]

> 0. The boundary can be defined at 4GB increments. The mapping of each MMIOH range to SPS

ports is defined in

Section 3.6.7

. This register should be set to the same value as

SIOH0.MMIOSH[5]+ 1.

Device:

Node_ID

Function: 0-5

Offset:

B8h

Bit

Attr

Default

Description

7:6

RV

0

Reserved

5:3

RW

0

SIOH1: The port which all MMIOL/H, SAR, etc. range 1 traffic is sent.

2:0

RW

010

SIOH0: The port which all MMIOL/H, SAR, etc. range 0 traffic is sent. The SIOH on

this port contains the compatibility bus (PCI Bus 0) and is programmed the same

as CB_PORT.

Device:

Node_ID

Function: 0-5

Offset:

B4h

Bit

Attr

Default

Description

7:0

RW

0

Segment Address: Requests with A[31:24] >= MMIOLS will be routed to

SIOH_MAP.SIOH0. Otherwise, they will be routed to SIOH_MAP.SIOH1.If there is

only one SIOH, this register should be set to 0.

Device:

Node_ID

Function: 0-5

Offset:

BCh

Bit

Attr

Default

Description

7:0

RW

00

Segment Address: Requests with A[39:32] >= MMIOHS will be routed to

SIOH_MAP.SIOH0. Otherwise, they will be routed to SIOH_MAP.SIOH1. If there is

only one SIOH, this register should be set to 0.

Configuration Registers

3-12

Intel

Æ

E8870SP Scalability Port Switch (SPS) Datasheet

3.6.10

SARS: SAPIC Range Segment Register

This register divides the SAPIC range between the two possible SIOHs connected to this SPS. SP

requests to the SAPIC range have (Attr = MMIO) and (A[43:20] = 0FECh). The boundary can be

defined at 256 Byte increments. The mapping of each range to SPS ports is defined in

Section 3.6.7

. The PCI hot plug range is located within this range as well. This register should be

set to the same value as the SIOH0.SSEG[5]-1.

3.6.11

IOPORTS: I/O Space Segment Address

This register divides the I/O space between the two possible SIOHs connected to this SPS. As

opposed to the memory mapped I/O spaces, range1 is defined to be the higher range. IO write and

IO read requests with Attr = DND are routed according to this register. The boundary can be

defined at 2 KB increments. The mapping of each IO sub-range to SPS ports is defined in

Section 3.6.7

. This register should be set to the same value as SIOH0.IOL[5]-1.

3.6.12

PSEG: PCI Configuration Bus Segment Address

This register divides the PCI configuration space between the two possible SIOHs connected to the

SPS. The configuration read and write transactions are routed according to this register (using the

BusNo). The mapping of each sub-range to SPS ports is defined in

Section 3.6.7

. This register

should be set to the same value as SIOH0.BusNo[5]-1.

BusNo 0xFFh gets special handling, since it is reserved for the E8870 chipset. If the BusNo is

0xFFh, the SPS routes the configuration read/configuration write by matching the device number

in the configuration address to the NodeID field in the CBC register. If there is not a match, the