Intel StrataFlash

Æ

Memory (J3)

256-Mbit (x8/x16)

Datasheet

Product Features

Capitalizing on Intel's 0.25 and 0.18 micron, two-bit-per-cell technology, the Intel StrataFlash

Æ

Memory (J3)

device provides 2X the bits in 1X the space, with new features for mainstream performance. Offered in 256-

Mbit (32-Mbyte), 128-Mbit (16-Mbyte), 64-Mbit, and 32-Mbit densities, the J3 device brings reliable, two-bit-

per-cell storage technology to the flash market segment. Benefits include more density in less space, high-speed

interface, lowest cost-per-bit NOR device, support for code and data storage, and easy migration to future

devices.

Using the same NOR-based ETOXTM technology as Intel's one-bit-per-cell products, the J3 device takes

advantage of over one billion units of flash manufacturing experience since 1987. As a result, J3 components

are ideal for code and data applications where high density and low cost are required. Examples include

networking, telecommunications, digital set top boxes, audio recording, and digital imaging.

By applying FlashFileTM memory family pinouts, J3 memory components allow easy design migrations from

existing Word-Wide FlashFile memory (28F160S3 and 28F320S3), and first generation Intel StrataFlash

Æ

memory (28F640J5 and 28F320J5) devices.

J3 memory components deliver a new generation of forward-compatible software support. By using the

Common Flash Interface (CFI) and the Scalable Command Set (SCS), customers can take advantage of density

upgrades and optimized write capabilities of future Intel StrataFlash

Æ

memory devices. Manufactured on Intel

Æ

0.18 micron ETOXTM VII (J3C) and 0.25 micron ETOXTM VI (J3A) process technology, the J3 memory device

provides the highest levels of quality and reliability.

Performance

--110/115/120/150 ns Initial Access Speed

--125 ns Initial Access Speed (256 Mbit

density only)

--25 ns Asynchronous Page mode Reads

--30 ns Asynchronous Page mode Reads

(256Mbit density only)

--32-Byte Write Buffer

--6.8 µs per byte effective

programming time

Software

--Program and Erase suspend support

--Flash Data Integrator (FDI), Common

Flash Interface (CFI) Compatible

Security

--128-bit Protection Register

--64-bit Unique Device Identifier

--64-bit User Programmable OTP Cells

--Absolute Protection with V

PEN

= GND

--Individual Block Locking

--Block Erase/Program Lockout during

Power Transitions

Architecture

--Multi-Level Cell Technology: High

Density at Low Cost

--High-Density Symmetrical 128-Kbyte

Blocks

--256 Mbit (256 Blocks) (0.18µm only)

--128 Mbit (128 Blocks)

--

64 Mbit (64 Blocks)

--32 Mbit (32 Blocks)

Quality and Reliability

--Operating Temperature:

-40 ∞C to +85 ∞C

--100K Minimum Erase Cycles per Block

--0.18 µm ETOXTM VII Process (J3C)

--0.25 µm ETOXTM VI Process (J3A)

Packaging and Voltage

--56-Lead TSOP Package

--64-Ball Intel

Æ

Easy BGA Package

--Lead-free packages available

--48-Ball Intel

Æ

VF BGA Package (32 and

64 Mbit) (x16 only)

--V

CC

=

2.7 V to 3.6 V

--V

CCQ

= 2.7 V to 3.6 V

Order Number: 290667-021

March 2005

Notice: This document contains information on new products in production. The specifications are

subject to change without notice. Verify with your local Intel sales office that you have the latest

datasheet before finalizing a design.

2

Datasheet

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTELÆ PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY

ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN

INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS

ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES

RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER

INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The 3 Volt Intel StrataFlashÆ Memory may contain design defects or errors known as errata which may cause the product to deviate from published

specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-

548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © 2005, Intel Corporation. All rights reserved.

Intel and ETOX are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

*Other names and brands may be claimed as the property of others.

Datasheet

3

Contents

Contents

1.0

Introduction....................................................................................................................................7

1.1

Nomenclature .......................................................................................................................7

1.2

Conventions..........................................................................................................................7

2.0

Functional Overview .....................................................................................................................8

2.1

Block Diagram ......................................................................................................................9

2.2

Memory Map.......................................................................................................................10

3.0

Package Information ...................................................................................................................11

3.1

56-Lead TSOP Package .....................................................................................................11

3.2

Easy BGA (J3) Package .....................................................................................................12

3.3

VF-BGA (J3) Package ........................................................................................................13

4.0

Ballout and Signal Descriptions ................................................................................................14

4.1

Easy BGA Ballout (32/64/128/256 Mbit) .............................................................................14

4.2

56-Lead TSOP (32/64/128/256 Mbit)..................................................................................15

4.3

VF BGA Ballout (32 and 64 Mbit) .......................................................................................15

4.4

Signal Descriptions .............................................................................................................16

5.0

Maximum Ratings and Operating Conditions...........................................................................18

5.1

Absolute Maximum Ratings ................................................................................................18

5.2

Operating Conditions ..........................................................................................................18

6.0

Electrical Specifications .............................................................................................................19

6.1

DC Current Characteristics.................................................................................................19

6.2

DC Voltage Characteristics.................................................................................................20

7.0

AC Characteristics ......................................................................................................................22

7.1

Read Operations.................................................................................................................22

7.2

Write Operations.................................................................................................................26

7.3

Block Erase, Program, and Lock-Bit Configuration Performance .......................................27

7.4

Reset Operation..................................................................................................................29

7.5

AC Test Conditions.............................................................................................................29

7.6

Capacitance........................................................................................................................30

8.0

Power and Reset Specifications ................................................................................................31

8.1

Power-Up/Down Characteristics.........................................................................................31

8.2

Power Supply Decoupling...................................................................................................31

8.3

Reset Characteristics..........................................................................................................31

9.0

Bus Operations............................................................................................................................32

9.1

Bus Operations Overview ...................................................................................................32

9.1.1

Bus Read Operation ..............................................................................................33

9.1.2

Bus Write Operation ..............................................................................................33

9.1.3

Output Disable .......................................................................................................33

9.1.4

Standby..................................................................................................................34

9.1.5

Reset/Power-Down ................................................................................................34

Contents

4

Datasheet

9.2

Device Commands .............................................................................................................35

10.0 Read Operations.......................................................................................................................... 37

10.1 Read Array.......................................................................................................................... 37

10.1.1 Asynchronous Page Mode Read ........................................................................... 37

10.1.2 Enhanced Configuration Register (ECR)............................................................... 38

10.2 Read Identifier Codes ......................................................................................................... 39

10.2.1 Read Status Register............................................................................................. 39

10.3 Read Query/CFI.................................................................................................................. 41

11.0 Programming Operations ........................................................................................................... 42

11.1 Byte/Word Program ............................................................................................................ 42

11.2 Write to Buffer..................................................................................................................... 42

11.3 Program Suspend............................................................................................................... 43

11.4 Program Resume................................................................................................................ 43

12.0 Erase Operations......................................................................................................................... 44

12.1 Block Erase......................................................................................................................... 44

12.2 Block Erase Suspend ......................................................................................................... 44

12.3 Erase Resume .................................................................................................................... 45

13.0 Security Modes ............................................................................................................................ 46

13.1 Set Block Lock-Bit............................................................................................................... 46

13.2 Clear Block Lock-Bits.......................................................................................................... 46

13.3 Protection Register Program .............................................................................................. 47

13.3.1 Reading the Protection Register............................................................................ 47

13.3.2 Programming the Protection Register.................................................................... 47

13.3.3 Locking the Protection Register............................................................................. 47

13.4 Array Protection .................................................................................................................. 49

14.0 Special Modes.............................................................................................................................. 50

14.1 Set Read Configuration Register Command ...................................................................... 50

14.2 Status (STS) ....................................................................................................................... 50

Appendix A Common Flash Interface.................................................................................................52

Appendix B Flow Charts ......................................................................................................................59

Appendix C Design Considerations ...................................................................................................68

Appendix D Additional Information ....................................................................................................70

Appendix E Ordering Information.......................................................................................................71

Datasheet

5

Contents

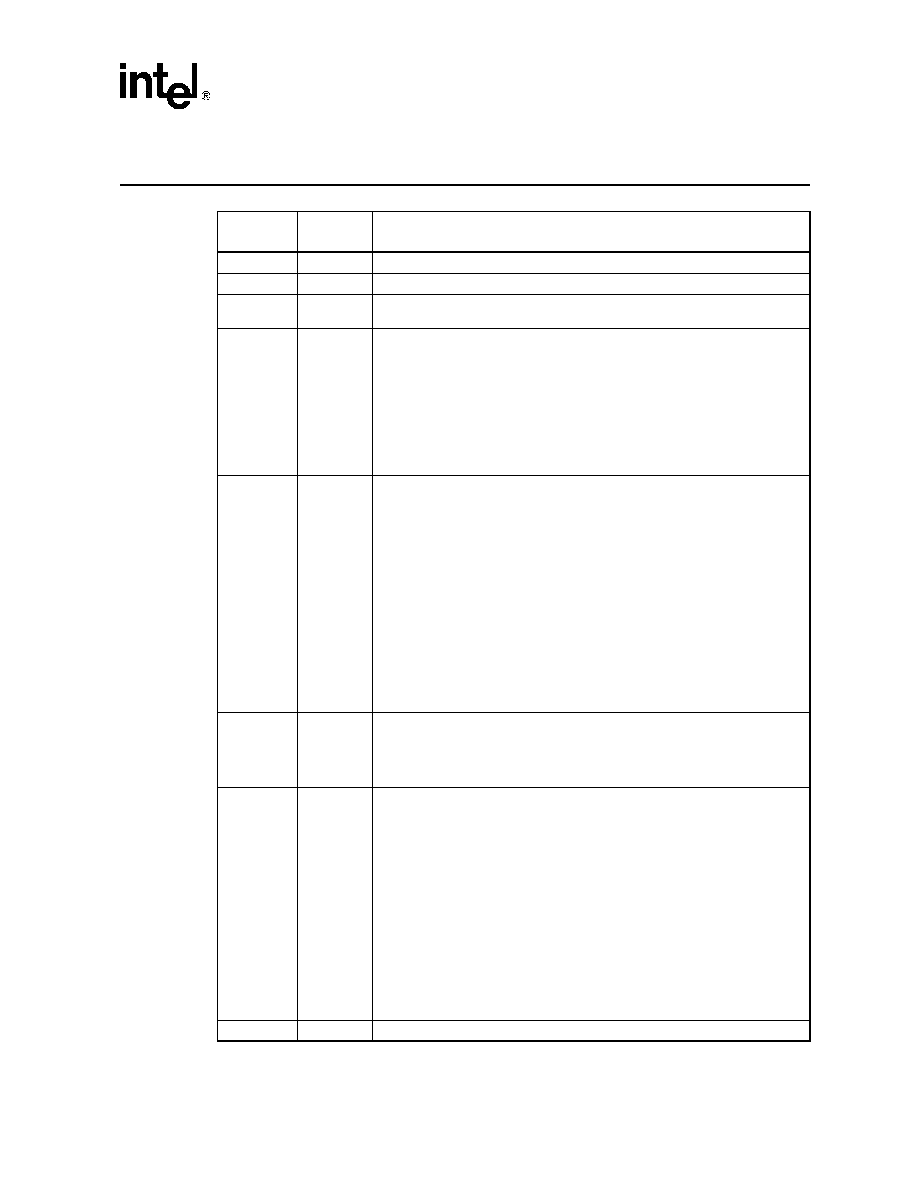

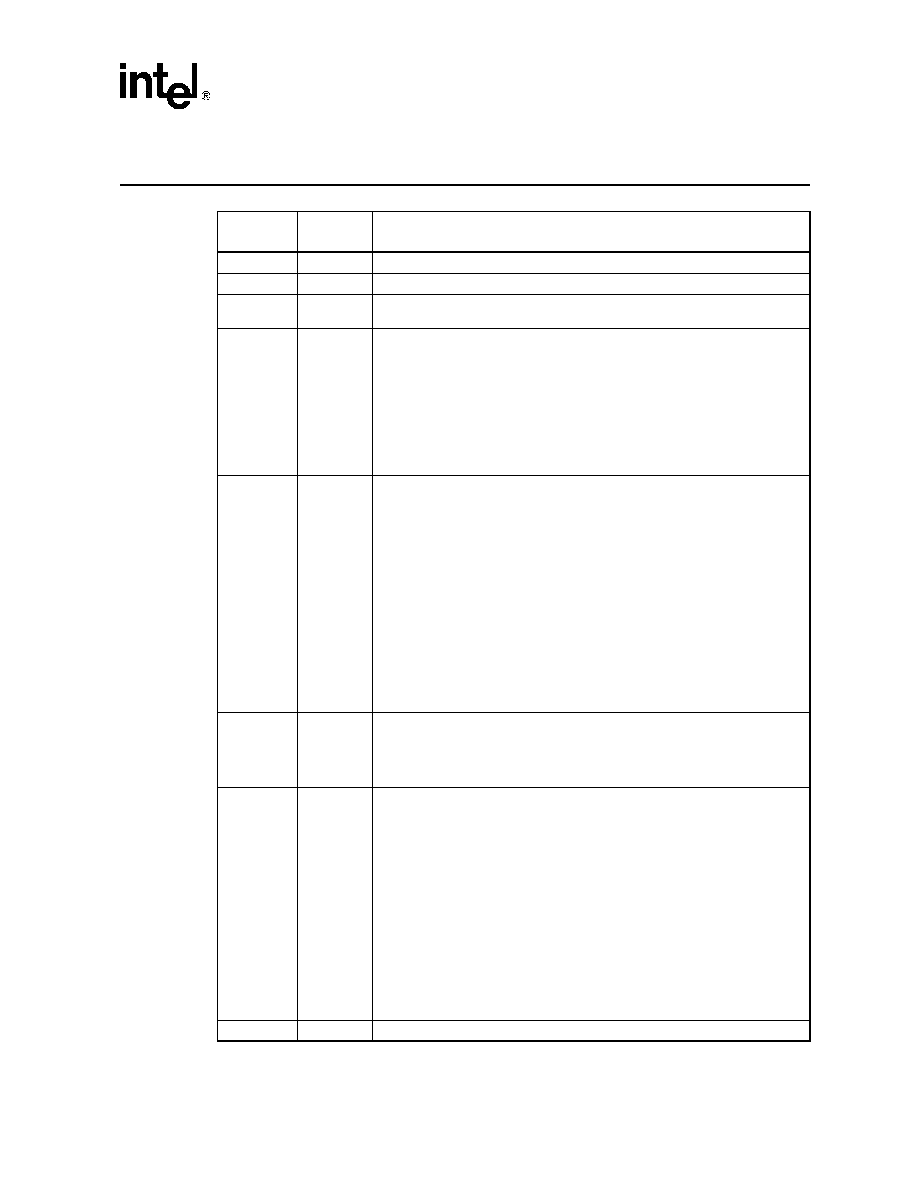

Revision History

Date of

Revision

Version

Description

07/07/99

-001

Original Version

08/03/99

-002

A

0

≠A

2

indicated on block diagram

09/07/99

-003

Changed Minimum Block Erase time,I

OL

, I

OH

, Page Mode and Byte Mode

currents. Modified RP# on AC Waveform for Write Operations

12/16/99

-004

Changed Block Erase time and t

AVWH

Removed all references to 5 V I/O operation

Corrected Ordering Information, Valid Combinations entries

Changed Min program time to 211 µs

Added DU to Lead Descriptions table

Changed Chip Scale Package to Ball Grid Array Package

Changed default read mode to page mode

Removed erase queuing from Figure 10, Block Erase Flowchart

03/16/00

-005

Added Program Max time

Added Erase Max time

Added Max page mode read current

Moved tables to correspond with sections

Fixed typographical errors in ordering information and DC parameter table

Removed V

CCQ1

setting and changed V

CCQ2/3

to V

CCQ1/2

Added recommended resister value for STS pin

Change operation temperature range

Removed note that rp# could go to 14 V

Removed V

OL

of 0.45 V; Removed V

OH

of 2.4 V

Updated I

CCR

Typ values

Added Max lock-bit program and lock times

Added note on max measurements

06/26/00

-006

Updated cover sheet statement of 700 million units to one billion

Corrected Table 10 to show correct maximum program times

Corrected error in Max block program time in section 6.7

Corrected typical erase time in section 6.7

2/15/01

-007

Updated cover page to reflect 100K minimum erase cycles

Updated cover page to reflect 110 ns 32M read speed

Removed Set Read Configuration command from Table 4

Updated Table 8 to reflect reserved bits are 1-7; not 2-7

Updated Table 16 bit 2 definition from R to PSS

Changed V

PENLK

Max voltage from 0.8 V to 2.0 V, Section 6.4, DC

Characteristics

Updated 32Mbit Read Parameters R1, R2 and R3 to reflect 110ns, Section 6.5,

AC Characteristics≠Read-Only Operations

(1,2)

Updated write parameter W13 (t

WHRL

) from 90 ns to 500 ns, Section 6.6, AC

Characteristics≠Write Operations

Updated Max. Program Suspend Latency W16 (t

WHRH1

) from 30 to 75 µs,

Section 6.7, Block Erase, Program, and Lock-Bit Configuration Performance

(1,2,3)

04/13/01

-008

Revised Section 7.0, Ordering Information