E

PRELIMINARY

October 1996

Order Number: 290578-003

n

High Performance Read

80/120 ns Max Access Time

40 ns Max. Output Enable Time

n

Low Power Consumption

20 mA Typical Read Current

n

x8-Only Input/Output Architecture

Space-Constrained 8-bit

Applications

n

Optimized Array Blocking Architecture

One 16-KB Protected Boot Block

Two 8-KB Parameter Blocks

One 96-KB Main Block

One 128-KB Main Block

Top Boot Location

n

Hardware Data Protection Feature

Erase/Write Lockout during Power

Transitions

Absolute Hardware Protection for

Boot Block

n

Software EEPROM Emulation with

Parameter Blocks

n

Extended Cycling Capability

100,000 Block Erase Cycles

n

Automated Byte Write and Block Erase

n

Industry-Standard Command User

Interface

Status Registers

Erase Suspend Capability

n

SRAM-Compatible Write Interface

n

Reset/Deep Power-Down Input

0.2 µA I

CC

Typical

Provides Reset for Boot Operations

n

Industry-Standard Surface Mount

Packaging

40-Lead TSOP

44-Lead PSOP

40-Lead PDIP

n

ETOXTM IV Flash Technology

5V Read

n

12V Write and Block Erase

V

PP

= 12V ±5% Standard

V

PP

= 12V ±10% Option

n

Independent Software Vendor Support

Intel's 2-Mbit flash memory is an extension of the Boot Block architecture which includes block-selective

erasure, automated write and erase operations, and a standard microprocessor interface. The 2-Mbit flash

memory enhances the Boot Block architecture by adding more density and blocks, x8 input/output control,

very high-speed, low-power, and industry-standard ROM-compatible pinout and surface mount packaging.

The Intel 28F002BC is an 8-bit wide flash memory offering. This high-density flash memory provides user-

selectable bus operation for 8-bit applications. The 28F002BC is a 2,097,152-bit nonvolatile memory

organized as 262,144 bytes of information. It is offered in 44-lead PSOP, 40- lead PDIP and 40-lead TSOP

package, which is ideal for space-constrained portable systems or any application with board space

limitations.

This device uses an integrated Command User Interface (CUI) and Write State Machine (WSM) for simplified

byte write and block erasure. The 28F002BC provides block locations compatible with Intel's MCSÆ-186

family, 80286, 90860CA, and the Intel386TM, Intel486TM, PentiumÆ, and Pentium Pro microprocessors.

The boot block includes a data protection feature to protect the boot code in critical applications. With a

maximum access time of 80 ns, this high-performance 2-Mbit flash memory interfaces at zero wait-state to a

wide range of microprocessors and microcontrollers. A deep power-down mode lowers the total V

CC

power

consumption to 1 µW typical. This power savings is critical in hand-held battery powered systems. For very

low-power applications using a 3.3V supply, refer to the Intel 28F002BV-T/B

2-Mbit SmartVoltage Boot Block

Flash Memory datasheet. Manufactured on Intel's 0.6 micron ETOXTM IV process technology, the 28F002BC

flash memory provides world-class quality, reliability, and cost-effectiveness at the 2-Mbit density.

28F002BC 2-MBIT (256K X 8)

BOOT BLOCK FLASH MEMORY

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or

otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of

Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to

sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or

infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life

saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

The 28F002BC may contain design defects or errors known as errata. Current characterized errata are available on request.

*Third-party brands and names are the property of their respective owners.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be

obtained from:

Intel Corporation

P.O. Box 7641

Mt. Prospect, IL 60056-7641

or call 1-800-879-4683

COPYRIGHT © INTEL CORPORATION, 1996

CG-041493

E

28F002BC 2-MBIT BOOT BLOCK FLASH MEMORY

3

PRELIMINARY

CONTENTS

PAGE

PAGE

1.0 INTRODUCTION .............................................5

1.1 Designing for Density Upgradeability............5

1.2 Main Features ..............................................5

1.3 Applications..................................................6

1.4 Pinouts.........................................................7

1.5 Pin Descriptions .........................................10

2.0 PRODUCT DESCRIPTION............................11

2.1 Memory Organization .................................12

2.1.1 Blocking...............................................12

2.1.2 28F002BC-T Block Memory Map.........12

3.0 PRINCIPLES OF OPERATION .....................12

3.1 Bus Operations ..........................................13

3.2 Read Operations ........................................13

3.2.1 Read Array ..........................................13

3.2.2 Intelligent Identifiers ............................14

3.3 Write Operations ........................................14

3.3.1 Command User Interface (CUI) ...........14

3.3.2 Status Register....................................17

3.3.3 Program Mode.....................................17

3.3.4 Erase Mode .........................................18

3.3.5 Extended Cycling ................................19

3.4 Boot Block Locking.....................................19

3.4.1 V

PP

= V

IL

for Complete Protection........19

3.4.2 RP# = V

HH

for Boot Block Unlocking....19

3.5 Power Consumption ...................................23

3.5.1 Active Power .......................................23

3.5.2 Standby Power ....................................23

3.5.3 Deep Power-Down...............................23

3.6 Power-Up/Down Operation.........................23

3.6.1 RP# Connected to System Reset ........23

3.6.2 V

CC

, V

PP

and RP# Transitions .............23

3.7 Power Supply Decoupling ..........................24

3.7.1 V

PP

Trace on Printed Circuit Boards ....24

4.0 ELECTRICAL SPECIFICATIONS..................25

4.1 Absolute Maximum Ratings ........................25

4.2 Operating Conditions..................................25

4.2.1 Capacitance.........................................26

4.2.2 Input/Output Test Conditions ...............26

4.2.3 DC Characteristics...............................27

4.2.4 AC Characteristics ...............................29

APPENDIX A: Ordering Information .................35

APPENDIX B:WSM Transition Table .................36

APPENDIX C: Additional Information ...............37

28F002BC 2-MBIT BOOT BLOCK FLASH MEMORY

E

4

PRELIMINARY

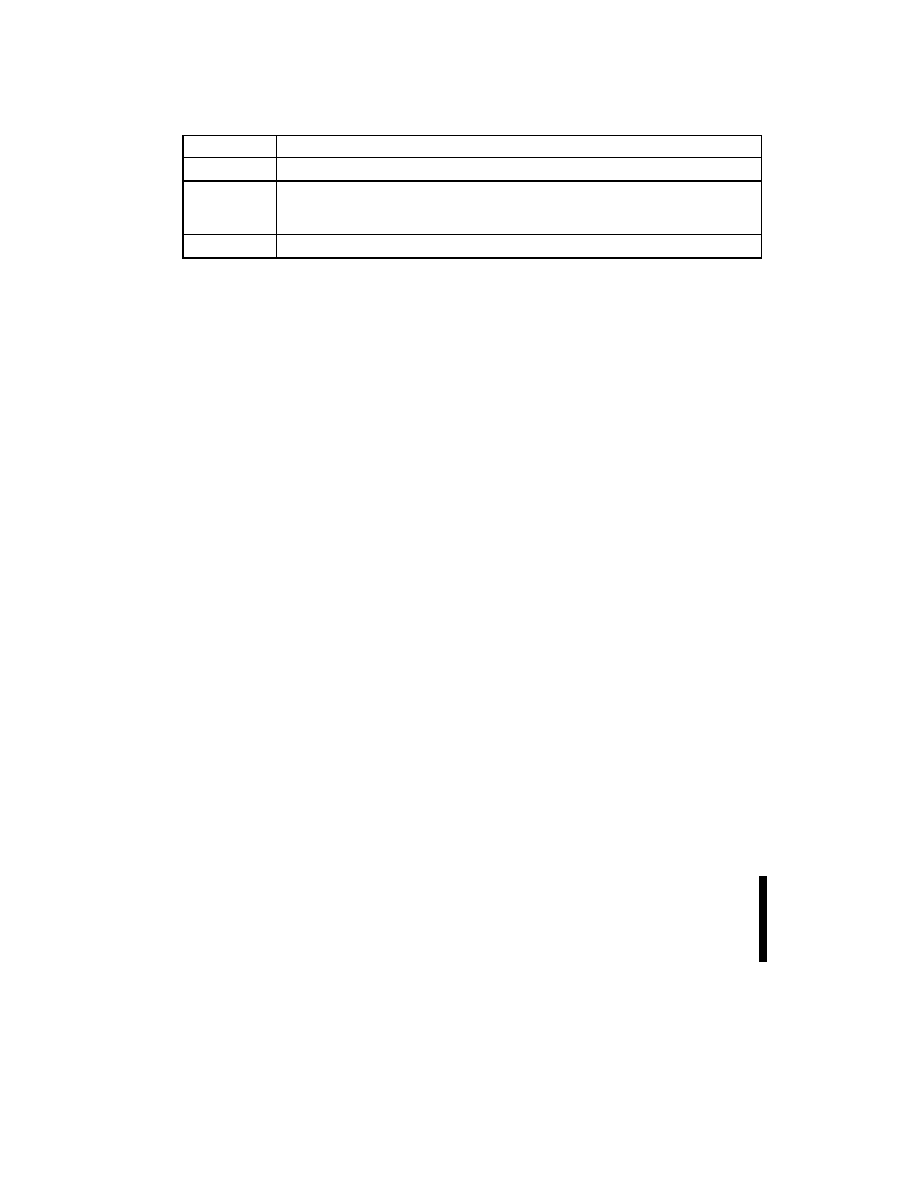

REVISION HISTORY

Number

Item

-001

Original version

-002

Pin 2 of 44-Lead PSOP changed from DU to NC

Alternate program command (10H) removed

WSM transition table added

-003

40-Lead PDIP package added

E

28F002BC 2-MBIT BOOT BLOCK FLASH MEMORY

5

PRELIMINARY

1.0

INTRODUCTION

This datasheet comprises the specifications for

the 28F002BC 2-Mbit flash memory. Section 1

provides an overview of the 2-Mbit flash memory,

including applications, pinouts, and pin

descriptions. Section 2 describes the memory

organization in detail. Section 3 defines a

description of the memory's principles of

operation. Finally, Section 4 details the memory's

operating specifications.

1.1

Designing for Density

Upgradeability

The 28F002BC has been optimized to meet

market requirements. Applications currently using

the 28F001BX and 28F002BX can migrate to this

product. Of course, both the 28F001BX and the

28F002BX devices use an 8-bit wide bus. Those

applications needing a 16-bit wide bus or lower

voltage can convert to the Smart 5 or

SmartVoltage family of flash memory products.

SmartVoltage is also the natural migration path to

the 4-Mbit density. Both the 28F002BC and the

4-Mbit SmartVoltage are offered in identical

packages to make upgrade seamless. A few

simple considerations can smooth the migration

path significantly:

1.

Connect the NC pin of the 28F002BC to GND

(this will retain boot block locking when a

4-Mbit SmartVoltage is inserted).

2.

Design a switchable V

PP

to take advantage of

the 5V V

PP

option on SmartVoltage devices.

3. If anticipating to use the 5V V

PP

option,

switch V

PP

to GND for complete write

protection.

Previous designs with Intel's 28F002BX devices

on occasion had to use a NOR gate (or some

other scheme) to prevent issues with floating

addresses latching incorrect data. The 28F002BC

has corrected this issue and does not need the

NOR gate. When migrating a design using the

28F002BX to the 28F002BC, the NOR gate can be

removed. When considering upgrading, packaging

is of paramount importance. Current and future

market trends indicate TSOP and PSOP as the

packages that will enable designs into the next

century.

1.2

Main Features

The 28F002BC Boot Block flash memory is a high-

performance, 2-Mbit (2,097,152 bit) flash memory

organized as 256 Kbytes (262,144 bytes) of 8 bits

each.

The 28F002BC has separately erasable blocks,

including a hardware-lockable boot block (16,384

bytes), two parameter blocks (8,192 bytes each)

and two main blocks (one block of 98,304 bytes

and one block of 131,072 bytes). An erase

operation typically erases one of the main blocks

in 2.4 seconds and the boot or parameter blocks in

1.0 second. Each block can be independently

erased and programmed 100,000 times.

The boot block is located at the top of the address

map to match the protocol of many systems,

including Intel's MCS-186 family, 80960CA, i860TM

microprocessors as well as Pentium and Pentium

Pro microprocessors. The hardware-lockable boot

block provides the most secure code storage. The

boot block is intended to store the kernel code

required for booting-up a system. When the RP#

pin is between 11.4V and 12.6V, the boot block is

unlocked and program and erase operations can

be performed. When the RP# pin is at or below

6.5V, the boot block is locked and program and

erase operations to the boot block are ignored.

The Command User Interface (CUI) serves as the

interface between the microprocessor or

microcontroller and the internal operation of the

28F002BC.

Program and Erase Automation allows program

and erase operations to be executed using an

industry standard two-write command sequence to

the CUI. Data writes are performed in byte

increments. Each byte in the flash memory can be

programmed independently of other memory

locations but is erased simultaneously with all

other locations within the block.

The status register (SR) indicates the status of the

internal Write State Machine (WSM), which reports

critical information on program and/or erase

sequences.

The maximum access time of 80 ns (t

ACC

) is

guaranteed over the commercial temperature

range (0∞C to +70∞C), 10% V

CC

supply voltage

range (4.5V to 5.5V) and 100 pF output load.