RHtMMU24

Rad Hard

Memory Management Unit

triple

triple

Data Sheet

FEATURES/BENEFITS:

DESCRIPTION:

Three DSP Memory Management Units in One Small

Package (A_MMU24, B_MMU24, C_MMU24)

Complements DSP24 and allows a complex sample rate

of 37.5 MHz for a 1K complex FFT with window

Polyphase addressing and control for FFT folding and

overlapping

Supports DSP, Complex math, Matrix math, FIRs, Block

Adds, Subtracts, Complex magnitude, etc.

Multiple RHtMMU24s maybe paralleled for increased

performance & radices up to Radix 1024

User programmable internal loops for virtually any DSP

memory address sequence.

Support for reduced latency stacked 1-D, 2-D, and 3-D

FFT algorithms.

Supports Radix 2 through Radix 1024 butterfly and

twiddle addressing

Simple 8-bit host interface reduces host address

decoding

Over 240 primitive DSP sequences buried in the chip

architecture dramatically reduce software development

Advanced sub-micron SOI process, (Honeywell HX3000

Gate Array) Extensive built in test including JTAG

FFT addressing from any offset address. Enhanced dual

(NN) real and double length (2N) real FFT support.

Total Dose > 300 K/Rads (1 Mrad Option Available)

ASIC silicon cores, Macro cells, Super cells, and

custom constructs available

RHtMMU24

SYSCLK EN

RESET

SYSCLK

VDD

START

VSS

R/W

DIR

CS

A0

A1

DB [7:0]

TCP

TC

PO

ACTIVE

CSWAP

MEMW

CCOMI

CCOMR

MEMOE

ADROE

ADR [19:0]

J [4:0]

FLAGS

MEMORY

CONTROL

SYSTEM

CONTROL

POWER

SUPPLY

HOST

INTERFACE

ADDRESS

OUTPUT

JTAG

ADDRESS

OUTPUT

ENABLE

20

5

8

8/4/2003

The RHtMMU24 Memory Management Unit is a high-

speed memory addressing device that is uniquely

designed to support FFT based approaches to real time

DSP applications, see Figure 1

The RHtMMU24 is a self-contained, small-pin-count

device with virtually no computational overhead. The

RHtMMU is intended to be used with DSP24 Digital

Signal Processor and other compatible execution units.

Each MMU in the RHtMMU24 can generate over 240

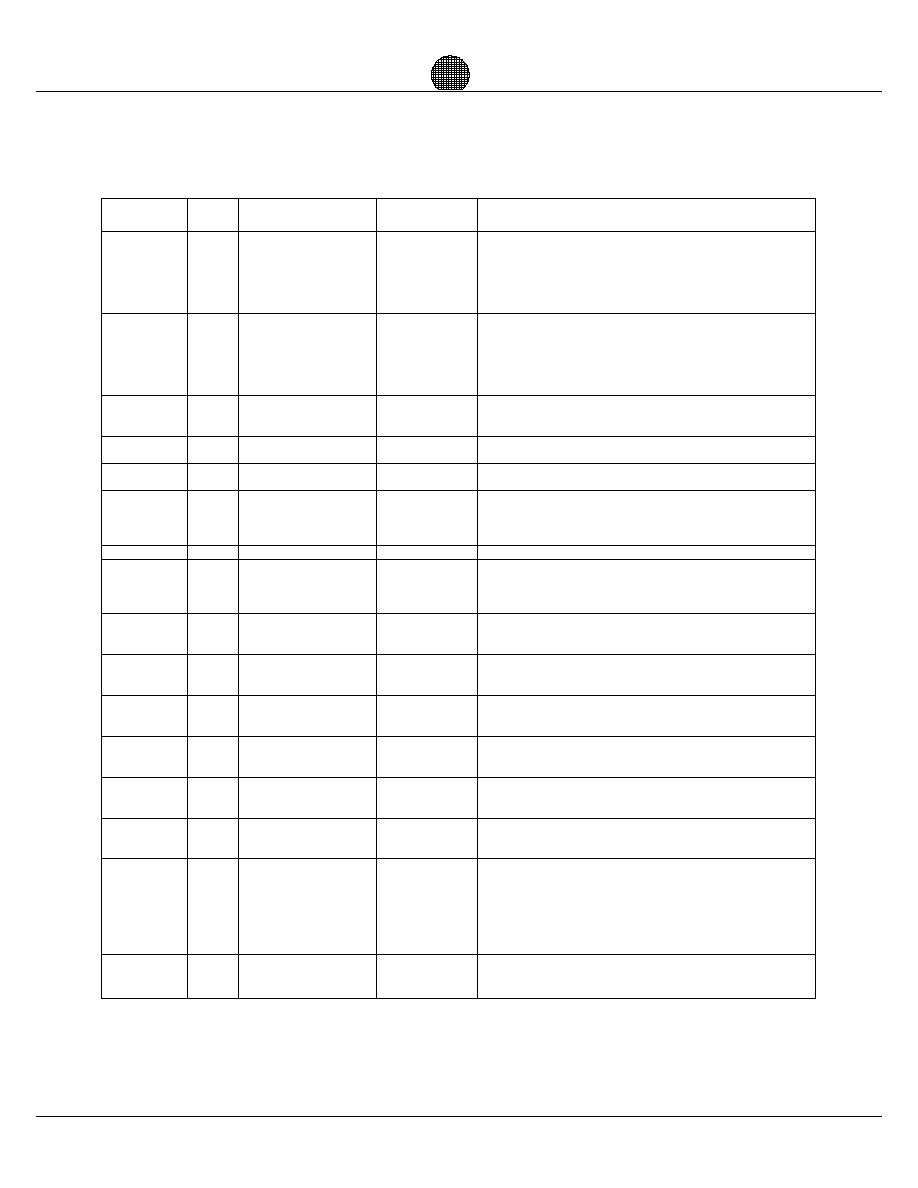

address patterns. Table 1 summarizes the MMU's

address pattern set.

The RHtMMU24 generates a series of addresses for

memory arrays. It is easily programmed to generate

addressing sequences between four points and one

million (1 Meg) points. The RHtMMU24 can be used for

standalone operation or as a peripheral on a host CPU

bus. The RHtMMU24 contains 32 words of program

memory that can be programmed via the 8-bit data bus

(internal memory mode). These 32 words (instructions)

of program memory are sufficient to generate algo-

rithms for many applications. For example, a 1 million

point, radix-32 FFT can be performed using only four

address patterns.

In contrast, in external memory mode, program memory

may be bypassed and the RHtMMU24 programmed in

external memory mode. For example, an adaptive

filtering algorithm that requires thousands of computed

passes is one type of algorithm that could be performed

in external mode.

Lastly, for unique applications the end user can gener-

ate custom address patterns with the RHtMMU24's dual

increment sequencer for such things as acquisition data

de-interleaving, 2-D and 3-D image corner turning,

polyphase overlapping wavelets, etc.

Architectures

TM

Transform Your World

DSP

X3

Figure 1. FFT Based Approach

PASS 1

BFLY4

PASS 2

BFLY4

PASS 3

BFLY4

PASS 4

BWND4

PASS 6

BFLY4

PASS 5

BFLY4

1

0

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

16

0

32

48

4

20

36

52

8

24

40

56

12

28

44

60

1

17

33

49

5

21

27

53

9

25

41

57

13

29

45

61

2

18

34

50

6

22

38

54

10

26

42

58

14

30

46

62

3

19

35

51

7

23

39

55

11

27

43

59

15

31

47

63

1

0

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

16

0

32

48

4

20

36

52

8

24

40

56

12

28

44

60

1

17

33

49

5

21

27

53

9

25

41

57

13

29

45

61

2

18

34

50

6

22

38

54

10

26

42

58

14

30

46

62

3

19

35

51

7

23

39

55

11

27

43

59

15

31

47

63

FFT

FFT

-1

first pass on inverse FFT

includes the filter response multiply

first pass on FFT includes the

window multiply, if any.

B

U

F

F

E

R

B

U

F

F

E

R

PASS 1

PASS 2

PASS 3

PASS 4

PASS 5

PASS 6

100 MSPS

100 MSPS

FFT

Filter Response

Coefficients

Multiply

FFT

Input

Output

-1

RHDSP24

S

R

A

M

SRAM

S

R

A

M

B

U

F

F

E

R

B

U

F

F

E

R

Ar

Dr

Er

Di

Ei

Br

Bi

Ai

Cr

Ci

PASS 1

FUNCTION

CODE

DATA

FLOW

PASS 2

PASS 3

PASS 4

PASS 5

PASS 6

6

9

Filter Response

Coefficients

Control

Input

Output

24

24

24

24

24

24

24

24

24

24

Data Sheet

Page 2

RHtMMU24

DSP Memory Manager

DSP

Architectures

RHtMMU24

1 Meg x 48

1 Meg x 48

1 Meg x 48

General Purpose/Utility Patterns

View Signature register

VIEWSIG

DUALINC1B

DUALINC1QNS

DUALINC1BQ

DUALINC1BQNS

DUALINC2

DUALINC2P

DUALINC2B

DUALINC2Q

DUALINC2QNS

DUALINC2BQ

DUALINC2BQNS

CLEARSIG

Dual Increment with Quadrant,

BitReverse(Turn off SWAP).

Use for windowing.

Dual Increment with Quadrant and

BitReverse enabled. Use

for windowing

Dual Increment with Quadrant

logic enabled (Turn off SWAP).

Use for windowing.

Dual Increment with BitReverse

enabled

Clear Signature register

Dual Increment with Quadrant,

BitReverse (Turn off SWAP).

Use for windowing.

Dual Increment with Quadrant and

BitReverse enabled.

Use for windowing.

Dual Increment with Quadrant

logic enabled (Turn off SWAP).

Use for windowing.

Dual Increment with Quadrant

(DEG90) logic enabled

Dual Increment with BitReverse

enabled

Dual Increment with PO enabled.

(Set SKEW PO High/Low for polarity)

Dual Increment (Use Configuration

Register Set #2)

General Purpose/Utility Patterns

Square of magnitude of a

complex number

Discard using late PO flag

Discard using early PO flag

Discard using PO flag

Discard

Pad at the start of a sequence

using late PO flag

Pad at the start of a sequence

using early PO flag

Pad at the start of a sequence

using PO flag

Pad at the start of a sequence

Pad at the end of a sequence

using late PO flag

Pad at the end of a sequence

using early PO flag

Pad at the end of a sequence

using PO flag

Pad at the end of a sequence

Replaced with DUALINC patterns

Replaced with DUALINC patterns

Replaced with DUALINC patterns

Index increment

No operation

Dual Increment with Quadrant

(DEG90) logic enabled

Dual Increment with PO enabled.

(Set SKEW PO High/Low for polarity)

Dual Increment (Use Configuration

Register Set #1)

NOP

INC

MODINC

MODDEC

PADHIGH

PADHIGHP

PADHIGHEP

PADHIGHLP

PADLOW

PADLOWP

PADLOWEP

PADLOWLP

OVERLAP

DISCARD

DISCARDP

DISCARDEP

DISCARDLP

CMAG

DUALINC1

DUALINC1P

DUALINC1Q

Table 1. RHtMMU24 Address Pattern Set Summary

Data Sheet

Page 3

RHtMMU24

DSP Memory Manager

Opcode

Opcode

E9

E8

E7

87

9D

9C

8A

89

9B

9A

95

94

99

98

7B

7A

72

00

FF

FE

F4

F3

F2

F1

F0

EF

EE

ED

EC

EB

EA

DSP

Architectures

Table 1. RHtMMU24 Address Pattern Set Summary (cont.)

Data Sheet

Page 4

RHtMMU24

DSP Memory Manager

Compatible Patterns

Compatible Patterns

Compatible Patterns

Digit Reverse Patterns

Digit reversed data address column 0

RBF0

TFx,MXBx,MXTx

BFx

Fast cosine transform separation

pass data addresses (2N point unload using late PO)

Fast cosine transform separation

pass data addresses (2N point unload using early PO)

Fast cosine transform separation

pass data addresses (2N point unload using PO flag)

Fast cosine transform separation

pass data addresses (N point unload, Store in N)

Fast cosine transform separation

pass data addresses (2N point unload, Store in 2N )

Fast cosine transform separation

pass data addresses (2N point unload, Store in N )

Fast cosine transform separation

pass twiddle addresses (2N points)

Fast cosine transform separation

pass data addresses (2N point load)

2 at-a-time real FFT separation

pass (2N point unload, Store in N)

2 at-a-time real FFT separation

pass (2N point unload)

2 at-a-time real FFT separation

pass (N point load)

2 at-a-time real FFT separation

pass (2N point load)

Recombine Patterns

BRFTL

BRFTLS

BRFTU

BRFTUS

BFCTL

BFCTT

BFCTUS

BFCTU

BFCTUS2

BFCTUP

BFCTUEP

BFCTULP

71

38

15

to

to

70

23

9F

9E

93

E6

92

91

90

8F

8E

8D

8C

8B

Opcode

Opcode

Opcode

DSP

Architectures

Table 1. RHtMMU24 Address Pattern Set Summary (cont.)

Figure 2. RHtMMU24 Interface Signals

Radix 32 twiddle factor Address

Column n (0 to 15)

Radix 16 twiddle factor Address

Column n (0 to 16)

Radix 8 twiddle factor Address

Column n (0 to 17)

Radix 4 twiddle factor Address

Column n (0 to 18)

Radix 2 twiddle factor Address

Column n (0 to 19)

Input/Output Butterfly Address

Column n (0 TO 19)

DSP Patterns

Opcodes

Opcodes

BFCn (0 to 19)

TF2Cn (0 to 19)

TF4Cn (0 to 18)

TF8Cn (0 to 17)

TF16Cn (0 to 16)

TF32Cn (0 to 15)

DSP Patterns (cont)

Radix 1024 twiddle factor Address

Column n (0 to 15)

Radix 512 twiddle factor Address

Column n (0 to 16)

Radix 256 twiddle factor Address

Column n (0 to 17 )

Radix 128 twiddle factor Address

Column n (0 to 18)

Radix 64 twiddle factor Address

Column n (0 to 19)

Data Sheet

Page 5

RHtMMU24

DSP Memory Manager

TF64Cn (0 to 19)

TF128Cn (0 to 18)

TF256Cn (0 to 17)

TF512Cn (0 to 16)

TF1024Cn (0 to 15)

01

to

14

24

to

37

24

to

37

A0

to

B2

A0

to

B2

B3

to

C4

B3

to

C4

C5

to

D5

C5

to

D5

D6

to

E5

D6

to

E5

RHtMMU24

SYSCLK EN

RESET

SYSCLK

VDD

START

VSS

R/W

DIR

CS

A0

A1

DB [7:0]

TCP

TC

PO

ACTIVE

CSWAP

MEMW

CCOMI

CCOMR

MEMOE

ADROE

ADR [19:0]

J [4:0]

FLAGS

MEMORY

CONTROL

SYSTEM

CONTROL

POWER

SUPPLY

HOST

INTERFACE

ADDRESS

OUTPUT

JTAG

ADDRESS

OUTPUT

ENABLE

20

5

8

DSP

Architectures

X3

SIGNAL

DIRECTION

SIGNAL NAME

DB[7:0]

A0,A1

R/W

CS

DIR

RESET

SYSCLK

START

SYSCLKEN

TC

TCP

ADR[19:0]

ADROE

CCOMR

CCOMI

SWAP

PO

MEMW

MEMOE

ACTIVE

VDD

VSS

JDO

JDI

JMS

JCK

JRST

I/O

I

I

I

I

I

I

I

I

O

O

O

I

I

I

I

I

O

O

O

O

O

O

O

O

P

P

Host Interface Data Bus

Host Control

Read/Write

Chip Select

System Clock

Start of Pass

Pause Address Generation when inactive (HIGH)

Terminal Count

Programmable TC

Address Outputs

Address Output Enable

Coefficient Complement Real (data to DSP24)

Coefficient Complement Imaginary (data to DSP24)

Swap Real and Imaginary (data to DSP24)

Programmable Output

Memory Write

Memory Output Enable

User Programmable Flag

+3.3 Volt Power Supply

Chip Ground

JTAG Test Signal

JTAG Test Signal

JTAG Test Signal

JTAG Test Signal

JTAG Test Signal

Host Interface Direction

Chip Reset

Table 2. RHtMMU24 Interface Signals

Data Sheet

Page 6

RHtMMU24

DSP Memory Manager

DSP

Architectures

INTERFACE SIGNALS

The RHtMMU24 interface signals are shown in Figure 2 and

summarized in Table 2.

DB[7:0] (Host Interface Data Bus)

In internal memory mode, the 8-bit data bus, DB[7:0], is used

to load RHtMMU24 registers via a two-step scheme: First

write the address of the target register, then write the data. In

external memory mode, the register address is set to one of

three predefined locations based on the A1, A0 signals. In this

case, the DB[7:0] data bus transfers data to the selected

predefined location.

A1,A0 (Host Control)

For internal memory mode, the A1,A0 signals define the input

to the DB[7:0] data bus as:

Address to a target register (A1 is LOW, A0 is HIGH)

Data to a target data (A1 is LOW, A0 is LOW).

In external memory mode, A1, A0 sets the register address to

one of the following predefined address location:

Location 31 of program memory (Host Register Address 1F)

Location 31 of pipeline/latency memory (Host Register

Address 3F)

MODE register (Host Register Address A2)

Refer to Host Interface Table 2 for more information.

R/W (Read/Write Host)

R/W loads each Host register on its rising edge, effectively

becoming the clock for all Host registers.

Note: R/W loads the Host registers. The SYSCLK signal

controls the execution and output of the RHtMMU24 after the

Host is loaded. The R/W and SYSCLK signals do

NOT have to be synchronous with one another. However, the

START signal must be synchronized to the SYSCLK.

CS (Chip Select)

When set LOW, CS enables the RHtMMU24 to communicate

with the Host to program the registers. When CS is set HIGH,

the RHtMMU24 disables the decoding of the DB[7:0], A1, and

A0 signals.

DIR (Read/Write Direction of the DB[7:0] Host Interface

Data Bus)

When DIR is set LOW, the DB[7:0] bus is tri-stated, and writing

of address and data values are allowed.

When DIR is set HIGH, the DB[7:0] bus is driven by the

RHtMMU24 with the register value located at the last written

address location.

RESET (Chip Reset)

When set HIGH, RESET does a hardware reset of the

RHtMMU24 chip. When set LOW, normal operation of the

RHtMMU24 chip is enabled.

START (Start of a Pass)

START is an edge-triggered signal that initiates the

generation of each addressing sequence. After the initial

START, the RHtMMU24 requires seven SYSCLK cycles

of latency before the first valid address is output. Each

subsequent START can be set to zero latency provided

START is issued before the end of the current sequence.

Note: START must be synchronized to the SYSCLK

signal and must not be issued at least two SYSCLK

cycles after the last write to the host memory.

START for "Pre-Starting" must go active at least 6 cycles

before last address.

START for "Pre-Starting" must NOT go active on the cycle

following TC rising edge.

External programming must be finished at least 7 cycles

before end of current pattern.

SYSCLK (System Clock)

SYSCLK controls the execution and output of the address

calculation logic. A new address is generated on each

rising edge of the SYSCLK signal. Refer to Address

Calculation for more information.

Note: The START signal must be synchronized to

SYSCLK.

SYSCLKEN

An active HIGH on the SYSCLKEN signal causes the

current address generation to stop, and continuously

output the last value. When SYSCLKEN returns inactive

(LOW), the address generation will resume.

TC (Terminal Count)

TC indicates when an addressing sequence has been

completed. By default, TC goes HIGH one cycle before

the end of the current addressing sequence. TC remains

HIGH until the next START signal causes a valid address

to be generated. The LOW to HIGH transition of TC can

be delayed by one cycle (to the actual end of the

sequence) by setting bit 3 in the MODE register to HIGH.

Refer to MODE Register. Once the transitions of TC are

defined, they may be skewed together by a value in the

SKEW register.

The TC region of activity may be skewed by -1 to +6

SYSCLK cycles from its normal offset of 0 as defined by

the SKEW register.

.

Data Sheet

Page 7

RHtMMU24

DSP Memory Manager

DSP

Architectures

Note: The PAUSE register affects The TC signal. If PAUSE is

used, TC transitions low to high one cycle before the

sequence length + PAUSE.

TCP (Programmable TC)

This signal is equivalent to the TC signal, with the additional

capability of allowing the user to invert the output polarity, or to

cause it to act like a mini-TC for address sequences that are

executed back-to-back via the MASTERREPEAT register.

(Strobe LOW and then HIGH one address before the last

address out for each of the individual address sequences.)

The controls for delaying TCP by a SYSCLK cycle, for

inversion, and for strobing during a MASTERREPEAT are

located in the SKEW register.

The TCP region of activity may be skewed by -1 to +6

SYSCLK cycles from its normal offset of 0 as defined by the

SKEW register.

Note: TCP is set HIGH after a reset.

ADR[19:0] Address Outputs

ADR[19:0] are the address outputs from the RHtMMU24.

They may be Tri-Stated with the ADDROE signal.

ADROE (Address Output Enable)

This signal controls how the ADR[19:0] are driven. When

active LOW, the ADR[19:0] signals are driven. When inactive

HIGH, the ADR[19:0] signals are Tri-Stated.

CCOMR, CCOMI, SWAP (Coefficient Complement Real

and Imaginary, and Swap Real/Imaginary)

These three signals can be used to manipulate coefficient

data when they are connected to the DSP24 corresponding

.

inputs. They indicate functions that should be applied to

the data input to the DSP24 coefficient port in order to

facilitate storage of Twiddle Coefficient data for FFT's in

1/4 of the normal required storage space or Window data

in 1/2 of the normal required storage space. These

signals are activated only when bit 4 in the MODE register

is set HIGH and a twiddle address pattern is used. All

signals are Tri-Stated when not used.

CCOMR, CCOMI, and SWAP are generated from the

quadrant in the lookup table that the output address is

pointing to. The MEMSIZE register defines the size of the

lookup table.

An Active HIGH level on the coefficient complement real

(CCOMR) signal indicates that the real coefficient point

should be complemented.

An Active HIGH level on the coefficient complement

imaginary (CCOMI) signal indicates that the real coeffi-

cient point should be complemented.

An Active HIGH level on the SWAP signal indicates that

the real and imaginary Coefficient data should be

exchanged. If active at the same time as CCOMR or

CCOMI, the CCOMR/CCOMI operation should be

performed first (This is the order of precedence the

DSP24 uses.)

The CCOMR, CCOMI, and SWAP signals region of

activity may be skewed by 0 to +6 SYSCLK cycles from its

normal offset of 0 as defined by the SKEW register

PO (Programmable Output)

PO indicates when an index address is being produced.

When HIGH, the PO signal indicates that the actions

shown in Table 3 need to be performed.

s

.

Data Sheet

Page 8

RHtMMU24

DSP Memory Manager

DUALINC2P

DUALINC1P

BFCTULP

BFCTUEP

BFCTUP

DISCARDLP

DISCARDEP

DISCARDP

PADLOWLP

PADLOWEP

PADLOWP

PADHIGHLP

PADHIGHEP

PADHIGHP

Table 3. PO Signal Selections

User defined flag for custom solutions

User defined flag for custom solutions

Data for the previous address (highest frequency component) needs to be written

Data for the next address (highest frequency component) needs to be written

Data for the highest frequency component needs to be discarded

Data for the previous address needs to be discarded

Data for the next address needs to be discarded

Data needs to be discarded

Data for the previous address needs to be padded

Data for the next address needs to be padded

Data needs to be padded

Data for the previous address neeeds to be padded

Data for the next address needs to be padded

Data needs to be padded

DSP

Architectures

The PO region of activity may be skewed by -1 to +6 SYSCLK

cycles from its normal offset of 0 as defined by the SKEW

register.

The phase of PO (PADHIGH or PADLOW) is defined by the

SKEW register for the DUALINC1P and DUALINC2P address

patterns.

Note: after a reset or if PO is not used by a valid addressing

sequence, this signal is set to high-impedance.

MEMW (Memory write)

MEMW indicates when the execution unit is to write to the

SRAM. This signal is controlled by bit 7 of the pipe-

line/memory latency memory. MEMW is pulsed LOW when

data is to be written to the SRAM. MEMW is set HIGH when

data is read from the SRAM.

The MEMW region of activity may be skewed by -1 to +6

SYSCLK cycles from its normal offset of 0 as defined by the

SKEW register.

Note: MEMW is set inactive HIGH after a reset.

MEMOE (Memory Output Enable)

MEMOE controls the output enable of the SRAM. This signal

is controlled by bit 7 of the pipeline/memory latency memory.

MEMOE is set LOW when data is to be read from the SRAM.

MEMOE is set HIGH when data is to be written to the SRAM.

Data Sheet

Page 9

RHtMMU24

DSP Memory Manager

The MEMOE region of activity may be skewed by -1 to +6

SYSCLK cycles from its normal offset of 0 as defined by

the SKEW register.

Note: MEMOE is set inactive HIGH after a reset.

ACTIVE

ACTIVE is a user-defined flag that can be defined on a

pass basis alongside the Function Code and Latency.

When enabled, the ACTIVE signal will go LOW with the

first address output, and HIGH the cycle after the last

address, effectively framing the addresses of interest.

The ACTIVE region of activity may be skewed by -1 to +6

SYSCLK cycles from its normal offset of 0 as defined by

the current instruction pointer to the extended feature

memory.

Note: ACTIVE is set inactive HIGH after a reset.

VDD

VDD is the power supply for the chip

VSS

VSS is the ground for the chip.

J[4:0]

JTAG chip test pins.

Figure 3. RHtMMU24 Simplified Block Diagram

R/W

SYSCLK

ADDR[19:0]

CS

RESET

MEMW

START

MEMOE

PAUSE

CCOMR

CCOMI

SWAP

TC

TCP

PO

ACTIVE

DIR

HOST

PROGRAM

COUNTER

CLOCK

CONTROL

ADDRESS

CALCULATION

A0

A1

DB[7:0]

DSP

Architectures

BLOCK LEVEL DESCRIPTION

RHtMMU24 Block Diagram

The RHtMMU24 Memory Manager consists of the following

functional sections: Host, Address Calculation, Clock Control,

and Program Counter. See Figure 3

HOST

The Host Interface allows the RHtMMU24 to be programmed

and read from a simple 8-bit data bus. Through this data bus,

the user is able to access any of the 214 internal memory

locations.

The host memory is segmented into two major groups of

registers, which are the execution registers, and the configura-

tion registers.

See Host Memory Map Figure 4.

The execution registers are made up of the Program Memory,

Latency Memory, and the Extended Feature Memory register

files. Each of the locations of the register files may be pro-

grammed or read in any order, however, when the RHtMMU24

is started (via START) only one value from each of these

registers is used at a time. The values that are used are

determined by the current Program Counter's index.

The configuration registers make up the remainder of the

registers. These registers differ from the execution registers in

that multiple registers may be needed at any one time depend-

ing on the address pattern being executed. See Figure 7

REGISTER DEFINITIONS

Program Memory

The program memory contains 32, 8-bit registers (locations 0-

1F) that can store up to 32 address patterns.

Pipeline/Memory Latency Memory

The pipeline/memory latency memory contains 32, 8-bit

registers (locations 20-3F) that store the latency value for

each address pattern. The latency value defines when the

related address pattern is to be generated. Memory latency

values can range from 0 to 127 (bits[6:0]). However, by

setting bit 5 of the mode register to HIGH, the latency

numbers can be multiplied by 2, thus extending the latency

range to 254. Bit 7 of the pipeline/memory latency memory

indicates that the RHtMMU24 is reading from or writing to the

SRAM. Refer to MEMOE (Memory Output Enable) Signal,

MEMW (Memory Write) Signal, and to MODE Register. See

LATENCY Register Figure 5.

Extended Feature Memory

The Extended Feature memory is divided into two banks of

32. The first bank contains 32, 8-bit registers (locations 40-

5F) that store 5 additional MSB bits for the latency value for

each address pattern. The upper 3 MSB's define the

relative skew (-1 to +6 SYSCLK cycles from its normal

offset of 0) for the ACTIVE signal.

The second bank contains 32, 1-bit registers (locations 60-

7F) that store the enable control for the ACTIVE signal. See

EXTENDED MEMORY Register Figure 5.

Configuration Registers

The configuration registers (A0-F6) comprise the remainder

of the RHtMMU24 Host Memory

PCSTART Register

The 5-bit PCSTART register (A0) points to the first address

pattern to be executed in program memory or where the next

address pattern will come from if the current address pattern

equals PCEND.

In external memory mode, PCSTART is disabled and the first

address pattern to be executed points to location 31 of the

program memory.

PCEND Register

The 5-bit PCEND register (D3) points to the last address

pattern to be executed in program memory. In external

memory mode, PCEND is disabled and the last address

pattern to be executed points to location 31 of program

memory.

MODE Register

The 8-bit Mode register (A2) defines the various modes of

operation of the RHtMMU24. The bits for the MODE register

shown in Figure 4 are defined as follows:

Bit 0, Determines when the RHtMMU24 is in internal or

external memory mode (internal is LOW, external is HIGH).

Bit 1, Enables the BREAKPOINT register (enable is HIGH,

disable is LOW).

Bit 2, Enables the DIGITREV logic. (enable is HIGH, normal

operation is LOW).

Bit 3, Delays the Low-to-High transition of TC by 1 cycle to

the actual end of the sequence (1 cycle delay is HIGH, no

delay is LOW). If delayed, TC goes HIGH at the same time

that the last address is generated. Bit 3 does not affect the

falling edge of TC.

Bit 4, Enables the Quadrant logic to force the output address

into 90 degrees of the MEMSIZE sized lookup table and

signal which quadrant the address is in via the CCOMR,

CCOMI, and SWAP signals.

Bit 5, Indicates when the values in the Latency Memory[12:0]

are multiplied by 2 (Multiplied by 2 is HIGH).

Bit 6, Enables the output of the signature register on the

ADDR[19:0] lines when active HIGH.

Bit 7, Clears the signature register when active HIGH.

Data Sheet

Page 10

RHtMMU24

DSP Memory Manager

DSP

Architectures

Data Sheet

Page 11

RHtMMU24

DSP Memory Manager

ADR2START [7:0]

ADR2START [15:8]

ADR2START [19:16]

ADR2LENGTH [7:0]

ADR2LENGTH [19:16]

ADR2LENGTH [15:8]

ADR2INC [7:0]

ADR2INC [15:8]

ADR2INC [19:16]

INDEX2LENGTH [7:0]

INDEX2LENGTH [15:8]

INDEX2LENGTH [19:16]

INDEXSTART [7:0]

INDEXSTART [15:8]

INDEXSTART [19:16]

ZEROPAD / INDEX2INC [7:0]

ZEROPAD / INDEX2INC [15:8]

ZEROPAD / INDEX2INC [19:16]

ADRSTART [7:0]

ADRSTART [15:8]

ADRSTART [19:16]

ADRLENGTH [7:0]

ADRLENGTH [15:8]

ADRLENGTH [19:16]

ADRINC [7:0]

ADRINC [15:8]

ADRINC [19:16]

INDEXLENGTH [7:0]

INDEXLENGTH [15:8]

INDEXLENGTH [19:16]

INDEXINC [7:0]

INDEXINC [15:8]

INDEXINC [19:16]

INDEX2START [7:0]

INDEX2START [15:8]

INDEX2START [19:16]

PAUSE [7:0]

PAUSE [15:8]

PAUSE [19:16]

BREAKPOINT [7:0]

BREAKPOINT [15:8]

BREAKPOINT [19:16]

DINC2PAIRS [7:0]

DINC2PAIRS [15:8]

DINC2PAIRS [19:16]

N [7:0]

N [15:8]

N [20:16]

ADDRESS PATTERN 31

ADDRESS PATTERN 1

ADDRESS PATTERN 0

LATENCY FOR PATTERN 0

LATENCY FOR PATTERN 31

LATENCY FOR PATTERN 1

EXT FEAT [7:0] FOR PATTERN 0

EXT FEAT [7:0] FOR PATTERN 31

EXT FEAT [8:8] FOR PATTERN 31

EXT FEAT [8:8] FOR PATTERN 1

EXT FEAT [8:8] FOR PATTERN 0

EXT FEAT [7:0] FOR PATTERN 1

NOT USED

NOT USED

NOT USED

NOT USED

NOT USED

PCSTART [4:0]

MODE [7:0]

SKEW [7:0]

SKEW [21:16]

SKEW [15:8]

HALT [0]

MASTER OFFSET [7:0]

MASTER OFFSET [15:8]

MASTER OFFSET [19:16]

MASTEROFFINC [7:0]

MASTEROFFINC [15:8]

MASTEROFFINC [19:16]

MASTERREPEAT [7:0]

MASTERREPEAT [15:8]

MASTERREPEAT [19:16]

MEMSIZE [7:0]

MEMSIZE [15:8]

MEMSIZE [20:16]

DISCARD / DINC1PAIRS [7:0]

DISCARD / DINC1PAIRS [15:8]

DISCARD / DINC1PAIRS [19:16]

INCINDEXSTART [7:0]

INCINDEXSTART [15:8]

INCINDEXSTART [19:16]

INCINDEX2START [7:0]

INCINDEX2START [15:8]

INCINDEX2START [19:16]

INCADRSTART [7:0]

INCADRSTART [15:8]

INCADRSTART [19:16]

INCADR2START [7:0]

INCADR2START [15:8]

INCADR2START [19:16]

DIGITREV [7:0]

DIGITREV [15:8]

DIGITREV [19:16]

PCEND [4:0]

CHIPID [7:0]

Figure 4. Host Memory Map

Program

Memory

Latency

Memory

Extended

Feature

Memory

AE

AD

AC

AB

AA

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

9F

81

80

7F

61

60

5F

41

40

3F

21

20

1F

1

0

D2

D1

D0

CF

CE

CD

CC

CB

CA

C9

C8

C7

C6

C5

C4

C3

C2

C1

C0

BF

BE

BD

BC

BB

BA

B9

B8

B7

B6

B5

B4

B3

B2

B1

B0

AF

F6

F5

F4

F3

F2

F1

F0

EF

EE

ED

EC

EB

EA

E9

E8

E7

E6

E5

E4

E3

E2

E1

E0

DF

DE

DD

DC

DB

DA

D9

D8

D7

D6

D5

D4

D3

DSP

Architectures

ACTIVE Enable

ACTIVE Skew

8

7

6

5

4

3

2

1

0

PO skew

PO High/Low

TCP Repeat

TCP Invert

TCP Delay rise by one cycle

TCP Skew

TC Skew

CCOMR/CCOMI/SWAP Skew

MEMOE Skew

MEMW Skew

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

SKEW Register

Modifies successive address patterns generated by the Repeat Count to come

from successive PROGRAM MEMORY locations by incrementing the PROGRAM

COUNTER. (This effectively concatenates address patterns)

Repeat Current Address Pattern 0 to 524,287

times more

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

MASTER REPEAT Register

Latency MSB (0 to 31)

(Latency=MSB*128 + LSB)

EXTENDED MEMORY Register

MEM Read/Write (0=Write, 1=Read)

7

6

5

4

3

2

1

0

Latency LSB (0 to 127)

LATENCY Register

Digit Reverse Enable

7

6

5

4

3

2

1

0

MODE Register (When Set:)

Use External Memory Access

Halt Enable

Delay TC Rising Edge

Degree 90 Enable

Clear Signature

View Signature

Latency Times 2

Figure 5. Register Bit Definitions

Data Sheet

Page 12

RHtMMU24

DSP Memory Manager

DSP

Architectures

DINC2PAIRS Register

The 20-bit (two 8-bit and one 4-bit register) register (A3-A5) is

used by the DUALINC2/P/B/Q/QNS/BQ/BQNS address

patterns.

When used by the DUALINC2/P/B/Q/QNS/BQ/BQNS address

patterns, this register defines the number of times to cycle the

addressing of each pair of sub-increment (ADRx and INDEXx)

address patterns.

DISCARD / DINC1PAIRS Register

The 20-bit (two 8-bit and one 4-bit register) register (DC-DE) is

u s e d b y t h e D I S C A R D / P / E P / L P a n d

DUALINC1/P/B/Q/QNS/BQ/BQNS address patterns.

When used by the DISCARD/P/EP/LP address patterns, this

register indicates the number of addresses to be discarded

(00000 H to FFFFF H). (If the P/EP/LP versions are used, PO

will signal this by going HIGH)

When used by the DUALINC1/P/B/Q/QNS/BQ/BQNS address

pattern, this register defines the number of times to cycle the

addressing of each pair of sub-increment (ADRx and INDEXx)

address patterns.

PAUSE Register

The 20-bit (two 8-bit and one 4-bit register) PAUSE register

(A6-A8) defines the number of cycles the RHtMMU24 is to

pause immediately after an addressing sequence is com-

pleted. If used, the effective length (N, ADRLENGTH or 2N) is

changed to the sequence length + PAUSE. In contrast to the

LATENCY MEMORY, which has a unique value for each

address pattern, PAUSE has a global value for all address

patterns and only extends the end of the address pattern not

the start.

The PAUSE register affects the TC signal. If PAUSE is used, TC

becomes active one cycle before sequence length + PAUSE.

NOTE: if MODE register bit 3 is set HIGH, TC transitions at the

same time as sequence length + PAUSE

BREAKPOINT Register

The 20-bit (two 8-bit and one 4-bit register) BREAKPOINT

register (A9-AB) defines the break point for an addressing

sequence (halts after a specific number of addresses are

output). The BREAKPOINT register is used only when bit 1 in

the MODE register is set HIGH.

If used, the value in the BREAKPOINT register becomes the

new length of the current sequence (instead of N,

ADRLENGTH, or 2N). When the number of addresses gener-

ated in the sequence reaches the value in the BREAKPOINT

register, the addressing sequence ends. In turn, the TC signal

becomes active one cycle before the value in the

BREAKPOINT register is reached. The BREAKPOINT stops

the current addressing sequence provided that the sequence

has not already ended, has not entered a PAUSE state and

SYSCLKEN is low.

N Register

The 21-bit (two 8-bit and one 5-bit register) N register (AC-

AE) defines the length of the addressing sequence for most

address patterns. In contrast, some address patterns use a

sequence length of 2N, such as BRFTL and BRFTU, or use

a value in the ADRLENGTH resister instead of N, such as

MODINC and MODDEC, or use a combination of

(ADRLENGTH+INDEXLENGTH)*DINCPAIRS, such as

DUALINC1x and DUALINC2x .

Note: because internally the RHtMMU24 requires the use of

all values of N which are divisible by powers of 2 (N/2, N/4,

N/8, ...), the N register is 21 bits wide. The multiples of N are

generated internally using a shift right. N must always be a

power of 2 between 000004 H and 100000 H

ADR2START Register

The 20-bit (two 8-bit and one 4-bit register) ADR2START

r e g i s t e r ( A F - B 1 ) i s u s e d b y t h e

DUALINC2/P/B/Q/QNS/BQ/BQNS address patterns. The

ADR2START register defines the starting address for the

first of two increment sequences. See Figure 6.

ADR2LENGTH Register

The 20-bit (two 8-bit and one 4-bit register) register (B2-B4)

is used by the DUALINC2/P/B/Q/QNS/BQ/BQNS address

patterns:

When used by the DUALINC2/P/B/Q/QNS/BQ/BQNS

address patterns, the ADR2LENGTH register defines the

number of addresses to output for the first of two increment

sequences.

ADR2INC Register

The 20-bit (two 8-bit and one 4-bit register) register (B5-B7)

is used by the DUALINC2/P/B/Q/QNS/BQ/BQNS address

patterns.

When used by the DUALINC2/P/B/Q/QNS/BQ/BQNS

address patterns, the ADR2INC register defines the amount

to increment each subsequent address by for the first of two

increment sequences.

Data Sheet

Page 13

RHtMMU24

DSP Memory Manager

DSP

Architectures

INDEX2LENGTH Register

The 20-bit (two 8-bit and one 4-bit register) register (B8-BA) is

used by the DUALINC2/P/B/Q/QNS/BQ/BQNS address

patterns.

When used by the DUALINC2/P/B/Q/QNS/BQ/BQNS address

patterns, the INDEX2LENGTH register defines the number of

addresses to output for the second of two increment

sequences.

INDEX2START Register

The 20-bit (two 8-bit and one 4-bit) register (BB-BD) is used by

the DUALINC2/P/B/Q/QNS/BQ/BQNS address patterns to

define the starting address for the second of two increment

sequences.

ZEROPAD / INDEX2INC Register

The 20-bit (two 8-bit and one 4-bit register) register (BE-C0) is

used by the PADLOW/P/EP/LP, PADHIGH/P/EP/LP, and

DUALINC2/P/B/Q/QNS/BQ/BQNS address patterns.

When used by the PADLOW/P/EP/LP address patterns, the

ZEROPAD register indicates the number of INDEX addresses

that are to be generated before the actual sequence starts.

When used by the PADHIGH/P/EP/LP address patterns, the

ZEROPAD register indicates when the INDEX address is to be

generated to replace the current sequence.

Note: The INDEX address starts at INDEXSTART and incre-

ments by INDEXINC. Also, when ZEROPAD = 0 or ZEROPAD

= ADRLENGTH, instead of having a 0 length/non-existent

index/address pattern, the routine will interpret the 0 length as

equal to 1 million.

When used by the DUALINC2/P/B/Q/QNS/BQ/BQNS address

patterns, the INDEX2INC register defines the amount to

increment each subsequent address by for the second of two

increment sequences.

ADRSTART Register

The 20-bit (two 8-bit and one 4-bit register) ADRSTART register

(C1-C3) is used by PADLOW/P/EP/LP, PADHIGH/P/EP/LP,

INC, and DUALINC1/P/B/Q/QNS/BQ/BQNS address patterns

to define the starting address in the sequence. (or the starting

address of the first of two address sequences for the

DUALINC1/P/B/Q/QNS/BQ/BQNS address patterns.)

ADRLENGTH Register

The 20-bit (two 8-bit and one 4-bit register) ADRLENGTH

r e g i s t e r ( C 4 - C 6 ) i s u s e d b y PA D L O W / P / E P / L P,

PA D H I G H / P / E P / L P, I N C , a n d D U A L I N C 1 / P / B / Q /

QNS/BQ/BQNS address patterns to indicate the number of

points the sequence contains. Unlike the N register,

ADRLENGTH does not have to be a power of 2.

(ADRLENGTH defines the starting address of the first of two

a d d r e s s s e q u e n c e s f o r t h e

DUALINC1/P/B/Q/QNS/BQ/BQNS address patterns.

Note: if a length of 1 million (1 mega word) is required, the

ADRLENGTH register must be set to zero.

ADRINC (Address Increment) Register

The 20-bit (two 8-bit and one 4-bit register) ADRINC register

(C7-C9) is used by PADLOW/P/EP/LP, PADHIGH/P/EP/LP,

INC, and DUALINC1/P/B/Q/QNS/BQ/BQNS address

patterns to indicate the amount by which each subsequent

address is to be incremented. (For the fist of two address

sequences for the DUALINC1/P/B/Q/QNS/BQ/BQNS

address patterns.

INDEXLENGTH Register

The 20-bit (two 8-bit and one 4-bit register) register (CA-CC)

is used by the DUALINC1/P/B/Q/QNS/BQ/BQNS address

patterns.

When used by the DUALINC1/P/B/Q/QNS/BQ/BQNS

address patterns, the INDEXLENGTH register defines the

number of addresses to output for the second of two incre-

ment sequences.

INDEXSTART Register

The 20-bit (two 8-bit and one 4-bit register) INDEXSTART

register (CD-CF) is used by the PADLOW/P/EP/LP,

PADHIGH/P/EP/LP, DISCARD/P/EP/LP, BFCTU/P/EP/LP,

and DUALINC1/P/B/Q/QNS/BQ/BQNS address patterns.

While the exact application for each address pattern differs,

the INDEXSTART value (00000 H to FFFFF H) can point to

an address space outside of the working space memory for a

particular address pattern.

Note: if the address patterns that use the indexing address

are used on the input side of the execution unit, data must be

written to the INDEXSTART location prior to running the

address pattern. If INDEXSTART is used on the output side

of the execution unit, the PO signal can be used in conjunc-

tion with the indexing address to determine when the data is

to be written to the RAM.

When used the by the DUALINC1/P/B/Q/QNS/BQ/BQNS

address patterns, INDEXSTART defines the starting

address for the second of two increment sequences.

address for the second of two increment sequences.

Data Sheet

Page 14

RHtMMU24

DSP Memory Manager

DSP

Architectures

INDEXINC Register

The 20-bit (two 8-bit and one 4-bit register) INDEXINC register

(D0-D2) is used by the PADLOW/P/EP/LP, PADHIGH/P/EP/LP,

and DUALINC1/P/B/Q/QNS/BQ/BQNS address patterns. The

INDEXINC value (00000 H to FFFFF H) identifies the amount

by which the INDEXADR value is to be incremented each time

an indexing address is generated.

When used by the DUALINC1/P/B/Q/QNS/BQ/BQNS address

patterns, the INDEXINC register defines the amount to

increment each subsequent address by for the second of two

increment sequences.

HALT Register

The 1-bit HALT register (D4) halts the current addressing

immediately when set HIGH. If halted, the inherent seven

SYSCLK cycle latency will occur after the next START signal

and before the first address is generated.

DIGITREV Register

The 20-bit (two 8-bit and one 4-bit register) DIGITREV register

(D5-D7) is used to calculate the digit reverse sequence for the

first column of an FFT

For DSP24 based FFT's, the DIGITREV value is 0

For non DSP24 implementations it is determined based on the

product of the radix combination. For example, an 8-point FFT

could contain three different digit reverse sequences depend-

ing on the radix combination being used as follows:

Radix-2 x Radix-2 x Radix x 2

Radix-2 x Radix-4

Radix-4 x Radix-2

Note: DIGITREV is the only register that requires the user to

provide information concerning the entire algorithm being

performed, rather than a specified pass.

MEMSIZE Register

The 21-bit (two 8-bit and one 5-bit register) MEMSIZE register

(D8-DA) is used by the following address patterns:

TF2Cn (0-19) TF4Cn (0-18), TF8Cn (0-17), TF16Cn (0-16),

TF32Cn (0-15), TF2n (0-19) TF4n (0-9), TF16n (0-4), MXT24n

(0-8), MXT216n (0-3), MXT416n (0-3), MXT2416n (0-3),

BFCTT, DUALINC1Q, DUALINC1QNS, DUALINC1BQ,

D U A L I N C 1 B Q N S , D U A L I N C 2 Q , D U A L I N C 2 Q N S ,

DUALINC2BQ, and DUALINC2BQNS.

For these address patterns, MEMSIZE defines the physical

memory size that contains 360 degrees of coefficient data for

address patterns on the coefficient side of the execution unit.

MEMSIZE permits a transform to be completed using a

coefficient array of any size when MEMSIZE is greater or equal

to N. Both MEMSIZE and N are a power of 2.

When used in conjunction with MODE bit 4 (DEG90), the

coeficients can be cut by three quarters. When MODE bit-4 is

set active HIGH, the addresses that are generated will come

from the 0 to MEMSIZE/4-1 address range.

CHIPID Register

This 8-bit, read only register (DB) contains chip revision

identification:

Bit[3:0]Last digit for the year

Bit[7:4]Number for the month

For example,

CHIPID = 67H would indicate that the chip version was

updated during June, 1997.

INCADRSTART Register

The 20-bit (two 8-bit and one 4-bit register) INCADRSTART

register (DF-E1) is used by the DUALINC1/P/B/Q/

QNS/BQ/BQNS address patterns to increment the current

ADRSTART value for the first of the two increment

sequences.

The current ADRSTART value is updated after each pair of

(ADR and INDEX) address increment patterns executes.

INCINDEXSTART Register

The 20-bit (two 8-bit and one 4-bit register)

INCINDEXSTART register (E2-E4) is used by the

DUALINC1/P/B/Q/QNS/BQ/BQNS address patterns to

increment the current INDEXSTART value for the second of

the two increment sequences.

The current INDEXSTART value is updated after each pair

of (ADR and INDEX) address increment patterns executes.

INCADR2START Register

The 20-bit (two 8-bit and one 4-bit register) INCADR2START

register (E5-E7) is used by the DUALINC2/P/B/Q/QNS/

BQ/BQNS address patterns to increment the current

ADR2START value for the first of the two increment

sequences.

The current ADR2START value is updated after each pair of

(ADR and INDEX) address increment patterns executes.

INCINDEX2START Register

The 20-bit (two 8-bit and one 4-bit register)

INCINDEX2START register (E8-EA) is used by the

DUALINC2/P/B/Q/QNS/BQ/BQNS address patterns to

increment the current INDEX2START value for the second

of the two increment sequences.

The current INDEX2START value is updated after each pair

of (ADR and INDEX) address increment patterns executes.

MASTEROFFSET Register

The 20-bit (two 8-bit and one 4-bit register)

MASTEROFFSET register (EB-ED) is used to add an

arbitrary 20-bit value to each and every address that is

generated by the current address pattern and associated

configuration registers. See Figure 7.

Data Sheet

Page 15

RHtMMU24

DSP Memory Manager

DSP

Architectures

MASTEROFFINC Register

The 20-bit (two 8-bit and one 4-bit register) MASTEROFFINC

register (EE-F0) is used increment the current value of the

MASTEROFFSET register after each successive address

pattern is finished, for each count of the MASTERREPEAT

register greater than zero.

MASTERREPEAT Register

The 20-bit (two 8-bit and one 4-bit register) MASTERREPEAT

register (F1-F3) is divided into two fields.

The first field (bits 18-0), is used to define how many additional

times the RHtMMU24 will execute another address sequence.

(A value of 2 indicates that the RHtMMU24 will run 3 complete

sequences.)

The second field/MSB, is used to defines what successive

address sequences will be.

When set LOW, successive address patterns will be repeats of

the current pattern pointed to by the Program Counter and its'

associated configuration registers.

When set HIGH, successive address patterns will come from

successive locations in Program Memory, and their associated

configuration registers. Thus concatenating multiple

sequences together to form ever more complex patterns.

The functionality of the MASTERREPEAT register, is to

internally pre-START the RHtMMU24, (the same as double

strobing the START signal externally), with the additional

feature that the TC signal covers the whole concatenated pass.

That is it does not strobe between sequences like an externally

strobed START pulse would cause.

Note: If the user would like a version of TC that DOES pulse

between sequences, the TCP signal's REPEAT bit in the

SKEW register may be set to accomplish this.

SKEW Register

The 22-bit (two 8-bit and one 6-bit register) SKEW register (F4-

F6) is used to move the timing of various signals forward and

backward an integer number of cycles relative to the address

output. The bits for the SKEW register shown in Figure 4 are

defined as follows:

Bits 2-0, Determines the relative skew of the MEMOE signal.

The MEMOE signal is delayed by an additional number of

SYSCLK cycles determined by the unsigned value of these

bits. (except for the value of 7 which corresponds to a negative

delay of one cycle) See Figure 5.

Bits 5-3, Determines the relative skew of the MEMW signal.

The MEMW signal is delayed by an additional number of

SYSCLK cycles determined by the unsigned value of these

bits. (except for the value of 7 which corresponds to a negative

delay of one cycle)

Bits 8-6, Determines the relative skew of the CCOMR,

CCOMI, and SWAP signals. The all of these signals are

delayed by an additional number of SYSCLK cycles deter-

mined by the unsigned value of these bits. (except for the

value of 7 which corresponds to ZERO delay cycles. Same

as a value of 0.)

Bits 11-9, Determines the relative skew of the TC signal. The

TC signal is delayed by an additional number of SYSCLK

cycles determined by the unsigned value of these bits.

(except for the value of 7 which corresponds to a negative

delay of one cycle)

Bits 14-12, Determines the relative skew of the TCP signal.

The TCP signal is delayed by an additional number of

SYSCLK cycles determined by the unsigned value of these

bits. (except for the value of 7 which corresponds to a

negative delay of one cycle)

Bit 15, Determines whether the TCP signals rising edge will

be delayed by an additional SYSCLK cycle. This bit the

equivalent of MODE bit-3 for the TC signal.

Bit 16, Sets the polarity of the TCP signal. When set LOW,

TCP is active LOW, when set HIGH, TCP is active HIGH.

Note: TCP will always power up inactive HIGH.

Bit 17, Determines whether or not the TCP signal will strobe

inactive between successive address sequences initiated

by the MASTERREPEAT register.

When set LOW, TCP will act like TC. It will go active with the

first address out, and inactive one cycle before the last

address of the last repeated sequence. (Plus or minus

SKEW and DELAY settings.)

When set HIGH, TCP will pulse inactive one cycle before the

last address of each repeated address sequence (Plus or

minus SKEW and DELAY settings.)

Bits 20-18, Determines the relative skew of the PO signal.

The PO signal is delayed by an additional number of

SYSCLK cycles determined by the unsigned value of these

bits. (except for the value of 7 which corresponds to a

negative delay of one cycle).

Bit 21, Sets the polarity of the PO signal for the DUALINC1P

and DUALINC2P address patterns.

When set LOW, the PO signal will go active during the first

address sequence of each set of address sequence pairs

that are executed (i.e. each ADRSTART/ADRLENGTH/

ADRINC sequence.)

When set HIGH, the PO signal will go active during the

second address sequence of each set of address sequence

pairs that are executed (i.e. each INDEXSTART/

INDEXLENGTH/INDEXINC sequence.)

Data Sheet

Page 16

RHtMMU24

DSP Memory Manager

DSP

Architectures

Data Sheet

Page 17

RHtMMU24

DSP Memory Manager

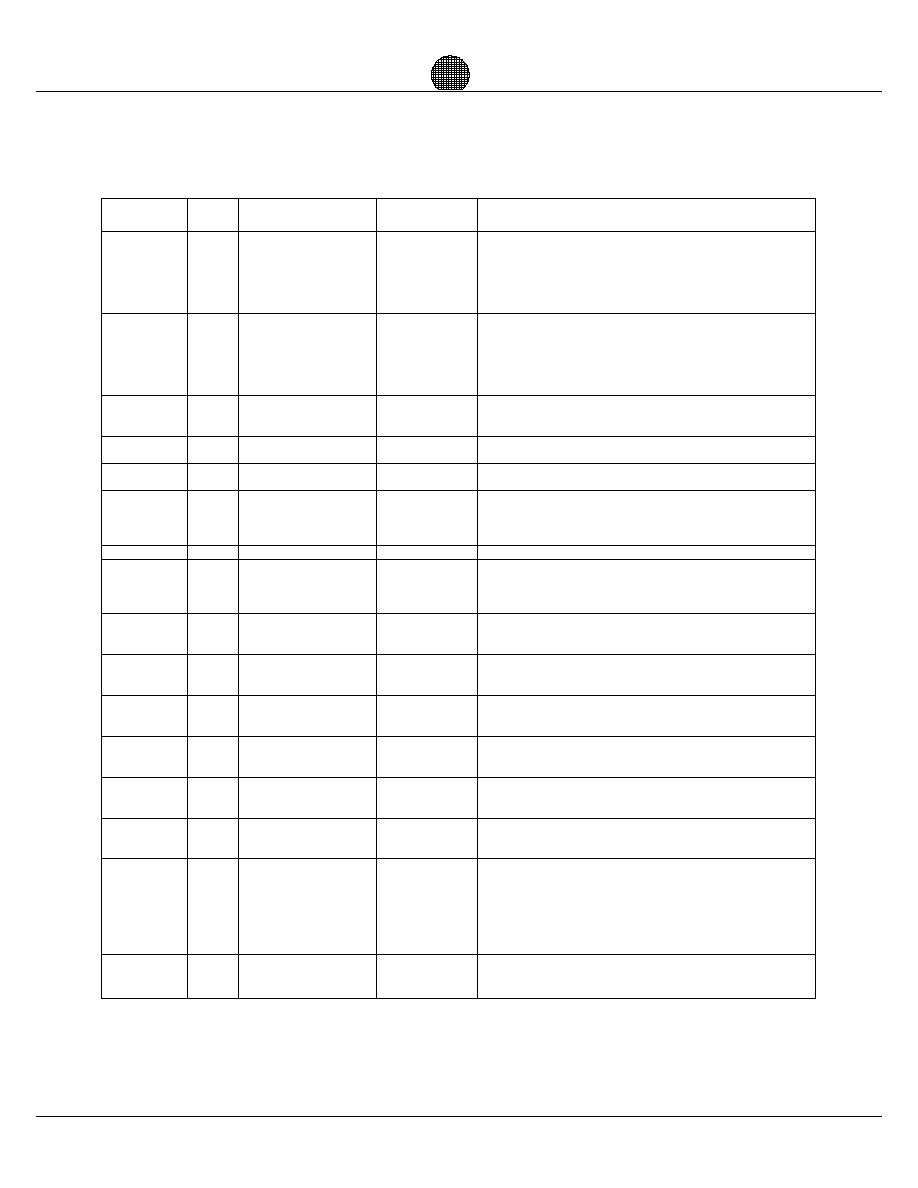

32, 9 bit register locations reserved to store additional

latency values (bits [4:0]). Skew range for the ACTIVE

signal (bit [7:5]) and an enable for ACTIVE (bit 8)

For internal memory mode, loads the Program Counter

with the first index to be executed from

Program/Latency/ Feature memory (disabled in external

memory mode).

Defines the various modes of operation

DINC2PAIRS: Defines the number of ADR-INDEX pairs

of sequences for the DUALINC2 functions.

Defines the number of cycles to extend the last address

and control signals output, before starting next function.

Active when MODE register bit1 is set HIGH. Causes

the RHtMMU24 to stop generating addresses after the

number of addresses generated in the sequence is equal

to the value in the BREAKPOINT register.

For most address patterns, N defines the length of the

address sequence, except those that use 2N,

ADRLENGTH, or INDEXLENGTH.

Defines the starting address location for the first half

sequence of the DUALINC2 pattern.

DUALINC2: Uses the value as the address length of the

1st half sequence.

DUALINC2: Uses the value as the address increment for

the 1st half sequence.

DUALINC2: Uses the value as the address length for the

2nd half sequence.

DUALINC2: Defines the starting address for the 2nd half

sequence.

PADLOW/P/EP/LP, PADHIGH/P/EP/LP: Defines the

number of INDEXing addresses to be generated before

or after the ADR addressing starts.

DUALINC2: Defines the address increment for the 2nd

half sequence.

PADLOW/P/EP/LP, PADHIGH/P/EP/LP, MODINC,

MODDEC, and INC: Defines the starting address in the

current sequence.

DUALINC1: Defines the starting address of the 1st half

sequence.

32, 8 bit register locations for storing address patterns.

The Program Counter determines which is used.

32, 8 bit register locations for storing latency values (bits

[6:0]). Bit 7 indicates reading or writing the SRAM

The Program Counter determines which is used.

VALID RANGE

(HEX)*

00000-FFFFF

00000-FFFFF

00000-FFFFF

00000-FFFFF

00000-FFFFF

00000-FFFFF

00000-FFFFF

000000-100000

00000-FFFFF

00000-FFFFF

00000-FFFFF

00-7F

00-1F

000-1FF

00-FF

00-FF

INDEX2START

ADRSTART

ZEROPAD/

INDEX2INC

INDEX2LENGTH

ADR2INC

ADR2LENGTH

ADR2START

N

BREAKPOINT

PAUSE

DINC2PAIRS

MODE

PCSTART

EXTENDED

FEATURE

MEMORY

LATENCY

MEMORY

PROGRAM

MEMORY

20

20

20

20

20

20

20

21

20

20

20

6

5

9

8

8

C1-C3

BE-CO

BB-BD

B8-BA

B5-B7

B2-B4

AF-B1

AC-AE

A9-AB

A6-A8

A3-A5

A2

A0

40-9F

20-3F

0-1F

NAME

BITS

USED

ADDRESS

DESCRIPTION

PADLOW/P/EP/LP, PADHIGH/P/EP/LP, MODINC, and

INC: Indicates the amount each subsequent address is

to be incremented by, when generated.

DUALINC1: Defines the address increment of the 1st

half sequence

PADLOW/P/EP/LP, PADHIGH/P/EP/LP, MODINC,

MODDEC, and INC: Indicates the number of points in

the current sequence.

DUALINC1: Defines the number of addresses of the 1st

half sequence

00000-FFFFF

00004-100000

ADRINC

ADRLENGTH

20

20

C7-C9

C4-C6

Figure 6. Internal Memory Description

DSP

Architectures

DUALINC1: Defines the number of addresses of the 2nd

half sequence

PADLOW/P/EP/LP, PADHIGH/P/EP/LP,

DISCARD/P/EP/LP, BFCTU/P/EP/LP: Points to an

address space outside of the working space memory for

a particular address pattern.

DUALINC1: Defines the stating address of the 2nd half

sequence

PADLOW/P/EP/LP, PADHIGH/P/EP/LP,

DISCARD/P/EP/LP: Identifies the amount to increment

the INDEXSTART pointer value by each time an

indexing address is generated.

DUALINC1: Defines the address increment of the 2nd

half sequence.

For internal memory mode, points to the last address

pattern to be executed in the program memory before

loading PCSTART. (disabled in external memory mode).

Halts the current addressing sequence after

BREAKPOINT address have been generated.

Defines the digit reverse sequence for the first column of

an FFT based on the combination of the radices used.

TFx, DECIM, ADECIM, BFCTT: Defines the physical

memory size that contains 360 degrees of coefficients in

a COS/SIN table (Whether or not they are all actually

stored.)

Chip identification/revision. (Read only)

DISCARD/P/EP/LP: Defines the number of addresses to

be discarded.

DINC1PAIRS: Defines the number of ADR-INDEX pairs

of sequences for the DUALINC1 functions

Defines the amount to increment the first starting

address by (ADRSTART), after executing both

sequences of a ADR/INDEX DUALINC1 pair.

Defines the amount to increment the second starting

address by (INDEXSTART), after executing both

sequences of a ADR/INDEX DUALINC1 pair.

Defines the amount to increment the first starting

address by (ADR2START), after executing both

sequences of a ADR/INDEX DUALINC2 pair.

Defines the amount to increment the second starting

address by (INDEX2START), after executing both

sequences of a ADR/INDEX DUALINC2 pair.

Defines a value (offset) to add to all addresses

generated by all address patterns defined by the above

registers.

Defines a value to increment the MASTEROFFSET

value by, after each iteration defined by the

MASTERREPEAT.

Bits [18:0] define the number additional times to execute

an address pattern. (Performs an internal double strobe

of the START signal.)

Bit 19 when set HIGH will cause the Program Counter to

increment on successive (repeated) address patterns,

which will essentially concatenate multiple address

patterns.

Defines positive and negative cycle timing of various

output control signals relative to ADDR[19:0], measured

in multiples of SYSCLK.

00000-FFFFF

00000-FFFFF

00000-FFFFF

00000-FFFFF

00000-FFFFF

00000-FFFFF

00000-FFFFF

00000-FFFFF

67

000000-100000

0-1

00-1F

00000-FFFFF

00000-FFFFF

00000-FFFFF

00000-FFFFF

000000-7FFFFF

VALID RANGE

(HEX)*

SKEW

MASTERREPEAT

MASTEROFFINC

MASTEROFFSET

INCINDEX2START

INCADR2START

INCINDEXSTART

INCADRSTART

DISCARD/

DINC1PAIRS

CHIPID

MEMSIZE

DIGITREV

HALT

PCEND

INDEXINC

INDEXSTART

INDEXLENGTH

NAME

19

19

19

19

19

19

19

22

19

8

21

1

5

20

20

20

20

BITS

USED

F4-F6

F1-F3

EE-F0

EB-ED

E8-EA

E5-E7

E2-E4

DF-E1

DC-DE

DB

D8-DA

D5-D7

D4

D3

D0-D2

CD-CF

CA-CC

ADDRESS

DESCRIPTION

Figure 6. Internal Memory Description (cont)

Data Sheet

Page 18

RHtMMU24

DSP Memory Manager

DSP

Architectures

HOST - INTERFACE

The host interface enables the RHtMMU24 to be programmed

in internal or external memory mode via the 8-bit data bus

DB[7:0] as was shown in Figure 2. In particular, the host decode

enables the data to be written to a specified address location

depending on the A1, A0 signals and whether it is in internal or

external mode as shown in Table 4.

Internal Memory Mode

For internal memory mode, the A1 and A0 signals determine

whether the DB[7:0] bus is latched into an address register (A1

is LOW and A0 is HIGH) or one of many data registers (A1 is

LOW and A0 is LOW). In internal mode, the address register is

decoded into an array of enable signals that determine which

specific data register is accessed for subsequent data reads

and data writes. Thus, the host decode loads the RHtMMU24

registers through a two step scheme: registering of the desired

address by writing to DB[7:0] with A1 LOW and A0 HIGH, and

then reading or writing data to the register just selected by

reading/writing DB[7:0] with A1 LOW and A0 LOW. The value of

the DIR signal determines whether the DB[7:0] bus is in input

mode for writing (DIR set LOW) or if the DB[7:0] bus is in output

mode for reading registers (DIR set HIGH).

External Memory Mode

In external memory mode, A1 and A0 permit the DB[7:0] data

bus to flow to the following predefined address locations:

!

L o c a t i o n 3 1 o f P r o g r a m M e m o r y ( 1 F ) -

A1 is LOW and A0 is LOW

!

L o c a t i o n 3 1 o f L a t e n c y M e m o r y ( 3 F ) -

A1 is LOW and A0 is HIGH

!

L o c a t i o n A 2 , t h e M O D E r e g i s t e r ( A 2 ) -

A1 is HIGH and A0 is LOW

In this mode, the address register is bypassed and the DB[7:0]

data bus transfers data to the predefined address (1F, 3F, or

A2) as assigned by the

A1 and A0 signals. In addition, the

MODE register address location (A2) can be accessed

externally to toggle back and forth between the internal and

external memory modes. See Table 4.

Note: because the address register is bypassed, program-

ming in external memory mode requires only half the program

length that would be utilized in internal memory mode, once

the configuration registers have been programmed.

ADDRESS CALCULATION

The address calculation logic of the RHtMMU24, produces

address patterns using the following logic:

!

Opcode Decode

!

Sequence Generation

!

Quadrant Lookup

!

Master Offset and Repeat

!

Control Signal Generation

The address calculation logic decodes each address pattern

and selects a set of seeds values which, in turn, control the

actual address sequence generation. The generated

sequence of addresses then pass through the quadrant logic

which can reduce the required coefficient table by a factor of

four when enabled.

After the Quadrant logic, each address passes though the

Master Offset logic, where the current Master Offset value is

added on to generate the final output address.

The progress of address generation, and the SKEW of

individual control signals is performed in parallel with the

address generation in the Control Signal Generation logic.

To help solve testability issues, the address calculation logic

contains a signature analyzer at the output of the final

address, that includes a primitive polynomial of degree 31.

Data Sheet

Page 19

RHtMMU24

DSP Memory Manager

H

H

L

L

A1

H

L

H

L

A0

Reserved

Reserved

Address

Data

Programming

Internal Memory

MODE(0)=L

Reserved

Mode register (A2)

(3F)

Program Memory

Location 31 of

(3F)

Program Memory

Location 31 of

Programming

External Memory

MODE(0)=H

Table 4. Host Decoder Truth Table

DSP

Architectures

Note: the RHtMMU24 contains two instructions (opcodes) that

are reserved for clearing and viewing the signature analyzer via

the 20-bit address output. CLEARSIG is the instruction for

clearing the signature to zero. (The signature is always cleared

after a reset.) VIEWSIG is the instruction that displays the

signature contents since the last CLEARSIG instruction.

In addition to the CLEARSIG and VIEWSIG instructions, the

RHtMMU24 allows the user to control these operations via two

bits in the MODE register. MODE bit-7 clears the signature

register like the CLEARSIG instruction. MODE bit-6 functions

like the VIEWSIG instruction by enabling the output of the

signature register on ADDR[19:0], when set HIGH, and re-

enabling the current address output on ADDR[19:0] when set

LOW.

Opcode Decode

The current opcode consists of the current address pattern,

Latency value, Read/Write value, and ACTIVE control signals

currently being pointed to by the internal Program Counter.

These values are decoded in a straightforward manner to

select a particular set of seeds for each address pattern.

These seeds are selected from the Configuration Registers

and various constants. They are selected according to the

address pattern and determine everything about the desired

address pattern to be generated. (i.e. They set algorithms, loop

sizes, initial values, increment amounts, etc.)

Sequence Generation

The complexity of the Sequence Generation logic is set up to

perform the radix-32 algorithm. All other address patterns are

generated using subsets.

The Sequence Generation logic is composed of a series of

adders that perform arithmetic operations and manipulate

addresses for a specified algorithm.

Quadrant Lookup

The Quadrant Lookup logic takes the address out of the

Sequence Generation block and compares it to the range of the

lookup table defined by the MEMSIZE register. When enabled,

the Quadrant Lookup logic then outputs a set of CCOMR,

CCOMI, and SWAP signals for each address, based on which

quadrant of the table the address is in, and then forces the

address to point into the first quadrant to save memory.

Master Offset and Repeat

The Master Offset logic is composed of two main blocks, the

offset/increment block, and the repeat block. Together, they

work to add an additional dimension to the address genera-

tion, by allowing the user to add arbitrary offsets to all

generated address patterns, and to seamlessly concatenate

successive patterns together to build arbitrarily complex

new unique patterns. See Figure 7.

The offset block is composed of a address offset adder and

an adder to increment the offset. On the very first address of

the very first sequence (if there are any repeats), the offset

register is loaded with the MASTEROFFSET register as the

initial value to offset the incoming addresses by. After each

sequence of done, if the user has chosen to

repeat/concatenate successive sequences, a new offset is

set from the value of the current offset plus the

MASTEROFFINC register value.

The repeat block controls the selection of the offsets, and the

registering of new offsets on a pass by pass basis.

Additionally, the repeat logic signals the RHtMMU24 to start

a new address sequence seamlessly from either the current

Program Counter location, or the next Program Counter

location, by incrementing it.

Control Signal Generation

The Control Signal Generation logic generates all the flags

and memory control signals output from the RHtMMU24 with

cycle timing relative to the ADR[19:0] signals, and modified

by the MODE, SKEW, and EXTENDED FEATURE Memory

registers.

CLOCK CONTROL

The clock control logic detects the rising edge of the START

signal, which initiates the execution of the current address

pattern pointed to by the Program Counter. The Program

Counter is incremented each time a rising edge of the

START signal is detected. (or each time a concatenated

repeat is performed. see above)

PROGRAM COUNTER

The Program Counter is a 5-bit counter whose starting

address is given by the PCSTART register and ending

address is given by the PCEND register. The Program

Counter is incremented by one each time the rising edge of

the START signal is detected. Upon reaching a value equal

to PCEND, the Program Counter is again re-loaded with the

value in the PCSTART register. The Program counter will

automatically be loaded from the PCSTART register after

reset or when a change in the PCSTART register is detected.

Note: For external memory mode, PCSTART and PCEND

are bypassed. The data is transferred directly to the prede-

fined addresses (1F, 3F, or A2) depending on the value of the

A1, A0 signals.

The Program Counter is also incremented each time a

concatenated repeat is performed.

Data Sheet

Page 20

RHtMMU24

DSP Memory Manager

D[19:0] = ADDR[19:0]

D[20] = PO

D[21] = PO_EN (internal)

D[22] = CCOMR

D[23] = CCOMR_EN (internal) D[24] = CCOMI

D[25] = CCOMI_EN (internal)

D[26] = SWAP

D[27] = SWAP_EN (internal)

D[28] = NOT TC

D[29] = NOT ACTIVE

D[30] = MEMW and MEMOE

DSP

Architectures

The signals that are connected to the signature analyzer are

as follows:

USING THE RHtMMU24

Initializing the RHtMMU24

The RHtMMU24 is initialized when the RESET signal is set

active HIGH. When this occurs, all internal counters and

registers are reset to zero. The RESET signal is asynchronous

and must be held HIGH for the minimum pulse duration for all

registers to be reset correctly

After the RHtMMU24 is reset, all internal execution and

configuration memory registers must be loaded with appropri-

ate values if different than their initial conditions. Only the

execution memory that is used needs to be programmed, and

only the configuration registers associated with each pro-

grammed address pattern need be programmed. (See Figure-

9, the Address Pattern/Register Cross Reference.)

The RHtMMU24 uses a simple "Tiered - Decode" that allows it

to be programmed like a common peripheral device off an 8-bit

address/data bus. When used with the DSP24, the DSP24's

Scheduler can program a group of RHtMMU24's by selecting

individual and/or multiple MMU's with the corresponding chip

select (CS) lines.

The Tiered - Decode means that the user must separately

program address and data values. To write internal registers

with data, the user must first write the 8-bit location/address of

the target register. Then the user can either write the data

value, or read the current registers contents.

Starting Execution

The generation of address sequences begins when the rising

edge of the START signal is detected. Before this occurs, all

relevant Program Memory, Latency Memory, Extended

Feature Memory, and Configuration registers must be loaded

with valid values. For the first START detected after a RESET,

or for START's that occur after the RHtMMU24 has finished its

current sequence, the RHtMMU24 takes 8 rising edges of the

SYSCLK (approximately 7 cycles) before the first address is

output. However, if a rising edge of the START signal is

detected during a running address sequence, and occurs more

than 6 cycles before last address, then the RHtMMU24 will

"pre-start" the next address sequence and immediately run the

next sequence after the current address pattern finishes,

without any pipeline delay.

Note: Since "Pre-Starting" the RHtMMU24, by strobing the

START signal during a pass, is equivalent to setting the

MASTERREPEAT register to a non-zero value, Pre-Starting

should not be used if the MASTERREPEAT register is being

used.

Stopping Execution

The RHtMMU24 is a deterministic machine. Given any set of

initial conditions it will eventually finish generating address

outputs and stay at the last generated output. The

RHtMMU24 then enters a waiting state. After waiting for the

number of cycles in the PAUSE register, the RHtMMU24 will

be ready to start new address patterns.

In order to pre-maturely stop the current sequence of

addresses or pause cycles, two methods may be used. The

first is to set the HALT register bit-0 HIGH to immediately