Other brands and names are the property of their respective owners

Information in this document is provided in connection with Intel products Intel assumes no liability whatsoever including infringement of any patent or

copyright for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products Intel retains the right to make

changes to these specifications at any time without notice Microcomputer Products may have minor variations to this specification known as errata

November 1994

COPYRIGHT

INTEL CORPORATION 1995

Order Number 270942-005

8XC196KC 8XC196KC20

COMMERCIAL EXPRESS CHMOS

MICROCONTROLLER

87C196KC

16 Kbytes of On-Chip OTPROM

83C196KC

16 Kbytes ROM

80C196KC

ROMless

Y

16 and 20 MHz Available

Y

488 Byte Register RAM

Y

Register-to-Register Architecture

Y

28 Interrupt Sources 16 Vectors

Y

Peripheral Transaction Server

Y

1 4 ms 16 x 16 Multiply (20 MHz)

Y

2 4 ms 32 16 Divide (20 MHz)

Y

Powerdown and Idle Modes

Y

Five 8-Bit I O Ports

Y

16-Bit Watchdog Timer

Y

Extended Temperature Available

Y

Dynamically Configurable 8-Bit or

16-Bit Buswidth

Y

Full Duplex Serial Port

Y

High Speed I O Subsystem

Y

16-Bit Timer

Y

16-Bit Up Down Counter with Capture

Y

3 Pulse-Width-Modulated Outputs

Y

Four 16-Bit Software Timers

Y

8- or 10-Bit A D Converter with

Sample Hold

Y

HOLD HLDA Bus Protocol

Y

OTPROM One-Time Programmable

Version

The 80C196KC 16-bit microcontroller is a high performance member of the MCS

96 microcontroller family

The 80C196KC is an enhanced 80C196KB device with 488 bytes RAM 16 and 20 MHz operation and an

optional 16 Kbytes of ROM OTPROM Intel's CHMOS III process provides a high performance processor

along with low power consumption

The 87C196KC is an 80C196KC with 16 Kbytes on-chip OTPROM The 83C196KC is an 80C196KC with 16

Kbytes factory programmed ROM In this document the 80C196KC will refer to all products unless otherwise

stated

Four high-speed capture inputs are provided to record times when events occur Six high-speed outputs are

available for pulse or waveform generation The high-speed output can also generate four software timers or

start an A D conversion Events can be based on the timer or up down counter

With the commercial (standard) temperature option operational characteristics are guaranteed over the tem-

perature range of 0 C to a70 C With the extended (Express) temperature range option operational charac-

teristics are guaranteed over the temperature range of b40 C to a85 C Unless otherwise noted the specifi-

cations are the same for both options

See the Packaging information for extended temperature designators

8XC196KC 8XC196KC20

PROCESS INFORMATION

This device is manufactured on PX29 5 or PX29 9 a

CHMOS III process Additional process and reliabili-

ty information is available in Intel's

Components

Quality and Reliability Handbook

Order Number

210997

270942 ≠ 43

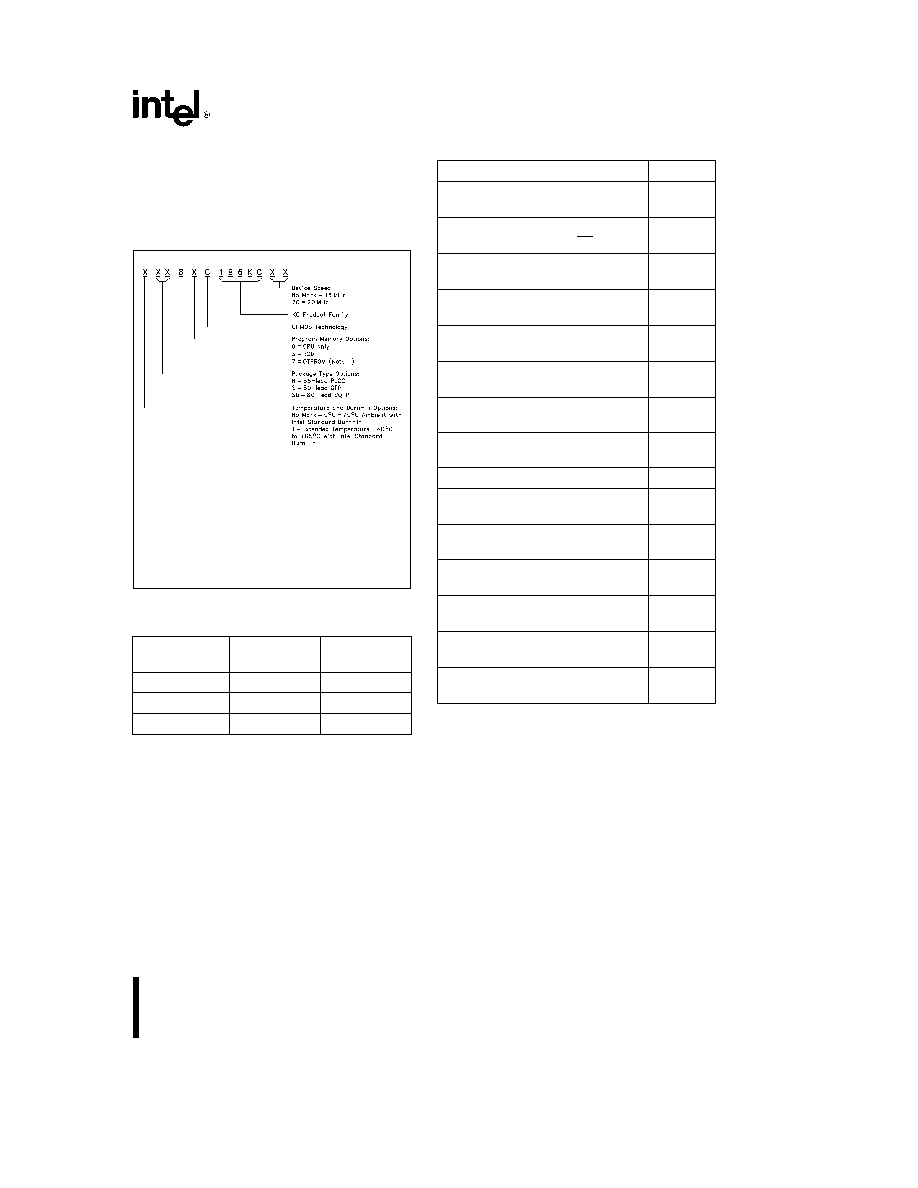

EXAMPLE

N87C196KC is 68-Lead PLCC OTPROM

16 MHz

For complete package dimensional data refer to the

Intel Packaging Handbook (Order Number 240800)

NOTE

1 EPROMs are available as One Time Programmable

(OTPROM) only

Figure 3 The 8XC196KC Family Nomenclature

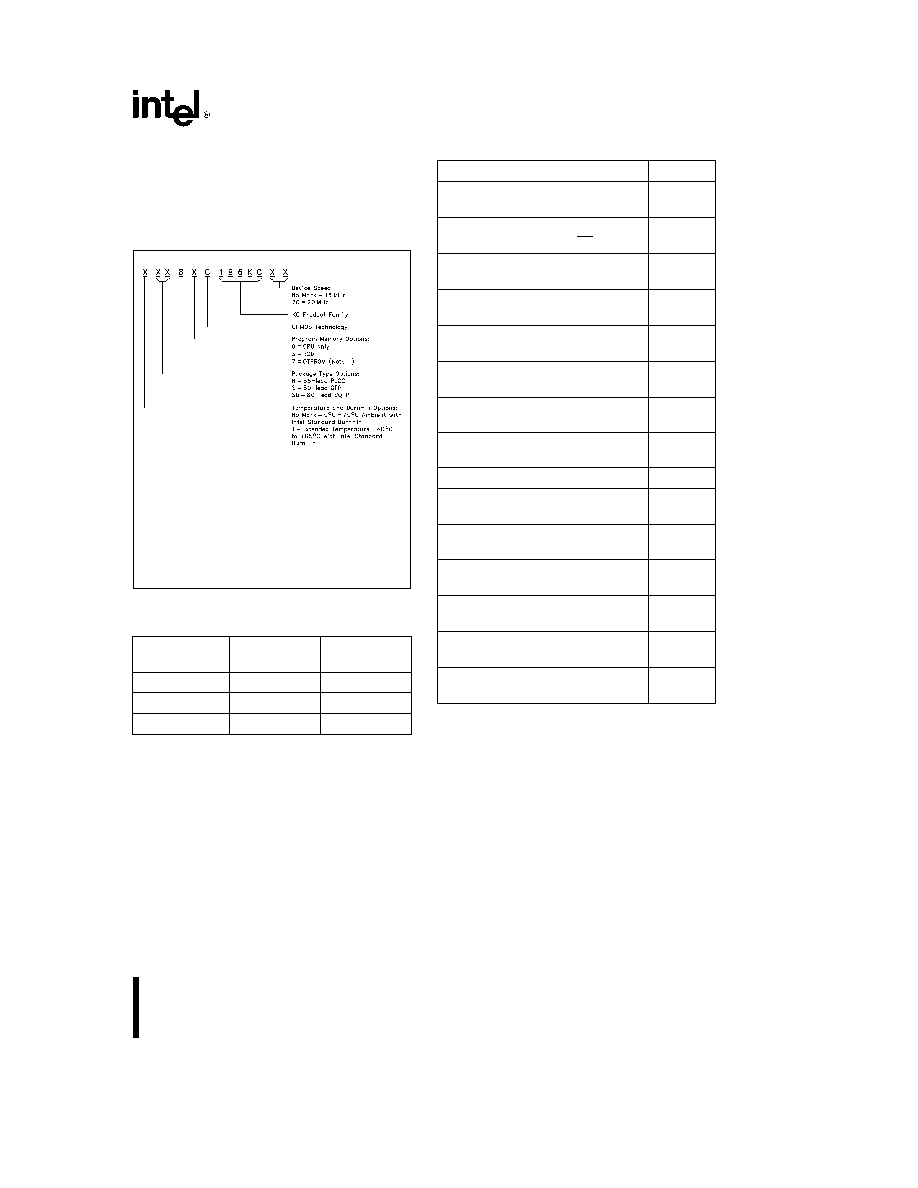

Table 1 Thermal Characteristics

Package

i

ja

i

jc

Type

PLCC

35 C W

13 C W

QFP

55 C W

16 C W

SQFP

TBD

TBD

All thermal impedance data is approximate for static air

conditions at 1W of power dissipation Values will change

depending on operation conditions and application See

the Intel

Packaging Handbook (order number 240800) for a

description of Intel's thermal impedance test methodology

Table 2 8XC196KC Memory Map

Description

Address

External Memory or I O

0FFFFH

06000H

Internal ROM OTPROM or External

5FFFH

Memory (Determined by EA)

2080H

Reserved Must contain FFH

207FH

(Note 5)

205EH

PTS Vectors

205DH

2040H

Upper Interrupt Vectors

203FH

2030H

ROM OTPROM Security Key

202FH

2020H

Reserved Must contain FFH

201FH

(Note 5)

201AH

Reserved Must Contain 20H

2019H

(Note 5)

CCB

2018H

Reserved Must contain FFH

2017H

(Note 5)

2014H

Lower Interrupt Vectors

2013H

2000H

Port 3 and Port 4

1FFFH

1FFEH

External Memory

1FFDH

0200H

488 Bytes Register RAM (Note 1)

01FFH

0018H

CPU SFR's (Notes 1 3 4)

0017H

0000H

NOTES

1 Code executed in locations 0000H to 01FFH will be

forced external

2 Reserved memory locations must contain 0FFH unless

noted

3 Reserved SFR bit locations must contain 0

4 Refer to 8XC196KC User's manual for SFR descriptions

5 WARNING Reserved memory locations must not be

written or read The contents and or function of these lo-

cations may change with future revisions of the device

Therefore a program that relies on one or more of these

locations may not function properly

3