1

Æ

March 1997

80C286

High Performance Microprocessor

with Memory Management and Protection

Features

∑ Compatible with NMOS 80286

∑ Wide Range of Clock Rates

- DC to 25MHz (80C286-25)

- DC to 20MHz (80C286-20)

- DC to 16MHz (80C286-16)

- DC to 12.5MHz (80C286-12)

- DC to 10MHz (80C286-10)

∑ Static CMOS Design for Low Power Operation

- ICCSB = 5mA Maximum

- ICCOP = 185mA Maximum (80C286-10)

220mA Maximum (80C286-12)

260mA Maximum (80C286-16)

310mA Maximum (80C286-20)

410mA Maximum (80C286-25)

∑ High Performance Processor (Up to 19 Times the 8086

Throughput)

∑ Large Address Space

∑ 16 Megabytes Physical/1 Gigabyte Virtual per Task

∑ Integrated Memory Management, Four-Level Memory

Protection and Support for Virtual Memory and Operat-

ing Systems

∑ Two 80C86 Upward Compatible Operating Modes

- 80C286 Real Address Mode

- PVAM

∑ Compatible with 80287 Numeric Data Co-Processor

∑ High Bandwidth Bus Interface (25 Megabyte/Sec)

∑ Available In

- 68 Pin PGA (Commercial, Industrial, and Military)

- 68 Pin PLCC (Commercial and Industrial)

Description

The Intersil 80C286 is a static CMOS version of the NMOS

80286 microprocessor. The 80C286 is an advanced, high-

performance microprocessor with specially optimized capa-

bilities for multiple user and multi-tasking systems. The

80C286 has built-in memory protection that supports operat-

ing system and task isolation as well as program and data

privacy within tasks. A 25MHz 80C286 provides up to nine-

teen times the throughput of a standard 5MHz 8086. The

80C286 includes memory management capabilities that map

2

30

(one gigabyte) of virtual address space per task into 2

24

bytes (16 megabytes) of physical memory.

The 80C286 is upwardly compatible with 80C86 and 80C88

software (the 80C286 instruction set is a superset of the

80C86/80C88 instruction set). Using the 80C286 real

address mode, the 80C286 is object code compatible with

existing 80C86 and 80C88 software. In protected virtual

address mode, the 80C286 is source code compatible with

80C86 and 80C88 software but may require upgrading to

use virtual address as supported by the 80C286's integrated

memory management and protection mechanism. Both

modes operate at full 80C286 performance and execute a

superset of the 80C86 and 80C88 instructions.

The 80C286 provides special operations to support the effi-

cient implementation and execution of operating systems.

For example, one instruction can end execution of one task,

save its state, switch to a new task, load its state, and start

execution of the new task. The 80C286 also supports virtual

memory systems by providing a segment-not-present excep-

tion and restartable instructions.

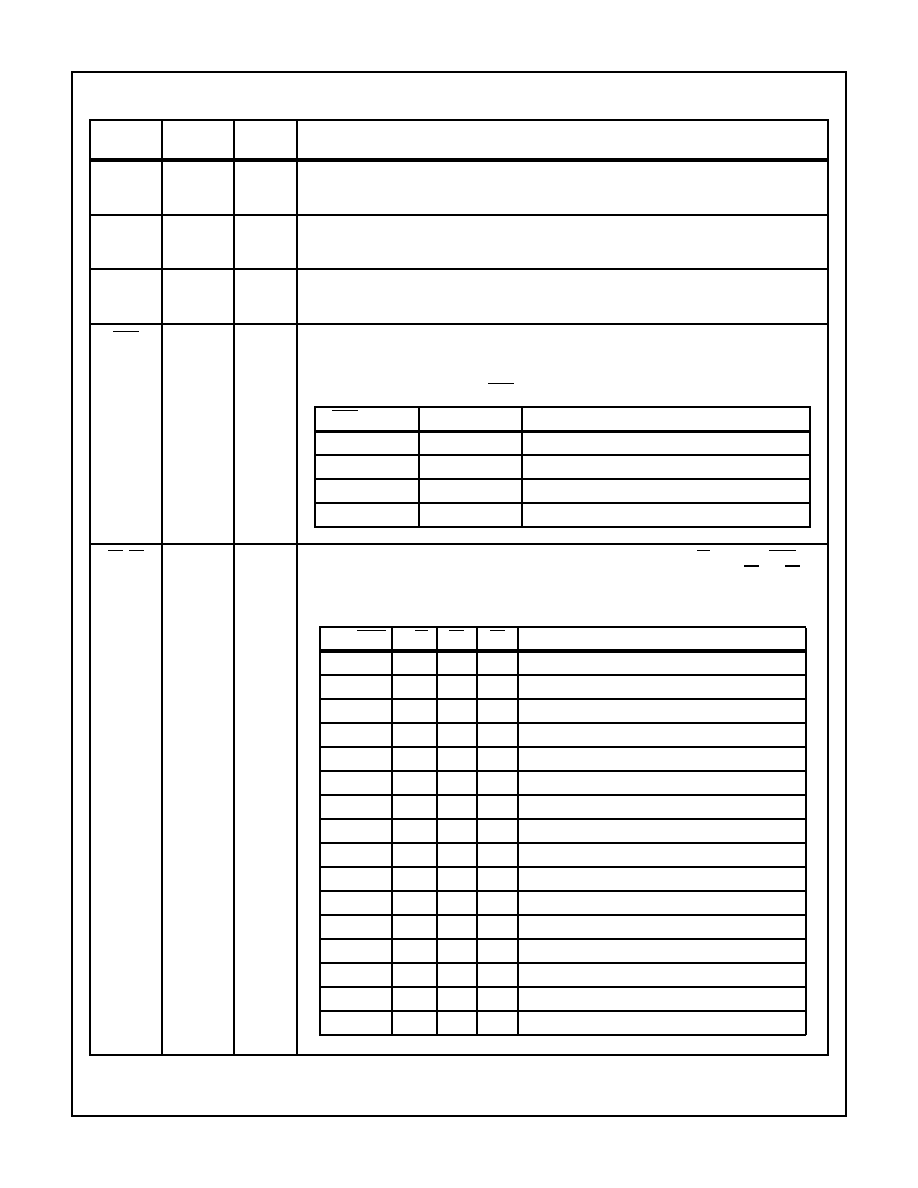

Ordering Information

PACKAGE

TEMP. RANGE

10MHz

12.5MHz

16MHz

20MHz

25MHz

PKG. NO.

PGA

0

o

C to +70

o

C

-

CG80C286-12

CG80C286-16

CG80C286-20

-

G68.B

-40

o

C to +85

o

C

IG80C286-10

IG80C286-12

-

-

-

G68.B

-55

o

C to +125

o

C 5962-

9067801MXC

5962-

9067802MXC

-

-

-

G68.B

PLCC

0

o

C to +70

o

C

-

CS80C286-12

CS80C286-16

CS80C286-20

CS80C286-25

N68.95

-40

o

C to +85

o

C

IS80C286-10

IS80C286-12

IS80C286-16

IS80C286-20

-

N68.95

FN2947.2

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143

|

Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright © Intersil Americas Inc. 2003. All Rights Reserved

All other trademarks mentioned are the property of their respective owners.

2

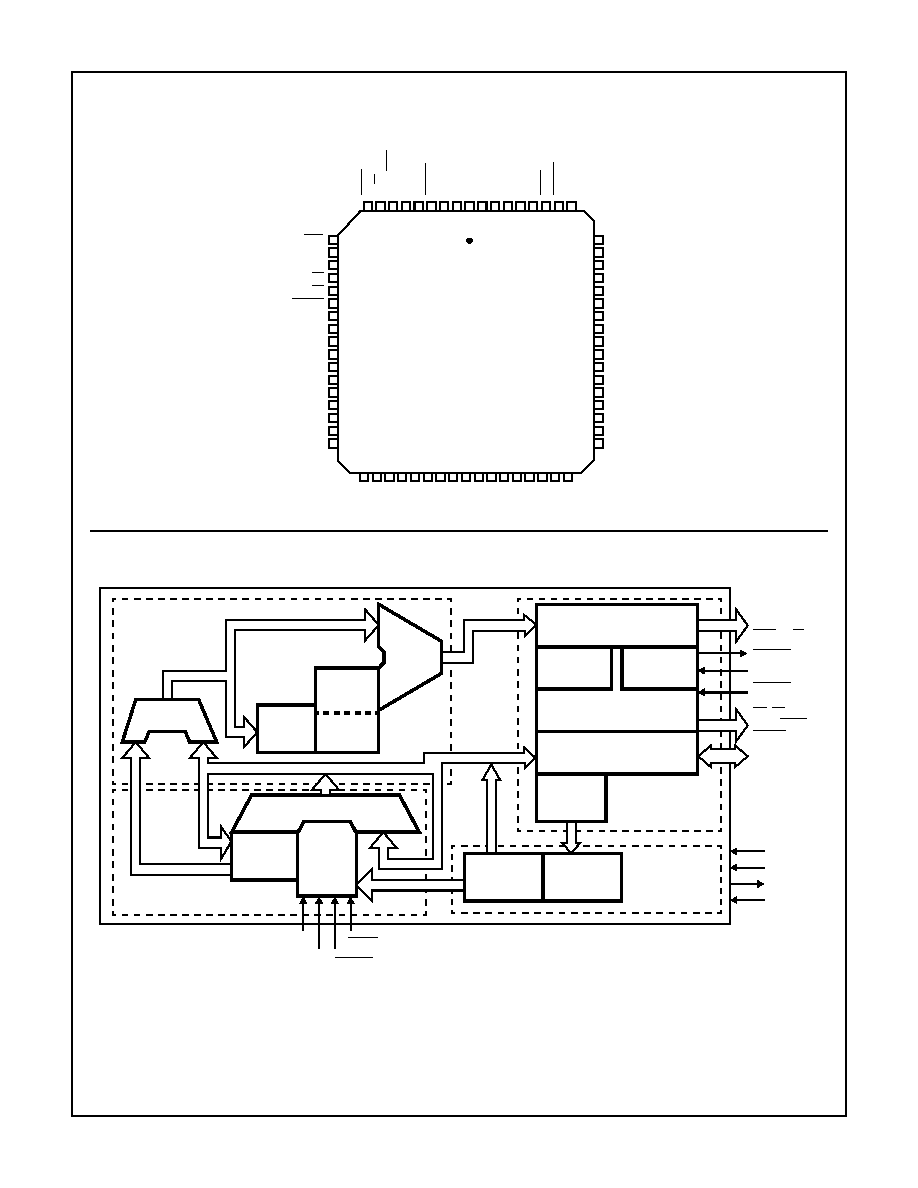

Pinouts

68 LEAD PGA

Component Pad View - As viewed from underside of the component when mounted on the board.

68 LEAD PGA

P.C. Board View - As viewed from the component side of the P.C. board.

68

66

64

62

60

58

56

54

52

53

51

55

57

59

61

63

65

67

2

1

3

5

7

9

10

4

6

8

12

11

13

14

16

15

17

19

18

21

20

22

24

26

28

30

32

34

23

25

27

29

31

33

36

35

37

38

40

39

41

42

44

43

45

46

48

47

49

50

E

RROR

D7

D6

D5

D4

D3

D2

D1

D0

NC

S1

PE

ACK

A2

2

A2

1

A1

9

A1

7

A1

5

A1

2

D0

A1

CLK

RESET

A4

A6

A8

A10

A12

ERROR

NC

INTR

NMI

PEREQ

READY

HLDA

M/IO

NC

NC

BUSY

NC

NC

V

SS

V

CC

HOLD

COD/INTA

LOCK

D1

5

D1

4

D1

3

D1

2

D11

D1

0

D9

D8

V

SS

BHE

NC

S0

A23

V

SS

A20

A18

A16

A14

A0

A2

V

CC

A3

A5

A7

A9

A11

A13

PIN 1 INDICATOR

68

66

64

62

60

58

56

54

52

53

51

55

57

59

61

63

65

67

2

1

3

5

7

9

10

4

6

8

12

11

13

14

16

15

17

19

18

21

20

22

24

26

28

30

32

34

23

25

27

29

31

33

36

35

37

38

40

39

41

42

44

43

45

46

48

47

49

50

ERR

O

R

D7

D6

D5

D4

D3

D2

D1

D0

NC

S1

P

E

ACK

A2

2

A2

1

A1

9

A1

7

A1

5

A1

2

D0

A1

CLK

RESET

A4

A6

A8

A10

A12

ERROR

NC

INTR

NMI

PEREQ

READY

HLDA

M/IO

NC

NC

BUSY

NC

NC

V

SS

V

CC

HOLD

COD/INTA

LOCK

D15

D14

D13

D12

D11

D10

D9

D8

V

SS

BHE

NC

S0

A2

3

V

SS

A2

0

A1

8

A1

6

A1

4

A0

A2

V

CC

A3

A5

A7

A9

A11

A13

PIN 1 INDICATOR

80C286

3

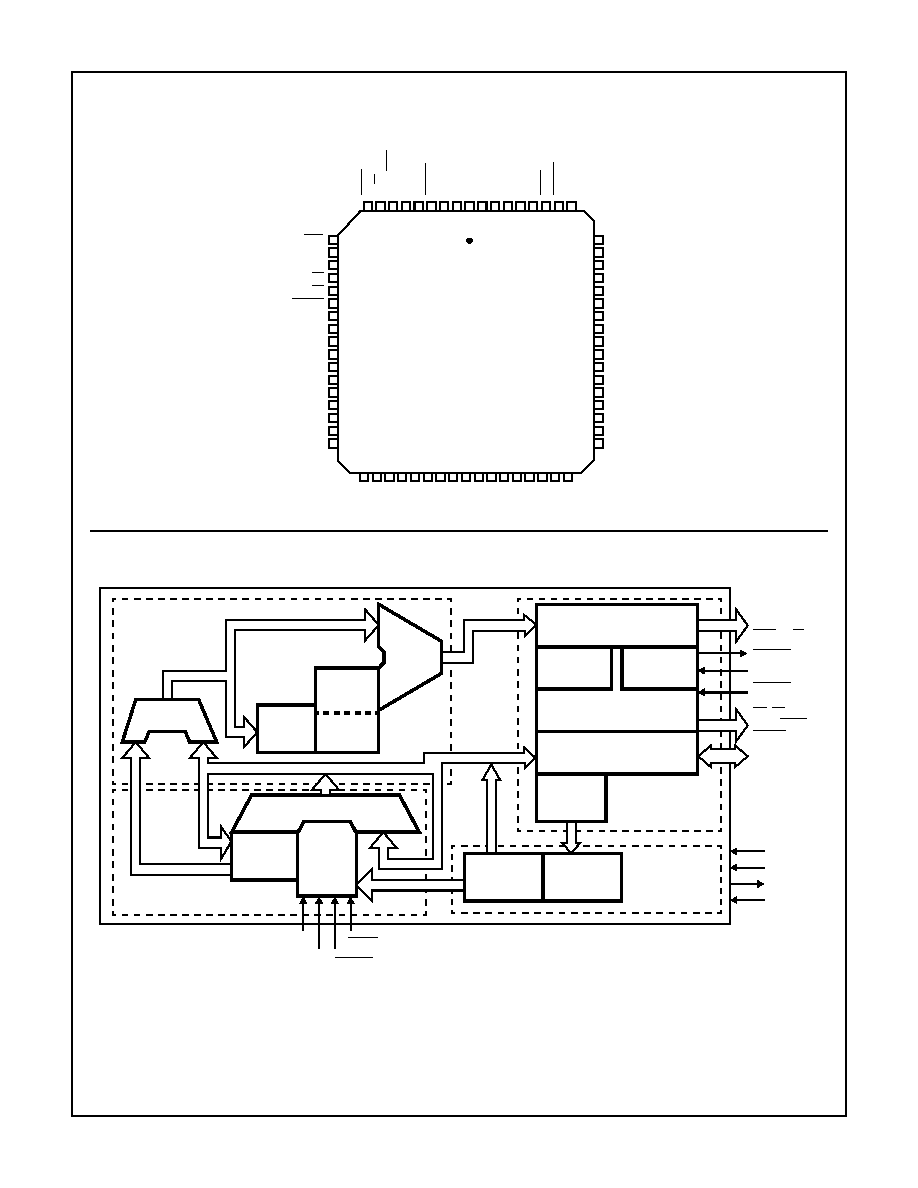

68 LEAD PLCC

P.C. Board View - As viewed from the component side of the P.C. board.

Functional Diagram

Pinouts

(Continued)

68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

D15

D7

D14

D6

D13

D5

D12

D4

D11

D3

D10

D2

D9

D1

D8

D0

V

SS

BHE

NC

NC

S1

S0

PEACK

A23

A22

V

SS

A21

A20

A19

A18

A17

A16

A15

A14

LOCK

M/

I

O

COD

/

INTA

HLDA

HOLD

RE

ADY

V

CC

PE

RE

Q

V

SS

NMI

NC

IN

T

R

NC

NC

BUS

Y

ER

ROR

NC

A1

3

A1

2

A11

A1

0

A9

A8

A7

A6

A5

A4

A3

R

ESE

T

V

CC

CLK

A2

A1

A0

OFFSET

ADDER

SEGMENT

LIMIT

CHECKER

SEGMENT

BASES

SEGMENT

SIZES

PHYSICAL

ADDRESS

ADDER

ALU

CONTROL

REGISTERS

ADDRESS

LATCHES AND DRIVERS

PRE-

BUS CONTROL

FETCHER

PROCESSOR

EXTENSION

INTERFACE

DATA TRANSCEIVERS

6-BYTE

PREFETCH

QUEUE

INSTRUCTION

UNIT (IU)

BUS UNIT (BU)

EXECUTION UNIT (EU)

ADDRESS UNIT (AU)

A

23

- A

0

,

BHE, M/IO

PEACK

3 DECODED

INSTRUCTION

QUEUE

INSTRUCTION

DECODER

PEREQ

READY,

HOLD,

S1, S0,

COD/INTA,

LOCK, HLDA

D

15

- D

0

RESET

CLK

V

SS

V

CC

NMI

BUSY

ERROR

INTR

80C286

4

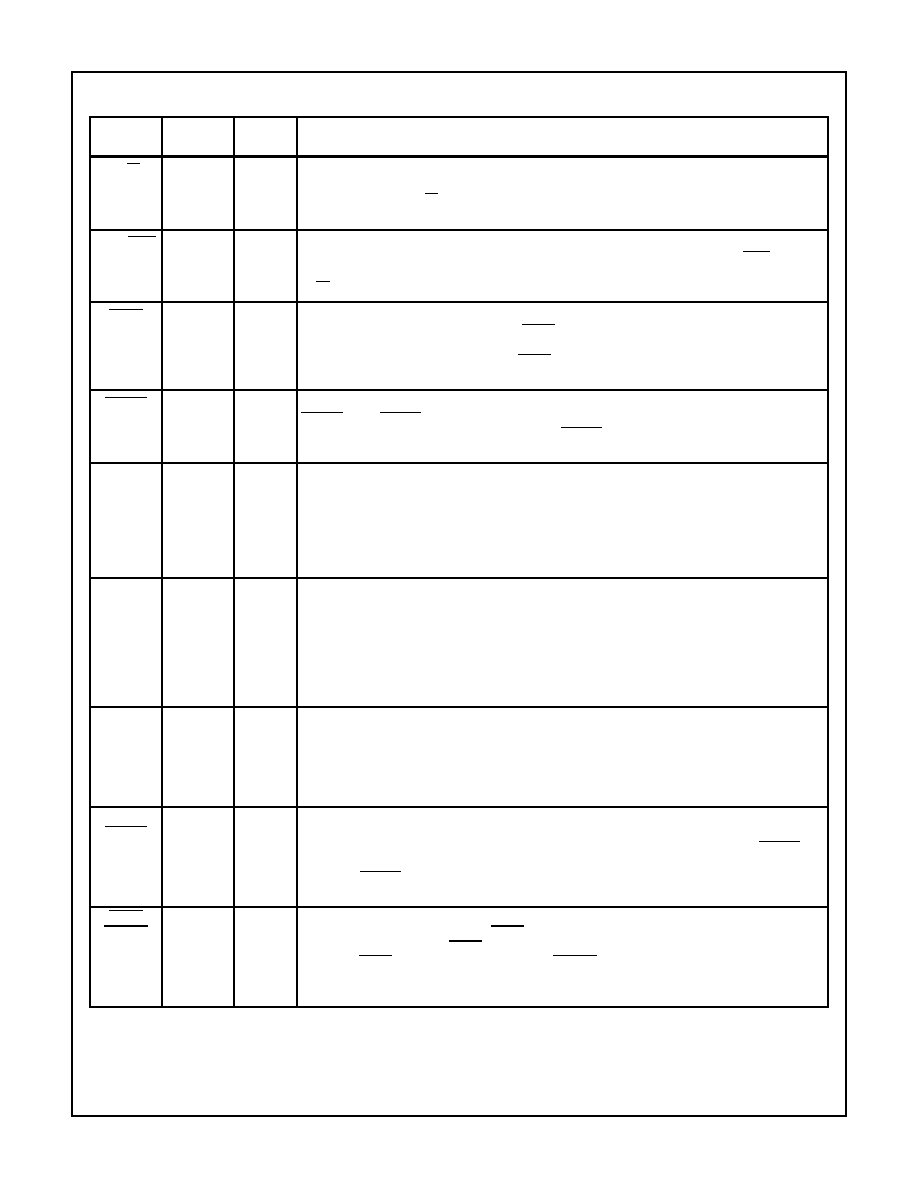

Pin Descriptions

The following pin function descriptions are for the 80C286 microprocessor.

SYMBOL

PIN

NUMBER

TYPE

DESCRIPTION

CLK

31

I

SYSTEM CLOCK: provides the fundamental timing for the 80C286 system. It is divided by two inside

the 80C286 to generate the processor clock. The internal divide-by-two circuitry can be synchro-

nized to an external clock generator by a LOW to HIGH transition on the RESET input.

D

15

- D

0

36 - 51

I/O

DATA BUS: inputs data during memory, I/O, and interrupt acknowledge read cycles; outputs data

during memory and I/O write cycles. The data bus is active HIGH and is held at high impedance to

the last valid logic level during bus hold acknowledge.

A

23

- A

0

7 - 8

10 - 28

32 - 43

O

ADDRESS BUS: outputs physical memory and I/O port addresses. A

23

- A

16

are LOW during I/O

transfers. A

0

is LOW when data is to be transferred on pins D

7

- D

0

(see table below). The address

bus is active High and floats to three-state off during bus hold acknowledge.

BHE

1

O

BUS HIGH ENABLE: indicates transfer of data on the upper byte of the data bus, D

15

- D

8

. Eight-bit

oriented devices assigned to the upper byte of the data bus would normally use BHE to condition chip

select functions. BHE is active LOW and floats to three-state OFF during bus hold acknowledge.

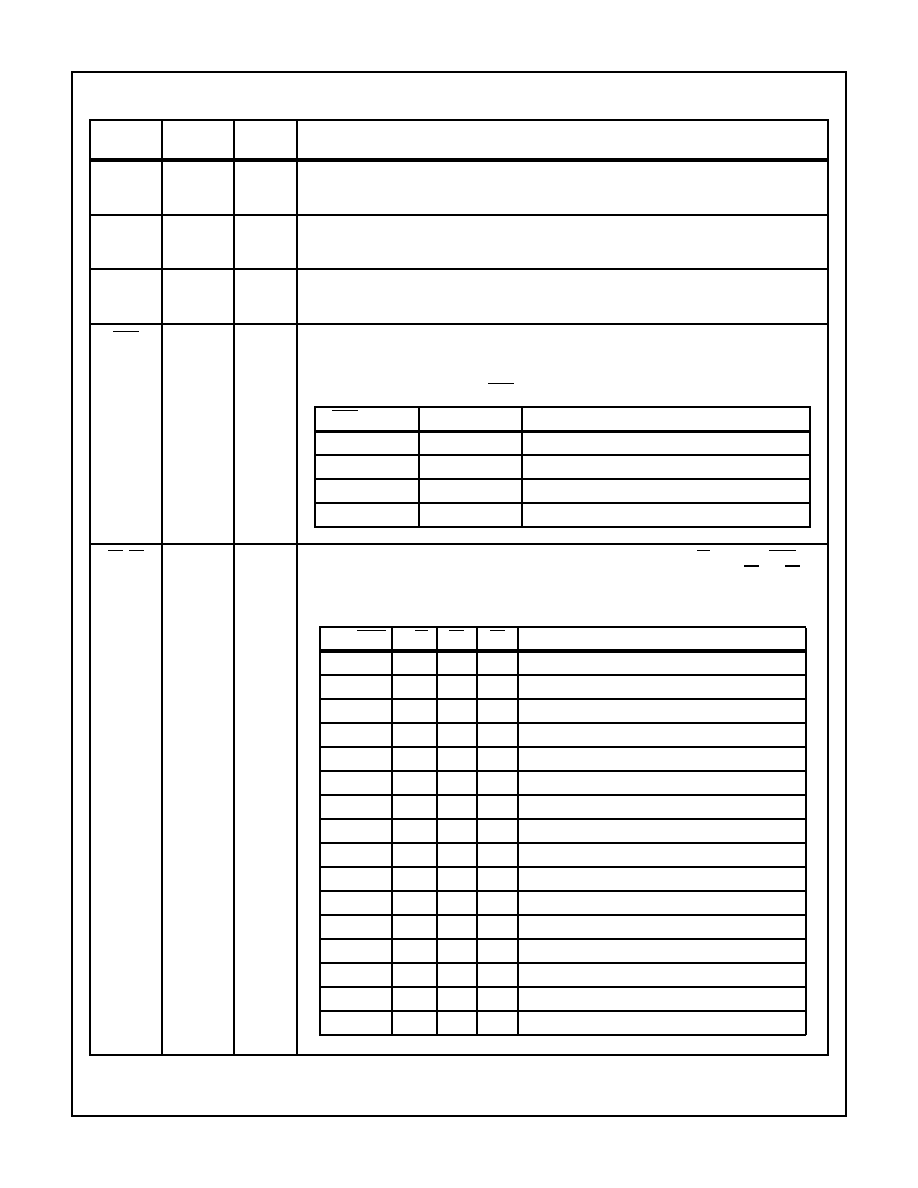

S1, S0

4, 5

O

BUS CYCLE STATUS: indicates initiation of a bus cycle and along with M/IO and COD/lNTA, de-

fines the type of bus cycle. The bus is in a T

S

state whenever one or both are LOW. S1 and S0 are

active LOW and are held at a high impedance logic one during bus hold acknowledge.

BHE AND A

0

ENCODINGS

BHE VALUE

A

0

VALUE

FUNCTION

0

0

Word transfer

0

1

Byte transfer on upper half of data bus (D

15

- D

8

)

1

0

Byte transfer on lower half of data bus (D

7

- D

0

)

1

1

Reserved

80C286 BUS CYCLE STATUS DEFINITION

COD/INTA

M/IO

S1

S0

BUS CYCLE INITIATED

0(LOW)

0

0

0

Interrupt acknowledge

0

0

0

1

Reserved

0

0

1

0

Reserved

0

0

1

1

None; not a status cycle

0

1

0

0

If A

1

= 1 then halt; else shutdown

0

1

0

1

Memory data read

0

1

1

0

Memory data write

0

1

1

1

None; not a status cycle

1(HIGH)

0

0

0

Reserved

1

0

0

1

I/O read

1

0

1

0

I/O write

1

0

1

1

None; not a status cycle

1

1

0

0

Reserved

1

1

0

1

Memory instruction read

1

1

1

0

Reserved

1

1

1

1

None; not a status cycle

80C286

5

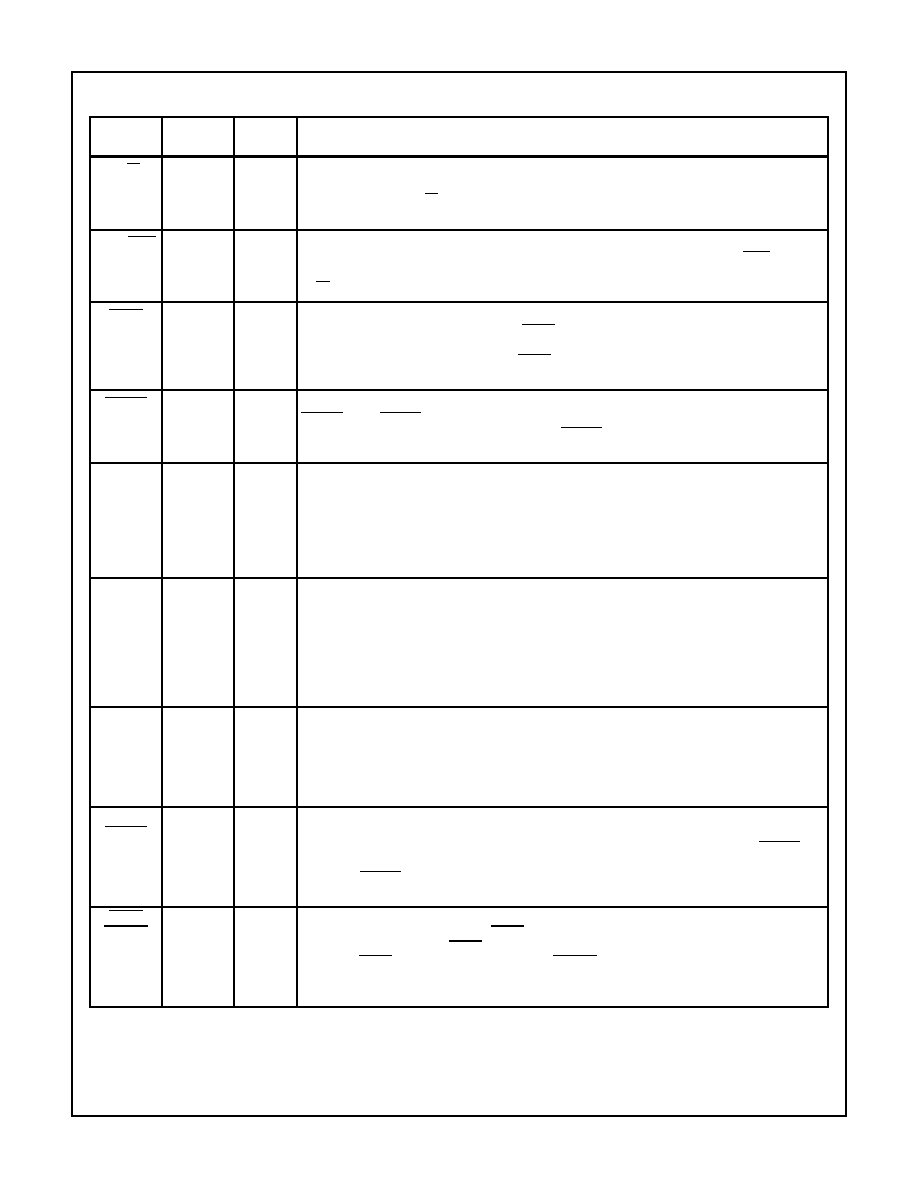

M/IO

67

O

MEMORY I/O SELECT: distinguishes memory access from I/O access. If HIGH during T

S

, a mem-

ory cycle or a halt/shutdown cycle is in progress. If LOW, an I/O cycle or an interrupt acknowledge

cycle is in progress. M/IO is held at high impedance to the last valid logic state during bus hold ac-

knowledge.

COD/lNTA

66

O

CODE/INTERRUPT ACKNOWLEDGE: distinguishes instruction fetch cycles from memory data

read cycles. Also distinguishes interrupt acknowledge cycles from I/O cycles. COD/lNTA is held at

high impedance to the last valid logic state during bus hold acknowledge. Its timing is the same as

M/IO.

LOCK

68

O

BUS LOCK: indicates that other system bus masters are not to gain control of the system bus for

the current and following bus cycles. The LOCK signal may be activated explicitly by the "LOCK"

instruction prefix or automatically by 80C286 hardware during memory XCHG instructions, interrupt

acknowledge, or descriptor table access. LOCK is active LOW and is held at a high impedance logic

one during bus hold acknowledge.

READY

63

l

BUS READY: terminates a bus cycle. Bus cycles are extended without limit until terminated by

READY LOW. READY is an active LOW synchronous input requiring setup and hold times relative

to the system clock be met for correct operation. READY is ignored during bus hold acknowledge.

(See Note 1)

HOLD

HLDA

64

65

I

O

BUS HOLD REQUEST AND HOLD ACKNOWLEDGE: control ownership of the 80C286 local bus.

The HOLD input allows another local bus master to request control of the local bus. When control is

granted, the 80C286 will float its bus drivers and then activate HLDA, thus entering the bus hold ac-

knowledge condition. The local bus will remain granted to the requesting master until HOLD be-

comes inactive which results in the 80C286 deactivating HLDA and regaining control of the local

bus. This terminates the bus hold acknowledge condition. HOLD may be asynchronous to the sys-

tem clock. These signals are active HIGH. Note that HLDA never floats.

INTR

57

I

INTERRUPT REQUEST: requires the 80C286 to suspend its current program execution and service

a pending external request. Interrupt requests are masked whenever the interrupt enable bit in the

flag word is cleared. When the 80C286 responds to an interrupt request, it performs two interrupt

acknowledge bus cycles to read an 8-bit interrupt vector that identifies the source of the interrupt.

To ensure program interruption, INTR must remain active until an interrupt acknowledge bus cycle

is initiated. INTR is sampled at the beginning of each processor cycle and must be active HIGH at

least two processor cycles before the current instruction ends in order to interrupt before the next

instruction. INTR is level sensitive, active HIGH, and may be asynchronous to the system clock.

NMI

59

l

NON-MASKABLE INTERRUPT REQUEST: interrupts the 80C286 with an internally supplied vector

value of two. No interrupt acknowledge cycles are performed. The interrupt enable bit in the 80C286

flag word does not affect this input. The NMI input is active HIGH, may be asynchronous to the sys-

tem clock, and is edge triggered after internal synchronization. For proper recognition, the input must

have been previously LOW for at least four system clock cycles and remain HIGH for at least four

system clock cycles.

PEREQ

PEACK

61

6

l

O

PROCESSOR EXTENSION OPERAND REQUEST AND ACKNOWLEDGE: extend the memory

management and protection capabilities of the 80C286 to processor extensions. The PEREQ input

requests the 80C286 to perform a data operand transfer for a processor extension. The PEACK out-

put signals the processor extension when the requested operand is being transferred. PEREQ is ac-

tive HIGH. PEACK is active LOW and is held at a high impedance logic one during bus hold

acknowledge. PEREQ may be asynchronous to the system clock.

BUSY

ERROR

54

53

l

I

PROCESSOR EXTENSION BUSY AND ERROR: indicates the operating condition of a processor

extension to the 80C286. An active BUSY input stops 80C286 program execution on WAIT and

some ESC instructions until BUSY becomes inactive (HIGH). The 80C286 may be interrupted while

waiting for BUSY to become inactive. An active ERROR input causes the 80C286 to perform a pro-

cessor extension interrupt when executing WAIT or some ESC instructions. These inputs are active

LOW and may be asynchronous to the system clock.

Pin Descriptions

The following pin function descriptions are for the 80C286 microprocessor. (Continued)

SYMBOL

PIN

NUMBER

TYPE

DESCRIPTION

80C286