| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 8403602ZA | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

1

TM

March 1997

HM-65162

2K x 8 Asynchronous

CMOS Static RAM

Features

∑ Fast Access Time . . . . . . . . . . . . . . . . . . . 70/90ns Max

∑ Low Standby Current. . . . . . . . . . . . . . . . . . . .50

µ

A Max

∑ Low Operating Current . . . . . . . . . . . . . . . . . 70mA Max

∑ Data Retention at 2.0V . . . . . . . . . . . . . . . . . . .20

µ

A Max

∑ TTL Compatible Inputs and Outputs

∑ JEDEC Approved Pinout (2716, 6116 Type)

∑ No Clocks or Strobes Required

∑ Equal Cycle and Access Time

∑ Single 5V Supply

∑ Gated Inputs

∑ No Pull-Up or Pull-Down Resistors Required

Description

The HM-65162 is a CMOS 2048 x 8 Static Random Access

Memory manufactured using the Intersil Advanced SAJI V

process. The device utilizes asynchronous circuit design for

fast cycle time and ease of use. The pinout is the JEDEC 24

pin DIP, and 32 pad 8-bit wide standard which allows easy

memory board layouts flexible to accommodate a variety of

industry standard PROMs, RAMs, ROMs and EPROMs. The

HM-65162 is ideally suited for use in microprocessor based

systems with its 8-bit word length organization. The conve-

nient output enable also simplifies the bus interface by allow-

ing the data outputs to be controlled independent of the chip

enable. Gated inputs lower operating current and also elimi-

nate the need for pull-up or pull-down resistors.

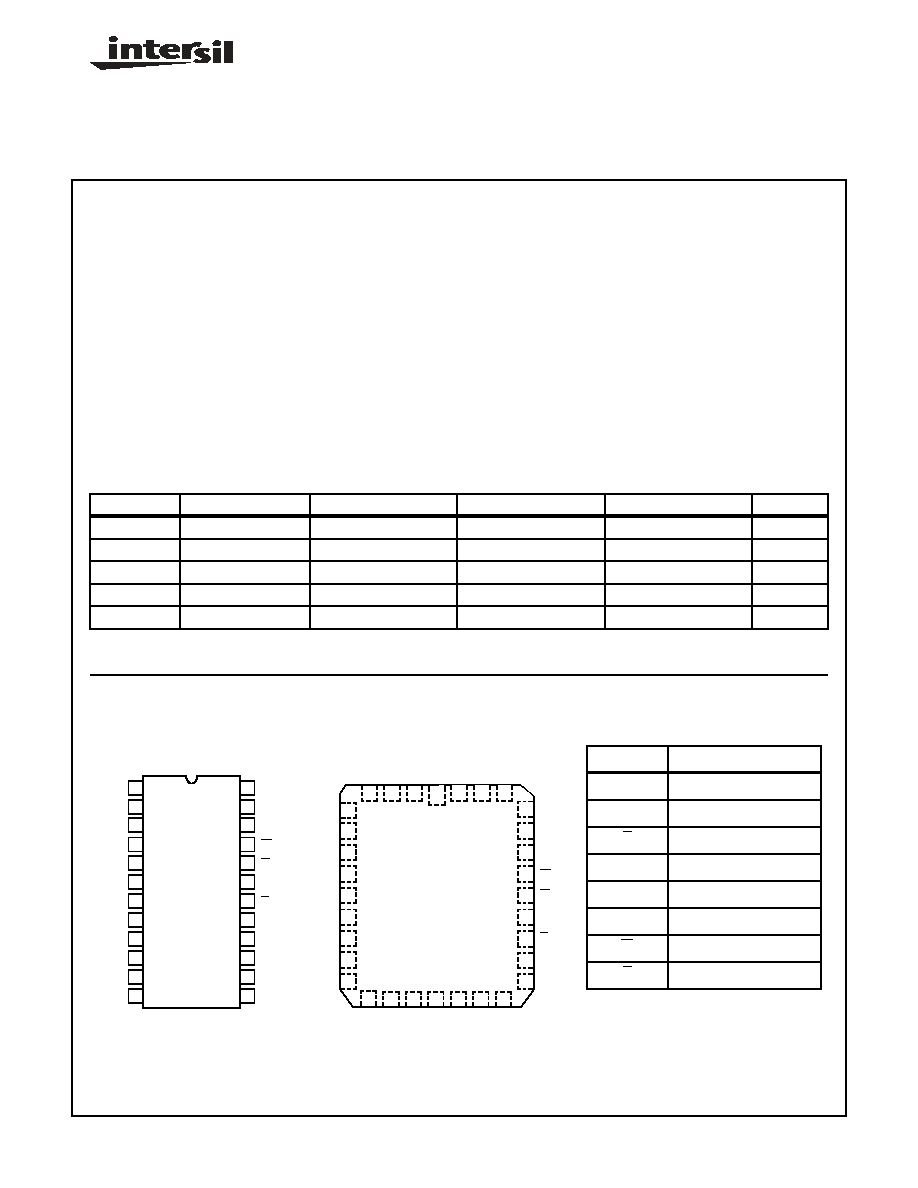

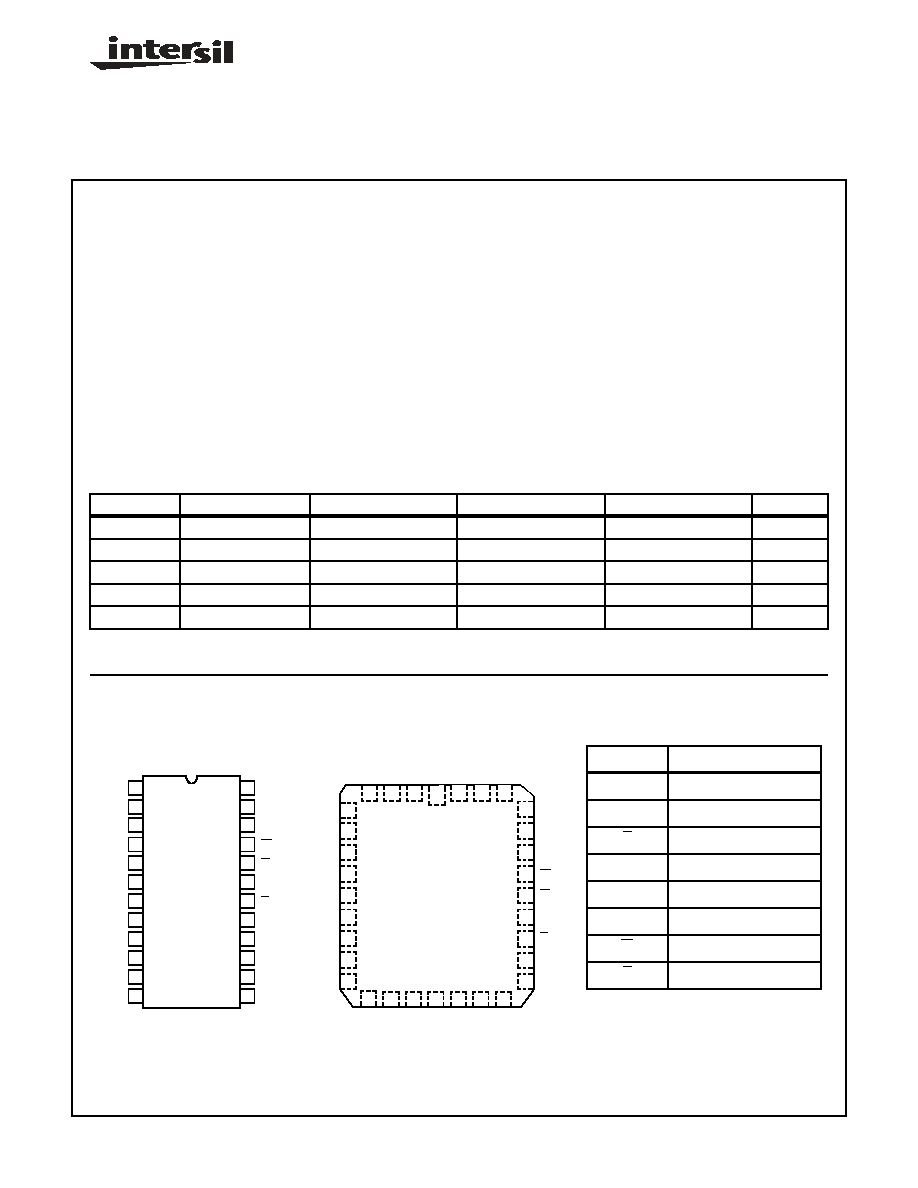

Pinouts

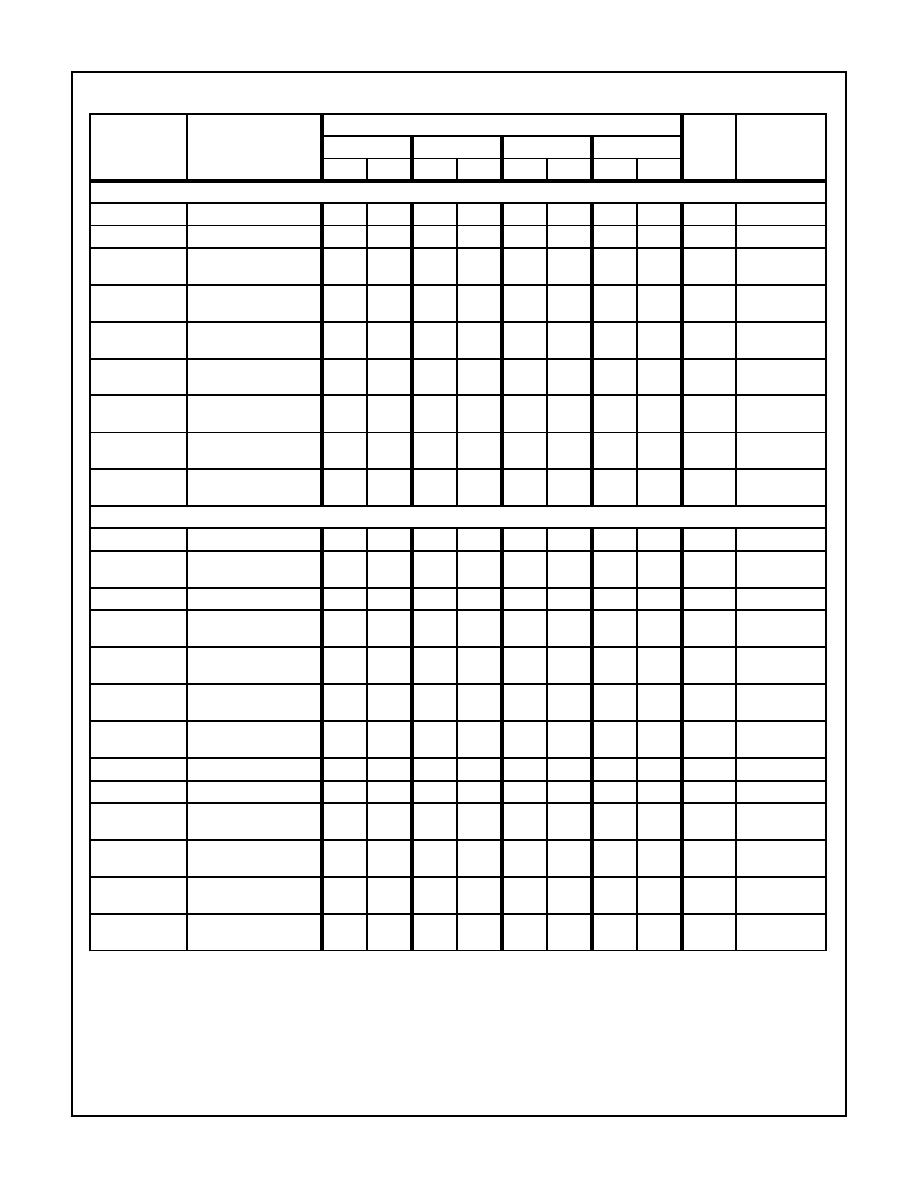

Ordering Information

PACKAGE

TEMP. RANGE

70ns/20

µ

A (NOTE 1)

90ns/40

µ

A (NOTE 1)

90ns/300

µ

A (NOTE 1)

PKG. NO.

CERDIP

-40

o

C to +85

o

C

HM1-65162B-9

HM1-65162-9

HM1-65162C-9

F24.6

JAN#

-55

o

C to +125

o

C

29110BJA

29104BJA

-

F24.6

SMD#

-55

o

C to +125

o

C

8403606JA

8403602JA

8403603JA

F24.6

CLCC

-40

o

C to +85

o

C

HM4-65162B-9

HM4-65162-9

HM4-65162C-9

J32.A

SMD#

-55

o

C to 125

o

C

8403606ZA

8403602ZA

8403603ZA

J32.A

NOTE:

1. Access time/data retention supply current.

HM-65162

(CERDIP)

TOP VIEW

HM-65162

(CLCC)

TOP VIEW

1

2

3

4

5

6

7

8

9

10

11

12

16

17

18

19

20

21

22

23

24

15

14

13

V

CC

A9

W

G

A10

DQ7

DQ5

DQ4

DQ3

A8

E

DQ6

A7

A6

A5

A4

A3

A2

A1

A0

DQ0

DQ1

DQ2

GND

5

6

7

8

11

10

9

13

12

27

28

29

26

25

24

23

22

21

3

2

1

4

32 31 30

16 17 18 19 20

14 15

A6

A5

A4

A3

A2

A1

A0

NC

DQ0

DQ

1

DQ

2

GN

D

NC

DQ

3

DQ

4

DQ

5

V

CC

NC

NC

A7

NC

NC

NC

A8

A9

NC

G

A10

E

DQ7

DQ6

W

PIN

DESCRIPTION

NC

No Connect

A0 - A10

Address Input

E

Chip Enable/Power Down

V

SS

/GND

Ground

DQ0 - DQ7

Data In/Data Out

V

CC

Power

(+5V)

W

Write Enable

G

Output Enable

FN3000.1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143

|

Intersil (and design) is a trademark of Intersil Americas Inc.

Copyright © Intersil Americas Inc. 2002. All Rights Reserved

2

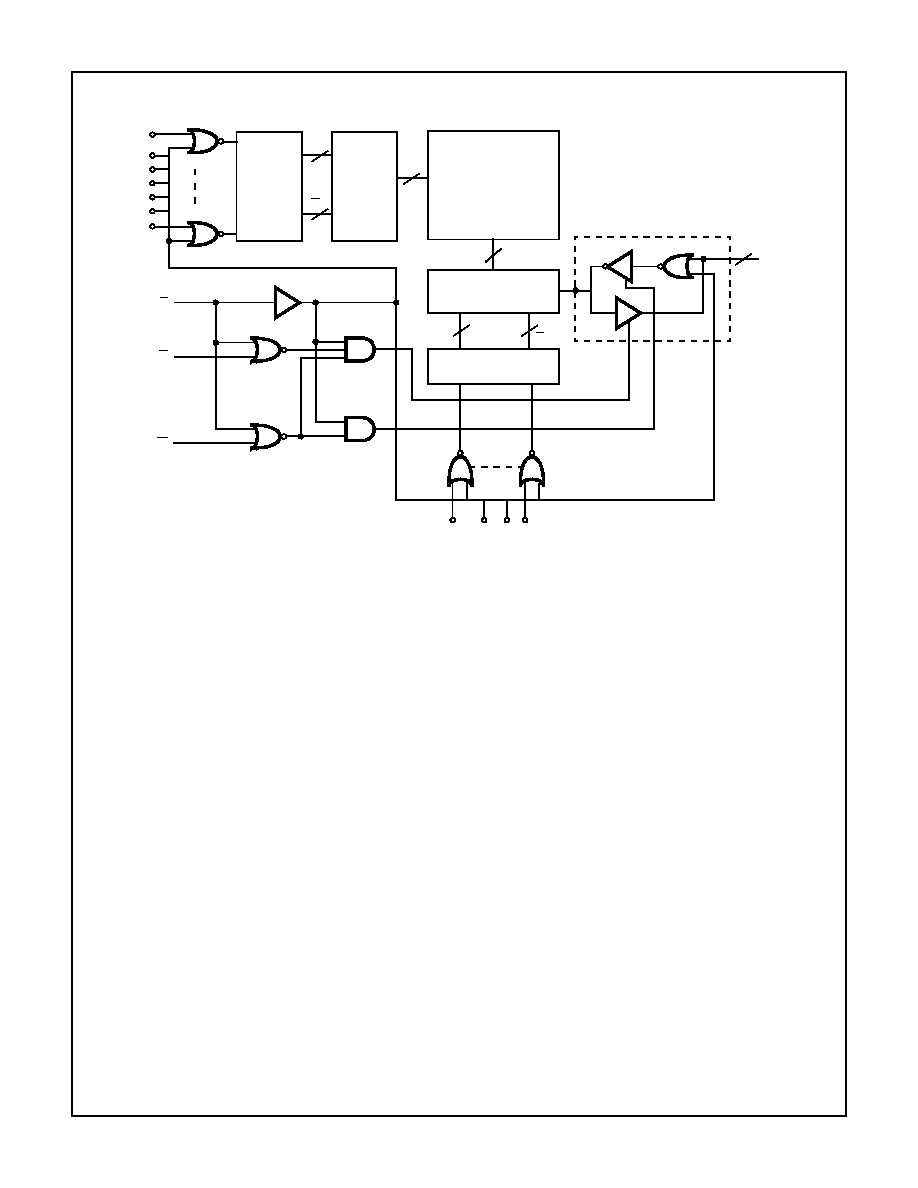

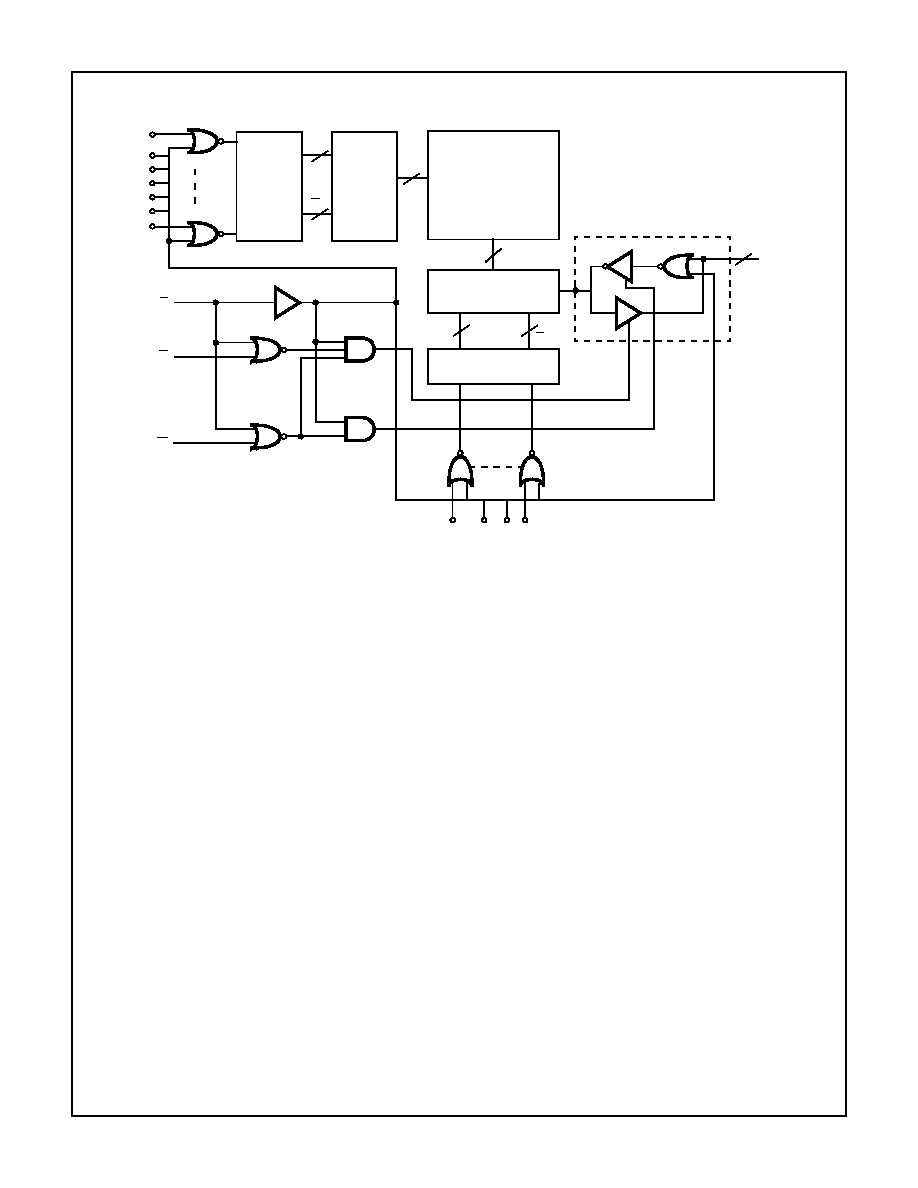

Functional Diagram

ROW

DECODER

ROW

ADDRESS

BUFFER

128

7

7

A1

A2

A3

A4

A5

A6

A7

1 OF 8

8

DQ0

THRU

DQ7

128

E

W

128 X 128

MEMORY ARRAY

A

4

A

4

A0

A8 A9 A10

G

A

A

COLUMN DECODER

AND DATA

INPUT / OUTPUT (X8)

COLUMN

ADDRESS BUFFER

HM-65162

3

Absolute Maximum Ratings

Thermal Information

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +7.0V

Input, Output or I/O Voltage . . . . . . . . . . . GND -0.3V to V

CC

+0.3V

Typical Derating Factor . . . . . . . . . . 05mA/MHz Increase in ICCOP

ESD Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Class 1

Operating Conditions

Operating Voltage Range . . . . . . . . . . . . . . . . . . . . . +4.5V to +5.5V

Operating Temperature Range

HM-65162S-9, HM-65162B-9,

HM-65162-9, HM65162C-9. . . . . . . . . . . . . . . . . . -40

o

C to +85

o

C

Thermal Resistance

JA

(

o

C/W)

JC

(

o

C/W)

CERDIP Package . . . . . . . . . . . . . . . .

48

8

CLCC Package . . . . . . . . . . . . . . . . . .

66

12

Maximum Storage Temperature Range . . . . . . . . .-65

o

C to +150

o

C

Maximum Junction Temperature. . . . . . . . . . . . . . . . . . . . . . +175

o

C

Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . . +300

o

C

Die Characteristics

Gate Count . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26000 Gates

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating

and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

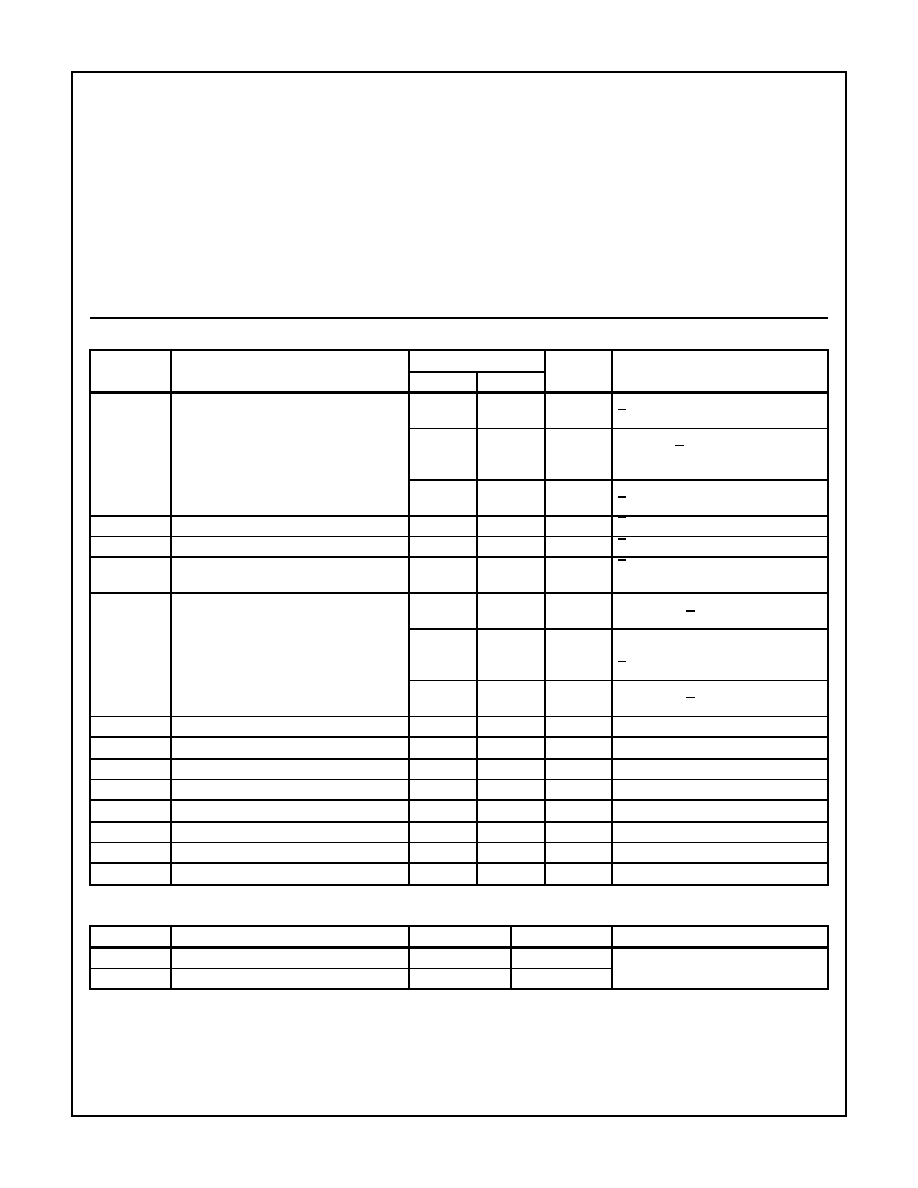

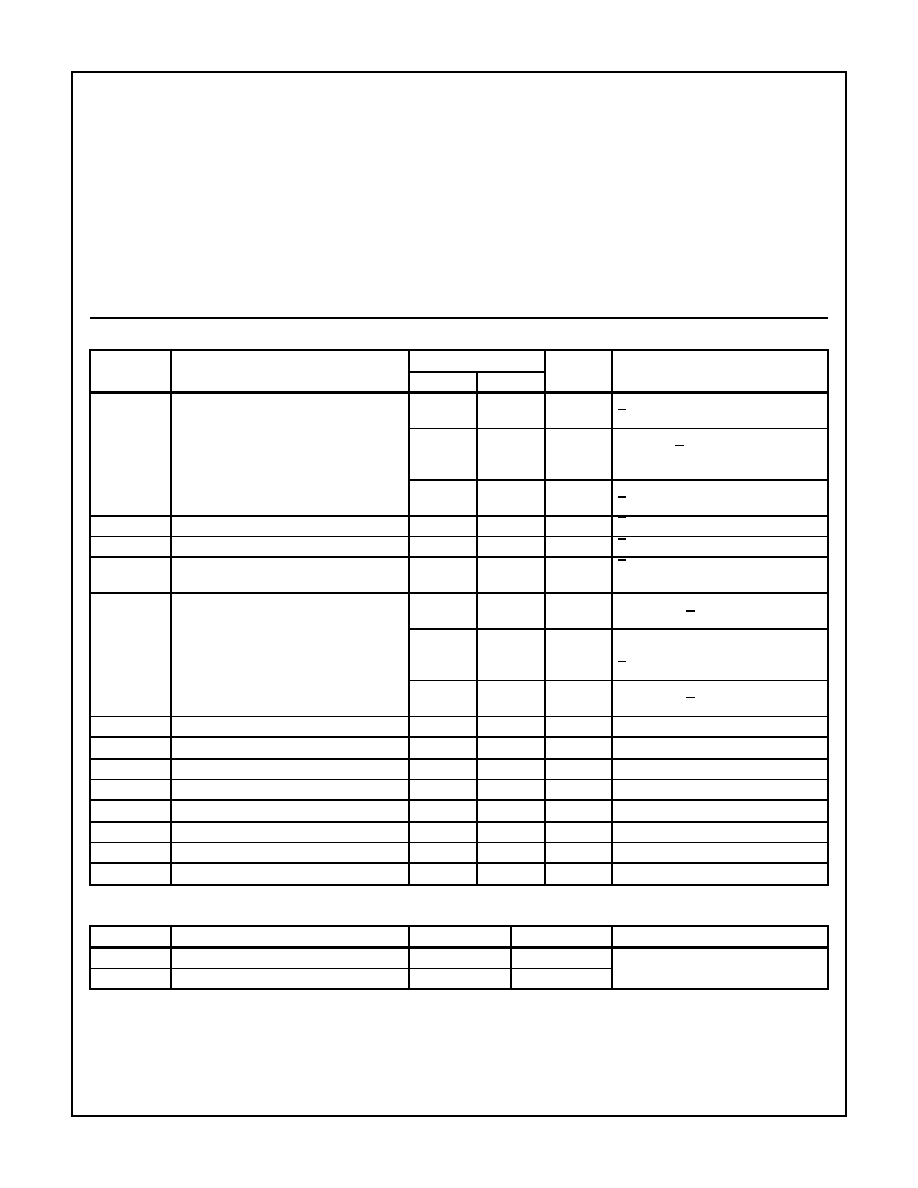

DC Electrical Specifications

V

CC

= 5V

±

10%; T

A

= -40

o

C to +85

o

C (HM-65162S-9, HM-65162B-9, HM-65162-9, HM-65162C-9)

SYMBOL

PARAMETER

LIMITS

UNITS

TEST CONDITIONS

MIN

MAX

ICCSB1

Standby Supply Current

-

50

µ

A

HM-65162B-9, IO = 0mA,

E = V

CC

- 0.3V, V

CC

= 5.5V

-

100

µ

A

HM-65162S-9, HM65162-9,

IO = 0mA, E = V

CC

- 0.3V,

V

CC

= 5.5V

-

900

µ

A

HM-65162C-9, IO = 0mA,

E = V

CC

- 0.3V, V

CC

= 5.5V

ICCSB

Standby Supply Current

-

8

mA

E = 2.2V, IO = 0mA, V

CC

= 5.5V

ICCEN

Enabled Supply Current

-

70

mA

E = 0.8V, IO = 0mA, V

CC

= 5.5V

ICCOP

Operating Supply Current (Note 1)

-

70

mA

E = 0.8V, IO = 0mA, f = 1MHz,

V

CC

= 5.5V

ICCDR

Data Retention Supply Current

-

20

µ

A

HM-65162B-9, IO = 0mA,

V

CC

= 2.0V, E = VCC - 0.3V

-

40

µ

A

HM-65162S-9, HM-65162-9,

IO = 0mA, V

CC

= 2.0V,

E = V

CC

- 0.3V

-

300

µ

A

HM-65162C-9, IO = 0mA,

V

CC

= 2.0V, E = V

CC

- 0.3V

VCCDR

Data Retention Supply Voltage

2.0

-

V

II

Input Leakage Current

-1.0

+1.0

µ

A

VI = V

CC

or GND, V

CC

= 5.5V

IIOZ

Input/Output Leakage Current

-1.0

+1.0

µ

A

VIO = V

CC

or GND, V

CC

= 5.5V

V

IL

Input Low Voltage

-0.3

0.8

V

V

CC

= 4.5V

V

IH

Input High Voltage

2.2

V

CC

+0.3

V

V

CC

= 5.5V

VOL

Output Low Voltage

-

0.4

V

IO = 4.0mA, V

CC

= 4.5V

VOH1

Output High Voltage

2.4

-

V

IO = -1.0mA, V

CC

= 4.5V

VOH2

Output High Voltage (Note 2)

V

CC

-0.4

-

V

IO = -100

µ

A, V

CC

= 4.5V

Capacitance

T

A

= +25

o

C

SYMBOL

PARAMETER

MAX

UNITS

TEST CONDITIONS

CI

Input Capacitance (Note 2)

10

pF

f = 1MHz, All measurements are

referenced to device GND

CIO

Input/Output Capacitance (Note 2)

12

pF

NOTES:

1. Typical derating 5mA/MHz increase in ICCOP.

2. Tested at initial design and after major design changes.

HM-65162

4

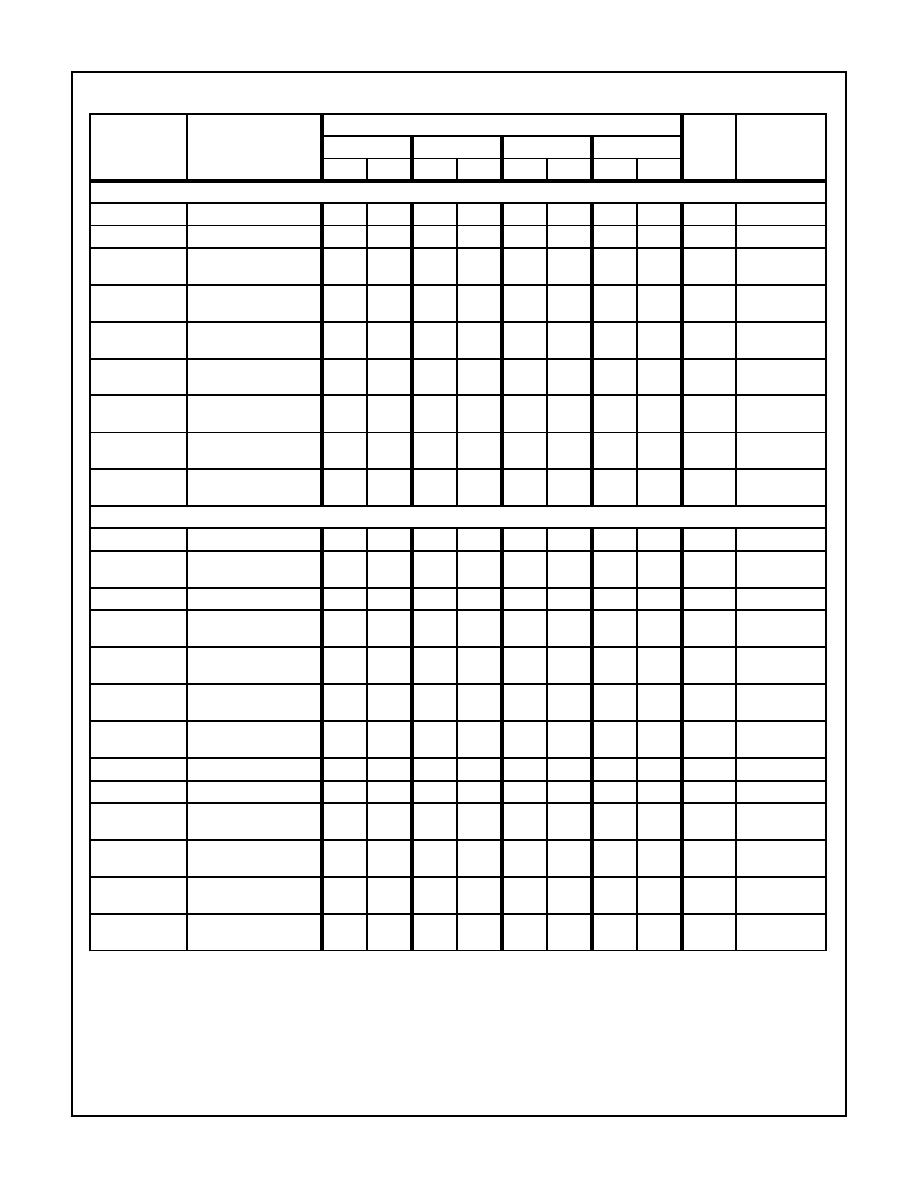

AC Electrical Specifications

V

CC

= 5V

±

10%, T

A

= -40

o

C to +85

o

C (HM-65162S-9, HM-65162B-9, HM65162-9, HM-65162C-9)

SYMBOL

PARAMETER

LIMITS

UNITS

CONDITIONS

HM-65162S-9

HM-65162B-9

HM-65162-9

HM-65162C-9

MIN

MAX

MIN

MAX

MIN

MAX

MIN

MAX

READ CYCLE

(1) TAVAX

Read Cycle Time

55

-

70

-

90

-

90

-

ns

(Notes 1, 3)

(2) TAVQV

Address Access Time

-

55

-

70

-

90

-

90

ns

(Notes 1, 3, 4)

(3) TELQV

Chip Enable Access

Time

-

55

-

70

-

90

-

90

ns

(Notes 1, 3)

(4) TELQX

Chip Enable Output

Enable Time

5

-

5

-

5

-

5

-

ns

(Notes 2, 3)

(5) TGLQV

Output Enable Access

Time

-

35

-

50

-

65

-

65

ns

(Notes 1, 3)

(6) TGLQX

Output Enable Output

Enable Time

5

-

5

-

5

-

5

-

ns

(Notes 2, 3)

(7) TEHQZ

Chip Enable Output

Disable Time

-

35

-

35

-

50

-

50

ns

(Notes 2, 3)

(8) TGHQZ

Output Enable Output

Disable Time

-

30

-

35

-

40

-

40

ns

(Notes 2, 3)

(9) TAVQX

Output Hold From

Address Change

5

-

5

-

5

-

5

-

ns

(Notes 1, 3)

WRITE CYCLE

(10) TAVAX

Write Cycle Time

55

-

70

-

90

-

90

-

ns

(Notes 1, 3)

(11) TELWH

Chip Selection to End of

Write

45

-

45

-

55

-

55

-

ns

(Notes 1, 3)

(12) TAVWL

Address Setup Time

5

-

10

-

10

-

10

-

ns

(Notes 1, 3)

(13) TWLWH

Write Enable Pulse

Width

40

-

40

-

55

-

55

-

ns

(Notes 1, 3)

(14) TWHAX

Write Enable Read

Setup Time

10

-

10

-

10

-

10

-

ns

(Notes 1, 3)

(15) TGHQZ

Output Enable Output

Disable Time

-

30

-

35

-

40

-

40

ns

(Notes 2, 3)

(16) TWLQZ

Write Enable Output

Disable Time

-

30

-

40

-

50

-

50

ns

(Notes 2, 3)

(17) TDVWH

Data Setup Time

25

-

30

-

30

-

30

-

ns

(Notes 1, 3)

(18) TWHDX

Data Hold Time

10

-

10

-

15

-

15

-

ns

(Notes 1, 3)

(19) TWHQX

Write Enable Output

Enable Time

0

-

0

-

0

-

0

-

ns

(Notes 1, 3)

(20) TWLEH

Write Enable Pulse

Setup Time

45

-

40

-

55

-

55

-

ns

(Notes 1, 3)

(21) TDVEH

Chip Enable Data

Setup Time

25

-

30

-

30

-

30

-

ns

(Notes 1, 3)

(22) TAVWH

Address Valid to End of

Write

45

-

50

-

65

-

65

-

ns

(Notes 1, 3)

NOTES:

1. Input pulse levels: 0 to 3.0V; Input rise and fall times: 5ns (max); Input and output timing reference level: 1.5V; Output load: 1 TTL gate

equivalent and C

L

= 50pF (min) - for C

L

greater than 50pF, access time is derated by 0.15ns per pF.

2. Tested at initial design and after major design changes.

3. V

CC

= 4.5 and 5.5V.

4. TAVQV = TELQV + TAVEL.

HM-65162

5

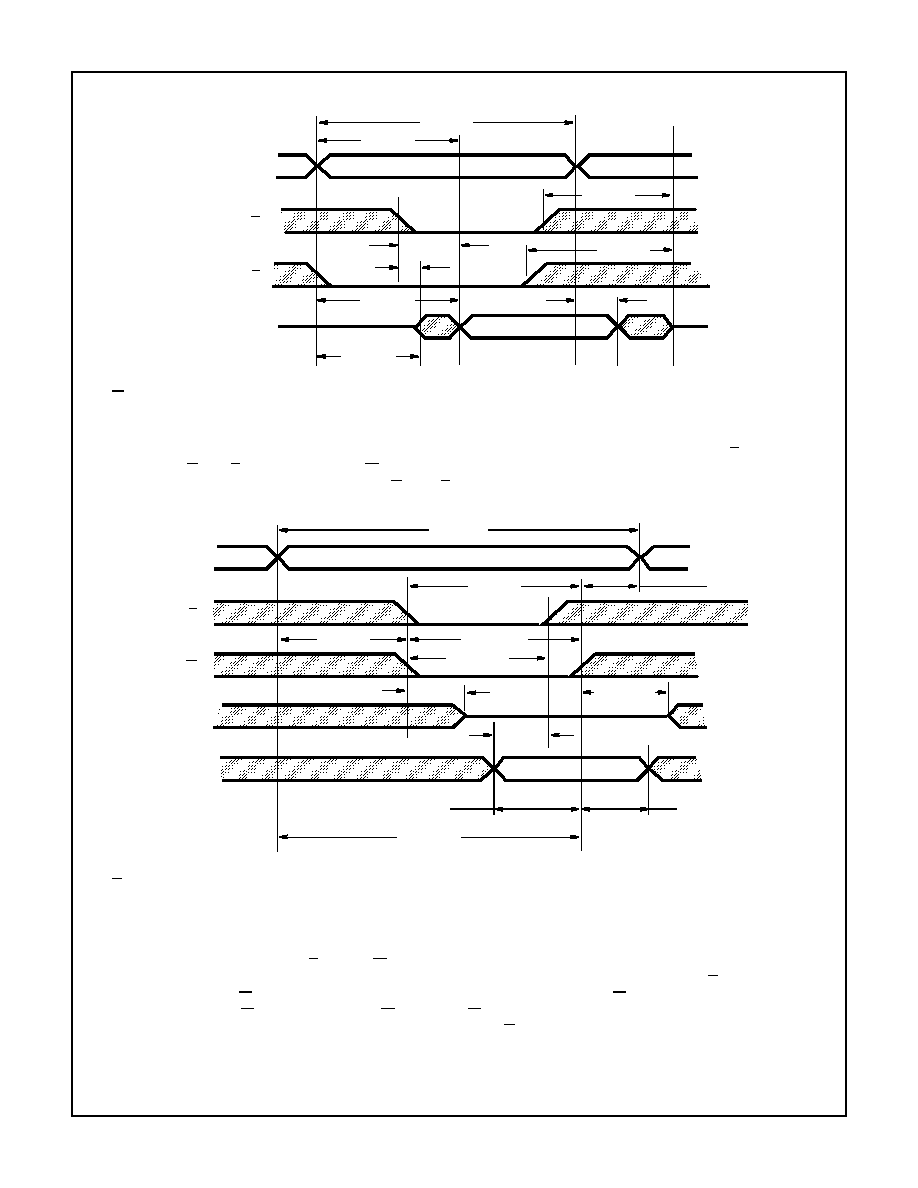

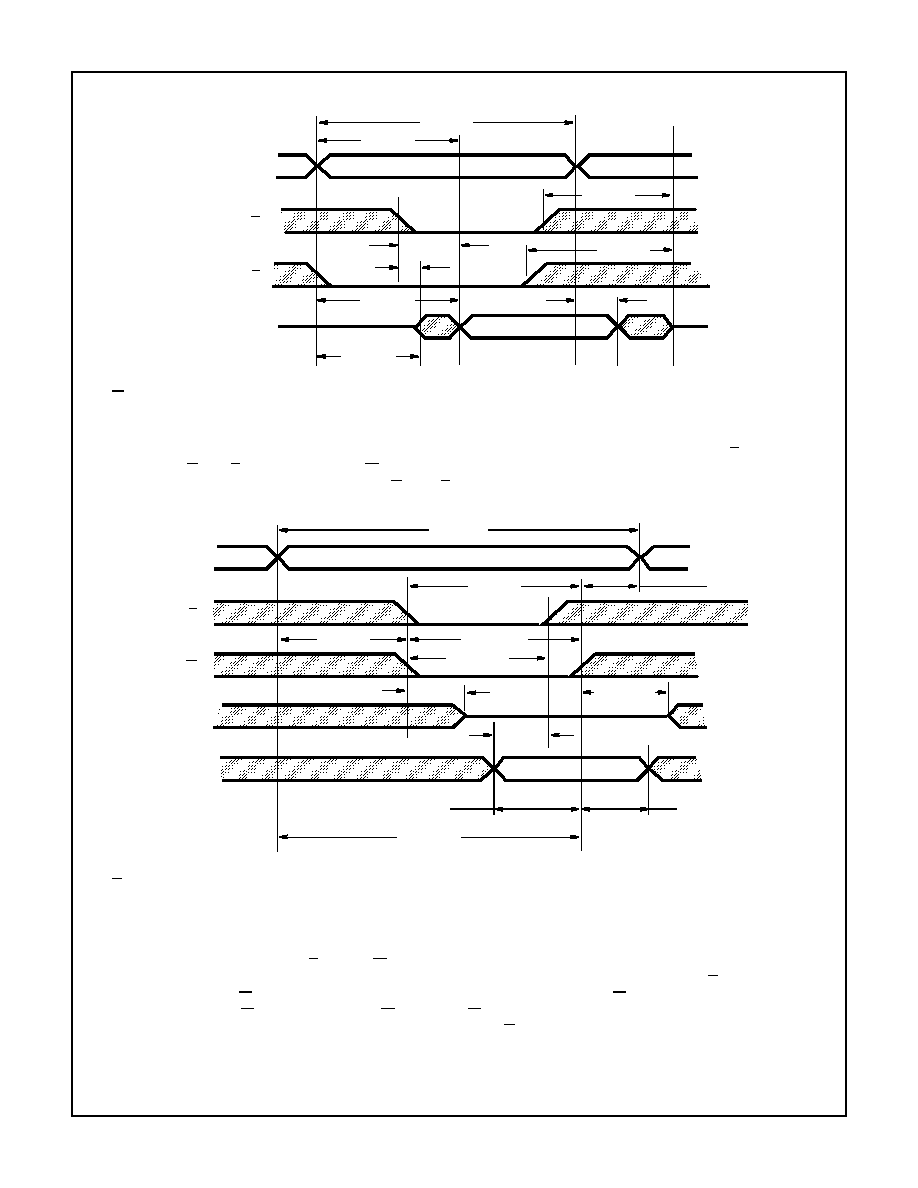

Timing Waveforms

Addresses must remain stable for the duration of the read

cycle. To read, G and E must be

V

IL

and W

V

IH

. The

output buffers can be controlled independently by G while E

is low. To execute consecutive read cycles, E may be tied

low continuously until all desired locations are accessed.

To write, addresses must be stable, E low and W falling low

for a period no shorter than TWLWH. Data in is referenced

with the rising edge of W, (TDVWH and TWHDX). While

addresses are changing, W must be high. When W falls low,

the I/O pins are still in the output state for a period of TWLQZ

and input data of the opposite phase to the outputs must not

be applied, (Bus contention). If E transitions low

simultaneously with the W line transitioning low, or after the

W transition, the output will remain in a high impedance

state. G is held continuously low.

(9) TAVQX

(6) TGLQX

(5) TGLQV

ADDRESS

G

E

Q

(1) TAVAX

(2) TAVQV

(8) TGHQZ

(7) TEHQZ

(3) TELQV

(4) TELQX

FIGURE 1. READ CYCLE

NOTE:

1. W is high for a Read Cycle.

(14) TWHAX

(16) TWLQZ

(21)

(17) TDVWH

(18) TWHDX

ADDRESS

E

W

Q

D

(10) TAVAX

(11) TELWH

(12) TAVWL

(13) TWLWH

(20) TWLEH

TDVEH

(22) TAVWH

FIGURE 2. WRITE CYCLE I

(19) TWHQX

NOTE:

1. G is low throughout Write Cycle.

HM-65162