| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 8405201QA | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

3-141

80C86

CMOS 16-Bit Microprocessor

Features

∑ Compatible with NMOS 8086

∑ Completely Static CMOS Design

- DC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5MHz (80C86)

- DC . . . . . . . . . . . . . . . . . . . . . . . . . . . .8MHz (80C86-2)

∑ Low Power Operation

- lCCSB . . . . . . . . . . . . . . . . . . . . . . . . . . . . .500

µ

A Max

- ICCOP . . . . . . . . . . . . . . . . . . . . . . . . . 10mA/MHz Typ

∑ 1MByte of Direct Memory Addressing Capability

∑ 24 Operand Addressing Modes

∑ Bit, Byte, Word and Block Move Operations

∑ 8-Bit and 16-Bit Signed/Unsigned Arithmetic

- Binary, or Decimal

- Multiply and Divide

∑ Wide Operating Temperature Range

- C80C86 . . . . . . . . . . . . . . . . . . . . . . . . . . 0

o

C to +70

o

C

- l80C86 . . . . . . . . . . . . . . . . . . . . . . . . . -40

o

C to +85

o

C

- M80C86 . . . . . . . . . . . . . . . . . . . . . . . -55

o

C to +125

o

C

Description

The Intersil 80C86 high performance 16-bit CMOS CPU is

manufactured using a self-aligned silicon gate CMOS pro-

cess (Scaled SAJI IV). Two modes of operation, minimum for

small systems and maximum for larger applications such as

multiprocessing, allow user configuration to achieve the

highest performance level. Full TTL compatibility (with the

exception of CLOCK) and industry standard operation allow

use of existing NMOS 8086 hardware and software designs.

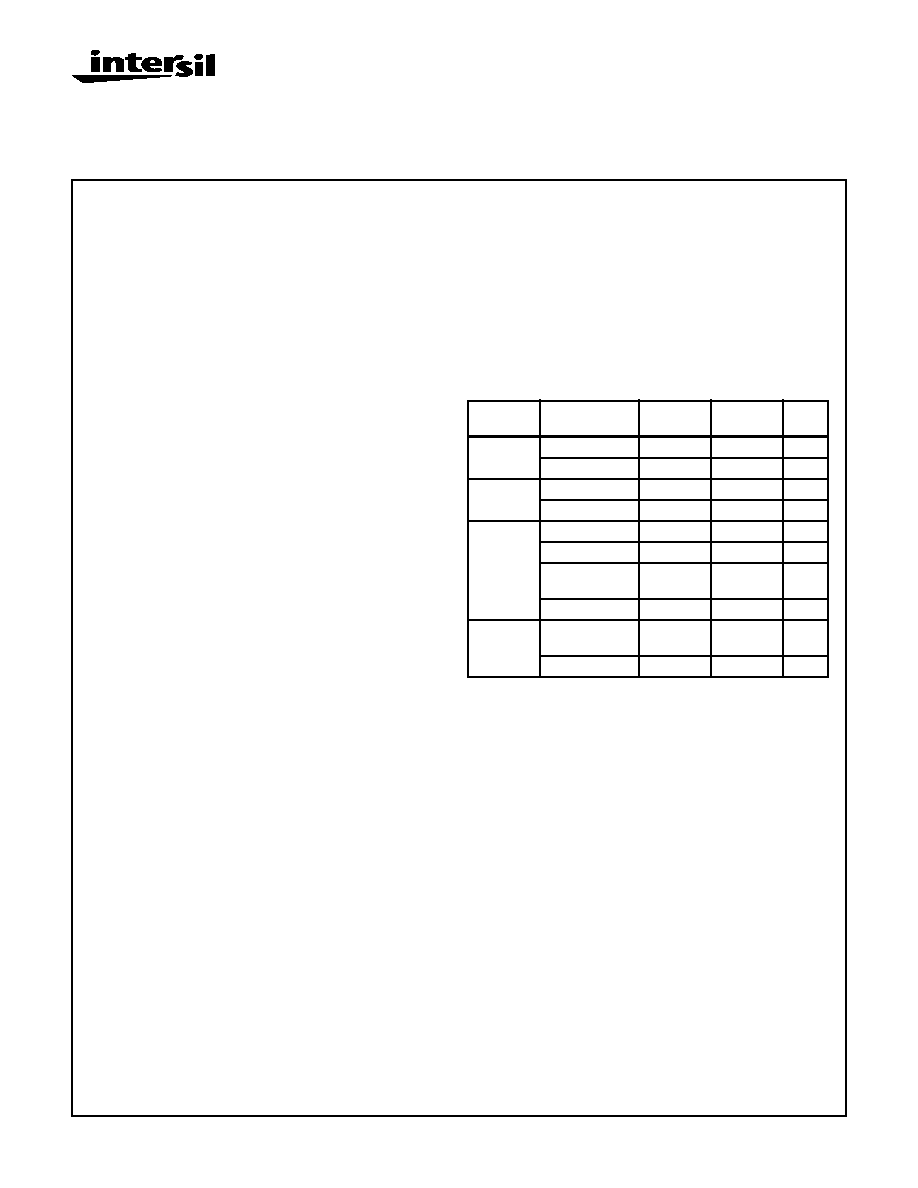

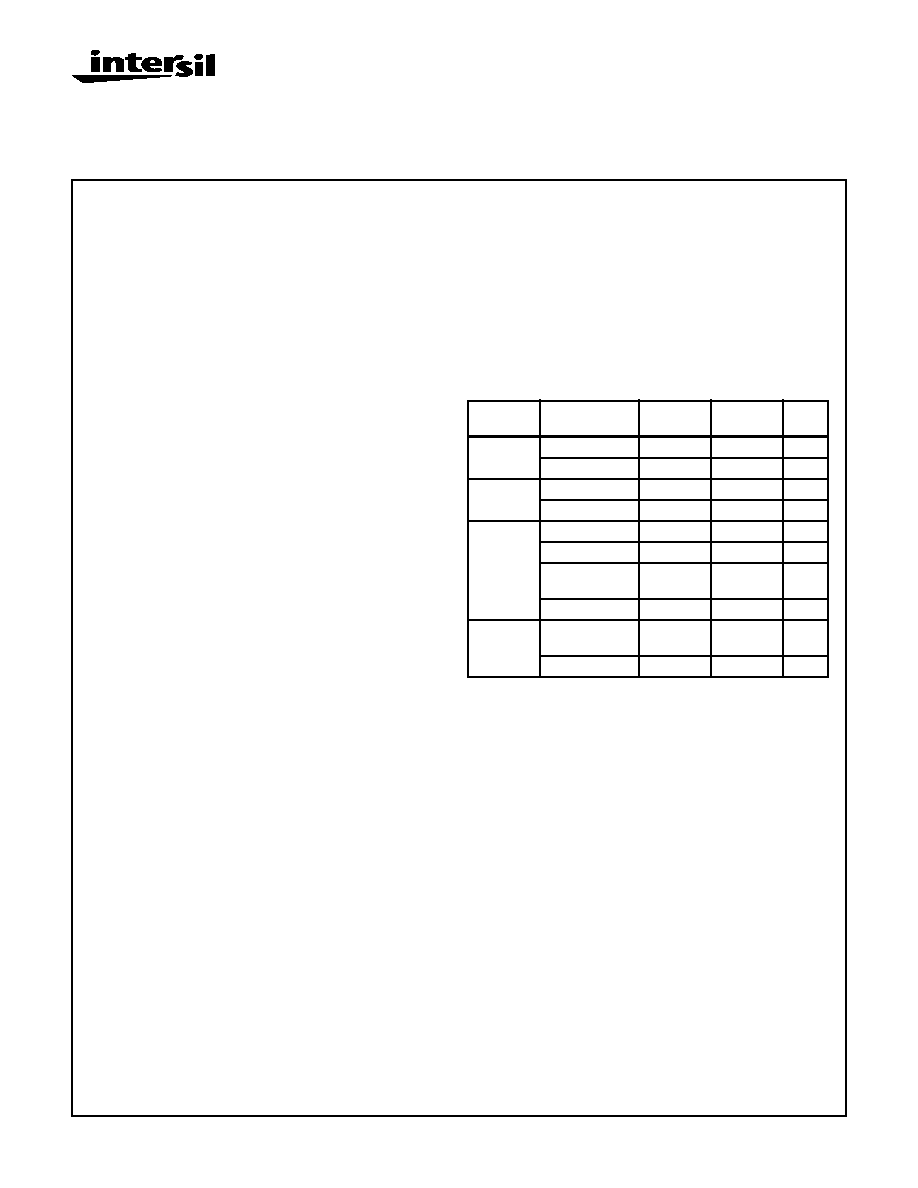

Ordering Information

PACKAGE

TEMP. RANGE

5MHz

8MHz

PKG.

NO.

PDIP

0

o

C to +70

o

C

CP80C86

CP80C86-2 E40.6

-40

o

C to +85

o

C

lP80C86

IP80C86-2

E40.6

PLCC

0

o

C to +70

o

C

CS80C86

CS80C86-2 N44.65

-40

o

C to +85

o

C

lS80C86

IS80C86-2

N44.65

CERDIP

0

o

C to +70

o

C

CD80C86

CD80C86-2 F40.6

-40

o

C to +85

o

C

ID80C86

ID80C86-2

F40.6

-55

o

C to +125

o

C MD80C86/B MD80C86-

2/B

F40.6

SMD#

-55

o

C to +125

o

C 8405201QA 8405202QA F40.6

CLCC

-55

o

C to +125

o

C MR80C86/B MR80C86-

2/B

J44.A

SMD#

-55

o

C to +125

o

C 8405201XA 8405202XA J44.A

March 1997

File Number

2957.1

[ /Title

(80C86

)

/Sub-

ject

(CMO

S 16-

Bit

Micro-

proces-

sor)

/Autho

r ()

/Key-

words

(Inter-

sil

Corpo-

ration,

Inter-

sil

Corpo-

ration,

16 Bit

uP,

micro-

proces-

sor,

8086,

PC)

/Cre-

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

|

Copyright

©

Intersil Corporation 1999

3-142

Pinouts

80C86 (DIP)

TOP VIEW

80C86 (PLCC, CLCC)

TOP VIEW

13

1

2

3

4

5

6

7

8

9

10

11

12

14

15

16

17

18

19

20

GND

AD14

AD13

AD12

AD11

AD10

AD9

AD8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

NMI

INTR

CLK

GND

28

40

39

38

37

36

35

34

33

32

31

30

29

27

26

25

24

23

22

21

V

CC

AD15

A16/S3

A17/S4

A18/S5

A19/S6

BHE/S7

MN/MX

RD

RQ/GT0

RQ/GT1

LOCK

S2

S1

S0

QS0

QS1

TEST

READY

RESET

(INTA)

(ALE)

(DEN)

(DT/R))

(M/IO)

(WR)

(HLDA)

(HOLD)

MAX

(MIN)

14

13

12

11

10

9

8

7

17

16

15

2

5

30

35

39

38

37

36

33

34

32

31

29

4

6

3

1

40

41

42

43

44

28

27

26

25

24

23

22

21

20

19

18

A19/S6

BHE/S7

MN/MX

RD

HOLD

HLDA

WR

M/IO

DT/R

DEN

NC

NC

A19/S6

BHE/S7

MN/MX

RD

RQ/GT0

RQ/GT1

LOCK

S2

S1

S0

AD9

AD8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

AD10

AD10

AD9

AD8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

AD12

AD13

AD14

GND

NC

V

CC

AD15

A16/S3

A17/S4

A18/S5

AD11

AD11

AD12

AD13

AD14

GND

NC

V

CC

AD15

A16/S3

A17/S4

A18/S5

NMI

INTR

CLK

GND

NC

RESET

READ

Y

TEST

QS1

QS0

NC

NC

NMI

INTR

CLK

GND

NC

RESET

READ

Y

TEST

INT

A

ALE

MAX MODE

80C86

MIN MODE

80C86

MAX MODE

80C86

MIN MODE

80C86

80C86

80C86

3-143

Functional Diagram

REGISTER FILE

EXECUTION UNIT

CONTROL AND TIMING

INSTRUCTION

QUEUE

6-BYTE

FLAGS

16-BIT ALU

BUS INTERFACE UNIT

16

4

QS0, QS1

S2, S1, S0

2

4

3

GND

V

CC

CLK

RESET READY

BUS INTERFACE UNIT

RELOCATION

REGISTER FILE

3

A19/S6

A16/S3

INTA, RD, WR

DT/R, DEN, ALE, M/IO

BHE/S7

2

SEGMENT REGISTERS

AND

INSTRUCTION POINTER

(5 WORDS)

DATA POINTER

AND

INDEX REGS

(8 WORDS)

TEST

INTR

NMI

HLDA

HOLD

RQ/GT0, 1

LOCK

MN/MX

3

ES

CS

SS

DS

IP

AH

BH

CH

DH

AL

BL

CL

DL

SP

BP

SI

DI

ARITHMETIC/

LOGIC UNIT

B-BUS

C-BUS

EXECUTION

UNIT

INTERFACE

UNIT

BUS

QUEUE

INSTRUCTION

STREAM BYTE

EXECUTION UNIT

CONTROL SYSTEM

FLAGS

MEMORY INTERFACE

A-BUS

AD15-AD0

80C86

3-144

Pin Description

The following pin function descriptions are for 80C86 systems in either minimum or maximum mode. The "Local Bus" in these description is

the direct multiplexed bus interface connection to the 80C86 (without regard to additional bus buffers).

SYMBOL

PIN

NUMBER

TYPE

DESCRIPTION

AD15-AD0

2-16, 39

I/O

ADDRESS DATA BUS: These lines constitute the time multiplexed memory/lO address (T1) and

data (T2, T3, TW, T4) bus. A0 is analogous to BHE for the lower byte of the data bus, pins D7-

D0. It is LOW during Ti when a byte is to be transferred on the lower portion of the bus in memory

or I/O operations. Eight-bit oriented devices tied to the lower half would normally use A0 to con-

dition chip select functions (See BHE). These lines are active HIGH and are held at high imped-

ance to the last valid logic level during interrupt acknowledge and local bus "hold acknowledge"

or "grant sequence".

A19/S6

A18/S5

A17/S4

A16/S3

35-38

O

ADDRESS/STATUS: During T1, these are the four most significant address lines for memory op-

erations. During I/O operations these lines are LOW. During memory and I/O operations, status

information is available on these lines during T2, T3, TW, T4. S6 is always LOW. The status of

the interrupt enable FLAG bit (S5) is updated at the beginning of each clock cycle. S4 and S3

are encoded as shown.

This information indicates which segment register is presently being used for data accessing.

These lines are held at high impedance to the last valid logic level during local bus "hold ac-

knowledge" or "grant sequence".

BHE/S7

34

O

BUS HIGH ENABLE/STATUS: During T1 the bus high enable signal (BHE) should be used to

enable data onto the most significant half of the data bus, pins D15-D8. Eight bit oriented devices

tied to the upper half of the bus would normally use BHE to condition chip select functions. BHE

is LOW during T1 for read, write, and interrupt acknowledge cycles when a byte is to be trans-

ferred on the high portion of the bus. The S7 status information is available during T2, T3 and

T4. The signal is active LOW, and is held at high impedance to the last valid logic level during

interrupt acknowledge and local bus "hold acknowledge" or "grant sequence", it is LOW during

T1 for the first interrupt acknowledge cycle.

RD

32

O

READ: Read strobe indicates that the processor is performing a memory or I/O read cycle, de-

pending on the state of the M/IO or S2 pin. This signal is used to read devices which reside on

the 80C86 local bus. RD is active LOW during T2, T3 and TW of any read cycle, and is guaran-

teed to remain HIGH in T2 until the 80C86 local bus has floated.

This line is held at a high impedance logic one state during "hold acknowledge" or "grand se-

quence".

READY

22

I

READY: is the acknowledgment from the addressed memory or I/O device that will complete the

data transfer. The RDY signal from memory or I/O is synchronized by the 82C84A Clock Gener-

ator to form READY. This signal is active HIGH. The 80C86 READY input is not synchronized.

Correct operation is not guaranteed if the Setup and Hold Times are not met.

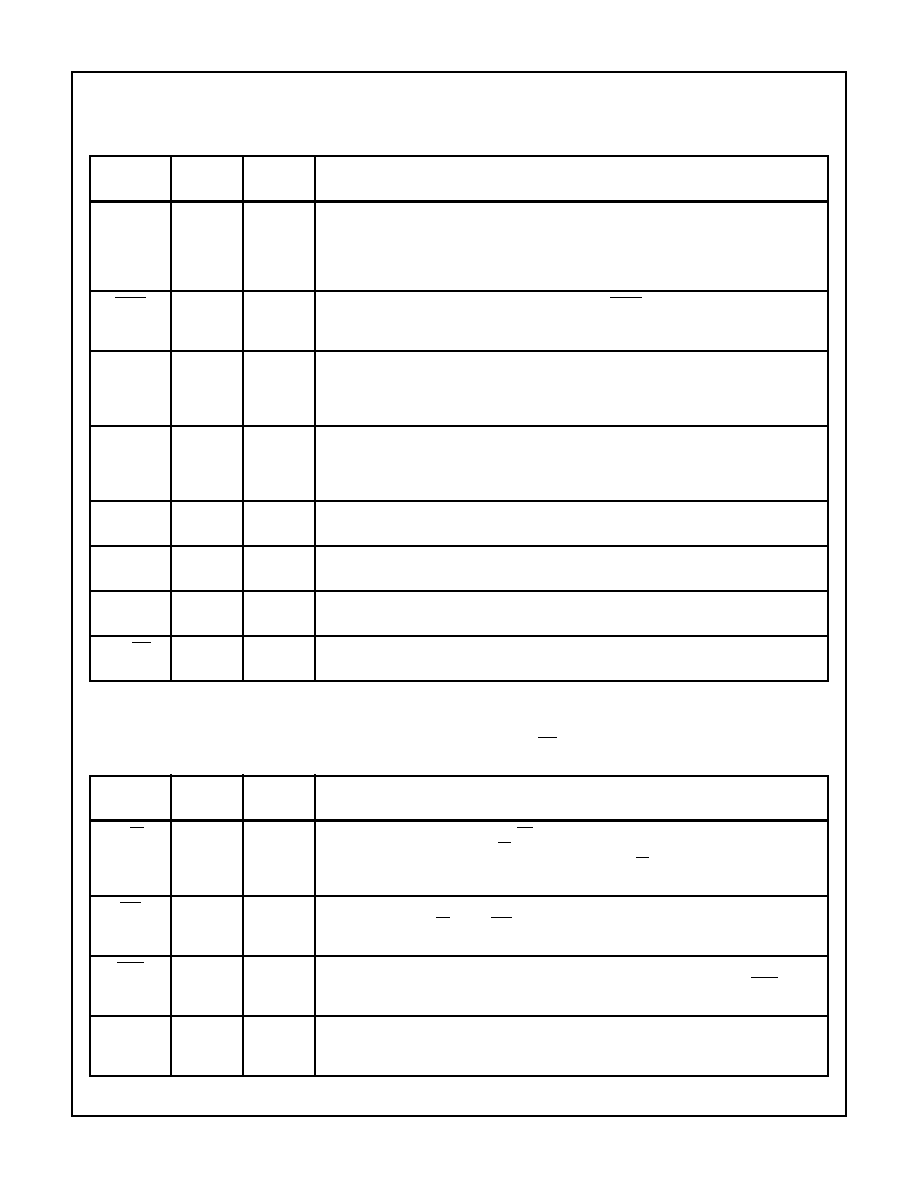

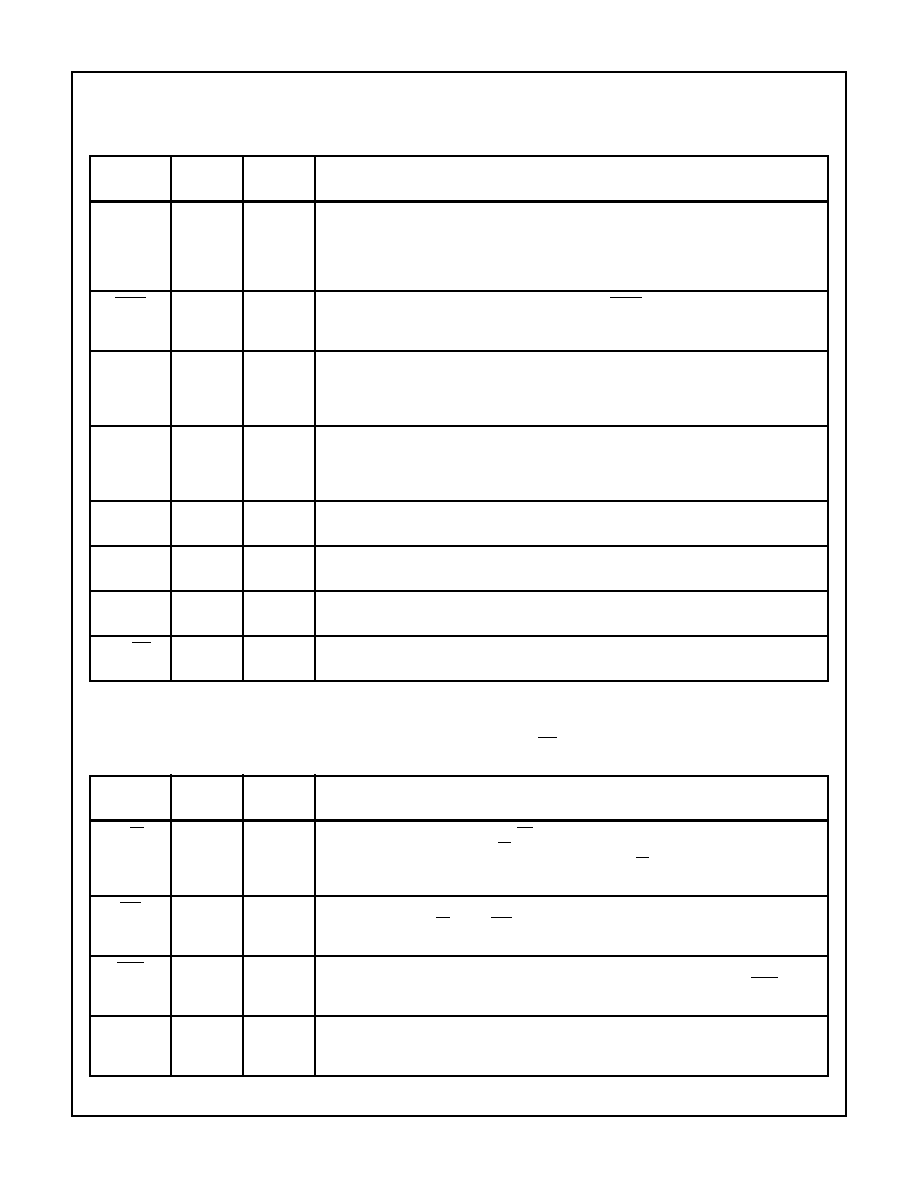

S4

S3

CHARACTERISTICS

0

0

Alternate Data

0

1

Stack

1

0

Code or None

1

1

Data

BHE

A0

CHARACTERISTICS

0

0

Whole Word

0

1

Upper Byte From/to Odd Address

1

0

Lower Byte From/to Even address

1

1

None

80C86

3-145

INTR

18

I

INTERRUPT REQUEST: is a level triggered input which is sampled during the last clock cycle

of each instruction to determine if the processor should enter into an interrupt acknowledge op-

eration. A subroutine is vectored to via an interrupt vector lookup table located in system mem-

ory. It can be internally masked by software resetting the interrupt enable bit.

lNTR is internally synchronized. This signal is active HIGH.

TEST

23

I

TEST: input is examined by the "Wait" instruction. If the TEST input is LOW execution continues,

otherwise the processor waits in an "Idle" state. This input is synchronized internally during each

clock cycle on the leading edge of CLK.

NMI

17

I

NON-MASKABLE INTERRUPT: is an edge triggered input which causes a type 2 interrupt. A

subroutine is vectored to via an interrupt vector lookup table located in system memory. NMI is

not maskable internally by software. A transition from LOW to HIGH initiates the interrupt at the

end of the current instruction. This input is internally synchronized.

RESET

21

I

RESET: causes the processor to immediately terminate its present activity. The signal must tran-

sition LOW to HIGH and remain active HIGH for at least four clock cycles. It restarts execution,

as described in the Instruction Set description, when RESET returns LOW. RESET is internally

synchronized.

CLK

19

I

CLOCK: provides the basic timing for the processor and bus controller. It is asymmetric with a

33% duty cycle to provide optimized internal timing.

VCC

40

VCC: +5V power supply pin. A 0.1

µ

F capacitor between pins 20 and 40 is recommended for de-

coupling.

GND

1, 20

GND: Ground. Note: both must be connected. A 0.1

µ

F capacitor between pins 1 and 20 is rec-

ommended for decoupling.

MN/MX

33

I

MINIMUM/MAXIMUM: Indicates what mode the processor is to operate in. The two modes are

discussed in the following sections.

Minimum Mode System

The following pin function descriptions are for the 80C86 in minimum mode (i.e., MN/MX = V

CC

). Only the pin functions which are unique to

minimum mode are described; all other pin functions are as described below.

SYMBOL

PIN

NUMBER

TYPE

DESCRIPTION

M/IO

28

O

STATUS LINE: logically equivalent to S2 in the maximum mode. It is used to distinguish a mem-

ory access from an I/O access. M/lO becomes valid in the T4 preceding a bus cycle and remains

valid until the final T4 of the cycle (M = HIGH, I/O = LOW). M/lO is held to a high impedance logic

one during local bus "hold acknowledge".

WR

29

O

WRITE: indicates that the processor is performing a write memory or write I/O cycle, depending

on the state of the M/IO signal. WR is active for T2, T3 and TW of any write cycle. It is active

LOW, and is held to high impedance logic one during local bus "hold acknowledge".

INTA

24

O

INTERRUPT ACKNOWLEDGE: is used as a read strobe for interrupt acknowledge cycles. It is

active LOW during T2, T3 and TW of each interrupt acknowledge cycle. Note that INTA is never

floated.

ALE

25

O

ADDRESS LATCH ENABLE: is provided by the processor to latch the address into the

82C82/82C83 address latch. It is a HIGH pulse active during clock LOW of T1 of any bus cycle.

Note that ALE is never floated.

Pin Description

(Continued)

The following pin function descriptions are for 80C86 systems in either minimum or maximum mode. The "Local Bus" in these description is

the direct multiplexed bus interface connection to the 80C86 (without regard to additional bus buffers).

SYMBOL

PIN

NUMBER

TYPE

DESCRIPTION

80C86