| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 84065023A | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

4-1

March 1997

82C54

CMOS Programmable Interval Timer

Features

∑ 8MHz to 12MHz Clock Input Frequency

∑ Compatible with NMOS 8254

- Enhanced Version of NMOS 8253

∑ Three Independent 16-Bit Counters

∑ Six Programmable Counter Modes

∑ Status Read Back Command

∑ Binary or BCD Counting

∑ Fully TTL Compatible

∑ Single 5V Power Supply

∑ Low Power

- ICCSB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

µ

A

- ICCOP . . . . . . . . . . . . . . . . . . . . . . . . . . 10mA at 8MHz

∑ Operating Temperature Ranges

- C82C54 . . . . . . . . . . . . . . . . . . . . . . . . . .0

o

C to +70

o

C

- I82C54 . . . . . . . . . . . . . . . . . . . . . . . . . -40

o

C to +85

o

C

- M82C54 . . . . . . . . . . . . . . . . . . . . . . . -55

o

C to +125

o

C

Description

The Intersil 82C54 is a high performance CMOS Program-

mable Interval Timer manufactured using an advanced 2

micron CMOS process.

The 82C54 has three independently programmable and

functional 16-bit counters, each capable of handling clock

input frequencies of up to 8MHz (82C54) or 10MHz

(82C54-10) or 12MHz (82C54-12).

The high speed and industry standard configuration of the

82C54 make it compatible with the Intersil 80C86, 80C88,

and 80C286 CMOS microprocessors along with many other

industry standard processors. Six programmable timer

modes allow the 82C54 to be used as an event counter,

elapsed time indicator, programmable one-shot, and many

other applications. Static CMOS circuit design insures low

power operation.

The Intersil advanced CMOS process results in a significant

reduction in power with performance equal to or greater than

existing equivalent products.

Pinouts

82C54 (PDIP, CERDIP, SOIC)

TOP VIEW

82C54 (PLCC/CLCC)

TOP VIEW

1

2

3

4

5

6

7

8

9

10

11

12

16

17

18

19

20

21

22

23

24

15

14

13

D7

D6

D5

D4

D3

D2

D1

D0

CLK 0

OUT 0

GATE 0

GND

VCC

RD

CS

A1

A0

OUT 2

CLK 1

GATE 1

OUT 1

WR

CLK 2

GATE 2

GND

NC

OUT 1

GA

TE 1

CLK 1

OUT 0

GA

TE 0

D7

NC

VCC

WR

RD

D5

D6

CS

A1

A0

CLK2

NC

GATE 2

OUT 2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

D3

D2

D1

D0

D4

NC

CLK 0

File Number

2970.1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

|

Copyright

©

Intersil Corporation 1999

4-2

Functional Diagram

Ordering Information

PART NUMBERS

TEMPERATURE

RANGE

PACKAGE

PKG. NO.

8MHz

10MHz

12MHz

CP82C54

CP82C54-10

CP82C54-12

0

o

C to +70

o

C

24 Lead PDIP

E24.6

IP82C54

IP82C54-10

IP82C54-12

-40

o

C to +85

o

C

24 Lead PDIP

E24.6

CS82C54

CS82C54-10

CS82C54-12

0

o

C to +70

o

C

28 Lead PLCC

N28.45

IS82C54

IS82C54-10

IS82C54-12

-40

o

C to +85

o

C

28 Lead PLCC

N28.45

CD82C54

CD82C54-10

CD82C54-12

0

o

C to +70

o

C

24 Lead CERDIP

F24.6

ID82C54

ID82C54-10

ID82C54-12

-40

o

C to +85

o

C

24 Lead CERDIP

F24.6

MD82C54/B

MD82C54-10/B

MD82C54-12/B

-55

o

C to +125

o

C

24 Lead CERDIP

F24.6

MR82C54/B

MR82C54-10/B

MR82C54-12/B

-55

o

C to +125

o

C

28 Lead CLCC

J28.A

SMD # 8406501JA

-

8406502JA

-55

o

C to +125

o

C

24 Lead CERDIP

F24.6

SMD# 84065013A

-

84065023A

-55

o

C to +125

o

C

28 Lead CLCC

J28.A

CM82C54

CM82C54-10

CM82C54-12

0

o

C to +70

o

C

24 Lead SOIC

M24.3

Pin Description

SYMBOL

DIP PIN

NUMBER

TYPE

DEFINITION

D7 - D0

1 - 8

I/O

DATA: Bi-directional three-state data bus lines, connected to system data bus.

CLK 0

9

I

CLOCK 0: Clock input of Counter 0.

OUT 0

10

O

OUT 0: Output of Counter 0.

GATE 0

11

I

GATE 0: Gate input of Counter 0.

GND

12

GROUND: Power supply connection.

OUT 1

13

O

OUT 1: Output of Counter 1.

GATE 1

14

I

GATE 1: Gate input of Counter 1.

CLK 1

15

I

CLOCK 1: Clock input of Counter 1.

GATE 2

16

I

GATE 2: Gate input of Counter 2.

OUT 2

17

O

OUT 2: Output of Counter 2.

CONTROL

WORD

REGISTER

READ/

WRITE

LOGIC

DATA/

BUS

BUFFER

COUNTER

2

COUNTER

1

COUNTER

0

INTERNAL B

U

S

INTERNAL BUS

CONTROL

LOGIC

CONTROL

WORD

REGISTER

STATUS

LATCH

STATUS

REGISTER

CLK n

GATE n

OUT n

OUT 2

GATE 2

CLK 2

OUT 1

GATE 1

CLK 1

OUT 0

GATE 0

CLK 0

WR

RD

D

7

- D

0

A

0

A

1

CS

OL

M

OL

L

CE

CR

M

CR

L

COUNTER INTERNAL BLOCK DIAGRAM

8

82C54

4-3

Functional Description

General

The 82C54 is a programmable interval timer/counter

designed for use with microcomputer systems. It is a general

purpose, multi-timing element that can be treated as an

array of I/O ports in the system software.

The 82C54 solves one of the most common problems in any

microcomputer system, the generation of accurate time

delays under software control. Instead of setting up timing

loops in software, the programmer configures the 82C54 to

match his requirements and programs one of the counters

for the desired delay. After the desired delay, the 82C54 will

interrupt the CPU. Software overhead is minimal and vari-

able length delays can easily be accommodated.

Some of the other computer/timer functions common to micro-

computers which can be implemented with the 82C54 are:

∑ Real time clock

∑ Event counter

∑ Digital one-shot

∑ Programmable rate generator

∑ Square wave generator

∑ Binary rate multiplier

∑ Complex waveform generator

∑ Complex motor controller

Data Bus Buffer

This three-state, bi-directional, 8-bit buffer is used to inter-

face the 82C54 to the system bus (see Figure 1).

Read/Write Logic

The Read/Write Logic accepts inputs from the system bus and

generates control signals for the other functional blocks of the

82C54. A1 and A0 select one of the three counters or the Con-

trol Word Register to be read from/written into. A "low" on the

RD input tells the 82C54 that the CPU is reading one of the

counters. A "low" on the WR input tells the 82C54 that the CPU

is writing either a Control Word or an initial count. Both RD and

WR are qualified by CS; RD and WR are ignored unless the

82C54 has been selected by holding CS low.

CLK 2

18

I

CLOCK 2: Clock input of Counter 2.

A0, A1

19 - 20

I

ADDRESS: Select inputs for one of the three counters or Control Word Register for read/write

operations. Normally connected to the system address bus.

CS

21

I

CHIP SELECT: A low on this input enables the 82C54 to respond to RD and WR signals. RD and

WR are ignored otherwise.

RD

22

I

READ: This input is low during CPU read operations.

WR

23

I

WRITE: This input is low during CPU write operations.

V

CC

24

V

CC

: The +5V power supply pin. A 0.1

µ

F capacitor between pins VCC and GND is recommended

for decoupling.

Pin Description

(Continued)

SYMBOL

DIP PIN

NUMBER

TYPE

DEFINITION

A1

A0

SELECTS

0

0

Counter 0

0

1

Counter 1

1

0

Counter 2

1

1

Control Word Register

CONTROL

WORD

REGISTER

COUNTER

2

COUNTER

1

COUNTER

0

INTERNAL B

U

S

OUT 2

GATE 2

CLK 2

OUT 1

GATE 1

CLK 1

OUT 0

GATE 0

CLK 0

WR

RD

D

7

- D

0

A

0

A

1

CS

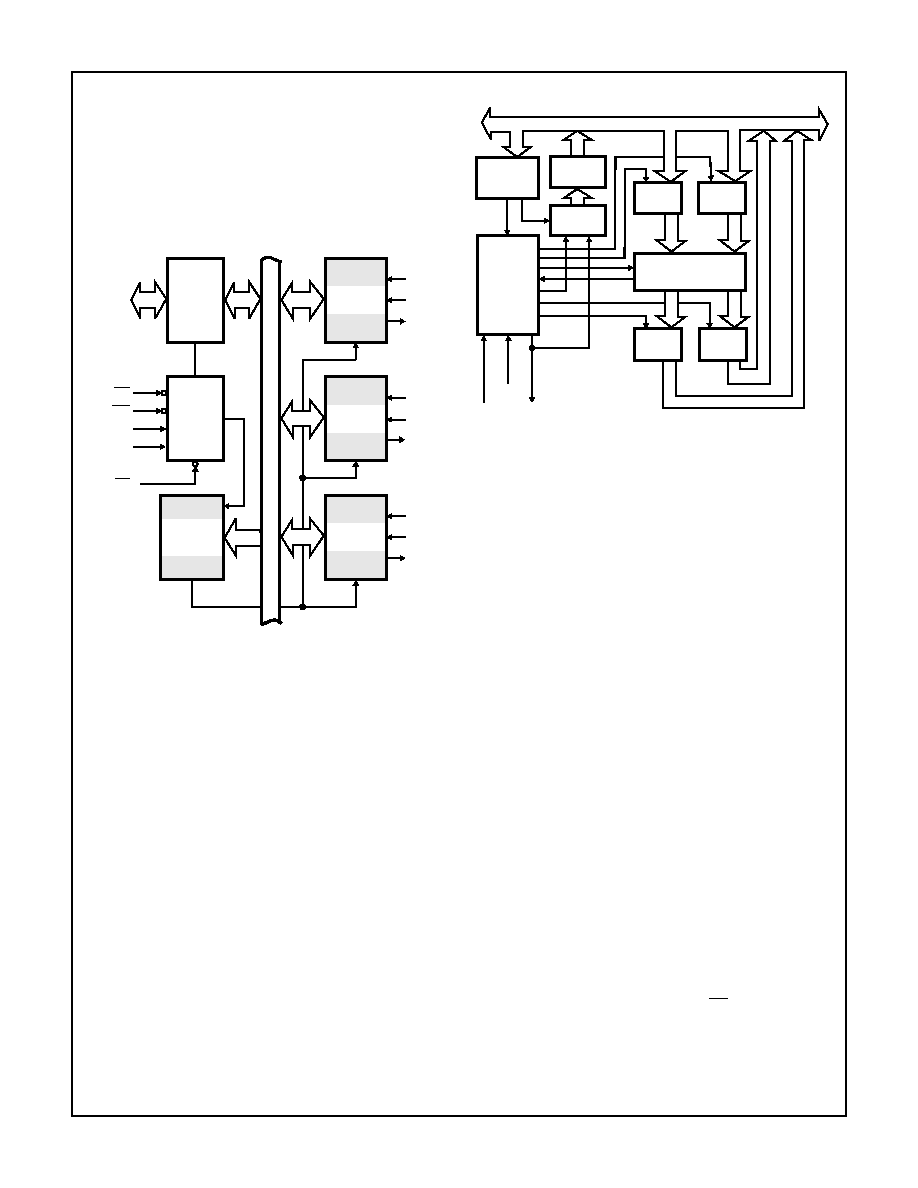

FIGURE 1. DATA BUS BUFFER AND READ/WRITE LOGIC

FUNCTIONS

8

DATA/

BUS

BUFFER

READ/

WRITE

LOGIC

82C54

4-4

Control Word Register

The Control Word Register (Figure 2) is selected by the

Read/Write Logic when A1, A0 = 11. If the CPU then does a

write operation to the 82C54, the data is stored in the Con-

trol Word Register and is interpreted as a Control Word used

to define the Counter operation.

The Control Word Register can only be written to; status

information is available with the Read-Back Command.

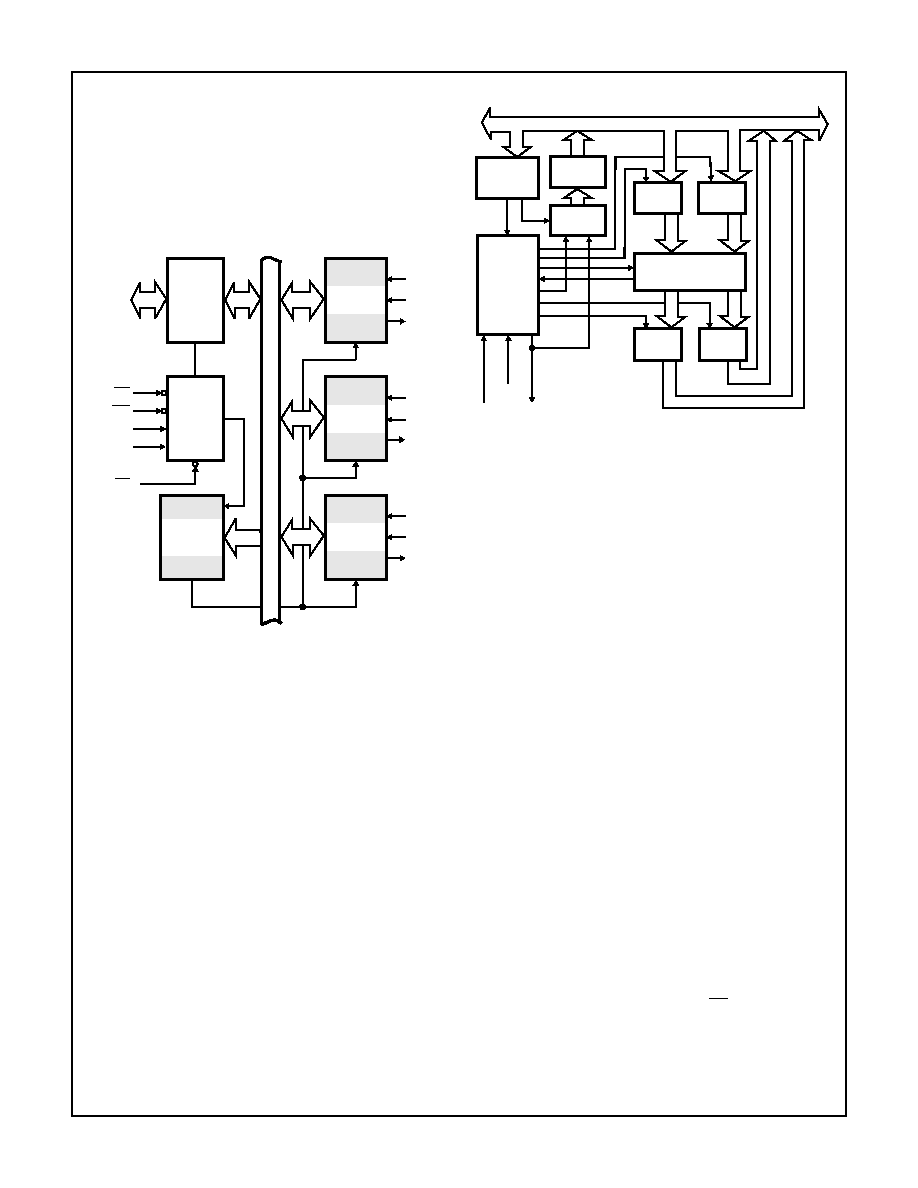

Counter 0, Counter 1, Counter 2

These three functional blocks are identical in operation, so

only a single Counter will be described. The internal block

diagram of a signal counter is shown in Figure 3. The

counters are fully independent. Each Counter may operate

in a different Mode.

The Control Word Register is shown in the figure; it is not

part of the Counter itself, but its contents determine how the

Counter operates.

The status register, shown in the figure, when latched, con-

tains the current contents of the Control Word Register and

status of the output and null count flag. (See detailed expla-

nation of the Read-Back command.)

The actual counter is labeled CE (for Counting Element). It is

a 16-bit presettable synchronous down counter.

OLM and OLL are two 8-bit latches. OL stands for "Output

Latch"; the subscripts M and L for "Most significant byte" and

"Least significant byte", respectively. Both are normally referred

to as one unit and called just OL. These latches normally "fol-

low" the CE, but if a suitable Counter Latch Command is sent to

the 82C54, the latches "latch" the present count until read by

the CPU and then return to "following" the CE. One latch at a

time is enabled by the counter's Control Logic to drive the inter-

nal bus. This is how the 16-bit Counter communicates over the

8-bit internal bus. Note that the CE itself cannot be read; when-

ever you read the count, it is the OL that is being read.

Similarly, there are two 8-bit registers called CRM and CRL (for

"Count Register"). Both are normally referred to as one unit and

called just CR. When a new count is written to the Counter, the

count is stored in the CR and later transferred to the CE. The

Control Logic allows one register at a time to be loaded from

the internal bus. Both bytes are transferred to the CE simulta-

neously. CRM and CRL are cleared when the Counter is pro-

grammed for one byte counts (either most significant byte only

or least significant byte only) the other byte will be zero. Note

that the CE cannot be written into; whenever a count is written,

it is written into the CR.

The Control Logic is also shown in the diagram. CLK n,

GATE n, and OUT n are all connected to the outside world

through the Control Logic.

82C54 System Interface

The 82C54 is treated by the system software as an array of

peripheral I/O ports; three are counters and the fourth is a

control register for MODE programming.

Basically, the select inputs A0, A1 connect to the A0, A1

address bus signals of the CPU. The CS can be derived

directly from the address bus using a linear select method or

it can be connected to the output of a decoder.

READ/

WRITE

LOGIC

DATA/

BUS

BUFFER

INTERNAL B

U

S

OUT 2

GATE 2

CLK 2

OUT 1

GATE 1

CLK 1

OUT 0

GATE 0

CLK 0

WR

RD

D

7

- D

0

A

0

A

1

CS

FIGURE 2. CONTROL WORD REGISTER AND COUNTER

FUNCTIONS

8

CONTROL

WORD

REGISTER

COUNTER

2

COUNTER

1

COUNTER

0

INTERNAL BUS

CONTROL

LOGIC

CONTROL

WORD

REGISTER

STATUS

LATCH

STATUS

REGISTER

CLK n

GATE n

OUT n

OL

M

OL

L

CE

CR

M

CR

L

FIGURE 3. COUNTER INTERNAL BLOCK DIAGRAM

82C54

4-5

Operational Description

General

After power-up, the state of the 82C54 is undefined. The

Mode, count value, and output of all Counters are undefined.

How each Counter operates is determined when it is pro-

grammed. Each Counter must be programmed before it can

be used. Unused counters need not be programmed.

Programming the 82C54

Counters are programmed by writing a Control Word and

then an initial count.

All Control Words are written into the Control Word Register,

which is selected when A1, A0 = 11. The Control Word spec-

ifies which Counter is being programmed.

By contrast, initial counts are written into the Counters, not

the Control Word Register. The A1, A0 inputs are used to

select the Counter to be written into. The format of the initial

count is determined by the Control Word used.

FIGURE 4. 82C54 SYSTEM INTERFACE

Write Operations

The programming procedure for the 82C54 is very flexible.

Only two conventions need to be remembered:

1. For Each Counter, the Control Word must be written

before the initial count is written.

2. The initial count must follow the count format specified in the

Control Word (least significant byte only, most significant byte

only, or least significant byte and then most significant byte).

Since the Control Word Register and the three Counters have

separate addresses (selected by the A1, A0 inputs), and each

Control Word specifies the Counter it applies to (SC0, SC1 bits),

no special instruction sequence is required. Any programming

sequence that follows the conventions above is acceptable.

Control Word Format

A1, A0 = 11; CS = 0; RD = 1; WR = 0

D7

D6

D5

D4

D3

D2

D1

D0

SC1

SC0

RW1

RW0

M2

M1

M0

BCD

ADDRESS BUS (16)

CONTROL BUS

DATA BUS (8)

I/OR I/OW

WR

RD

CS

A0

A1

A1

A0

8

COUNTER

0

OUT GATE CLK

COUNTER

1

COUNTER

2

OUT GATE CLK

OUT GATE CLK

D0 - D7

82C54

SC - Select Counter

SC1

SC0

0

0

Select Counter 0

0

1

Select Counter 1

1

0

Select Counter 2

1

1

Read-Back Command (See Read Operations)

RW - Read/Write

RW1 RW0

0

0

Counter Latch Command (See Read Operations)

0

1

Read/Write least significant byte only.

1

0

Read/Write most significant byte only.

1

1

Read/Write least significant byte first, then most

significant byte.

M - Mode

M2

M1

M0

0

0

0

Mode 0

0

0

1

Mode 1

X

1

0

Mode 2

X

1

1

Mode 3

1

0

0

Mode 4

1

0

1

Mode 5

BCD - Binary Coded Decimal

0

Binary Counter 16-bit

1

Binary Coded Decimal (BCD) Counter (4 Decades)

NOTE: Don't Care bits (X) should be 0 to insure compatibility with

future products.

Possible Programming Sequence

A1

A0

Control Word - Counter 0

1

1

LSB of Count - Counter 0

0

0

MSB of Count - Counter 0

0

0

Control Word - Counter 1

1

1

LSB of Count - Counter 1

0

1

MSB of Count - Counter 1

0

1

Control Word - Counter 2

1

1

LSB of Count - Counter 2

1

0

MSB of Count - Counter 2

1

0

Possible Programming Sequence

A1

A0

Control Word - Counter 0

1

1

Control Word - Counter 1

1

1

Control Word - Counter 2

1

1

LSB of Count - Counter 2

1

0

82C54