| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CA3280AE | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

1

CA3280, CA3280A

Dual, 9MHz, Operational

Transconductance Amplifier (OTA)

The CA3280 and CA3280A types consist of two variable

operational amplifiers that are designed to substantially reduce

the initial input offset voltage and the offset voltage variation

with respect to changes in programming current. This design

results in reduced "AGC thump," an objectionable characteristic

of many AGC systems. Interdigitation, or crosscoupling, of

critical portions of the circuit reduces the amplifier dependence

upon thermal and processing variables.

The CA3280 has all the generic characteristics of an

operational voltage amplifier except that the forward transfer

characteristics is best described by transconductance rather

than voltage gain, and the output is current, not voltage. The

magnitude of the output current is equal to the product of

transconductance and the input voltage. This type of

operational transconductance amplifier was first introduced in

1969, and it has since gained wide acceptance as a gateable,

gain controlled building block for instrumentation and audio

applications, such as linearization of transducer outputs,

standardization of widely changing signals for data processing,

multiplexing, instrumentation amplifiers operating from the

nanopower range to high current and high speed comparators.

For additional application information on this device and on

OTAs in general, please refer to Application Notes: AN6818,

AN6668, and AN6077.

Pinout

CA3280

(PDIP, CERDIP)

TOP VIEW

Features

∑ Low Initial Input Offset Voltage: 500

µ

V (Max) (CA3280A)

∑ Low Offset Voltage Change vs I

ABC

: <500

µ

V (Typ)

for All Types

∑ Low Offset Voltage Drift: 5

µ

V/

o

C (Max) (CA3280A)

∑ Excellent Matching of the Two Amplifiers for All

Characteristics

∑ Internal Current-Driven Linearizing Diodes Reduce the

External Input Current to an Offset Component

∑ Flexible Supply Voltage Range. . . . . . . . . . .

±

2V to

±

15V

Applications

∑ Voltage Controlled Amplifiers

∑ Voltage Controlled Oscillators

∑ Multipliers

∑ Demodulators

∑ Sample and Hold

∑ Instrumentation Amplifiers

∑ Function Generators

∑ Triangle Wave-to-Sine Wave Converters

∑ Comparators

∑ Audio Preamplifier

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

I

D

, A1

EMITTER, A1

I

ABC

, A1

V-

NC

I

ABC

, A2

I

D

, A2

EMITTER, A2

+IN, A1

V+, A1

OUT, A1

OUT, A2

V+, A2

-IN, A2

+IN, A2

-IN, A1

-

+

A1

-

+

A2

Ordering Information

PART NUMBER

TEMP.

RANGE (

o

C)

PACKAGE

PKG.

NO.

CA3280AE

-55 to 125

16 Ld PDIP

E16.3

CA3280E

0 to 70

16 Ld PDIP

E16.3

CA3280AF3

-55 to 125

16 Ld CERDIP

F16.3

Data Sheet

September 1998

File Number

1174.4

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143

|

Copyright

©

Intersil Corporation 1999

2

.

Functional Diagram

4

14

2

3

1

16

15

13

-

+

10

9

8

6

12

7

11

2K

2K

1/2 CA3280

CA3280, CA3280A

3

Absolute Maximum Ratings

Thermal Information

Supply Voltage (Between V+ and V-) . . . . . . . . . . . . . . . . . . . . +36V

Differential Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5V

Input Voltage Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V+ to V-

Input Current at I

D

= 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

µ

A

Amplifier Bias Current (I

ABC

) . . . . . . . . . . . . . . . . . . . . . . . . . . 10mA

Output Short Circuit Duration (Note 1). . . . . . . . . . . . . . . . Indefinite

Linearizing Diode Bias Current, I

D

. . . . . . . . . . . . . . . . . . . . . . . 5mA

Peak Input Current with Linearizing Diode. . . . . . . . . . . . . . . . . .

±

I

D

Operating Conditions

Temperature Range

CA3280 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0

o

C to 70

o

C

CA3280A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -55

o

C to 125

o

C

Supply Voltage Range (Typ) . . . . . . . . . . . . . . . . . . . . .

±

2V to

±

15V

Thermal Resistance (Typical, Note 2)

JA

(

o

C/W)

JC

(

o

C/W)

CERDIP Package . . . . . . . . . . . . . . . . .

65

16

PDIP Package . . . . . . . . . . . . . . . . . . .

100

N/A

Maximum Junction Temperature (CERDIP Package). . . . . . . . .175

o

C

Maximum Junction Temperature (Plastic Package) . . . . . . . .150

o

C

Maximum Storage Temperature Range . . . . . . . . . . -65

o

C to 150

o

C

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . 300

o

C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

1. Short circuit may be applied to ground or to either supply.

2.

JA

is measured with the component mounted on an evaluation PC board in free air.

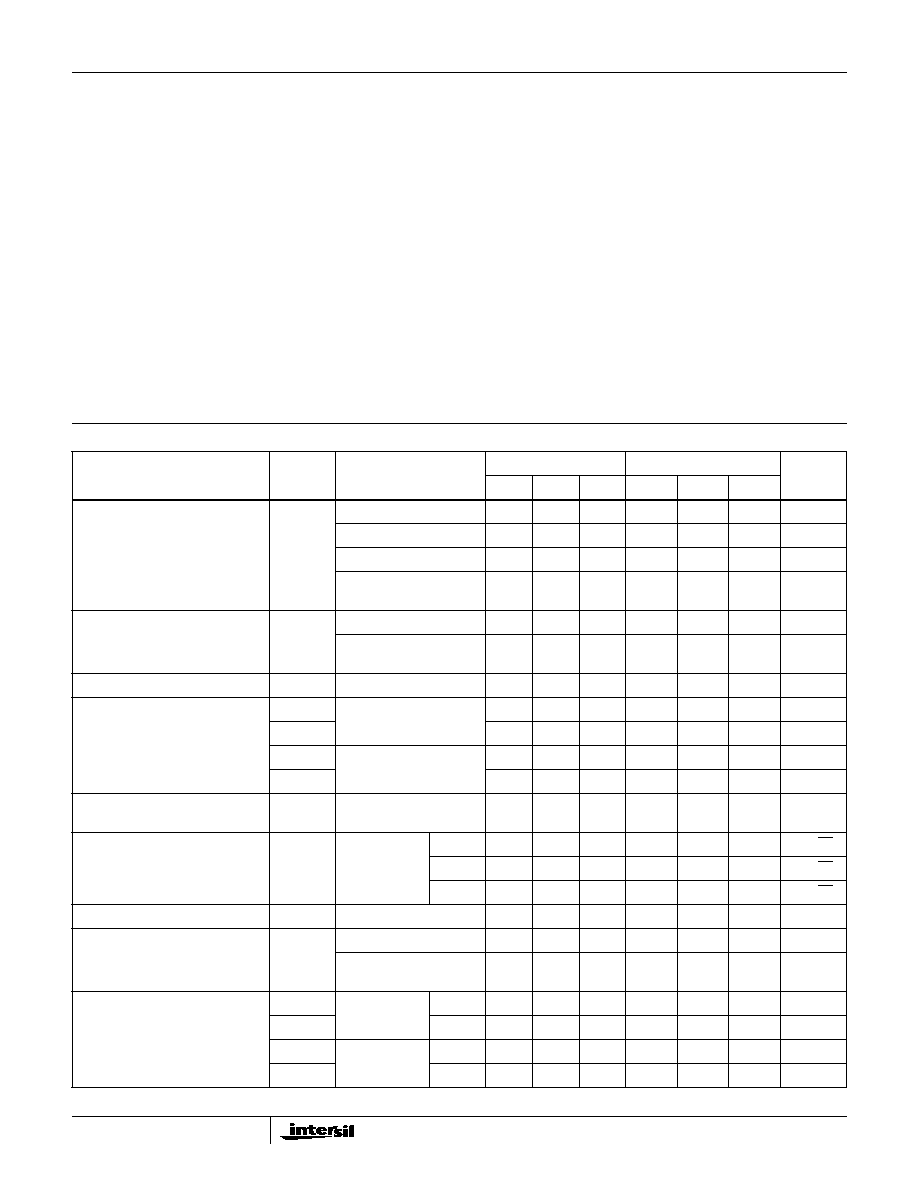

Electrical Specifications

For Equipment Design, at T

A

= 25

o

C, V

SUPPLY

=

±

15V, Unless Otherwise Specified

PARAMETER

SYMBOL

TEST CONDITIONS

CA3280

CA3280A

UNITS

MIN

TYP

MAX

MIN

TYP

MAX

Input Offset Voltage

V

IO

I

ABC

= 1mA

-

-

3

-

-

0.5

mV

I

ABC

= 100

µ

A

-

0.7

3

-

0.25

0.5

mV

I

ABC

= 10

µ

A

-

-

3

-

-

0.5

mV

I

ABC

= 1mA to 10

µ

A,

T

A

= Full Temp. Range

-

0.8

4

-

0.8

1.5

mV

Input Offset Voltage Drift

|

V

IO

|

I

ABC

= 1

µ

A to 1mA

-

0.5

1

-

0.5

1

mV

I

ABC

= 100

µ

A, T

A

= Full

Temperature Range

-

5

-

-

3

5

µ

V/

o

C

Amplifier Bias Voltage

V

ABC

I

ABC

= 100

µ

A

-

1.2

-

-

1.2

-

V

Peak Output Voltage

V

OM

+

I

ABC

= 500mA

12

13.7

-

12.5

13.7

-

V

V

OM

-

12

-14.3

-

-13.3

-14.3

-

V

V

OM

+

I

ABC

= 5

µ

A

12

13.9

-

12.5

13.9

-

V

V

OM

-

12

-14.5

-

-13.5

-14.5

-

V

Common Mode Input Voltage

Range

V

ICR

I

ABC

= 100

µ

A

-13

-

13

-13

-

13

V

Noise Voltage

e

N

I

ABC

= 500

µ

A

10Hz

-

20

-

-

20

-

nV/

Hz

1kHz

-

8

-

-

8

-

nV/

Hz

10kHz

-

7

-

-

7

-

nV/

Hz

Input Offset Current

I

IO

I

ABC

= 500

µ

A

-Z

0.3

0.7

-

0.3

0.7

µ

A

Input Bias Current

I

IB

I

ABC

= 500

µ

A

-

1.8

5

-

1.8

5

µ

A

I

ABC

= 500

µ

A, T

A

= Full

Temperature Range

-

3

8

-

3

8

µ

A

Peak Output Current

I

OM

+

I

ABC

= 500

µ

A

Source

350

410

650

350

410

650

µ

A

I

OM

-

Sink

-350

-410

-650

-350

-410

-650

µ

A

I

OM

+

I

ABC

= 5

µ

A

Source

3

4.1

7

3

4.1

7

µ

A

I

OM

-

Sink

-3

-4.1

-7

-3

-4.1

-7

µ

A

CA3280, CA3280A

4

Peak Output Current Sink and

Source

I

OM

-,

I

OM

+

I

ABC

= 500

µ

A, T

A

= Full

Temperature Range

350

450

550

350

450

550

µ

A

Linearization Diodes

I

D

= 100

µ

A

-

10

-

-

10

-

µ

A

Offset Current

I

D

= 10

µ

A

-

0.5

1

-

0.5

1

µ

A

Dynamic Impedance

I

D

= 100

µ

A

-

700

-

-

700

-

Diode Network Supply Current

I

ABC

= 100

µ

A

250

400

800

250

400

800

µ

A

Amplifier Supply Current

(Per Amplifier)

I+

I

ABC

= 500

µ

A

-

2

2.4

-

2

2.4

mA

Amplifier Output Leakage Current

I

OL

I

ABC

= 0, V

O

= 0V

-

0.015

0.1

-

0.015

0.1

nA

I

ABC

= 0, V

O

= 30V

-

0.15

1

-

0.15

1

nA

Common Mode Rejection Ratio

CMRR

I

ABC

= 100

µ

A

80

100

-

94

100

-

dB

Power Supply Rejection Ratio

PSRR

I

ABC

= 100

µ

A

86

105

-

94

105

-

dB

Open Loop Voltage Gain

A

OL

I

ABC

= 100

µ

A,

R

L

=

,

V

O

= 20V

P-P

94

100

-

94

100

-

dB

50

100

-

50

100

-

kV/V

Forward Transconductance

G

M

I

ABC

= 50

µ

A, Large Signal

-

0.8

1.2

-

0.8

1.2

mS

g

M

I

ABC

= 1mA, Small Signal

-

16

22

-

16

22

mS

Input Resistance

R

I

I

ABC

= 10

µ

A

0.5

-

-

0.5

-

-

M

Channel Separation

f = 1kHz

-

94

-

-

94

-

dB

Open Loop Total

Harmonic Distortion

THD

f = 1kHz, I

ABC

= 1.5mA,

R

L

= 15k

, V

O

= 20V

P-P

-

0.4

-

-

0.4

-

%

Bandwidth

f

T

I

ABC

= 1mA, R

L

= 100

-

9

-

-

9

-

MHz

Slew Rate, Open Loop

SR

I

ABC

= 1mA

-

125

-

-

125

-

V/

µ

s

Capacitance

C

I

I

ABC

= 100

µ

A

Input

-

4.5

-

-

4.5

-

pF

C

O

Output

-

7.5

-

-

7.5

-

pF

Output Resistance

R

O

I

ABC

= 100

µ

A

-

63

-

-

63

-

M

Test Circuits and Waveforms

FIGURE 1. LEAKAGE CURRENT TEST CIRCUIT

FIGURE 2. CHANNEL SEPARATION TEST CIRCUIT

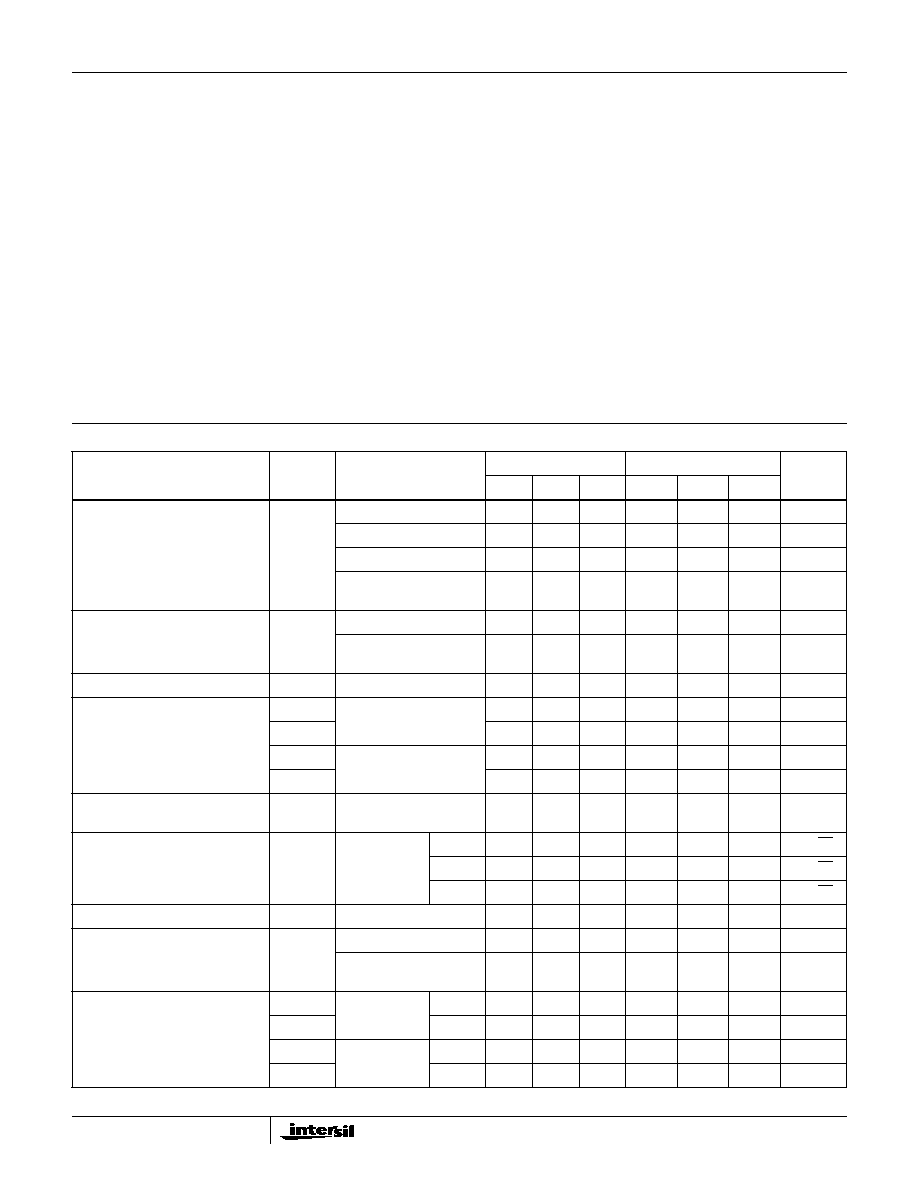

Electrical Specifications

For Equipment Design, at T

A

= 25

o

C, V

SUPPLY

=

±

15V, Unless Otherwise Specified (Continued)

PARAMETER

SYMBOL

TEST CONDITIONS

CA3280

CA3280A

UNITS

MIN

TYP

MAX

MIN

TYP

MAX

1/2

+

-

13

CA3280

3

14

4

1

16

15

I

30V

0V

TEST

POINT

+30V

1/2

+

-

13

CA3280

4

14

3

15

16

V+

0.1

µ

F

OUTPUT

10k

V+

V-

INPUT

30k

0.1

µ

F

1k

1k

30k

CA3280, CA3280A

5

Application Information

Figures 4 and 5 show the equivalent circuits for the current

source and linearization diodes in the CA3280. The current

through the linearization network is approximately equal to the

programming current. There are several advantages to driving

these diodes with a current source. First, only the offset current

from the biasing network flows through the input resistor.

Second, another input is provided to extend the gain control

dynamic range. And third, the input is truly differential and can

accept signals within the common mode range of the CA3280.

Typical Applications

The structure of the variable operational amplifier eliminates

the need for matched resistor networks in differential to single

ended converters, as shown in Figure 6. A matched resistor

network requires ratio matching of 0.01% or trimming for 80dB

of common-mode rejection. The CA3280, with its excellent

common mode rejection ratio, is capable of converting a small

(

±

25mV) differential input signal to a single-ended output

without the need for a matched resistor network.

Figure 7 shows the CA3280 in a typical gain control application.

Gain control can be performed with the amplifier bias current

(l

ABC

). With no diode bias current, the gain is merely g

M

R

L

. For

example, with an l

ABC

of 1mA, the g

M

is approximately 16mS.

With the CA3280 operating into a 5k

resistor, the gain is 80.

The need for external buffers can be eliminated by the use of

low value load resistors, but the resulting increase in the

required amplifier bias current reduces the input impedance

FIGURE 3A. EFFECTS OF DIODE LINEARIZATION, WITH DIODE PROGRAMMING TERMINAL ACTIVE

FIGURE 3B. WITH DIODE PROGRAMMING TERMINAL CUTOFF

FIGURE 3. CA3280 TRANSFER CHARACTERISTICS

Test Circuits and Waveforms

(Continued)

1/2

13

CA3280

1

14

4

3

15

16

15V

I

DIODE

I

ABC

-15V

1k

V+

10k

10k

V-

I

OUT

V

IN

I

ABC

= 650

µ

A, I

D

= 200

µ

A; Vertical = 200

µ

A/Div.;

Horizontal = 1V/Div.

1/2

12

CA3280

8

11

6

4

10

9

15V

I

DIODE

I

ABC

1k

V+

10k

10k

-15V

V-

I

OUT

V

IN

I

ABC

= 650

µ

A; I

D

= 0; Vertical = 200

µ

A/Div.;

Horizontal = 25mV/Div.

CA3280, CA3280A