6-1

Æ

January 1998

ICL7112

12-Bit, High-Speed,

CMOS

µP-Compatible A/D Converter

Features

∑ 12-Bit Resolution and Accuracy

∑ No Missing Codes

∑ Microprocessor Compatible Byte-Organized Buffered

Outputs

∑ Auto-Zeroed Comparator for Low Offset Voltage

∑ Low Linearity and Gain Errors

∑ Low Power Consumption (60mW)

∑ No Gain or Offset Adjustment Necessary

∑ Provides 3% Usable Overrange

∑ Fast Conversion (40

µs)

Description

The ICL7112 is a monolithic 12-bit resolution, fast

successive approximation A/D converter. It uses thin film

resistors and CMOS circuitry combined with an on-chip

PROM calibration table to achieve 12-bit linearity without

laser trimming. Special design techniques used in the DAC

and comparator result in high speed operation, while the

fully static silicon-gate CMOS circuitry keeps the power

dissipation very low.

Microprocessor bus interfacing is eased by the use of

standard memory WRite and ReaD cycle timing and control

signals, combined with Chip Select and Address pins. The

digital output pins are byte-organized and three-state gated

for bus interface to 8-bit and 16-bit systems.

The lCL7112 provides separate Analog and Digital grounds

for increased system accuracy. Operating with

±5V supplies,

the lCL7112 accepts 0V to +10V input with a -10V reference

or 0V to -10V input with a +10V reference.

Ordering Information

PART NO.

TEMP. RANGE (

o

C)

PACKAGE

RESOLUTION WITH NO MISSION

CODES

ICL7112JCDL

0 to 70

40 Ld CERDIP

11-Bit

ICL7112KCDL

0 to 70

40 Ld CERDIP

12-Bit

ICL7112LCDL

0 to 70

40 Ld CERDIP

12-Bit (Note)±

ICL7112JIDL

-25 to 85

40 Ld CERDIP

11-Bit

ICL7112KIDL

-25 to 85

40 Ld CERDIP

12-Bit

ICL7112LIDL

-25 to 85

40 Ld CERDIP

12-Bit (Note)±

ICL7112JMDL

-55 to 125

40 Ld CERDIP

11-Bit

ICL7112KMDL

-55 to 125

40 Ld CERDIP

12-Bit

ICL7112LMDL

-55 to 125

40 Ld CERDIP

12-Bit (Note)±

NOTE: Over operating temperature range.

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143

|

Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright © Intersil Americas Inc. 2002. All Rights Reserved

File Number

3639.1

NOT

REC

OMM

END

ED F

OR N

EW D

ESIG

NS

6-2

Pinout

ICL7112

TOP VIEW

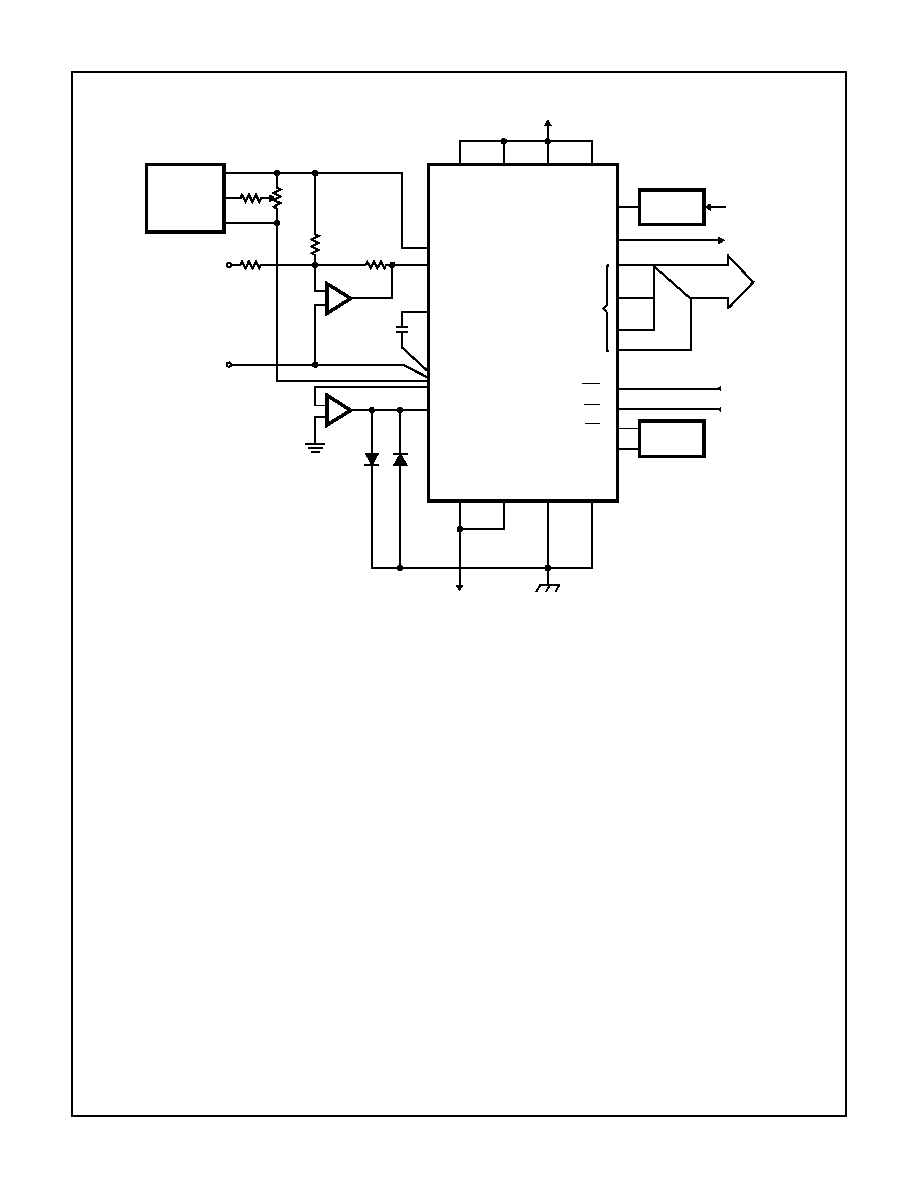

Functional Block Diagram

13

1

2

3

4

5

6

7

8

9

10

11

12

14

15

16

17

18

19

20

NC

AGNDf

CS

RD

A

0

BUS

DGND

(MSB) D

11

D

10

D

9

D

8

D

7

D

6

D

5

D

4

D

3

D

2

D

1

(LSB) D

0

NC

28

40

39

38

37

36

35

34

33

32

31

30

29

27

26

25

24

23

22

21

NC

AGNDs

V

REF

V

IN

COMP

V

-

C

AZ

WR

TEST

OSC2

OSC1

TEST

PROG

V

+

OVR

EOC

NC

NC

NC

NC

ICL7112

+

PROM

DAC

R-1.85R

-

SAR

CONTROL LOGIC

C

AZ

WR

EOC

LATCH

THREE-STATE

OUTPUTS

LATCH

ADDER

ACCCUM

AGND

Y

+

DGND

V

-

V

REF

V

IN

COMP

OSC1

OSC2

OVR

D

11

(MSB)

D

0

(LSB)

BUS

A

0

CS

RD

R

IN

ICL7112

6-3

Absolute Maximum Ratings

T

A

= 25

o

C

Thermal Information

Supply Voltage (V

+

to DGND) . . . . . . . . . . . . . . . . . . -0.3V to +6.5V

Supply Voltage (V

-

to DGND). . . . . . . . . . . . . . . . . . . +0.3V to -6.5V

V

REF

, V

IN

to DGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

±25V

AGND to DGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +1V to -1V

V

REF

, V

IN

, AGND Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25mA

Digital I/O Pin Voltages. . . . . . . . . . . . . . . . . . . . . -0.3V to V+ +0.3V

PROG to DGND Voltage . . . . . . . . . . . . . . . . . . . . V

-

to (V+ +0.3V)

Operating Conditions

ICL7112XCXX. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0 to 70

ICL7112XIXX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -25 to 70

ICL7112XMXX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -55 to 125

Thermal Resistance (Typical, Note 1)

JA

(

o

C/W)

JC

(

o

C/W)

CERDIP Package . . . . . . . . . . . . . . . .

___

___

Maximum Power Dissipation (Note 2). . . . . . . . . . . . . . . . . . 500mW

Derate above 70

o

C at 10mW/

o

C

Maximum Junction Temperature (Ceramic Package) . . . . . . . . 175

o

C

Maximum Storage Temperature Range . . . . . . . . . . -65

o

C to 150

o

C

Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . . . 300

o

C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

1.

JA

is measured with the component mounted on an evaluation PC board in free air.

2. All voltages with respect to DGND, unless otherwise noted.

3. Assumes all leads soldered or welded to printed circuit board.

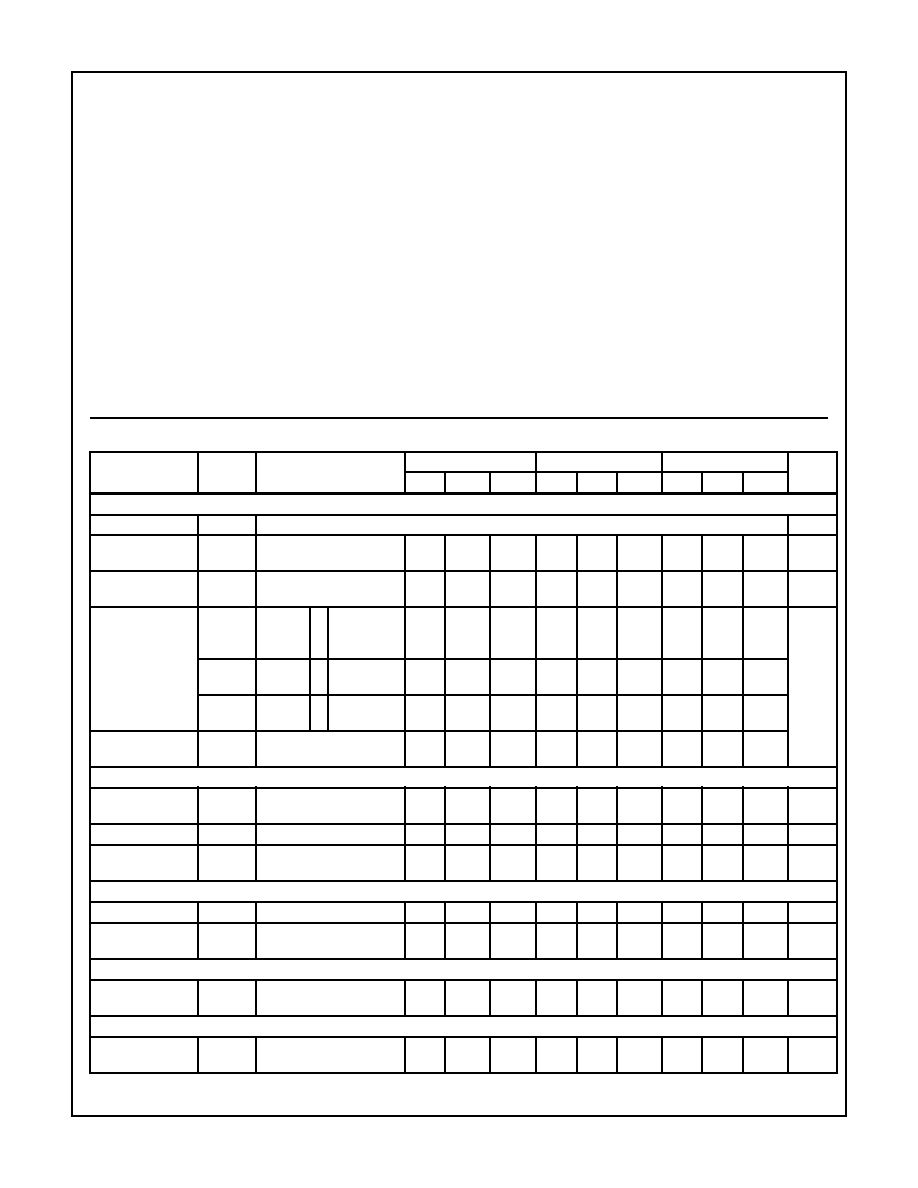

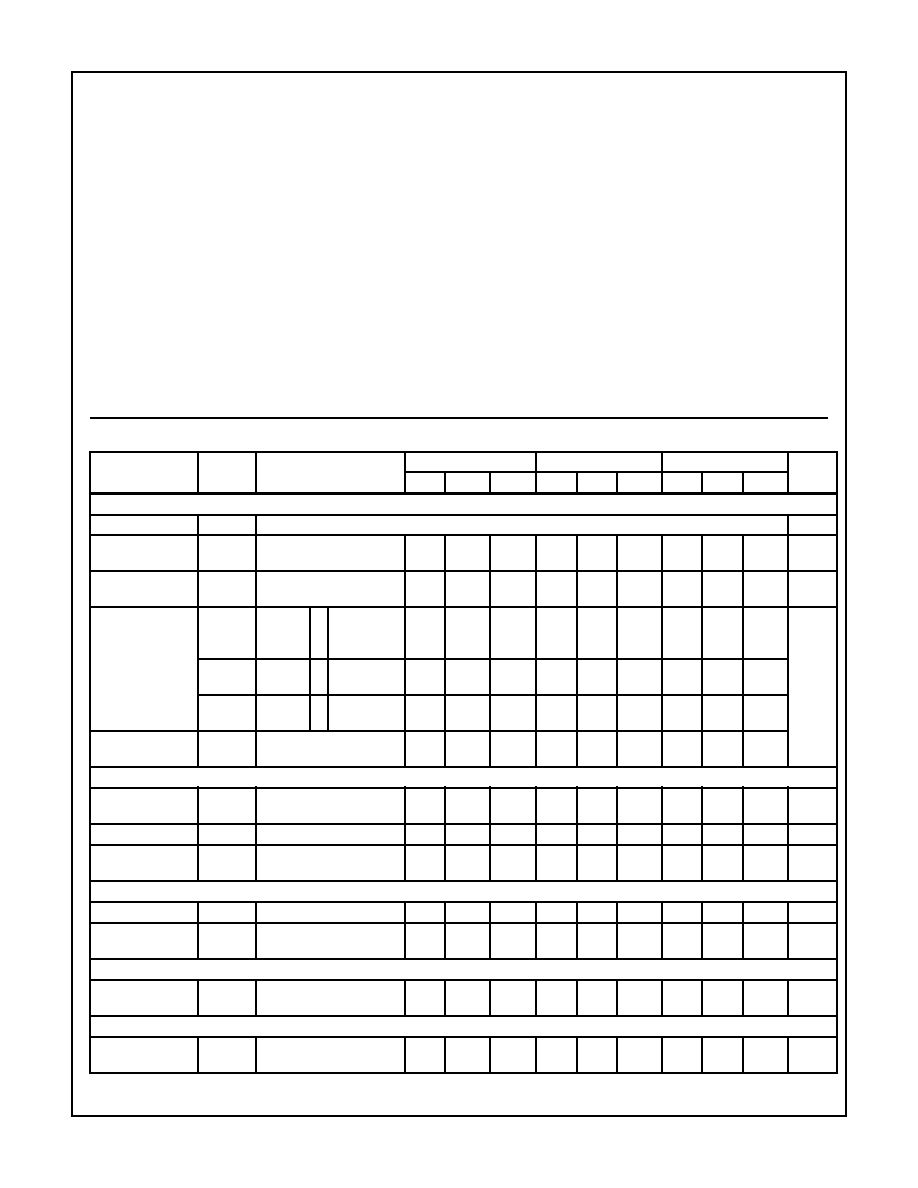

Electrical Specifications

Test Conditions: V+ = +5V, V- = -5V, V

REF

= -10V, T

A

= 25

o

C, f

CLK

= 500kHz, Unless Otherwise Noted

PARAMETER

SYMBOL

TEST

CONDITIONS

J

K

L

UNITS

MIN

TYP

MAX

MIN

TYP

MAX

MIN

TYP

MAX

ACCURACY

Resolution

RES

12

Bits

Resolution with No

Missing Codes

RES

(NMC)

Notes 4, 5, 6

R

M

T

MIN

-T

MAX

11

10

-

-

12

11

-

-

12

12

-

-

Bits

Integral Linearity

Error

I

LE

Notes 4, 5

R

M

T

MIN

-T

MAX

-

-

±0.024

±0.030

-

-

±0.012

±0.020

-

-

±0.012

±0.020

%FSR

Unadjusted Full

Scale Error

FSE

Adjust-

able to

Zero

C

R

M

T

MIN

T

MAX

-

-

±0.10

±0.12

-

-

±0.08

±0.10

-

-

±0.08

±0.10

%FSR

I

R

M

T

MIN

-T

MAX

-

-

±0.10

±0.13

-

-

±0.08

±0.11

-

-

±0.08

±0.11

M

R

M

T

MIN

-T

MAX

-

-

±0.10

±0.14

-

-

±0.08

±0.12

-

-

±0.08

±0.12

Zero Error

ZE

Notes 4, 5

R

M

T

MIN

-T

MAX

-

-

±1

±1.5

-

-

±1

±1.5

-

-

±1

±1.5

ANALOG INPUT

Analog Input

Range

V

IN

0

-

10.3

0

-

10.3

0

-

10.3

V

Input Resistance

R

IN

Notes 5, 8

4

-

9

4

-

9

4

-

9

k

Temperature

Coefficient of R

IN

T

C

(R

IN

)

T

MIN

-T

MAX

-

-300

-

-

-300

-

-

-300

-

ppm/

o

C

REFERENCE INPUT

Analog Reference V

REF

-

-10.0

-

-

-10.0

-

-

-10.0

-

V

Reference

Resistance

R

REF

-

5

-

-

5

-

-

5

-

k

POWER SUPPLY SENSITIVITY

Power Supply

Rejection Ration

PSRR

V

+

, V

-

= 4.5 -5.5V

RM

T

MIN

-T

MAX

-

±0.5

±1

±2

-

±0.5

±1

±2

-

±0.5

±1

±2

LSB

LOGIC INPUT

Low State

Input Voltage

V

IL

T

MIN

-T

MAX

-

-

0.8

-

-

0.8

-

-

0.8

V

ICL7112

6-4

High State

Input Voltage

V

IH

T

MIN

-T

MAX

2.4

-

-

2.4

-

-

2.4

-

-

V

Logic Input

Current

I

LIH

0 < V

IN

< V

+

-

1

10

-

1

10

-

1

10

µA

Logic Input

Capacitance

C

IN

-

15

-

-

15

-

-

15

-

pF

LOGIC OUTPUT

Low State Output

Voltage

V

OL

I

OUT

= 1.6mA

T

MIN

-T

MAX

-

-

0.4

-

-

0.4

-

-

0.4

V

High State Output

Voltage

V

OH

I

OUT

= -200

µA

T

MIN

-T

MAX

2.8

-

-

2.8

-

-

2.8

-

-

V

Three-State Output

Current

I

OX

0 < V

OUT

< V

+

-

1

-

-

1

-

-

1

-

µA

Logic Output

Capacitance

C

OUT

Three-State

-

15

-

-

15

-

-

15

-

pF

POWER REQUIREMENTS

Supply Voltage

Range

V

SUPPLY

Functional Operation Only

±4.5

-

±6.0

±4.5

-

±6.0

±4.5

-

±6.0

V

Supply Current,

I+, I-

I

SUPPLY

R

M

T

MIN

-T

MAX

-

2

4

6

-

2

4

6

-

2

4

6

mA

NOTES:

4. Full scale range (FSR) is 10V (reference adjusted).

5. Assume all leads are soldered or welded to printed circuit board.

6. "J" and "K" versions not production tested. Guaranteed by Integral Linearity Test.

7. Typical values are not tested, for reference only.

8. Not production tested. Guaranteed by design.

Electrical Specifications

Test Conditions: V+ = +5V, V- = -5V, V

REF

= -10V, T

A

= 25

o

C, f

CLK

= 500kHz, Unless Otherwise Noted

PARAMETER

SYMBOL

TEST

CONDITIONS

J

K

L

UNITS

MIN

TYP

MAX

MIN

TYP

MAX

MIN

TYP

MAX

AC Electrical Specifications

Test Conditions V+ = +5V, V- = -5V, T

A

= 25

o

C, f

CLK

= 500kHz, unless otherwise noted. Data

derived from extensive characterization testing. Parameters are not production tested

PARAMETER

SYMBOL

TEST

CONDITIONS

MIN

TYP

MAX

UNITS

READ CYCLE TIMING

Propagation Delay CS to Date

t

cd

RD Low, A

0

Valid

-

-

200

ns

Propagation Delay A

0

to Data

t

ad

CS Low, RD Low

-

-

200

Propagation Delay RD to Data

t

rd

CS Low, A

0

Valid

-

-

200

Propagation Delay Data to Three-State

t

rx

-

-

150

Propagation Delay EOC High to Data

t

ed

-

-

200

WRITE CYCLE TIMING

WR Low Time

t

wr

150

-

-

ns

Propagation Delay WR Low to EOC Low

t

we

Wait Mode

1

-

2

EOC High Time

t

eo

Free Run Mode

0.5

-

1.5

1/f

CLK

Conversion Time

t

conv

-

-

20

Clock Frequency Range

f

CLK

Functional Operation Only

-

500

-

kHz

NOTE:

9. All typical values have been characterized, but are not tested.

ICL7112

6-5

Pin Descriptions

PIN NO.

NAME

DESCRIPTION

1

No connection.

2

AGND

f

FORCE input for analog ground.

3

CS

Chip Select enables reading and writing (active low).

4

RD

ReaD (active low).

5

A

0

Byte select (low = D

0

-D

7

, high = D

8

-D

11

, OVR).

6

BUS

Bus select (low = outputs enabled by A

0

, high = all outputs enabled together).

7

DGND

Digital GrouND return.

8

D

11

Bit 11 (most significant bit).

High Byte

9

D

10

Bit 10

10

D

9

Bit 9

11

D

8

Bit 8

12

D

7

Bit 7

13

D

6

Bit 6

14

D

5

Bit 5

Low Byte

15

D

4

Bit 4

16

D

3

Bit 3

17

D

2

Bit 2

18

D

1

Bit 1

19

D0

Bit 0 (least significant bit).

20

No connection.

21

No connection.

22

No connection.

23

No connection.

24

No connection.

25

EOC

End of conversion flag (low = busy, high = conversion complete).

26

OVR

OVerRange flag (valid at end of conversion when output code exceeds full-scale;

three-state output enabled with high byte).

27

V

+

Positive power supply input.

28

PROG

Used for programming only. Must tie to V

+

for normal operation.

29

TEST

Used for programming only. Must tie to V

+

for normal operation.

30

OSC1

Oscillator inverter input.

31

OSC2

Oscillator inverter output.

32

TEST

Must tie to V

+

for normal operation.

33

WR

WRite pulse input (low starts new conversion).

34

C

AZ

Auto-zero capacitor connection (Note).

35

V

-

Negative power supply input.

36

COMP

Used in test, tie to V

-

.

37

V

IN

SENSE line for input voltage.

38

V

REF

SENSE line for reference input.

39

AGND

s

SENSE line for analog ground.

40

No connection

NOTE: The voltage of CAZ is driven; NEVER connect directly to ground.

Output

Data

Bits

(High =True)

ICL7112

6-6

Detailed Description

The ICL7112 is basically a successive approximation A/D

converter with an internal structure much more complex than

a standard SAR-type converter. The Functional Block Dia-

gram shows the functional diagram of the ICL7112 12-bit

A/D converter. The additional circuitry incorporated into the

ICL7112 is used to perform error correction and to maintain

the operating speed in the 40

µs range.

The internal DAC of the ICL7112 is designed around a radix

of 1.85, rather than the traditional 2.00. This radix gives each

bit of the DAC a weight of approximately 54% of the previous

bit. The result is a usable range that extends to 3% beyond

the full-scale input of the A/D. The actual value of each bit is

measured and stored in the on-chip PROM. The absolute

value of each bit weight then becomes relatively unimportant

because of the error correction action of the ICL7112.

The output of the high-speed auto-zeroed comparator is fed

to the data input of a successive approximation register

(SAR). This register is uniquely designed for the ICL7112 in

that it tests bit pairs instead of individual bits in the manner of

a standard SAR. At the beginning of the conversion cycle,

the SAR turns on the MSB (D

11

) and the MSB 4-bit (D

7

).

The sequence continues for each bit pair, B

X

and B

x-4

, until

only the four LSBs remain. The sequence concludes by test-

ing the four LSBs individually.

The SAR output is fed to the DAC register and to the prepro-

grammed PROM where it acts as PROM address. PROM

data is fed to a full-adder/accumulator where the decoded

results from each successive phase of the conversion are

summed with the previous results. After 20 clock cycles, the

accumulator contains the final binary data which is latched

and sent to the three-state output buffers. The accuracy of

the A/D converter depends primarily upon the accuracy of

the data that has been programmed into the PROM during

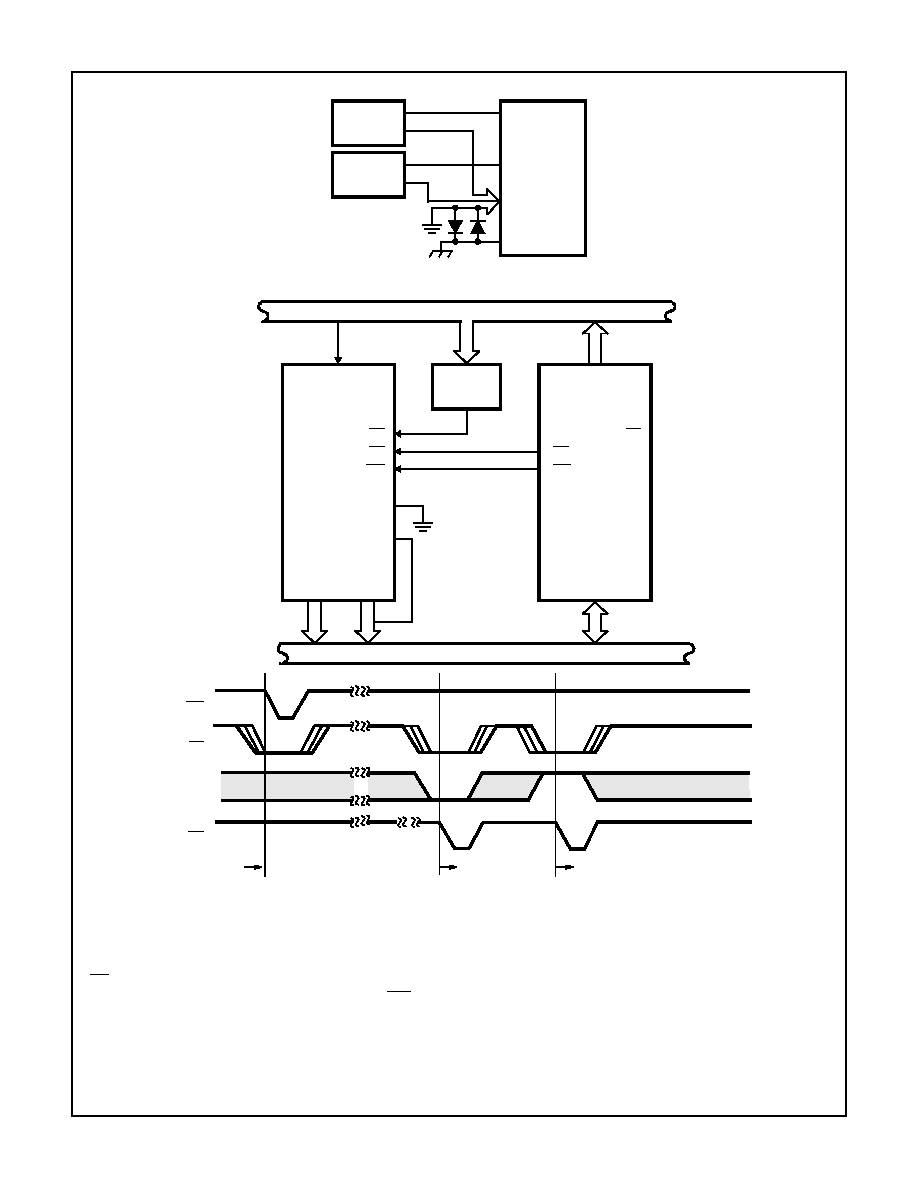

Timing Diagrams

FIGURE 1. READ CYCLE TIMING

FIGURE 2. WRITE CYCLE TIMING

CS

A

0

RD

D

0

- D

13

EOC

= DON'T CARE

VALID

VALID

t

ED

t

RD

t

AD

t

CD

t

RX

= DON'T CARE

CS

WR

EOC

t

EO

t

CONV

t

WE

t

WR

TABLE 2: I/O CONTROL

CS WR RD A

0

BUS

FUNCTION

0

0

x

x

x

Initiates a conversion.

1

x

x

x

x

Disables all chip commands.

0

x

0

0

0

Low byte is enabled.

0

x

0

1

0

High byte is enabled.

0

x

0

x

1

Low and High bytes enabled togeth-

er.

x

x

1

x

x

Disables outputs (high-impedance).

TABLE 3: TRANSFER FUNCTION

INPUT VOLTAGE

EXPECTED OUTPUT CODE

V

REF

= -10.0V

OVR

MSB

LSB

0

+0.00244

0

0

0

0

0000000000

0000000000

0

1

+0.30029

0

0

0000111101

1

+4.99756

+5.00000

0

0

0

1

1111111111

0000000000

1

0

+9.99512

+9.99756

+10.00000

+10.00244

0

0

1

1

1

1

0

0

1111111111

1111111111

0000000000

0000000000

0

1

0

1

+10.29000

1

0

0000111101

1

ICL7112

6-7

the final test portion of the manufacturing process.

The error correcting algorithm built into the ICL7112 reduces

the initial accuracy requirements of the DAC. The overlap in

the testing of bit pairs reduces the accuracy requirements on

the comparator which has been optimized for speed. Since

the comparator is auto-zeroed, no external adjustment is

required to get ZERO code for ZERO input voltage.

Twenty clock cycles are required for the complete 12-bit con-

version. The auto-zero circuitry associated with the compar-

ator is employed during the last three clock cycles of the

conversion to cancel the effect of offset voltage. Also during

this time, the SAR and accumulator are reset in preparation

for the start of the next conversion.

The overflow output of the full-adder is also the OVer Range

(OVR) output of the ICL7112. Unlike standard SAR type A/D

converters, the ICL7112 has the capability of providing valid

usable data for inputs that exceed the fullscale range by as

much as 3%.

Optimizing System Performance

When using A/D converters with 12 or more bits of resolu-

tion, special attention must be paid to grounding and the

elimination of potential ground loops. A ground loop can be

formed by allowing the return current from the lCL7112's

DAC to flow through traces that are common to other analog

circuitry. If care is not taken, this current can generate small

unwanted voltages that add to or detract from the reference

or input voltages of the A/D converter.

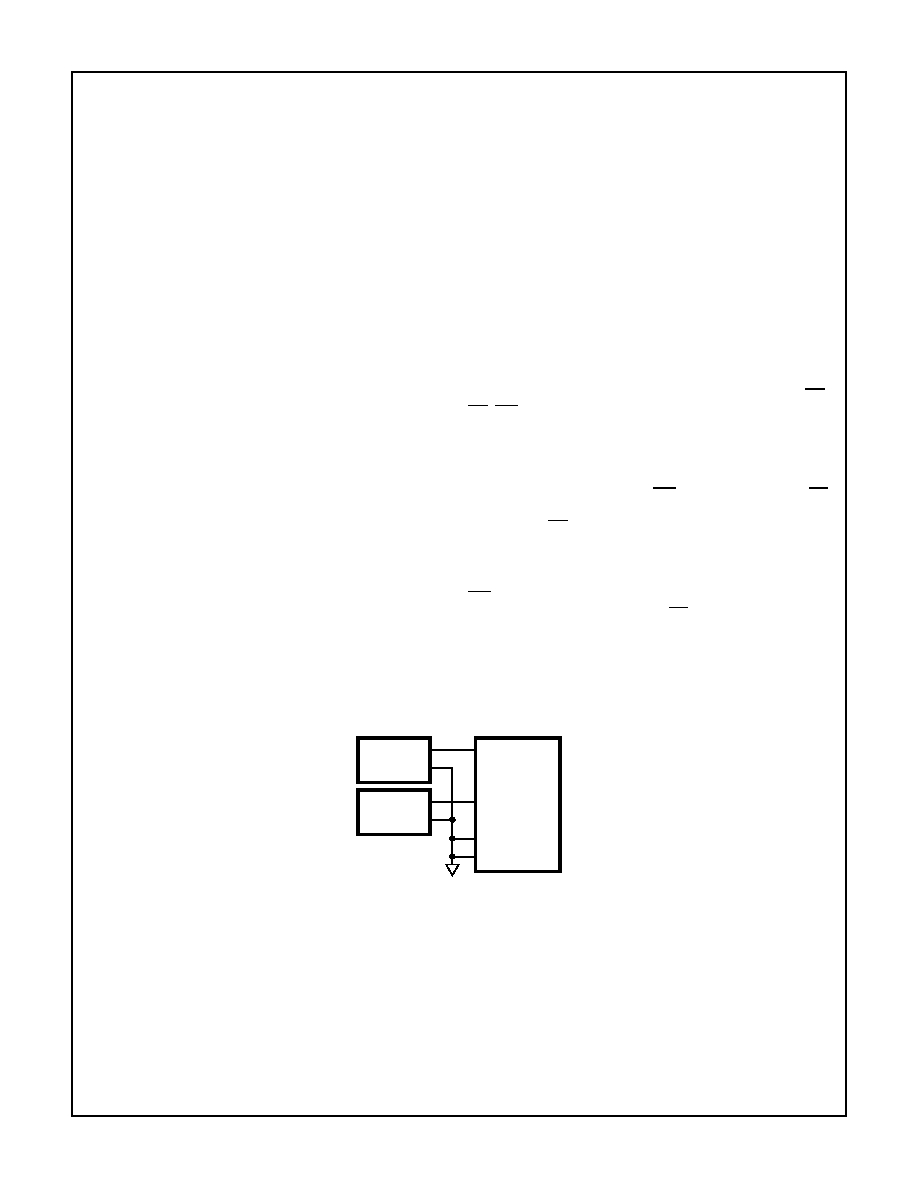

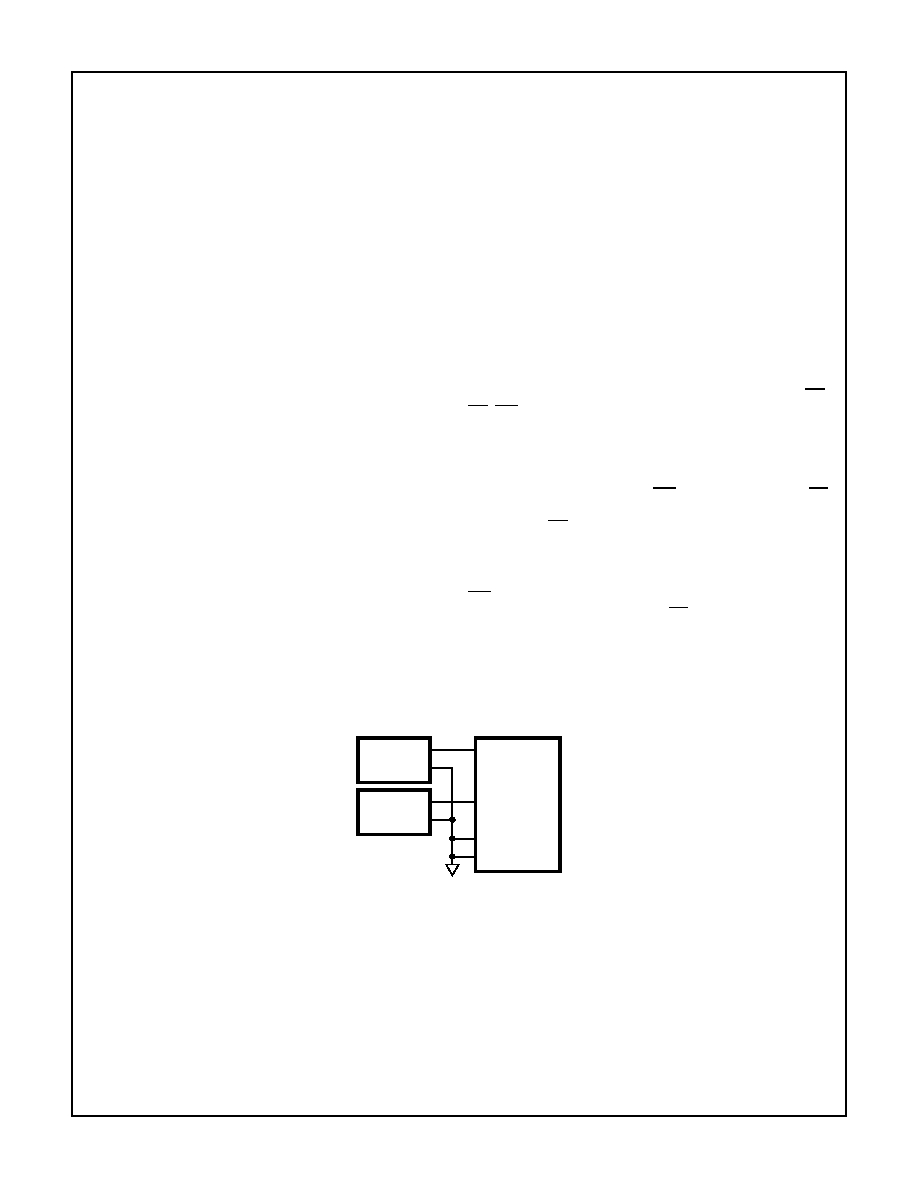

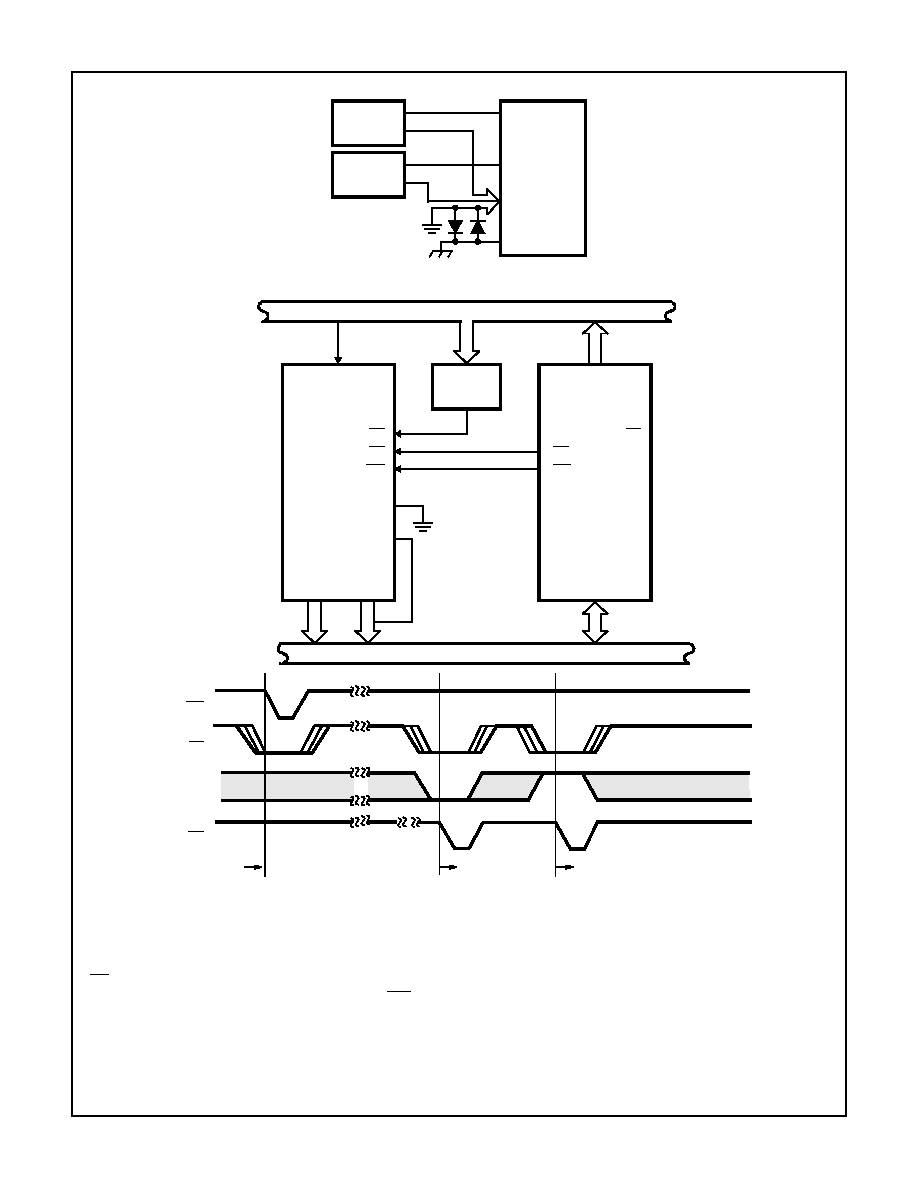

Figure 3 and Figure 4 show two different grounding tech-

niques. Although the difference between the two circuits may

not be readily apparent, the circuit of Figure 3 is very likely to

have significant ground loop errors which the circuit of Fig-

ure 4 avoids. In Figure 3, the supply currents for analog

ground, digital ground, and the reference voltage all flow

through a lead, common to the input. This will generate a DC

offset voltage due to the currents flowing in the resistance of

the common lead. This offset voltage will vary with the input

voltage and with the digital output. Even the auto-zero loop

of the ICL7112 cannot remove this error.

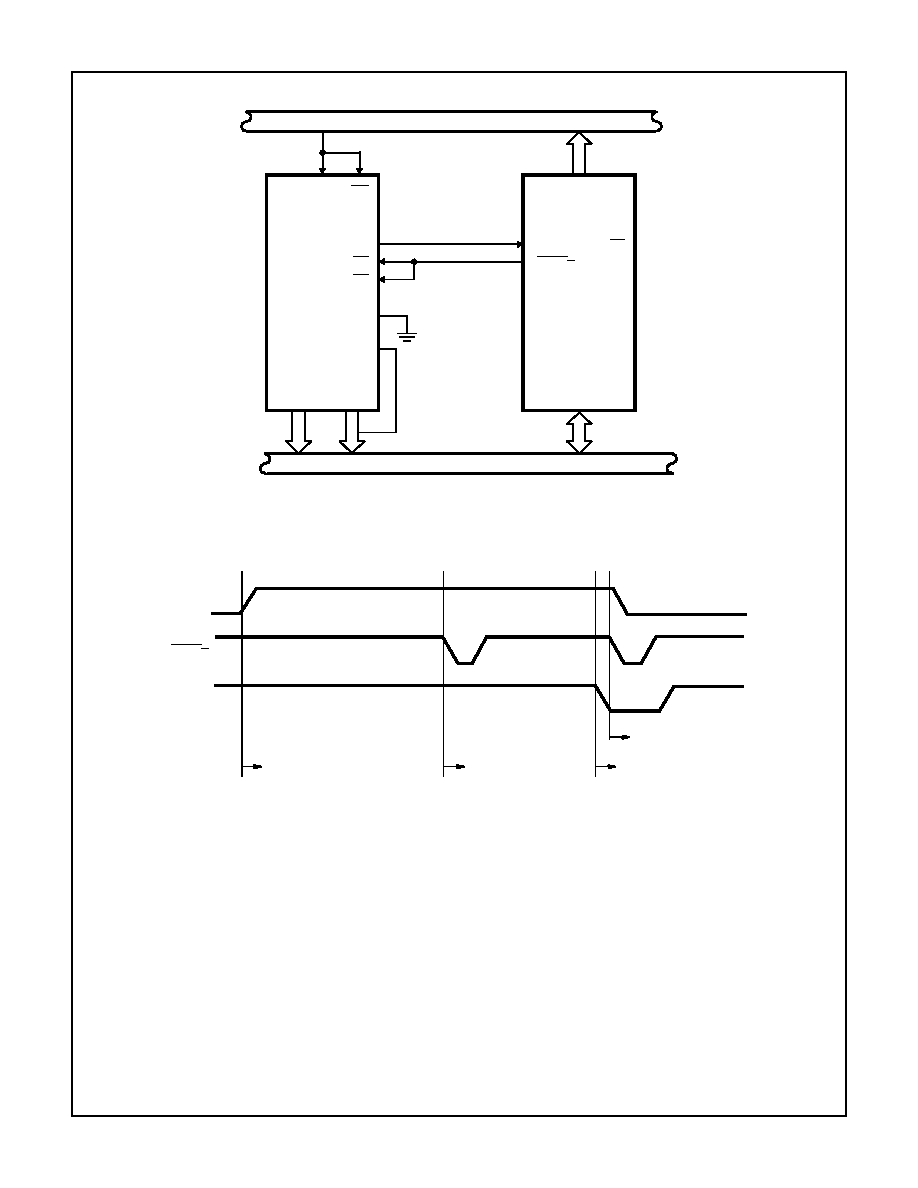

Figure 4 shows a much better arrangement. The ground and

reference currents do not flow through the input common

lead, eliminating any error voltages. Note that the supply

currents and any other analog system currents must also be

returned carefully to analog ground. The clamp diodes will

protect the ICL7112 against signals which could result from

separate analog and digital grounds. The absolute maximum

voltage rating between AGND and DGND is

±1.0V. The two

inverse-parallel diodes clamp this voltage to less than

±0.7V.

Input Warning

As with any CMOS integrated circuit, no input voltages

should be applied to the lCL7112 until the

±5V power sup-

plies have stabilized.

Interfacing To Digital Systems

The_ICL7112 provides three-state data output buffers, CS,

RD, WR, and bus select inputs (A

0

and BUS) for interfacing

to a wide variety of microcomputers and digital systems. The

I/O Control Truth Table shows the functions of the digital

control lines. The BUS select and A

0

lines are provided to

enable the output data onto either 8-bit or 16-bit data buses.

A conversion is initiated by a WR pulse (pin 33) when CS

(pin 3) is low. Data is enabled on the bus when the chip is

selected and RD (pin 4) is low.

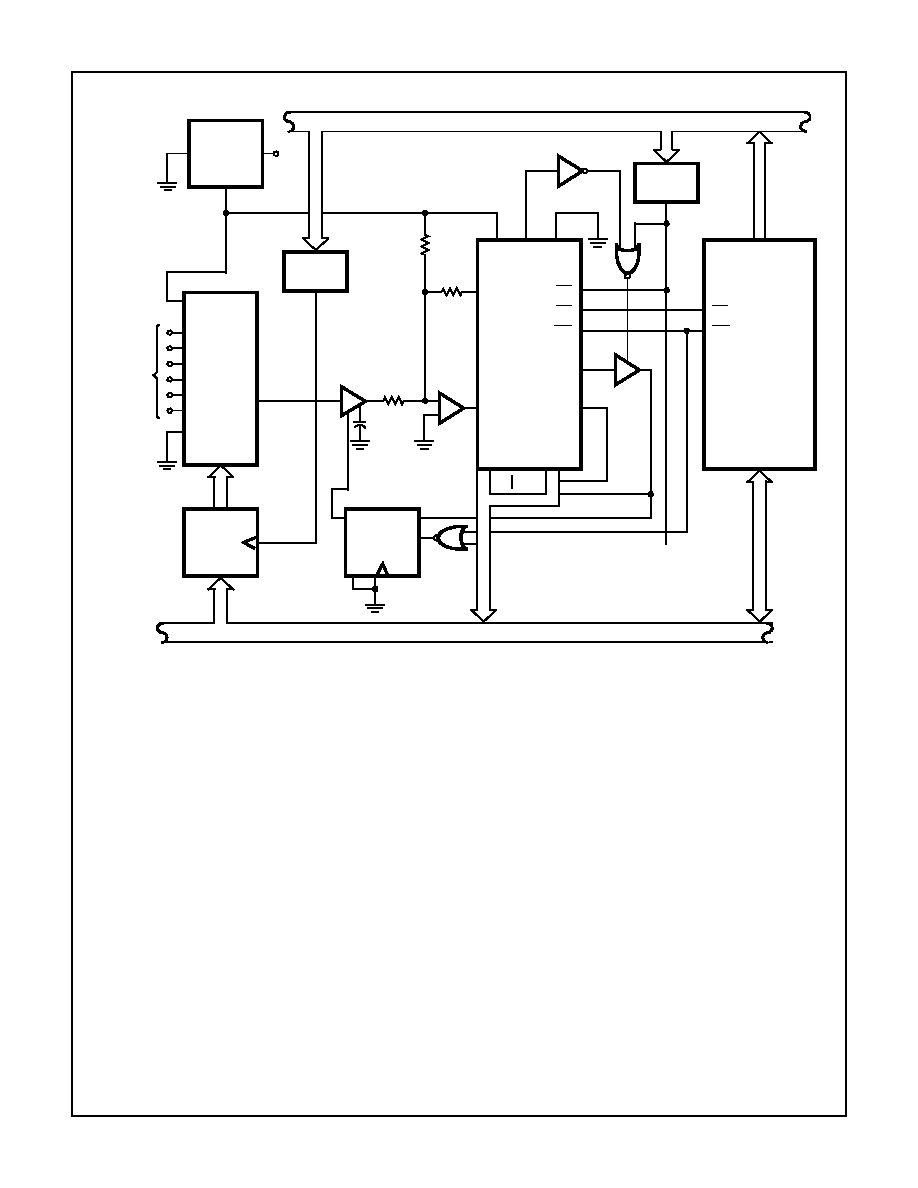

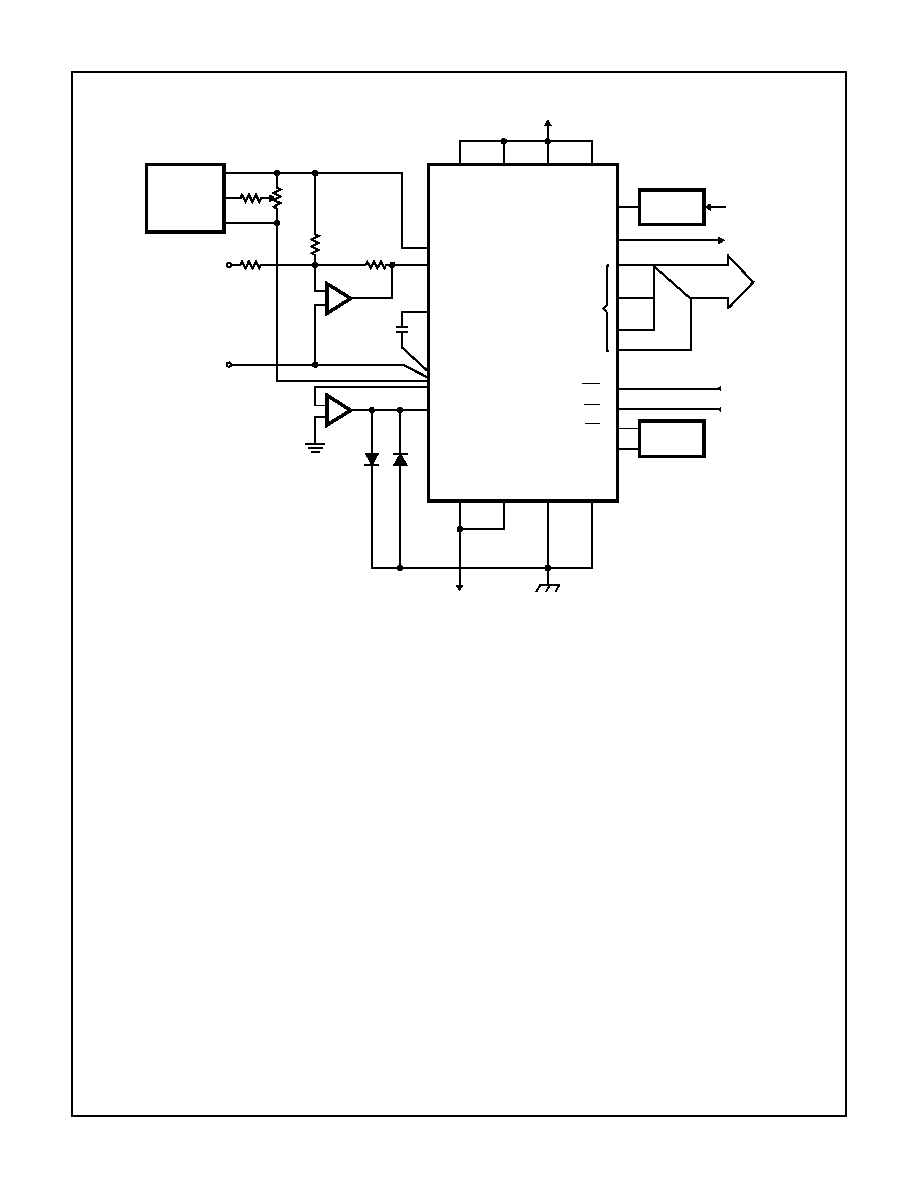

Figure 5 illustrates a typical interface to an 8-bit microcom-

puter. The "Start and Wait" operation requires the fewest

external components and is initiated by a low level on the

WR input to the ICL7112 after the I/O or memory mapped

address decoder has brought the CS input low. After execut-

ing a delay or utility routine for a period of time greater than

the conversion time of the ICL7112, the processor issues

two consecutive bus addresses to read output data into two

bytes of memory. A low level on A

0

enables the LSBs, and a

high level enables the MSBs.

V

IN

V

REF

AGND

DGND

ICL7112

V

IN +

SOURCE -

V

REF -

SOURCE +

FIGURE 3. IMPROPER GROUNDING TECHNIQUE WILL CAUSE GROUND LOOP ERRORS

ICL7112

6-8

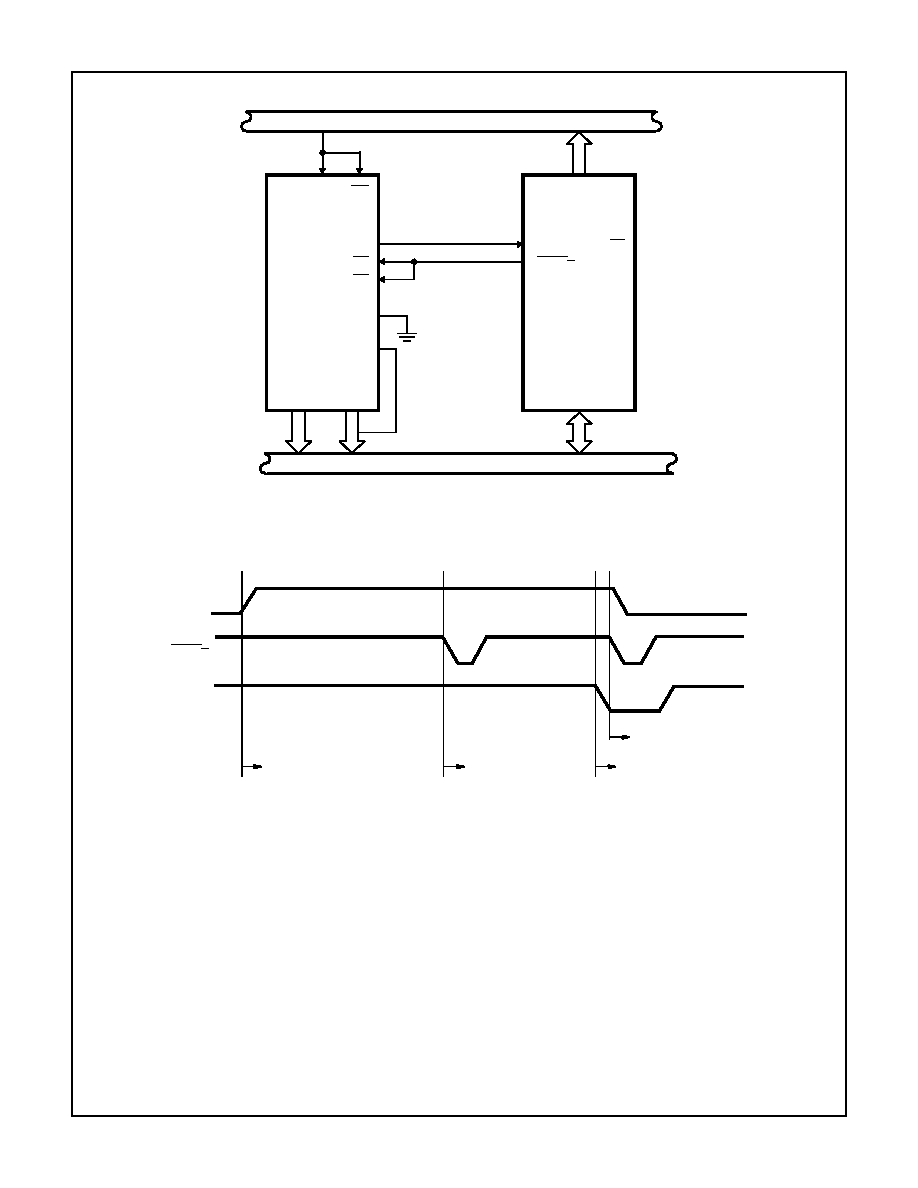

By adding a three-state buffer and two control gates, the

End-of-Conversion (EOC) output can be used to control a

"Start and Poll" interface (Figure 6). In this mode, the A

0

and

CS lines connect the EOC output to the data bus along with

the most significant byte of data. After pulsing the WR line to

initiate a conversion, the microprocessor continually reads

the most significant byte until it detects a high level on the

EOC bit. The "Start and Poll" interface increases data

throughput compared with the "Start and Wait" method by

eliminating delays between the conversion termination and

the microprocessor read operation.

Other interface configurations can be used to increase data

throughput without monopolizing the microprocessor during

waiting or polling operations by using the EOC line as an

interrupt generator as shown in Figure 7. After the conver-

sion cycle is initiated, the microprocessor can continue to

execute routines that are independent of the A/D converter

until the converter's output register actually holds valid data.

For fastest data throughput, the ICL7112 can be connected

directly to the data bus but controlled by way of a Direct

V

IN

V

REF

AGND

DGND

ICL7112

V

IN +

SOURCE -

V

REF -

SOURCE +

FIGURE 4. RECOMMENDED GROUNDING TECHNIQUE TO ELIMINATE GROUND LOOP ERRORS

ICL7112

A

0

CS

RD

BUS

OVR

D

8

- D

11

D

0

- D

7

WR

A

0

- A

N

CS

RD

µP

OVR

D

0

- D

7

WR

ADDRESS

DECODE

ADDRESS BUS

DATA BUS

A

0

READ

LOW BYTE

READ

HIGH BYTE

START

CONVERSION

WAIT

RD

A

0

CS

WR

FIGURE 5. "START AND WAIT" OPERATION

ICL7112

6-9

Memory Access (DMA) controller as shown in Figure 8.

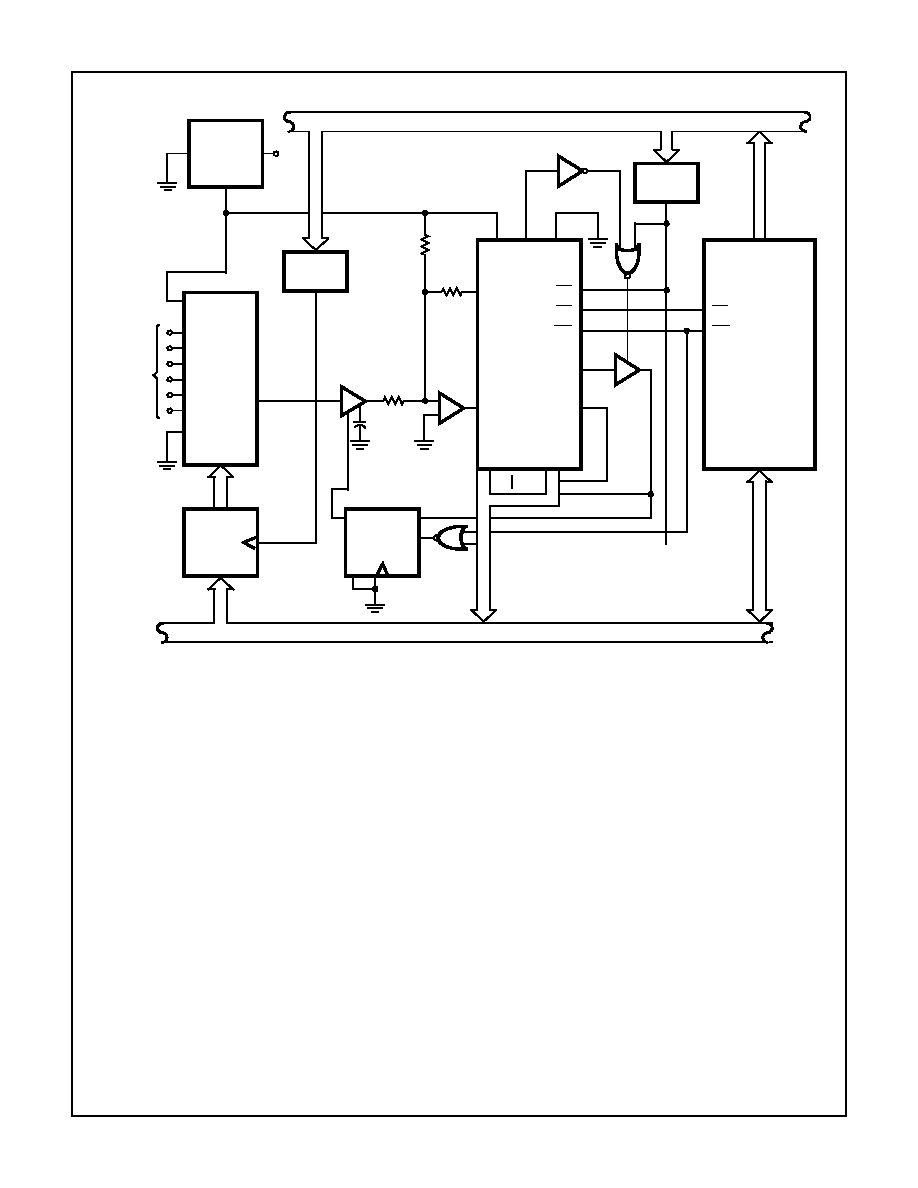

Applications

Figure 9 shows a typical application of the ICL7112 12- bit

A/D converter. A bipolar input voltage range of +10V to -10V

is the result of using the current through R

2

to force a 1/2

scale offset on the input amplifier (A

1

). The output of A

1

swings from 0V to -1 0V. The overall gain of the A/D is varied

by adjusting the 100

trim resistor, R

5

. Since the ICL7112 is

automatically zeroed every conversion, the system gain and

offset stability will be superb as long as a reference with a

tempco of 1ppm/

o

C and stable external resistors are used.

If is important to note that since the 7112's DAC current

flows in A

1

, the amplifier should be a wideband (GBW >

20MHz) type to minimize errors.

The clock for the ICL7112 is taken from whatever system

clock is available and divided down to the level for a conver-

sion time of 40

µs. Output data is controlled by the BUS and

A

0

inputs. Here they are set for 8-bit bus operation with BUS

grounded and A

0

under the control of the address decode

section of the external system.

Because the ICL7112's internal accumulator generates

accurate output data for input signals as much as 3% greater

than full-scale, and because the converter's OVR output

flags overrange inputs, a simple microprocessor routine can

be employed to precisely measure and correct for system

gain and offset errors. Figure 10 shows a typical data acqui-

sition system that uses a 10V reference, input signal multi-

plexer, and input signal Track/Hold amplifier. Two of the

multiplexer's input channels are dedicated to sampling the

system analog ground and reference voltage. Here, as in

Figure 9, bipolar operation is accommodated by an offset

resistor between the reference voltage and the summing

junction of A

1

. A flip-flop in IC

3

sets 1

C2

's Track/Hold input

after the microprocessor has initiated a WR command, and

resets when EOC goes high at the end of the conversion.

The first step in the system calibration routine is to select the

multiplexer channel that is connected to system analog

ground and initiate a conversion cycle for the ICL7112. The

results represent the system offset error which comes from

the sum of the offsets from IC

1

, IC

2

, and A

1

. Next the chan-

nel connected to the reference voltage is selected and mea-

sured. These results, minus the system offset error,

represent the system full-scale range. A gain error correction

factor can be derived from this data. Since the lCL7112 pro-

vides valid data for inputs that exceed full-scale by as much

as 3%, the OVR output can be thought of as a valid 13th

data bit. Whenever the OVR bit is high, however, the total

12-bit result should be checked to ensure that it falls within

100% and 103% of full-scale. Data beyond 103% of full-

scale should be discarded.

Clock Considerations

The ICL7112 provides an internal inverter which is brought

out to pins OSC1 and OSC2, for crystal or ceramic resonator

oscillator operation. The clock frequency is calculated from:

f

CLK

=

20

t

CONV

------------------

ICL7112

6-10

FIGURE 6. START AND POLL" OPERATION

DATA BUS

ICL7112

A

0

WR

CS

EOC

BUS

D

8

- D

11

D

0

- D

7

RD

A

0

- A

N

CS

RD

µP

D

0

- D

7

WR

ADDRESS

DECODE

A

0

1/4 74125

OVR

READ

HIGH BYTE

READ

HIGH BYTE

START

CONVERSION POLL

RD

EOC

WR

CS

A

0

READ

LOW BYTE

END OF

CONVERSION

ADDRESS BUS

( )

(B)

ICL7112

6-11

FIGURE 7. USING EOC AS AN INTERRUPT

ICL7112

A

0

CS

RD

EOC

BUS

D

8

- D

11

D

0

- D

7

WR

A

0

- A

N

RD

µP

D

0

- D

7

WR

ADDRESS

DECODE

ADDRESS BUS

DATA BUS

A

0

OVR

WR

CS

EOC

A

0

RD

START

CONVERSION

READ

LOW BYTE

READ

HIGH BYTE

INTERRUPT

INT

ICL7112

6-12

FIGURE 8. DATA TO MEMORY VIA DMA CONTROLLER

ICL7112

A

0

EOC

RD

BUS

OVR

D

8

- D

11

D

0

- D

7

CS

A

0

- A

11

CS

DACK

N

DMA

D

0

- D

7

ADDRESS BUS

DATA BUS

A

0

WR

DRQ

N

CONTROLLER

END OF

CONVERSION

READ

HIGH BYTE

READ

LOW BYTE

START

CONVERSION

EOC

DACK

N

A

0

ICL7112

6-13

FIGURE 9. TYPICAL APPLICATION WITH BIPOLAR INPUT RANGE, FORCED GROUND, AND 10V ULTRA STABLE REFERENCE

DATA BUS

PROG

TEST

V

+

V

+

DGND

BUS

V

IN

V

REF

CAZ

AGND

AGND

ICL7112

OSC

EOC

DATA

OUT

WR

RD

CS

A

0

25

30

26

HIGH

BYTE

13

14

LOW BYTE

21

33

4

3

5

ADDRESS

DECODE

DIVIDER

8-BIT

10V

REFERENCE

COMP

R

4

R

5

36

+5V

100K

+-

A

2

37

39

34

R

2

100k

R

3

50k

0.22

µF

2

+-

INPUT VOLTAGE

+10V TO -10V

36

35

7

6

-5V

DIGITAL

GROUND

PINS 1, 20, 21, 22, 23, 24, 40

NO CONNECTIONS

SYSTEM

CLOCK

TEST

28

32

29

27 500KHz

DIODES

1N914

R

1

100k

LO

A

2

HI

ICL7112

6-14

FIGURE 10. MULTI-CHANNEL DATA ACQUISITION SYSTEM WITH ZERO AND REFERENCE LINES BROUGHT TO MULTIPLEXER

FOR SYSTEM GAIN AND OFFSET ERROR CORRECTION

V

REF

BUS

A

0

D

8

- D

13

D

0

- D

7

ICL7112

CS

RD

WR

EOC

OVR

V

S

V

R

+

-

ADDRESS

DECODE

10k

IC 2

LF398

IC

3

1/2 4013

R

S

Q

D

A

0

- A

N

RD

WR

µP

D

0

- D

7

1/2

74125

ADDRESS

DECODE

IC

1

IH5108

I

S

I

R

OUT

A

0

- A

2

DATA

LATCH

ANALOG

INPUTS

REFERENCE

10V

V

CC

ADDRESS BUS

DATA BUS