| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: IRF7506 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

V

DSS

= -30V

R

DS(on)

= 0.27

HEXFET

Æ

Power MOSFET

PD - 9.1268F

MICRO8

Fifth Generation HEXFETs from International Rectifier

utilize advanced processing techniques to achieve

extremely low on-resistance per silicon area. This

benefit, combined with the fast switching speed and

ruggedized device design that HEXFET Power MOSFETs

are well known for, provides the designer with an extremely

efficient and reliable device for use in a wide variety of

applications.

The new Micro8 package, with half the footprint area of the

standard SO-8, provides the smallest footprint available in

an SOIC outline. This makes the Micro8 an ideal device

for applications where printed circuit board space is at a

premium. The low profile (<1.1mm) of the Micro8 will

allow it to fit easily into extremely thin application

environments such as portable electronics and PCMCIA

cards.

All Micro8 Data Sheets reflect improved Thermal Resistance, Power and Current -Handling Ratings- effective

only for product marked with Date Code 505 or later .

D1

D1

D2

D2

G 1

S 2

G 2

S 1

T o p V iew

8

1

2

3

4

5

6

7

l

Generation V Technology

l

Ultra Low On-Resistance

l

Dual P-Channel MOSFET

l

Very Small SOIC Package

l

Low Profile (<1.1mm)

l

Available in Tape & Reel

l

Fast Switching

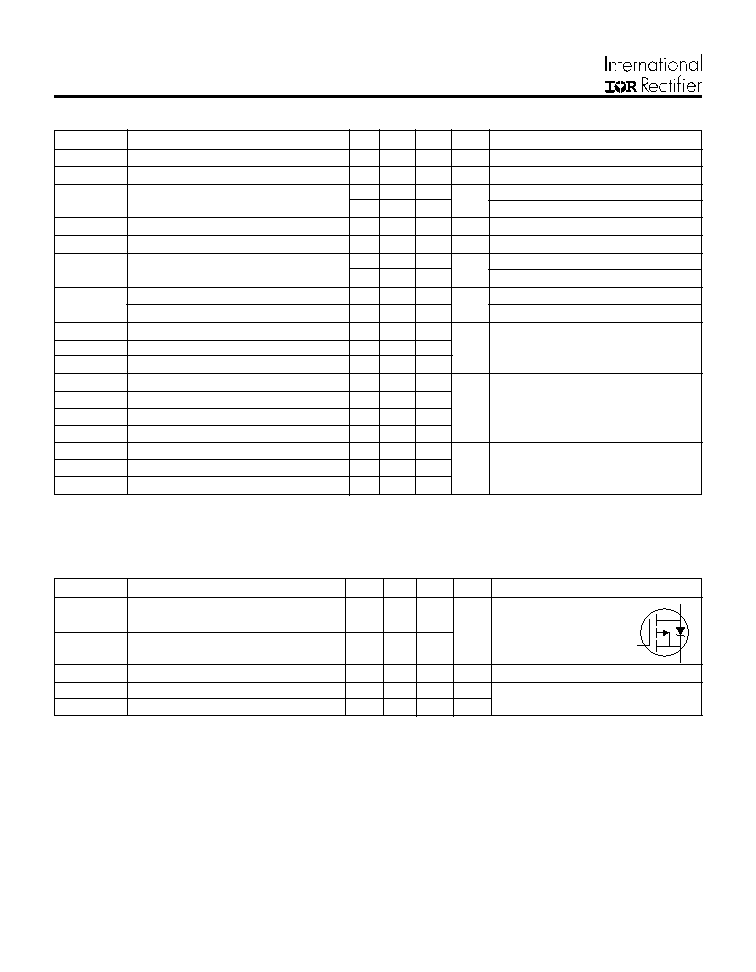

Absolute Maximum Ratings

Parameter

Max.

Units

I

D

@ T

A

= 25∞C

Continuous Drain Current, V

GS

@ -10V

-1.7

I

D

@ T

A

= 70∞C

Continuous Drain Current, V

GS

@ -10V

-1.4

A

I

DM

Pulsed Drain Current

-9.6

P

D

@T

A

= 25∞C

Power Dissipation

1.25

W

Linear Derating Factor

10

mW/∞C

V

GS

Gate-to-Source Voltage

± 20

V

dv/dt

Peak Diode Recovery dv/dt

5.0

V/ns

T

J,

T

STG

Junction and Storage Temperature Range

-55 to + 150

∞C

8/25/97

Description

IRF7506

Thermal Resistance Ratings

Parameter

Typ.

Max.

Units

R

JA

Maximum Junction-to-Ambient

≠≠≠

100

∞C/W

IRF7506

Parameter

Min. Typ. Max. Units

Conditions

V

(BR)DSS

Drain-to-Source Breakdown Voltage

-30

≠≠≠

≠≠≠

V

V

GS

= 0V, I

D

= -250µA

V

(BR)DSS

/

T

J

Breakdown Voltage Temp. Coefficient

≠≠≠ -0.039 ≠≠≠

V/∞C

Reference to 25∞C, I

D

= -1mA

≠≠≠

≠≠≠

0.27

V

GS

= -10V, I

D

= -1.2A

≠≠≠

≠≠≠

0.45

V

GS

= -4.5V, I

D

= -0.60A

V

GS(th)

Gate Threshold Voltage

-1.0

≠≠≠

≠≠≠

V

V

DS

= V

GS

, I

D

= -250µA

g

fs

Forward Transconductance

0.92

≠≠≠

≠≠≠

S

V

DS

= -10V, I

D

= -0.60A

≠≠≠

≠≠≠

-1.0

V

DS

= -24V, V

GS

= 0V

≠≠≠

≠≠≠

-25

V

DS

= -24V, V

GS

= 0V, T

J

= 125∞C

Gate-to-Source Forward Leakage

≠≠≠

≠≠≠

-100

V

GS

= -20V

Gate-to-Source Reverse Leakage

≠≠≠

≠≠≠

100

V

GS

= 20V

Q

g

Total Gate Charge

≠≠≠

7.5

11

I

D

= -1.2A

Q

gs

Gate-to-Source Charge

≠≠≠

1.3

1.9

nC

V

DS

= -24V

Q

gd

Gate-to-Drain ("Miller") Charge

≠≠≠

2.5

3.7

V

GS

= -10V, See Fig. 6 and 9

t

d(on)

Turn-On Delay Time

≠≠≠

9.7

≠≠≠

V

DD

= -15V

t

r

Rise Time

≠≠≠

12

≠≠≠

I

D

= -1.2A

t

d(off)

Turn-Off Delay Time

≠≠≠

19

≠≠≠

R

G

= 6.2

t

f

Fall Time

≠≠≠

9.3

≠≠≠

R

D

= 12

,

See Fig. 10

C

iss

Input Capacitance

≠≠≠

180

≠≠≠

V

GS

= 0V

C

oss

Output Capacitance

≠≠≠

87

≠≠≠

pF

V

DS

= -25V

C

rss

Reverse Transfer Capacitance

≠≠≠

42

≠≠≠

= 1.0MHz, See Fig. 5

Electrical Characteristics @ T

J

= 25∞C (unless otherwise specified)

I

GSS

µA

R

DS(on)

Static Drain-to-Source On-Resistance

I

DSS

Drain-to-Source Leakage Current

nA

ns

Notes:

Repetitive rating ≠ pulse width limited by max. junction temperature (see fig. 11)

I

SD

-1.2A, di/dt

-140A/µs, V

DD

V

(BR)DSS

, T

J

150∞C

Pulse width

300µs ≠ duty cycle

2%

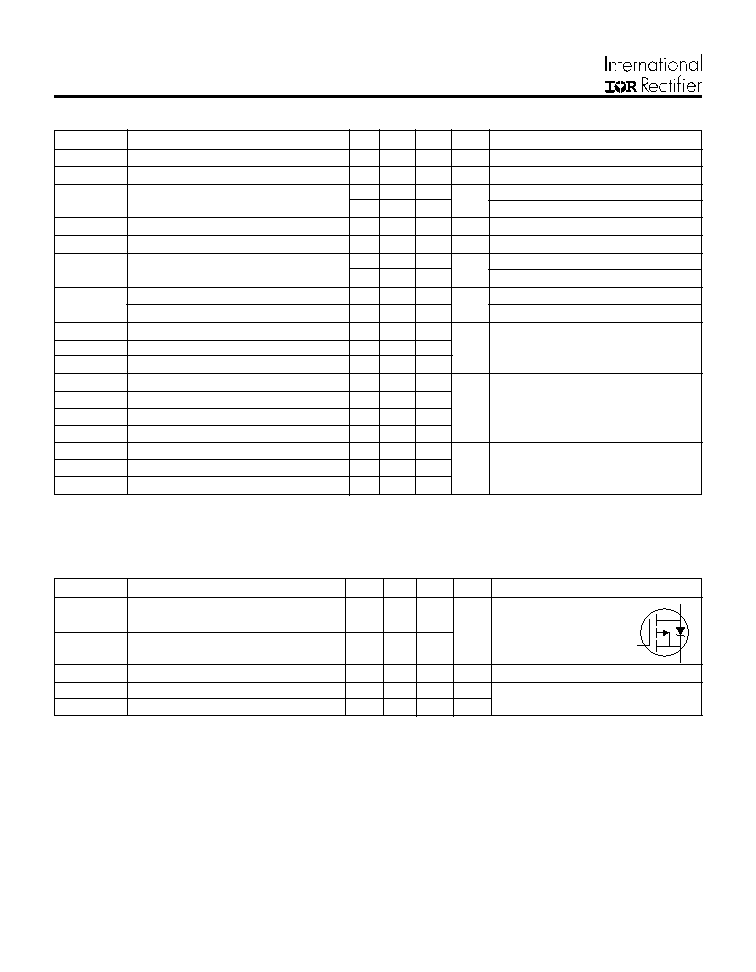

Parameter

Min. Typ. Max. Units

Conditions

I

S

Continuous Source Current

MOSFET symbol

(Body Diode)

showing the

I

SM

Pulsed Source Current

integral reverse

(Body Diode)

p-n junction diode.

V

SD

Diode Forward Voltage

≠≠≠

≠≠≠

-1.2

V

T

J

= 25∞C, I

S

= -1.2A, V

GS

= 0V

t

rr

Reverse Recovery Time

≠≠≠

30

45

ns

T

J

= 25∞C, I

F

= -1.2A

Q

rr

Reverse RecoveryCharge

≠≠≠

37

55

nC

di/dt = -100A/µs

Source-Drain Ratings and Characteristics

A

-9.6

≠≠≠

≠≠≠

≠≠≠

-1.25

≠≠≠

S

D

G

Surface mounted on FR-4 board, t

10sec.

IRF7506

Fig 3. Typical Transfer Characteristics

Fig 4. Normalized On-Resistance

Vs. Temperature

Fig 2. Typical Output Characteristics

Fig 1. Typical Output Characteristics

0 . 1

1

1 0

0 . 1

1

1 0

D

D S

20 µs P U LSE W I DTH

T = 25 ∞C

A

-I

,

D

r

a

i

n

-

t

o

-S

o

u

r

c

e

C

u

rr

e

n

t

(

A

)

-V , D ra in-to-S ou rce V o lta ge (V )

J

-3.0 V

VGS

TOP - 15V

- 10V

- 7.0V

- 5.5V

- 4.5V

- 4.0V

- 3.5V

BOTT OM - 3.0V

0 . 1

1

1 0

0 . 1

1

1 0

D

D S

A

-I

,

D

r

a

i

n

-

t

o

-S

o

u

r

c

e

C

u

rr

e

n

t

(

A

)

-V , D ra in-to-S ou rce V o lta ge (V )

-3. 0V

VGS

TOP - 15V

- 10V

- 7.0V

- 5.5V

- 4.5V

- 4.0V

- 3.5V

BOTT OM - 3.0V

20 µs P U LSE W I DTH

T = 15 0∞C

J

0 . 1

1

1 0

3 . 0

4 . 0

5 . 0

6 . 0

7 . 0

T = 2 5 ∞C

T = 1 5 0 ∞C

J

J

G S

D

A

-

I

, D

r

a

i

n

-

to

-

S

o

u

r

c

e

C

u

r

r

e

n

t

(

A

)

-V , Ga te -to -S o u rce V o ltag e (V )

V = -1 0 V

2 0 µ s P U L S E W ID T H

DS

0 . 0

0 . 5

1 . 0

1 . 5

2 . 0

- 6 0

- 4 0

- 2 0

0

2 0

4 0

6 0

8 0

1 0 0

1 2 0

1 4 0

1 6 0

J

T , Ju nctio n T emp eratu re (∞C)

R

,

D

r

a

i

n

-

to

-

S

o

u

r

c

e

O

n

R

e

s

i

s

t

a

n

c

e

D

S

(

on)

(

N

o

r

m

a

l

i

z

ed)

A

V = -10 V

G S

I = -1. 2A

D

IRF7506

Fig 8. Maximum Safe Operating Area

Fig 6. Typical Gate Charge Vs.

Gate-to-Source Voltage

Fig 5. Typical Capacitance Vs.

Drain-to-Source Voltage

Fig 7. Typical Source-Drain Diode

Forward Voltage

0

4

8

1 2

1 6

2 0

0

2

4

6

8

1 0

1 2

G

GS

A

-

V

, G

a

te

-

t

o

-

S

o

u

r

c

e

V

o

l

t

a

g

e

(

V

)

Q , Tota l Gate Ch arge (n C)

V = -24 V

V = -15 V

DS

DS

I = -1.2 A

D

FO R TEST C IR C U IT

SEE F IGU R E 9

0 . 1

1

1 0

1 0 0

1

1 0

1 0 0

OPE R ATIO N IN TH IS A RE A LI MI TE D

BY R

D S(o n)

T = 25 ∞C

T = 15 0∞C

S ing le Pulse

A

-I

,

D

r

a

i

n

C

u

rre

n

t

(A

)

-V , D rain-to-S ource Volta ge (V )

D S

D

A

J

1 ms

10m s

10 0µs

10µ s

0

1 0 0

2 0 0

3 0 0

4 0 0

1

1 0

1 0 0

C

,

C

a

pac

i

t

anc

e (

p

F

)

A

D S

-V , Drain -to -So urce V oltag e (V)

V = 0V , f = 1MH z

C = C + C , C SH OR TED

C = C

C = C + C

G S

is s gs g d ds

rs s g d

os s ds gd

C

is s

C

o s s

C

rs s

0 . 1

1

1 0

0 . 4

0 . 6

0 . 8

1 . 0

1 . 2

1 . 4

T = 25 ∞C

T = 1 50 ∞C

J

J

V = 0 V

G S

S D

SD

A

-

I

,

R

e

v

e

r

s

e D

r

ai

n

C

u

r

r

ent

(

A

)

-V , S ou rce -to -Drain V olta ge (V )

IRF7506

0.1

1

10

100

1000

0.00001

0.0001

0.001

0.01

0.1

1

10

100

Notes:

1. Duty factor D =

t / t

2. Peak T = P

x Z

+ T

1

2

J

DM

thJA

A

P

t

t

DM

1

2

t , Rectangular Pulse Duration (sec)

Thermal Response

(Z )

1

thJA

0.01

0.02

0.05

0.10

0.20

D = 0.50

SINGLE PULSE

(THERMAL RESPONSE)

Fig 10b. Switching Time Waveforms

Fig 10a. Switching Time Test Circuit

Fig 9a. Basic Gate Charge Waveform

Fig 9b. Gate Charge Test Circuit

V

DS

-10V

Pulse Width

1

µs

Duty Factor

0.1 %

R

D

V

GS

V

DD

R

G

D.U.T.

+

-

Q

G

Q

GS

Q

GD

V

G

Charge

-10V

V

DS

90%

10%

V

GS

t

d(on)

t

r

t

d(off)

t

f

D.U.T.

V

DS

I

D

I

G

-3mA

V

GS

.3

µ

F

50K

.2

µ

F

12V

Current Regulator

Same Type as D.U.T.

Current Sampling Resistors

+

-

Fig 11. Maximum Effective Transient Thermal Impedance, Junction-to-Ambient