| ÐлекÑÑоннÑй компоненÑ: IRU3004CF | СкаÑаÑÑ:  PDF PDF  ZIP ZIP |

Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

IRU3004

1

Rev. 1.7

07/16/02

www.irf.com

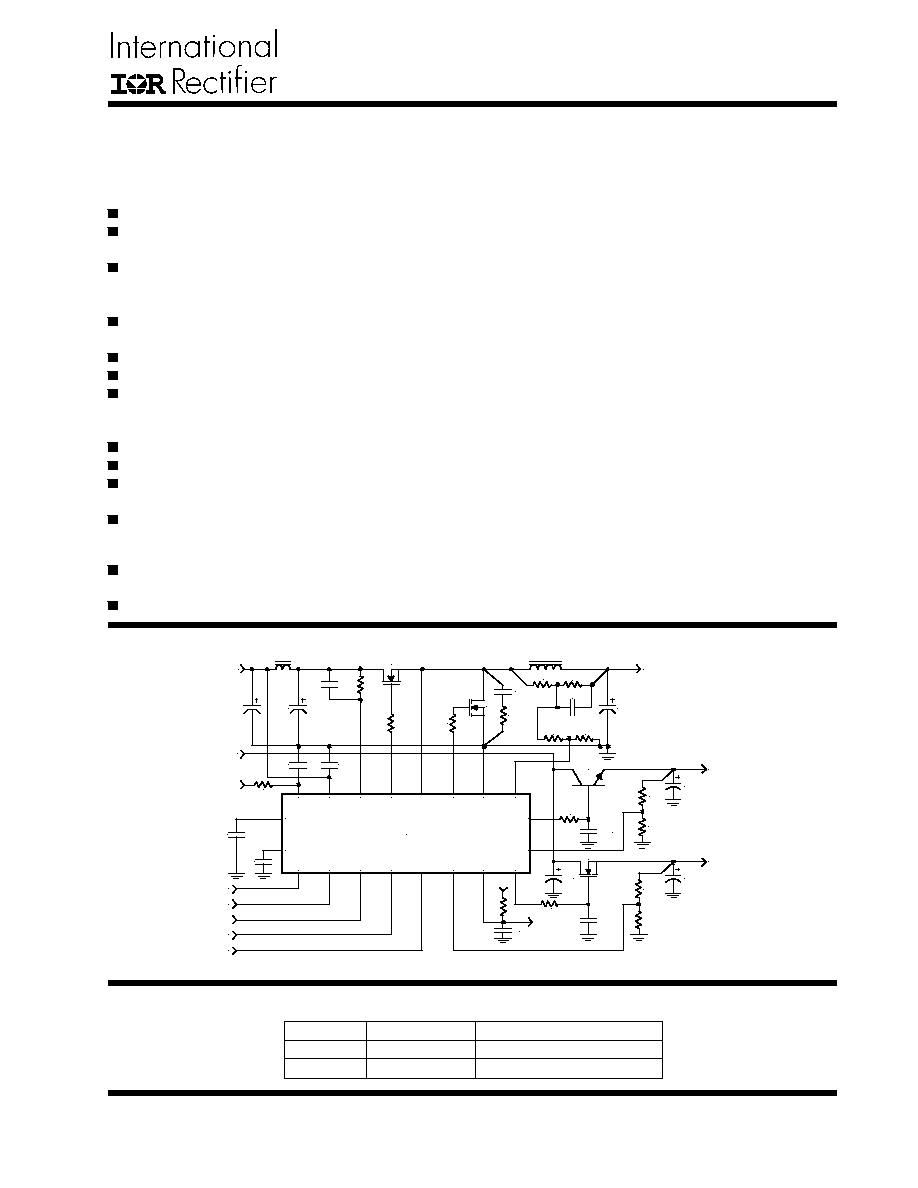

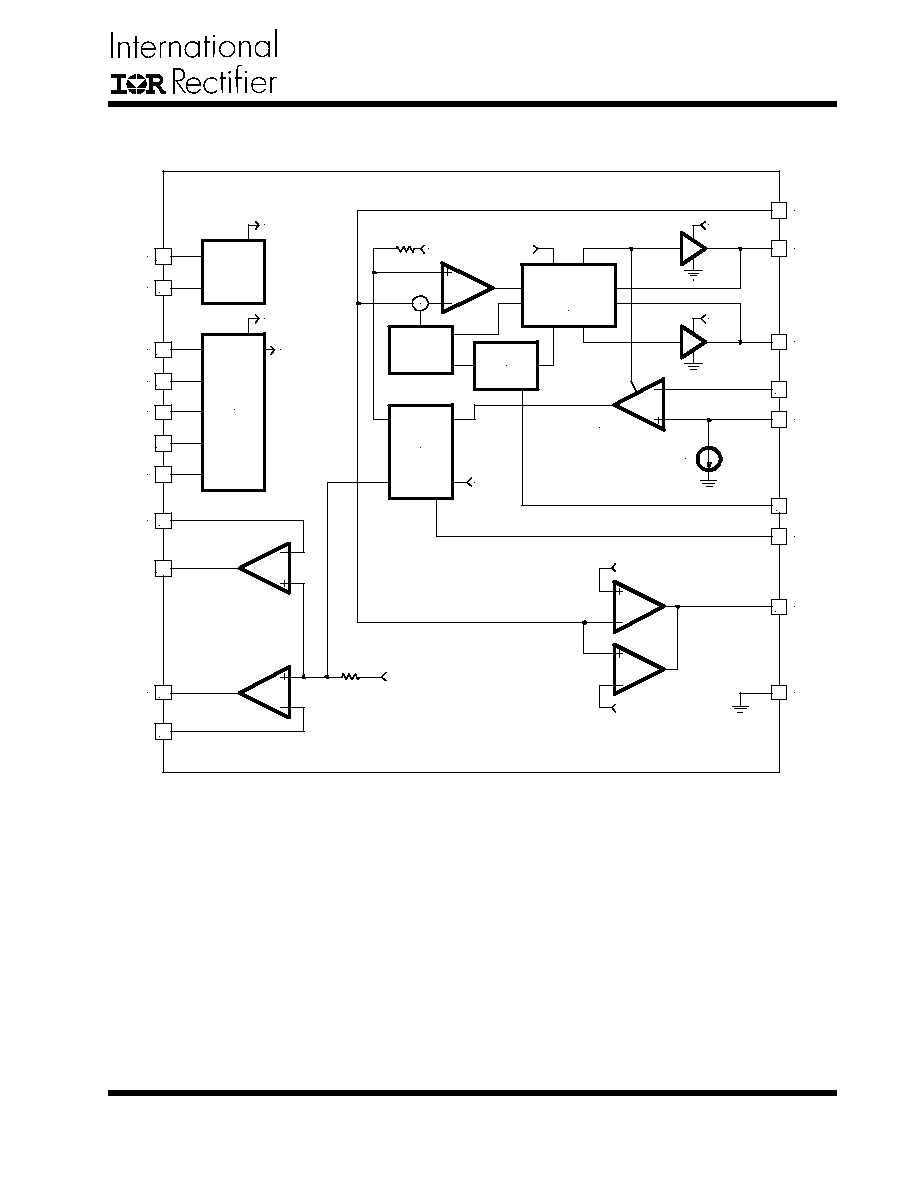

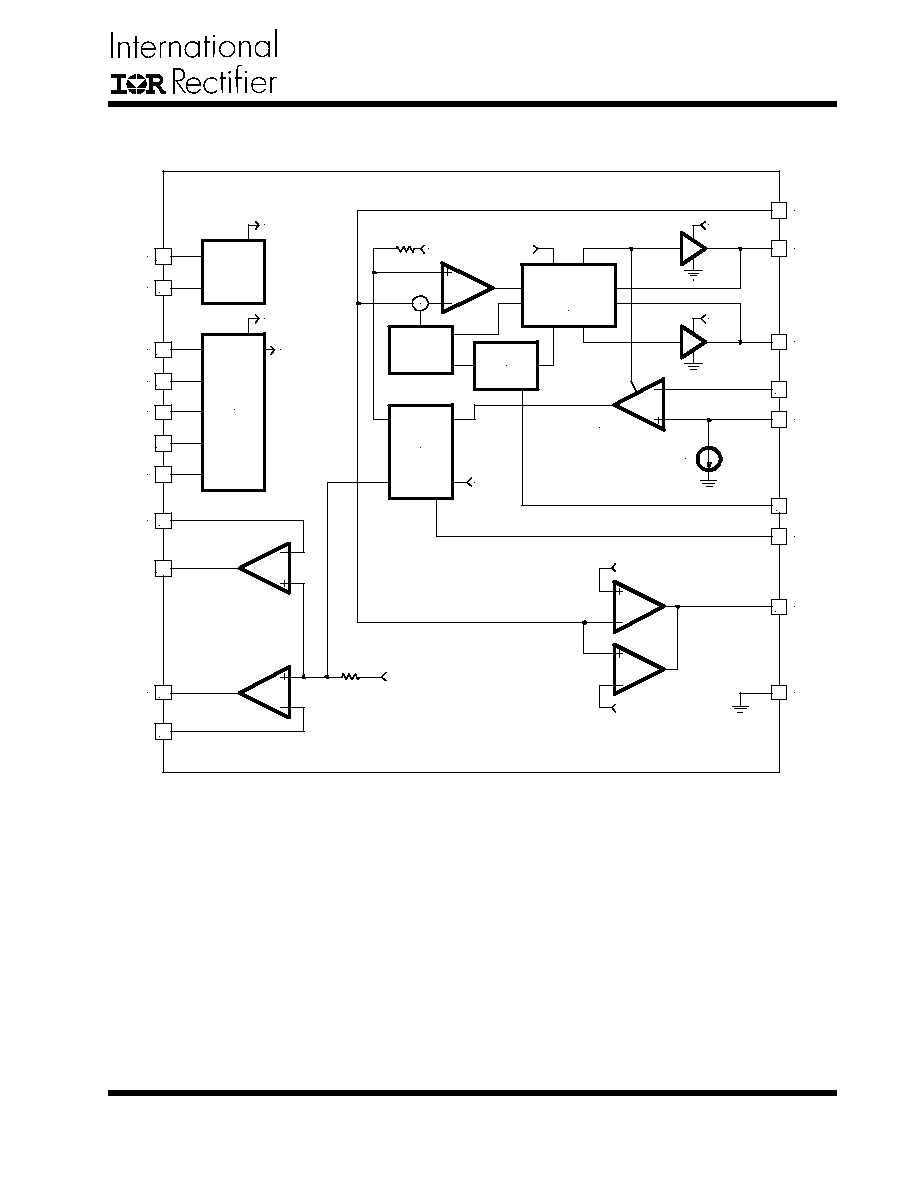

TYPICAL APPLICATION

DESCRIPTION

The IRU3004 controller IC is specifically designed to meet

Intel specifications for Pentium III

TM

microprocessor

applications as well as the next generation P6 family

processors. The IC provides a single chip controller IC

for the Vcore, GTL+ and clock supplies required for the

Pentium III applications. The IRU3004 features a pat-

ented topology, that in combination with a few external

components as shown in the typical application circuit,

will provide in excess of 20A of output current for an on-

board DC-DC converter while automatically providing the

right output voltage via the 5-bit internal DAC meeting

the latest VRM specification. The IRU3004 also features

loss-less current sensing by using the R

DS(on)

of the high

side power MOSFET as the sensing resistor and a Power

Good window comparator that switches its open collec-

tor output low when the output is outside of a

±

10%

window. Other features of the device are: under-voltage

lockout for both 5V and 12V supplies, an external pro-

grammable soft-start function as well as programming

the oscillator frequency by using an external capacitor.

Meets latest VRM 8.4 specification for PentiumIII

Provides single chip solution for Vcore, GTL+ and

clock supply

On-Board DAC programs the output voltage from

1.3V to 3.5V. The IRU3004 remains on for VID code

of (11111)

Dual linear regulator controller on-board for 1.5V

GTL+ and 2.5V clock supplies

Loss-less Short Circuit Protection

Synchronous operation allows maximum efficiency

Patented architecture allows fixed frequency opera-

tion as well as 100% duty cycle during dynamic

load

Minimum Part Count, No External Compensation

Soft-Start Function

High current totem pole driver for direct driving of the

external power MOSFET

Power Good Function

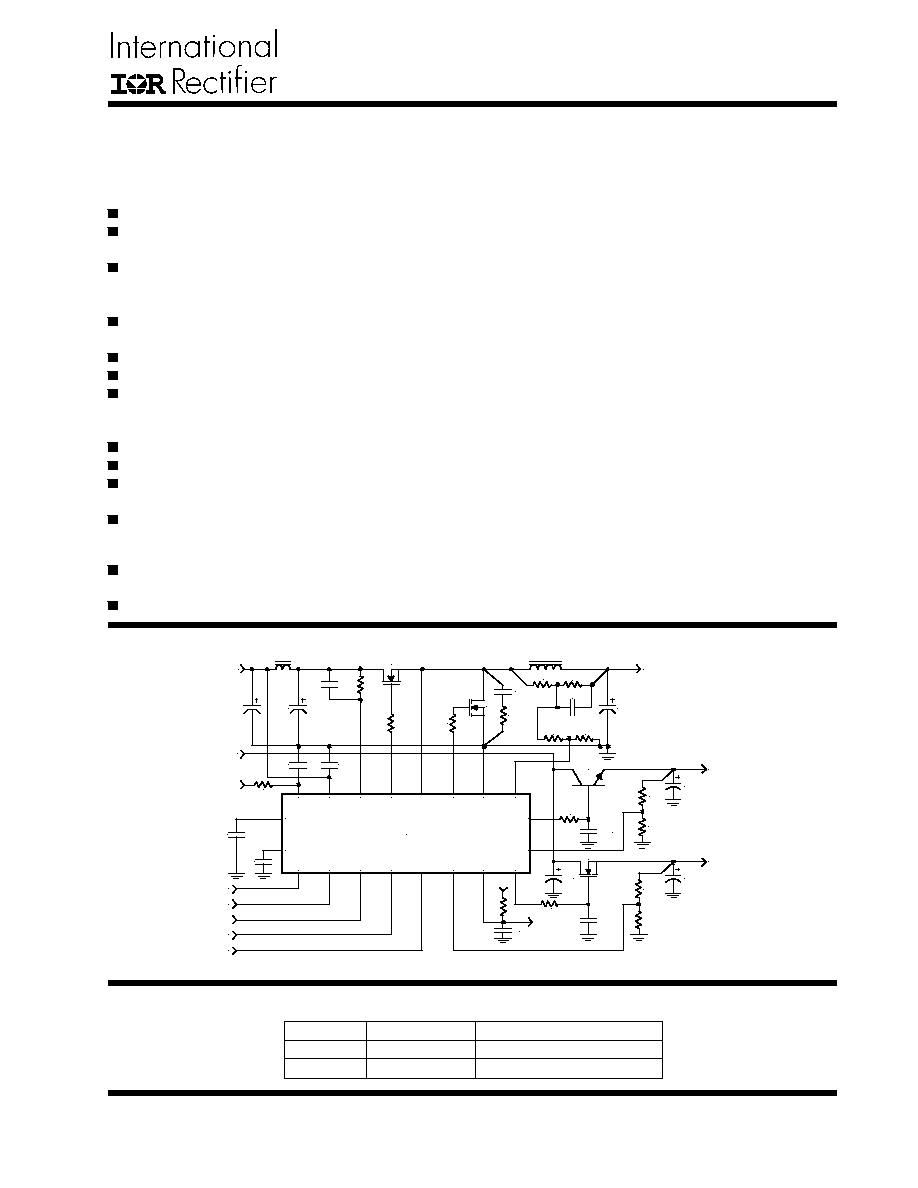

PACKAGE ORDER INFORMATION

FEATURES

5-BIT PROGRAMMABLE SYNCHRONOUS BUCK

CONTROLLER IC WITH DUAL LDO CONTROLLER

APPLICATIONS

Pentium III & next generation processor DC to DC

converter application

Low Cost Pentium with AGP

T

A

(

8

C)

DEVICE PACKAGE

0 To 70 IRU3004CW 20-Pin Plastic SOIC (W)

0 To 70 IRU3004CF 20-Pin Plastic TSSOP (F)

Note: Pentium III is trademark of Intel Corp.

Data Sheet No. PD94140

Figure 1 - Typical application of the IRU3004.

V

OUT

3

5V

12V

VID0

V

OUT

2

V

OUT

1

3.3V

Q2

C9

Q4

VID1

VID2

VID3

VID4

L1

L2

C5

R1

C3

C4

C6

Q1

R2

R3

C7

R4

C10

Q3

R7

R8

C11

C12

C1

C2

C13

R9

R11

C15

C14

R12

R14

R15

Power Good

R5

C8

3.3V

R16

R17

R13

C16

R18

HDrv

LDrv

Ct

SS

CS+

Gnd

V

FB3

D3

D2

D4

D1

D0

PGd

IRU3004

Lin1

V

FB1

CS-

V12

V5

V

FB2

Lin2

2

Rev. 1.7

07/16/02

IRU3004

www.irf.com

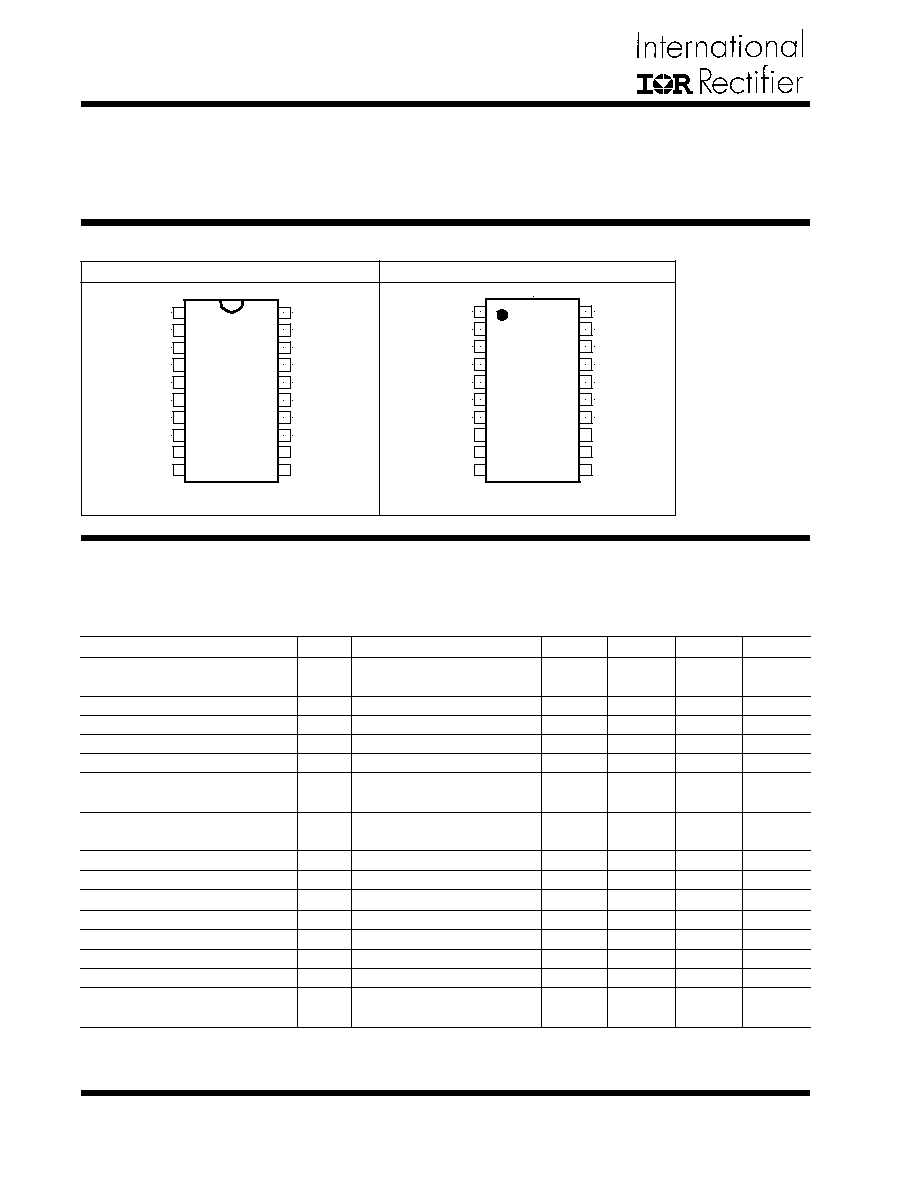

ELECTRICAL SPECIFICATIONS

Unless otherwise specified, these specifications apply over V12=12V, V5=5V and T

A

=0 to 70°C. Typical values refer

to T

A

=25°C. Low duty cycle pulse testing is used which keeps junction and case temperatures equal to the ambient

temperature.

ABSOLUTE MAXIMUM RATINGS

V5 Supply Voltage .................................................... 10V

V12 Supply Voltage .................................................. 20V

Storage Temperature Range ...................................... -65°C To 150°C

Operating Junction Temperature Range ..................... 0°C To 125°C

PACKAGE INFORMATION

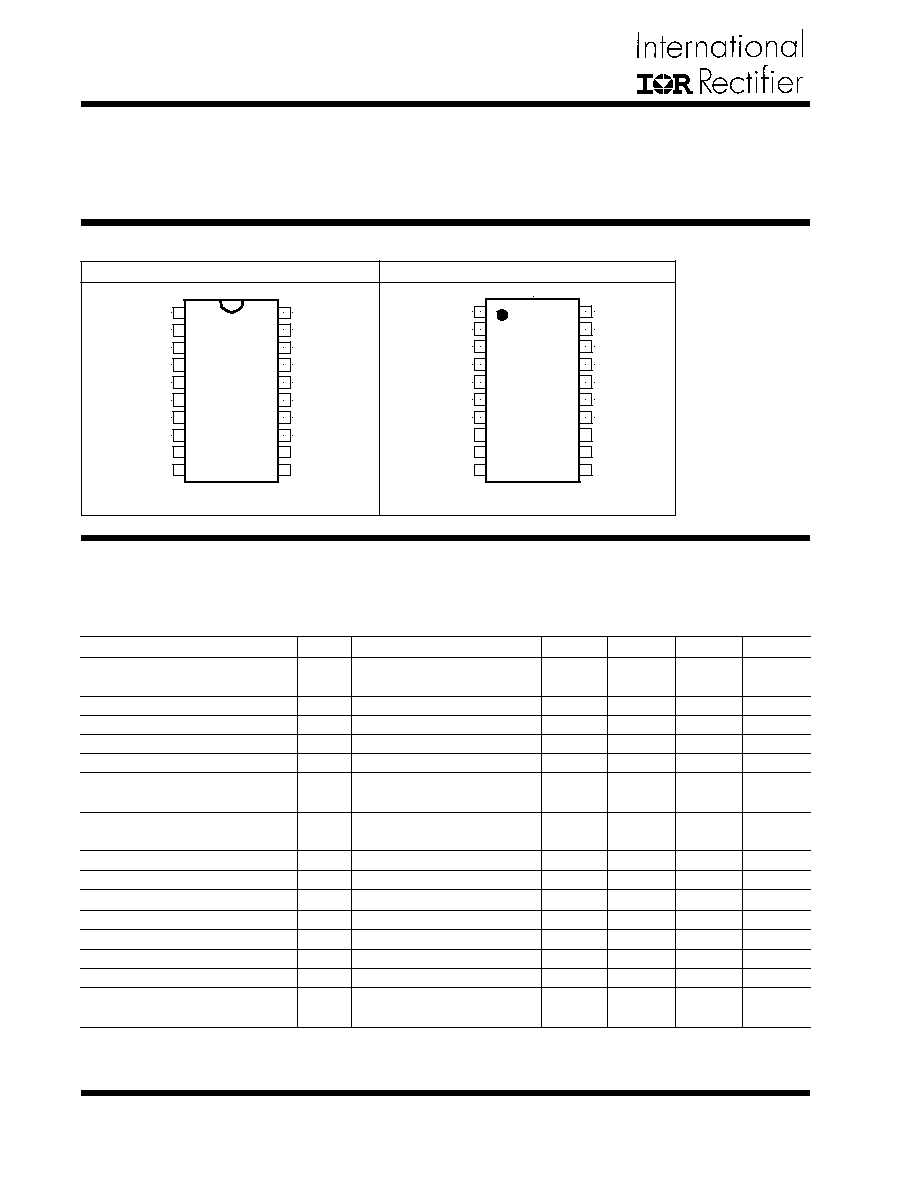

20-PIN WIDE BODY PLASTIC SOIC (W)

20-PIN PLASTIC TSSOP (F)

VID Section

DAC Output Voltage (Note 1)

DAC Output Line Regulation

DAC Output Temp Variation

VID Input LO

VID Input HI

VID Input Internal Pull-Up

Resistor to V5

Power Good Section

Under-Voltage lower trip point

Under-Voltage upper trip point

UV Hysteresis

Over-Voltage upper trip point

Over-Voltage lower trip point

OV Hysteresis

Power Good Output LO

Power Good Output HI

Soft-Start Section

Soft-Start Current

u

JA

=85

8

C/W

Lin2

D 0

D 1

D 2

D 3

D 4

V

FB3

SS

V12

LDrv

C t

Lin1

V

FB1

V

FB2

V5

PGd

CS-

CS+

HDrv

Gnd

4

3

2

1

7

6

5

18

19

20

TOP VIEW

11

13

12

14

10

15

9

16

8

17

Lin2

D 0

D 1

D 2

D 3

D 4

V

FB3

SS

V12

LDrv

C t

Lin1

V

FB1

V

FB2

V5

PGd

CS-

CS+

HDrv

Gnd

4

3

2

1

7

6

5

18

19

20

TOP VIEW

11

13

12

14

10

15

9

16

8

17

u

JA

=90

8

C/W

PARAMETER

SYM TEST CONDITION MIN TYP MAX UNITS

V

OUT

Ramping Down

V

OUT

Ramping Up

V

OUT

Ramping Up

V

OUT

Ramping Down

R

L

=3mA

R

L

=5K Pull-Up to 5V

CS+=0V, CS-=5V

0.98Vs

2

0.89Vs

0.015Vs

1.09Vs

0.015Vs

4.8

Vs

27

0.90Vs

0.92Vs

0.02Vs

1.10Vs

1.08Vs

0.02Vs

10

1.02Vs

0.1

0.5

0.4

0.91Vs

0.025Vs

1.11Vs

0.025Vs

0.4

V

%

%

V

V

K

V

V

V

V

V

V

V

V

V

m

A

IRU3004

3

Rev. 1.7

07/16/02

www.irf.com

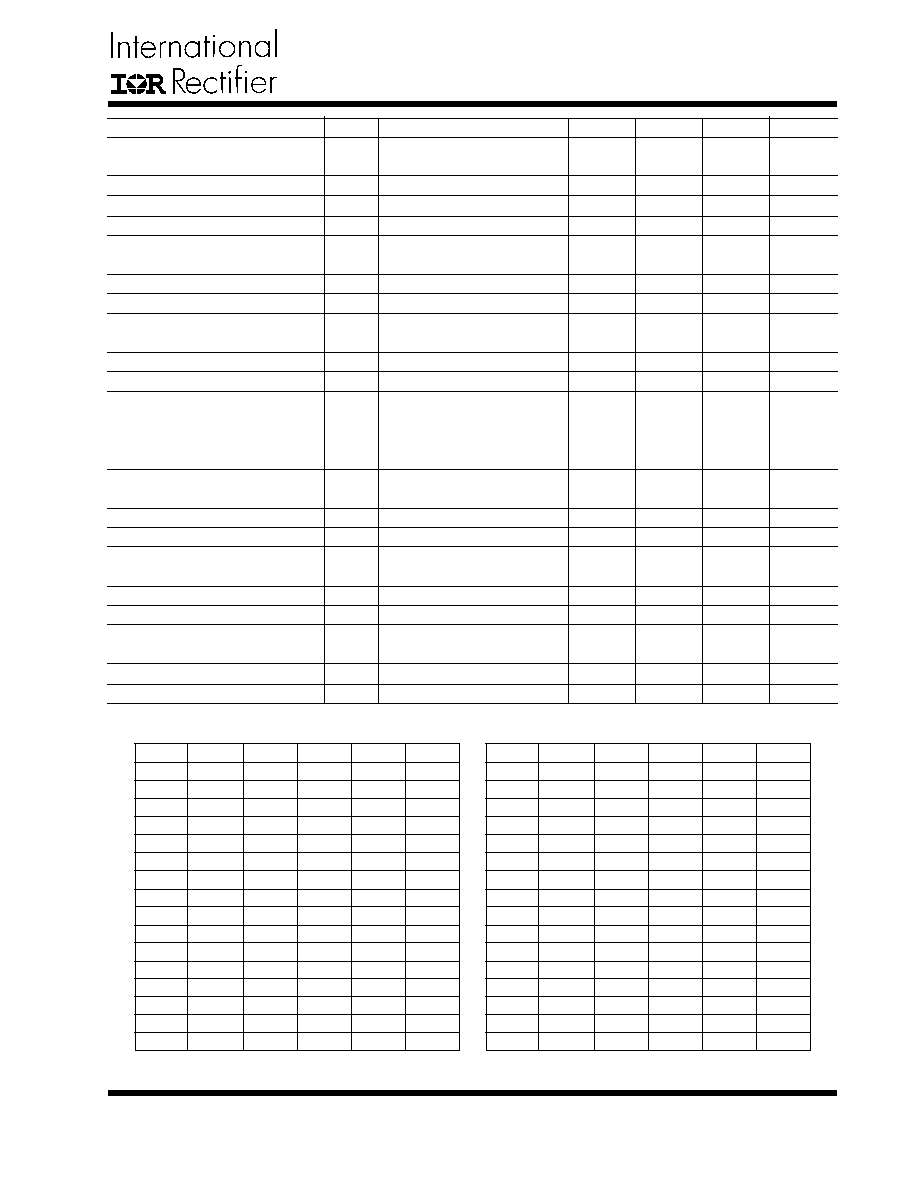

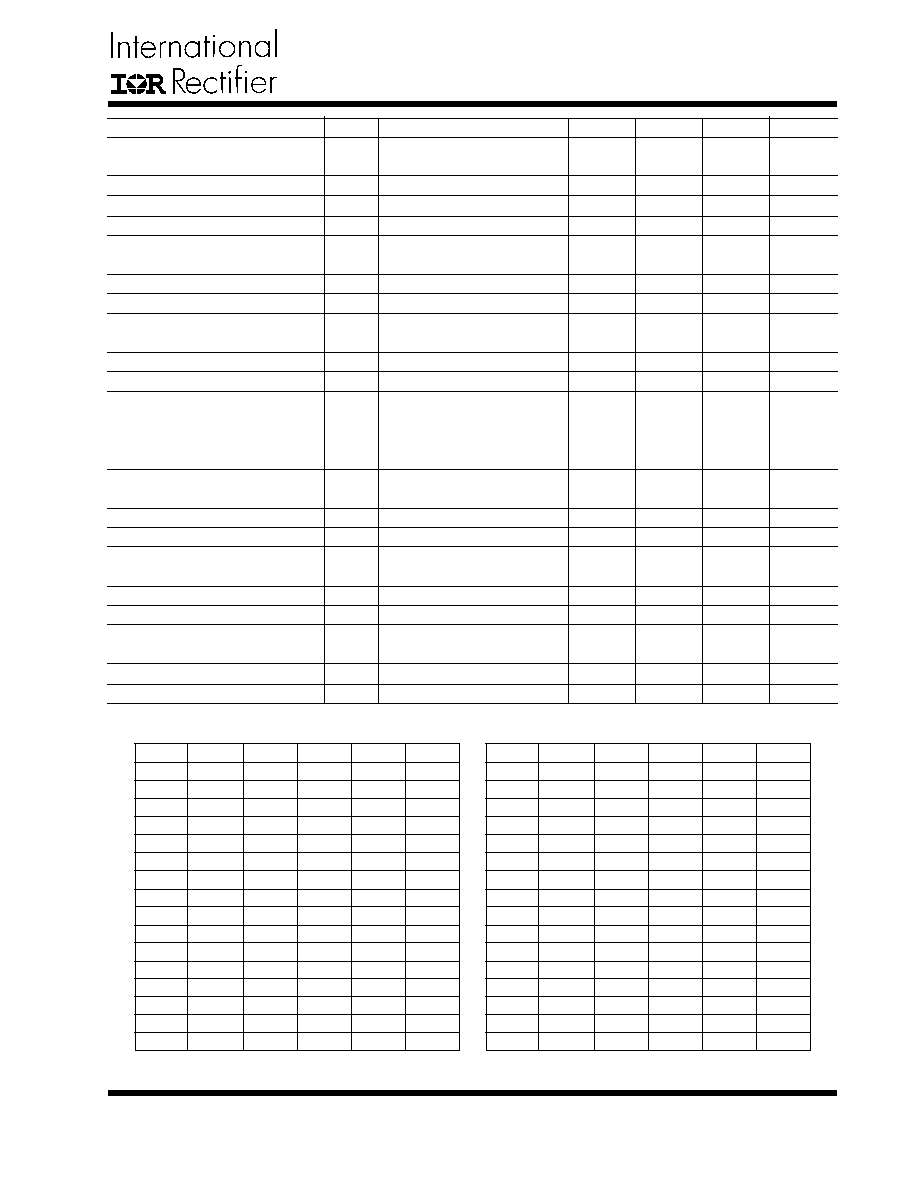

D4

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

D3

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

D2

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

D1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

D0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

Vs

1.30

1.35

1.40

1.45

1.50

1.55

1.60

1.65

1.70

1.75

1.80

1.85

1.90

1.95

2.00

2.05

D4

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

D3

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

D2

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

D1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

D0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

Vs

2.0

2.1

2.2

2.3

2.4

2.5

2.6

2.7

2.8

2.9

3.0

3.1

3.2

3.3

3.4

3.5

Table 1 - Set point voltage vs. VID codes.

UVLO Section

UVLO Threshold-12V

UVLO Hysteresis-12V

UVLO Threshold-5V

UVLO Hysteresis-5V

Error Comparator Section

Input Bias Current

Input Offset Voltage

Delay to Output

Current Limit Section

CS Threshold Set Current

CS Comp Offset Voltage

Hiccup Duty Cycle

Supply Current

Operating Supply Current

Output Drivers Section

Rise Time

Fall Time

Dead Band Time

Oscillator Section

Osc Frequency

Osc Valley

Osc Peak

LDO Controller Section

V

FB1

& V

FB2

Input Bias Current

Lin1 or Lin2 Drive Current

PARAMETER

SYM TEST CONDITION MIN TYP MAX UNITS

Supply Ramping Up

Supply Ramping Up

V

DIFF

=10mV

Css=0.1

m

F

C

L

=3000pF:

V5

V12

C

L

=3000pF

C

L

=3000pF

C

L

=3000pF

Ct=150pF

9.2

0.3

4.1

0.2

-2

160

-5

100

160

1.455

10

0.4

4.3

0.3

200

20

14

70

70

200

220

V5

1.500

50

10.8

0.5

4.5

0.4

2

+2

100

240

+5

2

100

130

300

260

0.2

1.545

2

V

V

V

V

m

A

mV

ns

m

A

mV

%

mA

ns

ns

ns

KHz

V

V

V

m

A

mA

Note 1: Vs refers to the set point voltage given in Table 1.

4

Rev. 1.7

07/16/02

IRU3004

www.irf.com

PIN DESCRIPTIONS

This pin programs the oscillator frequency in the range of 50KHz to 500KHz with an

external capacitor connected from this pin to the ground.

This pin controls the gate of an external transistor for either the GTL+ linear regulator or

Clock supply.

This pin provides the feedback for the linear regulator that its output drive is Lin1 pin.

This pin provides the feedback for the linear regulator that its output drive is Lin2 pin.

5V supply voltage.

This pin is an open collector output that switches LO when the output of the converter is

not within

±

10% (typical) of the nominal output voltage. When Power Good pin switches

LO the sat voltage is less than 0.4V at 3mA.

This pin is connected to the Source of the power MOSFET for the Core supply and it

provides the negative sensing for the internal current sensing circuitry.

This pin is connected to the Drain of the power MOSFET of the Core supply and it

provides the positive sensing for the internal current sensing circuitry. An external resis-

tor programs the CS threshold depending on the R

DS

of the power MOSFET. An external

capacitor is placed in parallel with the programming resistor to provide high frequency

noise filtering.

Output driver for the high-side power MOSFET.

This pin serves as the ground pin and must be connected directly to the ground plane. A

high frequency capacitor (0.1 to 1

m

F) must be connected from V5 and V12 pins to this

pin for noise free operation.

Output driver for the synchronous power MOSFET.

This pin is connected to the 12 V supply and serves as the power Vcc pin for the output

drivers. A high frequency capacitor (0.1 to 1

m

F) must be connected directly from this pin

to ground pin in order to supply the peak current to the power MOSFET duringthe transi-

tions.

This pin provides the soft-start for the switching regulator. An internal current source

charges an external capacitor that is connected from this pin to the ground which ramps

up the outputs of the switching regulator, preventing the outputs from overshooting as

well as limiting the input current. The second function of the Soft-Start cap is to provide

long off time (HICCUP) for the synchronous MOSFET during current limiting.

This pin is connected directly to the output of the Core supply to provide feedback to the

Error comparator.

This pin selects a range of output voltages for the DAC. When in the LOW state the

range is 1.3V to 2.05V. For VID codes of all "1" the IRU3004 keeps all the outputs on.

MSB input to the DAC that programs the output voltage. This pin can be pulled-up exter-

nally by a 10K resistor to either 3.3V or 5V supply.

Input to the DAC that programs the output voltage. This pin can be pulled up externally

by a 10K resistor to either 3.3V or 5V supply.

Input to the DAC that programs the output voltage. This pin can be pulled up externally

by a 10K

V

resistor to either 3.3V or 5V supply.

LSB input to the DAC that programs the output voltage. This pin can be pulled-up exter-

nally by a 10K resistor to either 3.3V or 5V supply.

This pin controls the gate of an external transistor for either the GTL+ linear regulator or

Clock supply.

PIN# PIN SYMBOL

PIN DESCRIPTION

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

Ct

Lin1

V

FB1

V

FB2

V5

PGd

CS-

CS+

HDrv

Gnd

LDrv

V12

SS

V

FB3

D4

D3

D2

D1

D0

Lin2

IRU3004

5

Rev. 1.7

07/16/02

www.irf.com

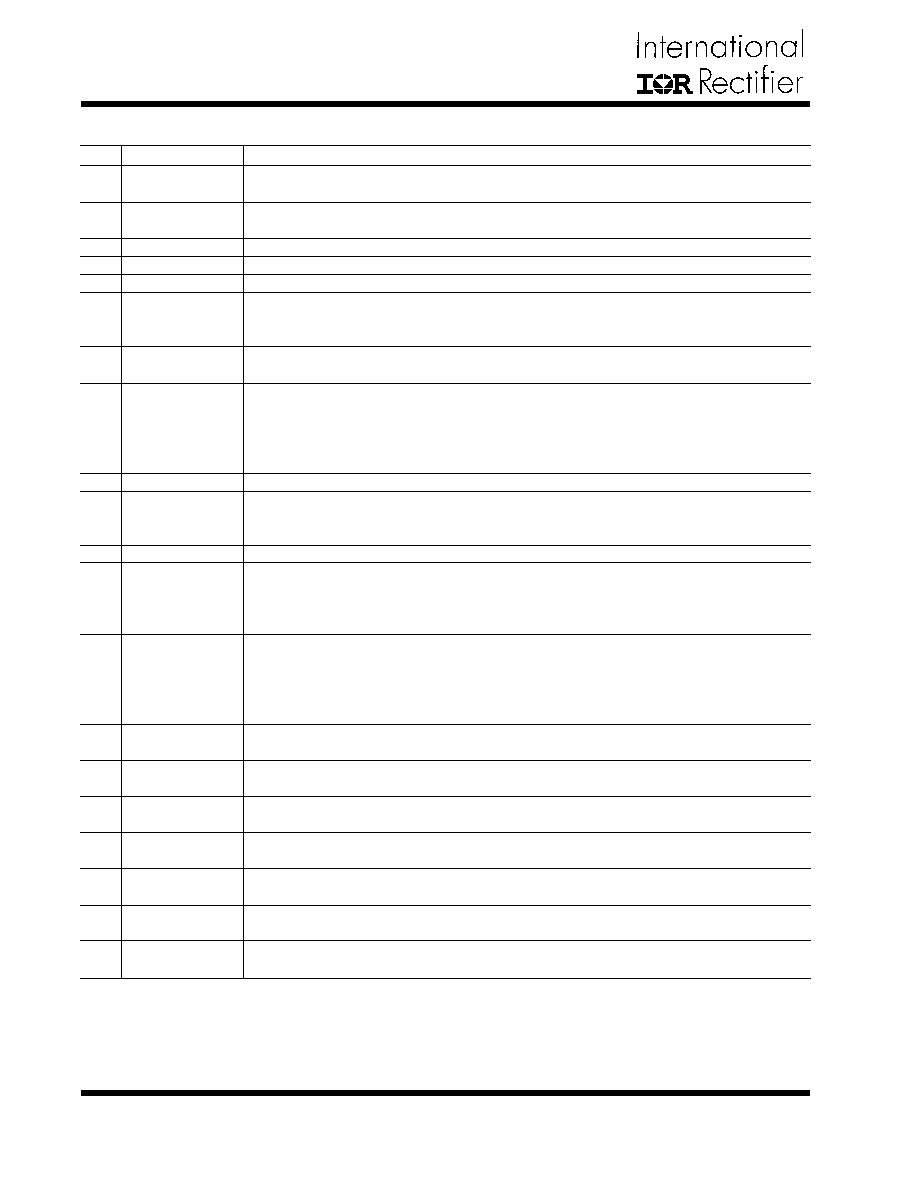

BLOCK DIAGRAM

Figure 2 - Simplified block diagram of the IRU3004.

PWM

Control

V12

V12

Osc

Slope

Comp

+

1.5V

5Bit

DAC,

Ctrl

Logic

Enable

Soft

Start &

Fault

Logic

200uA

0.9Vset

1.1Vset

Vset

Enable

UVLO

Vset

Enable

V

FB1

Lin1

Lin2

V

FB2

D4

V5

V12

SS

Gnd

PGd

CS-

Ct

CS+

LDrv

HDrv

V

FB3

D3

D2

D1

D0

Over

Current

Enable

12

5

19

18

17

16

15

4

20

2

3

14

9

11

7

8

1

13

6

10